# Modules intégrés en technologie LTCC pour des applications en bande D (110 - 170 GHz)

Malika Tlili

#### ▶ To cite this version:

Malika Tlili. Modules intégrés en technologie LTCC pour des applications en bande D (110 - 170 GHz). Electronique. Ecole nationale supérieure Mines-Télécom Atlantique, 2020. Français. NNT: 2020 IMTA 0165. tel-02538427

## HAL Id: tel-02538427 https://theses.hal.science/tel-02538427v1

Submitted on 9 Apr 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESE DE DOCTORAT DE

L'ÉCOLE NATIONALE SUPERIEURE MINES-TELECOM ATLANTIQUE BRETAGNE PAYS DE LA LOIRE - IMT ATLANTIQUE

ECOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies

de l'Information et de la Communication

Spécialité: Génie électrique

Par

Malika TLILI

Modules intégrés en technologie LTCC pour des applications en bande D (110-170 GHz)

Thèse présentée et soutenue à Brest , le 22 janvier 2020

Unité de recherche : Laboratoire Lab-STICC

Thèse N°: 2020IMTA0165

#### Rapporteurs avant soutenance :

Philippe Ferrari Professeur à l'Université de Grenoble

Stéphane Bila Directeur de recherche au CNRS, XLIM Limoges

#### Composition du Jury :

Président : Philippe Ferrari Professeur à l'Université de Grenoble

Examinateurs : Stéphane Bila Directeur de recherche au CNRS, XLIM Limoges

Anne-Laure Billabert Maître de conférences HDR à ESYCOM/ Le Cnam

Camilla Kärnfelt Ingénieur d'études à IMT Atlantique

Dir. de thèse : Alain Peden Professeur à IMT Atlantique

Invité(s)

Daniel Bourreau Maître de conférences à IMT Atlantique

## Remerciements

La réalisation de cette thèse a été possible grâce au concours de plusieurs personnes à qui je voudrais témoigner toute ma gratitude.

Je voudrais tout d'abord adresser toute ma reconnaissance à Madame Camilla KÄRNFELT qui m'a encadrée, pour sa patience, sa disponibilité et surtout ses judicieux conseils qui ont contribué à alimenter ma réflexion ainsi que sa confiance et son soutien inestimable. Je tiens à exprimer ma reconnaissance aussi à mon directeur de thèse Professeur Alain PEDEN de m'avoir encadrée, orientée, aidée et conseillée et pour avoir eu la patience de répondre à mes innombrables questions. Un grand merci également à mon encadrant Monsieur Daniel BOURREAU qui m'a fourni les outils nécessaires à la réussite des mesures effectuées tout au long de ma thèse.

J'adresse mes plus vifs remerciements à Monsieur Philippe FERRARI professeur à l'Université de Grenoble président et rapporteur du jury, à Monsieur Stéphane BILA directeur de recherche au CNRS, XLIM Limoges rapporteur et à Madame Anne-Laure BILLABERT maître de conférences HDR à ESYCOM le Cnam examinateur, de l'intérêt qu'ils ont porté à ce travail en prenant part au jury et en me permettant de soutenir cette thèse.

Je tiens à témoigner toute ma gratitude à Pascal COANT, technicien de laboratoire qui m'a appris les étapes de fabrication du substrat LTCC ainsi que l'utilisation des différentes machines nécessaires. J'aimerais exprimer ma gratitude également à Maïna SINOU ingénieure de recherche et développement, pour sa contribution dans plusieurs tests et expériences effectués. Un grand merci à Jérémie HEMERY, ingénieur de recherche et développement pour son aide et sa patience lors de la préparation des différents bancs de mesure nécessaires à la caractérisation des différents prototypes élaborés.

J'aimerais exprimer ma gratitude à l'entreprise GOTMIC qui nous a fourni les puces MMIC ainsi que leur aide pour pouvoir effectuer la mesure thermique à l'université de Chalmers. Je remercie également les enseignants et chercheurs, trop nombreux pour les citer, qui ont pris le temps de discuter de mon sujet. Chacun de ces échanges m'a aidé à faire avancer mon analyse.

Je remercie également la direction scientifique de l'IMT Atlantique et le responsable du département Micro-onde Patrice PAJUSCO pour leur facilitation des différentes procédures administratives tout au long des 3 années de thèse.

Un grand merci à mes amis à l'IMT Atlantique, Emna BELKAMEL, Ankit JEAN et Oumaima MHADHBI pour leur support moral et leurs encouragements.

Finalement, je remercie mes parents, mon frère Chokri et mon mari Ahmed d'être toujours là pour me pousser en avant, m'encourager et me donner de la confiance en moi.

# **Table des matières**

| Table des ill    | ustrations                                              | 6   |

|------------------|---------------------------------------------------------|-----|

| Liste des tab    | oleaux                                                  | 11  |

| Liste d'abré     | viations et sigles                                      | 12  |

|                  | ıboles                                                  |     |

| Constantes p     | physiques                                               | 16  |

| Contexte de      | thèse                                                   | 17  |

| I. État de       | l'art de la mise en boitier des puces MMIC              | 21  |

| I.1 In           | troduction                                              | 22  |

| I.2 La           | n mise en boitier                                       | 23  |

| I.2.1            | Définition                                              | 23  |

| I.2.2            | Mise en boitier pour des applications hautes fréquences | 23  |

| I.2.2            |                                                         |     |

| I.2.2            | .2 Boitier QFN                                          | 25  |

| I.2.2            | .3 Boitier SIP                                          | 26  |

| I.2.2            | .4 Boitier CSP                                          | 27  |

| I.2.2            | .5 Boitier SOP                                          | 28  |

| I.2.2            |                                                         |     |

| I.2.2            |                                                         |     |

| I.3 La           | technologie LTCC                                        |     |

|                  | Définition                                              |     |

|                  | Les tapes LTCC                                          |     |

|                  | Étapes de fabrication des circuits en technologie LTCC  |     |

| I.3.3            |                                                         |     |

| I.3.3            | 1 1                                                     |     |

| I.3.3            |                                                         |     |

|                  | echniques d'interconnexions                             |     |

|                  | Micro-câblage                                           |     |

| I.4.1            | C                                                       |     |

| I.4.1<br>I.4.1   | e                                                       |     |

| I.4.1<br>I.4.1   |                                                         |     |

|                  | Flip-chip                                               |     |

|                  | onclusion                                               |     |

|                  | de puces MMIC sur substrat LTCC                         |     |

|                  | troduction                                              |     |

|                  | eport et interconnexion de puces MMIC sur substrat LTCC |     |

| II.2 Ke          | <u>.</u>                                                |     |

| II.2.1<br>II.2.1 | Report et interconnexion de puces MMIC coplanaires      |     |

| II.2.1<br>II.2.1 | $\mathcal{S}$                                           |     |

|                  | r                                                       |     |

| II.2.1           |                                                         |     |

| II.2.2           | Report et interconnexion des puces MMIC microruban      |     |

| II.2.2           | - 6 · · · · · · · · · · · · · · · · · ·                 |     |

| II.2.2           |                                                         |     |

| II.2.2           | 1                                                       |     |

| II.2.2           |                                                         |     |

| II.3 Co          | onclusion                                               | O.D |

| III. Solutions de refroidissement                                          | 86  |

|----------------------------------------------------------------------------|-----|

| III.1 Introduction                                                         | 87  |

| III.2 Problème de dissipation de chaleur dans l'amplificateur de puissance | 88  |

| III.3 Solutions de refroidissement                                         | 89  |

| III.3.1 Solutions actives                                                  | 89  |

| III.3.2 Solutions passives                                                 | 90  |

| III.4 Solutions proposées                                                  | 93  |

| III.4.1 Problème à résoudre                                                | 93  |

| III.4.2 Solutions                                                          | 95  |

| III.4.2.1 Micro-caloduc                                                    | 95  |

| III.4.2.2 Refroidissement par intégration du conducteur dans LTCC          | 118 |

| III.5 Conclusion                                                           |     |

| IV. Module intégré en LTCC                                                 | 128 |

| IV.1 Introduction                                                          | 129 |

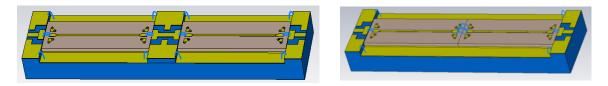

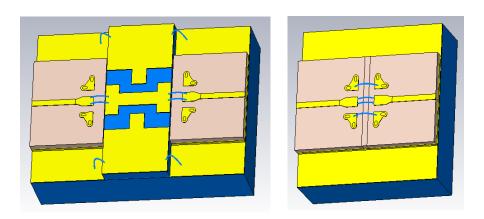

| IV.2 Les puces actives de Gotmic                                           |     |

| IV.3 Report sur le substrat LTCC                                           |     |

| IV.3.1 Montage du multiplieur sur le LTCC                                  |     |

| IV.3.2 Montage du multiplieur + mélangeur sur le LTCC                      | 137 |

| IV.3.2.1 Montage par micro-câblage                                         | 137 |

| IV.3.2.2 Montage par flip-chip                                             |     |

| IV.3.2.3 Montage par micro-câblage et flip-chip                            | 141 |

| IV.3.3 Réalisation et mesure des modules                                   |     |

| IV.3.3.1 Réalisation des modules                                           | 144 |

| IV.3.3.2 Montages des puces et mesures                                     | 146 |

| IV.4 Conclusion                                                            | 158 |

| Conclusion générale                                                        | 159 |

| Perspectives                                                               | 162 |

| Bibliographie                                                              | 163 |

| Annexe 1 : Matériaux d'ESL                                                 |     |

| Annexe 2 : Règles de conception LTCC                                       |     |

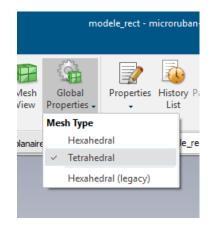

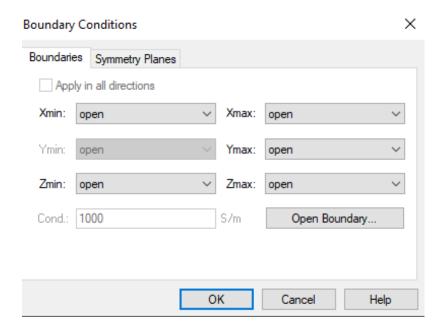

| Annexe 3 : Simulation électromagnétique sous CST                           |     |

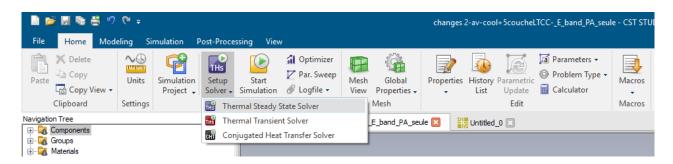

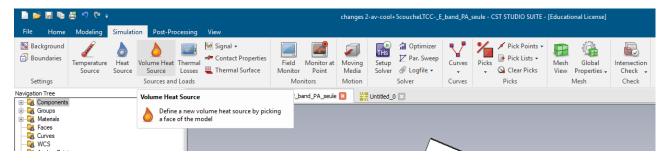

| Annexe 4 : Simulation thermique sous CST                                   |     |

| Annexe 5 : Equations pour le micro-caloduc                                 | 184 |

# **Table des illustrations**

| Figure 1. Puce de l'émetteur-récepteur (à gauche) et le boitier BGA (à droite) ; vue de dessus (en haut) et vu                                                      | ıe de                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| dessous (en bas) [4] © [2016]                                                                                                                                       | _ 24                   |

| Figure 2. Vue de dessous de le boitier (à gauche) et vue de dessus (à droite) [5] © [2014]                                                                          | 25                     |

| Figure 3. Boitier QFN conçu pour la bande E [8] © [2013]                                                                                                            | _ 26                   |

| Figure 4. Vue de dessus du SIP 122 GHz [10] © [2016]                                                                                                                | 26                     |

| Figure 5. Mise en boitier CSP [12] © [2011]                                                                                                                         | _ 27                   |

| Figure 6. Mise en boitier FC-CSP [13] © [2016]                                                                                                                      | _ 27                   |

| Figure 7. Technologie SOP [15] © [2005]                                                                                                                             | _ 28                   |

| Figure 8. Prototype du module LTCC encapsulé dans une structure métallique; à gauche vue en perspecti                                                               | ve, à                  |

| droite vue de côté [20] © [2014]                                                                                                                                    | 29                     |

| Figure 9. Prototype de module LTCC encapsulé dans un enclos métallique; à gauche vue en perspective, à d                                                            | roite                  |

| vue de côté [20] © [2014]                                                                                                                                           | 29                     |

| Figure 10. Prototype de module MCM-L de l'interface Antenne-MMIC [21] © [2013]                                                                                      | 30                     |

| Figure 11. Exemple de module MCM-D [22] © [2009]                                                                                                                    | <br>31                 |

| Figure 12. Photographies du module HTCC: à droite vue de dessus, à gauche vue de dessous [23] © [2012]                                                              | _<br>31                |

| Figure 13. Prototype de l'antenne patch [24] © [2016]                                                                                                               | 32                     |

| Figure 14. Substrat LTCC                                                                                                                                            | <br>33                 |

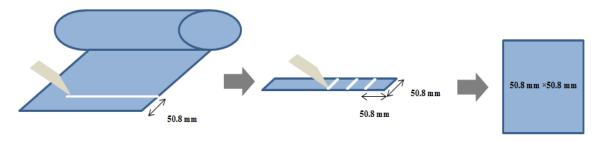

| Figure 15. Découpe des tapes LTCC                                                                                                                                   | 36                     |

| Figure 16. Indication de l'orientation des tapes                                                                                                                    | _ 36                   |

| Figure 17. Tapes tournés de 90° degrés                                                                                                                              | _ 36                   |

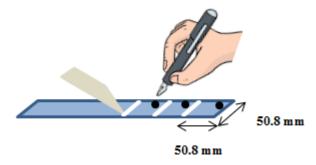

| Figure 18. Tape ESL41010 avec trous d'alignement et trous d'orientation                                                                                             | _ 37                   |

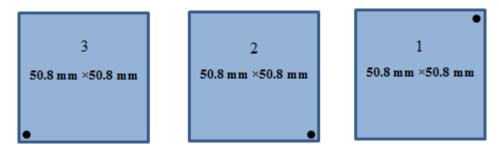

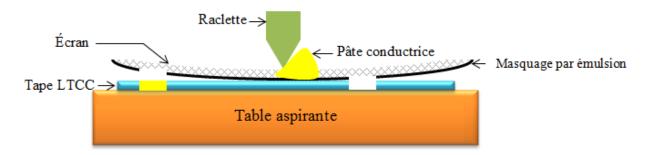

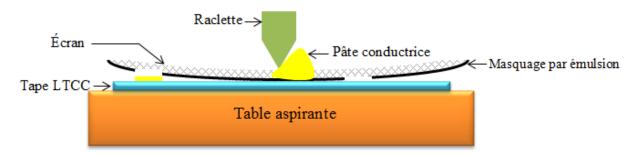

| Figure 19. Remplissage des vias par sérigraphie                                                                                                                     | _ 38                   |

| Figure 20. Sérigraphie de la pâte conductrice sur un tape LTCC                                                                                                      | _ 38                   |

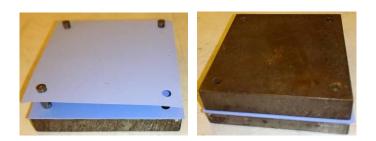

| Figure 21. Support d'empilement des couches LTCC utilisé au laboratoire                                                                                             | _ 39                   |

| Figure 22. Tapes empilés                                                                                                                                            | _ 39                   |

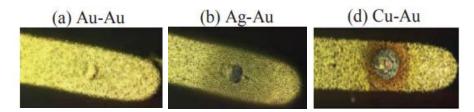

| Figure 23. Ball bonding avec liaison Au-Au, Ag-Au et Cu-Au [36] © [2015]                                                                                            | _ 33<br>42             |

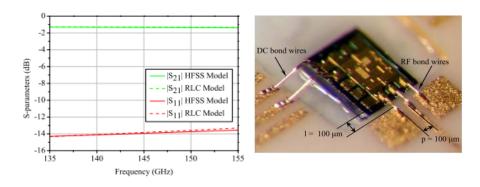

| Figure 24. Simulation sous HFSS (à gauche) micro câblage entre la puce MMIC et l'antenne [38] © [2015]                                                              | _                      |

| Figure 25. Capture écran de CAD (à gauche) et photo du module de l'amplificateur de puissance (à droite) [3                                                         |                        |

| [2014]                                                                                                                                                              | ی<br>43                |

| Figure 26. Cinq types de micro câblage [41] © [2014]                                                                                                                | _ 43<br>44             |

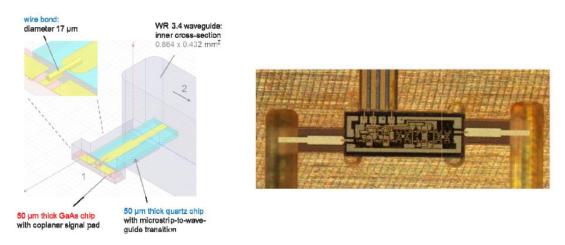

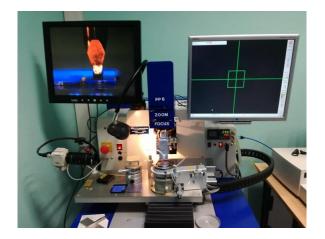

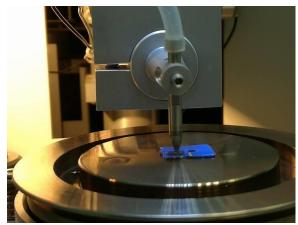

| Figure 27. Machine flip-chip disponible au laboratoire                                                                                                              | <br>46                 |

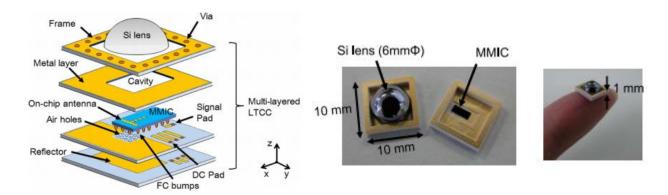

| Figure 28. Boitier LTCC avec le récepteur MMIC et l'antenne lentille [44] © [2016]                                                                                  |                        |

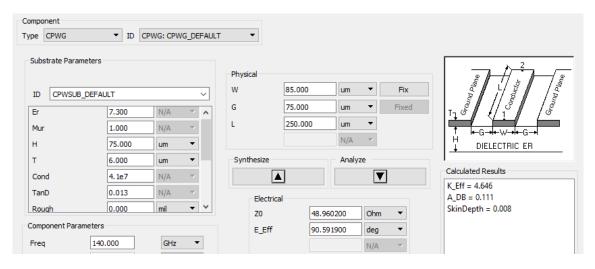

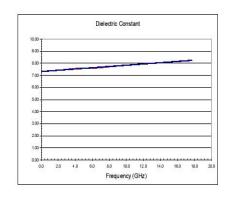

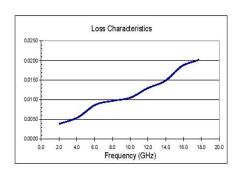

| Figure 29. Mesure et extraction des caractéristiques de l'ESL 41020 dans la bande D                                                                                 | _ <del>4</del> 0<br>51 |

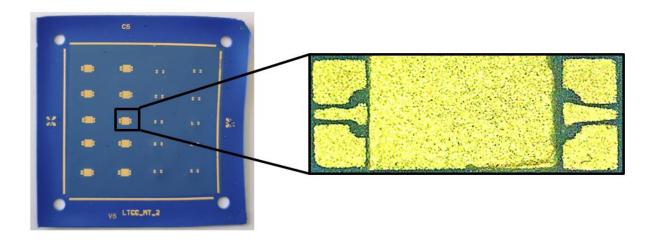

| Figure 30. Puce MMIC (L2) de deux lignes coplanaires                                                                                                                | _ 51<br>52             |

|                                                                                                                                                                     |                        |

| Figure 31. Support LTCC fabriqué pour le montage de la puce L2                                                                                                      | _ 53                   |

| Figure 32. Support LTCC après ablation avec le laser                                                                                                                | _ 53                   |

| Figure 33. Puce MMIC (L2) intégrée sur un substrat LTCC  Figure 34. Masure et simulation sous CST et ADS Mamontum des paramètres 5 de la ligne L3. 1 de la puse L3. | _ 54                   |

| Figure 34. Mesure et simulation sous CST et ADS Momentum des paramètres S de la ligne L2-1 de la puce L2 de l'intégration sous le substant LTCC                     |                        |

| l'intégration sur le substrat LTCC                                                                                                                                  | _ 54                   |

|                                                                                                                                                                     | -                      |

| l'intégration sur le substrat LTCC                                                                                                                                  | _ 55                   |

| Figure 36. Mesure des paramètres S de la ligne L2-1 de la puce L2 avant et après l'intégration sur le substrat                                                      |                        |

|                                                                                                                                                                     | _ 56                   |

| Figure 37. Montage de la puce sur LTCC: interconnexion avec lignes coplanaires prolongées (à gau                                                                    |                        |

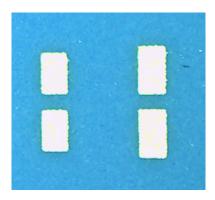

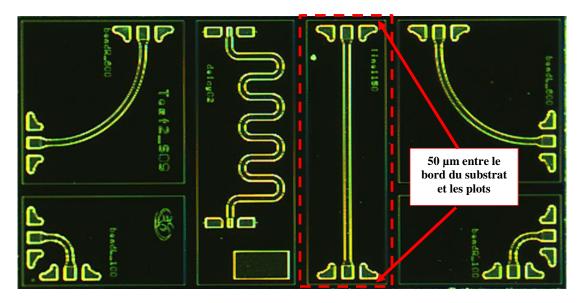

| Interconnexion avec des courtes lignes coplanaires (à droite)                                                                                                       | _ 56                   |

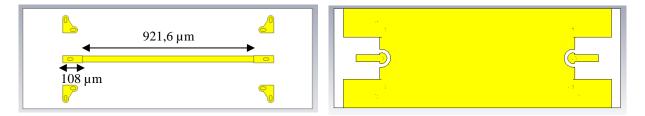

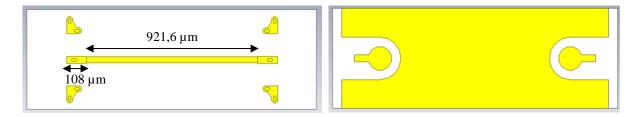

| Figure 38. Puce 1 d'une ligne microruban                                                                                                                            | _ 57                   |

| Figure 39. Layout de la face avant (gauche) et la face arrière (droite) de la puce                                                                                  |                        |

| Figure 40. Vue 3D (sous CST) de la puce (gauche) et de la métallisation de la puce (droite)                                                                         | _ 58                   |

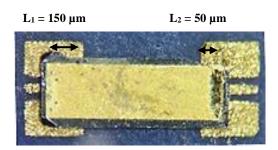

| Figure 41. Taille des plots en entrée et sortie de la puce                                                                                                          | _ 59                   |

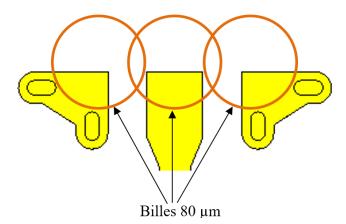

| Figure 42. Les billes de diamètre 80 μm placés sur les plots de la puce                                                                                             | _ 59                   |

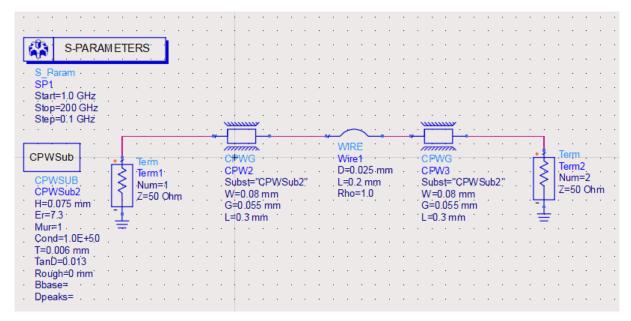

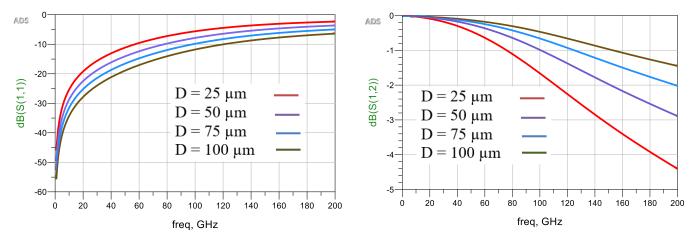

| Figure 43. Circuit de deux lignes coplangires interconnectées par micro-câblage                                                                                     | 60                     |

| Figure 44. Paramètres S simulés du circuit (figure 43) pour différentes valeurs de diamètre du micro-câblage_                               | 60         |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------|

|                                                                                                                                             | 61         |

| 3 3 (3 ) ( ) <u></u>                                                                                                                        | 61         |

| J J J                                                                                                                                       | 62         |

| Figure 48. Paramètres S simulés du circuit (figure 47) pour différentes valeurs de longueur du micro-câblage_                               |            |

|                                                                                                                                             | 63         |

| Figure 50. Courbes des paramètres S des montages de la figure 49 : montage de la puce sans (à gauche) et av                                 | <i>'ec</i> |

| ,                                                                                                                                           | 63         |

| g                                                                                                                                           | 64         |

| <u></u>                                                                                                                                     | 64         |

| 3 , i , <u>, , , , , , , , , , , , , , , , </u>                                                                                             | 65         |

| 3 1 1 3 <u></u>                                                                                                                             | 66         |

|                                                                                                                                             | 66         |

| g                                                                                                                                           | 67         |

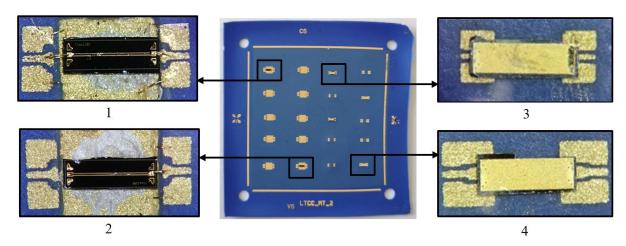

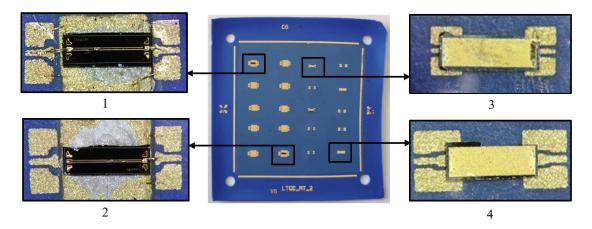

| Figure 57. Puces des lignes microruban montées sur le substrat LTCC : (1) puce montée par micro câblage                                     |            |

| entrée et sortie (2) puce montée par micro câblage en sortie seulement (3) puce montée par flip-chip premié                                 |            |

|                                                                                                                                             | 67         |

|                                                                                                                                             | ge<br>68   |

| Figure 59. Puces avec accès 35 $\Omega$ (gauche) et avec accès 50 $\Omega$ (droite)                                                         | 68         |

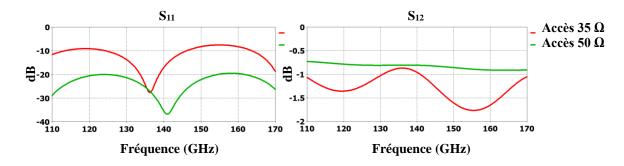

| Figure 60. Simulation des puces avec accès 35 $\Omega$ (courbe rouge) et avec accès 50 $\Omega$ (courbe verte)                              | 69         |

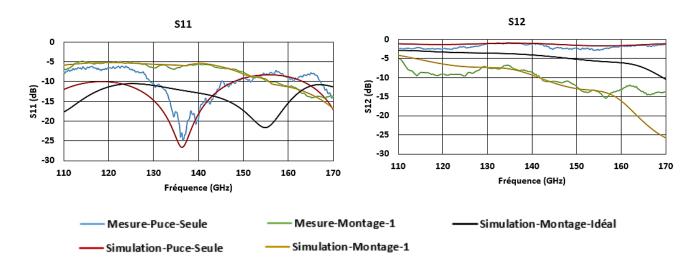

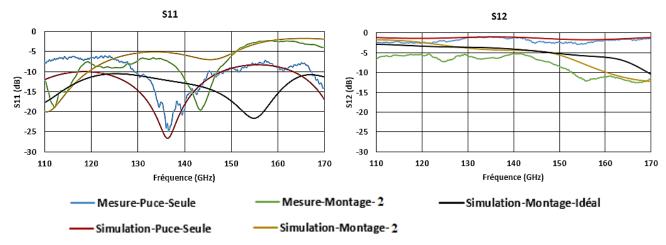

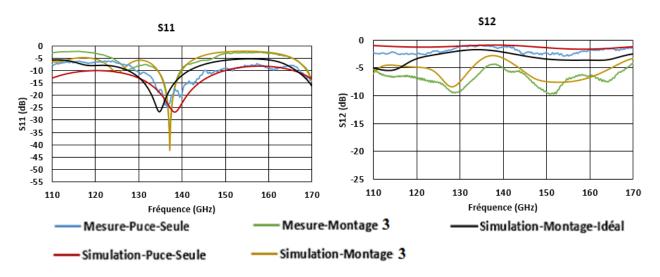

| Figure 61. Simulations et mesures de la puce « ligne microruban » seule, du montage 2 et simulation du monta idéal                          | ge<br>70   |

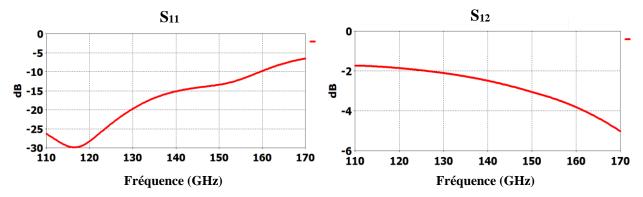

| Figure 62. Simulation de la puce avec accès 50 $\Omega$ montée sur le substrat LTCC par un micro-câblage de longue                          | 2ur        |

|                                                                                                                                             | 71         |

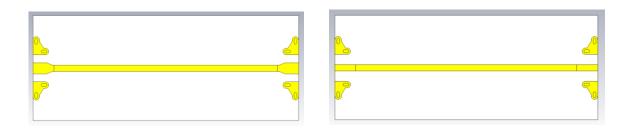

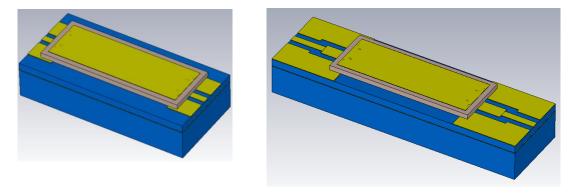

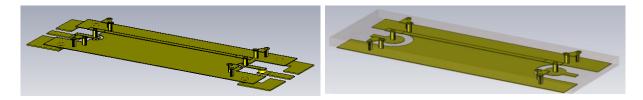

| Figure 63. Vue 3D des deux solutions proposées du montage par flip-chip                                                                     | 72         |

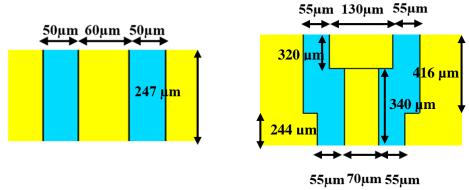

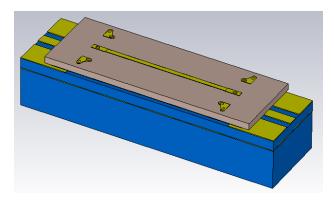

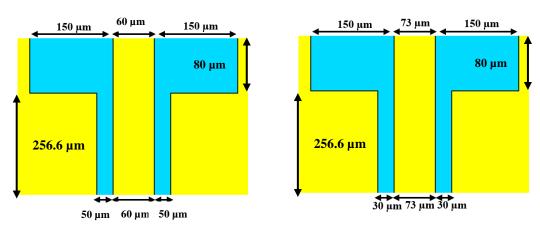

| Figure 64. Dimensions des plots sur le substrat LTCC pour les deux solutions proposées                                                      | 73         |

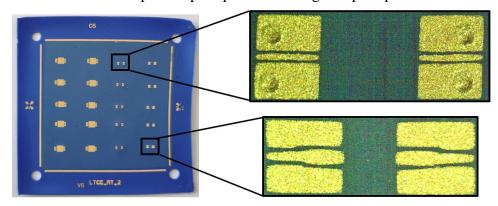

| Figure 65. Substrat LTCC pour le montage des puces des lignes microruban : plots montage 3 en haut à droite plots montage 4 en bas à droite | et<br>73   |

| Figure 66. Puces des lignes microruban montées sur le substrat LTCC : (1) puce montée par micro câblage                                     | _          |

| entrée et sortie (2) puce montée par micro câblage en sortie seulement (3) puce montée par flip-chip premié                                 |            |

|                                                                                                                                             | 73         |

|                                                                                                                                             | 74         |

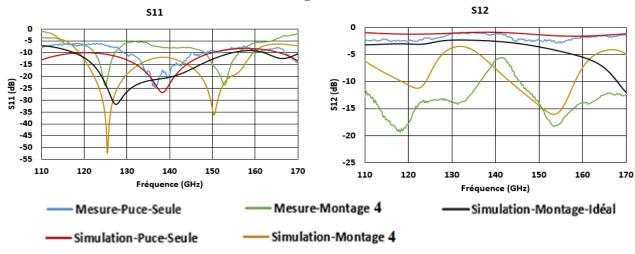

| Figure 68. Simulations et mesures de la puce « ligne microruban » seule, du montage 3 et simulation du monta                                | ge<br>74   |

| Figure 69. Simulations et mesures de la puce « ligne microruban » seule, du montage 4 et simulation du monta                                |            |

|                                                                                                                                             | , .<br>75  |

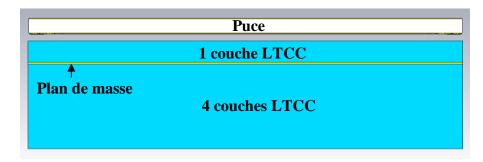

|                                                                                                                                             | 76         |

|                                                                                                                                             | 76         |

|                                                                                                                                             | 76         |

| Figure 74. Simulation du montage 3 avec différentes longueurs des accès coplanaires qui débordent sous la pu                                |            |

| Figure 75. Simulation de la puce avec accès 50 $\Omega$ montée sur le substrat LTCC par la première solution flip-cl                        |            |

| Figure 76. Simulation de la puce avec accès 50 $\Omega$ montée sur le substrat LTCC par la deuxième solution flip-cl                        |            |

|                                                                                                                                             | 80         |

|                                                                                                                                             | 80         |

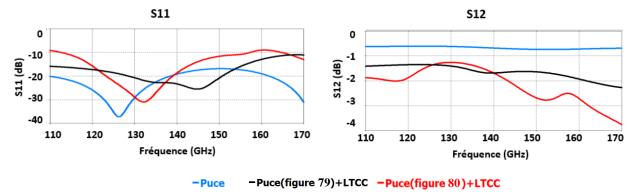

| Figure 79. Vue de dessus (gauche) et vue de dessous (droite) de la puce proposée sans respect des règles                                    |            |

|                                                                                                                                             | 81         |

| Figure 80. Vue de dessus (gauche) et vue de dessous (droite) de la puce proposée avec respect des règles                                    |            |

|                                                                                                                                             | 81         |

| Figure 81. Vue 3D de la partie métallique de la puce sans respect des règles de conception de « W                                           |            |

|                                                                                                                                             | 81         |

| Figure 82. Dimension des plots de la puce proposée : plots de face avant (gauche) plots de face arrière (droit                              |            |

|                                                                                                                                             | я<br>1     |

| Figure 83. Dimension des plots de la puce proposée : plots de face avant (gauche) plots de face arrière (droi                                                          | ite<br>82                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Figure 84. Intégration de puce sur LTCC                                                                                                                                | 82                       |

| Figure 85. Dimensions des plots sur LTCC pour puce figure 79 (gauche) et dimensions des plots sur LTCC pour put figure 80 (droite)                                     | исе<br>82                |

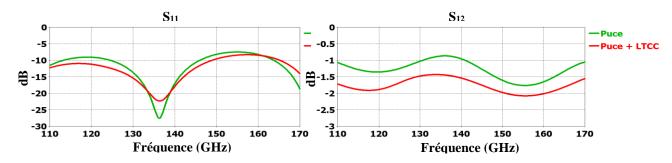

| Figure 86. Simulation de la puce proposée avant et après l'intégration sur le substrat LTCC                                                                            | 83                       |

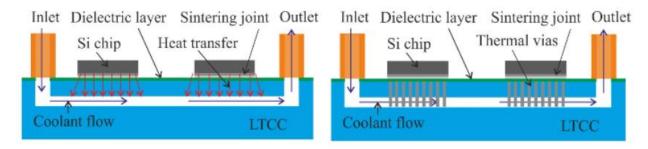

| Figure 87. Vue 3D de l'amplificateur placé sur des couches conductrices et des vias avec des micros canaux dessous de l'ensemble [62] © [2017]                         | au<br>89                 |

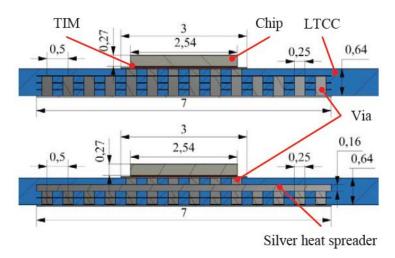

| Figure 88. Vue en coupe des deux solutions de refroidissement proposées en [63] © [2017]                                                                               | 90                       |

| Figure 89. Les vias conducteurs à travers le tape fugitif [63] © [2017]                                                                                                | 90                       |

| Figure 90. Vue en coupe des modèles réalisés : modèle avec vias (en haut), modèle avec dissipateur de chale (en bas) [64] © [2017]                                     | eu<br>91                 |

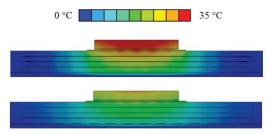

| Figure 91. Distribution de la température pour les deux modèles réalisés : modèle avec vias (en haut) et mod avec dissipateur de chaleur (en bas) [64] © [2017]        | lèle<br>91               |

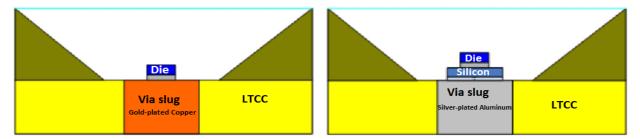

| Figure 92. Photo des deux solutions : bloc de cuivre plaqué or (à gauche) et bloc d'aluminium plaqué argent                                                            | t (d<br>92               |

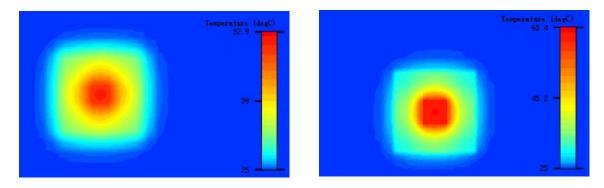

| Figure 93. Distribution de la température pour la solution avec bloc de cuivre plaqué or (à gauche) et avec b d'aluminium plaqué argent (à droite) [65] © [2012]       | loc<br>92                |

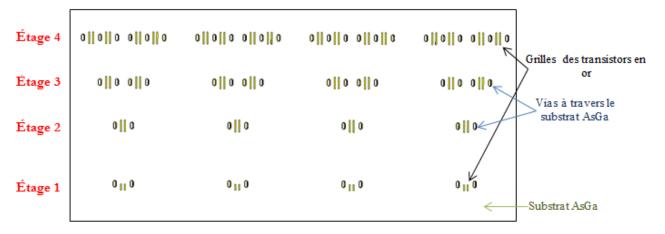

| Figure 94. Layout des grilles des transistors intégrés dans l'amplificateur de puissance                                                                               | 93                       |

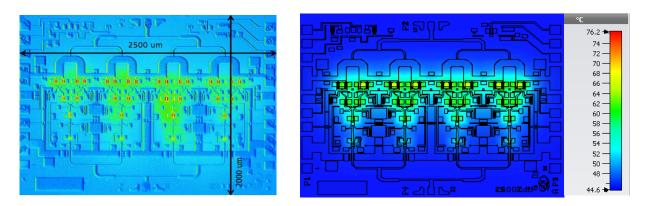

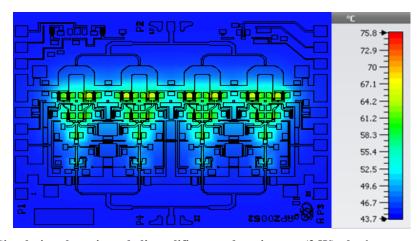

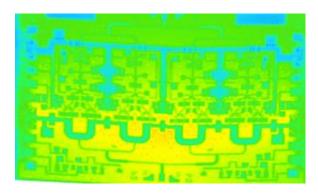

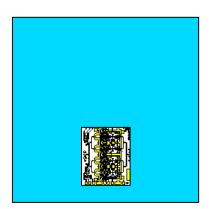

| Figure 95. Mesure (gauche) et simulation (droite) thermique de l'amplificateur de puissance placé sur un supp 45°C                                                     | ori<br>94                |

| Figure 96. Simulation thermique de l'amplificateur de puissance collé sur une couche de LTCC                                                                           | 94                       |

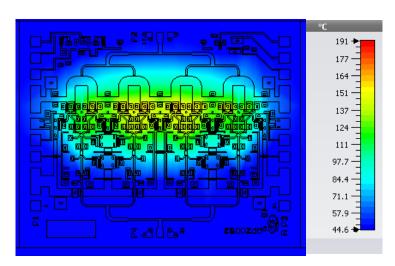

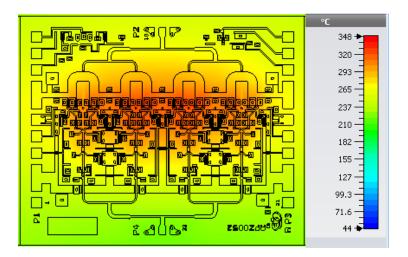

| Figure 97. Simulation thermique de l'amplificateur de puissance placé sur cinq couche de LTCC<br>Figure 98. Kit de démonstration de chez Thermacore Europe             | 95<br>96                 |

| Figure 99. Mesure du caloduc                                                                                                                                           | 96                       |

| Figure 100. Mesure de la barre en aluminium                                                                                                                            | 97                       |

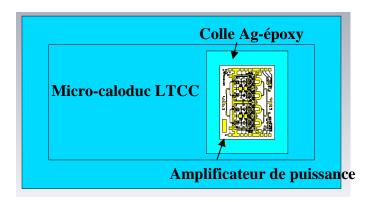

| Figure 101. Illustration de l'amplificateur de puissance collé sur le micro-caloduc                                                                                    | 98                       |

| Figure 102. Simulation thermique de l'amplificateur de puissance (3 W) placé sur un micro-caloduc qui évacue W                                                         | 1,5<br>98                |

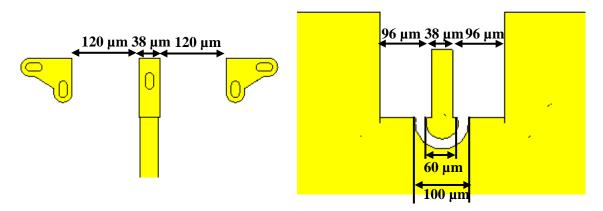

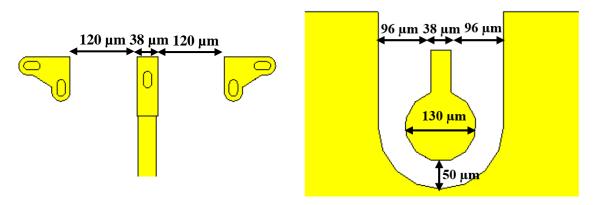

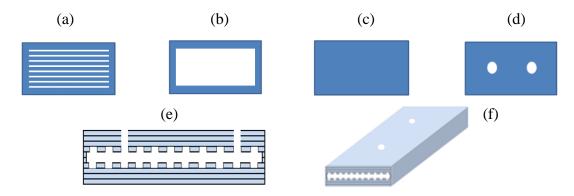

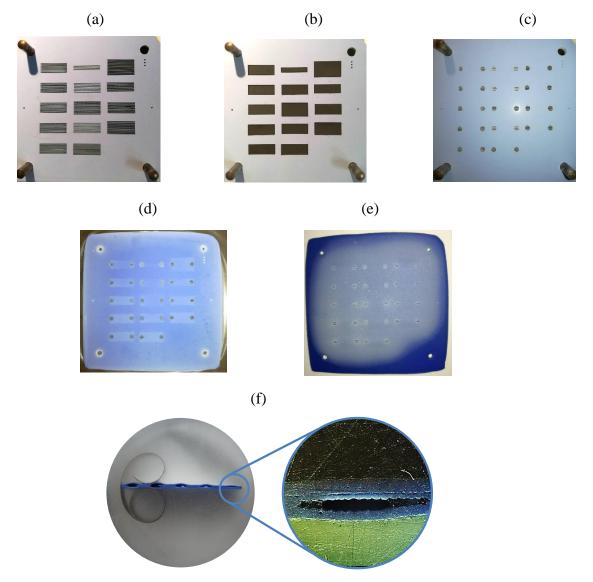

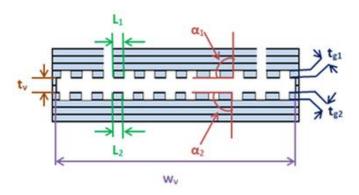

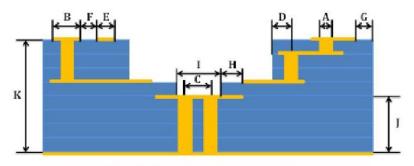

| Figure 103. (a) couches des rainures (b) couches de l'espace vapeur (c) couches au-dessous du micro-caloduc                                                            | (d                       |

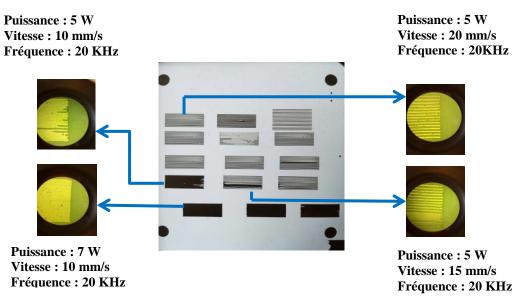

| couches au-dessus du micro-caloduc (e) vue en coupe du micro-caloduc (f) Structure du micro-caloduc<br>Figure 104. Tests effectués pour le paramétrage du laser        | 99                       |

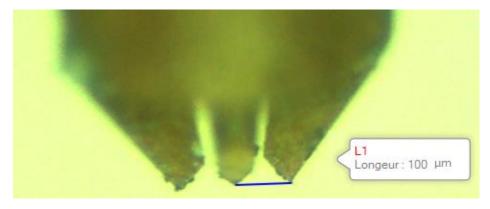

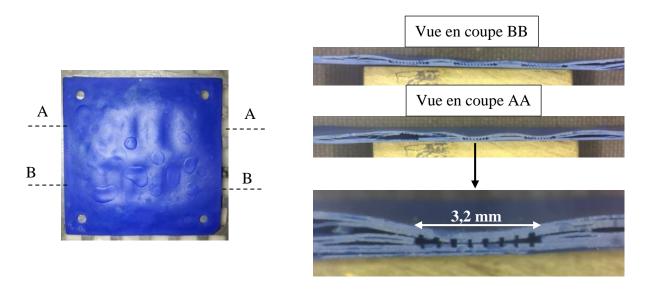

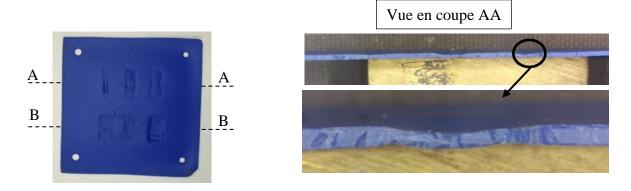

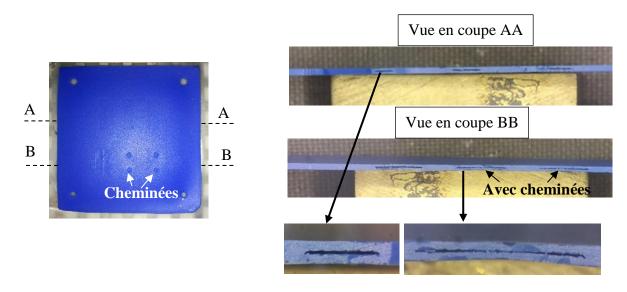

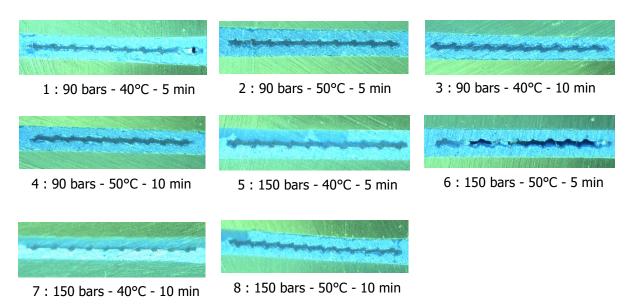

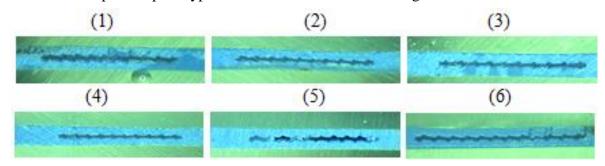

| Figure 104. Tests effectués pour le paramétrage du laser                                                                                                               |                          |

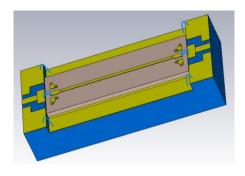

| vapeur (b), les couches qui se situent au-dessus des micro-caloducs (c), le substrat LTCC après laminage (d                                                            |                          |

|                                                                                                                                                                        | 103                      |

|                                                                                                                                                                        | 103                      |

| Figure 108. Photos du substrat ESL 41020 laminé par un laminage chimique froid avec saliveaprès cuisson: vue                                                           |                          |

| Figure 109. Photos de substrat ESL 41020 laminé par un laminage chimique froid avec miel après cuisson: vue                                                            |                          |

|                                                                                                                                                                        | 104                      |

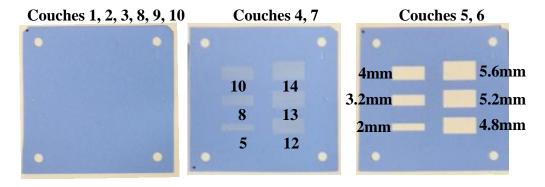

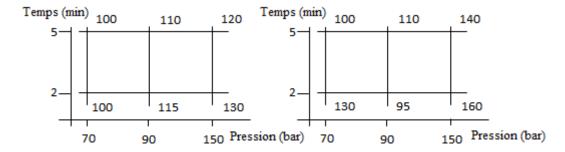

| 1                                                                                                                                                                      | 106                      |

| Figure 111. Photos du substrat ESL 41020 après cuisson avec le SVM alcool cytélique : vue de dessus du subst (à gauche) et vue en coupe (à droite)1                    | tra<br>106               |

| Figure 112. Photos de substrat ESL 41020 après cuisson avec SVM PMMA : vue de dessus du substrat (à gauc                                                               | he,                      |

| et vue en coupe (à droite)1                                                                                                                                            | 106                      |

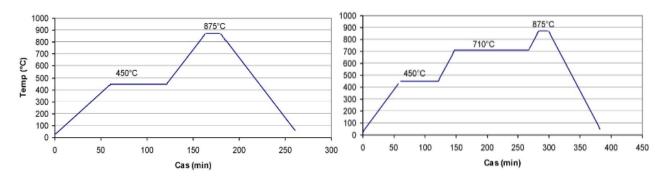

| Figure 113. Profil de cuisson standard (à gauche) et prolongé (à droite) [74] © [2009]                                                                                 |                          |

|                                                                                                                                                                        | 108                      |

| J                                                                                                                                                                      | 109                      |

|                                                                                                                                                                        | ЛА,<br>арв<br>ЛА,<br>109 |

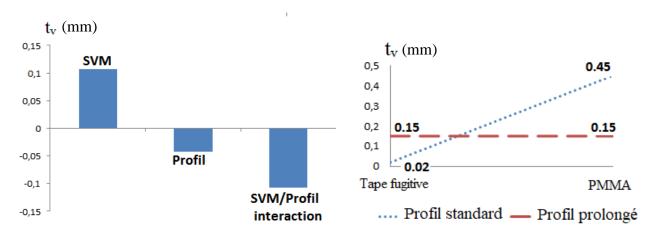

| Figure 117. Diagramme Paréto des effets principaux sur l'épaisseur de l'espace vapeur (à gauche) et cour d'interaction entre le SVM et le profil de cuisson (à droite) | rbe<br>111               |

| a interaction entre le avivi et le broni de CUISSON IU UTOILET                                                                                                         | 441                      |

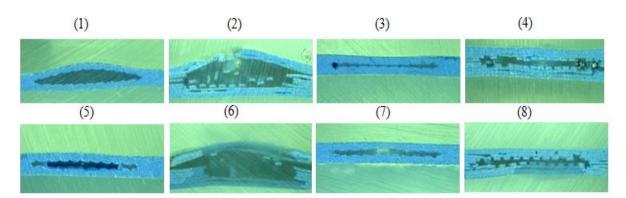

| Figure 118. Vue en coupe des huit prototypes réalisés                                                             | 112          |

|-------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 119. Vue en coupe des six prototypes réalisés : (1) 70 bars et 2 min, (2) 70 bars et 5 min, (3) 9          | 0 bars et 2  |

| min, (4) 90 bars et 5 min, (5) 150 bars et 2 min, (6) 150 bars et 5 min                                           | 113          |

| Figure 120. Valeurs des angles $\alpha_1$ (gauche) et $\alpha_2$ (droite) mesurées pour les 6 prototypes réalisés | 113          |

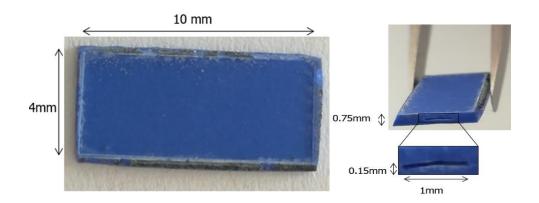

| Figure 121. Vue de dessus du micro-caloduc réalisé (gauche) et vue de côté (droite)                               | 114          |

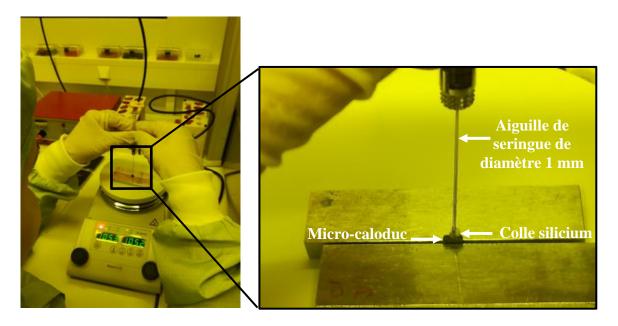

| Figure 122. Remplissage du micro-caloduc par la méthode 1                                                         | 115          |

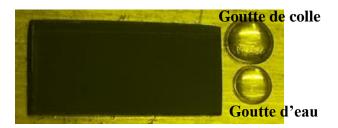

| Figure 123. Goutte d'eau et goutte de colle placées en face de l'ouverture du micro-caloduc                       | 115          |

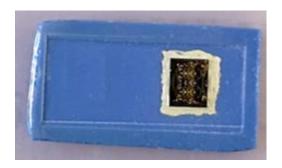

| Figure 124. Amplificateur de puissance collé sur la surface d'un micro-caloduc                                    | 116          |

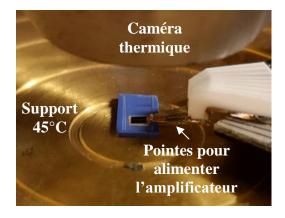

| Figure 125. Banc de mesure thermique (gauche) micro-caloduc sur lequel placé l'amplificateur aliment              | té à travers |

| des pointes DC (droite)                                                                                           | 116          |

| Figure 126. Photo de la mesure thermique de l'amplificateur placé sur le micro-caloduc rempli avec la             | méthode 3    |

| (température maximale 192,5°C)                                                                                    | 117          |

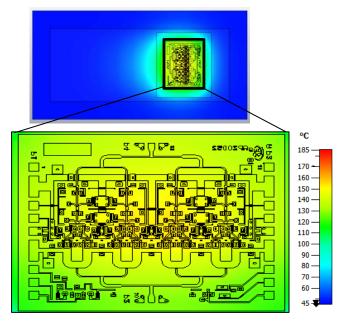

| Figure 127. Simulation thermique de l'amplificateur placé sur un micro-caloduc rempli par i                       | néthode 3    |

| (température maximale 185°C)                                                                                      | 117          |

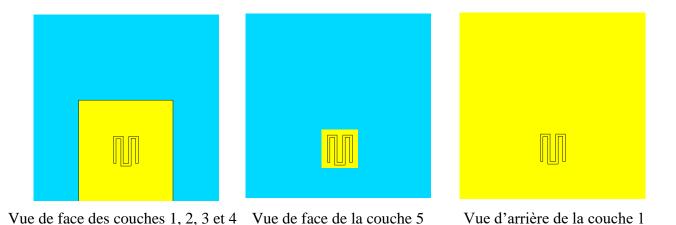

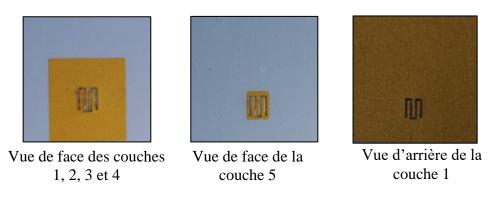

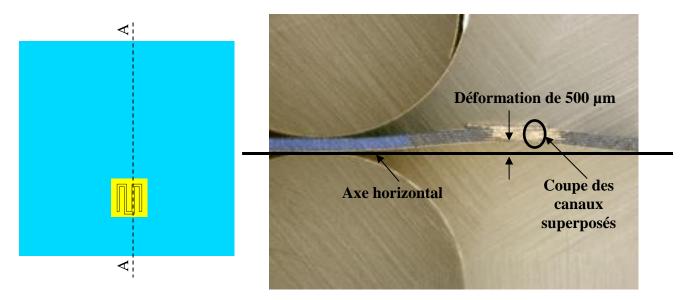

| Figure 128. Les couches LTCC pour réaliser la solution proposée                                                   | 118          |

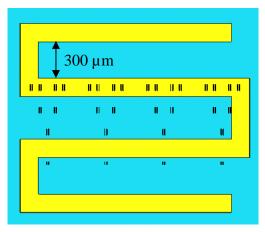

| Figure 129. Position du canal par rapport aux grilles des transistors de l'amplificateur                          | 119          |

| Figure 130. L'amplificateur de puissance placé sur la solution de refroidissement                                 | 119          |

| Figure 131. Simulations de l'amplificateur placé sur la solution de refroidissement proposée                      | 120          |

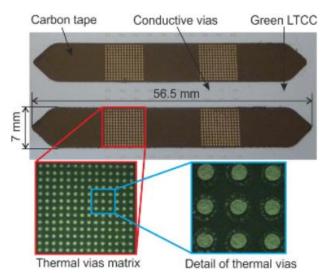

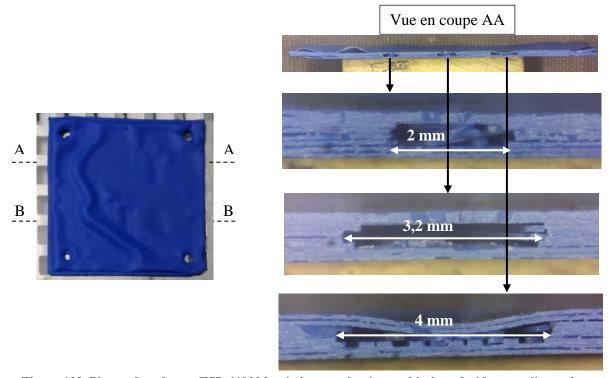

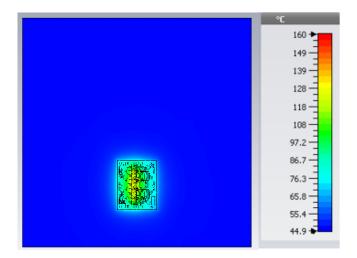

| Figure 132. Les couches LTCC de la solution de refroidissement                                                    | 120          |

| Figure 133. Vue en coupe du prototype réalisé                                                                     | 121          |

| Figure 134. Rétro-simulation thermique du prototype déformé avec un focus sur l'amplificateur de pu               | issance 121  |

| Figure 135. Photo thermique de mesure de l'amplificateur de puissance placé sur la solution de refro              | idissement   |

| (température maximale 220 °C)                                                                                     | 122          |

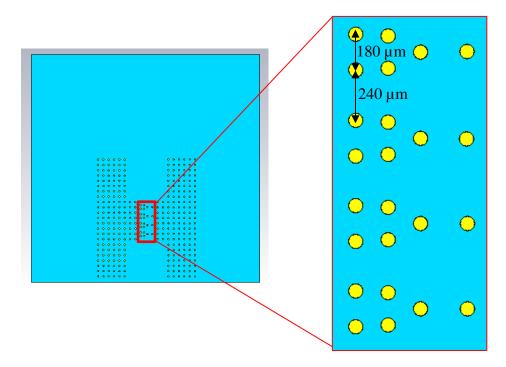

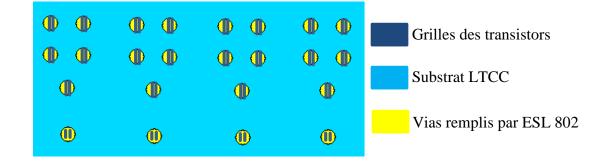

| Figure 136. Remplissage des vias de diamètre 150, 115 et 80 μm par le conducteur ESL 802                          | 122          |

| Figure 137. Les couches LTCC pour réaliser la solution proposée                                                   | 123          |

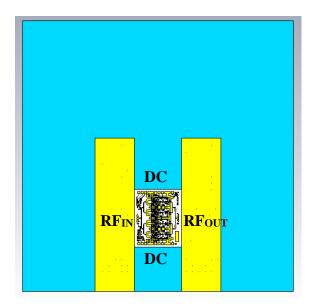

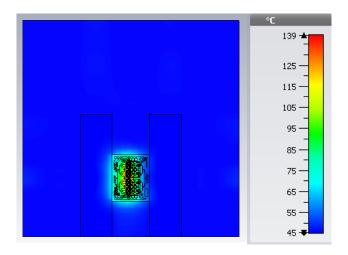

| Figure 138. Vias au-dessous de l'amplificateur                                                                    | 124          |

| Figure 139. Emplacement des vias par rapport aux grilles des transistors de l'amplificateur                       | 124          |

| Figure 140. L'amplificateur de puissance placé sur la solution de refroidissement                                 | 125          |

| Figure 141. Simulations de l'amplificateur placé sur la solution de refroidissement proposée                      | 125          |

| Figure 142. Les couches LTCC de la solution de refroidissement                                                    | 125          |

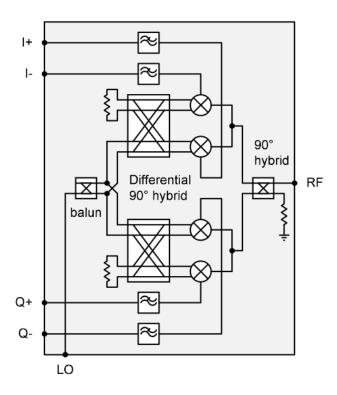

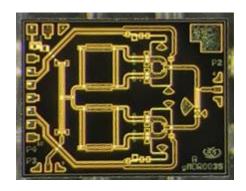

| Figure 143. Synoptique du mélangeur gMDR0035                                                                      | 130          |

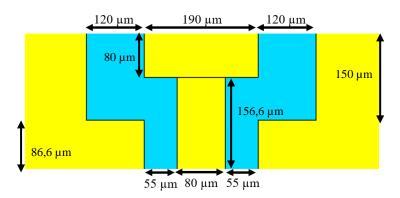

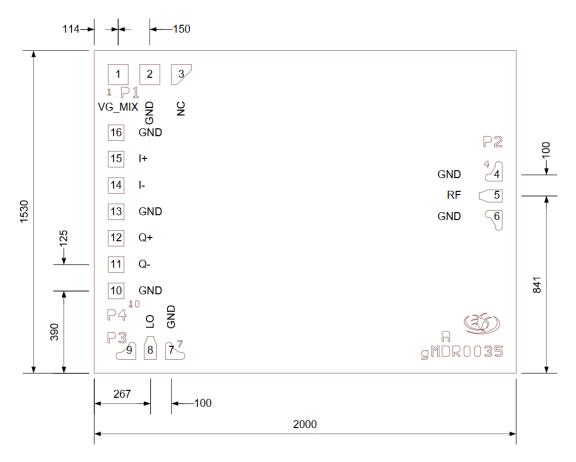

| Figure 144. Dimensions (μm) du mélangeur avec emplacement des différents plots                                    | 131          |

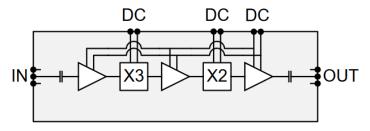

| Figure 145. Diagramme du multiplieur gXSB0025                                                                     | 132          |

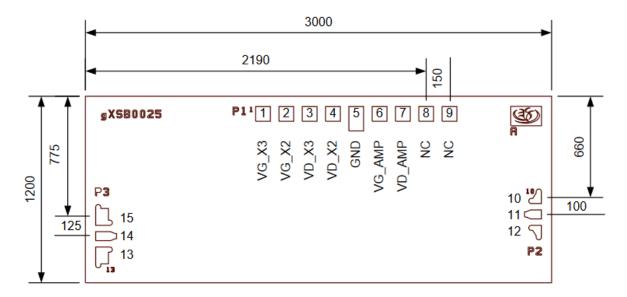

| Figure 146. Dimensions (μm) du multiplieur avec emplacement des différents plots                                  | 132          |

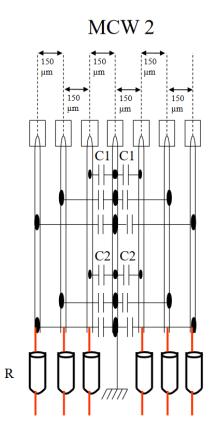

| Figure 147. Pointes MCW (Multi Contact Wedge) pour l'alimentation DC                                              | 134          |

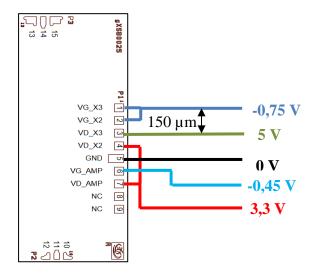

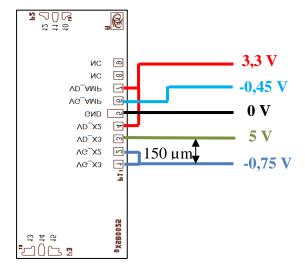

| Figure 148. Valeur de la tension de chaque plot du multiplieur                                                    | 135          |

| Figure 149. Conception du montage par micro-câblage du multiplieur sur LTCC                                       | 136          |

| Figure 150. Multiplieur retourné pour un montage par flip-chip                                                    | 136          |

| Figure 151. Conception du montage par flip-chip du multiplieur sur LTCC                                           | 137          |

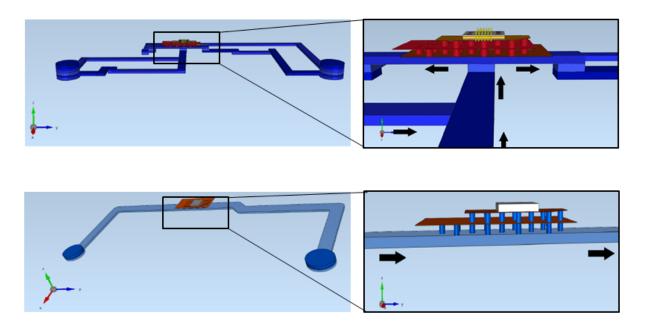

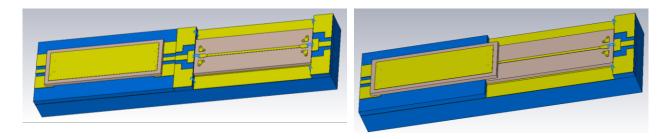

| Figure 152. Topologie 1 (gauche) et topologie 2 (droite) pour deux puces « ligne microruban » montées             | •            |

| câblage                                                                                                           | 138          |

| Figure 153. Topologie 1 (gauche) et topologie 2 (droite)                                                          | 138          |

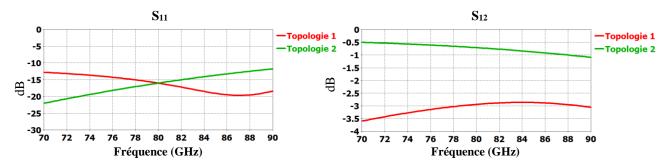

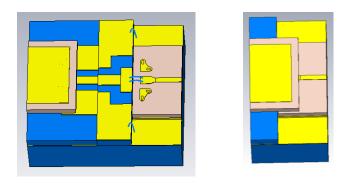

| Figure 154. Simulation des deux topologies données par la figure 153                                              |              |

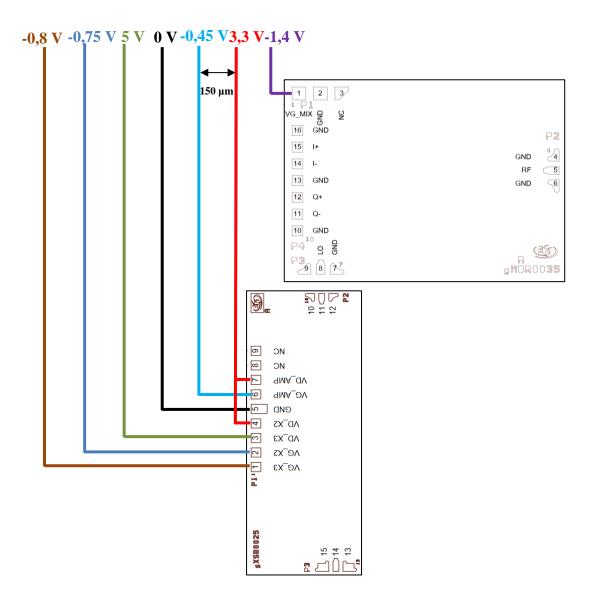

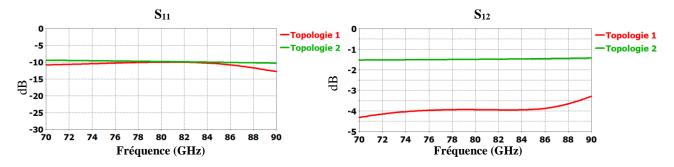

| Figure 155. Réseau d'alimentation DC du multiplieur + mélangeur                                                   | 139          |

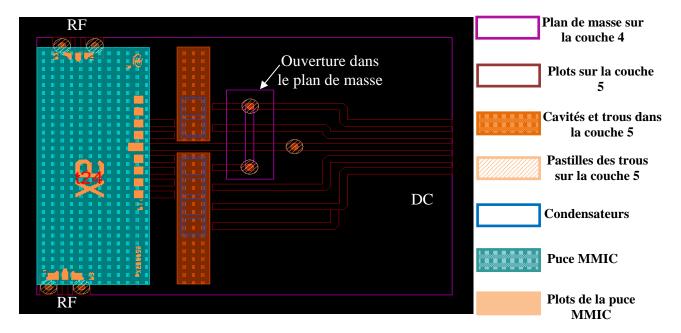

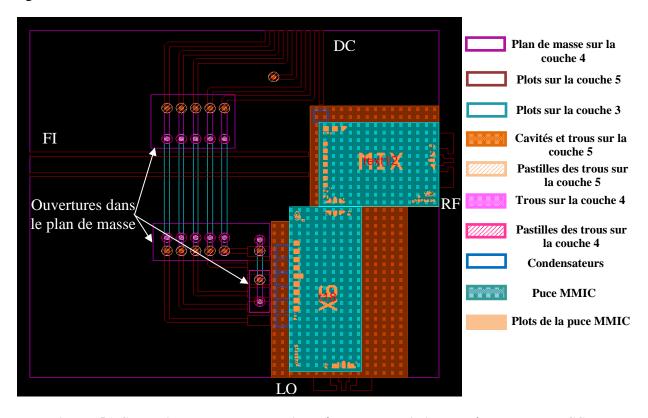

| Figure 156. Conception du montage par micro-câblage du multiplieur + mélangeur sur LTCC                           |              |

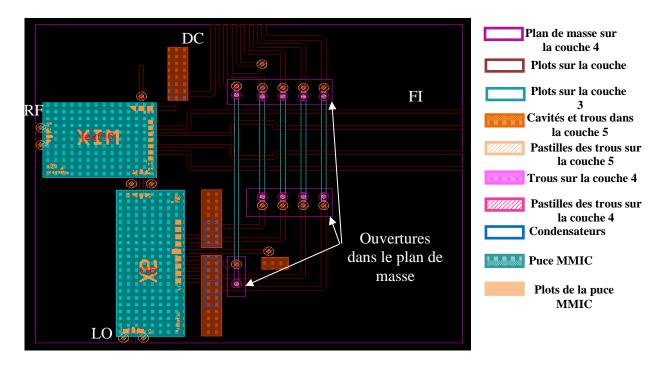

| Figure 157. Conception du montage par flip-chip du multiplieur + mélangeur sur LTCC                               | 141          |

| Figure 158. Topologie 1 (gauche) et topologie 2 (droite) pour deux puces « ligne microruban »                     | 141          |

| Figure 159. Topologie 1 (gauche) et topologie 2 (droite)                                                          | 142          |

| Figure 160. Simulation des deux topologies données par la figure 159                                              | 142          |

| Figure 161. Conception du montage du multiplieur + mélangeur sur LTCC (topologie 1)                               |              |

| Figure 162. Conception du montage du multiplieur + mélangeur sur LTCC (topologie 2)                               | 143          |

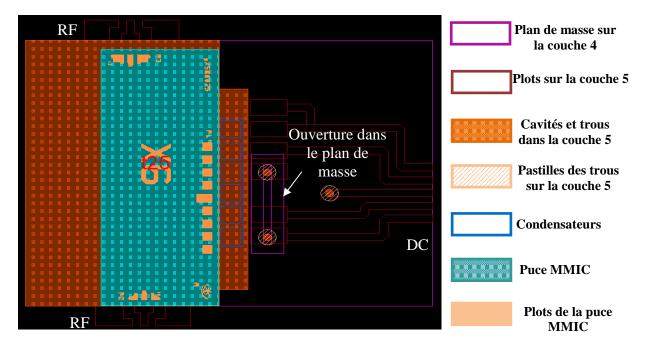

| Figure 163. Couches 4 et 5 pour le montage du multiplieur par micro-câblage (à gauche) (conception d              |              |

| figure 149) et par flip-chip (à droite) (conception donnée à la figure 151)                                       | 144          |

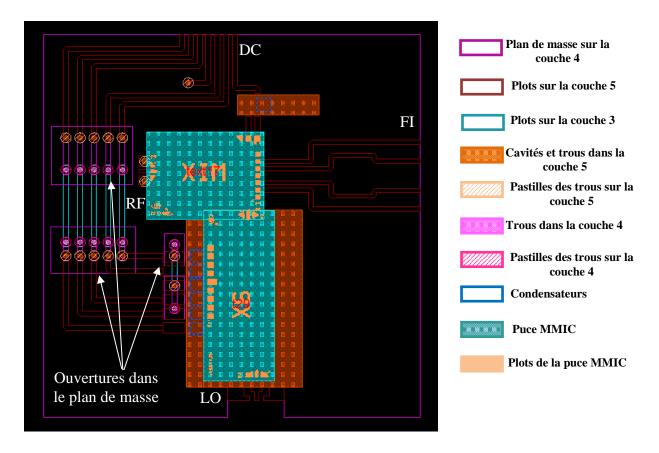

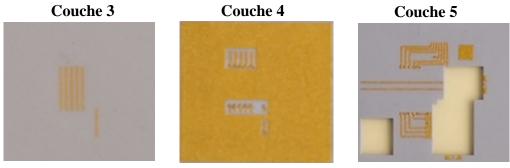

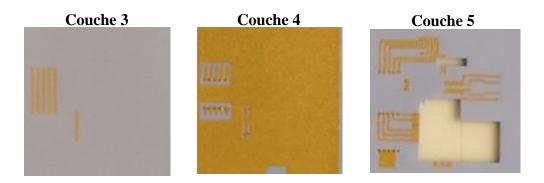

| Figure 164. Couches 3, 4 et 5 pour le montage du multiplieur + mélangeur par micro-câblage (concept               |              |

| à la figure 156)                                                                                                  | 144          |

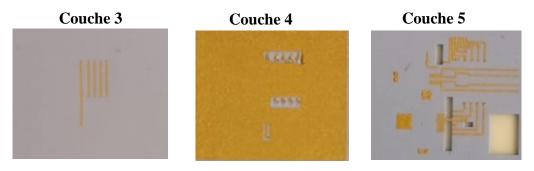

| Figure 165. Couches 3, 4 et 5 pour le montage du multiplieur + mélangeur par flip-chip (conception c              |              |

| figure 157)                                                                                                       | 144          |

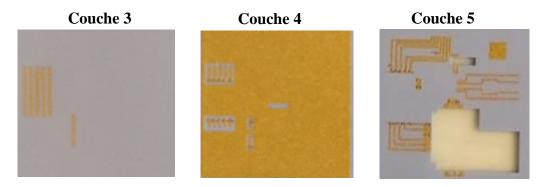

| Figure 166. Couches 3, 4 et 5 pour le montage du multiplieur + mélangeur par micro-câblage et flip-chip   | topologie   |

|-----------------------------------------------------------------------------------------------------------|-------------|

| 1 (conception donnée à la figure 161)                                                                     | 145         |

| Figure 167. Couches 3, 4 et 5 pour le montage du multiplieur + mélangeur par micro-câblage et flip-chip   | topologie   |

| 2 (conception donnée à la figure 162)                                                                     | 145         |

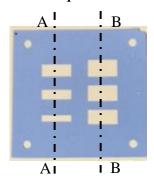

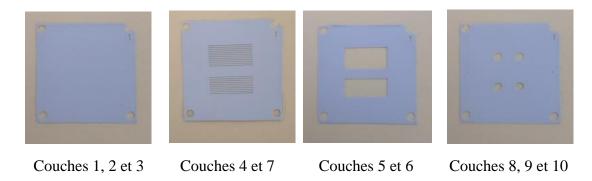

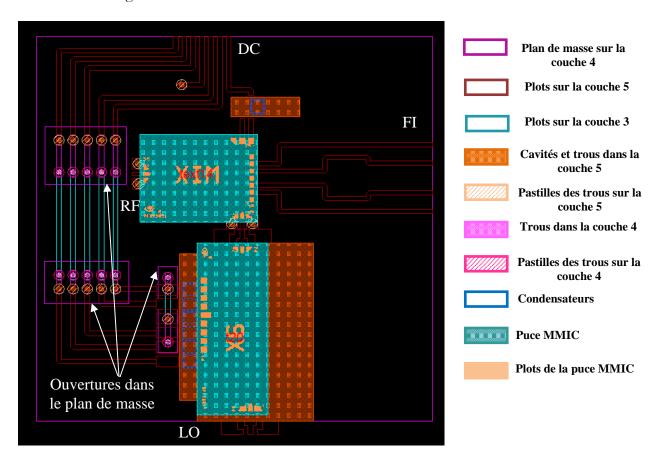

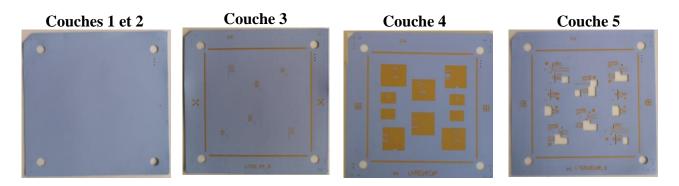

| Figure 168. Les différentes couches du substrat LTCC pour le montage du multiplieur et du multiplieur + n | nélangeur   |

|                                                                                                           | 145         |

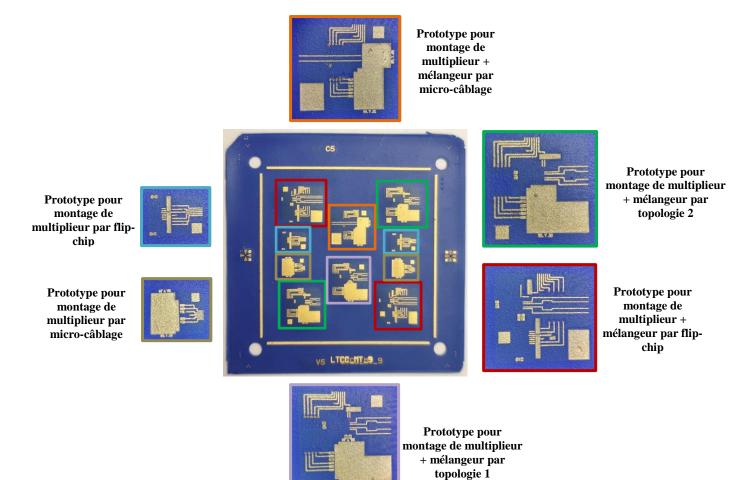

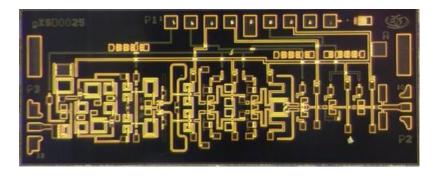

| Figure 169. Substrat réalisé pour les différents montages                                                 | 146         |

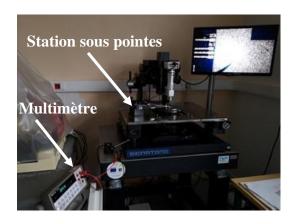

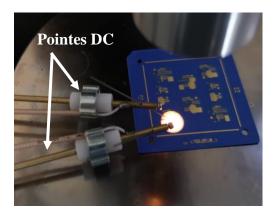

| Figure 170. Vérification du subsrat à l'aide des pointes DC                                               | 147         |

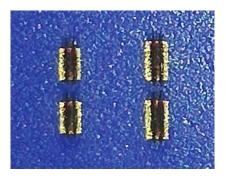

| Figure 171. Puce du multiplieur                                                                           | 147         |

| Figure 172. Multiplieur monté sur le substrat LTCC par micro-câblage                                      | 147         |

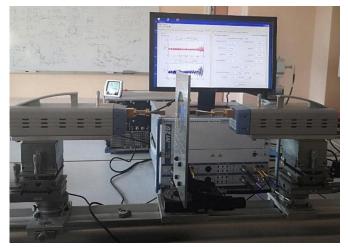

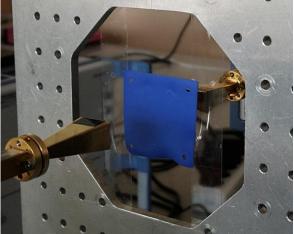

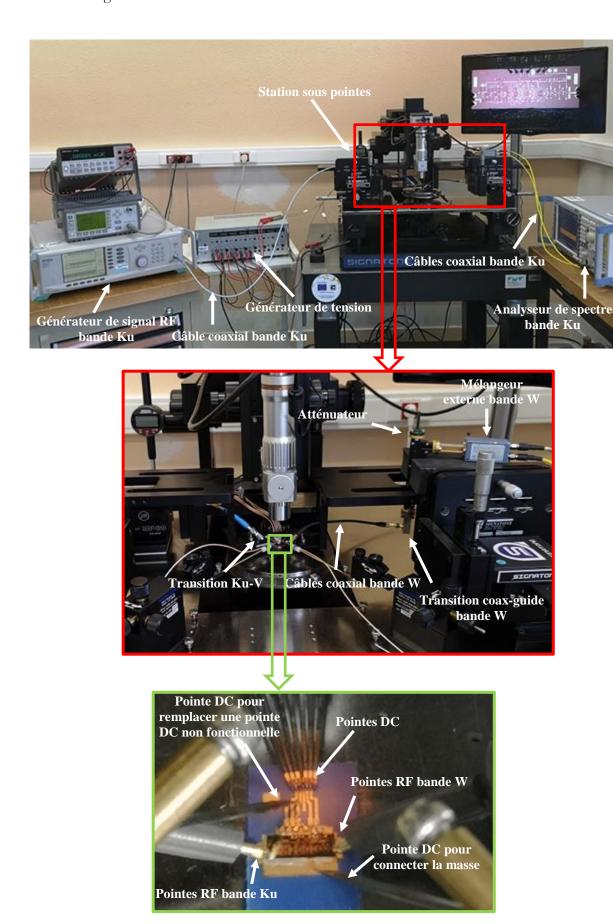

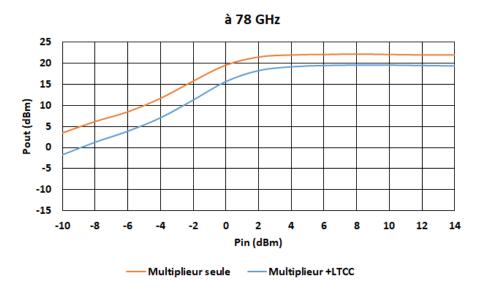

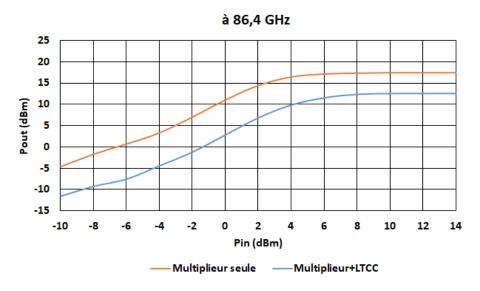

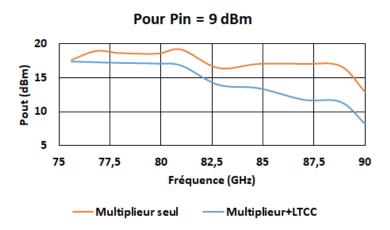

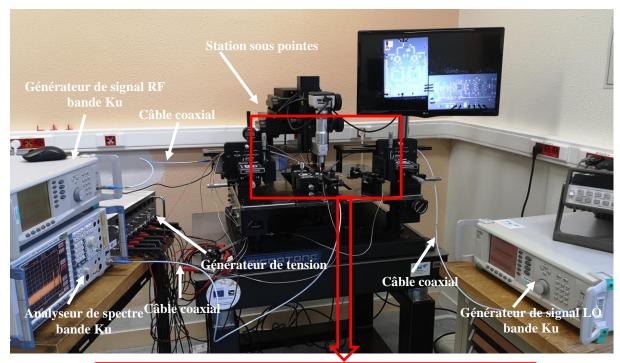

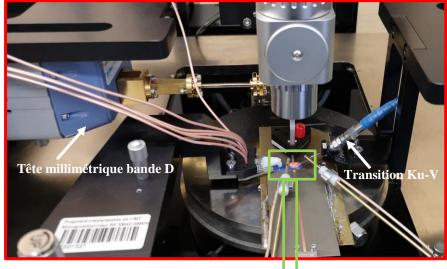

| Figure 173. Banc de mesure                                                                                | 149         |

| Figure 174. Puissance de sortie du multiplieur avant et après intégration sur le LTCC à 78 GHz pour d     | lifférentes |

| valeurs de puissance du signal d'entrée                                                                   | 150         |

| Figure 175. Puissance de sortie du multiplieur avant et après intégration sur le LTCC à 86,4 GHz pour d   | lifférentes |

| valeurs de puissance du signal d'entrée                                                                   | 150         |

| Figure 176. Puissance de sortie du multiplieur avant et après intégration sur le LTCC en fonction de la   | fréquence   |

| pour Pin = 9 dBm                                                                                          | 151         |

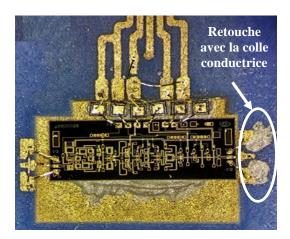

| Figure 177. Montage du multiplieur par micro-câblage sur le LTCC                                          | 152         |

| Figure 178. Puce du mélangeur                                                                             | 152         |

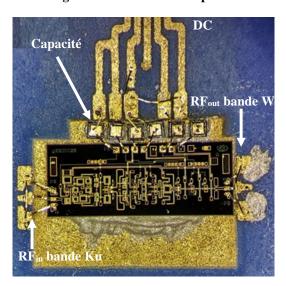

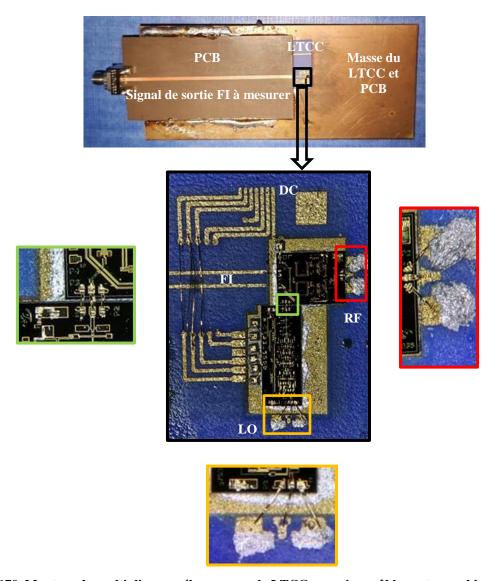

| Figure 179. Montage du multiplieur +mélangeur sur le LTCC par micro-câblage et assemblage avec le F       | PCB 153     |

| Figure 180. Banc de mesure                                                                                | 155         |

| Figure 181. Diagramme du montage réalisé                                                                  | 156         |

| Figure 182. Courbes des pertes de conversion en fonction de puissance de signal RF (gauche, PLO= 14 d     | 'Bm) et en  |

| fonction de puissance du signal LO (droite, PRF=-20 dBm) à 140 GHz pour VG_MIX = -1,1 V                   | 156         |

| Figure 183. Courbes des pertes de conversion en fonction de la fréquence (gauche, VG_MIX= -1,1 V) et e    | n fonction  |

| de VG_MIX (droite, fréquence= 140GHz) pour PRF = -20 dBm et PLO = 14 dBm                                  | 157         |

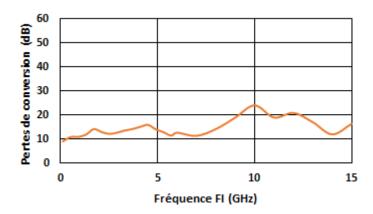

| Figure 184. Courbe des pertes de conversion en fonction de la fréquence FI pour PRF= -10 dBm, PLO =       | 14 dBm et   |

| VG_MIX = -1,1 V                                                                                           | 157         |

| Figure 185. Descriptif règles de conception                                                               | 179         |

|                                                                                                           |             |

# Liste des tableaux

| Tableau 1. Matériaux LTCC                                                                      | 35  |

|------------------------------------------------------------------------------------------------|-----|

| Tableau 2. Pâtes conductrices pour LTCC                                                        | 39  |

| Tableau 3. Performances d'une interconnexion par micro-câblage                                 | 72  |

| Tableau 4. Performances d'interconnexion par flip-chip                                         | 78  |

| Tableau 5. Comparaison des performances des interconnexions par flip-chip et par micro-câblage |     |

| Tableau 6. Performances d'interconnexion par « hot vias »                                      |     |

| Tableau 7. Comparaison des différentes solutions proposées                                     | 84  |

| Tableau 8. Résultats des tests effectués                                                       |     |

| Tableau 9. Dimensions calculées du micro-caloduc                                               | 109 |

| Tableau 10. Valeurs des paramètres de laminage testées                                         | 111 |

| Tableau 11. Valeurs de temps et pression testées                                               | 112 |

| Tableau 12. Règles de conception                                                               | 179 |

# Liste d'abréviations et sigles

| Abréviation | Explication                                         | Traduction français si besoin                   |  |

|-------------|-----------------------------------------------------|-------------------------------------------------|--|

| ADS         | Advanced Design System                              | Simulateur circuit de Keysight Technologies     |  |

| AiP         | Antenna-in-Package                                  | Antenne intégrée en boitier                     |  |

| APC         | Angled Physical Contact                             | Contact Physique Incliné                        |  |

| BGA         | Ball Grid Array                                     |                                                 |  |

| CI          | Circuits intégrés                                   |                                                 |  |

| CMOS        | Complementary Metal Oxide Semiconductor             | Semi-conducteur d'oxyde de métal complémentaire |  |

| СОВ         | Chip-On-Board                                       | Assemblage direct des puces sur une carte       |  |

| CPW         | Coplanar Waveguide                                  | Guide d'onde coplanaire                         |  |

| CPWG        | Grounded Coplanar Waveguide                         | Guide d'onde coplanaire avec plan de masse      |  |

| CSP         | Chip Scale Package                                  |                                                 |  |

| CST         | Computer Simulation Technology                      | Simulateur électromagnétque et thermique        |  |

| ESL         | Electroscience Laboratory                           |                                                 |  |

| FC-CSP      | Flip-Chip Chip Scale Package                        |                                                 |  |

| GAA         | Grid Array Antenna                                  |                                                 |  |

| GGW         | Grooved Gap Waveguide                               | Guide d'onde rainuré                            |  |

| Gotmic      | Göteborg Microwave Integrated Circuits              | Entreprise à Göteborg (Suède)                   |  |

| HFSS        | High Frequency Structure Simulator                  | Simulateur électromagnétque                     |  |

| нтсс        | High Temperature Co-fired Ceramic                   | Céramique cocuite à haute température           |  |

| LCP         | Liquid Crystal Polymer                              | Polymère à cristaux liquides                    |  |

| LED         | Light-emitting diode                                | Diode électroluminescente                       |  |

| LTCC        | Low Temperature Co-fired Ceramic                    | Céramique cocuite à basse température           |  |

| MCM         | Multi-Chip Module                                   | Module à plusieurs circuits intégrés            |  |

| мсм-с       | Multi-Chip Module co-fired Ceramic layers           | MCM à base des couches céramiques cocuites      |  |

| MCM-D       | Multi-Chip Module vapor-deposited Dielectric layers | MCM à base des couches diélectriques            |  |

| MCM-L       | Multi-Chip Module organic Laminates layers          | MCM à base des couches organic laminées         |  |

| MCQFN  | MicroCoax QFN                           |                                                     |

|--------|-----------------------------------------|-----------------------------------------------------|

| MMIC   | Microwave Monolithic Integrated Circuit | Circuit intégré monolithique micro-ondes            |

| РСВ    | Printed Circuit Board                   | Carte électronique imprimée                         |

| PMMA   | Poly Methyl MethAcrylate                | Poly MéthAcrylate de Méthyle                        |

| PWB    | Printed Wiring Board                    | Carte électronique imprimée de câblage              |

| QFN    | Quad Flat No Lead                       |                                                     |

| QFP    | Quad Flat Package                       |                                                     |

| SIP    | System-In-Package                       |                                                     |

| SIW    | Substrate Intégrated Waveguide          | Guide d'onde intégré dans un substrat               |

| SMA    | SubMiniature version A                  | Connecteur coaxial miniature                        |

| SMP    | SubMiniature Push on                    | Connecteur coaxial miniature                        |

| SOP    | System-On-Package                       |                                                     |

| SVM    | Sacrificial Volume Material             | Matériel de volume sacrificiel                      |

| V-LIW  | Vertical LTCC Intégrated Waveguide      | Guide d'onde vertical intégré dans un substrat LTCC |

| VQC    | ligne Verticale Quasi-Coaxiale          |                                                     |

| WL-CSP | Wafer Level Chip Scale Package          |                                                     |

# Liste de symboles

| Symbole                   | Explication                  | Unité             |

|---------------------------|------------------------------|-------------------|

| ВР                        | Bande passante               | %                 |

| F                         | Fréquence                    | Hz                |

| $\lambda_0$               | Longueur d'onde dans le vide | m                 |

| $\lambda_{ m g}$          | Longeur d'onde guidée        | m                 |

| $\mathcal{E}_0$           | Permittivité du vide         | F m <sup>-1</sup> |

| $arepsilon_{ m r}$        | Permittivité relative        |                   |

| $\mathcal{E}_{	ext{eff}}$ | Permittivité effective       |                   |

| μ <sub>0</sub>            | Perméabilité du vide         | H m <sup>-1</sup> |

| μr                        | Perméabilité relative        |                   |

| Ω                         | Pulsation                    | Rad/s             |

| С                         | Capacité                     | F                 |

# **Constantes physiques**

| Nom                                 | Symbole         | Valeur                                      |

|-------------------------------------|-----------------|---------------------------------------------|

| Célérité de la lumière dans le vide | С               | 3x10 <sup>8</sup> m/s                       |

| Pi                                  | π               | 3,14                                        |

| Permittivité du vide                | $\mathcal{E}_0$ | $8,854\ 187\ 82 \times 10^{-12}\ F\ m^{-1}$ |

| Perméabilité du vide                | $\mu_0$         | $4\pi \times 10^{-7} \ H \ m^{-1}$          |

## Contexte de thèse

Un circuit électronique analogique qui réalise une fonction déterminée (amplification, mélange, multiplication de fréquence,...) est généralement constitué de composants actifs (transistors, diodes) et passifs (résistances, condensateurs, inductances) connectés entre eux par des lignes. Ce circuit est soumis à différentes agressions environnementales telles que la chaleur, l'humidité, la poussière, les chocs, etc., qui peuvent dégrader ses performances ou provoquer son dysfonctionnement. Par ailleurs, aux fréquences très élevées, la longueur d'onde est telle que la taille réduite des circuits augmente leur fragilité et rend leur manipulation assez complexe. Afin de prendre en compte toutes ces contraintes et de les minimiser, une étape complémentaire et indispensable qui suit la fabrication des circuits est la mise en boitier.

La mise en boitier permet a priori la protection des circuits contre tous les facteurs d'agression extérieurs cités précédemment. Elle permet également de faciliter la connexion entre le circuit et les autres dispositifs et éléments du système au travers de connecteurs ou de lignes de connexion dans le cas d'un report sur substrat. Un autre intérêt de la mise en boitier est la possibilité de mettre en place un système de dissipation de la chaleur afin de garantir un équilibre thermique et prolonger la durée de vie des circuits.

Le boitier peut être réalisé à partir de différents matériaux tels que le métal, le plastique, la céramique,... Le choix est lié à plusieurs critères : la compatibilité avec le type de circuit en termes de bande de fréquence et de taille, le coût de fabrication qui dépend du matériau utilisé, le processus de fabrication ainsi que le temps nécessaire à la réalisation.

Pour les fréquences très élevées et en particulier pour la bande D (110–170 GHz), le boitier est généralement réalisé à partir de structures métalliques. Ces boitiers sont coûteux, volumineux et relativement longs à fabriquer. Pour les raisons citées précédemment, il est nécessaire de proposer un autre type qui permet la mise en boitier des circuits intégrés conçus pour cette bande de fréquence : c'est l'objet des travaux de cette thèse intitulée « Modules intégrés en technologie LTCC pour des applications en bande D (110 GHz – 170 GHz) ».

Cette thèse constitue un nouveau projet entre le laboratoire Lab-STICC au sein de l'Institut Mines-Télécom Atlantique qui travaille depuis 2009 sur la technologie LTCC (Low Temper Co-fired Ceramics) et l'entreprise suédoise GOTMIC, créée en 2008 et dont les activités sont la

conception et la réalisation de circuits intégrés en technlogie MMIC (Monolithic Microwave Integrated Circuits) ainsi que le développement de solutions de mise en boitier.

L'objectif de la thèse est de réaliser des modules d'émission-réception (front-end TRX) en bande D, faible coût, sur la base de puces intégrées de type MMIC reportées sur un substrat LTCC. Les applications visées à ces fréquences sont par exemple l'imagerie (sécurité), les radars automobiles ACC d'aide à la conduite, la radiométrie ou encore le « back-haul » des réseaux de téléphonie 5G.

Les principaux objectifs visés à travers cette thèse sont :

- Les interconnexions entre les puces MMIC et le support LTCC

Le laboratoire Lab-STICC dispose de deux machines pour la réalisation des interconnexions : machine de micro-câblage et machine flip-chip. La machine flip-chip est une machine de report de puces retournées acquise au travers du projet CPER Sophie STIC et Ondes. Elle permettra de comparer cette technique d'interconnexion avec le micro-câblage.

- Le contrôle thermique des puces ayant une dissipation importante

Les amplificateurs de puissance sont en général indissociables du module d'émission (TX). Du fait du rendement en puissance parfois très faible (< 20%), une grande partie de la puissance DC (Direct Current) de ces amplificateurs est convertie en chaleur qui, du fait de la faible conductivité thermique du LTCC, provoque une augmentation de la température qui peut endommager les puces. L'étude, la modélisation, la simulation et la réalisation d'une solution de refroidissement des puces dans les modules LTCC sont alors nécessaires.

- L'alimentation continue (DC) intégrée sur le module TRX

Les puces MMICs doivent être correctement alimentées en DC. En LTCC, les circuits d'alimentation (pistes et composants passifs) peuvent être réalisés sur une ou plusieurs couches. Une alimentation efficace est à étudier et à proposer.

Réalisation du module réception en bande D

L'intégration des puces MMIC actives sur le substrat LTCC représente l'étape finale pour réaliser un module réception en bande D. Les puces doivent être montées sur leur substrat LTCC avec l'interconnexion et le réseau d'alimentation convenable.

Ce manuscrit est composé de quatre chapitres :

- Le premier chapitre présente un état de l'art illustrant la mise en boitier sur la base des principales technologies d'encapsulation, dédiées aux applications à hautes fréquences, dont la technologie LTCC qui sera utilisée dans la suite du travail. Les différentes technologies d'interconnexion y sont également présentées.

- Le deuxième chapitre est dédié au report des puces MMIC sur un support LTCC en utilisant l'interconnexion par Flip-Chip ou par micro-câblage. Ces deux techniques d'interconnexion sont comparées en simulation et en mesure sur la base de puces MMIC GaAs. Ces MMICs sont constitués d'une simple ligne coplanaire puis microruban. Les résultats de simulations et de mesures sont analysés pour identifier l'influence de la technologie LTCC et de la technique d'interconnexion sur les performances des puces.

- Les solutions de refroidissement font l'objet du troisième chapitre. L'échauffement des circuits intégrés, tels que les amplificateurs de puissance liés à leur rendement électrique, nécessite l'étude de solutions de refroidissement qui sont proposées dans ce chapitre. Nous y présentons une solution réalisable, efficace et compatible avec la puce qui est utilisée.

- Le quatrième et dernier chapitre porte sur l'intégration d'un module simple constitué d'un multiplieur puis d'un multiplieur associé à un mélangeur (récepteur) sur le substrat LTCC par flip-chip et par micro-câblage. La mesure des modules réalisés et les résultats obtenus ont permis d'analyser l'effet du report des puces sur le substrat LTCC sur les performances du module dans la bande D par comparaison avec les données des puces seules.

#### TABLE DES MATIÈRES CHAPITRE I:

- I. État de l'art de la mise en boitier des puces MMIC

- I.1 Introduction

- I.2 La mise en boitier

- I.2.1 Définition

- I.2.2 Mise en boitier pour des applications hautes fréquences

- I.3 La technologie LTCC

- I.3.1 Définition

- I.3.2 Les tapes LTCC

- I.3.3 Étapes de fabrication des circuits en technologie LTCC

- I.4 Techniques d'interconnexions

- I.4.1 Micro-câblage

- I.4.2 Flip-chip

- I.5 Conclusion

## I.1 Introduction

La grande variété de boitiers disponibles peut être classée selon différents critères. On présente dans la première partie les différents types de mise en boitier des circuits conçus pour des applications à hautes fréquences (> 50 GHz). La technologie de mise en boitier LTCC (Low Temperature Cofired Ceramics) ainsi que ses avantages sont décrits dans la deuxième section. Enfin, une présentation des différentes technologies d'interconnexion entre le circuit intégré (CI) et son boitier ou entre les CIs intégrés dans un même boitier.

## I.2 La mise en boitier

### I.2.1 Définition

La mise en boitier d'un circuit électronique à pour objectif de le protéger contre tout type d'agressions mécaniques (choc) ou environnementales (effet des corps extérieurs tels que l'eau ou l'humidité, l'air, la poussière,...), de faciliter la manipulation lors des caractérisations expérimentales, de le connecter à d'autres circuits ou composants électroniques, ou encore de dissiper la chaleur produite par le circuit,... Les technologies de mise en boitier sont nombreuses et chacune a ses avantages et ses inconvénients. Les premiers critères sur lesquels se base le choix du boitier sont la fréquence d'utilisation du circuit, l'influence du boitier sur le comportement du circuit, la taille de circuit, le coût du boitier et le processus de fabrication. Dans la section qui suit, on présente quelques technologies de mise en boitier de circuits conçus pour des applications au delà de 50 GHz puisque notre projet vise des applications en bande D [1].

# I.2.2 Mise en boitier pour des applications hautes fréquences

La taille des circuits électroniques devient de plus en plus petite lorsque la fréquence augmente du fait de la réduction de la longueur d'onde. Cependant, l'augmentation de la fréquence de fonctionnement des circuits provoque généralement l'apparition d'effets parasites (couplages, effets capacitifs et inductifs) et induit des phénomènes de propagation et de rayonnement [1]. Face à ces effets souvent pénalisants en termes de performances (bande passante, adaptation, gain,...), le choix du boitier est une étape très importante car celui-ci doit rajouter le moins possible de perturbations au circuit.

Il existe une grande variété et diversité de technologies de mise en boitier pour des circuits visant des applications hautes fréquences. Dans le paragraphe suivant, des technologies de mise en boitier dans les bandes V (50-75 GHz), E (50-90 GHz), W (75-110 GHz) et D (110-170 GHz) sont présentées.

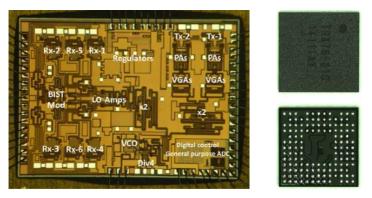

#### I.2.2.1 Matrice de billes BGA

La technologie BGA (Ball Grid Array) est caractérisée par un grand nombre des billes soudées sur la face arrière du boitier afin de monter le boitier sur le circuit imprimé (PCB: Printed Circuit Board). Ce type de boitier est souvent utilisé pour des circuits numériques (microprocesseurs, microcontrôleurs, mémoires,...) du fait de la haute densité des entrées/sorties (entre 200 et 500). Le BGA offre une taille réduite si on le compare à la technologie *Lead Frame* telle que le QFN (présentée par la suite). Le BGA est utilisé dans des applications en bande V comme le montre l'exemple du module, présenté en [3], compatible avec un émetteur/récepteur 60 GHz intégrant les antennes d'émission/réception. Le module proposé est faible coût et facile à fabriquer tout en offrant des performances de l'antenne acceptables. Le BGA est également utilisé pour encapsuler par flip-chip une puce émetteur-récepteur de 76 à 81 GHz (bande W) [4]. Les pertes résultant de la mise en boitier sont évaluées entre 1.5 et 2 dB ce qui représente une dégradation minimale des performances globales. La figure 1 ci-dessous montre la puce de l'émetteur-récepteur ainsi que le boitier BGA.

Figure 1. Puce de l'émetteur-récepteur (à gauche) et le boitier BGA (à droite) ; vue de dessus (en haut) et vue de dessous (en bas) [4] © [2016]

L'exemple présenté en [5] exploite un BGA pour mettre en boitier un émetteur-récepteur avec un réseau d'antenne en bande W composé de 64 éléments. Le réseau d'antenne est sur le dessus du boitier et l'émetteur-récepteur, composé de quatre circuits intégrés (CI) réalisés en technologie SiGe, et est connecté à la face inférieure du boitier par flip-chip. La figure 2 montre le boitier avec le réseau d'antennes et les quatre CIs de l'émetteur-récepteur.

Figure 2. Vue de dessous de le boitier (à gauche) et vue de dessus (à droite) [5] © [2014]

Le BGA peut cependant présenter plusieurs problèmes : billes absentes, billes de taille inférieure ou supérieure, billes déformées à cause de l'oxydation ou par contamination. Un autre inconvénient du BGA est sa sensibilité aux gradients de température auxquels il est exposé lors de l'encapsulation. Les différents coefficients de dilatation thermique (CTE) des matériaux contenus dans le boitier entraînent sa déformation (warpage). L'étude, présentée en [6], réalisée à l'aide du simulateur COMSOL Multiphysics sur la fiabilité du BGA soumis à un cycle de température montre que les billes de soudure écrasées sont essentiellement sur les bords. Ce travail est utile pour estimer la fatigue du boitier et par la suite augmenter l'efficacité de production.

#### I.2.2.2 Boitier QFN

Le boitier de type QFN (Quad Flat No Lead) dérive de la technique QFP (Quad Flat Package) mais le QFN n'a pas de « pattes » qui sortent du boitier. Le QFN est un boitier généralement en plastique et peut encapsuler un ou plusieurs CI. Ce boitier est de conception simple et offre une encapsulation facile qui peut être manuelle contrairement au BGA qui nécessite un processus de montage spécifique. Il est dédié à un faible nombre d'entrées-sorties (entre 6 et 80).

L'inconvénient majeur de ce boitier est le matériau utilisé : le plastique est un matériau qui absorbe l'humidité, ce qui peut endommager le circuit. Des études ont été réalisées sur le développement de nouveaux matériaux thermoplastiques à base de polymère à cristaux liquides pour concevoir des boitiers QFN [7]. Ces matériaux offrent une faible absorption de l'humidité et une haute résistance thermique, ce que prolonge la durée de vie du boitier.

Le QFN a été utilisé pour des applications à hautes fréquences, telles que la bande E [8]. Il s'agit d'un QFN pour lequel le câblage traditionnel est remplacé par un câblage appelé

MicroCoax similaire au câble coaxial. Ce MCQFN (MicroCoax QFN) offre une excellente isolation entre les signaux d'entrée-sortie, une bonne dissipation thermique, une intégration plus facile avec les PCB ainsi que des pertes faibles, ce qui augmente la bande passante du boitier. La figure 3 ci-dessous montre un boitier QFN avec une métallisation centrale pour dissiper la chaleur du circuit encapsulé.

Figure 3. Boitier QFN conçu pour la bande E [8] © [2013]

#### I.2.2.3 Boitier SIP

Le boitier SIP (System-In-Package) permet d'encapsuler tout un système qui peut contenir des composants actifs ou passifs et même des boitiers. Le SIP offre une structure 3D pouvant supporter plusieurs technologies (RF, analogique, numérique,...).

L'avantage du SIP si on le compare aux circuits imprimés (PCB) est la réduction de taille. La publication [9] présente la mise en boitier SIP de systèmes électroniques portables permettant une miniaturisation de 55 % par rapport au PCB avec potentiellement de meilleures performances.

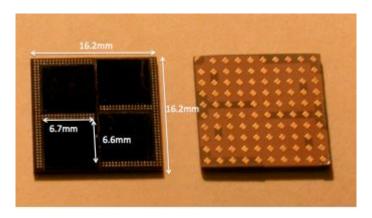

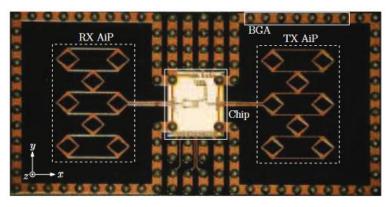

Le SIP peut être utilisé pour des applications en bande D comme proposé en [10] avec un capteur radar à 122 GHz. Le boitier SIP contient la puce de l'émetteur-récepteur ainsi que les antennes d'émission et de réception comme le montre la figure 4.

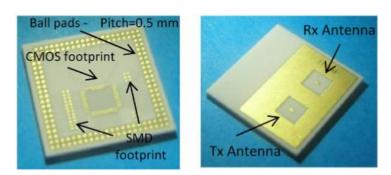

Figure 4. Vue de dessus du SIP 122 GHz [10] © [2016]

#### I.2.2.4 Boitier CSP

Le boitier CSP (Chip Scale Package) offre une taille similaire à celle du CI encapsulé. Il peut être monté directement sur la surface de la carte à travers des billes à souder. Le CI est connecté à travers le boitier par un micro-câblage ou des billes soudées (flip-chip). Ce dernier offre des meilleures performances électriques puisqu'on diminue les pertes en réduisant la longueur de la connexion [1].

Pour augmenter le rendement de production, on utilise le WL-CSP dérivé du CSP et caractérisé par la mise en boitier des CIs dans la phase de "Wafer Level" avant d'être découpé individuellement. Il permet d'encapsuler plusieurs CIs à la fois en ajoutant des couches protectrices et des billes à souder qui permettent les connexions aux boitiers.

L'amplificateur de puissance MMIC présenté en [11] a été conçu pour des applications en bandes E et W et est encapsulé dans un boitier CSP. Les interconnexions (RF et DC) sont réalisées par la création de vias dans le substrat permettant de souder par des billes la puce MMIC à la carte PCB. Cette technique d'interconnexion est compatible avec les CIs microruban et permet de réduire les problèmes causés par le micro-câblage (inductance parasite, pertes, couplage électromagnétique,...).

Les figures 5 et 6 ci-dessous donnent des exemples de mise en boitier de type CSP où la connexion entre la puce et le boitier est réalisée par micro-câblage (figure 5) ou par flip-chip (figure 6).

Figure 5. Mise en boitier CSP [12] © [2011]

Figure 6. Mise en boitier FC-CSP [13] © [2016]

#### I.2.2.5 Boitier SOP

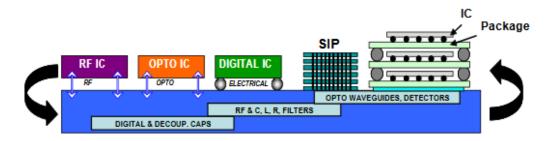

La technologie SOP (System-On-Package) n'est pas à proprement parler un boitier qui va être monté sur une carte pour compléter un système qui existe déjà mais elle représente plutôt un système complet qui regroupe toutes les fonctions nécessaires. Dans cette technologie, on peut trouver des composants passifs et actifs qui permettent de réaliser des modules numériques, RF ou optique [14] [15]. La figure 7 ci-dessous montre un exemple de SOP.

Figure 7. Technologie SOP [15] © [2005]

Cette technologie peut être utilisée pour les hautes fréquences comme le montre l'exemple en [16] où il s'agit d'encapsuler un amplificateur de puissance CMOS conçu pour la bande W en utilisant le polymère à cristaux liquides (LCP) ou encore en [17] où un transmetteur à 338 GHz est mis en boitier via la technologie SOP.

## I.2.2.6 Boitier métallique avec accès en guide d'onde

Parmi les boitiers utilisés pour encapsuler des CIs et surtout les MMIC, on trouve les boitiers métalliques qui peuvent être sous forme de capots permettant de couvrir et protéger un CI ou un ensemble de CIs ou sous forme de guides d'ondes qui facilitent la transmission des signaux entre les différents composants. Les boitiers métalliques sont très utilisés pour la mise en boitier des CIs conçus pour des applications à hautes fréquences du fait de la bonne isolation obtenue entre les différentes parties d'un système, ce qui diminue les pertes qui apparaissent à ces fréquences. L'utilisation d'un guide d'onde pour la bande D est proposée en [18] pour réaliser la transition en sortie d'un circuit MMIC. Cette transition est faite à l'aide d'une antenne à fente de type LTSA (Linearly Tapered Slot Antenna) placée dans le guide d'onde.

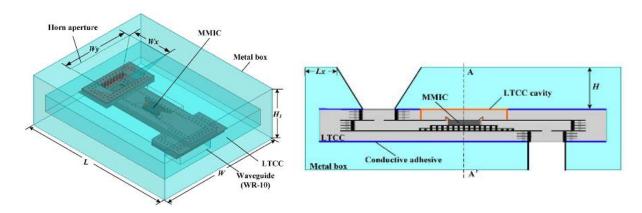

La figure 8 montre un guide d'onde GGW (Grooved Gap Waveguide) utilisé pour réaliser la transition d'une ligne microruban dans la bande V[19] avec la possibilité d'intégrer des circuits MMIC à l'intérieur de ce type de guide.

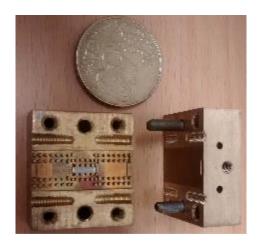

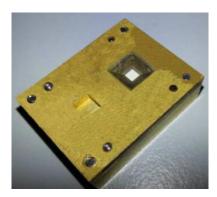

Figure 8. Prototype du module LTCC encapsulé dans une structure métallique; à gauche vue en perspective, à droite vue de côté [20] © [2014]

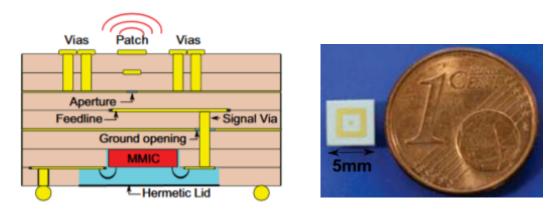

Un exemple de structure métallique utilisé pour encapsuler un module LTCC (Low Temperature Cofired Ceramic) est donné en [20]. Elle a été conçue pour la bande W et contient un circuit MMIC et une antenne AiP (Antenna-in-Package). Le choix de la structure métallique est justifié la forte résistance mécanique obtenue ainsi. Les dimensions de l'ouverture rayonnante sont déterminées pour optimiser les performances de l'antenne. La figure 9 montre le prototype réalisé.

Figure 9. Prototype de module LTCC encapsulé dans un enclos métallique; à gauche vue en perspective, à droite vue de côté [20] © [2014]

#### I.2.2.7 Boitier MCM

Un module MCM (Multi-Chip Module) permet d'encapsuler plusieurs CIs sur le même substrat et obtenir ainsi un ensemble de composants intégrés dans une même boitier, d'où le nom Multi Chip Module. Ce boitier est caractérisé par une structure multicouche ce qui donne une forme générale 3 D. Cette encapsulation existe sous trois formes différentes : MCM-L, MCM-D et MCM-C, qui diffèrent selon le type de substrat utilisé.

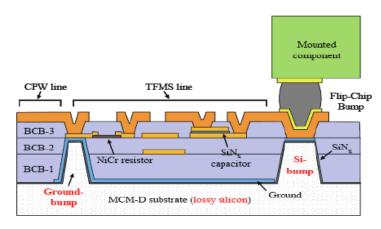

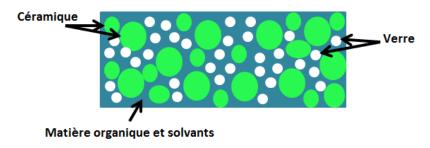

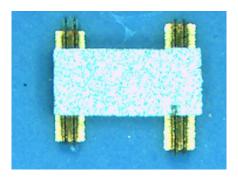

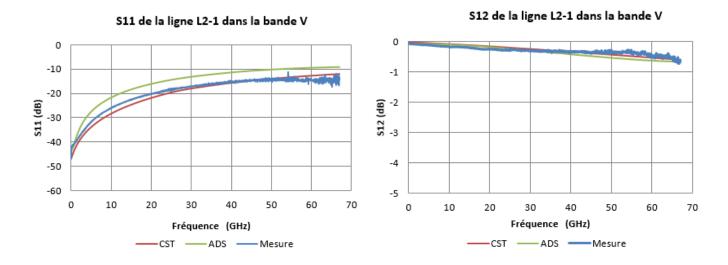

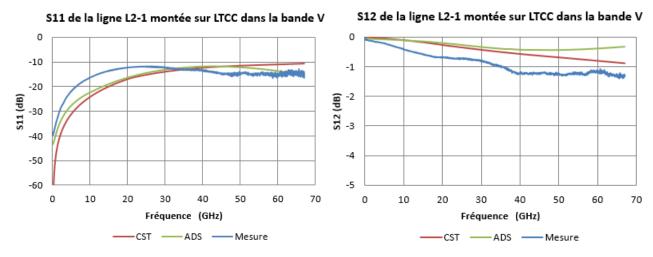

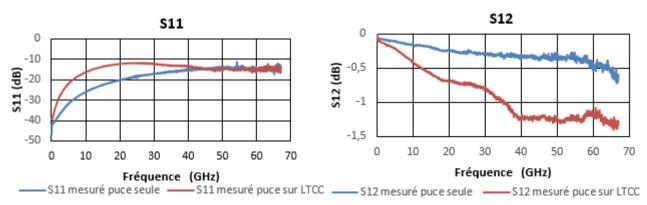

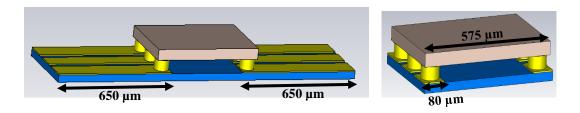

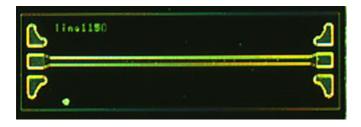

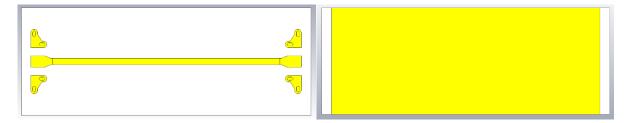

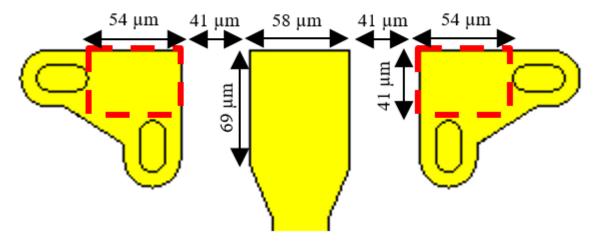

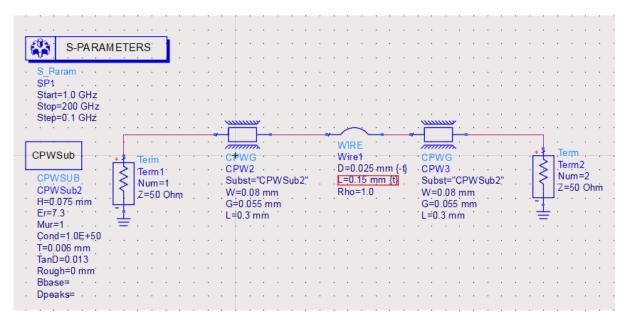

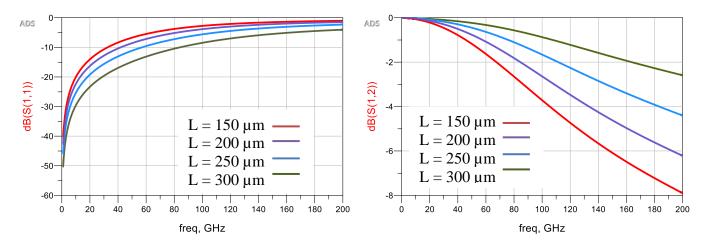

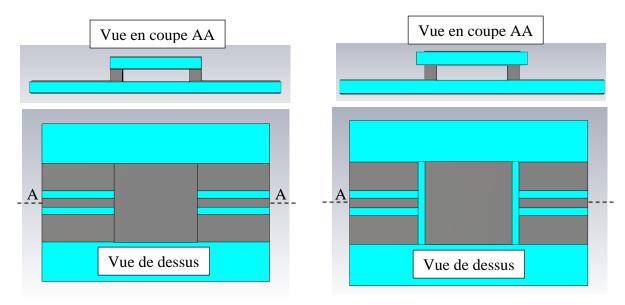

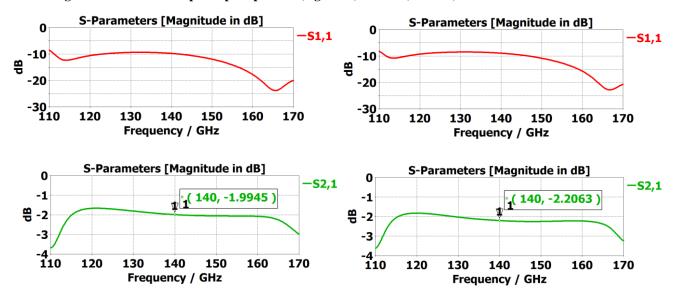

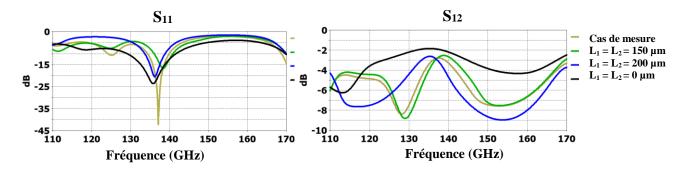

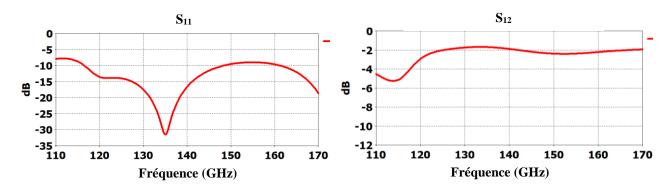

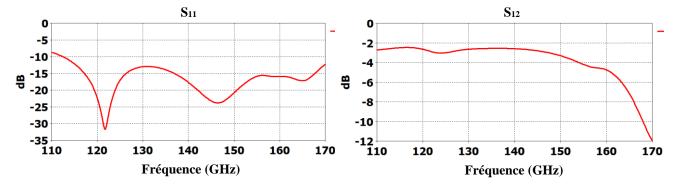

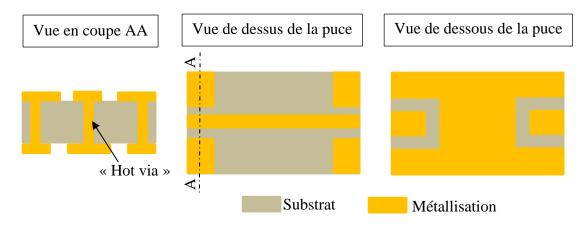

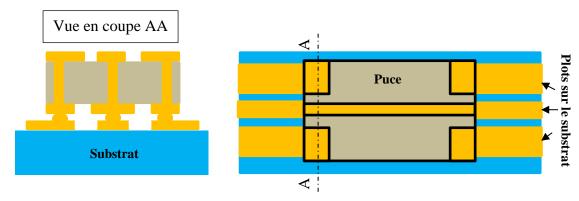

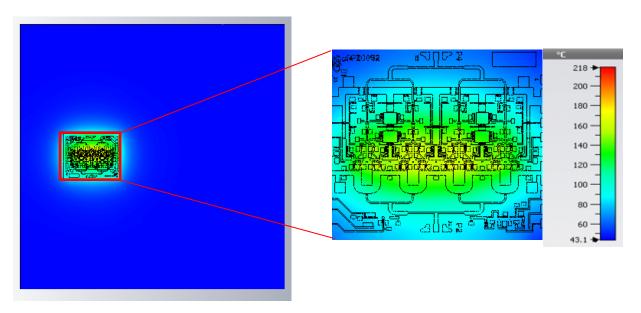

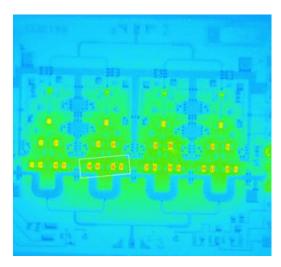

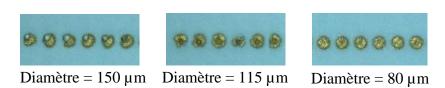

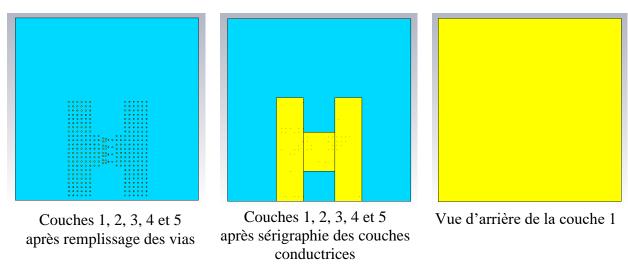

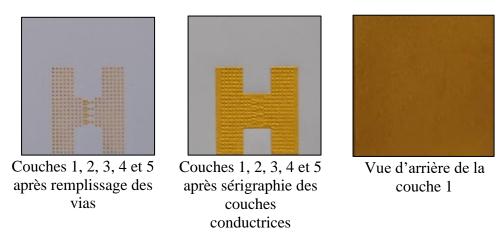

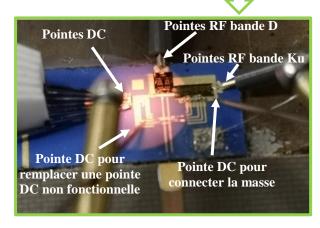

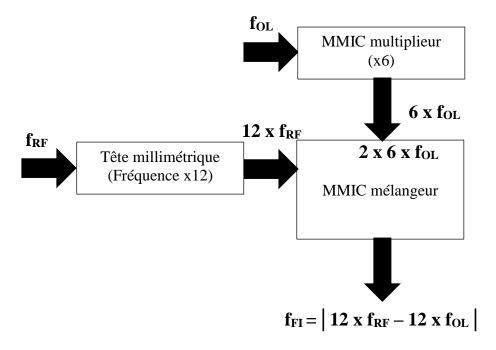

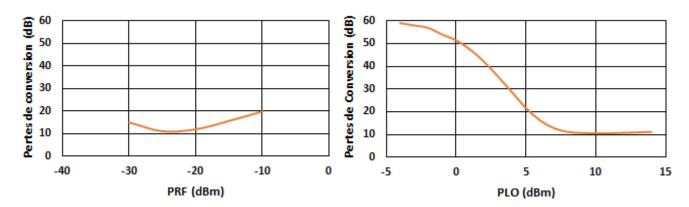

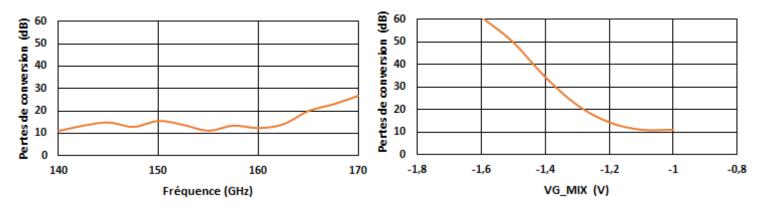

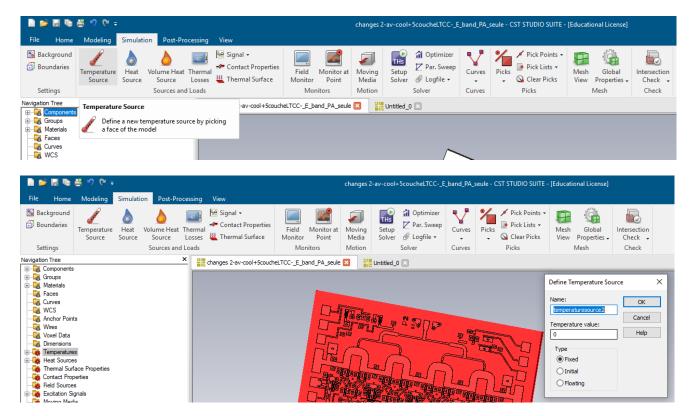

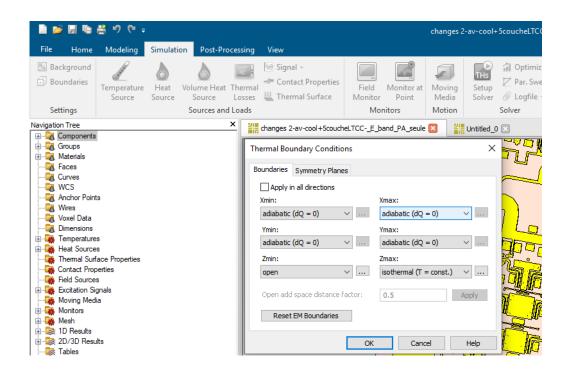

#### • MCM-L