# Contribution to the integration of supervisory control theory in a model-based system engineering method Xiaoshan Lu

#### ▶ To cite this version:

Xiaoshan Lu. Contribution to the integration of supervisory control theory in a model-based system engineering method. Automatic. Universit\'e de Lyon, 2019. English. NNT: 2019LYSEI072. tel-02570617

## HAL Id: tel-02570617 https://theses.hal.science/tel-02570617

Submitted on 12 May 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT: 2019LYSEI072

#### THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de INSA Lyon

# **Ecole Doctorale** N° 160 **Electronique Electrotechnique Automatique (EEA)**

#### Spécialité Automatique

Soutenue publiquement le 18/09/2019, par : **Xiaoshan Lu**

## Contribution to the Integration of Supervisory Control Theory in a Model-Based System Engineering Method

#### Devant le jury composé de :

Berruet, Pascal Professeur des Université de Rapporteur

Universités Bretagne Sud

Carré-Ménétrier, Professeur des Université de Rapporteuse

Véronique Universités Reims

Niel, Eric Professeur INSA de Lyon Directeur de thèse

Piétrac, Laurent Maître de INSA de Lyon Co-directeur de thèse

Conférences HDR

## Département FEDORA – INSA Lyon - Ecoles Doctorales – Quinquennal 2016-2020

| SIGLE     | ECOLE DOCTORALE                                                                                                                                                                                      | NOM ET COORDONNEES DU RESPONSABLE                                                                                                                                                                                                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СНІМІЕ    | CHIMIE DE LYON  http://www.edchimie-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage secretariat@edchimie-lyon.fr INSA: R. GOURDON                                                         | M. Stéphane DANIELE Institut de recherches sur la catalyse et l'environnement de Lyon IRCELYON-UMR 5256 Équipe CDFA 2 Avenue Albert EINSTEIN 69 626 Villeurbanne CEDEX directeur@edchimie-lyon.fr                                                                                          |

| E.E.A.    | ÉLECTRONIQUE, ÉLECTROTECHNIQUE, AUTOMATIQUE http://edeea.ec-lyon.fr Sec.: M.C. HAVGOUDOUKIAN ecole-doctorale.eea@ec-lyon.fr                                                                          | M. Gérard SCORLETTI École Centrale de Lyon 36 Avenue Guy DE COLLONGUE 69 134 Écully Tél: 04.72.18.60.97 Fax 04.78.43.37.17 gerard.scorletti@ec-lyon.fr                                                                                                                                     |

| E2M2      | ÉVOLUTION, ÉCOSYSTÈME, MICROBIOLOGIE, MODÉLISATION  http://e2m2.universite-lyon.fr Sec.: Sylvie ROBERJOT Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 INSA: H. CHARLES secretariat.e2m2@univ-lyon1.fr | M. Philippe NORMAND UMR 5557 Lab. d'Ecologie Microbienne Université Claude Bernard Lyon 1 Bâtiment Mendel 43, boulevard du 11 Novembre 1918 69 622 Villeurbanne CEDEX philippe.normand@univ-lyon1.fr                                                                                       |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-SANTÉ  http://www.ediss-lyon.fr Sec.: Sylvie ROBERJOT Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 INSA: M. LAGARDE secretariat.ediss@univ-lyon1.fr                       | Mme Sylvie RICARD-BLUM Institut de Chimie et Biochimie Moléculaires et Supramoléculaires (ICBMS) - UMR 5246 CNRS - Université Lyon 1 Bâtiment Curien - 3ème étage Nord 43 Boulevard du 11 novembre 1918 69622 Villeurbanne Cedex Tel: +33(0)4 72 44 82 32 sylvie.ricard-blum@univ-lyon1.fr |

| INFOMATHS | INFORMATIQUE ET MATHÉMATIQUES  http://edinfomaths.universite-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage Tél: 04.72.43.80.46 infomaths@univ-lyon1.fr                                  | M. Hamamache KHEDDOUCI Bât. Nautibus 43, Boulevard du 11 novembre 1918 69 622 Villeurbanne Cedex France Tel: 04.72.44.83.69 hamamache.kheddouci@univ-lyon1.fr                                                                                                                              |

| Matériaux | MATÉRIAUX DE LYON http://ed34.universite-lyon.fr Sec.: Stéphanie CAUVIN Tél: 04.72.43.71.70 Bât. Direction ed.materiaux@insa-lyon.fr                                                                 | M. Jean-Yves BUFFIÈRE INSA de Lyon MATEIS - Bât. Saint-Exupéry 7 Avenue Jean CAPELLE 69 621 Villeurbanne CEDEX Tél: 04.72.43.71.70 Fax: 04.72.43.85.28 jean-yves.buffiere@insa-lyon.fr                                                                                                     |

| MEGA      | MÉCANIQUE, ÉNERGÉTIQUE, GÉNIE CIVIL, ACOUSTIQUE  http://edmega.universite-lyon.fr Sec.: Stéphanie CAUVIN Tél: 04.72.43.71.70 Bât. Direction mega@insa-lyon.fr                                        | M. Jocelyn BONJOUR INSA de Lyon Laboratoire CETHIL Bâtiment Sadi-Carnot 9, rue de la Physique 69 621 Villeurbanne CEDEX jocelyn.bonjour@insa-lyon.fr                                                                                                                                       |

| ScSo      | ScSo* http://ed483.univ-lyon2.fr Sec.: Véronique GUICHARD INSA: J.Y. TOUSSAINT Tél: 04.78.69.72.76 veronique.cervantes@univ-lyon2.fr                                                                 | M. Christian MONTES Université Lyon 2 86 Rue Pasteur 69 365 Lyon CEDEX 07 christian.montes@univ-lyon2.fr                                                                                                                                                                                   |

## **Contents**

| 1 | Introduction                                                 | 1  |

|---|--------------------------------------------------------------|----|

|   | 1.1 Context and Motivations                                  | 1  |

|   | 1.2 Contributions                                            | 3  |

|   | 1.3 Outline                                                  | 3  |

| 2 | Research Context and Problem Statement                       | 5  |

|   | 2.1 Introduction                                             | 5  |

|   | 2.2 Supervisory Control Theory                               | 5  |

|   | 2.2.1 Goals of SCT                                           | 6  |

|   | 2.2.2 Theoretical Concepts                                   | 11 |

|   | 2.2.3 SCT-Based Modeling Process: Principles and Limitations | 17 |

|   | 2.2.4 Summary                                                | 25 |

|   | 2.3 Model-Based System Engineering                           | 26 |

|   | 2.3.1 Overview                                               | 26 |

|   | 2.3.2 Standard                                               | 28 |

|   | 2.3.3 Methods                                                | 29 |

|   | 2.3.4 Modeling Language                                      | 34 |

|   | 2.3.5 State of the Art                                       | 39 |

|   | 2.3.6 Summary                                                | 40 |

|   | 2.4 Challenges of Proposed Integrated Approach for AC        | 41 |

|   | 2.4.1 Formal Models and Semi-Formal Models                   | 41 |

|   | 2.4.2 Modeling Process for AC                                | 44 |

|   | 2.4.3 Integrating concepts                                   | 46 |

|   | 2.5 Conclusion                                               | 47 |

| 3 | Proposed Modeling Framework                                  | 49 |

|   | 3.1 Introduction                                             | 49 |

|   | 3.2 Integrated Architecture                                  | 50 |

| 3.2.1 Objective                                           | 50  |

|-----------------------------------------------------------|-----|

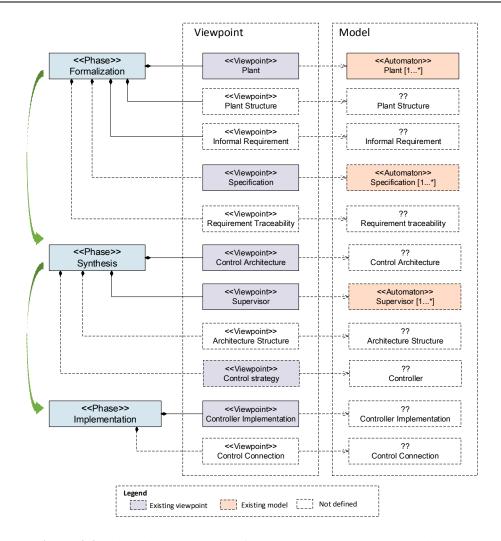

| 3.2.2 Architecture: Viewpoint, View and Model             | 51  |

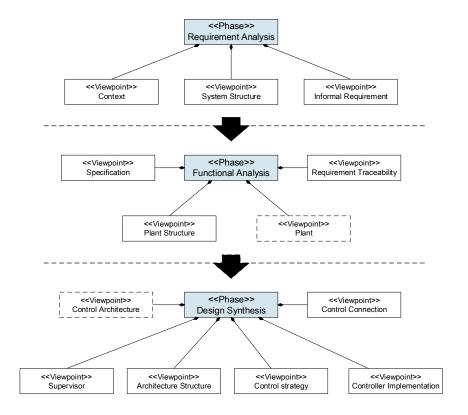

| 3.2.3 Viewpoints for AC                                   | 52  |

| 3.2.4 Integration in MBSE Process                         | 54  |

| 3.2.5 Model Definitions                                   | 56  |

| 3.2.6 Summary                                             | 60  |

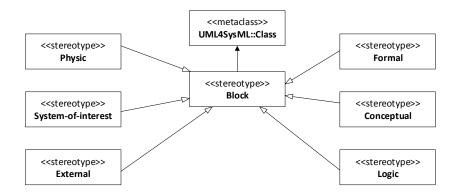

| 3.3 SysML Profile for AC                                  | 60  |

| 3.3.1 Objective                                           | 60  |

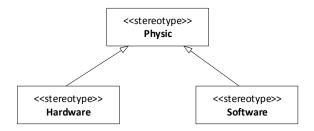

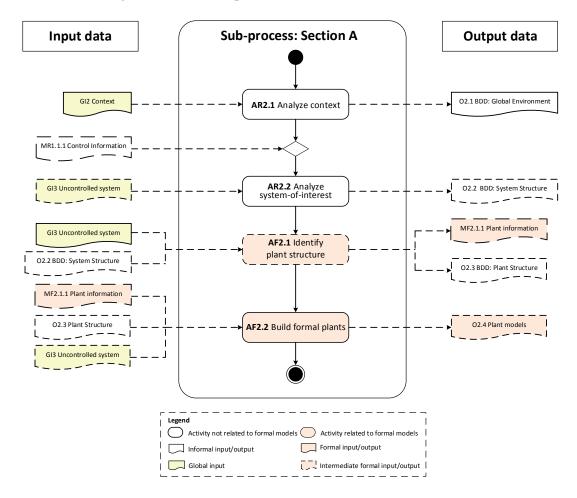

| 3.3.2 Block Extension                                     | 61  |

| 3.3.3 Block for Formal Model                              | 62  |

| 3.3.4 Relationship Extension                              | 63  |

| 3.3.5 Summary                                             | 64  |

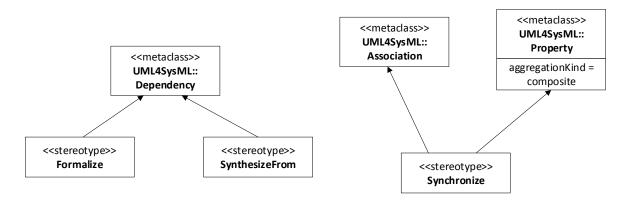

| 3.4 Global Modeling Process                               | 64  |

| 3.4.1 Overview                                            | 64  |

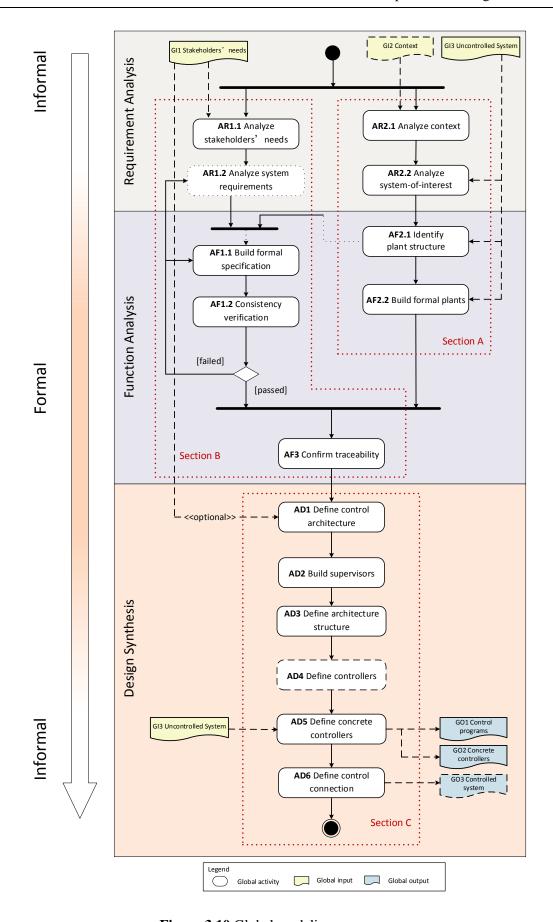

| 3.4.2 Sub-process: Section A                              | 68  |

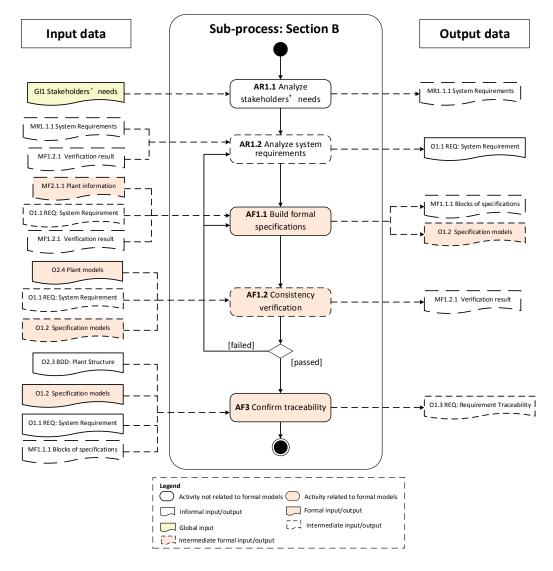

| 3.4.3 Sub-process: Section B                              | 76  |

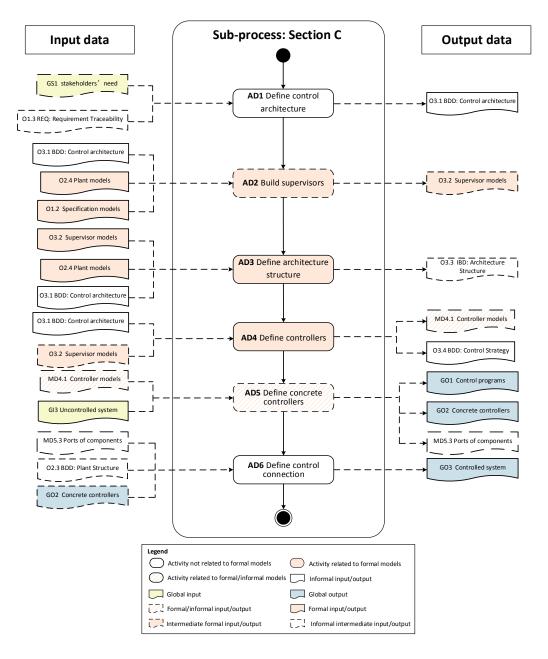

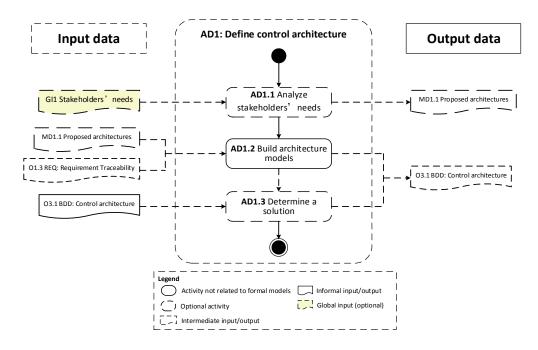

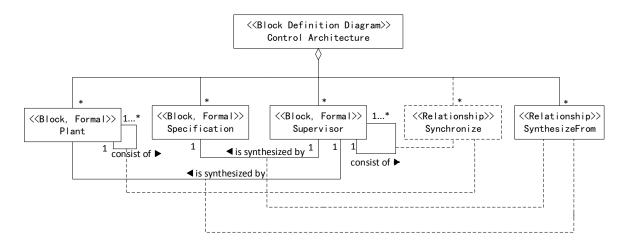

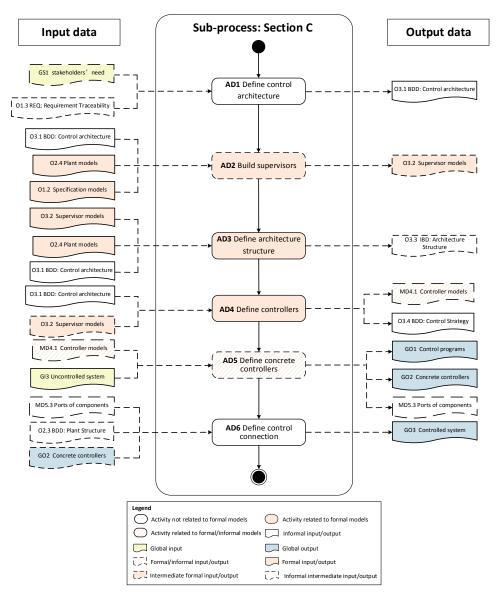

| 3.4.4 Sub-process: Section C                              | 82  |

| 3.5 Conclusion                                            | 93  |

| Consistency of Formal Models and SysML Models             | 95  |

| 4.1 Introduction                                          | 95  |

| 4.2 Consistency of Plants and Physic System               | 95  |

| 4.2.1 Concepts                                            | 96  |

| 4.2.2 Identification Process                              | 100 |

| 4.2.3 Template-Based Approach                             | 102 |

| 4.2.4 Summary                                             | 106 |

| 4.3 Consistency of Formal Specifications and Requirements | 107 |

| 4.3.1 E-specification                                     | 107 |

| 4.3.2 E-Requirement                                       | 108 |

| 4.3.3 Requirement Definition Diagram                      | 109 |

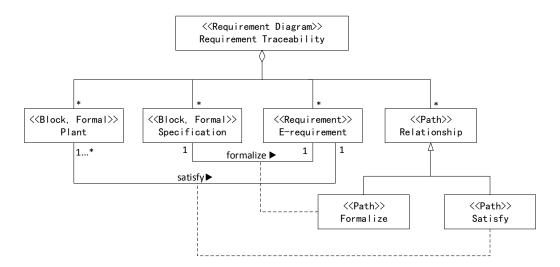

| 4.3.4 Requirement Traceability                            | 110 |

| 4.4 Conclusion                                            | 118 |

| 5 | 5 Application                                            | 121 |

|---|----------------------------------------------------------|-----|

|   | 5.1 Introduction                                         | 121 |

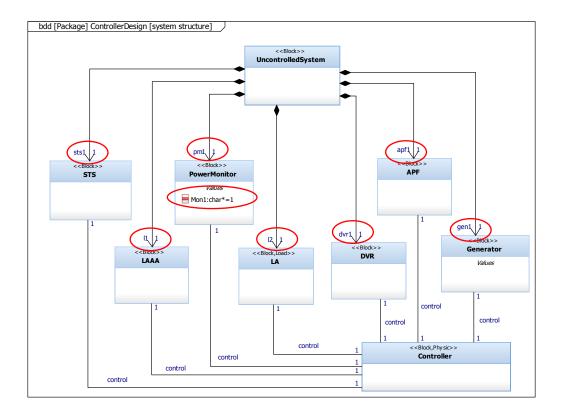

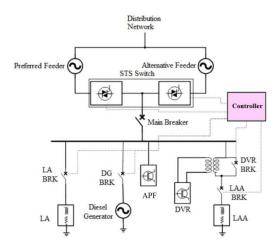

|   | 5.2 System Description                                   | 121 |

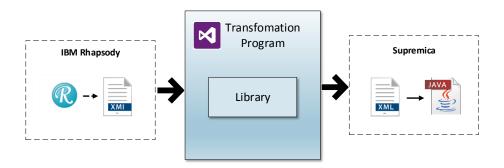

|   | 5.3 Tool Support                                         | 123 |

|   | 5.4 Modeling Results                                     | 124 |

|   | 5.4.1.1 Requirement Analysis                             | 124 |

|   | 5.4.1.2 Functional Analysis                              | 129 |

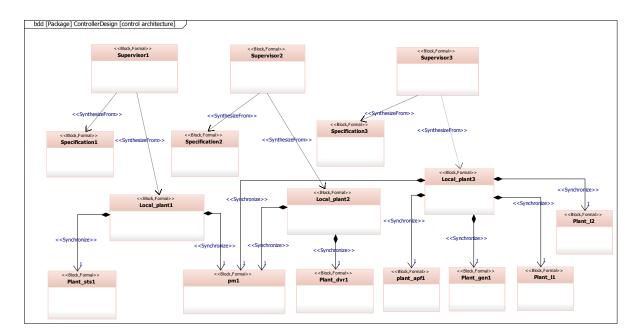

|   | 5.4.1.3 Design Synthesis                                 | 138 |

|   | 5.5 Conclusion                                           | 145 |

| 6 | 6 General Conclusion                                     | 147 |

|   | 6.1 Conclusion                                           | 147 |

|   | 6.2 Expectation                                          | 149 |

| В | Bibliography                                             | 151 |

| A | A Review on Supervisory Control Theory                   | 165 |

|   | A.1 Formal Language                                      | 165 |

|   | A.2 Automaton                                            | 166 |

|   | A.3 Examples of Specification                            | 168 |

|   | A.4 Supervisor Properties.                               | 169 |

|   | A.5 Supervisor Synthesis Algorithm                       | 170 |

| В | 3 Supplementary Results for Case Study                   | 173 |

|   | B.1 Specifications                                       | 173 |

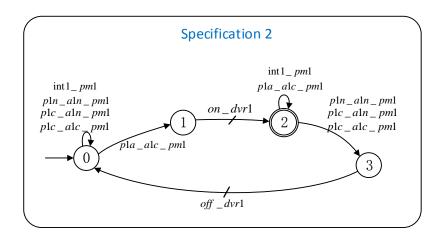

|   | B.1.1 Specification 2                                    | 173 |

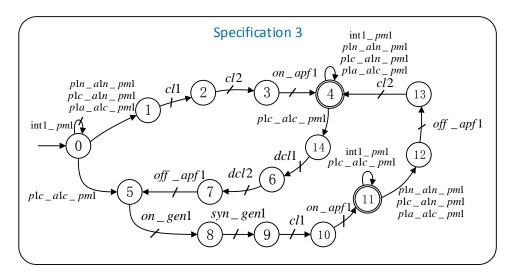

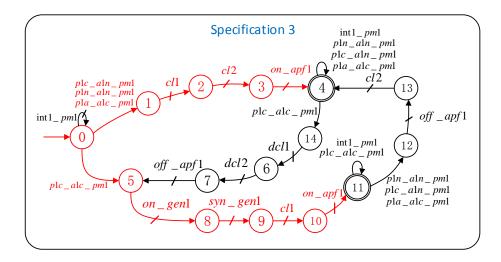

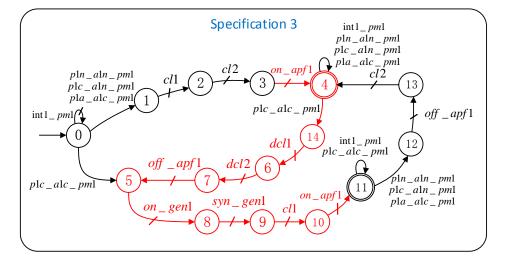

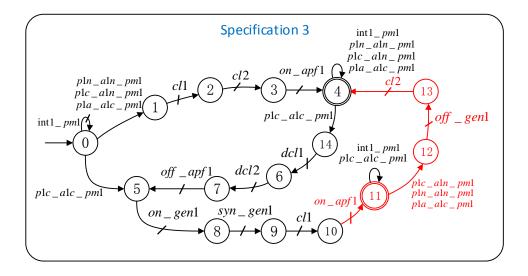

|   | B.1.2 Specification 3                                    | 174 |

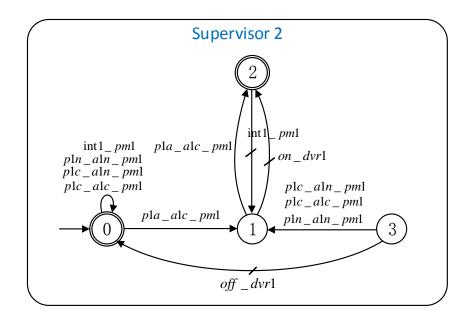

|   | B.2 Supervisors                                          | 176 |

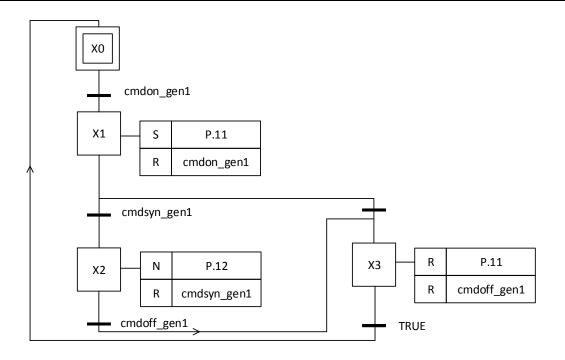

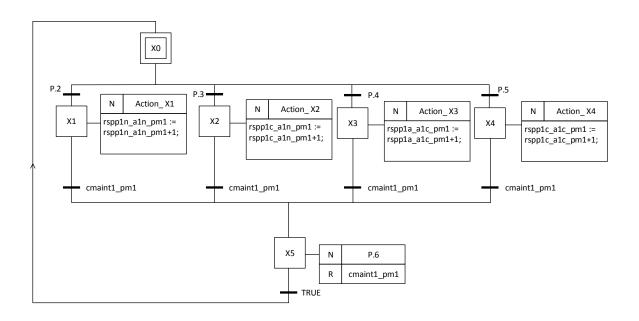

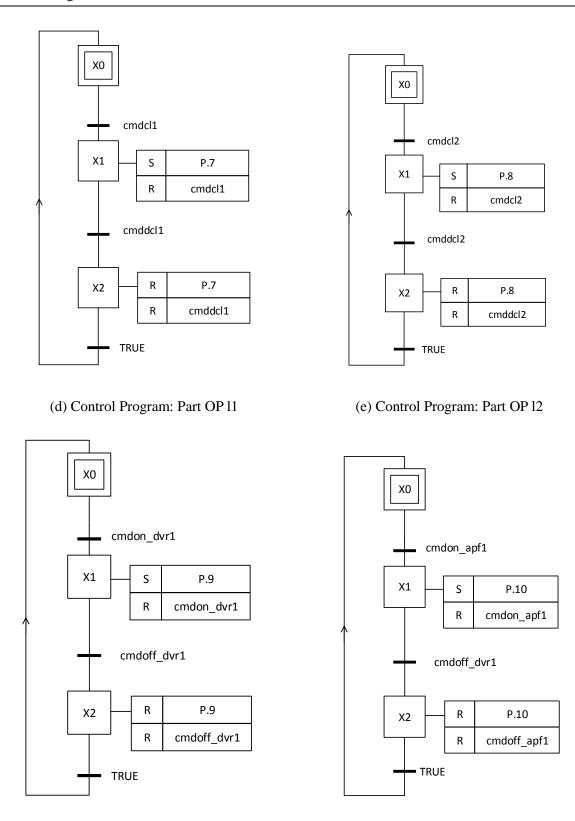

|   | B.3 Control Program                                      | 177 |

|   | B.4 Discussion on Supplementary Situations               | 185 |

|   | B.4.1 Structured Component                               | 185 |

|   | B.4.2 Modeling Process of Section A'                     | 186 |

|   | B.4.3 Local Modular Control Architecture                 | 190 |

|   | B.4.4 Distributed Concrete Controller                    | 191 |

| C | C R & um é                                               | 195 |

|   | C.1 Introduction àla Théorie du Contr de par Supervision | 195 |

|   | C.1.1 Contexte                                           | 195 |

| C.1.2 Concepts Th éoriques                                      | 195 |

|-----------------------------------------------------------------|-----|

| C.1.3 Mise en Œuvre                                             | 197 |

| C.2 Probl ématique                                              | 198 |

| C.3 MBSE                                                        | 202 |

| C.4 Verrous Scientifiques                                       | 206 |

| C.5 Cadre de Mod disation Propos é                              | 210 |

| C.5.1 Définitions de Modèle                                     | 210 |

| C.5.2 Processus de Mod disation Propos é                        | 213 |

| C.6 Coh érence des Mod des Formels et des Mod des SysML         | 219 |

| C.6.1 Coh érence des Proc éd és et du Système Physique          | 219 |

| C.6.2 Coh érence des sp écifications formelles et des exigences | 222 |

| C.7 Étude de Cas                                                | 224 |

| C.8 Conclusion                                                  | 233 |

# List of Figures

| 2.1 Partial classification of system [34]                            | 6  |

|----------------------------------------------------------------------|----|

| 2.2 The feedback loop of supervisory control                         | 14 |

| 2.3 Control architectures                                            | 16 |

| 2.4 Activities and models involved in AC development process for DES | 18 |

| 2.5 Basic Principle of Logic Controller                              | 19 |

| 2.6 Engineering process with supervisory control synthesis [41]      | 25 |

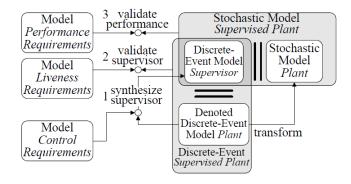

| 2.7 Integrated framework in proposition [69]                         | 25 |

| 2.8 A partial systems engineering standards taxonomy [80]            | 27 |

| 2.9 V-model                                                          | 30 |

| 2.10 Processes comparison                                            | 32 |

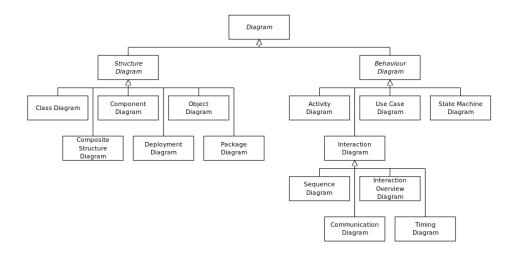

| 2.11 UML diagram taxonomy                                            | 35 |

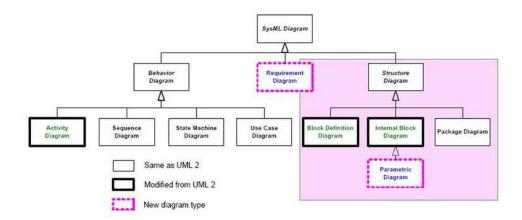

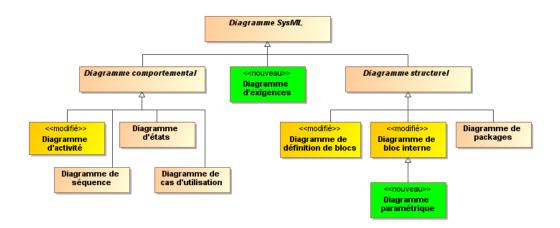

| 2.12 SysML diagram taxonomy                                          | 36 |

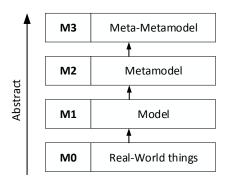

| 2.13 Model-driven architecture                                       | 45 |

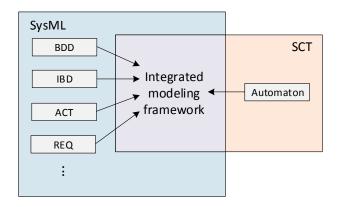

| 3.1 Model integration                                                | 50 |

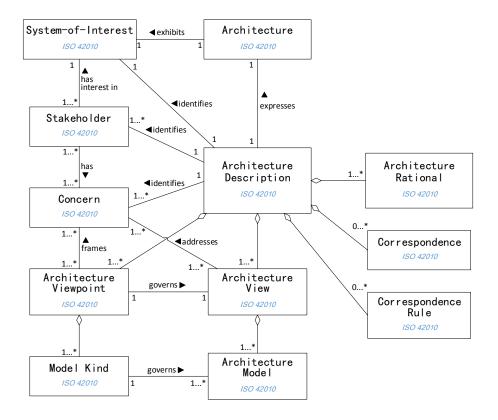

| 3.2 Concept Model of ISO 42010 [85]                                  | 52 |

| 3.3 Viewpoints and models for the adapted SCT-based architecture     | 54 |

| 3.4 Viewpoints allocated to the MBSE process                         | 56 |

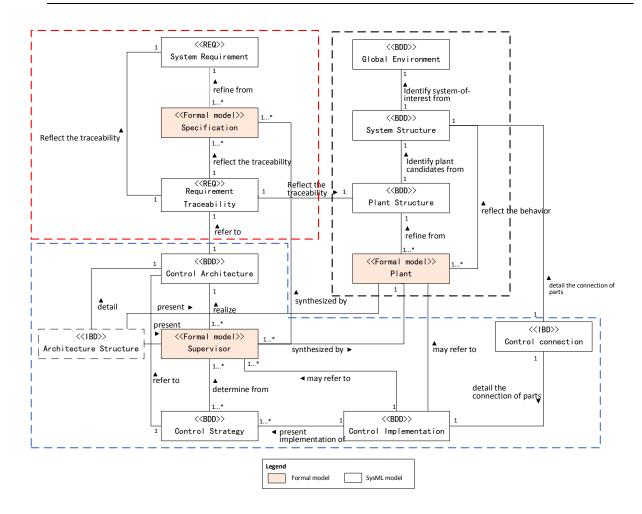

| 3.5 Definition and links of models                                   | 59 |

| 3.6 Extension of block                                               | 61 |

| 3.7 Extension of stereotype << Physic>>                              | 62 |

| 3.8 Block stereotyped by < <formal>&gt;</formal>                     | 62 |

| 3.9 Relationship extension                                           | 63 |

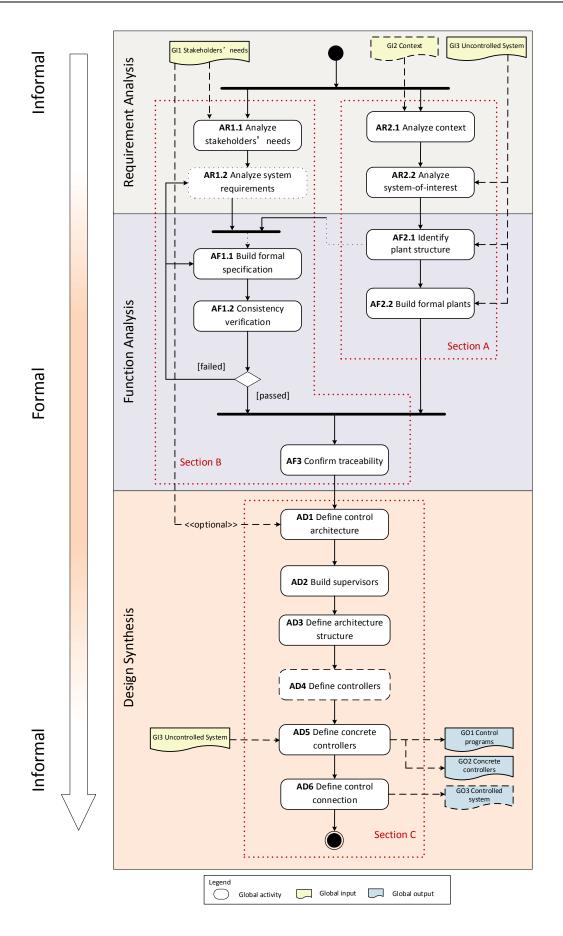

| 3.10 Global modeling process                                         | 67 |

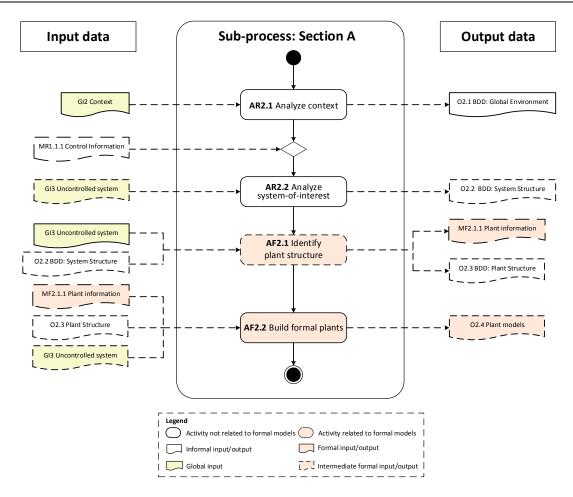

| 3.11 Workflow of sub-process of Section A                            | 68 |

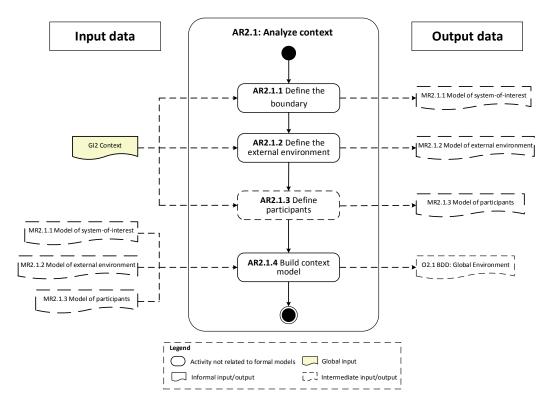

| 3.12 Workflow of activity AR2.1                                      | 69 |

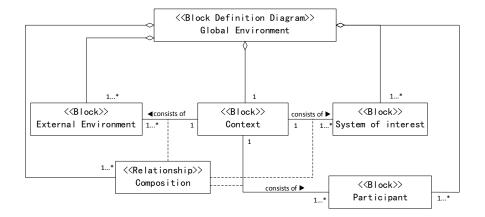

| 3.13 Metamodel of BDD: Global Environment                            | 70 |

| 3.14 Definition of system-of-interest                                | 70 |

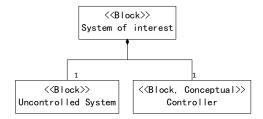

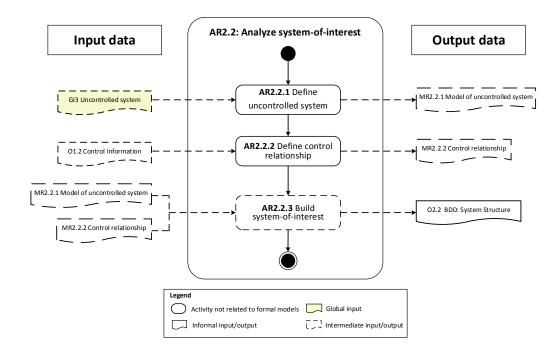

| 3.15 Workflow of sub-process of activity AR2.2                | 71  |

|---------------------------------------------------------------|-----|

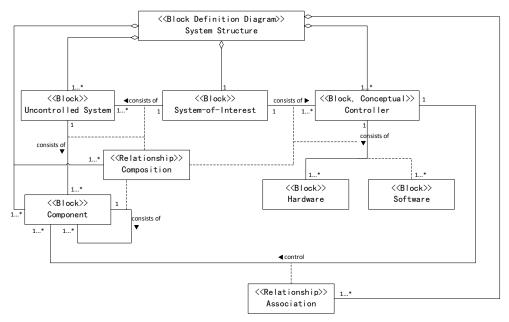

| 3.16 Metamodel of BDD: System Structure                       | 72  |

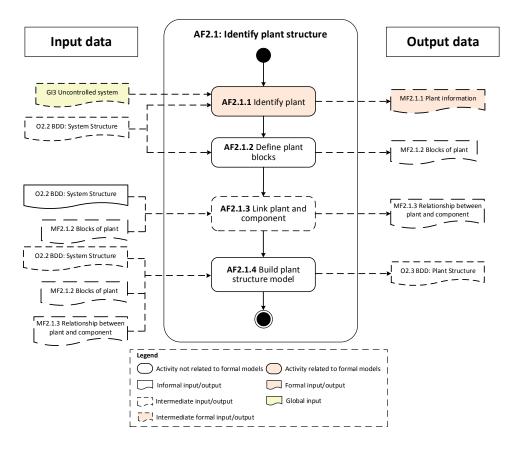

| 3.17 Workflow of sub-process of activity AF2.1                | 73  |

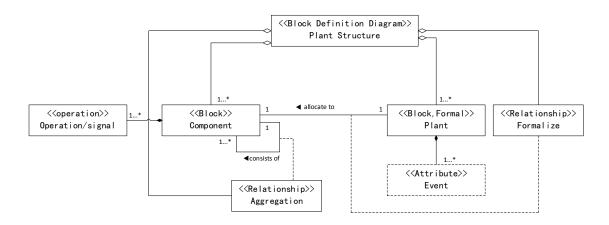

| 3.18 Metamodel of BDD: Plant Structure                        | 74  |

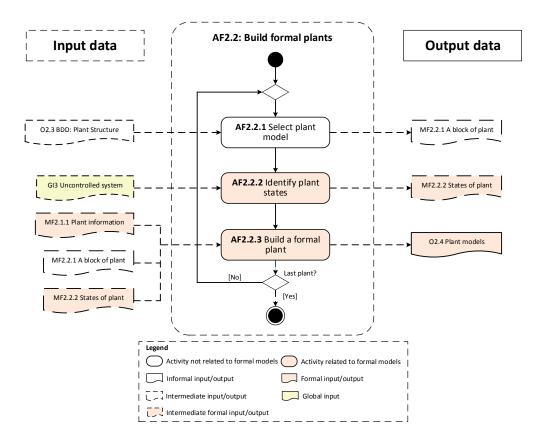

| 3.19 Workflow of sub-process of activity AF2.2                | 75  |

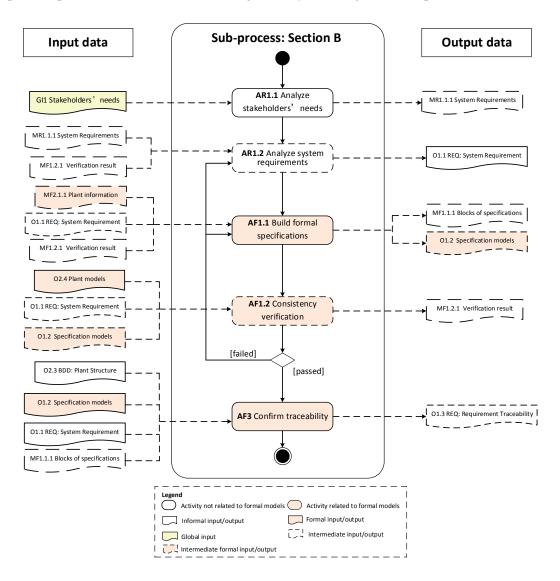

| 3.20 Workflow of sub-process of Section B                     | 76  |

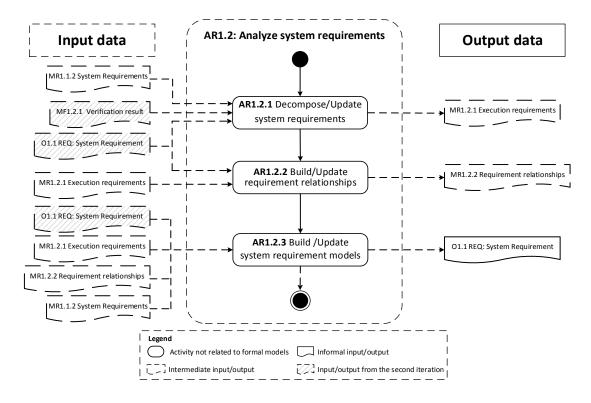

| 3.21 Workflow of sub-process of activity AR1.2                | 78  |

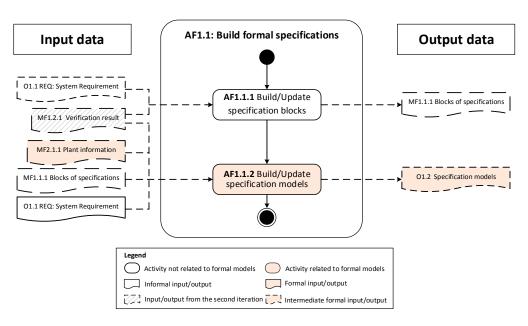

| 3.22 Workflow of sub-process of activity AF1.1                | 79  |

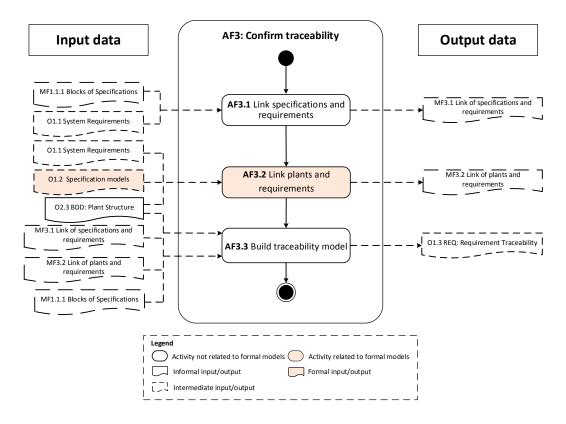

| 3.23 Workflow of sub-process of activity AF3                  | 81  |

| 3.24 Metamodel of REQ: Requirement Traceability               | 81  |

| 3.25 Workflow of sub-process of Section C                     | 83  |

| 3.26 Workflow of sub-process of activity AD1                  | 84  |

| 3.27 Metamodel of BDD: Control Architecture                   | 85  |

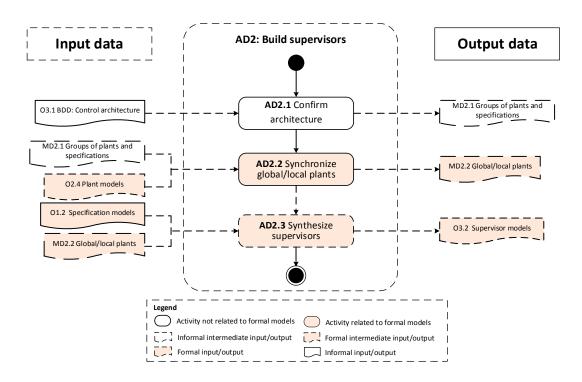

| 3.28 Workflow of sub-process of activity AD2                  | 86  |

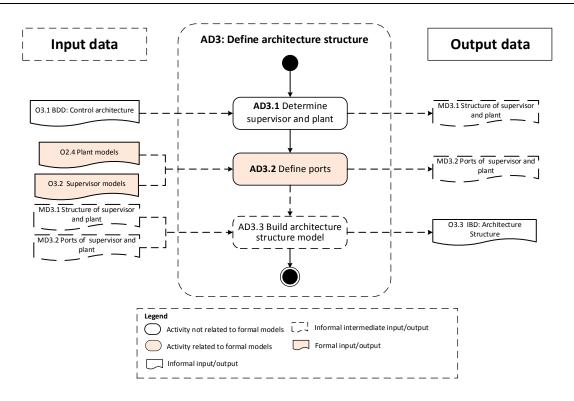

| 3.29 Workflow of sub-process of activity AD3                  | 87  |

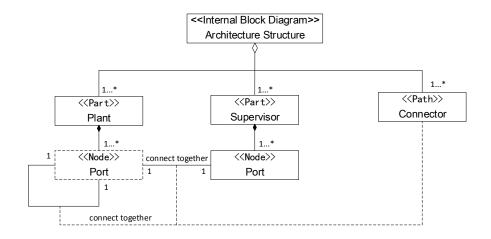

| 3.30 Metamodel of IBD: Architecture Structure                 | 87  |

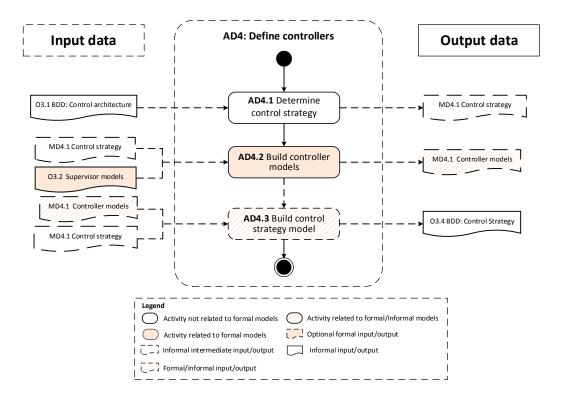

| 3.31 Workflow of sub-process of activity AD4                  | 88  |

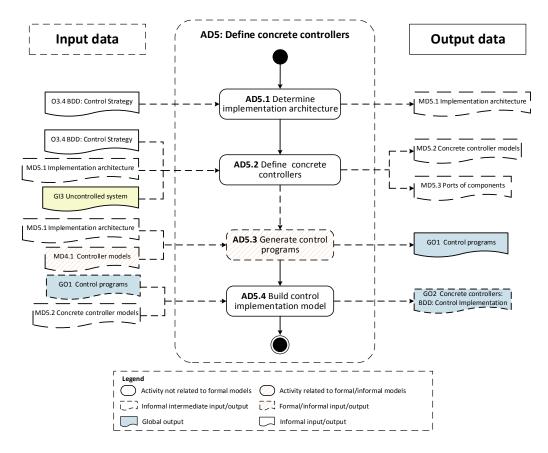

| 3.32 Workflow of sub-process of activity AD5                  | 89  |

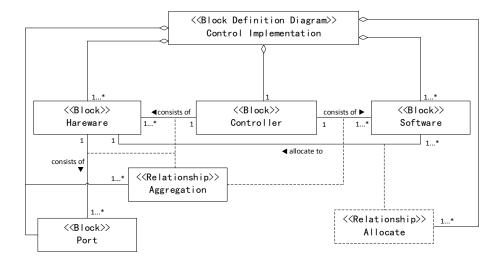

| 3.33 Metamodel of Control Implementation                      | 91  |

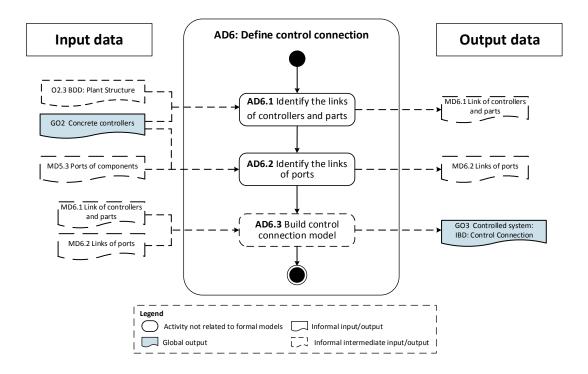

| 3.34 Workflow of sub-process of activity AD6                  | 91  |

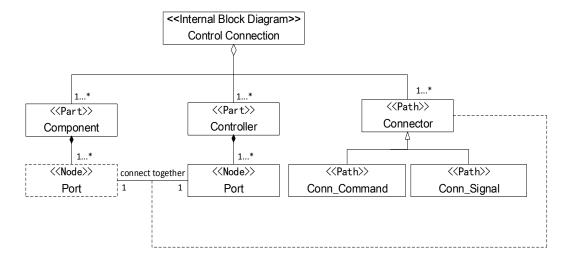

| 3.35 Metamodel of IBD: Control Connection                     | 92  |

| 4.1 Schematic of link between physic system and formal models | 96  |

| 4.2 Example of link between events and model elements         | 97  |

| 4.3 Composition identification of physic component            | 98  |

| 4.4 Example of orthogonal sub-system                          | 99  |

| 4.5 Robot with two degrees of freedom                         | 101 |

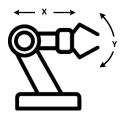

| 4.6 Plants of robot R1                                        | 101 |

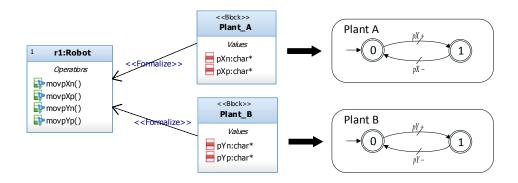

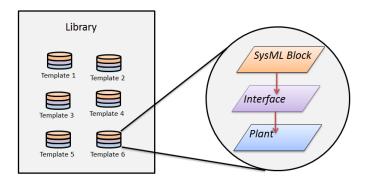

| 4.7 Schematic of the three-level template and library         | 103 |

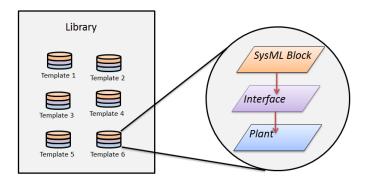

| 4.8 Example of parameterized component                        | 104 |

| 4.9 Program architecture                                      | 105 |

| 4.10 Transformation process                                   | 106 |

| 4.11 Metamodel of E-Requirement                               | 109 |

| 4.12 Metamodel of requirement diagram                         | 110 |

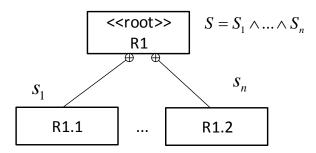

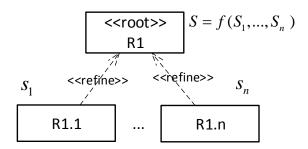

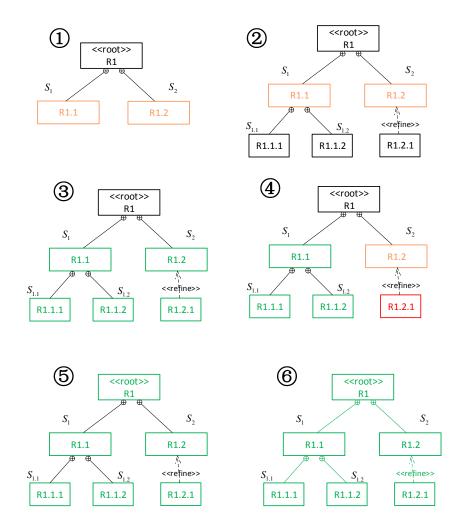

| 4.13 Semantic of two formalisms                                | . 112 |

|----------------------------------------------------------------|-------|

| 4.14 Requirement decomposition by < <contain>&gt;</contain>    | . 114 |

| 4.15 Requirement decomposition by < <refine>&gt;</refine>      | . 115 |

| 4.16 Example of analysis R1                                    | . 116 |

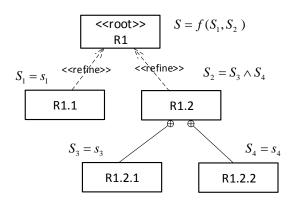

| 4.17 Workflow of sub-process of AF1.2                          | . 118 |

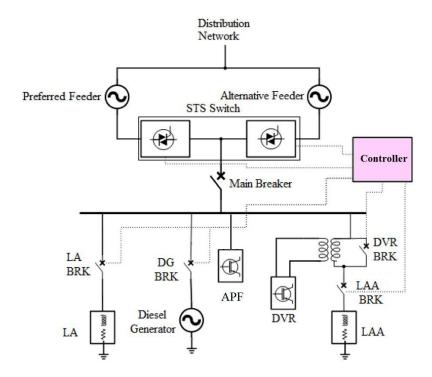

| 5.1 Custom Power Park [19]                                     | . 122 |

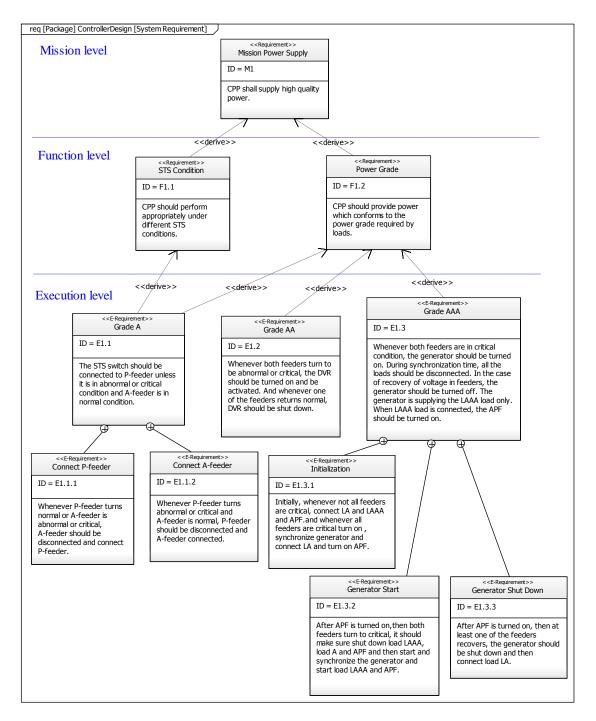

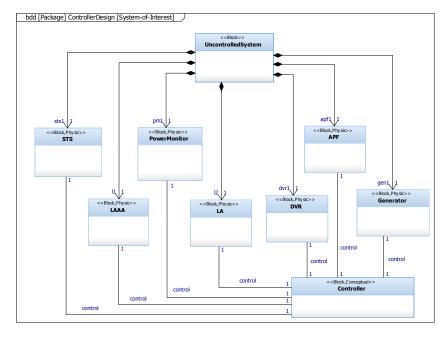

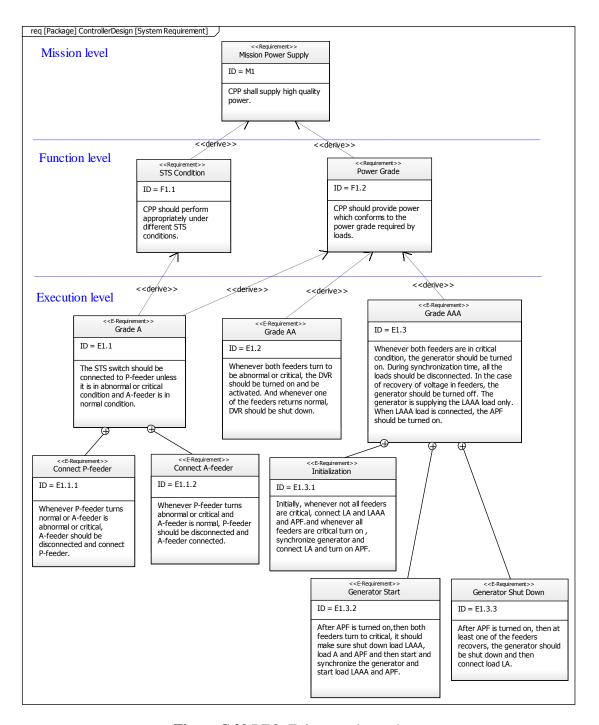

| 5.2 REQ: System Requirement                                    | . 127 |

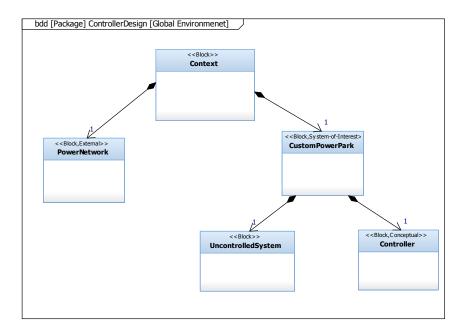

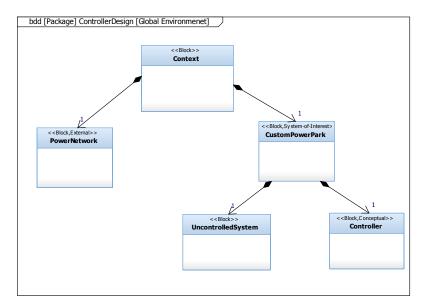

| 5.3 BDD: Global Environment                                    | . 128 |

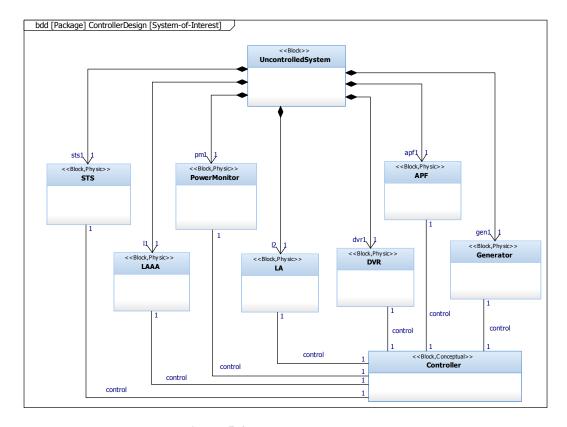

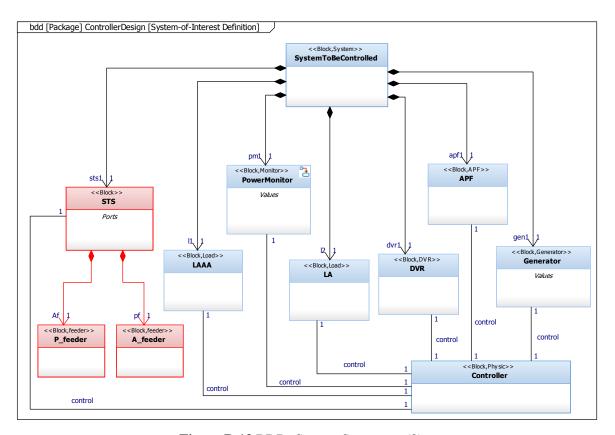

| 5.4 BDD: System Structure                                      | . 129 |

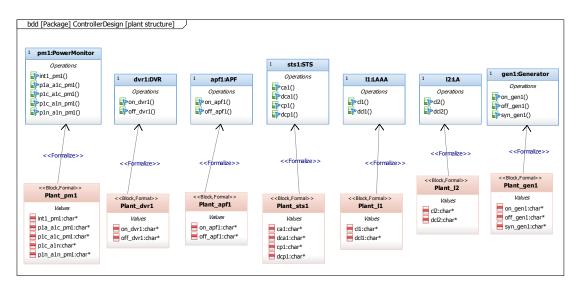

| 5.5 BDD: Plant Structure                                       | . 131 |

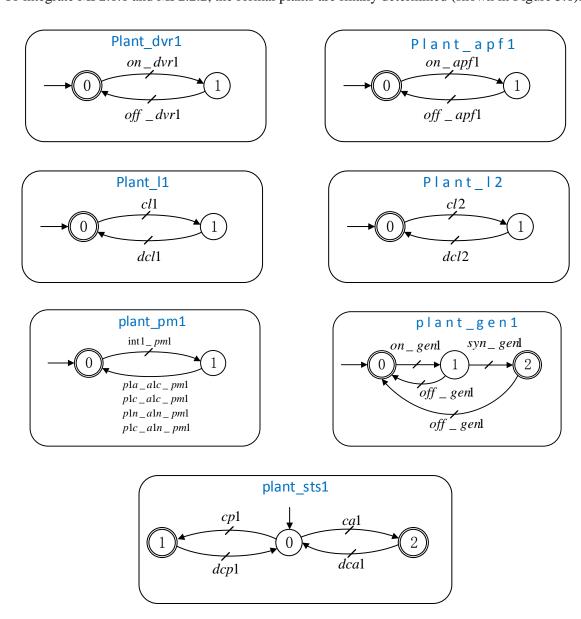

| 5.6 Plant model                                                | . 132 |

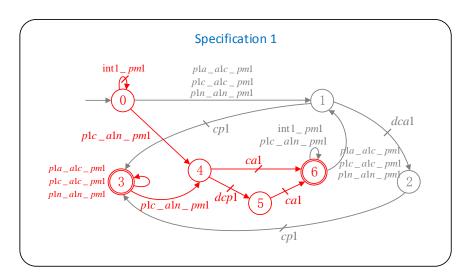

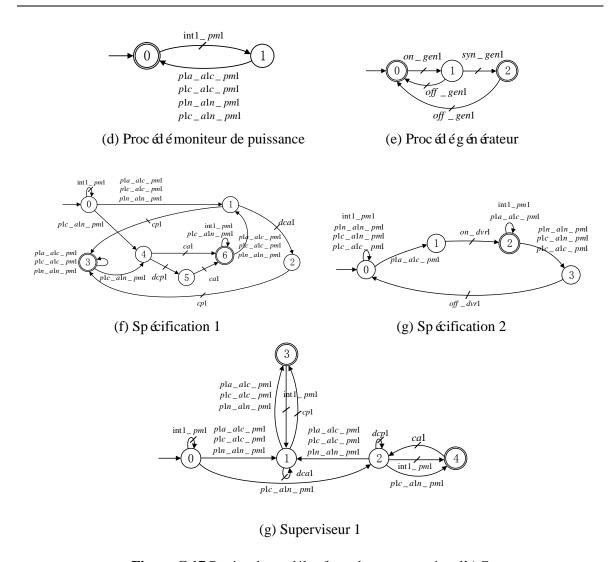

| 5.7 Specification 1                                            | . 133 |

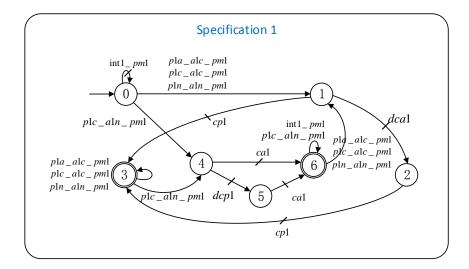

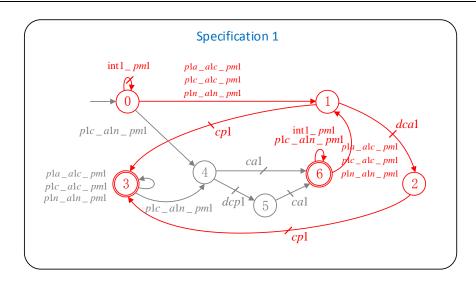

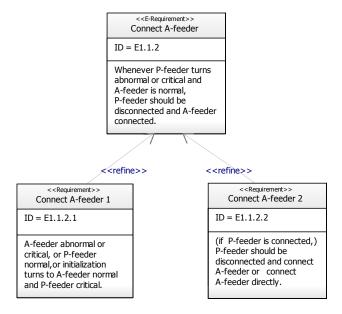

| 5.8 Decomposition of requirement E1.1.1                        | . 134 |

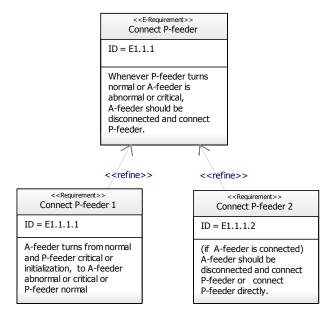

| 5.9 Consistency verification for E1.1.1                        | . 135 |

| 5.10 Decomposition of requirement E1.1.2                       | . 135 |

| 5.11 Consistency verification for E1.1.2                       | . 136 |

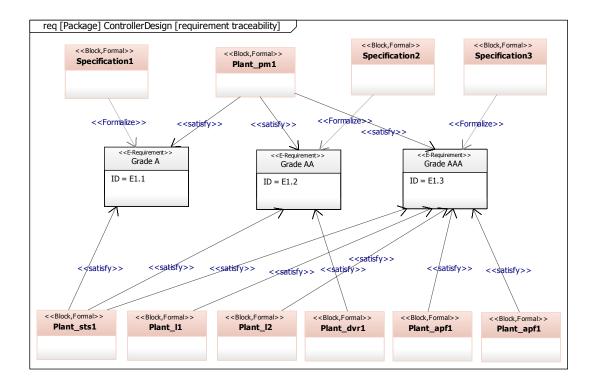

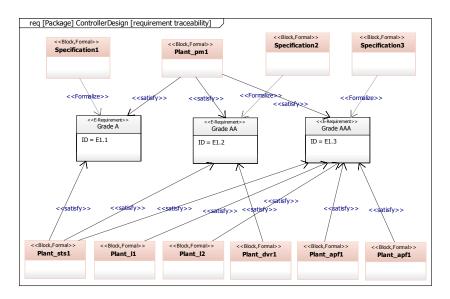

| 5.12 REQ: Requirement Traceability                             | . 137 |

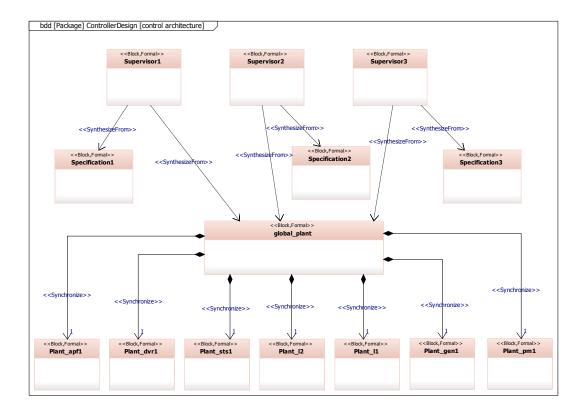

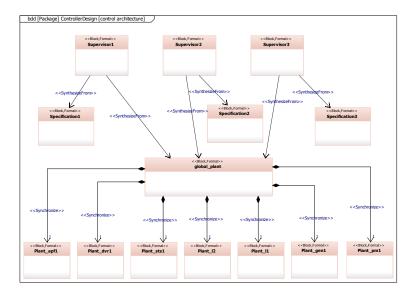

| 5.13 BDD: Control Architecture                                 | . 138 |

| 5.14 Model of supervisor 1                                     | . 139 |

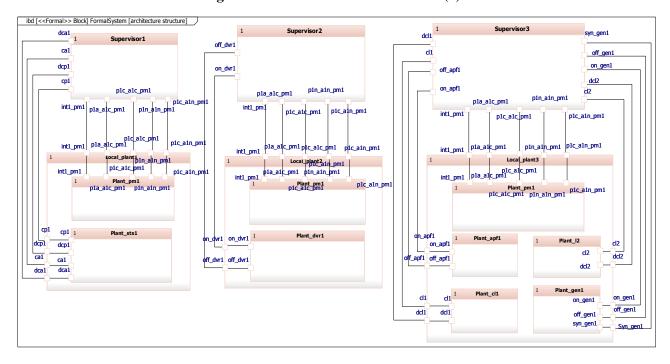

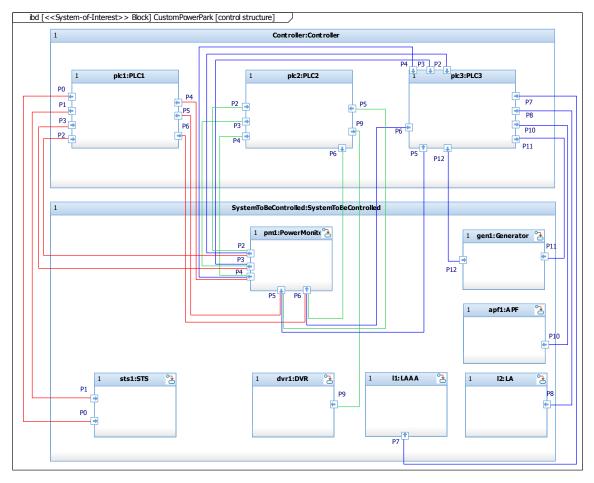

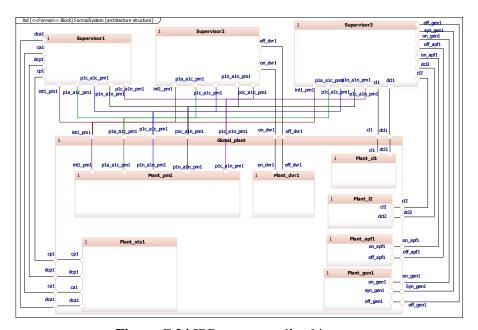

| 5.15 IBD: Architecture Structure                               | . 140 |

| 5.16 BDD: Controller Strategy                                  | . 141 |

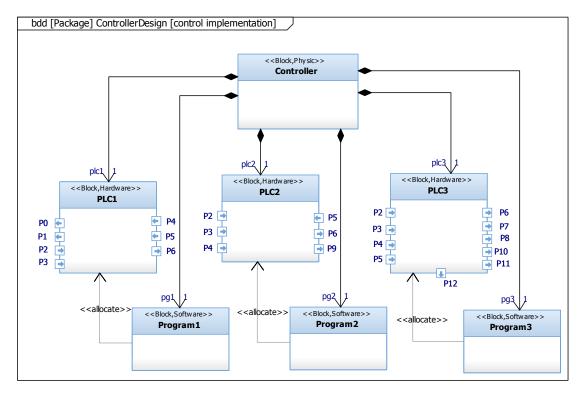

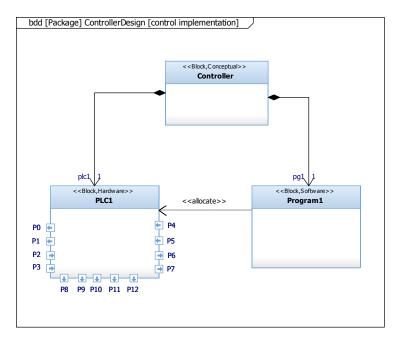

| 5.17 GO2 BDD: Control Implementation                           | . 142 |

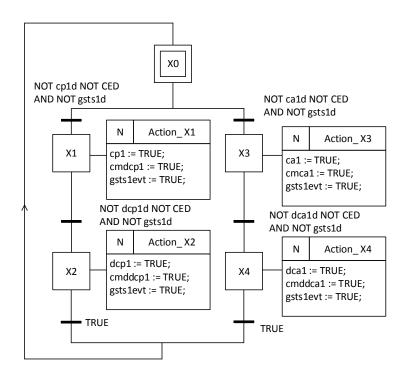

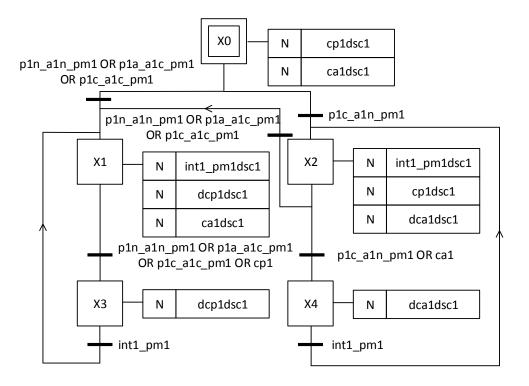

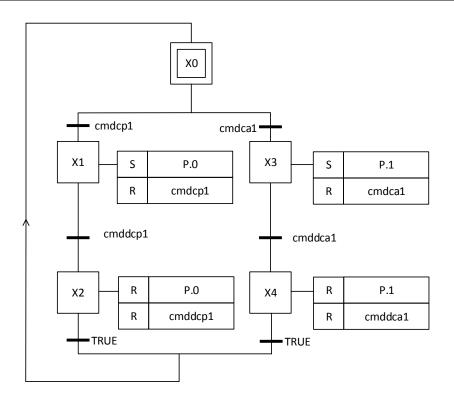

| 5.18 Control Program: Part PS sts1                             | . 143 |

| 5.19 Control Program: Part MS Sup1                             | . 143 |

| 5.20 GO1 Control Program: Part OP sts1                         | . 144 |

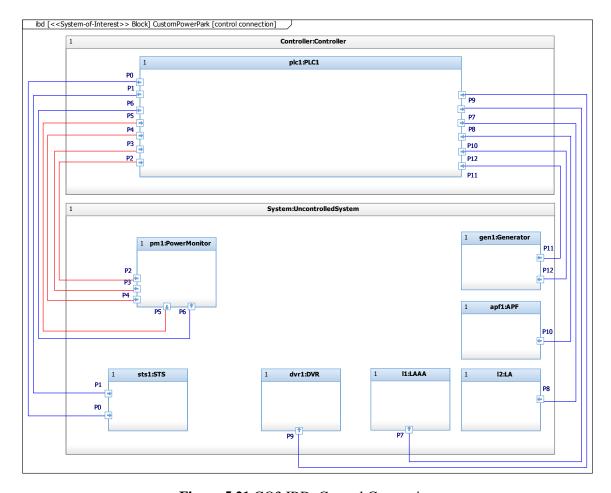

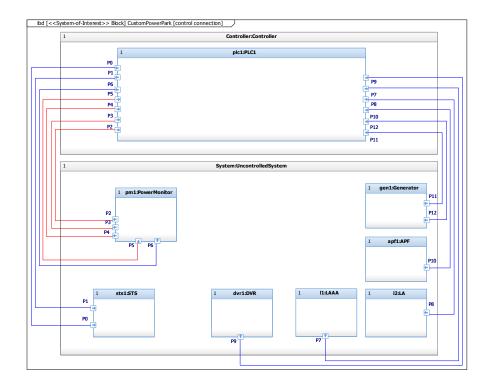

| 5.21 GO3 IBD: Control Connection                               | . 145 |

| 5.22 Comparison between SCT-based process and proposed process | . 146 |

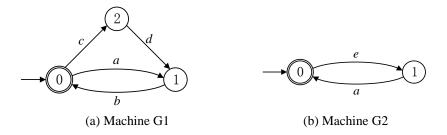

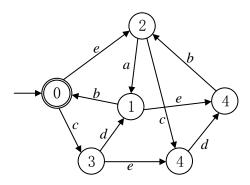

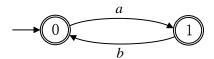

| A.1 Two simple automata                                        | . 167 |

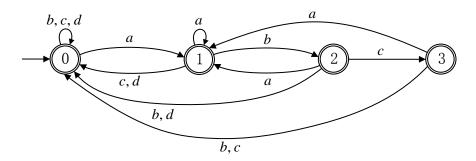

| A.2 Synchronous composition of two simple machines             | . 168 |

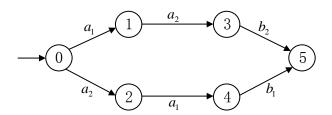

| A.3 State splitting specification                              | . 168 |

| A.4 Event alternation specification                            | . 168 |

| A.5 Illegal substring specification                            |       |

| B.1 Specification 2                                            | . 173 |

|                                                                |       |

| B.2 Specification 3                                              | 174 |

|------------------------------------------------------------------|-----|

| B.3 Consistency verification for E1.3.1                          | 175 |

| B.4 Consistency verification for E1.3.2                          | 175 |

| B.5 Consistency verification for E1.3.3                          | 176 |

| B.6 Model of supervisor 2                                        | 176 |

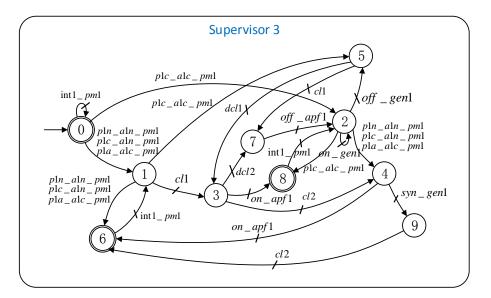

| B.7 STM: Model of supervisor 3                                   | 177 |

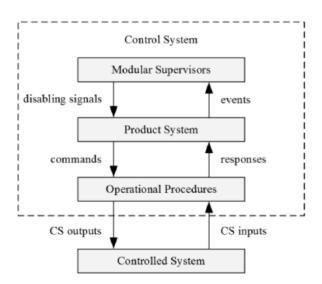

| B.8 Implementation approach of local modular supervisory control | 177 |

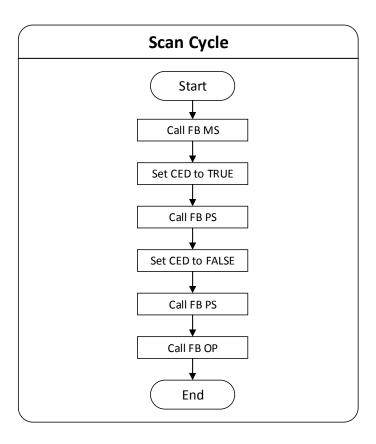

| B.9 Activities in one PLC scan cycle                             | 178 |

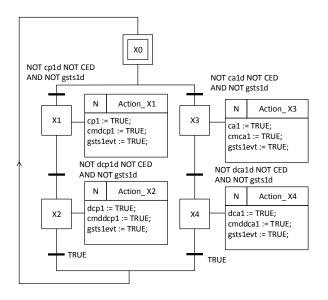

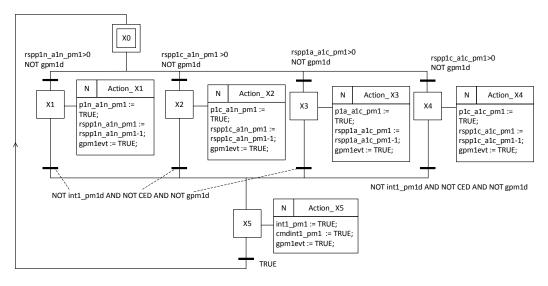

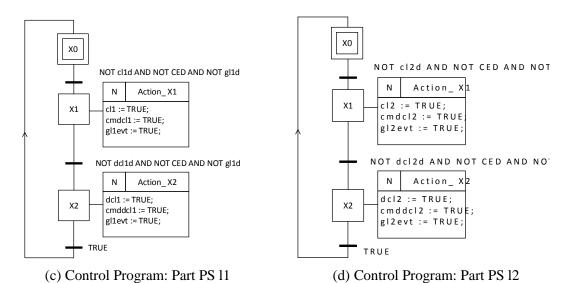

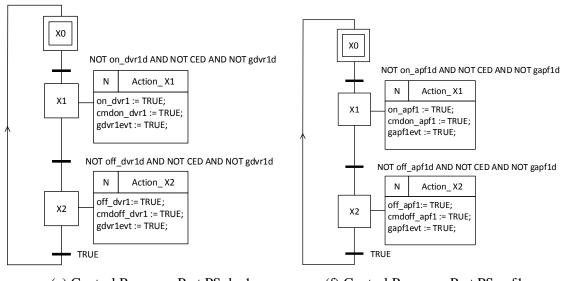

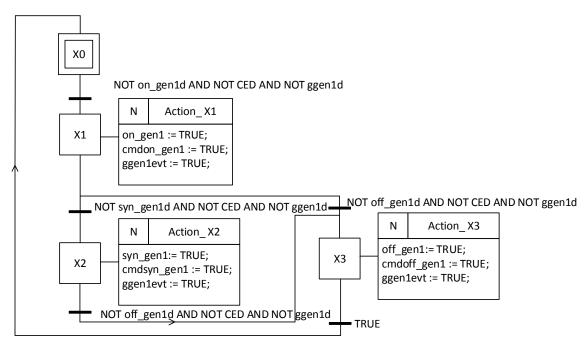

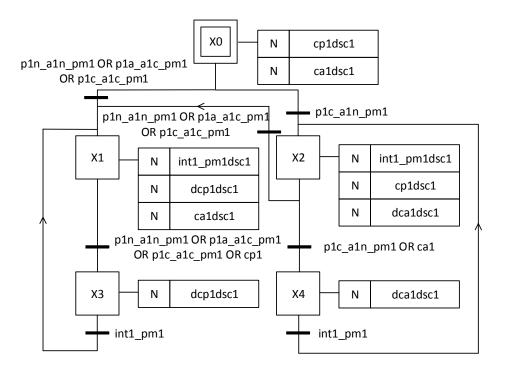

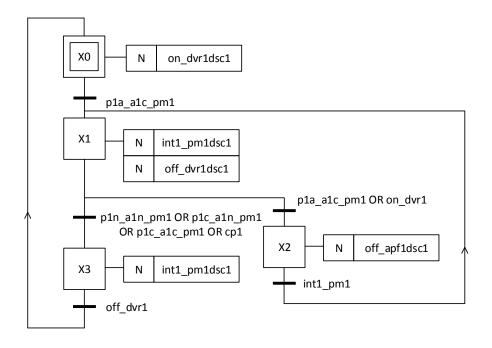

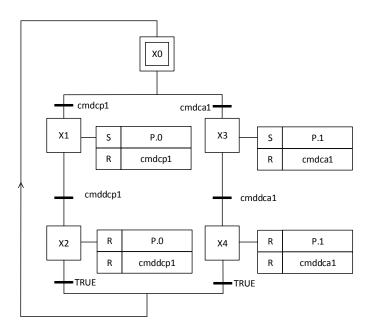

| B.10 Control Program: PS level                                   | 180 |

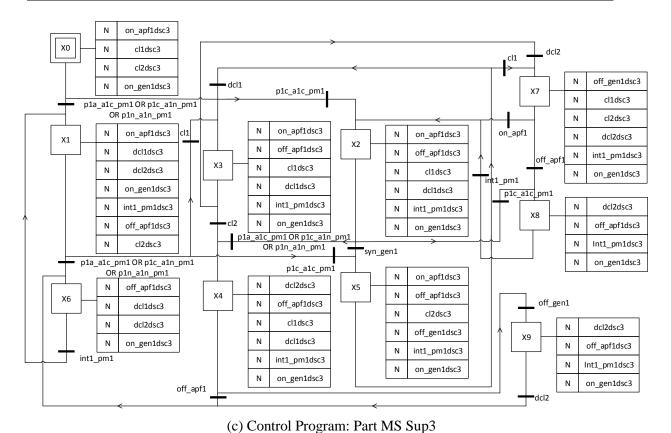

| B.11 Control Program: MS level                                   | 182 |

| B.12 Control Program: OP level                                   | 184 |

| B.13 BDD: System Sturecture (2)                                  | 185 |

| B.14 Plant of STS                                                | 186 |

| B.15 BDD: System Structure (2)                                   | 187 |

| B.16 Implementation framework of transformation.                 | 188 |

| B.17 Partial of the XMI of BDD                                   | 189 |

| B.18 Partial of the XML of formal models                         | 190 |

| B.19 BDD: Control Architecture (2)                               | 191 |

| B.20 IBD: Architecture Structure (2)                             | 191 |

| B.21 GO2 BDD: Control Implementation (2)                         | 192 |

| B 22 GO3 IBD: Control Connection (2)                             | 193 |

## List of Tables

| 2.1 Taxonomy of terminologies                          | 18  |

|--------------------------------------------------------|-----|

| 2.2 A summary of Solutions for implementation problems | 21  |

| 2.3 A summary of possible solutions                    | 40  |

| 3.1 Proposed viewpoints and concerns for AC            | 53  |

| 3.2 Complementary viewpoints and concerns for MBSE     | 55  |

| 3.3 Example plant information list                     | 73  |

| 3.4 A summary of proposed solutions                    | 93  |

| 4.1 List of plant information                          | 101 |

| 4.2 Typical descriptions of E-specifications           | 112 |

| 5.1 Voltage level in feeders                           | 123 |

| 5.2 MR1.1.2 list of system requirements                | 124 |

| 5.3 List of requirements                               | 125 |

| 5.4 List of sub-requirement                            | 126 |

| 5.5 List of components                                 | 129 |

| 5.6 MF2.1.1 Plant information list                     | 130 |

| 5.7 Semantic of state                                  | 131 |

| 5.8 List of involved events in specification 1         | 133 |

| 5.9 Allocation of specification to E-requirement       | 137 |

| 5.10 Allocation plant to E-requirement                 | 137 |

| 5.11 Supervisor synthesis                              | 139 |

| 5.12 Event identification of supervisor                | 139 |

| 5.13 List of control strategies                        | 140 |

| 5.14 MD4.3 Port of controlled components               | 141 |

| B.1 List of templates                                  | 187 |

| B.2 Supervisor synthesis (2)                           | 190 |

| B.3 Port definition for controller                     | 192 |

## Chapter 1

## Introduction

#### 1.1 Context and Motivations

In the field of automatic control system, one of the interesting scientific branches is the study on the control of Discrete Event System (DES), which is extensively involved in different application domains such as manufacture system, electric system, traffic system, etc. DES is an area concerned with systems usually discrete in time and state space, driven by instantaneous events other than (or in addition to) the tick of a clock and 'nondeterministic' in the sense of making state-transitional choices by internal chance or other mechanisms not necessarily modeled by the system analyst [1].

Supervisory Control Theory (SCT), firstly introduced by Ramadge and Wonham in 1987 [2], is one of the most important academic theories for Automatic Control (AC) of DES. With SCT, the requirements which are checked afterward in traditional engineering are used as input for generation of the design of the controller that is correct by construction. By the scientific achievements within the past several decades, the framework of SCT forms a systematically formal paradigm to synthesize controllers for DESs and a series of concepts and methods are proposed, such as supervisor synthesis [3], controllability [4], observability [5], and supremal sublanguage [6] [7]. Attempts to apply SCT to industrial problems encountered the barrier notorious as exponential state space explosion, different control architectures such as modular control and distributed control are consequently proposed by related research works [8-11]. Nowadays, there are still a lot of emerging contributions which continuously push forwards the front edge of SCT. Some contributions focus on the extending SCT to other formal models rather than automata, such as Extended Finite Automata (EFAs) [12] [13], Binary Decision Diagrams (BDDs) [14] and Petri Nets [15] [16], etc. Other contributions are devoted to the study on application of SCT in real systems. The results show that SCT can be widely applied in the control on DESs of different industrial domains, which include a number of case studies such as autonomous robot [17] [18], power management [19] and health care system [20]. In addition,

some researchers study on the implementation architecture of SCT. As PLC (Programmable Logic Controller) plays an important role in industrial automation applications, efforts are made to achieve the implementation by PLC controller [21] [22]. Besides, a part of contributions focus on performing control simulation based on SCT paradigm supported by toolkits such as STATEFLOW [23] [24].

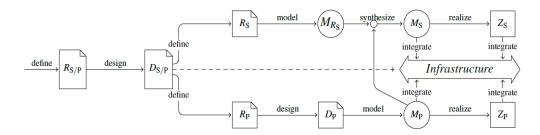

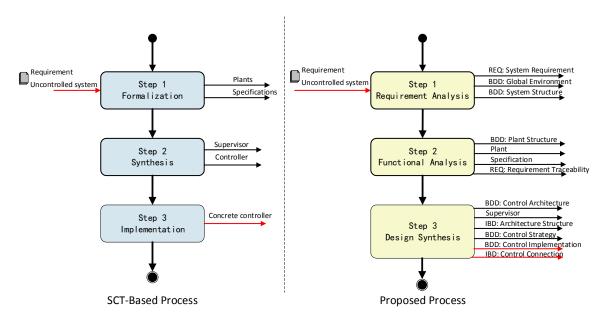

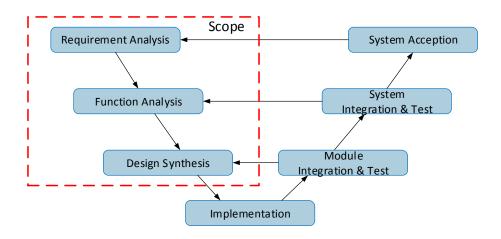

However, despite the academic achievements of SCT, there are still gaps between the theoretical development and applications of SCT in engineering practice. The state-of-the-art SCT-based modeling process for AC is composed of three main phases: formalization, supervisor/controller synthesis and implementation [25]. In this process, SCT provides a theoretical basis for behavior analysis of components and constraints in the form of formal models. On the other hand, the typical system development process in engineering context is usually based on V-model [26-28], which can be divided into a series of phases: requirements analysis, functional analysis, design synthesis, implementation traceability and validation. For each modeling phase of V-model, a variety of models are built to present the different aspects of the studied system including structure, requirements, function and behavior, etc. Compared with V-model, several issues can be found in the typical SCT-based process:

- The formal models of SCT just represents the behavior aspect of the system and the structure models such as concepts, components, the interfaces or interaction can hardly be identified; Besides, there is lack of models representing the traceability within SCT paradigm.

- The SCT doesn't provide the global modeling process from analyzing and decomposing the informal requirements to sub-systems to transform models to implementation.

In fact, the issues above attribute to the limitation of modeling scope of formal model within the SCT paradigm. Therefore, it becomes our focus point in this study that how the modeling scope of SCT paradigm can be extended with the help of other modeling languages and methods so as to form an development framework for AC in engineering practice.

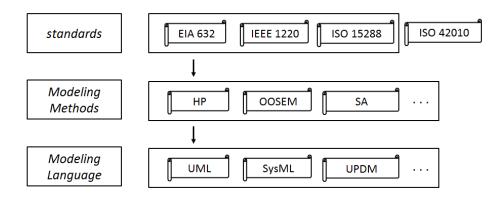

The Model-Based System Engineering (MBSE) provides the possibility to deal with the limitations of SCT. MBSE is the actual state-of-the-art global design process in engineering practice. Some case studies and scientific projects show that MBSE is practical and prospective system development technology [29] [30]. On the other hand, MBSE are supported by a number of methods, modeling languages and toolkits. Compared with conventional engineering process, MBSE provides model-based approaches rather than document-based ones. Particularly, SysML is a general-purpose modeling language for MBSE, which supports the specification, analysis, design, verification and validation of a broad range of systems [31-33]. SysML defines nine kinds of diagram providing comprehensive description for system design, which can be used to cope with the limitation of formal models. The existing modeling propositions are investigated based on

formal language and MBSE method. Unfortunately, all of the existing contributions more or less have their limitations for the target of dealing the limitations of SCT and there is still gap in this research domain. Therefore, in this dissertation, it is of great interest and necessity to propose an integrated modeling framework based on SCT and MBSE.

#### 1.2 Contributions

The main objective of the work is to propose a novel modeling framework for DES AC by combining Supervisory Control Theory with Model-Based System Engineering, in order to overcome the existing limitations of SCT. The main contributions of the work are as following:

- Based on the comparison between SCT-based process and MBSE process, the limitations

of SCT are identified and validated. For the purpose for dealing with the limitations SCT,

this study investigates and analyzes the SysML models which are necessary for AC from

the perspective of MBSE.

- The MBSE modeling framework which integrate SysML models and SCT paradigm is proposed. Ten SysML diagrams are defined to present different aspects of the system description along with the modeling process. A case study is presented to validate the applicability and improvement of the proposed framework compared with typical one.

- The gap of formal model and SysML model are bridged. We investigate concepts and elements exclusively within SCT paradigm, such as controllable/uncontrollable event, plant/specification/supervisor by SysML elements. Besides, the methods of modeling and traceability verification which link formal models and SysML models are proposed.

#### 1.3 Outline

This dissertation is structured as following:

- Chapter 2 presents the state of the art of Supervisor Control Theory and Model-Based Systems Engineering Methods. The typical modeling process of SCT is compared with MBSE process and existing limitations and issues of SCT are discussed. Besides, the possible solutions are reviewed and discussed.

- Chapter 3 introduces the global modeling process of the proposed framework for AC by integrating SCT and MBSE. The necessary models we need to describe a DES control system and the model types which should be used for modeling are analyzed based on the MBSE viewpoint. The details of the proposed framework such as sub-processes, models, activities, methods and input/output of each step are presented.

- Chapter 4 presents the methods for dealing with the consistency problems between formal

models and SysML models faced in the proposed framework. Aimed at formalization of

plants and specifications respectively, different solutions are proposed and detailed in this

chapter.

- Chapter 5 presents a case study based on the proposed modeling framework. A global

design process of controller for Customed Power Park (CPP) and the modeling results for

each step will be detailed. Besides, some more situations will be discussed to verify the

modeling scope of proposed framework.

A conclusion and global perspectives are commented at the end of this dissertation.

## **Chapter 2**

## **Research Context and Problem Statement**

#### 2.1 Introduction

The Supervisory Control Theory (SCT) is one of the most important modeling theories for DES AC. Since the Supervisory Control Theory was introduced by Ramadge and Wonham in 1987 [2], the theory has developed prosperously in the academic field and a large number of contributions come out. The large number of application shows that SCT can be widely used in a variety of academic contexts.

However, despite the academic achievements of SCT over last several decades, there are few application cases in engineering practice. By reviewing related state of the art of SCT paradigm such as the concepts, the supervisor synthesis approach and typical modeling process, the existing limitations which lead to the gap between academic and engineering are recalled. On the other hand, from perspective of the engineering process, the investigation of the model-based system engineering is furthered to specify the limitations of typical modeling process in SCT and the interest and feasibility of integration of MBSE and SCT will be detailed.

In this chapter, based on the reviews on both SCT and MBSE and the comparison of these two domains, the issues and possible solutions will be discussed and the objectives of this study will be presented at the end of this chapter.

## 2.2 Supervisory Control Theory

In this section, the application, theoretical concepts, methods and modeling processes of SCT are reviewed. With regard to the challenge and limitation faced by SCT, existing issues within the SCT paradigm are discussed.

#### 2.2.1 Goals of SCT

#### 2.2.1.1 Automatic Control for Discrete Event System

System is one of those primitive concepts whose understanding can be defined in different ways according to different contexts. There are two common salient features among these definitions. First, a system consists of interacting "components", and second a system is associated with a "function" it is presumably intended to perform [34].

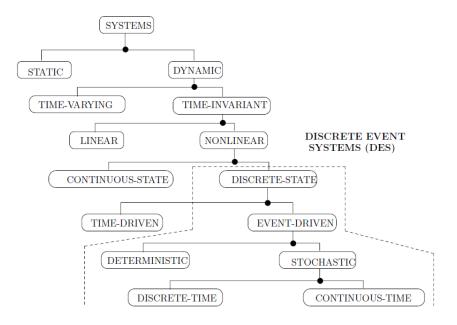

In the scientific domain of automatic control (AC), the model of system can be partially classify in a way shown in Figure 2.1 [34]. In Continuous-Variable Dynamic Systems (CVDS), the state continuously changes as time changes and the model is usually a differential equation on the variable of time. With every "clock tick" the state is expected to change, since continuous state variables continuously change with time. However, in event-driven systems, the state changes only at certain points in time through instantaneous transitions. In between event occurrences the state remains unaffected.

**Definition 2.1** (Discrete Event System): is a discrete-state, event-driven system, that is, its state evolution depends entirely on the occurrence of asynchronous discrete events over time.

Figure 2.1 Partial classification of system [34]

Two aspects of DES are usually on focus at academic level. The first focus is on the formalization of DES. As the mathematic model of time varying dynamic system represented by differential equation and difference equation, the model which can accurately represent the system behavior is

of vital important. In DES, a number of modeling formalizations have been proposed such as automaton, Petri Nets, CTL, etc. On the other hand, another focus is on the methods of analysis, control, verification and simulations.

Supervisory Control Theory (SCT), firstly introduced by Ramadge and Wonham in 1987, is one of the most important academic theories and formal modeling paradigms for DES formalization, supervisor synthesis and verification. In CVDS, closed-loop (feedback) control is usually used to regulate the system performance based on the established target. Similarly, SCT takes advantage of "feedback loop" to achieve the real-time control on DES [34]. In the supervisory control paradigm, a supervisor continuously gets state information from the system and the environment, and feeds control information back to the system, in order to enforce some functional properties: either make invariant a given behavior which the system should always feature, or enforce a target configuration, which the system should eventually reach [35].

The controller and system to be controlled are formalized at the abstracted level within the SCT paradigm. The SCT provides algorithms for the synthesis of supervisory controllers from their specifications: a supervisor is computed from two distinct automata representing a given plant and the specification that describe the required controlled behavior of plant [25]. Therefore, supervisors operate synchronously with the plant to restrict the behavior of the plant to respect the specifications. Besides, recent studies have also proposed the SCT paradigm modeled by Petri Nets [15] [16] [36], which are out of the scope of this study however.

#### 2.2.1.2 Application

Since the year when SCT was introduced by Ramadge and Wonham, the theory caught great academic interest and a large number of applications and solutions based on SCT emerge in endlessly over decades. The application cases which involve a wide range of domains prove the applicability of the theory and prominence in the AC community.

#### A. Manufacturing System

Manufacturing system is one of the application domains attracting earliest academic focus. The research team of Queiroz and Cury contributed a lot for SCT application in the domain of manufacturing system. In [22] [37], authors introduced SCT-based solution for coordinating equipment operation in a flexible manufacturing system, which usually consists of workstations, robots and buffers, which are modeled by plant. On the other hand, the producing processes are usually modeled by specifications. Local modular supervisors are converted systematically into a PLC application program and the solution allows one to use existing PLC hardware and software designed for the sequential control of subsystems.

The case studies show that SCT are quite applicable for AC of manufacturing system. Plants and specifications are used to model the behavior of operation units and manufacturing processes respectively. Methods for SCT implementation by PLC, which is widely used as concrete controller in manufacturing systems, make it prospective for SCT application in this domain.

#### B. Autonomous Robot

In [17], authors demonstrated an approach for formally synthesizing control software for a set of cooperating ground robots, which is based on modular supervisory controllers that are guaranteed to meet a given set of logical specifications. In the study, the behavior of each robot is modeled by plant and task precedence constraints are modeled by specification. The study explained how the supervisory level of control interacts with the robot-level algorithms that control each robot's heading and velocity. In [18], authors present a method for mobile robot navigation in industrial environments in which the open-loop behavior of the robot and the specifications are based on automata. A modular supervisor is built, which is the conjunction of two supervisors: the first one that enforces the robot to follow the path defined by a planner and the second one that guarantees the satisfaction of the specifications such as prevention of collisions and task and movement management. The modular supervisor is embedded in the mobile robot, whereas the planner runs in an external agent (plant), which makes the adaptation of the proposed navigation architecture to different environments easy. In [38], authors introduced an application of SCT on warehouse automation using mobile robots. The warehouse automation can be expected to provide a solution to the labor shortage problem so that it is a prospective and important application to meet the challenge of population decline. The supervisory control is used to realize navigation for assigned tasks. In the study, the supervisory control is implemented by the platform LEGO MINDSTORMS EV3 with an external laptop computer to realize a wireless communication. [39] presents a method for modeling and controlling autonomous mobile robots by SCT. In this study, through a sumo robot for competitions, are showed a systematic procedure for the modeling, design and implementation of the supervisor in a real controller, which provided a fast and efficient way to create strategies for robot attack and defense on the fly. The review shows that the robots in different domains can be applied by SCT. Plants and Specifications are usually used to model the behavior of robot and constraints for tasks respectively. The supervisory control can be implemented in different ways for robot: the industrial robots usually use PLC controller while the small scale mobile robots use microcontroller to realize supervisory control.

#### C. Electrical System

[23] introduces an application of a solution for the electric Vehicle Scheduling Problem (eVSP). A supervisory control is used to manage the power admission control of a group of local Plug-in Electric Vehicles (PEV). The admission control problem is formulated in the framework DES by creating the DES model of appliances and control specification. A supremal non-blocking

controller is designed so as to handle requests from PEVs while meeting the grid limits and fairly distributing the capacity among PEVs. Another case study of power park management in the application scene is power delivery networks, introduced by the same research team in [19]. A supervisory control is developed for high level control of the operation of a typical custom power park (CPP) using SCT. In this study, the behaviors of each electrical appliance are modeled by plants and the reaction strategy for different power qualities are modeled by specifications. Three modular supervisors are synthesized to realize the supervisory control for guarantee the high quality power to the loads. In [24], authors introduced an application of SCT in admission control of thermal appliances in the context of smart buildings. The scheduling of thermal devices operation is formulated in the framework of DESs, which allows for the modeling and design of admission control to be carried out in a systematic manner and ensuring the existence of the feasible scheduling prior to exploring control solutions. In [40], authors proposed an approach to manage the control responses to deploy in a High-Voltage Direct Current (HVDC) grid based on SCT. A decentralized grid control which focuses on local control and limits the number of non-critical events to be communicated is synthesized. These case studies in this domains show that the behavior of electrical components can be formalized as plants and power management strategies are modeled by specifications. Besides, in [19] [23] [24], the simulation studies are carried out in MATLAB and STATEFLOW. The simulation results validate the effectiveness and functionality of supervisory control.

#### D. Others

Apart from the aforementioned application domains, more case studies can be found in other domains. In [41], authors introduced a case study of development of control system of Multi Mover (theme park vehicle) based on SCT. The components on the vehicle are formalized by plants and three safety-related control strategies are modeled by specifications. The supervisor synthesized for the theme park vehicle has successfully been implemented and integrated in the existing resource-control platform. In [42], authors showed the applicability of SCT to the design of controllers for waterway locks. The controller is implemented by PLC and a code generation algorithm is implemented to generate structured text (ST) PLC code. The results achieved in this case study presents the applicability of the procedure for supervisor synthesis and automatic PLC code generation for industrialized systems. In [20], author proposed an application of SCT for Healthcare MRI scanner development. In this study, author applied SCT in two cases respectively, namely the patient support table and the patient communication system. Each case is modeled by a monolithic plant and requirement. In this study, the author focuses on the use of SCT to realize a formal development process instead of conventional process. The formal process shows its advantage in control code generation. In [43], authors used SCT to develop command sequences and fault recovery of a spacecraft propulsion subsystem. The supervisor controls the system in such a way that the design specifications are satisfied in both normal and faulty modes of

operation. In this study, authors extend the concept of supervisory control by "robust". The study shows the use of robust supervisor is necessary in many aerospace systems when we try to solve the control and fault recovery problem.

#### 2.2.1.3 Discussion

The growing complexity of the controllers, the demand for reduced development time, and the possible reuse of existing software modules result in the need for a formal approach in engineering practice [25]. The large number of case studies shows that SCT can be widely used in a variety of application domains and adopted by researchers thanks to its rigorous formal methods from formalization to implementation. According to the investigation result of applications, the major industrial ACs which need the help of formal approach of SCT usually have such features as follow:

Flexibility: In the field of engineering systems design, flexibility refers to designs that can adapt when external changes occur. Flexibility for an engineering system is the case with which the system can respond to uncertainty. The Flexible Manufacturing System (FMS), as introduced in the aforementioned cases in [22] [27] is a representative system with feature of flexibility. The covers the system's ability to be changed to produce new product types, and ability to change the order of operations executed on a part or ability to use multiple machines to perform the same operation on a part. The challenge of AC on flexible system structure or changeable tasks requires powerful approaches to guarantee that the designed AC can perform correctly and avoid such failures as blocking or unexpected system behavior. Apart from FMS, the feature of flexibility can also be found in other systems such as autonomous robot, whose trajectory are determined according to different control targets, and electrical system, which usually has to handle uncertain failures.

Complexity/large-scale: A complex or large-scaled system is a system which is generally composed of a couple of interconnected systems, possess different local dynamic behaviors, are equipped with multiple control loops and operate under different local environments and varying loads. Nowadays, industrial systems, such as FMS, power network, sustainable energy systems, transportation systems, and so forth, are becoming more complex, which have higher requirement for operation performance, productiveness, availability, reliability, and safety. Therefore, enormous challenges have great impacts on improving to development techniques in modeling, monitoring, and AC for complex industrial systems.

To face the challenge of AC on the systems above, formal approaches can be made the use of as excellent technique for modeling, development, synthesis, verification and validation of AC. In the applications, the SCT has been proven to be a unified modeling framework to handle the control

on different kinds of systems: the free behaviors of components are usually modeled by plant and the control targets or processes are modeled by specification. Different control architectures are synthesized for particular needs of each case study. On the other hand, the case studies show that supervisors can be implemented by concrete logic controllers or simulation. In a number of case studies, SCT are used to help to generate control code instead of conventional direct coding.

With the help of SCT, the development challenge can be handled faced in typical direct implementation process. For engineering practice, SCT-based formal approach has the advantages as follows:

- The formal approach provides rigorous mathematic modeling methods by which the modeling and computation results can be proven to be correct by designer;

- There are numbers of existing theoretical methods and algorithms proposed within the SCT paradigm which improve the reusability of the global modeling process;

- Based on the SCT, the verification of controller after synthesis and implementation is eliminated, as SCT can guarantee the properties of supervisory control. SCT increases safety, reduces the development cost and the cycle time and provides greater liberty for designers;

- Tool support is an important aspect for the application of formal approaches. In fact, a number of tools have been developed. TCT and Supremica are two main tools to realize the computation and verification of supervisory control. Other formal verification tools such as UPPAAL and NuSMV are usually used for formal verification and model checking.

In fact, the engineering can benefit a lot from formal approaches. Nonetheless, although SCT perform well in these case studies at scientific level, the case studies of SCT can hardly be found in engineering practice. Therefore, the study on the theoretical paradigm is furthered for the purpose of investing this issue of SCT.

## 2.2.2 Theoretical Concepts

The SCT has formed its systematic theoretical framework by scientific contributions. It includes s series of concepts, models and methods aimed at formalization and supervisor synthesis. This section presents an overview of the theoretical concepts within the original theory for supervisory control to briefly introduce the fundamental modeling principle of this paradigm. More details about SCT can be found in [34] or Appendix A.

11

#### 2.2.2.1 Classification of Model

Models are expressed in some modeling language, and depending on the nature of the language, can be informal, semi-formal, and formal [44]:

- *Informal* models are expressed using natural language or loose diagrams, charts, tables, etc. They are genuinely ambiguous, heavily rely on human intuition, and no software tool can analyze them objectively;

- Semi-formal models are expressed in a modeling language that has a precisely-defined syntax, conveys some intuitive meaning, but has no formal (i.e., mathematical, self-contained, unambiguous) semantics. Examples of semi-formal specification languages are class diagrams, data flow diagrams, decision trees, entity relationship models, object models, pseudocode, state diagrams, etc.;

- Formal models are written in a language that has a precisely defined syntax and a formal semantics. Examples of formal specification languages are algebraic data types, synchronous languages, process calculi, automata, etc.

#### 2.2.2.2 Formal Language and Automaton

The modeling paradigm of DES defines the behavior as a collection of sequences of events. The system is usually assumed as asynchronized which means only one event may occur at each moment. To model the behavior of a DES, the original SCT framework takes advantage of two formal models: formal language and finite-state automaton.

**Definition 2.2** (Formal language): Each DES has an associated underlying event set  $\Sigma$  called an *alphabet*. A sequence of events from the alphabet is called a "word" or "string". An empty event string is denoted by  $\varepsilon$ . We denote the cardinality of an event set  $\Sigma$  as  $|\Sigma|$ . For a particular event set  $\Sigma$ , we denote its set of all possible finite strings of events by  $\Sigma^*$ . A *formal language* defined over an event set  $\Sigma$  is a subset of  $\Sigma^*$ .

Formal language, which is known as a kind of *regular languages*, specifies all admissible sequences of events that the DES is capable of "processing" or "generating", while bypassing the need for any additional structure. Actually, regular languages are seldom directly used to present the system and they are more suitable to prove properties. The reason is that regular languages are not intuitive way to model and present a repetitive behavior of system. Instead, the most usual modeling artifact is the finite state automaton [35].

**Definition 2.3** (Finite-state automaton): A finite state automaton is defined as a 5-tuple:

$$G = (Q, \Sigma, \delta, q_0, Q_m)$$

Where.

Q is a finite set of states;

$\Sigma$  is a finite set of events associated with G;

$\delta: Q \times \Sigma \to Q$  is the transition function;

$q_0$  is the initial state;

$Q_m \subseteq Q$  is a set of marked or accepting states.

**Definition 2.4** (Active event function). Define active event function  $\Gamma: Q \to 2^{\Sigma}$  as following:

$$\Gamma(q) = {\sigma \mid \delta(q, \sigma) \text{ is defined}}$$

Note that if there cannot be two transitions with the same event label out of a state, we call G a deterministic finite-state automaton. The event set  $\Sigma$  includes all events that appear as transition labels in the state transition diagram of automaton G. States are marked when it is desired to attach a special meaning to them. Marked states are also referred to as "accepting" states or "final" states. The transition function  $\delta$  is usually a partial function. Thus each state can be associated with a set of events which are admissible at that particular state, i.e. for which  $\Gamma(q)$  is defined.

The regular language and automaton are not two uncorrelated models. In fact, each regular language defined on a finite set of events can be generated by a deterministic finite state automaton. Therefore, there is equivalence between these two models [45].

#### 2.2.2.3 Plant and Specification

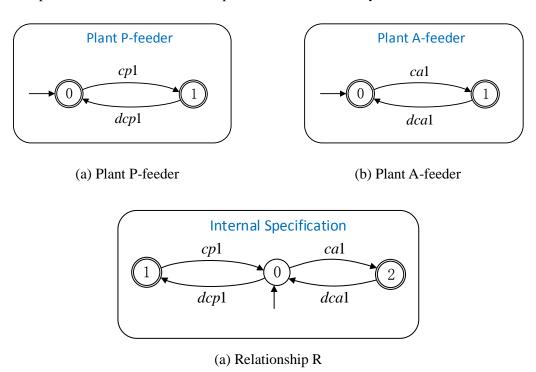

In SCT, the model of behavior of the uncontrolled system is always called *plant*, which represents the formal abstraction of system and indicates the relation between an input signal and the output signal of a system without feedback, commonly determined by physical properties of the system. A complex system may have several modular models of plant based on the components or subsystems it consists of. SCT provides synchronous composition method to compose multi-plants to be a global monolithic plant. Whether to choose modular plants or a monolithic plant depends on the system complexity and control architecture in each particular case.

In order to constrain the free behavior of the system and make its behaviors respects the expectation, it is necessary to define *specifications*. In SCT, specification is also be modeling by automaton. Cassandra and Lafortune [34] introduce four typical kinds of specification shown as follow (examples for these specifications can be seen in Appendix A):

- Illegal states: specification identifies certain states of plant as illegal, then it suffices to delete these states from the plants;

- State splitting: a specification requires remembering how a particular state of plant was reached in order to determine what future behavior is admissible, then that state must be split into as many states as necessary;

- Event alternation: a specification requires that two events occur alternately;

- Illegal substring: a specification identifies as illegal all strings of L(G) that contain substring  $s_f = \sigma_1 \sigma_2 ... \sigma_n \in \Sigma^*$ .

In practice, the plants and specifications are usually modeled by people's expertise and directly formalized from the requirements. An issue of formalization exists: the use of an explicit model of the plant and specification may therefore be necessary to identify the correct behavior of the control realization, and to perform model analysis and control synthesis accurately [25]. Besides, there is no existing technique to indicate if the constructed models respect to the requirements, and all depend on the peoples' experience.

#### 2.2.2.4 Supervisor Synthesis

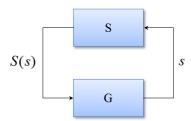

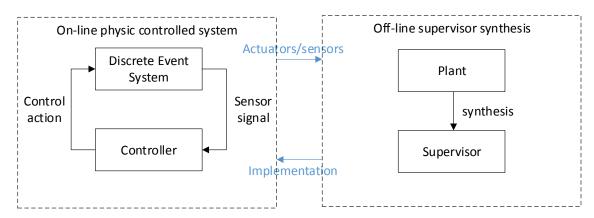

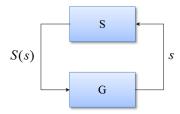

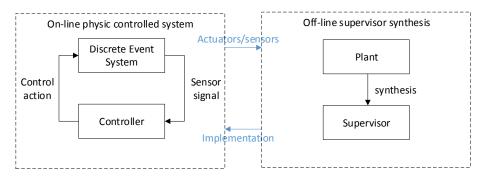

The Supervisor Control Theory paradigm regards any system as composition of a plant to be controlled and a supervisor which ensures the control logic respect to the specifications. We usually introduce the supervisor synthesis started by the system consisting of one monolithic plant and one monolithic supervisor. The control feedback loop between the plant and supervisor is shown in Figure 2.2.

Figure 2.2 The feedback loop of supervisory control

Consider a DES modeled by a plant  $G = (Q, \Sigma, \delta, q_0, Q_m)$  and assume that all the events in  $\Sigma$  generated by G are observed by supervisor. A supervisor, denoted by S, is adjoined to interact with G in a feedback manner. Here, let  $\Sigma$  be partitioned into two disjoint subsets

$$\Sigma = \Sigma_c \cup \Sigma_{uc}$$

With,  $\Sigma_c$  is the set of controllable events;

$\Sigma_{uc}$  is the set of uncontrollable events.

The transition function of G can be controlled by S in the sense that the controllable events of G can be dynamically enabled or disabled by S. Formally, a supervisor S is a function from the language generated by G to the power set of  $\Sigma$ :

$$S: L(G) \rightarrow 2^{\Sigma}$$

For each  $s \in L(G)$  generated so far by G (under the control of S):

$$S(s) \cap \Gamma(\delta(x_0, s))$$

is the set of *enabled events* that G can execute at its current state  $\delta(x_0, s)$ . We call S(s) the *control action* at s. In fact, the S(s) is determined by the specifications which is purposed to constrain the behaviors of system.

There are two basic properties of supervisor should be verified during synthesis: the controllability and nonblocking. The supervisor synthesis algorithm is the core of SCT, based on which the resulting supervisory control on plants with regards to the given specifications is proved to be controllable and nonblocking. SCT provides an iterative algorithm for supervisor synthesis and property verification (refer to Appendix A).

#### 2.2.2.5 State Explosion Problem

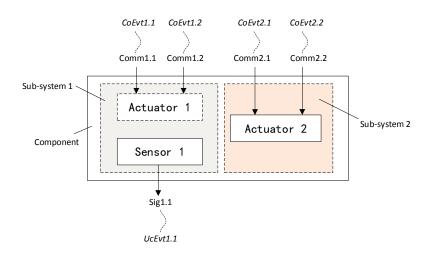

Generally, if the system is not complex, the centralized/monolithic control approach is enough to synthesis one unique supervisor *S* on plant *G* (Figure 2.2). Unfortunately, to model a large-scale system, the centralized approach cannot overcome the state-space explosion problem. The total number of states of a plant model increases quickly when the number of local components increases, due to the synchronous product which incurs Cartesian product [11].

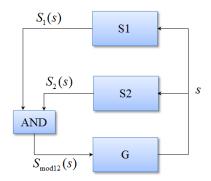

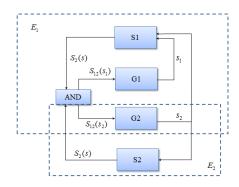

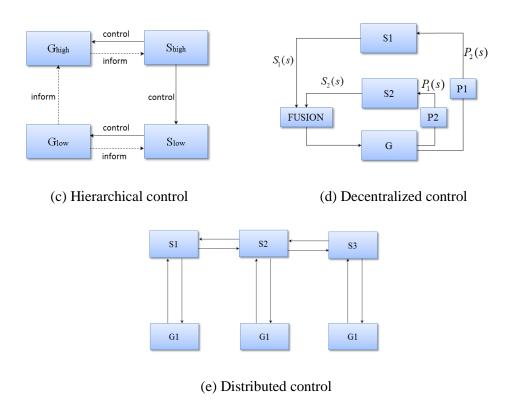

(a) Modular control

(b) Local modular control

Figure 2.3 Control architectures

A number of efforts focused on the methods to overcome this difficulty. One contribution proposes the concept of modularity (shown in Figure 2.3(a)) [8], which is extended to the concept of local modularity (shown in Figure 2.3(b)) [9]. In this control architecture, where the global supervisor is local modular, a global nonblocking of supervisory control must be verified.

In [46] [47], authors introduced a hierarchical method (shown in Figure 2.3(c)) that decomposes a system into two subsystems, and restricts the interaction of the subsystems by means of an interface. Thus, the complete system model never needs to be constructed, offering potentially significant savings in computational effort.

#### 2.2.2.6 Distributed Control

In a system that have several "processing nodes" that are jointly controlling a given system, apart from the modular control, decentralized control (shown in Figure 2.3(d)) and distributed control (shown in Figure 2.3(e)) can also be used [48-50] to realize distributed control. A decentralized discrete-event system is a global plant modeled as a DES with two or more observed event streams and two or more inputs of enabled events. Each controller receives an observed event stream defined by either a projection or a mask, and inputs a subset of enabled events. In contrary, the distributed control usually has several local plants (agents) for large-scale DES. [51] studied the design of distributed control for large-scale discrete-event systems. Supervisor localization

approach is applied to allocate external supervisory control action to individual plant components as their internal control architectures. In [52], author proposed distributed supervisory control architecture for automated manufacturing system. This approach exploits modular models of the plant and logical equations in Boolean algebra for constraints modeling, which can avoids the combinatorial explosion of the state space.

#### 2.2.3 SCT-Based Modeling Process: Principles and Limitations

#### 2.2.3.1 General Process

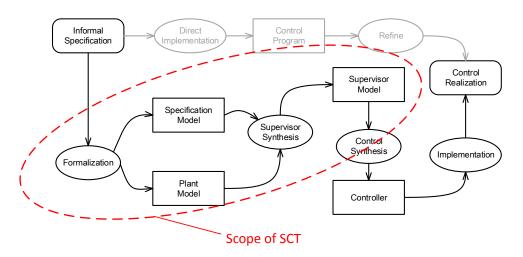

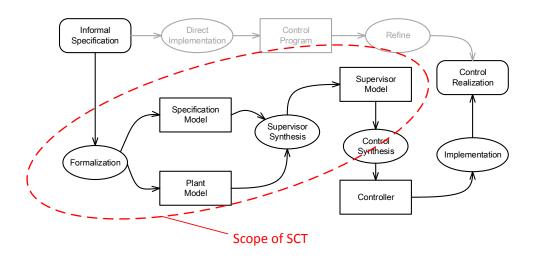

[25] introduces the typical SCT-based development process by reviewing the state of the art of synthesis and implementation methods. The overall process, shown in Figure 2.4, involves three generic activities: formalization, synthesis (supervisor synthesis and control synthesis) and implementation as follows:

#### (1) Formalization

The formalization of the informal specification is a human core capability. Two kinds of formal models should be constructed. The models of specification formalize the desired behavior constraints to be fulfilled by the controller or the controlled process according to the requirements. Formalizing the required properties may also be a difficult task that causes many trials and errors and requires a dedicated expertise related both to the plant (to express the constraints related to the actuator and sensor operations and technology choices) and to behavioral model required for the subsequent synthesis procedure.

#### (2) Synthesis

In synthesis step, two sub-activities are necessary to perform: supervisor synthesis and control synthesis. The fundamental difference between a supervisor and a controller is that a supervisor forbids the occurrences of some controllable events in view of maintaining the plant behavior in legal states and sequences, while a controller acts by forcing the plant inputs in a way to achieve the desired goal [25]. Within the SCT paradigm, the synthesis approach consists in synthesizing a supervisor from a description of the plant and the specification. Such a supervisor aims at enforcing the specifications while offering a maximum behavioral flexibility. The controller can be regarded as the intermediate between formal supervisor and concrete controller. The controller is built based on the *control strategy*. Although there is not systematic study on the control strategy to transform supervisor to controller, a number of case studies have proposed their proper solutions. In [53], the authors proposed a trajectory choice approach in order to make the control behavior "deterministic". The principle of the trajectory choice is to make sure the states in the

automaton are all accessible and co-accessible. In [54], the authors developed an algorithm for the generation of valid controllers which strengthened the coreachability property in order to guarantee that a marked state is eventually reached, irrespective of the plant's behavior. In [18], the authors proposed a planner in the navigation architecture under supervisory control. The planner, composed of several algorithms (including Dijkstra Algorithm), helps the modular supervisor to select a best choice of following path.

#### (3) Implementation

Regardless in academic context or industrial context, the supervisor/controller is usually implemented by *concrete controller* for validation, which is the target of this step. Based on the different objectives, the implementation can be classified by two kinds: concrete logic controller and simulation, which will be discussed in detail in the following part.

Figure 2.4 Activities and models involved in AC development process for DES

**Remark** The concepts and terminologies in synthesis and implementation are important for the following study. Therefore, the taxonomy of relevant terminologies is presented in Table 2.1.

|                | Formal               | Logic            | Physic                 |

|----------------|----------------------|------------------|------------------------|

| Concept        | Control architecture | Control strategy | Control implementation |

| Representation | Supervisor           | Controller       | Concrete controller    |

**Table 2.1** Taxonomy of terminologies

### 2.2.3.2 Controller Implementation

The case studies present that kinds of concrete logic controllers which can be used to realize supervisory control. As PLC is one of the primary executors of industrial automation, a lot of

study contributed in the SCT implementation by PLC control program, which are written in standardized languages, such as ladder diagram (LD), structured text (ST) or instruction list (IL), or SFC (Sequential Function Charts) (IEC 61131-3). Other case study [39] presents the supervisory control implemented by microcontroller from the Microchip PIC18F and dsPIC30F families. In [55], an application of supervisory control implemented the ATS, which is aimed at assisting RATP metro line management at the line control center to realize the traffic control and security control.

In addition, a part of contributions focus on performing control simulation based on SCT paradigm, which can be seen in case studies [19] [23] and [24]. The simulation is usually implemented by STATEFLOW toolkit in Simulink, which enables modeling of the controller in for of state transition based on signals from the workspace. It is also possible to send commands in each state to the workspace. One points should be taken into account when implementation by simulation. Physic characteristic of the controlled system components should be clarified when we want to validate the control performance by simulation. As shown in [19], the effects of control action are illustrated by the voltage change of three-phase AC. Therefore, besides the model of controller in simulation model, we also need the models of physic system.

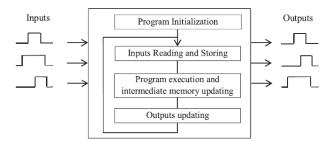

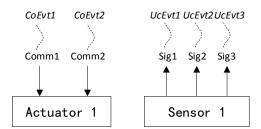

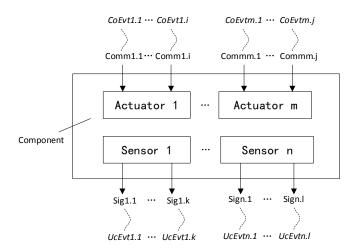

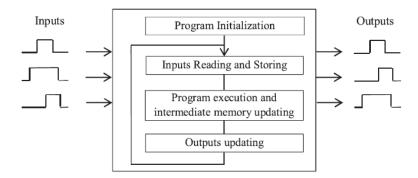

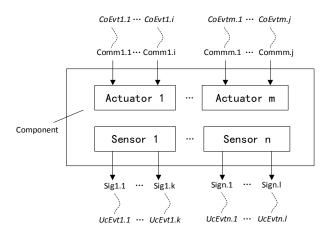

The principle of concrete logic controller is shown in Figure 2.5. Controller receives input signals coming from sensors and send output signals to actuators, in accordance with control laws implemented into a user program. A controller cyclically performs three tasks: reading and storing the inputs, program execution, and outputs updating. The period of this task may be constant (periodic scan) or may vary (cyclic scan). For the outside viewer, and specifically the plant, the controller can be considered as a reactive system as the output signals change their state simultaneously in response to the input signals, given that the scan time is short with respect to the time constant of the plant.

Figure 2.5 Basic Principle of Logic Controller

Due to some common characteristics such as input scan cycle, nearly all types of controller will encounter difficulties, which are systematically introduced in [56]. The study concluded five main concerns when moving from asynchronous, finite automata model of the supervisor, to the synchronous nature of, but not limited to, PLC control system. An interesting insight about the related phenomena is given in [57].

#### A. Inexact Synchronization

During the program execution a change in any controller input signal may occur and, this change will only be recognized at the beginning of the next scan cycle. The control reasoning is always performed on old frozen data. Therefore the communication between the controller and the plant is subject to delays due to periodic reading of the input signals. This inexact synchronization can be a problem when a change in a PLC input signal invalidates a control action (the choice made by the program, which corresponds to the generation of a controllable event).

#### B. Binary signals and events

The SCT deals with symbolic events that can occur asynchronously at any instant of time, whereas controller handles Boolean valued signals that are usually updated synchronously. *Avalanche Effect* occurs when a change on the value on a given controller input signal is registered as an event that makes the software jump over an arbitrary number of states within the same scan cycle.

#### C. Causality

SCT assumes that all events are spontaneously generated by the plant and that supervisors should only disable events generated by the plant. However, controllable events on practical applications are not spontaneously generated by the physical plant, but as responses to given control commands. Thus, for implementation purposes, "who generates what?" must be answered.

#### D. Simultaneity

Due to the cyclical nature of the control processing in which input signals readings are performed only at the beginning of each scan cycle, the occurrence of uncontrollable events from the plant is recognized by the controller once there are changes in the input signals values. Therefore, if in between successive scan cycles two or more signals change, they will all be recognized as simultaneous uncontrollable events regardless of their exact timing. As a result, the controller is unable to recognize the exact order of uncontrollable events that happen between scan cycles.

#### E. Choice

The supervisors obtained by the SCT are required to be "minimally restrictive", which means that the supervisors might provide alternative paths for the plant to choose from. Often a supervisor presents more than one possible controllable event from a single state. Thus, before producing a signal-change in the controller outputs it may have to choose only one among them because according to [56], generating more than one controllable event in a scan cycle can be contradictory and catastrophic. [58] shows that when the choice problem prioritizes the execution of a controllable event over the other, the controlled behavior may be blocking, even though the originating supervisor is deadlock free.

In order to overcome the difficulties and narrow the gap between the supervisor and its implementation, different control implementation approaches have been developed to provide possible solutions. In [59], the authors propose a solution based on the reordering of controller program instructions or the introduction of supplementary memory elements in controller programs for the detection and elimination of the avalanche effect problem. [60] proposes a direct transformation method from supervisor to PLC program. The main problems of supervisor implementation on a PLC are pointed out and some solutions to alleviate the problems are proposed. In [58] [61], conditions and algorithms are provided to guarantee that every deterministic controller derived from the supervisor (i.e., whatever controllable event corresponding to a controller order at a given state is chosen/enabled, supposing that only one will be taken and the others will therefore be disabled) is nonblocking. In [21], solutions based on the reordering of PLC program instructions or the introduction of supplementary memory elements in PLC programs have been proposed for the detection and elimination of the avalanche effect problem. [37] proposes a three-level model of PLC implementation for local modular supervisory control. The proposition introduces the conceptual aspects of a systematic procedure to structure and to detail the program to be implemented in a programmable logical controller. The proposition can be used to the implementation of local modular control. In order to coordinate the control action of local controller, the three-level structure is deliberately design. [62] presents a nine step methodology, named DECON9, to implement SCT into PLCs in standardized, efficient and robust ways, closer to real size plants. The methods it allows the control logic to deal with many events at each scan cycle, which improves existing approaches that are constrained to only one event at a time and a nonblocking property is achieved due to the random selection of controllable events approach that solves the choice problem. Besides, there is no fear of an avalanche effect thanks to the use of auxiliary memories and uncontrollable events are prioritized. To sum up, the implementation of supervisory control based on PLC platform is systematically studied and the state-of-the-art methods are proven to be able to transform supervisor to PLC control program for different control architectures.

**Table 2.2** A summary of Solutions for implementation problems

| Problem                   | Solution                     |

|---------------------------|------------------------------|

| Inexact Synchronization   | [37] [62]                    |

| Binary signals and events | [37] [59]                    |

| Causality                 | [21] [37] [58] [60][61] [62] |

| Simultaneity              | [37] [60][62]                |

| Choice                    | [21] [37] [58] [60][61] [62] |

### 2.2.3.3 Problematic

Although a systematic theory is constructed for SCT according the aforementioned review, the paradigm has its limitations from the perspective of engineering context. As shown in Figure 2.4, the scope in SCT is limited the formalization and supervisor synthesis. Even if the controller implementation is considered as the extension of SCT, when SCT-based process is applied in engineering practice, several issues have to be faced:

#### **Limitation 1: Formalization**

The quality of the synthesis results highly depends on the relevance of the requirements proposed by the engineering inputs. The formalization of the informal requirements and free behaviors of the system to be controlled is one of the major difficulties facing the existing control synthesis approaches in engineering practice [25].

Firstly, systems' requirements are usually written in an informal narrative since it generally means a greater understanding among the various stakeholders. On the other hand, formal models such as automaton have unambiguous semantic, which means a sentence cannot be understood in different ways. Most of case studies, however, achieve their controller modeling and implementation by directly formalizing the requirement as the beginning. It is still difficult to link the formalization and informal narrative requirements. For example, a controllable event defined as uncontrollable event by mistake leads to problems for final results. In fact, the typical SCT-based modeling process pays little attention to the verification of consistency between informal requirements and formal specification in form of automaton. Besides, another limitation is lack of representation of the link between the informal requirement and formal specification. In engineering practice, the requirements must be traced and a number of tools such as requirement traceability matrix (RTM) or graphic models (SysML requirement diagram) are used in the development process [63] [64]. The requirement traceability representation for formal models within SCT paradigm still unsolved.

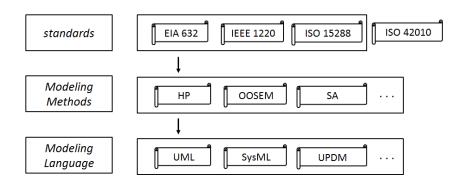

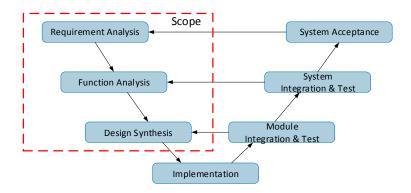

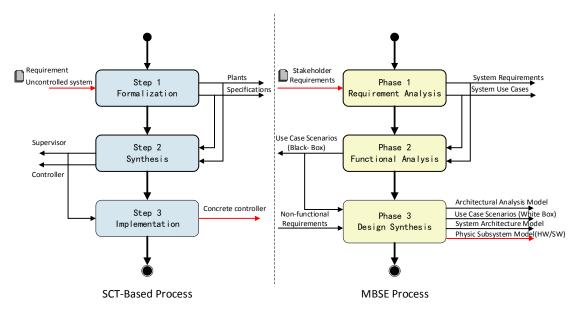

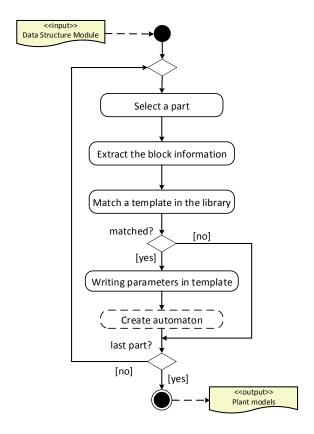

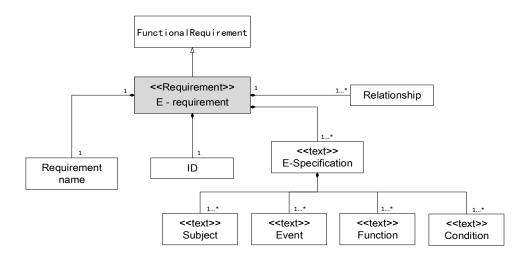

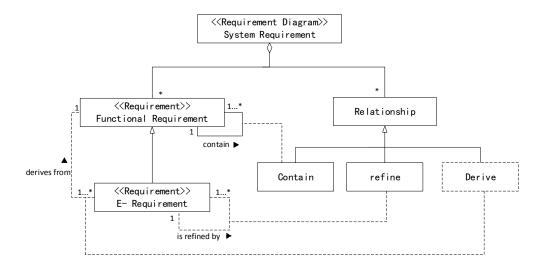

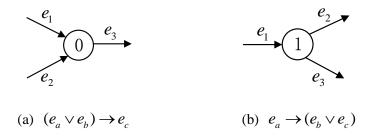

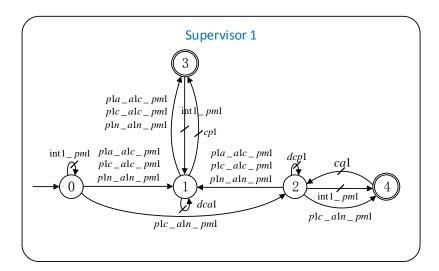

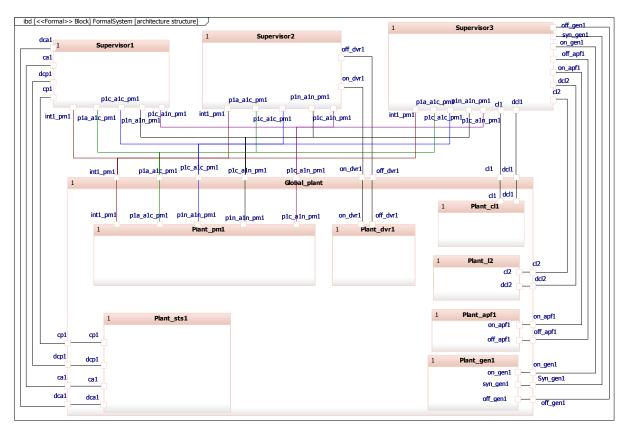

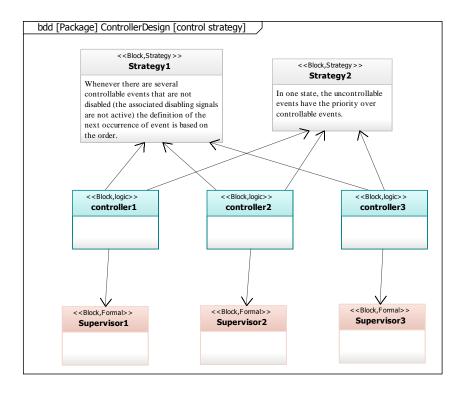

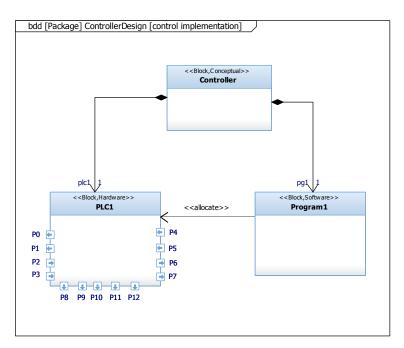

Secondly, the formalization of free behavior of the system is also questionable. The identification of plant from the system to be controlled is of important for engineering practice. However, few contributions can be found to provide systematic methods. For example, the buffer, as a component of physic system, is usually formalized by specification rather than plant. On the other hand, in [18], the behavior of mobile robot is formalized by several plants. A contradiction can be seen by comparing these two situations and a question can be put forward: how on earth formal plants can be linked with physic system to be controlled? Indeed, in a number of contributions, the plants are supposed to be formalized by identifying the signals from sensors and commands to actuators, in accordance with control laws implemented into a user program [20] [25] and [30]. However, there is no study can be found particular for this point. Secondly, similarly to