# Test and characterization of 3D high-density interconnects

Imed Jani

#### ▶ To cite this version:

Imed Jani. Test and characterization of 3D high-density interconnects. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2019. English. NNT: 2019GREAT094. tel-02634259

# HAL Id: tel-02634259 https://theses.hal.science/tel-02634259v1

Submitted on 27 May 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité: NANO ELECTRONIQUE ET NANO

**TECHNOLOGIES**

Arrêté ministériel: 25 mai 2016

Présentée par : Imed JANI

Thèse dirigée par Edith BEIGNE, Directeur de Recherche, CEA et codirigée par Didier LATTARD et Pascal VIVET préparée au sein du Laboratoire CEA/LETI dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

# Test et caractérisation des interconnexions 3D haute densité

# Test and characterization of high-density 3D interconnects

Thèse soutenue publiquement le 28 Novembre 2019, devant le jury composé de :

#### Mme. Lorena Anghel

Professeur, Laboratoire TIMA Grenoble, France, Président de jury

#### Mme. Aida Todri-Sanial

Chargé de recherche, CNRS/LIRMM, Montpellier, France, Rapporteur

#### M. Alberto Bosio

Professeur, Ecole centrale de Lyon, France, Rapporteur

#### M. Alexis Farcy

Ingénieur R&D, STMicroelectronics, Grenoble, France, Examinateur

#### Mme. Edith Beigné

Directeur de recherche, CEA Grenoble, Membre

#### M. Didier Lattard

Ingénieur R&D, CEA Grenoble, Membre

#### M. Pascal Vivet

Directeur scientifique, CEA Grenoble, Membre

# **ACKNOWLEDGMENTS**

This work was funded thanks to the French national program "Programme d'Investissements d'Avenir, IRT Nanoelec" ANR-10-AIRT-05. My research work was carried out in collaboration between the technology department (LICL laboratory) and design department (LISAN laboratory) of CEA-Leti.

I thank all the PhD students and the R&D engineers from both departments for the warm welcome and the help they gave me during three years.

I would like to express my gratitude to all the members of the jury, in all their diversity of specializations for having accepted to assess my work.

I would like to thank very sincerely my thesis director Edith BEIGNE and my co-supervisors Didier LATTARD & Pascal VIVET for their supervision, direction, and scientific contributions during this thesis.

Thanks to all the peoples who works on 3D integration project, more particularly, Severine CHERAMY, Lucile ARNAUD, Nicolas BRESSON ...

Thank you Alexis FARCY, Joris JOURDON, Yann HENRION, Emilie DELOFFRE and Halim BILGEN for your precious help to specify, fabricate and characterize the misalignment test structure. I'm very grateful also to you Jean DURUPT and Sebastien THURIES for the design and test activities.

To my family: my parents Moncef JANI and Souad TALBI, my wife Marwa and my daughter Miral, my brother Adel and my sister Malek, thank you for encouraging me in all of my pursuits and inspiring me to follow my dreams.

# Table of contents

| Chapte | er I. Introduction                                                     | 9  |

|--------|------------------------------------------------------------------------|----|

| I. C   | General context                                                        | 9  |

| II.    | High-Density 3D-IC interconnects                                       | 12 |

| 1.     | Overview                                                               | 12 |

| 2.     | Cu-Cu hybrid bonding interconnects                                     | 12 |

| 3.     | High density TSVs                                                      | 14 |

| III.   | Applications                                                           | 15 |

| 1.     | CMOS image sensor                                                      | 15 |

| 2.     | High performance computing.                                            | 16 |

| IV.    | Test and characterization challenges of HD 3D-ICs                      | 18 |

| 1.     | High-density 3D-IC interconnect defect                                 | 18 |

| 2.     | Test challenges at system level                                        | 20 |

| a      | Challenges of pre-bond test                                            | 20 |

| b      | ,                                                                      |    |

| V.     | PhD objectives and contributions                                       | 21 |

| Chapte | er II. Characterization of high-density 3D-IC interconnects            | 25 |

| I. I   | mpact of defects on electrical characteristics                         | 25 |

| 1.     | Overview                                                               | 25 |

| 2.     | Impact of misalignment defect on electrical characteristics            | 28 |

| 3.     | Impact of μ-void defects on electrical characteristics                 | 28 |

| II.    | Characterization methods: state of the art                             | 29 |

| 1.     | Morphological methods                                                  | 29 |

| 2.     | Electrical measurements                                                | 31 |

| III.   | Proposed structure to test bonding alignment and characterize HD 3D-IC |    |

| interc | onnects                                                                | 32 |

| 1.     | Overview                                                               | 32 |

| 2.     | Principle of the proposed test structure                               | 34 |

| 3.     | Misalignment test structure architecture                               | 35 |

| 4.     | Test structure validation                                              | 37 |

| a      | Test results: pitch 3.42μm and 1.44μm                                  | 37 |

| b      | Comparison of misalignment test structure results with overlay measurements | 40  |

|--------|-----------------------------------------------------------------------------|-----|

| IV.    | Characterization of HD 3D-IC interconnect using the proposed test structure | 43  |

| V.     | Conclusion                                                                  | 45  |

| Chapte | er III. Test of high density 3D-IC interconnect at system level             | 47  |

| I. S   | State of the art                                                            | 47  |

| 1.     | IEEE 1149.1 (JTAG)                                                          | 48  |

| 2.     | IEEE Std 1500                                                               | 50  |

| 3.     | IEEE P1687 (IJTAG)                                                          | 52  |

| 4.     | IEEE Std P1838: 3D Test standard                                            | 54  |

| 5.     | Conclusion                                                                  | 55  |

| II.    | Testability of high-density 3D-IC interconnects                             | 56  |

| 1.     | Face-to-Face (F2F)                                                          | 56  |

| 2.     | Face-to-Back (F2B)                                                          |     |

| 3.     | Interpretation                                                              |     |

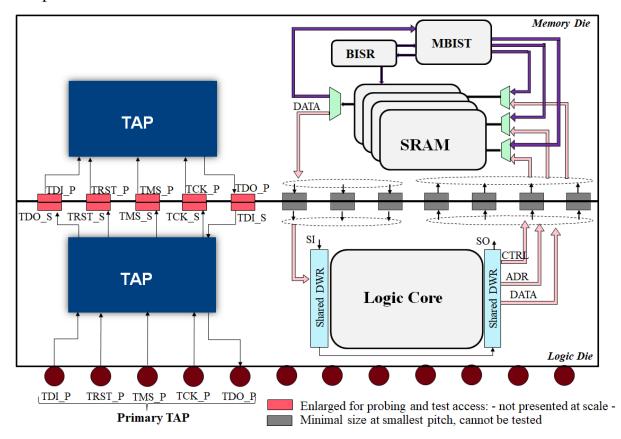

| III.   | Proposed DFT architecture for 3D SRAM-on-Logic partitioning                 |     |

| 1.     | Overview                                                                    |     |

| 2.     | Optimized DFT architecture for SRAM/Logic 3D-IC                             |     |

| IV.    | Discussion                                                                  |     |

| V.     | Conclusion                                                                  | 63  |

| Chapte | er IV. Structural test of high density 3D-IC interconnects                  | 65  |

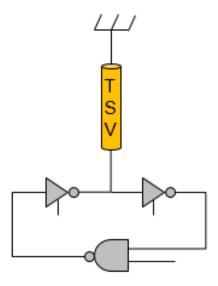

| I. F   | Related works                                                               | 65  |

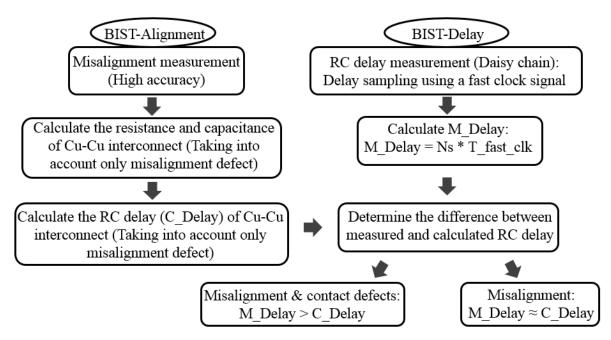

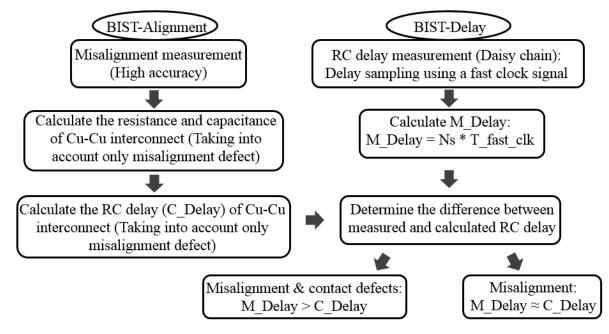

| II.    | Proposed BIST's to test and characterize high-density 3D-IC interconnects   | 67  |

| 1.     | Overview                                                                    | 67  |

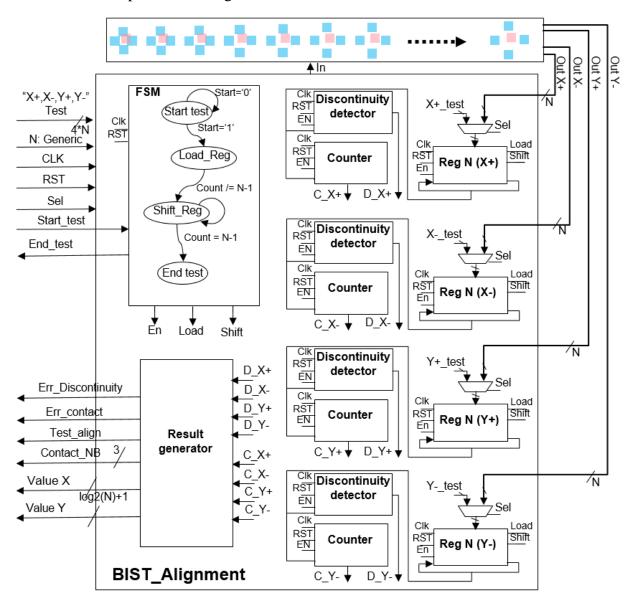

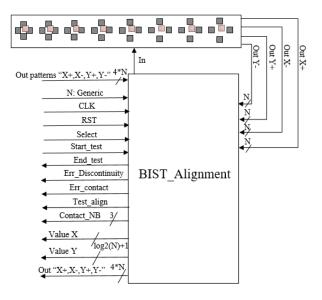

| 2.     | BIST alignment                                                              | 68  |

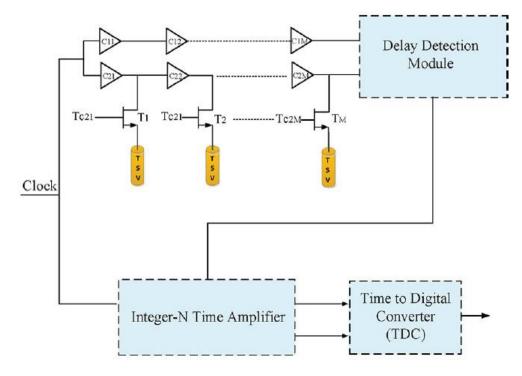

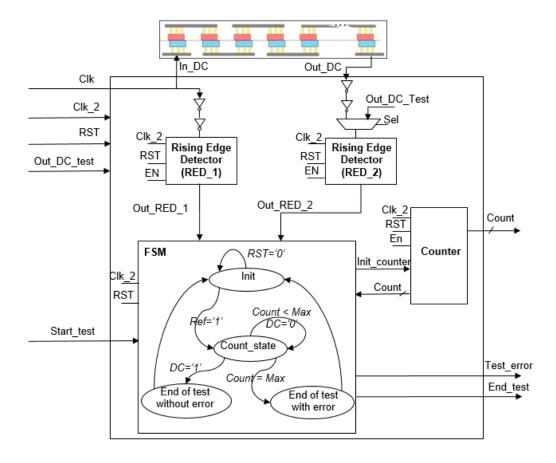

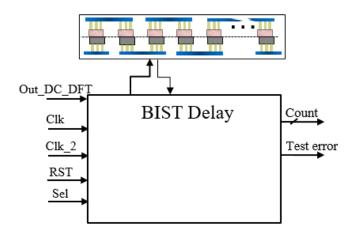

| 3.     | BIST delay                                                                  | 70  |

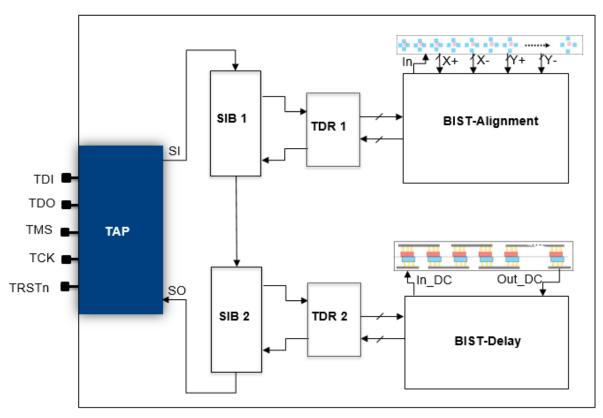

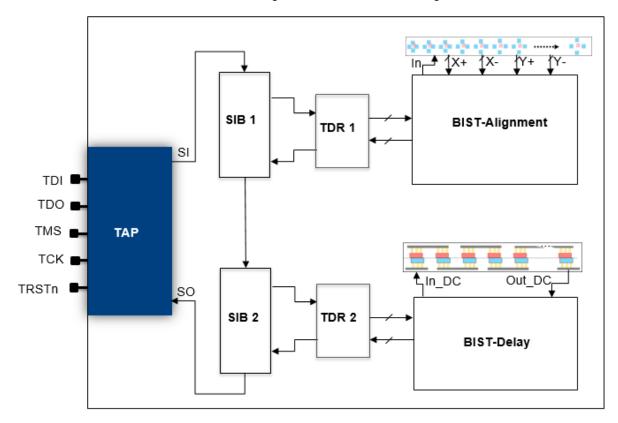

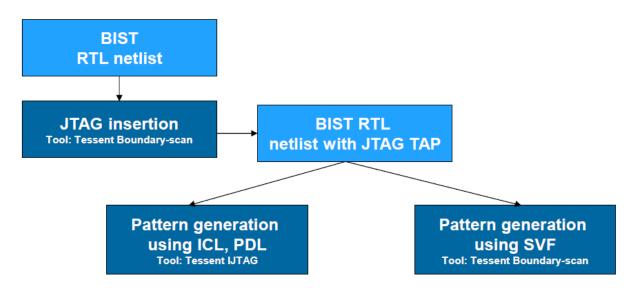

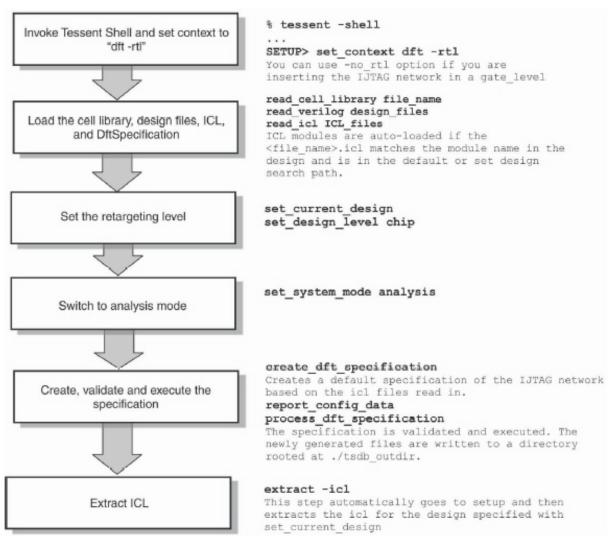

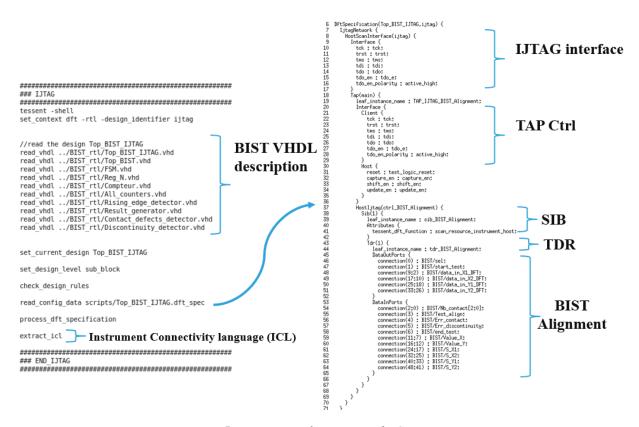

| III.   | IJTAG architecture                                                          | 71  |

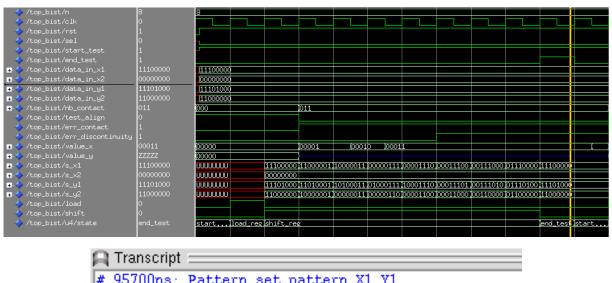

| IV.    | Simulation results                                                          | 73  |

| 1.     | Electrical results                                                          | 73  |

| 2.     | System integration                                                          | 75  |

| V.     | Conclusion                                                                  | 76  |

| Chapte | er V. Conclusion and perspectives                                           | 79  |

|        | Résumé en français                                                          | 82  |

|        | References                                                                  | 91  |

|        | Publications                                                                |     |

|        |                                                                             |     |

|        | Appendix A: Misalignment Matlab simulator                                   | y / |

| Appendix B: BISTs misalignment & μ-void, specifications, DFT |     |

|--------------------------------------------------------------|-----|

| insertion flow and implementation                            | 100 |

| Abstract                                                     | 107 |

| Résumé                                                       | 108 |

# List of figures

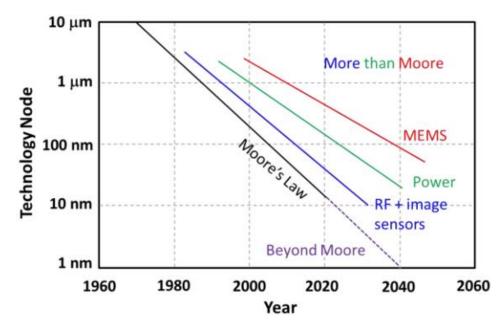

| Figure 1: Evolution of More-Moore and More-than-Moore (source [2])                         | 9  |

|--------------------------------------------------------------------------------------------|----|

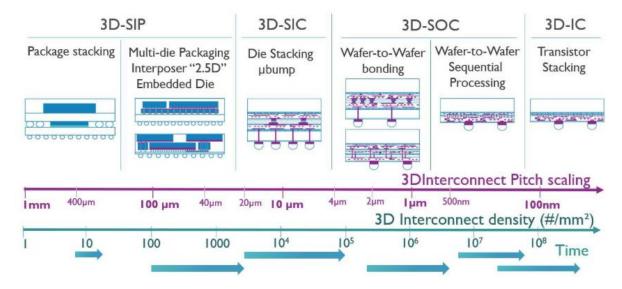

| Figure 2: Evolution of 3D integration (source [8])                                         | 10 |

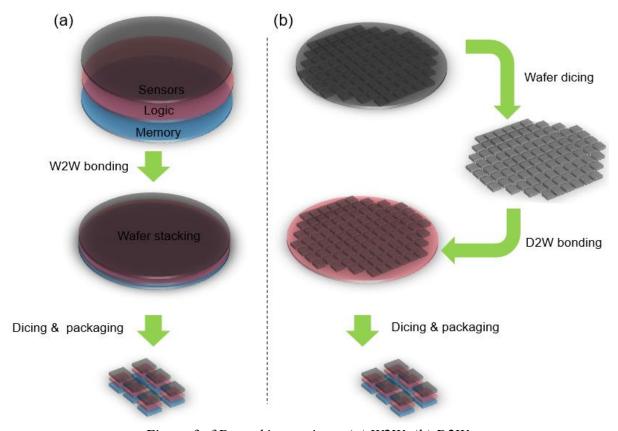

| Figure 3: 3D stacking options: (a) W2W, (b) D2W                                            | 11 |

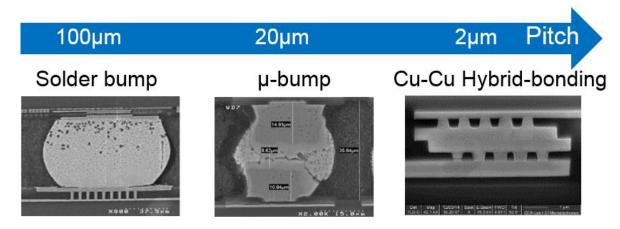

| Figure 4: Evolution of inter-dies interconnects                                            |    |

| Figure 5: Cross-sectional view of high density 3D-IC structures:                           |    |

| (a) F2F, (b) F2B                                                                           | 13 |

| Figure 6: Example of hybrid bonding process flow (source [15])                             |    |

| Figure 7: Via-first, via-middle and via-last illustration (source [16])                    |    |

| Figure 8: Structure of stacked CMOS image sensor:                                          |    |

| (a) two layers, (b) three layers                                                           | 15 |

| Figure 9: Micrograph of "Exmor RS" CMOS image sensor (source [23])                         | 16 |

| Figure 10: architecture of Virtex-7 HT (source [31])                                       | 17 |

| Figure 11: AMD Fury: HBM and CPU/GPU implementation using a passive interposer             |    |

| (source [34])                                                                              | 17 |

| Figure 12: Intact system architecture overview (source [38])                               | 18 |

| Figure 13: μ-voids and misalignment defect in Cu-Cu interconnects                          |    |

| Figure 14: Impact of probing process                                                       | 21 |

| Figure 15: Test of 3D-IC interconnects at system level                                     | 21 |

| Figure 16: Equivalent electrical model of Cu-Cu interconnects                              | 26 |

| Figure 17: Impact of Cu-Cu interconnect defect on electrical characteristics               | 26 |

| Figure 18: Parallel-plate capacitor model                                                  | 27 |

| Figure 19: Variation of the resistance and parasitic capacitance of a Cu-Cu pad            |    |

| (pitch: 7.6, 3.45 and 1.4µm) as a function of misalignment.                                | 28 |

| Figure 20: Variation of the resistance and coupling capacitance of a Cu-Cu pad             |    |

| (pitch: 7.6, 3.4 and 1.4μm) as a function of μ-void volume.                                | 29 |

| Figure 21: IR metrology tool principle (source [50])                                       | 30 |

| Figure 22: Example of SEM image of Cu-Cu interconnect (source [55])                        | 31 |

| Figure 23: Electrical measurement test vehicle:                                            |    |

| (a) Kelvin, (b) Daisy chain                                                                | 31 |

| Figure 24: Wafer map: example of misalignment simulation                                   |    |

| Figure 25: The reference pattern of misalignment test structure                            | 34 |

| Figure 26: N patterns using different "offset" values                                      |    |

| Figure 27: Misalignment test structure architecture                                        | 35 |

| Figure 28: Layout of the proposed test structure                                           |    |

| Figure 29: Misalignment test structure results (Pitch= 3.42µm)                             | 37 |

| Figure 30: Misalignment wafer map for five wafers (Pitch= 3.42µm)                          |    |

| Figure 31: Misalignment test structure results (Pitch= 1.44µm)                             |    |

| Figure 32: Misalignment wafer map for five wafers (Pitch= 1.44µm)                          |    |

| Figure 33: Overlay measurements distribution                                               |    |

| Figure 34: Wafer map results using overlay measurements                                    |    |

| Figure 35: Comparison of test structure results (3.42µm pitch) and overlay measurements is |    |

| and Y direction                                                                            | 42 |

| Figure 36: | Comparison of test structure results (1.44 $\mu m$ pitch) and overlay measurements in  | X              |

|------------|----------------------------------------------------------------------------------------|----------------|

| and Y      | direction                                                                              | <del>1</del> 3 |

| Figure 37: | Overall test misalignment flow                                                         | 44             |

| Figure 38: | Resistance and capacitance values distribution (W14 with a pitch=1.44µm)               | 44             |

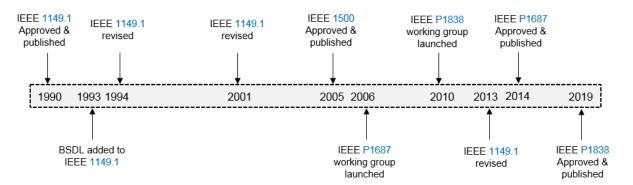

| Figure 39: | History of DFT test standards                                                          | 48             |

| Figure 40: | IEEE 1149.1 boundary scan test                                                         | 49             |

| Figure 41: | Boundary-Scan-Register (BSR) architecture                                              | 49             |

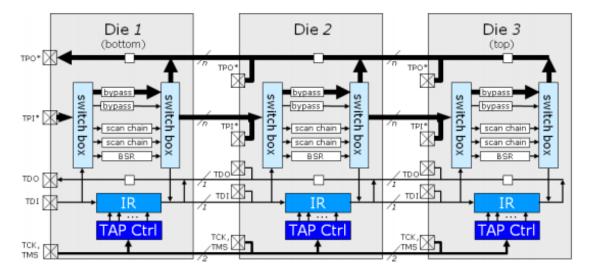

| Figure 42: | 3D DFT architecture based on IEEE 1149.1 (source [62])                                 | 50             |

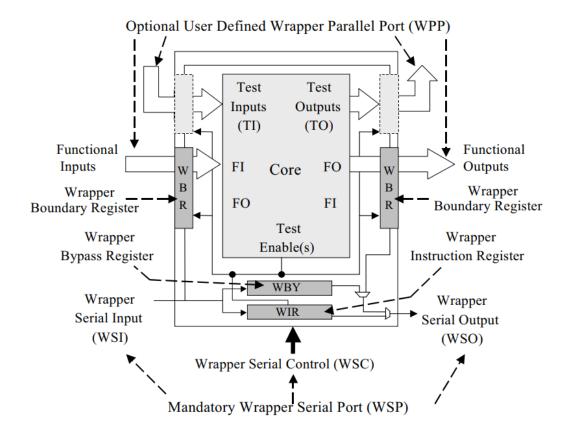

| Figure 43: | IEEE Std 1500 wrapper components (source [58])                                         | 51             |

| Figure 44: | Wrapper-Boundary-Register (WBR) architecture                                           | 51             |

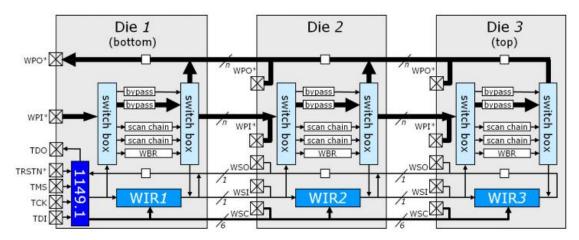

| Figure 45: | 3D DFT architecture based on IEEE 1500 (source [62])                                   | 52             |

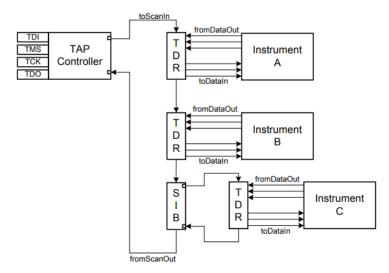

| _          | Conceptual IEEE 1687 network                                                           |                |

| Figure 47: | 3D DFT architecture based on IEEE P1687 (source [64])                                  | 53             |

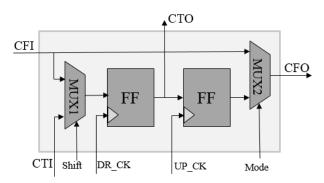

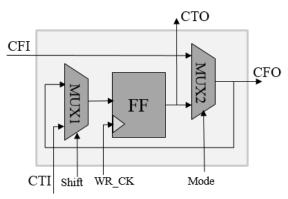

| Figure 48: | Serial control mechanism (SCM) (source: [68])                                          | 55             |

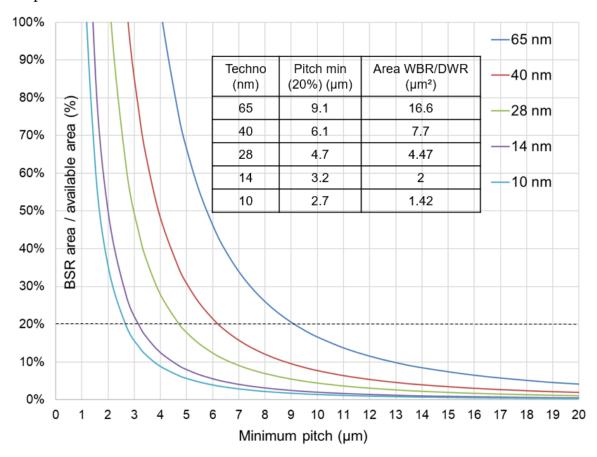

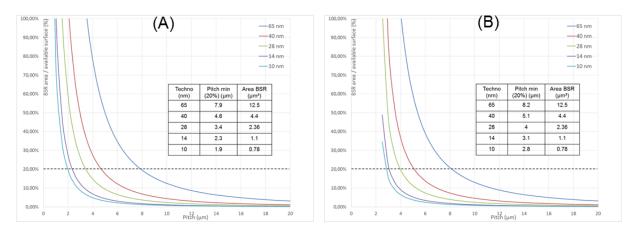

| Figure 49: | Variation of the ratio between the area of WBR/DWR and the available area as a         |                |

| functi     | on of the minimum pitch (Face-to-Face)                                                 | 56             |

| _          | 3D view of 3D-IC interconnects (Face-to-Back stacking mode)                            |                |

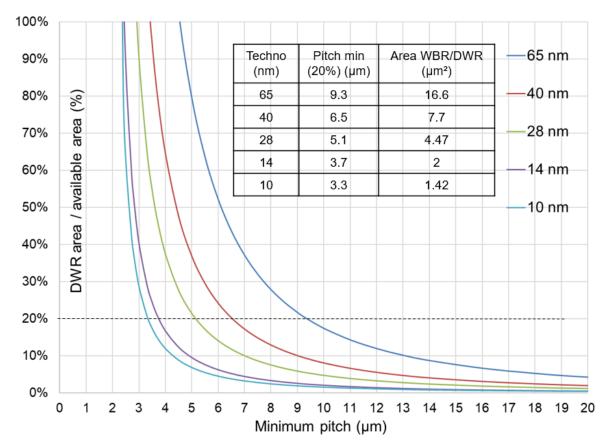

| 0          | Variation of the ratio between the area of WBR/DWR and the available area as a         |                |

|            | on of pitch (Face-to-Back)                                                             |                |

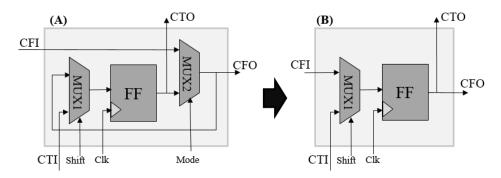

|            | Dedicated (a) and (b) shared wrapper cell                                              |                |

|            | Optimized DFT architecture for SRAM/Logic 3D-IC                                        |                |

| _          | 3D SRAM-on-Logic RISC-V floorplan                                                      |                |

| _          | Example of delay measurement method (source [71])                                      |                |

| •          | Test TSV using ring oscillator example                                                 |                |

| _          | Proposed structural test flow for Cu-Cu interconnects                                  |                |

| _          | Proposed structural test flow for Cu-Cu interconnects                                  |                |

| _          | Daisy chain                                                                            |                |

| -          | BIST delay architecture                                                                |                |

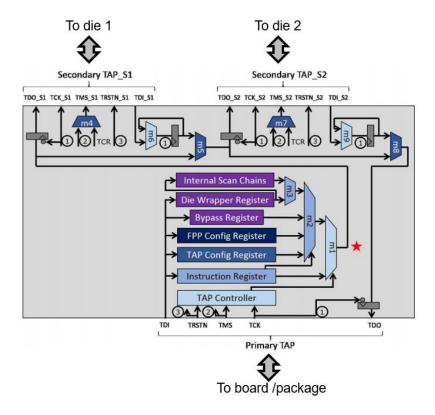

| U          | BIST's architecture integration within IJTAG infrastructure                            |                |

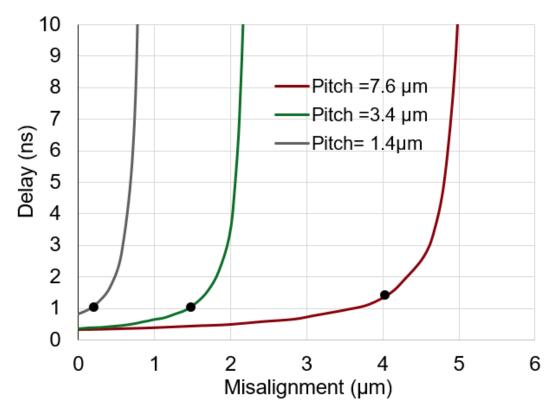

| •          | Delay variation of a daisy chain (10,000 Cu-Cu pads) (pitch: 7.6, 3.45 and 1.4 μm      | -              |

|            | unction of the misalignment                                                            |                |

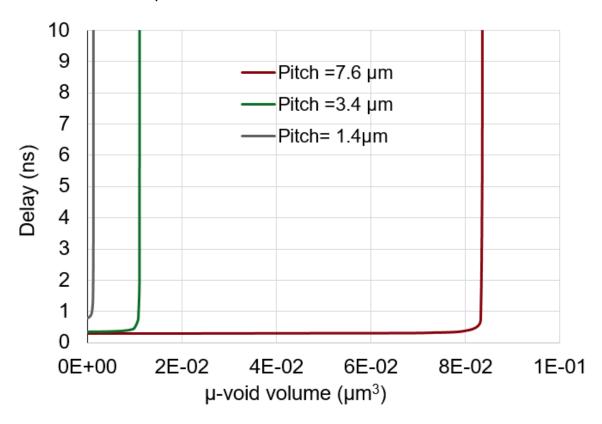

|            | Delay variation of a daisy chain (10,000 Cu-Cu pads) (pitch: 7.6, 3.45 and 1.4 $\mu$ m |                |

|            | unction of μ-void volume                                                               |                |

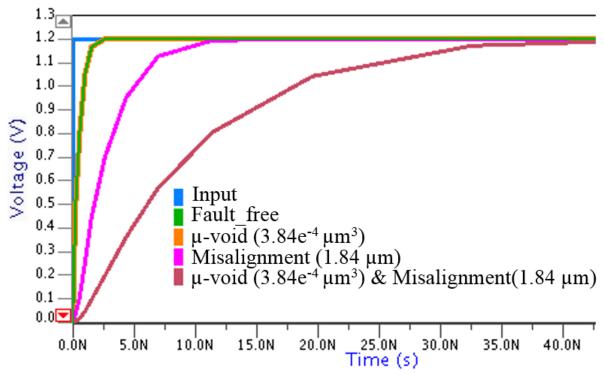

| •          | Simulation of the electrical equivalent model of daisy chain (10,000 Cu-Cu pads;       |                |

| -          | -3.45 μm)                                                                              |                |

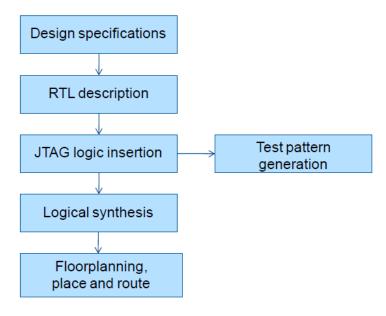

| Figure 65: | Design flow of the test chip circuit                                                   | /6             |

# List of tables

| Table 1: Offset values                                                | 36 |

|-----------------------------------------------------------------------|----|

| Table 2: Statistical data of misalignment test results (Pitch=3.42µm) | 38 |

| Table 3: Statistical data of misalignment test results (Pitch=1.44µm) | 40 |

| Table 4: Test standards comparison                                    | 55 |

| Table 5: Test methodologies                                           |    |

| Table 6: Contact_NB output interpretation                             |    |

| Table 7: Area of the proposed test architecture (pitch= 3.4μm)        |    |

# Acronyms

${\it 3D-IC: Three-Dimensional\ Integrated\ Circuit}$

ATPG: Automatic Test Pattern Generation

Ball Grid Array (BGA)

BEOL: Back End Of the Line

BIST: Built In Self Test BSC: Boundary Scan Cell BSR: Boundary-scan Register CIS: CMOS Image Sensors

CMOS: Complementary Metal Oxide

Semiconductors D2W: Die to Wafer DFT: Design for Test

DWR: Die Wrapper Register

F2B: Face to back F2F: Face to face

FDSOI: Fully Depleted Silicon On Insulator

FEOL: Front End Of the Line

FPGA: Field Programmable Gate Array

**HB**: Hybrid Bonding

ICL: Instrument Connection Language IJTAG: Internal Joint Test Action Group

JTAG: Joint Test Action Group

KGD: Known Good Die KGS: Known Good Stack

PDL: Procedural Description Language

RF: Radio Frequency

SI: Scan Input

SIC: Stacked Integrated Circuit

SIP: System In Package

SO: Scan Output

SOC: System On Chip SVF: Serial Vector Format TAM: Test Access Mechanism

TAP: Test Access Port

TCK: Test Clock

TDI: Test Data Input

TDO: Test Data Output

TMS: Test Mode Select

TRST: Test Reset

TSV: Through Silicon Via W2W: Wafer to Wafer

WBR: Wrapper Boundary Register WIR: Wrapper Instruction Register

WPI: Wrapper Parallel Input WPO: Wrapper Parallel Output WSC: Wrapper Serial Control WSI: Wrapper Serial Input WSO: Wrapper Serial Output

# Chapter I. Introduction

#### I. General context

Moore's law is the observation that the number of transistors per unit area doubling about every two years. The rate now is at the limits of physics, TSMC (Taiwan Semiconductor Manufacturing Company) can already scale its process to 5nm Fin Field-Effect Transistor (FinFET) [1]. Beyond that, miniaturization is very difficult and faces a lot of technological and physical issues. So, a new concepts are needed to overcome the technology limitations for CMOS scaling.

In 2000s, a new concept named "More than Moore" has thus appeared in order to extend Moore's Law and to enhance the overall chip performances. Figure 1 shows the different scaling directions to enhance system performances. This new "More than Moore" concept consists on vertical stacking; associate in single chip diversified integrated circuits such as analog/RF, passive, sensors, digital, biochips... This kind of integration is called Three-Dimensional (3D) integration which consists on the fact of stacking various functional blocks in a vertical way in order to form a single chip with high performances.

*Figure 1: Evolution of More-Moore and More-than-Moore (source [2])*

The 3D interconnect technology landscape was illustrated in figure 2. The graph represents the various 3D integration approaches with respect to the achievable 3D interconnect density and pitch [3]. The first vertically stacked circuit was the system in package (SIP) using wire bonding technology or Ball Grid Array (BGA) technique (Package-On-Package (POP) stacking) with a contact pitches in the order of 400µm [4].

Afterwards, the 3D Stacked Integrated Circuit (SIC) appeared thank to a new bonding technique that is based on TSVs (Through Silicon Vias) and  $\mu$ -bumps interconnects, Coarse contact pitches in the order of  $20\mu m$  can be achieved [5]. Copper-to-copper (Cu-Cu) Hybrid Bonding (HB) technology is another alternative for System-On-Chip (SoC) implementation to scale the contact pitch down to  $2\mu m$  [6].

The 3D connections are achieved by direct bonding of top and bottom dies/wafers using copper contacts on top of each metal layer stack and TSVs connect the lowest metal layer to backside solder bumps. Next come 3D sequential integration, also named 3D monolithic integration, consists in stacking active device layers on top of each other in a sequential manner to achieve a contact pitch below 100nm [7].

Figure 2: Evolution of 3D integration (source [8])

3D-ICs can be stacked in two major options: wafer-to-wafer (W2W), die-to-wafer (D2W) (Figure 3).

- ➤ W2W stacking consists on bonding a wafer on the top of another wafer and requires having the same size of dies. W2W stacking offers high throughput to address the needs of several applications such as smart imagers [9]. However W2W stacking is limited when talking about exploiting Known-Good Die (KGD) test results.

- ➤ Die-to-wafer (D2W) stacking consists on bonding a die on the top of a wafer. This assembly approach address the needs of several applications such as High

Performance Computing (HPC) [10] and it is advantageous for yield reasons (Known-Good-Die) and to integrate different sizes dies from different manufacturing lines.

Figure 3: 3D stacking options: (a) W2W, (b) D2W

In this thesis work, we focuses on fine pitch interconnects, that optimize performance of 3D-IC by integration of fine grained architectures. The functional units are vertically stacked using inter-die interconnects like  $\mu$ -bumps or Cu-Cu interconnects and intra-die interconnects Through Silicon Vias (TSV). 3D stacking integration has been providing an alternative to:

- ➤ Reduce the interconnections length and associated RC delay

- ➤ Integrate heterogeneous and homogeneous integrations

- > Offer a small form factor

- ➤ Integrate different technology nodes

- ➤ Reduce power consumption

## II. High-Density 3D-IC interconnects

#### 1. Overview

Current high-end electronics consist of advanced 2D system-on-chips (SoC) stacking onto each other – usually named by 3D stacked ICs. This 3D integration has been driven by economically and technically attractive viewpoints for further developing high performance systems. However, the semiconductor industry is continuously demanding products with higher integration density, higher performance, lower power consumption and reduced cost.

Compared to  $\mu$ -bumps integration, that face major challenges to go beyond 10 $\mu$ m pitch due to pattern processing complexity, stacking alignment accuracy and stable solder material, Cu-Cu direct bonding technique is more promising for fine pitch and high density interconnects [11] (Figure 4).

Cu-Cu hybrid bonding is a direct bonding technology which obtains metal-metal bonding and dielectric-dielectric bonding simultaneously and provides a solution for scaling below 10µm pitch with improved physical as well as an efficient 3D connection between processors and memories, digital and analogue circuits and MEMS cointegration [12].

Figure 4: Evolution of inter-dies interconnects

### 2. Cu-Cu hybrid bonding interconnects

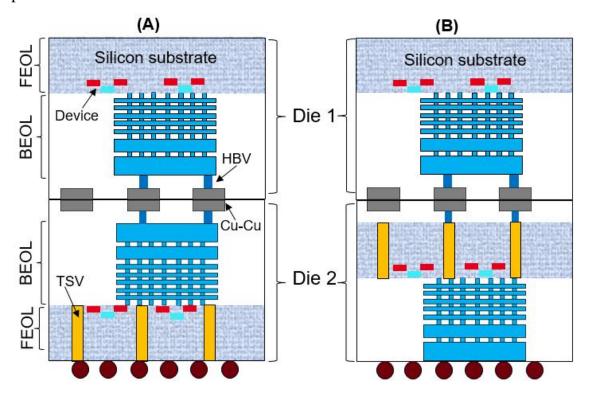

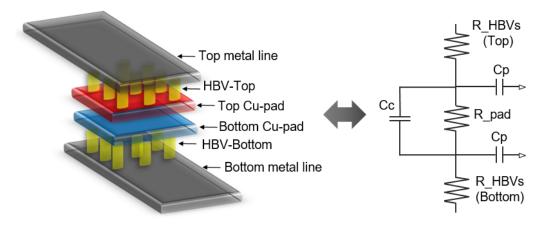

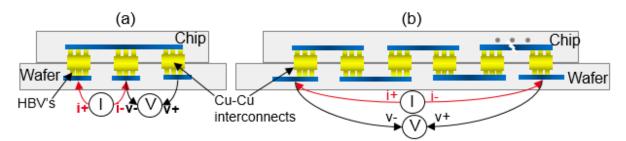

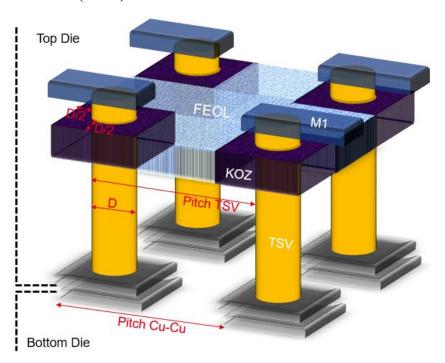

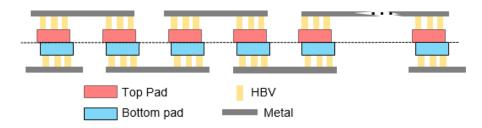

Figure 5 presents an example of high density 3D-IC using F2F bonding technology (Figure 5.a); the wafers/dies are connected thanks to Hybrid Bonding Metal pads (HBM) and Hybrid Bonding Vias (HBV): for both dice, HBV connect the top metal layer to the Cu-pads. The lowest metal layer of bottom die is connected to backside bumps using larger TSVs. Compared to conventional wire-bond chip interconnections, TSVs offer a number of key advantages: high density, low latency, and low power dissipation [13].

For F2B stacking orientation (Figure 5.b); silicon substrate side of a first die is bonded with metal layer of the second die using high density TSVs. The stacking process depends on many parameters such as the specifications of the application and the cost, and has an impact on the test of the 3D stack.

Figure 5: Cross-sectional view of high density 3D-IC structures: (a) F2F, (b) F2B

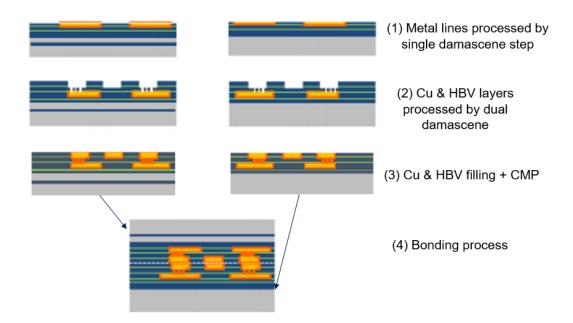

An example of process flow described in [14], [15] is shown in figure 6. Firstly, the metal lines are processed by single damascene step. Thereafter, the hybrid bonding level is deposited using a double damascene process; in this approach, two wafers/ dies modified to ensure very low final surface roughness and minimal Cu recess at the surface. After Chemical Mechanical Polishing (CMP) process for surface planarization and copper dishing minimization, the top and bottom wafer/die level are bonded. Finally, the wafer is thinned and the backside is opened to metal lines.

Figure 6: Example of hybrid bonding process flow (source [15])

### 3. High density TSVs

The idea of using through-silicon-via (TSV) technology has been around for many years. A through-silicon via (TSV) cross vertically the silicon layers in order to establish electrical links between the different stacked dies in the 3D-IC system. TSVs are often use as an alternative to wire-bond and flip chips. Many 2.5D and 3D packages are using the TSV technology compared Package-on-Package (PoP) technology. This is because the small pitch between TSVs that allows a high density of interconnections.

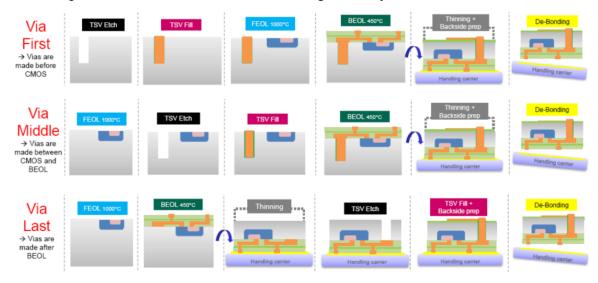

Figure 7: Via-first, via-middle and via-last illustration (source [16])

There are three main types of TSV approaches: TSV-first, TSV-middle, and TSV-last that correspond to three fabrication ways (Figure 7). The via-first TSV is fabricated directly on the silicon before any step of integration of active components, which means before the Front End of the Line (FEOL). The Via-middle TSV is fabricated after the

active components, which means after the FEOL process but before the Back End of the Line (BEOL) process. The via-last TSV is made after the FEOL and BEOL processes.

The semiconductor industry is actively pursuing 3D Integrated Circuits (3D-ICs) with TSV technology. The semiconductor industries already succeeded to reduce the pitch of hybrid bonding interconnects below 2µm. On the other hand, many methodology demonstrate the fabrication of reliable high-density TSVs that can be fabricated on the same Cu-Cu interconnects pitch [17], [18].

# III. Applications

#### 1. CMOS image sensor

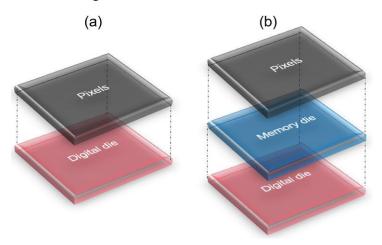

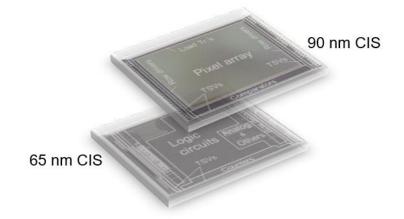

CMOS image sensors (CISs) are widely used widely used in products such as digital still cameras or digital video [19]. Conventional CMOS image sensors contain the pixel section and the analog logic circuit on the same chip, which imposes many constraints due to large footprint. High density 3D integrations has many advantages for this kind of application; it helps maintain high performance and offers advanced functionality in a compact chip size. The principle of 3D CISs is to dedicate the top layer to pixels and bottom layer for logic processing (two layers image sensor) [20], [21] (see Figure 8.a). There are another implementation using three layers [22]; a memory layer is used to achieve high-speed readout (Figure 8.b).

Figure 8: Structure of stacked CMOS image sensor: (a) two layers, (b) three layers

Sony was first to bring stacked image sensor chips to market; "Exmor RS" is the first stacked CMOS image sensor announced by Sony on 20 August 2012, widely used for phone cameras, which combine superior image quality and advanced functionality with a compact size with a pixel size of 1.12µm [23] (Figure 9). The via-last TSVs are used to connect top and bottom [24]. However, imperfect parallel processing limits the performance in such sensors because the TSV/micro-bump is larger than the pixel size (less than 10µm). High-density 3D-IC integration allows pixel-parallel signal processing

and provides excellent electrical connectivity and reliability with a higher 3D interconnect density (more than  $10^6/\text{cm}^2$ ).

Figure 9: Micrograph of "Exmor RS" CMOS image sensor (source [23])

In 2016, Sony shifted its interconnect strategy for image sensors using Cu-Cu hybrid bonding with a pitch of 6.3  $\mu$ m with dummies Cu-Cu pads covering most of the active pixel array and peripheral regions [25], [26]. In 2019, Sony was successfully developed a fine pitch 3  $\mu$ m pitch Cu-Cu hybrid bonding process [27].

Among the producers of 3D image sensors there are also OmniVision with a first stacked chips, fabricated on the PureCel-S platform using TSV technology and a 1.12  $\mu$ m pixel size. Later, OmniVision released 1.1  $\mu$ m pixel generation PureCelPlus-S chips, fabricated by foundry partner TSMC [28], [29]. In 2018, Samsung Electronics introduced also the three-layer ISOCELL Fast 2L3 image sensor with a pixel size of 1.4 $\mu$ m.

In 2018, CEA-Leti and STMicroelectronics developed the hybrid bonding technology for image sensors with a pitch of 1.44µm [6]. It is expected that the future generations of 3D image sensors will allow pixel-parallel signal processing. So, the pitch of 3D interconnects must be equivalent to pixel size.

### 2. High performance computing

3D stacking integration allows integrating heterogeneous components such as Processor, FPGA, GPU, Memory, etc. and offers excellent platform to achieve superior bandwidth, low power consumption. It's the main driver of the high end computing applications such as data centers [30].

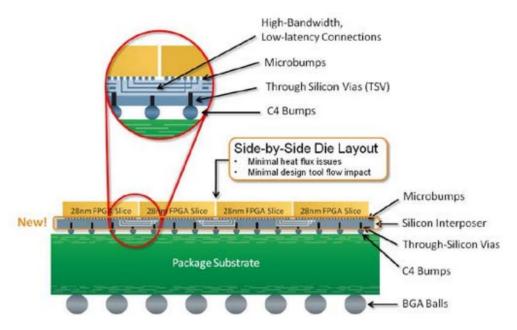

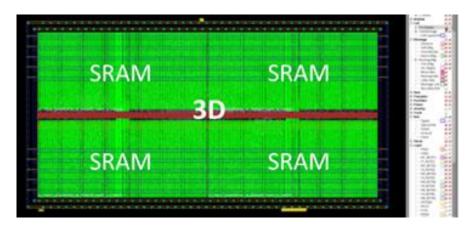

3D integration offers a possibility to integrate multiple technologies (logic, memory, RF, sensors ...) stacked together in a single package. Xilinx has developed Virtex-7 HT FPGA the world's first heterogeneous architecture for high-bandwidth and high-performance FPGAs (Figure 10). The architecture includes four separate 28nm FPGA dies were connected to each other through a 65nm passive silicon interposer using thousands of  $\mu$ -bumps with a pitch of 45 $\mu$ m [31].

Figure 10: architecture of Virtex-7 HT (source [31])

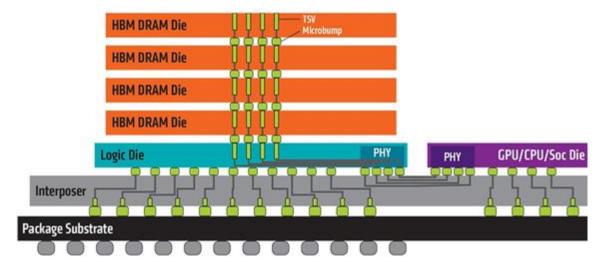

The ability to stack high density DRAM, such as High Bandwidth Memory (HBM) and Hybrid Memory Cube (HMC), on top of the logic die is extremely precious for several applications because of the reduction of the interconnect length witch increases the performance in terms of RC delay, power consumption and form factor. A stacking example of high-density DRAM dies on the top of each other, with one logic die at the bottom for control have been introduced in [32], [33]. Another example of high-density DRAM towers connected to the CPU or GPU through an interposer using TSVs and µ-bumps is shown in [34] (see Figure 11).

Figure 11: AMD Fury: HBM and CPU/GPU implementation using a passive interposer (source [34])

The main objective and challenge, in High Performance Computing (HPC) context, is to define modular and scalable computing with relatively low cost. Chiplet partitioning allows to reduce the overall system cost by designing smaller chips in an advanced technology (FinFET 14nm or 10nm), which will be sorted using Know-Good-Die (KGD) method and finally assembled onto a large scale interposer structure. As recent examples, [35] is a chiplet based architecture, from AMD, with chiplet stacking onto large scale organic substrate with up to 4 chiplets, while [36] is a chiplet based approach from TSMC using Chip-on-Wafer-on-Substrate (CoWos) 2.5D passive interposer technology, and finally [37] is chiplet based approach from INTEL using Embedded Interconnect Bridges (EMIB) technology. All these technologies are using  $\mu$ -bumps with different pitches, ranging from  $40\mu m$  to  $100\mu m$  pitches. HPC is not yet using hybrid-bonding technology, and for such application, the requirements are aggressive interconnect pitch and Die-to-Wafer (D2W) assembly scheme.

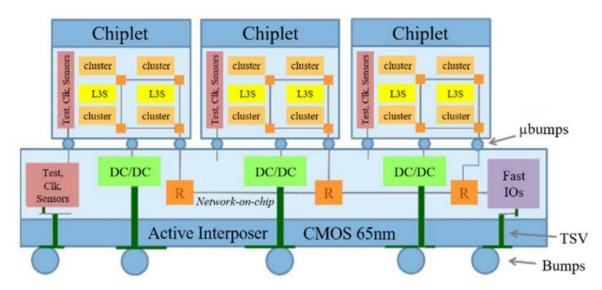

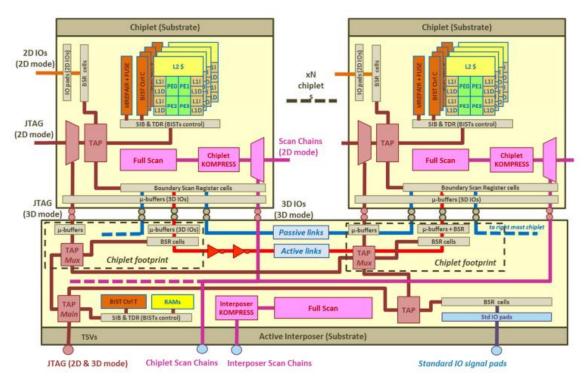

Another example of chiplet partitioning of a multi-core system was proposed by CEA-Leti and called Intact [38], [39] and [40]. Figure 12 shows the system architecture based on six identical 22mm² 28nm FD-SOI chiplets 3D-stacked onto 200 mm² 65 nm CMOS active interposer. The overall architecture integrates 96 cores with an innovative L1/L2/L3 coherent cache; 16 cores per chiplet (32-bit Microprocessor without Interlocked Pipelined Stage (MIPS) cores). The interposer integrates chip-to-chip communications using a robust asynchronous 3D Network-On-Chip (NoC), design-fortest, clocking and power management.

Figure 12: Intact system architecture overview (source [38])

# IV. Test and characterization challenges of HD 3D-ICs

### 1. High-density 3D-IC interconnect defect

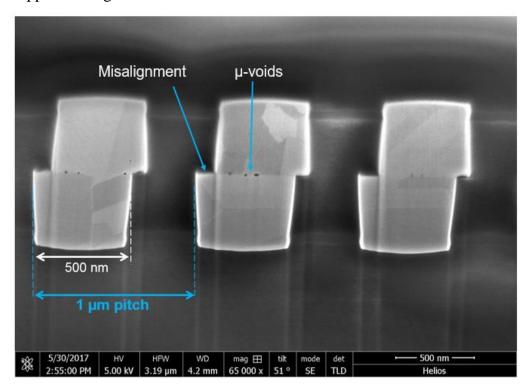

Cu-Cu hybrid bonding interconnects are prone to many structural defects due to fabrication process. Figure 13 shows misalignment and micro-voids defects in a Cu-Cu 3D-IC. A high precision wafer bonding tool it is important for 3D-IC fabrication, because it is necessary to have an important factor of accuracy to have a functional and performant

circuit. However, despite the rapid development of these new stacking technologies providing more and more interconnection density and even if stacking tools accuracy has been improved, providing accuracy down to ~200nm for Wafer-to-Wafer bonding and down to ~1μm for Die to-Wafer bonding [41].

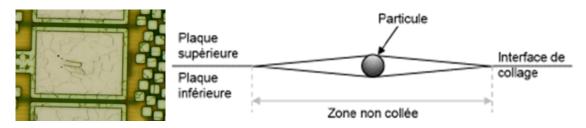

Translation, rotation and the magnification effect (run-out) are the causes of local misalignment; the global translation and rotation value depend on bonding equipment accuracy and are steadily minimized by continued developments of commercial bond alignment tools. But the run-out effect, which is related to the wafer expansion due to the thermal stress, is still one of the most challenging issues in 3D-IC bonding process [42].  $\mu$ -voids defects are in the form of cavity caused by practices at the contact surface level due to insufficient cleaning before bonding, they depend on particle size. A non-optimized CMP process may generate also  $\mu$ -void defects in the range of few nanometers due to copper dishing.

*Figure 13:* μ-voids and misalignment defect in Cu-Cu interconnects

The presence of this defects increases the interconnect resistance/ capacitance which will impact the performance and reduce the life time of 3D-ICs. Misalignment defect affects electrical characteristics (reduce the effective contact surface) and can cause leakage current overheads, resulting in an undesirable conductive path between two adjacent Cu-Cu interconnects which decrease the life time of the 3D-IC [43]. Therefore it is necessary to detect  $\mu$ -void defects, measure the alignment after bonding and electrically characterize the vertical interconnections in order to estimate the potential impact on the global performances.

### 2. Test challenges at system level

The test in system level is based on Design for Testing or design for testability (DFT), which consists adding testability features to a hardware product design. The added features make it easier to develop and apply manufacturing tests to the designed hardware. The purpose of manufacturing tests is to validate that the product hardware contains no manufacturing defects that could adversely affect the product's correct functioning. Tests are applied at several steps in the hardware manufacturing flow and, for certain products, may also be used for hardware maintenance in the customer's environment.

The tests are generally driven by test programs using Automatic Test Equipment (ATE), the response of vectors (patterns) from a good circuit is compared with the response of vectors (using the same patterns) from a DUT (device under test). If the response is the same, the circuit is good. Otherwise, the circuit is not used.

Traditionally, in 2D context, there are two moments of test of the individual dies: the first one is the test at wafer level that is performed after wafer fabrication and before assembly and packaging. The second test is the final test which is done after assembly and packaging. In 3D context, the test may have to be performed at pre-bond phase in order to provide Known Good Die (KGD) before stacking, mid-bond phase to test a partially assembled 3D stacks to Known Good Stack (KGS), post-bond phase to tests the complete 3D stacks yet still not packaged and finally test the packaged product [44].

#### a) Challenges of pre-bond test

The pre-bond test is done using Electrical Wafer Sort (EWS), also known as probing, is used to check the electrical functionality of the die at the wafer level. As mentioned previously, this test is performed at the end of the front-end part of the process, before assembly. The Probe Card [45], [46] and [47] holds the contact elements that establish the connection with pads and perform the electrical measurements. There are two major challenges in pre-bond test of high-density 3D-ICs:

- ➤ Despite the development of probe cards, the probing pitch is much higher than the pitch of Cu-Cu interconnects. So it's necessary to include non-contact testing methods such as Built-In-Self-Test (BIST) or adding oversized probe pads for probe needle touchdown.

- ➤ The probing process can damage the probing pads, causes particles at surface level and impact the bonding process (Figure 14); the damage in the bonding surface is equal to a thousand times that of the particle size. For this reason, the pre-bond test in D2W stacking option is unachievable.

Figure 14: Impact of probing process

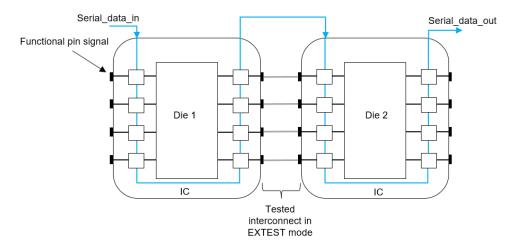

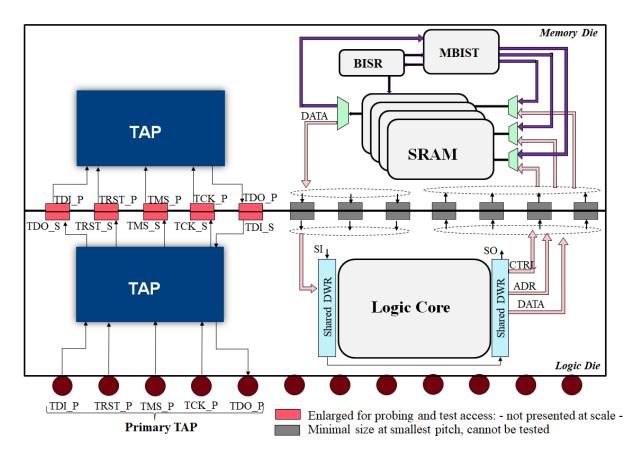

#### b) Challenge to test high-density 3D-IC interconnects

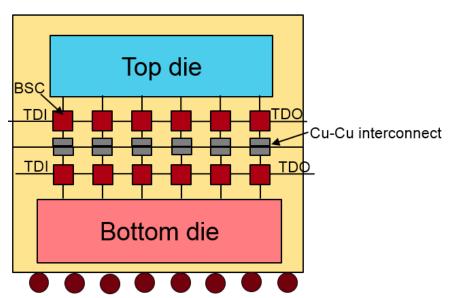

A DFT test access infrastructure is indispensable to achieve a high-quality test; some DFT structures are used such as internal scan chains, built-in self-test (BIST, Memory BIST) and Boundary Scan Cells (BSCs) around the embedded cores to provide isolation for internal testing (INTEST) and also external testing (EXTEST) of the 3D-IC interconnects between dies without requiring access to the entire die [48].

The BSCs on the first die provide observability, and the BSCs on the second die provide controllability (Figure 15). For timing reasons, the BSC cell must be close to the 3D interconnect to reduce the functional path length and the test time. For a high-density 3D circuit, the limited space for BSCs must be taken into account (the available surface per interconnect =Pitch²). Moreover, in F2B stacking orientation, the TSV and the keep-out-zone (KOZ) reduces the available surface.

Figure 15: Test of 3D-IC interconnects at system level

# V. PhD objectives and contributions

In this PhD thesis, we distinguish three main research axes:

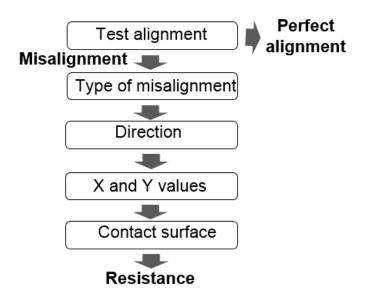

After studying the impact of Cu-Cu interconnect defect on electrical parameters, we need detect the presence of misalignment defect: our aims is to implement innovative and low cost test structures into the bonding interface

using Cu-Cu interconnects, used either in a passive way for technological process validation and characterization and obtain an additional information in case of misalignment such as direction, accurate value and obtain an additional information in case of misalignment such as direction and an accurate value. The proposed test structure will be explained, implemented for high-density 3D-IC interconnects in process development context and validated using overlay measurements obtained using IR metrology. Moreover, we need characterize Cu-Cu interconnects and estimate indirectly the contact resistance values.

- In the application circuit context, 3D DFT architecture ensures the test of all the components of the 3D system including the different stacked dies and the 3D interconnections at all the 3D bonding levels: pre, mid and post-bond levels. Test infrastructure of high-density 3D-ICs presents new test challenges because of the high interconnects density and the area cost for test features. Our objective is to analyze the testability of HD 3D-IC; we define the most optimized Design-For-Test infrastructure depending on used standard and the minimum acceptable pitch value for a given technology node to ensure the testability of circuits. Afterwards, we need propose an optimized DFT architecture allowing pre-bond and post-bond for high-bandwidth and high-density 3D-IC application (SRAM-on-Logic) in line with the ongoing IEEE P1838 standard.

- Finally, we try to implement the proposed misalignment test structure used either in a passive way for technological process validation and characterization in the 3D DFT architecture to detect misalignment and μ-void defects and assess performance of high-density 3D-ICs using BISTs. If the functional interconnection test is impossible because of the aggressive pitch of 3D interconnects, the proposal must be used to perform functional and structural test of high-density 3D functional interfaces

This thesis is organized as follows:

Chapter 2 focuses mainly on the measurement of misalignment defect. Initially, we present the proposed solution to measure bonding misalignments. Afterwards, test results are detailed to validate the proposed test structure. Finally, we present the impact of misalignment defect on R & C parameters.

Chapter 3 focuses on the test of high-density 3D-IC interconnects at system level. Firstly, we analyses the testability of HD 3D-IC interconnect. Then, we present the

optimized DFT architecture for high density SRAM/Logic 3D-IC. Finally, simulation results are detailed.

Chapter 4 explains in details the need to add the proposed test structure, discussed in chapter 2, to the application circuit. Initially, the test flow is explained in details, followed by the description of the proposed BISTs to test misalignment and  $\mu$ -void defects. Finally, the validation of the model is explained by supporting simulation results.

Chapter 5 concludes the thesis with final outcome and future perspectives.

# Chapter II. Characterization of highdensity 3D-IC interconnects

Cu-Cu hybrid bonding is currently the ultimate fine pitch 3D interconnect solution with target pitch of  $1\mu m$ , but that generates new challenges for characterization; Cu-Cu interconnects are prone to many structural defects due to fabrication process such as misalignment and  $\mu$ -voids that affect the electrical characteristics. For technology development, before the production of the wafers with all FEOL and BEOL layers, several short loops, with only the top metal layer, must be carried out to enable incremental test and characterization. Several test vehicles are necessary to validate the technological process and perform electrical characterization of Cu-Cu interconnects: electrical characteristics, yield, reliability and electro-migration. In this chapter, we focus on characterization of Cu-Cu interconnects and we propose an innovative test vehicle to measure several information after bonding: perfect alignment, misalignment (direction, value) and contact resistance.

# I. Impact of defects on electrical characteristics

#### 1. Overview

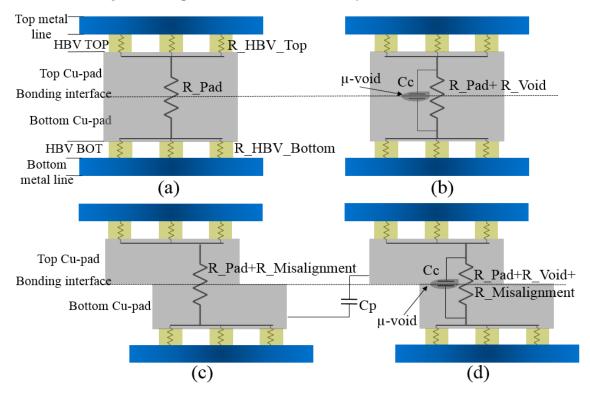

Misalignment and  $\mu$ -void defect affects electrical characteristics and can cause leakage current between Cu-Cu pads. Figure 16 illustrates the equivalent electrical model of Cu-Cu interconnect [49] to be used in simulation. The pad resistance (R\_pad) depends on the effective contact surface and the resistance of Hybrid Bonding Vias (R\_HBV) depends on the number of vias connecting the top metal layer to the Cu-pads, the gap between top and bottom Cu pad forms a coupling capacitance Cc and Cp is the parasitic capacitance due to the proximity between two adjacent Cu pads.

Figure 17 shows the impact of physical defects on our electrical model; in the defect-free case (Figure 17.a) the resistance of the Cu-Cu pad (R\_pad) is typically quite small and equal to the theoretical resistance with 100% of contact surface.  $\mu$ -voids at the bonding interface increase the resistance (Figure 17.b). Also, depending on the void area and the height (h), there may be a significant coupling capacitance (Cc). ). In the case of a misalignment defect (Figure 17.c), a parasitic capacitance (Cp) is inserted depending

on the distance between two adjacent Cu-pads and the resistivity effect due to the contact area decrease. Figure 17.d illustrates the overlay of misalignment and  $\mu$ -voids defects. Based on the proposed electrical model of Cu-Cu interconnects, we studied the impact of misalignment defect and  $\mu$ -voids on the capacitance and resistance values.

Figure 16: Equivalent electrical model of Cu-Cu interconnects

Figure 17: Impact of Cu-Cu interconnect defect on electrical characteristics

The first part of my work has been to study the impact of misalignment defect and  $\mu$ -voids on the capacitance and resistance values using the proposed electrical model of Cu-Cu interconnects. The theoretical resistance and capacitance values are obtained using respectively equation 1 and 2; the Cu-Cu interconnect resistance is the sum of the resistance of HBVs top and bottom, that depend on HBV length "l", HBV diameter "D" and the copper resistivity " $\rho$  Cu", and the resistance of Cu pads, that depend on the

copper resistivity, the effective contact surface between top and bottom pad and the pad thickness "h".

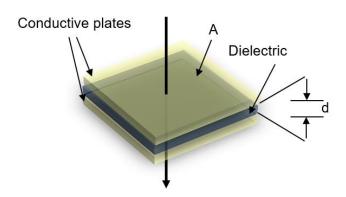

For capacitance calculation, the parallel-plate capacitor principle is used (Figure 18). The simplest model capacitor consists of two thin parallel conductive plates each with an area of "A" separated by a uniform gap of thickness "d" filled with a dielectric with permittivity  $\epsilon$ . It is assumed the gap d is much smaller than the dimensions of the plates. For the calculation of coupling capacitance "Cc", the area "A" and the gap thickness "d" are equal respectively to the  $\mu$ -void-surface and  $\mu$ -void-height. But, for parasitic capacitance calculation, the area "A" and the gap thickness "d" are equal respectively to Pad Size "PS" \* pad thickness "h" and the distance between two adjacent pads.

Figure 18: Parallel-plate capacitor model

Misalignment

$$(M) = \sqrt{X^2 + Y^2}$$

(1)

$$R = \frac{2 \times \rho cu \times h}{contact \, surface} + R(HBV's_{Top}; HBV's_{Bottom}) \tag{2}$$

With: - " $\rho$ cu" is the copper resistivity = 1.69×10<sup>-8</sup>  $\Omega$ .m. - R (HBV's Top/Bottom) is the Hybrid Bonding via resistance. - "h" is the pad thickness.

$$C = \mathcal{E} * \frac{A}{d}$$

(3)

With: - "E" is the permittivity =  $\mathcal{E}0* \mathcal{E}r = 3.45 \times 10^{-11} F.m^{-1}$ .

- "A" is the area and "d" is the gap thickness

Using the equations shown previously, we performed simulations to quantify the electrical impact of misalignment and  $\mu$ -void defects.

### 2. Impact of misalignment defect on electrical characteristics

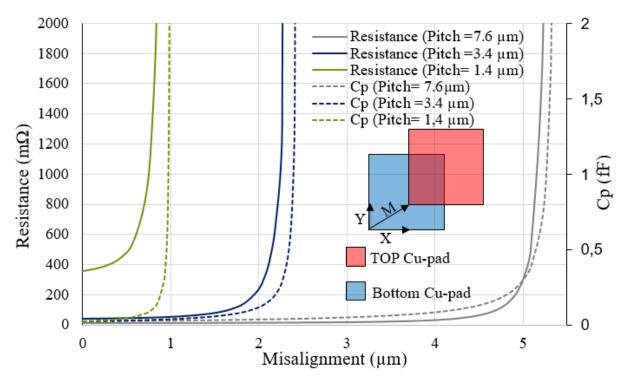

Figure 19 shows the variation of pad resistance (R\_pad) and parasitic capacitance (Cp) as a function of the misalignment value obtained using (1) (X=Y). The highest values of R\_pad and Cp are obtained at the limit of misalignment for a given pitch; i.e. for a pitch of 1.4  $\mu$ m (Pad-size=Pitch/2), the limit of misalignment  $\approx (0.7^2 + 0.7^2)1/2 \approx 0.99 \ \mu$ m. The optimal pad resistance values (corresponding to the perfect alignment M  $\approx$  0) vary from one pitch to another: they depend on the pad size and the number of HBVs (equal respectively to 25, 9 and 1 for pitch of 7.6, 3.45 and 1.4  $\mu$ m).

Figure 19: Variation of the resistance and parasitic capacitance of a Cu-Cu pad (pitch: 7.6, 3.45 and 1.4µm) as a function of misalignment.

### 3. Impact of $\mu$ -void defects on electrical characteristics

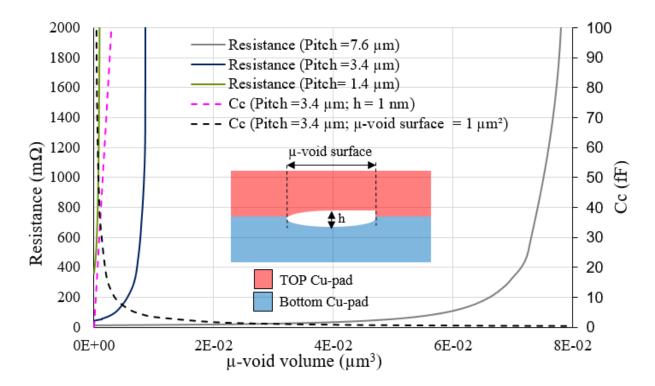

Figure 20 shows the impact of  $\mu$ -void on R and C parameters; the resistance depends only on the  $\mu$ -void surface but the coupling capacitance Cc depends on  $\mu$ -void surface and the height h, for these reason the impact of the surface and the height on Cc are studied separately (Pink and black dashed lines). When the  $\mu$ -void surface becomes comparable to the pad surface, the resistance and coupling capacitance reaches the maximum. In the other side, we observe that the increasing in Cc values becomes more important with a lower "h" values.

According to the study of high-density 3D-IC interconnects defects impact on electrical characteristics, we can affirm that misalignment and  $\mu$ -void impact becomes more important with a lower pitch (1.4 $\mu$ m). We show also that electrical impact is mostly

resistive and it's similar for misalignment and  $\mu$ -void defects since it depends on the effective contact surface, which makes it difficult to separate defects.

Figure 20: Variation of the resistance and coupling capacitance of a Cu-Cu pad (pitch: 7.6, 3.4 and 1.4 $\mu$ m) as a function of  $\mu$ -void volume.

In the other hand, actually the parasitic capacitance "Cp" has a small value except in the case of high misalignment values (i.e. Misalignment in X or Y direction  $\approx$  pad size). But the coupling capacitance "Cc" can have great values mostly when one or more  $\mu$ -voids appears in the contact surface interface.

#### II. Characterization methods: state of the art

# 1. Morphological methods

There are lots of methods for failure analysis of damages on wafer, including but not limited to: optical microscopy, Scanning Electron Microscope (SEM), Transmission Electron Microscopy (TEM), X-ray and Scanning Acoustic Microscopy (SAM).

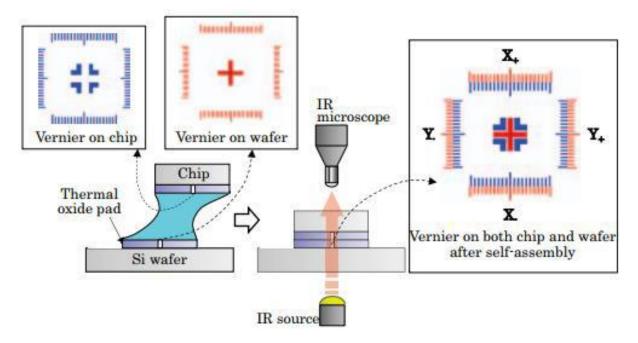

The Infra-Red (IR) metrology tool (IR light system and alignment marks) [50] controls and evaluate bonding quality before and after bonding process (Figure 21). This module allows to control the fine movement of the wafers before bonding process [51]. Although both translational and rotational errors could be controlled and minimized during the alignment step, the run-out error remains a key contributor to the entire overlay error. Therefore, to handle a wafer without damaging it and to achieve higher alignment accuracy, the wafer should be affixed to flat using an electrostatic chuck [52]. After

bonding process, the misalignment measurements for all wafer reticles, using IR metrology tool, require a long testing time. Moreover, the measurements must be disturbed because of the absorption of the IR ray by all the dielectric layers.

Figure 21: IR metrology tool principle (source [50])

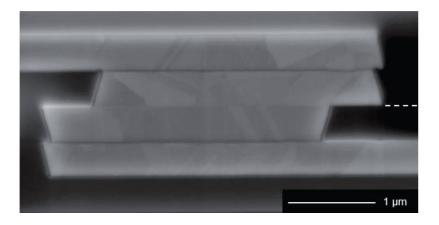

In 3D-IC context, Scanning Electron Microscopy (SEM) and transmission electron microscopy (TEM) are the most used techniques, allows to visualize defects at the bonding interface [53]. The method used in SEM is based on scattered electrons while TEM is based on transmitted electrons. The scattered electrons in SEM produced the image of the 3D interconnects after the microscope collects and counts the scattered electrons. In TEM electrons are directly pointed toward the 3D interconnects. SEM provides a three-dimensional image but TEM delivers a two-dimensional picture. In terms of resolution, TEM has an advantage compared to SEM. The resolution of TEM is less than 0.2 angstroms while SEM has a few of nanometers. Contrariwise this techniques need a very expensive equipment's and must be housed in an area free of any possible electric, magnetic or vibration interference [54]. Moreover, this techniques are destructive, figure 22 shows an example of SEM image of Cu-Cu interconnect.

Figure 22: Example of SEM image of Cu-Cu interconnect (source [55])

#### 2. Electrical measurements

Another alternative to detect misalignment is based on electrical measurements (resistance and capacitance) with two classical test structures (Kelvin and Daisy chain) [56]. In these works, Rth is obtained using equation (2) with contact surface equal to the pad area (PS $^2$ ). The principle of the Kelvin measurement method is shown in figure 23.a. Four-point V+, V-, I+, I- method is used for an accurate measurement of a single interconnect in regard to a typical 2- point resistance measurement. If we have a perfect alignment then R=Rth. And if we have a misalignment defect, the resistance value increases when top-bottom contact surface decreases. The same principle is used for daisy chains (Figure 23.b), but in this case the measured resistance value also includes horizontal interconnects resistance through the daisy chain. Electrical measurements allow to characterize high-density 3D-IC but do not allow to obtain an accurate information about defects characteristics (direction, contact surface ...) because of the similar effect of the misalignment and  $\mu$ -void defects on the electrical characteristics.

Figure 23: Electrical measurement test vehicle: (a) Kelvin, (b) Daisy chain

Cu-Cu hybrid bonding offers very high-density interconnects (pitch around  $2\mu m$  or less) in 3D stacking integrated circuits, but the smaller the Cu pad size, the more the bonding defects, such as misalignment and  $\mu$ -voids, have an important impact on resistance and capacitance parameters. The currently used methods are all focusing on

process characterization and are not able to provide active performance characteristics of a real 3D Integrated Circuit because of the test time and cost.

Our aims is to implement innovative and low cost test structures into the bonding interface using Cu-Cu interconnects, used either in a passive way for technological process validation and characterization and implemented in high-density 3D-ICs to assess performance; we need distinguish defects (misalignment and/or  $\mu$ -voids); obtain an additional information in case of misalignment such as direction, accurate value and detect also  $\mu$ -void defect. In a second time, we try to characterize Cu-Cu interconnects and estimate indirectly the contact resistance values.

In the next part, a new methodology to determine both misalignment characteristics and performances as described thereafter. Firstly, the proposed test structure will be explained, implemented for high-density 3D-IC interconnects in process development context and validated using overlay measurements obtained using IR metrology. Subsequently, the proposed test structure will be implemented in an application circuit for a structural test of the 3D functional interfaces and will be used in conjunction with other test structure to detect  $\mu$ -void defects.

### III. Proposed structure to test bonding alignment and characterize HD 3D-IC interconnects

#### 1. Overview

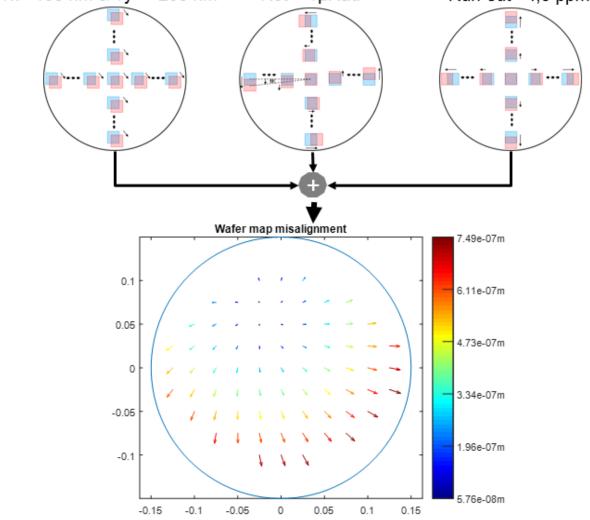

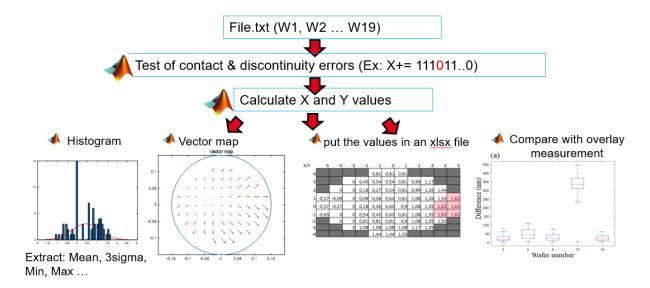

The vector formula of translation, rotation and run-out, that are the causes of local misalignment, are explained respectively in (4), (5) and (6). Translation ( $T_x$  and ( $T_y$ ) and rotation ( $\theta$ ) relate to the misalignment of the wafer. The run-out effect ( $\rho$ ) relates to the wafer size change or wafer expansion due to processing. Wafer processing will include a variety of stressed thin film depositions, hot anneals, and other processes which can change the wafer size. The run-out effect is expressed in ppm (parts per million, i.e., 10-6) range. So, to exhibit misalignment defect on a wafer map, we developed a specific tool using MATLAB in W2W context "virtual wafer vector map tool" to enable us to easily visualize the superposition of translation, rotation and end-of-course effects as a wafer map vectors.

$$\begin{pmatrix} x' \\ y' \end{pmatrix} = \begin{pmatrix} x \\ y \end{pmatrix} + \begin{pmatrix} T_{-}x \\ T_{-}y \end{pmatrix} \tag{4}$$

$$\begin{pmatrix} x' \\ y' \end{pmatrix} = \begin{pmatrix} \cos(\theta) & -\sin(\theta) \\ \sin(\theta) & \cos(\theta) \end{pmatrix} * \begin{pmatrix} x \\ y \end{pmatrix}$$

(5)

$$\begin{pmatrix} x' \\ y' \end{pmatrix} = \begin{pmatrix} 1+\rho & 0 \\ 0 & 1+\rho \end{pmatrix} * \begin{pmatrix} x \\ y \end{pmatrix}$$

(6)

$$\begin{pmatrix} x' \\ y' \end{pmatrix} = \begin{bmatrix} \cos(\theta) & -\sin(\theta) \\ \sin(\theta) & \cos(\theta) \end{pmatrix} * \begin{pmatrix} 1+\rho & 0 \\ 0 & 1+\rho \end{pmatrix} * \begin{pmatrix} x \\ y \end{pmatrix} \end{bmatrix} + \begin{pmatrix} T_{-}x \\ T_{-}y \end{pmatrix}$$

(7)

$$\downarrow \downarrow \downarrow$$

$$x' = [x * \cos(\theta) * (1+\rho)] - [y * \sin(\theta) * (1+\rho)] + T_{-}x$$

$$y' = [x * \sin(\theta) * (1+\rho)] + [y * \cos(\theta) * (1+\rho)] + T_{-}x$$

Tx= 150 nm & Ty= - 250 nm Rot = 1 $\mu$ Rad Run-out= 4,3 ppm

Figure 24: Wafer map: example of misalignment simulation

Figure 24 shows an example of simulation, the misalignment vectors shown in the wafer map are the results of the superposition of translation effect (T\_X=150nm and

$T_Y=-250$ nm), rotation of 1µRad and a run-out of 4.3ppm (part per million). For each vector, (x, y) are the origin coordinates of the vector (position in wafer) and (x', y') are the head coordinates of the vector calculated using (7). The color bar present misalignment value calculated using (1). We show that the maximum local misalignment value is equal to 750nm. In complement of misalignment prediction, the developed tool will also be used later to analyze the fabricated wafers.

In the other hand, we can affirm that the misalignment is not uniform at wafer level. So, a misalignment measurement module is needed in each reticle of the wafer to quantify misalignment defect, characterize high-density interconnects in the process development phase and classify the application circuits in order of performance in production phase.

#### 2. Principle of the proposed test structure

According to the misalignment analysis shown previously, a low cost test structure is needed to measure accurately the misalignment defect and determine the misalignment direction in W2W and D2W stacking options. On the other side, as long as the structure will be implemented using Cu-Cu interconnects, there are many constraints that we can face: the respect of the bonding-interface planarity and the number of needed metal levels. Moreover, the test structure must be implemented for process development (using only metal layers) and for application circuit (using digital circuit), therefore for stimulus, the same signal must be used but it will be translated as analog signal (voltage) in the case of characterization (process development) and as a digital signal ('0', '1') in the application circuit.

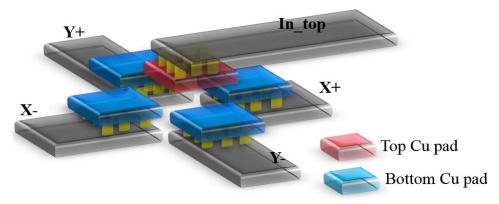

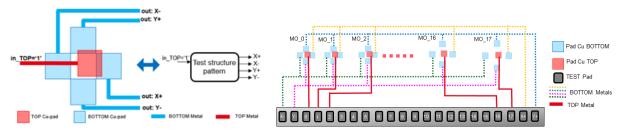

In order to measure the misalignment, we describe a specific structure based on alignment reference patterns composed by a top Cu-pad (Red) and four Bottom Cu-pads (blue) (Figure 25). To test the bonding misalignment and its direction, we inject a signal at the input (in\_TOP) and we observe the binary digital outputs: X+, Y+, X-, and Y-. In case of misalignment, the top Cu-pad is in contact with one or more bottom Cu-pads. On the other hand if there is no contact between top and bottoms pads, we can conclude that the alignment is perfect.

Figure 25: The reference pattern of misalignment test structure

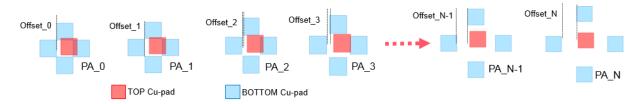

The duplication of the reference pattern, using different spacing values (Offset\_N) between bottom Cu-pads, offers the possibility to estimate the misalignment value (Figure 26). The misalignment value in X+, X-, Y+ or Y- direction is equal to the offset value of the last pattern which has top/bottom connections (contact between top pad and the tested direction bottom pad). So, the accuracy of the proposed test structure depend on the offset values as well as the number of the used patterns.

Figure 26: N patterns using different "offset" values

#### 3. Misalignment test structure architecture

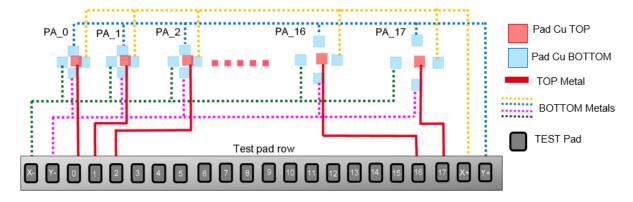

The implementation of the proposal for process development requires a probing test row to stimulus patterns. To reduce the number of test pads, the outputs are grouped to have common signals (X+, X-, Y+ and Y-) for all patterns. So, the number of patterns depends on probing test row pads. In this implementation a probing test row with 22 test pads is used: 4 test pads for the common signals (X+, X-, Y+ and Y-) and 18 for inputs patterns. The offset values will be set according to the used pitch as well as the accuracy of bonding equipment.

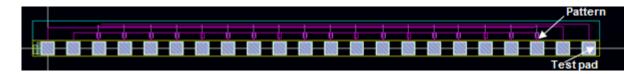

Figure 27 shows the architecture of the misalignment test structure. It contains 18 patterns ( $PA_0...PA_17$ ) and a probing test row (22 test pads). To measure misalignment values, electrical test consists in current injection through pattern inputs and sensing outputs X+, X-, Y+ and Y- or vice versa. The layout of the proposed test structure is shown in figure 28; the area of the test structure is around 0.2 mm² and we show that the area of test pads is very large compared to that of the patterns.

Figure 27: Misalignment test structure architecture

Figure 28: Layout of the proposed test structure

The test vehicle was fabricated in a Wafer-to-Wafer (W2W) assembly configuration with either a pitch of 3.42 $\mu$ m and 1.44 $\mu$ m using a very small measurement step for an accurate misalignment test structure. Table 1 shows the accuracy (step) and the offset values of the proposed misalignment test structure. We distinguish four zones; Z1, Z2 and Z3 corresponding to the coverage of the test structure while Z4 is out of the structure coverage. Due to test chip constraints, for the pitch of 3.42 $\mu$ m we have implemented X direction only and Y direction only with a double step of 45nm in Z1. While for the finest pitch (1.44 $\mu$ m), we have implemented X and Y with a step of 22.5nm to provide the best accuracy measurement.

|       | Bloc X only<br>3.4 µm<br>Offset (nm) | Bloc Y only<br>3.4 µm<br>Offset (nm) | Step 3.4 (nm) | Bloc 1.4 µm<br>Offset (nm) | Step 1.4 (nm) | Z  |

|-------|--------------------------------------|--------------------------------------|---------------|----------------------------|---------------|----|

| PA_0  | 22.5                                 |                                      |               | 22.5                       |               |    |

| PA_1  |                                      | 45                                   |               | 45                         |               |    |

| PA_2  | 67.5                                 |                                      |               | 67.5                       |               |    |

| PA_3  |                                      | 90                                   |               | 90                         |               |    |

| PA_4  | 112.5                                |                                      | 4.5           | 112.5                      | 22.5          |    |

| PA_5  |                                      | 135                                  | 45            | 135                        | 22.5          |    |

| PA_6  | 157.5                                |                                      |               | 157.5                      |               | Z1 |

| PA_7  |                                      | 180                                  |               | 180                        |               |    |

| PA_8  | 202.5                                |                                      |               | 202.5                      |               |    |

| PA_9  |                                      | 225                                  |               | 225                        |               |    |

| PA_10 | 247.5                                |                                      |               | 247.5                      |               |    |

| PA_11 |                                      | 270                                  |               | 270                        |               |    |

| PA_12 | 292.5                                |                                      |               | 292.5                      |               |    |

| PA_13 |                                      | 315                                  |               | 315                        |               |    |

| PA_14 | 360                                  |                                      | X:67          | 360                        | 45            | Z2 |

| PA_15 |                                      | 540                                  | Y:225         | 405                        |               |    |

| PA_16 | 810                                  |                                      | X:450         | 495                        | 90            | Z3 |

| PA_17 |                                      | 1260                                 | Y:720         | 585                        |               |    |

Table 1: Offset values

#### 4. Test structure validation

a) Test results: pitch 3.42µm and 1.44µm

#### > Pitch 3.42μm

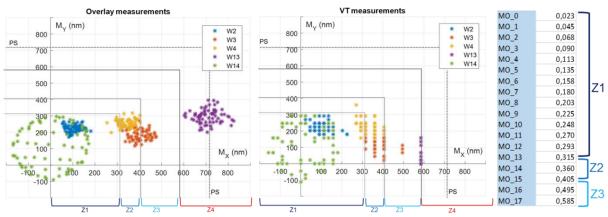

After the bonding process using W2W assembly, an electrical test was performed for five multi-pitch wafers. Figure 29 shows the misalignment distributions of the five wafers using misalignment test structure (pitch = $3.42\mu m$ ) with 71 measurement points for each wafer (superposition for some measurements).

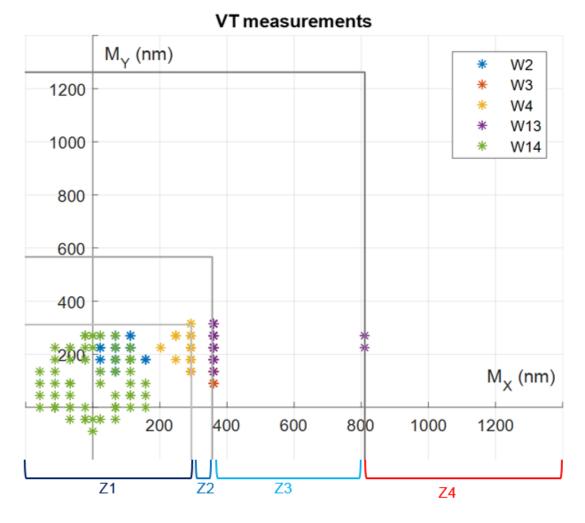

We distinguish four zones; Z1, Z2 and Z3 corresponding to the coverage of the test structure (see Table 1) while Z4 is out of the structure coverage. The misalignment values of W2 and W14 are located in Z1 and those of W3, W4 and W13 are in Z2 and Z3 area. For instance, in real wafers misalignment values are all included in the capability of our test structure. In addition, our design provides high resolution (45nm) for a misalignment values between 0 and 300nm (Zone 1) but this resolution decreases for higher misalignment values.

Figure 29: Misalignment test structure results (Pitch=  $3.42\mu m$ )

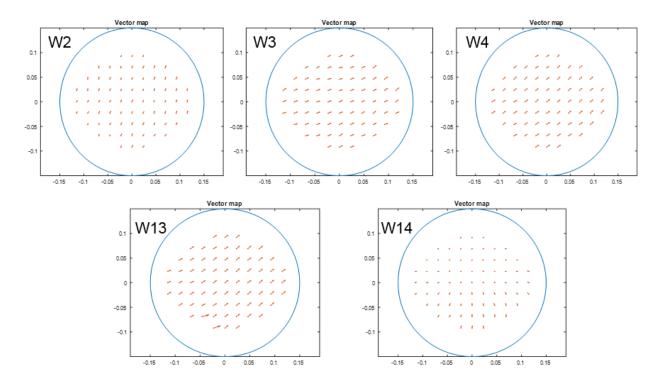

The test coverage of the misalignment test structure is equal to  $0.8\mu m$  for X direction and  $1.2\mu m$  for Y direction. Using the virtual wafer vector map tool developed previously, we visualize the misalignment wafer map of the five tested wafer (see Figure 30). For W2, W3, W4 and W13 it happens that translation is the predominant effect whereas runout is predominant for W14. Table 2 shows minimum, maximum, mean and 3sigma values for wafers.

*Figure 30: Misalignment wafer map for five wafers (Pitch= 3.42μm)*

|        | W2     |             | W3  |             | W4  |             | W13 |             | W14  |         |  |

|--------|--------|-------------|-----|-------------|-----|-------------|-----|-------------|------|---------|--|

| Axis   | X      | Y           | X   | Y           | X   | Y           | X   | Y           | X    | Y       |  |

| Max    | 158    | 270         | 360 | 315         | 360 | 320         | 810 | 320         | 158  | 270     |  |

| Min    | 23     | 140         | 293 | 90          | 203 | 140         | 360 | 140         | -160 | -90     |  |

| Mean   | 81     | 200         | 350 | 161         | 309 | 240         | 370 | 270         | 0    | 90      |  |

| 3 σ    | 102    | 90          | 72  | 147         | 117 | 120         | 210 | 150         | 267  | 330     |  |

| Effect | Transl | Translation |     | Translation |     | Translation |     | Translation |      | Run-out |  |

*Table 2: Statistical data of misalignment test results (Pitch=3.42µm)*

We observe that the five wafers exhibit a different range of misalignment values; the minimum misalignment values are observed for W2 and W14 and the maximum

misalignment values are observed for W13. The 3-sigma value represents the dispersion of misalignment values and explain the distorted wafers (run-out effects).

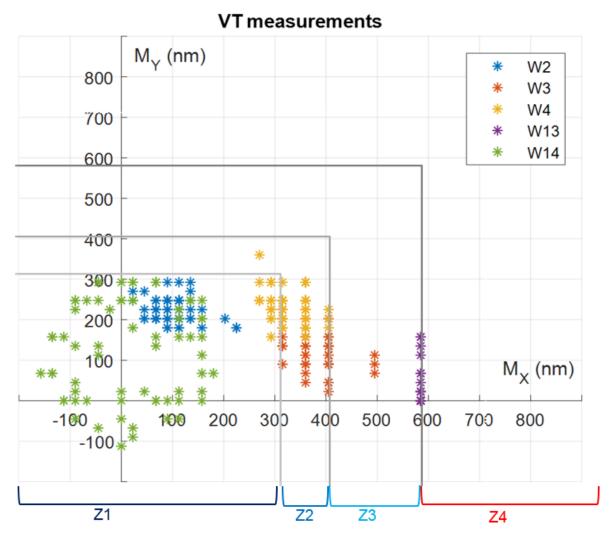

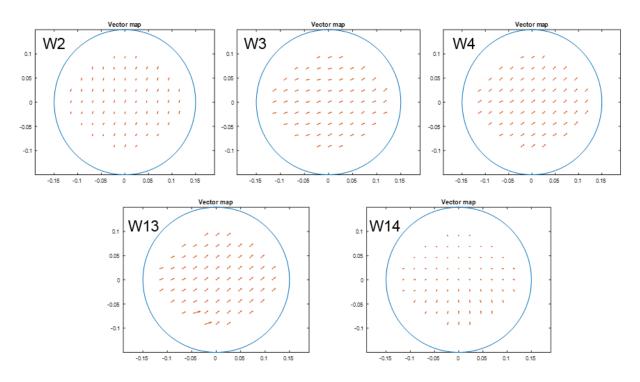

#### ➤ Pitch 1.44µm

Figure 31 and figure 32 show respectively the misalignment distribution and the wafer map of the five wafers using the test structure (pitch=1.44 $\mu$ m) with 71 measurement points for each wafer (superposition for some measurements). We show that the misalignment values of W2 and W14 are in Z1 area, those of W3 are in Z2 and Z3 and that and those of W4 are in Z2 (including some results in Z1). For W13 the misalignments values are in Z4 (off cover zone). Moreover, for W13 (in X direction), there are some misalignment measurements that exceed the pad size (PS) and induce an artifact on the results of Y direction.

Figure 31: Misalignment test structure results (Pitch=  $1.44\mu m$ )

Table 3 shows the minimum, maximum, mean and 3 sigma values for each wafer. W2, W3, W4 and W14 the measurements are very close to the 3.42 µm pitch results, due to the small distance between the test structures as well as the offset values. W13

misalignment values (in X direction) are greater than our actual structure's coverage. For the rest, we will not take the W13 measurements into consideration.

Figure 32: Misalignment wafer map for five wafers (Pitch=  $1.44\mu m$ )

|        | W2          |     | W3      |       | W4          |     | W13         |     | W14     |      |

|--------|-------------|-----|---------|-------|-------------|-----|-------------|-----|---------|------|

| Axis   | X           | Y   | X       | Y     | X           | Y   | X           | Y   | X       | Y    |

| Max    | 225         | 293 | 495     | 292   | 405         | 360 | 585         | 157 | 180     | 293  |

| Min    | 22          | 180 | 315     | 22    | 270         | 158 | 585         | 0   | -158    | -113 |

| Mean   | 98          | 227 | 377     | 139   | 325         | 232 | 585         | 14  | 16      | 123  |

| 3 σ    | 118         | 91  | 122     | 176   | 103         | 113 | 0           | 117 | 292     | 364  |

| Effect | Translation |     | Transla | ation | Translation |     | Translation |     | Run-out |      |

*Table 3: Statistical data of misalignment test results (Pitch=1.44µm)*

### b) Comparison of misalignment test structure results with overlay measurements

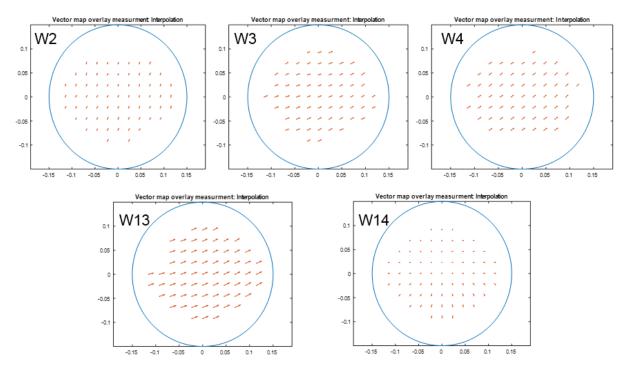

The test results of the five wafers for the pitches of 3.42 and 1.44 are similar and offer a different range of misalignment values. To validate the proposed test structure, we compare the test results with the overlay measurements obtained using IR imaging tool. Figure 33 and figure 34 show respectively the overlay measurements distribution and the wafer map of the five wafers with 71 measurement points for each wafer.

#### Overlay measurements

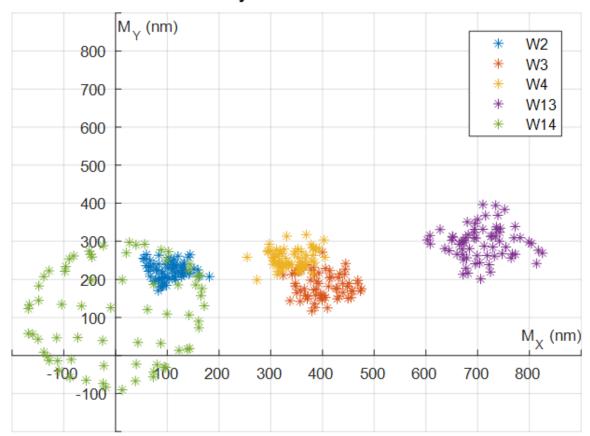

Figure 33: Overlay measurements distribution

Figure 34: Wafer map results using overlay measurements

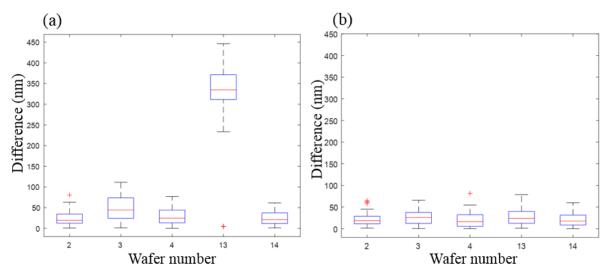

### > Comparison of misalignment test structure results (pitch 3.42μm) with overlay measurement

The comparison between overlay measurements and test structures results is done using "boxplot" plots. On each box, the central mark indicates the median, and the bottom and top edges of the box indicate the 25th and 75th percentiles, respectively. The whiskers extend to the most extreme data points not considered outliers, and the outliers are plotted individually using the '+' symbol. We differentiate between overlay measurements and misalignment test vehicle results for each wafer and for 71 measurement points.

Figure 35: Comparison of test structure results (3.42 $\mu$ m pitch) and overlay measurements in X and Y direction

Figure 35 shows the comparison results for the five wafers in X and Y direction. For W2 and W14, we show that the most of difference values are smaller than the resolution in Z1 (45 nm), for W3 and W4 the difference is smaller than the resolution of Z2 (90nm) and Z3 (X/Y: 450/720nm) and for W13 the difference values are very high since the measurements are in Z3.

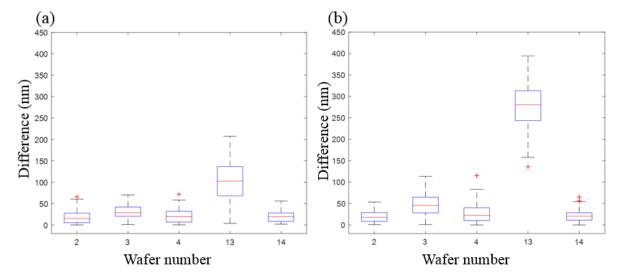

#### Comparison of misalignment test structure results (pitch 1.44μm) with overlay measurement

Figure 36 shows the comparison for the five wafers in X and Y direction; concerning W2 and W14 we show that the majority of difference values are less than the resolution in Z1 (22.5 nm), for W4 and W3 the differences is respectively less than the resolution of Z2 (45nm) and Z3 (90nm). Then for W13 the differences values are very high. Because for X direction the misalignment values are in Z4 (off cover zone) and some misalignment values exceeds the pad size, it is not possible to measure misalignment in Y direction using this test structure. Therefore, we do not include the results of W13 in

the comparison. In conclusion for the wafers W2, W3, W4 and W14, we can affirm that the test structure results are aligned with conventional overlay measurements.

Figure 36: Comparison of test structure results (1.44 $\mu$ m pitch) and overlay measurements in X and Y direction

After comparison, we can claim that the test results of misalignment test structure with  $3.42\mu m$  and  $1.44\mu m$  pitch are aligned with conventional overlay measurements. The proposed test structure must replace the actual destructive methods to measure misalignment defect in process development phase. The accuracy of misalignment measurements, using the proposed test structure, depends on offset values. So, more patterns are needed for an accurate misalignment measurement but this increase the area of test pads. Therefore another alternative for test access is needed. In the next part, we need study the impact of this misalignment defect on resistance and capacitance parameters.

## IV. Characterization of HD 3D-IC interconnect using the proposed test structure

The proposed method allows to measure misalignment values, the accuracy depends on offset values. Using the measurement values, we can estimate the contact surface and finally calculate the resistance using equation (2). The test flow is shown in figure 37.

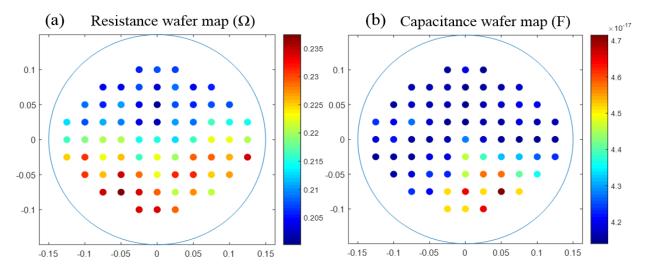

We study the impact of misalignment defect on R and C parameters for the wafers used in III example W14 with a pitch of  $1.44\mu m$  (because of the variation of misalignment values in the case of the run-out effect) using MATLAB tool. Figure 38.a and figure 38.b show respectively the resistance (of Cu-Cu pads and HBVs) and capacitance wafer map distribution (the run-out is the predominant effect).

Figure 37: Overall test misalignment flow

Figure 38: Resistance and capacitance values distribution (W14 with a pitch=1.44μm)

The maximum misalignment values in X and Y direction are equal to 180nm and 293nm respectively and the pad size (PS) is equal to 720nm. While the effective contact surface remains large, there is not a great variation in the resistance values; the minimum value is equal to  $202m\Omega$  and the maximum is equal to  $237m\Omega$ .

Concerning capacitance values, the distance between two adjacent Cu pads is large, so we do not have a big variation (min=0.042fF, max=0.047fF). On the contrary, the simulation of the electrical model of Cu-Cu pad (with a pitch of 1.44 $\mu$ m) shows that a 700nm misalignment value in X and Y direction increases significantly the resistance from 197 m $\Omega$  to 50 $\Omega$  and the capacitance from 0.02fF to 0.74fF.

#### V. Conclusion