# Hardware support for the security analysis of embedded softwares: applications on information flow control and malware analysis

Muhammad Abdul Wahab

#### ▶ To cite this version:

Muhammad Abdul Wahab. Hardware support for the security analysis of embedded softwares: applications on information flow control and malware analysis. Hardware Architecture [cs.AR]. Centrale-Supélec, 2018. English. NNT: 2018CSUP0003. tel-02634340

## HAL Id: tel-02634340 https://theses.hal.science/tel-02634340

Submitted on 27 May 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

#### **CENTRALESUPELEC**

COMUE UNIVERSITE BRETAGNE LOIRE

**ECOLE DOCTORALE N° 601** Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Electronique

#### Muhammad Abdul WAHAB

## Support matériel pour l'analyse de sécurité du comportement des applications

Application au contrôle de flux d'information et à l'analyse des logiciels malveillants

Thèse présentée et soutenue à Rennes, le 10 décembre 2018

Unité de recherche : IETR, UMR 6164

Thèse N°: 2018-08-TH

#### Rapporteurs avant soutenance:

Pascal Benoit Maître de Conférences Université de Montpellier 2

Jean-Luc Danger Directeur des études

Télécom ParisTech

#### **Composition du Jury:**

Laurence Pierre Professeur Université de Grenoble Présidente

Pascal Benoit Maître de Conférences

Université de Montpellier 2

Jean-Luc Danger Directeur des études

Télécom ParisTech

Guillaume Hiet Maître de Conférences

CentraleSupélec, campus de Rennes Pascal Cotret Ingénieur R&D

Directeur de thèse

Christophe Moy Professeur

Université de Rennes 1

Invité(s)

Guy Gogniat Professeur Université de Bretagne-Sud

| I would like to dedicate this thesis to my loving parents and all my family members |

|-------------------------------------------------------------------------------------|

|                                                                                     |

|                                                                                     |

|                                                                                     |

|                                                                                     |

|                                                                                     |

|                                                                                     |

|                                                                                     |

|                                                                                     |

#### Acknowledgments

In the name of Allah the most Merciful and Beneficient.

First and Foremost praise is to Allah, the Almighty, the greatest of all, on whom ultimately we depend on sustenance and guidance. I would like to thank Allah azza wa jal for giving me the opportunity, determination, and strength to do my research. His continuous grace and mercy was with me throughout my life and even more during the tenure of my research.

Prophet Muhammad, peace and blessings of Allah be upon him, said, "He who does not thank people, does not thank Allah" (Ahmad, Tirmidhi). I would like to express my sincere and deep gratitude to Dr.-Ing. Pascal Cotret for his continuous support, guidance, and encouragement. In addition to being an excellent supervisor, he is an extremely hardworking researcher. I tried my best to follow his example but I could not meet half of his dedication. I appreciate all his contributions of time, support, and ideas.

I would also like to express my gratitude to Prof. Guillaume Hiet, who helped me a lot throughout this work especially the last year. His methodology and way of guidance helped me carry on this work in the right direction during tough times. I also appreciate the support of Christophe MOY who played an important part throughout this thesis and a special thanks for his instructive reviews and guidance on this manuscript. I am extremely thankful to Prof. Guy Gogniat and Prof. Vianney Lapotre for their valuable guidance throughout this work. Their experience and feedback helped me a lot and I cannot thank them enough for their support.

I would like to thank my friend Mounir Nasr Allah for his help, support, and important feedback especially during our tea-break discussions. Our short talks were very valuable to me. I would like to thank my current and previous teammates Rami Othman, Vincent Gouldieff, Quentin Bodinier, Rémi Bonnefoi, Malek Naoues, Lilian Besson, Ali Cheaito, Hussein Chour, Majed Saad, Julio Cesar Manco Vasquez, Salah Eddine Kabbour, Xiguang Wu, Yifan Zhou, Abir Amri, Mouna Ben Mabrouk, Marwa Chafii, and all fellows in CentraleSupélec-Rennes for their help and kindness. A special thanks to Haifa Fares for her kind advice that was very helpful.

I would also like to extend my gratitude to the SCEE members: Amor Nafkha, Jacques Palicot, Carlos Bader, Yves Louet and all professors of CentraleSupélec, Rennes. I extend

my sincere thanks to Karine Bernard and Jeannine Hardy for their administrative support. I am very grateful to Professor Alberto Ferrante for his guidance during the mobility. I am very thankful to Olivier Deforges and Wassim Hamidouche from VAADER team to allow me to finish my manuscript in great conditions. I am also very thankful to the jury members of my thesis committee for reviewing this work.

Finally, I would like to thank my family for their unconditional support and sacrifices. A special thanks to my mother (Nusrat Parveen) and father (Muhammad Anwar) who have always encouraged me to engage in higher and better education. All my sisters played an important part in my education and my brother, my role model, inspired me with his dedication and hard work. I thank all my relatives and friends who contributed to my well-being and this work.

#### Résumé

La sécurité dans les systèmes embarqués devient un sujet de plus en plus important, notamment en raison de la multiplication des appareils portables capables de gérer des données sensibles (smartphones, tablettes, etc.). L'utilisation d'un support matériel pour implémenter des mécanismes de sécurité paraît incontournable afin de protéger efficacement ces systèmes contre les attaques logicielles, tout en minimisant l'impact sur le temps d'exécution des applications. Le contrôle de flux d'informations, Dynamic Information Flow Tracking (DIFT), permet de détecter différents types d'attaques logicielles tels que les dépassements de tampon ou les injections SQL. Pour suivre et contrôler les flux d'informations, les travaux existants modifient l'architecture interne du processeur ou utilisent des processeurs de type softcore, c'est-à-dire des processeurs synthétisés sur un FPGA, tels que les Leon3. De plus, la plupart des approches existantes ne sont pas portables sur des processeurs de type hardcore (câblés dans une puce). Dans cette thèse, une solution ciblant les processeurs hardcore ARM Cortex-A9 est proposée. Notre approche s'appuie sur des composants ARM CoreSight, qui permettent de tracer l'exécution des programmes exécutés par le processeur, afin de réaliser le contrôle de flux d'informations. Le co-processeur DIFT que nous proposons est réalisé dans la partie FPGA Artix-7 du système sur puce (Soc) Zynq, afin de bénéficier de la présence sur la même puce de cœurs ARM Cortex-A9 dans la partie PS (Processing System) et d'une partie reconfigurable FPGA dans la partie PL (Programmable Logic). Il est montré que l'utilisation des composants ARM CoreSight n'ajoute pas de surcoût en terme de temps d'exécution et permet une amélioration du temps de communication entre le processeur ARM et le coprocesseur DIFT. De plus, les flux d'informations induits par les appels système ne sont pas pris en compte dans les travaux existants, ce qui les rend vulnérables aux attaques provenant de fichiers tels que la fuite d'information contenue dans un fichier. La solution proposée dans ces travaux utilise RFBlare, un noyau Linux modifié, qui se charge du stockage et de la récupération des étiquettes associées aux fichiers afin de protéger contre ces attaques.

#### Abstract

Embedded security is more and more crucial with the huge increase in the number of mobile equipment dealing with sensible data (smartphones, tablets, etc.). Runtime efficient protection from software attacks requires architectural support. DIFT (Dynamic Information Flow Tracking) is a technique that allows detecting software attacks such as buffer overflows or SQL injection by monitoring information flows. In order to track information flows, existing works modify internal CPU architecture or target softcore CPUs. Most of the existing approaches are not portable to hardcore CPUs. In this thesis, a solution that targets ARM Cortex-A9 hardcore CPUs and takes advantage of ARM CoreSight components, that allow tracing the CPU, is proposed in order to efficiently track information flows. DIFT co-processor is implemented in Artix-7 FPGA included in Zyng SoC in this work, taking advantage of both PS (Processing System containing ARM Cortex-A9 cores) and PL (Programmable Logic providing an FPGA) on the same chip. It is shown that ARM CoreSight components do not add execution time overhead which results in an improvement of communication time overhead between the ARM CPU and the DIFT coprocessor. In addition, information flows induced by system calls are not considered in existing works making them unsafe to attacks originating from files such as data leaks. The solution proposed in this thesis takes advantage of RFBlare, a modified Linux kernel, that provides support to store and retrieve tags associated to files in order to protect against these attacks.

## Résumé étendu

Depuis plus d'une décennie, le nombre de vulnérabilités logicielles ne cesse d'augmenter. De nombreuses attaques logicielles exploitent les mécanismes architecturaux de bas niveau. Dans le contexte de la sécurité informatique, le contrôle de flux d'informations (Dynamic Information Flow Tracking en anglais) est un mécanisme de sécurité qui permet de lutter efficacement contre un large spectre d'attaques logicielles, par exemple celles exploitant les vulnérabilités de type buffer overflow, les cross-site scripting, les injections SQL ou les fuites de données en générale. Le contrôle de flux d'informations consiste à rajouter une étiquette (tag ou taint en anglais) sur chaque conteneur d'information. Le conteneur d'information varie suivant le niveau auquel on effectue le contrôle: par exemple, il peut s'agir d'un registre ou d'une adresse mémoire si on s'intéresse au niveau architectural, d'une variable si on s'intéresse au niveau d'un application ou d'un fichier au niveau d'un système d'exploitation. A chaque fois qu'une instruction est exécutée par le processeur, l'étiquette est également propagée entre les conteneurs d'information. Une politique de sécurité permet de préciser à quel moment l'étiquette doit être vérifiée afin de détecter une attaque. Par exemple, si on considère une attaque qui consiste à lire une zone/adresse mémoire non initialisée, la politique de sécurité consiste à détecter qu'il y a une écriture sur une adresse avant toute lecture de la même adresse. La détection de l'écriture peut se faire en vérifiant la valeur de l'étiquette. On peut considérer que lors de chaque écriture d'une adresse mémoire, son étiquette est mise à 1. Lorsque l'adresse mémoire est adressée pour une lecture, son étiquette est vérifiée pour savoir si elle a été initialisée (étiquette 1) ou non (étiquette 0).

Le contrôle de flux d'information peut être réalisé de plusieurs façons : de manière logicielle, matérielle ou en utilisant une solution hybride logicielle/matérielle. L'approche logicielle est la plus flexible, c'est-à-dire qu'elle permet de protéger contre de multiples attaques, mais en contrepartie elle ralentit l'application de 3 à 37 fois [1]. L'approche matérielle permet de réduire l'impact sur le temps d'exécution de l'application mais le spectre des attaques détectées est plus restreint et surtout il est figé dans le temps. L'approche hybride ([2, 3, 4, 5]) permet d'obtenir le meilleur compromis entre performance du système et flexibilité. Nos travaux se basent sur cette approche hybride et permettent de répondre aux questions suivantes qui sont non-traitées dans les travaux existants :

- Comment contrôler les flux d'informations sur un processeur ARM *hardcore* (c'est-à-dire un processeur dont l'architecture ne peut être modifiée)

- Comment s'assurer de la sécurité du coprocesseur ?

- Comment mettre en œuvre plusieurs politiques de sécurité de différentes granularités ?

- Comment protéger une application contenant plusieurs fils d'exécution (threads) ?

Pour pouvoir contrôler les flux d'informations, il faut déterminer tous les flux qui sont effectués lors de chaque opération exécutée par le processeur: chargement, mémorisation, affectation, opérations arithmétiques, etc. Dans les travaux existants [1, 2, 3, 4, 5], les processeurs qui exécutent l'application sont des processeurs de type softcore (c'est-à-dire des processeurs réalisés dans un FPGA) qui permettent de récupérer l'information nécessaire pour suivre et contrôler les flux d'information en utilisant des signaux existants. Sur un processeur de type hardcore (câblé dans une puce donc non modifiable), il n'est pas possible d'utiliser cette approche. Dans nos travaux, nous proposons une approche utilisant à la fois le mécanisme de trace offert par les composants ARM CoreSight, une analyse statique, l'instrumentation du code de l'application et RFBlare [6] (un noyau Linux modifié) afin de récupérer l'information et de la transférer à un co-processeur implémenté sur la partie reconfigurable d'un SoC (système sur puce) Zynq. Les composants CoreSight du cœur ARM sont utilisés pour déterminer le chemin d'exécution pris par l'application. En effet, à l'aide des traces générées par ces composants, il est possible de déterminer quel bloc de base le processeur est en train d'exécuter. En revanche, ces traces ne permettent pas d'inférer directement les flux d'informations générés à l'intérieur d'un bloc de base. C'est pourquoi une analyse statique est réalisée en complément lors de la compilation de l'application, pour déterminer tous les flux d'information à l'intérieur de chaque bloc de base. Le résultat de cette analyse est stocké dans le fichier exécutable de l'application et fourni au co-processeur lors du chargement de l'application. Toutefois, l'analyse statique ne peut déterminer toutes les adresses mémoires des instructions mémoires (par exemple, ldr et str). Aussi, lors de la compilation, il est également nécessaire d'instrumenter le code afin de récupérer les adresses mémoires des instructions ldr et str à l'exécution de l'application. RFBlare est quant à lui nécessaire pour pouvoir récupérer et mettre à jour les étiquettes associées à des fichiers. Il a été vu d'une part qu'en utilisant l'approche proposée, qu'il est possible de déterminer tous les flux d'information. D'autre part, l'approche proposé dans ces travaux est meilleure en termes du temps d'exécution que l'approche proposée dans l'état de l'art [4].

Le composant CoreSight PTM, disponible sur le SoC Zynq, génère la trace (autrement dit, des paquets qui permettent d'avoir des informations sur le code exécuté par le processeur). Cette trace peut être envoyée vers la partie reconfigurable du SoC (système sur une puce) en utilisant l'interface EMIO (Extended Multiplexed Input/Output en anglais). Le support pour les composants CoreSight n'existait pas pour le Zynq SoC dans le noyau Linux. Nous avons donc modifié le device tree pour pouvoir utiliser les pilotes associés à ces composants.

Par ailleurs, le pilote Linux existant ne mettait pas en œuvre toutes les caractéristiques offertes par ces composants: par exemple, il n'était pas possible de récupérer l'adresse des branchements directs. Nous avons donc également modifié le pilote des composants CoreSight pour rajouter ce support. Nous avons soumis un patch au mainteneur. Ce patch a été accepté et il est maintenant intégré dans le noyau Linux. Le pilote pour le TPIU (Trace Port Input/Output Unit) n'était pas complet et nous l'avons également modifié pour pouvoir utiliser ce composant afin de récupérer la trace sur la partie reconfigurable (FPGA) du SoC.

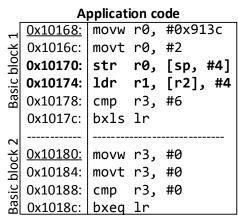

Pour effectuer l'analyse statique, un algorithme qui permet d'analyser chaque bloc de base d'un graphe de flot de contrôle a été proposé. La sémantique de chaque instruction exécutée par le processeur est analysée pour déterminer les flux d'informations générés par cette instruction. Par exemple, lorsque le processeur exécute une instruction add r0, r1, r2, il y a un flux d'information depuis les registres r1 et r2 vers le registre r0. L'analyse statique permet de récupérer cette information pour l'ensemble des instructions d'un bloc de base. Il faut également arriver à déterminer les adresses mémoires utilisées dans le programme. Or, cela n'est pas possible pour certaines instructions notamment pour les instructions mémoire (ldr, str, ...) qui sont relatives aux registres. Pour ces instructions, il faut instrumenter le code c'est-à-dire rajouter des instructions dans le code pour récupérer l'information sur l'adresse mémoire. L'analyse statique est réalisée en utilisant le désassembleur Capstone [7] qui fournit une API (Application Programming Interface) pour différentes architectures. Le chapitre 3 détaille l'utilisation des composants CoreSight, l'analyse statique et l'instrumentation pour pouvoir récupérer l'information nécessaire pour le contrôle de flux d'informations.

Un premier prototype a été réalisé et a permis d'évaluer la faisabilité de l'approche proposée. Le prototype permet de montrer comment le contrôle de flux d'information peut être réalisé pour protéger le système contre la fuite de données. Dans un premier temps, un processeur générique est utilisé pour effectuer les opérations nécessaires pour le contrôle de flux d'information. Le chapitre 4 détaille l'architecture réalisée.

Dans un deuxième temps, un coprocesseur dédié a été développé afin d'accélérer le contrôle de flux d'information. Les coprocesseurs dédiés de l'état de l'art considèrent que l'application n'exécute qu'un seul thread. Or, les applications utilisent de plus en plus toutes les ressources disponibles sur un processeur afin d'accélérer l'exécution. C'est pourquoi, il est important de s'assurer que les applications qui utilisent plusieurs threads soient également protégées des attaques logicielles. L'approche proposée a été améliorée pour pouvoir récupérer les informations nécessaires pour suivre les flux d'informations d'une application contenant plusieurs threads. Une configuration différente des composants CoreSight a été utilisée pour obtenir le context ID d'une application dans les traces. Le context ID inclut le ASID (Application Specific ID) et le TID (Thread ID). A l'aide de ces informations, le coprocesseur peut identifier le thread actuellement exécuté et donc réaliser le contrôle de flux d'information pour chaque tread. Par ailleurs, l'architecture du coprocesseur dédié que nous avons proposé

permet de découpler les deux opérations qu'il doit effectuer : reconstruire le chemin d'exécution de l'application et suivre les flux d'informations à l'aide des instructions générées par l'analyse statique. Le chapitre 5 détaille l'architecture du coprocesseur et comment l'utiliser pour protéger plusieurs threads ou suivre plusieurs politiques de sécurité en parallèle.

Par ailleurs, une mobilité a été effectuée entre décembre 2017 et février 2018 au sein du laboratoire ALARI à l'Université de la Suisse Italienne (à Lugano). Au cours de cette mobilité, la détection dynamique de logiciel malveillants (malware) pour les appareils portables à l'aide des accélérateurs matérielles a été étudiée. Avec l'augmentation du volume d'appareils intelligents, l'intérêt d'attaquer ces appareils est fortement en croissance, faisant de leur sécurité un défis majeur. Le vecteur d'attaque couramment utilisé pour détourner ces appareils de leur usage est l'utilisation d'un logiciel malveillant. Les deux moyens de protection contre ces logiciels malveillants sont l'analyse statique et l'analyse dynamique. Alors que les analyses statiques couramment utilisées s'appuient sur des signatures et ne peuvent détecter que les attaques connues, l'analyse dynamique nécessite des ressources de calcul qui ne conviennent pas aux appareils portables fonctionnant sur batterie. Une solution qui utilise les FPGAs embarqués dans les SoCs a été proposée afin de réaliser un calcul économe en énergie pour l'analyse dynamique, ce qui permet de l'adopter pour les appareils portables. La solution proposée peut également accélérer l'analyse dynamique grâce aux accélérateurs matériels générés à l'aide d'un outil de synthèse de haut niveau. Plus précisément, trois algorithmes de classification (la régression logistique, la classification naïve bayésienne et les machines à vecteur de support) ont été réalisés en matériel à l'aide de Vivado HLS. L'efficacité en termes du temps d'exécution et de la consommation énergétique ont été évalués. Le chapitre 6 détaille ces travaux.

Le chapitre 7 résume les travaux présentés dans ce manuscrit et décrit les perspectives futures. Il a notamment été montré dans ce manuscrit comment le contrôle de flux d'informations peut être réalisé sur une architecture ARM en utilisant les composants CoreSight, l'analyse statique, l'instrumentation et RFBlare (un noyau Linux modifié). L'architecture réalisée permet de protéger des applications contenant plusieurs threads et permet également de mettre en œuvre plusieurs politiques de sécurité en utilisant l'architecture modulaire du coprocesseur proposé. Par ailleurs, une version économe en consommation énergétique a été développée pour trois algorithmes de classification afin de détecter des applications malveillantes et d'augmenter la durée d'utilisation de la batterie des smartphones. En ce qui concerne le contrôle de flux d'information, les perspectives futures consistent en l'utilisation de l'architecture afin de détecter différentes attaques logicielles (tels que XSS (cross-Site Scripting) et attaque par traversée de chemin) et l'utilisation de l'approche proposée sur des processeurs Intel qui possèdent également un composant de debug similaire au composant ARM CoreSight PTM notamment Intel PT (Processor Trace).

# Contents

| $\mathbf{A}$ | bstra | ıct     |                                                                                 | v    |

|--------------|-------|---------|---------------------------------------------------------------------------------|------|

| $\mathbf{R}$ | ésum  | ié éten | ndu                                                                             | vii  |

| N            | omer  | ıclatur | re                                                                              | xvii |

| Li           | st of | Figur   | es                                                                              | xxi  |

| Li           | st of | Table   | s                                                                               | xxv  |

| Li           | st of | Listin  | $_{ m logs}$                                                                    | xxvi |

| 1            | Inti  | oduct   | ion                                                                             | 1    |

|              | 1.1   | Backg   | ground and Motivations                                                          | . 1  |

|              | 1.2   | Securi  | ity policies                                                                    | . 4  |

|              | 1.3   | Non-e   | exhaustive list of software attacks                                             | . 5  |

|              |       | 1.3.1   | Buffer Overflow                                                                 | . 5  |

|              |       | 1.3.2   | DIFT security policy                                                            | . 6  |

|              | 1.4   | Open    | Research questions                                                              | . 7  |

|              |       | 1.4.1   | Question 1: How to recover required information for DIFT on hardcore CPUs?      | . 7  |

|              |       | 1.4.2   | Question 2: DIFT on ARM architecture (hardcore CPU)                             | . 8  |

|              |       | 1.4.3   | Question 3: How to implement multiple security policies of different tag size ? | . 8  |

|              |       | 1.4.4   | Question 4: Multi-threaded system / Multicore system                            | . 8  |

|              | 1.5   | Manu    | script organization and contributions                                           | . 9  |

|              |       | 1.5.1   | Manuscript organization                                                         | . 9  |

|              |       | 1.5.2   | Manuscript contributions                                                        | . 9  |

|              | 1.6   | Cumm    | NO. WY                                                                          | 10   |

| 2 | Rel | ated works                                              | 11 |

|---|-----|---------------------------------------------------------|----|

|   | 2.1 | Introduction                                            | 11 |

|   | 2.2 | Different types of IFT                                  | 12 |

|   |     | 2.2.1 Static IFT (SIFT)                                 | 12 |

|   |     | 2.2.2 Dynamic IFT (DIFT)                                | 12 |

|   | 2.3 | Different levels of IFT                                 | 12 |

|   |     | 2.3.1 Application level IFT                             | 14 |

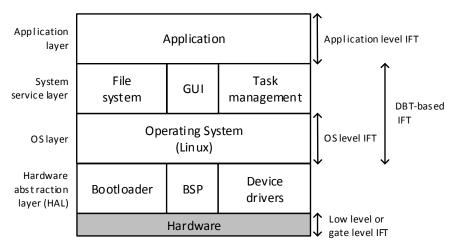

|   |     | 2.3.2 OS level IFT                                      | 16 |

|   |     | 2.3.3 Low level IFT                                     | 17 |

|   |     | 2.3.4 DBT-based IFT                                     | 17 |

|   |     | 2.3.5 Gate level IFT                                    | 17 |

|   | 2.4 | Hardware-assisted                                       | 17 |

|   |     | 2.4.1 New CPU architecture                              | 18 |

|   |     | 2.4.2 In-core                                           | 18 |

|   |     | 2.4.3 Off-loading                                       | 18 |

|   |     | 2.4.4 Off-core                                          | 20 |

|   | 2.5 | Proposed solution for DIFT on hardcore CPUs             | 23 |

|   |     | 2.5.1 Specifications                                    | 23 |

|   |     | 2.5.2 Comparison                                        | 23 |

|   | 2.6 | Summary                                                 | 25 |

| 3 | Rec | covering information required for DIFT on hardcore CPUs | 27 |

| Ū | 3.1 | Introduction                                            | 27 |

|   | 3.2 | Context of the proposed approach                        | 28 |

|   | 3.3 | CoreSight components                                    | 31 |

|   | 3.3 | 3.3.1 Trace Source                                      | 31 |

|   |     | 3.3.2 Trace Link                                        | 37 |

|   |     | 3.3.3 Trace Sink                                        | 39 |

|   | 3.4 | Proposed approach                                       | 42 |

|   | 0.1 | 3.4.1 CS components                                     | 42 |

|   |     | 3.4.2 Static analysis                                   | 47 |

|   |     | 3.4.3 Instrumentation IP                                | 52 |

|   |     | 3.4.4 OS-related information                            | 54 |

|   | 3.5 | Evaluation of the proposed approach                     | 57 |

|   | J.J |                                                         | ٠. |

|                  |                     | 5.4.2                                       | ISA of the TMC unit                                 | 95                                     |

|------------------|---------------------|---------------------------------------------|-----------------------------------------------------|----------------------------------------|

|                  |                     | 5.4.3                                       | Microarchitecture of the DIFT coprocessor           | 98                                     |

|                  |                     | 5.4.4                                       | Software running on the DIFT coprocessor            | 103                                    |

|                  | 5.5                 | Evalua                                      | ation of the proposed coprocessor                   | 105                                    |

|                  |                     | 5.5.1                                       | Case studies                                        | 106                                    |

|                  |                     | 5.5.2                                       | Performance overhead                                | 109                                    |

|                  |                     | 5.5.3                                       | Comparison with previous works                      | 113                                    |

|                  | 5.6                 | Summ                                        | ary                                                 | 114                                    |

| 6                | Har                 | dware                                       | accelerators for malware detection                  | 117                                    |

|                  | 6.1                 | Introd                                      | uction                                              | 117                                    |

|                  | 6.2                 | Propo                                       | sed hardware accelerators                           | 118                                    |

|                  |                     | 6.2.1                                       | Design methodology                                  | 118                                    |

|                  |                     | 6.2.2                                       | Power and performance optimizations                 | 119                                    |

|                  | 6.3                 | Imple                                       | mentation details and evaluation                    | 123                                    |

|                  |                     | 6.3.1                                       | Evaluation method                                   | 123                                    |

|                  |                     | 6.3.2                                       | Results                                             | 124                                    |

|                  | 6.4                 | Summ                                        | ary                                                 | 128                                    |

| 7                | Con                 | clusio                                      | ns and Perspectives                                 | 129                                    |

|                  | 7.1                 | Conclu                                      | usions                                              | 129                                    |

|                  | 7.2                 | Perspe                                      | ectives for future works                            | 130                                    |

| $\mathbf{A}_{]}$ | ppen                | dix A                                       | ZedBoard development board                          | 133                                    |

|                  |                     |                                             |                                                     |                                        |

| $\mathbf{A}$     | ppen                | dix B                                       | Development and Evaluation method                   | 135                                    |

| $\mathbf{A}$     | p <b>pen</b><br>B.1 |                                             | Development and Evaluation method  vare development |                                        |

| $\mathbf{A}_{]}$ | -                   |                                             | -                                                   | 135                                    |

| $\mathbf{A}_{]}$ | -                   | Hardw                                       | vare development                                    | 135<br>136                             |

| $\mathbf{A}_{1}$ | -                   | Hardw<br>B.1.1<br>B.1.2                     | vare development                                    | 135<br>136<br>136                      |

| $\mathbf{A}_{]}$ | B.1                 | Hardw<br>B.1.1<br>B.1.2<br>Softwa           | vare development                                    | 135<br>136<br>136<br>136               |

| $\mathbf{A}_{]}$ | B.1<br>B.2          | Hardw<br>B.1.1<br>B.1.2<br>Softwa           | vare development                                    | 135<br>136<br>136<br>136<br>137        |

| $\mathbf{A}_{]}$ | B.1<br>B.2          | Hardw<br>B.1.1<br>B.1.2<br>Softwa<br>Evalua | Vare development                                    | 135<br>136<br>136<br>136<br>137<br>137 |

|              | Contents                                     | xv  |

|--------------|----------------------------------------------|-----|

| Appendix C   | The DIFT coprocessor instruction set details | 139 |

| C.1 DIFT     | coprocessor                                  | 139 |

| C.1.1        | Dispatcher instruction set details           | 139 |

| C.1.2        | TMC                                          | 139 |

| Appendix D   | Publications                                 | 147 |

| Bibliography |                                              | 149 |

# Nomenclature

#### Acronymes et Abréviations

ABI Application Binary Interface

ALU Arithmetic and Logical Unit

ASIC Application Specific Integrated Circuit

ASLR Address Space Layout Randomization

AXI Advanced eXtensible Interface

BSP Board Support Package

CFG Control Flow Graph

CLB Configurable Logic Block

CPU Central Processing Unit

CS CoreSight

CTI Cross Trigger Interface

CTM Cross Trigger Matrix

DAP Debug Access Port

DEP Data Execution Prevention

DIFC Dynamic Information Flow Control

DIFT Dynamic Information Flow Tracking

DTB Device Tree Blob

DTS Device Tree Script

ECT Embedded Cross Trigger

ELF Executable and Linkable Format

EMIO Extended Multiplexed Input Output

ETB Embedded Trace Buffer

#### xviii | Nomenclature

ETM Event Trace Macrocell

FF Flip Flop

FPGA Field Programmable Gate Array

FPU Floating Point Unit

FSM Finite State Machine

FTM Fabric Trace Macrocell

HDL Hardware Description Language

HLS High Level Synthesis

IP Intellectual Property

ISA Instruction Set Architecture

ITM Instruction Trace Macrocell

LLVM Low-Level Virtual Machine

LR Logistic Regression

LUT LookUp Table

MIO Multiplexed Input Output

MMU Memory Management Unit

NB Naive Bayes

OCM On-Chip Memory

OS Operating System

PFT Program Flow Trace

PL Programmable Logic

PS Processing System

PTE Page Table Entry

PTM Program Trace Macrocell

ROP Return-Oriented Programming

SDK Software Development Kit

SoC System on Chip

SVM Support Vector Machine

syscall System Call

TCR Tag Check Register

TMC Tag Management Core

TMMU Tag Memory Management Unit

TPIU Trace Port Interface unit

TPR Tag Propagation Register

VHDL Very High Speed Integrated Circuit Hardware Description Language

# List of Figures

| 1.1  | Initial state of the system before the program starts execution | 6  |

|------|-----------------------------------------------------------------|----|

| 1.2  | Final state of the system after the execution of program code   | 7  |

| 2.1  | A simplified sample Control Flow Graph                          | 13 |

| 2.2  | Software architecture of an embedded system                     | 13 |

| 2.3  | Blare approach                                                  | 16 |

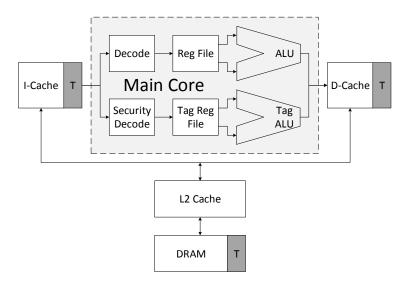

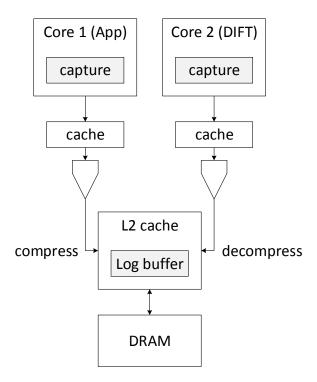

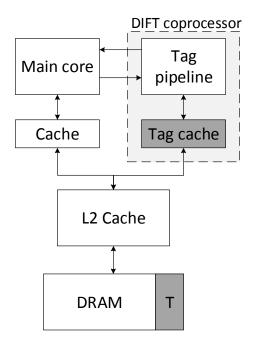

| 2.4  | In-core DIFT (adapted from [2])                                 | 19 |

| 2.5  | Off-loading DIFT: Log-based approach (adapted from [2])         | 19 |

| 2.6  | Off-core DIFT (adapted from [2])                                | 20 |

| 3.1  | Simplified CFG of the C code of Listing 3.1                     | 30 |

|      | •                                                               |    |

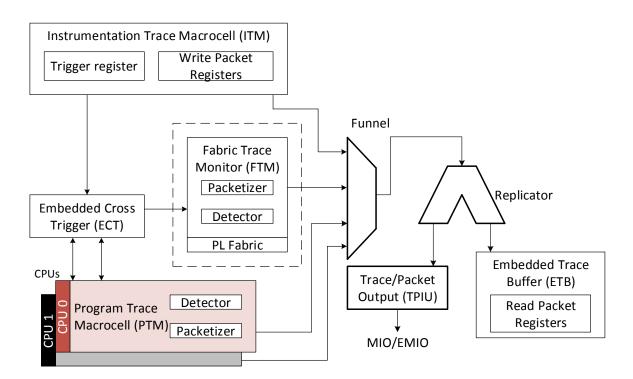

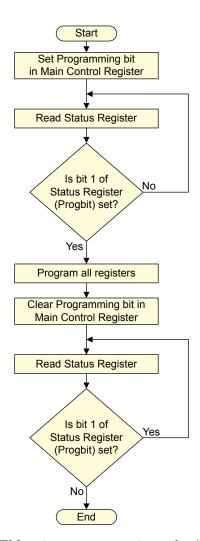

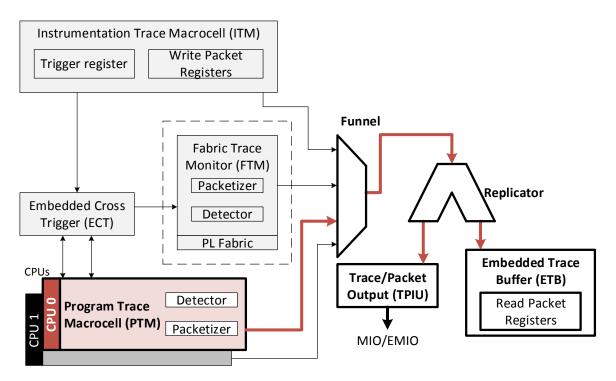

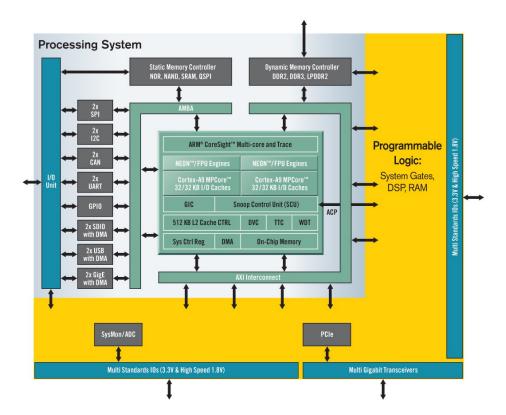

| 3.2  | CS components in Xilinx Zynq [55]                               | 32 |

| 3.3  | PTM registers programming order (taken from [56])               | 36 |

| 3.4  | CS components with trace trajectory shown by red bold lines     | 38 |

| 3.5  | CS Funnel (Link class component)                                | 38 |

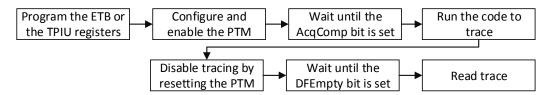

| 3.6  | Program flow for programming CS components and retrieving trace | 39 |

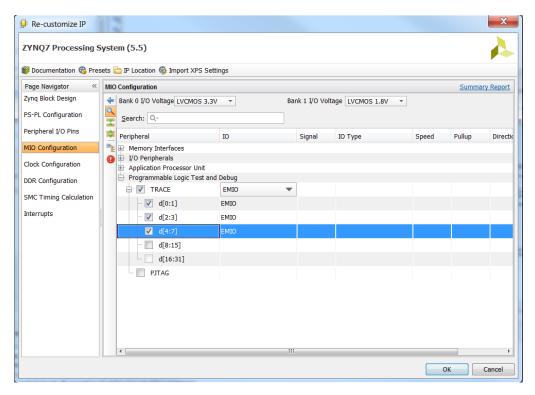

| 3.7  | TPIU trace connected to EMIO using Xilinx Vivado                | 40 |

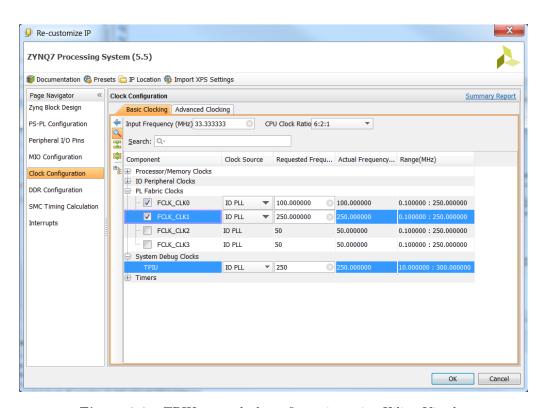

| 3.8  | TPIU trace clock configuration using Xilinx Vivado              | 40 |

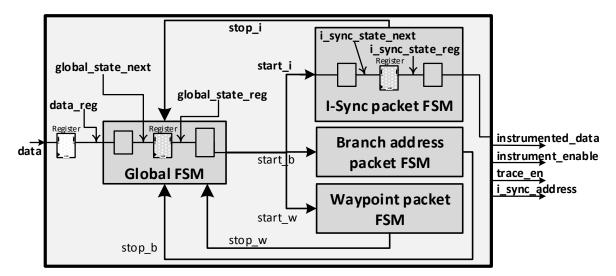

| 3.9  | Overall architecture of PFT Decoder                             | 43 |

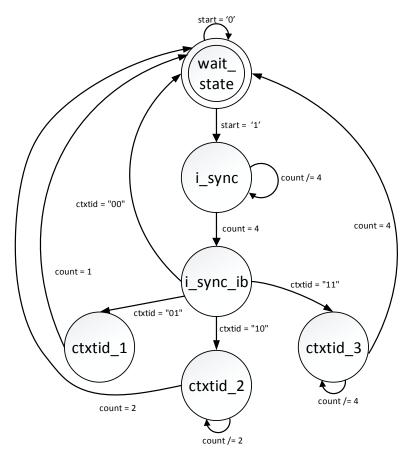

| 3.10 | State machine diagram for I-sync packet                         | 44 |

| 3.11 | Timing diagram of global FSM and I-Sync FSM of PFT decoder      | 45 |

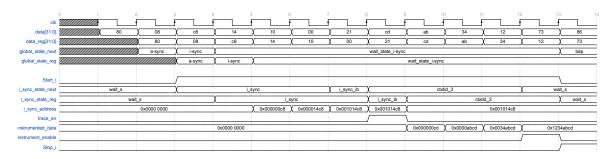

| 3.12 | Vivado design to recover trace on the PL                        | 46 |

| 3.13 | Vivado design to decode trace on the PL                         | 46 |

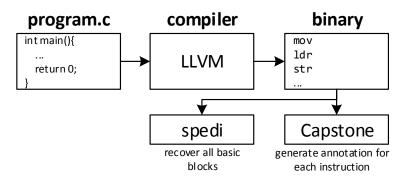

| 3.14 | Overall schematic of static analysis using the Capstone disassembly engine [7].                                                     | 48  |

|------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.15 | Simplified schematic of the instrumentation IP                                                                                      | 53  |

| 3.16 | Simplified schematic of the optimized instrumentation IP                                                                            | 54  |

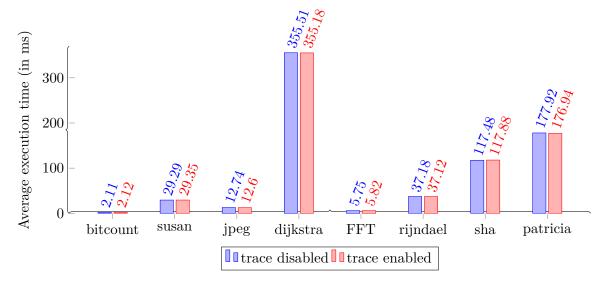

| 3.17 | CoreSight components time overhead for MiBench benchmark                                                                            | 58  |

| 3.18 | Instrumentation overhead                                                                                                            | 59  |

| 3.19 | Hardware design to evaluate power overhead of the PFT decoder                                                                       | 60  |

| 3.20 | Hardware design to evaluate power overhead of communication buffers                                                                 | 61  |

| 4.1  | Threat model                                                                                                                        | 64  |

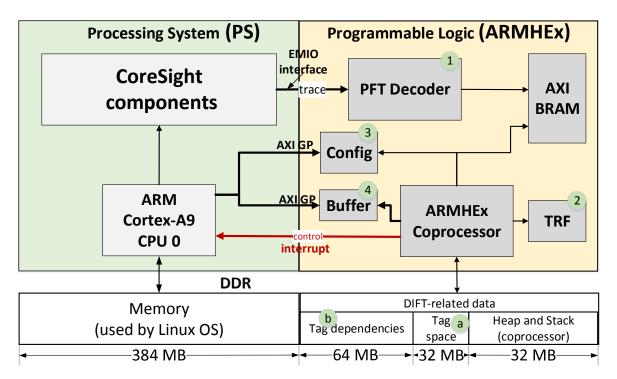

| 4.2  | Internal architecture of an ARMHEx-based system                                                                                     | 67  |

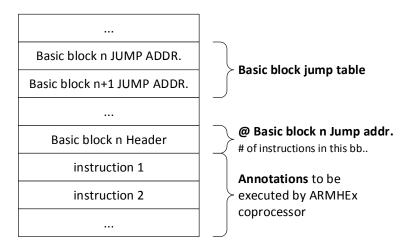

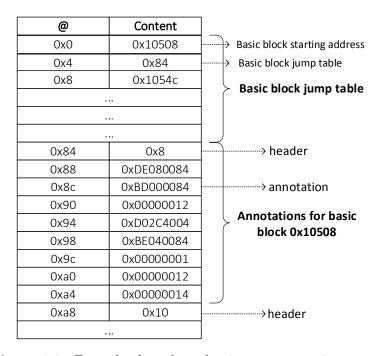

| 4.3  | Tag dependencies structure layout                                                                                                   | 68  |

| 4.4  | Example of tag dependencies memory section content                                                                                  | 68  |

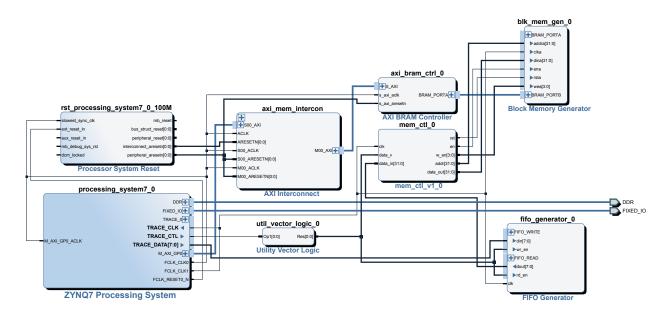

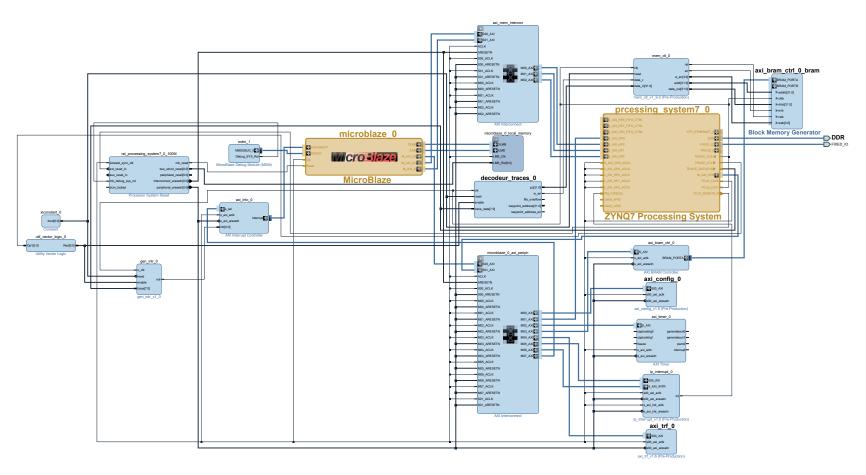

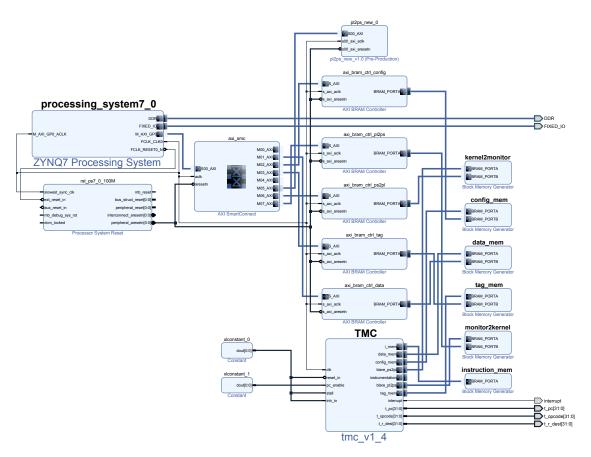

| 4.5  | ARMHEx Vivado design                                                                                                                | 69  |

| 4.6  | TrustZone hardware protected isolation                                                                                              | 74  |

| 4.7  | TrustZone protection on ARMHEx                                                                                                      | 75  |

| 4.8  | DDR memory protection using ARM TrustZone                                                                                           | 81  |

| 5.1  | DIFT coprocessor design requirements                                                                                                | 86  |

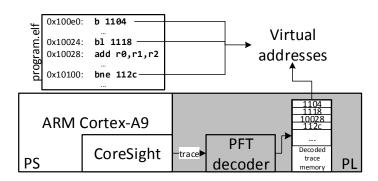

| 5.2  | Virtual addresses in the decoded trace                                                                                              | 88  |

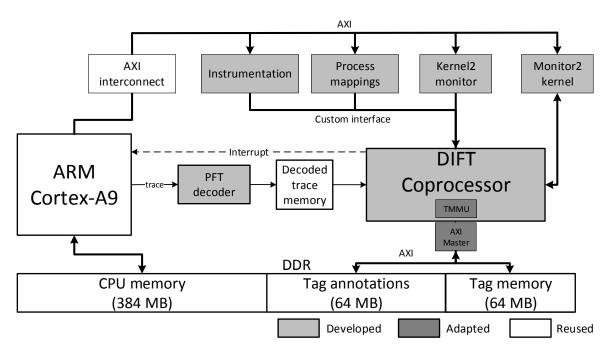

| 5.3  | Global architecture with the DIFT coprocessor                                                                                       | 89  |

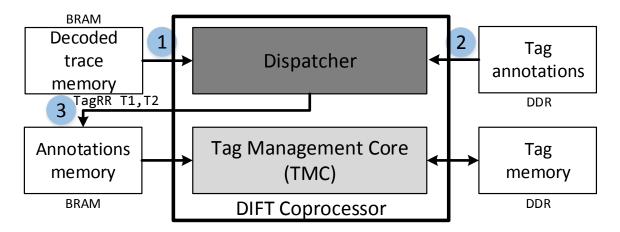

| 5.4  | [Architecture of the DIFT coprocessor.] Architecture of the DIFT coprocessor in the black box and its connetions with memory blocks | 90  |

| 5.5  | Binary instrumentation using modified LLVM                                                                                          | 91  |

| 5.6  | Microarchitecture of the DIFT coprocessor with 5 pipeline stages                                                                    | 98  |

| 5.7  | Compound annotation (TagITR). example on the TMC core                                                                               | 99  |

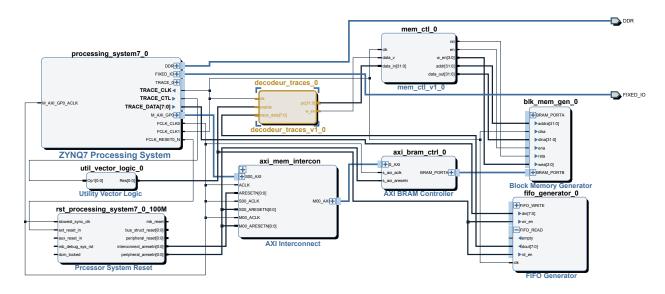

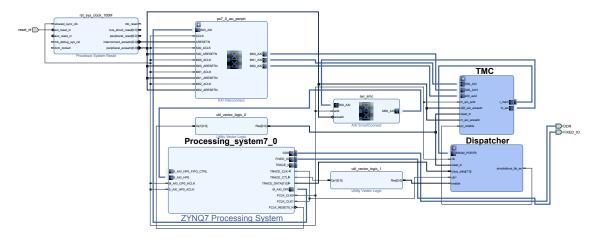

| 5.8  | Dispatcher design with Vivado tools on Zynq SoC                                                                                     | 101 |

| 5.9  | TMC design with Vivado tools on Zynq SoC                                                                                            | 102 |

| 5.10 | System design with the DIFT coprocessor                                                                                             | 102 |

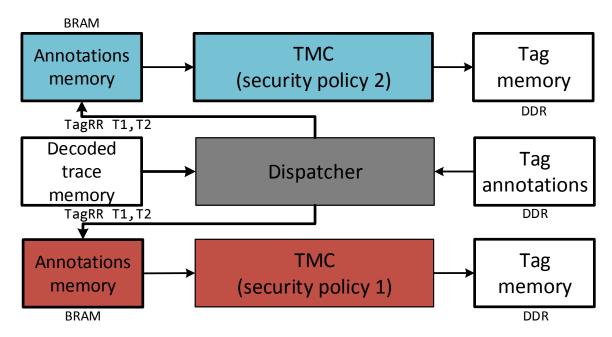

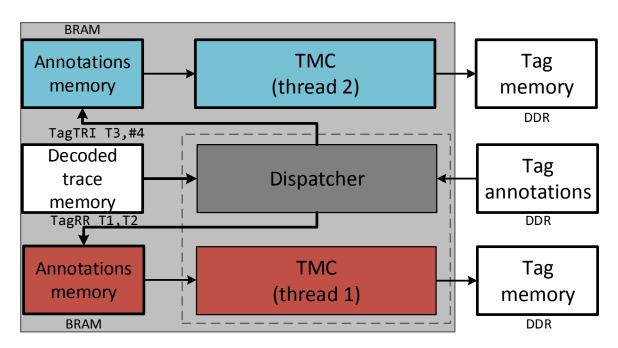

| 5.11 | DIFT coprocessor for multiple security policies                                                                                     | 107 |

| 5.12 | DIFT coprocessor for multiple threads                                                                                               | 108 |

| 5.13 | Decoded trace for multiple threads                                                 | 108 |

|------|------------------------------------------------------------------------------------|-----|

| 5.14 | Runtime overhead of instrumentation with custom benchmark                          | 110 |

| 5.15 | Memory footprint of custom benchmark                                               | 111 |

| 6.1  | Proposed detection system (taken from [16])                                        | 118 |

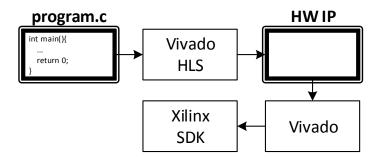

| 6.2  | Methodology used in order to develop hardware version of classification algorithms | 119 |

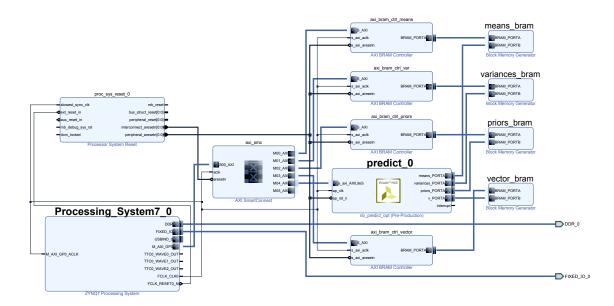

| 6.3  | Vivado implementation of the NB algorithm                                          | 123 |

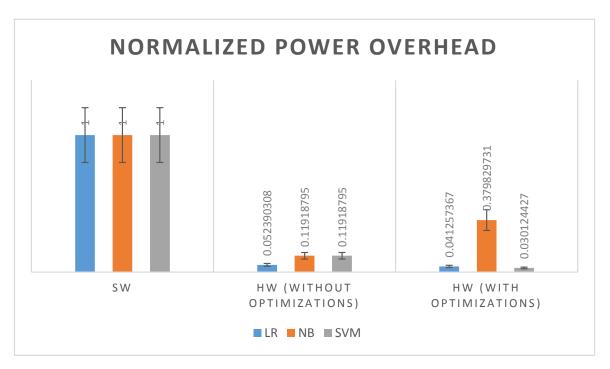

| 6.4  | Power overhead of the implemented algorithms                                       | 124 |

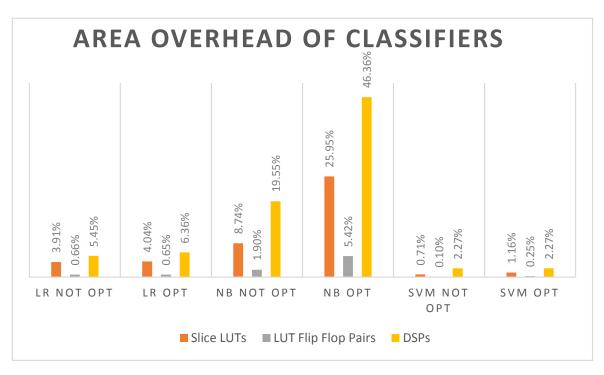

| 6.5  | Area overhead of the implemented algorithms                                        | 125 |

| 6.6  | Runtime overhead of LR algorithm                                                   | 126 |

| 6.7  | Runtime overhead of NB algorithm                                                   | 127 |

| 6.8  | Runtime overhead of SVM algorithm                                                  | 128 |

| A.1  | Zedboard                                                                           | 133 |

| A.2  | Zynq SoC                                                                           | 134 |

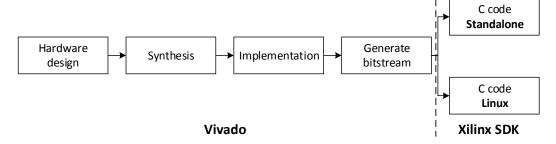

| R 1  | Davidopment design flow with Viling tools                                          | 195 |

# List of Tables

| 2.1  | Features comparison with related works                         | 24 |

|------|----------------------------------------------------------------|----|

| 2.2  | Features comparison with related works                         | 24 |

| 3.1  | Information required for DIFT in existing works                | 28 |

| 3.2  | Example code and corresponding trace                           | 32 |

| 3.3  | PTM registers, configuration values and purpose                | 36 |

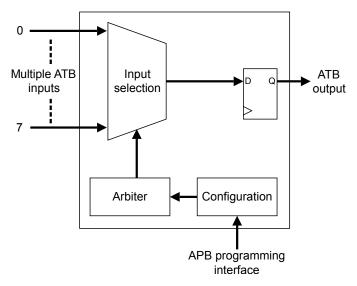

| 3.4  | PTM Configuration registers                                    | 37 |

| 3.5  | Funnel registers, configuration values and purpose             | 37 |

| 3.6  | ETB registers, configuration values and purpose                | 39 |

| 3.7  | PFT packet formats                                             | 43 |

| 3.8  | Example annotations                                            | 47 |

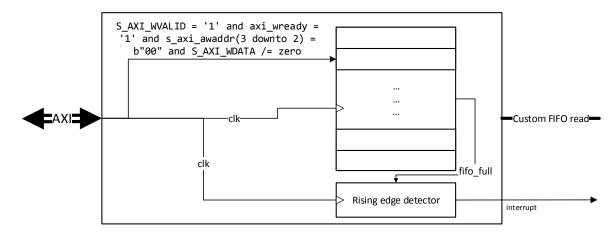

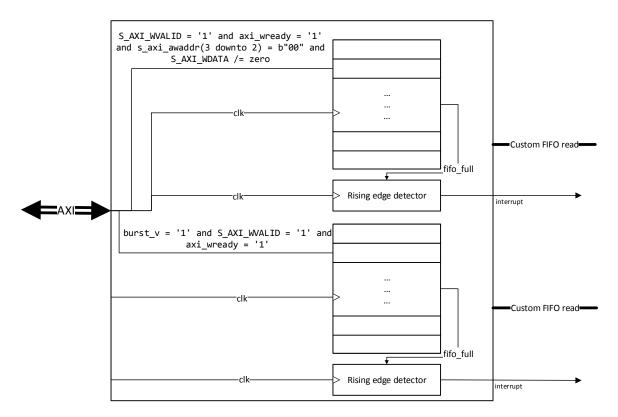

| 3.9  | Registers for kblare FIFO IPs                                  | 55 |

| 3.10 | Area results of developed IPs on Xilinx Zynq Z-7020            | 59 |

| 3.11 | Power results of PFT Decoder on Xilinx Zynq Z-7020             | 60 |

| 3.12 | Power results of communication buffers on Xilinx Zynq Z-7020   | 61 |

| 4.1  | Threat model summary                                           | 65 |

| 4.2  | DIFT memory section containing annotations for the DLP example | 79 |

| 4.3  | Jump table contained in the DIFT memory section                | 79 |

| 4.4  | Annotations contained in the DIFT memory section               | 79 |

| 4.5  | Area results of ARMHEx on Xilinx Zynq Z-7020                   | 80 |

| 4.6  | Power consumption results of ARMHEx on Xilinx Zynq Z-7020      | 81 |

| 4.7  | Performance comparison with related works                      | 82 |

| xxvi | List | of | Tables |

|------|------|----|--------|

|------|------|----|--------|

| 5.1 | TMMU entry                                                  |

|-----|-------------------------------------------------------------|

| 5.2 | Overview of instructions executed by the dispatcher         |

| 5.3 | Overview of annotations executed by the TMC                 |

| 5.4 | Post-synthesis area results on Xilinx Zynq Z-7020           |

| 5.5 | Power results of overall architecture on Xilinx Zynq Z-7020 |

| 5.6 | Performance comparison with previous off-core approaches    |

| C.1 | Dispatcher instruction set                                  |

| C.2 | FUNC field of the A/L instruction                           |

| C.3 | TMC core instructions (called annotations)                  |

| C.4 | Func field for the tag_arith_log annotation                 |

# List of Listings

| 1.1 | Buffer overflow example code                                                   |

|-----|--------------------------------------------------------------------------------|

| 1.2 | Simplified assembly code for the buffer overflow example code (Listing 1.1)    |

| 2.1 | Example C code                                                                 |

| 2.2 | Tracking program code for application level IFT                                |

| 2.3 | Application level IFT                                                          |

| 2.4 | Example ARM assembly code (instrumented)                                       |

| 3.1 | Example C code for DIFT                                                        |

| 3.2 | Decoded trace of main function of the binary compiled from Listing 3.1 29      |

| 3.3 | Patch developed for adding support for branch broadcasting feature of CS       |

|     | components in a Zynq SoC (Excerpt from patch)                                  |

| 3.4 | Patch developed for adding support for CS components in a Zynq SoC (Excerpt    |

|     | from patch)                                                                    |

| 3.5 | Patch developed for adding the CS TPIU driver in Linux kernel (Excerpt from    |

|     | patch)                                                                         |

| 3.6 | Raw trace of .text section related to the compiled binary of C code in $3.142$ |

| 3.7 | ·                                                                              |

| 3.8 | Example code for OS-related information required for DIFT                      |

| 3.9 | ·                                                                              |

| 4.1 | Buffer overflow example code                                                   |

| 4.2 | Pseudo-code of the program running on the ARMHEx coprocessor 70                |

| 4.3 | <del>-</del>                                                                   |

| 4.4 |                                                                                |

|     | single value                                                                   |

| 4.5 | 1                                                                              |

| 4.6 | •                                                                              |

| 4.7 |                                                                                |

| 4.8 | •                                                                              |

| 5.1 |                                                                                |

| 5.2 | _                                                                              |

| 6.1 | 1                                                                              |

| 6.2 | Optimization directives for the LR algorithm                                   |

| xxviii | List of Listings                              |

|--------|-----------------------------------------------|

|        |                                               |

| 6.3    | Accelerated portion of the NB algorithm       |

| 6.4    | Optimization directives for the NB algorithm  |

| 6.5    | Accelerated portion of the SVM algorithm      |

| 6.6    | Optimization directives for the SVM algorithm |

# Chapter 1

## Introduction

In this chapter, background context and motivations for this work are described. Then, the important notion of security policy is explained with the help of an uninitialized memory attack. A non-exhaustive list of software attacks is presented in order to understand the type of attacks that can be detected using information flow tracking.

#### Contents

| 1.1 | Background and Motivations                | 1  |  |

|-----|-------------------------------------------|----|--|

| 1.2 | Security policies                         | 4  |  |

| 1.3 | Non-exhaustive list of software attacks   | 5  |  |

| 1.4 | Open Research questions                   | 7  |  |

| 1.5 | Manuscript organization and contributions | 9  |  |

| 1.6 | Summary                                   | 10 |  |

|     |                                           |    |  |

### 1.1 Background and Motivations

Software security is still one of the main concerns in today's systems even though an important amount of research has been done on the subject. There is no universal solution for software security because the security has been overlooked for performance from the dawn of the computer age. From the invention of transistor-based computers, the focus of research and development has been put on the improvement of speed rather than the security of computers. This leads to devices considering security as an optional feature rather than a compulsory one. In the 1980s, the first impactful software attacks showed the need for making research efforts in the domain of software security.

Since the beginning of this field, most of the solutions proposed in research are not being widely adopted by hardware vendors and software developers and there are a few reasons for that. One of the main reason is the scope of existing works. Most related works provide

an answer to a particular type of software attacks. There are a huge variety of attacks that target different aspects: some target a particular aspect of the hardware while others take advantage of a software misconception. In average, 40 new software vulnerabilities have been detected every single day of 2017 [8]. In addition to the different level of attacks, there has been a diversification of targeted devices. The attacks are no longer limited to the personal computer but can affect all the connected devices. For all these major concerns, there is an important need of providing architectures that provide security features.

This paragraph briefly discusses important software security notions. First of all, there are three important software security principles that are briefly discussed: confidentiality, integrity, and availability. Confidentiality consists of making sure that only the authorized users has access to the data while integrity consists of making sure that only the authorized users can modify the data. Availability refers to the accessibility of data or the system to authorized users at all time. The security policy details which information containers (files, variables, registers, ...) are being considered as well as the security properties that are studied. Security mechanisms are used to detect, prevent or recover from a security attack. There are two important types of security mechanisms: preventive and reactive mechanisms. The preventive mechanisms are used in order to reduce the probability of an attack (e.g. cryptographic mechanisms, isolation, and formal proof). However, the attackers end up finding security loopholes in the existing code and bypass these mechanisms. Therefore, reactive mechanisms have been proposed in order to monitor the system and detect a security policy violation in order to recover. One of the most generic and universal solution to detect software attacks is the dynamic information flow tracking.

DIFT approaches target confidentiality and integrity principles. Existing software-based DIFT approaches are flexible (multiple security policies can be applied in order to detect multiple types of software attacks) while requiring an important amount of computation time. Therefore hardware-assisted approaches have been proposed in order to speed up the execution time of DIFT operations. However, almost all of these hardware-assisted DIFT approaches target open architectures such as SPARC V8 [9] whereas ARM, Intel, and AMD architectures are widely used in the industry are left unstudied. Furthermore, some related works target a system with a standalone OS (*Operating System*) which is not the case in most systems used in the industry. All these reasons showed the need to bridge this gap by providing a solution that can protect from most types of software attacks and is portable to existing systems.

There are two main types of approaches in order to detect software attacks: signature-based and behavioral-based. The signature-based approach consists in comparing the action or code sequence of the application with a known set of "signatures" (i.e. known pieces of code that indicate an attack or a malware). The behavioral-based approach consists in monitoring program behavior and comparing it with a model of the legitimate behavior: it works well in

order to detect new unknown attacks while a signature-based approach only detects known attacks.

The goal of the work proposed in this thesis is to propose a solution for software security on an ARM-based CPU running Linux OS in order to bridge the gap between research and industry. The ARM architecture is one of the most used architectures in embedded devices (smartphones, tablets and other electronic devices). In 2013, ARM-based chips were found in 60 % of the world's mobile devices [10]. The Linux kernel is also one of the most used OS in the world. The choice of the architecture and the OS is crucial in order to make sure that the end user would be able to take advantage of the approach proposed in this work.

This work studies behavioral-based solutions in order to detect software attacks. More precisely, we rely on taint-based and anomaly-based approaches. Taint-based detection scheme consists in adding tags to the information container, propagating the tag each time the information container is accessed or modified and checking the value of the tag when it is copied or written to another information container. The information container differs depending on which level the detection is made. For instance, if the low-level scheme is used, then the information container is a register or a memory address. The anomaly-based detection scheme consists in detecting programs that are likely to present a threat and block them. Chapters 2, 3, 4 and 5 studies taint-based detection in embedded systems running the Linux kernel while chapter 6 studies anomaly-based detection in embedded systems running Android.

#### HardBlare project

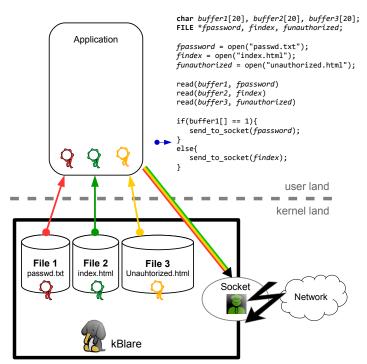

This work is done in the frame of the HardBlare project [11]. This project aims at exporting compute-intensive operations of the Blare project [12, 13, 14] to a dedicated hardware coprocessor. Blare, an OS-level taint-based approach, consists in providing security features in the Linux kernel using LSM (*Linux Security Modules*) hooks. It allows detecting security policy violations such as intrusions and malware.

Blare is an OS-level information flow monitor. The information container at the OS level is a file: it means that tags are associated with files. Each time a program accesses a file, then the tag of the file is associated with the program. Conversely, each time the program writes to a file, the tag of this file is updated with the tag of the program and the security policy verifies whether this information flow is authorized or not. The propagation and check required by the security policy are all done by the Linux kernel. Furthermore, the memory used by the process is considered to be tagged by all the files read. For instance, if the program reads two files, then the whole memory area used by the process is tagged with both tags instead of tagging only the region where bytes read from the file are located. It results in an important number of false positives and false negatives.

HardBlare uses Blare in order to properly initialize tags of the file in the kernel. When a read operation is made by the process, the kernel sends some information to the coprocessor in order to propagate tag. When the kernel writes to a file, the Blare part recovers the tag of the file being written and requests the tag of the file from the hardware accelerator. It allows having a more accurate vision of the memory as only the area that contains the file read by the process are tagged using the tag of the file (the behavior is similar for write operations).

#### 1.2 Security policies

The security policy states how to initialize, propagate, and check tags. Defining proper security policies in order to detect software attacks with few false positives and false negatives require formal verification and some deep knowledge on the attack that needs to be detected. This problem correspond to a dedicated research field and is out of the scope of this thesis. This work aims at providing users a framework allowing them to implement any security policy.

Some works such as [15] try to analyze and formally verify that the security policy succeeds in detecting software attacks. For instance, if an uninitialized memory corruption attack is considered, then the security policy states the propagation and check rules shown in equations 1.1 and 1.2. For the purpose of simplicity, only two tag values are considered: 0 and 1 where the value 0 means that the tag is uninitialized, the value 1 means that the memory is initialized and  $t_m$  represents the tag of the memory address being accessed or modified by the instruction.

$$Store: \{t_m = 1\} \tag{1.1}$$

Load:

$$(t_m = 0) \rightarrow interrupt$$

(1.2)

The bold text shows that the operation must happen if the instruction being executed on the main CPU has the mentioned opcode, then the propagation or the check operation should take place. If the instruction is a store instruction (equation 1.1: it could be either str, stm, vstr or vstm instruction), then the tag of the memory address should be set to 1. Otherwise, if the instruction is a load instruction (equation 1.1: it could be either ldr, ldm, vldr or vldm instruction), then the tag of the memory address should be checked. If it is equal to 0, then an uninitialized memory address is being accessed allowing to detect the memory corruption. For all other instructions, there is no propagation or check operation. This simple example shows how the security policy is specified and how it can be used in order to protect against uninitialized memory corruption attack. Similarly, there is a security policy that

specifies how to propagate and check tags in order to implement information flow control. DIFT (*Dynamic Information Flow Tracking*) requires that for each instruction executed by the CPU, another operation must be done on the tag of operands used in the instruction. Depending on the instruction type and the software attack protected, propagation and check rules of the security policy may differ.

#### 1.3 Non-exhaustive list of software attacks

This section presents the buffer overflow attack that can be protected using DIFT. The attack itself and the security policy used in order to detect this attack are explained. There are other types of attacks (Format string, SQL injection, Cross-Site Scripting, Directory traversal...) that can be detected using DIFT and specific security policies as described in [15].

#### 1.3.1 Buffer Overflow

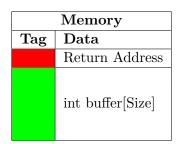

Buffer overflow is one of the first software attacks that resulted in the emerge of the software security field. It consists of overwriting some buffer in memory to modify program control flow and execute some malicious code. The goal of the security policy is to enforce the integrity of return address in order to prevent from modification of program control flow. Listing 1.1 shows an example code that can result in a buffer overflow. The user types an input that is stored in idx variable. It is then used to modify an element of the buffer. If the user types an index value that is greater than the buffer size, then this could result in modifying the elements outside the buffer which could corrupt the program data. Historically, the attacker overflows the buffer in such a way that the input data contains malicious code which could be executed after overflow by modifying the return address stored in memory (as shown in Figure 1.1). When the return address is used, it points towards the specially crafted malicious injected code by the attacker.

```

int idx = tainted_input; //stdin (> BUFFER SIZE)

buffer[idx] = x; // buffer overflow

```

**Listing 1.1** – Buffer overflow example code.

There is an important amount of techniques that allow preventing from buffer overflows: stack canaries, DEP (Data Execution Prevention) and ASLR (Address Space Layout Randomization) are the most common ones. Compilers can insert stack canaries after each buffer in order to detect a change of this value after execution allowing to successfully detect the attack. DEP consist in adding a mark using a special NX (Non eXecutable) bit available in the MMU (Memory Management Unit). It allows preventing the attacker to execute injected code from the stack. So, even if the attacker succeeds in modifying return value and pointing

| Registers |                |  |  |

|-----------|----------------|--|--|

| Tag       | Data           |  |  |

|           | r1:&input      |  |  |

|           | r2:idx=input   |  |  |

|           | r3:&buffer     |  |  |

|           | r4:&buffer+idx |  |  |

|           | r5:x           |  |  |

| Memory |                  |  |  |

|--------|------------------|--|--|

| Tag    | Tag Data         |  |  |

|        | Return Address   |  |  |

|        | int buffer[Size] |  |  |

Figure 1.1 – Initial state of the system before the program starts execution.

it towards the injected code, the attacker will not be able to run that code residing in the stack. To bypass the DEP, attackers come up with another attack named ROP (Return-Oriented Programming). Instead of overwriting the return address to point towards the injected code on the stack, the attacker manipulates the return address to point towards the instructions already available in the program also known as "gadgets" (i.e. existing code in the .text section). ASLR was designed in order to protect against ROP attacks. It works by randomizing the value of .text and data segments on each run. Therefore, the attacker cannot precisely determine the address of "gadgets" and cannot take advantage of the ROP attack.

#### 1.3.2 DIFT security policy

DIFT consists in adding a tag to a register or a memory address. Each time an instruction is executed in the CPU, it makes an operation from one or multiple source operands (register or memory address) towards a destination operand (a register or memory address). DIFT consists in propagating the tag alongside the instruction in order to monitor program behavior. The goal of this paragraph is to show how the DIFT can be used to prevent from buffer overflows. Listing 1.2 shows the simplified assembly code of the program shown in Listing 1.1.

```

set r1 \leftarrow \&tainted_input

load r2 \leftarrow M[r1]

add r4 \leftarrow r2 + r3

store M[r4] \leftarrow r5

```

Listing 1.2 – Simplified assembly code for the buffer overflow example code (Listing 1.1).

Figure 1.1 shows the initial state of the system before program execution. The main CPU registers are extended to contain an additional information about the tag. Green tags represent private tags while red tags represent public tags. Private tags mean that the information is coming from a secure source whereas public tags mean that the information is originating from a non-secure (or public) interface such as the standard input stdin. Each time an instruction is executed, the corresponding operation is realized on the tag. For

| Registers    |                |  |  |

|--------------|----------------|--|--|

| Tag          | Data           |  |  |

|              | r1:&input      |  |  |

| r2:idx=input |                |  |  |

|              | r3:&buffer     |  |  |

|              | r4:&buffer+idx |  |  |

|              | r5:x           |  |  |

Figure 1.2 – Final state of the system after the execution of program code.

instance, if the first instruction in Listing 1.2 (consisting in moving address of tainted\_input in register r1) is executed on the CPU, the tag of tainted\_input is also copied into register r1. When the second instruction is executed, the tag of r1 is also copied into r2. r4 is tainted after executing the third instruction because r2 is tainted. When the store operation on the line four takes place, the tag of the r4 register is copied to the r5 register. Figure 1.2 shows the final state of the system after the program has finished execution. When the return address is used, the tag is checked which will result in the generation of an exception due to the fact that the return address is tagged as non-secure.

# 1.4 Open Research questions

This section presents some important research questions that are not dealt in existing works.

# 1.4.1 Question 1: How to recover required information for DIFT on hard-core CPUs?

Most of existing works target softcore CPUs for DIFT implementations. It results in important design considerations that cannot be fulfilled on a hardcore CPU. One example is the interface between the CPU and the DIFT accelerator often implemented in FPGA. Decoupling tag operations on FPGA requires some information from the CPU. Existing works consider that this information can be taken from existing CPU signals. If the target CPU is a softcore, then all internal signals can be easily extracted and used in order to recover information required for DIFT. However, this is not the case on a hardcore CPU as internal signals cannot be extracted. Therefore, it is important to propose an approach allowing to recover information required for DIFT on a hardcore CPU.

#### 1.4.2 Question 2: DIFT on ARM architecture (hardcore CPU)

Most devices (smartphones, tablets and electronic systems) include ARM-based CPUs. Therefore, it is important that the proposed approach provides a solution designed for the ARM architecture. It provides general purpose registers and an FPU (Floating Point Unit) in order to speed up computation on floating point numbers. The FPU requires special instructions that are not considered in existing works. Furthermore, software considerations are different on such an architecture. For instance, the ABI (Application Binary Interface) is different from the SPARC architecture considered in related works. Therefore, it is important to target the ARM architecture in order to provide a solution that is easily usable by researchers, developers and experienced users.

DIFT coprocessors proposed in the literature lack some important features such as the tag initialization support from the OS. Furthermore, the tag management scheme consists of a simple bitmap which is not adapted on a hardcore. It is important to provide these missing features in order to improve flexibility and reusability.

# 1.4.3 Question 3: How to implement multiple security policies of different tag size ?

A program may need require a protection based on multiple security policies. Existing works provide limited support for this feature. For instance, most hardware-assisted DIFT approaches can implement multiple security policies of 1-bit tag. If the tag size needs to be bigger than 4 bits, then the security policy cannot be implemented. Therefore, it is important to provide an architecture able to run multiple security policies with different tag sizes in order to detect multiple attacks.

#### 1.4.4 Question 4: Multi-threaded system / Multicore system

Most applications take advantage of multicore systems in order to speed up execution by using multiple threads. However, no existing hardware-assisted DIFT approach provides a way to manage multiple threads. Therefore, it is important to propose an approach that can be used with a multi-threaded program.

# 1.5 Manuscript organization and contributions

#### 1.5.1 Manuscript organization

This section presents the overall organization of this thesis. Chapter 2 describes important existing works on the topic of information flow tracking and provides a comparison of features proposed in this work. Then, chapter 3 explains the first contribution of this work that details how to recover information required for DIFT on an ARM-architecture based hardcore CPU. Chapter 4 presents a first proof-of-concept implemented using a MicroBlaze softcore CPU in order to experiment that the proposed approach can allow implementing DIFT on a hardcore CPU. Later, chapter 5 shows a detailed view of the custom DIFT coprocessor that is implemented in order to improve the execution time of tag operations. Chapter 6 describes a different approach for malware detection on Android smartphones. The main goal is to propose an energy-efficient implementation of a malware detection approach proposed in [16]. Finally, chapter 7 concludes this work by summarizing proposed contributions and providing future perspectives. In addition to the main content, this manuscript contains four appendices.

- Appendix A details some characteristics of the development board used in this work.

- Appendix B details the design and evaluation method followed in order to test the developed IPs in this work.

- Appendix C details the ISA (*Instruction-Set Architecture*) of the DIFT coprocessor proposed in chapter 6.

- Appendix **D** lists the publications that the author has contributed to during the Ph.D.

#### 1.5.2 Manuscript contributions

The contributions of this thesis are the following:

- It provides a method to recover information required for DIFT on ARM CPUs. It proposes to use CoreSight PTM, static analysis, and binary instrumentation to recover information required for DIFT. It is shown that the PTM does not add any execution time overhead. This contribution is detailed in chapter 3 and chapter 4.

- Two patches have been added in the Linux kernel in order to add support for missing features [17].

- It proposes a method to protect the DIFT coprocessor using ARM TrustZone. This contribution is detailed in chapter 4.

- It provides flexible security policies implementation in hardware: previous off-core hardware-assisted approaches lack ways of specifying security policies (compile-time or

runtime only) and do not offer support for multiple security policies of different tag granularities (page, word, etc.). This contribution is explained in chapter 5.

- This work is compatible with multi-threaded applications mainly thanks to the context ID information obtained from CoreSight PTM. It allows filtering trace using Context ID and to determine the exact order of operations on the CPU for each thread. This contribution is explained in chapter 5.

- This work tracks all information flows unlike most existing works. It allows detecting a wider range of attacks. This contribution is explained in chapter 5.

- This work provides a power-efficient and runtime-efficient implementation of three classification algorithms: LR, NB, and SVM. This contribution is explained in chapter 6.

# 1.6 Summary

This chapter sums up the gap between research and industry in the domain of embedded software security. One of the main reasons for this gap is that solutions in the literature do not consider architectures widely used in the industry especially ARM. This work focus on minimizing this gap by targeting the ARM architecture. There are some other important research questions that are not handled in existing works such as multiple security policies of different tag sizes or tracking multiple threads in an hardware-assisted approach. This work focuses on providing an architecture able to track multiple security policies with different tag sizes and providing a method to recover information required for DIFT for multiple threads or multiple processes by taking advantage of a unique feature of CoreSight debug components.

# Chapter 2

# Related works

This chapter presents existing works on information flow tracking with an emphasis on hardware-assisted DIFT architectures. It also details specifications for this work and compares them with existing works.

#### Contents

| 2.1 | Introduction                                | 11        |

|-----|---------------------------------------------|-----------|

| 2.2 | Different types of IFT                      | <b>12</b> |

| 2.3 | Different levels of IFT                     | <b>12</b> |

| 2.4 | Hardware-assisted                           | 17        |

| 2.5 | Proposed solution for DIFT on hardcore CPUs | 23        |

| 2.6 | Summary                                     | <b>25</b> |

|     |                                             |           |

#### 2.1 Introduction

This chapter introduces existing works in order to fully understand the contributions reported in this thesis. Section 2.2 describes different types of IFT (Information Flow Tracking): static IFT (SIFT) and dynamic IFT (DIFT) both explained in section 2.2. SIFT is mainly used to test an application binary while DIFT is used to protect against software attacks [1]. Section 2.3 explains different levels of IFT (from application to gate level): IFT can be used at different levels in order to monitor a program behavior, to detect software security attacks and even to detect hardware trojans using gate-level information flow tracking [18]. Section 2.4 describes different hardware assisted DIFT solutions. Section 2.5 explains the benefits of this work compared to existing solutions. Finally, section 2.6 summarizes this chapter.

# 2.2 Different types of IFT

There are two types of IFT approaches: static and dynamic IFT, each one has its own goals.

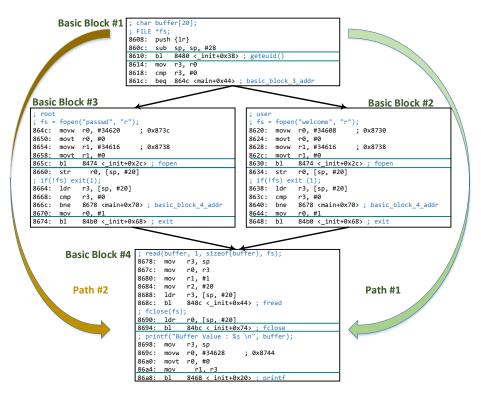

#### 2.2.1 Static IFT (SIFT)

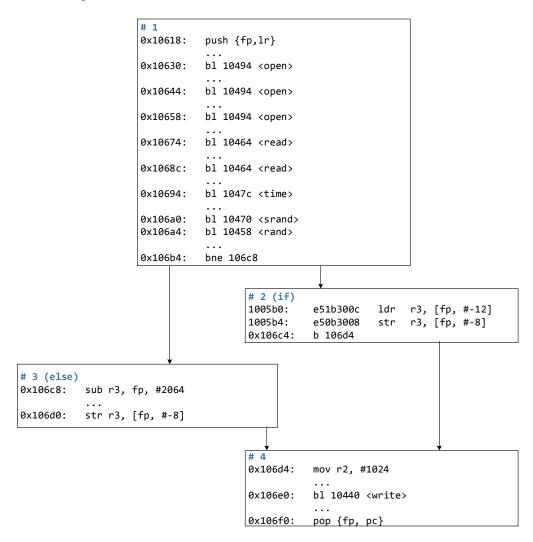

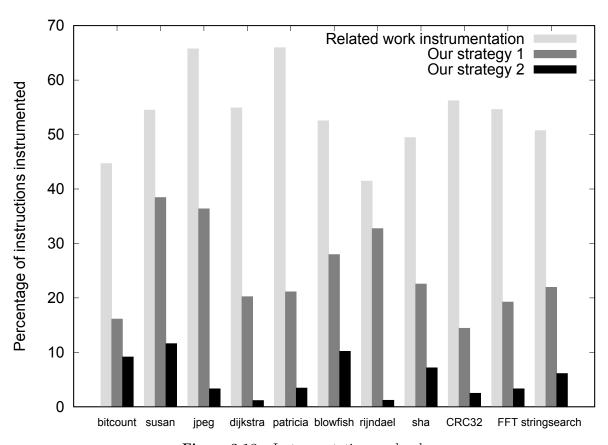

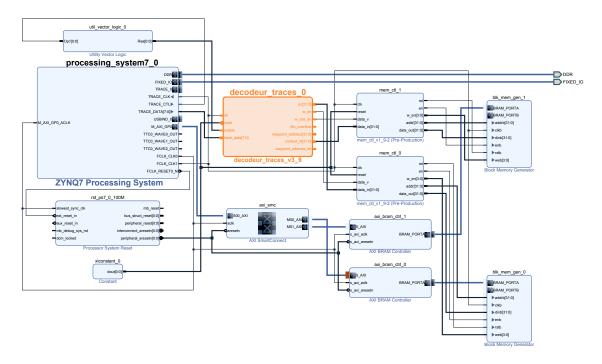

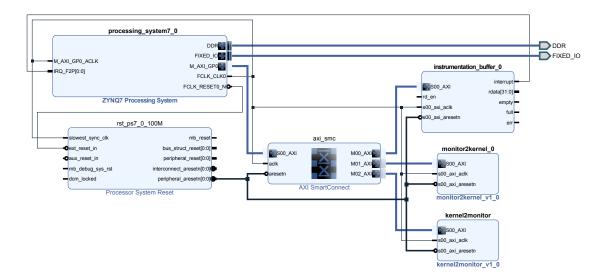

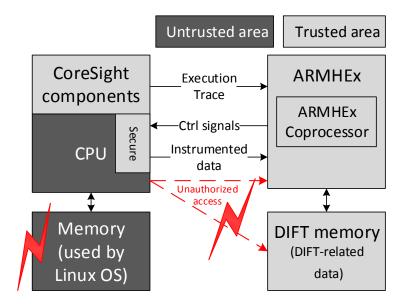

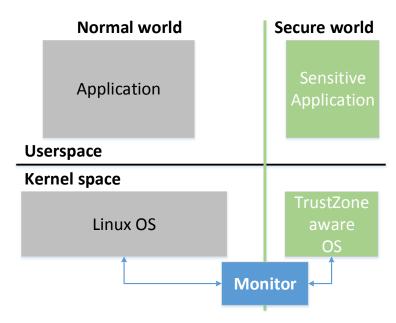

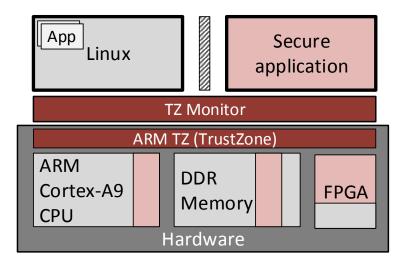

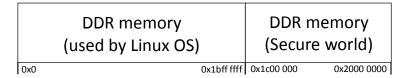

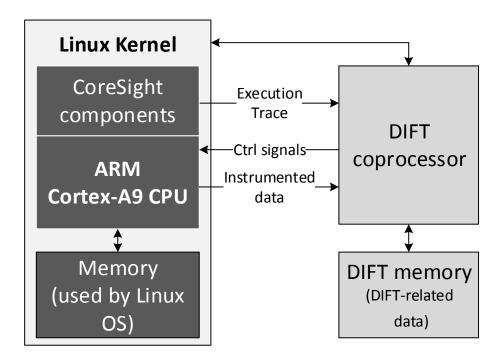

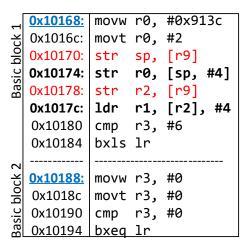

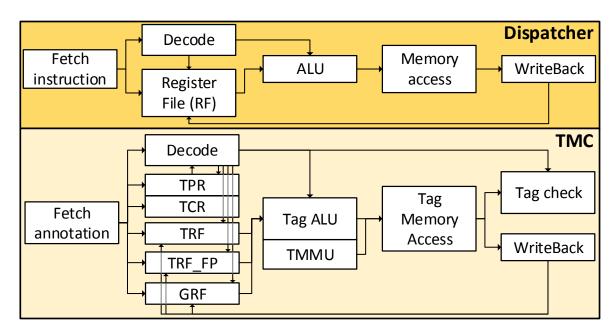

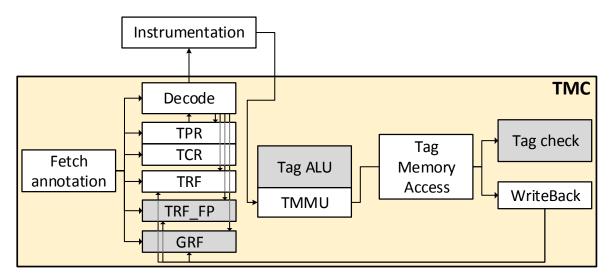

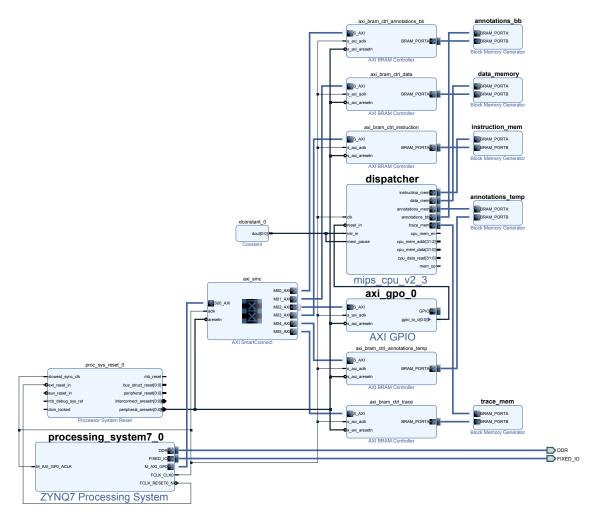

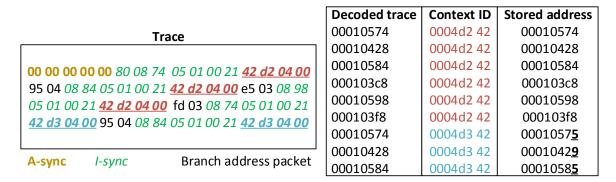

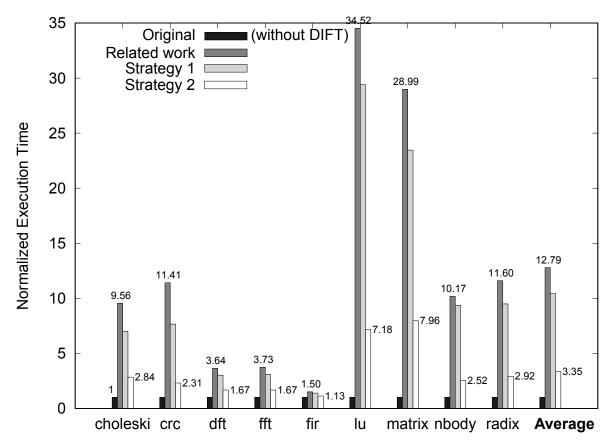

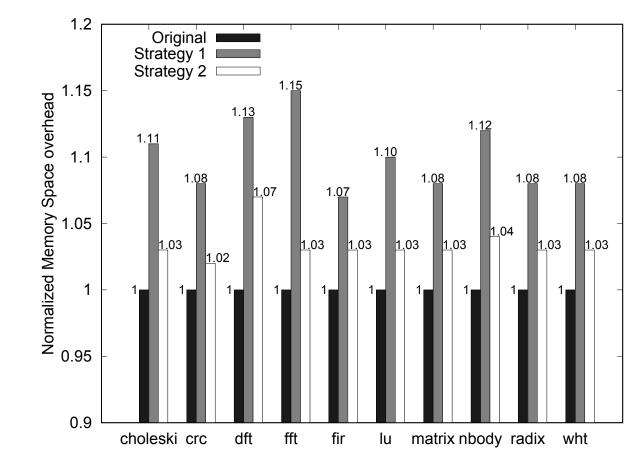

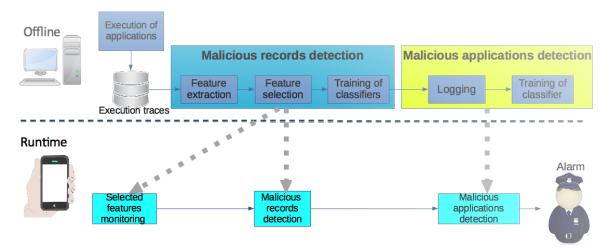

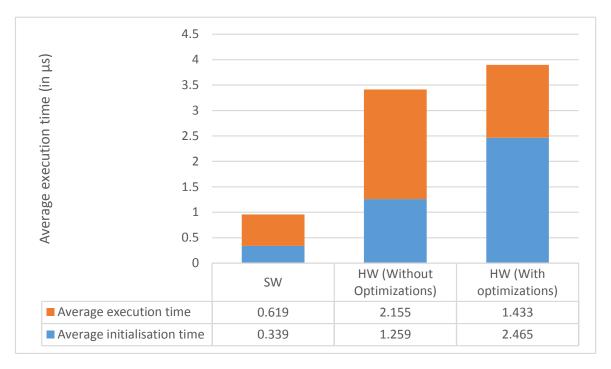

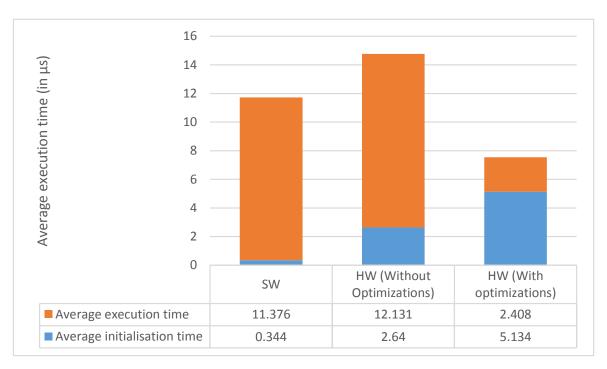

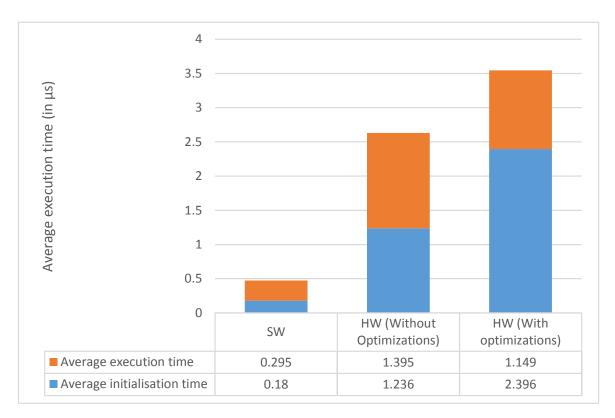

SIFT is an offline analysis of the application aiming to check that all branches of the control flow graph are trustworthy. SIFT is mainly used for the purposes of general program understanding, detection of attacks and vulnerabilities. Figure 2.1 shows a simplified CFG (Control Flow Graph) of an application compiled for the ARM-v7 architecture. The application opens a file depending on the user type determined using the geteuid function: if the user is root, the secret file passwd is opened. Otherwise, a public file welcome is opened. Then, contents of the file are copied into a buffer and printed on the stdout. The content of the passwd file should not be printed on the stdout. The CFG shows two possible paths for the application depending on the output of the test made in basic block #1. The path #1 is made up of execution of basic blocks #1, #2 and #4 while path #2 consists of the execution of basic blocks #1, #3 and #4. SIFT will analyze both these paths in order to find security vulnerabilities. As the analysis is done offline before execution, SIFT does not add runtime overhead. However, it is possible that the analyzed path may never be used by the application during execution. As a consequence, SIFT tends to produce an important number of false positives.