## Femto second sampler

Hanae Zegmout

### ▶ To cite this version:

Hanae Zegmout. Femto second sampler. Optics / Photonic. Université Grenoble Alpes, 2019. English. NNT: 2019GREAT084. tel-02634439

## HAL Id: tel-02634439 https://theses.hal.science/tel-02634439v1

Submitted on 27 May 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : OPTIQUE ET RADIOFREQUENCES

Arrêté ministériel : 25 mai 2016

Présentée par

### **Hanae ZEGMOUT**

Thèse dirigée par **Jean-François ROUX** et codirigée par **Jean-Iouis COUTAZ**, USMB et **Denis PACHE**, STMicroelectronics

préparée au sein du Laboratoire Institut de Microélectronique, Electromagnétisme et Photonique - Laboratoire d'hyperfréquences et de caractérisation dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

# Echantillonneur opto-electronique femto seconde

## Femto second sampler

Thèse soutenue publiquement le **10 juillet 2019**, devant le jury composé de :

### **Monsieur ERIC CASSAN**

PROFESSEUR, UNIVERSITE PARIS-SUD, Président

#### **Monsieur JEAN-LOUIS COUTAZ**

PROFESSEUR, UNIVERSITE SAVOIE MONT BLANC, Directeur de thèse

### **Monsieur DENIS PACHE**

INGENIEUR DE RECHERCHE, ST MICROELECTRONICS CROLLES, Co-directeur de thèse

### **Madame CATHERINE ALGANI**

PROFESSEUR, CNAM - PARIS, Rapporteur

#### **Monsieur ANTHONY GHIOTTO**

MAITRE DE CONFERENCES, UNIVERSITE DE BORDEAUX, Rapporteur

### **Monsieur BERTRAND SZELAG**

INGENIEUR DE RECHERCHE, CEA GRENOBLE, Examinateur

# **Declaration of Authorship**

I, Hanae ZEGMOUT, declare that this thesis titled, "Femto-second sampler" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

| Signed: ——— | ———— Hanae ZEGMOUT |

|-------------|--------------------|

| Date: ————  | 10/10/2019         |

# Acknowledgements

I would like to express my sincere gratitude to all my supervisors for their much appreciated guidance and help during this thesis.

I am highly indebted to Mr Jean-François Roux for his very active involvement in my research work. His deep theoretical knowledge along with his enthusiasm for this thesis research topic helped me in multiple times dig deeper into my work.

I would like to give a special thank you to Mr Denis Pache from STMicroelectronics. It was a delight to be working alongside this great man whose clever remarks and deep understanding of the topic in hand alleviated many problems that I faced during my research work.

I would like to thank Mr Jean-Louis Coutaz for the very enriching discussions that we had and most precisely his very impressive insights in semiconductor physics that were very helpful to my work.

I would like to thank Mr Stephane Le Tual for the much appreciated time and help he gave me with the microelectronics design part of this thesis.

I am very grateful to the amazing people who kindly surrounded me during my thesis work at STMicroelectronics and were always there to cheer me up: Mr Christophe Arricastres, Mrs Sarah Verhaeren and Mrs Valerie Danelon.

I would like to thank equally my colleagues from IMEP-LAHC for their help and support.

I am very grateful to CEA-Leti characterization team for their much appreciated measurement work on my circuits. A very special thank you to Mr Philippe Grosse for his time, dedication and amazing humor.

I would like also to express my deepest appreciation to my jury members and thank them for having accepted to take part in this adventure: Mr Eric Cassan, Mrs Catherine Algani, Mr Anthony Ghiotto and last but not least, my current boss: Mr Bertrand Szelag.

Finally, I would like to thank, very dearly, my parents and sisters without whom this work would have never been done. Thank you very much for your love, support and confidence....

To my parents and my sisters Hind & Laila and to all my friends and coworkers . . .

# Résumé de thèse : Echantillonneur femto-seconde

Dans un monde de plus en plus connecté, il devient indispensable de trouver des moyens d'augmenter le débit d'informations qu'il est possible de véhiculer et de traiter. Ce besoin impose aux ingénieurs des contraintes plus serrées en termes de bande passante et de fréquence d'horloge des circuits qu'ils conçoivent.

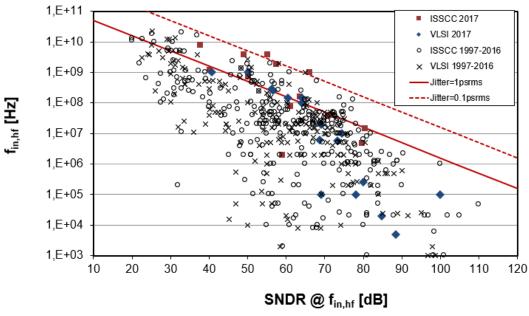

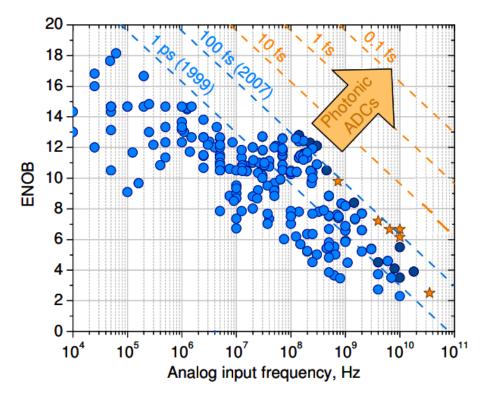

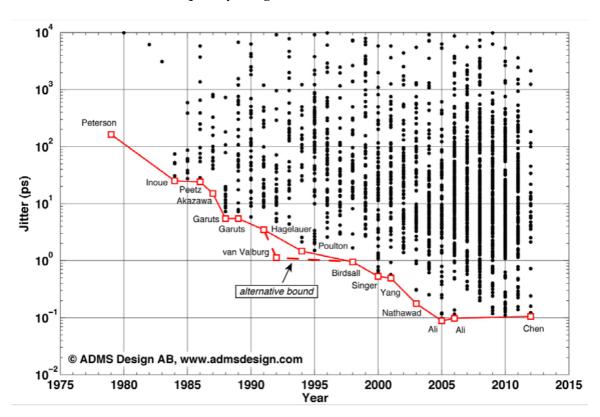

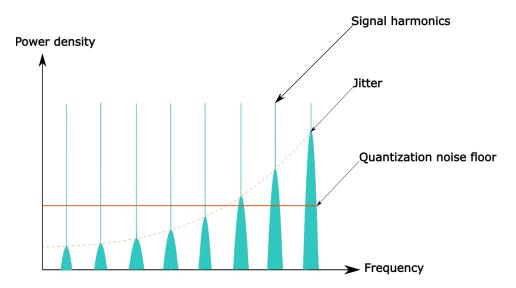

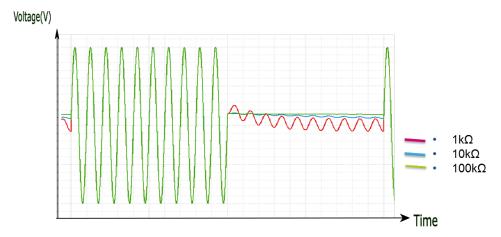

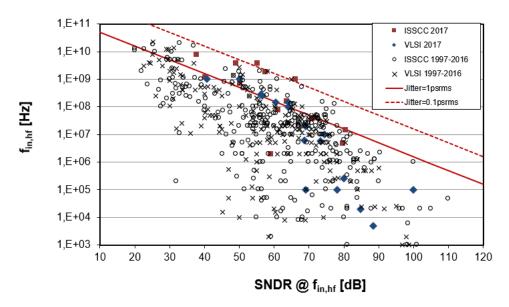

En microélectroniques, cela constitue un réel obstacle pour la conception de circuits plus avancés. En effet, les horloges électroniques sont limitées par leur performance en termes de stabilité de la période d'horloge (cf fig1). Cela provient du bruit qui est inhérent à la structure du circuit de l'horloge.

Figure 1: Limitation de la fréquence d'échantillonnage en fonction de la gigue d'horloge

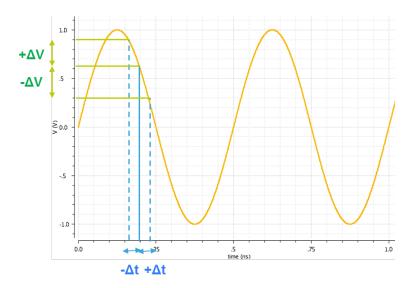

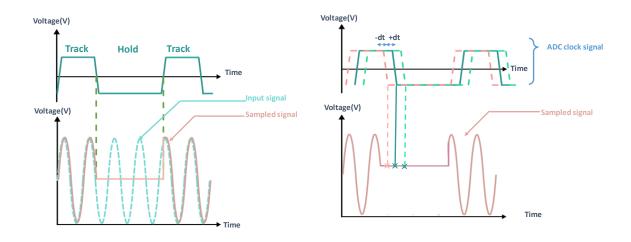

En effet, une période d'horloge instable implique que le signal à traiter n'est pas échantillonné au bon moment. L'erreur alors commise au niveau

du signal échantillonné est d'autant plus grande que la fréquence du signal échantillonné est haute.

La photonique intégrée sur Silicium constitue une solution potentielle à ce problème. En effet, les horloges optiques, i.e les lasers pulsés, présentent des performances très intéressantes en termes de stabilité ou de gigue en comparaison avec les horloges en microélectroniques. Les lasers pulsés en photoniques présentent, même en version industrielle, des gigues de l'ordre de 10fs alors que les horloges microélectroniques atteignent à peine les 50fs de gigue, et seulement dans la littérature.

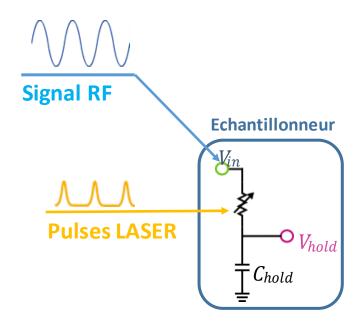

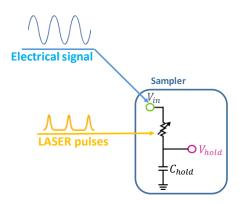

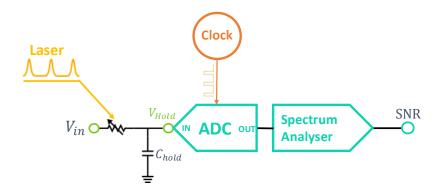

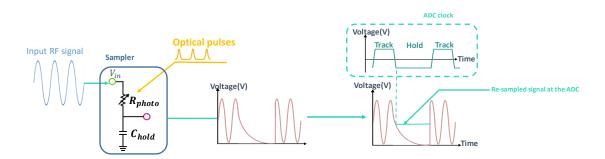

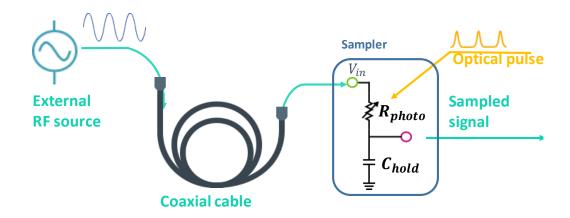

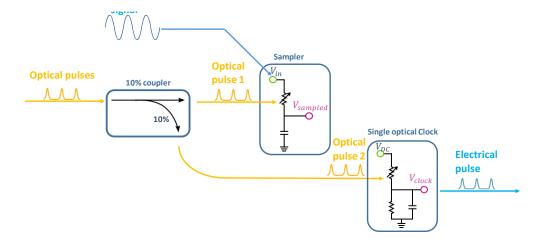

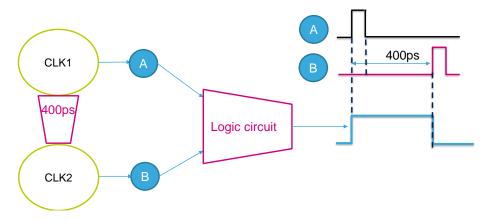

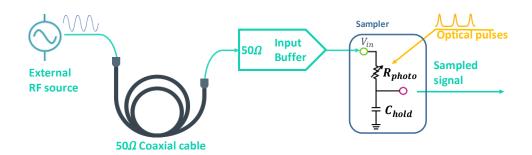

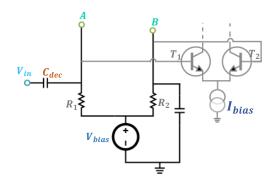

L'idée principale de cette thèse est de tirer profit de la performance des lasers pulsés en gigue en concevant un circuit optoélectronique piloté par le laser et permettant d'échantillonner un signal électrique RF (cf figure 2).

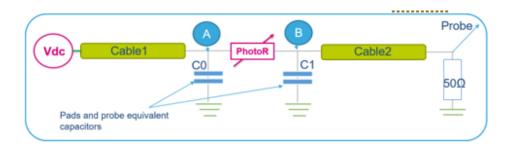

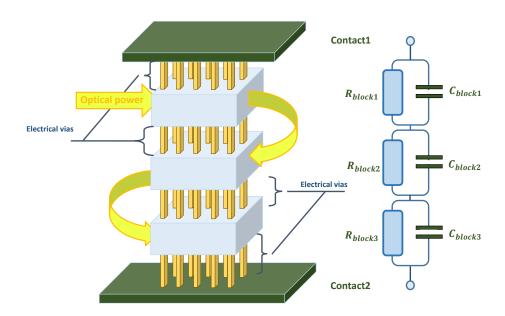

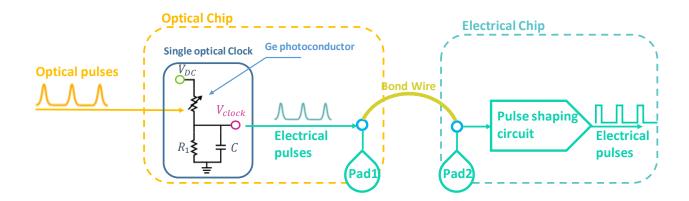

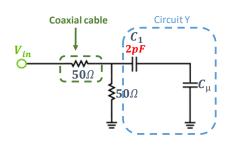

Figure 2: Circuit de base de l'échantillonneur optoélectronique

On utilise dans cette thèse un laser de longueur d'onde : 1550nm présentant une gigue de 11fs avec des pulses de 100fs toutes les 10ns. Les pulses du laser sont couplés dans une fibre et sont ainsi élargis de façon à ce que le circuit d'échantillonnage perçoive des pulses de 3,4ps au lieu de 100fs. Cette étape est nécessaire au fonctionnement du circuit parce que

100fs est une valeur très faible comparée aux constantes de temps de la partie électrique du circuit.

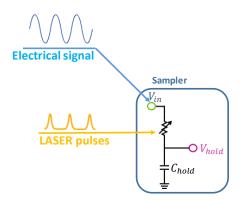

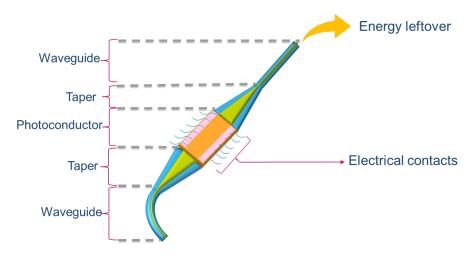

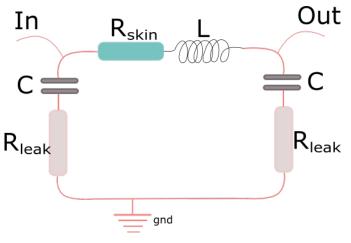

La brique de base du circuit en question est un photoconducteur en Germanium : une résistance en Germanium dont la résistivité varie selon la puissance du signal optique qu'elle reçoit du laser pulsé. Le photoconducteur dans ce cas précis jour le rôle d'un interrupteur piloté par le laser, et connecte l'entrée RF à la capacité d'échantillonnage (cf fig2). Quand l'interrupteur reçoit un pulse de lumière sa résistance chute et le signal RF peut être copié vers la capacité. Dès que le pulse de lumière s'arrête, le photoconducteur en Germanium retrouve sa résistance initiale et déconnecte ainsi l'entrée RF de la capacité qui contient le signal échantillonné.

Cette thèse se propose d'étudier la faisabilité d'un tel circuit et la possibilité d'exploiter la performance des lasers en termes de stabilité de l'horloge dans l'échantillonnage d'un signal électrique.

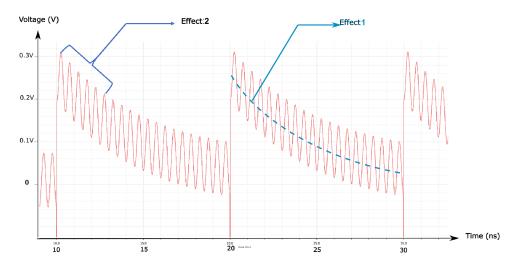

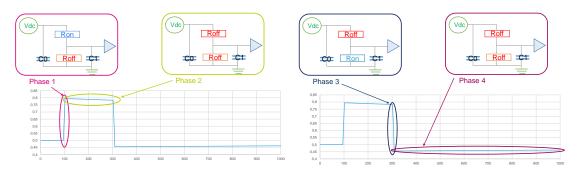

Dans un premier temps, nous avons essayé d'implémenter le circuit de base présenté auparavant. Nous avons constaté plusieurs problèmes :

- Effet 1: Les valeurs des résistances Off du photoconducteur utilisées n'étaient pas assez élevées pour permettre de déconnecter entièrement le signal RF de la capacité d'échantillonnage. Cette

- Effet 2: Le passage de la valeur Off à la valeur On du photoconducteur en Germanium ne se fait pas de manière instantanée ce qui complique d'autant plus le travail de l'échantillonneur.

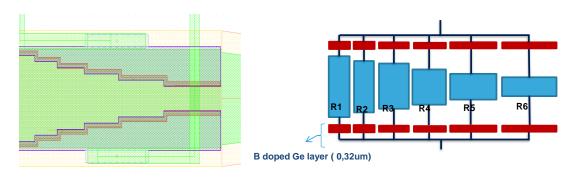

Le premier effet provient de la présence d'un dopage résiduel de type P (Bore) au niveau du Germanium que nous avons utilisé. Ce dopage est relatif au procédé de fabrication à STMicroelectronics et ne peut pas être évité en amont (au moins pas à notre niveau). Cet effet est très gênant au niveau de la fonctionnalité du circuit d'échantillonnage parce qu'une faible résistance Off implique que le signal échantillonné n'est pas stocké longtemps au niveau de la capacité d'échantillonnage.

Le simple fait d'utiliser une géométrie plus conséquente pour le photoconducteur afin d'obtenir une grande valeur de Roff n'est pas une bonne option car cela entraînerait une augmentation de la value de Ron, ce qui impliquerait que le signal ne serait même pas copié proprement vers la capacité d'échantillonnage.

Le deuxième effet est également important parce que ses conséquences sur le signal échantillonné sont du même ordre que celles du premier effet.

Nous avons donc essayé de contourner ces problèmes en utilisant trois méthodes :

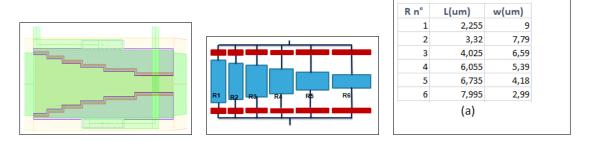

- Méthode 1 : une nouvelle géométrie des photoconducteurs en Germanium qui permettrait de maximiser les rapport Roff/Ron (géométrie brevetée).

- Méthode 2 : Un contre dopage de type N (Phosphore) afin de contourner le dopage résiduel du Germanium.

- Méthode 3 : L'utilisation d'un circuit électronique qui permet de re-échantillonner le signal en sortie du circuit de base avant qu'il soit perdu à cause des deux effets précédemment expliqués.

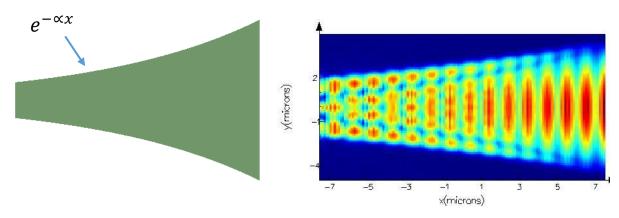

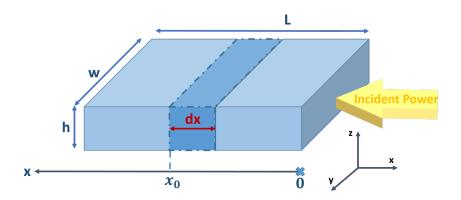

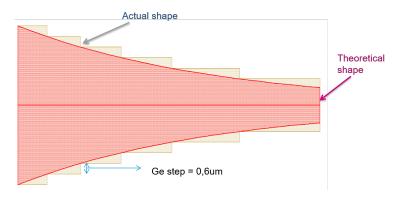

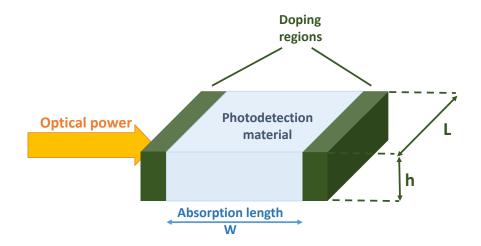

La première méthode repose sur le constat que la lumière est absorbée au niveau du Germanium de manière exponentiellement décroissante. Aussi, la géométrie utilisée épouse la décroissance de la lumière et permet ainsi d'avoir une densité de porteurs de charge photo-générés qui est homogène tout au long du photoconducteur.

Figure 3: Propagation de la lumière dans une géométrie exponentielle

L'utilisation de cette géométrie permet d'avoir un rapport Roff/Ron deux fois plus grand que le rapport Roff/Ron d'une structure rectangulaire traditionnelle avec la même résistance Roff.

La deuxième méthode a également permis d'optimiser les rapport Roff/Ron: on a obtenu un rapport six fois plus grand que le rapport Roff/Ron initial tout en conservant la même valeur de Ron. Cela veut dire que la structure cristalline du Germanium n'a pas été altérée par l'application du contre-dopage.

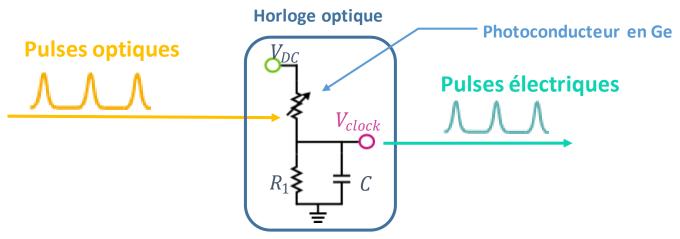

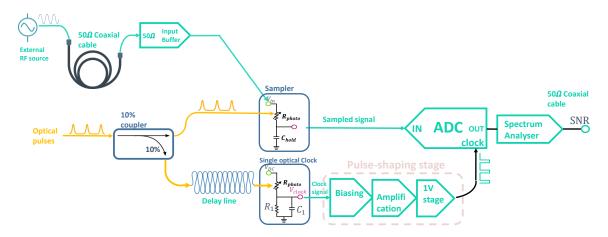

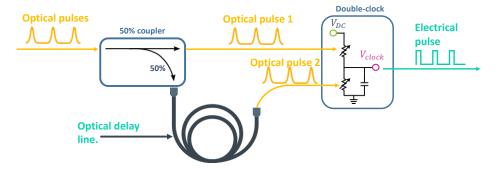

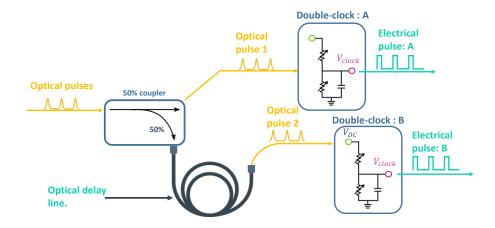

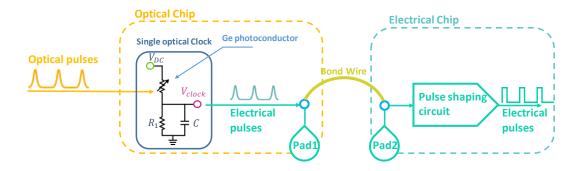

La troisième méthode est plus élaborée, elle consiste à échantillonner le signal stocké au niveau de la capacité d'échantillonnage dès que le pulse de lumière est terminé. Afin de conserver la performance en gigue, on a utilisé pour cela un CAN (convertisseur analogique numérique) piloté par une horloge photonique créée à) partir des mêmes pulses de lumière du laser.

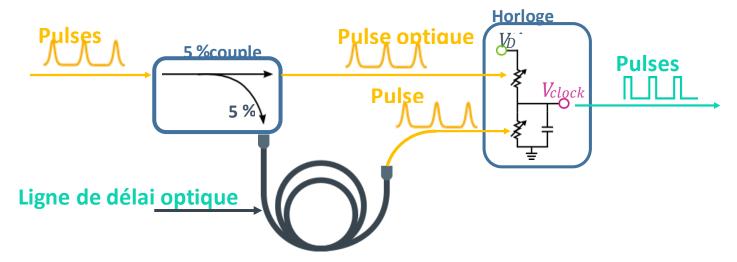

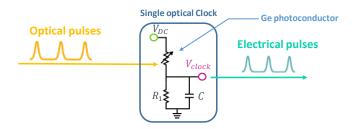

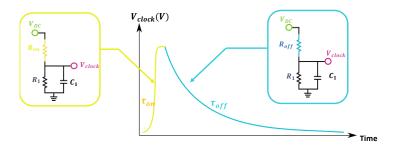

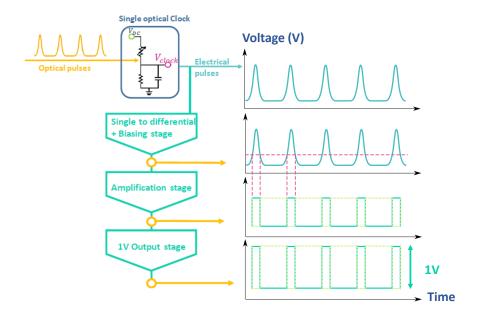

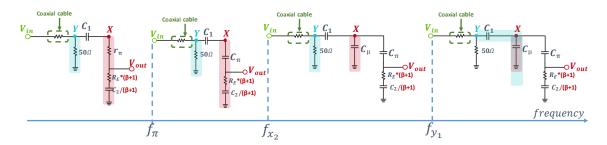

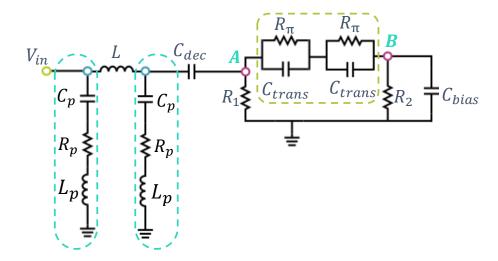

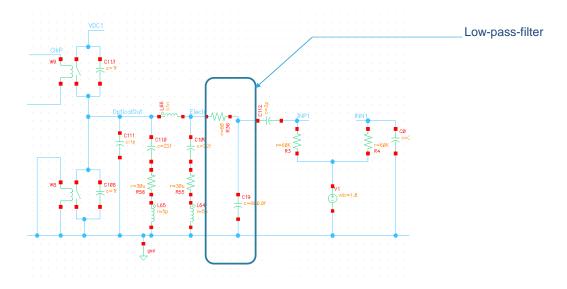

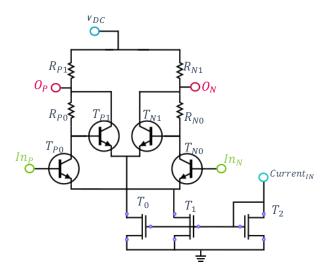

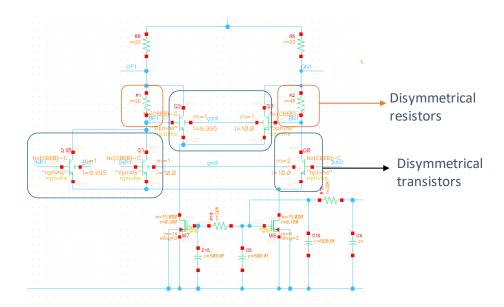

Figure 4: Schéma du circuit de l' horloge optique

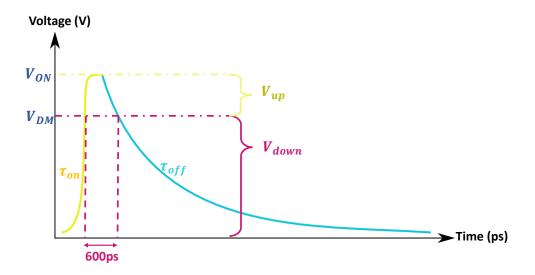

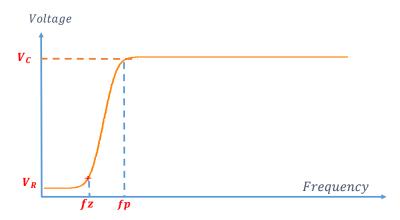

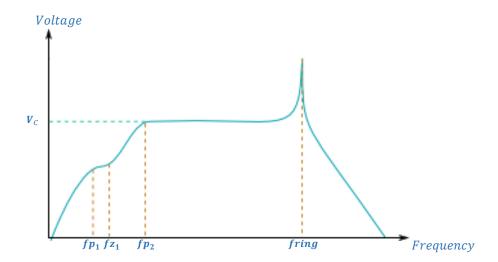

Le schéma des horloges optiques ainsi créés est présenté sur la figure 4. Le seul inconvénient de ces structures est qu'elles présentent un temps de descente du signal électrique qui est très long (ce qui est dû à la valeur de Roff et le temps de passage de Ron à Roff).

La durée des pulses générés par ce circuit est également limitée à des dizaines de picosecondes. En effet, la génération du pulse de l'horloge est possible du moment que le signal de l'horloge reste relativement dans l'état haut.

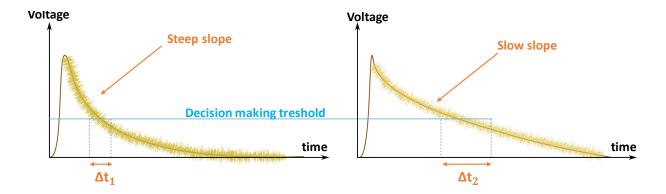

Dans un premier temps, nous avons conçu une structure d'horloge optique qui permet d'avoir des fronts montant et descendant assez droits, ce

qui permet de maximiser la stabilité du signal d'horloge quand il se propage dans les circuits en aval (cf fig.5).

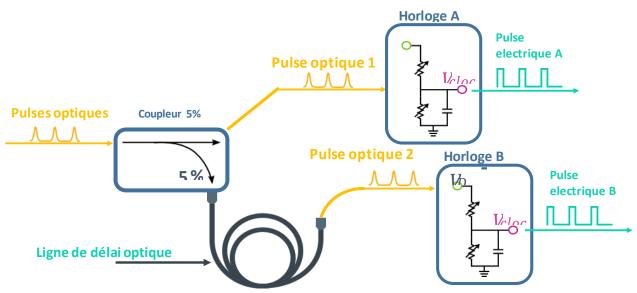

Figure 5: Schéma du circuit de la deuxième horloge optique

La durée de ces pulses est également limitée de la même manière que la structure d'horloge d'origine, dans ce cas précis, la ligne de délai optique génère un retard de 100ps.

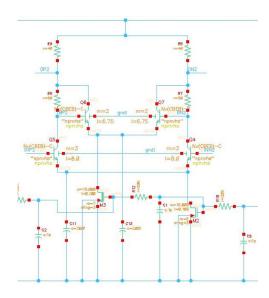

Nous avons conçu également une dernière structure d'horloge qui utilise deux briques semblables à celles présentées dans la figure5 et qui les combine pour créer un signal d'horloge à durée variable (cf figure 6).

Figure 6: Schéma fonctionnel de la troisième horloge optique

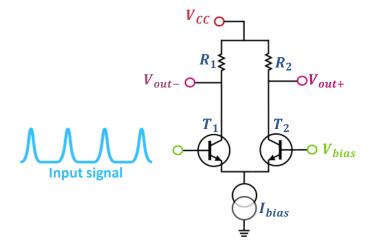

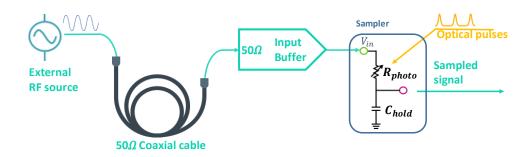

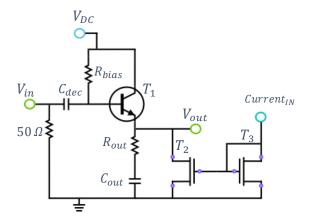

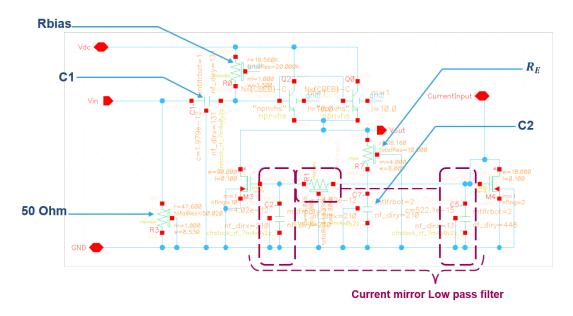

Afin d'implémenter le premier circuit (échantillonneur + horloge optique simple), nous avons conçu un circuit électronique qui permet de coupler le signal électrique dans le circuit d'échantillonnage après le passage dans un câble coaxial (signal RF d'une source extérieur). Nous avons également implémenté un circuit de mise en forme du signal de l'horloge optique qui permet d'obtenir des signaux rectangulaires de durée adéquate à l'ADC en aval (approximativement 600ps).

Le dernier circuit d'horloge a également nécessité la conception d'un circuit de bascule avec les signaux Set et reset générés par les signaux en sortie des deux horloges optiques de base.

# **Contents**

| Co | onten           | ts        |                                                             | i  |

|----|-----------------|-----------|-------------------------------------------------------------|----|

| 1  | Gen             | eral in   | troduction                                                  | 1  |

| 2  | 2 Introduction: |           |                                                             |    |

|    | 2.1             | Jitter i  | n communications                                            | 3  |

|    |                 | 2.1.1     | Jitter in electronic clocks                                 | 4  |

|    |                 | 2.1.2     | Jitter in photonics                                         | 5  |

|    |                 | 2.1.3     | Photonic ADCs                                               | 5  |

|    | 2.2             | Silicor   | n Photonics                                                 | 7  |

|    |                 | 2.2.1     | A brief history of Silicon Photonics                        | 8  |

|    | 2.3             | State o   | of the art: photodetectors                                  | 10 |

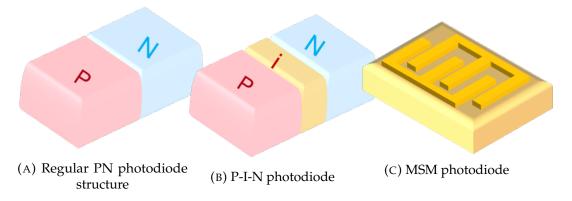

|    |                 | 2.3.1     | Photodiodes                                                 | 10 |

|    |                 |           | 2.3.1.1 Fermi level                                         | 11 |

|    |                 |           | 2.3.1.2 Space-charge region                                 | 11 |

|    |                 |           | 2.3.1.3 Photodiode types                                    | 11 |

|    |                 |           | 2.3.1.4 State of the art                                    | 15 |

|    |                 | 2.3.2     | Photo-conductors                                            | 21 |

|    |                 | 2.3.3     | Conclusion                                                  | 22 |

| 3  | Ger             | maniur    | n in silicon photonics                                      | 23 |

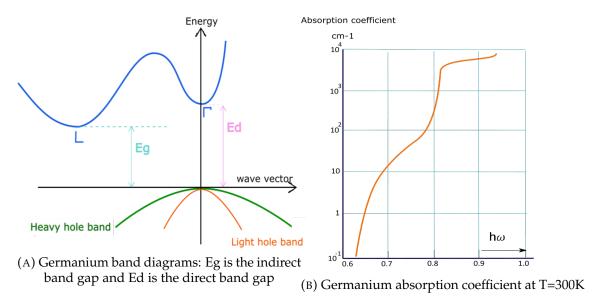

|    | 3.1             |           | anium photo-conductors: presentation                        | 23 |

|    |                 | 3.1.1     | Photo-detection in germanium                                | 23 |

|    |                 | 3.1.2     | Technology impact on absorption in germanium                | 25 |

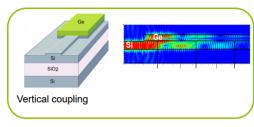

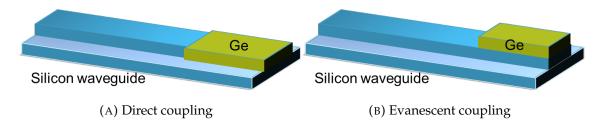

|    |                 |           | 3.1.2.1 Absorption versus coupling type                     | 25 |

|    |                 |           | 3.1.2.2 Absorption versus lattice strain                    | 26 |

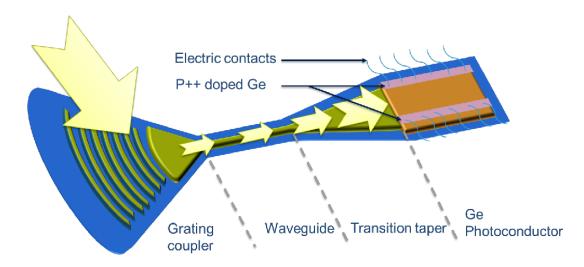

|    |                 | 3.1.3     | Photo-conductors design scheme                              | 26 |

|    |                 | 3.1.4     | Photo-conductors fabrication process                        | 29 |

|    |                 | 3.1.5     | Photo-conductors operation                                  | 30 |

|    | 3.2             |           | nuous wave measurements and model                           | 32 |

|    |                 | 3.2.1     |                                                             | 32 |

|    |                 |           | 3.2.1.1 Versus voltage                                      | 33 |

|    |                 |           | 3.2.1.2 Versus geometry                                     | 37 |

|    |                 | 3.2.2     | I-V characterization of the photoconductors under continu-  |    |

|    |                 | 5 · _ · _ | ous illumination                                            | 38 |

|    |                 |           | 3.2.2.1 Versus voltage                                      | 40 |

|    |                 |           | 3.2.2.2 Electrical equivalent model of the photo-detector . | 43 |

|    |                 |           | 3.2.2.3 Versus optical power                                | 44 |

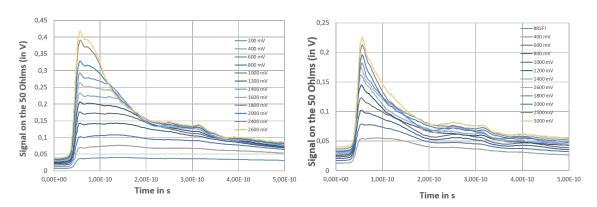

|    | 3.3             | Pulsed    | d measurements                                              | 51 |

|   |     | 3.3.1   |           | nch                                        |     |

|---|-----|---------|-----------|--------------------------------------------|-----|

|   |     | 3.3.2   | Measur    | ements results                             | 52  |

|   |     | 3.3.3   | Analysi   | s and model                                | 56  |

|   |     |         | 3.3.3.1   | First approach                             | 56  |

|   |     |         | 3.3.3.2   | Model simulation                           | 58  |

|   |     |         | 3.3.3.3   | Conclusions                                | 60  |

|   |     | 3.3.4   | Conclus   | sion                                       | 63  |

| 4 | Ger | maniu   | m photo-  | sampler:                                   | 65  |

|   | 4.1 | Basic   | sampler o | circuit: operation and problems            | 65  |

|   |     | 4.1.1   | Sample    | r circuit                                  |     |

|   |     | 4.1.2   | Jitter in | ADC                                        |     |

|   |     | 4.1.3   | Test circ | cuit limitations                           | 69  |

|   |     | 4.1.4   | Conclus   | sion                                       | 74  |

|   | 4.2 | Basic   | sampler o | circuit: alternative solutions             | 74  |

|   |     | 4.2.1   | Novel g   | geometry                                   | 75  |

|   |     |         | 4.2.1.1   | Basic concept                              | 75  |

|   |     |         | 4.2.1.2   | Theoretical explanation                    | 75  |

|   |     |         | 4.2.1.3   |                                            |     |

|   |     | 4.2.2   | Other g   | eometries                                  | 88  |

|   |     |         | 4.2.2.1   | Conclusion                                 | 97  |

|   |     | 4.2.3   | Counter   | r-doping                                   | 98  |

|   |     | 4.2.4   |           | ound circuit                               |     |

|   |     |         | 4.2.4.1   | Clock generation: circuit operation        | 102 |

|   |     |         | 4.2.4.2   | Clock generation: circuit limitations      |     |

|   |     |         | 4.2.4.3   | Clock generation: final circuit scheme     |     |

|   |     |         | 4.2.4.4   | Input Buffer circuit:                      |     |

|   |     |         | 4.2.4.5   | Final sampler circuit scheme:              |     |

|   |     |         | 4.2.4.6   | Conclusion and perspectives                |     |

|   | 4.3 | Photo   | nic clock | circuit                                    |     |

|   |     | 4.3.1   |           | photonic clock circuit                     |     |

|   |     | 4.3.2   |           | photonic clock circuit                     |     |

|   | 4.4 |         |           |                                            |     |

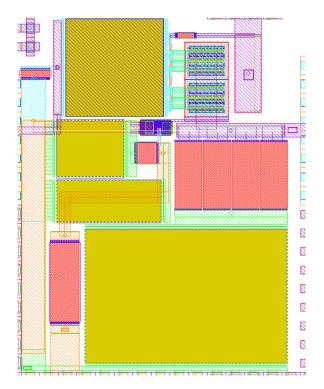

| 5 | Des | ign and | d layout  |                                            | 125 |

|   | 5.1 | Techn   | ology     |                                            | 125 |

|   | 5.2 |         |           | t design                                   |     |

|   |     | •       | 5.2.0.1   | Input Buffer                               |     |

|   |     | 5.2.1   | Clock g   | eneration circuit:                         |     |

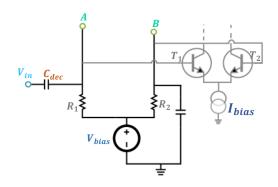

|   |     |         | 5.2.1.1   | The single-to-differential + biasing stage | 145 |

|   |     |         | 5.2.1.2   | The amplification stage                    |     |

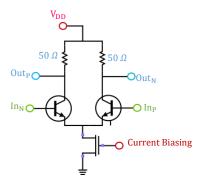

|   |     |         | 5.2.1.3   | The 1V output stage                        |     |

|   |     |         | 5.2.1.4   |                                            |     |

|   |     |         | 5.2.1.5   | Conclusion                                 |     |

|   | 5.3 | Doub    |           | eneration circuit                          |     |

|   | 5.4 |         | _         | ·                                          |     |

| 6 | Conclusion and perspectives                           | 175            |

|---|-------------------------------------------------------|----------------|

| A | Appendix: Photodetectors description  A.1 GenerationA | 181            |

| В | Appendix: Cables model  B.1 Cables model              | <b>189</b> 189 |

| C | Appendix: PCB making                                  | 193            |

# **List of Figures**

| 1.1  | Electrical circuit of a basic sampler                                                                                                 | 1          |

|------|---------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.1  | Plot representing the jitter impact on ENOB (Effective Number Of Bits) as a function of input frequency for ADCs (extracted from [1]) | 3          |

| 2.2  | Plot representing jitter evolution over the years                                                                                     | 4          |

| 2.3  | Schematic diagram of Taylor's optical A/D converter (taken from [2])                                                                  | 6          |

| 2.4  | Cisco forecasts for global IP traffic growth                                                                                          | 7          |

| 2.5  | Silicon Photonics market for the 2013-2023 period forecast according                                                                  |            |

|      | to Yole Développement                                                                                                                 | 8          |

| 2.6  | Silicon indirect gap versus GaAs direct gap (from [3])                                                                                | 9          |

| 2.7  | Silicon crystal structure: face-centered cubic                                                                                        | 9          |

| 2.8  | Band theory, adapted from [4]                                                                                                         | 12         |

| 2.9  | Lattice constant of the main semiconductor materials used in photo-                                                                   |            |

|      | detection [4]                                                                                                                         | 13         |

| 2.10 | Barrier heights in eV for metal-semiconductor barriers                                                                                | 14         |

| 2.11 | Plots of different photodiode structures                                                                                              | 14         |

| 2.12 | Germanium dangling bonds                                                                                                              | 16         |

| 2.13 | Parallel plate Ge junction photodiodes with different silicon doping                                                                  |            |

|      | configurations                                                                                                                        | 17         |

|      | Bandwidth optimization techniques summary                                                                                             | 18         |

| 2.15 | Ways of coupling light into a lateral germanium-on-silicon photode-                                                                   | 10         |

| 2.16 | tector                                                                                                                                | 19         |

|      | Plot of the different techniques used to reduce metal contact loss                                                                    | 20         |

| 2.17 | Plot of the different techniques used to reduce loss in the contact doping regions                                                    | 20         |

| 2 18 | Responsivity state-of-the-art table                                                                                                   | 21         |

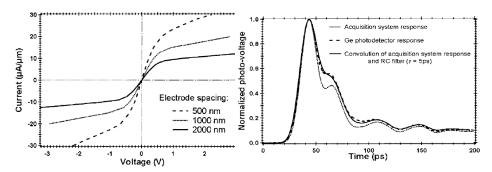

|      | Dark current and pulsed light response of Ge MSM photoconductor                                                                       | <b>4</b> 1 |

| 2.17 | in [5]                                                                                                                                | 22         |

|      | III [0]                                                                                                                               |            |

| 3.1  | Plots of germanium band diagram and absorption coefficient                                                                            | 24         |

| 3.2  | Plots of different coupling techniques for integrated Ge photo-                                                                       |            |

|      | detectors                                                                                                                             | 26         |

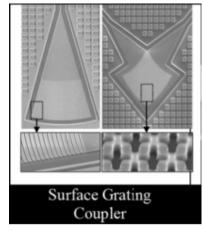

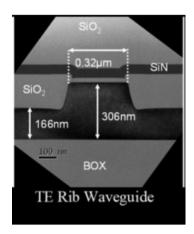

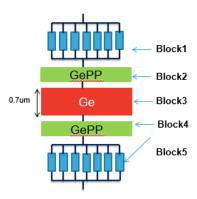

| 3.3  | Photo-conductors integration scheme                                                                                                   | 27         |

| 3.4  | Plots of SGC and 1330nm single mode waveguide of STMicroelec-                                                                         |            |

|      | tronics PIC25G technology                                                                                                             | 28         |

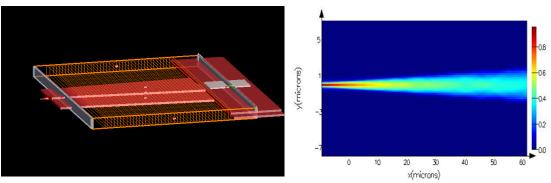

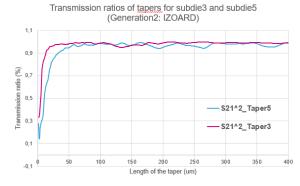

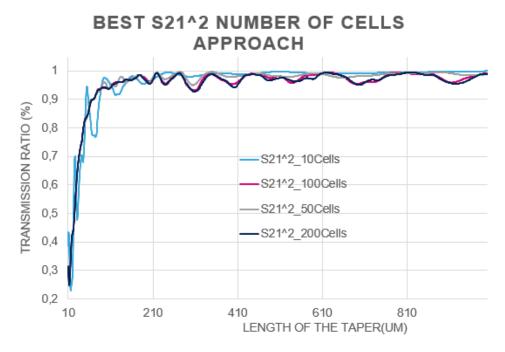

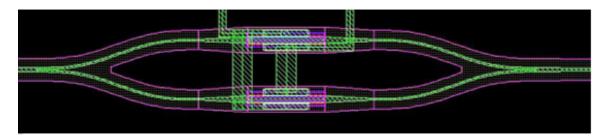

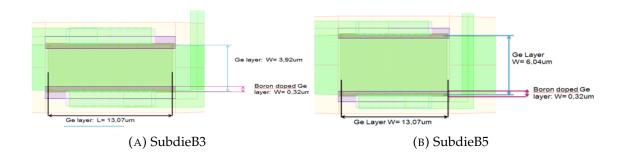

| 3.5  | Eigenmode solver simulation to optimize taper's length for Subdie3 and Subdie5                                                        | 29         |

| 3.6  | Effect of taper length on the transmission ratio calculations                                                                         | 30         |

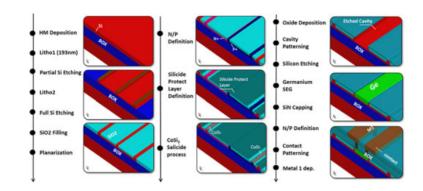

| 3.7  | PIC25G photoconductors/photodiodes fabrication process flow                                                                           | 30         |

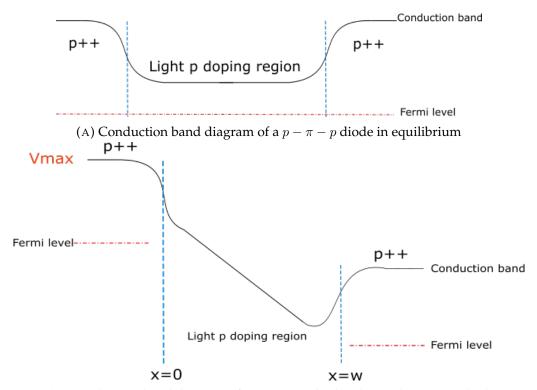

| 3.8         | Plots of $p - \pi - p$ diode conduction band diagrams in equilibrium         |    |

|-------------|------------------------------------------------------------------------------|----|

|             | and when voltage is applied                                                  | 31 |

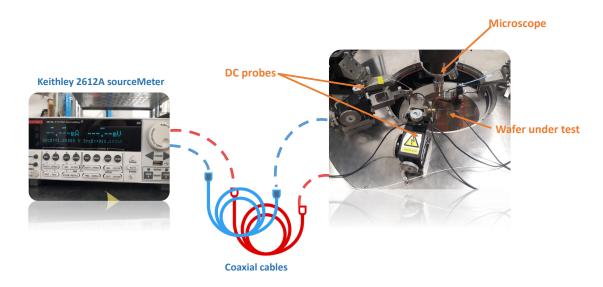

| 3.9         | Dark current measurement setup at CEA-Leti                                   | 33 |

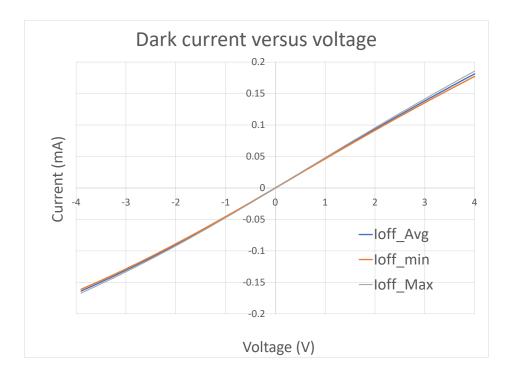

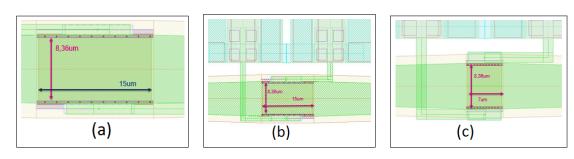

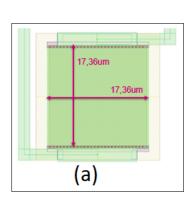

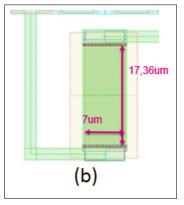

| 3.10        | Dark current versus voltage for a W=17.36 $\mu$ m × L=7 $\mu$ m              | 34 |

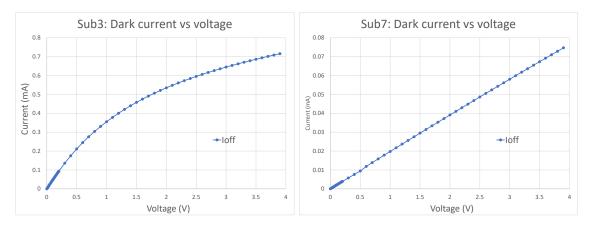

| 3.11        | Plots of dark current versus velocity saturation model for two sub-          |    |

|             | dies with different geometries                                               | 34 |

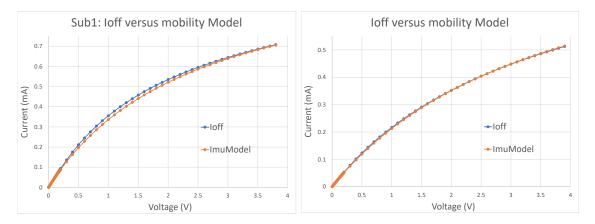

| 3.12        | Plots of measured dark current versus velocity saturation model for          |    |

|             | two subdies with different geometries                                        | 37 |

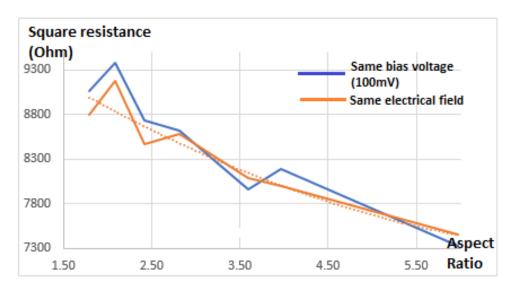

| 3.13        | Square resistance dependency on aspect ratio                                 | 38 |

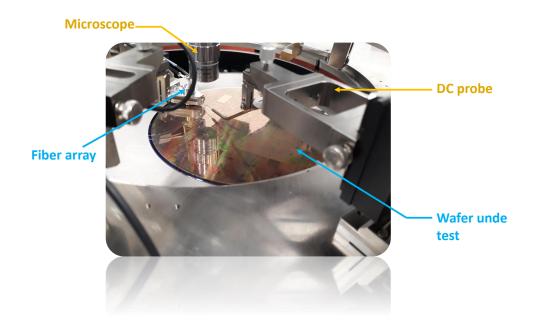

|             | ON measurements test bench                                                   | 39 |

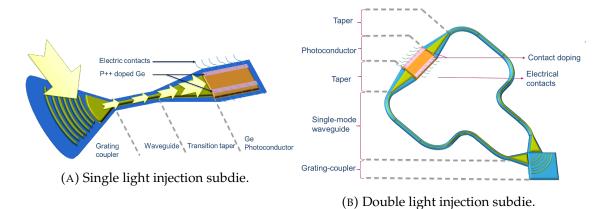

|             | Plots of the different light injection patterns                              | 39 |

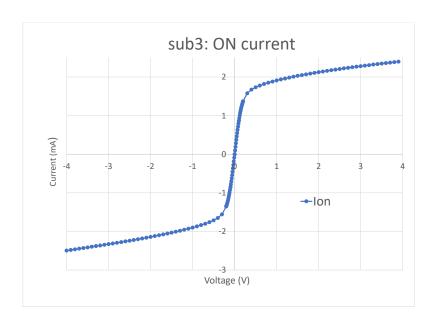

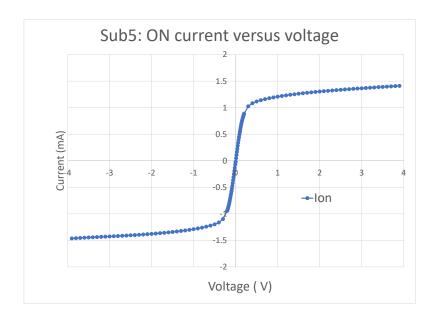

|             | Plots of ON current versus voltage for two subdies with different            |    |

|             | geometries                                                                   | 41 |

| 3.17        | Measured ON current versus velocity saturation model for a $5.4\mu m \times$ |    |

|             | $13\mu m$ subdie                                                             | 42 |

| 3.18        | ON current versus conductance saturation model for a $5.4\mu m \times$       |    |

|             | $13\mu m$ subdie                                                             | 43 |

| 3.19        | Electrical model of the photo-conductor                                      | 44 |

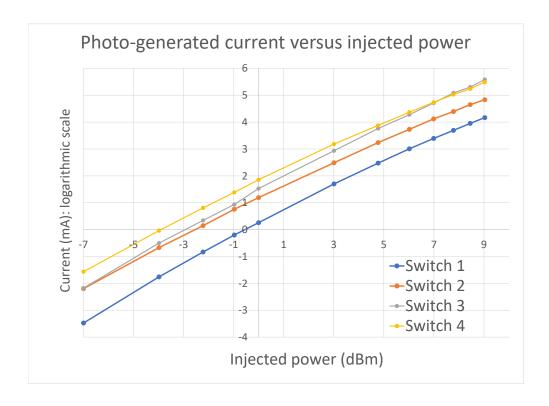

|             | Photo-generated current versus the injected power for different              |    |

|             | subdie geometries                                                            | 44 |

| 3.21        | Photo-generated current versus the injected optical power with               |    |

|             | logarithmic scale for Subdie7 and Subdie11 at 50mV DC bias                   | 47 |

| 3.23        | Photo-generated current versus the injected power at $\lambda = 1330nm$ .    | 49 |

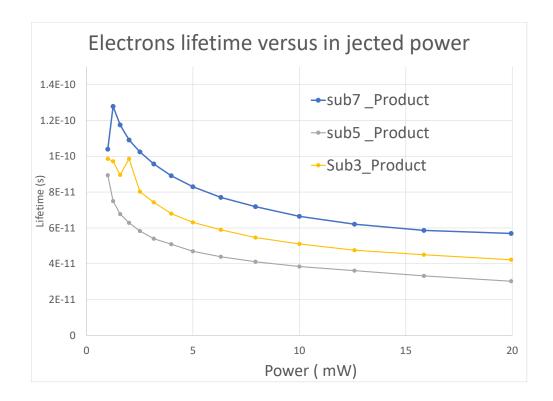

|             | Lifetime versus power for three subdies with different geometries            | 50 |

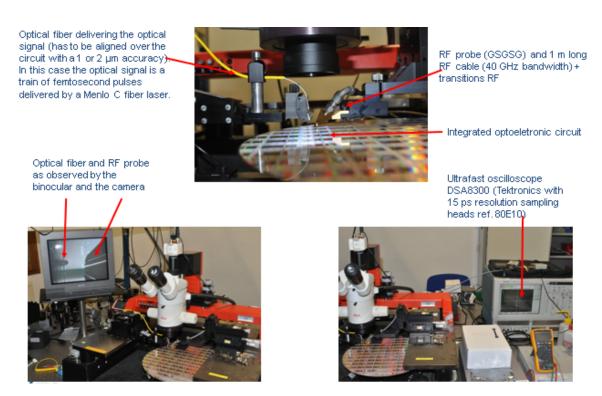

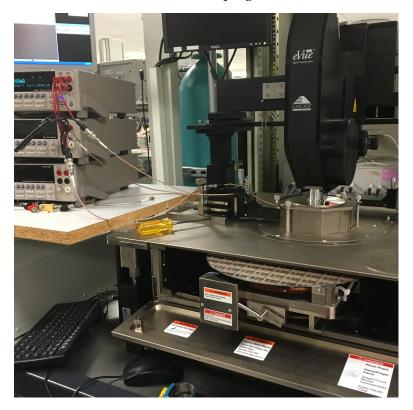

|             | Pictures of the test bench used to simulate the pulsed response of           |    |

|             | the photoconductors.                                                         | 51 |

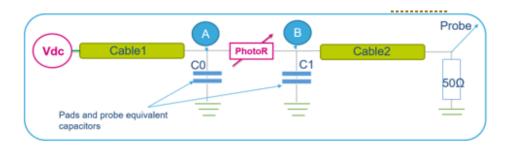

| 3.26        | Electrical scheme of the pulsed measurements test bench                      | 52 |

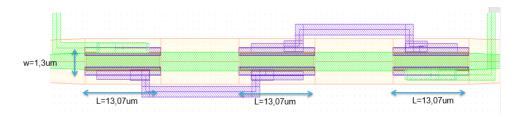

| 3.27        | subdie2 (generationB) layout scheme                                          | 52 |

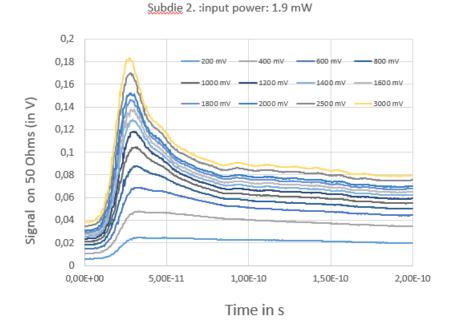

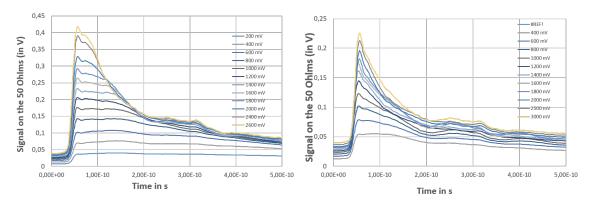

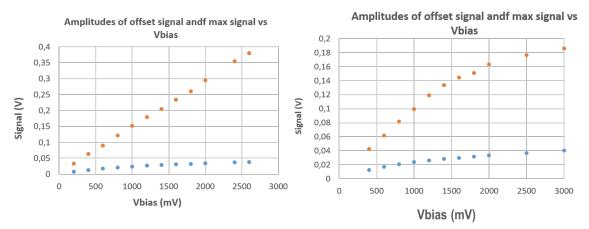

|             | Pulsed response of subdie2(generationB) for different biasing volt-          |    |

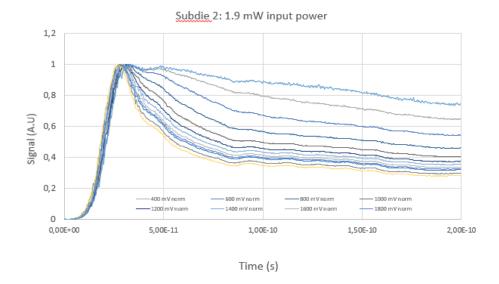

|             | ages                                                                         | 53 |

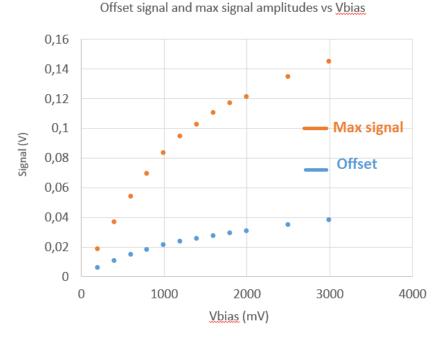

| 3.29        | Offset signal and max signal vs Vbias for subdie2 (generationB)              | 53 |

| 3.30        | Normalized pulsed response of subdie2 for different biasing voltages         | 54 |

|             | Pulsed response and normalized pulsed response of subdie2 under              |    |

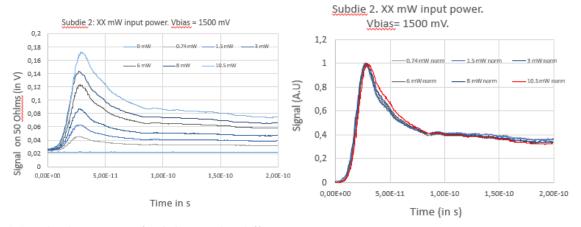

|             | different optical power levels                                               | 55 |

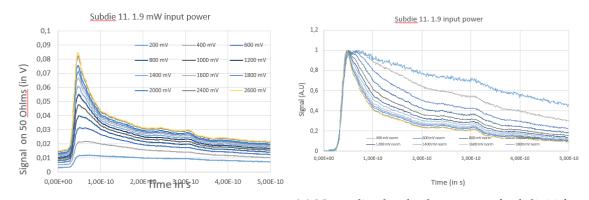

| 3.32        | Pulsed response and normalized pulsed response of subdie11 under             |    |

|             | different optical power levels                                               | 55 |

| 3.33        | Electrical scheme of the pulsed measurements test bench                      | 56 |

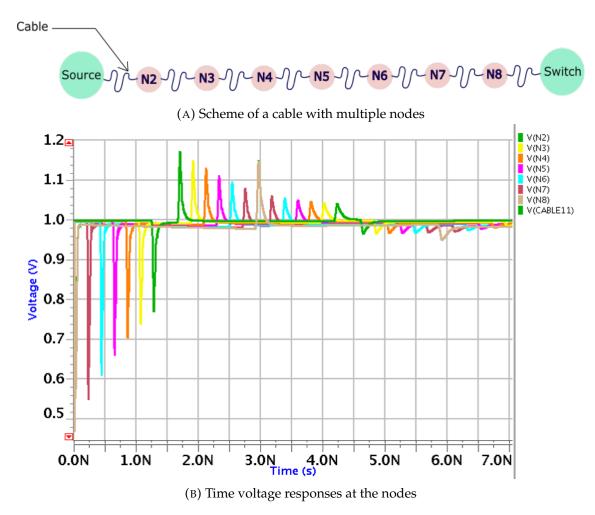

| 3.34        | Time response of a cable, at different nodes, to a current call at the       |    |

|             | switch                                                                       | 57 |

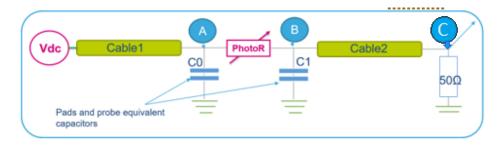

| 3.35        | Electrical scheme of the test bench                                          | 58 |

| 3.36        | Signals evolution in nodeA, nodeB and nodeC                                  | 59 |

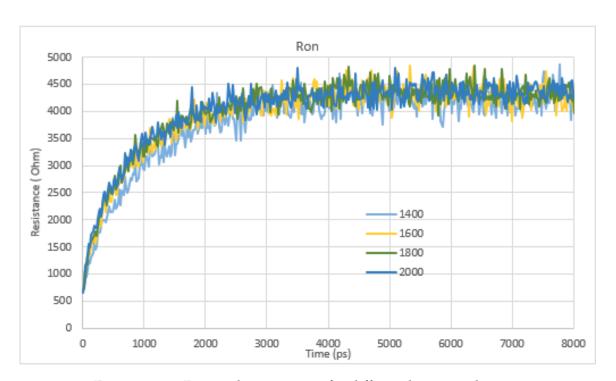

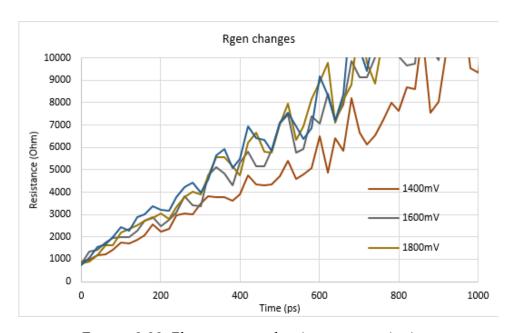

| 3.37        | Ron evolution in time for different biasing voltages                         | 60 |

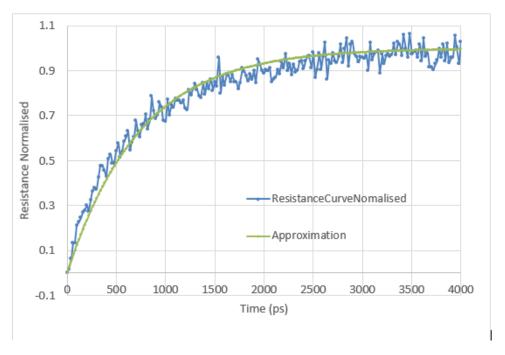

| 3.38        | Photo-generated resistance curve in time                                     | 61 |

|             | Exponential approximation of the Ron curve                                   | 62 |

| 4.1         | Floatrical circuit of a basic sampler                                        | 66 |

| 4.1         | Electrical circuit of a basic sampler                                        | 66 |

| <b>+.</b> ∠ | Effect of jitter at the sampler output                                       | U/ |

| 4.3  | Jitter power density distribution over frequency                             | 68  |

|------|------------------------------------------------------------------------------|-----|

| 4.4  | Jitter measurement circuit scheme                                            | 69  |

| 4.5  | Plots of the test bench operation                                            | 69  |

| 4.6  | Sampler output signal in the case of low $R_{off}$                           | 70  |

| 4.7  | Sampler output signal in the case of different $R_{off}$ values              | 71  |

| 4.8  | Illustration of the impact of effect1 on the sampled signal                  | 72  |

| 4.9  | ADC jitter FOM survey by Boris Murmann                                       | 73  |

| 4.10 | Exponential photo-conductor view                                             | 75  |

|      | Overview of the photo-conductor                                              | 76  |

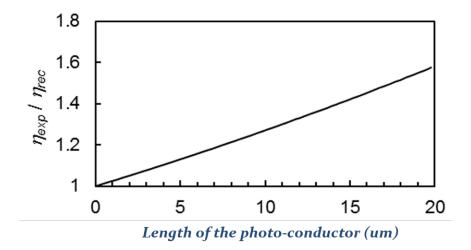

| 4.12 | Evolution of $\eta_{exp}$ on $\eta_{rect}$ over the photo-conductor length   | 78  |

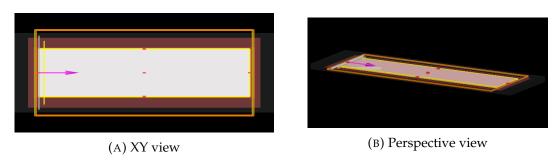

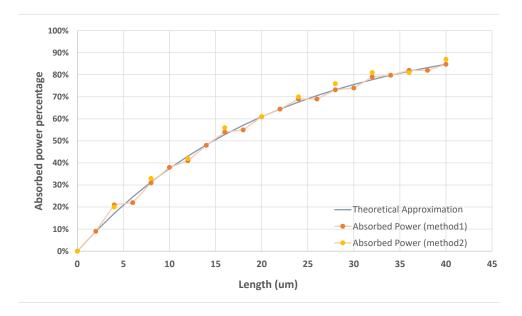

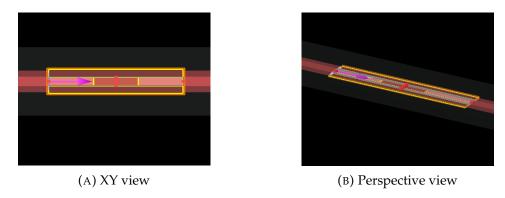

| 4.13 | Views of method1 simulations on Lumerical FDTD solver                        | 80  |

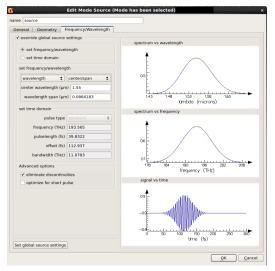

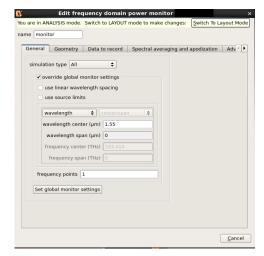

| 4.14 | Method2 simulation settings                                                  | 81  |

|      | Views of method2 simulations on Lumerical FDTD solver                        | 81  |

| 4.16 | Absorbed power percentage over propagation length                            | 82  |

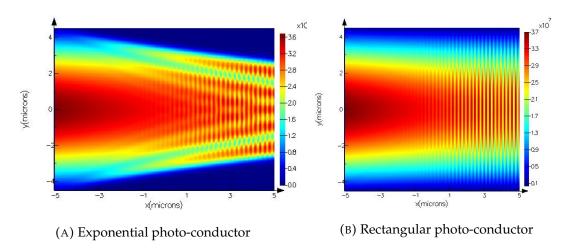

|      | Optical electrical field distribution for the exponential and rectan-        |     |

|      | gular photo-conductors                                                       | 83  |

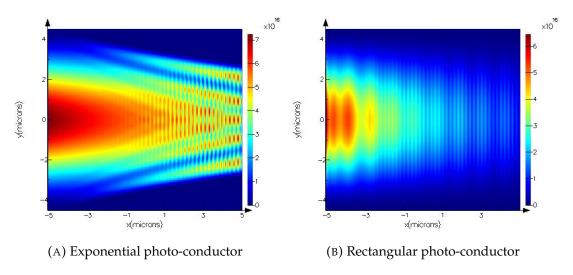

| 4.18 | Absorbed power density for the exponential and rectangular photo-            |     |

|      | · · · · · · · · · · · · · · · · · · ·                                        | 83  |

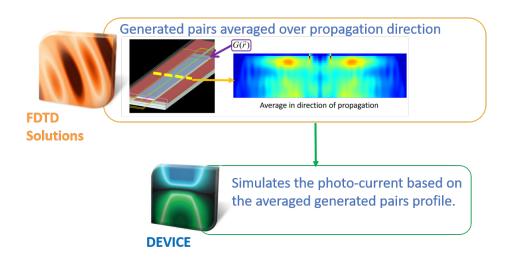

| 4.19 | Lumerical optoelectronic simulation protocole                                | 84  |

| 4.20 | plots of the new work flow applied to an exponential device                  | 85  |

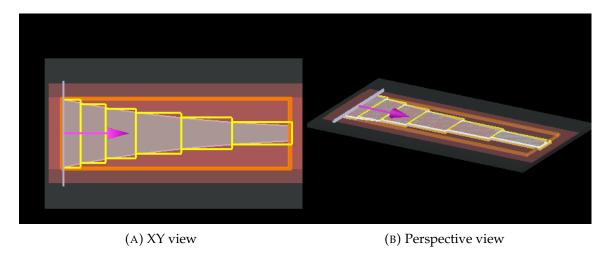

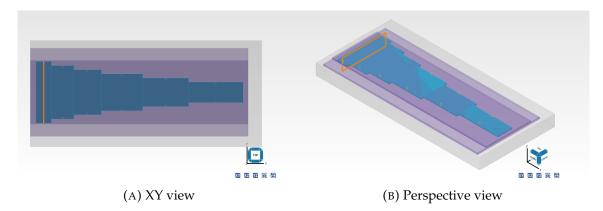

| 4.21 | Plots of the exponential photo-conductor in for DEVICE simulations           | 86  |

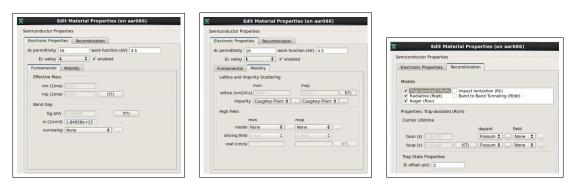

| 4.22 | Germanium DEVICE model                                                       | 86  |

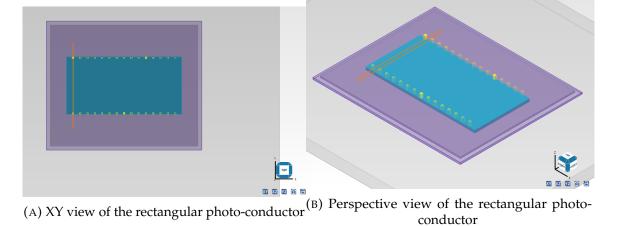

| 4.23 | Plots of the rectangular photo-conductor in for DEVICE simulations           | 86  |

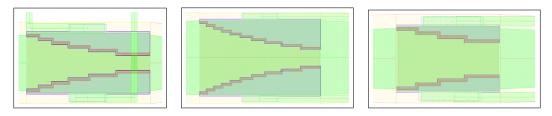

| 4.24 | Exponential photo-conductor: implemented versus theoretical shape            | 87  |

| 4.25 | GenerationB subdie8 break down                                               | 87  |

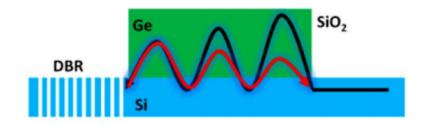

| 4.29 | Upper injection photo-conductor scheme                                       | 89  |

| 4.30 | Optimized germanium photodiode using a DBR, courtesy image                   |     |

|      | from [120]                                                                   | 89  |

| 4.31 | Upper injection photo-conductor scheme                                       | 90  |

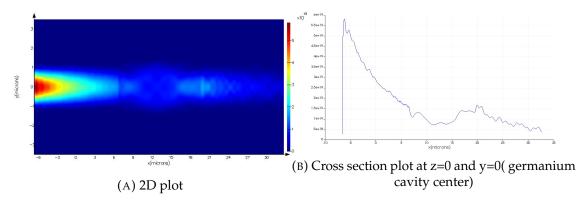

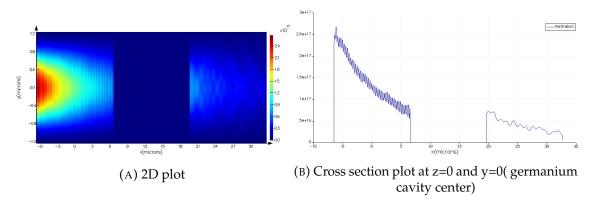

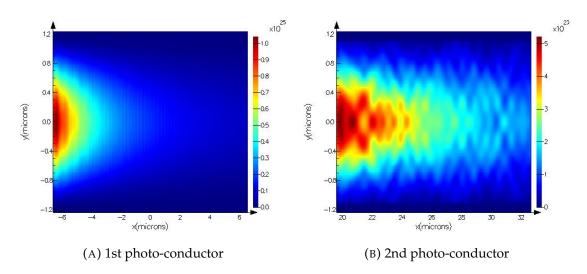

| 4.32 | Views of the FDTD simulation of the series geometry                          | 91  |

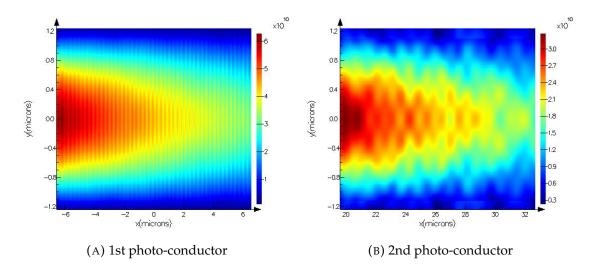

| 4.33 | Power density plot in the series photo-conductors geometry                   | 92  |

| 4.34 | Optical electrical field distribution in the two photo-conductors in         |     |

|      | series                                                                       | 93  |

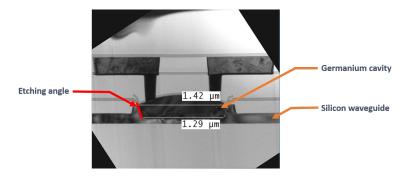

| 4.35 | Cross section of a germanium photo-conductor                                 | 93  |

| 4.36 | Absorbed power density across the series photo-conductors                    | 94  |

| 4.37 | Generation rate in the two photo-conductors in series                        | 94  |

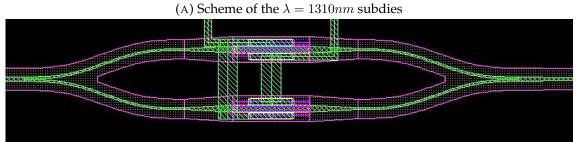

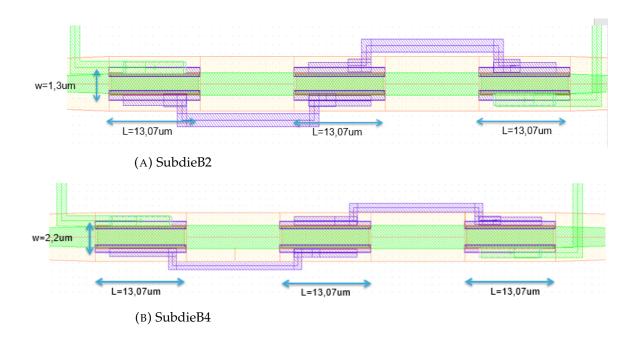

| 4.38 | Scheme of subdie2 from Generation2 circuits                                  | 95  |

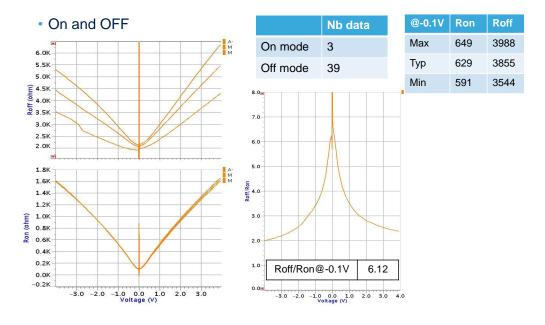

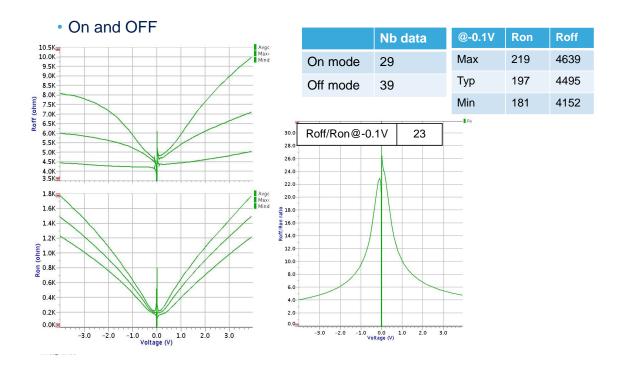

| 4.39 | Geneartion2's subdie4 off measurements and CW on measurements                | 95  |

| 4.40 | Measurement results of subdie11 under continuous light                       | 96  |

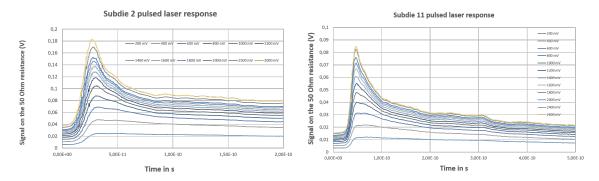

| 4.41 | Plots of subdie2 and subdie11 pulsed laser measurements                      | 97  |

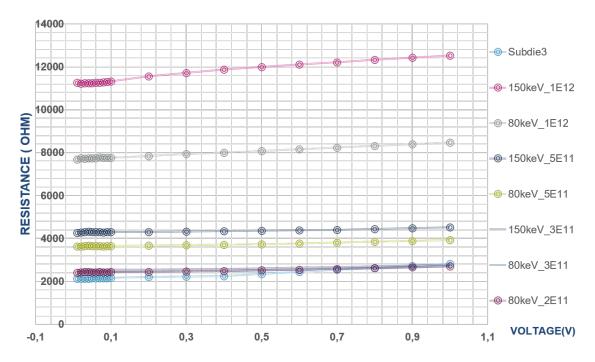

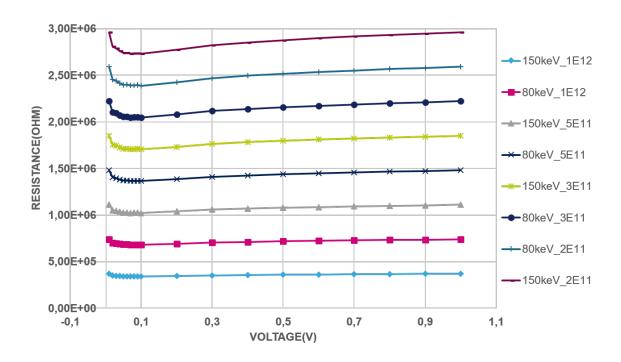

|      | Subdie $R_{off}$ for different voltages and different counter-dopings .      | 98  |

|      |                                                                              | .00 |

| 4.44 | Subdie $R_{off}$ for different voltages and different counter-dopings . 1    | .00 |

|      | Summary of the $R_{off}$ on $R_{on}$ ratios obtained with different counter- |     |

|      | doping combinations                                                          |     |

| 4.46 | Workaround circuit concept illustrated                                       |     |

| 4.47 | Clock generation circuit scheme                                   | 102 |

|------|-------------------------------------------------------------------|-----|

| 4.48 | Clock generation operation process                                | 103 |

| 4.49 | Clock circuit scheme                                              | 104 |

| 4.50 | Clock signal versus time                                          | 105 |

|      | Effect of a steep and a slow slope on jitter                      |     |

|      | Pulse shaping circuit diagram                                     |     |

| 4.53 | Basic biasing circuit                                             | 109 |

|      | Clock circuit with connections explicited                         |     |

|      | Scheme of the 1V stage design                                     |     |

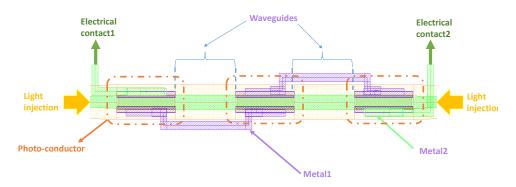

|      | Photo-conductors integration scheme                               |     |

| 4.57 | New sampler circuit scheme with input Buffer included             | 114 |

|      | Input buffer electrical scheme                                    |     |

|      | Final sampler scheme                                              |     |

| 4.60 | Optical scheme implemented to feed the clock generation circuit   |     |

|      | with $10\%$ of the laser pulse energy                             | 116 |

| 4.61 | Optical scheme implemented to feed the clock generation circuit   |     |

|      | with the non-absorbed leftover energy                             | 117 |

| 4.62 | Single photonic clock circuit                                     |     |

| 4.63 | Plots of double clock operation process                           | 120 |

| 4.64 | Double photonic clock circuit operation                           | 121 |

|      | Double photonic clock circuit layout                              |     |

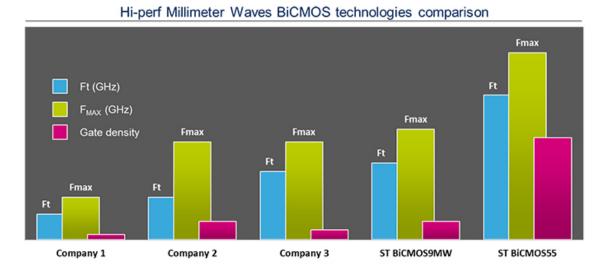

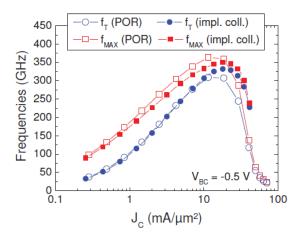

| 5.1  | STMicroelectronics BiCMOS technologies performance evolution      |     |

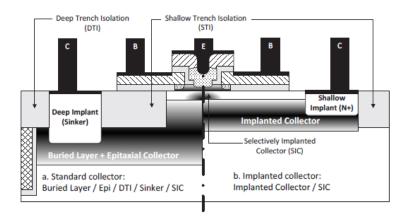

| 5.2  | Illustration of SiGe HBT different collector variations           | 126 |

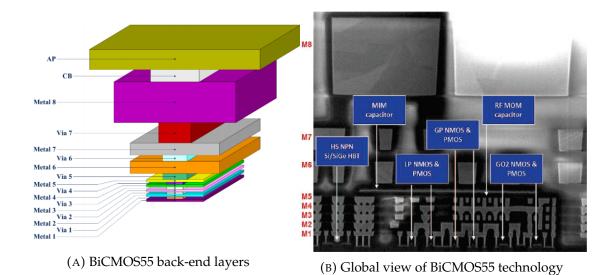

| 5.3  | Sketches of STMicroelectronics BiCMOS55 technology features       |     |

| 5.4  | Input buffer integration scheme                                   |     |

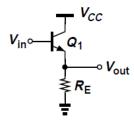

| 5.5  | Emitter follower basic scheme                                     |     |

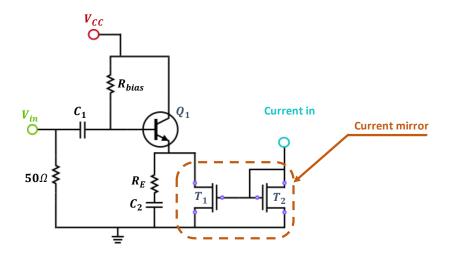

| 5.6  | Input buffer updated circuit scheme                               |     |

| 5.7  | Input buffer small signal model                                   |     |

| 5.8  | Input buffer small signal model with approximated component value |     |

| 5.9  | Emitter follower small signal circuit below and above $f_{\pi}$   |     |

| 5.10 | Emitter follower small signal circuit below and above $f_{x_2}$   | 135 |

|      | Input Buffer small signal model evolution with frequency          | 136 |

| 5.12 | Transit and maximum oscillation frequency variation with the cur- |     |

|      | rent density in BiCMOS55 HS-HBT                                   |     |

|      | Input buffer final circuit scheme                                 |     |

|      | Input buffer test circuit scheme                                  |     |

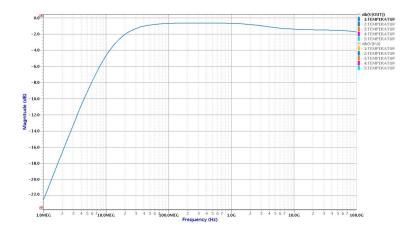

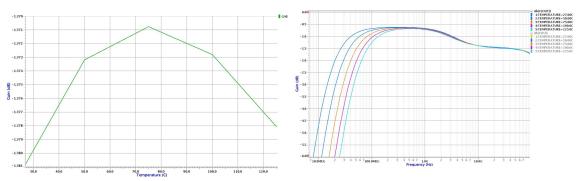

|      | Input buffer AC response                                          |     |

|      | Input buffer gain versus temperature                              |     |

|      | Input buffer AC response                                          |     |

|      | Input buffer layout                                               |     |

|      | Basic biasing circuit                                             |     |

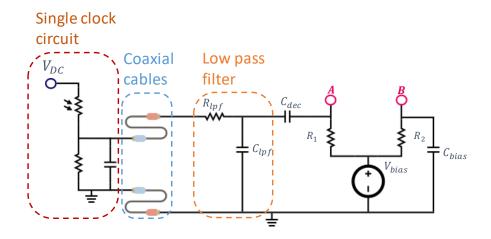

|      | Clock circuit with connections explicited                         |     |

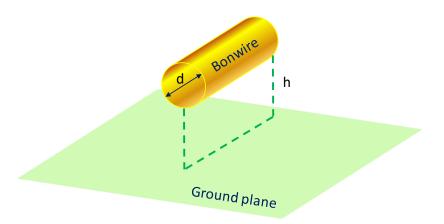

|      | Pad model                                                         |     |

|      | Wire bond inductance estimation scheme                            |     |

|      | Wire bonding connections and mutual inductance illustrated        |     |

| 5.24 | Small signal model of the complete circuit of biasing             | 151 |

| 5.25 | Transfer function of $\frac{V_{AB}}{V_A}$                              | 152 |

|------|------------------------------------------------------------------------|-----|

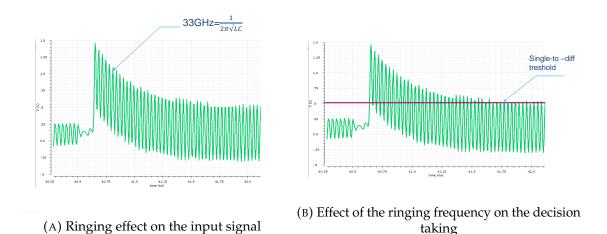

|      | Transfer function of the biasing stage                                 |     |

|      | Zoom in the effect of ringing frequency on biasing stage               |     |

|      | Biasing circuit: version 2                                             |     |

|      | New biasing stage circuit scheme                                       |     |

|      | New single to differential stage                                       |     |

|      | Cherry Hooper basic circuit                                            |     |

|      | First Cherry Hooper stage                                              |     |

|      | The second Cherry-Hooper stage                                         |     |

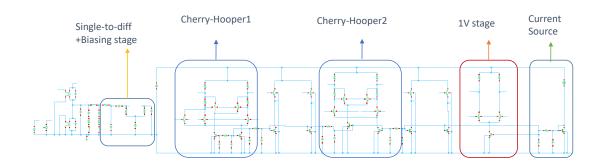

|      | Final design of the pulse-shaping circuit                              |     |

|      | Optical clock electrical model                                         |     |

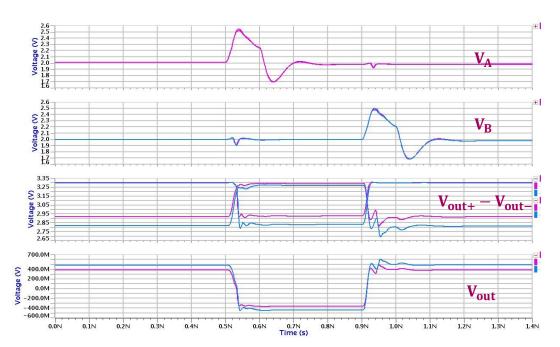

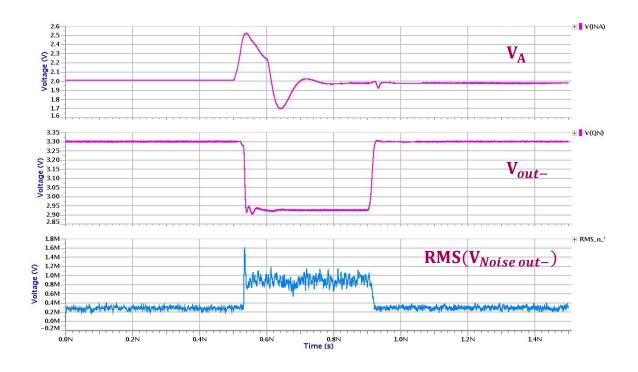

|      | Signal evolution through the pulse-shaping stage                       |     |

| 5.38 | Jitter performance across the pulse shaping stage                      | 166 |

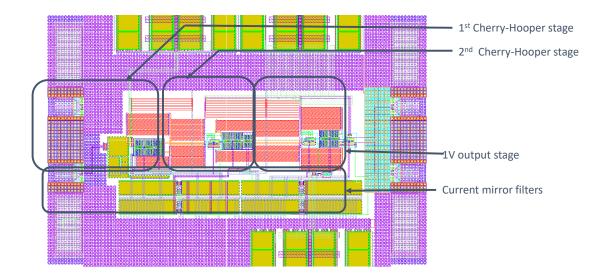

|      | Final layout of the pulse-shaping circuit                              |     |

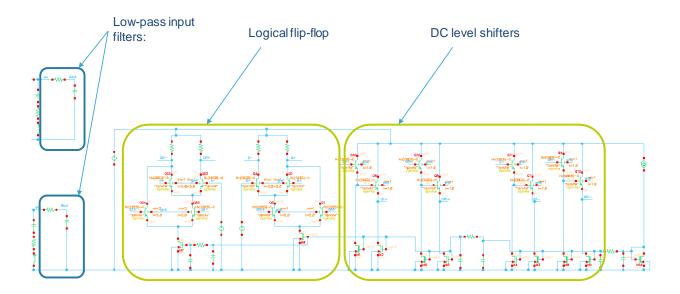

|      | Design of the latch circuit                                            |     |

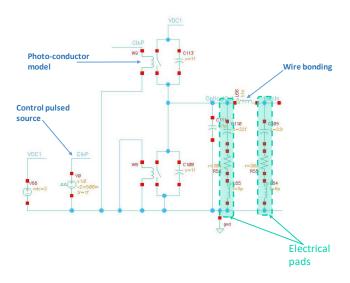

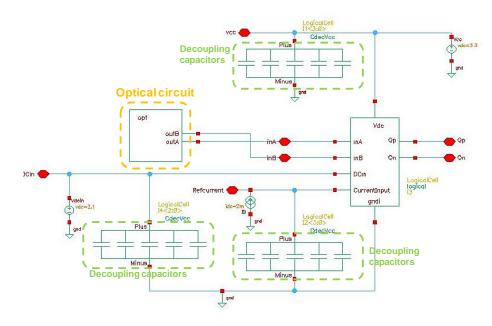

|      | Logical circuit test bench                                             |     |

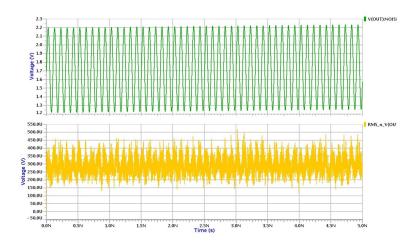

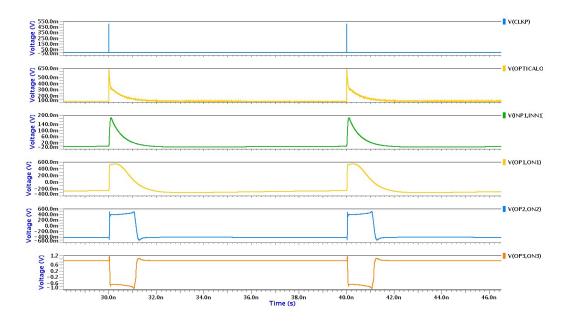

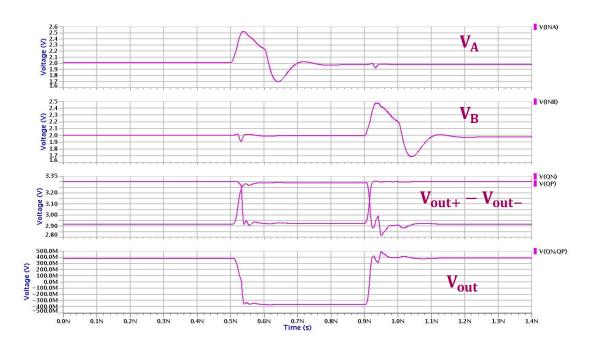

|      | Plots of the logical circuit output signals versus temperature         |     |

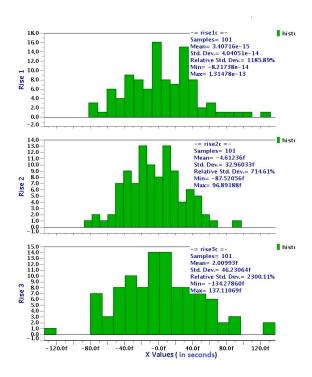

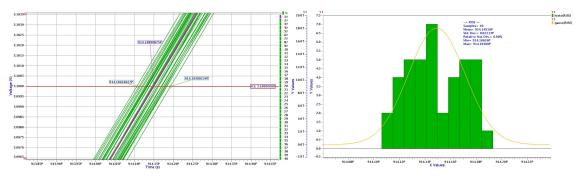

|      | Noise simulation on double clock output signal over 40 simulations     |     |

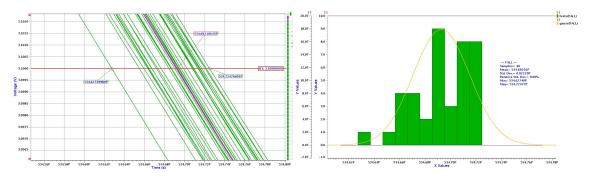

|      | Plots of double clock rising edge curves for the 40 simulations        |     |

|      | Plots of double clock falling edge curves for the 40 simulations       |     |

| 5.46 | Layout of the logical circuit of the double photonic clock             | 171 |

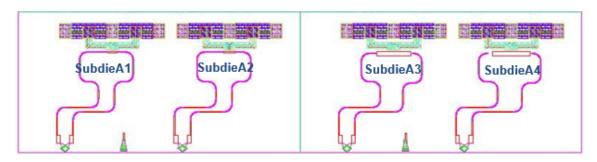

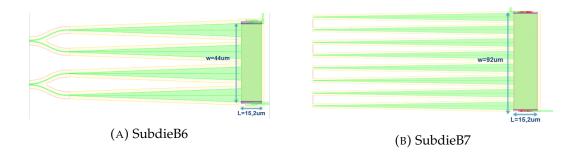

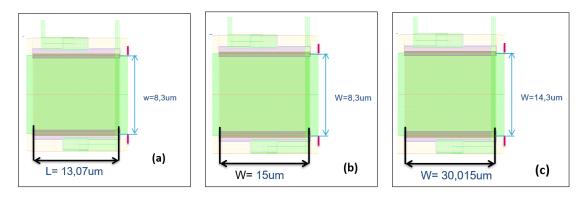

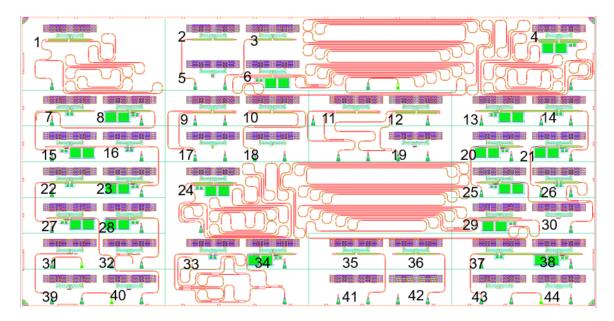

| A.1  | Overview of the first generation subdies                               | 179 |

|      | Plots of Germanium band diagram and absorption coefficient             |     |

|      | Build-up of subdieA1 and subdieA3                                      |     |

|      | SubdieA2 and SubdieA4 layout scheme                                    |     |

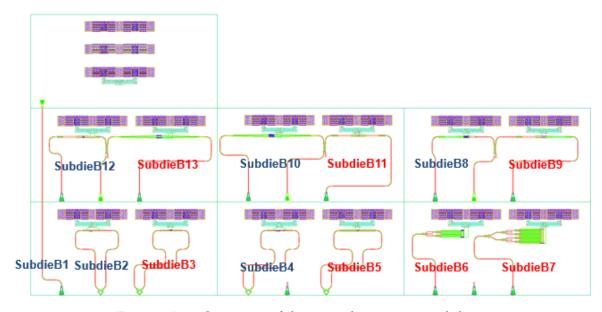

| A.5  | Overview of the second generation subdies                              |     |

|      | Layout scheme of respectively: subdieB9, subdieB11 and subdieB13       |     |

|      | Layout scheme of respectively: subdieB8, subdieB10 and subdieB12       |     |

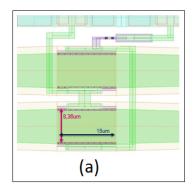

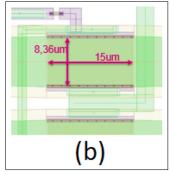

|      | (a): SubdieB8, (b): deconstruction of subdieB8 (c): subdieB8 dimen-    |     |

|      | sions                                                                  | 184 |

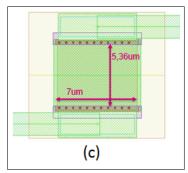

| A.12 | SubdieB10 and SubdieB12 dimensions                                     | 184 |

| A.13 | GenerationC overview                                                   | 185 |

|      | Single injection subdies: (a): SubdieC2, (b): SubdieC35 (c): SubdieC36 |     |

|      | No light injection subdies:(a): SubdieC5, (b): SubdieC17 (c): Sub-     |     |

|      | dieC18                                                                 | 186 |

| A.16 | Double injection subdies:(a): SubdieC1, (b): SubdieC12 (c): SubdieC19  |     |

| D 1  |                                                                        | 100 |

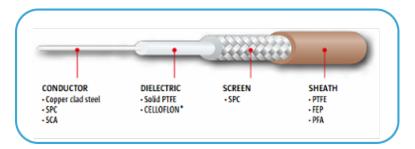

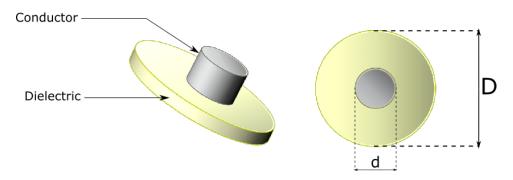

| B.1  |                                                                        |     |

| B.2  | Cable layers composition                                               |     |

| B.3  | Cable layers composition                                               | 19U |

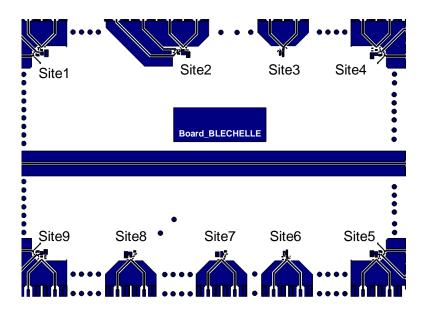

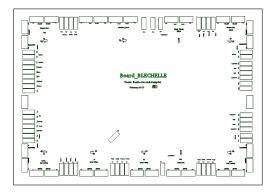

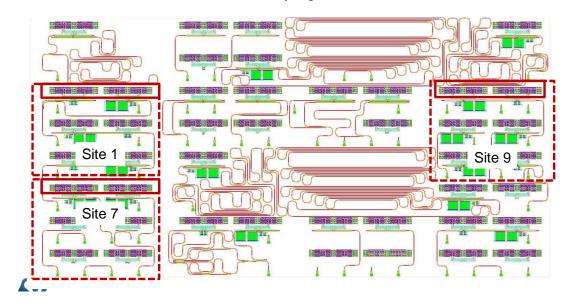

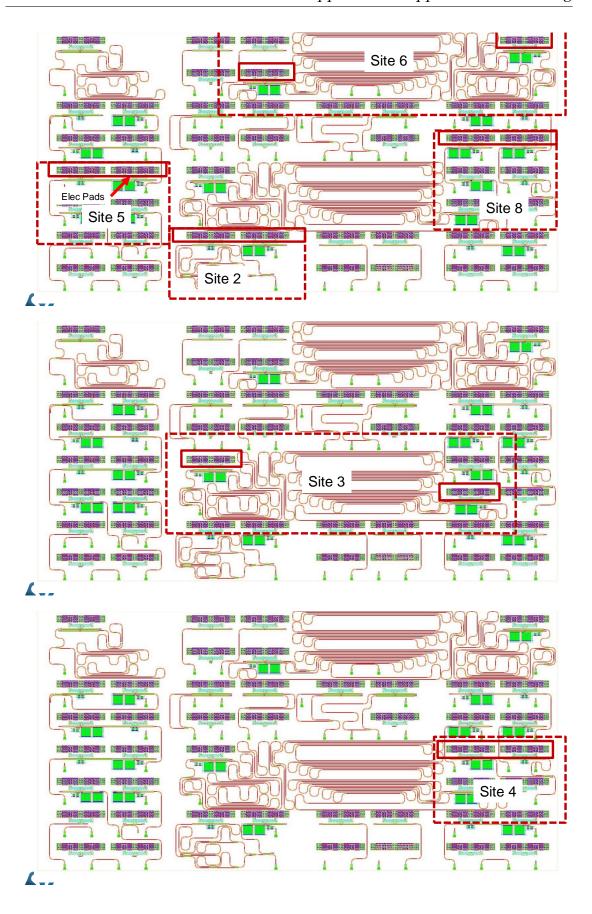

| C.1  | PCB top layer with the nine sites depicted                             | 193 |

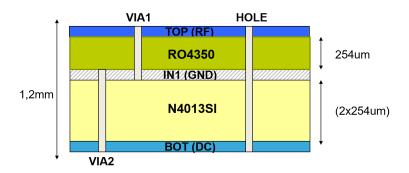

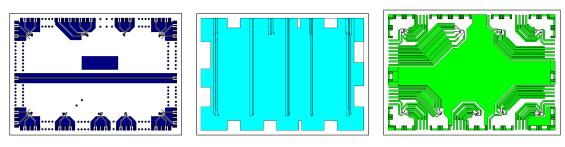

| C.2  | PCB layers stack-up detailed                                           |     |

| C.3  | Plots of the three copper layers in the PCB stack-up respectively:     |     |

| •    | top layer, intermediate layer and bottom layer                         | 194 |

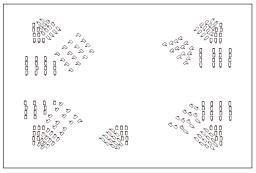

| Plots of the three metal interconnection layers in the PCB stack-up  |                                                                                                                                                                                                      |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| respectively: Via1 layer, Via2 layer and Hole layer                  | 195                                                                                                                                                                                                  |

| Plots of the two silkscreen layers in the PCB stack-up respectively: |                                                                                                                                                                                                      |

| silkscreen1 layer (Top layer print), silkscreen2 layer (Bottom layer |                                                                                                                                                                                                      |

| print)                                                               | 195                                                                                                                                                                                                  |

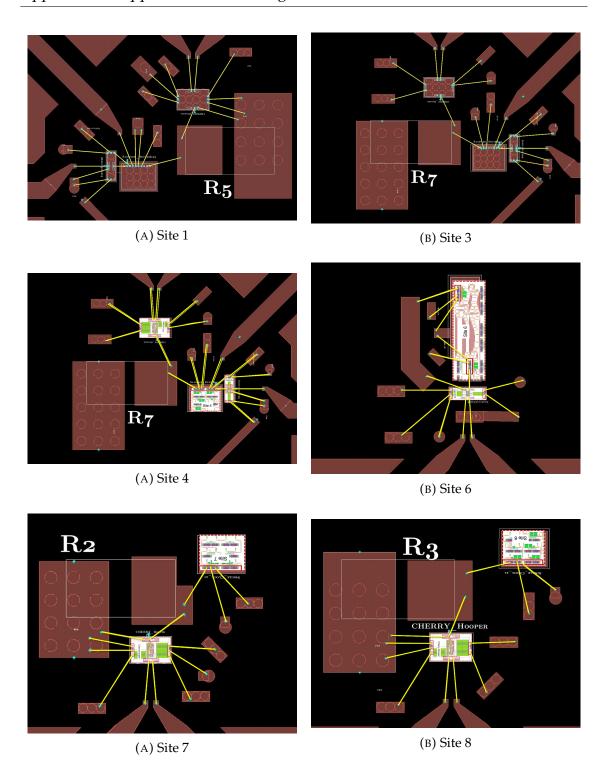

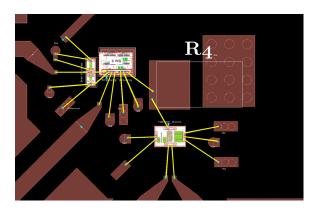

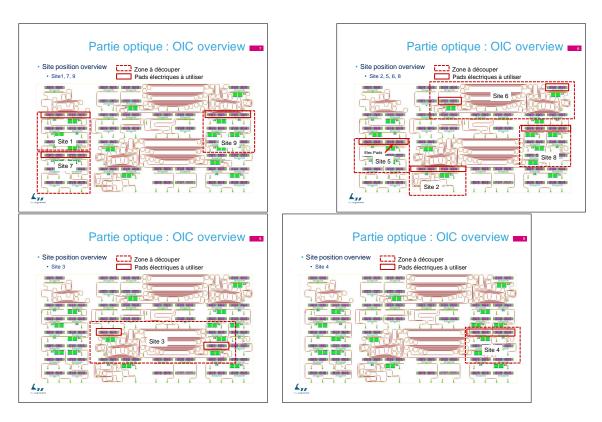

| Site 9                                                               | 198                                                                                                                                                                                                  |

| Plots of the three metal interconnection layers in the PCB stack-up  |                                                                                                                                                                                                      |

| respectively: Via1 layer, Via2 layer and Hole layer                  | 198                                                                                                                                                                                                  |

|                                                                      | respectively: Via1 layer, Via2 layer and Hole layer Plots of the two silkscreen layers in the PCB stack-up respectively: silkscreen1 layer (Top layer print), silkscreen2 layer (Bottom layer print) |

# Chapter 1

## General introduction

As the world becomes more and more connected, the need for higher data throughout becomes increasingly urgent. This implies more creativity from designers to come up with higher bandwidth circuits and faster pace clocks to drive them.

However, the traditional microelectronics clock circuits fail short to fulfill the ever increasing need for higher sampling frequencies because of their inherent noise. The latter renders the sampled data altogether unusable and therefore hinders the efforts towards higher streams of data.

A fairly promising new technology field, integrated photonics, may bring an end to this problem. Indeed, when it comes to pulsed lasers, a "not that new" technology, the optical pulses clocking features a very low noise compared to its microelectronics counterpart. Indeed, even for the industrialized pulsed lasers, the clock noise, namely the jitter, is 5 times lower than the best microelectronics clock, yet the latter is only cited in literature and no industrial clock circuit was ever able to exhibit its performance.

With this idea in head, we try in this thesis to demonstrate the feasibility of a sampler with ultra low jitter using an external pulsed laser with ultra-low jitter (11fs).

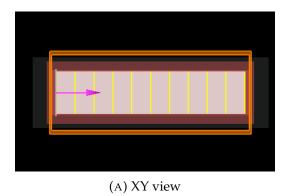

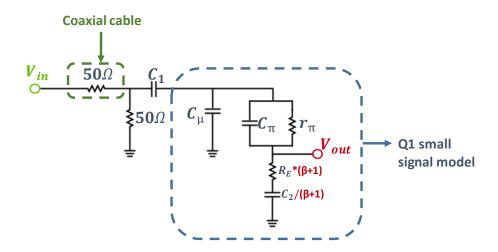

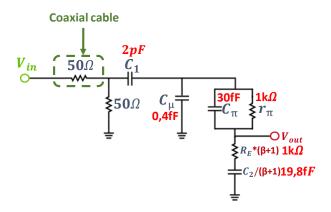

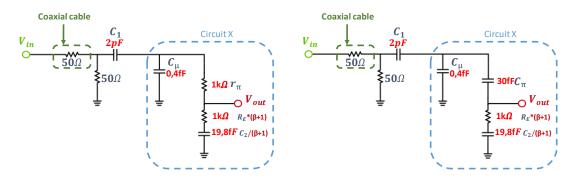

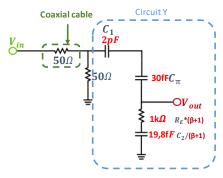

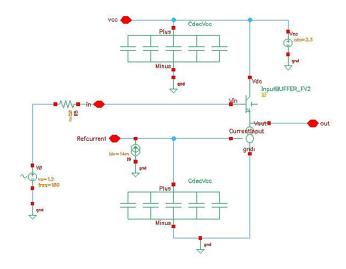

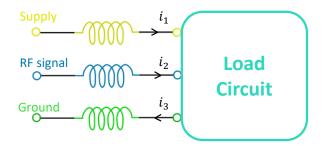

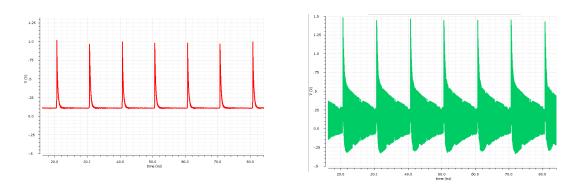

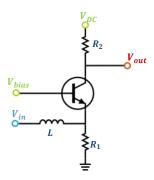

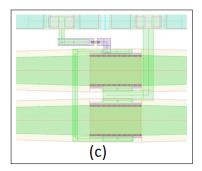

FIGURE 1.1: Electrical circuit of a basic sampler

The basic idea we start with is that of a classical microelectronics sampler, where the switch is replaced by a photo conducting material driven by the pulsed laser as depicted in fig.1.1.

As illustrated in the scheme, the switch plays the role of a variable resistance that is driven by the pulsed laser. This component counterpart in integrated photonics is a photo-conductor and is rarely used in nowadays photonics circuit.

Indeed, most of the optical interconnects are built with photo-diodes as light receivers. This choice is mainly due to the fact that the response of a photo-diode is directly proportional to the light intensity it receives while a photo-conductor current depends both on the light intensity and the electrical field that is applied on it. Therefore, photo-diodes fit more on interconnect circuits where the data is mainly coded by light, which is not what we are heading for in this application. This also explains why the literature is very poor when it comes to photo-conductors while it is very impressive for photo-diodes.

The photo-conducting material that we use is germanium. This is mainly due to the ease of integrating germanium in silicon-based technologies. Germanium absorption spectrum also fits perfectly with the laser wavelength (1550nm).

This thesis outline is the following:

In chapter 3, we will explain in details the photo-conductivity phenomenon. We will also discuss Germanium as our photo-conducting material and describe its properties. Finally we will present the photo-conducting circuits that we have designed, discuss their results and try to explain the behaviors they exhibit.

In chapter 4, we will present the different solutions that we intend to design. The circuits will be featured in this chapter only with their system view and generic design. We will explain each solution and present its optical and electrical components.

In chapter 5, the circuits will be presented in great details. We will explain the design choices that we made and illustrate the results of the simulations and of the final circuits, when available.

# **Chapter 2**

## **Introduction:**

## 2.1 Jitter in communications

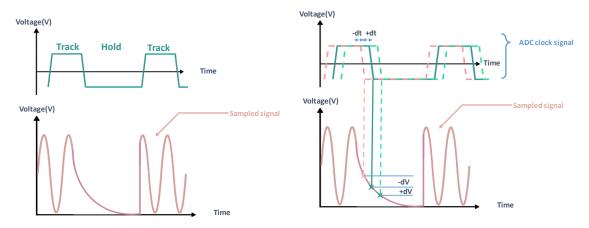

In a reception chain, the analog-to-digital conversion (ADC) block role is highly sensitive. Errors during the conversion phase carry over the total receiver block chain performance and are hardly recovered afterwards. These errors originate possibly from the quality of the comparators, the accuracy of the comparison references, the linearity of the track and hold block but also from the accuracy of the sampling timing.

FIGURE 2.1: Plot representing the jitter impact on ENOB ( Effective Number Of Bits) as a function of input frequency for ADCs ( extracted from [1])

Jitter is a deviation of a given clock signal from the ideal equivalent clock output. This implies, in the case of an ADC, that the signal is sampled at the wrong time, which amounts to having an error at the sampled signal.

When the frequency of the signal is high, the signal changes very rapidly, which means that a small timing error yields a consequent error at the sampled signal. This is why jitter affects and limits ADCs performance significantly at higher frequencies, see Fig.2.1.

### 2.1.1 Jitter in electronic clocks

The electronics-based clocks have inherent sources of noise, mainly thermal noise, that make it hard to go under a certain limit of jitter in room temperature operation. Indeed, the best electronic ADCs, to our knowledge, deliver jitter levels of 60 to 80 fs in the 100-400MHz frequency range [6].

FIGURE 2.2: Plot representing jitter evolution over the years

The plot in Fig.2.2 shows the jitter evolution at any frequency taken from literature as it was described in Walden's report <sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>Source:https://converterpassion.wordpress.com/2012/07/30/adc-performance-evolution-jitter

### 2.1.2 Jitter in photonics

Photonics offers an alternative solution to the jitter bottleneck problem thanks to mode-locked pulsed lasers.

These lasers exhibit nowadays, even in their commercial form, very low values of jitter (15fs).

The physical phenomena that lay behind lasers noise depends on their structure and operation process. However, in most cases, timing jitter in lasers is limited by quantum noise but is mainly dominated by the laser resonator vibrations and drift [7] [8].

The advantage that mode-locked lasers offer compared to electronic clocks has been rapidly spotted in the 70's and used in sampling and quantizing electrical signals with different methods as explained in the hereafter section.

### 2.1.3 Photonic ADCs

In his review [9], Valley defines a photonic ADC as a device with an *analog RF electronic input and a digital electronic output that uses photonics in the digitization process*. This is the definition that we will use in this section as well.

Although the first paper relating an RF signal sampling by optical sampling dates back to 1970 [10], the purpose of the paper was just to measure the duration of the optical pulses. The idea of effectively using the optical signal as a clock on an electrical circuit was first introduced by Auston with his paper on electro-optical switching in 1975 [11]. Wright et al designed, around the same period (1974), an optical quantization scheme [12].

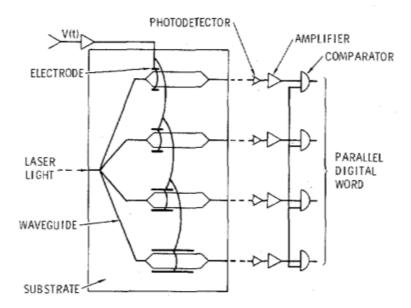

Later on, Taylor would combine the idea of Wright and Kuizenga to design the first all photonic ADC see fig.2.3 (optical sampling and quantification) [2], [13]. From that moment on, the research focused on improving Taylor's scheme [14–23].

There are generally four classes of photonic ADCs [9]:

#### • Class 1:

Photonic assisted ADC: this first category includes circuits in which a photonic device is added to an electronic ADC to improve its performance. The overall trend is to use optical switches made of photo-diodes to drive track and hold circuits [24], [25].

### • Class 2:

ADCs in which sampling is achieved optically but quantification is done electrically .

The basic device for this class of ADCs is a mode-locked laser that feeds an

FIGURE 2.3: Schematic diagram of Taylor's optical A/D converter (taken from [2])

electro-optic modulator. The latter is driven by the input RF signal. The output of the modulator, i.e. the modulated optical pulses are then detected by a photodiode. The electrical signal at the output of the photodiode is eventually quantized through an ADC. Many researches were driven around this class of photonic ADCs since the 90's [26–34].

#### • Class 3:

ADCs in which sampling is achieved electrically but quantification is done optically.

The RF input signal is in this case sampled through a track and hold electrical circuit. The output code is then used to vary the wavelength of a semiconductor laser.

Many research works have been conducted around this theme [35–40].

#### • Class 4:

All-optical ADCs for electrical input signals: the signal is sampled and quantized optically.

The basic scheme for this class is the Taylor's one[13]. The works that have been conducted later on are just improvements of it [16],[17],[18],[19]. The system operates as follows: the RF signal drives 4 modulators that receive pulses from a laser. The modulators are of different lengths, with ratios of 2, as they represent the bits. The output of each modulator is injected into a photodetector (a high speed photodiode) then the obtained electrical signal goes through comparators to conclude on the final code.

We will now describe the technology of such photonic ADCs.

### 2.2 Silicon Photonics

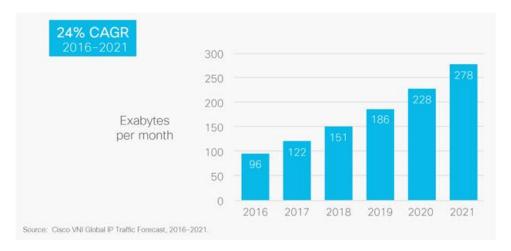

In the social network era we are living, the internet traffic is increasing with an unprecedented pace: Cisco forecasts the global IP traffic to triple from 2016 to 2021 with an increase from 96 EB <sup>2</sup> per month to 278 EB per month, see Fig.2.4.

FIGURE 2.4: Cisco forecasts for global IP traffic growth

This tendency means that the bandwidth necessary to process and vehicle this data must follow the same pace. Optical technology is then proposed as a solution to counter the problem of bandwidth congestion in inter-data centers communications and again as a solution to drive the bandwidth inside the data centers.

As a matter of fact, the web giants (Google, Apple, Facebook, Amazon and Microsoft) are pushing the market towards new transceivers photonic technology to cover up their needs for data management. Some of them are already developing their own optical data centers technology in partnership with semiconductor manufacturers: Facebook and Microsoft have indeed started to work on theirs with Intel.

However, as the communications become faster and denser, the interconnect problem let alone the heat dissipation issue and the high cost of denser circuits, becomes a real bottleneck to achieve further bandwidth gains. Silicon Photonics, as a silicon-based optical technology, comes out as a new approach to the problem, offering both the cost-friendly silicon integration advantage as well as the possibility of overcoming the interconnect problem.

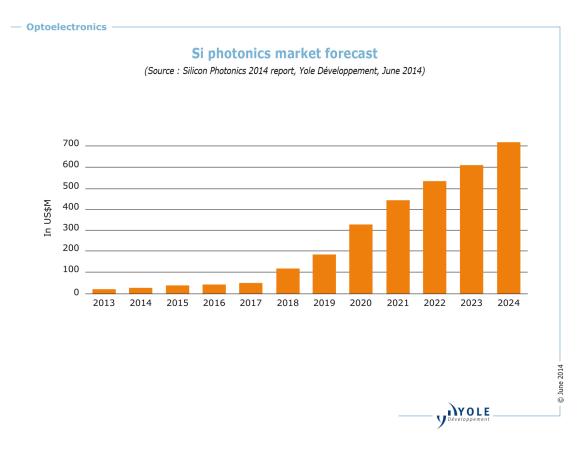

This tendency is even clearer when we see the forecasts for silicon photonics market that are expected to grow exponentially in the forthcoming decade, see Fig2.5.

$<sup>^2</sup>$ EB stands for ExaByte and is equal to  $10^{18}$  Bytes

FIGURE 2.5: Silicon Photonics market for the 2013-2023 period forecast according to Yole Développement.

## 2.2.1 A brief history of Silicon Photonics

In the mid-eighties, many research centers launched projects around using light as a means of communication in an integrated circuit rather than electrical charge. Therefore, the choice of silicon as the main material for an optical integrated technology was obvious: not only is it inexpensive and very well studied and understood, it also provides a very easily native oxide, perfect electrical and thermal properties and a strong optical confinement on the optical wavelengths [41].

However, the silicon photonics research did not kick start right away as it was held back by two main problems [42]:

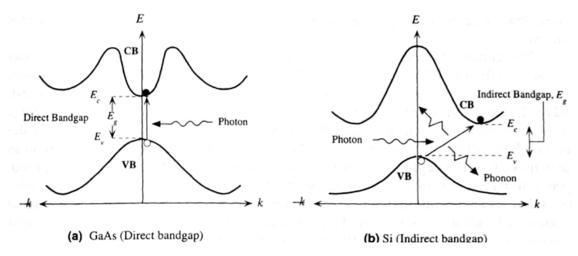

Silicon has an indirect gap [43]. At that time, it was claimed that laser operation (negative absorption) in indirect bandgap semiconductors is nearly impossible [44]. This was backed by the belief that the small optical gain that could be achieved through phonon-aided band-to-band transitions will be largely counterpoised by free carrier absorption.

The up said means that designing light sources in a silicon based technology would be very challenging and call for nontraditional methods, unlike other

semi-conducting materials, see Fig.2.6. This is mainly why the III-V semiconductors were of choice to make lasers in the early years of silicon photonics.

FIGURE 2.6: Silicon indirect gap versus GaAs direct gap (from [3])

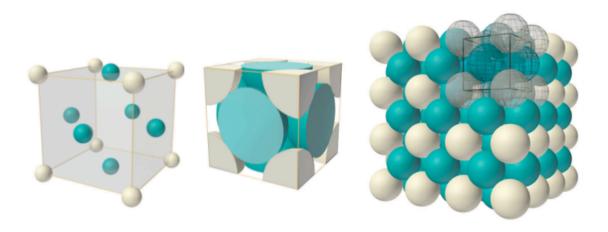

FIGURE 2.7: Silicon crystal structure: face-centered cubic

The crystal structure of silicon being a face-centered diamond cubic, or a

"two interpenetrating face-centered cubic" [45] which can be seen in Fig.2.7,

<sup>3</sup> there is no Pockels effect in silicon. This amounts to say that there is no

linear electro-optical effect in silicon and thus no traditional way to design

modulators such as the ones manufactured at that time in III-V materials.

Silicon emission remained for a long time the Holy Grail of Silicon Photonics, [46] [47], [48]. The interest given to this problem is not overrated, indeed resolving it would make it possible to bypass the heat dissipation problem and the limitations due to interconnect between Silicon Photonics circuits and ICs [49].

$<sup>^3</sup> The \ drawings \ are \ from: \ http://perso.neel.cnrs.fr/xavier.blase/OLDER/ssp_Blase.pdf$

The fundamental claim that the indirect bandgap of Silicon was enough to make the laser operation impossible was quickly evicted by researches [50] [51] [52], showing that the optical gain in Silicon can overcome the recombination rate and therefore a laser operation is possible.

Research on other semi-conducting materials, namely on InGaAsP/InP, had just proven that the refractive index of a semiconductor waveguide is impacted significantly by injection of carriers (about  $10^{18}$  per cm<sup>3</sup>) from a forward-biased p-n junction [53]. Soref and Lorenzo used the same principle later on to prove the possibility of making a silicon-based modulator [54].

Starting from the latter publication, Silicon Photonics took off and became an independent research field in itself. The heavy investments that were drawn to Silicon Photonics contributed largely to its spawning in the nineties.

## 2.3 State of the art: photodetectors

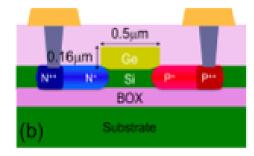

The first germanium on silicon photodetector was published in 1984 by Luryi et al.[55]. But, just like photonics, the research around these photodetectors became very intensive in the late 1990's. This is mostly due to the spawn of germanium on silicon epitaxy [56], [57],[58] [59] with CVD <sup>4</sup> technique that replaced the MBE <sup>5</sup> that was used before.

Early germanium photodetectors were mostly vertical PN or PIN photodiodes (see 2.3.1.3) as they were designed for a surface illumination [60]. Later on, lateral PIN junction designs became the preference for designers for high speed applications especially for 1550nm devices since they require longer absorption lengths [61].

In this section, we will mainly focus on high speed germanium photodetectors as they are the ones we will use in our circuit.

### 2.3.1 Photodiodes

Photodiodes can be in general described as photosensitive components that exhibit an intrinsic potential barrier or a space-charge region. In order to understand the space-charge concept, we may first introduce Fermi levels in semiconductors.

<sup>&</sup>lt;sup>4</sup>CVD stands for Chemical Vapor Deposition

<sup>&</sup>lt;sup>5</sup>MBE stands for Molecular Beam Epitaxy

### 2.3.1.1 Fermi level

Consider a semiconductor material: electrons are distributed between conduction band and valence band. Fermi energy is a hypothetical energy level that stands for the maximum energy an electron has in a given material at zero Kelvin. It can also be defined as an energy level that is 50 % likely to be filled with electrons at a given temperature [62][63].

In less savvy terms, the Fermi level qualifies the electrons distribution in a semiconductor: for example the closer it is to the conduction band, the more electrons are in the conduction band compared to valence band and vice-versa. It is worth noting that the Fermi level of an intrinsic semiconductor changes with doping: it increases towards conduction band in the case of an N-doping (which increases the electrons density in the conduction band) and decreases towards valence band with a P-type doping.

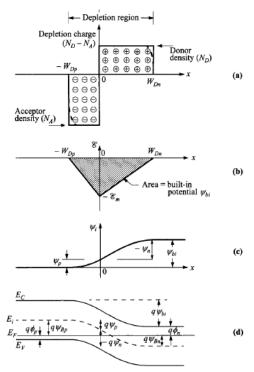

### 2.3.1.2 Space-charge region

Now given the upsaid, say we bring together two portions of a semiconductor with opposite doping types. From the previous discussion, we know that the Fermi levels of these portions are not the same. This amounts to say that the density of electrons in the conduction band at one side (N-doping side) is higher than in the other side. The electrons then move from one side to another in order to even out their distribution, because the Fermi level of the whole device must be constant whatever the location in the device. The holes do the same, but in the opposite direction.

The movement of these electrons and holes, which is a diffusion current, is as said triggered by the difference in their density along the semiconductor.

While the electrons an holes move from one side to another, they create two adjacent opposite sign regions. This means that they create a voltage accross the device, which is called the built-in voltage, see fig2.8, the electrical field that is relative to this voltage is called the intrinsic field.

The electrons and holes continue to move from one side to another until the density difference attractive force is counterpoised by the built-in voltage. The space-charge region that is then governed by the intrinsic field is a depletion region, i.e a semiconductor region that is depleted of free charge carriers [64].

### 2.3.1.3 Photodiode types

Photodiodes, as said earlier, are based on the space-charge region. The latter can be engineered in two different ways:

• Different dopings in the same semiconductor: this is the case that was discussed early on.

Fig. 1 Abrupt p-n junction in thermal equilibrium. (a) Space-charge distribution. Dashed lines indicate corrections to depletion approximation. (b) Electric-field distribution. (c) Potential distribution where  $\psi_{bi}$  is the built-in potential. (c) Energy-band diagram.

FIGURE 2.8: Band theory, adapted from [4]

• Different materials: by using two different materials, we have the same outcome of two different doping types since the Fermi level is generally not the same.

The second category of photodiodes, namley heterojunction photodiodes, can be engineered in two different ways that mead to two different uses of photodiodes:

- Semiconductor heterojunction photodiodes: these are made of two different semi-conducting materials.

- Metal-Semiconductor heterojunction photodiodes: in this case, the energy gap is between the semiconductor Fermi level and the metal Fermi level.

#### **Semiconductor heterojunction photodiodes** :

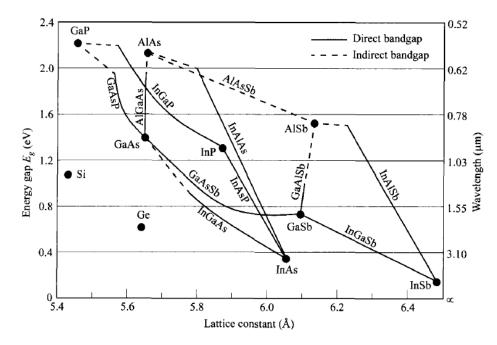

Semiconductor hetero-junctions have one constraint: the two semiconductors must have small lattice mismatch (see Fig.2.9), otherwise the hetero junction operation would be hampered by the dislocations due to the lattice mismatch [65].

FIGURE 2.9: Lattice constant of the main semiconductor materials used in photo-detection [4]

The hetero-junction energy offset is generally emphasized through doping the two semiconducting materials. In photonics, there are many well known and studied elemental and compound heterojunction sets [66] such as: n-Si/p-SiGe, n-ZnSe/p-GaAs, p-AlGaAs/n-GaAs, p-Ge/n-GaAs, n-InGaAs/n-InP, p-InAlAs/n-InGaAs, p-GaN/n-InGaN, and p-AlGaN/n-InGaN.

#### Semiconductor-metal heterojunction photodiodes :

In the case of metal-semiconductor heterojunctions, the set of used materials is chosen according to the work function of the metal compared to the Fermi level of the semiconductor [67] [68]. Here again the energy gap is emphasized through doping and the most used pairs are as depicted in Fig.2.10.

Overall, in the up-said discussion, we considered the case of a PN photodiode type for the semiconductor hetero and homo-junctions cases and an MS photodiode for the metal-semiconductor case. However, this kind of photodiodes is in reality very little used in the industry of photo-detection. Indeed, since the detection area in a photodiode is the space-charge region, then, PN photodiodes offer very small responsivity (photogenerated current per injected optical power) notwithstanding the high parasitic junction capacitance that goes to decrease the bandwidth of the photodetector. One may argue that using smaller doping values would yield a wider space-charge region, but this has another side effect which is increasing the photodiode contact resistance.

The alternative photodiode structure is a PIN photodiode and an MSM photodiode:

|                            | Ag   | Al   | Au   | Cr   | Ni   | Pt   | W    |

|----------------------------|------|------|------|------|------|------|------|

| Φ <sub>M</sub> (in vacuum) | 4.3  | 4.25 | 4.8  | 4.5  | 4.5  | 5.3  | 4.6  |

| n-Ge                       | 0.54 | 0.48 | 0.59 | 3    | 0.49 |      | 0.48 |

| p-Ge                       | 0.5  |      | 0.3  |      |      |      |      |

| n-Si                       | 0.78 | 0.72 | 0.8  | 0.61 | 0.61 | 0.9  | 0.67 |

| p-Si                       | 0.54 | 0.58 | 0.34 | 0.5  | 0.51 |      | 0.45 |

| n-GaAs                     | 0.88 | 0.8  | 0.9  | 0    |      | 0.84 | 0.8  |

| p-GaAs                     | 0.63 |      | 0.42 |      |      |      |      |

FIGURE 2.10: Barrier heights in eV for metal-semiconductor barriers

FIGURE 2.11: Plots of different photodiode structures

- P-I-N photodiode: is simply regular PN junction but with an intrinsic region in the middle, see Fig.2.11b. This addition makes the detection area bigger and acts as an extension to the space-charge region.

- MSM photodiode: is a photodiode made out of two metal-semiconductor junctions (two Schottky junctions). It has generally very high responsivity and bandwidth but features high dark currents as the metal-semiconductor barrier is generally not very high.

There is another class of photodiodes that is pretty close to PINs but serves another purpose: the avalanche photodiode. The latter is constructed exactly as a PIN but with and extra layer: a multiplication layer. The concept of an APD photodiode is to increase the velocity of photo-generated charge carriers to the point where they generate a new electron-hole pair through impact ionization [69],[70]. The newly created ones go through the same process again, so that the originally photo-generated pair creates multiple others.

This structure is widely used for sensitive detection applications [71] and exhibits great results compared to the other germanium-based silicon photonics

active component. The latter is mainly due to the fact that germanium APD structures rely mainly on their multiplication region performances, but since it is grown over silicon [72], the outcome is not hampered by lattice mismatch of excess noise in germanium as in other devices.

We will only discuss in the forthcoming state-of-the-art section the advances in high speed germanium photo-diodes because they are the closest to our application case.

#### 2.3.1.4 State of the art

Before we dive in the state-of-the-art of the high speed germanium photo-diodes, we will first explain the measured metrics related to a photo diode performance, i.e.. dark current, responsivity and bandwidth. State-of-the-art optimization of each one of these metrics will be described and a final state-of-the-art summary will be given where performance records are detailed.

#### Dark current:

Dark current is the current of the photodiode in the absence of light. In a photodiode design, the aim is to reduce the dark current because having a high value of dark current implies:

- Reduced threshold of minimum detectable power for very sensitive detectors.

- More noise.

- It will be interpreted, in an eye diagram, exactly like a decrease in responsivity (less open eye diagram).

In Germanium photodiodes, the total dark current is the combination of bulk dark current and surface dark current contributions [73][74] where:

$$I_{dark} = I_{bulk} + I_{surface} = S * J_{bulk} + P * J_{surface}$$

(2.1)

$J_{bulk}$  : the bulk dark current density in  $A/m^2$   $J_{surface}$  : the surface dark current density in  $A/m^2$

S: the photodiode surfaceP: the photodiode perimeter

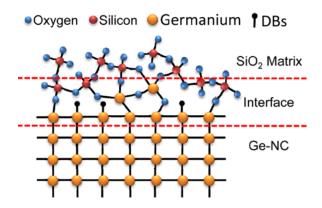

Generally, in germanium photodetectors, the contribution of surface dark current is non negligible as it stems from the presence of dangling bonds [75], see Fig.2.12. These bonds include the ones in the edge of the germanium structure and at the interface with silicon dioxide. Indeed, unlike silicon, germanium annealing proves inefficient and several techniques are till now studied to improve its outcome [76].

FIGURE 2.12: Germanium dangling bonds.

#### **Bandwidth:**

The bandwidth of a photodiode is determined by two factors:

- Transit time: the time that it takes the photo-generated charge carriers to cross from an electrode to another.

- RC constant: the low-pass RC filter made out of the junction capacitance  $C_j$  and the series resistance made out of the contact resistance and the bulk resistance.

The final bandwidth is given by the following equation:

$$f_{3dB} = \frac{1}{\sqrt{\frac{1}{f_{RC}^2} + \frac{1}{f_{transit}^2}}}$$

(2.2)

Where:

$$f_{RC} = \frac{1}{2\pi RC} \tag{2.3}$$

And

$$f_{transit} = 0,44 * \frac{v_d}{d} \tag{2.4}$$

$v_d$  is the average drift velocity of the carriers and can be approximated by the saturation velocity  $v_{sat}$ . d is the junction depletion width.

Based on the above, there are two straightforward ways of increasing bandwidth: reducing the transit time or reducing the RC constant.

The first method, i.e. reducing transit time amounts to bringing the pGe and nGe closer to each other for full Ge photodiodes, which yields a smaller intrinsic region (less responsivity) and absorption within the doped regions (see Responsivity optimization).

For SiGeSi photodiodes [77], this reduction is limited because of:

- Optical power confinement in germanium: indeed if the germanium width becomes very small, the optical mode will expand out of germanium and this would cause a decrease in responsivity.

- Process limits: to have a proper Germanium epitaxy, the Germanium cavity should be around 300nm large for most manufacturing processes.

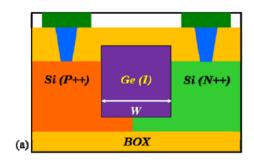

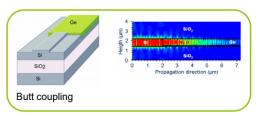

An alternative way to decrease transit time without impacting very much the width of the germanium cavity is to use a parallel plate junction as described in fig.2.13

By using parallel plate junctions, the transit time is reduced by strategically modifying the electrical field profile while keeping the Ge cross section relatively wide.

(A) Parallel plate Ge junction with Silicon  $PN_{(B)}$  Parallel plate Ge junction with Silicon PIN from [77] from [74]

FIGURE 2.13: Parallel plate Ge junction photodiodes with different silicon doping configurations

This solution requires a thin Ge layer so that the electrical field is high enough over the Ge section. It also comes with a big parallel junction capacitance (the Si junction). It may also feature a « tail » response in the Eye diagram (similar to a jitter effect) since for the upper part of Ge, electrons and holes take a longer time to transit.

There are, up till now, two ways to implement this solution: either use a silicon P-I-N junction underneath the Germanium photodiode as in [78], see Fig.2.13a or use a silicon PN junction instead as in [77], see Fig.2.13a.

In the literature, there is a third method to increase bandwidth without changing the geometry of the photo-diode: inductive-gain peaking [79]. This technique was already in use in microelectronics for amplifier design [80] [81], and photo-receiver amplification [82] [83] [84].

The main idea here is to consider the RC equivalent circuit of the photo-diode and add an inductance in series with it so that the bandwidth can be improved. Design of high Q inductors in silicon photonics circuits became possible since the processing became mature and increasingly approaching the complexity of microelectronics designs. Indeed, nowadays several layers of metal are used to cover the needs of silicon photonics complex designs [85] and the use of high resistivity handle wafers for silicon on insulator is not uncommon anymore [86].

There are several ways of implementing this technique that yield improvements ranging from 40% up to many folds the original bandwidth [87].

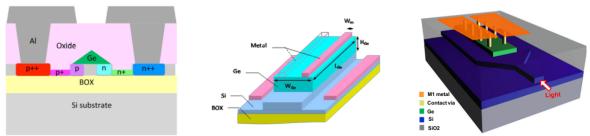

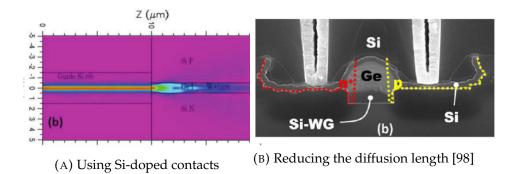

We have summarized the different optimization techniques and their yield in the following table, see Fig.2.14.

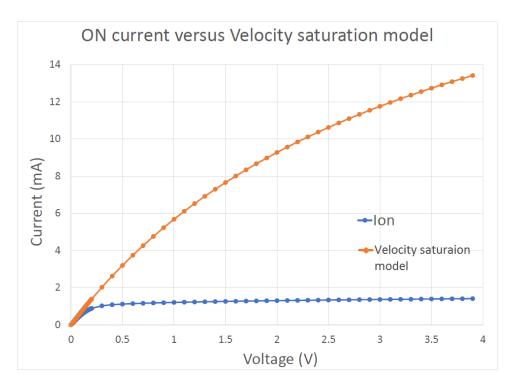

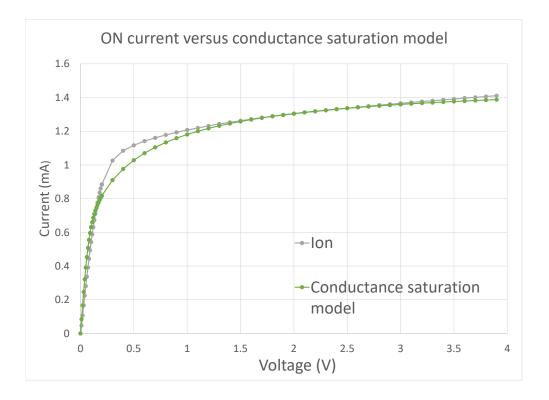

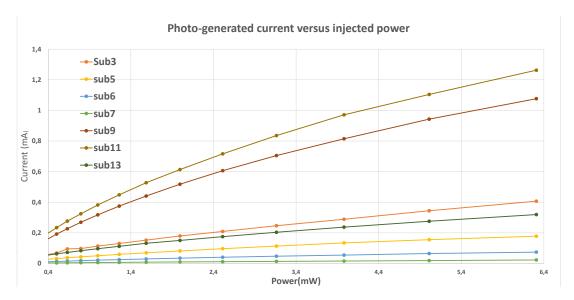

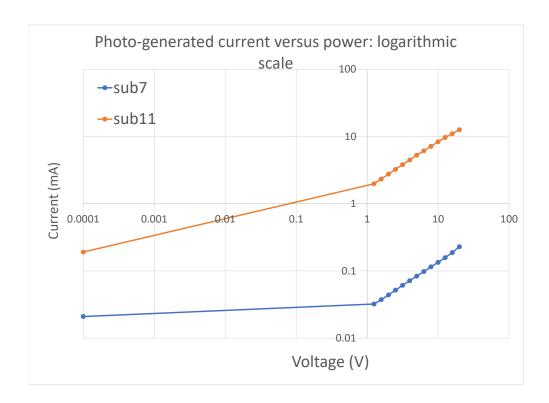

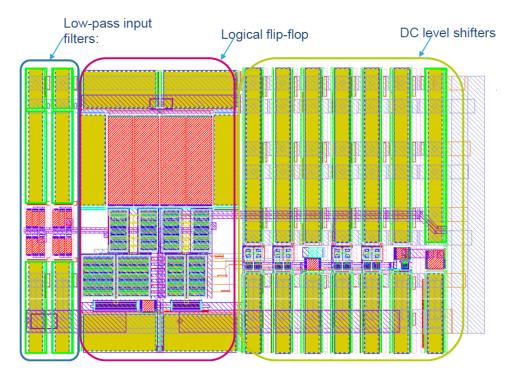

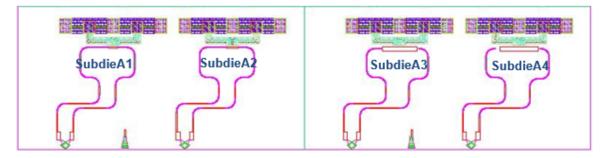

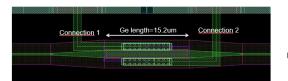

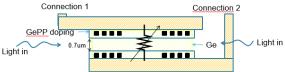

| Bandwidth                                                                                        | Main Optimization                                                                                                                                                                                                                                                       | Design                                                      | Reference                                                                                                                                                                                              |