# Subutai: Distributed synchronization primitives for legacy and novel parallel applications

Rodrigo Cadore Cataldo

# ▶ To cite this version:

Rodrigo Cadore Cataldo. Subutai : Distributed synchronization primitives for legacy and novel parallel applications. Distributed, Parallel, and Cluster Computing [cs.DC]. Université de Bretagne Sud; Pontifícia universidade católica do Rio Grande do Sul, 2019. English. NNT : 2019LORIS541 . tel-02865408

# HAL Id: tel-02865408 https://theses.hal.science/tel-02865408

Submitted on 11 Jun 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

L'UNIVERSITÉ BRETAGNE SUD

COMUE UNIVERSITE BRETAGNE LOIRE

ÉCOLE DOCTORALE N° 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Électronique

Par

# « Rodrigo Cadore CATALDO »

# « SUBUTAI: Distributed synchronization primitives for legacy and novel parallel applications »

Thèse présentée et soutenue à Porto Alegre, le 16 décembre 2019 Unité de recherche : Lab-STICC Thèse N° : 541

#### Rapporteurs avant soutenance :

| Eduardo Augusto BEZERRA |                                                           |  |

|-------------------------|-----------------------------------------------------------|--|

| -                       | Professeur, Universidade Federal de Santa Catarina (UFSC) |  |

| Marcio KREUTZ           |                                                           |  |

|                         | Professeur, Universidade Federal                          |  |

|                         | do Rio Grande do Norte (UFRN)                             |  |

| Avelino Francisco ZORZO |                                                           |  |

|                         | Professeur, Pontifícia                                    |  |

|                         | Universidade Católica do Rio                              |  |

|                         | Grande do Sul (PUCRS)                                     |  |

## Composition du Jury :

| Kevin Martin                                      | Maître de conférences, Université<br>Bretagne Sud |

|---------------------------------------------------|---------------------------------------------------|

| Directeur de thèse<br>Jean-Philippe DIGUET        | 0                                                 |

| Co-directeur de thèse /<br>César Augusto Missio I |                                                   |

Subutai : Distributed synchronization primitives for legacy and novel parallel applications Rodrigo Cadore Cataldo 2019

# List of Figures

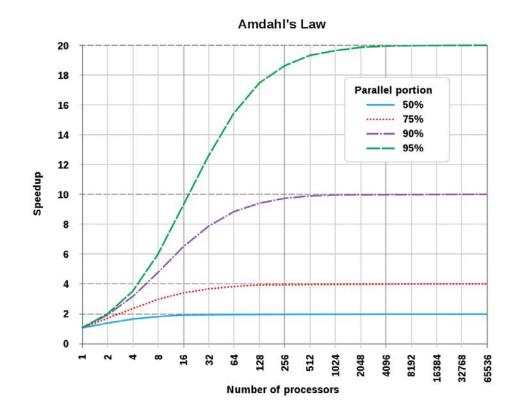

| Figure | 1.1 – The speedup of a parallel application is severely limited by how much of the application can be parallelized [Wik19].                                                                                                                                                                     | 18 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

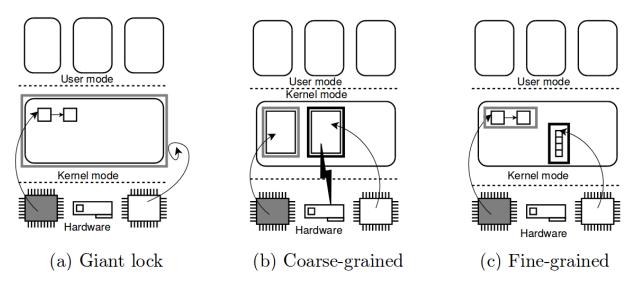

| Figure | 1.2 – The essential approaches to parallelizing code. Thick lines depict locks and the flash symbol denote device interrupt [Kå05].                                                                                                                                                             | 19 |

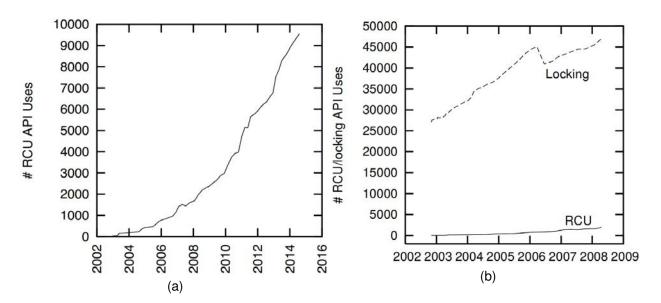

| Figure | 1.3 – (a) RCU usage over the years [MBWW17]; (b) RCU and Locking usage over the years [MW08].                                                                                                                                                                                                   | 20 |

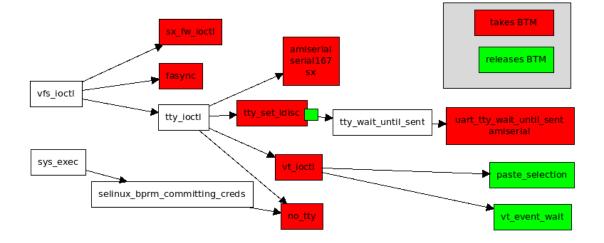

| Figure | 1.4 $-$ Snippet of the locking scheme for the TTY subsystem [BC19a] [BC19b].                                                                                                                                                                                                                    | 23 |

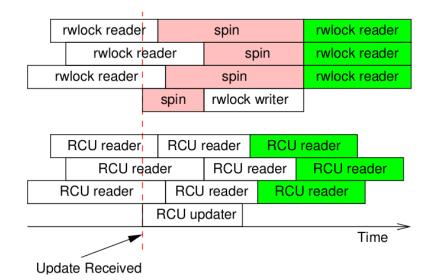

| Figure | 1.5 – Execution of reader-writer lock and RCU. The green color is used to represent up to date data [McK19a].                                                                                                                                                                                   | 24 |

| Figure | 1.6 – Cost of each production step of multiple generations of transistor technology [Spe19].                                                                                                                                                                                                    | 25 |

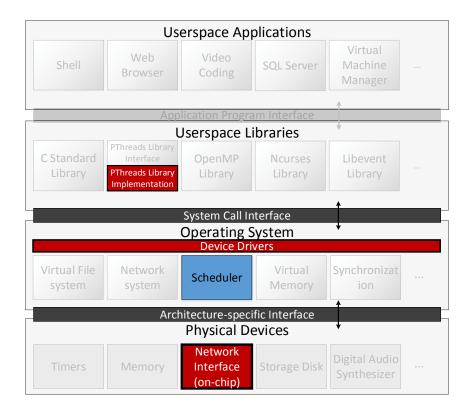

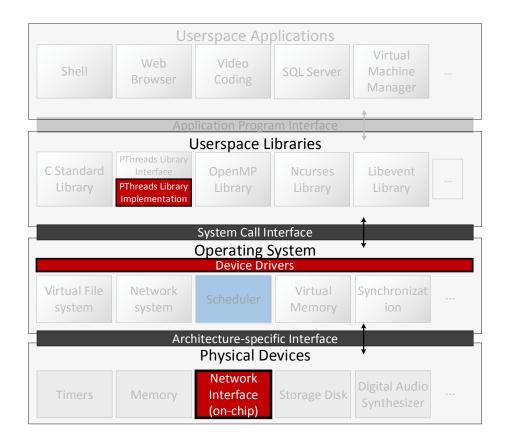

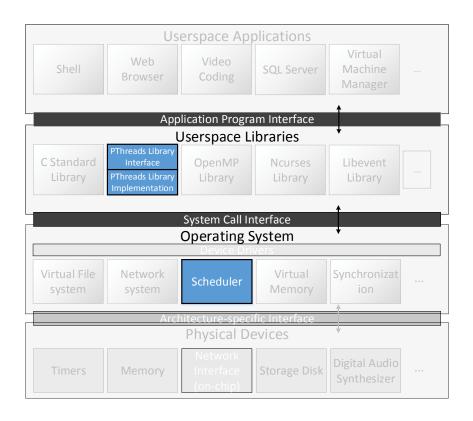

| Figure | 1.7 – Subutai components are highlighted in red in the computing stack.<br>Subutai only requires changes in the (i) on-chip NI, (ii) OS NI driver and (iii)<br>PThreads implementation. Additionally, a new scheduling policy (in blue) is<br>explored in this work as an optional optimization | 26 |

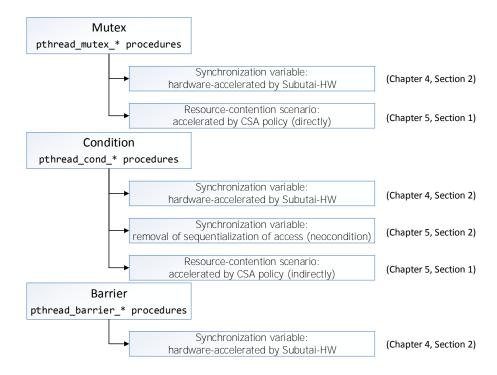

| Figure | 1.8 – Synchronization acceleration with the Subutai solution for different scenarios.                                                                                                                                                                                                           | 27 |

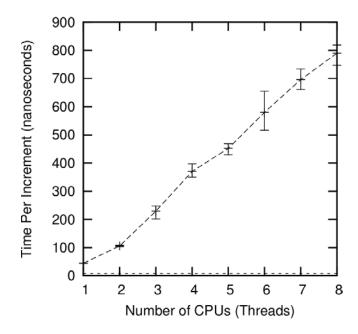

| Figure | 2.1 – Atomic increment scalability on a Nehalem Intel processor [McK19a].                                                                                                                                                                                                                       | 31 |

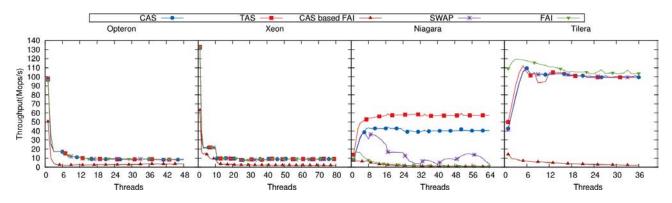

| Figure | 2.2 – Throughput of different atomic operations on a single memory position [DGT13].                                                                                                                                                                                                            | 31 |

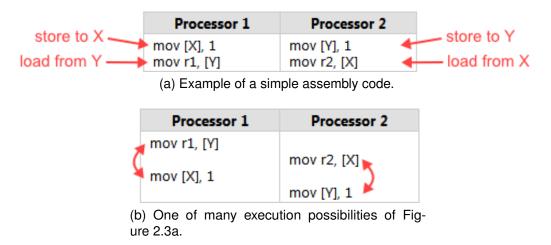

| Figure | 2.3 – Reordering example from the Intel Manual [Int17] [Pre19b]                                                                                                                                                                                                                                 | 32 |

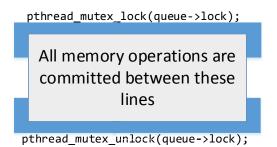

| Figure | 2.4 – The net effect of using lock-based procedures: implicit memory barriers (represented as blue fences) (based on [Pre19a])                                                                                                                                                                  | 36 |

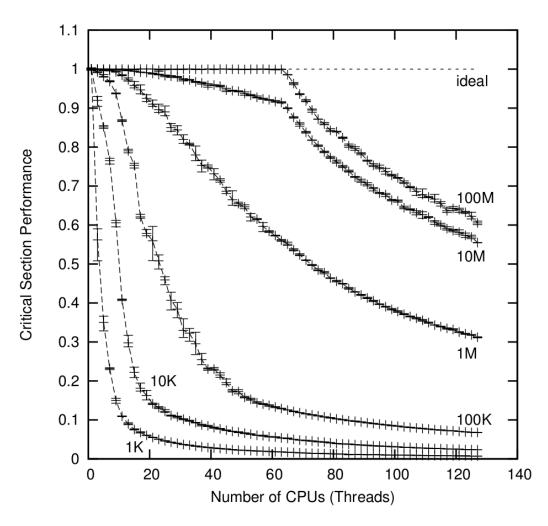

| Figure | 2.5 – Scalability of the Reader-Writer Lock mechanism. A parameter is used to simulate the critical section range in instructions, which ranges from a thousand (1K on the graph) to 100 million (100M on the graph) instructions [McK19a].                                                     | 39 |

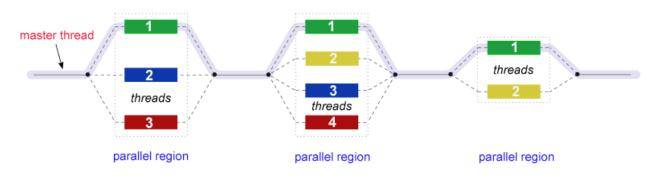

| Figure | 3.1 – The fork-join model of OpenMP [Bar19a].                                                                                                                                                                                                                                                   | 47 |

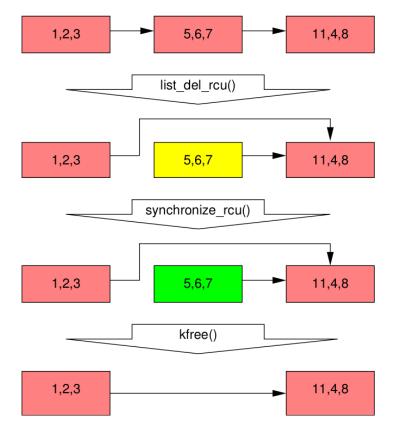

|        | 3.2 – RCU deletion example [McK19a].                                                                                                                                                                                                                                                            | 50 |

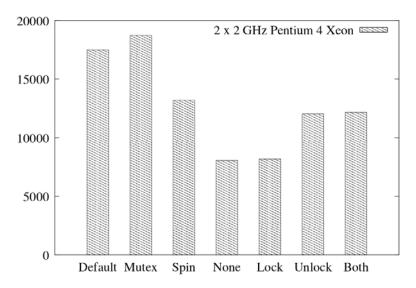

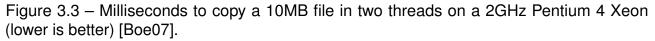

|        | 3.3 – Milliseconds to copy a 10MB file in two threads on a 2GHz Pentium 4 Xeon (lower is better) [Boe07].                                                                                                                                                                                       | 52 |

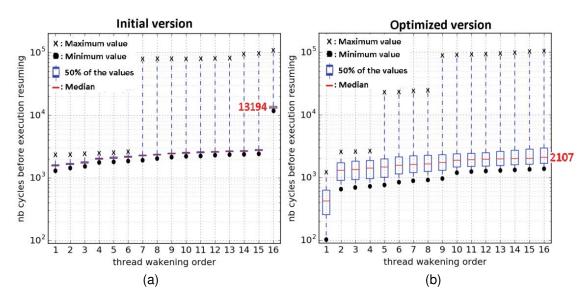

| Figure | 3.4 – Delays to complete the barrier release process for a 16-thread application on a 16-core system (a) without and (b) with optimization [FPMR18].                                                                                                                                            | 53 |

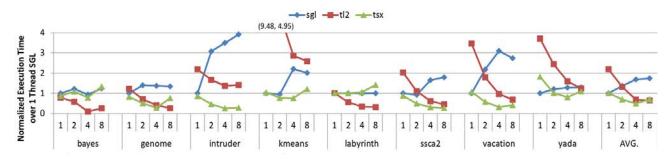

| Figure     | 3.5 – Normalized execution time of eight applications from the STAMP benchmark from 1 up to 8 threads; AVG represents the average execution     |     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | time of all applications [YHLR13].                                                                                                              | 56  |

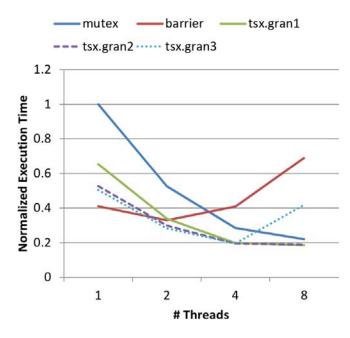

| Figure     | 3.6 – Comparison of different synchronization schemes for                                                                                       |     |

|            | PhysicsSolver [YHLR13]                                                                                                                          | 57  |

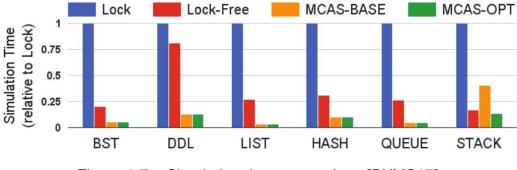

| Figure     | 3.7 – Simulation time comparison [PKMS17]                                                                                                       | 58  |

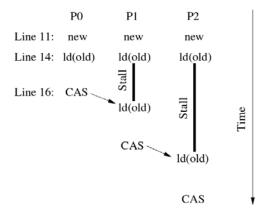

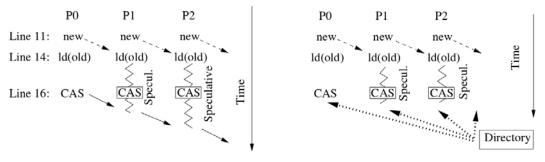

| Figure     | 3.8 – Ideas behind the CASPAR architecture [GMT16]                                                                                              | 60  |

| Figure     | 3.9 - Experimental results for the CASPAR architecture design [GMT16].                                                                          | 61  |

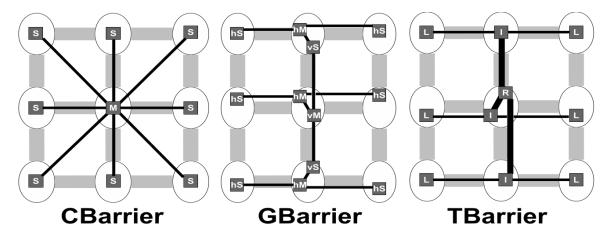

| Figure     | 3.10 – Three barrier synchronization topologies [AFA+12].                                                                                       | 62  |

| Figure     | 3.11 – Gather phase for (a) CBarrier, (b) GBarrier, and (c) TBarrier [AFA+12].                                                                  | 63  |

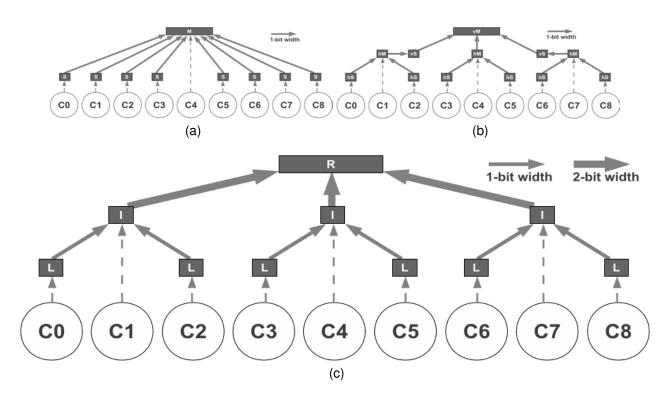

| Figure     | 3.12 – (a) Optimal frequencies and (b) area overhead running at 600MHz for all analyzed topologies [AFA+12].                                    | 64  |

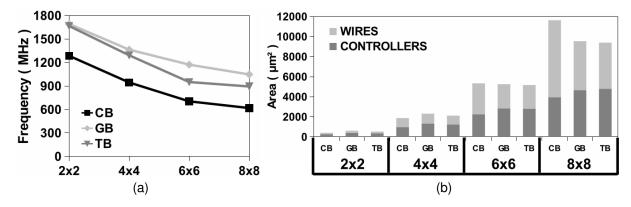

| Figure     | 3.13 – The barrier cost of (a) SW and (b) HW implementation in cycles [AFA+12].                                                                 | 65  |

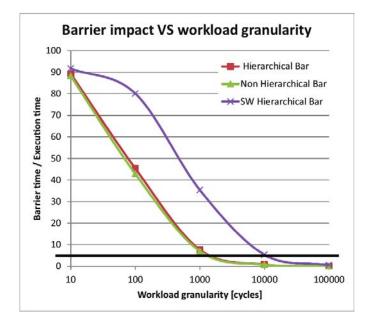

| Figure     | 3.14 – Barrier overhead for varied-sized parallel workload [AFA <sup>+</sup> 12].                                                               | 65  |

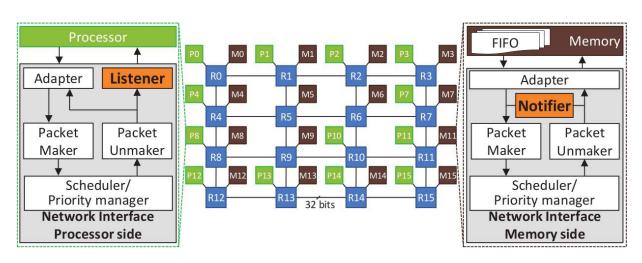

| -          | 3.15 – Target architecture with Notifying Memories [MRSD16].                                                                                    | 67  |

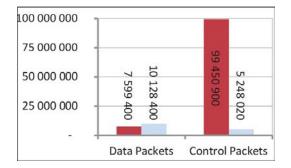

| -          | 3.16 – Classification of packets transported after 10 decoded frames of                                                                         | •   |

| .90.0      | ice [MRSD16]                                                                                                                                    | 69  |

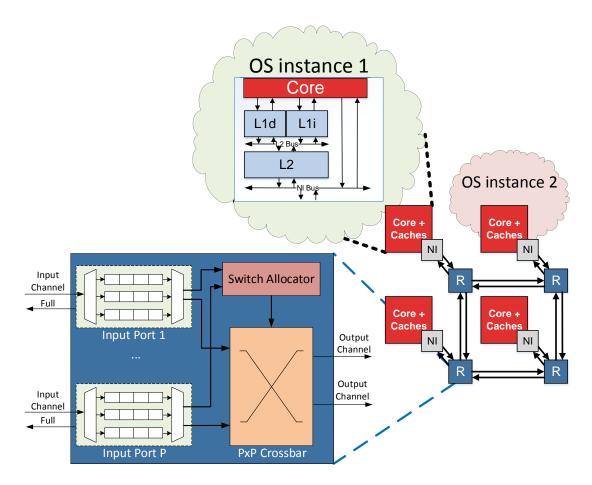

| Figure     | 4.1 – The Subutai solution; Subutai components are highlighted in red                                                                           | 79  |

|            | 4.2 – Schematic of the target architecture for Subutai; the target architecture                                                                 |     |

|            | is comprised of 64 cores                                                                                                                        | 81  |

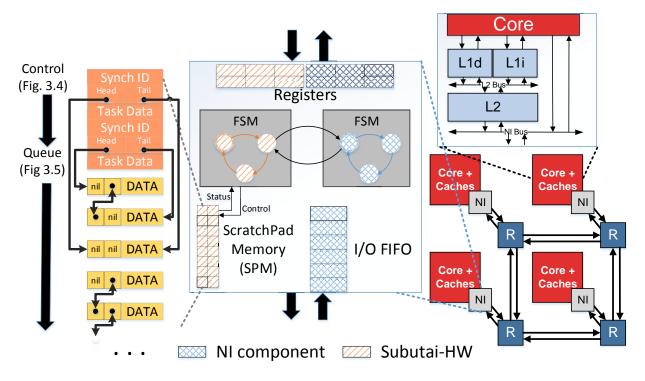

| Figure     | 4.3 – Schematic representation of Subutai-HW and the NI. The hardware elements required by Subutai-HW implementation are highlighted in orange. | 82  |

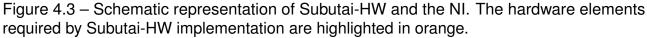

| Figure     | 4.4 – Subutai-HW control structure.                                                                                                             | 83  |

| Figure     | 4.5 – Subutai-HW queue structure.                                                                                                               | 83  |

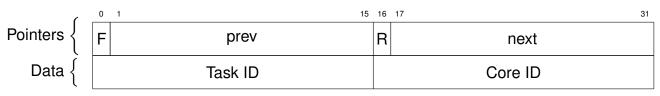

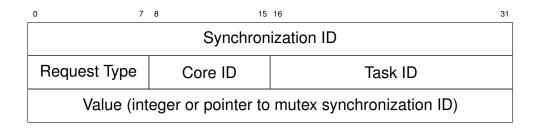

| Figure     | 4.6 – Subutai's packet format.                                                                                                                  | 87  |

| Figure     | 4.7 – Futex kernel implementation [Har19].                                                                                                      | 91  |

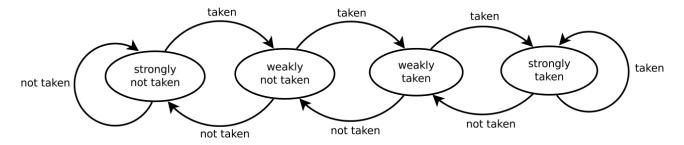

| Figure     | 4.8 – 2-bit saturating counter for branch prediction [Dia19]                                                                                    | 94  |

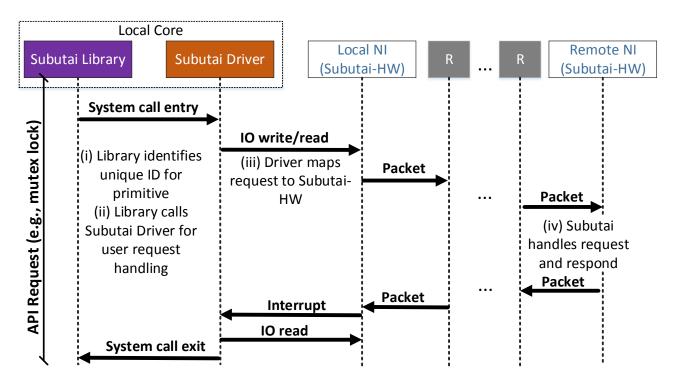

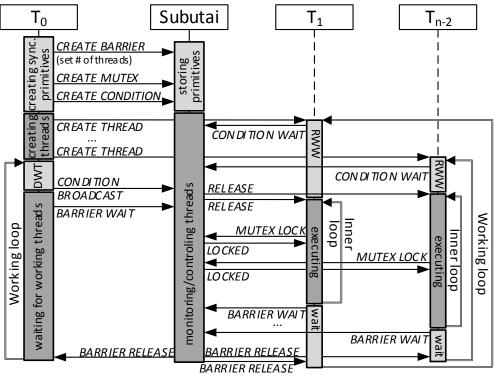

| Figure     | 4.9 – Communication flow of Subutai.                                                                                                            | 95  |

| Figure     | 5.1 – The Subutai extensions are highlighted in blue.                                                                                           | 97  |

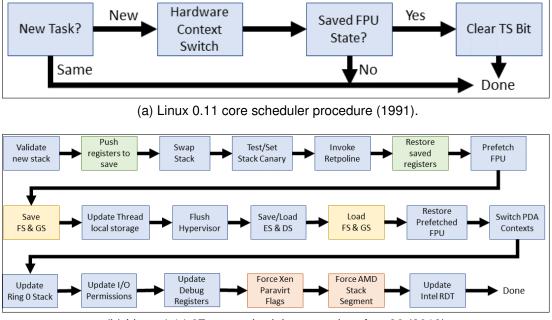

| Figure     | 5.2 - Core scheduler procedure switch_to steps for two Linux kernel                                                                             | 00  |

| <b>-</b> : | versions [Mai19].                                                                                                                               | 99  |

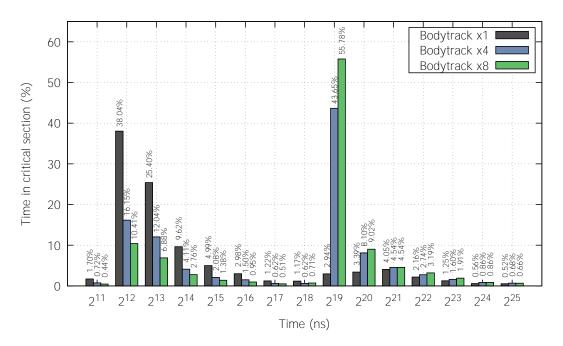

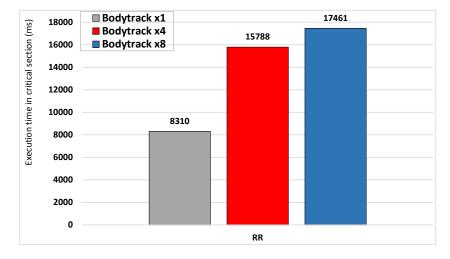

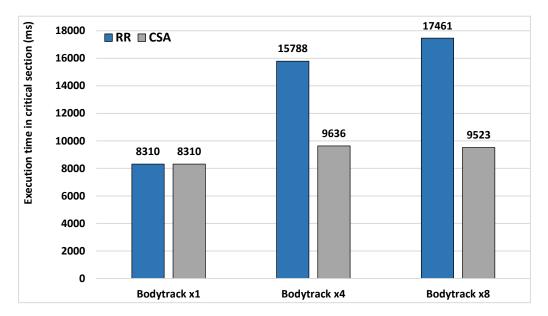

| rigure     | 5.3 – Overall time spent in the critical sections for all the work-related mutexes of Bodytrack on a RR scheduler.                              | 100 |

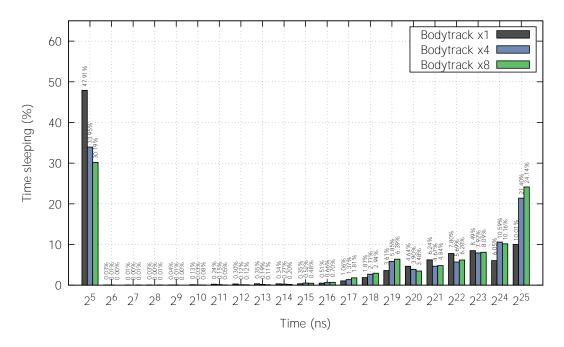

| Figure     | 5.4 – Overall time spent in mutex queues for all the work-related mutexes of Bodytrack on a RR scheduler.                                       | 101 |

| Figure 5.5 – Total execution time spent in critical sections for all the work-related mutexes of Bodytrack on a RR scheduler.                                                                                                                                                                                               |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

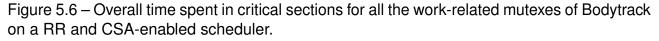

| Figure 5.6 – Overall time spent in critical sections for all the work-related mutexes of Bodytrack on a RR and CSA-enabled scheduler.                                                                                                                                                                                       |       |

| Figure 6.1 – Experimental setup for Subutai evaluation.                                                                                                                                                                                                                                                                     | . 120 |

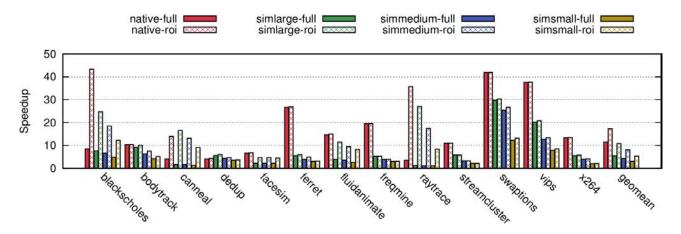

| Figure 6.2 – Maximum speedup measured for a 48-core system for each bench-<br>mark, region, and input set combination. Full and ROI inputs represent the<br>entire application and parallel portion, respectively [SR15]                                                                                                    | ;     |

| Figure 6.3 – Bodytrack's output.                                                                                                                                                                                                                                                                                            | . 126 |

| Figure 6.4 – Bodytrack's core workflow                                                                                                                                                                                                                                                                                      | . 127 |

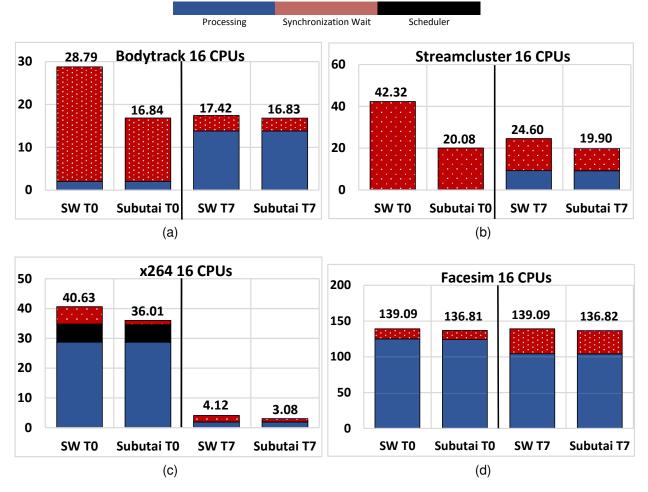

| Figure 6.5 – The execution time in seconds (10 <sup>9</sup> ns) of our application set on SW-<br>only and Subutai solutions for 16 threads. Due to the order of magnitude,<br>Subutai-HW and NoC latencies are not visible.                                                                                                 | ı     |

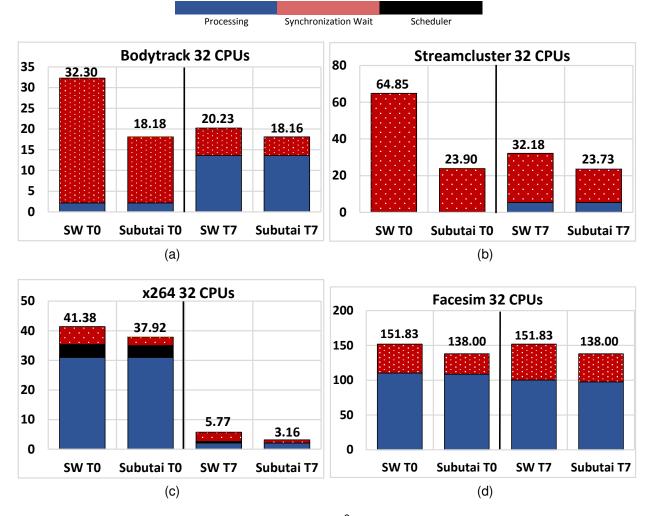

| Figure 6.6 – The execution time in seconds (10 <sup>9</sup> ns) of our application set on SW-<br>only and Subutai solutions for 32 threads. Due to the order of magnitude<br>Subutai-HW and NoC latencies are not visible.                                                                                                  | ,     |

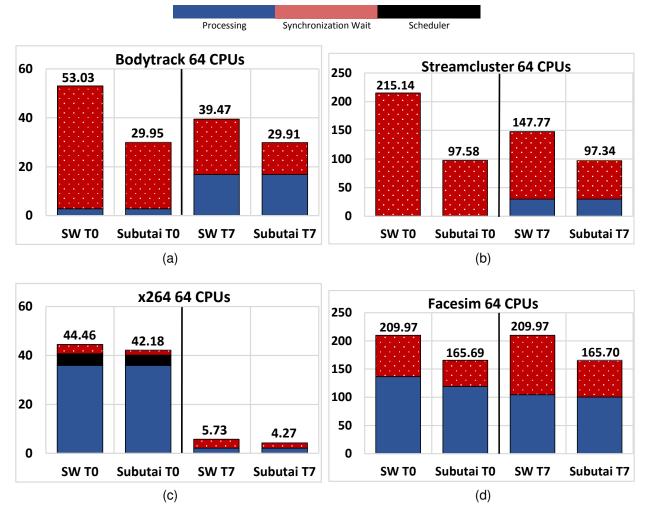

| Figure 6.7 – The execution time in seconds (10 <sup>9</sup> ns) of our application set on SW-only and Subutai solutions for 64 cores. Due to the order of magnitude, Subutai-HW and NoC latencies are not visible.                                                                                                          | ,     |

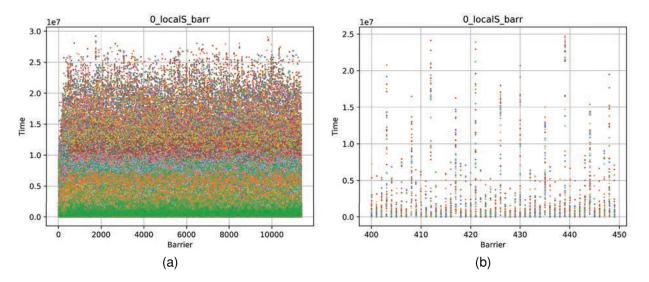

| Figure 6.8 – Relative time for every thread to reach the barrier localS; (a) is a plot<br>for all barrier calls during the application execution, while (b) is a snippet of<br>50 barrier calls for better visualization.                                                                                                   | f     |

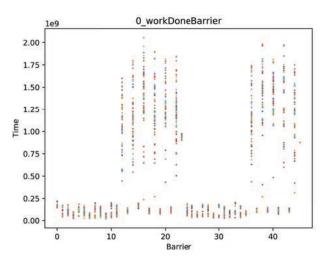

| Figure 6.9 - Relative time for every thread to reach all barriers calls of workDone-<br>Barrier.                                                                                                                                                                                                                            |       |

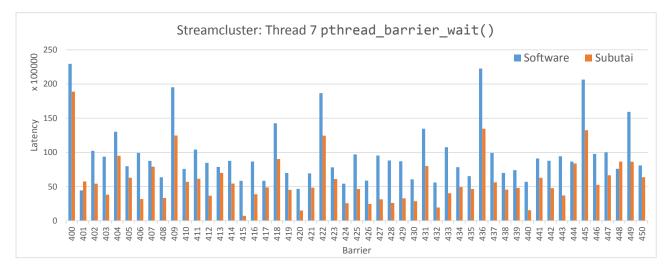

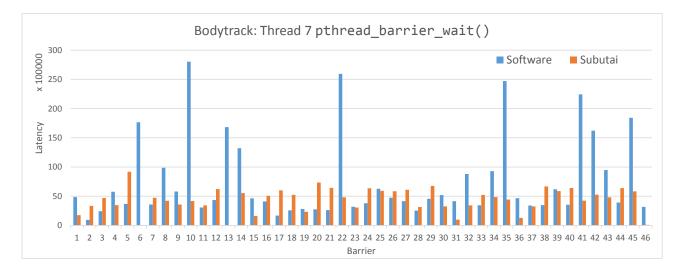

| Figure 6.10 – Comparison of latency for the procedure pthread_barrier_wait for SW-only and Subutai. The results are for T <sub>7</sub> for a subset of barrier calls (400 up to 450)                                                                                                                                        | )     |

| Figure 6.11 – Comparison of latency for the procedure pthread_barrier_wait<br>for SW-only and Subutai. The results are for T <sub>7</sub> for all barrier calls of<br>poolReadyBarrier                                                                                                                                      | F     |

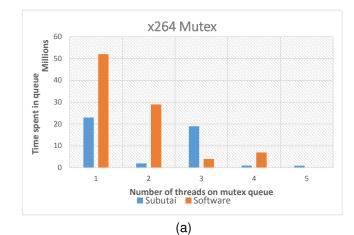

| <ul> <li>Figure 6.12 – Time spent, in 10<sup>6</sup> ns, on the mutex queue of Bodytrack and x264.</li> <li>(a) and (b) are plots of time spent (Y-axis) by the number of threads on the queue (X-axis) for x264 and Bodytrack, respectively; (c) and (d) are the total time spent for the same application set.</li> </ul> | )<br> |

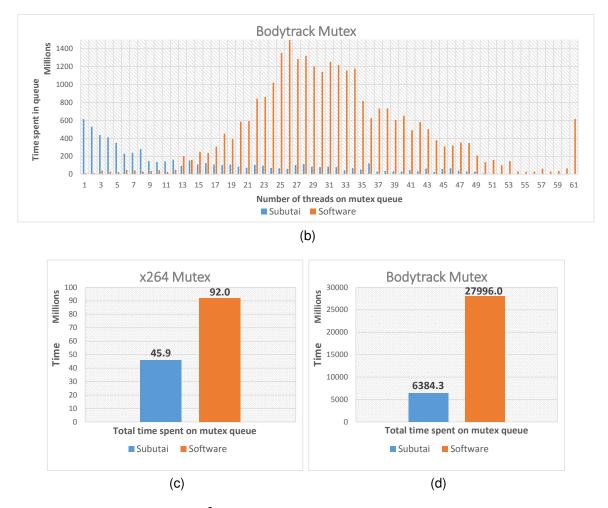

| Figure 6.13 – Execution in seconds (10 <sup>9</sup> ns) for multiple application sets (lower is better) (Exec = Execution).                                                                                                                                                                                                 | 5     |

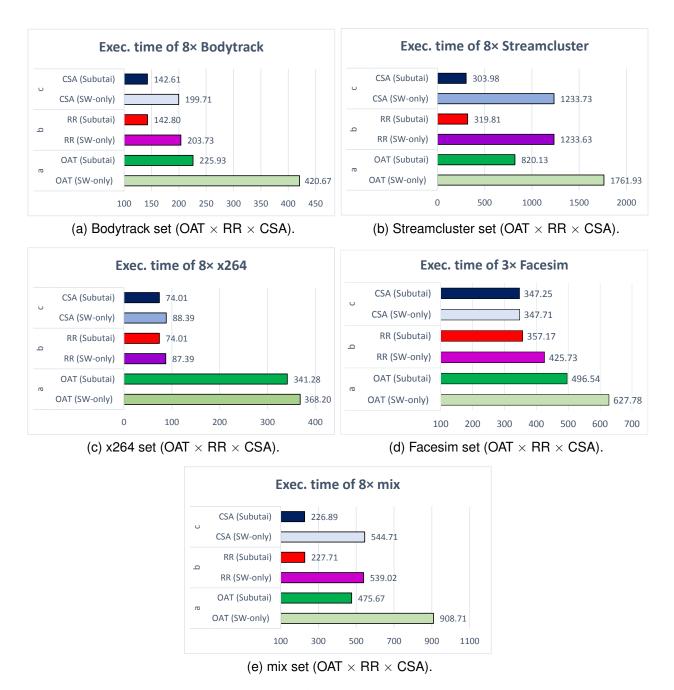

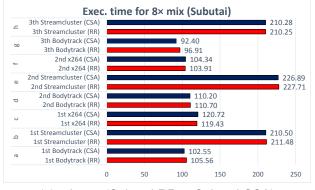

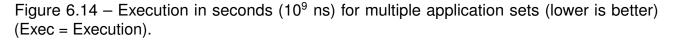

| Figure 6.14 – Execution in seconds (10 <sup>9</sup> ns) for multiple application sets (lower is better) (Exec = Execution). | 145 |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

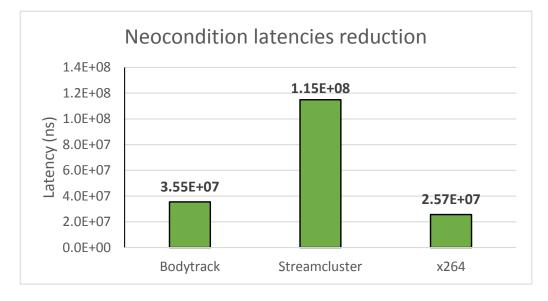

| Figure 6.15 – Latency reduction in nanoseconds of the total execution time for three                                        |     |

| PARSEC applications                                                                                                         | 148 |

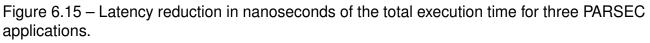

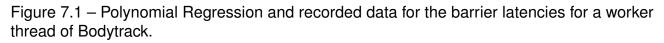

| Figure 7.1 – Polynomial Regression and recorded data for the barrier latencies for                                          |     |

| a worker thread of Bodytrack.                                                                                               | 157 |

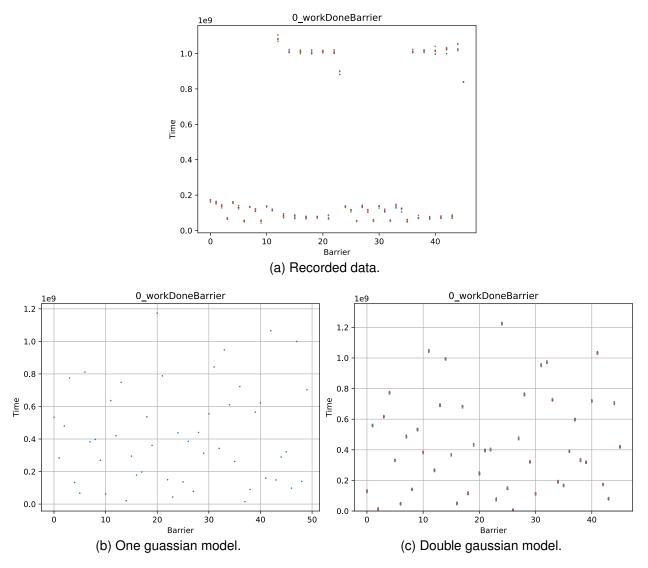

| Figure 7.2 – Barrier latencies from Bodytrack for (a) recorded data, (b) one gaus-                                          |     |

| sian and (c) double gaussian models.                                                                                        | 158 |

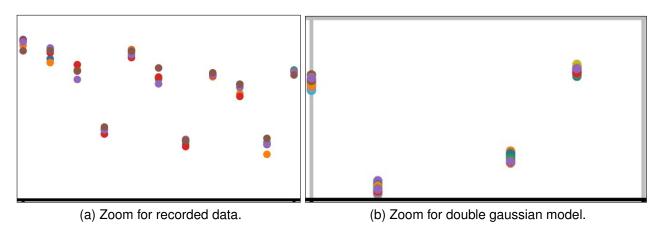

| Figure 7.3 $-$ A zoom for some of the first 10 barriers of Bodytrack from Figure 7.2.                                       | 159 |

# List of Tables

| Table 1.1 – Breakdown of RCU usage by kernel subsystems [MBWW17]                                                                                                     | 21  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1 – Overview of some memory barriers [Int17] [Lea19] [SPA93].                                                                                                | 32  |

| Table 2.2 – Memory barriers used by some PThread implementations for mutexes.                                                                                        |     |

| Adapted from [Boe07]                                                                                                                                                 | 33  |

| Table 2.3 – An execution scenario from Listing 2.11 [Sta19].                                                                                                         | 43  |

| Table 3.1 – Traits and behavior of mutexes. Based on [Rei07] [Int19d].                                                                                               | 48  |

| Table 3.2 – Memory barriers used by some PThreads implementations for spin-                                                                                          |     |

| locks. Adapted from [Boe07]                                                                                                                                          | 51  |

| Table 3.3 – Gains for the release phase on TSAR and Alpha architectures [FPMR18].                                                                                    | 54  |

| Table 3.4 – Unsuccessful firing rules attempts and its reasons [MRSD16].                                                                                             | 66  |

| Table 3.5 – Notification memory gain for decoding 10 frames of five video se-                                                                                        |     |

| quences [MRSD16]                                                                                                                                                     | 68  |

| Table 3.6    —    Related work summary.                                                                                                                              | 73  |

| Table 3.7 – Related work key contribution.                                                                                                                           | 74  |

| Table 4.1 – Latency of essential queue procedures. $m =$ memory latency                                                                                              | 84  |

| Table 4.2 – Latencies of Subutai-HW states. $c = cycle$ latency, $m = memory$                                                                                        |     |

| latency, $n =$ number of synchronization variables handled by Subutai-HW, $\rho$                                                                                     |     |

| = number of threads on a barrier.                                                                                                                                    | 85  |

| Table 4.3 – Latency of Subutai-HW states with parameters $c = 1 ns$ , $m = 2 ns$ ,                                                                                   | 00  |

| $n = 4, \rho = 63, FSMentry = 4ns, and FSMexit = 1ns.$                                                                                                               | 86  |

| Table 4.4 – Cache space reduction of synchronization primitives.         Table 5.4 – Cache space reduction of synchronization primitives.                            | 92  |

| Table 5.1 – Impact of <i>CSALimit</i> on the Bodytrack application set employing a timeslet of time. CS – Critical Section                                           | 104 |

|                                                                                                                                                                      | 104 |

| Table 5.2 – Complexity of neocondition states. $c =$ cycle latency, $m =$ memory latency, $n =$ number of synchronization variables handled by Subutai-HW, $\varrho$ |     |

| = number of threads on a neocondition                                                                                                                                | 116 |

| Table 5.3 – Positive and negative attributes of neocondition compared to PThreads                                                                                    |     |

| conditions.                                                                                                                                                          | 117 |

| Table 6.1 – Simulation time for some NoC simulators executing 1 second of simu-                                                                                      |     |

| lated time without injecting packets.                                                                                                                                | 121 |

| Table 6.2 – Qualitative summary of key characteristics of PARSEC benchmarks                                                                                          |     |

| [BKSL08]                                                                                                                                                             | 123 |

| Table 6.3 – Breakdown of finer details of the benchmark applications for input size                                                                                  |     |

| simlarge on an 8-core system [BKSL08]                                                                                                                                | 124 |

| Table 6.4 – Number of events of synchronization primitives during the execution of  |     |

|-------------------------------------------------------------------------------------|-----|

| PARSEC applications                                                                 | 125 |

| Table 6.5 – Number of synchronization primitives for PARSEC (simmedium input).      |     |

| <i>n</i> = number of threads                                                        | 125 |

| Table 6.6       –       Synthesis results for Subutai-HW and SPM using 28 nm SOI.   | 129 |

| Table 6.7 – State-of-the-art area consumption.                                      | 130 |

| Table 6.8 – Detailed execution time (ns) and the speedup for the application set    |     |

| executing on 16 cores.                                                              | 134 |

| Table 6.9 – Detailed execution time (ns) and the speedup for the application set    |     |

| executing on 32 cores.                                                              | 135 |

| Table 6.10 – Detailed execution time (ns) and the speedup for Bodytrack and         |     |

| Streamcluster executing on 64 cores                                                 | 136 |

| Table 6.11 – Characteristics of the application set executing on CSA (CS = Critical |     |

| Section; all data are averages achieved for all applications)                       | 146 |

| Table 6.12 – Unfairness metric for CSA and RR schedulers (lower is better)          | 147 |

| Table 6.13 – Results for one producer and many consumer applications running        |     |

| with six threads.                                                                   | 151 |

| Table 7.1 – The software exploration of neocondition: execution time of PThreads    |     |

| condition and SW-only neocondition.                                                 | 161 |

# List of Listings

| 2.1  | Lock-free message processing [HMDZ19]                                             | 34  |

|------|-----------------------------------------------------------------------------------|-----|

| 2.2  | Generated code for lock-free message processing [HMDZ19]                          | 34  |

| 2.3  | Source code from an if statement [HMDZ19]                                         | 35  |

| 2.4  | Compiled source code from Listing 2.3 [HMDZ19]                                    | 35  |

| 2.5  | Queue structure.                                                                  | 36  |

| 2.6  | Lock-based enqueue operation. Synchronization procedures are colored red.         | 37  |

| 2.7  | SPARC-RMO assembly code for locking and unlocking operations [Mar19]              | 37  |

| 2.8  | C-like code for the CAS procedure.                                                | 38  |

| 2.9  | Pseudo-code of lock-free enqueue operation (Synchronization procedures are        |     |

|      | colored red) [PKMS17] [MS96]                                                      | 40  |

| 2.10 | Lock-based dequeue operation.                                                     | 41  |

| 2.11 | Lock-free dequeue operation susceptible to the ABA problem [Sta19]                | 42  |

| 3.1  | Conceptual implementation of the synchronize_rcu primitive [McK19a]               | 49  |

| 3.2  | Example of HTM-enabled parallel code.                                             | 69  |

| 3.3  | Lock-free CAS algorithm [PKMS17]                                                  | 70  |

| 3.4  | Lock-free MCAS algorithm [PKMS17].                                                | 70  |

| 3.5  | Example of Dataflow application flow. Adapted from [MRSD16]                       | 71  |

| 3.6  | Intuitive, but incorrect, implementation for an HTM-enabled application [Kle19b]. | 77  |

| 3.7  | A correct implementation for an HTM-enabled library. Based on [Kle19b]            | 77  |

| 4.1  | Definition of pthread_mutex_t.                                                    | 89  |

| 4.2  | SPARC locking procedure                                                           | 90  |

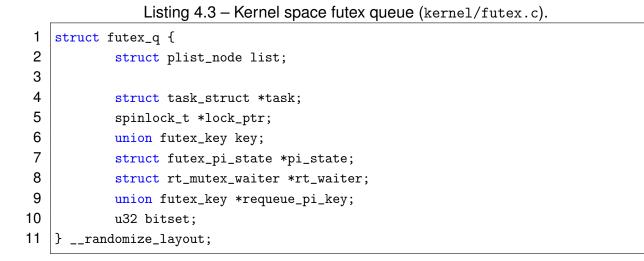

| 4.3  | Kernel space futex queue (kernel/futex.c)                                         | 91  |

| 4.4  | The pthread_mutex_t employed by the Subutai Solution                              | 92  |

| 4.5  | Simplified Subutai driver implementation                                          | 93  |

| 5.1  | Example of two conditions and their associated predicates for a FIFO. Initial-    |     |

|      | ization and error-checking are not shown for simplification purposes              | 105 |

| 5.2  | Multiple awakenings by condition signal. Numbered comments refer to the           |     |

|      | order of events. [IEE16].                                                         | 108 |

| 5.3  | Bodytrack's condition variable usage. Adapted from C++ to C                       | 110 |

| 5.4  | Streamcluster's condition variable usage. Adapted from C++ to C                   | 111 |

| 5.5  | Ferret's condition variable usage.                                                | 112 |

| 5.6  | Common API among PThreads condition and neocondition.                             | 114 |

| 6.1  | Shared structure for the producer-consumer application                            | 149 |

| 6.2  | A producer-consumer solution based on synchronization provided by PThreads.       |     |

|      | Synchronization procedures are colored red (based on [ADAD15])                    | 150 |

| A.1  | Queue-related macros for the SPM                                                  | 177 |

| A.2  | Pointer-related macros for Subutai-HW.                                            | 178 |

| A.3 | Queue procedures pseudo-code implementation         | 179 |

|-----|-----------------------------------------------------|-----|

| A.4 | Subutai-HW state machine pseudo-code implementation | 186 |

# List of Acronyms

- API Application Programming Interface

- BKL Big Kernel Lock

- BTM Big TTY Mutex

- CAS Compare-And-Swap

- **CBarrier Central Barrier**

- CMP Chip MultiProcessor

- CSA Critical-Section Aware

- DAC Design Automation Conference

- FAI Fetch-And-Increment

- FIFO First-In-First-Out

- FOSS Free/Open Source Software

- FPU Floating Point Unit

- FSM Finite State Machine

- Futex Fast Userspace muTEX

- GBarrier Gline-based Barrier

- GCC GNU Compiler Collection

- GNU GNU's Not Unix!

- HPC High-Performance Computing

- HTM Hardware Transactional Memory

- I/O Input/Output

- ICC Intel C++ Compiler

- ID IDentification

- IRQ Interrupt Request

- ISA Instruction Set Architecture

- LoC Lines of Code

- MPSoC MultiProcessor System-on-a-Chip

- mutex MUTual EXclusion

- NI Network Interface

- NoC Network-on-Chip

- NUMA Non-Uniform Memory Access

- OAT One Application at a Time

- OpenMP Open MultiProcessing

OS – Operating System

PARSEC – Princeton Application Repository for Shared-Memory Computers

PThreads – POSIX Threads

RCU - Read-Copy-Update

- RR Round-Robin

- RTL Register Transfer Level

- rwlock Reader-Writer Lock

- SGL Single Global Lock

- SMP Symmetric MultiProcessing

- SoC System-on-Chip

- SOI Silicon on Isolator

- SPM ScratchPad Memory

- Subutai-HW Subutai-Hardware

- TBarrier Tree-based Barrier

- TBB Threading Building Blocks

- tl2 Software Transactional Memory

- TSX Transactional Synchronization eXtensions

# Contents

| 1     |                                                                                                                      | 17 |

|-------|----------------------------------------------------------------------------------------------------------------------|----|

| 1.1   | CONTEXT                                                                                                              | 17 |

| 1.2   | MOTIVATION                                                                                                           | 18 |

| 1.3   | PROBLEM STATEMENT AND THESIS CONTRIBUTIONS                                                                           | 24 |

| 1.4   | DOCUMENT STRUCTURE                                                                                                   | 27 |

| 2     | DATA SYNCHRONIZATION IN PARALLEL APPLICATIONS                                                                        | 29 |

| 2.1   | SYNCHRONIZATION IN UNIPROCESSOR SYSTEMS                                                                              | 29 |

| 2.2   | SYNCHRONIZATION IN MULTIPROCESSOR SYSTEMS                                                                            | 30 |

| 2.2.1 | MEMORY AND COMPILER BARRIERS                                                                                         | 30 |

| 2.2.2 | LOCK-BASED APPLICATIONS                                                                                              | 35 |

| 2.2.3 | LOCK-FREE APPLICATIONS                                                                                               | 39 |

| 3     | RELATED WORK                                                                                                         | 45 |

| 3.1   | SOFTWARE-ORIENTED SOLUTIONS                                                                                          | 45 |

| 3.1.1 | POSIX THREADS (PTHREADS)                                                                                             | 45 |

| 3.1.2 | OPEN MULTIPROCESSING (OPENMP)                                                                                        | 46 |

| 3.1.3 | THREADING BUILDING BLOCKS (TBB)                                                                                      | 47 |

| 3.1.4 | READ-COPY-UPDATE (RCU)                                                                                               | 48 |

| 3.1.5 | REORDERING CONSTRAINTS FOR PTHREAD-STYLE LOCKS                                                                       | 50 |

| 3.1.6 | OPTIMIZATION OF THE GNU OPENMP SYNCHRONIZATION BARRIER IN MPSOC                                                      | 52 |

| 3.2   | HARDWARE-ORIENTED SOLUTIONS                                                                                          |    |

| 3.2.1 |                                                                                                                      |    |

| 3.2.2 | A HARDWARE IMPLEMENTATION OF THE MCAS SYNCHRONIZATION PRIM-                                                          |    |

| 3.2.3 | CASPAR: BREAKING SERIALIZATION IN LOCK-FREE MULTICORE SYN-CHRONIZATION                                               | 59 |

| 3.2.4 | DESIGN OF A COLLECTIVE COMMUNICATION INFRASTRUCTURE FOR<br>BARRIER SYNCHRONIZATION IN CLUSTER-BASED NANOSCALE MPSOCS | 61 |

| 3.2.5 |                                                                                                                      | 66 |

| 3.3   |                                                                                                                      | 72 |

| 3.3.1 | THE CHOICE OF PTHREADS                                      | 75  |

|-------|-------------------------------------------------------------|-----|

| 3.3.2 | SUBUTAI COMPATIBILITY WITH OTHER LEGACY-CODE COMPATIBLE SO- |     |

|       | LUTIONS                                                     | 75  |

| 4     | SUBUTAI SOLUTION                                            | 79  |

| 4.1   | TARGET ARCHITECTURE                                         | 80  |

| 4.2   | SUBUTAI HARDWARE (SUBUTAI-HW)                               | 82  |

| 4.2.1 | SUBUTAI-HW RTL IMPLEMENTATION AND VERIFICATION              | 87  |

| 4.3   | SUBUTAI SOFTWARE                                            | 88  |

| 4.3.1 | USER SPACE PTHREADS LIBRARY                                 | 88  |

| 4.3.2 | KERNEL SPACE FUTEX                                          | 90  |

| 4.3.3 | SUBUTAI IMPLEMENTATION                                      | 91  |

| 5     | SUBUTAI EXTENSIONS                                          | 97  |

| 5.1   | CRITICAL-SECTION AWARE (CSA) SCHEDULING POLICY              | 98  |

| 5.1.1 | ΜΟΤΙΥΑΤΙΟΝ                                                  | 98  |

| 5.1.2 | BASELINE SCHEDULER DESIGN                                   | 100 |

| 5.1.3 | APPLICATION EXAMPLE                                         | 100 |

| 5.1.4 | DESIGN AND IMPLEMENTATION CHOICES                           | 102 |

| 5.2   | NEOCONDITION                                                | 104 |

| 5.2.1 | ΜΟΤΙΥΑΤΙΟΝ                                                  | 104 |

| 5.2.2 | CONDITION USAGE EXAMPLES FROM THE PARSEC BENCHMARK          | 109 |

| 5.2.3 | DESIGN AND IMPLEMENTATION CHOICES                           | 113 |

| 5.2.4 | THE POSITIVE AND NEGATIVE ATTRIBUTES OF NEOCONDITION        | 116 |

| 6     |                                                             | 119 |

| 6.1   | EXPERIMENTAL SETUP                                          | 119 |

| 6.2   | PARSEC – BENCHMARK SUITE FOR MULTIPROCESSING                | 122 |

| 6.2.1 | BODYTRACK COMMUNICATION MODEL                               | 126 |

| 6.2.2 | STREAMCLUSTER COMMUNICATION MODEL                           | 127 |

| 6.2.3 | FACESIM COMMUNICATION MODEL                                 | 128 |

| 6.2.4 | X264 COMMUNICATION MODEL                                    | 128 |

| 6.3   | EXPERIMENTAL RESULTS                                        | 128 |

| 6.3.1 | SUBUTAI'S AREA CONSUMPTION AND STATE-OF-THE-ART COMPARISON  | 129 |

| 6.3.2 | PARSEC EXPERIMENTAL RESULTS                                 | 130 |

| 6.3.3 | MICRO-BENCHMARK                                             | 148 |

| 7     | CONCLUSIONS                                                 | 153 |

|-------|-------------------------------------------------------------|-----|

| 7.1   | CONTRIBUTIONS OF THIS WORK                                  | 154 |

| 7.1.1 | OTHER CONTRIBUTIONS                                         | 155 |

| 7.2   | DISCUSSION AND FUTURE WORK                                  | 155 |

| 7.2.1 | PSY: SYNTHETIC DATA SYNCHRONIZATION COMMUNICATION CREATOR . | 156 |

| 7.2.2 | ENERGY-AWARE DESIGN EXPLORATION FOR SUBUTAI-HW              | 159 |

| 7.2.3 | BARRIER-AWARE POLICY FOR SCHEDULERS INTENDED FOR PARALLEL   |     |

|       | APPLICATIONS                                                | 159 |

| 7.2.4 | SW-ONLY NEOCONDITION IMPLEMENTATION                         | 160 |

| 7.2.5 | QUEUE OPTIMIZER: SCHEDULER-AWARE HARDWARE QUEUE             | 161 |

|       | REFERENCES                                                  | 163 |

|       | APPENDIX A – Subutai-HW Pseudo-Code Implementation          | 177 |

| A.1   | QUEUE SIZES                                                 | 177 |

| A.2   | MACROS                                                      | 178 |

| A.3   | QUEUE PROCEDURES                                            | 179 |

| A.4   | SUBUTAI-HW STATE MACHINE                                    | 186 |

|       | APPENDIX B – List of Published Articles                     | 193 |

Subutai : Distributed synchronization primitives for legacy and novel parallel applications Rodrigo Cadore Cataldo 2019

# 1. INTRODUCTION

There are 3 rules to follow when parallelizing large codes. Unfortunately, no one knows what these rules are.

#### W. Somerset Maugham, Gary Montry

Parallel applications are essential for efficiently using the computational power of any system comprised of multiple processing cores. Unfortunately, these applications do not scale effortlessly with the number of cores for various architectural and functional constraints. A key factor for limiting the scalability of parallel applications is the use of synchronization operations that take away valuable computational time and restrict the parallelization gains. Moreover, many of the synchronization operations are implemented to be sequentially executed, further diminishing the parallelization potential. Multiple solutions in research and industry have been proposed to tackle the synchronization bottleneck. They range from software-based, hardware-based, and mixed solutions. However, these solutions restrict the implementation to a subset of synchronization primitives, require refactoring the source code of applications, or both. Hence, a solution that eliminates both limitations is needed. This Thesis provides a step toward the realization of a solution capable of executing and accelerating any legacy parallel application without refactoring its source code. We chose, for this work, parallel applications that use the POSIX Threads (PThreads) as the basis for synchronization operations. Besides, novel applications can also be developed to employ our solution. This chapter exposes the motivation, goals, and contributions of this Thesis.

### 1.1 Context

Since the end of the last century, a significant shift has occurred in the industry transitioning the processor chips from a single- to a multicore design using a dozen of cores due to the stagnation of processing frequency [DKM<sup>+</sup>12]. Recently, this paradigm has evolved to incorporate hundreds or even thousands of simple cores to continue to deliver higher performance. For instance, Ephiphany-V is a 1024-processor System-on-Chip (SoC) designed in 16nm transistor technology [Olo16]. Intel also provides manycore architecture such as Xeon Phi (formerly known as Knight's Landing) with up to 72 cores [Int19c].

Unfortunately, the multiplication of cores by itself does not translate directly to the increase of performance as the applications must be parallel-compatible to exploit the chip parallelism paradigm. Therefore, parallel programming techniques had to be adopted. The shift from sequential to parallel execution demands a detailed understanding of algorithms, architecture designs, and synchronization libraries. Where once a single sequential thread

could do the execution, now the developer must divide the workload into multiple execution threads and synchronize the data and threads themselves. Also, the parallel execution has to deal with deadlock, livelock, race, and non-deterministic events [McK19a]. Decisions regarding both partitioning and synchronization are crucial to determine the achievable performance of the application on a multicore design because even small sequential portions of execution can have a significant performance impact. This is known as Amdahl's law [Gus11] shown in Figure 1.1. Because of such impact, parallelization is mainly done manually, as to allow fine-grained performance optimizations.

Figure 1.1 – The speedup of a parallel application is severely limited by how much of the application can be parallelized [Wik19].

#### 1.2 Motivation

A developer has multiple alternatives to design a parallel application from a legacy sequential or parallel codebase. According to the constraints of a given project, it can use software-based, hardware-based, or a mixed solution to provide the parallel software primitives. Software-based solutions require the implementation of libraries and kernel support for some of the operations through system calls. PThreads and Open MultiProcessing (OpenMP) are examples of available and widely employed software-based solutions. Hardware-based solutions, however, require specific hardware to offload operations that are generally done in software. Compare-and-swap (CAS), for example, is an instruction capable of comparing and swapping a value atomically. Such a solution is limited to the available instruction set of the processor and hardware modules. A mixed solution can be employed when the hardware does not handle some application scenarios. For instance, CAS instructions are limited to a single memory position; therefore, if the developer has to change multiple memory positions, this has to be handled in software.

An essential concept for synchronization is mutual exclusion, also called locking. For deterministic data structures, some operations have to be limited to a single instance at a given time [AGH<sup>+</sup>11], which can be achieved by a mutual exclusion mechanism. Figure 1.2 shows three essential types of locking schemes to deal with parallelism: giant, coarse-grained and fine-grained lock. The giant lock serializes the access to the entire code to a single user. The coarse-grained approach allows different processes to access independent parts of the system. Finally, the fine-grained approach allows different processes to access the same part of the system. Naturally, the complexity of the approach is proportional to its ability to execute in parallel.

Figure 1.2 – The essential approaches to parallelizing code. Thick lines depict locks and the flash symbol denote device interrupt [Kå05].

Unfortunately, the limitation to all of these solutions is that the developer must refactor the source code to be able to use them. The redesign also applies to the already parallel-compatible codes, as the procedure interfaces of different solutions are not the same. Additionally, the refactoring of source code has some limitations described as follows.

Software redevelopment cost - The software cost is difficult to estimate [Nas06] as an industry-grade application has many additional costs besides Lines of Code (LoC). They include but are not limited to the use of managers, technical documentation, tests, administrative activities (meetings, milestones), and support for post-release. The COCOMO model proposed by Boehm [Boe81] can estimate models with multiple parameters to estimate the software cost. Using such model, COCOMO can calculate the cost of redesigning a complex software such as the Linux kernel. We use the Linux kernel as an example for two reasons: (i) as stated before, parallel libraries can demand new features to the kernel to execute properly; and (ii) the kernel has always been open-sourced, a crucial feature to understand the impact of parallel source code refactoring. The discussion focuses on two openly available aspects: LoC and estimation of time spent.

First, redesigning the entire Linux kernel in 2004 was estimated to cost 612 million dollars [Whe19]. In 2011, the cost jumped to 3 billion dollars [sz19]. Additionally, there are two examples of adding new concurrency features to the kernel: the addition/removal of the Big Kernel Lock (BKL), and the addition of Read-Copy-Update (RCU). None of them had to redesign the entire kernel, but they did refactor multiple, up to all, subsystems of the kernel code.

The BKL was the first attempt of the Linux kernel to support Symmetric MultiProcessing (SMP) that allowed only one process to enter in the kernel space at a given time (i.e., BKL was a giant lock). This restriction required that every entry and exit kernel calls had to be refactored to acquire/release the BKL. Initially, there were only nine calls to the BKL code; yet, as the kernel code grew, it reached 761 calls [LH02] and over 200 source code files [Ber19b]. The increase of BKL calls is due to the effort of adding kernel concurrency. The giant lock was being shifted to a coarse-grained lock that allowed multiple processes in the kernel space when possible. Finally, the shift from a giant lock to a coarse-grained and then to a fine-grained lock system was the work result of countless developers and over ten years of refactoring [Ber19a].

Figure 1.3 – (a) RCU usage over the years [MBWW17]; (b) RCU and Locking usage over the years [MW08].

RCU is a specialized synchronization technique that can replace reader-writer locking. It defers operations to achieve a better read-side performance, which comes at the cost of having to deal with possible stale data. RCU was introduced to the Linux kernel in 2002 [MW08]. Figure 1.3a shows that RCU has continuously been employed for more than ten years – over 9000 calls in 2015. It did not replace all cases of locking, as shown in Figure 1.3b. A critical factor in this is the complexity of understanding the RCU mechanism, which is discussed shortly. Figure 1.1 shows all subsystems of the Linux kernel that employs RCU for synchronization. RCU influences over 16 million LoC across 15 subsystems.

| Subsystem | Uses  | LoC        | Uses / KLoC |

|-----------|-------|------------|-------------|

| ipc       | 92    | 9,094      | 10.12       |

| virt      | 82    | 10,037     | 8.17        |

| net       | 4519  | 839,441    | 5.38        |

| security  | 289   | 73,134     | 3.95        |

| kernel    | 885   | 224,471    | 3.94        |

| block     | 76    | 37,118     | 2.05        |

| mm        | 204   | 103,612    | 1.97        |

| lib       | 75    | 94,008     | 0.80        |

| fs        | 792   | 1,131,589  | 0.70        |

| init      | 2     | 3,616      | 0.55        |

| include   | 331   | 642,722    | 0.51        |

| drivers   | 1949  | 10,375,284 | 0.19        |

| crypto    | 12    | 74,794     | 0.16        |

| arch      | 249   | 2,494,395  | 0.10        |

| tools     | 2     | 144,181    | 0.01        |

| Total     | 9,559 | 16,257,496 | 0.59        |

Table 1.1 – Breakdown of RCU usage by kernel subsystems [MBWW17].

We presented two synchronization mechanisms introduced into the Linux Kernel: BKL and RCU. Both of them share essential aspects to the software development cost: many years of development to assimilate with existing code and increased difficulty in refactoring code. For instance, the substitution of RCU in 2014 with an alternative synchronization mechanism would affect 15 kernel subsystems and over 16 million lines of kernel code (Table 1.1).

Challenge of parallel code refactoring - Source code modification is always susceptible to introducing additional flaws in the software (i.e., software bug). McConnell estimates that software bugs range from 0 to 100 per thousand LoC as a consequence of the development methods employed [McC04]. Refactoring parallel code is even more susceptible than sequential code, as it is common for developers to be befuddled

with the use of synchronization techniques. The same synchronization mechanisms discussed previously can illustrate such a challenge.

The kernel concurrency became paramount to fulfill the multicore machine requirements. Therefore, the kernel changed, over time, its locking technique from a giant lock to a fine-grained approach. First, the transformation allowed the execution of several processes in independent subsystems, and, then, the execution of several processes into the same subsystem. The refactoring took over ten years and is described by Lindsay as [LH02]:

"Sometimes it's not clear that even the authors understood why it [BKL] was needed; they appear to have invoked it either because the code they were copying from invoked it, or simply because they feared angering the ancient gods of coding by omitting it."

Igno Molnár, one of the current maintainers of the scheduler and locking subsystems, said the following about removing the BKL [Mol19]:

"This task is not easy at all. 12 years after Linux has been converted to an SMP OS we still have 1300+ legacy BKL using sites. There are 400+ lock\_kernel() critical sections and 800+ ioctls. They are spread out across rather difficult areas of often legacy code that few people understand and few people dare to touch."

Lindsay also created a series of documents to detail every usage of the BKL in different kernel releases [Ber19b]. This document describes that multiple instances of the BKL use were: (i) confusing, and (ii) contradicted comments left by the original developers. The following is an example of BKL usage on the TTY subsystem:

"Held during *do\_tty\_hangup()* – code suggests it is protecting a data structure I can't find. A comment here screams "FIXME! What are the locking issues here?" which suggests the reasons for grabbing this lock may not be well understood."

Now that the kernel uses fine-grained locks it is even harder to refactor it again. Figure 1.4 shows the use of a coarse-grained lock specifically for the TTY subsystem called Big TTY Mutex (BTM). Developers for the TTY subsystem now must understand and respect these rules for locking. The challenge is that there are procedures that: (i) do not deal with BTM; (ii) acquire BTM; (iii) release BTM; and (iv) acquire and release BTM. However, there is no easy indicator of the specific case for each procedure besides documentation and source code commentary, both susceptible to be out-of-date. The

Figure 1.4 – Snippet of the locking scheme for the TTY subsystem [BC19a] [BC19b].

complexity is even higher for fine-grained locks because it requires dealing with multiple locks instead of a single one.

On the fine-grained approach, RCU is intended to be used for code that requires fast read-side performance. Different from reader-writer locks, the RCU readers never spin nor block. Figure 1.5 shows the effects of using either of these synchronization techniques. While RCU shows impressive results, it demands a thorough understanding of computer architecture design. Similar to other fine-grained approaches, RCU presents a trade-off: it offers performance gains with increasing code and maintainability complexity. McKenney and Walpole, leading developers of RCU, stated the following about the RCU gains and its design complexity [MW08] [McK19a]:

"This leads to the question "what exactly is RCU?", and, not infrequently, "how could RCU **possibly** work??", to say nothing of the assertion that RCU cannot possibly work."

"... RCU readers might access stale data, and might even see inconsistencies, either of which can render conversion from reader-writer locking to RCU non-trivial."

McKenney and Walpole also discuss their experience working with the Linux community to bring RCU to the kernel as RCU being dramatically changed by Linux than by Linux being changed by RCU. Free/Open Source Software (FOSS) developers understand that changing source code results in non-trivial refactoring of code; hence they require assurances. From the Linux community, McKenney and Walpole noted that they had to refactor the RCU code even before being accepted into the kernel. They also propose that source code be considered a liability instead of an asset, due to the complexity of servicing, supporting, and maintaining it [MW08].

Figure 1.5 – Execution of reader-writer lock and RCU. The green color is used to represent up to date data [McK19a].

Lost legacy source code - The essential requirement to refactor a legacy parallel application is the availability of the application source code. However, it is common for the legacy source code to be lost [Cur19] [McA19] [Wal19]. Even when the source code is available, it may be out-of-date [Mat19]. Hence, developers may prefer to rewrite the entire code than to rely on existing code by simulating the legacy application behavior [Fle19]. Redeveloping existing code, for either of the reasons listed earlier, goes against the expected practice of reusing software, as it increases the total software cost.

## 1.3 Problem Statement and Thesis Contributions

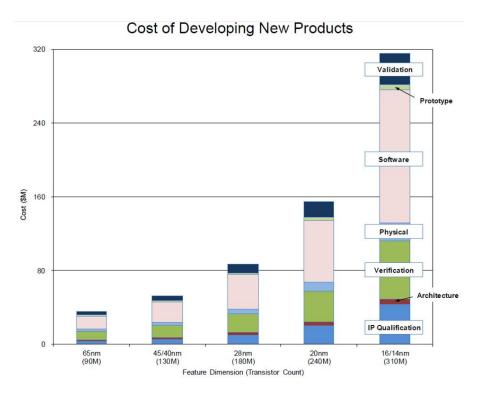

As previously explained, architectures powered by multiple cores require parallel applications to exploit its potential, and software development is costly regarding return on investment. Figure 1.6 shows that software development has been the dominant cost of developing new products for multiple generations of transistor technology, and it is getting worse.

Using the Linux kernel, as an illustration, we saw that refactoring a parallel code is also costly, demanding years of work. BKL was easily manageable in the beginning, with a dozen of calls, but it became strenuous when developers wanted to substitute it for a more refined approach, and its code has been widely distributed on the kernel, with over thousands of calls. For the adoption of the RCU, developers wanted assurances to make the shift for a new synchronization technique, as it required an understanding of a new paradigm for synchronizing existing code.

Figure 1.6 – Cost of each production step of multiple generations of transistor technology [Spe19].

Given the exposed motivation and problem description, this Thesis aims to provide faster application execution time without source code modification. We employ an HW/SW co-design for implementing our solution. The following set of specific objectives were defined to accomplish our goals:

- The definition of a solution, namely Subutai, to provide fast synchronization for legacy and novel parallel applications. The solution is demonstrated by performance benefits on analytical models, informal micro-benchmarks, and real applications achieved with no increase in application complexity;

- The presentation and development of two software components to interact with our hardware – an Operating System (OS) driver for HW/SW communication and a user space library that provides the PThreads Application Programming Interface (API);

- 3. The presentation of an analytical and Register Transistor Level (RTL) implementation of the hardware component, namely Subutai Hardware (Subutai-HW). It further allows for future development; and

- 4. The definition of two Subutai extensions optional features for accelerating parallel applications in particular scenarios. Firstly, we propose a scheduler policy, called Critical-Section Aware (CSA), for accelerating parallel applications in a highly-contended scheduling scenario, while maintaining the fairness of scheduler timeslot distribution. Secondly, we define the 'neocondition' synchronization variable a variable that behaves

as the condition variable from PThreads while removing the serialization of access to it (i.e., no mutex is required).

Figure 1.7 depicts the Subutai solution with a general-purpose computing stack, highlighting the components required (in red) and optional (in blue) for its operation. Subutai is comprised of: (i) a hardware module specialized in accelerating the essential synchronization operations (Subutai-HW); (ii) an OS driver for hardware/software communication (Subutai Driver); and (ii) a custom user space library, with the same function signature as PThreads, for parallel programming to use our solution without modifying the application source code. These components are discussed in-depth in the next chapters.

Figure 1.7 – Subutai components are highlighted in red in the computing stack. Subutai only requires changes in the (i) on-chip NI, (ii) OS NI driver and (iii) PThreads implementation. Additionally, a new scheduling policy (in blue) is explored in this work as an optional optimization.

Figure 1.8 shows the mechanisms employed in Subutai for accelerating synchronization operations of PThreads. We target all the data synchronization operations supported by PThreads, namely: mutex, condition, and barriers. We accelerate them by making use of our hardware module while maintaining the same functionality as provided by the software solution (i.e., libpthread). We currently only support the standard variants of these primitives; in other words, the attribute parameter attr must be nil. Generally, that is the case, as, for instance, the applications provided by PARSEC. Additionally, we provide a new synchronization primitive called neocondition, which is a derived primitive from the condition definition of PThreads. Its key difference is the absence of the use of mutexes; hence, no serialization is required to access it. Finally, the CSA policy was designed to accelerate critical sections of parallel applications for highlycontended scheduler scenarios without reducing the performance of other applications (i.e., a fair scheduler). This policy directly accelerates the mutex primitive since it creates the critical sections of an application. Besides, conditions also indirectly profited from the policy as it employs mutexes as well.

Figure 1.8 – Synchronization acceleration with the Subutai solution for different scenarios.

### 1.4 Document Structure

The remainder of this Thesis is organized into six chapters. Chapter 2 discusses synchronization operations on uni- and multiprocessor designs; this chapter also defines a basic terminology that is used throughout the document. Chapter 3 discusses the state-of-the-art related work on data synchronization. Chapter 4 discusses the design of hardware and software components required by Subutai; additionally, it presents the target architecture intended for using Subutai. Chapter 5 explores two optional extensions for Subutai: (i) a scheduling policy called CSA; and (ii) a new synchronization variable called neocondition. Chapter 6 presents the experimental results on area consumption, real parallel applications, and micro-benchmark. Finally, Chapter 7 presents the final considerations of this work and directions for future work.

# 2. DATA SYNCHRONIZATION IN PARALLEL APPLICATIONS

Take heed. You got it wrong. Admit it. Locking is \_hard\_. SMP memory ordering is HARD. So leave locking to the pro's. They \_also\_ got it wrong, but they got it wrong several years ago, and fixed up (...) This is why you use generic locking. ALWAYS.

#### Linus Torvalds

A program can be comprised of many computational units. These units range from threads, processes, coroutines, interrupt handlers, etcetera. When they work, the result of each computational unit might affect or be affected by those of the other computational units [McK04]. We use the term thread as a generic word to encompass these computational units.

A major concern in any parallel application is the access and update of application data. This problem is called synchronization, and many solutions have been studied and proposed over the past decades [McK04]. Solutions can be focused on proposing new software or hardware designs. Yet, all solutions need basic hardware operations to deal with atomicity.

This chapter reviews the design of data synchronization for parallel applications. Section 2.1 presents a brief discussion of synchronization for uniprocessor systems, while Section 2.2 discusses in-depth the challenging synchronization techniques for multiprocessor systems.

#### 2.1 Synchronization in Uniprocessor Systems

The use of synchronization primitives in uniprocessor systems may seem superfluous at first glance, as only a single thread may be running at a given time. However, this is not the case even for a sequential – one thread – application since interrupting and preemptive scheduling events can affect such systems. Functions that are called by both the application and the interrupt/schedule event do not behave correctly unless a reentrant version of the function exists. Unfortunately, multiple functions provided by the standard C library, such as malloc and fprintf [GCC19b], are not reentrant since they use static data. Thus, other solutions are required to deal with such a situation. A common solution is to disable interrupts and preemptive scheduling at the cost of loss of system responsiveness. Another solution is to provide locking primitives to the user application, although it may also be necessary to disable interrupts for sensitive locking operations [McK04].

#### 2.2 Synchronization in Multiprocessor Systems

Techniques that depend on disabling interrupts, like the ones described in the previous section, will fail on multiprocessor systems, as disabling interrupts affect only the local core [Moy13]. Rather than successfully suspending the execution of the interrupt code, the code will execute concurrently in another core. Therefore, it is not possible to rely solely on disabling interrupts; the ability to perform a set of operations without interruption is necessary. This is achieved by atomic operations.

An atomic operation is either entirely successful or entirely unsuccessful, and algorithms have to deal with both cases [Moy13]. Generally, unsuccessful cases retry the operation with either the same request or an updated one. Unfortunately, atomic operations are more expensive than simple instructions, and their cost increases as the number of threads access the same memory position. Figure 2.1 shows the scalability of a Fetch-And-Increment (FAI) operation on a simple counter variable: every thread reads the current value and increments it by one atomically. Figure 2.2 shows the throughput of different atomic operations, including FAI, for four architectures comprised of 48 (Opteron), 80 (Xeon), 8 (Niagara), and 36 (Tilera) cores [DGT13]. None of them has improved throughput for FAI operations after six threads; hence, the scalability is far from the ideal. A key factor in this phenomenon is the cache line bouncing [McK19a]. For every thread requesting to write, there will be multiple invalidation messages to the other caches through the interconnection architecture. In addition, these caches will need to fetch the line with the new value as well. In this case, the elimination of cache bouncing requires redesigning the application. A second factor influencing scalability is the necessity of memory barriers<sup>1</sup>. Developers that worked with lock-based algorithms may never have to deal with memory barriers directly; the same cannot be said for lock-free and operating system designers. The importance of memory barriers is explained in the following section.

#### 2.2.1 Memory and Compiler Barriers

Architecture optimizations have been developed to make user applications run faster while running the same source code. A relaxed memory model is an optimization that affords opportunities to improve application performance [Mar19] for uniprocessoring as well as multiprocessoring systems. They include but are not limited to [HMDZ19]: reordering instructions, reordering memory operations, deferral of memory operations, speculative loads, and speculative stores. However, some optimizations may produce an improper result; for instance, the processor may change the order of memory read/write operations. Figure 2.3a

<sup>&</sup>lt;sup>1</sup>The use, for instance, of GCC atomic builtin operations imply full memory barriers [GCC19a].

Figure 2.1 – Atomic increment scalability on a Nehalem Intel processor [McK19a].

Figure 2.2 – Throughput of different atomic operations on a single memory position [DGT13].

depicts a reordering example provided by the software manual of Intel [Int17]. Suppose that both variables X and Y are initialized as 0, and both processors<sup>2</sup> are running in parallel. It is natural to assume that the parallel execution produce [r1 = r2 = 1]. Nevertheless, according to the Intel manual [Int17], it is perfectly valid that the result can also be [r1 = r2 = 0], [r1 = 1, r2 = 0], or [r1 = 0, r2 = 1]. The reordering of operations, demonstrated in this example, is not restricted to Intel processors.

The assumption of [r1 = r2 = 1] may not hold because the processor can, unless stated otherwise, reorder a load with an earlier store to a different memory location, as they do not have an explicit dependency. Figure 2.3b shows one possibility of the application execution, where the assumption does not hold. This behavior breaks a simple but fundamental assumption that generated code will be executed in the order described by the source code.

Therefore, it is mandatory to inform the processor of the data/control dependency of instructions to avoid reordering, as shown in Figure 2.3b. This is done by using a memory

<sup>&</sup>lt;sup>2</sup>Although some authors use the term 'processor' to designate the processing unit, instead of 'core,' we emphasize that they are equivalent for the purposes of this work.

Figure 2.3 – Reordering example from the Intel Manual [Int17] [Pre19b].

barrier. There are multiple types of memory barriers, and not all Instruction Set Architectures (ISAs) need all of them. Thus, the lack of a standard behavior makes creating portable code harder, as applications can execute as expected in one ISA, but not in another. Following, we detail some of the memory barriers currently employed by different ISAs.

Table 2.1 is organized in three columns. The first column is a mnemonic name for the barrier. The second column is the guarantee that the barrier provides the application. Note that we use a generic specification of the guarantee; the real guarantee may vary according to each ISA. Finally, the third column identifies which ISAs need to use the barrier to receive the guarantee. For ISAs not specified, they do not need to use any barrier as it is already guaranteed by the ISA specification. The SPARC specification allows three implementations for its ISA (RMO, PSO, and TSO).

| Barrier    | Guarantees<br>(All (1) instructions executed prior to<br>the barrier commit before the core execute<br>any additional (2) instructions) | Required by ISA<br>(x86, ARM, PowerPC, ALPHA,<br>SPARC-{RMO, PSO, TSO}) |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| LoadLoad   | (1) Load; (2) Load                                                                                                                      | ARM, PowerPC, ALPHA,<br>SPARC-RMO                                       |

| LoadStore  | (1) Load; (2) Store                                                                                                                     | ARM, PowerPC, ALPHA,<br>SPARC-{RMO, PSO}                                |

| StoreStore | (1) Store; (2) Store                                                                                                                    | ARM, PowerPC, ALPHA,<br>SPARC-{RMO, PSO}                                |

| StoreLoad  | (1) Store; (2) Load                                                                                                                     | x86, ARM, PowerPC, ALPHA,<br>SPARC-{RMO, PSO, TSO}                      |

Table 2.1 – Overview of some memory barriers [Int17] [Lea19] [SPA93].

Table 2.2 establishes the use of memory barriers for the locking and unlocking operations on different ISAs for the GNU implementation of the standard C library. The acquire barrier is comprised of LoadLoad and LoadStore barriers. The release barrier is

comprised of LoadStore and StoreStore [HMDZ19]. The full barrier is the combination of all barriers presented in Table 2.1. However, it is important to state that the barriers of Table 2.1 are only applied when the architecture requires them. For instance, the x86 architecture applies only the StoreLoad barrier for the full memory barrier mentioned in Table 2.2.

Environmentlock memory barrierunlock memory barrierglibc 2.4 Itaniumfullfullglibc 2.4 x86fullfullglibc 2.4 ALPHAacquirereleaseglibc 2.4 PowerPCacquirerelease

Table 2.2 – Memory barriers used by some PThread implementations for mutexes. Adapted from [Boe07]

The estimation of the general cost of memory barriers is challenging, as it: (i) affects ISAs in different ways; and (ii) inhibits speculative operations that exist or not depending on the application employed. Memory barriers must be employed only when strictly necessary to avoid performance degradation. Agner Fog found that the minimum latency for a full memory barrier is 23 clock cycles for an Intel Nehalem architecture [Fog19]. Boehm [Boe07] shows that the cost of a pair of lock and unlock operation calls can vary by roughly a factor of two depending on whether a memory barrier is needed in the unlock operation.

Unfortunately, reordering instructions and memory operations are not limited to the processing unit [Boe07]. The reorder can occur even earlier by optimizations done at the compilation time. Until C11 (C standard revision), concurrency was not built on the C language itself. Hence, the C compiler assumes, unless stated otherwise, that there is only one thread of execution in a given application [Cor19]. The effect of assuming a single-threaded application is shown in Listings 2.1, 2.2, 2.3, 2.4.

Listing 2.1 is a lock-free message processing application. The message is captured on process execution, and a flag called ready is set for this event. The message and flag are shown in lines 4 and 5. Periodically, an interrupt arrives at the application and, if the flag is set, the packet is processed. The corresponding code is shown in lines 11 and 12. Alas, there is nothing to prevent the compiler from switching lines 4 and 5 (as shown in Listing 2.2), as there is no indication of dependency. Now the flag is set before the message is fetched, resulting in an application execution with undefined behavior.

Listing 2.3 is a simple application composed of an if-then-else statement. The variable var\_b may be equal to the value of 42 or variable var\_a, if var\_a is zero or not, respectively. The compiler can optimize this code by removing one of the branching scenarios; it speculates that the value of variable var\_a is zero, so var\_b is 42 and writes to var\_b again otherwise. The generated code is shown in Listing 2.4. For a single-threaded application,

```

1

void

process_level(void)

2

3

{

4

msg = get_message();

5

ready = true;

6

}

7

8

void

9

interrupt_handler(void)

10

{

11

if (ready)

12

process_message(msg);

13

}

```

Listing 2.2 – Generated code for lock-free message processing [HMDZ19].

```

1

void

2

process_level(void)

3

{

4

ready = true;

5

msg = get_message();

6

}

7

8

void

9

interrupt_handler(void)

10

{

11

if (ready)

12

process_message(msg);

13

}

```

this represents a performance gain, and it maintains the expected application behavior. For multi-threaded applications, this generates a subtle spurious value of 42 that can be seen by other threads. Once again, this behavior breaks the assumption that compiled code will be executed in the order expected by the source code [HMDZ19].

Listings 2.1 and 2.3 demonstrate cases that demand compiler barriers to prevent the compiler from moving memory accesses from one side of the barrier to the other side. However, memory barriers already imply the use of compiler barriers [HMDZ19], so they are not explicitly required when a memory barrier is employed.

| 1 | int var_a;            |

|---|-----------------------|

| 2 | <pre>int var_b;</pre> |

| 3 | ()                    |

| 4 | if (var_a)            |

| 5 | <pre>var_b = a;</pre> |

| 6 | else                  |

| 7 | var_b = 42;           |

Listing 2.3 – Source code from an if statement [HMDZ19].

|   | Listing 2.4 – Compiled source code from Listing 2.3 [HMDZ19]. |

|---|---------------------------------------------------------------|

| 1 | int var_a;                                                    |

| 2 | <pre>int var_b;</pre>                                         |

| 3 | ()                                                            |

| 4 | var_b = 42;                                                   |