# Design of a generic digital front-end for the internet of things

Ali Zeineddine

### ▶ To cite this version:

Ali Zeineddine. Design of a generic digital front-end for the internet of things. Other [cs.OH]. CentraleSupélec, 2019. English. NNT: 2019CSUP0001. tel-02877254

### HAL Id: tel-02877254 https://theses.hal.science/tel-02877254

Submitted on 22 Jun 2020

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THESE DE DOCTORAT DE

### **CENTRALESUPELEC**

COMUE UNIVERSITE BRETAGNE LOIRE

ECOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies

de l'Information et de la Communication

Spécialité : Automatique Productique et Rob

Spécialité : Automatique, Productique et Robotique - Signal, Image,

Vision - Télécommunications

Par

### « Ali ZEINEDDINE »

« Conception d'un Front-End Numérique Générique pour l'Internet des Objets »

« Design of a Generic Digital Front-End for the Internet of Things »

Thèse présentée et soutenue à « Rennes », le « 06 Novembre 2019 »

Unité de recherche : IETR - SCEE

Thèse N°: 2019CSUP0001

#### Rapporteurs avant soutenance:

Christophe JEGO Professeur des Universités, IMS Bordeaux, France

Markku RENFORS Professor of Telecommunications, Tampere University of Technology, Finlande

### **Composition du Jury:**

Présidente Marie-Laure BOUCHERET Professeur des Universités, INP-ENSEEIHT / IRIT, France

Rapporteurs Christophe JEGO Professeur des Universités, IMS Bordeaux, France

Markku RENFORS Professor of Telecommunications, Tampere Uni. of Technology, Finlande

Examinateurs Dominique MORCHE Ingénieur de Recherche au CEA-LETI, Grenoble, France

Marie-Laure BOUCHERET Professeur des Universités, INP-ENSEEIHT / IRIT, France

Encadrants Amor NAFKHA Enseignant-Chercheur à CentraleSupélec, Campus de Rennes, France

Pierre-Yves JEZEQUEL Ingénieur Expert Technique et Chef de Projet à TDF, Liffré, France Stéphane PAQUELET Responsable de Laboratoire et Senior Scientist à b-com, Rennes, France

Directeur de thèse Christophe MOY Professeur des Universités, Université de Rennes 1 / IETR, France

"Ecoutez, je crois que j'ai fait tout ce qui était en mon pouvoir, j'ai fait le maximum, à ce niveau là où on en est, je crois qu'on peut dire à la grâce de Dieu, et allez..."

- Simon JÉRÉMI

### Acknowledgments

This thesis is the result of three years of work financed by TDF, and took place at the premises of b-com. Through the few lines below, I would like to acknowledge, at the beginning of this thesis, the help and support of many people, without whom this thesis and its success would not have been possible. These acknowledgments are not in order of importance and are not limited to the names mentioned.

My deepest gratitude goes first to my supervisor, Christophe Moy, from University of Rennes 1, for his continuous guidance throughout these three years, for his help in theoretical and practical developments, and of course for the efforts he put into revising every article published, including this thesis manuscript. I also appreciate the time he dedicated to manage many administrative procedures all along the duration of this PhD.

I am very grateful to TDF, for proposing and financing this PhD. I would like to thank Pierre-Yves Jezequel for investing his time into supervising my work, and for his valuable insights on many subjects. I also appreciate the help of my administrative supervisor Christian Nieps who always ensured that my PhD is progressing well. I would also like to thank François Picand, the director of the innovation department at TDF, who regularly followed the advancement of my PhD, and showed genuine interest in my work. Last but not least, special thanks go to Amélie Kerbellec who helped me in my integration at TDF and in managing many administrative procedures at work.

During these three years, I worked at b-com in a very productive environment. I am deeply grateful to Stéphane Paquelet, my supervisor at b-com, who initiated many of the ideas developed in this thesis thanks to his deep mathematical and technical expertise in the domain, and provided the basis of most contributions. I am also grateful to Michel Corriou, my research lab director, for ensuring I had the needed resources for performing my work at b-com, and presenting my work in international conferences. I would also like to address special thanks to Bertrand Guilbaud, the CEO of b-com, for following the advancement of my work, and for his cordial connection with the b-com staff.

My most special thanks goes to Amor Nafkha, my supervisor at CentraleSupélec, who worked closely with me to develop many ideas, provided me with many insights, and also helped me on many occasions to manage both professional and personal aspects of my PhD life. I would also like to thank Karine Bernard from CentraleSupélec, who helped me in many administrative procedures. I'm also grateful to Philippe Benabes and Francis Trélin, who gave me access to the ASIC design tools available in their laboratory. I will surely not forget to recognize the efforts of Jacques Palicot, the recently retired director of the SCEE research team, who put constant effort to make sure that the work of all the PhD students in the team is successful.

This work was possible thanks to the "Investissements d'avenir" project initiated by the French government in 2010, and is underway until today. I thank everyone who worked on this project, from governmental, to industrial, to academic entities.

Finally, I would like to address one big *thank you* to my family, friends and colleagues, who were around me during these three years, and who constantly tried to remind me that there is more in life than just work.

### Résumé

Le nombre de technologies et de normes de communications sans fil est en augmentation constante afin de fournir des solutions de communication à distance pour les différents besoins technologiques actuels et à venir. Ceci est particulièrement le cas de l'Internet des objets (IoT), où déjà de nombreuses solutions sont disponibles, et de nombreuses autres sont attendues. Pour un déploiement efficace du réseau IoT, l'interopérabilité entre les différentes solutions est essentielle pour éviter la fragmentation de ce réseau, ce qui augmente ses coûts d'installation et d'exploitation et complique sa gestion. L'interopérabilité sur le plan physique est fournie par des modems multistandards prenant en charge le plus grand nombre de normes avec un coût de mise en œuvre minimal. Ces modems sont possibles grâce au front end numérique (DFE), qui offre une interface radio flexible capable de traiter une large gamme de signaux. Cette thèse développe tout d'abord deux architectures génériques de DFE pour la transmission et la réception, pouvant être facilement adaptées aux différentes normes IoT. Ces architectures mettent en évidence le rôle principal du changement de rythme (SRC) dans le DFE et l'importance de l'optimisation de la mise en œuvre de cette fonction. Cette optimisation est ensuite réalisée grâce à une étude approfondie des fonctions SRC, et au développement de nouvelles structures plus efficaces en termes de complexité de mise en œuvre et de consommation, pour des performances égales ou supérieures. La dernière partie de la thèse concerne l'optimisation de la mise en œuvre matérielle du DFE, réalisée par le développement d'une méthode de quantification optimale qui minimise l'utilisation de ressources matérielles tout en garantissant un certain niveau de performance. Les résultats obtenus sont enfin mis en valeurs en comparant différentes stratégies de mise en œuvre sur des cibles FPGA et ASIC.

### Abstract

The number of wireless communication technologies and standards is constantly increasing to provide communication solutions for today's technological needs. This is particularly relevant in the domain of the Internet of Things (IoT), where many standards are available, and many others are expected. To efficiently deploy the IoT network, the interoperability between the different solutions is critical in order to avoid the fragmentation of this network, which increases its installation and operation costs, and complicates its management. Interoperability on the physical level is achieved through multi-standard modems that support the largest number of standards with minimal added implementation costs. These modems are made possible through the digital front-end (DFE), that offers a flexible radio front-end able of processing a wide range of signal types. This thesis first develops a generic architecture of both transmission and reception DFEs, which can be easily adapted to support different IoT standards. These architectures highlight the main role of sample rate conversion (SRC) in the DFE, and the importance of optimizing the SRC implementation. This optimization is then achieved through an in-depth study of the SRC functions, and the development of new structures of improved efficiency in terms of implementation complexity and power consumption, while offering equivalent or improved performance. The final part of the thesis addresses the optimization of the DFE hardware implementation, which is achieved through developing an optimal quantization method that minimizes the use of hardware resources while guaranteeing a given performance constraint. The obtained results are finally highlighted through implementing and comparing different implementation strategies on both field programmable gate array (FPGA) and application specific integrated circuit (ASIC) targets.

## Résumé Étendu en Français

### Contexte et Motivations

Suite aux dernières révolutions technologiques de l'Internet et les réseaux mobiles qui ont rendu possible la communication quasi permanente et directe des hommes à travers la planète, une nouvelle révolution commence à prendre forme qui va permettre à presque tout objet de communiquer. On appelle "Internet des objets" (Internet of Things IoT) le concept de réseau reliant ces objets, qui devrait accueillir plus de 75 milliards objets d'ici 2025. Chaque objet connecté répond à une application spécifique qui impose des contraintes particulières et la grande variété d'applications crée une importante diversité de contraintes. Par conséquent, une multitude de technologies et de standards de communication sont proposés, chacune utilisant des techniques de transmission et des caractéristiques de signal spécifiques, pour proposer une solution à un certain cas d'application. Parallèlement, de nouvelles normes sont en cours de développement qui ont l'objectif de prendre en charge le plus grand nombre de cas d'applications. Un exemple est le réseau mobile de quatrième génération (4G) Long Term Evolution (LTE), qui définit de nombreuses catégories d'appareils, chacune utilisant des techniques de transmission spécifiques au cas d'application ciblé. La cinquième génération de ce réseau vise à encore plus considérer de cas différents. En outre, les concepts de radio logicielle et de radio intelligente visent la construction des systèmes radio hétérogènes de plus en plus complexes, capables de commuter automatiquement de technologie de communication en fonction de l'environnent radio.

Cette diversité des solutions de communication crée un défi pour les opérateurs de réseau et les fournisseurs de services de télécommunication. C'est le cas à TDF, un des principaux opérateurs français d'infrastructures radio, soucieux du déploiement efficace des solutions IoT récemment proposées et du futur réseau mobile de cinquième génération (5G). Si chacune des solutions de communication est traitée indépendamment des autres, le déploiement du réseau devient fragmenté, ce qui tue l'interopérabilité, complique la gestion de la qualité de service (Quality of Service QoS) et augmente considérablement les coûts de déploiement (comprenant l'installation initiale, la maintenance et la consommation). Ces problèmes sont au cœur des systèmes 5G. TDF s'est associé à l'institut de recherche technologique (IRT) b-com pour développer des solutions de déploiement efficaces qui favorisent et améliorent l'interopérabilité dans les futurs réseaux.

Il est alors utile de se référer au modèle usuel de représentation en couches des systèmes de communication, le modèle OSI, pour comprendre sur une description suffisamment générique et abstraite, comment ces questions peuvent être traitées. Nous pourrions nous contenter d'assurer l'interopérabilité et les fonctions transverses sur les couches dites « hautes » (du transport à l'application), mais ce serait négliger les questions de compacité et sobriété énergétique des équipements, critiques aussi bien pour les objets que pour les stations de collectes (Gateways). Il faut donc considérer les couches « matérielles », i.e physique (traitements analogiques et numériques), liaison (adresse MAC), paquet (adresse IP). La priorité de ce travail est la couche physique.

S'agissant de la couche physique, les enjeux d'interopérabilité et de transversalité se ramè-

nent à fournir une plateforme modem suffisamment flexible pour accueillir les différentes technologies. En ajoutant les contraintes de compacité et sobriété énergétique, les choix techniques s'orientent naturellement vers une mutualisation des fonctions sur des unités de traitement définitivement câblées (compacité et consommation) mais paramétrables par un jeu de registre permettant le basculement d'un système à l'autre (flexibilité). Il s'agit d'une vision Software Defined Radio (SDR) dans laquelle le partage des traitements entre le processeur et la structure matérielle câblée (FPGA/ASIC) est plutôt centré sur cette dernière, qui est chargée des traitements simples (additions/multiplications), systématiques et paral-lélisables, tandis que le processeur se voit affecté des calculs complexes dont les contraintes de temps d'exécution sont relâchées. Le niveau d'optimalité d'un tel système peut être évalué selon le critère suivant : le degré de flexibilité qui est assurée vis-à-vis d'un certain nombre de technologies considérées, et dans un mode donné, le degré de complexité ou de consommation du modem par rapport à celle qu'aurait une réalisation dédiée pour ce mode.

### Objectifs et Contributions

On peut décomposer la partie numérique du modem en trois parties : le front-end numérique (Digital Front-End DFE), le traitement en bande de base et la correction d'erreur (Forward Error Correction FEC). Dans un modem moderne, le DFE est généralement réalisé en matériel, tandis que les deux autres parties sont souvent réalisées en logiciel. Par "matériel", on désigne ici une mise en œuvre sur cible matérielle numérique tels que les FPGA ou ASIC (conçue en VHDL). Par "logiciel", on considère une mise en œuvre sur un processeur (par programmation en langage informatique). Ce travail vise l'optimisation de la mise en œuvre matérielle du front-end numérique (DFE) afin de réduire les coûts et la consommation de l'interface radio.

Le DFE comporte plusieurs fonctions de traitement du signal, mais il a deux rôles principaux: le filtrage et le changement de la fréquence d'échantillonnage ( $Sample\ Rate\ Conversion\ SRC$ ). La fonction SRC est souvent intégrée dans autres fonctions du DFE, comme le filtrage et la synchronisation. Cela fait du SRC la fonction la plus essentielle du DFE. Les principaux objectifs de la thèse sont alors définis :

- 1. Concevoir une architecture générique et efficace du DFE qui s'adapte facilement à toute norme ou technologie de communication, en particulier pour l'IoT.

- Optimiser la fonction SRC dans le DFE en développant des nouvelles solutions, puis mettre en œuvre les structures nouvellement développées et évaluer leurs niveaux de complexité et de consommation.

- 3. Définir une méthode à suivre pour la mise en œuvre matérielle, à utiliser avec toutes les fonctions du DFE, concernant la quantification et l'architecture du circuit numérique.

Pour parvenir à ces objectifs, cette thèse développe les contributions suivantes.

La première de ces contributions est la proposition d'architectures génériques pour le DFE dans les deux sens d'émission et de réception, ainsi que leur intégration dans le modem en combinaison avec le front-end analogique. Cette contribution est présentée dans le Chapitre 1. Ce chapitre présente d'abord le contexte de l'IoT ainsi que le problème de la diversité des normes et des technologies de communications sans fil. Un modem multistandard est alors proposé comme solution, le DFE étant un élément principal de ce modem. Puis, les fonctions principales du DFE sont présentées, qui sont ensuite utilisées pour construire les architectures génériques du DFE. Ces architectures génériques mettent en évidence que les fonctions SRC, qui sont utilisées à plusieurs endroits dans le DFE, constituent le cœur de ce système et que leur optimisation est cruciale pour une mise en œuvre efficace de l'ensemble du modem.

La deuxième contribution développée dans le Chapitre 2 propose une nouvelle présentation concise des filtres SRC disponibles dans la littérature. Le but de cette présentation est de

rassembler la littérature des filtres SRC sous une seule vision unifiée. Cette présentation est réalisée en regroupant les cinq principales structures de filtre SRC à réponse impulsionnelle finie (FIR) autour d'une racine commune, le filtre FIR à phase linéaire, à partir de laquelle les cinq structures sont ensuite dérivées. En pratique, il existe deux catégories de SRC : l'une réalisant un facteur d'interpolation ou de décimation entier, éventuellement grand, la seconde réalisant une fraction proche de un, aussi précise que l'on veut. Leur combinaison permet systématiquement d'atteindre un changement de rythme arbitraire (ASRC). S'agissant de la mise en œuvre du SRC fin, les choix techniques restent encore très ouverts à l'intérieur du cadre général des filtres à retard variable (V-FDF), qui s'avèrent aujourd'hui les structures les plus appropriées.

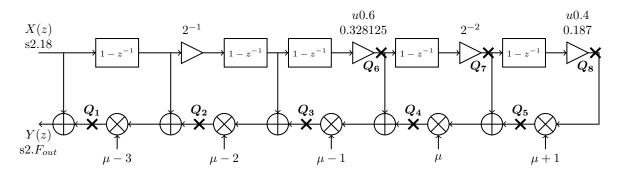

Le Chapitre 2 présente également les aspects de la mise en œuvre matérielle pour chaque structure afin de fournir un guide complet et concis sur le SRC, tant du point de vue théorique que pratique. Cette vision unifiée est développée pour les filtres SRC d'interpolation dans le Chapitre 2, le cas complémentaire des filtres SRC de décimation est présenté dans l'Appendice A. La suite du travail étudie en profondeur la structure de Newton, et nous montrons son intérêt pour construire de nouvelles solutions SRC plus efficaces.

Le Chapitre 3 aborde deux aspects théoriques liés à la structure de Newton, et nécessaires pour définir de manière rigoureuse la réponse du filtre, ce qui constitue la troisième contribution. Tout d'abord, la relation directe entre les expressions de l'interpolation de Lagrange et la série de Newton est développée. Cette relation est ensuite utilisée pour démontrer la convergence de la fonction de transfert de la structure de Newton.

La quatrième contribution est la conception de nouveaux filtres SRC basés sur la structure de Newton. Jusqu'en 2009, la structure de Farrow était la solution la plus répandue pour la mise en œuvre des V-FDF [Far88]. Ensuite, la structure de Newton [Tas96] a été proposée afin de tirer profit de sa simplicité et de sa faible complexité [Leh09], mais limitée à un seul gabarit de filtrage, celui de l'interpolation de Lagrange. En 2016, le travail publié par D. Lamb et al. dans [Lam16] a montré que les structures de Farrow et de Newton peuvent être reliées par une transformation matricielle. Cette transformation permet d'exploiter davantage la structure de Newton en la modifiant pour mettre en œuvre différentes réponses V-FDF. C'est cette approche que nous nous proposons d'étendre dans cette contribution. Ceci fournit non seulement des solutions ASRC plus performantes, mais réduit également la complexité matérielle, et donc le coût et la consommation du DFE.

Trois nouvelles modifications sont développées et présentées dans le Chapitre 4. Tout d'abord, nous proposons une modification de la structure de Newton pour l'interpolation de Hermite. Cette interpolation est un cas général d'interpolation de Lagrange, dans lequel les contraintes d'égalité sont imposées non seulement aux valeurs des échantillons, mais également à leurs dérivées. Par conséquent, davantage de degrés de liberté sont disponibles pour ajuster l'interpolation utilisée. En général, la réponse du filtre d'interpolation de Hermite conserve la même bande passante que celle de l'interpolation de Lagrange, tout en améliorant les performances en termes de rejet des images. Parallèlement à cette performance de filtrage améliorée, la mise en œuvre de cette interpolation offre une complexité plus faible vis-à-vis la structure de Newton classique pour l'interpolation de Lagrange.

La transformation de Farrow-Newton permet théoriquement la mise en œuvre de toute interpolation polynomiale par le biais d'une structure de Newton généralisée. Cependant, en s'appuyant sur cette transformation, la relation entre les coefficients de cette structure généralisée et la réponse du filtre n'est pas connue. Pour trouver cette relation, l'expression de la réponse fréquentielle de la structure de Newton généralisée doit être développée en utilisant les propres coefficients de cette structure. Cela fait, il est ensuite possible d'utiliser des méthodes d'optimisation de filtre permettant d'approximer une réponse de filtre idéale souhaitée. Ces méthodes d'optimisation offrent également l'avantage d'imposer des contraintes pour personnaliser la structure optimisée. Par exemple, il est possible d'imposer que seules les lignes de

retour provenant du dernier élément de retard soient possibles. Cela permet de concevoir des structures de Newton optimisées ayant des performances comparables à celles des structures de Farrow optimisées, tout en nécessitant qu'une fraction de complexité de ces dernières.

La structure de Newton classique peut être identifiée dans toutes les nouvelles structures proposées. En écrivant la fonction de transfert sous la forme d'une combinaison linéaire de celle de la structure de Newton classique et de n'importe quelle seconde structure de Newton modifiée, il est possible de trouver des structures qui sont reconfigurables via un seul paramètre variable. Une telle structure est capable de mettre en œuvre les deux interpolations considérées, ainsi qu'une plage d'interpolations combinant les caractéristiques des deux interpolations en faisant varier le paramètre de reconfiguration. De plus, cette structure reconfigurable garde une complexité comparable à celle de la structure de Newton classique, ce qui n'est pas le cas si on rend la structure de Farrow reconfigurable. Cela est dû au fait que le paramètre de reconfiguration introduit ne modifie que certains coefficients de la structure de Newton, et par conséquent seul un nombre limité de multiplieurs doit être ajouté pour permettre la reconfigurabilité. Ces structures reconfigurables offrent une solution très intéressante pour les applications de radio intelligente ou les systèmes multistandards, dans lesquels le système doit s'adapter en permanence au signal reçu et à son environnement.

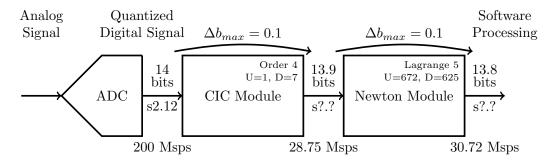

La suite de ce travail aborde les problèmes d'optimisation de la quantification et de la mise en œuvre matérielle. La cinquième contribution, présentée dans le Chapitre 5, est le développement d'un algorithme simple de quantification optimal, qui trouve le nombre d'éléments binaires minimal pour représenter chaque signal, en garantissant une contrainte de précision donnée. La première section de ce chapitre présente les principes et l'état de l'art des méthodes de quantification disponibles dans la littérature. La deuxième section développe la nouvelle méthode analytique de quantification optimale. La dernière section applique la méthode développée à un exemple d'un DFE simpliste, afin de démontrer l'utilisation pratique de cette méthode.

Le Chapitre 6 développe la dernière contribution, qui est la réalisation matérielle de différents filtres SRC sur cibles FPGA et ASIC. La première partie étudie les contraintes de mise en œuvre et les stratégies utilisées pour développer des architectures matérielles. Cette étude montre l'importance d'utiliser la stratégie de mise en œuvre appropriée en fonction des exigences de l'application. Puis, les architectures de plusieurs structures de SRC sont développées en utilisant les différentes stratégies de mise en œuvre. La complexité et la consommation de ces implémentations sont analysées et comparées pour mettre en évidence les avantages de chaque architecture. Un résultat important du travail de cette thèse est le développement des architectures qui permettent la mise en œuvre du SRC d'un facteur fin à un coût similaire à celui de SRC grossier, ce qui était inconcevable avant le début de ce travail.

### Conclusion et Perspectives

Cette thèse propose une architecture générique optimisée d'un front-end numérique destiné aux modems multistandards de l'Internet des objets (IoT) en ciblant la fonction SRC au cœur du DFE. Les développements réalisés dans ce travail offrent des solutions SRC plus flexibles avec une efficacité améliorée. La deuxième optimisation est faite en développant une méthode de quantification optimale utilisée ensuite pour une mise en œuvre matérielle efficace du modem multistandard.

Les études et développements réalisés dans cette thèse ouvrent par la suite de nombreux nouveaux sujets de recherche. Les sujets les plus prometteurs sont: le développement des mesures de performance du SRC plus exhaustives, l'intégration du SRC dans des bancs de filtres reconfigurables, l'automatisation de la méthode de quantification, et l'optimisation éventuelle du reste des fonctions du DFE.

## Contents

| A                         | cknov                    | wledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | v            |

|---------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| $\mathbf{R}$              | ésum                     | ıé                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | vi           |

| A                         | bstra                    | net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ix           |

| $\mathbf{R}$              | ésum                     | né Étendu en Français                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | X            |

| $\mathbf{C}$              | onter                    | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xvi          |

| $\mathbf{L}^{\mathrm{i}}$ | ist of                   | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | XX           |

| Li                        | ist of                   | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | XX           |

| In                        | trod                     | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1            |

| 1                         | Dig<br>1.1<br>1.2<br>1.3 | Internet of Things Network  1.1.1 What is the Internet of Things  1.1.2 IoT Networks Types, Standards, and Technologies  1.1.3 Internet of Things Deployment Challenges  Multi-standard Internet of Things Modems  1.2.1 Generic Architecture  1.2.2 Hardware/Software Partitioning  1.2.3 Multi-standard LP-WAN Modem Example  Generic Digital Front-End  1.3.1 The Main Roles of the Digital Front-End  1.3.2 Digital Front-End Core: Linear Functions  1.3.3 Complete Digital Front-End with Enhancement Functions  Conclusion | 6<br>9<br>11 |

| 2                         | Uni<br>2.1<br>2.2<br>2.3 | fied Vision of Sample Rate Conversion FIR Filters  Sample Rate Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |

|                           | 24                       | CIC Filter: A Multiplier Free Solution for Coarse SRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46           |

xvi CONTENTS

|   |            | 2.4.1 Filter Structure Derivation                                  |

|---|------------|--------------------------------------------------------------------|

|   |            | 2.4.2 Practical Implementation                                     |

|   | 2.5        | Newton Structure: A Low Cost Solution for Arbitrary SRC            |

|   |            | 2.5.1 Newton Structure Derivation                                  |

|   |            | 2.5.2 Farrow to Newton Transformation 51                           |

|   |            | 2.5.3 Practical Implementation                                     |

|   | 2.6        | Comparison and Applications                                        |

|   |            | 2.6.1 Characteristics Comparison                                   |

|   |            | 2.6.2 Implementing an SRC Application                              |

|   | 2.7        | Conclusion                                                         |

| _ |            |                                                                    |

| 3 |            | oretical Insights on the Newton Structure 57                       |

|   | 3.1        | Equivalence Between Lagrange and Newton Interpolations             |

|   |            | 3.1.1 Lagrange Interpolation                                       |

|   |            | 3.1.2 Newton's Forward Difference Formula                          |

|   |            | 3.1.3 Newton's Backward Difference Formula                         |

|   | 3.2        | Newton Structure Transfer Function Convergence 61                  |

|   |            | 3.2.1 Fractional Delay Definition 61                               |

|   |            | 3.2.2 The Newton Structure Transfer Function                       |

|   |            | 3.2.3 Proof of convergence                                         |

|   | 3.3        | Conclusion                                                         |

| 4 | Cor        | neralized and Reconfigurable Newton Structures 69                  |

| 4 | 4.1        | Generalized Newton Structure                                       |

|   | 4.1        | 4.1.1 Generalization of the Newton Structure                       |

|   |            | 4.1.2 Farrow to Newton Transformation                              |

|   |            |                                                                    |

|   | 4.0        | 4.1.3 Vector Form Transformation                                   |

|   | 4.2        | Modified Newton Structure - Hermite Interpolation                  |

|   |            | 4.2.1 V-FDF Based on Hermite Interpolation                         |

|   |            | 4.2.2 Proposed Low Complexity Hermite Interpolation Based V-FDF 74 |

|   |            | 4.2.3 Performance and Complexity                                   |

|   | 4.3        | Re-configurable Newton Structure                                   |

|   |            | 4.3.1 Derivation of the Transfer Function                          |

|   |            | 4.3.2 Complexity Comparison                                        |

|   |            | 4.3.3 Application Examples                                         |

|   | 4.4        | Optimized Newton Structure                                         |

|   |            | 4.4.1 Generalized Newton Structure Frequency Response 82           |

|   |            | 4.4.2 Filter Optimization Application                              |

|   | 4.5        | Conclusion                                                         |

| 5 | Ont        | imal Fixed-Point Quantization 87                                   |

| Э | -          | •                                                                  |

|   | 5.1        | Hardware Quantization                                              |

|   |            | 5.1.1 Quantization Fundamentals                                    |

|   | <b>.</b> . | 5.1.2 Literature of Quantization Methods                           |

|   | 5.2        | Optimal Analytical Quantization                                    |

|   |            | 5.2.1 Integer Part Quantization                                    |

|   |            | 5.2.2 Fractional Part Quantization                                 |

|   | 5.3        | Application Example                                                |

|   |            | 5.3.1 CIC Module Quantization                                      |

|   |            | 5.3.2 Newton Module Quantization                                   |

|   | 5.4        | Conclusion                                                         |

| CONTENTS | xvii |

|----------|------|

|          |      |

| 6  | Har                | $\mathbf{dware}$ | Implementation                                       | 113 |

|----|--------------------|------------------|------------------------------------------------------|-----|

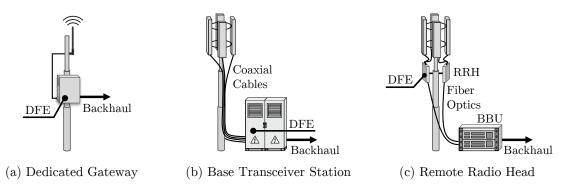

|    | 6.1                | Digita           | l Front-End Implementation                           | 114 |

|    |                    | 6.1.1            | Deployment Environment                               | 114 |

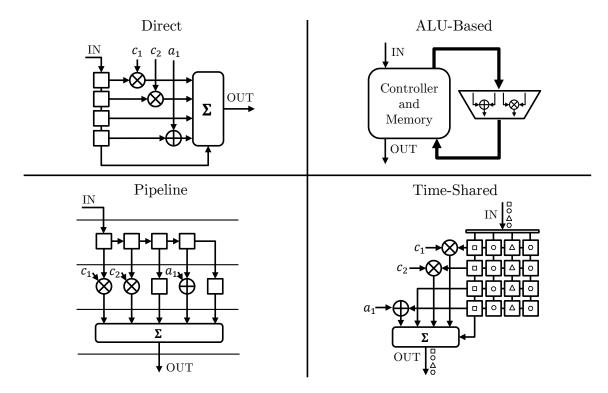

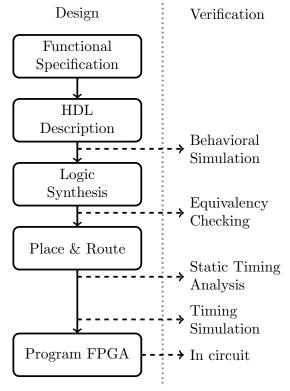

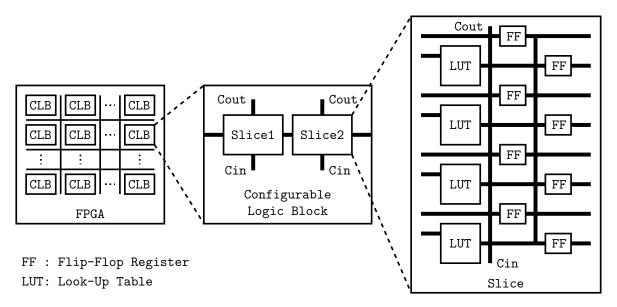

|    |                    | 6.1.2            | Hardware Implementation                              | 116 |

|    | 6.2                | SRC I            | Implementation Architecture                          | 118 |

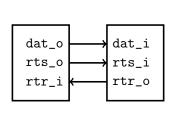

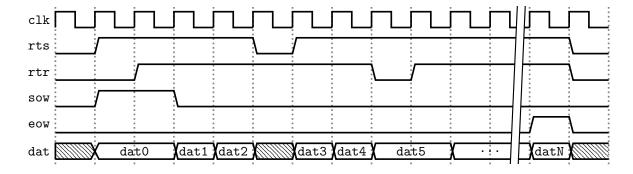

|    |                    | 6.2.1            | Interconnection Protocol                             | 118 |

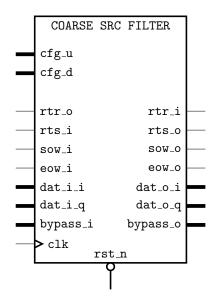

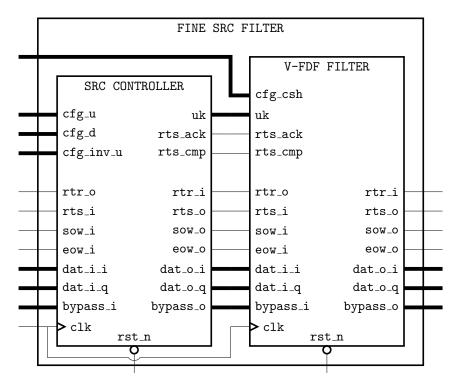

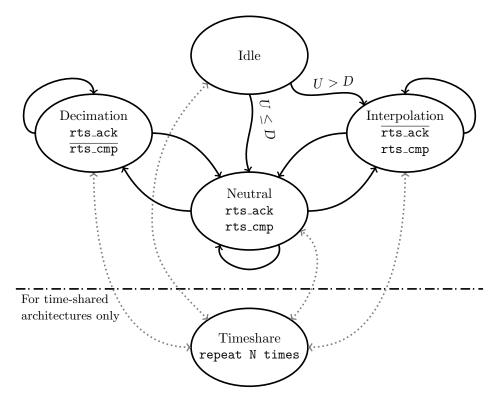

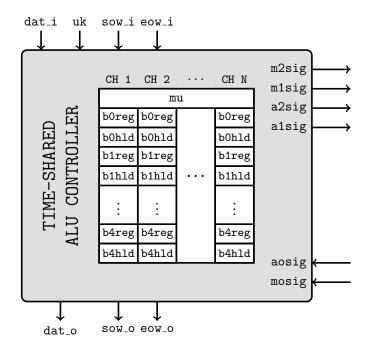

|    |                    | 6.2.2            | SRC System Architecture                              | 120 |

|    |                    | 6.2.3            | SRC Controller Architecture                          | 122 |

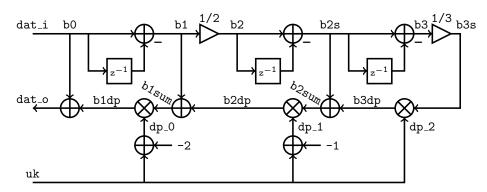

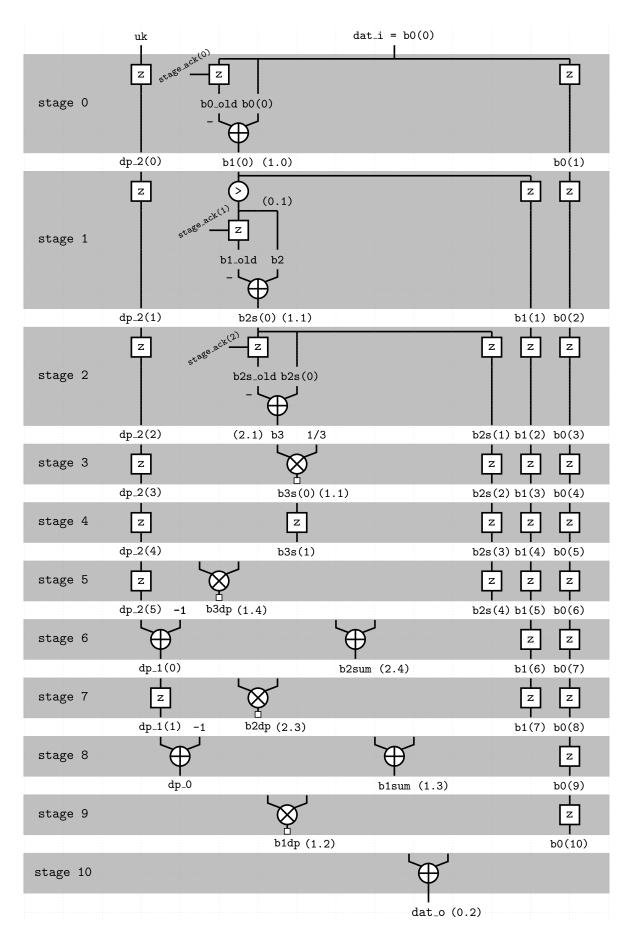

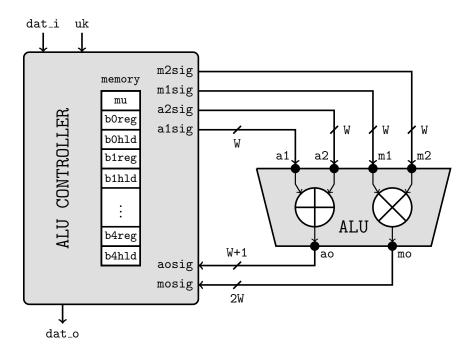

|    |                    | 6.2.4            | SRC Filter Architecture                              | 124 |

|    | 6.3                | Imple            | mentation Results                                    | 128 |

|    |                    | 6.3.1            | Implementation Context                               | 128 |

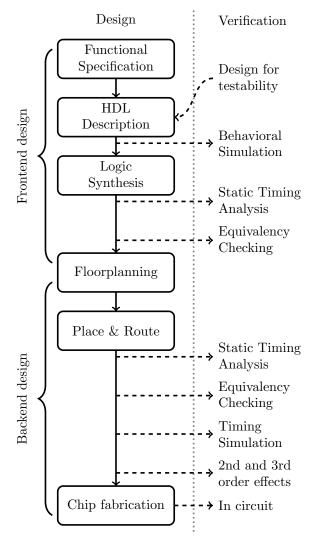

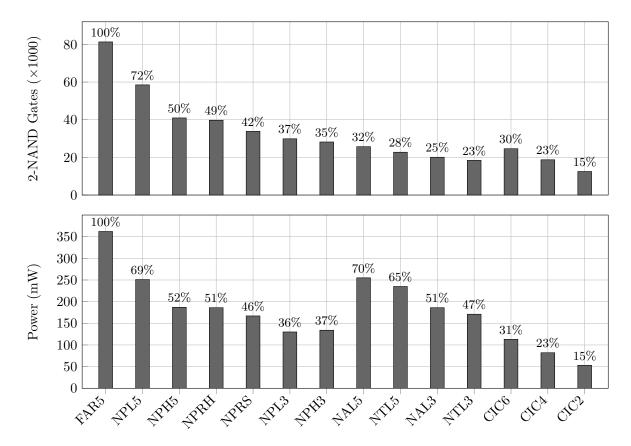

|    |                    | 6.3.2            | ASIC Implementation                                  |     |

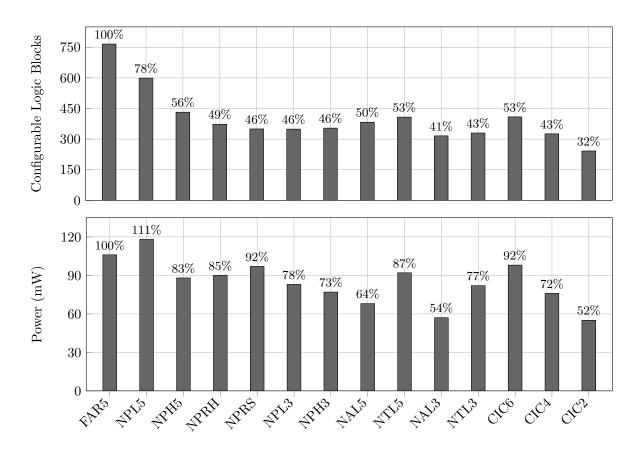

|    |                    | 6.3.3            | FPGA Implementation                                  | 133 |

|    | 6.4                | Concl            | usion                                                |     |

| Co | onclu              | sion a           | and Perspectives                                     | 139 |

| Aj | ppen               | dices            |                                                      | 143 |

| Α  | Dua                | dity a           | nd Transposition                                     | 145 |

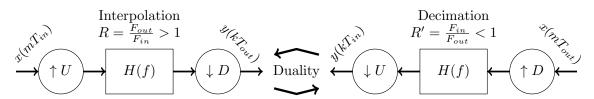

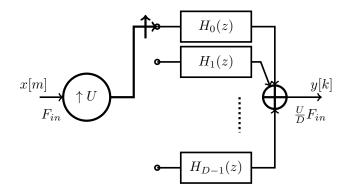

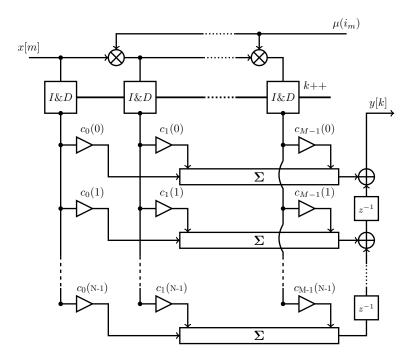

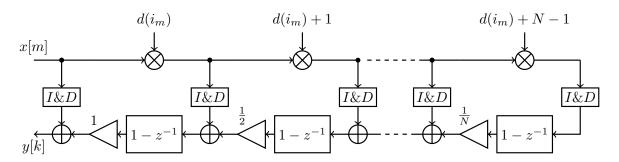

|    | A.1                | •                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |

|    |                    |                  | posed SRC Filters                                    |     |

| Li | st of              | Publi            | cations                                              | 149 |

| Bi | bliog              | graphy           |                                                      | 162 |

| Li | ist of Acronyms 16 |                  |                                                      |     |

xviii CONTENTS

## List of Figures

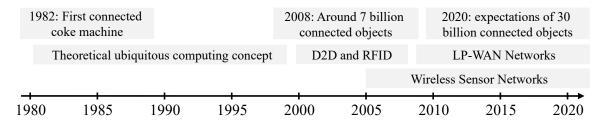

| 1.1  | Evolution of the IoT concept and deployment                                  | 1  |

|------|------------------------------------------------------------------------------|----|

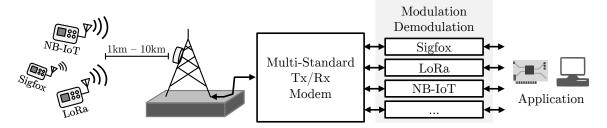

| 1.2  | IoT Deployment Scenario for LP-WAN networks                                  | 12 |

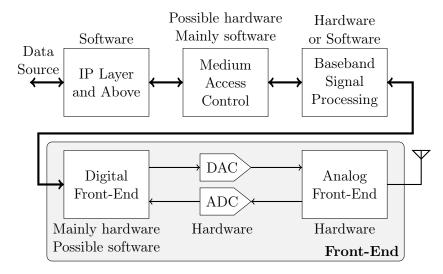

| 1.3  | A generic architecture for a wireless multi-standard system                  | 13 |

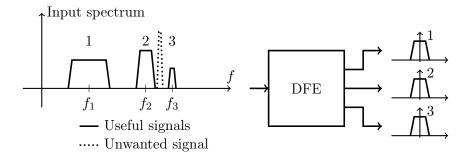

| 1.4  | The role of the digital front end in reception                               | 18 |

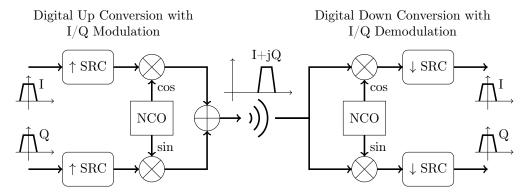

| 1.5  | Digital Up/Down Conversion Structures                                        | 20 |

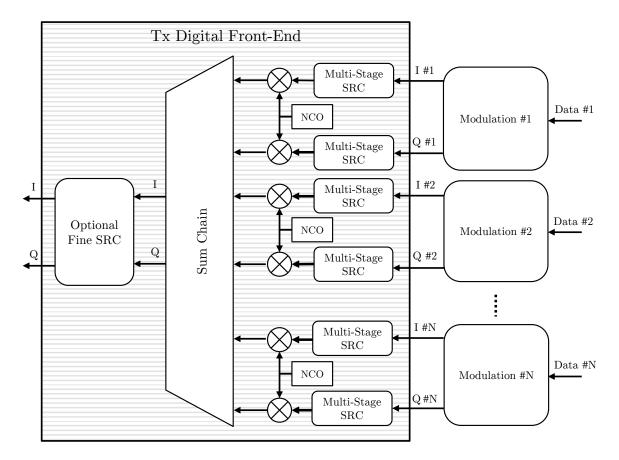

| 1.6  | Tx Digital Front-End Core                                                    | 22 |

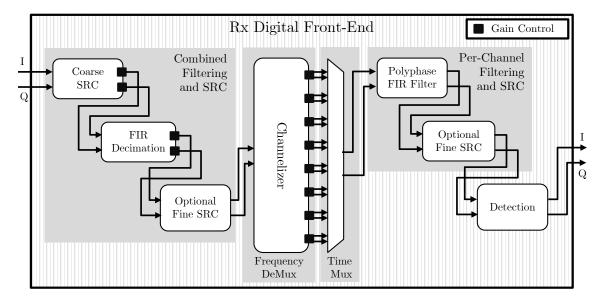

| 1.7  | Rx Digital Front-End Core                                                    | 23 |

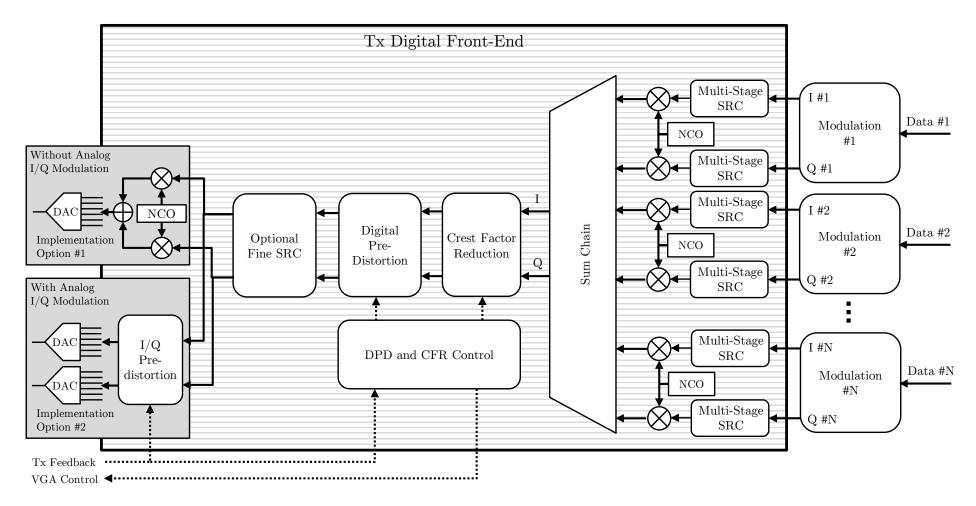

| 1.8  |                                                                              | 25 |

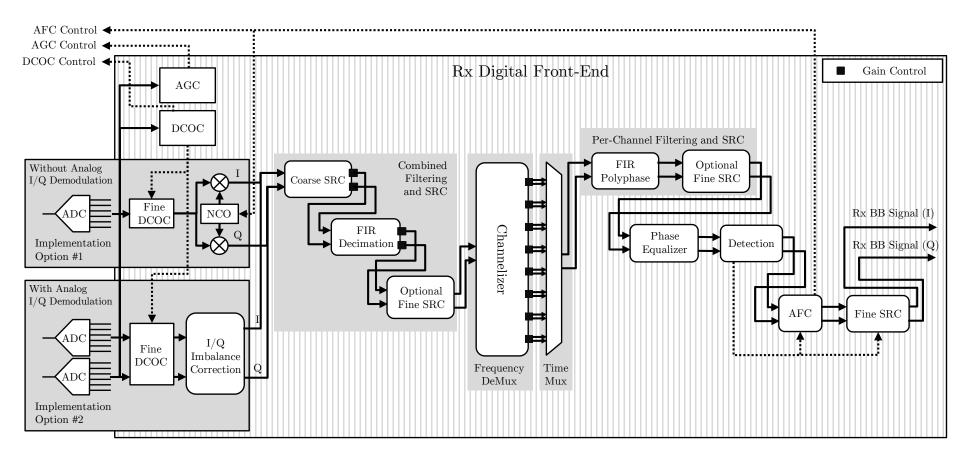

| 1.9  | Generic Receiver DFE Architecture                                            | 28 |

| 1.10 | Interface between the AFE and the DFE                                        | 29 |

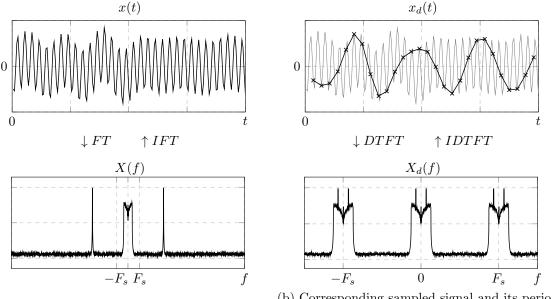

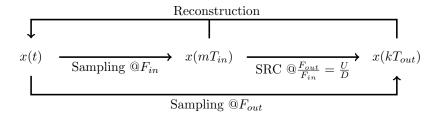

| 2.1  | Time and frequency representations of the continuous and sampled signals 3   | 33 |

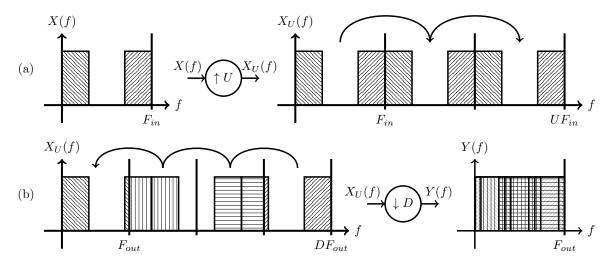

| 2.2  | 1 0, 1 0                                                                     | 34 |

| 2.3  |                                                                              | 35 |

| 2.4  | 1 1 0/                                                                       | 36 |

| 2.5  |                                                                              | 37 |

| 2.6  |                                                                              | 39 |

| 2.7  | • •                                                                          | 42 |

| 2.8  |                                                                              | 44 |

| 2.9  |                                                                              | 45 |

| 2.10 | 1 ( )                                                                        | 47 |

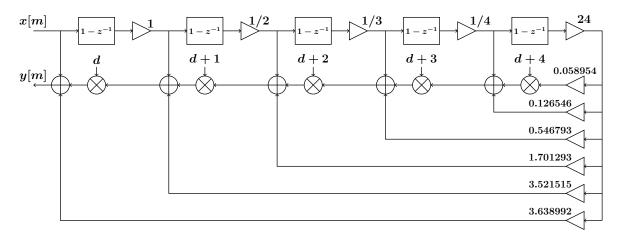

|      | 1 0 0                                                                        | 48 |

|      | · ·                                                                          | 50 |

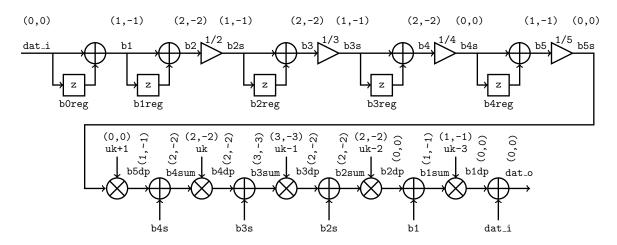

| 2.13 | The Newton Structure implementing Lagrange interpolation of order $N$        | 51 |

| 3.1  | Interpolation Indexing                                                       | 58 |

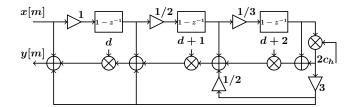

| 4.1  | The generalized Newton structure of order 3 $(M = N = 4) \dots \dots$        | 71 |

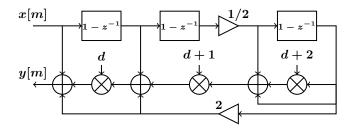

| 4.2  | Modified Newton structure adapted to Hermite interpolation of order 3        | 75 |

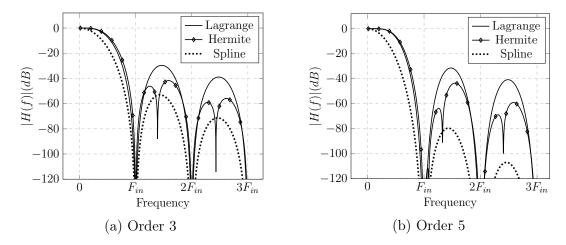

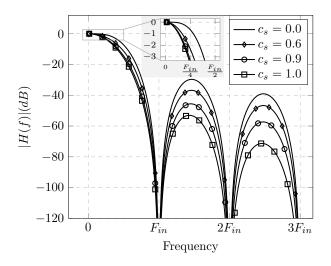

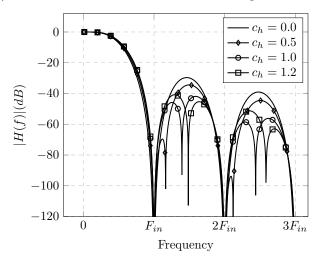

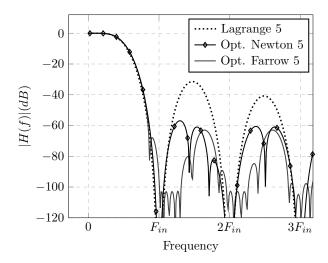

| 4.3  | · · · · · · · · · · · · · · · · · · ·                                        | 76 |

| 4.4  | Frequency response of the discussed interpolation methods for order 3 and 5. | 76 |

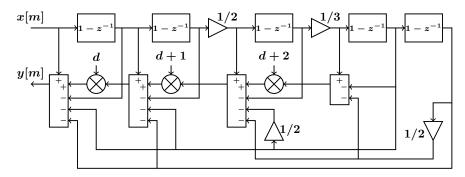

| 4.5  | The Spline based reconfigurable Newton structure                             | 79 |

| 4.6  | 9                                                                            | 80 |

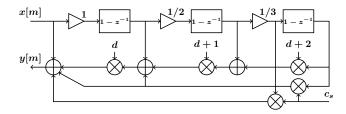

| 4.7  | •                                                                            | 35 |

| 4.8  | The frequency responses of Farrow and Newton optimized structures 8          | 36 |

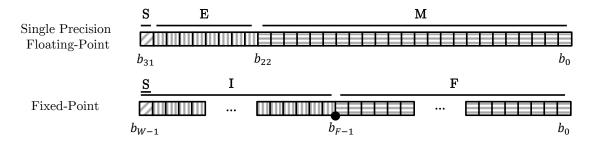

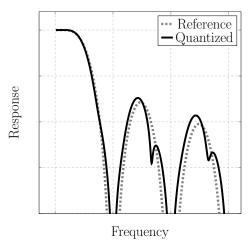

| 5.1  |                                                                              | 38 |

| 5.2  | 1 9 1                                                                        | 91 |

| 5.3  | A simplistic NB-IoT DFE example                                              |    |

| 5.4  | CIC Decimation Filter of order 4                                             |    |

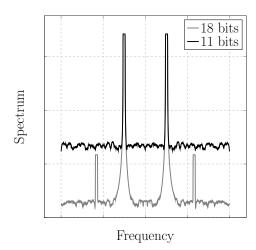

| 5.5  | Fractional Part Quantization of the Newton Module                            | )9 |

xx LIST OF FIGURES

| 6.1  | Three deployment strategies that place the DFE in different parts of the system | 114 |

|------|---------------------------------------------------------------------------------|-----|

| 6.2  | The different implementation strategies implementing the same module            | 117 |

| 6.3  | Three deployment strategies that place the DFE in different parts of the system | 119 |

| 6.4  | Coarse SRC hardware module                                                      | 120 |

| 6.5  | Fine SRC hardware module                                                        | 122 |

| 6.6  | SRC controller state transition diagram                                         | 123 |

| 6.7  | Newton structure of order 3                                                     | 124 |

| 6.8  |                                                                                 | 125 |

| 6.9  | ALU-based implementation architecture                                           | 126 |

| 6.10 |                                                                                 | 126 |

| 6.11 | Time-shared ALU-based implementation architecture                               | 128 |

| 6.12 | ASIC design flow                                                                | 130 |

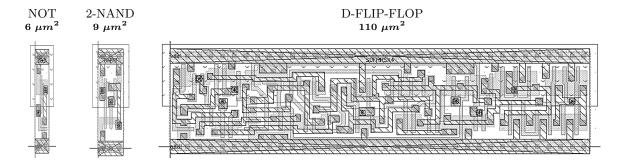

| 6.13 | Die surface of different X-FAB XH018 logic gates                                | 131 |

| 6.14 | ASIC implementation results using the X-FAB XH018 technology                    | 133 |

| 6.15 | FPGA design flow                                                                | 134 |

| 6.16 | Simplified presentation of the Virtex-6 FPGA architecture                       | 135 |

| 6.17 | FPGA implementation results using the Xilinx Virtex-6                           | 136 |

| Λ 1  | Duality Property Potygon Internalation and Designation                          | 145 |

| A.1  |                                                                                 |     |

| A.2  | 0.1                                                                             | 146 |

| A.3  | •                                                                               | 147 |

| A.4  |                                                                                 | 148 |

| A.5  | The Decimation Newton Structure of order N                                      | 148 |

## List of Tables

| 1.1 | Wireless Area Network IoT Standards                               |

|-----|-------------------------------------------------------------------|

| 1.2 | LP-WAN Standards Specifications Summary                           |

| 2.1 | Comparison of SRC FIR Filters of Order $N$                        |

| 2.2 | The most adapted SRC filters for different SRC applications       |

| 4.1 | Frequency Response for order 3 interpolations                     |

| 4.2 | Frequency Response for order 5 interpolations                     |

| 4.3 | Complexity of Order 3 Newton Implementations                      |

| 4.4 | Complexity of Order 5 Newton Implementations                      |

| 4.5 | Complexity comparison of reconfigurable Newton structures         |

| 4.6 | Complexity comparison of the optimized structures                 |

| 5.1 | Fractional Part Quantization Parameters for the CIC Filter        |

| 5.2 | Fractional Part Quantization Parameters for the Newton Module 110 |

| 6.1 | Handshake protocol behavior                                       |

| 6.2 | Coarse SRC hardware module ports                                  |

| 6.3 | Fine SRC hardware module specific ports                           |

| 6.4 | Scheduling of the ALU-based implementation                        |

| 6.5 | ASIC implementation results using the X-FAB XH018 technology 132  |

| 6.6 | FPGA implementation results using the Xilinx Virtex-6             |

xxii LIST OF TABLES

### Introduction

After the Internet and mobile network revolutions of the 1990's that allowed humans to communicate across the planet, the digital world is preparing a new revolution allowing objects to communicate. The internet of things (IoT) is the label given to the network connecting these objects, that is expected to accommodate over 75 billion devices by 2025 [Luc16]. Each connected object has a specific application with particular requirements. The wide variety of applications makes the communication requirements of these objects very diverse. Hence, a large number of technologies and communication standards have been proposed for the different application cases, each using specific transmission techniques and signal characteristics. In parallel, new standards are being built with the objective to support the largest number of application cases. An example is the fourth generation (4G) long term evolution (LTE) mobile network, that defines many different device categories, each having specific technical transmission specifications. Furthermore, smart radio concepts are currently being developed, with the objective to build radio systems able of autonomously switching the technology or standard used for communication depending on the radio environment.

The diversity of modern communication solutions creates a challenge for network operators and telecommunication service providers. This is the case at TDF, a leading French radio infrastructure operator, concerned with the efficient deployment of the recently proposed IoT solutions and the future fifth generation (5G) mobile network. Considering each of these communication solutions independently induces deployment fragmentation, which kills interoperability, complicates quality of service (QoS) control, and increases deployment costs (including initial setup, maintenance, and power consumption). These issues are at the heart of 5G systems. TDF teamed up with the technological research institute b-com to solve this challenge by developing efficient deployment solutions.

To approach this problem, it is useful to refer to the Open Systems Interconnection (OSI) model, that represents network connectivity through seven layers. Implementing interoperability at the high software layers (from transport to application) offers a unified processing and management solution, however it does not solve the physical deployment challenge. To address the energy efficiency and the total costs of deploying radio infrastructures, it is necessary to consider the lower material layers (physical, data-link, and network). The priority in this manuscript is the physical layer that is the main influence on the cost and consumption of the radio infrastructure interfaces.

Regarding the physical layer, the issues of interoperability and transversality are addressed by providing a modem platform that is sufficiently flexible to accommodate the different standards and technologies. For the best energy efficiency and implementation compactness, the privileged solution is a single hardware processing system that is configurable through a set of variable parameters, allowing switching between multiple technologies. This is the software defined radio (SDR) vision, in which the processing is shared between a general purpose processor (GPP) and a hard wired structure implemented using field programmable gate array (FPGA) or application specific integrated circuits (ASIC). The hard wired part implements the main digital signal processing functions, while the GPP is assigned complex computations whose execution time constraints are relaxed. The optimal system would be the one capable of supporting all the considered technologies, while having for a given transmission

2 LIST OF TABLES

mode a complexity and consumption equivalent to that of a dedicated implementation.

### Objectives and Contributions

Having provided the general framework, this work's objectives are identified. A digital modem consists of three main sections: digital front-end (DFE), baseband processing, and forward error correction (FEC). In modern systems, the DFE is usually implemented in hardware, while the two following sections are often done in software. This work focuses on optimizing the hardware implementation to reduce the cost and consumption of the physical interface. Therefore the main system in question is the digital front-end.

The DFE contains numerous signal processing functions, however it has two main roles: filtering and sample rate conversion (SRC). It is very common to combine filtering with SRC, and to use the SRC function to implement more advanced functions. This makes the SRC a core function of the DFE. Knowing this, the main objectives of this work are the following:

- 1. Design an efficient generic DFE architecture that is easily adapted to any communication standard or technology.

- 2. Optimize the SRC function in the DFE, then implement the newly developed structures, and evaluate their practical complexity and consumption.

- 3. Develop hardware implementation guidelines, to be used with all the DFE functions, related to the quantization problem and the implementation strategies.

To achieve these objectives, this work developed the following contributions:

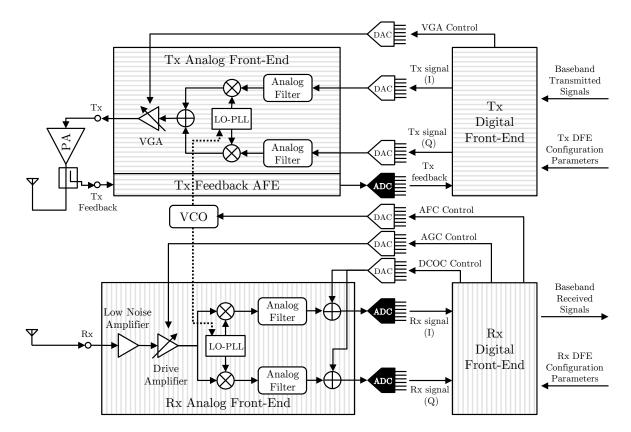

- 1. First, generic DFE architectures for both transmission and reception are proposed, and their integration in combination with a generic analog front-end (AFE) is explained.

- 2. Second, a new concise presentation of the SRC filters available in the literature is developed. The purpose of this presentation is to assemble the scattered literature of SRC filters under one single unified vision. Then the work studies in depth the Newton structure, that seems promising to build new and more efficient SRC solutions. A tutorial article presenting the unified vision is planned to be published in the near future.

- 3. The third contribution is the development of certain missing theoretical aspects related to the Newton structure, that are needed to rigorously define the response of this filter. A new mathematical proof of the Newton series convergence was published in the IEEE signal processing letters.

- Paquelet, S.; Zeineddine, A.; Nafkha, A.; Jezequel, P. & Moy, C., Convergence of the Newton Structure Transfer Function to the Ideal Fractional Delay Filter, IEEE Signal Processing Letters.

- 4. The fourth contribution is the design of new SRC filters based on the Newton structure, where three new modifications are developed: Hermite interpolation, reconfigurable response, and optimized coefficients filters. This work resulted in three conference publications and one patent application.

- Zeineddine, A.; Nafkha, A.; Moy, C.; Paquelet, S. & Jezequel, P.-Y. Variable fractional delay filter: A novel architecture based on hermite interpolation, 25th International Conference on Telecommunications (ICT), 2018, 93-97

- Zeineddine, A.; Paquelet, S.; Nafkha, A.; Moy, C. & Jezequel, P.-Y. Generalization and Coefficients Optimization of the Newton Structure, 25th International Conference on Telecommunications (ICT), 2018, 98-103

LIST OF TABLES 3

• Zeineddine, A.; Paquelet, S.; Kanj, M.; Moy, C.; Nafkha, A. & Jezequel, P. Reconfigurable Newton structure for sample rate conversion, IEEE Global Conference on Signal and Information Processing (GlobalSIP), 2018, 271-275

- Zeineddine, A.; Paquelet, S.; Filtre interpolateur numérique, dispositif de changement de rythme et équipement de réception correspondants, INPI n°FR17 62632

- 5. The rest of this work addressed the quantization and the hardware implementation optimization problems. The fifth contribution is the development of an optimal yet simple quantization algorithm, that finds the minimal signals bit width that guarantees a given precision constraint. The developed quantization method is kept confidential and is not published in the public version of this thesis.

- 6. Finally, different SRC solutions for the DFE are implemented in hardware using both FPGA and ASIC, using different implementation strategies. Then the complexity and consumption of these SRC solutions and the different implementation strategies used are analyzed and compared, which helps in selecting the appropriate solution for certain given application requirements. Some of these results were published in the New Circuits and Systems (NEWCAS) conference.

- Zeineddine, A.; Paquelet, S.; Nafkha, A.; Jezequel, P.-Y. & Moy, C. Efficient Arbitrary Sample Rate Conversion for Multi-Standard Digital Front-Ends, 17th International IEEE NEW Circuits and Systems Conference (NEWCAS), 2019

### Organization of the Thesis

The work of this thesis is presented over 6 chapters having the following organization.

Chapter 1 presents the IoT context and the communication standards and technologies diversity problem. The multi-standard modem is then presented as the solution to this problem, with the DFE being at the heart of this modem. Finally, the DFE concept and its main functions are presented, and a generic DFE architecture enabling multi-standard modems is developed on both transmission and reception sides, alongside the interfaces with the AFE.

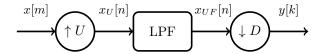

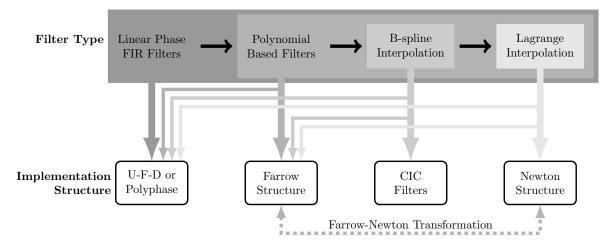

Chapter 2 develops the unified vision of the finite impulse response (FIR) based SRC filters. The five main filter structures available in the literature are grouped under one common root, that is the linear-phase FIR filters, from which the five structures are then derived. This chapter also presents the hardware implementation aspects for each filter structure in order to provide a complete and concise guide on SRC from both theoretical and practical point of views. This chapter develops the case of interpolation SRC filters, the complementary decimation SRC filters case is presented in Appendix A.

Chapter 3 addresses two missing theoretical aspects related to the Newton structure that were needed for the developments done in this work. First, the direct relation between the expressions of Lagrange interpolation and the Newton backward difference formula (NBDF) is developed. Second, a new rigorous proof of the Newton structure transfer function convergence is proposed.

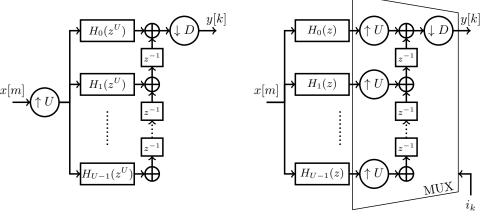

Chapter 4 is based on the proposition done in [Lam16] that proposes a generalization for the Newton structure through matrix transformations. This chapters starts by developing the closed form expressions of these transformations which are then used to design new SRC filter structures. First, the modified Newton structure for Hermite interpolation is developed. Second, by writing the transfer function of the generalized Newton structure as a linear combination of two interpolation methods, the reconfigurable Newton structure is derived. Third and finally, the closed form expression of the frequency response for the generalized Newton structure is developed, and is then used in combination with filter optimization techniques to propose optimized Newton structures.

4 LIST OF TABLES

Chapter 5 studies the quantization problems, necessary for the efficient implementation of the DFE signal processing functions in hardware. The first section of this chapter presents the fundamentals and state-of-the-art of the available quantization methods. The second section then addresses the complexity of the proposed methods in the literature, and develops a new analytical method that is simple yet optimal. The developed quantization method is omitted from the public version of this thesis. The final section applies the developed method to a simplistic DFE example, in order to show how this method is practically used.

Chapter 6 develops the hardware implementation of different SRC filters on both FPGA and ASIC targets. First, the different hardware implementation constraints and strategies are presented. Then the architectures of the newly proposed SRC solutions are developed using different implementation strategies. Finally, the filters are implemented in hardware and then the complexity and consumption results are analyzed.

### Chapter 1

Contents

1.3.1 1.3.2

1.4

## Digital Front-End for the Internet of Things

| 1.1 | Inte           | rnet of Things Network                                                                                            | 6         |

|-----|----------------|-------------------------------------------------------------------------------------------------------------------|-----------|

|     | 1.1.1          | What is the Internet of Things                                                                                    | 6         |

|     | 1.1.2          | IoT Networks Types, Standards, and Technologies                                                                   | 9         |

|     | 1.1.3          | Internet of Things Deployment Challenges                                                                          | 11        |

| 1.2 | $\mathbf{Mul}$ | ti-standard Internet of Things Modems                                                                             | <b>12</b> |

|     | 1.2.1          | Generic Architecture                                                                                              | 13        |

|     | 1.2.2          | ${\bf Hardware/Software\ Partitioning}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 14        |

|     | 1.2.3          | Multi-standard LP-WAN Modem Example                                                                               | 15        |

| 1.3 | $\mathbf{Gen}$ | eric Digital Front-End                                                                                            | 17        |

23

30

Internet of Things (IoT) is the network that connects everyday devices to the Internet. This concept witnessed an important growth since early 2010, but only recently its concrete implementation and deployment started to appear. The wide adoption of the IoT trend created an important global market that is expected to continuously grow with time. However, IoT applications are numerous, and the required performance from the connected devices varies with each application. This motivated many actors to propose different transmission standards and technologies, with the objective to offer deployment solution for the IoT network. To propose solutions for all IoT applications, each standard and/or technology proposition tried to address the communication needs for IoT applications with a different approach, by exploiting the advantages of a specific transmission technique and signal type. Moreover, the number of connected devices is estimated to reach 75.4 billion by 2025 [Luc16]. The IoT network will not be uniform, but rather heterogeneous, e.g. there will be a plurality of IoT networks in each given covered area, necessitating to have a dedicated gateway for each communication standard. An efficient deployment solution would be the use of multistandard gateways, that are capable of communicating with the largest number of standards, and thereby the largest number of devices. Then one multi-standard gateway can replace multiple ones to provide service for many devices of different standards.

These multi-standard gateways are based on a Digital Front-End (DFE), as emphasized by the software defined radio (SDR) technology [Mit95][Pal13]. The software radio concept has

an ideal objective of implementing the radio functions, found today in the analog front-end (AFE), using digital signal processing functions in hardware and software. This is desirable in order to offer a fully reconfigurable radio front-end, that can be adapted to any radio signal at both transmission and reception. However, with today's technology, this stays an ideal concept and some AFE function are always necessary, followed by a DFE having digital functions that replace or compensate what was previously processed in the analog domain. Nonetheless, by using a hybrid AFE/DFE combination, it is possible to build multi-standard gateways that process different IoT standards. This manuscript is focused on some of the DFE functions allowing this flexibility.

In this chapter, the concepts that motivated this PhD work are presented, and a generic DFE architecture is developed. The IoT concept, technologies, and deployment challenges are presented in Section 1.1. Section 1.2 then develops the multi-standard modem solution that helps addressing some of the IoT deployment challenges. The DFE function in the multi-standard modem is then studied in Section 1.3, and generic architectures are proposed for both transmitter (Tx) and receiver (Rx) implementations. Section 1.4 concludes this chapter and presents the work done in this thesis that aims at optimizing the DFE implementation.

### 1.1 Internet of Things Network

The context of the present thesis is the deployment of the Internet of things network. A good understanding of this context is necessary for the correct formulation of the problematic, and for identifying the best corresponding solution. This section starts by introducing the Internet of things concept in Section 1.1.1. The standards and technologies designed for IoT applications are then classified and presented in Section 1.1.2. Finally, the deployment challenges of the IoT network are identified in Section 1.1.3. The rest of this thesis then aims at finding a deployment solution that helps addressing these challenges, and facilitating the deployment of the IoT network.

### 1.1.1 What is the Internet of Things

The Internet of things is a commonly used term in today's research community. This section presents the IoT concept from three points of view: birth and evolution, applications, and market. This will help to better understand the IoT technologies and challenges presented in later sections.

#### 1.1.1.1 Birth and Evolution

In the IoT literature, it is often considered that the first example of a connected object was developed at the Carnegie Mellon School of Computer Science in the 1980s [Eve90]. It consisted of a coke machine that was connected to the Advanced Research Projects Agency Network (ARPANET) at first, before it was later connected to the Internet in the 1990s. What motivated the researchers to connect this machine was their need to verify that the machine is not empty before making the trip to get a coke, since their office was far from the machine. This was the first example of a monitoring application using connected objects.

Through the 1990s, the IoT concept witnessed some basic proof of concept propositions by researchers. The advancement of integrated circuits technologies, and their price reduction, further motivated the research in this area. This concept started as a ubiquitous computing concept at first [Wei91], where the idea was to add computing and communication capabilities to everyday objects. Later on more visions for the future IoT "smart networks" were proposed, and adequate communication standards for such applications started to be investigated and developed [Raj94]. Device to device (D2D) communication using a multitude of standards (WiFi, Bluetooth, ZigBee, radio-frequency identification RFID, ...) was the main trend with

Figure 1.1: Evolution of the IoT concept and deployment

the beginning of the 21<sup>st</sup> century. RFID technology and wireless sensor networks were the foundation of many applications with a massive scale deployment.

The International Telecommunications Union ITU addressed this topic for the first time in 2005 with a dedicated report [Int05], providing a definition for this concept: "Connections will multiply and create an entirely new dynamic network of networks - an Internet of Things". According to Cisco, the IoT was born sometime between 2008 and 2009, at the point in time when more objects were connected to the Internet than the number of people on earth [Eval1]. Since 2008, the number of commercialized connected devices keeps on multiplying, and it was expected to surpass the 30 billion devices by 2020 [Lun14][Luc16].

To offer wireless connectivity to these devices, new solutions and technologies emerged destined for IoT applications. Low-power wide area networks (LP-WAN) that started appearing as of 2009 [Raz17], were a solution aimed at answering most IoT applications constraints on low power consumption and long distance transmissions. These proposed standards are discussed in more details in Section 1.1.2. The birth and evolution of the IoT concept and deployment are summed-up in Figure 1.1.

The list of applications and opportunities the IoT domain opens up is endless, and this is justified by the great number of published standards, the regional and national efforts of many countries to develop this sector, and the continuously growing market. In addition, the large scale deployment of IoT devices creates and helps the development of many other domains. For example it is a catalyst to the big data concept, that is concerned with managing the gigantic amount of data generated by all of these devices. IoT devices can also contribute to the spread of artificial intelligence, by farming their generated data and using it to train algorithms. Another domain that can also benefit from the IoT is augmented reality, where devices deployed everywhere can be used to manage the user virtual experience for example. These are some examples of the many domains tied to the IoT network.

#### 1.1.1.2 Applications

The wide variety of IoT applications explains the great number of proposed standards that will be presented later. This variety also highlights the challenges that are associated with the deployment of the IoT network. Below is a non-exhaustive list of the possible applications that are enabled by the IoT network, sorted by the application domain. After presenting the applications, we can then deduce the constraints imposed on the devices depending on their application target.

### 1. Agriculture [Dlo15]

- (a) **Cultivation**: Connected low-cost sensors can be implemented in the field to monitor different aspects of the planting environment. These devices can also be controllers that automate certain tasks, such as the watering of plants.

- (b) **Farming**: Connected devices can be either animal health monitors, or sensors tracking the food or waste levels, and also the animals and their movement. Controllers can be used to manage automated food distribution mechanisms.

### 2. Industry [Da 14]

- (a) **Monitoring**: Sensors and RFID tags can be implemented to follow the inventory stocks in the factory, and also to monitor the automated processes in the factory.

- (b) **Controlling**: Connected actuators may be used to implement finely tuned control mechanisms in order to automatize the manufacturing process.

- (c) **Security**: Connected devices used to regulate access and detect intrusion are necessary to guarantee the security of factories.

### 3. Smart City [Li11][Zan14]

- (a) Environmental: In a smart city, the levels of pollution are already monitored. Whether it's natural, sound, nuclear or electromagnetic pollution. Forest fire, water quality, and many other aspects may also be monitored.

- (b) **Infrastructures**: Sensors will remotely monitor infrastructures status, such as bridges vibration, traffic congestion, waste pipelines, etc. Smart connected cars of the future are expected to be autonomous thanks to many sensors, actuators, and trackers responsible for ensuring their correct operation and safety.

- (c) **Smart Grid**: Monitoring the consumption of power and controlling its distribution is a key point to improve the efficiency of the electrical grid. Smart metering will also greatly facilitate managing the electricity grid of any scale.

### 4. Smart Home [Sto17]

- (a) **Automation**: From simple light bulbs, to coffee and washing machines, ending with completely automated heating and cooling controllers, almost everything in our homes may be remotely and automatically controlled.

- (b) **Monitoring**: Automation functions using information generated by monitoring different aspects such as temperature, humidity, power consumption, etc.

- (c) **Security**: Smart locks, intrusion detectors, and trackers, may be all connected to the Internet to alarm their owner or the police in case of any emergency.

#### 5. Tracking [Gni15]

- (a) **Private Property**: Tracking valuable vehicles and properties will be possible with the IoT network by using very small devices that have geo-localization capabilities that will continuously report their position.

- (b) **Logistics & Delivery**: We can already find delivery services that offer the customer the ability to track the position of his/her parcel. Tracking logistics are also an important concern for production companies.

- (c) Rented Assets: In recent years we witnessed many renting services that aim to promote sharing bikes, cars, or boats between citizens. Tracking these rented assets is crucial to keep control over the business.

### 6. Wearables [Wei14]

- (a) ID Tags: Identification tags that a person carry are already part of many workplaces. However with the IoT network development, we might see a much wider use for these tags in everyday life, for identification, fast payment, or to save a person's medical record.

- (b) **Health**: These devices will be widespread between seniors to keep track of their health status, or between persons with a sickness that requires constant monitoring.

(c) **Fitness**: Activity trackers are already widely commercialized, and they're very helpful in informing the person using them of his activity level and his sleeping time and quality.

These different applications do not share the same operation constraints. For example when it comes to cultivation applications, the main concern would be low-power consumption, where it is not practical to frequently change the devices batteries. However when it comes to the different control and security applications the reliability of the wireless connection is far more critical. Therefore this variety of application scenarios can explain the large number of IoT standards that are proposed in the market, presented in Section 1.1.2. Each of these standards tries to answer the requirements of a certain number of applications.

#### 1.1.1.3 Market

Every year, the number of connected devices keeps on increasing. And as the IoT applications get more mature, and the IoT standards become available, a great number of new devices will be commercialized and deployed in the next coming years. This IoT market has been investigated by many marketing and finance analysis firms, that published an important number of reports. The number of IoT devices was estimated by the International Data Corporation (IDC) to be 9.1 billion devices in 2013 [Lun14]. This number was expected to grow and reach 13.7 billion and 28.1 billion on 2015 and 2020 respectively. IHS Markit published another study [Luc16] in 2016 that estimated the number of connected devices in 2015 to be 15.4 billion, with a grow to 30.7 billion and 75.4 billion by 2020 and 2025 respectively.

Behind this great number of deployed devices, there is an important global market. The value of this market was estimated by IDC in 2013 to be worth 1.9 trillion dollars, with an expected worth of 7.1 trillion dollars in 2020 [Lun14]. In this growing sector, telecommunication providers and industries are facing new challenges. In the classical cellular network era, the service was provided mainly as a subscription based model, or as a metered post-payed service. However for the new applications of IoT devices, these business models are not always applicable. For example we find today IoT services that are billed as 1\$ per device per year. Alongside the financial challenge, the technical deployment of the IoT services will also be different. With the many newly proposed IoT standards using non-licensed ISM bands, private or public sector companies can start offering wireless services, and start competing with the classical network service providers using licensed bands for IoT (LTE CAT-M1, EC-GSM, etc).

To better understand the evolution of this market, different studies investigated its adoption and its future. The work in [Hsu16] is one example, where the authors addressed the influences affecting the adoption of the IoT market. The results showed that the perceived critical mass, compatibility, and complementary were the main influences. Users also cared about the availability of access points. The widely discussed privacy and security aspects of IoT were a concern as well, however they did not seem to disable the adoption of this market.

#### 1.1.2 IoT Networks Types, Standards, and Technologies

The majority of the IoT applications presented in the previous section rely on wireless connections to transfer their data. To answer the different needs for wireless service, many actors proposed telecommunication standards and technologies built for IoT applications. These solutions have different characteristics, and each one of them targets a certain sector of IoT applications. Before introducing these standards, the different types of IoT networks are presented. Then for each network type, the associated proposed standards are presented.

| Standards                                   | Network Type        | Range     |  |  |  |

|---------------------------------------------|---------------------|-----------|--|--|--|

| W-PAN                                       |                     |           |  |  |  |

| NFC / FeliCa / Mifare                       | Proximity           | < 20 cm   |  |  |  |

| Radio Frequency Identification (RFID)       | Proximity           | < 10 m    |  |  |  |

| ZigBee / MiWi / Thread / Z-Wave / EnOcean   | W-HAN               | < 50 m    |  |  |  |

| WirelessHART / ISA100.11a                   | W-FAN               | < 50 m    |  |  |  |

| Bluetooth                                   | W-PAN               | < 100 m   |  |  |  |

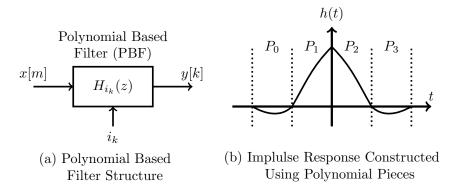

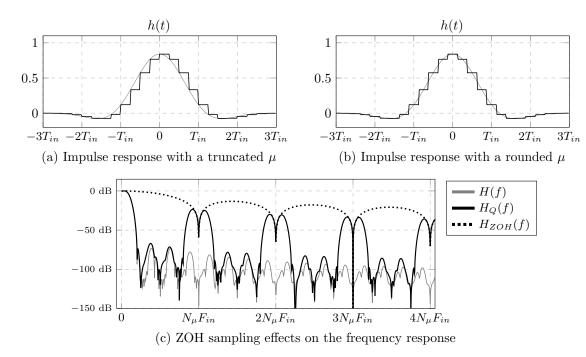

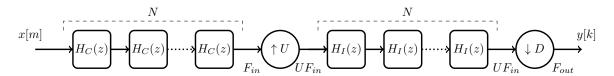

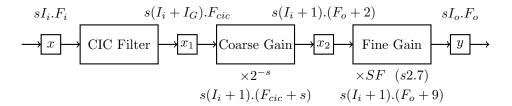

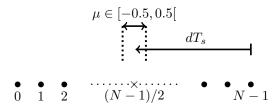

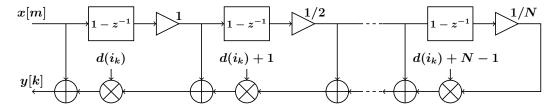

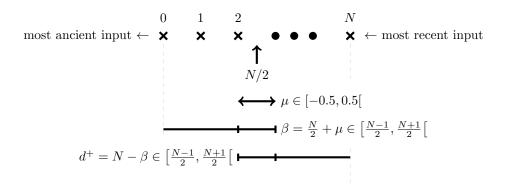

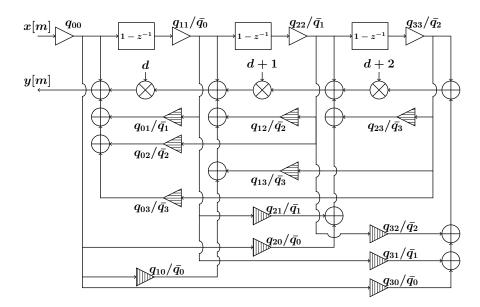

| W-LAN                                       |                     |           |  |  |  |