### True random number generators for cryptography: Design, securing and evaluation

Oto Petura

### • To cite this version:

Oto Petura. True random number generators for cryptography: Design, securing and evaluation. Micro and nanotechnologies/Microelectronics. Université de Lyon, 2019. English. NNT: 2019LY-SES053. tel-02895861

### HAL Id: tel-02895861 https://theses.hal.science/tel-02895861

Submitted on 10 Jul 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### N° d'ordre NNT : 2019LYSES053

### THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de

### Laboratoire Hubert Curien

### Ecole Doctorale Nº 488

Sciences Ingénierie Santé

### Specialité de doctorat:

Microélectronique

Soutenue publiquement le 23 octobre 2019, par :

### Oto Peťura

Générateurs de nombres aléatoires pour la cryptographie :

### Conception, sécurisation et évaluation

Devant le jury composé de :

| Danger, Jean-Luc   | PR                  | Télécom Paritech                | Rapporteur         |

|--------------------|---------------------|---------------------------------|--------------------|

| Dutertre, Jean-Max | PR                  | Ecole de Mines de Saint-Etienne | Rapporteur         |

| Bossuet, Lilian    | PR                  | Université Jean Monnet          | Examinateur        |

| Dumas, Cécile      | Ingénieur-Chercheur | CEA-Leti                        | Examinateur        |

| Haddad, Patrick    | PhD                 | STMicroelectronics              | Examinateur        |

| Fischer, Viktor    | PR                  | Université Jean Monnet          | Directeur de thèse |

| Aubert, Alain      | MC                  | Université Jean Monnet          | Co-encadrant       |

### PhD thesis from UNIVERSITE DE LYON

carried out at

Laboratoire Hubert Curien

Doctoral school Nº 488

Sciences Engineering Health

### PhD topic:

Microelectronics

Publicly defended on October  $23^{rd}$ , 2019, by:

### Oto Peťura

True random number generators for cryptography:

Design, securing and evaluation

In front of the jury consisting of:

| Danger, Jean-Luc   | Télécom Paritech                | Reviewer             |

|--------------------|---------------------------------|----------------------|

| Dutertre, Jean-Max | Ecole de Mines de Saint-Etienne | Reviewer             |

| Bossuet, Lilian    | Université Jean Monnet          | Examiner             |

| Dumas, Cécile      | CEA-Leti                        | Examiner             |

| Haddad, Patrick    | STMicroelectronics              | Examiner             |

| Fischer, Viktor    | Université Jean Monnet          | Thesis supervisor    |

| Aubert, Alain      | Université Jean Monnet          | Thesis co-supervisor |

This work has received funding from the European Union's Horizon 2020 research and innovation programme in the framework of the project HECTOR (Hardware Enabled Crypto and Randomness) under grant agreement No 644052.

### Contents

| $\mathbf{C}$ | onte                           | nts                                                                                                           | i    |

|--------------|--------------------------------|---------------------------------------------------------------------------------------------------------------|------|

| Li           | ist of                         | Figures                                                                                                       | vii  |

| Li           | ist of                         | Tables                                                                                                        | xi   |

| Li           | ist of                         | Symbols                                                                                                       | xiii |

| In           | trod                           | uction                                                                                                        | 1    |

| 1            | Rai                            | dom number generators in cryptography – state of the art                                                      | 9    |

|              | 1.1                            | Sources of randomness in logic devices                                                                        | . 11 |

|              |                                | 1.1.1 Clock jitter                                                                                            | . 12 |

|              |                                | 1.1.2 Metastability $\ldots$ | . 17 |

|              |                                | 1.1.2.1 Metastability in logic devices $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$              | . 17 |

|              |                                | 1.1.2.2 Oscillatory metastability                                                                             | . 18 |

|              | 1.2                            | Extraction of randomness from the clock jitter                                                                | . 19 |

|              | 1.3 Models and dedicated tests |                                                                                                               | . 23 |

|              | 1.4                            | Post-processing                                                                                               | . 24 |

|              | 1.5                            | Standards for TRNG design and certification                                                                   | . 25 |

|              |                                | 1.5.1 Summary of AIS-20/31 requirements on TRNGs                                                              | . 26 |

|              |                                | 1.5.1.1 PTG.1 low security TRNG class                                                                         | . 27 |

|              |                                | 1.5.1.2 PTG.2 class                                                                                           | . 28 |

|              |                                | 1.5.1.3 PTG.3 high-security TRNG class                                                                        | . 30 |

|              |                                | 1.5.2 Summary of NIST 800-90B requirements on TRNGs                                                           | . 31 |

|              |                                | 1.5.3 Conclusions of TRNG security certification                                                              | . 32 |

|              | 1.6                            | Conclusions                                                                                                   | . 33 |

| <b>2</b>     | Sele                           | ction and evaluation of TRNGs cores                                                                           | 35   |

|              | 2.1                            | Evaluation methodology                                                                                        | . 36 |

|   |             | 2.1.1   | Choice of TRNG cores                                   | 36 |

|---|-------------|---------|--------------------------------------------------------|----|

|   |             | 2.1.2   | Hardware used for evaluation                           | 37 |

|   |             | 2.1.3   | Evaluation criteria                                    | 38 |

|   |             |         | 2.1.3.1 Area                                           | 38 |

|   |             |         | 2.1.3.2 Power consumption and energy efficiency        | 38 |

|   |             |         | 2.1.3.3 Entropy and output bit rate                    | 40 |

|   |             |         | 2.1.3.4 Feasibility and repeatability                  | 40 |

|   |             | 2.1.4   | Initial measurements                                   | 41 |

|   | 2.2         | Imple   | mentation of selected TRNG cores                       | 42 |

|   |             | 2.2.1   | Elementary ring oscillator based TRNG                  | 42 |

|   |             | 2.2.2   | Coherent sampling based TRNG using ring oscillators    | 44 |

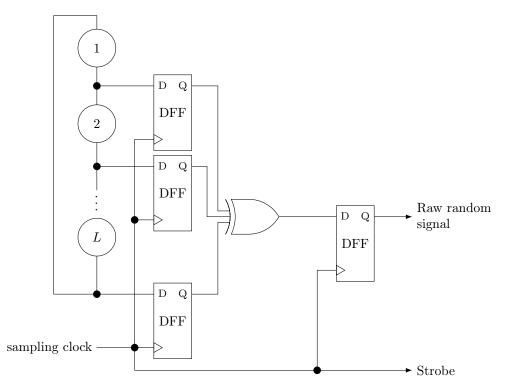

|   |             | 2.2.3   | Multi-ring oscillator based TRNG                       | 45 |

|   |             | 2.2.4   | Transient effect ring oscillator based TRNG            | 47 |

|   |             | 2.2.5   | Self-timed ring based TRNG                             | 48 |

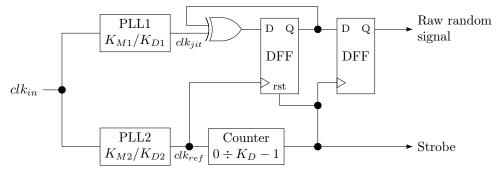

|   |             | 2.2.6   | Phase-locked loop based TRNG                           | 50 |

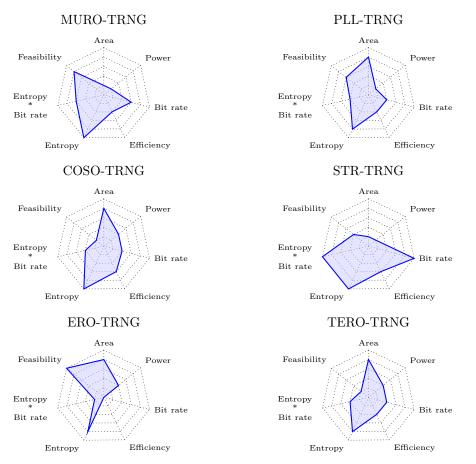

|   | 2.3         | Imple   | mentation results and their evaluation                 | 52 |

|   | 2.4         | Concl   | usion                                                  | 54 |

| 3 | Im          | olemei  | ntation of selected TRNGs in ASICs                     | 59 |

| Ö | 3.1         |         | design flow                                            | 59 |

|   | 3.2         |         | ΓOR ASIC design                                        | 62 |

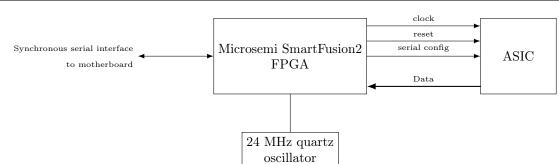

|   | 0.2         | 3.2.1   | HECTOR ASIC evaluation platform                        | 62 |

|   |             | 3.2.2   | HECTOR ASIC v1                                         | 63 |

|   |             | -       | 3.2.2.1 PLL-TRNG in HECTOR ASIC v1                     | 64 |

|   |             | 3.2.3   | HECTOR ASIC v2                                         | 66 |

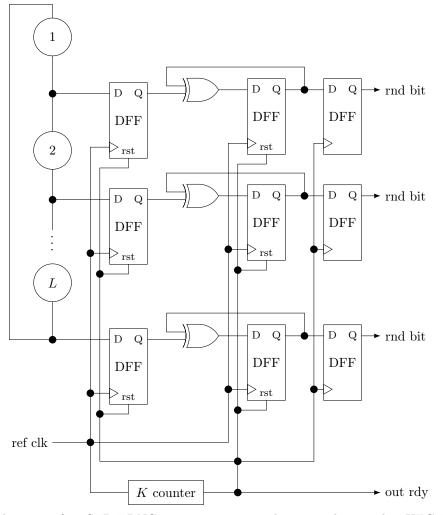

|   |             |         | 3.2.3.1 ERO-TRNG in HECTOR ASIC v2                     | 67 |

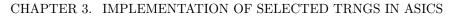

|   |             |         | 3.2.3.2 STR-TRNG in HECTOR ASIC v2                     | 69 |

|   |             | 3.2.4   | ASIC controller and control bus                        | 71 |

|   |             | 3.2.5   | Interface to the outside world                         | 72 |

|   | 3.3         | Testir  | ng and evaluation of TRNGs implemented in HECTOR ASICs | 73 |

|   |             | 3.3.1   | Evaluation of PLL-TRNG in HECTOR ASIC v1               | 74 |

|   |             | 3.3.2   | Evaluation of ERO-TRNG in HECTOR ASIC v2               | 75 |

|   |             | 3.3.3   | Evaluation of STR-TRNG in HECTOR ASIC v2               | 75 |

|   | 3.4         | Concl   | usion                                                  | 76 |

| 4 | Des         | sign of | f a secure PLL-TRNG                                    | 81 |

| - | <b>4</b> .1 | 0       | view of the PLL-TRNG design                            | 81 |

|   |             |         |                                                        |    |

|   | 4.2                                           | PLL-TRNG design optimization                       |                                                                                                                     | 84                                     |

|---|-----------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   |                                               | 4.2.1                                              | Genetic algorithm explored $\ldots \ldots \ldots$    | 85                                     |

|   |                                               |                                                    | 4.2.1.1 Generic open-source GA implementation                                                                       | 86                                     |

|   |                                               |                                                    | 4.2.1.2 Custom GA implementation                                                                                    | 86                                     |

|   |                                               | 4.2.2                                              | Optimized exhaustive search                                                                                         | 88                                     |

|   |                                               | 4.2.3                                              | Modifying the PLL-TRNG design to overcome its limitations                                                           | 94                                     |

|   | 4.3                                           | Embe                                               | dded tests                                                                                                          | 95                                     |

|   | 4.4                                           | Stabil                                             | ity of the PLL-TRNG                                                                                                 | 96                                     |

|   |                                               | 4.4.1                                              | Testing methodology                                                                                                 | 97                                     |

|   |                                               | 4.4.2                                              | Test results                                                                                                        | 97                                     |

|   | 4.5                                           | Concl                                              | usion                                                                                                               | 98                                     |

|   |                                               |                                                    |                                                                                                                     |                                        |

| 5 | Rar                                           | ndomr                                              | ness extraction and embedded testing of oscillator based TRNGs                                                      | 105                                    |

| 5 | <b>Ra</b> r<br>5.1                            |                                                    | ess extraction and embedded testing of oscillator based TRNGs<br>barison of different randomness extraction methods | <b>105</b><br>107                      |

| 5 |                                               | Comp                                               | parison of different randomness extraction methods                                                                  |                                        |

| 5 | 5.1                                           | Comp                                               | barison of different randomness extraction methods                                                                  | 107                                    |

| 5 | 5.1                                           | Comp<br>Varia                                      | barison of different randomness extraction methods                                                                  | 107<br>110                             |

| 5 | 5.1                                           | Comp<br>Varian<br>5.2.1                            | Parison of different randomness extraction methods                                                                  | 107<br>110<br>111                      |

| 5 | 5.1                                           | Comp<br>Varian<br>5.2.1<br>5.2.2<br>5.2.3          | Parison of different randomness extraction methods                                                                  | 107<br>110<br>111<br>112               |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Comp<br>Varian<br>5.2.1<br>5.2.2<br>5.2.3          | barison of different randomness extraction methods                                                                  | 107<br>110<br>111<br>112<br>112        |

| C | 5.1<br>5.2<br>5.3<br>onclu                    | Comp<br>Varian<br>5.2.1<br>5.2.2<br>5.2.3<br>Concl | Parison of different randomness extraction methods                                                                  | 107<br>110<br>111<br>112<br>112<br>124 |

# Sommaire

| 0        | Introduction                                                                              | 5   |

|----------|-------------------------------------------------------------------------------------------|-----|

| 1        | Générateurs des nombres véritablement aléatoires pour la cryptographie –<br>état de l'art | 34  |

| <b>2</b> | Sélection et évaluation des noyaux TRNG                                                   | 57  |

| 3        | Implémentation sur ASIC des TRNGs sélectionnés                                            | 79  |

| 4        | Conception d'un PLL-TRNG sécurisé                                                         | 102 |

| 5        | Extraction d'aléa et tests embarqués des TRNGs basés sur les oscillateurs                 | 126 |

| <b>5</b> | Conclusion                                                                                | 135 |

# List of Figures

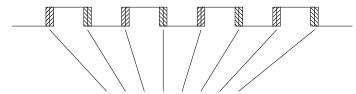

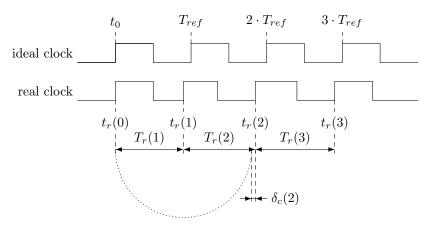

| 1.1  | Clock jitter                                                                                                                                                                     | 12 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

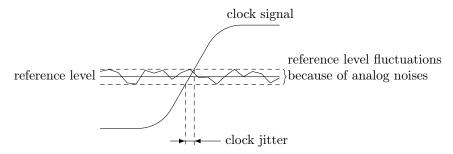

| 1.2  | Reference level fluctuations originating from analog noises causing clock jitter in digital                                                                                      |    |

|      | circuits                                                                                                                                                                         | 13 |

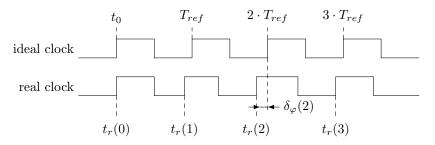

| 1.3  | Illustration of the phase jitter of the second rising edge of the clock signal                                                                                                   | 13 |

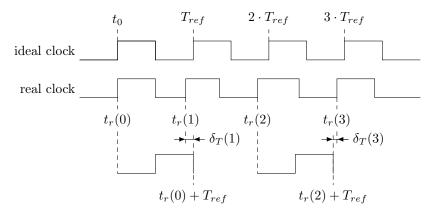

| 1.4  | Illustration of the period jitter of a real clock signal compared to the ideal clock $\ldots$                                                                                    | 14 |

| 1.5  | Illustration of the cycle to cycle jitter                                                                                                                                        | 15 |

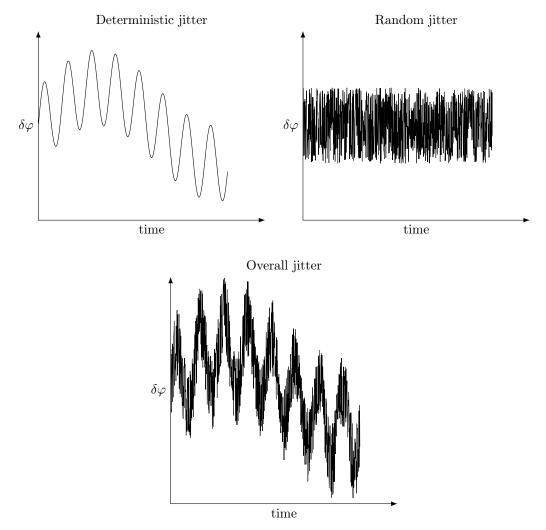

| 1.6  | Overview of deterministic and random jitter components                                                                                                                           | 16 |

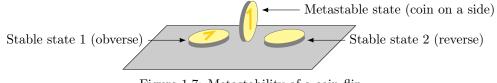

| 1.7  | Metastability of a coin flip                                                                                                                                                     | 17 |

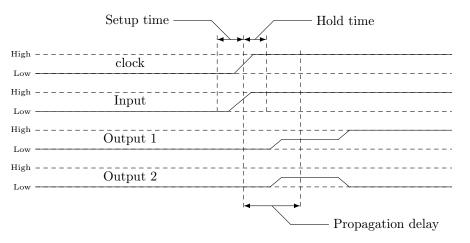

| 1.8  | Example waveforms of a metastable register                                                                                                                                       | 18 |

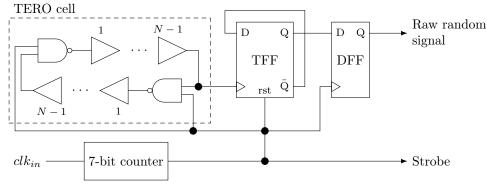

| 1.9  | Internal structure of a TERO                                                                                                                                                     | 19 |

| 1.10 | Example waveforms of a TERO                                                                                                                                                      | 19 |

| 1.11 | Randomness extraction from the jittered clock signal by its sampling on the rising                                                                                               |    |

|      | edge of the reference clock signal $\hdots \ldots \ldots$ | 19 |

| 1.12 | Elementary ring oscillator TRNG                                                                                                                                                  | 20 |

| 1.13 | Block diagram of multi-ring oscillator based TRNG proposed by Sunar et al. [1] and                                                                                               |    |

|      | enhanced (dashed DFFs) by Wold <i>et al.</i> [2]. Reference clock is generated by a ring                                                                                         |    |

|      | oscillator.                                                                                                                                                                      | 21 |

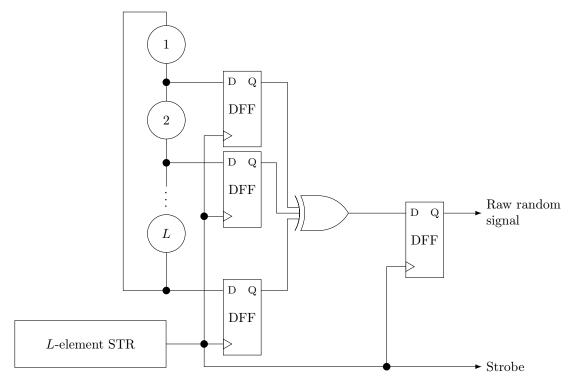

| 1.14 | Block diagram of STR-TRNG. Reference clock is generated by an $L$ -element STR.                                                                                                  | 21 |

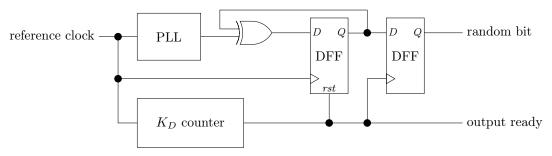

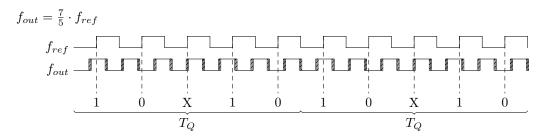

| 1.15 | PLL-TRNG block diagram                                                                                                                                                           | 22 |

| 1.16 | PLL-TRNG subsampling principle                                                                                                                                                   | 23 |

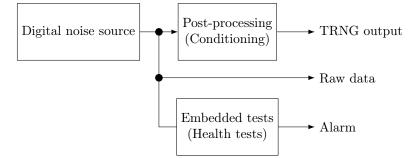

| 1.17 | TRNG block diagram according to AIS-20/31 and NIST 800-90B (NIST 800-90B $$                                                                                                      |    |

|      | terminology in parentheses) $\ldots \ldots \ldots$               | 26 |

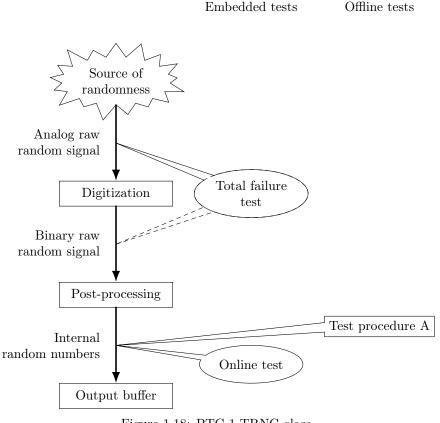

| 1.18 | PTG.1 TRNG class                                                                                                                                                                 | 28 |

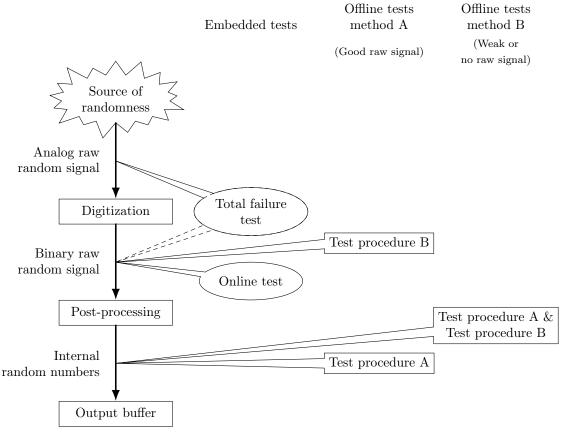

| 1.19 | PTG.2 TRNG class                                                                                                                                                                 | 29 |

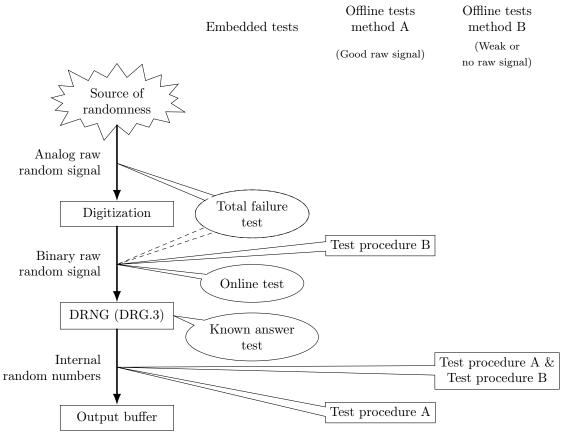

| 1.20 | PTG.3 TRNG class                                                                                                                                                                 | 30 |

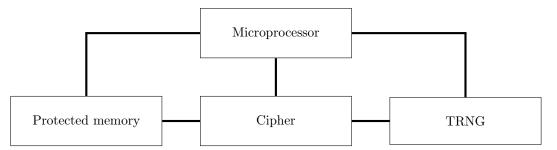

| 2.1  | Cryptographic system integrating multiple components                                                                                                                             | 35 |

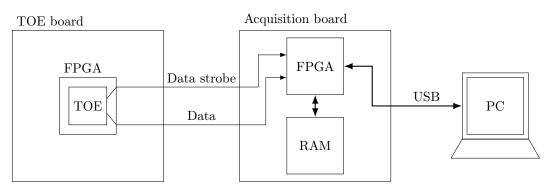

| 2.2  | Hardware platform used for TRNG evaluation                                                                                                                                       | 37 |

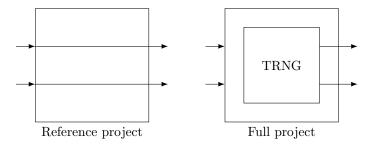

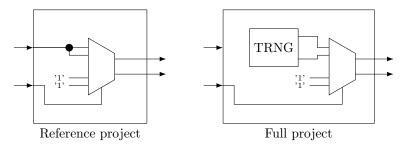

| 2.3  | Unsuitable power consumption measurement using an empty reference project                   | 39 |

|------|---------------------------------------------------------------------------------------------|----|

| 2.4  | Correct power consumption measurement using a multiplexer at the output $\ \ldots \ \ldots$ | 39 |

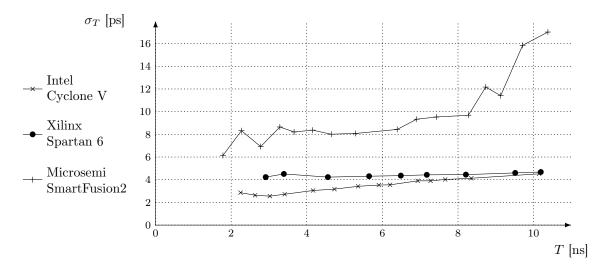

| 2.5  | Period jitter measured for selected FPGA families                                           | 41 |

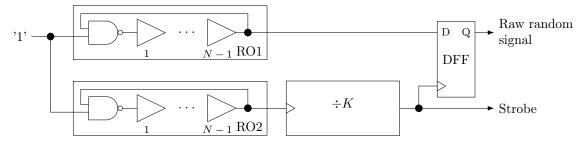

| 2.6  | Architecture of the elementary ring oscillator based TRNG                                   | 42 |

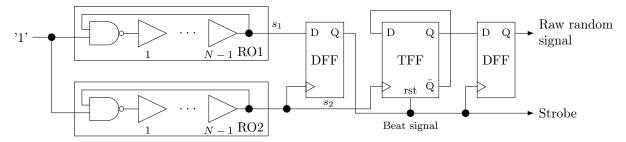

| 2.7  | Architecture of the coherent sampling ring oscillator based TRNG                            | 44 |

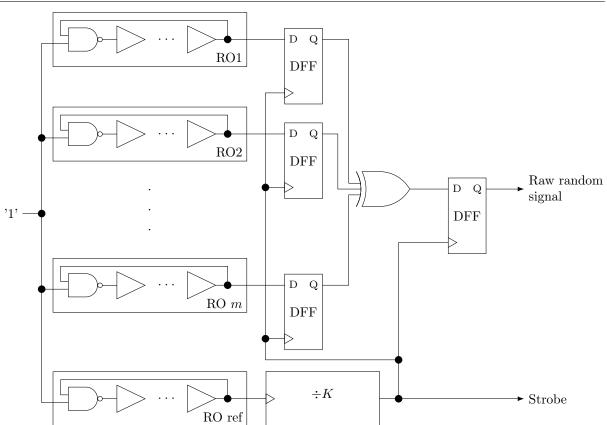

| 2.8  | Architecture of the implemented MURO-TRNG                                                   | 46 |

| 2.9  | Architecture of the TERO-TRNG                                                               | 47 |

| 2.10 | Architecture of the STR-TRNG implemented for evaluation                                     | 48 |

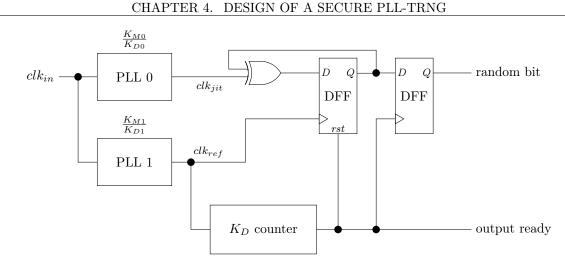

| 2.11 | Architecture of a PLL-TRNG using two PLLs                                                   | 50 |

| 2.12 | Visual comparison of evaluated TRNG cores                                                   | 54 |

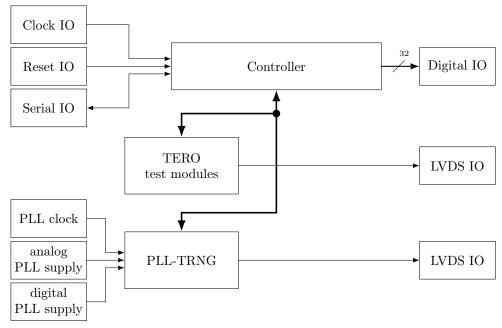

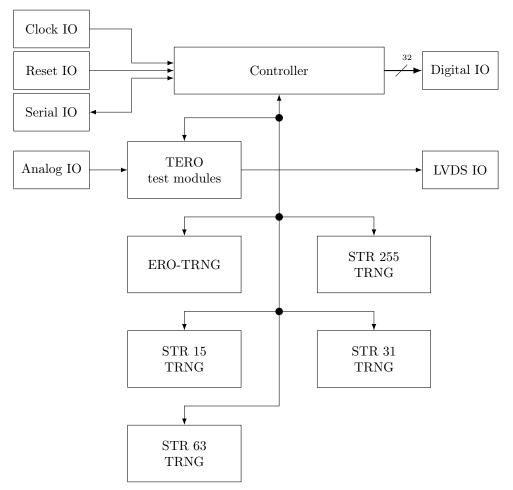

| 3.1  | Block diagram of HECTOR ASIC daughter board                                                 | 63 |

| 3.2  | Block diagram of HECTOR ASIC v1                                                             | 63 |

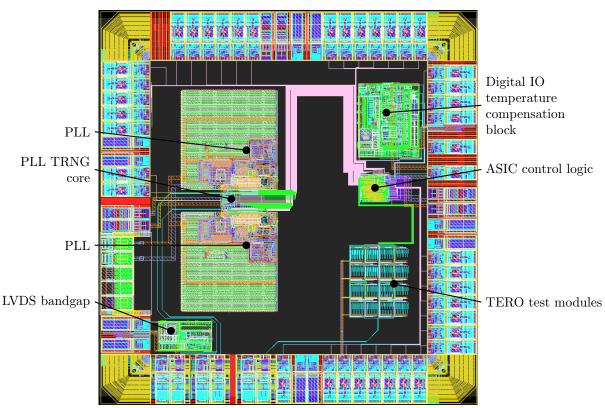

| 3.3  | Physical layout of HECTOR ASIC v1                                                           | 64 |

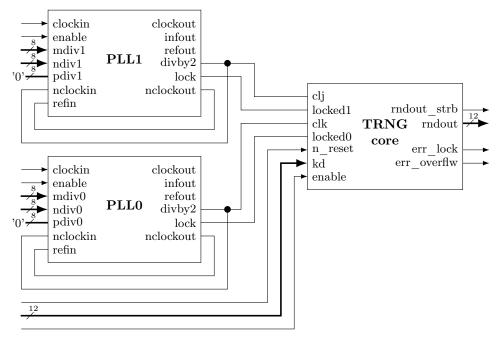

| 3.4  | HECTOR ASIC v1 PLL-TRNG block diagram                                                       | 65 |

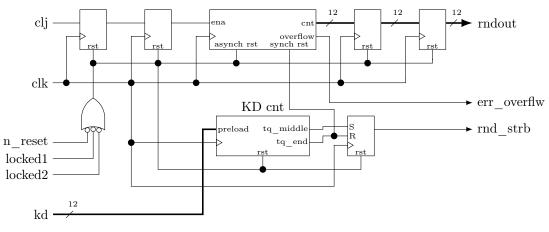

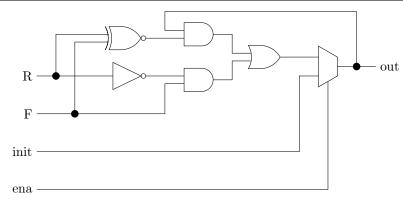

| 3.5  | HECTOR ASIC v1 PLL-TRNG core schematic                                                      | 66 |

| 3.6  | Block diagram of HECTOR ASIC v2                                                             | 67 |

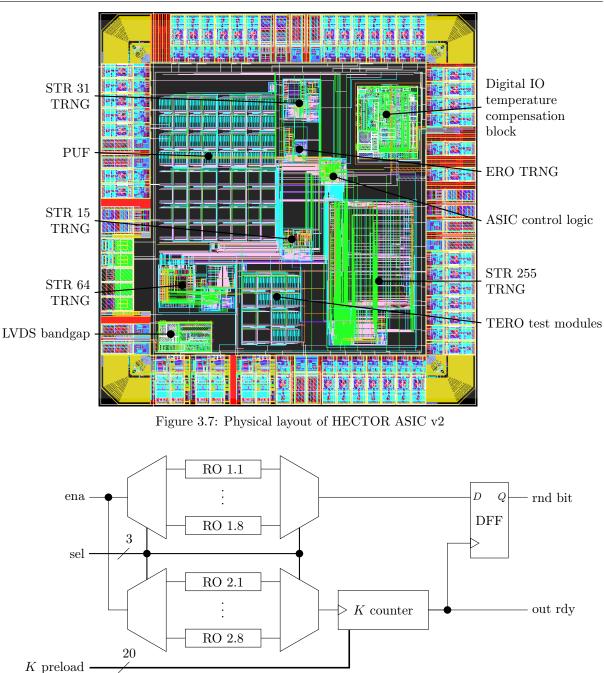

| 3.7  | Physical layout of HECTOR ASIC v2                                                           | 68 |

| 3.8  | Architecture of the ERO-TRNG implemented in HECTOR ASIC v2 $\hfill \ldots$ .                | 68 |

| 3.9  | Schematic of an STR-TRNG using jitter accumulation implemented in HECTOR                    |    |

|      | ASIC v2                                                                                     | 70 |

| 3.10 | Schematic of a pre-chargeable C-element constructed from the standard cells                 | 71 |

| 4.1  | Two PLL variant of the PLL-TRNG                                                             | 82 |

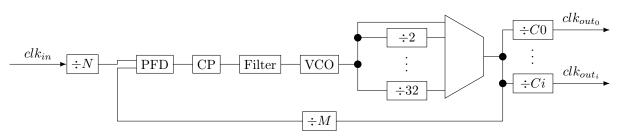

| 4.2  | Internal structure of PLLs as implemented in all major FPGA families (PFD – phase           |    |

|      | frequency detector, CP – charge pump, VCO – voltage controlled oscillator, $N,C_i$ –        |    |

|      | division factors of the PLL, $M$ – multiplication factor of the PLL $\ldots \ldots \ldots$  | 83 |

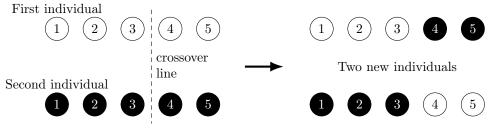

| 4.3  | Crossover operation                                                                         | 85 |

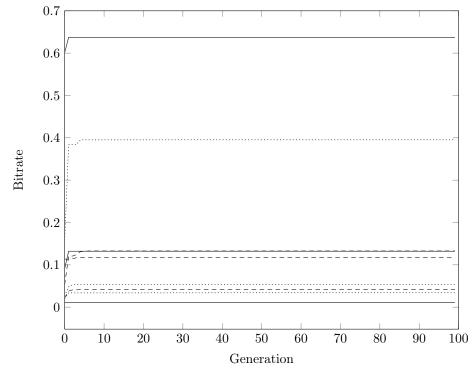

| 4.4  | Best configurations of the single PLL variant of the PLL-TRNG found by several runs         |    |

|      | of the genetic algorithm. Fitness penalty set to 0                                          | 88 |

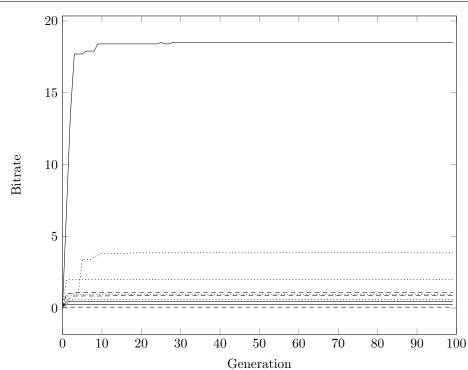

| 4.5  | Best configurations of the single PLL variant of the PLL-TRNG found by several runs         |    |

|      | of the genetic algorithm. Fitness penalty set to 0.1                                        | 89 |

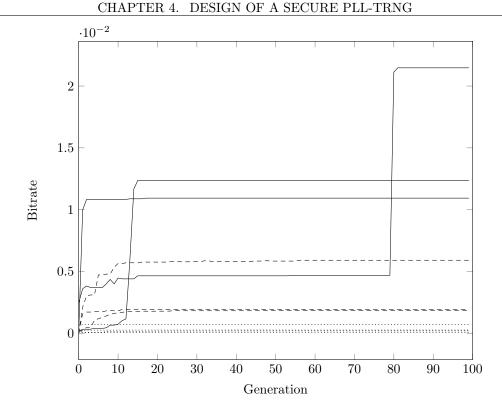

| 4.6  | Best configurations of the two PLL variant of the PLL-TRNG found by several runs            |    |

|      | of the genetic algorithm. Fitness penalty set to 0.1                                        | 90 |

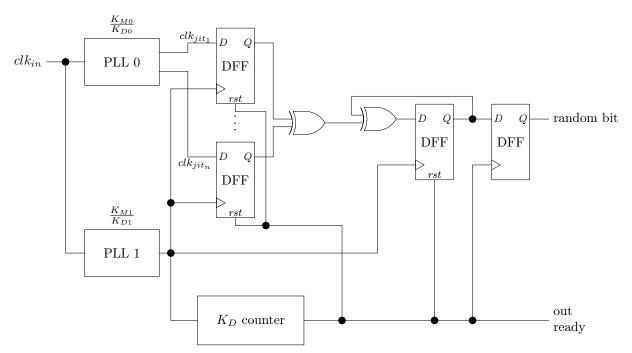

| 4.7  | PLL-TRNG design using multiple phase shifted clocks to increase the output bit rate         | 94 |

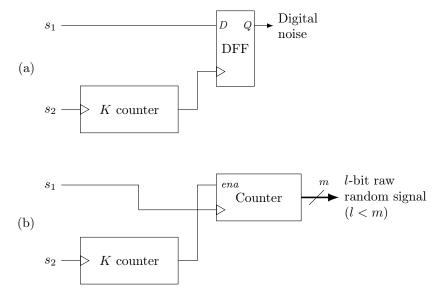

| 5.1  | Randomness extraction using (a) sampling of jittered clock and (b) counting the jit-                    |     |

|------|---------------------------------------------------------------------------------------------------------|-----|

|      | tered periods $\ldots$ | 107 |

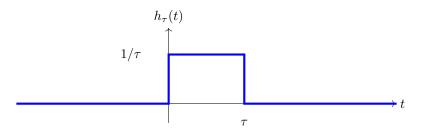

| 5.2  | Convolution computation window of the statistical variance $\ldots \ldots \ldots \ldots \ldots \ldots$  | 111 |

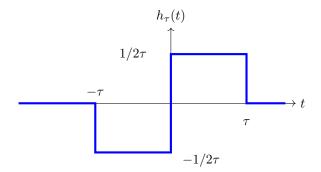

| 5.3  | Allan variance convolution window                                                                       | 112 |

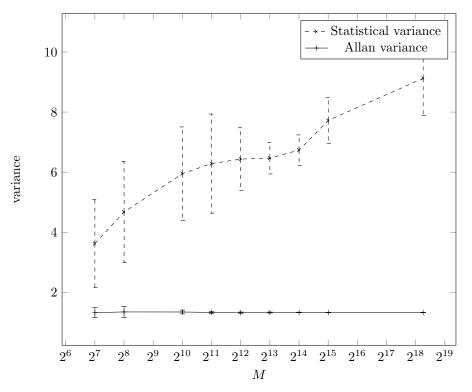

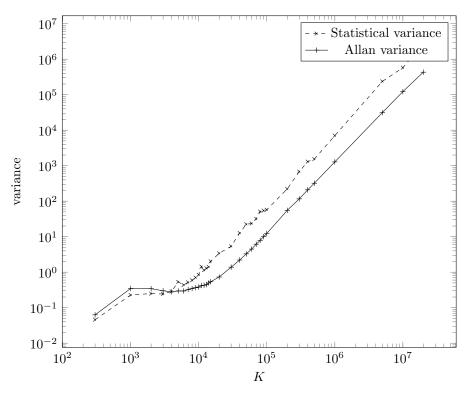

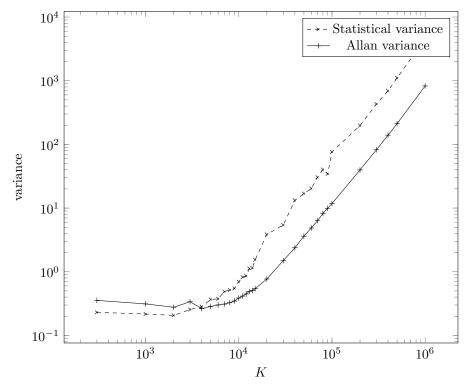

| 5.4  | Variance measurement results dependence on the parameter $M$ $\ .$                                      | 113 |

| 5.5  | Variance of counter values depending on $K$ with two ROs as a source $\ldots \ldots \ldots$             | 114 |

| 5.6  | Variance of counter values depending on $K$ with two STRs as a source $\ldots \ldots \ldots$            | 115 |

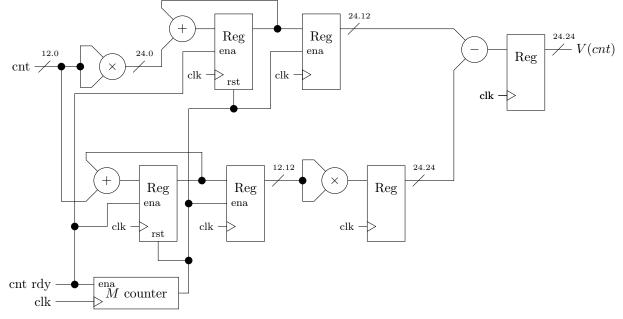

| 5.7  | Statistical variance measurement circuitry                                                              | 116 |

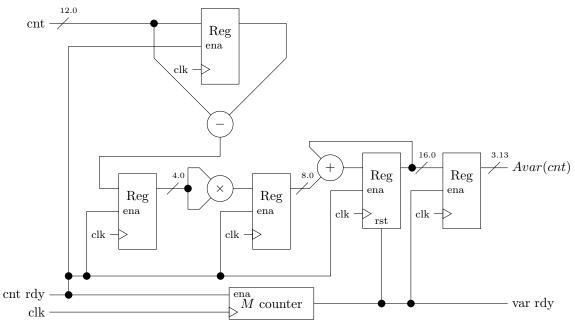

| 5.8  | Allan variance measurement circuitry                                                                    | 116 |

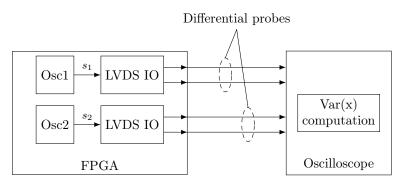

| 5.9  | External jitter measurement using oscilloscope and differential probes                                  | 117 |

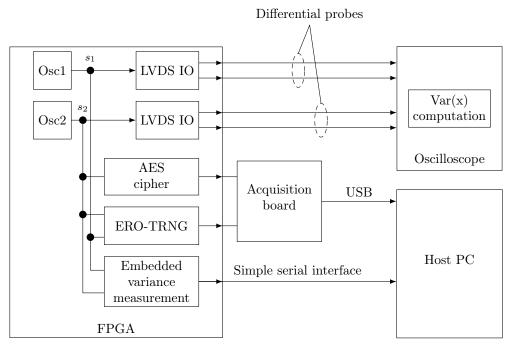

| 5.10 | External jitter measurement using oscilloscope and differential probes together with                    |     |

|      | internal variance measurement and other components of the cryptographic SoC $$                          | 118 |

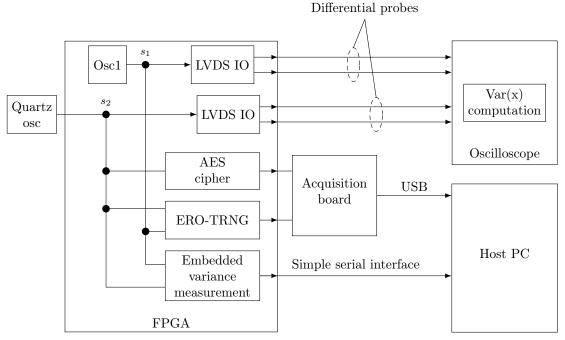

| 5.11 | Crypto SoC with one internal and one external oscillator as source of randomness                        | 118 |

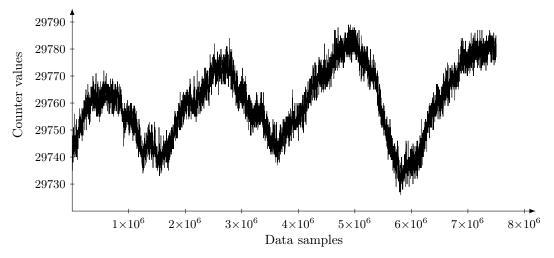

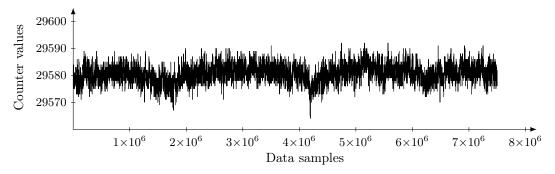

| 5.12 | Counter values acquired using a quartz oscillator for $s_2 \ldots \ldots \ldots \ldots \ldots \ldots$   | 120 |

| 5.13 | Counter values acquired using two identical ROs for $s_1$ and $s_2$                                     | 120 |

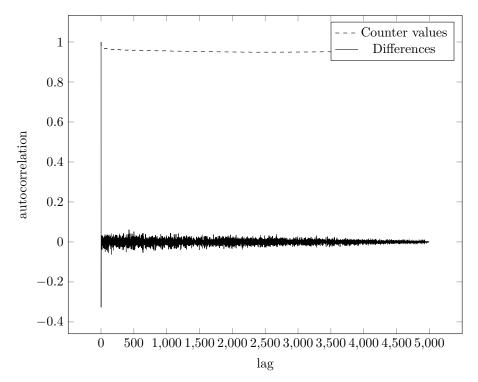

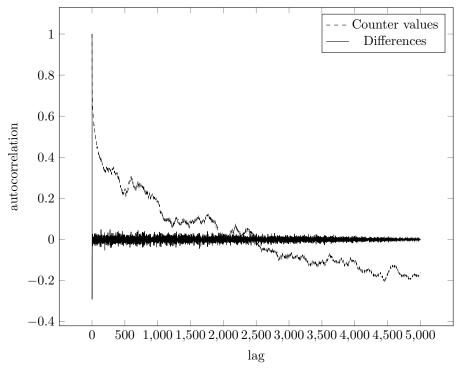

| 5.14 | Autocorrelation function of counter values and their first order differences when gen-                  |     |

|      | erated by one RO and one external quartz oscillator                                                     | 121 |

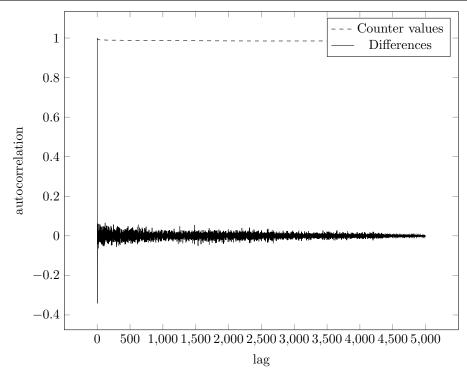

| 5.15 | Autocorrelation function of counter values and their first order differences when gen-                  |     |

|      | erated by one STR and one external quartz oscillator $\hdots$                                           | 122 |

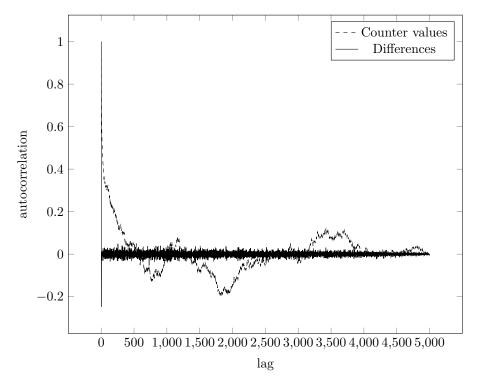

| 5.16 | Autocorrelation function of counter values and their first order differences when gen-                  |     |

|      | erated by two identical ROs                                                                             | 122 |

| 5.17 | Autocorrelation function of counter values and their first order differences when gen-                  |     |

|      | erated by two identical STRs                                                                            | 123 |

## List of Tables

| 2.1 | PLL parameters and corresponding distance between samples ( $\Delta$ ) for selected FPGA |     |

|-----|------------------------------------------------------------------------------------------|-----|

|     | families                                                                                 | 51  |

| 2.2 | Implementation results of selected TRNGs                                                 | 52  |

| 2.3 | Scoring system for TRNG comparison                                                       | 53  |

| 3.1 | Ring oscillator frequencies used in ERO-TRNG in HECTOR ASIC v2 $\ldots \ldots \ldots$    | 69  |

| 3.2 | PLL configurations of the PLL-TRNG tested in HECTOR ASIC v1                              | 74  |

| 3.3 | Results of statistical testing of the PLL-TRNG implemented in HECTOR ASIC v1 $$ .        | 74  |

| 3.4 | Results of statistical testing of the ERO-TRNG implemented in HECTOR ASIC v2 .           | 75  |

| 3.5 | Comparison between expected and real frequencies of sampling sources of STR-TRNG         |     |

|     | in HECTOR ASIC v2                                                                        | 76  |

| 3.6 | Results of statistical testing of the 15 element STR-TRNG with the sampling source       |     |

|     | 4 from Table 3.5                                                                         | 77  |

| 3.7 | Results of statistical testing of the 15 element STR-TRNG with the sampling source       |     |

|     | 5 from Table 3.5                                                                         | 77  |

| 4.1 | PLL specifications for Intel Cyclone V, Xilinx Spartan-6, and Microsemi SmartFusion2     |     |

|     | FPGA families                                                                            | 84  |

| 4.2 | Three PLL-TRNG configurations found by the GA for each tested FPGA family. Best          |     |

|     | candidate is highlighted in bold                                                         | 87  |

| 4.3 | Best PLL configurations for the two PLL variant of the PLL-TRNG with jitter sensi-       |     |

|     | tivity $S > 0.09 p s^{-1}$                                                               | 93  |

| 4.4 | HECTOR PLL-TRNG parameters                                                               | 95  |

| 4.5 | PLL-TRNG temperature and voltage sensitivity tests according to AIS-20/31 and            |     |

|     | embedded tests                                                                           | 98  |

| 4.6 | PLL-TRNG temperature and voltage sensitivity tests according to NIST800-90B $$           | 99  |

| 5.1 | Entropy estimation using two internal ROs and the sampling method of extraction          | 108 |

| 5.2 | Entropy estimation using two internal STRs and the sampling method of extraction.        | 108 |

| 5.3 | Entropy estimation using two internal ROs and extracting the least significant bits of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | counter values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 109 |

| 5.4 | Entropy estimation using two internal ROs and extracting the least significant bits of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|     | the first differences of counter values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 109 |

| 5.5 | Entropy estimation using two internal STRs and extracting the least significant bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|     | of counter values. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 109 |

| 5.6 | Entropy estimation using two internal STRs and extracting the least significant bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|     | of the first differences of counter values. $\hdots \hdots \hdot$ | 110 |

| 5.7 | Implementation results of different variance measurement methods in Intel Cyclone V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|     | FPGA device 5CEBA4F17C8N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 117 |

| 5.8 | Impact of surrounding logic on the randomness source as well as on the embedded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|     | variance measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 119 |

# List of Symbols

| ASIC                 | Application Specific Integrated Circuit      |

|----------------------|----------------------------------------------|

| COSO-TRNG            | Coherent sampling ring oscillator based TRNG |

| $\operatorname{CSV}$ | Comma Separated Values                       |

| DFF                  | D flip-flop                                  |

| DRC                  | Design Rules Check                           |

| DRNG                 | Deterministic Random Number Generator        |

| EA                   | Evolutionary Algorithm                       |

| ERO-TRNG             | Elementary ring oscillator based TRNG        |

| FIT                  | Failure In Time                              |

| FPGA                 | Field Programmable Logic Array               |

| GA                   | Genetic Algorithm                            |

| KAT                  | Known Answer Test                            |

| LUT                  | Look-up table                                |

| LVS                  | Layout Versus Schematic check                |

| MAC                  | Multiply and accumulate                      |

| MPW                  | Multi Project Wafer                          |

| MTBF                 | Mean Time Between Failures                   |

| MURO-TRNG            | Multi-ring oscillator based TRNG             |

| NPTRNG               | Non-Physical True Random Number Generator    |

| PLL                  | Phase-locked loop                            |

| PLL-TRNG             | Phase-locked loop based TRNG                 |

| PRNG      | Pseudo-Random Number Generator              |

|-----------|---------------------------------------------|

| PTRNG     | Physical True Random Number Generator       |

| RNG       | Random Number Generator                     |

| STR       | Self-timed ring                             |

| STR-TRNG  | Self-timed ring oscillator based TRNG       |

| TERO      | Transient Effect Ring Oscillator            |

| TERO-TRNG | Transient effect ring oscillator based TRNG |

| TFF       | T-flip flop                                 |

| TRNG      | True Random Number Generator                |

### Introduction

Random numbers are widely used in many areas of our lives. We use them to pick who starts on serve in a tennis match, they control our fate in a board game, and they play an integral role in cryptography and information security. To chose the starting player in tennis, we can simply flip a coin. To play a board game, we need more than two random values and thus we use a dice. Cryptography, on the other hand, requires more than just rolling a dice in order to secure our data, digital communication, bank transactions, etc.

One of the fundamental principles of modern cryptography is the Kerchkhoffs's principle, which states that a cryptographic system must remain secure even if everything about it, except the key, is public knowledge. In other words, the whole security of all our digital information stands and falls on the security of the key. This principle puts strong requirements on the characteristics of cryptographic keys. The first requirement is that the key must never leave the cryptographic system in clear and it must be safely stored to prevent any unauthorized access to it. But it is not sufficient to only store it securely if an adversary could just guess the key. To prevent anyone from guessing the key, two conditions must be met:

- A key must be very difficult or ideally impossible to guess. If a key is based on any kind of known data, it makes the guesswork much easier. But if a key is not derived from any known data (*i.e.* random), the only way to guess it is a brute force.

- A key must be periodically renewed to prevent anyone from brute forcing it. Even if the only choice left is to brute force the key, it is still possible to do with sufficient resources and time. To prevent this from happening, we need to renew the key before an adversary can guess it.

A key satisfying these conditions can be generated by a random number generator (RNG).

In this thesis, we will deal with true random number generators (TRNGs) exploiting physical phenomena in hardware (Physical TRNGs). Since implementation of the post-processing algorithms in logic devices is quite straightforward, we aim our attention at implementation of the TRNG core. The difficulty is to find and exploit physical random phenomena, which are intrinsically random, inside logic devices that are designed to implement deterministic systems. It is a challenging task to find a proof that a TRNG is indeed using intrinsically random phenomena.

This was one of the main objectives of the HECTOR project presented in the next paragraph.

### **HECTOR** project

The work presented in this thesis was done in the framework of European research project HECTOR (Hardware Enabled CrypTo and Randomness). Main research topics of this project are development of cryptographic primitives, such as TRNGs, PUFs (Physical Unclonable Functions), and authenticated encryption algorithms, and their integration in a complete cryptographic system. The project efforts are heavily driven by industrial requirements since 6 out of 9 partners are industrial partners, three of them small or middle enterprises. Partners of HECTOR project include:

- Technikon Forschungs–und Planungsgesellschaft mbH, Austria

- Katholieke Universiteit Leuven, Belgium

- Université Jean Monnet Saint-Etienne, France

- Thales Communications & Security SAS, France

- STMicroelectronics Rousset SAS, France

- STMicroelectronics SRL, Italy

- Micronic AS, Slovakia

- Technische Universität Graz, Austria

- Brightsight BV, Netherlands

The main objectives of the project were:

- Efficient implementations of state-of-the-art cryptographic algorithms, as well as resistance to physical attacks. Efficiency objectives can be multi-dimensional: low-area or low memory footprint (e.g. for portable embedded applications), high throughput (e.g. for cloud applications), power-efficiency (when limited power supply or cooling of high end systems), energy-efficiency (for battery operated devices), or low latency (for real-time applications). Multiple objectives may have to be combined.

- Cryptographic algorithms, protocols and many countermeasures against physical attacks expect perfect random numbers, yet in reality they are difficult to generate. A major objective of the HECTOR project was to provide robust and high entropy random numbers including quality metrics. HECTOR provided design, models, implementation, evaluations and advanced tests and robustness evaluations of random number generators and PUFs. It also provided methods and procedures for on-the-fly entropy testing.

- Cryptographic algorithms and many physical security countermeasures such as masking, will fail with poor quality random numbers (e.g. after manipulation). HECTOR aimed at mastering gradual degradation of security levels of cryptographic primitives and hardware

security countermeasures as a function of randomness quality. Existing state-of-the-art algorithms (e.g. AES or KECCAK) were investigated and novel cryptographic primitives that are error or noise tolerant were developed.

- Cryptographic implementations also need to be resistant to attacks. Countermeasures against physical attacks, such as side-channel attacks, fault and electro-magnetic perturbation attacks are expensive in terms of silicon area, execution time, power or energy consumption. Thus another objective of this project was to balance efficiency and robustness and to aim at more efficient countermeasures.

- Efforts were driven by practical challenges, requirements and use cases provided by the industrial partners of the project.

- HECTOR provided inputs to standardization and certification efforts such as hardwarefriendlier/friendliest cryptographic algorithms or protocols, e.g. light weight algorithms or authenticated encryption. It also provided inputs towards certification and standardization regarding quality testing and evaluation of random numbers.

Most of the effort in HECTOR project was focused on random number generation – TRNG and PUF implementation and testing. Practical requirements driven by industrial partners required a new specialized evaluation platform. So HECTOR evaluation boards [3] were created especially for TRNG and PUF testing.

### Thesis objectives

This thesis deals with TRNG development within the frame of industrial requirements of HECTOR project. The objectives of the thesis are hence based on the objectives of the HECTOR project, namely:

- Implementation and evaluation of high entropy TRNGs and design, implementation and evaluation of dedicated embedded tests for TRNGs.

- On top of the HECTOR requirements, we also focus on study and optimization of the PLL-TRNG design and oscillator based TRNGs in general.

- We wish to provide automated tools for the PLL-TRNG design, which would enable rapid development of high quality TRNGs within different technological constraints.

- For oscillator based TRNGs, we are searching for efficient methods of randomness extraction and embedded testing, which would improve both bit rate and quality of random numbers produced.

### Introduction

Les nombres aléatoires sont largement utilisés dans de nombreux domaines de notre vie. Nous nous en servons pour choisir qui commence au service dans un match de tennis, ils contrôlent notre destin dans un jeu de société et ils jouent un rôle essentiel dans la cryptographie et la sécurité de l'information. Pour choisir le premier joueur de tennis, il suffit de lancer une pièce de monnaie. Pour jouer à un jeu de société, nous avons besoin de plus de deux valeurs aléatoires et nous utilisons donc un dé. La cryptographie, en revanche, nécessite plus que de lancer un dé pour sécuriser nos données, nos communications numériques, nos transactions bancaires, etc.

L'un des principes fondamentaux de la cryptographie moderne est le principe de Kerchkhoff, selon lequel un système cryptographique doit rester sécurisé même si tout ce qui le concerne, à l'exception de la clé, est de notoriété publique. En d'autres termes, toute la sécurité de toutes nos informations numériques repose sur la sécurité de la clé. Ce principe impose de fortes exigences sur les caractéristiques des clés cryptographiques. La première exigence est que la clé ne doit jamais sortir du système cryptographique en clair et qu'elle doit être stockée en toute sécurité pour empêcher tout accès non autorisé à celle-ci. Mais il ne suffit pas de la stocker en toute sécurité si un adversaire peut deviner la clé. Pour empêcher quiconque de deviner la clé, deux conditions doivent être remplies :

- Une clé doit être très difficile ou idéalement impossible à deviner. Si une clé est basée sur n'importe quel type de données connues, c'est beaucoup plus facile de la deviner. Mais si une clé n'est dérivée d'aucune donnée connue (*i.e.* aléatoire), le seul moyen de la deviner est par la force brute.

- Une clé doit être renouvelée périodiquement pour empêcher quiconque de la deviner par la force brute. Même si le seul choix qui reste est de deviner la clé par la force brute, c'est encore possible de le faire avec les ressources et le temps suffisants. Pour éviter complètement cette possibilité, nous devons renouveler la clé avant qu'un adversaire puisse la deviner.

Une clé qui remplit ces conditions peut être générée par un générateur de nombres aléatoires (RNG).

Dans cette thèse, nous nous intéressons aux générateurs de nombres véritablement aléa-

toires (TRNGs) exploitant des phénomènes physiques dans les circuits électroniques (TRNG physiques). L'implémentation des algorithmes de post-traitement dans les circuits logiques étant assez simple, nous concentrons notre attention sur l'implémentation du noyau du TRNG. La difficulté est de trouver et d'exploiter des phénomènes aléatoires physiques, intrinsèquement aléatoires, à l'intérieur de circuits logiques, destinés à l'implémentation de systèmes déterministes. C'est un défi de prouver qu'un générateur de nombres aléatoires utilise effectivement des phénomènes intrinsèquement aléatoires. C'était un des objectifs principaux du projet HECTOR présenté dans le paragraphe suivant.

### **Projet HECTOR**

Le travail présenté dans cette thèse a été réalisé dans le cadre du projet de recherche européen HECTOR (CrypTo et Randomness Enabled Hardware). Les sujets principaux de recherche de ce projet sont le développement de primitives cryptographiques, telles que les TRNG, les PUF (fonctions physiques non clonables) et les algorithmes de chiffrement authentifiés, ainsi que leur intégration dans un système cryptographique complet. Les efforts du projet sont fortement motivés par les exigences industrielles puisque six partenaires sur neuf sont des partenaires industriels, dont trois petites ou moyennes entreprises. Les partenaires du projet HECTOR comprennent :

- Technikon Forschungs-und Planungsgesellschaft mbH, Autriche

- Katholieke Universiteit Leuven, Belgique

- Université Jean Monnet Saint-Etienne, France

- Thales Communications & Security SAS, France

- STMicroelectronics Rousset SAS, France

- STMicroelectronics SRL, Italie

- Micronic AS, Slovaquie

- Technische Universität Graz, Autriche

- Brightsight BV, Pays-Bas

Les principaux objectifs du projet étaient:

— L'implémentation efficace d'algorithmes cryptographiques de l'état de l'art, ainsi que leur résistance aux attaques physiques. Les objectifs d'efficacité peuvent être multidimensionnels : faible surface ou faible empreinte mémoire (par exemple pour les applications embarquées portables), débit élevé (par exemple pour les applications sur le cloud), efficacité en puissance (lorsque l'alimentation électrique ou le refroidissement des systèmes haut de gamme sont limités), efficacité énergétique (pour les appareils alimentés par batterie), ou faible latence (pour les applications temps réel). Il peut être nécessaire de combiner plusieurs objectifs.

- Les algorithmes cryptographiques, les protocoles et de nombreuses contre-mesures contre les attaques physiques attendent des nombres aléatoires parfaits, mais ils sont en réalité difficiles à générer. L'un des objectifs principaux du projet HECTOR était de fournir des nombres aléatoires robustes à entropie élevée, ainsi que des mesures de qualité. HECTOR a fourni la conception, les modèles, la mise en œuvre, les évaluations, ainsi que les tests avancés et les évaluations de robustesse des générateurs de nombres aléatoires et des PUF. Il a également fourni des méthodes et des procédures pour les tests d'entropie à la volée.

- Les algorithmes cryptographiques et de nombreuses contre-mesures de sécurité physique, telles que le masquage, échoueront avec des nombres aléatoires de qualité médiocre (par exemple, après manipulation). HECTOR visait à maîtriser la dégradation progressive des niveaux de sécurité des primitives cryptographiques et des contre-mesures de sécurité matérielles en fonction de la qualité du caractère aléatoire. Des algorithmes de pointe existants (par exemple, AES ou KECCAK) ont été étudiés et de nouvelles primitives cryptographiques qui tolèrent les erreurs ou le bruit ont été développées.

- Les implémentations cryptographiques doivent également être résistantes aux attaques. Les contre-mesures contre les attaques physiques, telles que les attaques par canaux auxiliaires, les attaques en fautes ou par perturbations électromagnétiques sont coûteuses en termes de surface de silicium, de temps d'exécution, de consommation énergétique. Un autre objectif de ce projet était donc de trouver un équilibre entre efficacité et robustesse et de rechercher des contre-mesures plus efficaces.

- Les efforts ont été motivés par les défis pratiques, les exigences et les cas d'utilisation fournis par les partenaires industriels du projet.

- HECTOR a contribué aux efforts de normalisation et de certification en proposant des algorithmes ou des protocoles cryptographiques plus conviviaux d'un point de vue matériel ou algorithmique, comme les algorithmes légers ou le cryptage authentifié. Il a également contribué à la certification et à la normalisation de tests de qualité et d'évaluation de nombres aléatoires.

Le projet HECTOR s'est principalement concentré sur la génération de nombres aléatoires – mise en œuvre et tests de TRNG et de PUF. Les exigences pratiques dictées par les partenaires industriels nécessitaient une nouvelle plate-forme d'évaluation spécialisée. Les cartes d'évaluation HECTOR [3] ont donc été crées spécialement pour les tests de TRNG et PUF.

### Objectifs de la thèse

Cette thèse traite du développement de TRNG dans le cadre des exigences industrielles du projet HECTOR. Les objectifs de la thèse sont donc basés sur les objectifs du projet HECTOR,

### à savoir:

- Implémentation et évaluation de TRNG à haute entropie et conception, implémentation et évaluation de tests embarqués dédiés pour les TRNG.

- Outre les exigences d'HECTOR, nous nous concentrons également sur l'étude et l'optimisation de la conception du TRNG basé sur les PLLs et des TRNG basées sur les oscillateurs en général.

- Nous souhaitons fournir des outils automatisés pour la conception du PLL-TRNG, qui permettraient le développement rapide de TRNG de haute qualité avec différentes contraintes technologiques.

- Pour les TRNG basés sur les oscillateurs, nous recherchons des méthodes efficaces d'extraction d'aléa et des tests intégrés permettant d'améliorer à la fois le débit et la qualité des nombres aléatoires produits.

### Chapter 1

# Random number generators in cryptography – state of the art

Cryptography is used in every information system nowadays and random number generators (RNGs) are an essential part of any cryptographic system. In a cryptographic system, RNGs are used (not only) to generate cryptographic keys, but also nonces, initialization vectors, and random masks for protection against side channel attacks.

Despite there being a lot of different applications of random numbers in a cryptographic system they all share two basic requirements:

- Good statistical properties, namely uniform probability distribution. Every value of any random number used in a cryptographic system must be equally likely to appear. This requirement is of utmost importance since a biased probability distribution would open the door to an attacker e.g. by making frequency attacks possible.

- **Unpredictability of random numbers.** Random numbers, especially those used for secret parameters such as keys, must be unpredictable to prevent an attacker from being able to compute future or preceding values from the already generated and captured data.

Given the vast spectrum of RNG applications in cryptography, it is only natural that many different RNG principles exist to satisfy their various needs. Based on the method used to generate random numbers, we distinguish two fundamental RNG types:

**Deterministic/Pseudo random number generator (DRNG, PRNG)** is a system, which produces random-looking sequence mathematically. Produced numbers seem random in short term, but the sequence is periodic, usually with a long period. In order to produce less predictable output, these RNGs use initialization values called seeds to start from. For

every seed, there is a different sequence generated. Output sequence of a good DRNG is perfectly uniformly distributed. DRNGs achieve high output bit rates.

- True random number generators (TRNGs), on the other hand, are not algorithmic, but instead they are systems, which extract randomness from non-algorithmic random phenomena. These phenomena may be temperature fluctuations, radioactive decay, ambient radio noise, hard disk access times, or user interactions with the PC. Since the phenomena used are intrinsically unpredictable, TRNGs produce real random data instead of just randomlooking periodic sequences. The behavior of a TRNG is not defined by a mathematical formula, which is the case of DRNGs. Since the quality of generated random sequence depends on physical properties, the output sequence may exhibit some statistical defects such as bias. TRNGs are in general slower than DRNGs.' Based on the source used, they can be further divided to:

- *Physical TRNG (PTRNG)* uses physical noise on electron level present in all semiconductors. A PTRNG is a physical device and uses physical noise.

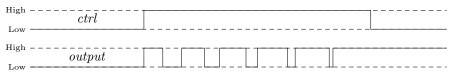

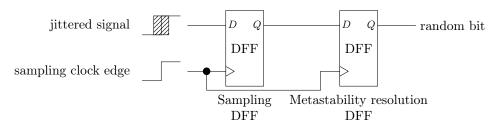

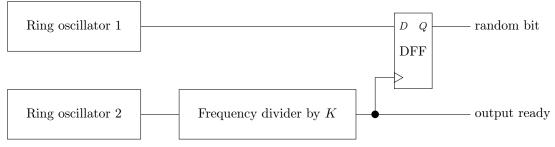

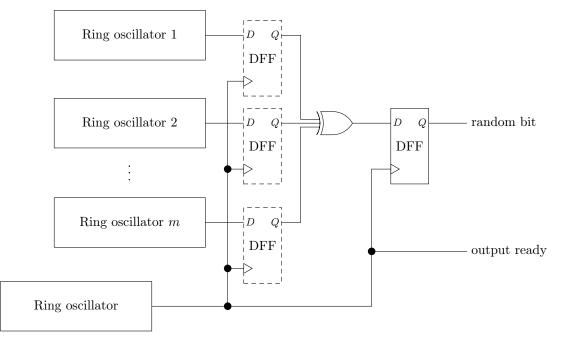

- *Non-physical TRNG (NPTRNG)* may not be a physical device, but instead a piece of software. It uses non-physical randomness source such as user interactions with an operating system.