# Etude et implantation d'algorithmes pour le placement et l'ordonnancement d'applications Dataflow

Hamza Deroui

### ▶ To cite this version:

Hamza Deroui. Etude et implantation d'algorithmes pour le placement et l'ordonnancement d'applications Dataflow. Traitement du signal et de l'image [eess.SP]. INSA de Rennes, 2019. Français. NNT: 2019ISAR0022. tel-02903493

## HAL Id: tel-02903493 https://theses.hal.science/tel-02903493

Submitted on 21 Jul 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

L'INSTITUT NATIONAL DES SCIENCES **APPLIQUEES RENNES**

COMUE UNIVERSITE BRETAGNE LOIRE

**ECOLE DOCTORALE N° 601** Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Signal, Image, Vision

Par

### Hamza DEROUI

Étude et implantation d'algorithmes pour l'ordonnancement d'applications Dataflow.

Thèse présentée et soutenue à Rennes, le 06/12/2019

Unité de recherche : IETR Thèse N°: 19ISAR 29 / D19 - 29

### Rapporteurs avant soutenance:

### **Emmanuel JEANNOT**

Directeur de Recherche à l'INRIA Bordeaux Sud-Ouest Matthieu MOY

Maître de conférences, HDR, à l'Université Claude Bernard Lyon 1

### **Composition du Jury:**

### Jocelyn SEROT

Professeur d'Université à l'Institut Pascal de Clermont Ferrand / Président du jury

### **Emmanuel JEANNOT**

Directeur de Recherche à l'INRIA Bordeaux / Rapporteur

### **Matthieu MOY**

Maître de conférences, HDR à l'Université Claude Bernard Lyon 1 / Rapporteur

### Jean-François NEZAN

Professeur d'Université à l'INSA Rennes / Directeur de thèse

### **Karol DESNOS**

Maître de conférences à l'INSA Rennes / Examinateur

### **Alix MUNIER-KORDON**

Professeur d'Université à Sorbonne Université, LIP6 / Examinatrice

### Intitulé de la thèse :

Étude et implantation d'algorithmes pour l'ordonnancement d'applications Dataflow.

### **Hamza DEROUI**

# En partenariat avec :

Document protégé par les droits d'auteur

# Contents

| A | cknov | wledge  | ments                                                         | 1  |

|---|-------|---------|---------------------------------------------------------------|----|

| 1 | Intr  | oducti  | on                                                            | 3  |

|   | 1.1   | Genera  | al Context                                                    | 3  |

|   |       | 1.1.1   | Embedded Systems                                              | 3  |

|   |       | 1.1.2   | Designing Embedded Systems                                    | 4  |

|   | 1.2   | Contri  | butions                                                       | 5  |

|   | 1.3   | Outlin  | e                                                             | 6  |

| 2 | Dat   | aflow I | Models of Computation                                         | 7  |

|   | 2.1   | Introd  | uction                                                        | 7  |

|   | 2.2   | Datafle | ow Programming                                                | 8  |

|   |       | 2.2.1   | Semantics                                                     | 8  |

|   |       | 2.2.2   | Expression of parallelism                                     | 9  |

|   | 2.3   | Static  | Dataflow Models of Computation                                | 10 |

|   |       | 2.3.1   | Synchronous Dataflow (SDF) model                              | 10 |

|   |       | 2.3.2   | Homogeneous SDF (HSDF), Single-Rate SDF (srSDF), and Directed |    |

|   |       |         | Acyclic Graph (DAG) models                                    | 11 |

|   |       | 2.3.3   | Cyclo-Static DataFlow (CSDF) model                            | 11 |

|   | 2.4   | Dynan   | nic Dataflow Models                                           | 12 |

|   |       | 2.4.1   | Scenario Aware Dataflow (SADF)                                | 12 |

|   |       | 2.4.2   | Boolean Dataflow (BDF)                                        | 13 |

|   | 2.5   | Hierar  | chical Static Dataflow Models                                 | 14 |

|   |       | 2.5.1   | Hierarchical SDF                                              | 14 |

|   |       | 2.5.2   | Interface-based SDF (IBSDF)                                   | 15 |

|   | 2.6   | Hierar  | chical Parametric Dataflow Models                             | 16 |

|   |       | 2.6.1   | Parameterized SDF (PSDF)                                      | 16 |

|   |       | 2.6.2   | Parameterized and interfaced SDF ( $\pi$ SDF)                 | 18 |

|   | 2.7   | Conclu  | ısion                                                         | 19 |

| 3 | Dev   | elopm   | ent Process of Dataflow Graphs                                | 21 |

|   | 3.1   | Introd  | uction                                                        | 21 |

|   | 3.2   | Rapid   | Prototyping                                                   | 22 |

|   |       | 3.2.1   | Preesm Rapid Prototyping Framework                            | 23 |

${\it CONTENTS}$

|   |             | 3.2.2 Preesm Typical workflow                                    | 23         |

|---|-------------|------------------------------------------------------------------|------------|

|   | 3.3         | Consistency Evaluation and Repetition Vector (RV)                | 24         |

|   |             | 3.3.1 Consistency of a Synchronous Dataflow (SDF) graph          | 24         |

|   |             | 3.3.2 Consistency of a Hierarchical SDF (Hierarchical SDF) graph | 25         |

|   |             | 3.3.3 Consistency of an Interface-Based SDF (IBSDF) graph        | 25         |

|   | 3.4         | Dataflow graphs Conversion                                       |            |

|   |             | 3.4.1 SDF graph conversions                                      |            |

|   |             | 3.4.2 Flattening the hierarchy of an IBSDF graph                 |            |

|   | 3.5         | Liveness Evaluation                                              |            |

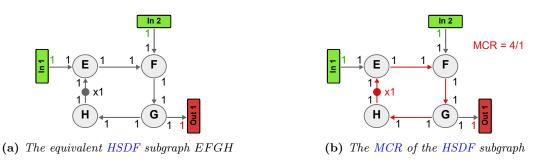

|   | 0.0         | 3.5.1 Liveness evaluation of Homogeneous SDF (HSDF) graph        |            |

|   |             | 3.5.2 Liveness evaluation of SDF graph                           |            |

|   |             | 3.5.3 Liveness evaluation of IBSDF graph                         |            |

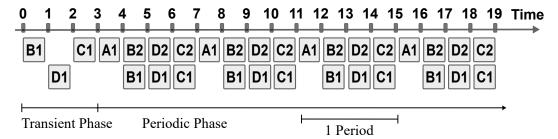

|   | 3.6         | Simulating a Dataflow graph                                      |            |

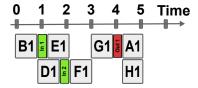

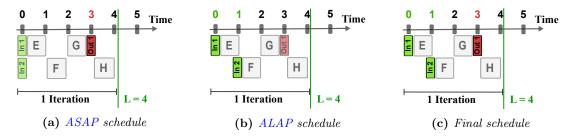

|   | 0.0         | 3.6.1 ASAP Schedule                                              |            |

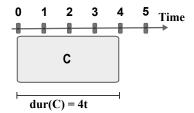

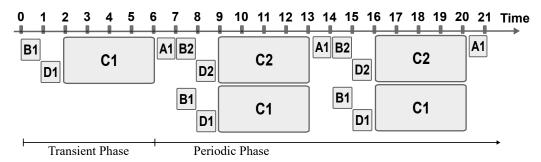

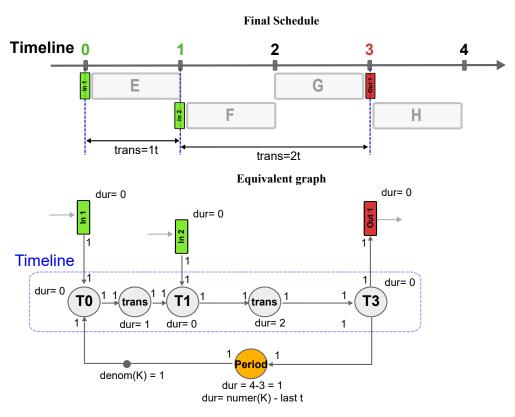

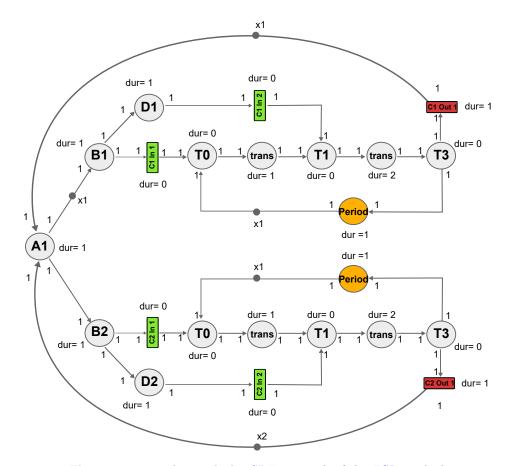

|   |             | 3.6.2 Periodic Schedule                                          |            |

|   | 3.7         | Mapping and Scheduling Dataflow Graphs                           |            |

|   | 0.1         | 3.7.1 Scheduling Methodologies                                   |            |

|   |             | 3.7.2 Solving the mapping and scheduling problem                 |            |

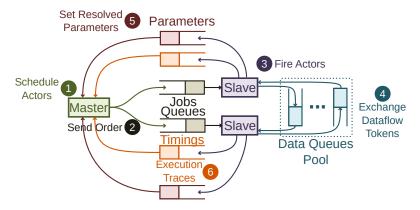

|   | 3.8         | SPIDER: a Run-time Manager for dataflow graphs                   |            |

|   | <b>3.</b> 6 | 3.8.1 Overview of SPIDER                                         |            |

|   |             | 3.8.2 SPIDER Structure                                           |            |

|   |             | 3.8.3 SPIDER Operations                                          |            |

|   | 3.9         | Tools                                                            |            |

|   | 3.9         | 3.9.1 SDF3 tool                                                  |            |

|   |             |                                                                  |            |

|   | 2.10        | 3.9.2 Turbine tool                                               |            |

|   | 3.10        | Conclusion                                                       | <b>3</b> C |

| 4 | Thr         | oughput Evaluation of IBSDF graph                                | 39         |

| _ | 4.1         | Introduction                                                     |            |

|   | 4.2         | SDF State-Of-The-Art Methods                                     |            |

|   | 1.2         | 4.2.1 HSDF based method                                          |            |

|   |             | 4.2.2 Max-plus Algebra-based method                              |            |

|   |             | 4.2.3 State-Space Exploration method                             |            |

|   |             | 4.2.4 Periodic schedule based method                             |            |

|   |             | 4.2.5 K-Iter method                                              |            |

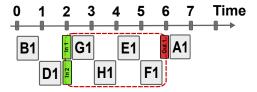

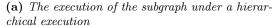

|   | 4.3         | Execution Modes of IBSDF graph                                   | 46         |

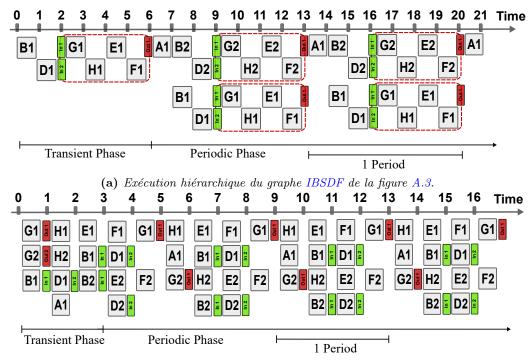

|   | 4.0         | 4.3.1 Hierarchical Execution                                     | 46         |

|   |             | 4.3.2 Relaxed Execution                                          |            |

|   | 4.4         | Throughput Evaluation by Flattening the Hierarchy                | 49         |

|   | 4.4         | 4.4.1 Classical Approach                                         | 49         |

|   |             | 4.4.2 Modeling the Firing Rules                                  | 49         |

|   | 4.5         | Throughput Evaluation without Flattening the Hierarchy           | 51         |

|   | 4.0         | 4.5.1 The Schedule-Replace (SR) technique                        | 51         |

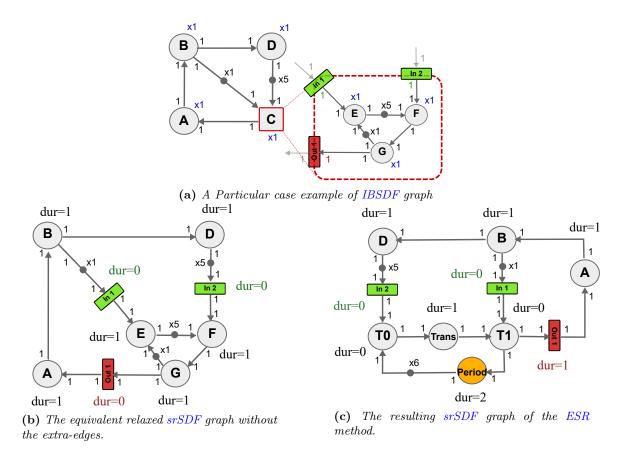

|   |             | 4.5.1 The Schedule-Replace (SR) technique                        | 51<br>54   |

|   | 16          | -                                                                |            |

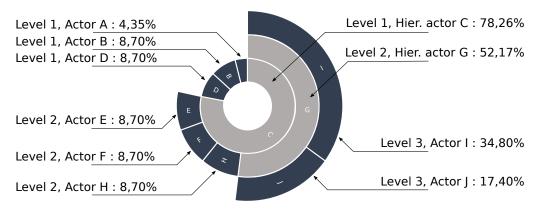

|   | 4.6         | Experimental Results                                             | 60         |

|   |             |                                                                  |            |

|   | 4 7         | 4.6.2 Results                                                    | 61         |

|   | 4.7         | Conclusion                                                       | 63         |

*CONTENTS* iii

| 5  | Late        | ency Evaluation of IBSDF graph                                     | 65    |

|----|-------------|--------------------------------------------------------------------|-------|

|    | 5.1         | Introduction                                                       | . 65  |

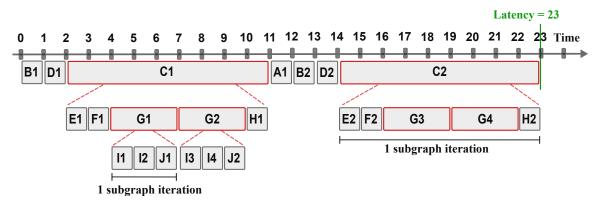

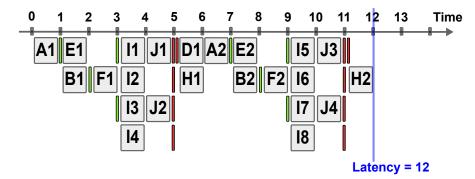

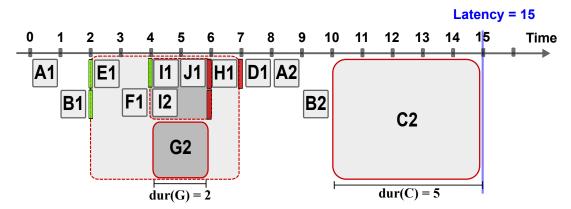

|    | 5.2         | Mono-Core Latency Evaluation                                       | . 67  |

|    |             | 5.2.1 For SDF graph                                                | . 67  |

|    |             | 5.2.2 For IBSDF graph                                              | . 67  |

|    |             | 5.2.3 The Mono-Core Latency from the hierarchy perspective         | . 69  |

|    | 5.3         | Multi-Core Latency Evaluation by flattening the hierarchy          | . 71  |

|    |             | 5.3.1 Critical-Path Method (CPM)                                   | . 71  |

|    |             | 5.3.2 Symbolic-Execution (SE)                                      | . 73  |

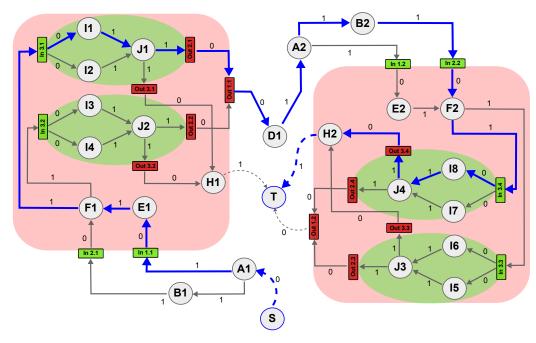

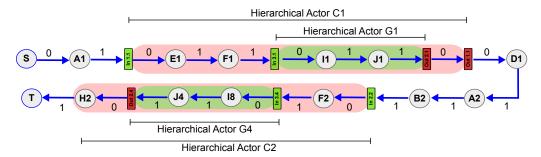

|    | 5.4         | Multi-Core Latency Evaluation without Flattening the Hierarchy     |       |

|    |             | 5.4.1 Hierarchical-Symbolic-Execution (H-SE)                       |       |

|    |             | 5.4.2 Hierarchical-Critical-Path-Method (H-CPM)                    |       |

|    | 5.5         | Experimental Results                                               |       |

|    |             | 5.5.1 Experimental Setup                                           |       |

|    |             | 5.5.2 Results                                                      |       |

|    | 5.6         | Conclusion                                                         |       |

|    | 0.0         |                                                                    | . 00  |

| 6  | Con         | nclusion                                                           | 91    |

|    | 6.1         | Summary                                                            | . 91  |

|    | 6.2         | Future Work                                                        | . 92  |

|    |             | 6.2.1 Modular Mapping and scheduling                               | . 93  |

| A  | Frei        | nch Summary                                                        | 95    |

|    | <b>A</b> .1 | Introduction                                                       | . 95  |

|    | A.2         | Modèles de flot de données                                         | . 96  |

|    |             | A.2.1 Synchronous Dataflow (SDF)                                   | . 97  |

|    |             | A.2.2 Interface-Based SDF (IBSDF)                                  | . 98  |

|    | A.3         | PREESM: un outil de prototypage rapide                             | . 98  |

|    | A.4         | Evaluation du Débit maximal                                        | . 99  |

|    |             | A.4.1 Modes d'exécution d'un graph IBSDF                           | . 99  |

|    |             | A.4.2 Méthode classique pour l'évaluation du débit                 | . 100 |

|    |             | A.4.3 Nouvelle Méthode : Schedule-Replace (SR)                     | . 101 |

|    |             | A.4.4 Nouvelle Méthode : Evaluate-Schedule-Replace (ESR)           |       |

|    | A.5         | Evaluation de la latence minimal                                   |       |

|    |             | A.5.1 Méthode classique pour l'évaluation de la latence            | . 103 |

|    |             | A.5.2 Nouvelle Méthode : Hierarchical-Symbolic-Execution (H-SE)    |       |

|    |             | A.5.3 Nouvelle Méthode : Hierarchical-Critical-Path Method (H-CPM) |       |

|    | A.6         | Experimentations numériques                                        |       |

|    |             | A.6.1 Déroulement des tests                                        |       |

|    |             | A.6.2 Résultats des tests pour l'évaluation du débit               |       |

|    |             | A.6.3 Résultats des tests pour l'évaluation de la latence          |       |

|    | A.7         | Conclusion                                                         |       |

| т; |             | Figures                                                            | 109   |

|    |             |                                                                    |       |

| Li | st of       | Tables                                                             | 113   |

| A  | crony       | /ms                                                                | 115   |

| Personal Publications | 119 |

|-----------------------|-----|

| Bibliography          | 121 |

| Bibliography          | 126 |

### Acknowledgements

I would first, like to thank my thesis advisors Pr. Jean-François Nezan and Pr.Karol Desnos at the National Institute of Applied Sciences (INSA) of Rennes and Pr. Alix Munier-Kordon at Sorbonne University whose help cannot be overestimated and whose the door of their offices was always open whenever I had a question about my research or writing. Thank you for steering me in the right direction and unwavering support.

I would also like to extend my deepest gratitude to the experts who were involved in the validation survey for this research project: Dr. Emmanuel Jeannot senior researcher scientist at INRIA Bordeaux Sud-Ouest, Pr. Matthieu Moy at Claude Bernard Lyon 1 University, and Pr. Jocelyn Serot at Institut Pascal. Without their invaluable insight, the validation survey could not have been successfully conducted.

To all members of the VAADER team of the IETR, thank you for making me feel part of the team since the beginning. Special thanks to all my officemates and coworkers during these three years: Alexandre Sanchez, Pierre-Loup Cabarat, Julien Heulot, Justine Bonnot, Maxime Pelcat, Jean-Gabriel Cousin, Meriem Outtas, and Naty Sidaty. Thanks also to Frédéric Garesché for his IT support and many thanks to Corinne Calo, Aurore Gouin and Jocelyne Trémier for their administrative support.

To my parents and sisters, thank you for surrounding me with love and prayers all along with my school and professional career I will be forever in your debt.

Finally, many thanks to my wife Kaoutar for providing me with unfailing support and continuous encouragement throughout my years of study and through the process of researching and writing this thesis and for accepting nothing less than excellence from me.

Thank you from the bottom of my heart

# CHAPTER 1

Introduction

### 1.1 General Context

### 1.1.1 Embedded Systems

Today, almost every device we use is an embedded system. Remarkably adaptable and versatile, embedded systems can be found at homes, at offices, in industries and automation systems. From the basic ones, like washing machines, home security systems, digital cameras, vending machines, to the highly complex ones, like self-driving cars, missile guidance systems, airplanes and satellites. Embedded systems have been one of the most remarkable technological advances.

Formally, an embedded system is a combination of computer hardware and software, designed to perform a dedicated function. The hardware part includes all the electronic elements of the embedded system, like microprocessors, timers, memory, input/output interfaces, display and sensors. The software part, includes the computer program which is a sequence of instructions executed by the processing elements of the embedded system. The computer program can be simple calculation instructions, a firmware, or an embedded Operating System (OS). Embedded systems can be stand alone devices or integrated as part of a larger embedded system that serves a more general purpose.

Historically, embedded systems date back to the 1960s. The first embedded system was developed by Charles Stark Draper at MIT in 1961 for the Apollo mission. The embedded system was designed to reduce the size and weight of the Apollo guidance computer; the digital system which helped astronauts collect real-time flight data. The Apollo guidance computer was the first computer to use the newly developed monolithic integrated circuits. In fact, it was considered as the riskiest item in the Apollo project. The first mass-produced embedded system was the D-17B, developed by Autonetics in 1965; a computer used in the Minuteman I missile guidance system. Besides, space and military industries, the Volkswagen 1600 was the first vehicle to use an embedded system in 1968. The integrated microprocessor was used to regulate the air-fuel mixture in the electronic fuel injection system of the vehicle, boosting its performance and fuel efficiency. By the late 1960s and early 1970s, embedded systems have come down in price and there has been a dramatic rise in processing power and functionality. Some of the important milestones are the release of the first commercial microcontroller in 1974 by Texas Instruments, the release

4 Introduction

of the wildly used x86 processor series by Intel in 1978, the release of the first embedded OS (VxWorks) by Wind River in 1987, followed by Microsoft's Windows Embedded CE in 1996. The embedded Linux system, which is used today in almost all the embedded devices, has appeared in the late 1990s.

Thanks to the continuous technological advancement in semiconductor device fabrication, both the size and the cost per unit of Systems-on-Chips (SoC) have been decreasing tremendously. Complementary Metal-Oxide-Semiconductor (CMOS) technology for example, has made possible to miniaturize transistors to the level where today mobile processors includes billions of transistors. As consequences, embedded systems have become more sophisticated. The best examples are smart devices, like smartphones, smartwatches, smart fitness bands, and smart credit cards. Furthermore, with the emerging technologies such as sensors, robotics, Internet of Things (IoT), Artificial Intelligence (AI), and 5G technology, the smart device concept has been enlarged to smart buildings, smart cities, smart grids, and smart factories. Today, cyber-physical systems are capable of cooperating and communicating with each other, even making decisions on their own. Without any doubt, embedded systems can be considered as the heart of the fourth industrial revolution.

### 1.1.2 Designing Embedded Systems

### **Embedded Systems Development Constraints**

Designing an embedded system is a hard task. Indeed, besides the complexity of the software and the hardware, many constraints must be satisfied which are often contradictory. These constraints are classified in [Des14] following three categories, application constraints, cost constraints and external constraints.

- Application constraints refer to the requirements that an embedded system must satisfy to serve its intended purpose. For example, many embedded systems have performance requirements and must react to external events within a limited amount of time, or must produce results at a fixed rate. Another example of an application constraint is the reliability of an embedded system that restricts the probability of a system failure, primarily for safety reasons. Size limitation and power consumption are also major requirements for handheld or autonomous embedded systems.

- Cost constraints refer to all factors influencing the total cost of an embedded system. These factors cover the engineering development cost, the production cost, the maintenance cost, and also include the recycling cost of an embedded system.

- External constraints refer to the requirements that an embedded system must satisfy but that are nonessential to its purpose. Regulations and standards are examples of external constraints that dictate certain characteristics of an embedded system, but non-compliance would not prevent an embedded system from serving its purpose. The environment in which an embedded system is used can also have an impact on its design. Extreme temperatures, high humidity, rapidly changing pressure are examples of external constraints.

All these constraints are often contradictory, even within a single category. For example, reducing the power consumption of an embedded system can be achieved by lowering its clock frequency, which in turn will decrease the performance of this system. Hence, the development of an embedded system often consists of satisfying the most important constraints, and finding an acceptable trade-off between remaining ones.

Contributions 5

### **Dataflow Programming**

Dataflow Model of Computation (MoC) have been introduced as a simple programming model which enables the developer to naturally express the parallelism of the software. A dataflow MoC consists on modeling the application with directed graph such that, each vertex is an independent computational module, and each edge represents an explicit communication channel between two vertices. Dataflow graphs have gained popularity due to their simplicity and their compatibility with legacy code. Indeed, dataflow graphs are used to specify networks of computational modules, but the specification of the internal behavior of these modules can be written in any programming language, including C code. Furthermore, the compatibility of dataflow MoC with legacy code enables the developers to reuse previously developed and optimized programs, which increase their productivity. Many dataflow MoC have been proposed in the literature since the introduction of the first one by Kahn in 1974 [Kah74]. Each new dataflow model extends the semantics and the expressivity of the previous one with a new properties. For example, the dynamic dataflow models extends the static ones with control task and data which enables the application to dynamically change its behavior.

### 1.2 Contributions

In this thesis, we study the development process of applications modeled with the Interface-Based SDF (IBSDF) model, in the context of rapid prototyping. The IBSDF MoC extends the well know Synchronous Dataflow (SDF) MoC with a hierarchy mechanism that enables the specification of the internal behavior of actors with a SDF subgraph instead of host code. The hierarchy mechanism of the IBSDF model is based on interfaces that insulate each subgraph from its upper graph in term of schedulability. Additionally to the interfaces, the IBSDF model defines execution rules to ease the analysis of the graph.

The IBSDF graph is often transformed to a non hierarchical graph during the development process of the application in order to verify and analyze its behavior. This transformation is called flattening the hierarchy. The flattening process often results in an exponential increase of the graph's size which makes the graph hard and even impossible to process with a reasonable time and memory. In fact, the flattening process has become the bottleneck of the development process of complex applications with the IBSDF model.

Our contributions aim to propose new techniques for the evaluation of some important metrics like the maximum throughput and the minimum latency. These metrics needs to be evaluated as early as possible by the developer. Indeed, very fast evaluation of this property is mandatory for real-time feedback to the developer during the application development, for the mapping and scheduling of the application on Multiprocessor Systemon-Chip (MPSoC), and for the MPSoC Design Space Exploration (DSE) i.e. the research of the best hardware for a specific application. The main contributions of this thesis are:

- 1. A new method named Schedule-Replace (SR) for the evaluation of the maximum throughput of an IBSDF graph when it is executed in the hierarchical execution mode.

- 2. A new method named Evaluate-Schedule-Replace (ESR) for the evaluation of the maximum throughput of an IBSDF graph when it is executed in the relaxed execution mode.

6 Introduction

3. A new method named Hierarchical-Symbolic-Execution (H-SE) for the evaluation of the minimum achievable latency of the IBSDF graph in the hierarchical execution modes.

4. A new method named Hierarchical-Critical-Path Method (H-CPM) for the evaluation of the minimum achievable latency of the IBSDF graph in the relaxed execution modes.

Until today, the maximum throughput and the minimum latency of an IBSDF graph were evaluated using a classical approach which consists of first flattening the hierarchy of the graphs and then evaluating its performance as if it was a large SDF graph. Since the flattening process results in an exponential growth of actors and edges number, the classical approach can be used only for small IBSDF graphs. For large IBSDF graphs, the classical method either fails to return a result or takes hours to evaluate the graphs. In contrast to the classical approach, the new techniques of this thesis are based on a modular approach which enables the evaluation of large IBSDF graphs without flattening their hierarchy. As consequences, the new techniques are capable of evaluating the maximum throughput and the minimum latency of large IBSDF graphs in few seconds, while the classical approach fails to return a result.

### 1.3 Outline

This thesis summarizes all the work done in this perspective plus our contributions, it is organized in six chapters as follows: The first chapter gives a short presentation of the scope of the thesis. Chapter 2 formally defines the concept of dataflow programming and gives an overview of the different categories of dataflow MoC. For each category, we present the semantics and characteristics of some of its dataflow models. Chapter 3 describes the development process of dataflow graphs in the context of rapid prototyping. Chapter 4 presents the new techniques for the throughput evaluation of the IBSDF model. Chapter 5 in turn, presents the new techniques for the latency evaluation of the IBSDF model. Finally, a summary conclusion of the work carried out, followed by a potential future research perspectives.

### **Dataflow Models of Computation**

### 2.1 Introduction

The complexity of Multiprocessor System-on-Chip (MPSoC) architectures is increasing exponentially to meet the rising computation power demand of signal processing applications. As consequences, programming modern MPSoC with the traditional thread-based programming languages have became more and more complex, due to the increasing number of Processing Elements (PEs) and their heterogeneity.

In this context, dataflow Models of Computation (MoC) is gaining popularity as the most suitable models for designing complex signal processing applications for MPSoC architectures. Dataflow MoC are diagram-based models, which consist on representing an application with a directed graph of tasks called actors. The edges of the graph represent the data exchange between the actors. This decomposition of the application into a set of interconnected actors offers the developer a natural way to express the parallelism and the data dependencies between the actors.

Furthermore, dataflow MoC can be used to specify a wide range of signal processing applications such as video decoding, telecommunication, and computer vision applications. The expressive power and the diversity of dataflow MoC; e.g. static, dynamic, hierarchical and parametric models; combined with powerful dataflow compilers gives the developer the best tools to easily design complex applications and fully exploit the computation power and the specifications of modern MPSoC architectures.

In this chapter, we give an overview of the different categories of dataflow MoC. We start by providing formal semantics for dataflow MoC by presenting the Kahn Process Network (KPN) and the Dataflow Process Network (DPN) models in section 2. In the same section, we show how the different types of parallelism are expressed in dataflow models. Then, we discuss the properties of the dataflow MoC which can be used to compare the different models and categories. In section 3, we present the static dataflow models which are the most studied and used in the industry. This category models applications in which data values have no impact on the system's behavior. Static dataflow models includes Synchronous Dataflow (SDF), Homogeneous SDF (HSDF), Single-Rate SDF (srSDF) and Cyclo-Static Dataflow (CSDF) models. In contrast, section 4 presents the dynamic dataflow MoC which are capable of adapting their behavior according to the data values. This category includes Boolean DataFlow (BDF) and Scenario-Aware

Dataflow (SADF) models. Next, we introduce the category of hierarchical dataflow MoC which extends the semantics of basic dataflow models with a hierarchy mechanism. Section 5 focuses on the static hierarchical models, the Hierarchical SDF (Hierarchical SDF) and the Interface-Based SDF (IBSDF) models. While section 6 focuses on the parametric hierarchical models, the Parameterized SDF (PSDF) and Parameterized and Interfaced SDF ( $\pi$ SDF) models. Finally, we give examples of real signal processing applications modeled with IBSDF graphs in section 7.

In this thesis, we are interested mainly in studying the behavior of the SDF model and its hierarchical extension, the IBSDF model.

### 2.2 Dataflow Programming

### 2.2.1 Semantics

Dataflow Programming is widely used for specifying the functionality of embedded systems. The first model to be introduced in the the context of parallel computation was the Computation graphs developed by Karp and Miller in the 60's [KM66]. In 1974, Kahn introduced the Kahn Process Network (KPN) [Kah74] as a parallel programming model that is Turing complete, meaning that the model can perform any computation described by an algorithm. Formally, the KPN MoC decomposes an application into tasks interconnected by directed First-In First-Out (FIFO) queues, forming a network of concurrent tasks. Each FIFO queue has an infinite memory and connects only one task to another, creating a data-dependency between the two tasks. Each task consumes (resp. produces) a number of data-tokens on its input FIFO queues (resp. output FIFO queues) at each execution. In 1995, Lee and Parks introduce the Dataflow Process Network (DPN) MoC [LP95] as a specialization of the KPN model. Formally, a DPN is a directed graph denoted  $G = \langle A, F \rangle$ , such that:

- A is the set of vertices of G. Each vertex  $a \in A$  represents an indivisible computational task, also called an actor. Each actor  $a \in A$  is defined as a tuple  $\mathbf{a} = \langle \mathbf{P}_{data}^{in}, \mathbf{P}_{data}^{out}, \mathbf{R}, \mathbf{rate} \rangle$  where:

- $\mathbf{P}_{data}^{in}$  and  $\mathbf{P}_{data}^{out}$  respectively refer to the set of data input and output ports of the actor.

- $-\mathbf{R} = \{R_1, R_2, ..., R_n\}$  is the set of firing rules of the actor. A firing rule  $R_i \in R$  is a condition that, when satisfied, can start an execution, called firing, of the associated actor.

- $\mathbf{rate}: (R, P_{data}^{in} \cup P_{data}^{out}) \to \mathbb{N}$  associates a firing rule to the number of atomic data objects, called *data tokens*, consumed or produced on a given data port, for a firing of the actor resulting from the validation of this firing rule.

- F is the set of edges of G. Each edge  $e \in F$  represents an unbounded FIFO queue used to connect and transmit data tokens from an actor to another. Each FIFO queue  $f \in F$  is defined as a tuple  $\mathbf{f} = \langle \mathbf{prod}, \mathbf{cons}, \mathbf{src}, \mathbf{snk}, \mathbf{delay} \rangle$  where:

- **prod** : F → A and **cons** : F → A associate producer and consumer actors to a Fifo.

- $\mathbf{src}: F \to P_{data}^{out}$  and  $\mathbf{snk}: F \to P_{data}^{in}$  associate source and sink ports to a Figo.

- **delay** :  $F \to \mathbb{N}$  corresponds to a number of data tokens present in the FIFO when the described application is initialized.

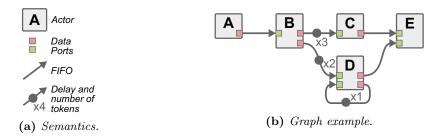

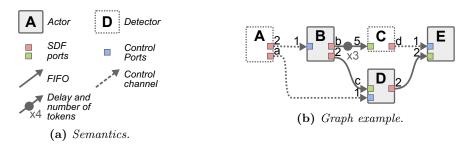

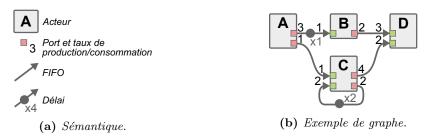

Figure 2.1 – Dataflow Process Network (DPN) MoC.

Figure 2.1 illustrates the graphical elements associated to the semantics of the DPN MoC and gives an example of a DPN graph. The example graph presented in Figure 2.1b contains 5 actors interconnected by a network of 6 Fifos. The Fifos linking actors B to C, actors B to D, and actor D to itself contain 3, 2, and 1 initial tokens respectively.

### 2.2.2 Expression of parallelism

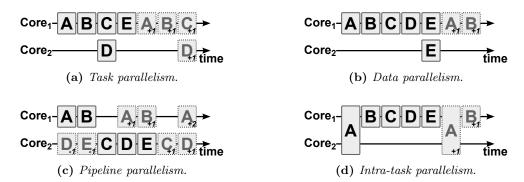

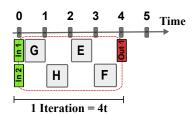

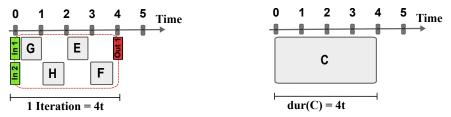

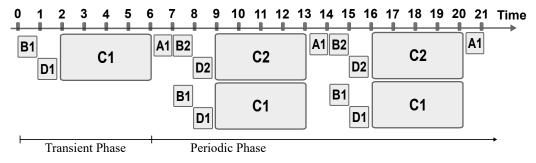

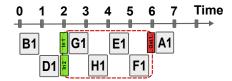

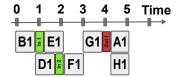

Dataflow MoCs support four types of parallelism [ZDP<sup>+</sup>13], which are illustrated in figure 2.2 and defined as follows:

- Task parallelism: is when data-independent actors are executed in parallel. Two actors are called data-independent if there is no path in the graph between the two of them. For instance, figure 2.2a shows a parallel execution of actors C and D which are two data-independent actors in the DPN graph of figure 2.1b.

- Data parallelism: is when there is enough data tokens to execute the same actor many times simultaneously. Figure 2.2b shows an example of a case where actor E has enough data tokens to be executed twice simultaneously.

- **Pipeline parallelism:** is when several executions of the same dataflow graph overlap when it is possible. For example, in figure 2.2c, the next execution of the graph (actors with dotted borders and +1) starts before the end of the current execution. Similarly, the current graph execution overlaps the previous one (actors with -1).

- Intra-task parallelism: in the DPN model, the internal behavior of actors is described by a source code which can be sequential or parallel. For example, if the source code is written in a thread-based programming language then the actor may have an inner parallelism which enables its execution on several PE simultaneously. Figure 2.2d shows an example of Intra-task parallelism where actor A is a parallel actor executed on two PEs simultaneously.

Figure 2.2 – Illustration of the four types of parallelism in dataflow MoC.

### 2.3 Static Dataflow Models of Computation

Static dataflow models are the most studied category of dataflow-based MoC. Their popularity is due to their decidability property which enables the use of compile-time analysis to verify and evaluate key properties of signal processing applications. Indeed, static dataflow models are non-reconfigurable and deterministic, meaning that the production and consumption rates of each actor are known at design time and remain static at run-time [LP95]. However, static dataflow models do not express conditional states, data dependent iterations or recursion. For instance, the if-then-else statement has no equivalent in static dataflow models. Therefore, static dataflow MoC are not Turing complete models.

In the following, we present the semantics and characteristics of some of the most used static dataflow models in the industry.

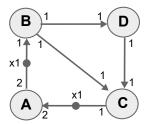

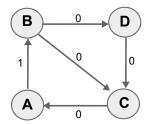

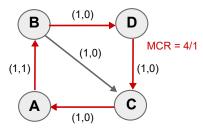

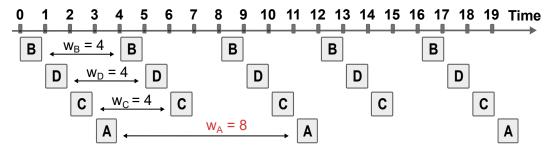

### 2.3.1 Synchronous Dataflow (SDF) model

The SDF MoC is the simplest and the most commonly used static dataflow model. The SDF model was introduced in 1987 by Lee and Messerschmitt [LM87b]. Like, the DPN model, a SDF graph  $G = \langle A, F \rangle$  decomposes an application into a set of actors A interconnected by a set of Fifo queue F to exchange data tokens. Each actor consumes (resp. produces) a fixed number of data-tokens from (resp. into) all its input Fifo (resp. output Fifo) at each execution. Thus, in contrast to the DPN model, each SDF actor has only one firing rule.

Formally, a Synchronous Dataflow (SDF) graph is a graph  $G = \langle A, F \rangle$  respecting the Dataflow Process Network (DPN) MoC with the following restrictions:

- Each actor  $a \in A$ , with  $a = \langle P_{data}^{in}, P_{data}^{out}, R, rate \rangle$ , is associated to a unique firing rule:  $R = \{R_1\}$

- For each data input port  $p \in P_{data}^{in}$  of an actor, the consumption rate associated to the unique firing rule  $R_1$  of the actor is a static scalar that also gives the number of data tokens that must be available in the FIFO to start the execution of the actor.

- For each data output port  $p \in P_{data}^{out}$  of an actor, the production rate associated to the unique firing rule  $R_1$  of the actor is a static scalar.

In addition to these restrictions, the following simplified notation is introduced.

• rate :  $A \times F \to \mathbb{N}$  is the production or consumption rate of actor  $a \in A$  on Fifo  $f \in F$ . If a is both producer and consumer of f, then rate(a, f) is the difference between the production and the consumption rates on f.

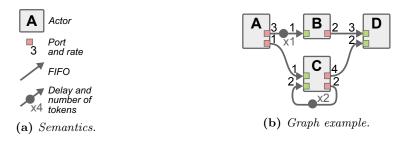

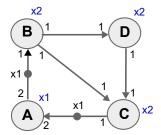

Figure 2.3 illustrates the graphical elements associated to the semantics of the SDF MoC and gives an example of SDF graph.

Figure 2.3 – Synchronous Dataflow (SDF) MoC.

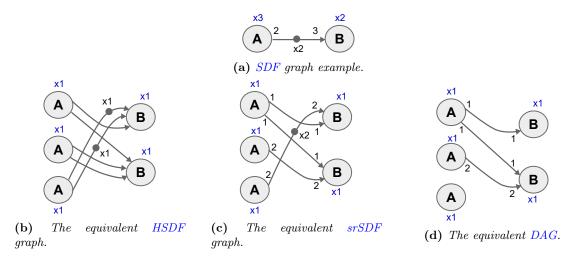

Figure 2.4 – Specializations of the Synchronous Dataflow (SDF) model.

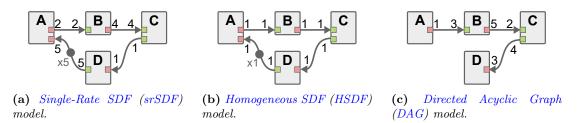

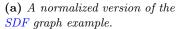

# 2.3.2 Homogeneous SDF (HSDF), Single-Rate SDF (srSDF), and Directed Acyclic Graph (DAG) models

The HSDF, srSDF, and Directed Acyclic Graph (DAG) models are a specialization of the SDF MoC. Each model respects the semantics of the SDF MoC with some restrictions. In fact, each of the HSDF and the srSDF models add restrictions on the consumption and production rates of the SDF actors. The DAG model on the other hand, adds a restriction on the structure of the SDF graph. These models are illustrated in figure 2.4 and defined as follows:

- srSDF model: is a SDF graph such that for each FIFO queue, the production rate of its source actor is equal to the consumption rate of its target actor.

- HSDF model: is a SDF graph such that the consumption and production rates of the actors are all equal to 1. The HSDF model can also be seen as a specialization of the srSDF graph.

- DAG model: is a SDF graph which does not contain any cycle. The DAG model can also be as HSDF graph or a srSDF graph with no cycle.

The restrictions of the HSDF graph makes it is easy to analyze than other static dataflow graph. In fact, as we will see in the next chapter, several static dataflow models are converted to the HSDF and DAG models to be able to evaluate and analyze their performance accurately.

### 2.3.3 Cyclo-Static DataFlow (CSDF) model

The Cyclo-Static Dataflow (CSDF) model [BELP95] is an extension of the SDF model with consumption and production of actors decomposed into phases executed cyclically. Each actor has a fixed number of phases and each phase produces or consumes a specific number of data tokens.

Formally, a Cyclo-Static Dataflow (CSDF) graph is a graph  $G = \langle A, F \rangle$  respecting the Synchronous Dataflow (SDF) MoC with the following additions:

- Each port  $p \in P_{data}^{in} \cup P_{data}^{out}$ , is associated to a sequence of static integers of size n noted  $seq(p) \in \mathbb{N}^n$ .

- Considering an actor  $a \in A$  and a port  $p \in P_{data}^{in} \cup P_{data}^{out}$ , the firing rule (i.e. the number of available tokens) and the production/consumption rates of p for the  $i^{th}$  firing of actor a is given by the  $(i \mod n + 1)^{th}$  element of seq(p).

Figure 2.5 illustrates the graphical elements associated to the semantics of the CSDF MoC and gives an example of CSDF graph.

Figure 2.5 – Cyclo-Static Dataflow (CSDF) MoC.

### 2.4 Dynamic Dataflow Models

Static dataflow models like SDF and CSDF MoC are totally predictable and offer a great analyzability of their behavior at design time. However, they remain limited in terms of expressivity and thus cannot be used to model all applications.

In this context, many generalizations of the SDF MoC have been proposed over the years, which allow modeling dynamic and re-configurable applications. The main purpose of these new models is to preserve as much predictability and analyzability as possible while improving the expressivity of static dataflow MoC.

The Scenario-Aware Dataflow (SADF) and the Boolean DataFlow (BDF) models are two of the dynamic dataflow MoC which extend the semantics of static dataflow models by adding a control mechanism. By a *control-channel* or a control-actor, each of SADF and BDF models are capable of re-configuring and adapting the behavior of actors according to the data values. In the following, we present the semantics of each one of them.

### 2.4.1 Scenario Aware Dataflow (SADF)

The Scenario-Aware Dataflow (SADF) MoC [TGB<sup>+</sup>06] is a reconfigurable generalization of the SDF MoC, which is designed to enforce the *analyzability* of applications.

The SADF model extends the semantics of the SDF model with the concept of scenarios and by introducing a new type of actors and FIFO queues called respectively *detectors* and *control channels*. The detectors are special actors that control the behavior of other actors with the so-called *control tokens*. The control channels are used to transmit the control tokens from a detector to another actor. In the SADF model, each actor has a set of execution *scenarios* which define its behavior. Controlling an actor consists of choosing which execution scenario will be activated.

Formally, a Scenario-Aware Dataflow (SADF) graph  $G = \langle A, F \rangle$  is a graph respecting the semantics of the SDF MoC with the following additions:

- Actors  $a \in A$  are associated with a non-empty finite set of **scenarios**  $S_a$ . For each actor, a unique scenario  $s \in S_a$  is active for each firing. The active scenario determines the production and consumption rates on the ports of the actor as well as the **execution time** t of the actor.

- Actors  $a \in A$  are associated with a possibly empty set of **control input ports**. Before firing an actor, a single **control token** is consumed from each control input port. The consumed control tokens are used to determine the scenario of the actor for the next firing.

- $\mathbf{D} \subset A$  is the detectors set. Each detector  $d \in D$  is associated with a Markov chain. The *scenario* of a detector changes depending on the current state of the Markov

Figure 2.6 – Scenario-Aware Dataflow (SADF) MoC.

chain. Detectors are the only actors that can write *control tokens* on an output port. The value and the number of *control tokens* produced by a detector solely depend on the current state of its Markov chain.

•  $\mathbf{C} \in F$  is the **control channels** set. A control channel  $c \in C$  is used to transmit control tokens from a detector to another actor or detector of the graph.

Figure 2.9 presents the graphical elements associated to the semantics of the SADF MoC and an example of SADF graph. The SADF graph of Figure 2.6b contains 2 detectors (A and C), and 3 regular actors (B, D, and E). In this graph, production and consumption rates written with numbers are statically fixed rates whereas rates written with letters depend on the scenario of their actor. Based on the definition of the SADF model given above, the consumption rate of all control ports is statically set to 1.

The stochastic process used in SADF to determine the production and consumption rates and the execution time of actors has been shown to give a great analyzability to the MoC. Indeed, beside proving the consistency or the schedulability of a SADF graph [TGB+06], methods exist to derive useful metrics for real-time applications such as the worst-case latency, or the long-time average throughput of an application modeled with a SADF graph [SGTB11].

Although Markov chain of SADF lends a great analyzability to the MoC, this stochastic process is not practical for describing the functional behavior of applications. For this reason, an executable Finite-State Machine (FSM)-based SADF MoC is introduced in [SGTB11]. In the FSM-based SADF MoC, the Markov chains associated to the detectors of the MoC are replaced with deterministic FSM.

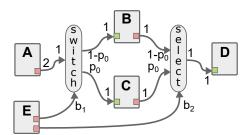

### 2.4.2 Boolean Dataflow (BDF)

The BDF MoC [BL93] extends the semantics of the SDF MoC by introducing a new type of actors called switch and select. The BDF MoC uses the switch and select actors respectively as a demultiplexers and multiplexers to model conditional statements like the if-then-else patterns. Depending on the data values, the switch and select actors will forward the data tokens to different FIFO. Based on the result of a boolean value, the switch actor either forwards its input tokens to its first output port or its second output port, and thus acting like a demultiplexer logic cell. The select actor in turn, behaves as a multiplexer. The boolean value selects the input port whose tokens are then sent to the unique output port. Thus, the BDF model adds a control flow to the SDF MoC and makes the model Turing complete [BL93].

Figure 2.7 shows an example of a BDF graph which contains one switch and one select actors. In this BDF graph example, the switch actor (resp. select actor) will forward data

Figure 2.7 – A Boolean DataFlow (BDF) graph example.

tokens to one (resp. from one) of the actors B and C depending one the boolean data value sent by actor E.

### 2.5 Hierarchical Static Dataflow Models

With the increasing complexity of signal processing applications, the average number of actors of dataflow graphs has become very large. As consequences, designing and analyzing complex applications have become a difficult task for the designers, as well as for the development tools. In this context, new dataflow models with a modularity property have been proposed to ease the development of complex signal processing applications. The concept of modularity in dataflow modeling is based on decomposing the application into modules such that each module is a group of tasks. The module itself can be decomposed into sub-modules and thus creating a hierarchy of modules.

In this section we present two hierarchical dataflow MoC that extend the semantics of the SDF MoC with a hierarchy mechanism.

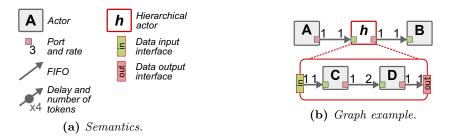

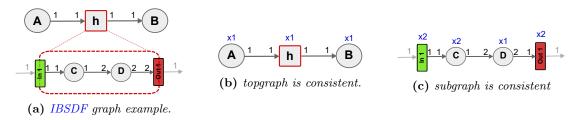

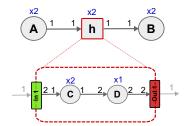

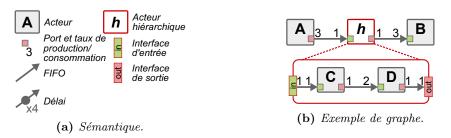

### 2.5.1 Hierarchical SDF

The Hierarchical SDF model [PL95] is the first hierarchical extension of the SDF MoC, which consists on associating an SDF graph to an actor as the description of its internal behavior. The associated actor is called a *hierarchical actor* which is described by an SDF subgraph. Similarly, an actor from the SDF subgraph can be associated in turn to another SDF subgraph. Thus, a Hierarchical SDF graph with multiple levels of hierarchy can be constructed. Figure 2.8 shows an example of a Hierarchical SDF graph composed of two hierarchical levels. The topgraph is composed of two regular actors A and B, and a hierarchical actor h. The hierarchical actor h is described by a SDF subgraph which is composed of two actors C and D.

The hierarchy mechanism of the Hierarchical SDF model is mainly used to ease the design phase of complex signal processing applications. In fact, during the actual execution of the application, each hierarchical actor is replaced by its subgraph which contains the actual actors to execute.

Figure 2.8 – Hierarchical SDF graph

Therefore, the Hierarchical SDF model is considered not compositional since all the actors are still data dependent even if they are organized into modules. Indeed, no subgraph in the Hierarchical SDF graph can be executed or analyzed independently from the whole graph.

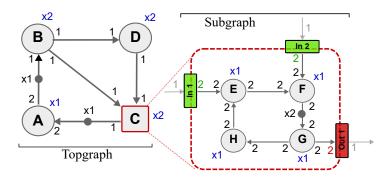

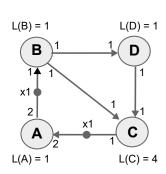

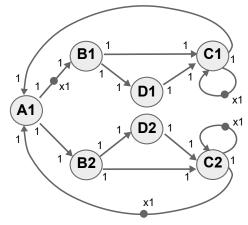

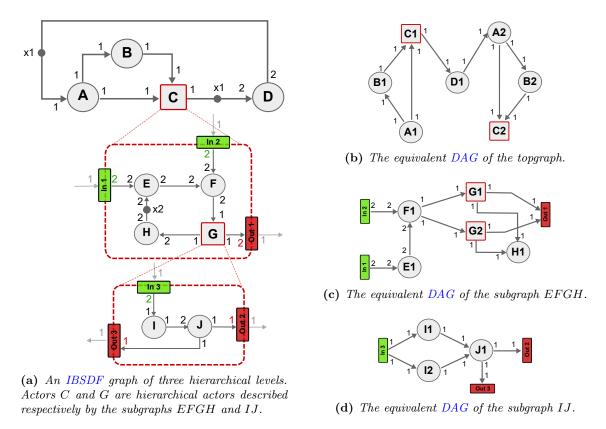

### 2.5.2 Interface-based SDF (IBSDF)

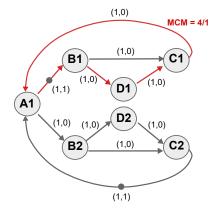

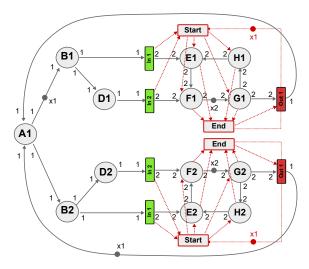

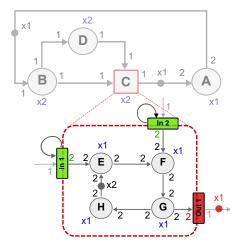

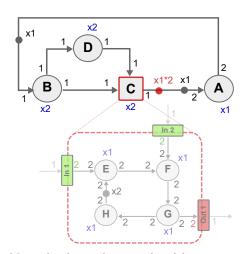

Like the Hierarchical SDF model, the Interface-Based SDF (IBSDF) MoC [PBR09] offers the choice of specifying the internal behavior of actors with a host code, or with a dataflow subgraph. In contrast to the Hierarchical SDF model, the hierarchy of the IBSDF model is based on hierarchical interfaces. Practically, for each input FIFO queue of a hierarchical actor, an associated data input interface is added to the subgraph. Similarly, for each output FIFO queue of a hierarchical actor, an associated data output interface is added to the subgraph. Figure 2.9b shows the same Hierarchical SDF graph example of figure 2.8 modeled as an IBSDF graph where data interfaces are added to the subgraph. Figure 2.9a shows the graphical elements associated to the semantics of the IBSDF model.

Figure 2.9 – Interface-Based SDF (IBSDF) MoC.

The main role of the data interfaces in an IBSDF graph is to transfer data tokens from the hierarchical actor to the subgraph and vice versa. Precisely, when the hierarchical actor is ready to execute, the data input interfaces transfer the data tokens consumed by the hierarchical actor from its input FIFO queues to its subgraph. Similarly, when the subgraph finishes processing all the data tokens received from its hierarchical actor, the data output interfaces transfer then the data tokens produced by the subgraph to its hierarchical actor. Once, the hierarchical actor receives data tokens from its subgraph, it produces them on its output FIFO queues in the topgraph, behaving like a regular actor.

Additionally, each of the data input and the data output interfaces has a special behavior which guarantees the compositionality of the IBSDF model:

- The input interfaces behave as circular buffers and reproduce the same data-tokens received from their hierarchical parent actor, as much as the subgraph needs to finish its execution

- The output interfaces receiving more data tokens than necessary from the subgraph will only transmit the number of data tokens defined by the hierarchical parent actor.

Thus, the hierarchical actor can behave exactly as a regular actor from the topgraph perspective. Indeed, the special behavior of the data interfaces guarantees that once a subgraph starts to execute, it will finishes and transfer data tokens to its hierarchical parent actor without requesting new data tokens from the topgraph. Hence, each subgraph in the IBSDF graph is data independent.

Therefore, unlike the naive hierarchy of the Hierarchical SDF model, the interface-based hierarchy of the IBSDF model introduces a compositionality that enables designing and analyzing each subgraph independently from the other subgraphs.

### 2.6 Hierarchical Parametric Dataflow Models

Like the dynamic dataflow models, the hierarchical parametric dataflow models add a dynamic property for the static hierarchical dataflow MoC. In this section we present two models, the PSDF MoC and the  $\pi$ SDF MoC which extends the semantics of the IBSDF MoC with the possibility to parameterize some attributes.

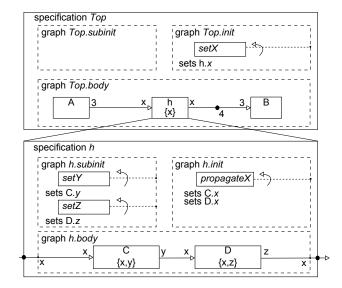

### 2.6.1 Parameterized SDF (PSDF)

In dataflow modeling, a meta-model is a model of model which consists on extending the semantic of an existing dataflow model with new elements that will enable new capabilities. The *Parameterized dataflow* for instance, is a meta-modeling framework introduced by Bhattacharya and Bhattacharyya in [BB01], which can be applied to many static dataflow models like the SDF and the CSDF models [BB01, DP18]. The *Parameterized dataflow* meta-model extends the semantics of the targeted MoC by adding dynamically reconfigurable hierarchical actors. Formally, the *Parameterized dataflow* meta-model extends the semantics of a targeted dataflow MoC with the following elements:

- param(a) is a set of parameters associated to an actor  $a \in A$ . A parameter  $p \in param(a)$  is an integer value that can be used as a production or consumption rate for actor a, and that can influence the internal behavior of actor a. The value of parameters is not defined at compile time but instead is assigned at run time by another actor. Optionally, a parameter can be restricted to take values only in a finite domain noted domain(p).

- Hierarchy levels, including subgraphs of hierarchical actors, are specified with 3 subgraphs, namely the init  $\phi_i$ , the subinit  $\phi_s$ , and the body  $\phi_b$  subgraphs.

- the  $\phi_i$  subgraph sets parameter values that can influence both the production and consumption rates on the ports of the hierarchical actor and the topology of the  $\phi_s$  and  $\phi_b$  subgraphs. The  $\phi_i$  subgraph is executed only once per iteration of the graph to which its hierarchical actor belongs and can neither produce nor consume data tokens.

- the  $\phi_s$  subgraph sets the remaining parameter values required to completely configure the topology of the  $\phi_b$  subgraph. The  $\phi_s$  subgraph is executed at the beginning of each firing of the hierarchical actor. It can consume data tokens on input ports of the hierarchical actor but can not produce data tokens.

- the  $\phi_b$  subgraph is executed when its configuration is complete, right after the completion of  $\phi_s$ . The body subgraph behaves as any graph implemented with the MoC to which the parameterized dataflow meta-model was applied.

Figure 2.10 shows an example of the PSDF model which is the resulting MoC when applying the *Parameterized dataflow* meta-model to the SDF MoC. The graphical semantics used in this figure are those proposed in [BB01]. In this example, the *top level* specification contains 4 actors. The setX actor, contained in the Top.init subgraph, assigns a value to parameter x, thus influencing the dataflow behavior of actor h in the Top.body subgraph.

Figure 2.10 – Example of Parameterized SDF (PSDF) graph

Actor h is a hierarchical actor whose subgraphs contain 5 actors. A parameter set in a level of hierarchy cannot influence directly parameters in body subgraphs of lower levels of hierarchy. For example, the value assigned to parameter x in the Top.init subgraph must be explicitly propagated by actor propagateX in subgraph h.init in order to be used in the body subgraph of actor h.

The execution of a PSDF graph follows the runtime operational semantics of the Parameterized dataflow meta-model defined by Bhattacharya and Bhattacharya in [BB01]. The runtime operational semantics successive steps followed during the execution of a hierarchical actor whose internal behavior is specified with the three subgraphs,  $\phi_i$ ,  $\phi_s$ , and  $\phi_b$  subgraphs. A detailed description of this runtime operational semantics of the Parameterized dataflow meta-model can be found in [BB01]. Shortly, the execution of a PSDF graph starts by propagating the new values of the dynamic parameters through the hierarchy in order to set the consumption and production rates of the actors. The propagation of the parameters value is done by executing the init subgraph  $\phi_i$  and the subinit subgraph  $\phi_s$  of the hierarchical actors. Once the behavior of a hierarchical actor is defined, its body subgraph  $\phi_b$  is executed.

As an example, the PSDF graph of figure 2.10 starts its execution by initializing and propagating the value of the parameter x of the hierarchical actor h through the hierarchy. First the actor setX of the init subgraph Top.init of the topgraph is executed to initialize the parameter x, then the actor propagateX of the init subgraph h.init of the hierarchical actor is executed to propagate the value of x. After that, the body subgraph top.body of the topgraph is executed. At each execution of the hierarchical actor h, the value of the parameters x and y of its subgraph are first initialized by executing the h.subinit subgraph. Once the consumption and production rates of the subactors C and D are defined, the body subgraph h.body of the hierarchical actor h is then executed. If we assume that the parameters x, y, and z are always set to 1 then we obtain the following execution:  $setX, propagateX, A, 3 \times (setY, setZ, C, D), B$  where the notation  $3 \times ()$  means that the content of the parenthesis is executed 3 times.

Although the *Parameterized dataflow* meta-model enables a dynamic hierarchy property, it makes the PSDF MoC less predictable than the original SDF MoC. Indeed, contrary

to the SDF model, the consumption and production rates of the PSDF actors are unknown at design time, as they depend on dynamically set parameter values.

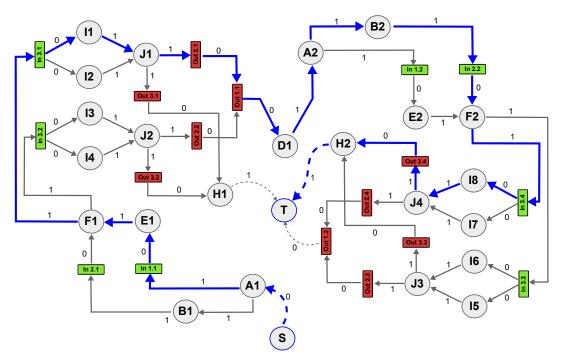

### 2.6.2 Parameterized and interfaced SDF ( $\pi$ SDF)

Similarly to the *Parameterized dataflow* meta-model, the Parameterized and Interfaced dataflow Meta-Model (PiMM) [DPN<sup>+</sup>13] extends the semantics of existing dataflow models with a parameterized hierarchy feature. However, the PiMM meta-model inherits its hierarchy semantics from the IBSDF model [PBR09] which is based on hierarchical interfaces.

The  $\pi SDF$  MoC for instance, is the semantic extension of the SDF MoC using the PiMM meta-model. Hence, the  $\pi SDF$  model extends the SDF model with a hierarchy mechanism which is based on interfaces like the IBSDF model, such that the consumption and production rates as well as the initial data tokens of the FIFO queues are dynamically set like the PSDF model.

Based on the definition given in [Heu15], the  $\pi SDF$  model extends the semantics of the SDF model with the following elements:

- I is a set of hierarchical interfaces. An interface is a vertex of the graph that passes data tokens or parameter values between levels of hierarchy.

- P is a set of parameters. A parameter is a vertex of the graph and is used to configure the application and to modify its behavior.

- D is a set of parameter dependencies. A parameter dependency is a directed edge of the graph that propagates parameter configurations to other elements of the graph.

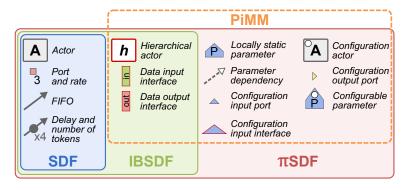

In [Des14], Desnos compares the semantics of the  $\pi SDF$  model with the semantics of each of the SDF and the IBSDF models. Figure 2.11, taken from [Des14], summarizes this comparison and shows the graphical elements associated to the semantics of each model.

Figure 2.11 – *PiMM semantics* [Des14]

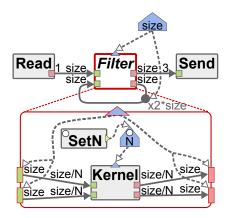

Multiple examples of real applications modeled with  $\pi SDF$  graph can be found in [Des14, Has18]. Figure 2.12 shows an example of a  $\pi SDF$  graph implementing an image filtering application. In this application, the *Read* and *Send* actor are respectively used for reading 1 pixel and sending a package of 3 pixels in a network. The purpose of the hierarchical actor *Filter* is to apply a filter on a 2D image for which the size is fixed by the parameter size. At each execution of the subgraph, actor SetN triggers a reconfiguration of the consumption and production rates of actor Kernel by assigning a new value to the parameter N. Reconfigurations enable a dynamic variation of the number of parallel execution of the Kernel actor.

Conclusion 19

Figure 2.12 – An example of the  $\pi SDF$  model of a image filter application [Des14]

Compared to the *Parameterized dataflow* meta-model, the PiMM meta-model enables modeling complex applications with a concise model where parameters value is set via the configuration actors and propagated automatically using the configuration channels. In terms of the behavior analysis, the  $\pi SDF$  model is more predictable than the PSDF model thanks to its interface-based hierarchy inherited from the IBSDF MoC.

### 2.7 Conclusion

In this chapter we have presented several dataflow models. The static dataflow models like the SDF model are fully predictable which enables precise analysis. However, static dataflow models are semantically limited compared to dynamic dataflow models which extend the expressivity of existing model with dynamic parameters. Dynamic dataflow models like the SADF and the BDF models enable the application to adapt its behavior to the data values.

With the increasing complexity of signal processing applications, designing and analyzing large dataflow graphs became a hard tasks for the designer as well for the development tools. In this context, the hierarchical dataflow models have been introduced to add a compositionality to the existing dataflow models. Among the two presented hierarchical dataflow models, the IBSDF model combines the statics behavior of the SDF model and the compositionality of a hierarchical dataflow model. In fact, the IBSDF model enables the decomposition of the application into several modules organized in an interface-based hierarchy such that the behavior of each module can be specified and analyzed separately from the graph.

The parametric dataflow model extends the hierarchical dataflow models with dynamic parameters. The  $\pi SDF$  model for example extends the SDF MoC with a parametrized hierarchy mechanism. Thus the  $\pi SDF$  benefits from the modularity advantages of the interface-based hierarchy and from the dynamic adaptation of actors behavior through parameters.

In this thesis we are interested specially on the IBSDF model which we consider to be the most suitable model for the development of complex signal processing application in the context of rapid prototyping.

# CHAPTER 3

### Development Process of Dataflow Graphs

### 3.1 Introduction

In this chapter we present the different phases of the development process of dataflow-based applications in the context of rapid prototyping. We first start by defining what is rapid prototyping and what is the motivation behind it. Next, we present Parallel and Real-time Embedded Executives Scheduling Method (PREESM), a rapid prototyping framework. PREESM framework offers a simple user interface to easily develop, analyze and compile dataflow graphs while all the complexity of the process is abstracted in a simple workflow. In fact all the contributions of this thesis are integrated to PREESM as a performance analysis module.

After briefly presenting the compilation process of dataflow graphs, we detail some of the important phases like the verification, the transformation, the analysis, the mapping and scheduling phases. In section 3, we discuss the consistency property of static dataflow graphs and how to evaluate it for each of the SDF, the Hierarchical SDF, and the IBSDF graphs. In section 4, we define how to convert an SDF graph into each of an equivalent HSDF graph, an equivalent srSDF, and an equivalent DAG. In the same section we present how to flatten the hierarchy of an IBSDF graph into each of an equivalent flat srSDF graph and an equivalent flat DAG. These dataflow graph transformations are used during the compilation process in order to ease the analysis or to expose all the parallelism of the application. In section 5, we discuss the liveness property of dataflow graphs which is an important property to check for the validation of the design phase. Section 6 defines the different type of schedules used for the simulation of dataflow graphs executions. Two type of schedules are presented in this section, the As Soon As Possible (ASAP) schedule and the periodic schedule. In section 7, we discuss the mapping and scheduling phase, which is the most critical phase in the development process of signal processing applications. Section 8 presents Synchronous Parameterized Interfaced Dataflow Embedded Runtime (SPIDER), a run-time manager for parametric dataflow graphs like the  $\pi SDF$  graph. Lastly, we present in section 9 some of the tools used in this thesis for the numerical experiments and the benchmarks. Section 10 concludes this chapter.

### 3.2 Rapid Prototyping

As presented by Cooling and Hughes in [CH89], rapid prototyping in computer science relies on two pillars: models to describe the behavior and the requirements of systems, and automatic methods and tools to quickly generate system simulations or system prototypes from the system models.

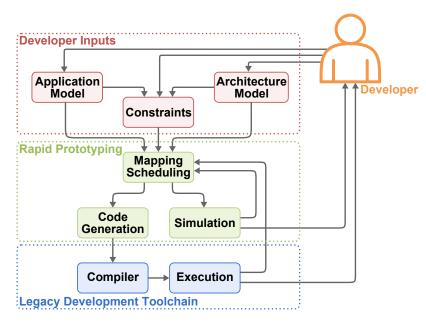

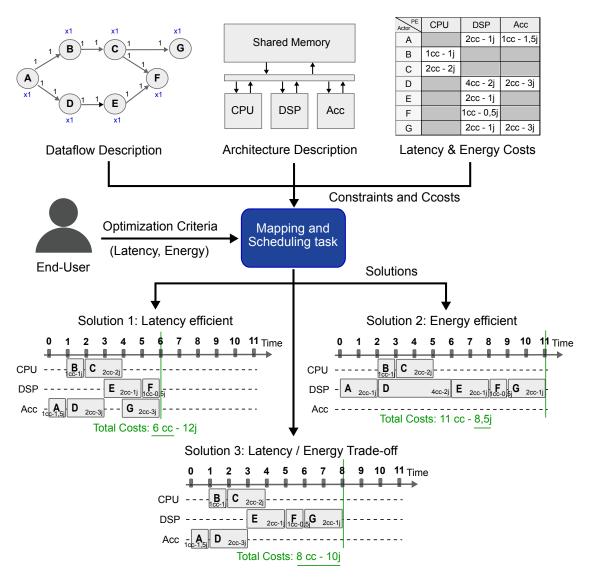

Figure 3.1, presents an overview of a typical rapid prototyping design flow. This design flow can be separated in 3 parts:

- **Developer Inputs**: Developer inputs consist of high-level models that enable the specification of all important properties of a system. In the co-design context, where designed systems have both hardware and software parts, developer inputs often gather a model of the application, a model of the targeted architecture, and a set of constraints for the deployment of the application on the architecture. As presented in the Algorithm-Architecture Adequation (AAA) methodology [GS03], the separation between the three inputs of the design flow ensures the independence between them, which eases the deployment of an application on several architectures or the use of a single architecture to deploy several applications.

- Rapid Prototyping: The rapid prototyping part of the design flow regroups the tasks that are executed to automatically explore the design space and to generate a prototype of the system described in the developer inputs. An important characteristic of these tasks is the rapidity with which they can be executed, even for complex applications and architectures. Contrary to a classic design flow, the purpose of a rapid prototyping design flow is not to generate an optimal solution, but to rapidly assess the feasibility of a system by generating a functional prototype that respects the specified constraints. Ideally, the obtained prototype will be refined and optimized in later stages of development.

- Legacy Development Toolchain: Optionally, the prototype generated by the design flow may be executed on a real target. In such a case, the generation of the

Figure 3.1 – Overview of a rapid prototyping design flow. (source [Des14]).

executable is supported by legacy development toolchains associated to the target. During the execution of the generated prototype, monitoring is generally used to record and characterize the system behavior in order to provide feedback to the rapid prototyping design flow and to the developer.

As illustrated in Figure 3.1, the rapid prototyping design flow is an iterative process that can use feedback from the simulation and the execution of the generated prototype to improve its quality. More importantly, the simulation or the execution of the generated prototype gives valuable information to the developer to guide the evolution of the design flow inputs. For example, this feedback can reveal resource deficiency of the architecture model or the presence of contradictory constraints.

### 3.2.1 Preesm Rapid Prototyping Framework

The Parallel and Real-time Embedded Executives Scheduling Method (PREESM) is an Eclipse-based framework that provides dataflow-based methods to study and program embedded multicore platforms [PDH<sup>+</sup>14]. PREESM is an open-source framework developed by VAADER team of the IETR Lab at INSA Rennes. Many tutorials can be found on the Preesm website https://preesm.org for the easy initiation of C/C++ programmers to multi-core programming.

The PREESM framework focuses on providing high level rapid prototyping information on algorithm parallelism and latency. It also proposes detailed analyses on system memory requirements. Moreover, a platform adaptable C/C++ code generation is provided to transform the dataflow representation into a runnable code.

This framework is based on the  $\pi SDF$  MoC. This dataflow model describes the input algorithm and actor code is not required by the framework for simulation purpose. The executable program resulting from jointly compiling the generated and the manual code and constitutes a multicore system prototype that is guaranteed to be deadlock-free and can be retargeted to a different number of cores within minutes.

However, since this framework is a compile-time analysis tool, all code generation of this framework is restricted to static  $\pi SDF$  graphs. A static  $\pi SDF$  graph only embeds parameter values that are fixed and known at compile time.

### 3.2.2 Preesm Typical workflow

A typical Preesm development workflow for an IBSDF graph consists of 6 main phases:

- 1. **Design phase**: The designer models the application with an IBSDF graph using the user interface of Preesm.

- 2. **Verification phase**: Verification of some necessary properties like the consistency and liveness.

- 3. Conversion phase: Flattening the hierarchy of the graph.

- 4. **Analysis phase**: Evaluate the performance of the graph.

- 5. Mapping and scheduling phase: Decides which actor to execute on which PE.

- 6. **Code generation**: Generates the actual source-code of the application which will be running on the targeted machine.

In the following, we present in detail some the important phases of the development process of dataflow graphs. We also simplifies the visual elements of the SDF and the IBSDF models, by ignoring the actor ports, and by representing the regular actors with circles and the hierarchical actors with squares.

### 3.3 Consistency Evaluation and Repetition Vector (RV)

Before analyzing the performance of a dataflow graph, a primarily step of the compilation consists on checking the deadlock freeness of the application; i.e. checking the consistency and the liveness of the graph. A dataflow graph is said to be consistent when its execution does not result in an accumulation of unconsumed data tokens. Meaning that a consistent graph can be executed indefinitely on MPSoC architectures with a sufficient bounded memory storage.

### 3.3.1 Consistency of a SDF graph

The consistency of a SDF graph  $G = \langle A, F \rangle$  is checked by solving a system of linear equations defined by the matrix equation  $\Gamma(G) * RV = 0$ . The topology matrix  $\Gamma(G)$  [LM87b], a |F|-by-|A| matrix, represents the consumption and production rates of the actors on the Fifo queues. Each column of the topology matrix  $\Gamma(G)$  is associated to an actor  $a \in A$ , and each row is associated to a Fifo queue  $f \in F$ . The matrix coefficients are defined as follows such that for each  $a \in A$  and each  $f \in F$ :

$$\Gamma_{a,f} = \begin{cases} prod(a,f) & \text{if } a \text{ is the source actor of } f \\ -cons(a,f) & \text{if } a \text{ is the target actor of } f \\ 0 & \text{otherwise} \end{cases}$$

The minimum solution vector of the system is called the Repetition Vector (RV). Each entry of the RV corresponds to the number of executions needed for an actor to restore the initial marking of the graph. If such vector exists, then the data-token production-consumption system is balanced and the graph is consistent.

Figure 3.2, the graph composed by the three actors A, B, and C represents a consistent SDF graph for which the repetition vector is RV = [3, 4, 2].

Another method to verify the consistency of an SDF graph is by computing the rank of the topology matrix. Based on the theorem introduced by Lee in [LM87a], a consistent SDF graph is consistent if the rank of its topology matrix  $\Gamma(G)$  is equal to the total number of its actors minus 1:  $rank(\Gamma) = |A| - 1$ .

In practice, the consistency of a SDF graph is checked by computing directly the RV of the graph using the polynomial algorithm of [BLM96a]. If the algorithm fails to compute the RV then the graph is not consistent.

(a) SDF graph example.

$$(A,B) \begin{bmatrix}

A & B & C \\

4 & -3 & 0 \\

0 & 1 & -2 \\

-2 & 0 & 3

\end{bmatrix} \times \begin{bmatrix}

3 \\

4 \\

2

\end{bmatrix} = \begin{bmatrix}

0 \\

0 \\

0

\end{bmatrix}$$

(b) The Topology matrix.

Figure 3.2 – An SDF graph example and its corresponding topology matrix.

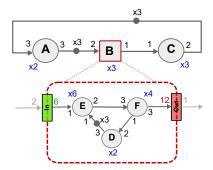

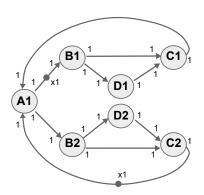

### 3.3.2 Consistency of a Hierarchical SDF graph

To evaluate the consistency of a Hierarchical SDF graph, the hierarchical actors must be replaced with their SDF subgraph description first. This process is called flattening the hierarchy of the graph, which results in an equivalent large non hierarchical SDF graph. For the Hierarchical SDF graph, this process is mandatory to be able to analyze the behavior of the graph. In fact, all the actors of a Hierarchical SDF graph are data dependent, even if each one of them belongs to a different level. Thus, in order to evaluate the consistency of the graph and to compute its RV, all the data dependencies of the actors must be revealed. Once the Hierarchical SDF graph is flattened, it is evaluated as an SDF graph using the classical methods described previously. Figure 3.3 shows a Hierarchical SDF graph example and its equivalent SDF graph after flattening its hierarchy. The equivalent SDF graph is consistent for which the RV is RV = [2, 2, 1, 2]. Thus, the whole Hierarchical SDF graph is consistent.

Figure 3.3 – Flattening the hierarchical of a Hierarchical SDF graph to compute its RV.

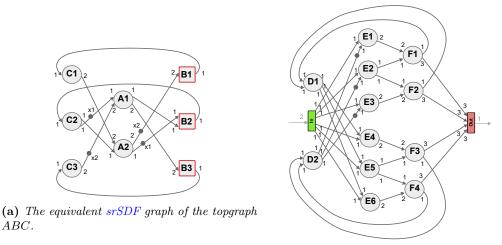

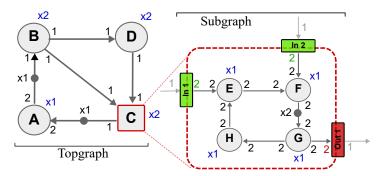

### 3.3.3 Consistency of an IBSDF graph

In contrast to the Hierarchical SDF model, the IBSDF MoC is a compositional model which enables the analysis of each subgraph independently. Indeed, with their special behavior, the input and output interfaces insulate each subgraph from the hierarchy in terms of data dependency. Thus, an IBSDF graph is consistent if each of its subgraphs is consistent, including the top-graph. Figure 3.4 shows the same hierarchical graph example of figure 3.3a but modeled with an IBSDF graph. Evaluating the consistency of the IBSDF graph example consists on checking the consistency of both the topgraph and the subgraph, but separately. Since both the graphs are consistent, the whole IBSDF graph example is consistent. The RV of the topgraph is RV = [1, 1, 1] (see fig. 3.4b), and the RV of the subgraph is RV = [2, 2, 1, 2] (see fig. 3.4c). More details on the consistency of the IBSDF model as well as a proof for the data dependency of the subgraphs can be found in [PBR09].

Figure 3.4 – Evaluating the consistency of an IBSDF graph.

In the IBSDF graph example, the behavior of the topgraph does not change regardless how many data tokens are required for actor D to execute. Indeed, the input interface duplicates the data tokens received from the hierarchical actor H as many times as needed

for the execution of actor D. Unlike the Hierarchical SDF graph example where actor A of the topgraph A must be executed twice to produce enough data tokens for actor D. Actor B in turn is executed twice to consume all the data tokens produced by actor D.

This example demonstrates the compositionality of the IBSDF model and it capability of insulating the different modules of the hierarchy in terms of data dependency. Furthermore, each module can be reused and integrated to other applications without changing the behavior of the module itself or the behavior of the new applications.

In this thesis, to simplify the computations and to preserve the semantics of the IBSDF model during the compilation process, we make the following modifications on the interface once the repetition factor of the IBSDF graph is computed:

- 1. For each input interface in, we set its production rate on its output FIFO queue f equal to  $Prod(in, f) \times RV(in)$ .

- 2. For each output interface out, we set its consumption rate on its input Fifo queue f equal to  $Cons(out, f) \times RV(out)$ .

- 3. For each input and output interface, we set its repetition factor equal to 1.

Figure 3.5 shows the new production and consumption rates of the interfaces of the IBSDF graph example after computing its RV.

Figure 3.5 – The IBSDF graph example after computing its RV

### 3.4 Dataflow graphs Conversion

Dataflow graphs are constantly converted at many stages of the compilation into equivalent simplified and more expressive graph versions. The HSDF and the DAG conversions are the most used transformations for static dataflow models. The main purpose of this two conversions is to expose all the parallelism in a dataflow graph in order to precisely analyze, map, and schedule the application. In the following we present the different graph transformations for the SDF and the IBSDF models.

### 3.4.1 SDF graph conversions

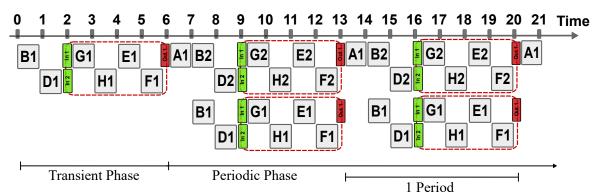

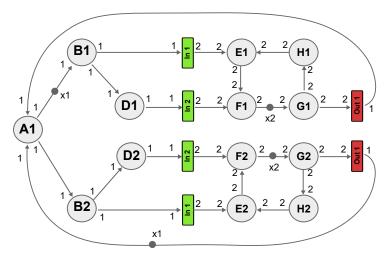

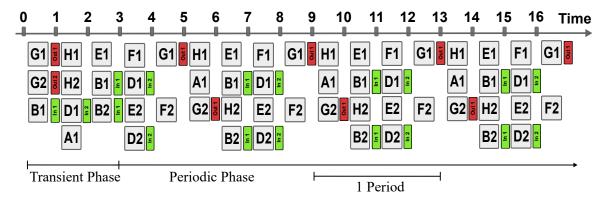

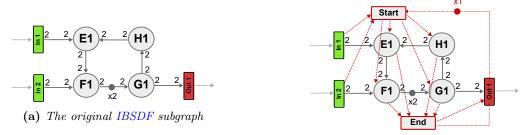

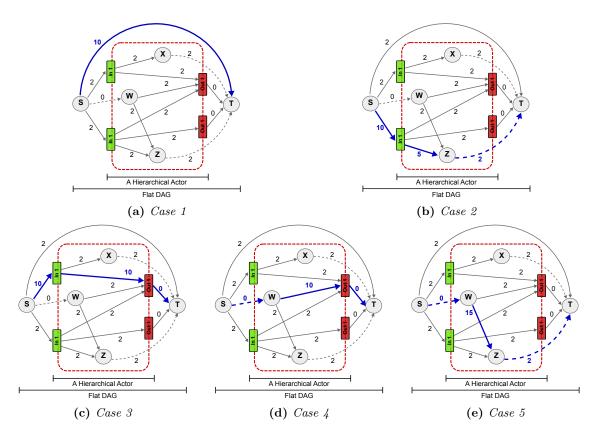

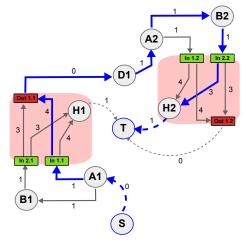

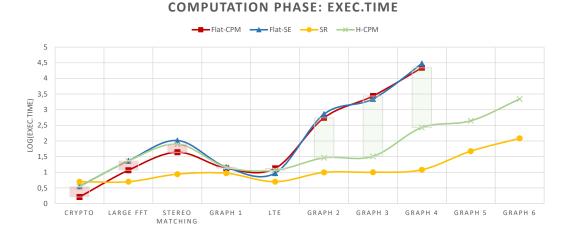

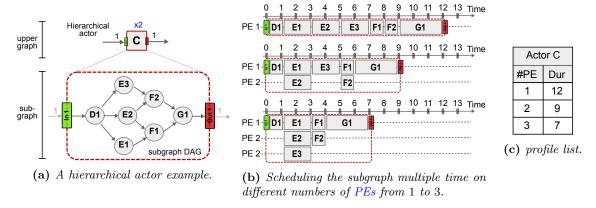

### SDF graph to HSDF graph