## Performance Debugging Toolbox for Binaries: Sensitivity Analysis and Dependence Profiling

Fabian Gruber

### ▶ To cite this version:

Fabian Gruber. Performance Debugging Toolbox for Binaries: Sensitivity Analysis and Dependence Profiling. Mathematical Software [cs.MS]. Université Grenoble Alpes, 2019. English. NNT: 2019 GREAM071. tel-02908498

## HAL Id: tel-02908498 https://theses.hal.science/tel-02908498v1

Submitted on 29 Jul 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique Arrêté ministériel : 25 mai 2016

Présentée par

## **Fabian GRUBER**

Thèse dirigée par Fabrice RASTELLO

préparée au sein du Laboratoire d'Informatique de Grenoble dans l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique

Débogage de performance pour code binaire: Analyse de sensitivité et profilage de dépendances

## Performance Debugging Toolbox for Binaries: Sensitivity Analysis and Dependence Profiling

Thèse soutenue publiquement le **17 décembre 2019**, devant le jury composé de :

#### **Monsieur FABRICE RASTELLO**

DIRECTEUR DE RECHERCHE, INRIA CENTRE DE GRENOBLE RHÔNE-ALPES, Directeur de thèse

#### Monsieur BARTON MILLER

PROFESSEUR, UNIVERSITY OF WISCONSIN-MADISON – USA, Rapporteur

### **Monsieur DENIS BARTHOU**

PROFESSEUR, BORDEAUX INP, Rapporteur

#### **Monsieur FRANZ FRANCHETTI**

PROFESSEUR, CARNEGIE MELLON UNIVERSITY – USA, Examinateur

#### **Monsieur FREDERIC PETROT**

PROFESSEUR, GRENOBLE INP, Président

#### Monsieur SVILEN KANEV

DOCTEUR-INGENIEUR, GOOGLE - USA, Examinateur

#### Résumé

Le débogage, tel qu'il est généralement défini, consiste à trouver et à supprimer les problèmes empêchant un logiciel de fonctionner correctement. Quand on parle de bogues et de débogage, on fait donc habituellement référence à des bogues fonctionnels et au débogage fonctionnel. Dans le contexte de cette thèse, cependant, nous parlerons des bogues de performance et de débogage de performance. Nous ne cherchons donc pas les problèmes engendrant de mauvais comportements du programme, mais les problèmes qui le rendent inefficace, trop lent, ou qui induisent une trop grande utilisation de ressources. À cette fin, nous avons développé des outils qui analysent et modélisent la performance pour aider les programmeurs à améliorer leur code de ce point de vue là. Nous proposons les deux techniques de débogage de performance suivantes: analyse des goulets d'étranglement basée sur la sensibilité et Suggestions d'optimisation polyédrique basées sur les dépendances de données.

Analyse des goulets d'étranglement basée sur la sensibilité Il peut être étonnamment difficile de répondre à une question apparemment anodine sur la performance d'un programme, comme par exemple celle de savoir s'il est limité par la mémoire ou par le CPU. En effet, le CPU et la mémoire ne sont pas deux ressources complètement indépendantes, mais sont composés de multiples sous-systèmes complexes et interdépendants. Ici, un blocage d'une ressource peut à la fois masquer ou aggraver des problèmes avec une autre ressource. Nous présentons une analyse des goulets d'étranglement basée sur la sensibilité qui utilise un modèle de performance de haut niveau implémenté dans Gus, un simulateur CPU rapide pour identifier les goulets d'étranglement de performance.

Notre modèle de performance a besoin d'une base de référence pour la performance attendue des différentes opérations sur un CPU, comme le pic IPC et comment différentes instructions se partagent les ressources du processeur. Malheureusement, cette information est rarement publiée par les fournisseurs de matériel, comme Intel ou AMD. Pour construire notre modèle de processeur, nous avons développé un système permettant de récupérer les informations requises en utilisant des micro-benchmarks générés automatiquement.

Suggestions d'optimisation polyédrique basées sur les dépendances de données Nous avons développé MICKEY, un profileur dynamique de dépendances de données qui fournit un retour d'optimisation de haut niveau sur l'applicabilité et la rentabilité des optimisations manquées par le compilateur. MICKEY exploite le modèle polyédrique, un puissant cadre d'optimisation pour trouver des séquences de transformations de boucle afin d'exposer la localité des données et d'implémenter à la fois le parallélisme gros-grain, c'est-à-dire au niveau thread, et grainfin, c'est-à-dire au niveau vectoriel. Notre outil utilise une instrumentation binaire dynamique pour analyser des programmes écrits dans différents langages de programmation ou utilisant des bibliothèques tierces pour lesquelles aucun code source n'est disponible.

En interne MICKEY utilise une représentation intermédiaire (RI) polyédrique qui code à la fois l'exécution dynamique des instructions d'un programme ainsi que ses dépendances de données. La RI ne capture pas seulement les dépendances de données à travers plusieurs boucles mais aussi à travers des appels de procédure, éventuellement récursifs. Nous avons développé un algorithme efficace de compression de traces qui construit cette RI polyédrique à partir de l'exécution d'un programme. L'folding algorithm trouve aussi des accès réguliers dans les accès mémoire pour prédire la possibilité et la rentabilité de la vectorisation. Il passe à l'échelle sur de gros programmes grâce à un mécanisme de sur-approximation sûr et sélectif pour les applications partiellement irrégulières.

#### Abstract

Debugging, as usually understood, revolves around finding and removing defects in software that prevent it from functioning correctly. That is, when one talks about bugs and debugging one usually means functional bugs and functional debugging. In the context of this thesis, however, we will talk about performance bugs and performance debugging. Meaning we want to find defects that do not cause a program to crash or behave wrongly, but that make it run inefficiently, too slow, or use too many resources. To that end, we have developed tools that analyse and model the performance to help programmers improve their code to get better performance. We propose the following two performance debugging techniques: sensitivity based bottleneck analysis and data-dependence profiling driven optimization feedback.

Sensitivity Based Performance Bottleneck Analysis Answering a seemingly trivial question about a program's performance, such as whether it is memory-bound or CPU-bound, can be surprisingly difficult. This is because the CPU and memory are not merely two completely independent resources, but are composed of multiple complex interdependent subsystems. Here a stall of one resource can both mask or aggravate problems with another resource. We present a sensitivity based performance bottleneck analysis that uses high-level performance model implemented in Gus, a fast CPU simulator to pinpoint performance bottlenecks.

Our performance model needs a baseline for the expected performance of different operations on a CPU, like the peak IPC and how different instructions compete for processor resources. Unfortunately, this information is seldom published by hardware vendors, such as Intel or AMD. To build our processor model, we have developed a system to reverse-engineer the required information using automatically generated micro-benchmarks.

Data-Dependence Driven Polyhedral Optimization Feedback We have developed MICKEY, a dynamic data-dependence profiler that provides high-level optimization feedback on the applicability and profitability of optimizations missed by the compiler. MICKEY leverages the polyhedral model, a powerful optimization framework for finding sequences of loop transformations to expose data locality and implement both coarse, i.e. thread, and fine-grain, i.e. vector-level, parallelism. Our tool uses dynamic binary instrumentation allowing it to analyze program written in different programming languages or using third-party libraries for which no source code is available.

Internally Mickey uses a polyhedral intermediate representation (IR) that encodes both the dynamic execution of a program's instructions as well as its data dependencies. The IR not only captures data dependencies across multiple loops but also across, possibly recursive, procedure calls. We have developed an efficient trace compression algorithm, called the folding algorithm, that constructs this polyhedral IR from a program's execution. The folding algorithm also finds strides in memory accesses to predict the possibility and profitability of vectorization. It can scale to real-life applications thanks to a safe, selective over-approximation mechanism for partially irregular data dependencies and iteration spaces.

## Dedication

This thesis is dedicated to my future wife Kim Hyunyoung, my family, and my friends. Thank you from the bottom of my heart.

## Acknowledgements

The work presented in this thesis has been done in collaboration with my advisor Fabrice Rastello, Louis-Noël Pouchet from the Colorado State University, Christophe Guillon and others from STMicroelectronics, my colleagues Diogo Nunes Sampaio, Manuel Selva, Nicolas Tollenare, Nicolas Derumigny, and many more.

I sincerely thank them all for their advice, help, and hard work.

Without them my thesis would not have been possible.

I also sincerely thank Imma Presseguer for all the administrative work, moral support and advice.

## Contents

| $\mathbf{R}$     | Résumé   |                                                                    |    |

|------------------|----------|--------------------------------------------------------------------|----|

| $\mathbf{A}$     | bstra    | act                                                                | v  |

| $\mathbf{C}_{0}$ | Contents |                                                                    |    |

| 1                | Intr     | roduction                                                          | 1  |

|                  | 1.1      | Performance Debugging                                              | 3  |

|                  | 1.2      | Background                                                         | 3  |

|                  |          | 1.2.1 Profiling                                                    | 3  |

|                  |          | 1.2.2 Instrumentation and dynamic binary analysis                  | 5  |

|                  |          | 1.2.3 The polyhedral model                                         | 6  |

|                  | 1.3      | Objectives                                                         | 8  |

|                  |          | 1.3.1 Sensitivity Based Performance Bottleneck Analysis            | 8  |

|                  |          | 1.3.2 Dependence Profiling Driven Polyhedral Optimization Feedback | 9  |

|                  |          | 1.3.3 Contributions                                                | 10 |

|                  | 1.4      | Structure of the Thesis                                            | 10 |

| 2                | Dyr      | namic Binary Instrumentation with QEMU                             | 11 |

|                  | 2.1      | QEMU                                                               | 12 |

|                  | 2.2      | The Tiny Code Generator                                            | 13 |

|                  | 2.3      | The TCG Plugin Infrastructure                                      | 16 |

|                  | 2.4      | Execution Tracing with QEMU                                        | 19 |

|                  |          | 2.4.1 Control-flow tracing                                         | 20 |

|                  |          | 2.4.2 Data Dependence Tracing                                      | 27 |

|                  |          | 2.4.3 Value tracing                                                | 28 |

|                  | 2.5      | Evaluation of the Overhead of Plugins                              | 28 |

|                  | 2.6      | Related Work                                                       | 29 |

|                  | 2.7      | Conclusion and Perspectives                                        | 34 |

|                  |          | -                                                                  |    |

| 3                | Sen      | sitivity Based Performance Bottleneck Analysis                     | 35 |

|                  | 3.1      | Introduction                                                       | 36 |

|                  | 3.2      | Modern CPU Microarchitecture                                       | 38 |

|                  |          | 3.2.1 Concepts of instruction level parallelism                    | 38 |

|                  |          | 3.2.2 Implementation of instruction level parallelism              | 39 |

|                  | 3.3      | Related Work                                                       | 41 |

|                  | 3.4      | Gus                                                                | 48 |

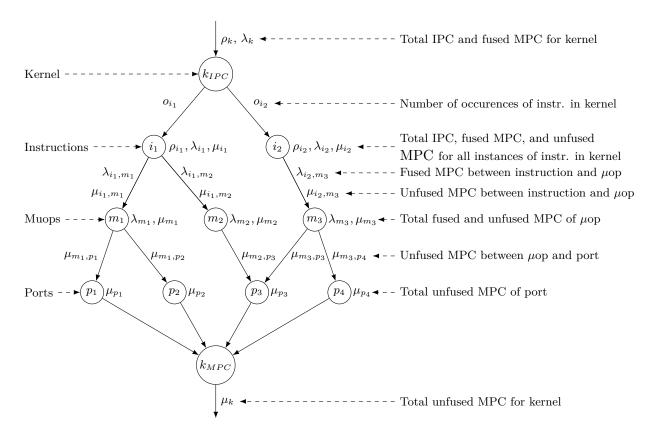

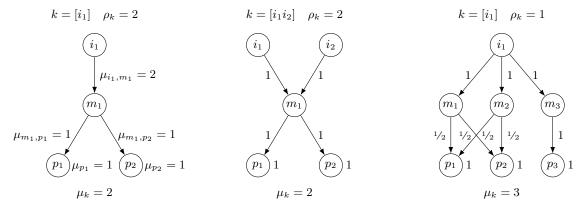

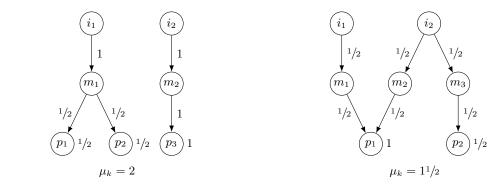

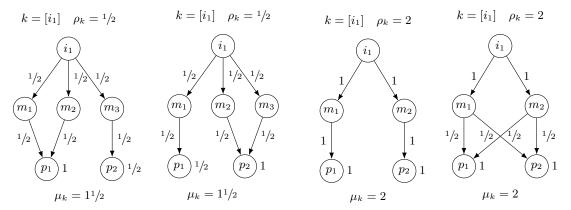

|                  |          | 3.4.1 A resource-centric CPU model                                 | 49 |

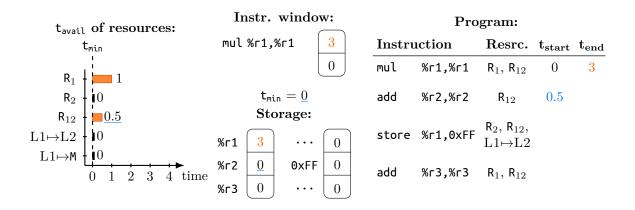

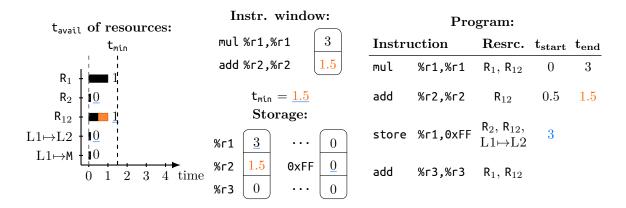

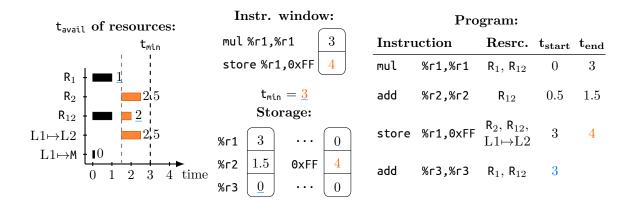

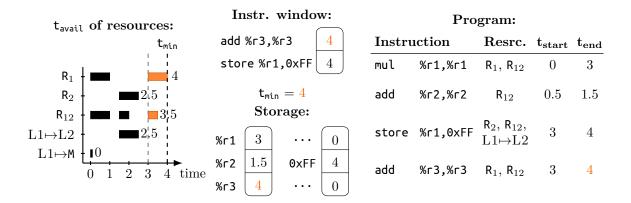

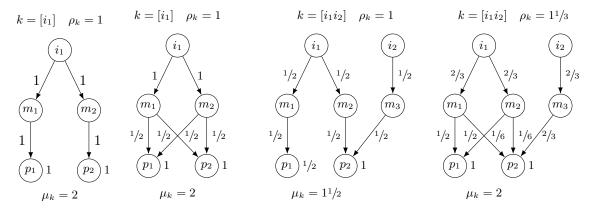

|                  |          | 3.4.2 An illustrative example                                      | 50 |

|                  |          | 3.4.3 The simulator algorithm                                      | 54 |

|                  | 3.5      | Pinedream                                                          | 56 |

xii CONTENTS

|    |       | 3.5.1 The instruction flow problem                      | 57  |

|----|-------|---------------------------------------------------------|-----|

|    |       | 3.5.2 Finding port mappings                             | 61  |

|    |       | 3.5.3 Converting port mappings to resource models       | 65  |

|    |       | 3.5.4 Benchmark design                                  | 66  |

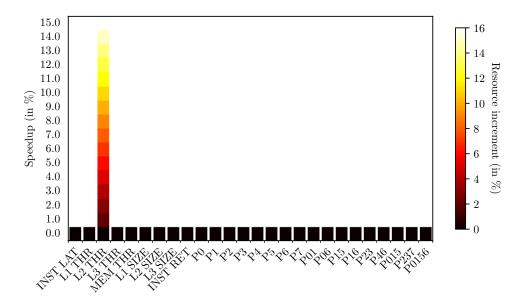

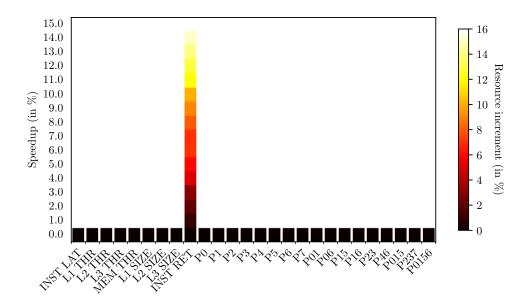

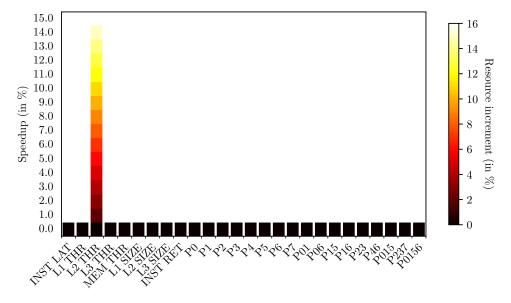

|    | 3.6   | Experiments                                             | 69  |

|    |       | 3.6.1 Gus                                               | 69  |

|    |       | 3.6.2 PIPEDREAM                                         | 78  |

|    | 3.7   | Conclusion and Future Work                              | 85  |

| 4  | Data  | a-Dependence Driven Optimization Feedback               | 89  |

|    | 4.1   | Introduction                                            | 90  |

|    | 4.2   | Illustrative Scenario                                   | 91  |

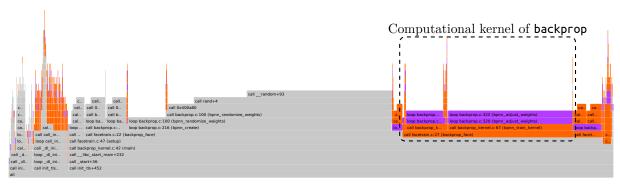

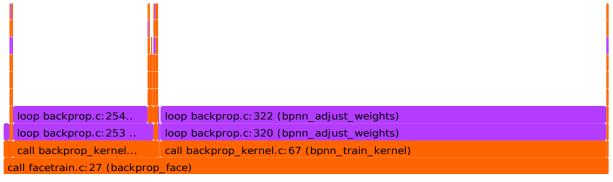

|    |       | 4.2.1 Example problem: backprop                         | 91  |

|    |       | 4.2.2 Solution: MICKEY                                  | 93  |

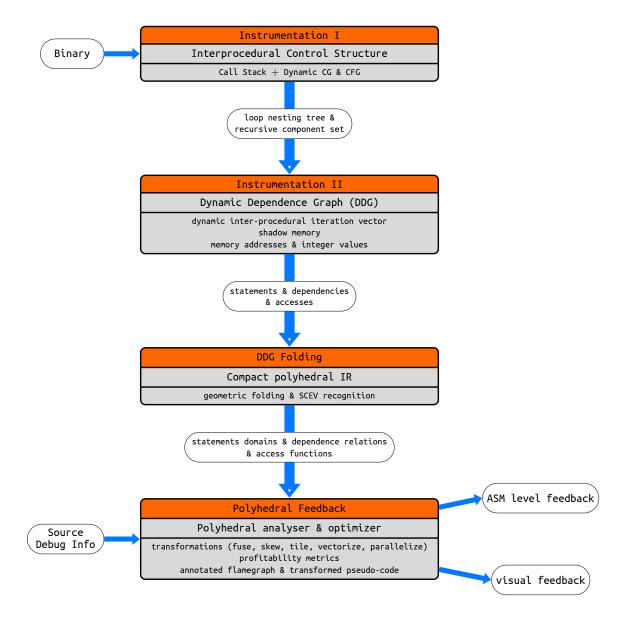

|    | 4.3   | Overview of Mickey                                      | 94  |

|    | 4.4   | Interprocedural Program Representation                  | 96  |

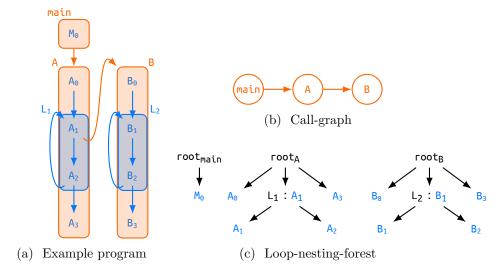

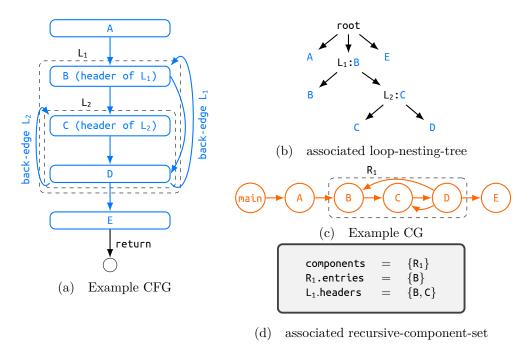

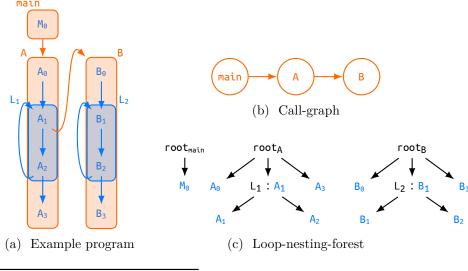

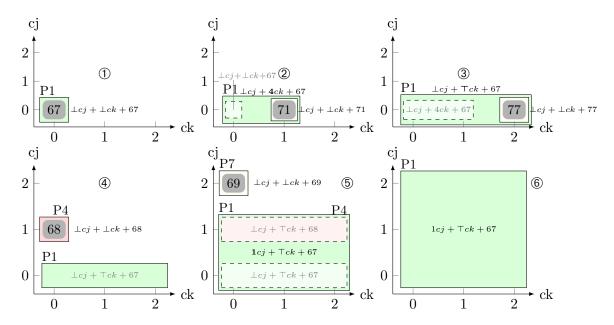

|    |       | 4.4.1 Control-flow-graph and loop-nesting-tree          | 97  |

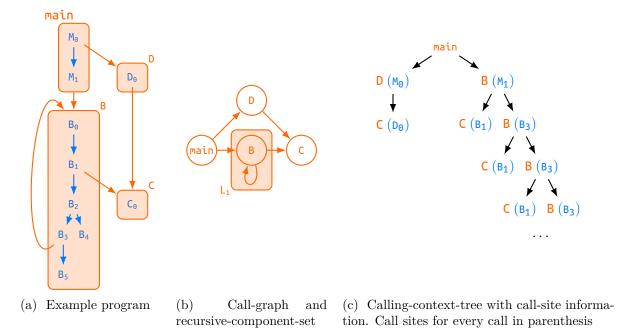

|    |       | 4.4.2 Call-graph and recursive-component-set            | 98  |

|    |       | 4.4.3 DDG: Dynamic Dependence Graph                     | 101 |

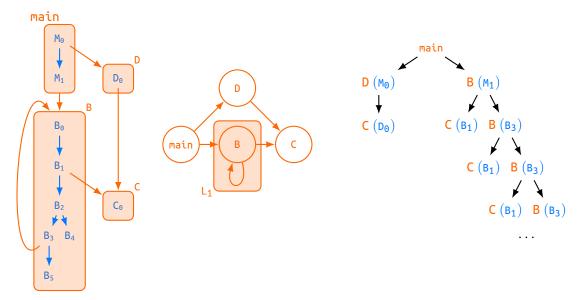

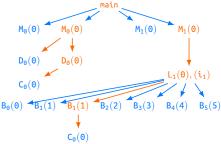

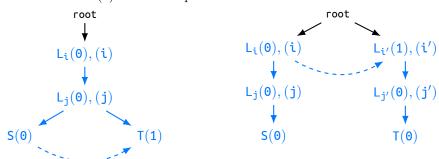

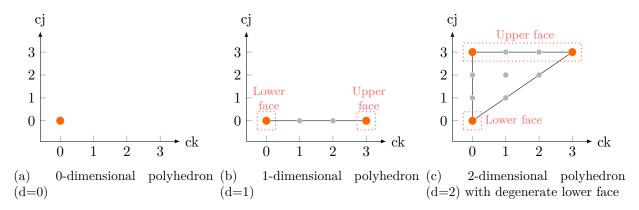

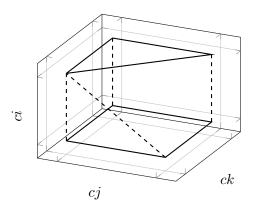

|    | 4.5   | The Folding Algorithm                                   | 106 |

|    |       |                                                         | 106 |

|    |       | 4.5.2 Outputs                                           |     |

|    |       | 4.5.3 Using the output                                  |     |

|    |       | 4.5.4 Overview                                          |     |

|    |       | 4.5.5 The algorithm                                     |     |

|    |       | 4.5.6 Complexity analysis                               |     |

|    | 4.6   | Polyhedral Feedback                                     |     |

|    | 1.0   | 4.6.1 Polyhedral compilation of folded-DDGs             |     |

|    |       | 4.6.2 User feedback                                     |     |

|    | 4.7   | Experimental Results                                    |     |

|    | 1.1   | 4.7.1 Case studies                                      |     |

|    |       | 4.7.2 Static polyhedral compilers and Rodinia           |     |

|    |       | 4.7.3 Optimization feedback on Rodinia                  |     |

|    |       | 4.7.4 Trace compression results                         |     |

|    | 4.8   | Related Work                                            |     |

|    | 4.9   | Conclusion and Perspectives                             |     |

|    | 4.9   | Conclusion and 1 erspectives                            | 190 |

| 5  | Con   | iclusion and Future Work                                | 139 |

|    | 5.1   | Summary                                                 | 140 |

|    |       | 5.1.1 Dynamic Binary Instrumentation with QEMU          | 140 |

|    |       | 5.1.2 Sensitivity-Based Performance Bottleneck Analysis | 140 |

|    |       | 5.1.3 Data-Dependence Driven Optimization Feedback      | 141 |

|    | 5.2   | Perspectives                                            |     |

|    | 5.3   | List of Publications                                    |     |

| Li | st of | Figures                                                 | 144 |

|    |       |                                                         | 146 |

|    |       |                                                         |     |

| LI | ու ու | Algorithms                                              | 147 |

| CONTENTS     | xiii |

|--------------|------|

| Bibliography | 149  |

| Glossary     | 167  |

xiv CONTENTS

# Chapter 1

## Introduction

| Contents |                                                                                                |

|----------|------------------------------------------------------------------------------------------------|

| 1.1      | Performance Debugging                                                                          |

| 1.2      | Background                                                                                     |

|          | 1.2.1 Profiling                                                                                |

|          | 1.2.2 Instrumentation and dynamic binary analysis 5                                            |

|          | 1.2.3 The polyhedral model                                                                     |

| 1.3      | Objectives                                                                                     |

|          | 1.3.1 Sensitivity Based Performance Bottleneck Analysis 8                                      |

|          | $1.3.2  \text{Dependence Profiling Driven Polyhedral Optimization Feedback} \ . \ . \ . \ \ 9$ |

|          | 1.3.3 Contributions                                                                            |

| 1.4      | Structure of the Thesis                                                                        |

It is now nearly fifteen years ago that Herb Sutter wrote his famous article "The Free Lunch Is Over" [201]. In this piece, he argued that the classical methods of boosting single-core performance, such as raising the CPU clock frequency and straight-line instruction throughput, are no longer feasible. He claims that the single-core performance of modern microprocessors has completely stagnated and that multi-core architectures and concurrent programming models are the only way to increase performance going forward. Only a few years later, Hill et al. [94] analysed the state of microprocessor designs of the time and gave some broad recommendations that, at least partially, contradict Sutter's conclusions. One of their recommendations states that "Researchers should seek methods of increasing [single] core performance even at a high cost."

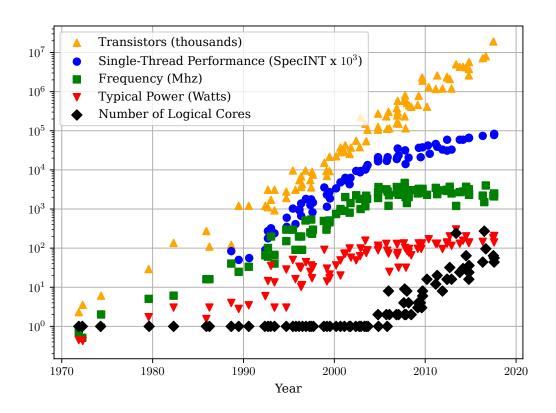

Figure 1.1 shows data describing the overall trends in performance parameters of microprocessors of the last 42 years. If we look at the data, it seems that both predictions have been, to some degree, proven correct. Clock frequency has completely stagnated, while the average core count of processors has exploded. And yet, the single-core performance of processors, as measured by the SpecINT [91, 92] benchmark suite, has not stopped rising. Albeit it is admittedly growing slower than it used to. Since the clock frequency has not been rising, we can deduce that the increase in performance has indeed been paid for "at a high", by an increase in complexity of hardware and software.

Figure 1.1 – 42 years of microprocessor trends [176].

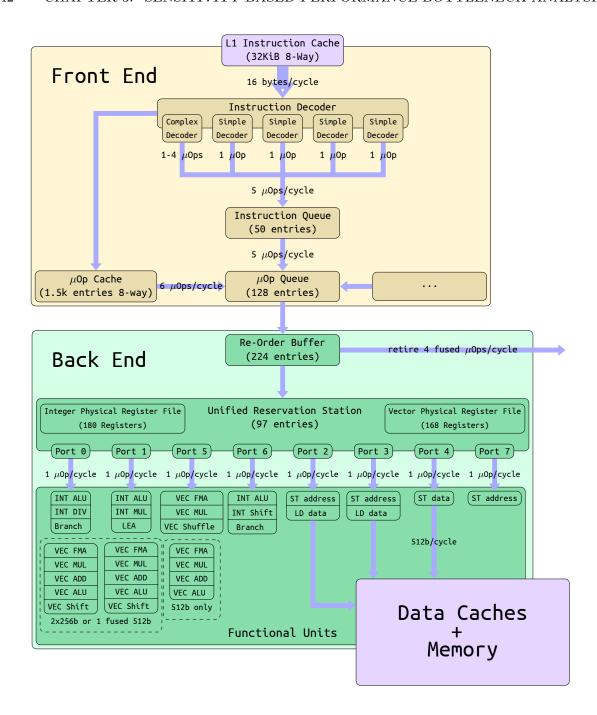

In day to day programming, this increase of complexity is often hidden behind abstractions. A modern x86 processor, for example, in many ways still pretends to work much the same as a model from the 1980s. That is, to a programmer it, seems that instructions execute sequentially and that every load and store directly touches main memory. Under the hood, however, a modern CPU is a sophisticated parallel system with a deep hierarchy of memory

caches. However, all these abstractions very quickly break down when one wants to study and understand the performance of an application. Then it suddenly becomes crucially important to know which data dependency stopped two instructions from execution in parallel or which memory access caused a cache miss. To effectively analyse and debug the performance of a program, one has to look under the hood and remove the abstractions. It is the goal of this thesis to propose tools and techniques for helping programmers better understand the behaviour of their programs and guide them in the process of performance optimization.

## 1.1 Performance Debugging

Debugging, as usually understood, revolves around finding and removing defects in software that prevent it from functioning correctly. That is, when one talks about bugs and debugging one usually means functional bugs and functional debugging. In the context of this thesis, however, we will talk about performance bugs and performance debugging. Meaning we want to find defects that do not cause a program to crash or behave wrongly, but that make it run inefficiently, too slow, or use too many resources.

Even the best programmer has, at some point, written a buggy program. When they observe that something is amiss they will often use *functional debugging* tools like GDB [74] that help find errors in the behaviour of programs. That is, the classical problems for which programmers turn to functional debuggers are:

- 1. Where is the program misbehaving or crashing?

- 2. Why is the program misbehaving or crashing?

Usually, these tools do not directly try to answer the question *how* one can prevent a program from misbehaving or crashing since this would require changing the semantics of the program. While there are approaches that attempt this from the fields of software verification, like runtime enforcement [69], they require a specification of the intended semantics of a program and are not yet commonly used.

Performance debuggers or performance analysis tools, on the other hand, help finding problems in the non-functional aspects of programs. That is, the problems which make a programmer turn to these tools are:

- 1. Where is the program slow?

- 2. Why is the program slow?

- 3. How can one make the program run faster?

Historically, existing techniques have only measured and predicted the current performance characteristics of programs and so, similarly to functional debugging tools, only help answer the first two questions. In this thesis, we will develop two approaches that try to extrapolate the possible performance a system could achieve to help answer the last two questions, i.e., why programs are slow and how they can be made more efficient.

## 1.2 Background

#### 1.2.1 Profiling

The standard approach for identifying performance bugs is profiling. The most straightforward profiling technique is to measure the time required to run a piece of code. Tools like GPROF [78] help automate this process by automatically inserting code to measure the runtime of individual functions via the compiler. Other tools like QPT [122] insert code to count the number of time every basic block in a program executes or how many times every edge in the control-flow-graph is taken. These approaches can help detect *hot* program regions, i.e., *where* a program is

spending most of its time. However, knowing only where the hot regions of a program are is all too often not enough to fix performance bugs.

To help pinpoint the causes of performance problems modern processors offer hardware performance counters <sup>1</sup>, also called hardware counters, or performance counters [44, 151]. Hardware counters allow measuring many different performance-related events, such as the number of instructions executed or the number of cache hits and misses at different cache levels. At the most basic level, performance counters work the same as time measurements. To measure, for example, the number of L2 cache misses that occur in a given function it suffices to insert code to read the current value of the corresponding counter at the beginning and the end of the function and subtract the two values.

Many processors also support sampling modes which make it possible to use hardware counters without having to modify an application to explicitly read counters. Different vendors and processor generations implement a wide variety of different sampling models such as, for example, event-based sampling, time sampling, and instruction-based sampling. The details of how these different sampling techniques work, how they can be used, and how precise they differ quite a lot. However, the overall idea is that at regular, user-configured intervals the processor halts normal execution and stores the current values of the hardware performance counters, usually by writing some data to a preconfigured memory location or by raising a special interrupt. Sampling-based profilers then use statistical methods to extrapolate the behaviour of instructions for which they have no samples. Directly using hardware performance counters is quite complicated and so over time a plethora of libraries and tools, such as PAPI [65], LIKWID [172], HPCToolkit [4], Linux perf [144], Intel VTune [169], have been developed for this purpose.

Despite their utility hardware performance counters suffer from some severe limitations. While configuring the CPU to count performance events has no, or barely any, overhead, the reading of counters, either directly or through sampling, is not free. Directly reading counters uses at least some CPU resources such as registers and profiling requires either a costly CPU interrupt or some writes to memory. Consequently using hardware counters can cause an observer effect where the act of measuring the performance of an application changes its performance. This can lead to so-called performance heisenbugs, named after Heisenberg's uncertainty principle. It also makes fine-grain profiling using performance counters difficult.

Linux perf, a widely used sampling-based profiling tool, for example, by default limits the maximum sampling rate. This is to prevent programs from accidentally spending more time reading performance counters and writing to internal buffers than actually executing real code [88] On an Intel i5-4590 CPU running at 3.3 GHz the limit is 50k samples per second, which means one can at best obtain one sample every 66k instructions.

Another problem with performance counters is that one is limited to measuring a fixed set of metrics. With this approach, it is impossible to profile for an event for which the hardware offers no counter. Furthermore, even on the most recent processors, one can not enable all available performance event counters at the same time, but usually only a small handful, around four to ten.

An alternative to using hardware performance counters is to use a simulator such as GEM5 [23]. A cycle-accurate simulator makes it possible to produce a detailed trace of performance-related events without during execution without perturbing the behaviour of the original program. Since simulators are software, it is also possible to add new performance counters if necessary.

However, the power and flexibility of simulators also come at a cost. Developing a cycle-level simulator is extremely time consuming and requires a lot of expertise. A detailed simulation is also quite costly in terms of computation and runs considerably slower than native execution. For example, GEM5 at its highest level of precision requires, on average, one year to run a single

<sup>&</sup>lt;sup>1</sup>The term "counter" can be misleading since modern processors do much more than just counting events.

1.2. BACKGROUND 5

SPEC2006 benchmark [180]. A common approach to speed up simulations is to only simulate parts of a program [188, 224] or to only simulate some aspect of the processor [36, 110, 152].

Simulators based on abstract high-level CPU core models, while not as accurate as a real cycle-level simulator, have been shown to provide reasonable accurate execution time predictions while running orders of magnitude faster than cycle-level simulation systems [68, 76, 202, 37].

At the end of the day, the data gathered using profiling, either using hardware counters or simulation, is still very low-level, recording information at the level of individual machine instructions. Tools like HPCToolkit [4], Intel VTune [169], and Linux perf [144] can map these results back to the source code of a program using debug information, making it possible to view aggregate results per loop or function. However, these tools still do not directly explain why a given piece of code has a performance problem, such as too many cache misses or stalled CPU cycles, or how to fix the problem. Finding and fixing the root causes of a performance problem often still require substantial expertise.

Feedback-Directed Optimization (FDO) takes one step towards the direction of using profiling information to improve performance [192, 11, 12]. FDO based systems collect runtime information using profiling and use it to guide optimization heuristics in compilers. Tools like, Intel Advisor [52] and AutoSCOPE [195], on the other hand, try to give human-readable optimization advice. They are, however, not able to automatically apply code transformations, or even necessarily prove that a transformation is valid. Instead, they propose optimizations such as parallelization or loop fusion, leaving the task of implementing this transformation to the programmer.

At this point, we have only given a brief overview of basic profiling techniques. Chapters 3 and 4 will present a number of more involved approaches using richer, but expensive to collect, performance events.

### 1.2.2 Instrumentation and dynamic binary analysis

Since profilers analyse events that occur during the execution of a program, they need some facility to trace these events. Sampling of hardware performance counters is an excellent low overhead method for collecting performance-related events, but it suffers from a number of limitations, as described in the previous section.

An alternative technique used by a large number of dynamic analysis tools, including those presented in this thesis, is instrumentation. Instrumentation, is a very versatile technique that allows capturing arbitrary program behaviour. Using instrumentation a profiler can implement any new performance counter it may require in software. Besides profiling, instrumentation is used in numerous other dynamic analyses such as dynamic control flow integrity [1] and memory corruption checking [185].

There are some new hardware-assisted program tracing technologies, such as Intel PT [51], on the horizon that may replace instrumentation for some profiling use cases. However, for the moment the available hardware is still somewhat unreliable and can lose events due to internal buffer overflows [75, 101].

Compiler based instrumentation, used by highly successful dynamic analysis tools such GPROF [78] and the LLVM Address Sanitizer [185], works directly in the compiler at the level of its intermediate representation (IR). Instrumenting programs during the compilation process has several advantages. In terms of productivity, the whole compiler infrastructure makes the task of implementing some instrumentation for profiling easy. Instrumentation can easily be performed at any level of the intermediate representation, allowing the profiling of high-level and low-level properties. It can also take advantage of all its knowledge of the program semantics and information provided by the diverse static analysis present in an optimizing compiler. In particular, any property that can be statically proven or is not data-dependent, does not have

to be profiled.

Binary instrumentation [196, 123, 134, 155, 134, 29, 145, 146], on the other hand, works directly at the level of machine code. Analysing and manipulating binaries is difficult and tedious, since, all too often, one has to re-discover the obvious. Because machine code contains much less structure than source code even relatively simple analyses needed for instrumentation, such as reconstructing the control-flow graph, become non-trivial or undecidable [145, 170]. However, working at the level of machine code has the important advantage of portability. That is, tools that directly handle machine code are not restricted to working with a given compiler, or programming language. It also makes it possible to compare the binaries produced by different compilers. If, for example, ICC turns out to generate the best performing code for an Intel platform, it is clearly interesting to be able to analyse this binary and not be limited to the output of GCC [80] or Clang [164]. Binary instrumentation even makes it possible to analyse programs for which no source code is available or which integrate closed source third-party libraries.

Another approach that can be used to implement static binary instrumentation is decompilation. SecondWrite [8] and DisIRer [104], for example, are two tools that convert machine code to LLVM IR and GCC IR respectively. These compiler IRs are semantically much richer than raw machine code, and there are a variety of existing tools that can be used to analyse and transform them. The advantage of this approach is that it has the portability of a binary analysis tool combined with ease of use of compiler-based instrumentation. However, it is only applicable to programs that can be statically decompiled.

There are also dynamic binary analysis frameworks that decompile machine code to compiler IR at runtime [64]. However, while this makes it possible to apply the powerful analyses available in a static compiler to arbitrary binaries, it also suffers from some drawbacks. The main problem is that static compilers can afford to invest much more time in analysing and optimizing programs than dynamic compilers. Due to this, authors of static compiler IRs and analyses often prioritize expressiveness and maintainability over performance. A number of failed attempts to re-use static compiler back-ends in a JIT have shown that this can lead to a prohibitive overhead at runtime [49, 50].

Dynamic binary instrumentation and the applications we have used it for will be described in detail in Chapter 2.

## 1.2.3 The polyhedral model

The most effective program optimizations for improving performance or energy consumption are typically based on the rescheduling of instructions to expose data locality, parallelism or both. The two main challenges for these kinds of optimizations are *what* transformations may be applied without breaking the program semantics and *where* in the program the optimizations should be applied to maximize the impact on the overall program performance. The *polyhedral model* [71], a mathematical model that allows reasoning about programs at the levels of loops, is one of the most powerful theoretical frameworks for finding and for applying such rescheduling optimizations.

The polyhedral model is usually applied in the context of static compilers [160, 211, 81, 162, 25, 218]. Here it is used to find sequences of loop transformations, including tiling, permutation, fusion, fission, and skewing, that aim to improve the temporal and spatial locality of data accesses and uncover both coarse (i.e., thread) and fine-grain (i.e., SIMD) parallelism. To determine the validity and profitability of these transformations, however, the polyhedral model needs precise information about data and control-flow dependencies. That is, it needs a precise model of the structure of loops and of the dependencies between statements.

The power of the polyhedral model comes, in part, from the fact that it does not try to model

1.2. BACKGROUND 7

```

5

4

3

for (i = 0; i <= 5; i++)

i

2

for (j = 0; j \le 5 - i; j++)

j>0

S: A[i][j] = B[i][j] + C[i] * D[j];

1

0

0

1

2

3

j

```

- (a) An simple loop nest with one statement S.

- (b) The 2D iteration space for statement S.

Figure 1.2 – An example program and its iteration space.

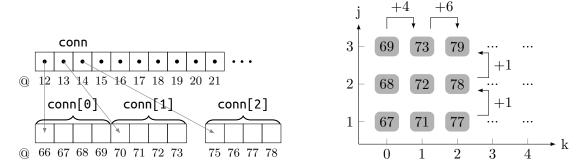

general programs. Instead, it focusses on regular loop nests operating on multi-dimensional arrays. Here, loop nests are represented by a finite Cartesian space, called the *iteration space* [223]. In this space, each level of the loop nest gives rise to one dimension. Every loop iteration then corresponds to a point in this iteration space whose coordinates are determined by the current values of the iteration variables of the enclosing loops. The polyhedral model requires that the bounds of every loop can be represented by a linear expression of the loop indices. Thanks to this restriction the iteration space can also be represented as an integer polyhedron, i.e., a set of points bounded by a set of linear constraints over the integers. Figure 1.2 shows a simple 2D loop nest and the corresponding iteration space. In this simple example, there is only one loop nest and only one statement and consequently also only one iteration space. In general, however, every statement in a program has its own iteration space. The polyhedral model also supports conditional statements, but conditionals are restricted to linear expressions in order to keep the iteration spaces representable. The expressions used to compute array indices, called access functions, are also restricted to linear functions.

Since every execution of a statement, i.e., every *dynamic instance*, is represented as a point in an iteration space the polyhedral model also uses linear relations to model data dependencies. Consider the following program:

Here every instance of the statement S depends on a previous instance of S. We note the instance of S executed in the ith iteration of the loop as S[i]. This dependence can then be expressed by the following relation (for simplicity, we omit the initialization of A and border conditions):

$$\{S[i] \to S[i']: i' = i - 1 \land 2 < i < 5\}$$

Despite this apparent simplicity, the polyhedral model is still quite expressive, but this also comes with a cost. Finding a set of optimizing loop transformations in the polyhedral model requires solving one ore more integer programs. A big strength of the polyhedral model is that the complexity of these problems is independent of the number of points in the iteration space.

Rather, the complexity is exponential in the number of different loop dimensions, statements and dependencies. As a consequence, polyhedral compilers can, in practice, only handle programs consisting of no more than a few hundred instructions.

In a compiler, the static analyses required to build this representation can only be applied to programs written in a very restrictive style with no function calls, simple control-flow and no pointer indirection [48, 62]. While there have been attempts to extend the polyhedral model to work on more general programs [197, 18] these have only met with limited success. In practice, one quickly runs into problems with pointer aliasing and pointer indirection, which make it impossible to calculate access functions statically. This, in turn, makes it impossible to build the data dependence relation. The other big hurdle one often runs into programs with complex or data-dependent loop bounds and conditionals.

To overcome these limitations, compilers have started using *hybrid analysis*, which leverages information only available at runtime to allow for more aggressive optimization. Using code versioning combined with runtime checks for the validity of a transformation allows optimizing programs even when the optimization statically cannot be proven to be legal or is not even legal for every possible program execution [177, 178, 6, 62].

The Apollo [139] and PolyJIT [190] projects push the envelope even further bringing the polyhedral model to the world of JIT compilers. They are dynamic polyhedral optimizers that both find and apply polyhedral loop transformations at runtime. Apollo is even able to speculatively execute optimistically optimized code, rolling back the execution if and when any non-affine behaviour occurs.

## 1.3 Objectives

A large part of today's performance-sensitive code is written in sequential imperative languages such as C, C++ and Fortran. There have been many attempts to extend or replace these languages and programming models, but for the foreseeable future, they will still dominate the field. In this work, we present tools that work on these kinds of programs. They allow analysing and modelling the performance of existing systems to help guide programmers improve their code to get better performance.

In this thesis, we focus on analysing and modelling the performance of relatively small compute-intensive scientific kernels. We focus on the computational and memory behaviour of programs and do not investigate aspects like network traffic or hard disk usage. All tools and techniques we present work at the level of machine code on compiled and optimised binary programs.

We propose the following two performance debugging techniques: sensitivity based bottleneck analysis and data-dependence profiling driven optimization feedback.

### 1.3.1 Sensitivity Based Performance Bottleneck Analysis

Performance Bottleneck analysis Even answering a seemingly trivial question about a program's performance, such as whether it is memory-bound or CPU-bound can be surprisingly difficult. This is because the CPU and memory are not simply two completely independent resources that a program uses independently. Instead, they are composed of multiple complex interdependent subsystems. Here a stall of one resource can both mask or aggravate problems with another resource. It is even more complicated to quantify by "how much" a resource is a bottleneck, that is, by how much performance could be improved if that one bottleneck is removed.

We propose a bottleneck analysis that is based on sensitivity analysis or differential profiling [141, 47, 118, 132, 99]. A conceptually simple approach to finding bottlenecks that works as

1.3. OBJECTIVES 9

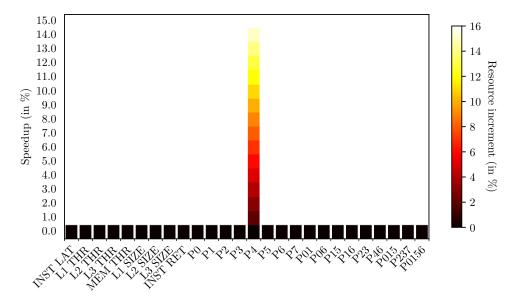

follows: One runs the program under observation multiple times, each time varying the capacity of one or more resources. The bottleneck is then the resource whose change in capacity has affected the overall change in performance the most.

A real-world example of this approach uses dynamic voltage and frequency scaling (DVFS) [100]. Here, a program or parts of it are executed repeatedly, every time with a different CPU frequency. Note that the frequency at which the CPU operates does not affect the speed at which memory works. So, if a program finishes in roughly the same time while running at a lower frequency as when running at a high frequency it is clearly not CPU-bound. Reversely, if execution time is significantly affected by CPU frequency the program is CPU-bound. However, DVFS only works at a relatively high granularity and only allows detecting the presence or absence of a general CPU bottleneck. Unfortunately, real hardware does not directly provide many other "levers" that one can use to easily vary the capacity of resources. It is, for example, not possible to reduce the throughput of the vector unit to see by how much this affects performance.

**Performance model** To allow for a more fine-grained sensitivity analysis we have developed an abstract, resource-based, performance model. We have built Gus, a prototypical implementation of this model in a CPU emulator to make it possible to apply it to real programs. Gus can arbitrarily change the capacity of every resource independently making it a powerful tool for pinpointing performance bottlenecks.

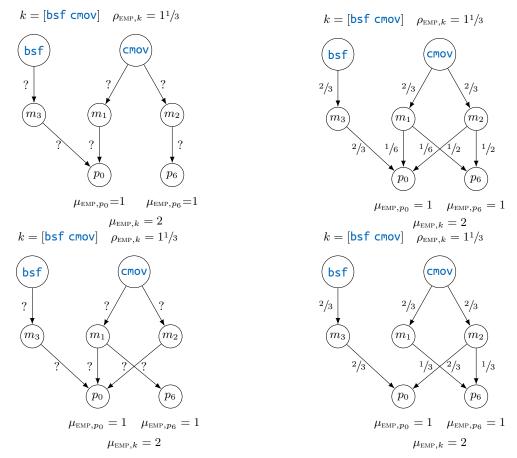

Our performance model needs a baseline, a detailed specification of the expected performance of different operations on a CPU. That is, we need to know how many instructions of a given type the processor can execute per cycle, how many cycles instructions require to finish, and how instructions interact with each other. Unfortunately, hardware vendors like Intel or AMD are not very forthcoming with this kind of information and do not publish comprehensive datasheets. To build our processor model we have developed a system to reverse-engineer the required information using automatically generated micro-benchmarks.

#### 1.3.2 Dependence Profiling Driven Polyhedral Optimization Feedback

The holy grail of performance debugging is to directly tell a user how they can change their code to improve performance. The most effective program transformations for improving performance or energy consumption are typically based on the rescheduling of instructions so as improve temporal and spatial locality. This can be used to uncover parallelism at both coarse, i.e., thread-level, and fine, i.e., vector-level, granularity. The two main challenges when using these kinds of optimizations are what transformations may be applied without breaking the program semantics and where in the program should the optimizations be applied to maximize the impact on the overall program performance.

The polyhedral model is a powerful framework for finding these and other kinds of optimizing transformations. The polyhedral model requires an exact description of both the control-flow of a program and the structure of its data dependencies. Historically, the polyhedral model has been designed to work on a restricted set of programs, called affine programs, for which it is easy to statically reconstruct exact dependence information [48]. While programs can be rewritten to fit these restrictions and help static analysis tasks, this requires significant effort and is not guaranteed to succeed. In full programs, and in particular those relying on external binaries visible only to the linker, often the data layout and calling context is inaccessible to static analyses.

Dynamic approaches [139, 190] push this boundary and handle programs which, even though they cannot be statically proven to fit the polyhedral model, do adhere to its restrictions at runtime. However, even tools that use dynamic information to build a polyhedral representation still face a number of problems. The main difficulty being how to model applications that include some non-affine dependencies and memory accesses in otherwise affine code To address this difficulty existing dynamic polyhedral approaches either use overly pessimistic approximations and lose information [199] or do not scale [112, 171].

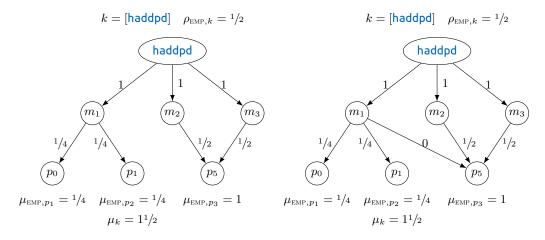

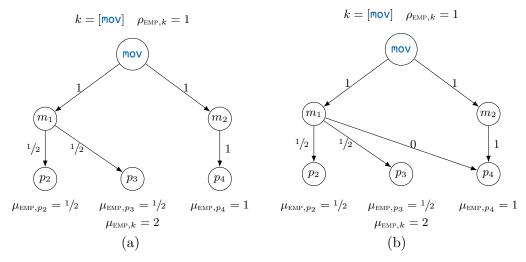

Data-dependence driven polyhedral optimization feedback We have developed MICKEY, a dynamic data-dependence profiler that builds a rich polyhedral IR from traces. MICKEY works on compiled binaries and provides feedback on the applicability and profitability of polyhedral loop transformations. It can scale to real-life applications thanks to a safe, selective overapproximation mechanism for partially irregular data dependencies and iteration spaces.

Polyhedral interprocedural IR MICKEY's polyhedral IR encodes both the dynamic execution of a program's instructions as well as its data dependencies. This IR captures the interprocedural loop nesting structure of a program in a form that is amenable to analysis by a polyhedral optimizer. It not only captures data dependencies across multiple loops but also, possibly recursive, procedure calls.

Linear time polyhedral trace compression To construct the polyhedral IR from a program's execution, we have developed the folding algorithm, an efficient trace compression algorithm. This technique was inspired by existing polyhedral trace compression techniques [112, 171], with the notable difference that it uses the geometry of iteration spaces which allows it to scale to large irregular programs. The folding algorithm also detects which instructions in a program are used to increment loop counters and finds strides in memory accesses by building scalar evolution expressions (SCEVs) [161, 213] for loads, stores and integer arithmetic instructions.

#### 1.3.3 Contributions

To summarize, in this thesis we present the following contributions:

- A sensitivity based analysis tool to detect performance bottlenecks in programs (Chapter 3).

- A tool to reverse engineer performance characteristics of instructions on modern x86 CPUs (Section 3.5).

- A data-dependence based profiling tool that provides high-level optimization feedback (Chapter 4).

- An interprocedural polyhedral intermediate representation (Section 4.4).

- A linear time polyhedral trace compression algorithm to construct this representation (Section 4.5.5).

### 1.4 Structure of the Thesis

This thesis consists of four main chapters and is organized as follows:

- Chapter 2 gives a technical description of the dynamic binary instrumentation platform we developed for our work. It contains mostly technical details and can be skipped on a first read.

- Chapter 3 describes the bottleneck analysis algorithm and the CPU performance reverseengineering tool.

- Chapter 4 presents our data dependence driven tool for giving optimization feedback.

- Finally, Chapter 5 concludes the thesis, giving a summary of the contributions and perspectives on possible future work.

# CHAPTER 2

## Dynamic Binary Instrumentation with QEMU

| Contents |                                       |

|----------|---------------------------------------|

| 2.1      | QEMU                                  |

| 2.2      | The Tiny Code Generator               |

| 2.3      | The TCG Plugin Infrastructure         |

| 2.4      | Execution Tracing with QEMU           |

|          | 2.4.1 Control-flow tracing            |

|          | 2.4.2 Data Dependence Tracing         |

|          | 2.4.3 Value tracing                   |

| 2.5      | Evaluation of the Overhead of Plugins |

| 2.6      | Related Work                          |

| 2.7      | Conclusion and Perspectives           |

Preliminary note: this chapter is very technical and describes the internals of some analyses on which techniques presented later in the thesis are based. This chapter does not necessarily present any novel approaches by itself, but gives the general technical context of the thesis. As a consequence, it is possible to skip it at first reading.

This chapter describes the internals of the QEMU CPU emulator and TCG plugin infrastructure (TPI), an infrastructure for building dynamic binary program analysis tools based on QEMU. It also gives a general overview over the field of dynamic binary translation and also show cases a number of analyses we have implemented using TPI. The chapter is intended to both show how TPI works in practice as well as to present some basic techniques which are used later throughput the thesis.

## 2.1 **QEMU**

QEMU [17, 166] is a processor emulator based on dynamic binary translation. That is, it allows running programs written for one CPU architecture on a different CPU architecture. QEMU only reproduces the functional aspects of a CPU, meaning it emulates the instruction set architecture (ISA). It does not, however, match the non-functional microarchitectural details of an architecture such as timing, cache effects, or speculative execution.

Vanilla QEMU only allows running programs on a different CPU architecture than the one they where written for. ONe can, for example, run a program compiled for a 64 bit x86 CPU on a 32 bit ARM computer, and vice versa. The machine code of the emulated program is translated and run as native machine code for the architecture QEMU is running on. This makes emulation relatively fast compared to interpreter based systems like GEM5 [23].

For the purposes of this work we use a modified version of QEMU [84] that includes TPI which makes it possible to alter programs as they execute. We chose to use QEMU for this since it can emulate a plethora of different CPU architectures and supports all major operating systems (OSs), including GNU/Linux, \*BSD, Mac OS X and Windows. QEMU furthermore has a simple, more or less architecture independent, intermediate representation (tiny code generator (TCG) IR). This makes it easy to write analysis tools that work at the level of machine code but are still portable across different system. Details of how this works will be presented in Section 2.3, for now we will focus on presenting QEMU itself.

QEMU internally uses the following terminology, which we will reuse:

- Host CPU/OS: the CPU and OS on which QEMU is running.

- Guest program/OS: the program/OS you run inside QEMU.

- Guest CPU or virtual CPU: The state of a CPU core as emulated by QEMU.

QEMU can be run under two different modes: full system mode and user mode. Full system mode emulates a whole computer, including the CPU and peripherals such as network cards or hard disks. This means a whole operating system, including a kernel, is running on the simulated machine inside QEMU. This is similar to what sytems like VirtualBox [57] or Bochs [126] provide, but they can only run x86 programs on x86 hosts. User mode runs a single user space process and translates the machine code from the guest ISA to the host ISA. Under this mode QEMU runs a program compiled for one CPU architecture as a process in an operating system for another architecture. To make this possible QEMU translates system calls to the ABI of the host kernel. All the work done in this thesis has used QEMU in user mode, but it could easily be modified to support full system mode.

## 2.2 The Tiny Code Generator

The TCG is the component of QEMU responsible for translating guest machine instructions to host machine instructions. TCG is essentially a just-in-time compiler (JIT) compiler that takes real machine code as input instead of byte code.

Since TCG is a JIT it translates a program piece by piece at runtime. As a consequence the execution of code and its compilation are interleaved. That is, when a program tries to run a sequence of guest instructions the emulated guest CPU is halted and TCG translates the code to host instructions. Once TCG has finished compiling the emulation resumes by executing the new native code on the host. In the following we will refer to the moments when emulation is halted and TCG takes over as translation time and the moments when the code of the emulated program is running as execution time.

TCG is essentially a trace based JIT [150]. That is to say, it does not translate whole programs or functions at a time but only works on small linear sequences of guest instructions called *trace blocks*. These trace blocks are formed from the guest program using a very simple mechanism. Whenever the guest CPU executes an instruction that has not been translated yet a new trace block is started. This first instruction of the trace block is referred to as its *entry*. QEMU then parses the guest instructions following the entry until it hits a branch instruction <sup>1</sup>. The final trace block then contains the entry, the terminating branch and all instructions in between. Note that instructions in the guest program that are never executed are also never translated by TCG.

Since we are using QEMU in user mode kernel space instructions are not visible to TCG. When guest code performs a system call this is translated to a corresponding system call on the host system. Instructions that perform a system call, i.e. sysenter and syscall on x86, still are considered trace block terminators. They do not, however, change the program counter of the virtual CPU and the emulated execution simply falls through to the next guest instruction once the system call has finished.

Due to the way trace blocks are constructed they are very similar the basic blocks of the guest binary. That is

- a trace block has only one entry,

- a trace block has only one exit, <sup>2</sup>

- and consequently once a trace block has been entered all instructions in it are executed exactly once, in order.

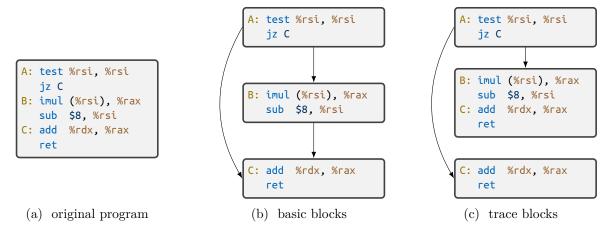

The important difference to the original guest basic blocks is that trace blocks can overlap, i.e. that a given guest instruction can be contained in multiple trace blocks. This happens for example if guest code branches to an instruction which is in the middle of another trace block that has already been translated. The only restriction being that an instruction can only be the entry for one trace block. An illustrative example showing how a piece of code is divided into basic blocks and trace blocks can be seen in Figure 2.1.

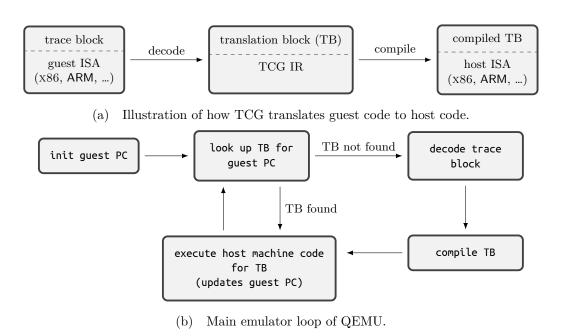

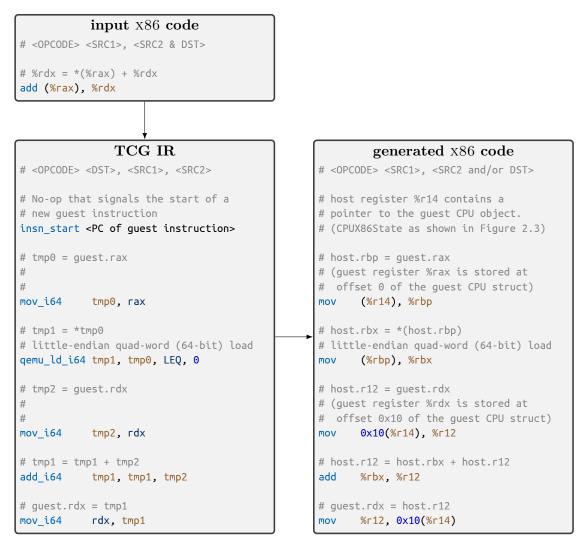

Internally, TCG does not directly translate the guest instructions in a trace block to host instructions. Instead it first translates traces to a more machine independent IR. Finally, the IR is then translated to machine instructions that can be executed directly on the host. The sequence instructions generated for a whole trace block is called a translation block (TB). This process is illustrated in Figure 2.2a.

TCG IR consists of simple RISC-like instructions working on registers and memory addresses. The IR distinguishes between registers of the simulated guest CPU and virtual registers in the

<sup>&</sup>lt;sup>1</sup>QEMU also terminates trace blocks before it finds a branch if the trace block is too long or if the guest instructions would span two pages in memory

<sup>&</sup>lt;sup>2</sup>like many other compilers QEMU is actually not very strict about this. Instructions that can fault, like memory accesses or division, are not considered block terminators.

Figure 2.1-A piece of x86 assembler in AT&T syntax and how it is divided into basic blocks and trace blocks. Note that B: and C are split into two basic blocks since C is the target of a branch. However, B and C form a single trace block since B does not end in a branch. There is a separate trace block containing only C which is created when the branch at the end of A is taken.

Figure 2.2 – High-level view of CPU emulation with QEMU.

IR used to hold intermediate values. It also uses distinct instructions to access memory of the guest CPU and the host memory used for QEMU's internal data structures. There are likewise distinct opcodes for branches inside a TB and for branches that leave the current TB.

TCG IR is typed using a very simple type system. The only types are 32 and 64 bit integers and pointers. Very recently, 128 and 256 bit vector types where added too. But notably there are no types to represent floating point values.

During emulation the state of the guest CPU is represented as an object in the heap of the QEMU process. For example, an x86 CPU has 16 general purpose 64 bit registers and so the CPU object for x86 guests contains an array with 16 64 bit integers. An excerpt of the definition of the structure used to represent x86 guest CPUs can be seen in Figure 2.3. Since the registers of the guest CPU reside in host memory every use of a register in a guest program is translated to a host memory access reading a field of the guest CPU object. Likewise, a write to

Figure 2.3 - C structure representing the state of an emulated x86 CPU in QEMU.

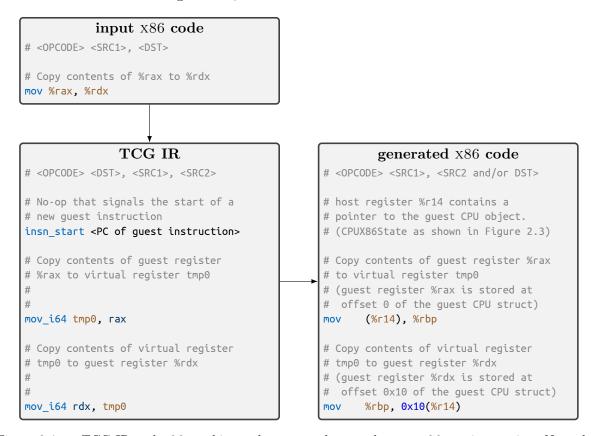

a guest register becomes a host memory write. An example of how TCG translates a simple x86 instruction that illustrates all this can be seen in Figure 2.4. To reduce the overhead introduced by these memory accesses TCG actually avoids inserting redundant loads and stores. Inside a TB it keeps the contents of guest CPU registers in host registers as much as possible and only flushes them back to host memory at the end of the block. This optimization is especially important for flag registers, like x86 condition codes, which are updated by most instructions but only read by a few.

TCGs IR is very simple, thus even translating a single guest machine instruction generates multiple IR instructions. Since real machine instructions can have quite complex behaviour the IR instructions for a single machine instruction can be a control flow graph (CFG) with loops and conditional branches. Fortunately, the CFG of the IR generated for a single guest instruction still is relatively simple though and follows some restrictions. That is, it only has one entry, and for any instruction, except for some branch instructions, it only has one exit. While TCG does perform some simple optimizations, such as simple dead code elimination and copy propagation passes, to clean up the IR before translating it, it is not an optimizing compiler.

Some complex instructions, such as those for handling system calls or exceptions, are not implemented directly as TCG IR instructions. Instead they are translated to calls to short functions implemented in C called helper functions

Since TCG IR does not have any floating-point types or instructions all guest machine instructions working with floating point numbers are translated to calls to helper functions written in C. Obviously these helper functions cannot directly accept floating-point values as arguments, since TCG IR has no way to represent them. Instead their arguments are passed to them as pointers to the host memory representing the guest CPU floating-point registers as arguments. This can be a source of significant performance overhead when running floating-point heavy programs in QEMU.

Quite recently vector types and instructions working on them have been added to TCGs IR. The current version of these instructions are relatively limited and only allow working with vectors of integer values. TCG instructions to accesses guest memory are also still limited to at most 64 bits. Consequently all guest vector loads and stores are split up into multiple load/store instructions in the IR. For the moment vector IR is not yet widely used throughout QEMU. In fact, only the ARM guest currently generates vector IR instructions for some vector guest instructions. Guest vector instructions of other platforms are still translated either to sequences of multiple scalar IR instructions or to calls of helper functions.

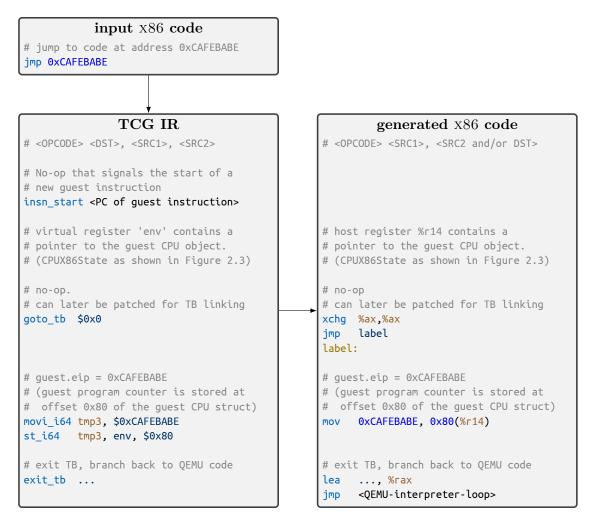

As shown in Figure 2.2b once a TB has finished executing in returns to the main emulator loop, which then looks up the next TB to run. To avoid the overhead of this lookup for every branch in the guest program, QEMU performs a dynamic optimization called *block chaining*.

When QEMU dynamically detects that a TB always branches to the same successor it patches a jump instruction into the host machine code for the TB. So, instead of exiting to the main emulator loop the first TB will directly branch to the code of the successor TB. This optimization allows QEMU to spend most of its time in generated machine code and to only exit to the main loop to translate new trace blocks or handle special events like interrupts

In user mode QEMU has spawns one OS thread per thread in the guest program where each OS thread has its own virtual CPU object. Therefore, the guest program can truly execute code concurrently. To ensure that the memory ordering rules of the guest ISA are respected by the host processor TCG inserts special memory barrier instructions wherever necessary [58]. Due to the way threads are emulated a guest CPU will have has at most as many cores running simultaneously as the host CPU. An accurate simulation of a highly parallel guest architecture on a less parallel host is therefore not possible.

Examples of how QEMU translates some simple x86 instructions to TCG IR and then back to x86 code are shown in Figures 2.4, 2.5 and 2.6.

Figure 2.4 – TCG IR and x86 machine code generated to emulate an x86 mov instruction. Note that the operand order in x86 and TCG IR is reversed.

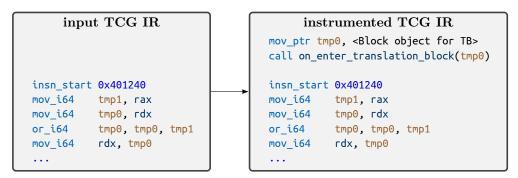

## 2.3 The TCG Plugin Infrastructure

As mentioned before the work presented in this thesis is not based on the main version of QEMU, but on a modified version [84, 85]. This modified QEMU has a mechanism for loading plugins, called the TCG plugin infrastructure (TPI), that can both observe and alter the translation process of TCG. To instrument a binary a plugin injects TCG IR instructions into TBs before they get translated back to host machine code. Since plugins operate at the IR level and not at the machine code level it is relatively easy to port plugins so they work with different guest

Figure 2.5 – TCG IR and x86 machine code generated to emulate an x86 add instruction (the IR to update the guest status flag register is omitted). Note that the operand order in x86 and TCG IR is reversed.

CPU architectures. Simple plugins whose behaviour does not depend on the exact semantics of guest instructions can work with multiple different guest ISA without any modification.

Even though a plugin can insert arbitrary code into the guest program the bulk of our instrumentation is not in TCG IR, but in C and C++. Instead of generating large amounts of IR we insert only small snippets that call the instrumentation functions. Even though this incurs some overhead we have chosen this approach to speed up the development process, since it is much easier to write in C/C++ than in the low level TCG IR.

Certain features of the design of QEMU and TCG incidentally work together to ease the development of plugins. TCG IR enforces a certain separation between host memory and guest memory, since it uses different opcodes to work with the one or the other. This means that the IR emitted can freely use separate virtual registers and does not have to take care not to accidentally clobber resources of the guest program. Guest programs also have no way of accessing the registers and memory of the plugin, meaning a faulty guest cannot cause faults in the emulator. Furthermore, temporary registers in TCG IR are distinct from guest machine registers, meaning one can freely insert code at any place without having to spill or restore values in and out of memory explicitly. TCGs register allocator automatically takes care of this.

Figure 2.6 – TCG IR and x86 machine code generated to emulate a x86 jmp instruction. Note that the operand order in x86 and TCG IR is reversed.

A TPI plugin is simply a shared library which QEMU loads into memory on startup, before it even starts emulating the guest program. TPI offers a C API allowing plugins to register callback functions which are then called whenever certain events occur. Most of these events are related to the translation of guest instructions to TCG IR. There are, for example, events that signal that TCG has started or finished constructing a new TB, and also events that signal that TCG has started or finished decoding a guest machine instruction. Whenever such a callback is called the plugin can then choose to insert new IR instructions into the TB, or alter the existing ones. A short excerpt of the plugin API is shown in Figure 2.7

TCG decodes trace blocks, i.e., it generates all IR instructions in a TB, in one pass. Virtual registers are not in static single assignment (SSA) form [174], and instead are reused as much as possible to reduce memory consumption of TCG itself during translation. Consequently, a TPI plugin written using only callbacks must emit its instrumentation directly as TCG emits its IR or take care not to clobber virtual registers. As TPI only provides this event based API instrumentation plugins have to be written as a state machine or in continuation passing style.

Since TCG IR generates multiple IR instructions even for the simplest guest instruction writing plugins that maintain state across a TB can quickly become quite tedious. To make writing plugins easier we have developed a thin C++ API wrapper around the original TPI API that allows working with TCG IR in a more straightforward fashion. It allows plugins to work

```

struct TPIOpCode;

// a single TCG IR instruction

struct Translation Block;

/// Object representing the state of a plugin.

/// Contains callbacks that will be called by TPI.

struct TCGPluginInterface {

// Called whenever TCG is about to start decoding a new trace block.

// IR for trace will be stored in 'tb'.

void (*before_decode_first_instr)(const TCGPluginInterface *tpi,

const TranslationBlock *tb);

/// Called whenever TCG has finished decoding a trace block.

void (*after_decode_last_instr)(const TCGPluginInterface *tpi,

const TranslationBlock *tb);

/// Called whenever TCG is about to decode the next instruction of

/// the current trace block.

void (*before_decode_instr)(const TCGPluginInterface *tpi, uint64_t pc);

/// Called whenever TCG has inserted a new IR instruction into

/// the current translation block.

void (*after_gen_opc)(const TCGPluginInterface *tpi, const TPIOpCode *opcode);

};

```

Figure 2.7 – Core events of the TPI C API

with the IR for an entire TB at once and to perform multiple passes over the IR and to insert code at any point in the TB. We have also wrapped TCGs routines for allocating and freeing virtual registers so a plugin author does not have to worry about overwriting registers used by the guest code itself.

TCG IR has control flow but does not directly represent basic blocks, it just has set\_label and branch to label instructions. Our IR layer also detects the basic blocks in a TB and makes it easy to iterate over successors and predecessors. However, the C++ TPI wrapper currently does not allow altering the control flow of a TB, i.e. it cannot change jump targets and also cannot insert or remove jumps.

## 2.4 Execution Tracing with QEMU

During this thesis we have developed different tools to perform high-level analyses on Executable and Linkable Format (ELF) [206] binaries. The input of these tools are traces of events describing different aspects of the execution of a program. This section describes three TPI plugins we have developed to trace a program's control-flow, data-dependencies and integer computations.

On a side note, we want to point out that execution traces of real world programs can become extremely large. So large, in fact, that realistically we cannot store entire traces in files. This can be illustrated with a little thought experiment. A modern CPU runs at a frequency of several GHz, meaning every second it can execute billions of instructions. When tracing a small program that only runs for one second if one retains even only one byte of data for every instruction that is executed the resulting raw trace will already contain more than one gigabyte of data. Consequently, all plugins presented here are designed as libraries that produce streams of events which can be treated directly in memory. If necessary, for example for debugging or

verification purposes, partial traces can still be stored to a file.

#### 2.4.1 Control-flow tracing

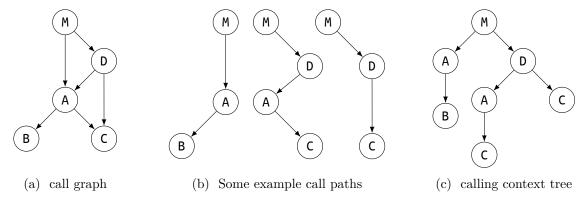

The control-flow tracing plugin we have developed observes the branches executed in a program and has the goal of distinguishing local control-flow inside a function and calls and returns between functions. This information can in turn be used to:

- Recover the interprocedural call graph (CG) and intraprocedural control flow graph (CFG) of a program and

- track the *calling-context*, that is a compact representation of the call stack, during execution.

Since portability, across CPU architectures as well as across languages, was one of our main concerns we took great efforts to make our plugin independent of platform and language ABIs. It does not inspect the call stack and only uses basic assumptions about branch instructions of a given architecture. This approach is also robust against of software stack unwinders as used, for example, for exception handling in C++.

The main problem with control-flow tracing is that, as mentioned earlier, binary machine code is much less structured than source code. The plethora of high-level control flow found in programs, like loops, conditionals, function calls, returns and exception handling, are all reduced down to a small number of branch instructions. On x86, for instance, all normal control flow is implemented using only call, ret, jmp and jcc. Hence, the machine code conflates at least some different types of control flow by implementing them using the same instructions. Compilers can also sometimes use different machine instructions to implement the same control flow construct depending on they context are used in, e.g., replacing calls with a cheaper jmp where possible. This means our plugin has to be able to detect the intended purpose of a branch instruction from the instructions immediately surrounding it and branch target.

Since the plugin needs to be able to distinguish different forms of guest branch instructions it cannot work solely at the level of TCG IR. To make it easier to port the plugin between different architectures the main part of the code works does not work directly with guest opcodes. Instead we map the different guest branch instructions to a reasonably small set of abstract terminator types shown in Figure 2.10. Thanks to this only a small part of the plugin that is responsible for categorizing guest instructions is architecture dependent. The majority of the code and also all the instrumentation we generate does not need to be changed to support new platforms.

In practice, local branches inside functions are mostly regular and easy to handle. The main problems arise when trying to handle calls and returns between functions. For example, the "normal" way to translate a function call in C is using the call instruction. But this is by far not only way that function calls are actually implemented. The most commonly occurring alternative implementation, tail call optimization, which has already been mentioned, uses jmp instructions instead, which are normally used for control-flow inside a function. But there are also other, more exotic, ways to implement function calls. In highly hand optimized assembly code, as can be found in the GNU C standard library, there are cases where a function call occurs via fall-through, i.e., without any branch instructions. An example of this can be seen in Figure 2.8. Another reason why interprocedural control flow is more difficult to handle is that in modern code bases using virtual function dispatch and function pointers or lambda expressions indirect branches are much more common. In general it is not possible to statically detect the target of such indirect branches meaning we have no information about the target of the branch before actually executing the branch.

There are also cases where call instructions are used for other purposes than function calls. On pre 64 bit x86 CPUs there is no direct support for RIP relative addressing, which is necessary for writing position independent code. One idiom used to work around this is show in Figure 2.9.

```

000000000149cd0 <__strcasecmp_ssse3>:

149cd0:

f3 Of 1e fa

endbr64

48 8b 05 e5 60 07 00

149cd4:

mov

0x760e5(%rip), %rax

64 48 8b 10

149cdb:

MOV

%fs:(%rax), %rdx

0f 1f 44 00 00

149cdf:

nopl

0x0(%rax, %rax, 1)

66 66 2e 0f 1f 84 00

data16 nopw %cs:0x0(%rax, %rax, 1)

149ce4:

149ceb:

00 00 00 00

149cef:

90

← fall-through!

non

000000000149cf0 <__GI___strcasecmp_l_ssse3>:

f3 Of 1e fa

149cf0:

149cf4:

48 8b 02

(%rdx), %rax

mov

f7 80 78 02 00 00 01

149cf7:

testl $0x1, 0x278(%rax)

00 00 00

149cfe:

Of 85 d9 ba f5 ff

149d01:

a57e0 <__strcasecmp_l_nonascii>

ine

%esi, %ecx

149d07:

89 f1

mov

89 f8

%edi, %eax

149d09:

mov

149d0b:

48 83 e1 3f

$0x3f, %rcx

and

149d0f:

48 83 e0 3f

$0x3f, %rax

and

. . .

. . .

```

Figure 2.8 — Example of a function call by fall-through. As seen in glibc 2.28.30 (Fedora 29) in x86 (AT&T syntax). \_\_strcasecmp\_ssse3 (an optimized version of strcasecmp using x86 SSSE3 [54] instructions) does not end in a branch instruction. Instead execution will always fall-through to \_\_GI\_\_\_strcasecmp\_l\_ssse3 (another optimized variant of strcasecmp).

```

call here

here: pop %rax

# %rax now contains the absolute address of `here'

```

Figure 2.9 - 32 bit x86 assembly code to obtain the value of the program counter (AT&T syntax).

It consists of a **call** instruction that jumps zero bytes away, that is, it only pushes the value of the program counter in the stack and falls through to the next instruction Even though this uses a call instruction it is not an actual function call and is never returned from.