## Méthodologie et développement de solutions pour la sécurisation des circuits numériques face aux attaques en tensions

Kamil Gomina

#### ▶ To cite this version:

Kamil Gomina. Méthodologie et développement de solutions pour la sécurisation des circuits numériques face aux attaques en tensions. Autre. Ecole Nationale Supérieure des Mines de Saint-Etienne, 2014. Français. NNT: 2014EMSE0751. tel-02917966

### HAL Id: tel-02917966 https://theses.hal.science/tel-02917966v1

Submitted on 20 Aug 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

NNT: 2014 EMSE 0751

### THÈSE

présentée par

#### Kamil GOMINA

pour obtenir le grade de Docteur de l'École Nationale Supérieure des Mines de Saint-Étienne

Spécialité : Microélectronique

# METHODOLOGIE ET DEVELOPPEMENT DE SOLUTIONS POUR LA SECURISATION DES CIRCUITS NUMERIQUES FACE AUX ATTAQUES EN TENSION

Soutenue à Gardanne, le 11 septembre 2014

#### Membres du jury

Rapporteurs: Régis LEVEUGLE Professeur, TIMA, Grenoble

Bruno ROUZEYRE Professeur, LIRMM, Montpellier

Directeur de thèse : Assia TRIA Ingénieur de recherche, CEA-TECH, Gardanne

Président du jury : Jean-Michel PORTAL Professeur, IM2NP, Marseille

Examinateurs: Jean-Baptiste RIGAUD Maitre-assistant, ENSM-SE, Gardanne

Philippe GENDRIER Ingénieur, STMicroelectronics, Crolles

Invité Philippe CANDELIER Ingénieur, STMicroelectronics, Crolles

Responsables:

se · Spácialitá

Spécialités doctorales Responsables

SCIENCES ET GENIE DES MATERIAUX K. Wolsk

MECANIQUE ET INGENIERIE S. Drapier

GENIE DES PROCEDES F. Gruy,

SCIENCES DE LA TERRE B. Guy, I

SCIENCES ET GENIE DE L'ENVIRONNEMENT D. Graille

K. Wolski Directeur de recherche S. Drapier, professeur F. Gruy, Maître de recherche B. Guy, Directeur de recherche D. Graillot, Directeur de recherche MATHEMATIQUES APPLIQUEES

INFORMATIQUE

O. Boissier, Professeur

IMAGE, VISION, SIGNAL

GENIE INDUSTRIEL

MICROELECTRONIQUE

O. Roustant, Maître-assistant

O. Boissier, Professeur

JC. Pinoli, Professeur

A. Dolgui, Professeur

S. Dauzere Peres, Professeur

| EMSE : Enseignants-chercheurs et chercheurs autorisés à diri |  |

|--------------------------------------------------------------|--|

|                                                              |  |

|                                                              |  |

| ABSI               | Nabil         | CR                     |                                                     | CMP   |

|--------------------|---------------|------------------------|-----------------------------------------------------|-------|

| AVRIL              | Stéphane      | PR2                    | Mécanique et ingénierie                             | CIS   |

| BALBO              | Flavien       | PR2                    | 1 0                                                 | FAYOL |

| BASSEREAU          | Jean-François | PR                     |                                                     | SMS   |

| BATTON-HUBERT      | Mireille      | PR2                    | Sciences et génie de l'environnement                | FAYOL |

| BERGER DOUCE       | Sandrine      | PR2                    | •                                                   | FAYOL |

| BERNACHE-ASSOLLANT | Didier        | PR0                    | Génie des Procédés                                  | CIS   |

| BIGOT              | Jean Pierre   | MR(DR2)                | Génie des Procédés                                  | SPIN  |

| BILAL              | Essaid        | DR                     | Sciences de la Terre                                | SPIN  |

| BOISSIER           | Olivier       | PR1                    | Informatique                                        | FAYOL |

| BORBELY            | Andras        | MR(DR2)                | Sciences et génie des matériaux                     | SMS   |

| BOUCHER            | Xavier        | PR2                    | Génie Industriel                                    | FAYOL |

| BRODHAG            | Christian     | DR                     | Sciences et génie de l'environnement                | FAYOL |

| BRUCHON            | Julien        | MA(MDC)                | Mécanique et ingénierie                             | SMS   |

| BURLAT             | Patrick       | PR2                    | Génie Industriel                                    | FAYOL |

| COURNIL            | Michel        | PR0                    | Génie des Procédés                                  | DIR   |

| DARRIEULAT         | Michel        | IGM                    | Sciences et génie des matériaux                     | SMS   |

| DAUZERE-PERES      | Stéphane      | PR1                    | Génie Industriel                                    | CMP   |

| DEBAYLE            | Johan         | CR                     | Image Vision Signal                                 | CIS   |

| DELAFOSSE          | David         | PR1                    | Sciences et génie des matériaux                     | SMS   |

| DESRAYAUD          | Christophe    | PR2                    | Mécanique et ingénierie                             | SMS   |

| DOLGUI             | Alexandre     | PR0                    | Génie Industriel                                    | FAYOL |

| DRAPIER            | Sylvain       | PR1                    | Mécanique et ingénierie                             | SMS   |

| FEILLET            | Dominique     | PR2                    | Génie Industriel                                    | CMP   |

| FEVOTTE            | Gilles        | PR1                    | Génie des Procédés                                  | SPIN  |

| FRACZKIEWICZ       | Anna          | DR                     | Sciences et génie des matériaux                     | SMS   |

| GARCIA             | Daniel        | MR(DR2)                | Génie des Procédés                                  | SPIN  |

| GERINGER           | Jean          | MA(MDC)                | Sciences et génie des matériaux                     | CIS   |

| GOEURIOT           | Dominique     | DR                     | Sciences et génie des matériaux                     | SMS   |

| GRAILLOT           | Didier        | DR                     | Sciences et génie de l'environnement                | SPIN  |

| GROSSEAU           | Philippe      | DR                     | Génie des Procédés                                  | SPIN  |

| GRUY               | Frédéric      | PR1                    | Génie des Procédés                                  | SPIN  |

| GUY                | Bernard       | DR                     | Sciences de la Terre                                | SPIN  |

| HAN                | Woo-Suck      | CR                     | Mécanique et ingénierie                             | SMS   |

| HERRI              | Jean Michel   | PR1                    | Génie des Procédés                                  | SPIN  |

| KERMOUCHE          | Guillaume     | PR2                    | Mécanique et Ingénierie                             | SMS   |

| KLOCKER            | Helmut        | DR                     | Sciences et génie des matériaux                     | SMS   |

| LAFOREST           | Valérie       | MR(DR2)                | Sciences et génie de l'environnement                | FAYOL |

| LERICHE            | Rodolphe      | CR                     | Mécanique et ingénierie                             | FAYOL |

| LI                 | Jean-Michel   |                        | Microélectronique                                   | CMP   |

| MALLIARAS          | Georges       | PR1                    | Microélectronique                                   | CMP   |

| MOLIMARD           | Jérôme        | PR2                    | Mécanique et ingénierie                             | CIS   |

| MONTHEILLET        | Frank         | DR                     | Sciences et génie des matériaux                     | SMS   |

| MOUTTE             | Jacques       | CR                     | Génie des Procédés                                  | SPIN  |

| NEUBERT            | Gilles        |                        |                                                     | FAYOL |

| NIKOLOVSKI         | Jean-Pierre   |                        |                                                     | CMP   |

| NORTIER            | Patrice       | PR1                    |                                                     | SPIN  |

| PIJOLAT            | Christophe    | PR0                    | Génie des Procédés                                  | SPIN  |

| PIJOLAT            | Michèle       | PR1                    | Génie des Procédés                                  | SPIN  |

| PINOLI             | Jean Charles  | PR0                    | Image Vision Signal                                 | CIS   |

| POURCHEZ           | Jérémy        | CR                     | Génie des Procédés                                  | CIS   |

| ROBISSON           | Bruno         |                        |                                                     | CMP   |

| ROUSSY             | Agnès         | MA(MDC)                |                                                     | CMP   |

| ROUSTANT           | Olivier       | MA(MDC)                |                                                     | FAYOL |

| ROUX               | Christian     | PR                     |                                                     | CIS   |

| STOLARZ            | Jacques       | CR                     | Sciences et génie des matériaux                     | SMS   |

| TRIA               | Assia         | Ingénieur de recherche | Microélectronique                                   | CMP   |

| VALDIVIESO         | François      | MA(MDC)                | Sciences et génie des matériaux                     | SMS   |

| VIRICELLE          | Jean Paul     | MR(DR2)                | Génie des Procédés                                  | SPIN  |

| WOLSKI             | Krzystof      | DR                     | Sciences et génie des matériaux                     | SMS   |

| XIE                | Xiaolan       | PR1                    | Génie industriel                                    | CIS   |

| YUGMA              | Gallian       | CR                     | Génie industriel                                    | CMP   |

|                    |               |                        | octorat (titulaires d'un doctorat d'État ou d'une l |       |

| DEDGHEAII          | Joan Michal   | DI I                   | Máganique et Ingánicaio                             | ENICE |

| ENISE:    | Enseignants-chercheurs et cherche | eurs autorisés à diriger des thèses de d | octorat (titulaires d'un doctorat d'État ou d'u | ne HDR) |

|-----------|-----------------------------------|------------------------------------------|-------------------------------------------------|---------|

| BERGHEAU  | Jean-Michel                       | PU                                       | Mécanique et Ingénierie                         | ENISE   |

| BERTRAND  | Philippe                          | MCF                                      | Génie des procédés                              | ENISE   |

| DUBUJET   | Philippe                          | PU                                       | Mécanique et Ingénierie                         | ENISE   |

| FEULVARCH | Eric                              | MCF                                      | Mécanique et Ingénierie                         | ENISE   |

| FORTUNIER | Roland                            | PR                                       | Sciences et Génie des matériaux                 | ENISE   |

| GUSSAROV  | Andrey                            | Enseignant contractuel                   | Génie des procédés                              | ENISE   |

| HAMDI     | Hédi                              | MCF                                      | Mécanique et Ingénierie                         | ENISE   |

| LYONNET   | Patrick                           | PU                                       | Mécanique et Ingénierie                         | ENISE   |

| RECH      | Joël                              | PU                                       | Mécanique et Ingénierie                         | ENISE   |

| SMUROV    | Igor                              | PU                                       | Mécanique et Ingénierie                         | ENISE   |

| TOSCANO   | Rosario                           | PU                                       | Mécanique et Ingénierie                         | ENISE   |

| ZAHOUANI  | Hassan                            | PU                                       | Mécanique et Ingénierie                         | ENISE   |

## TABLE DES MATIÈRES

| Ta | able o | des ma  | atières                                               | j  |

|----|--------|---------|-------------------------------------------------------|----|

| Ta | able o | des fig | ures                                                  | v  |

| Li | ste d  | les tab | leaux                                                 | ix |

| In | trod   | uction  |                                                       | 1  |

| 1  | Mei    | naces e | et sécurisation des circuits intégrés numériques      | 3  |

|    | 1.1    | Aperç   | u des attaques visant les circuits numériques         | 4  |

|    |        | 1.1.1   | Attaques invasives                                    | 4  |

|    |        | 1.1.2   | Attaques non invasives                                | 6  |

|    |        |         | 1.1.2.1 Attaques par canaux auxiliaires               | 6  |

|    |        |         | 1.1.2.2 Les attaques actives                          | 10 |

|    |        | 1.1.3   | Attaques semi-invasives                               | 13 |

|    | 1.2    | Contro  | emesures                                              | 15 |

|    |        | 1.2.1   | Protection contre les attaques invasives              | 15 |

|    |        | 1.2.2   | Protection contre les attaques actives                | 15 |

|    |        |         | 1.2.2.1 Redondance matérielle                         | 16 |

|    |        |         | 1.2.2.2 Redondance temporelle                         | 16 |

|    |        |         | 1.2.2.3 Redondance d'information                      | 18 |

|    |        | 1.2.3   | Protection contre les attaques par canaux auxiliaires | 19 |

|    |        | 1.2.4   | Bilan                                                 | 19 |

|    | 1.3    | Exem    | ple de critères d'évaluation : les critères communs   | 20 |

|    |        | 1.3.1   | Cible de sécurité et profil de protection             | 20 |

|    |        | 1.3.2   | Exigences d'assurance de sécurité                     | 21 |

|    |        | 1.3.3   | Analyse des vulnérabilités et potentiel d'attaque     | 21 |

|    | 1.4    | 0       | ation de contremesures dans le flot de conception     | 24 |

|    |        | 1.4.1   | Méthodes de conception                                | 24 |

|    |        |         | 1.4.1.1 Utilisation de processeurs                    | 24 |

|    |        |         | 1.4.1.2 Logique programmable                          | 24 |

ii

|          |     |        | 1.4.1.3<br>1.4.1.4 | 1                                                    | 25<br>26 |

|----------|-----|--------|--------------------|------------------------------------------------------|----------|

|          |     | 1.4.2  | Contrain           | - "                                                  | 26       |

|          |     | 1.4.3  |                    |                                                      | 31       |

|          | 1.5 | Concl  |                    | 11                                                   | 32       |

| <b>2</b> | Att | aques  | passives           | en tension 3                                         | 5        |

|          | 2.1 | Conso  | mmation            | des circuits                                         | 6        |

|          |     | 2.1.1  | Étude th           | néorique de la consommation d'un circuit numérique 3 | 6        |

|          |     |        | 2.1.1.1            | Différents types de consommation                     | 6        |

|          |     |        | 2.1.1.2            | Influence des paramètres physiques                   | 9        |

|          |     | 2.1.2  | Évaluati           | on de la consommation                                | 0        |

|          |     |        | 2.1.2.1            | Types d'analyse                                      | 1        |

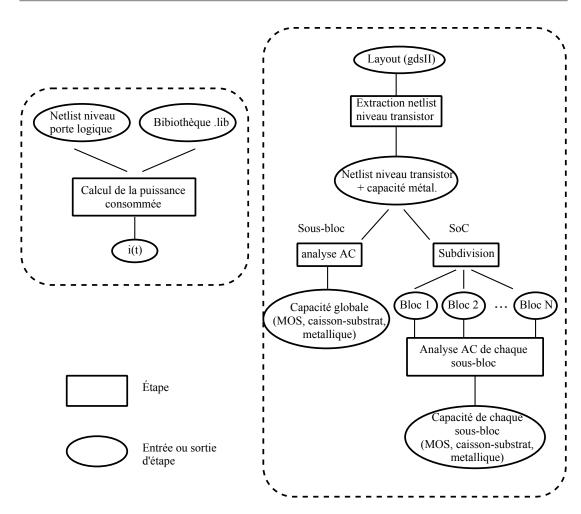

|          |     |        | 2.1.2.2            | Flot d'évaluation                                    | 2        |

|          |     | 2.1.3  | Bilan              |                                                      | 4        |

|          | 2.2 | Signat | ture de co         | nsommation électrique en phase de conception 4       | 5        |

|          |     | 2.2.1  | Intérêt d          | l'évaluer la signature                               | 5        |

|          |     | 2.2.2  | Niveaux            | hiérarchiques à considérer pour la signature         | 5        |

|          |     | 2.2.3  | Extraction         | on de la capacité de grille d'alimentation 4         | 6        |

|          |     |        | 2.2.3.1            | Capacités à extraire                                 | 6        |

|          |     |        | 2.2.3.2            | Méthodologie d'extraction                            | 7        |

|          |     | 2.2.4  | Modèle é           | équivalent de la signature en courant 5              | 4        |

|          |     |        | 2.2.4.1            | Présentation du modèle                               | 4        |

|          |     |        | 2.2.4.2            | Cas particuliers et paramètres additionnels 5        | 5        |

|          |     | 2.2.5  | Résultat           | s du modèle obtenu                                   | 6        |

|          |     |        | 2.2.5.1            | Paramètres expérimentaux                             | 6        |

|          |     |        | 2.2.5.2            | Résultats expérimentaux                              | 8        |

|          |     |        | 2.2.5.3            | Résultats de simulation                              | 9        |

|          |     |        | 2.2.5.4            | Comparaison et analyse                               | 1        |

|          | 2.3 | Évalu  | ation de c         | ontremesures à l'aide du modèle 6                    | 3        |

|          |     | 2.3.1  | Les catés          | gories de contremesure                               | 3        |

|          |     |        | 2.3.1.1            | Techniques de masquage                               | 3        |

|          |     |        | 2.3.1.2            | Techniques de dissimulation 6                        | 5        |

|          |     | 2.3.2  | Résultat           | s des modèles simulés                                | 9        |

|          |     |        | 2.3.2.1            | Masquage des données                                 | 9        |

|          |     |        | 2.3.2.2            | Capacités de découplage                              | 2        |

|          | 2.4 | Concl  | usion du c         | chapitre                                             | 4        |

| 3        | Att | aques  | actives e          | n tension 7                                          | 7        |

|          |     | -      |                    |                                                      | 8'       |

Table des matières iii

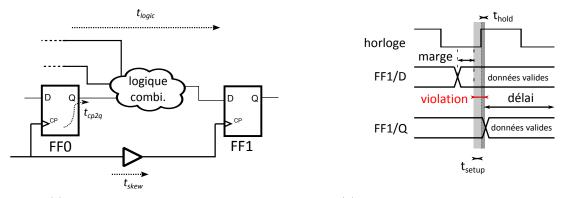

|        | 3.1.1   | Rappels théoriques                                                     | 8  |

|--------|---------|------------------------------------------------------------------------|----|

|        |         | 3.1.1.1 Contraintes temporelles de fonctionnement                      | 9  |

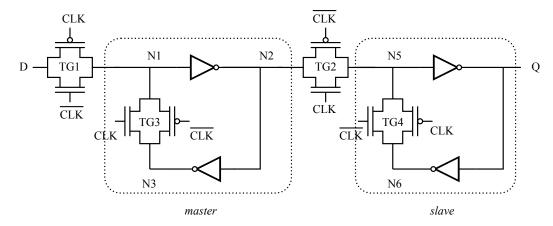

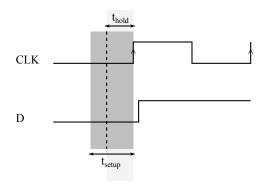

|        |         | 3.1.1.2 Définition des temps de $setup$ et $hold$ sur des bascules . 8 | 80 |

|        | 3.1.2   | Étude de l'impact de la variation de la tension sur la logique 8       | 31 |

|        |         | 3.1.2.1 Étude des temps de propagation 8                               | 32 |

|        |         | 3.1.2.2 Conséquence sur les paramètres des contraintes tempo-          |    |

|        |         | relles                                                                 | 86 |

|        |         | 3.1.2.3 Fonctionnement de la logique 8                                 | 88 |

|        | 3.1.3   | De la modification de tension à l'injection de fautes 9                | 0  |

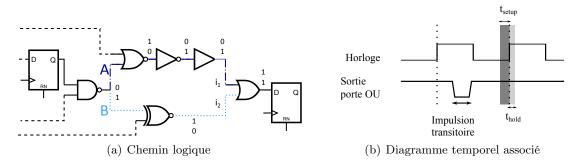

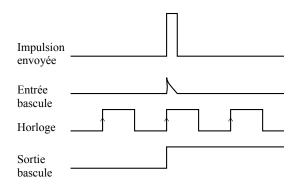

|        |         | 3.1.3.1 Violations de contraintes temporelles 9                        | 1  |

|        |         | 3.1.3.2 Impulsions transitoires à la sortie des portes combinatoires 9 | 1  |

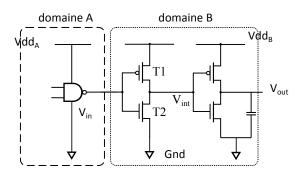

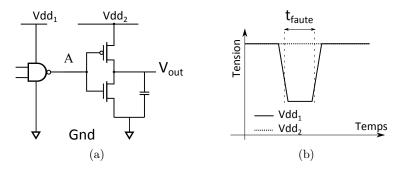

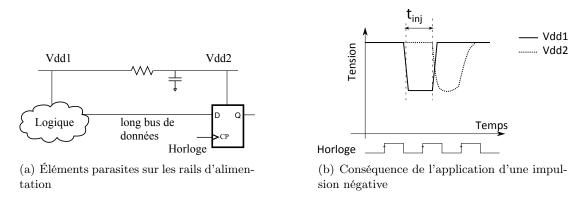

|        |         | 3.1.3.3 Cas de domaines d'alimentation séparés 9                       | 92 |

|        |         | 3.1.3.4 Autres phénomènes possibles 9                                  | 95 |

|        | 3.1.4   | Distribution temporelle des chemins dans la logique synchrone 9        | 7  |

|        |         | 3.1.4.1 Profil de distribution des chemins 9                           | 7  |

|        |         | 3.1.4.2 Paramètres modifiant la distribution temporelle 9              | 8  |

|        | 3.1.5   | Bilan                                                                  | 1  |

| 3.2    | Réalis  | ation de circuits de détection                                         | 1  |

|        | 3.2.1   | Travaux relatifs à la détection de violation de temps de $setup$ 10    | 12 |

|        | 3.2.2   | Principes de fonctionnement des circuits de détection 10               | 15 |

|        |         | 3.2.2.1 Description du fonctionnement                                  | 15 |

|        |         | 3.2.2.2 Détermination des marges de fonctionnement 10                  | 7  |

|        | 3.2.3   | Solutions étudiées                                                     | 19 |

|        |         | $3.2.3.1$ Convertisseur temporel vers numérique ( $TDC: Time\ to$      |    |

|        |         | $digital\ converter)$                                                  | .0 |

|        |         | 3.2.3.2 Circuits de détection                                          | 2  |

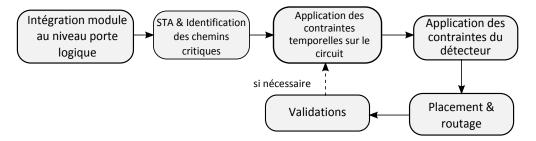

|        | 3.2.4   | Intégration des solutions                                              | 7  |

|        |         | 3.2.4.1 Implantation                                                   | 8  |

|        |         | 3.2.4.2 Vérification et caractérisation en phase de conception . 12    | 0  |

|        | 3.2.5   | Résultats des tests silicium                                           | 4  |

|        |         | 3.2.5.1 Dispositif expérimental                                        | 4  |

|        |         | 3.2.5.2 Procédure de test                                              | 6  |

|        |         | 3.2.5.3 Mesures et résultats                                           | 27 |

|        | 3.2.6   | Analyse et comparaison des mesures et des simulations 13               | 2  |

|        |         | 3.2.6.1 Comparaison avec les résultats théoriques                      | 2  |

|        |         | 3.2.6.2 Analyse des mesures                                            | 4  |

|        |         | 3.2.6.3 Comparaison des détecteurs                                     | 6  |

| 3.3    | Conclu  | sions                                                                  | 9  |

| Conclu | ısion g | énérale et perspectives 14                                             | 1  |

| iv                     | Table des matières |

|------------------------|--------------------|

| Glossaire              | 145                |

| Bibliographie          | 149                |

| Liste des publications | 161                |

# TABLE DES FIGURES

| 1.1  | Désassemblage du boîtier avec de l'acide nitrique [Kömmerling 1999]                  | 5  |

|------|--------------------------------------------------------------------------------------|----|

| 1.2  | Microcontrôleur Motorola MC68HC705C9A après gravure chimique                         |    |

|      | [Skorobogatov 2005]                                                                  | ٦  |

| 1.3  | Principe de l'attaque temporelle [Dhem 2000]                                         | 7  |

| 1.4  | Fonctionnement d'inverseur en technologie CMOS                                       | 7  |

| 1.5  | Analyse de courant simple de courant sur l'algorithme RSA [Selmane $2010$ ] .        | 8  |

| 1.6  | Les différents types d'impulsions sur les rails d'alimentation [Yanci $2008$ ]       | 12 |

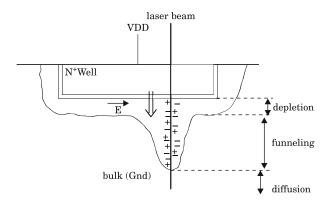

| 1.7  | Effet d'un faisceau laser sur une structure MOS [Roscian 2012]                       | 14 |

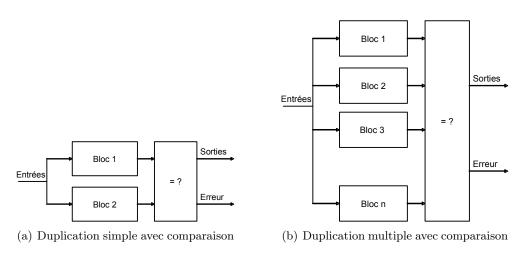

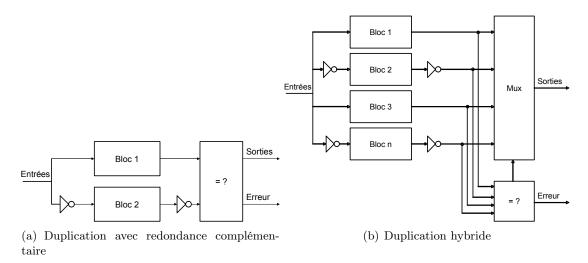

| 1.8  | Principe de la duplication simple et multiple                                        | 16 |

| 1.9  | Systèmes avancés de duplication                                                      | 17 |

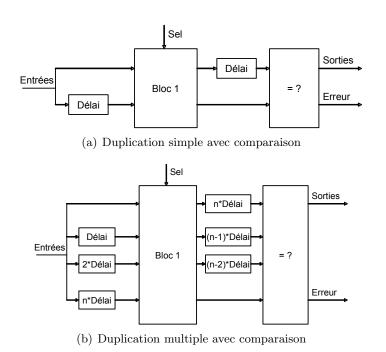

| 1.10 | Principe de la redondance temporelle simple et multiple                              | 17 |

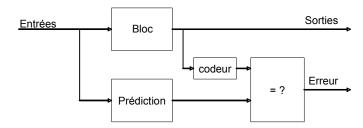

| 1.11 | Principe de fonctionnement d'un code détecteur d'erreur [Maingot 2009]               | 18 |

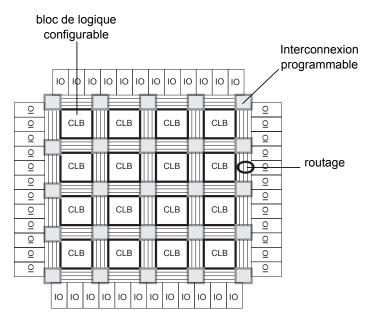

| 1.12 | Structure simplifiée d'un FPGA                                                       | 25 |

| 1.13 | Disposition des cellules standard dans un circuit                                    | 26 |

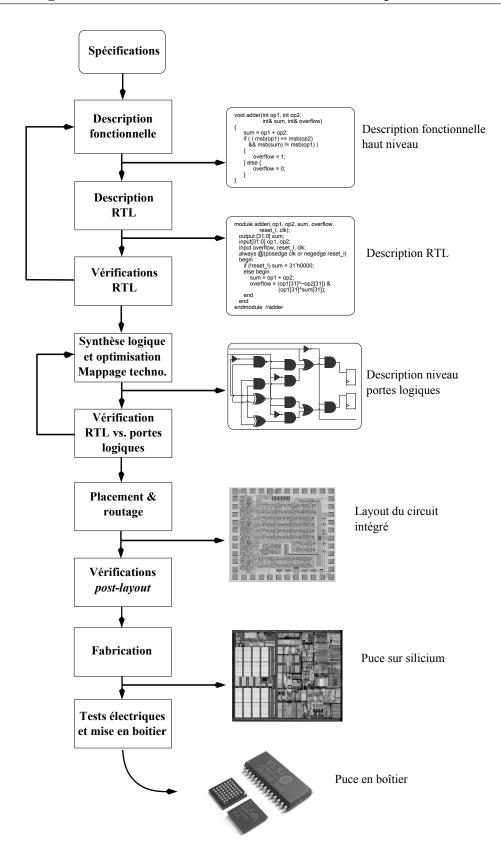

| 1.14 | Flot de conception numérique                                                         | 27 |

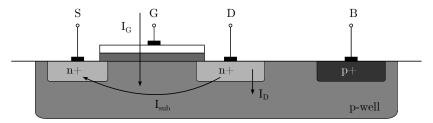

| 2.1  | Illustration des courants de fuite sur un transistor NMOS                            | 37 |

| 2.2  | Courant de court-circuit et de transition dans un inverseur CMOS $\dots$             | 38 |

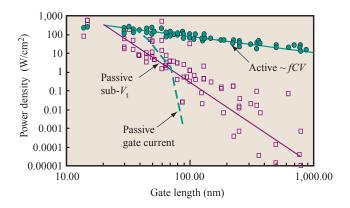

| 2.3  | Densité de puissance des composants CMOS en fonction de la taille de grille          |    |

|      | [Haensch 2006]                                                                       | 39 |

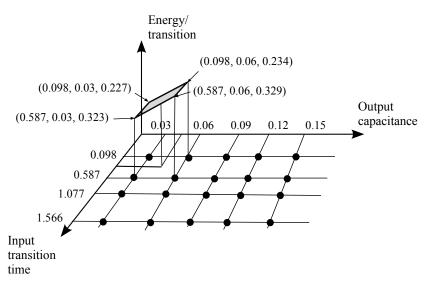

| 2.4  | Table de puissance dynamique de la sortie d'une cellule [Ope 2013]                   | 42 |

| 2.5  | Flot d'analyse dynamique de puissance                                                | 43 |

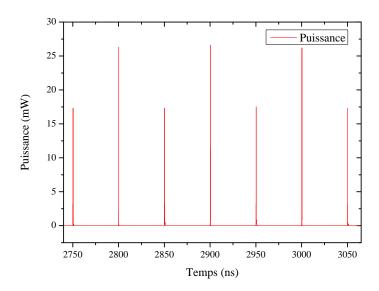

| 2.6  | Courbe de puissance obtenue avec $PrimeTime\ PX$                                     | 44 |

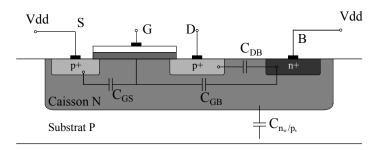

| 2.7  | Capacités du transistor MOS de type P $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 47 |

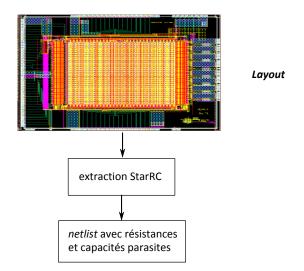

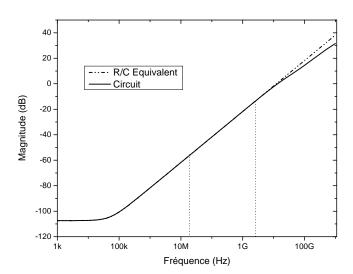

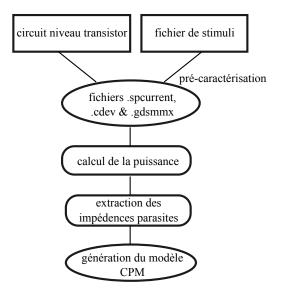

| 2.8  | Flot de génération des éléments parasites                                            | 48 |

| 2.9  | Analyse petit signal du courant traversant le circuit étudié et de son circuit       |    |

|      | équivalent                                                                           | 50 |

| 2.10 | Circuit équivalent en analyse petit signal                                           | 50 |

| 2.11 | Réseau de distribution d'alimentation et modèle simple de puissance d'un             |    |

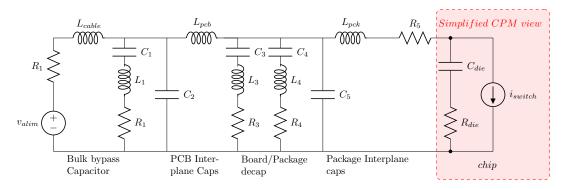

|      | circuit [Apa 2013]                                                                   | 52 |

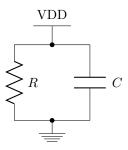

| 9 19 | flot de génération du modèle CPM                                                     | 59 |

| 2.13 | Modèle équivalent pour l'analyse de signature d'un circuit générique          | 55  |

|------|-------------------------------------------------------------------------------|-----|

| 2.14 | Dispositif expérimental                                                       | 57  |

| 2.15 | Courbes de consommation obtenues à l'oscilloscope                             | 58  |

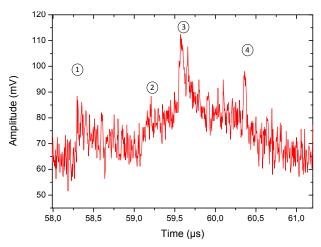

| 2.16 | Modèle électrique équivalent de l' <i>IP</i> étudiée                          | 59  |

| 2.17 | Signature de consommation donnée par le modèle électrique : les trois zones   |     |

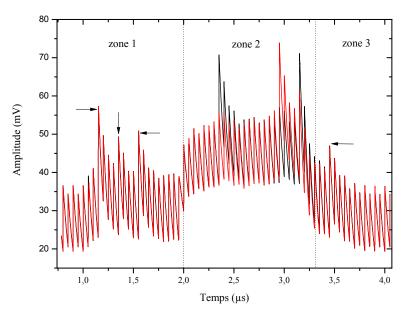

|      | représentent les différentes phases de l'opération                            | 60  |

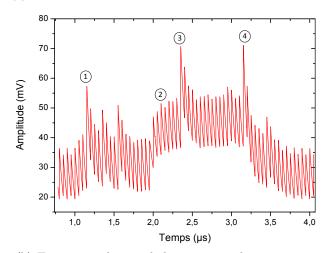

| 2.18 | Comparaison du modèle électrique et des mesures sur circuit                   | 62  |

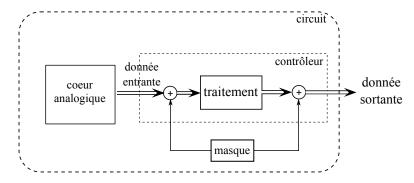

| 2.19 | Architecture du schéma de masquage implémenté                                 | 65  |

| 2.20 | Capacité de découplage intégrée dans les cellules standard                    | 68  |

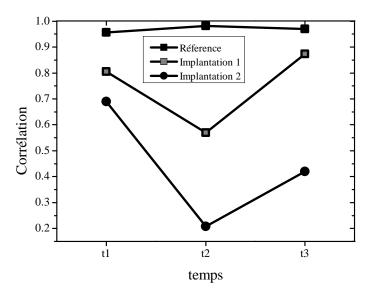

| 2.21 | Mesure de l'effet de masquage sur la corrélation entre la consommation et le  |     |

|      | poids de Hamming des données                                                  | 71  |

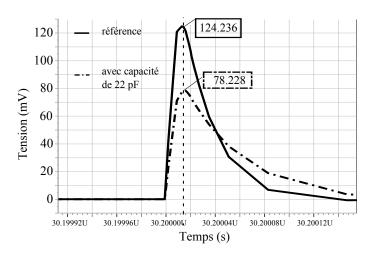

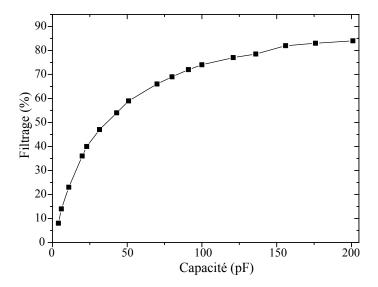

| 2.22 | Évaluation de l'atténuation de pics de courants avec des capacités de décou-  |     |

|      | plages intégrées                                                              | 73  |

| 2.23 | Lissage additionnel apporté par la capacité MIM                               | 73  |

| 2.24 | Résumé des étapes de construction du modèle électrique                        | 76  |

| 0.1  |                                                                               | 70  |

| 3.1  | Temps de propagation d'un chemin en logique synchrone                         | 79  |

| 3.2  | Bascule maître-esclave de type D                                              | 80  |

| 3.3  | Illustration d'un temps de <i>hold</i> négatif                                | 82  |

| 3.4  | Illustration des temps de propagation d'un inverseur CMOS                     | 82  |

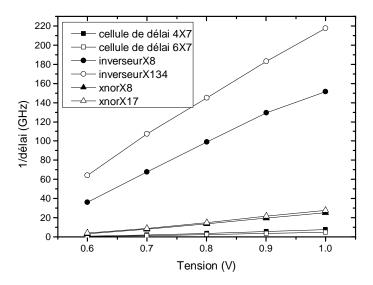

| 3.5  | Variation des temps de propagation pour différentes portes logiques           | 83  |

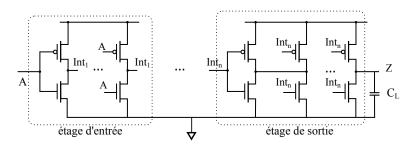

| 3.6  | Étages d'entrée et de sortie d'une porte logique                              | 85  |

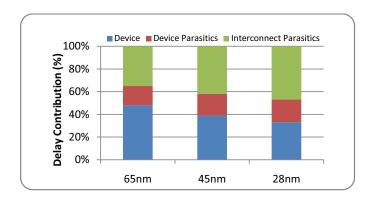

| 3.7  | Impact des éléments parasites pour des nœuds technologiques avancés           | 0.0 |

| 0.0  | [Shah 2009]                                                                   | 86  |

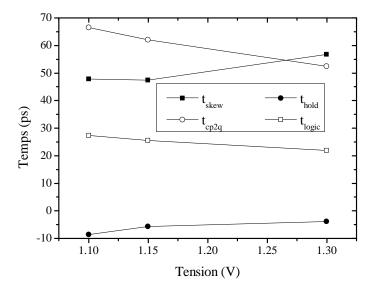

| 3.8  | Évolution des paramètres de la contrainte en hold sur un chemin               | 87  |

| 3.9  | Modification de la sortie d'un inverseur en présence d'une impulsion sur      | 00  |

| 0.10 | l'alimentation                                                                | 89  |

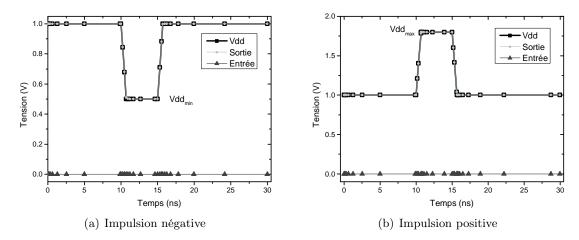

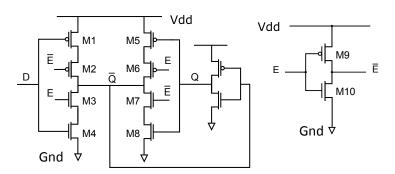

|      | Un verrou en technologie CMOS                                                 | 90  |

|      | Exemple d'impulsion transitoire à l'entrée d'une bascule                      | 92  |

|      | Exemple de logique dans deux domaines d'alimentation                          | 93  |

|      | Impulsion négative sur la tension en présence de deux domaines d'alimentation |     |

|      | Injection d'une faute par diaphonie                                           | 96  |

|      | Propagation d'une impulsion sur les rails d'alimentation                      | 96  |

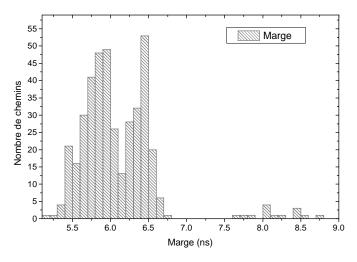

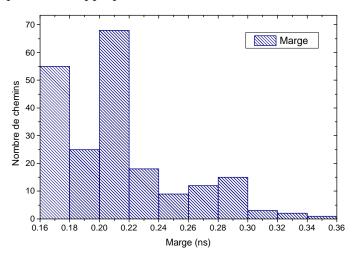

|      | Distribution des marges de temps de setup à 0.90 V                            | 97  |

|      | Distribution des marges de temps de hold à 1.10 V                             | 98  |

| 3.18 | Changement de la distribution des temps de propagation du aux éléments        | 00  |

| 9 10 | parasites de routage                                                          | 99  |

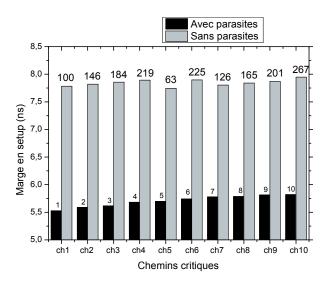

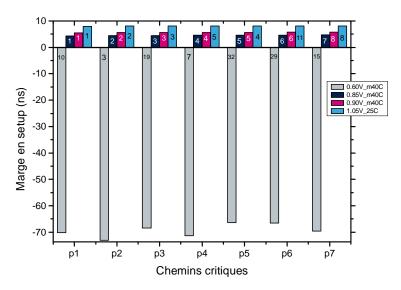

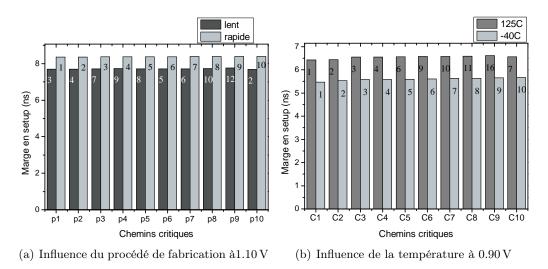

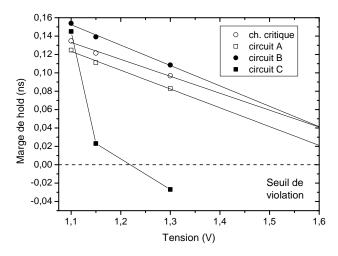

|      | Évolution des marges en <i>setup</i> pour différentes tensions                | 99  |

|      |                                                                               | 100 |

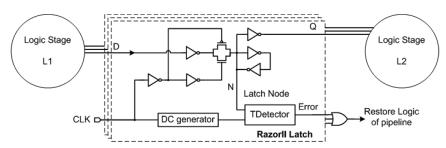

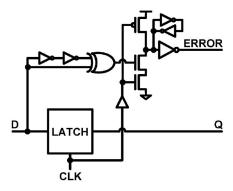

| J.21 | Bascule razorII [Das 2009]                                                    | 102 |

| 3.22 | Détecteur de transition avec partage de temps [Bowman 2009] 103                                                                                 |

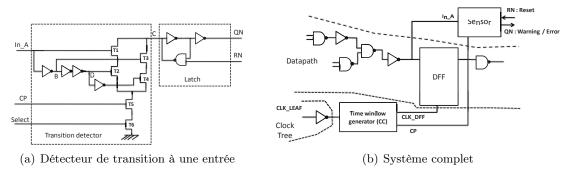

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

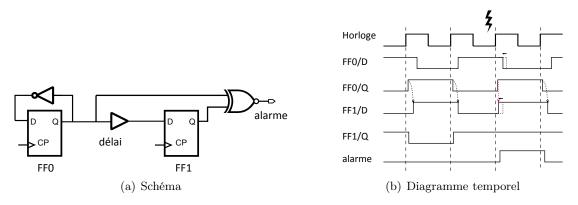

| 3.23 | Système de contrôle de marge de temps [Rebaud 2009]                                                                                             |

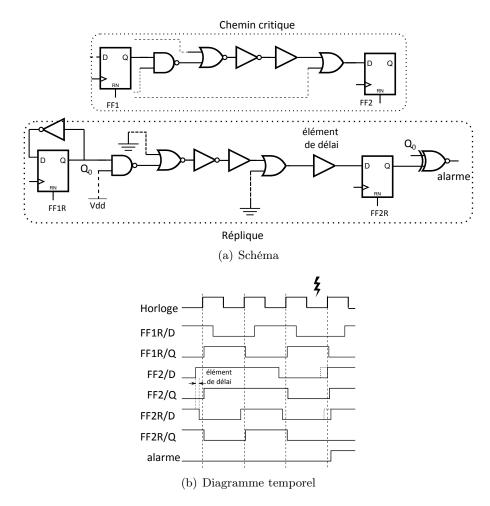

| 3.24 | Principe de fonctionnement d'un circuit répliqué                                                                                                |

| 3.25 | Utilisation du signal d'horloge comme entrée des circuits répliqués 106                                                                         |

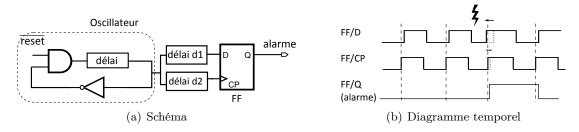

| 3.26 | Principe de détection avec circuits <i>EDS</i>                                                                                                  |

| 3.27 | Fenêtre de détection des circuits répliqués et $EDS$                                                                                            |

| 3.28 | Marges de fiabilité                                                                                                                             |

| 3.29 | Convertisseur temps vers numérique à base d'une ligne de délai [Henzler 2010]111                                                                |

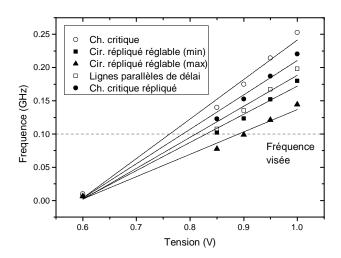

| 3.30 | Exemple d'implantation d'un TDC pour un fonctionnement entre $0.85\mathrm{V}$ et                                                                |

|      | 1.3 V                                                                                                                                           |

| 3.31 | Lignes parallèles de délai $\dots \dots \dots$  |

| 3.32 | Circuit répliqué réglable                                                                                                                       |

| 3.33 | Réplique de chemin critique $\dots \dots \dots$ |

| 3.34 | Circuit A                                                                                                                                       |

| 3.35 | Circuit C                                                                                                                                       |

| 3.36 | Méthodologie d'intégration des circuits de détection                                                                                            |

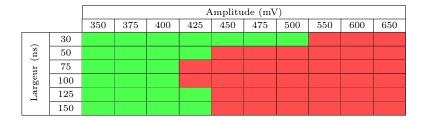

| 3.37 | Évaluation des détecteurs d'impulsions positives                                                                                                |

| 3.38 | Caractérisation des détecteurs d'impulsions négatives                                                                                           |

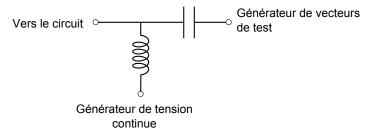

| 3.39 | Dispositif de test des circuits de détection                                                                                                    |

| 3.40 | Bias tee                                                                                                                                        |

| 3.41 | Déformation des signaux envoyés due au déséquilibre entre les temps de                                                                          |

|      | montée et de descente des portes logiques                                                                                                       |

| 3.42 | Exemple de rééquilibrage des temps de propagation avec l'insertion d'inverseurs 135                                                             |

## LISTE DES TABLEAUX

| 1.1  | Catégorisation des outils d'attaque [Criteria 2013]                               |

|------|-----------------------------------------------------------------------------------|

| 1.2  | Évaluation du potentiel d'attaque [Criteria 2013]                                 |

| 1.3  | Évaluation de la vulnérabilité pour les critères communs [Criteria $2013$ ] $23$  |

| 2.1  | Analyse de consommation d'une $IP$ dans un $SoC$                                  |

| 2.2  | Capacité extraite en fonction de la polarisation du circuit étudié 51             |

| 2.3  | Comparaison des deux méthodologies d'extraction de capacité 54                    |

| 2.4  | Comparaison des pics de consommation entre les mesures et le modèle $61$          |

| 2.5  | Comparaison des contremesures existantes                                          |

| 2.6  | Caractéristiques du circuit protégé                                               |

| 2.7  | Évaluation de l'effet des capacités de découplage sur les pics de consommation 72 |

| 3.1  | Effet de la variation de tension d'alimentation sur les contraintes de temps      |

|      | de propagation                                                                    |

| 3.2  | Valeur des signaux logiques aux interfaces en présence d'impulsions positives     |

|      | de tension                                                                        |

| 3.3  | Fonctionnement d'un verrou lorsqu'une impulsion positive est appliquée sur        |

|      | l'alimentation                                                                    |

| 3.4  | Avantages et limitations des solutions rapportées dans la littérature 105         |

| 3.5  | Caractéristiques du circuit testé                                                 |

| 3.6  | Variation de fréquence en fonction de la tension des détecteurs et du chemin      |

|      | critique                                                                          |

| 3.7  | Marges de détection requises et mesurées en simulation pour le chemin cri-        |

|      | tique répliqué                                                                    |

| 3.8  | Caractérisation des circuits de détection pour des tension statiques infé-        |

|      | rieures à la tension nominale                                                     |

| 3.9  | Caractérisation des circuits de détection pour des tensions statiques supé-       |

|      | rieures à la tension nominale                                                     |

| 3.10 | Impulsions négatives sur l' $AES$                                                 |

| 3.11 | Impulsions négatives sur le circuit répliqué réglable                             |

| 3.12 | Impulsions négatives sur les lignes parallèles de délai                           |

x Liste des tableaux

| .13 Impulsions négatives sur le chemin critique répliqué                                     |

|----------------------------------------------------------------------------------------------|

| .14 Impulsions positives sur l' $AES$                                                        |

| .15 Impulsions positives sur le circuit A                                                    |

| .16 Impulsions positives sur le circuit B                                                    |

| .17 Impulsions positives sur le circuit C                                                    |

| .18 Seuils de détections des circuits et de violation de l' $AES$ pour des sous-tensions 133 |

| .19 Seuils de détections des circuits et de violation de l' $AES$ pour des surtensions 133   |

| .20 Comparaison des circuits de détection d'attaques par impulsions positives $$ . 137       |

| .21 Comparaison des circuits de détection d'attaques par impulsions négatives $$ . 138       |

## INTRODUCTION

La multiplication des objets connectés ces dernières années a engendré l'augmentation des données partagées. Ces objets connectés à Internet échangent de nombreuses informations et notamment des données personnelles ou confidentielles. Selon une étude de l'IDate [Idate 2013], 15 milliards d'objets étaient connectés en 2012 contre 4 milliards en 2010. Il y a donc un besoin d'échanges et de stockage de ces informations de façon sécurisée. D'autre part, la sécurité des circuits qui était majoritairement liée au domaine des cartes à puce tend à s'ouvrir vers d'autres applications grand public comme la télévision à péage ou encore la téléphonie mobile.

La sécurisation des données dans les SoCs est généralement basée sur la cryptographie. Ce procédé consiste à chiffrer un message à l'aide d'une clé pour que celui-ci ne soit pas lisible par des personnes non autorisées. Les algorithmes de cryptographie reposent sur des propriétés mathématiques qui complexifient l'accès au message initial sans la clé nécessaire. Néanmoins, l'implantation de ces algorithmes au niveau d'un circuit présente des failles qui compromettent la confidentialité ou l'intégrité des données.

Ces dernières années, plusieurs techniques d'attaque qui mettent en exergue ces faiblesses se sont développées. Les attaques peuvent être passives ou actives, si elles nécessitent ou non de perturber les opérations du circuit. Dans tous les cas, les failles créées ou exploitées proviennent de phénomènes physiques inhérents au fonctionnement du circuit. Ces vulnérabilités peuvent donc apparaître quelle que soit la fonction réalisée par le circuit, qu'il s'agisse ou non d'une opération de cryptographie. Pour garantir la sécurité de ces systèmes, il est nécessaire, d'une part, de comprendre les mécanismes mis en jeu lors d'une attaque. D'autre part, les concepteurs cherchent à réduire la taille des circuits intégrés pour gagner en performances et en autonomie. Il convient donc de se demander quel est l'impact de l'utilisation de technologies avancées sur la sécurité des systèmes.

Afin de limiter les vulnérabilités de ces systèmes sensibles, il faut mettre en place des mesures de protection dès la phase de conception. L'intégration de ces mesures doit être prise en compte très tôt dans le flot de conception des circuits, dès l'étape de spécification fonctionnelle, pour obtenir les certifications de sécurité nécessaires, délivrées par des organismes indépendants d'évaluation sécuritaire tels que les CESTI (Centres d'Évaluation de la Sécurité des Technologies de l'Information). Ces contremesures visent

2 Introduction

généralement un type d'attaque. Le choix de la protection est donc primordial pour limiter son impact sur la surface et les performances du circuit.

Le travail présenté à travers ce manuscrit s'articule autour des attaques passives et actives en tension sur des circuits numériques conçus dans des nœuds technologiques avancés. Ces attaques sont particulièrement accessibles car les dispositifs nécessaires pour leur mise en œuvre sont peu coûteux. Les contributions de ce travail portent sur différents points :

- L'évaluation de vulnérabilités de circuits numériques vis-à-vis des attaques passives en tension durant la phase de conception.

- La compréhension des mécanismes d'injection de fautes induites par des attaques actives en tension.

- La conception et l'évaluation de solutions de détection d'attaques par impulsions sur la tension d'alimentation.

Le premier chapitre présentera les différentes techniques d'attaques sur les circuits. Il met en exergue l'ensemble des menaces visant les circuits et également les principales contremesures qui ont été proposées pour les protéger. Cette partie montre également les contraintes de conception numérique à considérer pour être en mesure de déployer des solutions dans un cadre industriel.

Dans le deuxième chapitre, les attaques par observation de l'alimentation du circuit sont étudiées en phase de conception. La signature électrique d'un circuit numérique sera analysée en développant un modèle électrique. Ce modèle sera utilisé pour évaluer aussi bien les circuits que les contremesures pour mieux anticiper les attaques.

Enfin, le dernier chapitre abordera les attaques par impulsions de tension d'alimentation. Les mécanismes d'injection de fautes seront analysés pour mieux comprendre les phénomènes impliqués. Par la suite, des contremesures seront étudiées puis conçues dans un flot numérique standard. Finalement, ces solutions seront évaluées sur silicium pour en déterminer les performances.

# MENACES ET SÉCURISATION DES CIRCUITS INTÉGRÉS NUMÉRIQUES

| Som | maire |

|-----|-------|

|     |       |

| Aperçı  | u des attaques visant les circuits numériques                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1.1   | Attaques invasives                                                                                                                     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.1.2   | Attaques non invasives                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.1.3   | Attaques semi-invasives                                                                                                                | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Contre  | emesures                                                                                                                               | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2.1   | Protection contre les attaques invasives                                                                                               | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2.2   | Protection contre les attaques actives                                                                                                 | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2.3   | Protection contre les attaques par canaux auxiliaires                                                                                  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2.4   | Bilan                                                                                                                                  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Exemp   | ole de critères d'évaluation : les critères communs                                                                                    | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.3.1   | Cible de sécurité et profil de protection                                                                                              | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.3.2   | Exigences d'assurance de sécurité                                                                                                      | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.3.3   | Analyse des vulnérabilités et potentiel d'attaque                                                                                      | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Intégra | ation de contremesures dans le flot de conception                                                                                      | <b>24</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.4.1   | Méthodes de conception                                                                                                                 | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.4.2   | Contraintes imposées par le flot numérique                                                                                             | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.4.3   | Contraintes industrielles de développement                                                                                             | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Conclu  | ısion                                                                                                                                  | <b>32</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | 1.1.1<br>1.1.2<br>1.1.3<br>Contre<br>1.2.1<br>1.2.2<br>1.2.3<br>1.2.4<br>Exemp<br>1.3.1<br>1.3.2<br>1.3.3<br>Intégra<br>1.4.1<br>1.4.2 | 1.1.2 Attaques non invasives  1.1.3 Attaques semi-invasives  Contremesures  1.2.1 Protection contre les attaques invasives  1.2.2 Protection contre les attaques actives  1.2.3 Protection contre les attaques par canaux auxiliaires  1.2.4 Bilan  Exemple de critères d'évaluation : les critères communs  1.3.1 Cible de sécurité et profil de protection  1.3.2 Exigences d'assurance de sécurité  1.3.3 Analyse des vulnérabilités et potentiel d'attaque  Intégration de contremesures dans le flot de conception  1.4.1 Méthodes de conception  1.4.2 Contraintes imposées par le flot numérique |

#### 1.1 Aperçu des attaques visant les circuits numériques

Au cours de ces 20 dernières années, de nombreux travaux portant sur les méthodes d'attaques de circuits sont apparus dans la littérature, suivis de mise en pratique, pour faire prendre conscience de la menace qui pèse sur la sécurité des circuits intégrés. Si ces techniques ciblent souvent des circuits cryptographiques, elles peuvent être utilisées sur d'autres systèmes afin de compromettre leur sécurité. En fonction des moyens et des connaissances dont disposent les attaquants, IBM a proposé une classification de ceux-ci [Abraham 1991]:

- la première classe est constituée des attaquants astucieux (clever outsiders) qui disposent de moyens limités et de connaissances disponibles publiquement. Il s'agit généralement de personnes isolées mais qui, sur du long terme, peuvent devenir nombreux et former un groupe potentiellement dangereux.

- la deuxième classe (knowlegeable insiders) dispose de compétences spécifiques et de moyens plus importants. Les attaquants sont capables de comprendre un système complexe grâce aux équipements auxquels ils ont accès.

- la dernière catégorie regroupe les organisations financées (funded organizations). Ces groupes sont capables de rassembler des experts aux compétences complémentaires et disposent de moyens financiers très importants. Ils peuvent également faire appel à des personnes faisant partie des classes I et II. Les attaquants appartenant à cette catégorie font généralement partie d'agences gouvernementales, de grandes entreprises ou de groupes de crimes organisés.

Cette première partie rappelle les moyens d'attaques répertoriés dans la littérature. Ils sont souvent distingués en fonction de leur caractère intrusif ou destructeur. La description de ces catégories d'attaques sera l'objet du paragraphe suivant. Les principales contremesures développées pour lutter contre ces attaques sont ensuite répertoriées. Elles permettent de renforcer la sécurité des systèmes, qui peut être évaluée selon plusieurs critères, nous verrons l'exemple des critères communs. Par la suite, l'intégration de ces contremesures en suivant le flot de conception standard des circuits numériques sera analysée. Les résultats de cette analyse nous aideront à prendre en compte les contraintes dans le choix et l'implantation de ces solutions.

#### 1.1.1 Attaques invasives

La première catégorie d'attaques est qualifiée d'invasive. Pour récupérer les informations sensibles, le circuit est désassemblé de son boîtier afin de pouvoir y déposer directement des sondes permettant d'observer les données. À l'aide de ces sondes, il est également possible de communiquer avec le circuit [Kömmerling 1999]. Une autre méthode consiste à réaliser la rétro-conception du circuit cible (reverse engineering). Elle est utilisée pour comprendre la structure du circuit afin d'apprendre ou d'émuler son comportement. Cette technique nécessite le même type d'équipements que ceux

utilisés pour la fabrication du circuit. Par conséquent, des équipements coûteux sont nécessaires pour mettre en place ces attaques. Il est aussi important de noter qu'elles peuvent prendre des jours voir des semaines pour être réalisées [Skorobogatov 2005]. À titre d'exemple, les différentes étapes de désassemblage d'une carte à puce sont données dans [Kömmerling 1999, Skorobogatov 2005]. Le plastique est d'abord chauffé jusqu'à ce

FIGURE 1.1 : Désassemblage du boîtier avec de l'acide nitrique [Kömmerling 1999]

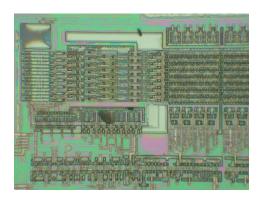

qu'il devienne flexible, la puce est alors détachée en pliant la carte. Ensuite, la résine qui recouvre le silicium est dissoute dans de l'acide (figure 1.1). L'étape suivante est d'enlever la couche de passivation afin d'avoir accès aux niveaux de métaux les plus élevés. On peut dès lors établir des contacts sur les pistes métalliques à l'aide d'équipements spécifiques. Ce désassemblage permet également d'accéder aux couches internes et d'observer la structure de la puce qui peut servir pour de la rétro-conception (figure 1.2).

FIGURE 1.2 : Microcontrôleur Motorola MC68HC705C9A après gravure chimique  $[{\tt Skorobogatov}~2005]$

#### 1.1.2 Attaques non invasives

Les attaques non invasives exploitent les informations inhérentes au fonctionnement du circuit comme le temps d'exécution, la consommation électrique, les émissions électromagnétiques, la température ou encore le bruit émis [Zhou 2005]. Ce sont en général des émissions non intentionnelles qui sont détournées en vue de mener une attaque. Ces informations peuvent être reliées statistiquement à l'activité, aux opérations internes ainsi qu'aux données manipulées dans le circuit. Certaines de ces attaques sont passives car elles ne nécessitent pas de perturber le circuit : on parle alors d'attaques par canaux auxiliaires. Les autres attaques sont donc actives, elles impliquent des modifications locales ou globales de l'environnement du circuit en jouant sur des paramètres tels que la tension d'alimentation, la fréquence de cadencement de l'horloge ou encore la température [Kim 2007]. Ces modifications peuvent engendrer la désactivation de solutions de protection du circuit ou entrainer une mauvaise opération.

Ces attaques ne nécessitent pas de préparation spécifique du circuit contrairement aux attaques invasives. Elles sont donc moins coûteuses à mettre en place et à réaliser. De plus, étant donné que la puce ne présente aucun dommage, il n'y a aucune trace pouvant attester que le circuit a été attaqué. Il s'agit donc d'une menace importante pour la sécurité des circuits. Toutefois, la récupération et l'analyse des données peut s'avérer longue avant de parvenir à l'information cherchée. Nous allons nous intéresser dans un premier temps aux attaques par canaux auxiliaires.

#### 1.1.2.1 Attaques par canaux auxiliaires

Les opérations réalisées par un circuit prennent un certain temps, consomment du courant électrique, et émettent des radiations électromagnétiques : tous ces canaux sont des sources d'informations liées aux données en cours de traitement lors du fonctionnement d'un circuit.

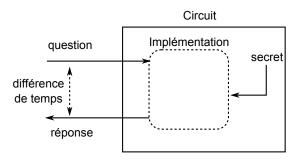

Attaques temporelles. Le principe des attaques temporelles a été présenté par Kocher [Kocher 1996] : les opérations qui ont lieu dans un circuit dépendent des données d'entrée du système. Une mesure précise du temps de réponse peut révéler des informations a priori secrètes. Dans ce cas, l'attaquant dispose d'un ensemble de messages qui sont traités par le circuit avec les temps correspondant à chaque durée de traitement. Le principe de cette attaque est montré sur la figure 1.3. Plusieurs algorithmes peuvent être vulnérables à cette attaque. Cela résulte souvent de l'implantation logicielle des algorithmes : pour des raisons de gain en performances, les opérations suivant des conditions et des embranchements sont contournées. Certaines opérations ayant des temps de calculs non constants comme des multiplications ou des divisions sont effectuées [Dhem 2000]. Il en résulte des dépendances des temps de calculs vis-à-vis des données secrètes. Un exemple récent d'étude sur les attaques temporelles est donné dans

FIGURE 1.3 : Principe de l'attaque temporelle [Dhem 2000]

[Danger 2014]. L'attaque porte sur un microcontrôleur 8 bits exécutant un chiffrement AES 128 bits. Les auteurs montrent qu'il est possible de retrouver la clé de l'algorithme, en mesurant le temps d'exécution. L'idée est de considérer le carré du temps total d'exécution ( $2^{nd}$  order timing attack) car il dépend de la clé utilisée pour le calcul.

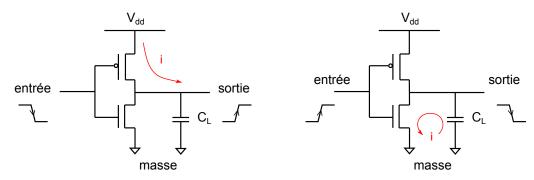

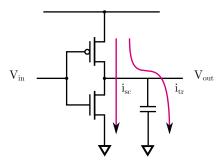

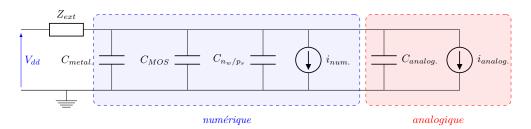

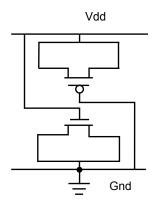

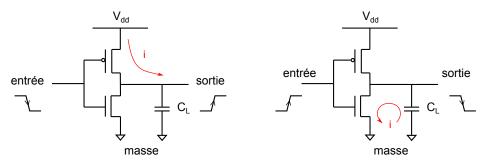

Attaques par analyse de consommation électrique. Cette attaque, présentée dans [Kocher 1999] se base sur la consommation électrique des circuits utilisant la technologie CMOS. Lorsqu'il y a une transition de la valeur de sortie d'une porte logique (de l'état haut vers l'état bas ou inversement), on peut mesurer une variation du courant consommé en fonction de la transition. Ce courant correspond à la charge et à la décharge de la capacité de l'étage logique suivant comme indiqué sur la figure 1.4.  $C_L$  représente la capacité de l'étage de sortie de l'inverseur. Les attaques par analyse

FIGURE 1.4: Fonctionnement d'inverseur en technologie CMOS

de consommation consistent à mesurer, puis à analyser la consommation de courant par le circuit en fonction du temps lors de ses opérations. Leur principe repose sur la corrélation entre ce courant consommé et les données ou instructions qui sont traitées pour une opération donnée. [Mangard 2010].

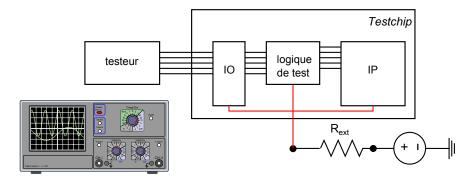

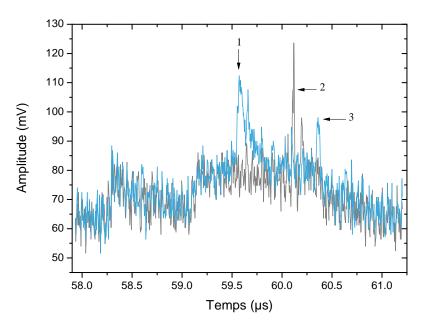

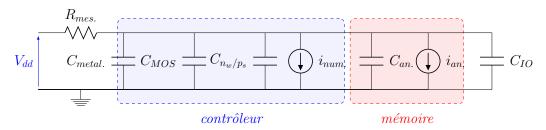

Concrètement, les attaques par analyse de consommation nécessitent une mesure physique de la consommation électrique du circuit attaqué. Plusieurs méthodes permettent d'obtenir ces informations de consommation. La plus simple et la plus répandue est l'utilisation d'une résistance placée sur la ligne d'alimentation en série avec le circuit. En général, il s'agit d'une résistance de petite valeur, typiquement de 1  $\Omega$  à 50  $\Omega$ . Cependant, cette valeur doit permettre de mesurer la tension à ses bornes à l'aide d'un oscilloscope numérique. Un exemple d'expérimentation sera donné dans le chapitre 2. Les sections suivantes indiquent comment ces mesures peuvent être exploitées.

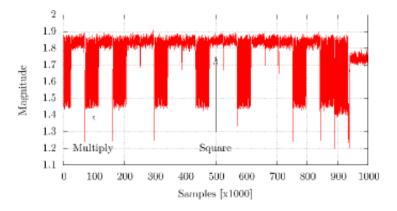

Simple Power Analysis (SPA) Le but de l'analyse de courant simple est d'estimer directement à partir de la consommation mesurée quelle instruction particulière est exécutée à un moment donné et quelle est la valeur des signaux internes. L'analyse de courant simple peut révéler une séquence d'instructions et donc peut être utilisée pour détecter un algorithme de cryptographie [Mangard 2010] ou même d'identifier les différentes étapes de celui-ci : repérer des permutations dans l'algorithme DES (Data Encryption Standard), les différentes rondes de l'algorithme AES (Advanced Encryption Standard) ou encore des multiplications et des exponentiations (square) de l'algorithme RSA (Rivest Shamir Adleman) comme indiqué sur la figure 1.5. En regardant la forme et la durée du courant mesuré, les opérations de multiplication (multiply) et d'exponentiation (square) peuvent être repérées.

FIGURE 1.5: Analyse de courant simple de courant sur l'algorithme RSA [Selmane 2010]

Differential Power Analysis (DPA) L'analyse différentielle de courant [Kocher 1999] est une attaque plus sophistiquée que l'analyse simple. Elle est généralement utilisée pour des algorithmes de cryptographie. Elle se base sur l'analyse statistique pour isoler les signaux qui intéressent l'attaquant de l'ensemble du circuit. Cette méthode statistique permet d'identifier des différences infimes dans la consommation de courant qui peuvent être utilisées pour retrouver des bits d'une donnée secrète de façon individuelle. La puissance de l'analyse repose sur sa capacité à récupérer une information même si la relation entre la consommation et la donnée secrète est trop complexe pour être directement identifiée par une analyse simple de courant. À

noter aussi que les attaques DPA se focalisent sur un instant donné pour déterminer la dépendance des données et de la consommation, la dépendance de la consommation vis-à-vis du temps n'est pas primordiale. En effet, on se place à un instant donné pour étudier la différence de consommation pour différents vecteurs d'entrée [Mangard 2010].

Attaques électromagnétiques. Cette attaque a été présentée pour la première fois par Quisquater et Samyde [Quisquater 2000]. Tout mouvement d'une charge provoque un champ électromagnétique. Ainsi, l'utilisation d'une micro-antenne peut identifier le réseau de distribution d'alimentation et permettre d'établir un profil de consommation de la puce. Un attaquant peut donc observer ces émanations pour avoir des indications sur les données en cours d'utilisation. Comme pour l'analyse de consommation électrique, on peut distinguer l'analyse électromagnétique simple et différentielle. Cependant, l'analyse de consommation électrique mesure la totalité du courant du circuit tandis que l'analyse électromagnétique peut se focaliser sur des zones restreintes. Agrawal et al. [Agrawal 2003] suggèrent que les émanations électromagnétiques proviennent de deux sources :

- les émanations directes provenant de la circulation du courant dans la puce

- les émanations non intentionnelles provenant des effets de couplage entre les sousblocs dus à leur proximité.

Selon les auteurs, les émanations non intentionnelles ont une meilleure portée et peuvent être mesurées jusqu'à 4.5 mètres. Même si cette attaque est non invasive, elle peut nécessiter une extraction de la puce de son boîtier pour obtenir une meilleure mesure.

Autres attaques par canaux auxiliaires. Il existe d'autres types d'attaques par canaux auxiliaires même si celles-ci sont moins développées dans la littérature.

Les attaques acoustiques consistent à analyser le son émis par le système pendant son fonctionnement. À l'instar des précédentes attaques répertoriées, il existe une différence de fréquences acoustiques émises par le circuit en fonction du calcul effectué. Cette technique a été utilisée dans [Genkin 2013] pour extraire la totalité des 4096 bits d'une clé de déchiffrement RSA. Le signal acoustique mesuré provient de la vibration des composants électroniques (bobines et condensateurs) dans le circuit de régulation de tension. Celui-ci parvient difficilement à fournir une tension d'alimentation constante au processeur à cause de la grande fluctuation de consommation causée par les différentes opérations effectuées par le CPU. Bien que cette attaque ait été réalisée dans des conditions favorables (choix des textes à déchiffrer, une seule machine en fonctionnement), elle met en avant l'utilisation d'un nouveau canal de mesure d'informations.

L'analyse de la lumière émise par un composant est une autre source d'informations qui peut être exploitée. Loughry et Umphress [Loughry 2002] ont décrit dans leurs travaux comment la lumière émise par la diode électroluminescente d'un ordinateur pouvait être corrélée aux informations qui étaient traitées.

#### 1.1.2.2 Les attaques actives

Le deuxième groupe d'attaques non invasives concerne les injections de fautes. Les attaques en fautes exploitent les propriétés physiques des composants.

Attaques par modification de la température. Les informations sensibles utilisées par un circuit au cours de son fonctionnement ont besoin d'être stockées. Elles ne sont pas censées être divulguées à l'extérieur du circuit. Les mémoires volatiles sont utilisées dans ce but : l'information est perdue lorsque l'alimentation est coupée. Toutefois, à cause du phénomène de rétention de données, si le temps nécessaire à la lecture de la mémoire est plus petit que le temps de rétention, la volatilité de la mémoire peut être contournée. Pour une cellule SRAM, le phénomène de rétention est activé aux alentours de -20°C. Dès lors, un attaquant peut alors récupérer le contenu de la mémoire [Ali 2011a].

Dans [Skorobogatov 2009], il est montré que le réchauffement local d'une mémoire non volatile flash ou E<sup>2</sup>PROM d'un microcontrôleur peut modifier son contenu de manière permanente. L'attaque a été utilisée pour effacer plusieurs bits de la mémoire.

D'autre part, les circuits sont spécifiés pour fonctionner dans une certaine gamme de températures. Au-delà de cette gamme, les temps de propagation sont modifiés au point de ne plus garantir le bon fonctionnement du composant. On peut retrouver la mise en évidence de ce phénomène dans [Dutertre 2010]. Des fautes ont été injectés dans un algorithme de cryptographie embarqué sur un FPGA. La température du circuit a été portée à  $210^{\circ}$ C pour obtenir les premières fautes.

Modification de la fréquence d'horloge. Le principe ici est d'augmenter la fréquence de l'horloge qui cadence les opérations du circuit. Cela ne concerne évidemment que les circuits synchrones. Au-delà d'une fréquence maximale, les opérations logiques n'ont pas le temps de s'effectuer avant le front d'horloge qui vient les mettre à jour. Cette méthode, bien qu'efficace, ne permet pas un contrôle spatial ou temporel des fautes injectées. En effet, en modifiant la fréquence d'horloge, les fautes sont potentiellement injectées à chaque cycle d'horloge, ce qui peut provoquer le non-fonctionnement complet du circuit attaqué.

Il existe une amélioration de cette méthode, qui consiste non pas à modifier le signal d'horloge en entier, mais à modifier la période d'un ou plusieurs cycles choisis par l'attaquant. Il s'agit ici d'impulsions créées sur le signal d'horloge afin d'en modifier temporairement la fréquence. Dans [Amiel 2006], il est mentionné que de tels raccourcissements de périodes d'horloge provoquent une modification d'un ou de plusieurs octets. L'idée est de diminuer progressivement la période d'un cycle jusqu'à ce qu'une faute apparaisse. Cette méthode d'injection de fautes a été présentée plus récemment dans [Agoyan 2010]. Il est montré qu'avec cette méthode, on est capable de modifier un seul

bit dans le circuit attaqué avec une bonne synchronisation temporelle et de manière reproductible.

Cependant, ces injections requièrent l'accès direct au signal d'horloge. Il n'est pas possible d'attaquer directement un circuit utilisant son propre système de génération d'horloge car la déconnexion de ce signal paraît difficile [Barenghi 2012]. D'autre part, les circuits numériques asynchrones ne possèdent pas de signal d'horloge, et peuvent donc s'avérer efficaces contre ce type d'attaque [Fournier 2003, Monnet 2006].

Modification de la tension d'alimentation. Les circuits intégrés sont conçus pour fonctionner dans une certaine gamme de tension. Cette tension dépend de la technologie des composants élémentaires CMOS. À titre d'exemple, pour les nœuds technologiques avancés actuels  $(28\,\mathrm{nm})$ , la tension d'alimentation nominale se situe autour de  $1\,\mathrm{V}$ . Au-delà de la gamme opérationnelle de tensions, il n'est plus possible de garantir le bon fonctionnement du circuit. Dès lors, plusieurs types d'attaques peuvent être menées en jouant sur la tension d'alimentation. La sous-alimentation d'un processeur peut entrainer des interruptions ou des sauts d'instructions. On peut ainsi induire des fautes transitoires sur un ou plusieurs bits au fur et à mesure que la tension est diminuée. La baisse de tension modifie les propriétés temporelles des portes logiques en les ralentissant. Ainsi, lorsque les contraintes temporelles ne sont plus respectées, les premières fautes apparaissent [Zussa 2012]. L'influence de la baisse de la tension d'alimentation sur un circuit implémenté sur FPGA est montrée de manière expérimentale dans [Dutertre 2010]. Ce mode opératoire a été utilisé dans [Selmane 2008] sur une carte à puce conçue en technologie 130 nm embarquant un coprocesseur AES.

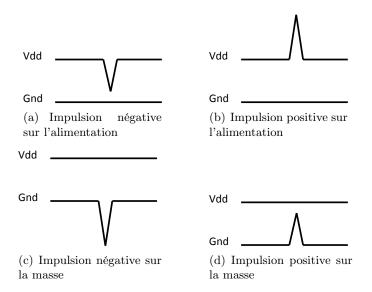

Comme pour les attaques par modification de la fréquence d'horloge, il est possible de modifier temporairement la tension d'alimentation en y créant une impulsion. L'avantage de cette méthode est d'avoir une meilleure synchronisation temporelle du moment où la faute est injectée. Il y a quatre principaux types d'impulsions qui peuvent être appliqués sur les rails d'alimentation d'un circuit (figure 1.6) :

- impulsion positive sur l'alimentation (1.6(b))

- impulsion négative sur l'alimentation (1.6(a))

- impulsion négative sur la masse (1.6(c))

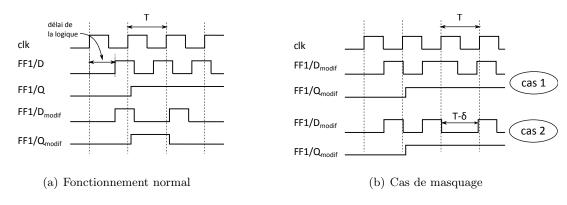

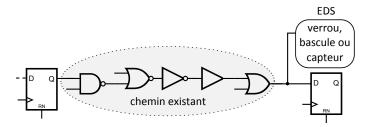

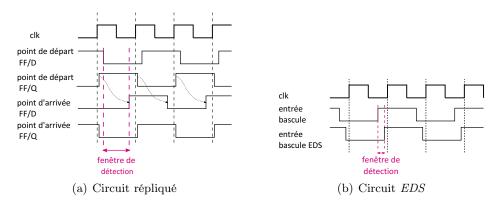

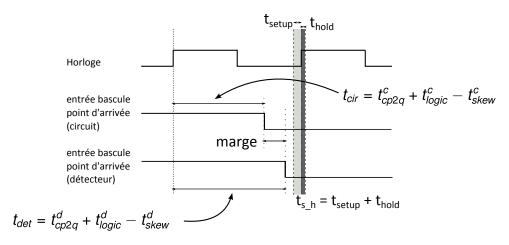

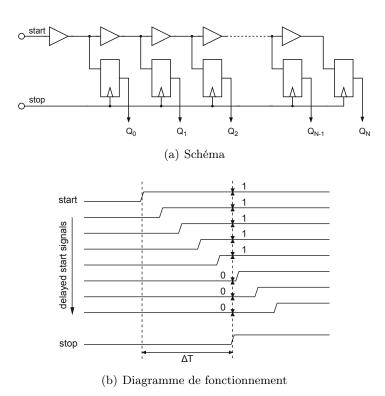

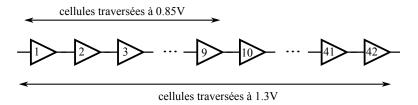

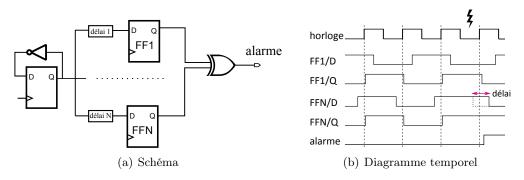

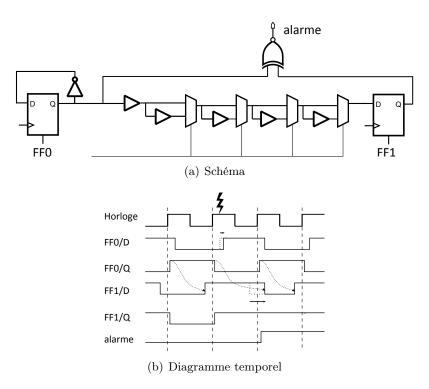

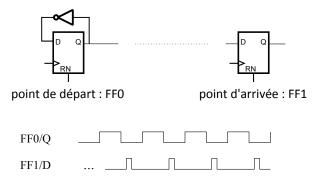

- impulsion positive sur la masse (1.6(d))