## Placement et routage de circuits mixtes analogiques-numériques CMOS

Eric Lao

#### ▶ To cite this version:

Eric Lao. Placement et routage de circuits mixtes analogiques-numériques CMOS. Architectures Matérielles [cs.AR]. Sorbonne Université, 2018. Français. NNT: 2018SORUS575. tel-02924679

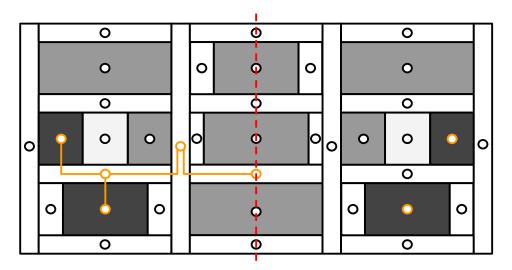

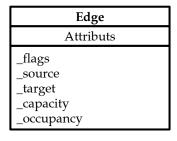

#### HAL Id: tel-02924679 https://theses.hal.science/tel-02924679

Submitted on 28 Aug 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Thèse de Doctorat de Sorbonne Université Spécialité Informatique

École Doctorale Informatique, Télécommunications et Électronique

Présentée par

#### Eric LAO

pour obtenir le grade de

Docteur de Sorbonne Université

# Placement et routage de circuits mixtes analogiques-numériques CMOS

Soutenue le 14 Septembre 2018 devant le jury composé de:

Directeur de thèse : **Mme. Marie-Minerve LOUËRAT**Co-encadrant de thèse : **M. Jean-Paul CHAPUT**

| Mme. Sonia BEN DHIA, Professeur, INSA Toulouse,          | Rapporteur  |

|----------------------------------------------------------|-------------|

| M. Philippe COUSSY, Professeur, Université Bretagne Sud, | Rapporteur  |

| M. Luca ALLOATTI, Docteur, ETH Zurich,                   | Examinateur |

| M. Laurent FESQUET, HDR, Université Grenoble Alpes,      | Examinateur |

| M. Hamid KOKABI, Professeur, Sorbonne Université,        | Examinateur |

| M. Habib MEHREZ, Professeur, Sorbonne Université,        | Examinateur |

| M. Marc SABUT, Ingénieur, STMicroelectronics,            | Invité      |

Sorbonne Université Laboratoire d'Informatique de Paris 6 - LIP6 Place Jussieu, 75005 Paris, France

#### Résumé

Avec l'évolution des procédés technologiques d'intégration, le traitement numérique devient de plus en plus rapide tout en coûtant moins en surface et en consommation d'énergie. La diminution des dimensions est effectuée au détriment de la précision des blocs analogiques. L'idée est de bénéficier des performances offertes par les circuits numériques pour relâcher les spécifications des blocs analogiques et gagner ainsi globalement en surface et consommation. Or les concepteurs de circuits mixtes analogiques-numériques sont confrontés à une situation où ils doivent choisir entre un flot purement analogique et un flot purement numérique, chacun des deux ignorant l'autre.

Cette thèse propose un flot de conception mixte permettant d'unifier le flot de conception numérique et analogique dans la phase de conception du dessin des masques. Le flot de conception se divise entre trois parties majeures : une phase de placement, une phase de routage global et une phase de routage détaillé. Dans la phase de placement, le concepteur est amené à décrire un placement relatif de son circuit sous la forme d'un script permettant à notre outil de générer un ensemble de placements valides respectant les contraintes décrites par le concepteur. Le choix du placement est réalisé de manière interactive à travers une interface graphique permettant de visualiser ce choix. Par la suite, une phase de routage global détermine de manière grossière les chemins les plus courts permettant de joindre les connecteurs de chaque *net*. Ces chemins prennent en compte diverses contraintes du circuit telles que des obstacles ou des contraintes de symétrie. Une phase de routage détaillé vient ensuite compléter la construction et la résolution des problèmes de superposition des fils de routage.

Notre flot de conception est appliqué à des circuits analogiques et mixtes de tailles différentes. Les résultats présentés montrent une capacité à placer et router en un temps court tout en respectant les contraintes des concepteurs. Notre approche a pour objectif de faire appel aux concepteurs et à leurs expériences tout au long de la conception du dessin des masques dans le but de choisir les meilleures solutions de placement routage.

**Mots clés :** dessin des masques, circuits intégrés, analogique, numérique, mixte, placement, routage global, routage détaillé, CMOS, outils de CAO, automatisation, flot de conception.

#### Remerciements

Je souhaite exprimer toute ma reconnaissance à Marie-Minerve Louërat et Jean-Paul Chaput, pour avoir tout fait pour rendre cette thèse possible et pour tous les efforts et le temps accordé à l'encadrement de ma thèse. Je vous remercie d'avoir partagé votre expérience et de m'avoir tant fait confiance durant l'intégralité de ces années de thèse mais également durant les années qui ont précédé cette thèse à travers plusieurs stages. Je souhaite aussi remercier Stéphane Fay de m'avoir accordé la chance d'effectuer ces conférences aux Palais de la Découverte durant près de deux années.

Je remercie M. Philippe Coussy et Mme. Sonia Ben Dhia d'avoir accepté d'être membres de mon jury et rapporteurs de mon manuscrit. Je remercie également les autres membres du jury : M. Hamid Kokabi, M. Habib Mehrez, M. Luca Alloatti, M. Laurent Fesquet et M. Marc Sabut de m'accorder de leur temps.

Je souhaite remercier l'ensemble de l'équipe pédagogique du master SESI de m'avoir inspiré durant toutes ces années et d'avoir suscité mon intérêt pour le monde de l'électronique et de l'informatique. Je pense en particulier à Farouk Vallette, Julien Denoulet, Sylvain Feruglio, Dimitri Galayko, Geoffroy Klisnick et Franck Wajsbürt. Je souhaite remercier particulièrement Hassan Aboushady de m'avoir encadré durant mon stage de fin de master et pour les discussions avec son équipe. Je remercie également Haralampos Stratigopoulos, Jacky Porte, Amine Rhouni et Naohiko Shimizu pour avoir pris le temps de partager leurs expériences avec nous.

Merci à tous mes collègues avec qui j'ai passé du temps durant ces années de thèse : Youen Lesparre, Olivier Tsiakaka, Cédric Klikpo, Jad Khatib, Armine Karami, Gabriel Gouvine et Orlando Chuquimia pour tous les moments de joie, tous les conseils et discussions intéressantes qu'on a pu partager. Je voudrais remercier également la gentillesse du personnel administratif en particulier Shahin-Léa Mahmoodian, Sabrina Vacheresse et de toutes les personnes que j'aurais oubliées de mentionner faisant partie du LIP6.

Je pense fort à mes parents et au reste de ma famille pour leurs encouragements et leur soutien dans les moments difficiles. Je remercie tous mes amis qui m'ont tant encouragé et soutenu durant ces années de thèse, leurs encouragements ont contribué à donner le meilleur de moi-même.

### Table des matières

| Ta | ıble d | les matières                                                     | vii |

|----|--------|------------------------------------------------------------------|-----|

| Li | ste d  | es figures                                                       | ix  |

| Li | ste d  | es tableaux                                                      | xv  |

| 1  | Intr   | roduction                                                        | 1   |

|    | 1.1    | Contexte                                                         | 2   |

|    | 1.2    | Conception du dessin des masques mixtes actuelle                 | 3   |

|    | 1.3    | Enjeux et motivations                                            | 5   |

|    | 1.4    | Contributions de cette thèse                                     | 6   |

|    | 1.5    | Plan de la thèse                                                 | 7   |

|    | 1.6    | Références                                                       | 8   |

| 2  | Éta    | t de l'art des outils de CAO pour circuits analogiques et mixtes | 9   |

|    | 2.1    | Introduction                                                     | 10  |

|    | 2.2    | Les outils de génération de dessins des masques                  | 10  |

|    | 2.3    | L'historique des outils de CAO au LIP6                           | 18  |

|    | 2.4    | Conclusion                                                       | 21  |

|    | 2.5    | Références                                                       | 25  |

| 3  | Plac   | cement                                                           | 29  |

|    | 3.1    | Introduction                                                     | 30  |

|    | 3.2    | Formalisation du problème du placement                           | 31  |

|    | 3.3    | Les méthodes de résolution existantes                            | 37  |

|    | 3.4    | Méthode de résolution                                            | 44  |

|    | 3.5    | Implémentation du placement                                      | 57  |

|    | 3.6    | Conclusion                                                       | 71  |

|    | 3.7    | Références                                                       | 72  |

| 4  | Rou    | itage global                                                     | 77  |

|    | 4.1    | Introduction                                                     | 78  |

|    | 4.2    | Formalisation du problème du routage global                      | 79  |

|    | 4.3    | Les méthodes de résolution existantes                            | 86  |

|    | 4.4    | Méthode de résolution                                            | 89  |

|    | 4.5    | Implémentation du routage mixte                                  | 103 |

|    | 4.6    | Conclusion                                                       | 127 |

|    | 4.7    | Références                                                       | 128 |

| <b>5</b> | Rou        | ıtage détaillé                                           | 129 |

|----------|------------|----------------------------------------------------------|-----|

|          | 5.1        | Introduction                                             | 130 |

|          | 5.2        | Achèvement du routage global                             | 131 |

|          | 5.3        | Résolution des superpositions                            |     |

|          | 5.4        | Contraintes des signaux analogiques                      | 148 |

|          |            | Conclusion                                               |     |

|          |            | Références                                               |     |

| 6        | Rés        | ultats                                                   | 153 |

|          | 6.1        | Introduction                                             | 154 |

|          | 6.2        | Amplificateur à transconductance de type Miller          | 155 |

|          | 6.3        | Amplificateur à source de courant ajustable              | 162 |

|          | 6.4        | Transconductance différentielle configurable             | 166 |

|          | 6.5        | Conclusion                                               | 169 |

|          | 6.6        | Références                                               | 169 |

| 7        | Con        | nclusion et perspectives                                 | 171 |

|          | 7.1        | Conclusions                                              | 172 |

| 8        |            | plications                                               | 177 |

|          | 8.1        | Références                                               | 177 |

| A        | Anr        | nexes                                                    | Ι   |

|          | <b>A.1</b> | Script de l'amplificateur à source de courant ajustable  | I   |

|          | <b>A.2</b> | Script de la transconductance différentielle contrôlable | IV  |

### Liste des figures

| 1.1  | Croissance des principales categories de marche de circuits integres[1]                                        |     |

|------|----------------------------------------------------------------------------------------------------------------|-----|

| 1.2  | (a) Flot de conception du dessin des masques numérique (b) Flot de conception du dessin des masques analogique | 3   |

| 1.3  |                                                                                                                | 3   |

| 1.3  | Flot de conception mixte : unification du flot de conception numérique analogique                              | 6   |

| 2.1  | Comparaison des approches des outils de génération de dessins des masques                                      |     |

|      | pour circuits analogiques et mixtes                                                                            | 12  |

| 2.2  | Structure et flot de conception d'ALSYN[6]                                                                     | 13  |

| 2.3  | Flot du générateur de dessins des masques de <i>BAG</i> [7]                                                    | 13  |

| 2.4  | Flot de conception d' <i>ALDAC</i> [19]                                                                        | 14  |

| 2.5  | Flot de conception d' $ALG[20]$                                                                                | 14  |

| 2.6  | Structure de l'outil de CAO ALADIN[24]                                                                         | 16  |

| 2.7  | Structure de l'outil de CAO LAYGEN II[25]                                                                      | 16  |

| 2.8  | Architecture d'Helix                                                                                           | 17  |

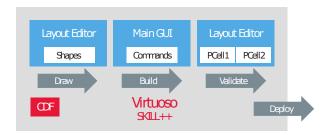

| 2.9  | Flot de développement des PCells dans Virtuoso                                                                 | 17  |

| 2.10 | Générateur d'IP de <i>CAIRO</i> +                                                                              | 19  |

|      | Architecture de CHAMS                                                                                          | 20  |

|      | Représentation chronologique des outils de CAO dédiés aux dessins des masqu                                    | ıes |

|      | analogique entre 1985 et 2018                                                                                  | 21  |

| 2.13 | Description des outils de génération de dessins des masques pour circuits                                      |     |

|      | analogiques et mixtes depuis 1985                                                                              | 23  |

| 2.14 | Description des outils de génération de dessins des masques pour circuits                                      |     |

|      | analogiques et mixtes depuis 1985(suite)                                                                       | 24  |

| 3.1  | Ensemble des modules générables par <b>Coriolis</b> [1]                                                        | 32  |

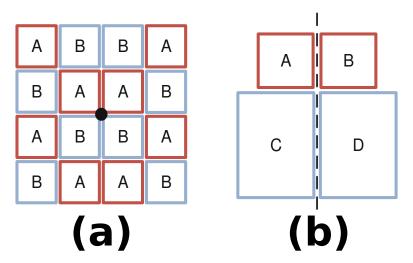

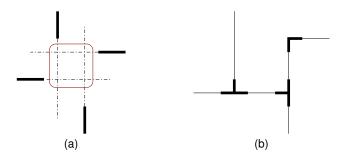

| 3.2  | Contraintes de centrage géométrique (a) et de symétries (b)[3]                                                 | 34  |

| 3.3  | Placement sans (a) et avec (b) une prise en compte du sens du courant[4] .                                     | 34  |

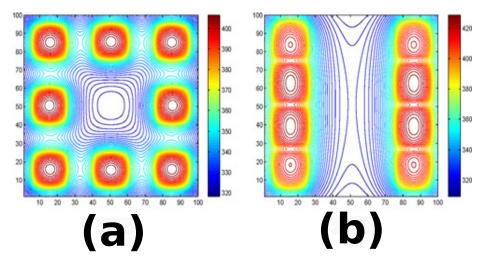

| 3.4  | Profil thermique du circuit lorsque tous les modules sont répartis équitable-                                  |     |

|      | ment entre les quatre côtés (a) et deux côtés (b) du circuit[5]                                                | 35  |

| 3.5  | Modules soumis à une contrainte de proximité (en rouge) pouvant être en-                                       |     |

|      | tourés d'un anneau de garde[3]                                                                                 | 35  |

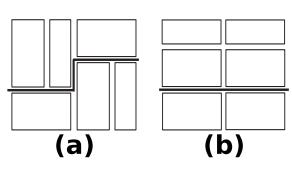

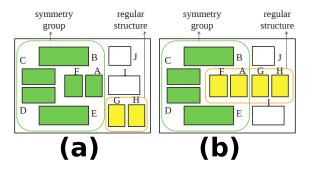

| 3.6  | (a) Placement sans prise en compte de la régularité (b) Placement avec prise                                   |     |

|      | en compte de la régularité[8]                                                                                  | 36  |

| 3.7  | (a) Placement privilégiant des contraintes de symétries plutôt que des con-                                    |     |

|      | traintes de régularité. (b) Placement tenant compte des contraintes de sy-                                     |     |

|      | métries et de régularité en même temps.[8]                                                                     | 36  |

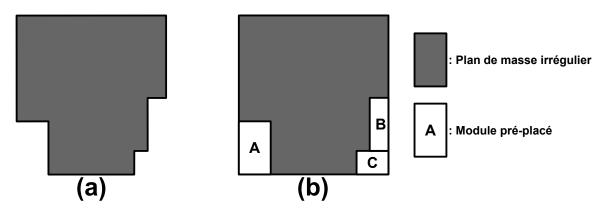

| 3.8  | Plan de masse irrégulier[9]                                                                                    | 36  |

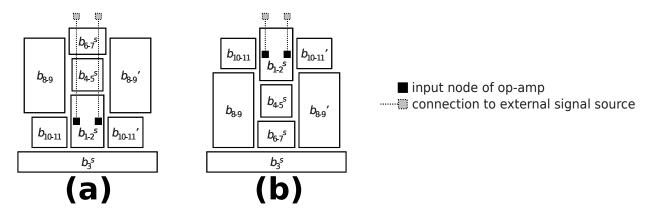

| 3.9  | Deux exemples de placement d'un amplificateur opérationel. (a) Les ports d'entrées sont placés au centre du groupe de modules symétriques (b) Les |          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | ports d'entrées sont placés en bordure du groupe de modules symétriques                                                                           |          |

|      | [10]                                                                                                                                              | 37       |

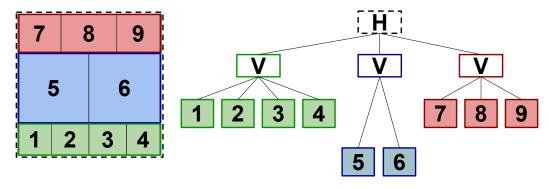

| 3.10 | Exemple de placement et sa représentation en <i>slicing tree</i> où "H" définit une                                                               | ٠.       |

| 0,10 | coupe horizontale et "V" une coupe verticale                                                                                                      | 38       |

| 3.11 | Exemple d'un placement représentable par un <i>slicing tree</i> (a) et d'un place-                                                                |          |

| 0.11 | ment non représentable (b)                                                                                                                        | 39       |

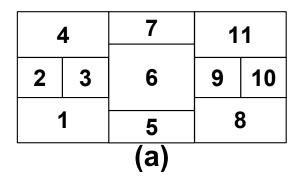

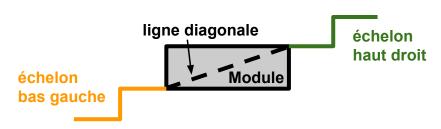

| 3.12 | Description d'un échelon positif pour un module                                                                                                   | 39       |

|      | (a) Échelons positifs résultant et $\Gamma_+ = ecadfb$ . (b) Échelons négatifs résul-                                                             | 00       |

| 0,10 | tant et $\Gamma_{-} = fcbead$ . [18]                                                                                                              | 40       |

| 3.14 | (a) Placement compact. (b) Représentation en $B^*$ -tree du placement com-                                                                        |          |

| 0111 | pact (a)                                                                                                                                          | 40       |

| 3.15 | (a) Une représentation en <i>O-tree</i> et (b) son placement correspondant. Pour                                                                  |          |

|      | ce placement de 8 modules, on a T= 0010110010110011 et $\pi$ =abcdefgh                                                                            | 41       |

| 3.16 | (a) Placement compact. (b) Représentation en <i>TCG</i> du placement compact                                                                      |          |

|      | (a)                                                                                                                                               | 42       |

| 3.17 | Notre approche permet la génération rapide de plusieurs placements                                                                                | 46       |

|      | Exemple d'écartement de placement autour du module D avec une repré-                                                                              |          |

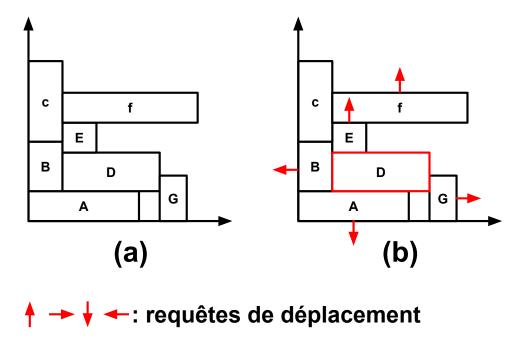

|      | sentation en <i>sequence pair</i>                                                                                                                 | 47       |

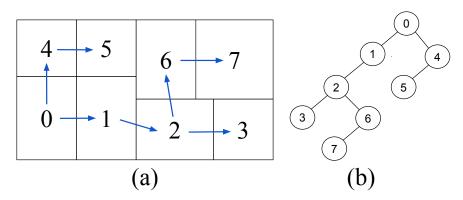

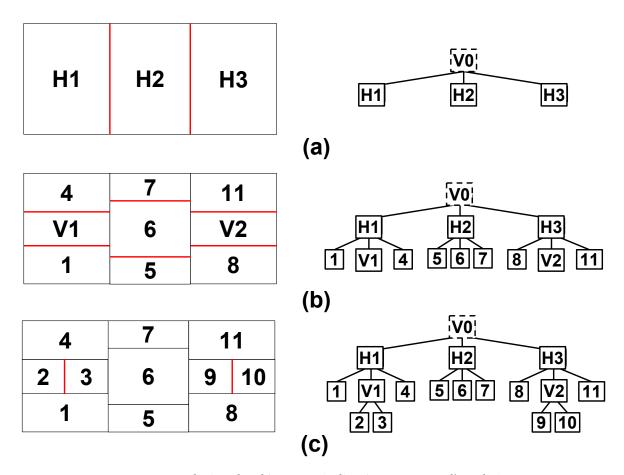

| 3.19 | Evolution des découpes (indiquées en rouge) d'un slicing tree                                                                                     | 48       |

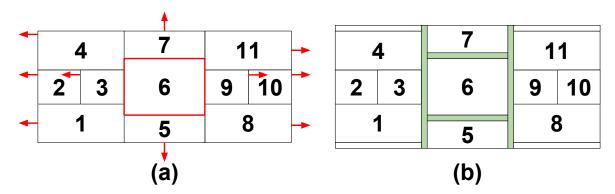

|      | Exemple de création d'espaces dédiés aux fils de routage. (a) Le module                                                                           |          |

|      | concerné et le déplacement des nœuds aux alentours du nœud 6 (b) Ré-                                                                              |          |

|      | sultat après écartement et en vert l'espace de routage créé autour du nœud                                                                        |          |

|      | 6                                                                                                                                                 | 49       |

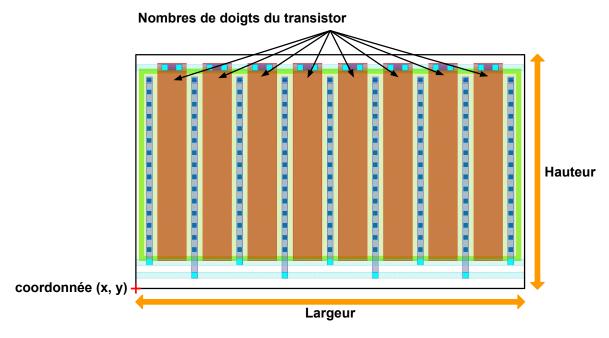

| 3.21 | Transistor simple à 8 doigts et la représentation de ses attributs                                                                                | 50       |

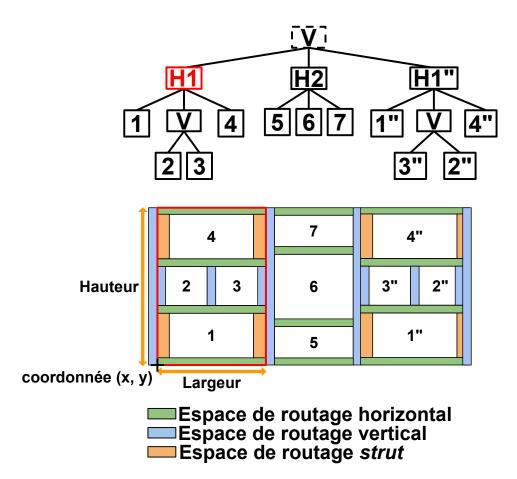

|      | Représentation des attributs d'un nœud hiérarchique                                                                                               | 52       |

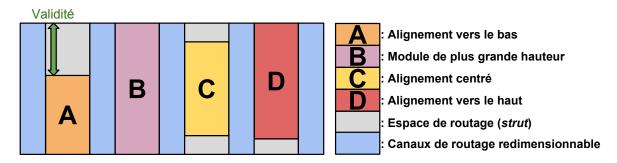

|      | Organisation en bande - Exemple de quatre modules (A, B, C et D) d'un                                                                             |          |

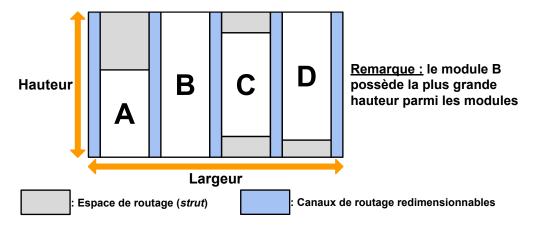

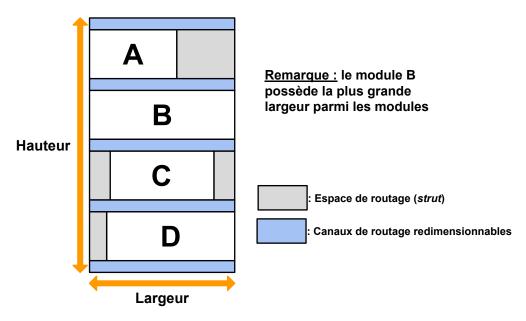

|      | nœud hiérarchique vertical                                                                                                                        | 52       |

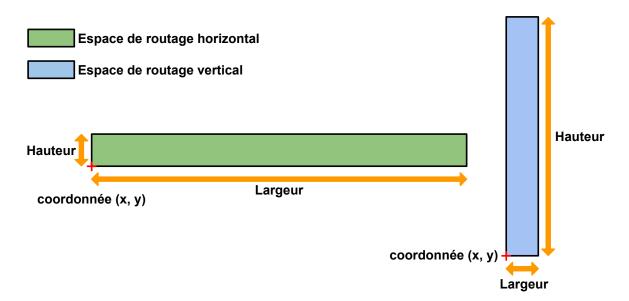

| 3.24 | Représentation des attributs d'un espace de routage vertical et d'un espace                                                                       |          |

|      | horizontal                                                                                                                                        | 54       |

| 3.25 | Hauteur et largeur d'un nœud hiérarchique vertical                                                                                                | 55       |

| 3.26 | Hauteur et largeur d'un nœud hiérarchique horizontal                                                                                              | 55       |

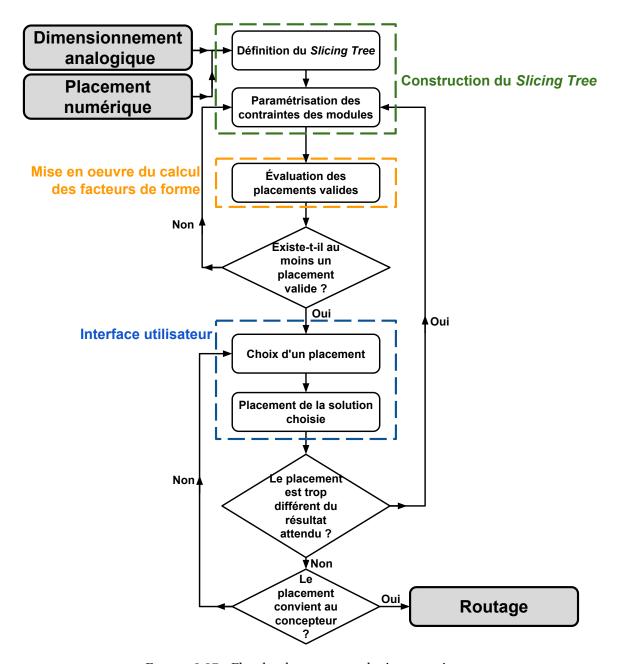

| 3.27 | Flot du placement analogique et mixte                                                                                                             | 58       |

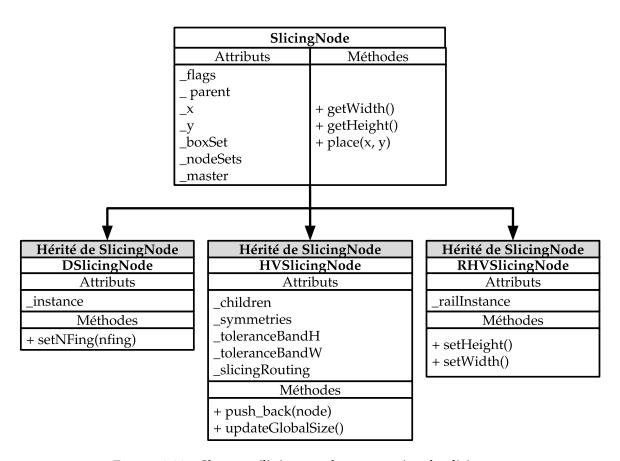

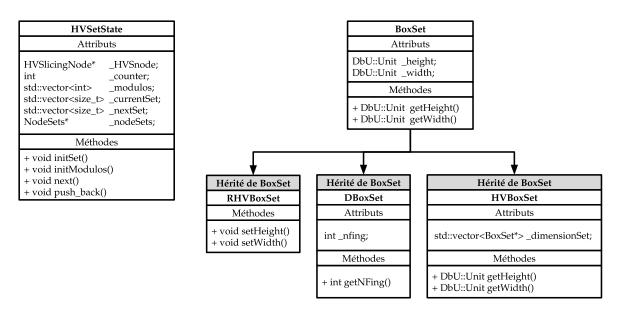

| 3.28 | Classes utilisées pour la construction du <i>slicing tree</i>                                                                                     | 59       |

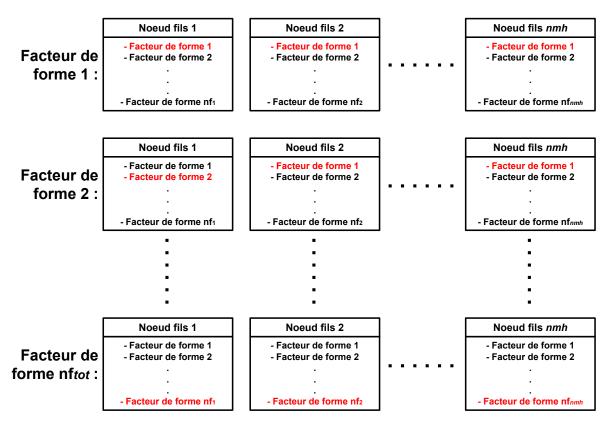

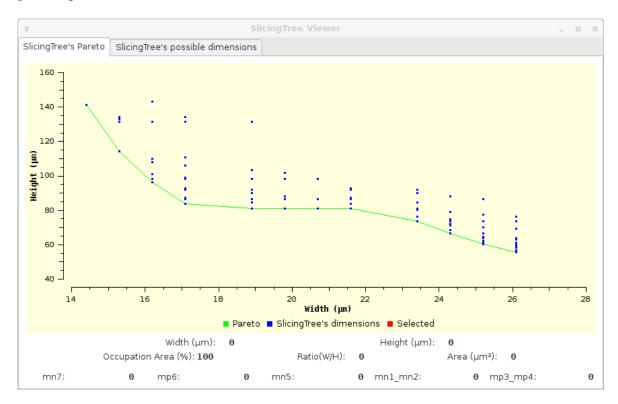

| 3.29 | Parcours des facteurs de forme possibles                                                                                                          | 65       |

| 3.30 | Classes utilisées pour évaluer et représenter les facteurs de forme                                                                               | 66       |

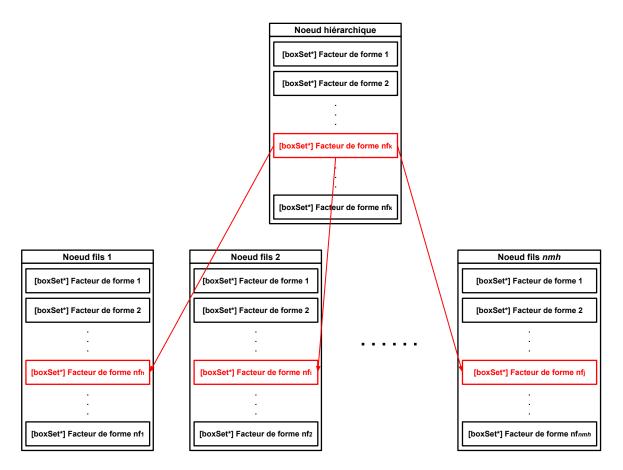

| 3.31 | Facteur de forme d'un nœud hiérarchique et celui de ses nœuds fils                                                                                | 67       |

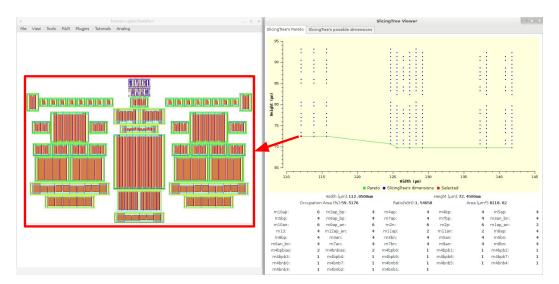

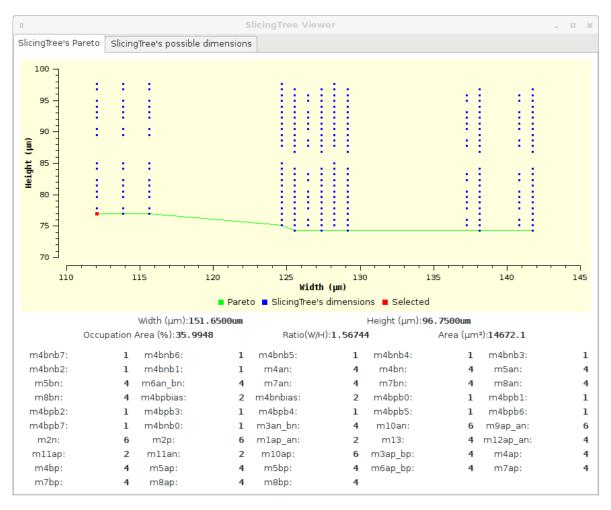

| 3.32 | Interface utilisateur - Graphe de points des facteurs de forme                                                                                    | 68       |

| 3.33 | Interface utilisateur - Visualisateur                                                                                                             | 69       |

| 3.34 | Interface utilisateur - Tableau des facteurs de forme                                                                                             | 70       |

|      |                                                                                                                                                   |          |

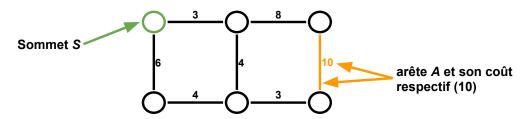

| 4.1  | Exemple de graphe de routage global $G(S, A)$                                                                                                     | 80       |

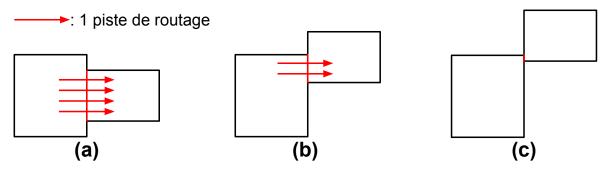

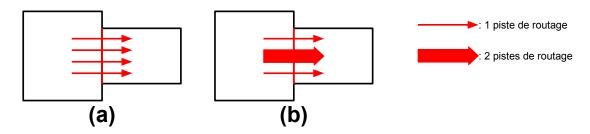

| 4.2  | (a) Arête avec une capacité de quatre pistes de routage (b) Arête avec une                                                                        |          |

|      | capacité de deux pistes de routage (c) Manque d'espace pour une piste de                                                                          | 0.1      |

| 4.0  | routage bien que les pavés soient adjacents                                                                                                       | 81       |

| 4.3  | Estimation de longueur d'un chemin dans un circuit numérique (a) et dans                                                                          | 01       |

| 1 1  | un circuit analogique (b)                                                                                                                         | 81<br>82 |

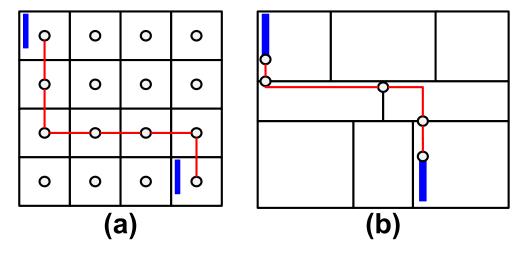

| 4.4  | OTADITE DE TOUTARE À UIT CITCUIT HUITIETIQUE (A) EL U UIT CITCUIT AHAIORIQUE (D)                                                                  | 02       |

| 4.5  | Représentation d'un <i>net</i> sur le graphe de routage d'un pavage numérique        |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | (a) et d'un pavage analogique (b)                                                    | 83  |

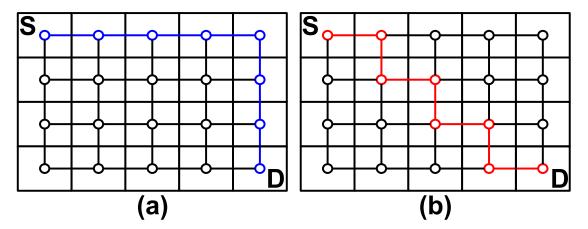

| 4.6  | Chemins connectant une source et une destination                                     | 84  |

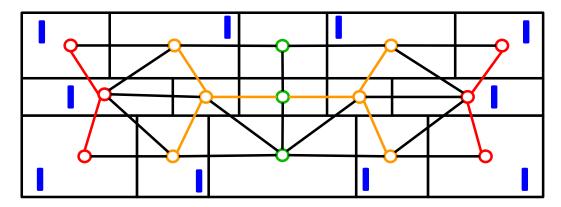

| 4.7  | Représentation de deux symétries : une paire de <i>nets</i> symétriques en rouge     |     |

|      | et un <i>net</i> dont les sommets sont symétriques en orange. Les sommets des        |     |

|      | pavés se trouvant sur l'axe de symétrie de ces deux <i>nets</i> sont représentés en  |     |

|      | vert                                                                                 | 84  |

| 4.8  | Occupation de pistes en fonction de la taille des fils. (a) est occupé par des       |     |

|      | fils avec un coût d'une 1 piste chacun (b) contient un fil avec une occupation       |     |

|      | de deux pistes de routage                                                            | 85  |

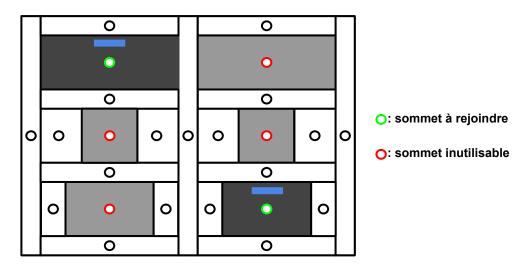

| 4.9  | Restriction d'accès de sommets du graphe de routage                                  | 85  |

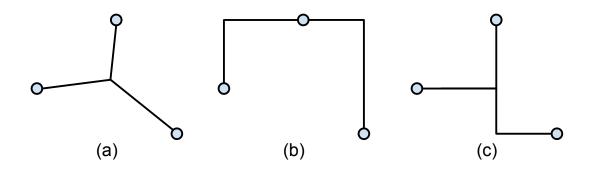

| 4.10 | (a) Arbre minimal de Steiner, (b) arbres de Steiner minimal rectilinéaire et (c)     |     |

|      | un arbre couvrant                                                                    | 86  |

| 4.11 | Exemple d'exploration exhaustive pour un <i>net</i> comprenant une source <i>S</i> , |     |

|      | une destination $D$ et un obstacle $(X)$                                             | 88  |

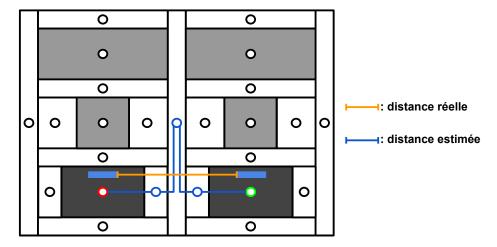

| 4.12 | Estimation de la longueur de fils d'un net d'un circuit analogique en utili-         |     |

|      | sant les distances centre à centre                                                   | 91  |

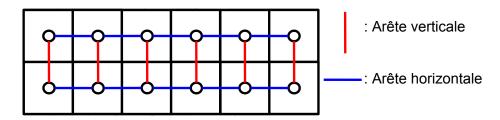

| 4.13 | Arêtes de type <i>horizontal</i> en bleu et <i>vertical</i> en rouge                 | 91  |

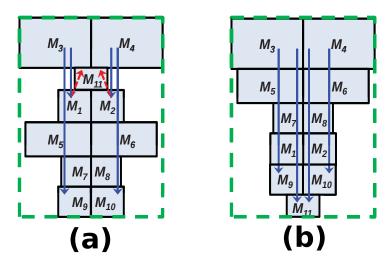

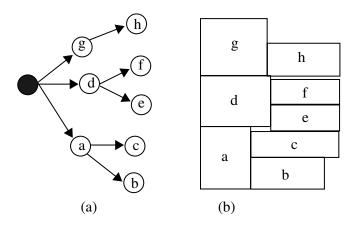

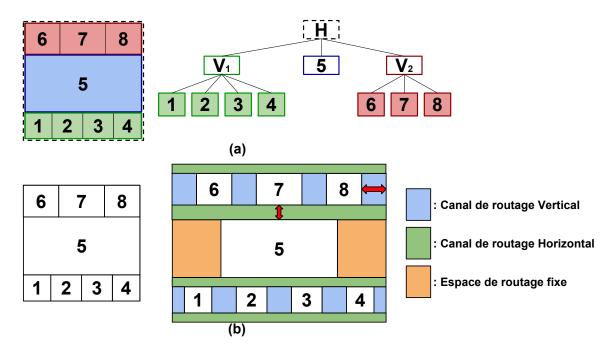

| 4.14 | Slicing tree d'un placement analogique (a) et la représentation de ses canaux        |     |

|      | de routage (b)                                                                       | 93  |

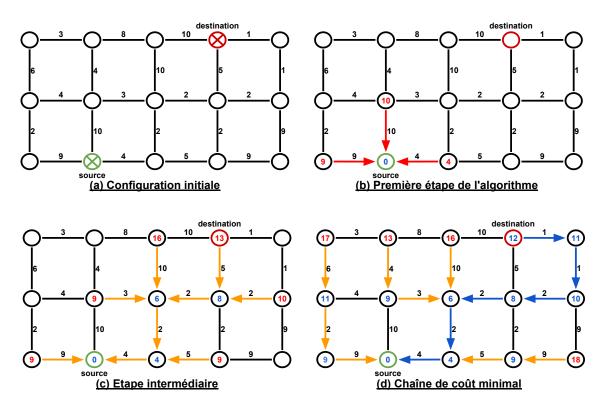

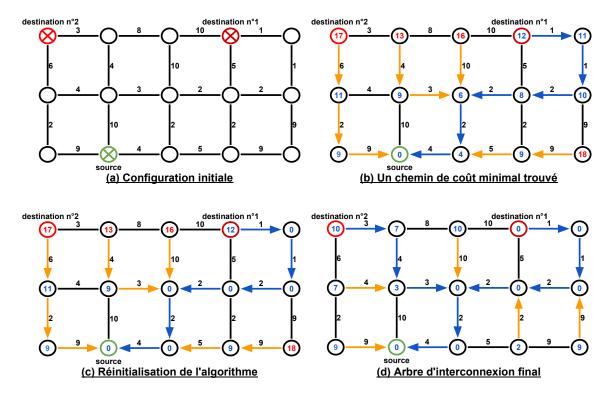

| 4.15 | Déroulement de l'algorithme de Dijkstra avec deux sommets à connecter .              | 95  |

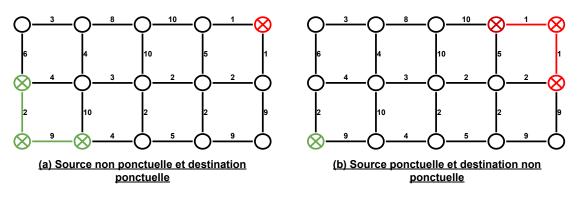

| 4.16 | Situations avec des sommets ponctuels et non ponctuels                               | 96  |

| 4.17 | Cas de composantes non ponctuelles                                                   | 97  |

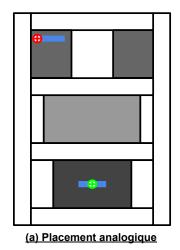

| 4.18 | Étape 0 - Placement analogique (a) et son graphe de routage correspondant            |     |

|      | (b)                                                                                  | 98  |

| 4.19 | Étape 1 - Estimation de coût de chemin (a) et leur graphe de routage corres-         |     |

|      | pondant (b)                                                                          | 99  |

| 4.20 | Étape 2 - Estimation de coût de chemin (a) et leur graphe de routage corres-         |     |

|      | pondant (b)                                                                          | 99  |

| 4.21 | Étape 3 - Estimation de coût de chemin (a) et son graphe de routage corres-          |     |

|      | pondant (b)                                                                          | 100 |

| 4.22 | Graphe de routage avec erreur d'estimation avec le chemin orange (a) et              |     |

|      | rouge (b)                                                                            | 100 |

| 4.23 | Estimation de coût de chemin (a) et son graphe de routage correspondant              |     |

|      | (b)                                                                                  | 101 |

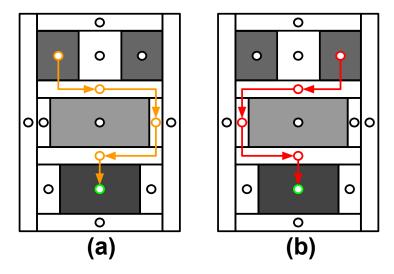

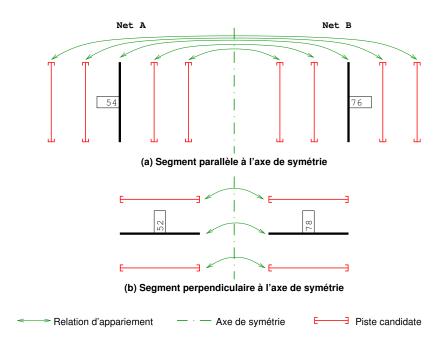

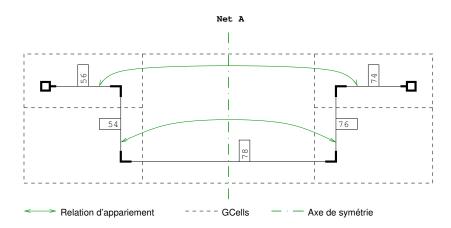

|      | Symétrie entre deux <i>nets</i>                                                      | 102 |

|      | Symétries entre sommets d'un <i>net</i> unique                                       | 102 |

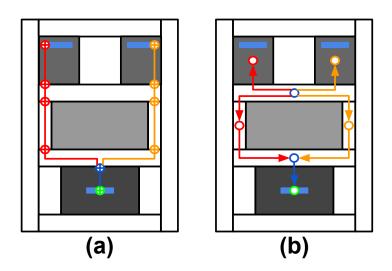

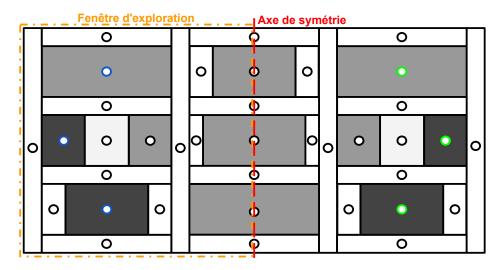

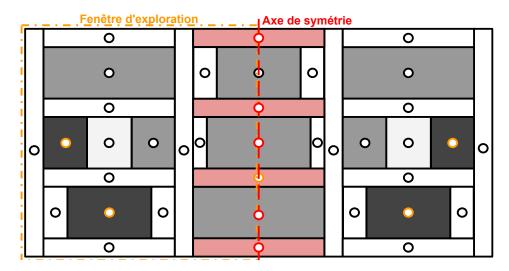

|      | Arbre d'interconnexions dans la fenêtre d'exploration                                | 103 |

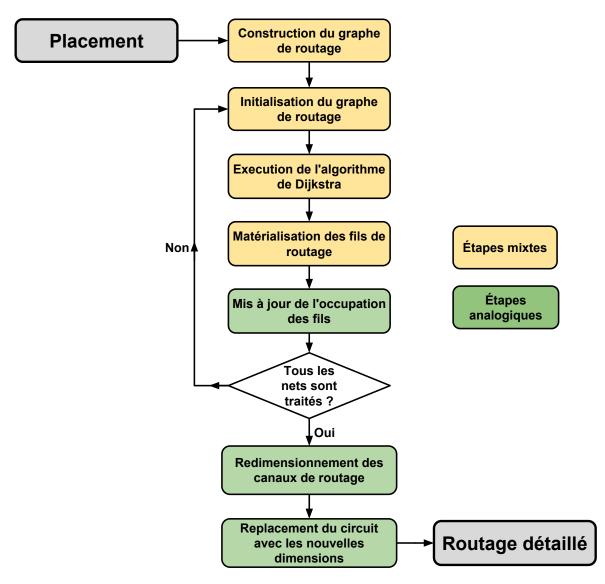

| 4.27 | Flot du routage global mixte. Les étapes numériques et analogiques du flot           |     |

|      | sont indiquées en jaune et les étapes concernant uniquement les étapes               |     |

|      | analogiques sont indiquées en vert                                                   | 104 |

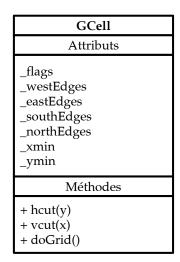

|      | Classes utilisées pour la construction du graphe de routage global                   | 106 |

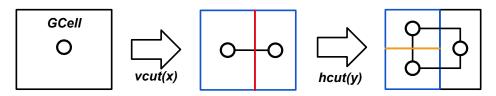

|      | Exemple d'utilisation des méthodes $vcut(y)$ et $hcut(x)$                            | 107 |

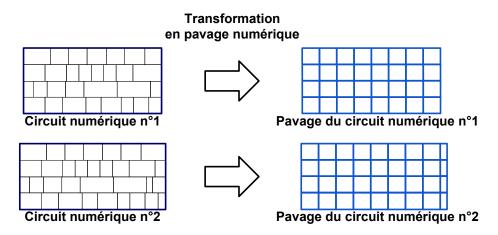

|      | Exemple de création de pavage numérique                                              | 107 |

|      | Création du pavage pour un nœud vertical d'un slicing tree                           | 108 |

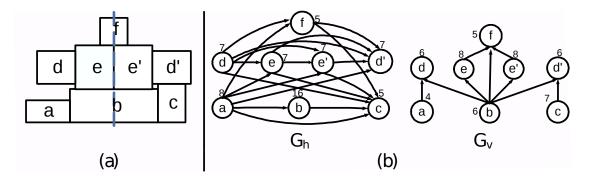

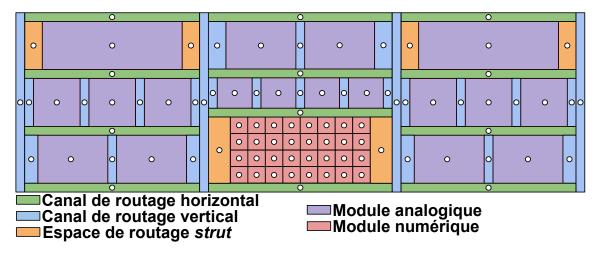

|      | Exemple de graphe de routage mixte                                                   | 108 |

|      | Classes utilisées pour l'algorithme de Dijkstra                                      | 109 |

|      | Étapes d'initialisation du graphe de routage                                         |     |

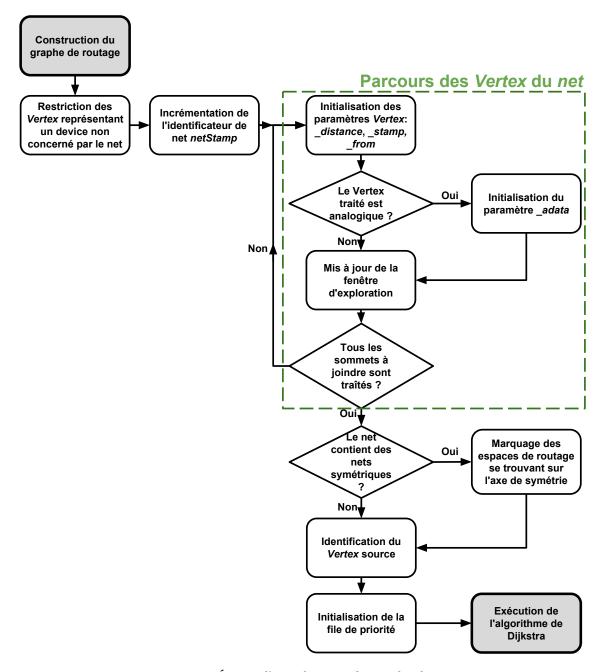

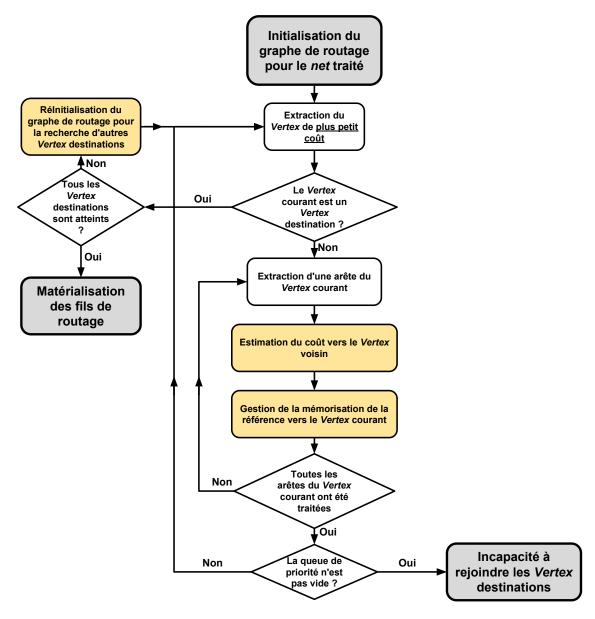

| 4.35 | Étapes du déroulement de la recherche d'arbres d'interconnexions                     | 113 |

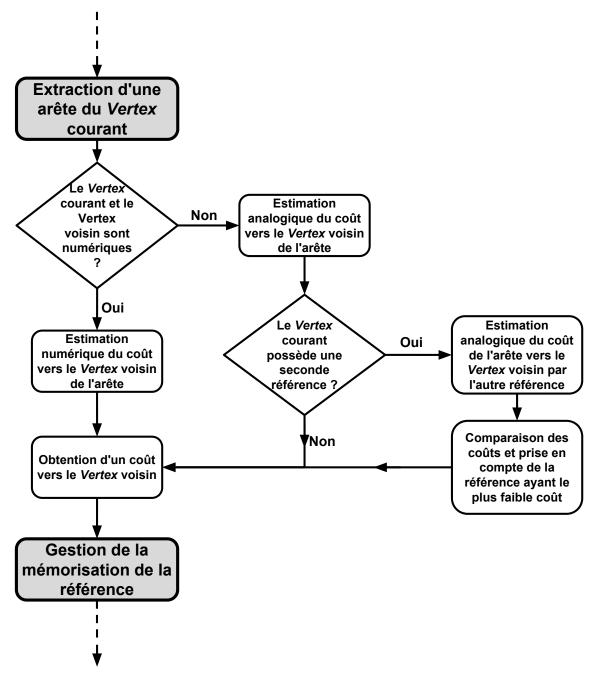

| 4.36 | Étapes de l'estimation du coût de l'arête en cours                                    | 114 |

|------|---------------------------------------------------------------------------------------|-----|

| 4.37 | Description de l'occupation d'un fil et de son coût en longueur dans un ca-           |     |

|      | nal de routage horizontal                                                             | 116 |

| 4.38 | Gestion d'estimation de coût de longueur avec un <i>Vertex</i> destination et un      |     |

|      | Vertex source                                                                         | 117 |

|      | Exemple de détection de présence de <i>VIAs</i>                                       | 117 |

| 4.40 | Gestion d'estimation de coût de longueur entre un Vertex numérique et un              |     |

|      | Vertex analogique                                                                     | 118 |

|      | Étapes de gestion de mémorisation de la référence                                     | 119 |

|      | Description de l'occupation d'un fil avec la classe <i>Interval</i>                   | 120 |

| 4.43 | Exemple de chemin de <i>Vertex</i> entre un Vertex source (sommet inférieur droit     |     |

|      | en vert) et un Vertex destination (sommet inférieur gauche en rouge)                  | 120 |

|      | Mise à jour des intervalles suite à l'atteinte d'un nouveau <i>Vertex</i> destination | 121 |

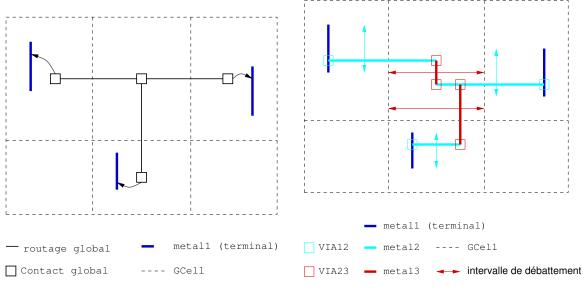

| 4.45 | Matérialisation des fils de routage global pour un exemple numérique (a)              |     |

|      | et un exemple analogique (b) pour un <i>net</i> . Les connecteurs à joindre sont      |     |

|      | représentés en bleu.                                                                  | 123 |

| 4.46 | Évolution de l'occupation de fils au sein d'un canal de routage horizontal            | 104 |

| 4 47 | après le traitement de quatre <i>nets</i> passant par cet canal de routage            | 124 |

|      | Méthodes des classes du <i>slicing tree</i> dédiées à l'étape de routage global       | 124 |

| 4.48 | Échanges d'informations entre la phase de placement et la phase de routage            | 127 |

| 5.1  | Exemple de fil électrique, routage global                                             | 131 |

| 5.2  |                                                                                       | 131 |

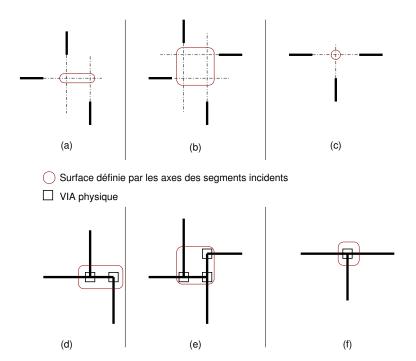

| 5.3  | Exemple de contacts non-ponctuels et ponctuels                                        | 132 |

| 5.4  | Exemple de décomposition en contacts ponctuels                                        | 133 |

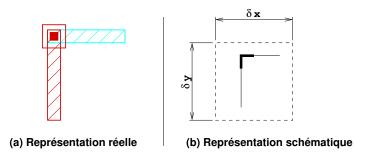

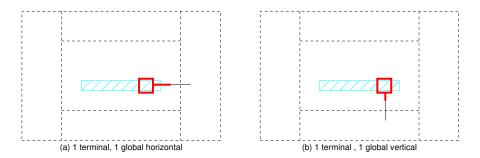

| 5.5  | Schéma du contact terminal                                                            | 133 |

| 5.6  | Schéma du coude ( <i>Turn</i> )                                                       | 134 |

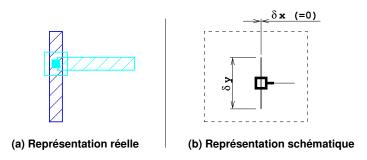

| 5.7  | Schéma de la branche horizontale ( <i>HTee</i> )                                      | 134 |

| 5.8  | Schéma de la branche verticale ( <i>VTee</i> )                                        | 135 |

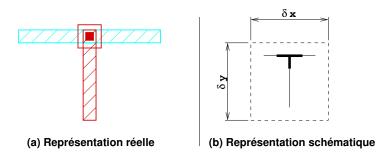

| 5.9  | Contrainte des segments globaux                                                       | 135 |

|      | Exemple d'ensemble de segments alignés                                                | 136 |

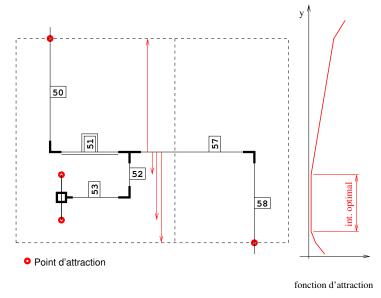

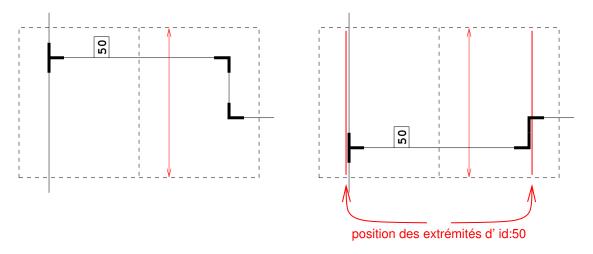

|      | Intervalle optimal, exemple avec perpendiculaires globaux seulement                   | 137 |

|      | Intervalle optimal, exemple avec perpendiculaires globaux et terminal                 | 137 |

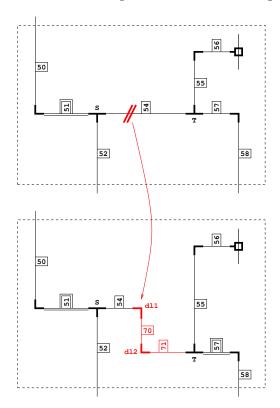

|      | Exemple de création de <i>dogleg</i>                                                  | 138 |

|      | Exemple de changement de <i>layer</i>                                                 | 139 |

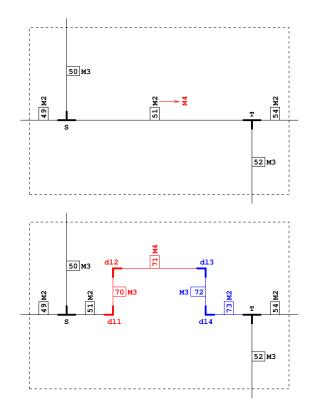

|      | Achèvement du routage d'un canal horizontal                                           | 140 |

|      | Achèvement d'un device                                                                | 141 |

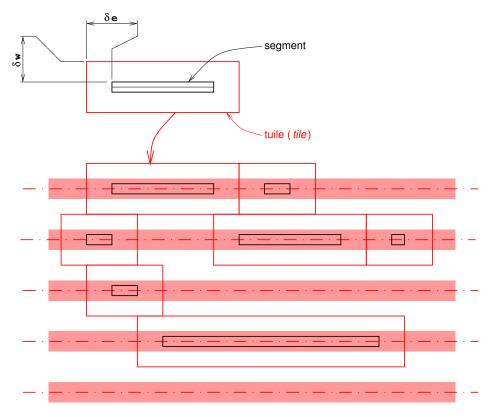

|      | Structure des pistes de routages                                                      | 141 |

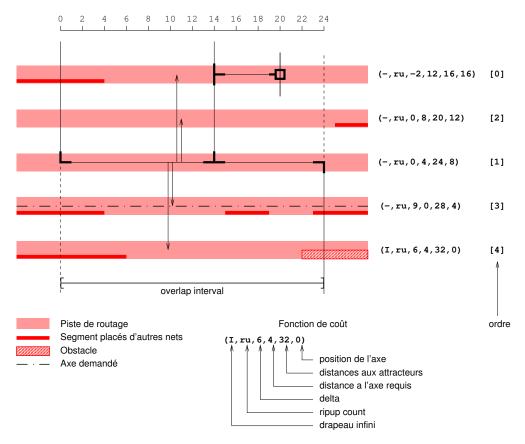

|      | Coulissage d'un segment                                                               | 142 |

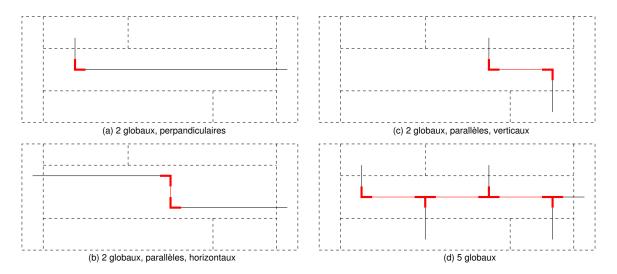

|      | Fonction de coût                                                                      | 145 |

|      | Rip-up des perpendiculaires                                                           | 146 |

|      | Suite au <i>rip-up</i> des perpendiculaires                                           | 147 |

|      | Résultat de la minimisation                                                           | 148 |

|      | Exemple de deux <i>nets</i> symétriques                                               | 149 |

|      | Appariement des coûts                                                                 | 149 |

|      | Exemple d'un <i>net</i> symétrique à lui-même                                         | 150 |

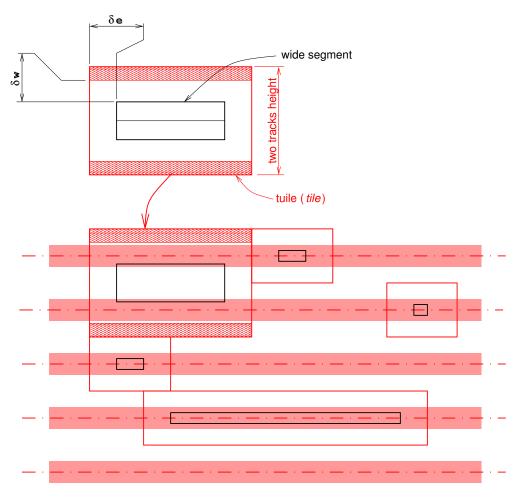

| 5.26 | Prise en compte des segments larges                                                   | 151 |

| 6.1  | Flot de conception mixte à travers les outils logiciels du LIP6                       | 154 |

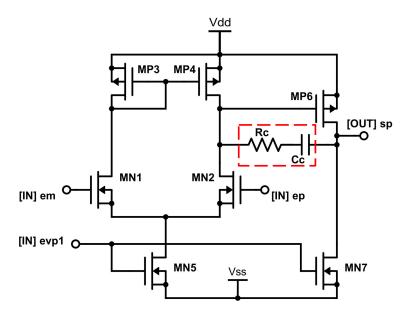

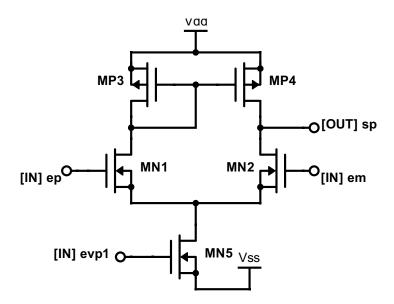

| 6.2  | Scháma álactrique de l'amplificateur Miller à transconductance                        | 155 |

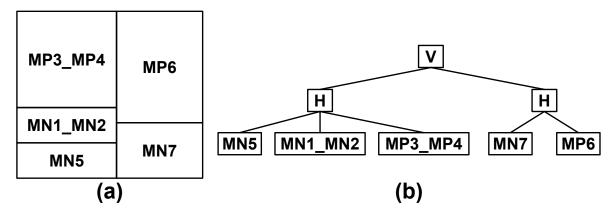

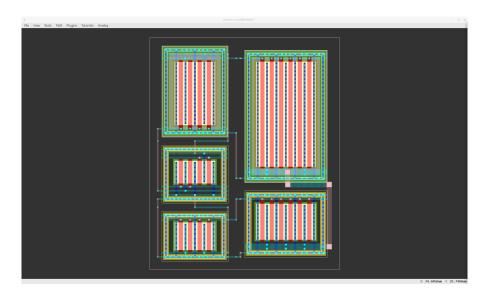

| 6.3  | Placement et <i>slicing tree correspondant</i> de l'amplificateur Miller     | 156 |

|------|------------------------------------------------------------------------------|-----|

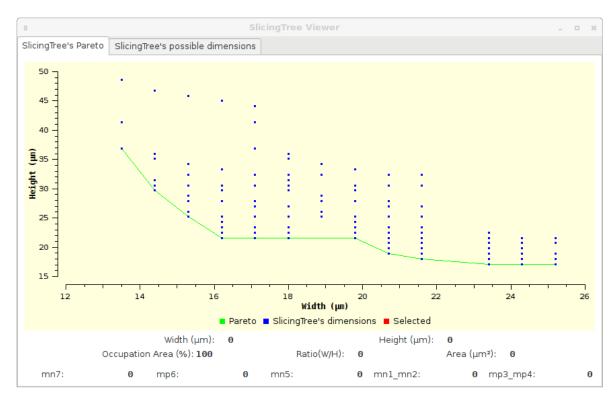

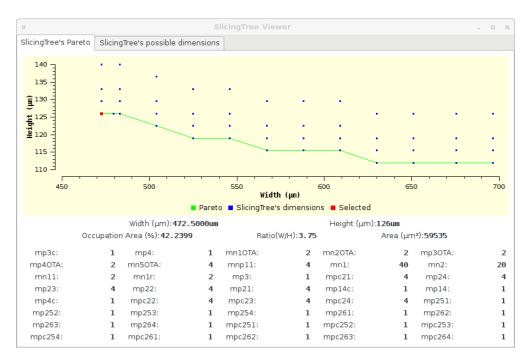

| 6.4  | Pour le dimensionnement 1 - Graphe de points des placements possibles .      | 158 |

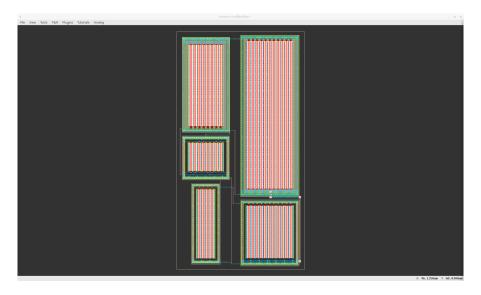

| 6.5  | Transistors de l'amplificateur Miller suite au routage global                | 159 |

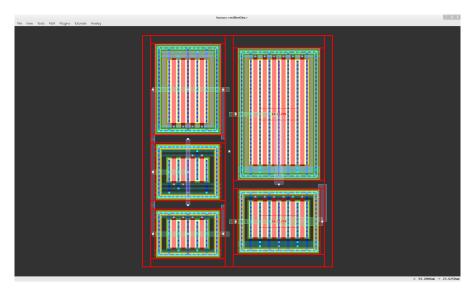

| 6.6  | Amplificateur Miller (sans la résistance et la capacité) placé et routé      | 159 |

| 6.7  | Pour le dimensionnement 2 - Graphe de points des placements possibles .      | 160 |

| 6.8  | Routage global des transistors de l'amplificateur Miller, dimensionnement 2  | 161 |

| 6.9  | Transistors de l'amplificateur Miller placés et routés, dimensionnement 2 .  | 161 |

| 6.10 | Schéma électrique de l'amplificateur à source de courant ajustable           | 162 |

| 6.11 | Schéma électrique de la polarisation                                         | 162 |

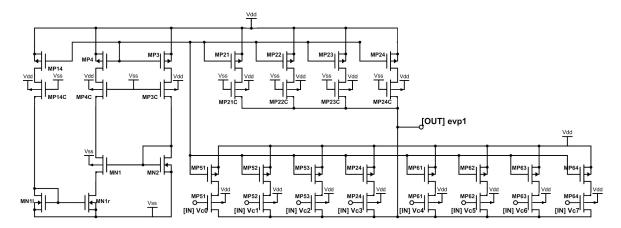

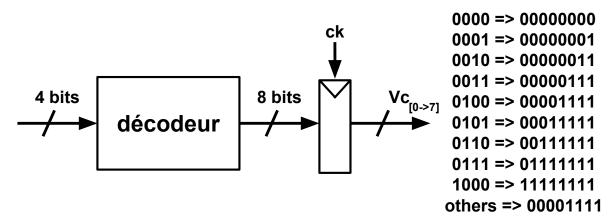

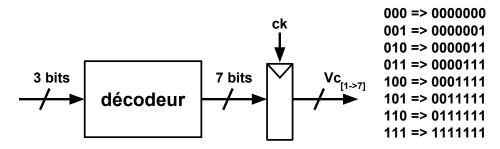

| 6.12 | Décodeur numérique contrôlant la polarisation                                | 163 |

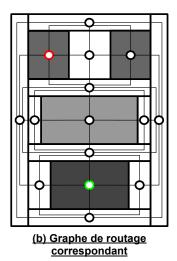

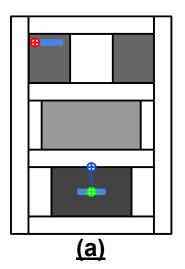

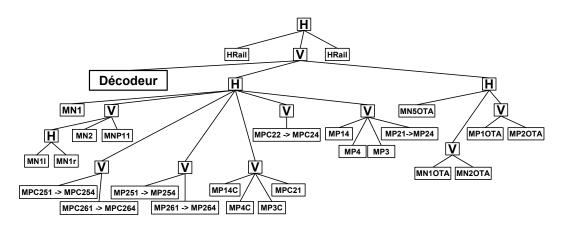

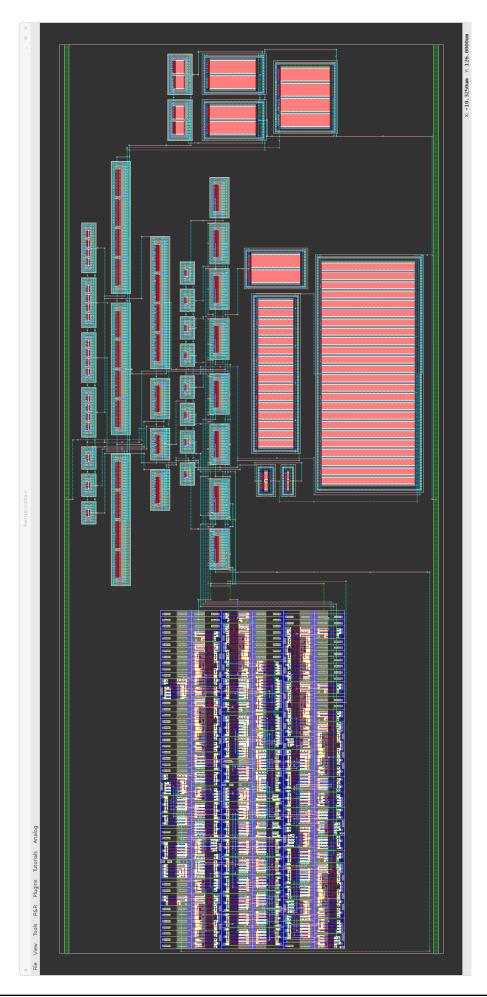

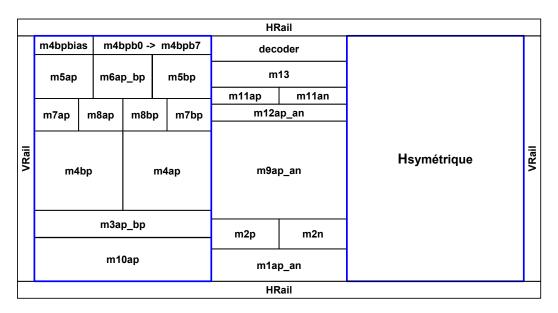

| 6.13 | Placement de l'amplificateur à source de courant ajustable                   | 163 |

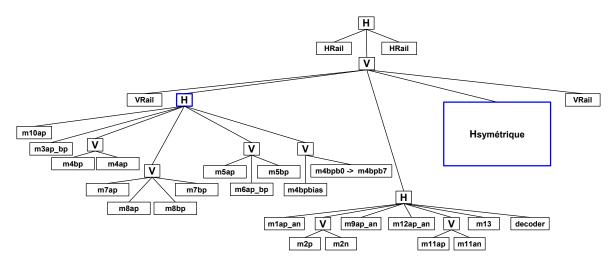

| 6.14 | Slicing tree du placement de l'amplificateur à source de courant ajustable . | 164 |

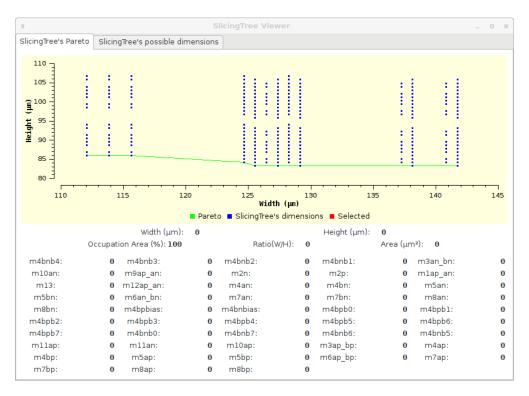

| 6.15 | Graphe de points des placements possibles                                    | 164 |

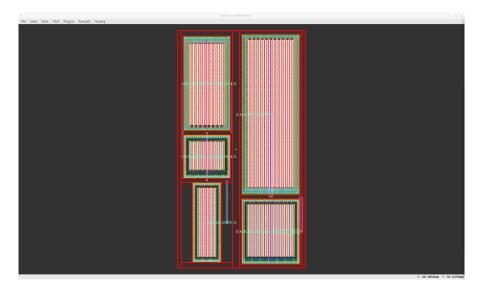

| 6.16 | Amplificateur à source de courant ajustable placé et routé                   | 165 |

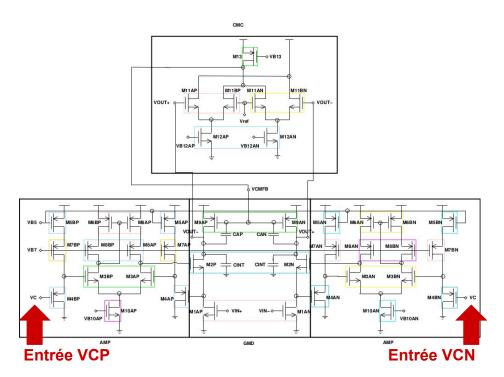

| 6.17 | Schéma électrique de la transconductance différentielle contrôlable          | 166 |

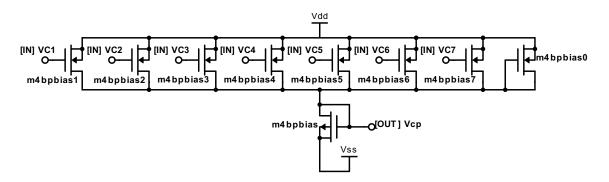

| 6.18 | Circuit intermédiaire entre les sorties du décodeur et de l'entrée VC        | 166 |

| 6.19 | Décodeur numérique contrôlant la tension d'entrée VC de la transconduc-      |     |

|      | tance différentielle                                                         | 167 |

| 6.20 | Placement de la transconductance différentielle configurable                 | 167 |

| 6.21 | Slicing tree du placement de la transconductance différentielle configurable | 168 |

| 6.22 | Graphe de points des placements possibles                                    | 169 |

| 6.23 | Transconductance différentielle configurable placée et routée                | 170 |

### Liste des tableaux

| 2.1 | De Cairo à Coriolis                                                            | 22 |

|-----|--------------------------------------------------------------------------------|----|

| 3.1 | Tableau récapitulatif de l'état de l'art des représentations de placement pour |    |

|     | les circuits analogiques                                                       | 43 |

### **Chapitre 1**

### Introduction

#### Sommaire

| 1.1 Contexte                                         | 2 |

|------------------------------------------------------|---|

| 1.2 Conception du dessin des masques mixtes actuelle | 3 |

| 1.3 Enjeux et motivations                            | 5 |

| 1.4 Contributions de cette thèse 6                   | 3 |

| 1.5 Plan de la thèse 7                               | 7 |

| 1.6 Références                                       | 3 |

#### 1.1 Contexte

Au cours de ces dernières décennies, les circuits analogiques ont pris une place particulièrement importante dans les systèmes sur puce dont les applications sont diverses telle que la télécommunication, l'automobile, l'internet des objets ou encore l'ingénierie médicale. Bien que la plupart des fonctionnalités de ces circuits intégrés soient implémentées en circuit numérique, des fonctionnalités requièrent des circuits analogiques faisant le lien avec le monde extérieur. Une étude réalisée par *IC Insights*[1] prévoit une augmentation des ventes des circuits intégrés sur les cinq prochaines années à venir.

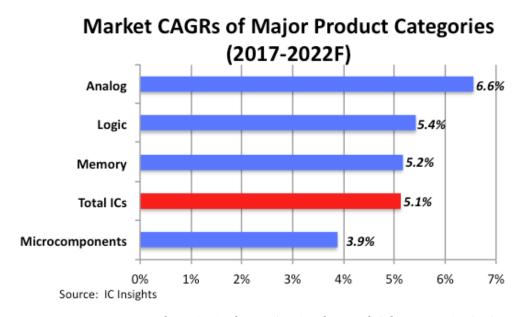

FIGURE 1.1 – Croissance des principales catégories de marché de circuits intégrés[1]

La figure 1.1 présente les estimations de l'étude sur la croissance des principales catégories de marché de circuits intégrés. On y observe en particulier que la croissance totale des ventes de tous les circuits intégrés augmentera de 5.1% et que celle des circuits analogiques est estimée comme étant la plus forte sur l'ensemble des marchés des circuits intégrés avec une croissance de 6.6%.

Malgré le besoin de circuits analogiques et de leur aptitude à être intégrés à des systèmes sur puce, les outils logiciels d'automatisation de conception de circuits analogiques restent bien moins avancés que ceux dédiés aux circuits numériques. Cela est dû à la complexité du problème de la conception de circuits analogiques :

- Il existe un grand nombre de classes de circuits spécifiques.

- Chaque classe de circuits nécessite sa propre approche de conception.

- Les circuits analogiques sont sensibles aux bruits et aux effets parasites liés aux procédés de fabrication.

La complexité de la conception de circuit analogique a pour conséquence que la conception reste "manuelle" afin de garder un maximum de contrôle sur l'ensemble des paramètres du circuit tout au long du flot de conception. En particulier, la conception du dessin des masques est une tâche de plus en plus fastidieuse avec l'augmentation du nombre

de règles de dessin des nouvelles technologies submicroniques. Il en résulte que ce processus est long et sujet à des erreurs. De manière générale, l'effort de conception de la partie analogique d'un circuit mixte est bien plus importante que celle de la partie numérique. Avec l'évolution des technologies de plus en plus fines couplée avec la constante augmentation de la demande, la conception de circuit analogique manuelle finira par nécessiter un effort de conception trop conséquent.

L'objectif de cette thèse consiste à proposer une méthodologie de conception de circuit mixte permettant d'accélérer la conception en automatisant certaines parties de la conception du dessin des masques mixte.

Avant de rentrer plus en détails dans notre approche, il est important de comprendre les limites du flot de conception actuel des circuits mixtes.

#### 1.2 Conception du dessin des masques mixtes actuelle

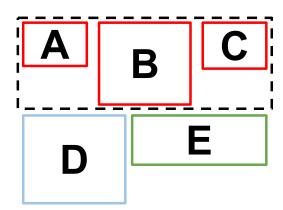

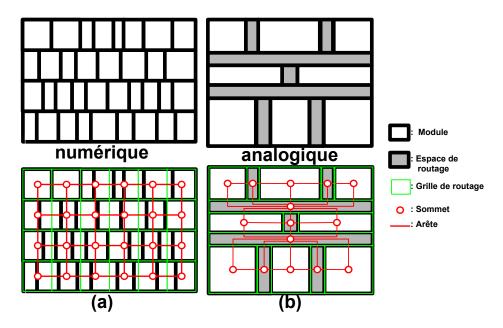

Un circuit dit mixte est un circuit comportant des parties analogiques et des parties numériques. L'association de ces deux différents types de circuits est complexe car leur flot de conception est différent, en particulier en ce qui concerne la conception du dessin des masques. Le flot de conception du dessin des masques des circuits numériques et des circuits analogiques est présenté par la figure suivante :

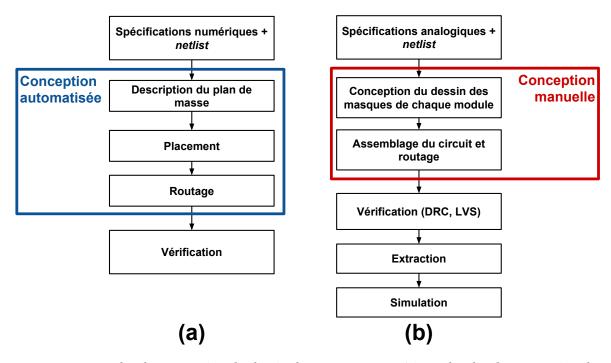

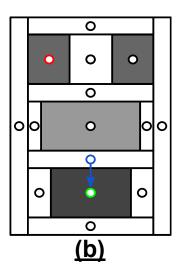

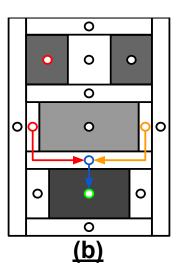

${\it Figure~1.2-(a)~Flot~de~conception~du~dessin~des~masques~num\'erique~(b)~Flot~de~conception~du~dessin~des~masques~analogique}$

Sur la figure 1.2.(a), le flot de conception du dessin des masques des circuits numériques se déroule suivant ces étapes majeures :

- **Description du plan de masse** : Définition des dimensions du circuit comprenant des informations telles que la taille des fils d'alimentation.

- Placement : Placement de l'ensemble des cellules standard représentant le circuit.

- **Routage** : Routage du signal d'horloge et routage des *nets* du circuit en deux phases (routage global et routage détaillé).

- Vérification : Vérification des règles de dessin et des contraintes de timing du circuit.

Les étapes de placement et de routage des circuits numériques sont les principales étapes de la conception du dessin des masques et sont automatisées. Cela implique que la création et le positionnement des couches de métaux sont réalisés par le biais d'outils logiciels capables de placer et router ces couches de métaux à partir des règles de dessins et des contraintes de timing d'une technologie donnée.

Sur la figure 1.2.(b), le flot de conception du dessin des masques des circuits analogiques se déroule suivant ces étapes majeures :

- Conception du dessin des masques de chaque module : Création des fils de métaux réalisant la fonctionnalité de chaque module du circuit suivant les règles de dessins de la technologie donnée.

- **Assemblage du circuit et routage** : Placement du dessin des masques de modules et création des couches de métaux joignant les connecteurs des *nets*.

- Vérification :

- Vérification (DRC, LVS): Vérification des règles de dessin et de la correspondance avec le schéma électrique initialement désiré.

- **Extraction**: Extraction des effets parasites liés aux procédés de fabrication.

- **Simulation**: Simulation du circuit *post layout*.

L'ensemble des étapes de conception implique le dimensionnement et le positionnement de toutes les couches de métaux du circuit tout en prenant soin de respecter les règles de dessin et les contraintes d'électromigration. Ces deux tâches sont réalisées manuellement. Si durant l'une de ces étapes les spécifications ne sont pas respectées, il est nécessaire de revenir à l'étape précédente voire de devoir recourir à un redimensionnement du circuit entrainant une nouvelle redéfinition complète du dessin des masques. Ces itérations peuvent engendrer des efforts de conception importants et coûteux en temps.

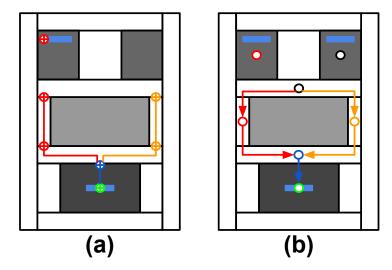

Dans le cas de la conception de circuits mixtes, il n'existe pas de flot de conception unique utilisé pour la conception de tous les circuits mixtes mais il existe deux approches de conception du dessin des masques qui sont les suivantes :

- Approche *digital-on-top*: Cette approche consiste à employer le flot de conception numérique, en particulier les logiciels dédiés à la conception de circuit numérique, pour concevoir le circuit mixte. La partie analogique, préalablement placée et routée avec le flot de conception analogique, est introduite comme une boite noire qui doit être placée au sein du plan de masse du circuit complet et être routée avec la partie numérique.

- Approche *analog-on-top*: Cette approche consiste à employer le flot de conception analogique pour concevoir le circuit mixte. Avec cette approche, la partie numérique, préalablement placée et routée avec le flot de conception numérique, est placée et routée avec la partie analogique manuellement. Il est également courant que les concepteurs souhaitent concevoir la partie numérique dans son intégralité en utilisant le flot de conception analogique uniquement.

Les concepteurs de circuits mixtes sont confrontés à une situation où ils doivent choisir entre un flot purement analogique et un flot purement numérique, chacun des deux ignorant l'autre. Les concepteurs ont complètement à leur charge de communiquer de façon ad-hoc des informations pertinentes entre les parties analogiques et numériques. Suite à ces observations sur les limites de la conception de circuits analogiques et mixtes, on peut en déduire les problématiques suivantes :

- **Problématique 1**: La conception manuelle du dessin des masques analogiques devient de plus en plus complexe avec l'augmentation du nombre de règles de dessins pour les nouvelles technologies. Un circuit analogique doit également être à nouveau dimensionné en cas de spécifications non respectées mais également pour toutes nouvelles technologies utilisées rendant le dessin des masques d'un circuit analogique non réutilisable.

- **Problématique 2**: Chacune des approches de conception de circuits mixtes entrainent des pertes d'informations. Dans le cas de l'approche *digital-on-top*, il est difficile d'intégrer des contraintes analogiques à travers les outils logiciels dédiées au placement routage numérique. Dans l'approche *analog-on-top*, la conception de modules supplémentaires alourdit davantage la problématique précédente.

#### 1.3 Enjeux et motivations

Le laboratoire d'informatique de Paris 6 (LIP6) s'intéresse au développement de méthodes de conception des composants numériques et analogiques pouvant être intégrés dans des systèmes sur puce depuis plus d'une vingtaine d'années. Le laboratoire a également lancé plusieurs *starts-ups* au cours de ces dernières années tels que FlexRas sur le partitionnement FPGA récemment acquis par Mentor Graphics, Intento Design sur la synthèse électrique et l'optimisation automatique des circuits analogiques, et Seamless Waves sur la radio cognitive. Ces faits montrent l'expérience en termes de conception de circuits numériques et analogiques au LIP6.

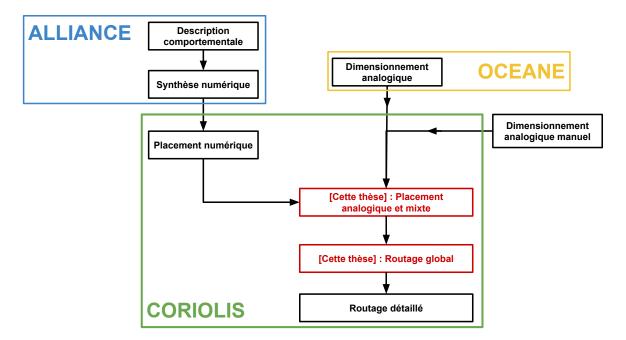

Le laboratoire est la source de plusieurs logiciels qui sont le fruit de travaux de thèse et de développement et sont dédiés à la réalisation de circuits numériques et de circuits analogiques :

- **Coriolis**[2]: pour le placement et le routage des circuits CMOS.

- Alliance[3]: un flot de CAO VLSI, incluant une bibliothèque de cellules standards.

- OCEANE[4]: pour le dimensionnement de fonctions analogiques intégrées sur silicium.

- TAS[5]: un outil d'analyse temporelle.

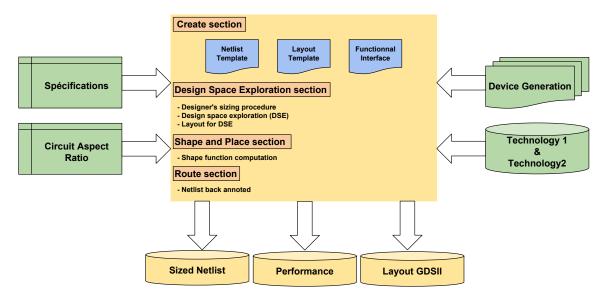

Initialement dédié aux circuits numériques, **Coriolis** comporte une extension de sa base de données dédiées à la conception de circuits analogiques appelé *CHAMS* (Cairo Hurricane AMS). Des travaux de thèse antérieurs ont enrichi cette base de données en y incorporant une bibliothèque de cellules analogiques permettant la génération du dessin des masques de blocs analogiques de base.

L'expérience de conception de circuits et de développement logiciels dédiés à la conception de circuits font partie des motivations pour proposer une solution aux problématiques de conception de circuits analogiques et mixtes.

#### 1.4 Contributions de cette thèse

L'objectif de cette thèse consiste à répondre aux problématiques de la partie 1.2 en proposant une approche de conception de circuits mixtes. Pour cela, la contribution de cette thèse consiste à définir un environnement de conception assistée unifié pour les blocs numériques et analogiques au niveau dessin des masques. Il s'agira d'offrir au concepteur un contrôle fin des phases de placement et routage tout en garantissant une automatisation partielle des tâches et une communication fluides des informations d'une part entre le dimensionnement électrique et le dessin des masques, et d'autre part entre les blocs analogiques et les blocs numériques.

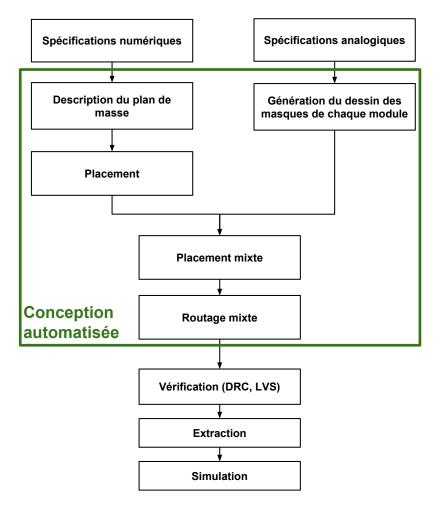

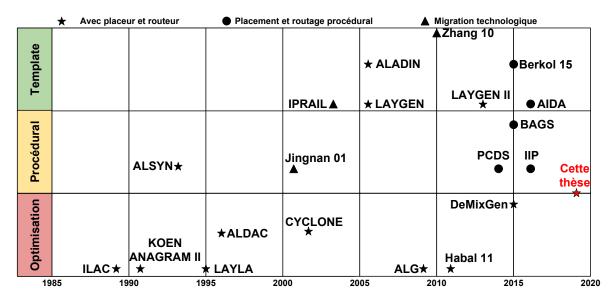

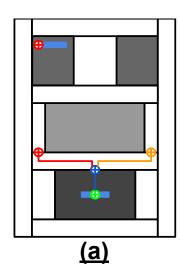

La méthodologie de conception de circuits mixtes que nous proposons repose sur l'uniformisation du flot de conception numérique et analogique. Nous jugeons nécessaire l'uniformisation de ces deux flots de conception dans le cadre de la conception de circuits mixtes. De par la nature du problème de la conception de circuit numérique, on souhaite préserver la distinction des étapes de placement, de routage global et de routage détaillé. C'est pourquoi notre approche de conception sera composée des étapes illustrées par la figure 1.3.

FIGURE 1.3 - Flot de conception mixte : unification du flot de conception numérique analogique

Unifier les flots de conception implique d'unifier les structures de données d'un point de vue logiciel. La qualité de l'architecture logicielle a un impact important sur l'exploita-

tion des ressources du circuit et l'efficacité des algorithmes exécutés. Notre architecture logicielle a été pensée avec l'optique de préserver la rapidité d'exécution des algorithmes de placement routage numérique qui nécessitent de manipuler un gros volume de données tout en étant capable d'appliquer des contraintes spécifiques aux circuits analogiques. Cela est réalisé à travers l'utilisation de classes communes qui sont enrichies pour les adapter aux problèmes du placement routage analogique.

Avec cette approche d'unification des deux flots de conception, nous souhaitons préserver au mieux l'efficacité des deux flots de conception. Le risque, en unifiant ces modes de conception, est de les détériorer en augmentant trop le volume de données à manipuler et le temps d'exécution. Les résultats présentés dans cette thèse montrent que ces risques sont limités.

L'objectif de cette thèse consiste à développer une méthodologie de placement routage mixte permettant de répondre aux problèmes liés au monde numérique et analogique afin d'unifier au mieux ces deux flots de conception. Les contributions de cette thèse sont les suivantes :

#### • Placement analogique et mixte :

- Définition d'une méthodologie de placement analogique et mixte faisant intervenir l'expérience du concepteur et lui donnant du contrôle durant l'intégralité de la phase de placement.

- Recherche de solution de placement en se basant sur la description d'un placement relatif à partir d'un *slicing tree* fourni par le concepteur comprenant en plus les contraintes de placement qu'il souhaite considérer.

- Interface graphique permettant la visualisation des solutions de placement.

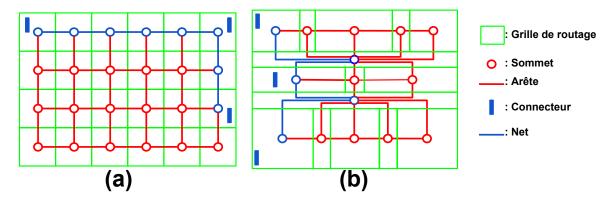

#### • Routage global mixte:

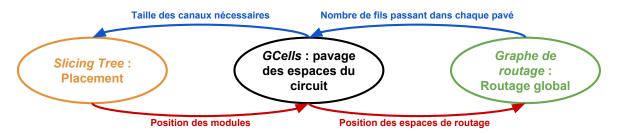

- Transformation d'un placement obtenu en un graphe de ressources de routage en représentant le circuit sous la forme d'un pavage pouvant représenter un module analogique ou numérique ou un espace de routage.

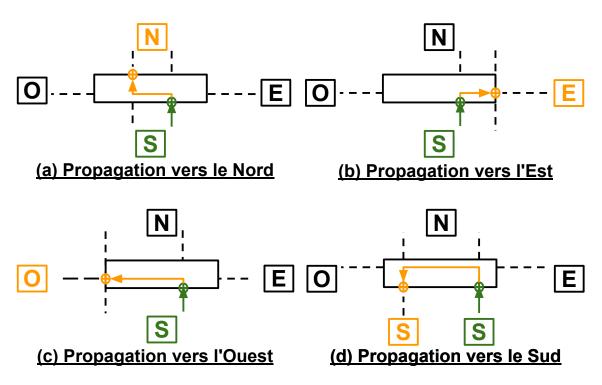

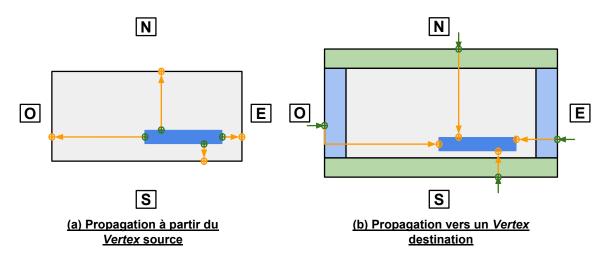

- Recherche de chemins d'interconnexions à travers les pavés pour l'ensemble des *nets* du circuit en utilisant un algorithme de Dijkstra adapté au problème du routage mixte. Estimation de longueurs de fils spécifiques aux *nets* analogiques à partir de la topologie du circuit en *slicing tree*.

- Redimensionnement des canaux de routage à partir du *slicing tree*.

- Routage détaillé : Construction des fils de routage à partir du résultat du routage global. Création des éléments atomiques du routage détaillé manipulés pour la résolution des superpositions des fils.

#### 1.5 Plan de la thèse

Ce manuscrit de thèse est organisé en 5 parties principales :

• Chapitre 2 - Etat de l'art : Ce chapitre présente l'état de l'art des outils logiciels d'automatisation de la conception analogique et mixte. L'ensemble des approches étudiées au cours de ces 20 dernières années y sont présentées et comparées afin de comprendre les approches précédemment étudiées. Le laboratoire d'informatique de Paris 6 est la source de plusieurs chaînes d'outils de CAO dédiées à la conception

- de circuits intégrés. Un historique des travaux précédents y sera présenté afin de pouvoir situer le contexte dans lequel s'inscrit cette thèse .

- Chapitre 3 Placement : Ce chapitre décrit le problème du placement mixte et les contraintes de placements les plus communément considérées. Un état de l'art spécifique aux approches de placement analogiques et mixtes y est décrit. On s'intéresse particulièrement au dessin des masques analogiques car elle est l'une des parties limitantes de la conception mixte. La description théorique et l'implémentation de notre méthodologie de placement mixte y est décrite ainsi que les raisons pour lesquelles nous avons choisi notre approche.

- Chapitre 4 Routage global : Ce chapitre présente le problème du routage global et les contraintes à prendre en compte pour les *nets* numériques et les *nets* analogiques. La phase de routage global a été particulièrement étudiée à travers des travaux passés au LIP6, une étude de l'état de l'art du routage analogique y est présentée. Ce chapitre contient également la description théorique de notre approche de routage global mixte et de son implémentation logicielle.

- Chapitre 5 Routage détaillé: Ce chapitre présente le routeur détaillé mixte et est le résultat de plus de 10 ans de travail dédié dans un premier temps aux circuits numériques. Ce routeur détaillé est particulièrement configurable et son fonctionnement a été enrichi pour prendre en compte les contraintes du routage analogique. Les travaux liés au routeur détaillé et réalisés dans le cadre de cette thèse y sont présentés ainsi qu'une description résumée du fonctionnement du routeur détaillé. Ce chapitre consiste à démontrer la capacité à utiliser le résultat du routage global pour obtenir un circuit complètement routé.

- Chapitre 6 Résultat : Ce chapitre contient 3 circuits de tailles différentes sur lesquels notre approche de placement routage mixte a été utilisée afin de produire un dessin des masques placé et routé. Les étapes de placement et de routage mixtes y sont décrites en détails ainsi que les informations pertinentes telles que la surface occupée, le nombre de segments et contacts créés et la longueur total de fils de routage.

#### 1.6 Références

- [1] IC Insight Research Bulletins. Analog ic market forecast with strongest annual growth through 2022, 2018. ix, 2

- [2] Christian Masson Gabriel Gouvine Sophie Belloeil Damien Dupuis Christophe Alexandre Hugo Clement Marek Sroka Jean-Paul Chaput, Rémy Escassut and Wu Yifei. Coriolis, 2018. 5

- [3] Alain Greiner and François Pêcheux. Alliance : A complete set of CAD tools for teaching vlsi design. 1992. 5

- [4] Jacky Porte. OCEANE: Outils pour la Conception et l'Enseignement des circuits intégrés ANalogiquEs – reference manual, January 2018. 5

- [5] Anthony Lester Grégoire Avot Pirouz Bazargan-Sabet Amjad Hajjar, Karim Dioury and Marie-Minerve Louërat. Tas, 2018. 5

### **Chapitre 2**

# État de l'art des outils de CAO pour circuits analogiques et mixtes

### Sommaire

| oomman | ~                                               |    |

|--------|-------------------------------------------------|----|

| 2.1    | Introduction                                    | 10 |

| 2.2    | Les outils de génération de dessins des masques | 10 |

|        | 2.2.1 Les outils académiques                    | 10 |

|        | 2.2.2 Les outils industriels                    | 16 |

| 2.3    | L'historique des outils de CAO au LIP6          | 18 |

|        | 2.3.1 Les travaux dédiés aux versions de CAIRO  | 18 |

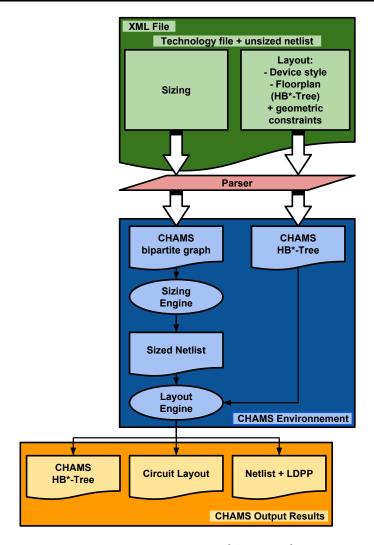

|        | 2.3.2 Les travaux dédiés à CHAMS                | 19 |

| 2.4    | Conclusion                                      | 21 |

| 2.5    | Références                                      | 25 |

#### 2.1 Introduction

Au cours des trois dernières décennies, de nombreuses approches ont été proposées dans le développement des outils de conception assisté par ordinateur (CAO) dédiés à l'automatisation de la génération du dessin des masques des circuits analogiques et mixtes. Ces approches d'automatisation proviennent majoritairement du milieu académique tandis que les outils industriels limitent l'automatisation à la génération d'un petit nombre de transistors paramètrables. Le laboratoire d'informatique de Paris 6 (LIP6) est la source d'outils de CAO dédiés à la conception de circuits intégrés. Des outils tels que Alliance ([1]), Coriolis ([2]), OCEANE ([3]) et Tas/Yagle ([4]) sont le résultat de plus d'une vingtaine d'années d'efforts et de travaux de recherches entrepris au sein du département System-On-Chip. Dans ce chapitre, nous présentons l'état de l'art des outils de CAO dédiés aux dessins des masques analogiques et mixtes ainsi que l'ensemble des travaux précédemment réalisés au LIP6 avant le début de cette thèse.

#### 2.2 Les outils de génération de dessins des masques

Dans cette section, on présente les outils de CAO dédiés aux dessins masques provenant du milieu académique et du milieu industriel. On s'intéresse ici en particulier aux travaux présentant une génération complète d'un dessin des masques. Les travaux qui se focalisent uniquement sur une seule partie de la génération seront présentés dans les chapitres consacrés au placement et au routage.

#### 2.2.1 Les outils académiques

Au cours des dernières décennies, les circuits intégrés analogiques ont gagné de plus en plus d'intérêt en majorité dû aux applications des systèmes sur puce (System-On-Chip) modernes qui sont des circuits comprenant des parties numériques et analogiques, autrement dit mixtes. Malgré cet intérêt porté aux circuits analogiques, les outils d'automatisation de la conception sont bien moins avancés pour l'analogique que pour le numérique. Cela s'explique par la difficulté à gérer toutes les contraintes de la génération du dessin des masques analogique. Par conséquent, l'état de l'art s'oriente davantage sur des recherches d'automatisation pour circuits analogiques que pour circuits mixtes.

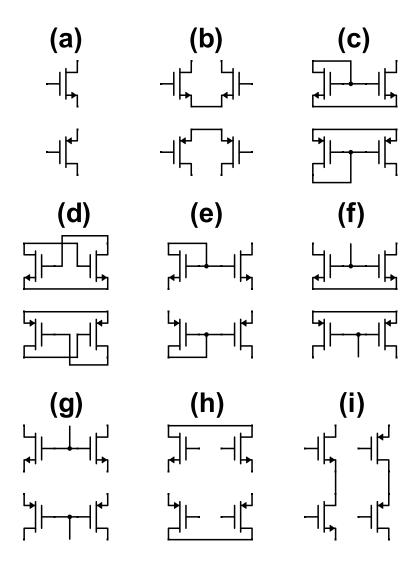

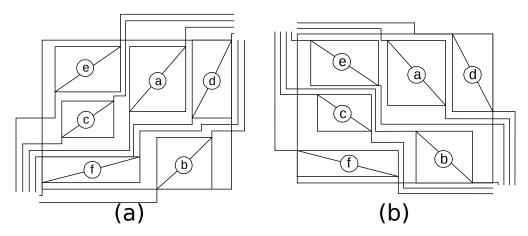

Les études de l'automatisation de la génération du dessin des masques des circuits analogiques et mixtes se focalisent sur deux étapes communes qui sont la phase de placement et la phase de routage. C'est en utilisant des modules analogiques pouvant être un transistor simple ou un petit bloc analogique réalisant une fonction simple (miroir de courant, paires différentielles, etc ...) que ces outils réalisent la phase de placement et de routage. Les outils modernes traitant ces sujets peuvent être classés selon l'approche suivie :

• Génération du dessin des masques analogiques et mixtes à partir de contraintes : À partir du schéma électrique du circuit et des contraintes de placement et de routage spécifiées par le concepteur, ces outils génèrent les modules analogiques, les placent de manière optimisée et déterminent le routage en minimisant la longueur des fils. De nombreux articles de l'art ont contribué à cette approche de génération de dessin des masques et portent sur une de ces trois étapes en incorporant la prise en compte de contraintes (symétries, appariement de modules, routage symétrique, etc ...).

• Migration technologique du dessin des masques pour de nouvelles spécifications: La réalisation du dessin des masques d'un circuit analogique requiert l'expérience et les connaissances adéquates. Le niveau d'expertise et les connaissances d'un concepteur influent de manière conséquente sur la qualité du dessin des masques. Par conséquent, l'exportation d'un circuit analogique d'une technologie à une autre est l'objectif d'une classe d'outils de CAO. Ces outils cherchent à capitaliser sur l'expertise des concepteurs afin de l'adapter pour une nouvelle technologie ou selon de nouvelles spécifications.

Que ces outils soient destinés à la génération du dessin des masques à partir de contraintes ou à la migration technologique, ils abordent le problème de la génération du dessin des masques en utilisant différentes approches. On classifie les approches des outils de l'état de l'art en 3 catégories se distinguant par les méthodes de résolution utilisées pour aborder le problème du placement routage analogique et mixte :

- Les outils procéduraux : On considère un outil procédural comme étant un outil qui permet au concepteur de décrire l'ensemble des étapes de placement et de routage. À l'aide d'un langage dédié, le circuit est entièrement décrit par un script indiquant l'emplacement de chacun des modules analogiques et des fils permettant la connectivité électrique. De cette manière, les outils procéduraux ont l'avantage de donner le contrôle au concepteur de la génération du circuit. L'exécution de ces outils est rapide car elle ne nécessite pas de temps de recherche de solutions et permettent une reproductibilité du circuit. Les scripts de ces outils procéduraux ont le désavantage d'être longs à décrire et ne sont valables que pour une technologie donnée. De plus, ils ne proposent pas d'aide au concepteur à la recherche de solutions de placement ou de routage.

- Les outils utilisant des méthodes d'optimisation : Cette dernière catégorie rassemble les outils fondés sur des méthodes métaheuristiques pour trouver une solution de placement routage. Le problème du placement et du routage nécessite de parcourir un très grand espace de solution et ces méthodes permettent d'obtenir une bonne solution rapidement. L'avantage de cette approche repose sur une mise en place rapide en laissant l'outil la charge de réaliser le choix du placement routage dans un espace de solutions souvent très grand. En revanche, l'exploration de l'espace de solutions peut s'avérer longue. L'ajustement des fonctions de coût peut s'avérer difficile pour le concepteur, la reproductibilité n'est pas toujours possible.

- Les outils se basant sur un *template*: Ces outils ont pour but de permettre au concepteur de partir d'une base pour réaliser un circuit. Un *template* est un patron incorporant les informations permettant de représenter une topologie de placement ou de routage basées sur l'expérience d'un concepteur. Ce *template* est par la suite optimisé ou réajusté afin de correspondre au besoin du circuit qu'on souhaite réaliser en particulier pour la réutilisation du circuit pour une nouvelle technologie. Dans la mesure où un *template* n'est pas capable de représenter le circuit désiré, le concepteur est obligé de créer un nouveau *template* ce qui peut être long et complexe. Ces outils incluent des méthodes d'optimisation pouvant optimiser la phase de placement ou de routage.

Le tableau de la figure 2.1 résume l'ensemble des avantages et des inconvénients que présente chacune de ces approches. Chaque approche possède son intérêt et il est difficile de déterminer laquelle de ces approches domine les autres en termes de qualité du placement routage de manière générale pour un temps raisonnable. Il est possible en revanche d'établir des critères de qualité permettant de juger individuellement la capacité

|               | Avantages et Inconvénients des approches de génération de dessins des masques analogiques                                                                                                                        |                                                                                                                                                                                                                             |                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Procédural                                                                                                                                                                                                       | Optimisation                                                                                                                                                                                                                | Template                                                                                                                                                                                     |

| Avantages     | <ul> <li>Paramètrage donnant un<br/>control total au<br/>concepteur</li> <li>Temps d'exécution court</li> <li>Reproductibilité du<br/>placement-routage</li> </ul>                                               | <ul> <li>Haut niveau<br/>d'abstraction</li> <li>Utilise des méthodes<br/>d'optimisation</li> <li>Temps de configuration<br/>rapide pour un nouveau<br/>circuit</li> </ul>                                                   | <ul> <li>Plus haut niveau<br/>d'abstraction qu'en<br/>procédural</li> <li>Incorpore l'expérience<br/>d'un concepteur</li> <li>Ré-utilisablilité pour une<br/>nouvelle technologie</li> </ul> |

| Inconvénients | <ul> <li>Configuration longue du<br/>script pour un circuit<br/>entier</li> <li>Non ré-utilisable pour<br/>une autre technologie<br/>donnée</li> <li>Pas d'utilisation de<br/>méthodes d'optimisation</li> </ul> | <ul> <li>Longue durée<br/>d'exécution</li> <li>Peu de contrôle par le<br/>concepteur sur le<br/>résultat final</li> <li>Petites modifications<br/>difficiles</li> <li>Reproductibilité pas<br/>toujours possible</li> </ul> | <ul> <li>Requièrt une 1ere description complète du template</li> <li>Difficile de convertir en template toutes les topologies</li> <li>Ne concerne que le placement</li> </ul>               |

FIGURE 2.1 – Comparaison des approches des outils de génération de dessins des masques pour circuits analogiques et mixtes

d'un outil à pouvoir générer le dessin des masques voulu par le concepteur.

Un outil de génération de dessins des masques analogiques et mixtes doit être en mesure à répondre au besoin du concepteur, c'est-à-dire être capable de représenter des topologies variées. La génération doit pouvoir se faire dans un temps raisonnable tant pour la phase de paramétrage que le temps d'exécution. On définit la qualité d'un outil de génération de dessins des masques à partir des critères suivants :

- Types de contraintes gérées : La qualité d'un dessin des masques, en particulier dans le cas des circuits analogiques et mixtes, est influencée par la prise en compte de contraintes de conception. Ces contraintes sont diverses et ont toutes pour but de limiter les effets parasites dus au dessin des masques et de préserver les performances du circuit. Ces contraintes concernent la phase de placement et de routage, les plus communes sont les contraintes d'appariement et de symétries. Les détails concernant l'ensemble des contraintes existantes sont respectivement présentés dans les chapitres de la thèse dédiés au placement et au routage.

- Catégorie de circuits réalisables : En particulier pour les circuits analogiques, certains outils de l'état de l'art se concentrent sur la conception d'une catégorie de circuit. Le dessin des masques d'un circuit radiofréquence ou d'un convertisseur analogique numérique présentent des différences en termes de contrainte de placement et de routage. La polyvalence et la spécialisation d'un outil présentent chacune des avantages et des inconvénients. La polyvalence permet de réaliser une plus grande diversité de circuit mais au risque de proposer une solution moins bonne. En opposition, la spécialisation permet de prendre en compte davantage de facteurs pour obtenir une meilleure solution mais risque de devenir obsolète pour les technologies futures en cas de spécialisation trop avancée.

- Temps de conception : Le niveau d'automatisation est un facteur important pour les outils de génération de dessin des masques de circuits analogiques et mixtes. Ce critère correspond au temps nécessaire pour que le concepteur interprète le circuit à réaliser au sein de l'outil. Ce temps de préparation combiné au temps d'exécution nécessite d'être significativement inférieur à une génération du dessin des masques manuelle. Malgré le grand nombre de contraintes imposées aux circuits analogiques, l'espace de solution pour un circuit donné reste toujours particulièrement grand et il est inconcevable que le temps d'une unique exécution dure plusieurs semaines.

- Fonctionnalités de conception : On définit une fonctionnalité comme toute aide supplémentaire apportée au concepteur. Celle-ci peut prendre plusieurs formes. Des aspects logiciels permettant une interactivité avec le circuit, la capacité à mémoriser la conception d'un script, une représentation de l'ensemble des données pertinentes du circuit ou bien l'interfaçage avec des outils logiciels extérieurs sont des fonctionnalités utiles dans l'accompagnement du concepteur dans l'étape de réalisation du dessin des masques.

L'étude du problème de l'automatisation de la génération du dessin des masques des circuits analogiques et mixtes débute avec la publication des premiers articles dans les années 1980. C'est en gardant en perspective l'ensemble des aspects mentionnés ci-dessus que nous présentons une vue d'ensemble de l'état de l'art de ces outils de CAO.

Les premières approches ayant pour but d'automatiser la génération du dessin des masques mixtes analogiques consistaient à générer de manière procédurale des modules [5]. Ces générateurs procéduraux définissent la représentation géométrique de la totalité du circuit. ALSYN[6] est capable de synthétiser le dessin des masques à partir d'une description niveau netlist pour une variété de circuits analogiques. L'outil avait pour but d'être flexible et de laisser beaucoup de contrôle au concepteur à travers un environnement de conception interactif. La figure 2.2 illustre le flot de conception d'ALSYN.

L'outil de Xu Jingnan et al.[8] utilise une librairie de modules paramétrables analogiques (*PCells*) décrits à partir du langage *SKILL*[9]. L'outil est développé à travers le Cadence Design Framework[10] et a pour but de générer des circuits analogiques et mixtes indépendamment des la technologie. Malgré la rapidité des outils procéduraux, ces outils manquent de flexibilité et le coût en temps de conception peut s'avérer long pour

FIGURE 2.2 – Structure et flot de conception FIGURE 2.3 – Flot du générateur de dessins des d'ALSYN[6]

masques de BAG[7]

la conception d'un nouveau circuit et la migration technologie de certains circuits peut entrainer des modifications. D'autres approches plus récentes cherchent également toujours à exploiter les *PCells*[11].

IIP Framework[12] est un environnement dédié au développement de générateurs de circuits analogiques indépendants de toute technologie et d'environnement de conception. L'outil consiste à paramétrer des descriptions de chaque vue d'un module analogique, c'est-à-dire la vue schéma électrique, symbolique et en dessin des masques. En particulier, leur objectif revient à permettre à la réutilisation de circuits analogiques.

*BAG*[7] est un environnement dédié à la génération de circuits analogiques et mixtes soumis à des contraintes de spécifications et indépendamment d'une technologie. <sup>´</sup>A partir d'un ensemble de classes, la codification des procédures de dimensionnement et la paramétrisation du dessin des masques sont décrites par le concepteur. La phase de placement routage est réalisée à partir de ces classes contenant différentes architectures et méthodes de routage. La figure 2.3 illustre le flot de conception de *BAG*.

*ILAC*[13] fait partie des premières études utilisant l'approche basée sur des techniques d'optimisation. *ILAC* est un outil issu d'un ensemble d'outils d'*IDAC*[14] et utilise l'algorithme du recuit simulé[15] en tenant de contraintes d'appariement, de symétries et de proximité.

KOEN/ANAGRAM II[16] est un outil rassemblant un outil de placement (KOEN) et un outil de routage (ANAGRAM II). Le placement est obtenu à partir de modules provenant d'une librairie de générateurs de modules et le routage est réalisé en routant au-dessus des modules et respectant des contraintes de symétries.

LAYLA[17] tient compte des contraintes de symétrie, des dégradations de performance dues aux effets parasites et de l'appariement des modules pour optimiser le placement du circuit. Tout comme pour KOEN/ANAGRAM II et ILAC, la technique d'optimisation utilisée est l'algorithme de recuit simulé. LAYLA a également été utilisé par l'outil CY-CLONE[18] ayant pour but de dimensionner et générer des oscillateurs LC.

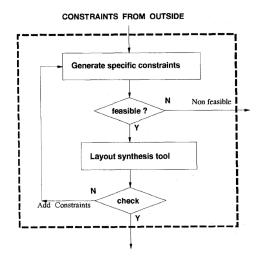

ALDAC[19] applique une méthodologie suivant trois points clés (voir figure 2.4). La

FIGURE 2.4 – Flot de conception d'*ALDAC*[19]

FIGURE 2.5 – Flot de conception d'*ALG*[20]

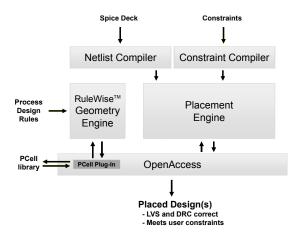

transformation de contraintes de spécifications en un jeu de contraintes garantissant la faisabilité de la génération. Les contraintes d'un haut niveau d'abstraction sont traduites en un jeu de contraintes sur les paramètres bas-niveau. Toute étape irréalisable est détectée au plus tôt du flot de conception.

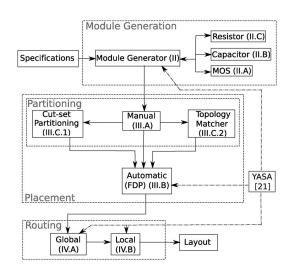

L'outil *ALG*[20] se divise trois parties : un générateur de modules, un placeur et un routeur (voir figure 2.5). La première étape consiste à générer l'ensemble des modules à partir des informations des données d'entrée qui sont la *netlist* du circuit et les spécifications. Ces modules sont ensuite placés avec plus ou moins d'automatisation selon le choix du concepteur. Le routeur est décomposé en deux étapes, une étape de routage global et une étape de routage local/détaillé.

Le flot de conception de l'outil de Husni Habal et al.[21] est dirigé par le schéma électrique et une liste de paramètres du circuit. Chaque dessin des masques pour chacun des modules est considéré et la configuration de modules proposant les meilleures spécifications géométriques est conservé. Le placement et le routage sont réalisés tout en préservant la faisabilité du circuit ainsi que la minimisation des effets parasites dus au routage. La solution obtenue est réutilisée pour de réajustements du dimensionnement.

*DeMixGen*[22] se concentre sur la conception de circuits mixtes, en particulier des modulateurs sigma-delta. Cet outil a pour but de résoudre les problèmes de bruit entre les signaux numériques et analogiques. La génération des circuits mixtes est réalisée en portant une attention particulière à la séparation de ces deux types de signaux. Á la différence des autres outils d'optimisation, le concepteur fournit la *netlist* du circuit qui est analysée pour réaliser le routage adéquat.

En parallèle aux approches basées sur l'optimisation, les approches basées sur des *templates* ont connu autant de succès que les précédentes approches pour leur capacité à intégrer l'expérience des concepteurs. Les premiers outils basés sur des *templates* avaient pour objectif de résoudre les problèmes de migrations technologiques.

*IPRAIL*[23] est un outil capable de redéfinir le dessin des masques de circuits analogiques existant pour une autre technologie ou pour de nouvelles spécifications. L'approche employée consiste à créer automatiquement un *template* à partir du circuit existant et imposer les nouvelles règles et spécifications aux modules redimensionnés.

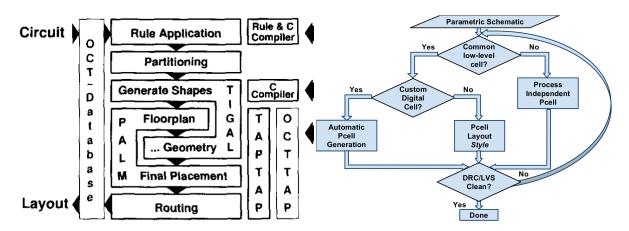

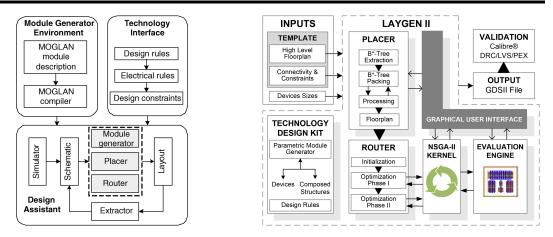

*ALADIN*[24] est composé de trois parties qui sont : un environnement de générateur de module, un assistant de conception et une interface de technologie (voir figure 2.6). Le générateur de modules permet au concepteur de décrire, indépendamment de la technologie et de l'application visée, la paramétrisation des modules. L'assistant de conception est intégré au Cadence FrameWork[10] et fournit une interface graphique à l'utilisateur pour optimiser la phase de conception. L'interface de technologie permet la description des règles technologiques ainsi que des contraintes spécifiques au circuit.

Gönenç Berkol et al.[26] proposent un flot de conception de circuits analogiques comprenant un outil de génération du dessin des masques. Le dessin des masques est instancié à partir d'un *template* et l'occupation de l'espace est minimisé en changeant des paramètres géométriques tels que le nombre de doigts d'un transistor. Le *template* est décrit en language LDS[27] et contient le code du placement et du routage.

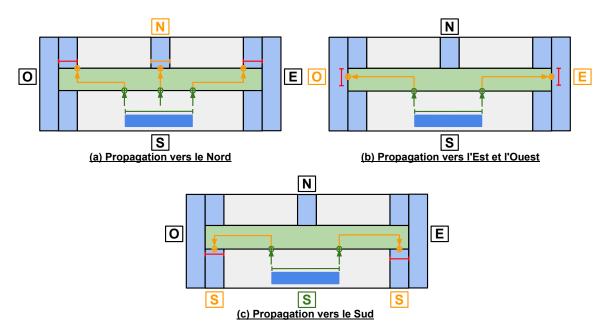

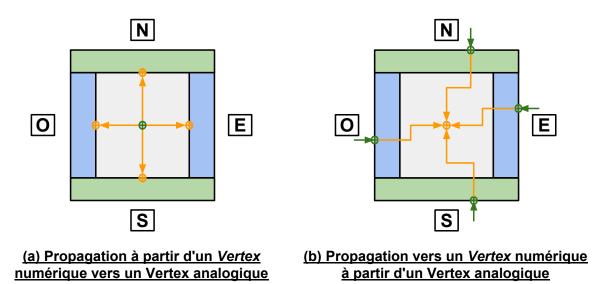

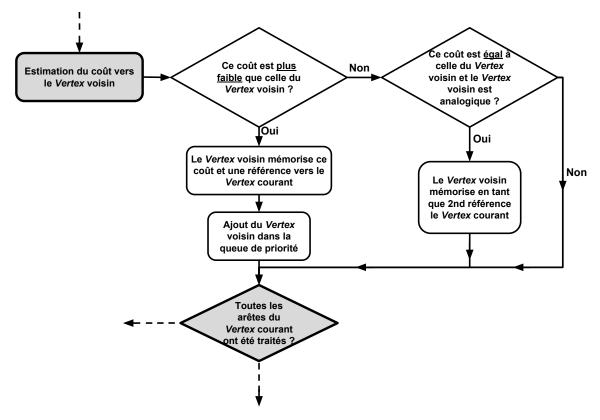

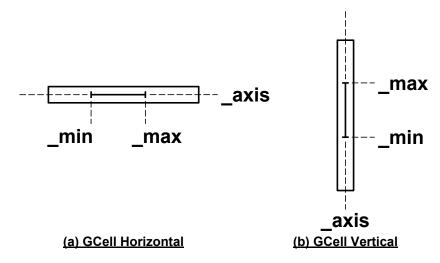

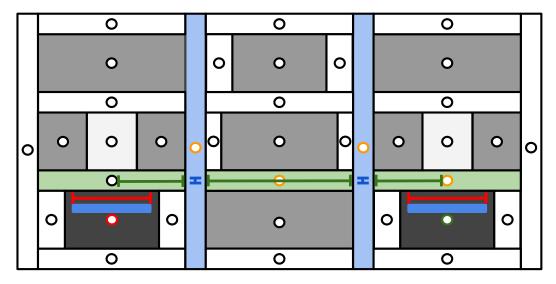

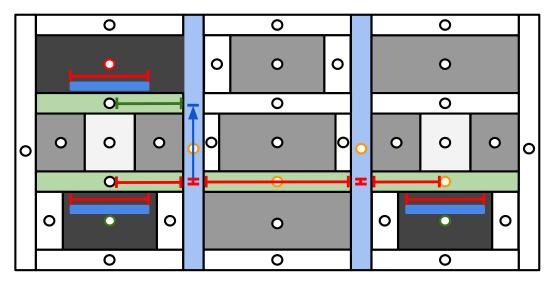

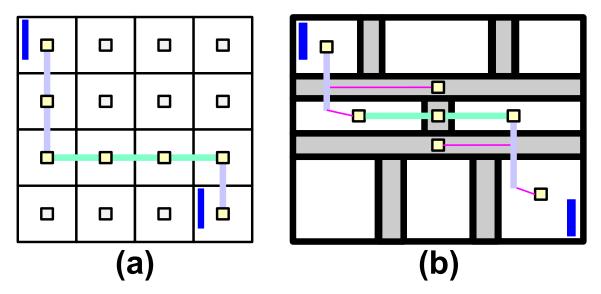

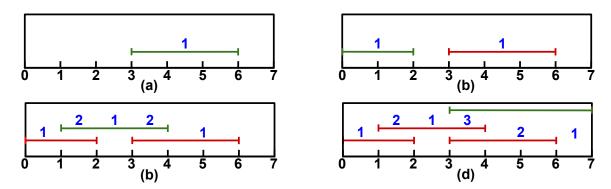

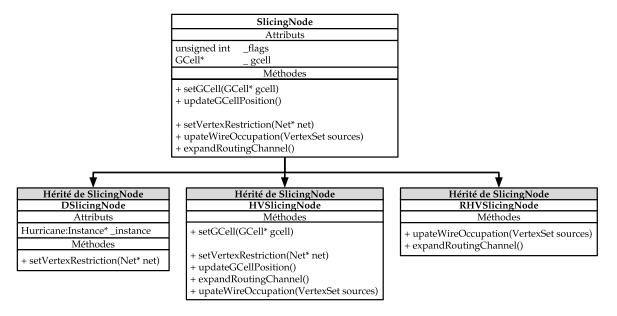

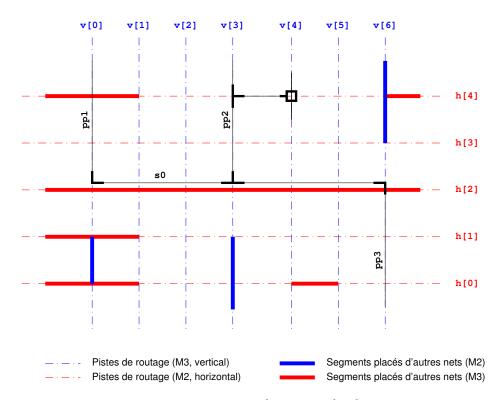

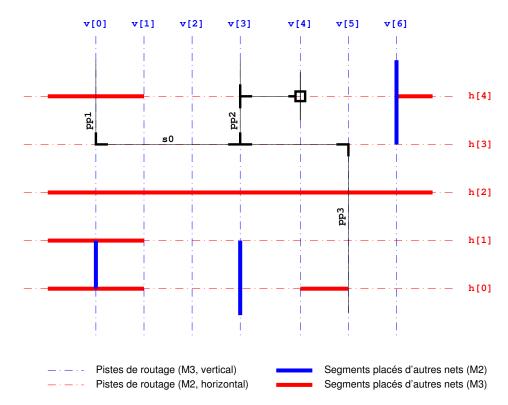

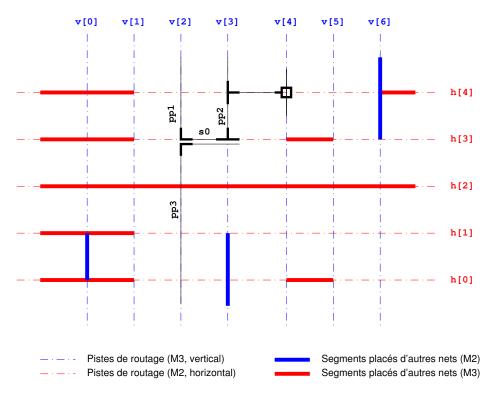

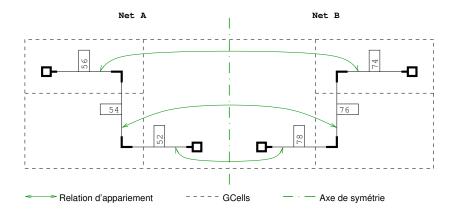

FIGURE 2.6 – Structure de l'outil de CAO FIGURE 2.7 – Structure de l'outil de CAO LAY-ALADIN[24] GEN II[25]