## Vers le support des systèmes à criticité mixte sur des architectures NoC

Mourad Dridi

#### ▶ To cite this version:

Mourad Dridi. Vers le support des systèmes à criticité mixte sur des architectures NoC. Génie logiciel [cs.SE]. Université de Bretagne occidentale - Brest, 2019. Français. NNT: 2019BRES0051. tel-02926475

#### HAL Id: tel-02926475 https://theses.hal.science/tel-02926475

Submitted on 31 Aug 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESE DE DOCTORAT DE

## L'UNIVERSITE DE BRETAGNE OCCIDENTALE

COMUE UNIVERSITE BRETAGNE LOIRE

ECOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Informatique

Par Mourad DRIDI

# Vers le support des systèmes à criticité mixte sur des architectures *NoC*

Thèse présentée et soutenue à Brest, le 18 Octobre 2019 Unité de recherche : Lab-STICC UMR CNRS 6285

#### Rapporteurs avant soutenance :

Abdoulaye GAMATIE Directeur de Recherche, CNRS, LIRMM Claire PAGETTI Maître de Recherche, ONERA, DTIM

#### **Composition du Jury:**

Président : Eric GRESSIER-SOUDAN Professeur des Universités, CNAM

**Examinateurs :** António CASIMIRO Maître de Conférences, Université de Lisbonne

Abdoulaye GAMATIE Directeur de Recherche, CNRS, LIRMM Claire PAGETTI Maître de Recherche, ONERA, DTIM

Dir. de thèse : Frank SINGHOFF Professeur des Universités, UBO, Lab-STICC Encadrant : Jean-Philippe DIGUET Directeur de Recherche, CNRS, Lab-STICC Encadrant : Stéphane RUBINI Maître de Conférences, UBO, Lab-STICC

## Remerciements

Pour commencer ce manuscrit, je tiens à remercier toutes les personnes qui ont contribué à divers degrés au bon déroulement de ce travail de recherche.

Je remercie tout d'abord Frank Singhoff, Professeur à l'Université de Bretagne Occidentale (UBO)/Lab-STICC, pour ses conseils toujours pertinents en tant que directeur de thèse. Je le remercie du temps qu'il a pu me consacrer, ainsi que de la confiance et du soutien qu'il a su m'accorder pour mener à bien ce manuscrit.

Je remercie vivement Stéphane Rubini, Maitre de conférences à l'Université de Bretagne Occidentale (UBO)/Lab-STICC et Jean-Philippe Diguet Directeur de recherche CNRS/Lab-STICC pour leur encadrement, leur expertise et leur soutien pendant la préparation de cette thèse. C'était un plaisir de travailler avec eux.

Je remercie particulièrement Abdoulaye Gamatié Directeur de recherche CNRS/-LIRMM, et Claire Pagetti ingénieur de recherche ONERA/DTIM pour avoir été rapporteurs de cette thèse; et également Antònio Casimiro Maître de conférences à l'Université de Lisbonne/Lasige d'être examinateur.

Je remercie particulièrement Eric Gressier-Soudan Professeur des Universités (CNAM)/Cédric d'être président du jury.

Mes remerciements vont vers Mounir Lallali pour son aide et ses conseils, et aussi Laurent Lemarchand et Valérie Marc pour nos discussions scientifiques.

Un remerciement particulier à Martha Johanna pour m'avoir accueilli dans son équipe durant mon séjour scientifique à l'Université Technique de Munich (TUM).

Je tiens de plus à saluer tous mes collègues (docteurs ou doctorants) au Lab-STICC avec qui j'ai partagé cette expérience de recherche : Rahma, Baccouri, Chabha, Antoine, Zerkane, Camélia, Steven, Valery, Nam, Arwa, Mayssa, Illham et Musaab.

Enfin, mes sentiments les plus chaleureux sont pour ma famille. En particulier, je remercie mes parents pour leur soutien et encouragement depuis toujours. Je voudrais également remercier mon frère Seif du soutien inconditionnel qu'il m'a apporté. Une pensée très chaleureuse à mes sœurs Chayma, Rim et Monia pour leur amour et encouragement. Un grand remerciement également à mon âme soeur Manel pour sa présence à mes côtés durant toutes ces années.

Bonne lecture!

### **Publications**

#### Journaux internationaux

- 1. Mourad Dridi, Stéphane Rubini, Mounir Lallali, Martha Johanna Sepúlveda Flórez, Frank Singhoff and Jean-Philippe Diguet. 2019. Design and Multi-Abstraction-Level Evaluation of a NoC Router for Mixed-Criticality Real-Time Systems. ACM Journal on Emerging Technologies in Computing Systems. Article 2: 1-37, February 2019. (Rang Q2)

- 2. Mourad Dridi, Stéphane Rubini, Frank Singhoff, Jean-Philippe Diguet. DTFM: a Flexible Model for Schedulability Analysis of Real-Time Applications on NoC-based Architectures. ACM SIGBED Review 14(4): 53-59 (2017). Special issue of the 4<sup>th</sup> International Workshop on Real-Time Computing and Distributed systems in Emerging Applications (REACTION).

- 3. José Rufino, António Casimiro, Antónia Lopes, Frank Singhoff, Stéphane Rubini, Valérie-Anne Nicolas, Mounir Lallali, Mourad Dridi, Jalil Boukhobza, Lyes Allache. NORTH: Non-intrusive Observation and RunTime verification of cyber-pHysical systems. Ada User Journal, 2018 vol 39, no 4

#### Conférences ou workshops internationaux

- Mourad Dridi, Frank Singhoff, Stéphane Rubini, Jean-Philippe Diguet.

ECTM: A New Communication Model to Network-On-Chip Schedulability

Analysis. 24th International Conference on Reliable Software Technologies

Ada-Europe 2019, June 2019, Varsow, Poland. (Rang B)

- Mourad Dridi, Stéphane Rubini, Mounir Lallali, Martha Johanna Sepulveda Florez, Frank Singhoff, Jean-Philippe Diguet. DAS: An Efficient NoC Router for Mixed-Criticality Real-Time Systems. 35th IEEE International Conference on Computer Design (ICCD) 2017, 229-232. Boston, MA, USA.

- 3. Mourad Dridi, Mounir Lallali, Stéphane Rubini, Jean-Philippe Diguet, Frank Singhoff. Modeling and Validation of a Mixed-Criticality NoC Router Using the IF Language. 10th International Workshop on Network-On-Chip Architectures (NoCArch), Boston, MA, USA.

## Séminaires, exposés

1. Mourad Dridi, Stéphane Rubini, Frank Singhoff, Jean-Philippe Diguet. NoC and Mixed-criticality Systems. GDR SOC2, Emerging Interconnect Technologies in ManyCore architectures, Paris, cité internationale – Collège d'Espagne. November 2017.

## Table des matières

| 1 | Inti | roduct | ion                                                                  | 1  |

|---|------|--------|----------------------------------------------------------------------|----|

|   | 1.1  | Motiv  | ations et objectifs                                                  | 2  |

|   | 1.2  | Contr  | ibutions                                                             | 3  |

|   | 1.3  | Plan   |                                                                      | 5  |

| Ι | Co   | ontex  | te - État de l'art                                                   | 7  |

| 2 | Les  | systèr | mes temps réel à criticité mixte                                     | 9  |

|   | 2.1  | Systèr | mes temps réel                                                       | 10 |

|   |      | 2.1.1  | Systèmes temps réel dur                                              | 11 |

|   |      | 2.1.2  | Systèmes temps réel mou                                              | 11 |

|   |      | 2.1.3  | Modèle de tâches                                                     | 12 |

|   |      | 2.1.4  | Modèle de support d'exécution                                        | 15 |

|   | 2.2  | Systèr | mes à criticité mixte                                                | 15 |

|   |      | 2.2.1  | Modèle de tâches                                                     | 17 |

|   |      | 2.2.2  | Changement de mode de criticité                                      | 17 |

|   | 2.3  | Introd | luction à l'analyse d'ordonnancement des systèmes temps réel         | 20 |

|   |      | 2.3.1  | Algorithme d'ordonnancement                                          | 20 |

|   |      | 2.3.2  | Analyse d'ordonnancement                                             | 22 |

|   | 2.4  | Ordon  | nancement temps réel multiprocesseur de tâches dépendantes           | 23 |

|   |      | 2.4.1  | Une taxonomie des algorithmes d'ordonnancement multi-<br>processeurs | 23 |

|   |      | 2.4.2  | Heuristiques d'ordonnancement par liste                              | 24 |

|   |      | 2.4.3  | Réseau sur puce                                                      | 27 |

|   | 2.5  | Concl  | usion                                                                | 28 |

| 3 | Les | réseau | ıx sur puce                                  | 29 |

|---|-----|--------|----------------------------------------------|----|

|   | 3.1 | Interc | onnexions dans les systèmes sur puce         | 31 |

|   |     | 3.1.1  | Techniques classiques d'interconnexion       | 31 |

|   |     | 3.1.2  | Réseau sur puce                              | 31 |

|   | 3.2 | Route  | eur du réseau sur puce                       | 33 |

|   | 3.3 | Conce  | epts relatifs aux réseaux sur puce           | 35 |

|   |     | 3.3.1  | Topologie                                    | 35 |

|   |     | 3.3.2  | Paquet                                       | 35 |

|   |     | 3.3.3  | Algorithme de routage                        | 36 |

|   |     | 3.3.4  | Technique de commutation                     | 37 |

|   |     | 3.3.5  | Politique de mémorisation et canaux virtuels | 39 |

|   |     | 3.3.6  | Politique d'arbitrage                        | 40 |

|   |     | 3.3.7  | Préemption                                   | 42 |

|   |     | 3.3.8  | Exemples de routeurs                         | 43 |

|   | 3.4 | Comm   | nunications temps réel et qualité de service | 45 |

|   |     | 3.4.1  | Communications temps réel                    | 45 |

|   |     | 3.4.2  | Qualité de service                           | 46 |

|   | 3.5 | Ordon  | nnancement des communications temps réel     | 47 |

|   |     | 3.5.1  | Modèle de flux                               | 47 |

|   |     | 3.5.2  | Temps de trajet                              | 48 |

|   |     | 3.5.3  | Pire temps de communication                  | 49 |

|   | 3.6 | Résea  | ux sur puce et systèmes à criticité mixte    | 51 |

|   |     | 3.6.1  | Architectures du réseau sur puce             | 52 |

|   |     | 3.6.2  | Protocoles pour isolation ou criticité mixte | 54 |

|   |     | 3.6.3  | ARTEMIS                                      | 55 |

|   |     | 3.6.4  | Bilan : NoC et système à criticité mixte     | 55 |

|   | 3.7 | Concl  | usion                                        | 56 |

| 4 M         | <b>Iotivatio</b>                                                       | ons et hypothèses                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.          | 1 Introd                                                               | luction                                                                                                                                                                                                                                                                                                                                                                |

| 4.5         | 2 Probl                                                                | ématiques étudiées                                                                                                                                                                                                                                                                                                                                                     |

|             | 4.2.1                                                                  | Incompatibilité des routeurs NoC avec les systèmes à criticité mixte                                                                                                                                                                                                                                                                                                   |

|             | 4.2.2                                                                  | Modèles de tâches incomplets                                                                                                                                                                                                                                                                                                                                           |

|             | 4.2.3                                                                  | Techniques d'analyse d'ordonnancement incomplètes                                                                                                                                                                                                                                                                                                                      |

| 4.3         | 3 Conte                                                                | exte du travail                                                                                                                                                                                                                                                                                                                                                        |

|             | 4.3.1                                                                  | Modèle de système à criticité mixte                                                                                                                                                                                                                                                                                                                                    |

|             | 4.3.2                                                                  | Modèle de NoC                                                                                                                                                                                                                                                                                                                                                          |

| 4.4         | 4 Les co                                                               | ontributions                                                                                                                                                                                                                                                                                                                                                           |

|             | 4.4.1                                                                  | Double Arbiter and Switching Router (DAS)                                                                                                                                                                                                                                                                                                                              |

|             | 4.4.2                                                                  | Dual Task and Flow Model (DTFM)                                                                                                                                                                                                                                                                                                                                        |

|             | 4.4.3                                                                  | Exact Communication Time Model (ECTM)                                                                                                                                                                                                                                                                                                                                  |

| Π           | Contri                                                                 | butions                                                                                                                                                                                                                                                                                                                                                                |

| 5 R         | outeur l                                                               | DAS (Double Arbiter and Switching Router)                                                                                                                                                                                                                                                                                                                              |

| 5.          | 1 Introd                                                               |                                                                                                                                                                                                                                                                                                                                                                        |

| Ε 6         |                                                                        | luction                                                                                                                                                                                                                                                                                                                                                                |

| 3           | 2 DAS                                                                  | duction                                                                                                                                                                                                                                                                                                                                                                |

| ð.,         | <ul><li>DAS</li><li>5.2.1</li></ul>                                    |                                                                                                                                                                                                                                                                                                                                                                        |

| <b>3.</b> . |                                                                        | (Double Arbiter and Switching Router)                                                                                                                                                                                                                                                                                                                                  |

| 0           | 5.2.1<br>5.2.2                                                         | (Double Arbiter and Switching Router)                                                                                                                                                                                                                                                                                                                                  |

| θ           | 5.2.1<br>5.2.2                                                         | (Double Arbiter and Switching Router)                                                                                                                                                                                                                                                                                                                                  |

| 9           | 5.2.1<br>5.2.2<br>5.2.3                                                | (Double Arbiter and Switching Router)                                                                                                                                                                                                                                                                                                                                  |

| 5           | 5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                              | (Double Arbiter and Switching Router)          Organisation des canaux virtuels          Technique SAF pour les flux HIGH          Technique WORMHOLE pour les flux LOW          Nombre de canaux virtuels                                                                                                                                                             |

|             | 5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                              | (Double Arbiter and Switching Router)          Organisation des canaux virtuels          Technique SAF pour les flux HIGH          Technique WORMHOLE pour les flux LOW          Nombre de canaux virtuels          Unités d'arbitrage                                                                                                                                 |

|             | 5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>3 Proto                   | (Double Arbiter and Switching Router)          Organisation des canaux virtuels          Technique SAF pour les flux HIGH          Technique WORMHOLE pour les flux LOW          Nombre de canaux virtuels          Unités d'arbitrage          cole de changement de mode de criticité                                                                                |

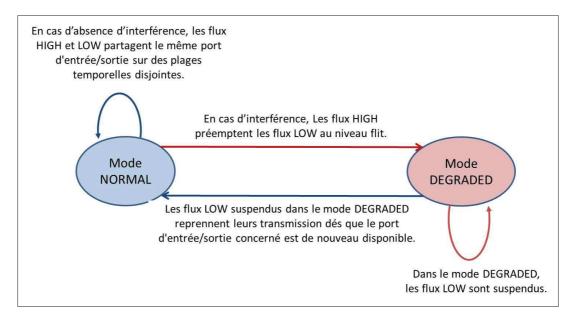

|             | 5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>3 Proto<br>5.3.1<br>5.3.2 | (Double Arbiter and Switching Router)          Organisation des canaux virtuels          Technique SAF pour les flux HIGH          Technique WORMHOLE pour les flux LOW          Nombre de canaux virtuels          Unités d'arbitrage          cole de changement de mode de criticité          Modes de criticité                                                    |

| 5.:         | 5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>3 Proto<br>5.3.1<br>5.3.2 | (Double Arbiter and Switching Router)          Organisation des canaux virtuels          Technique SAF pour les flux HIGH          Technique WORMHOLE pour les flux LOW          Nombre de canaux virtuels          Unités d'arbitrage          cole de changement de mode de criticité          Modes de criticité          Règles du changement de mode de criticité |

|   |     | 5.4.3            | Exemple d'analyse du pire temps de communication pour les flux HIGH | 81  |

|---|-----|------------------|---------------------------------------------------------------------|-----|

|   | 5.5 | Efficac          | cité de SAF pour les systèmes à criticité mixte                     | 83  |

|   |     | 5.5.1            | Réduction du pire temps de communication                            | 84  |

|   |     | 5.5.2            | Réduction du degré de pessimisme                                    | 85  |

|   | 5.6 | Conclu           | usion                                                               | 87  |

| 6 | Éva | luatio           | n de DAS sur plusieurs niveaux d'abstraction                        | 89  |

|   | 6.1 |                  | luction                                                             | 90  |

|   | 6.2 |                  | urs niveaux d'abstraction                                           | 90  |

|   | 6.3 | Évalua           | ation niveau circuit : évaluation du coût en surface                | 91  |

|   |     | 6.3.1            | Verilog HDL                                                         | 91  |

|   |     | 6.3.2            | Synthèse et résultats                                               | 92  |

|   | 6.4 | Évalua           | ation niveau transaction : évaluation du temps de communi-          |     |

|   |     | cation           |                                                                     | 92  |

|   |     | 6.4.1            | Temps de communication pour les flux HIGH                           | 93  |

|   |     | 6.4.2            | Temps de communication pour les flux LOW                            | 96  |

|   |     | 6.4.3            | Étude de cas basée sur l'application Rosace                         | 100 |

|   | 6.5 | Évalua           | ation niveau système : Validation formelle de DAS                   | 103 |

|   |     | 6.5.1            | Le langage IF                                                       | 104 |

|   |     | 6.5.2            | Modélisation de DAS                                                 | 105 |

|   |     | 6.5.3            | Validation                                                          | 111 |

|   | 6.6 | Bilan            | et conclusion                                                       | 114 |

| 7 |     | lonnan<br>es NoC | cement des systèmes à criticité mixte sur des architec-             | 115 |

|   | 7.1 | Introd           | luction                                                             | 116 |

|   | 7.2 | Appro            | che générale                                                        | 117 |

|   | 7.3 | Dual 7           | Task and Flow Model (DTFM)                                          | 118 |

|   |     | 7.3.1            | Modèle de tâches                                                    | 120 |

|   |     | 7.3.2            | Modèle de flux                                                      | 120 |

|   |     | 7.3.3            | La fonction G                                                       | 121 |

|   |     | 7.3.4            | Exemple                                                             | 122 |

| 8 | Con | clusio | n et perspectives                                  | 149    |

|---|-----|--------|----------------------------------------------------|--------|

|   | 7.8 | Concl  | usion                                              | . 146  |

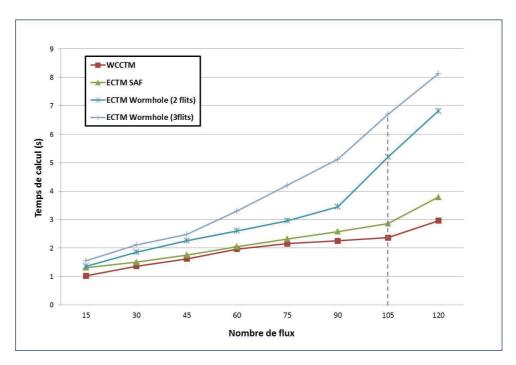

|   |     | 7.7.2  | Évaluation du temps de calcul                      | . 144  |

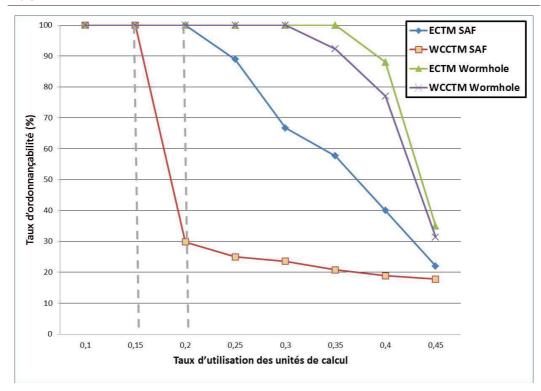

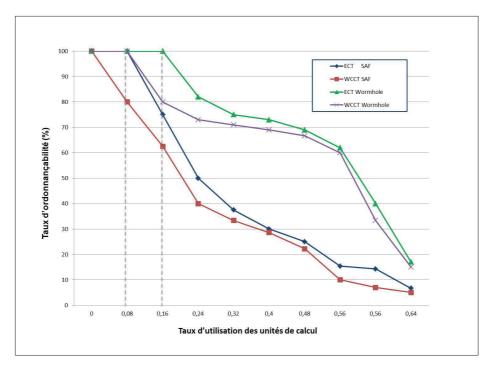

|   |     | 7.7.1  | Évaluation du taux d'ordonnançabilité              | . 143  |

|   | 7.7 | Évalu  | ${ m ations}$                                      | . 142  |

|   | 7.6 | Impla  | ntation                                            | . 141  |

|   |     | 7.5.2  | Exact Communication Time Model pour Wormhole       | . 138  |

|   |     | 7.5.1  | Exact Communication Time Model pour SAF            | . 136  |

|   | 7.5 | Valida | ation des modèles de communications                | . 134  |

|   |     | 7.4.5  | Exact Communication Time Model pour les NoC Wormho | le 130 |

|   |     | 7.4.4  | Exact Communication Time Model pour les NoC SAF $$ | . 128  |

|   |     | 7.4.3  | Worst Case Communication Time Model                | . 126  |

|   |     | 7.4.2  | Modèle d'analyse                                   | . 125  |

|   |     | 7.4.1  | Modèle d'architecture                              | . 124  |

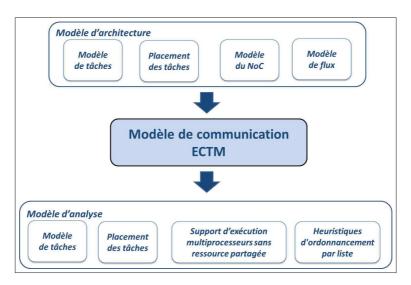

|   | 7.4 | Modèl  | les de communication pour les architectures NoC    | . 124  |

|   |     |        |                                                    |        |

## Table des figures

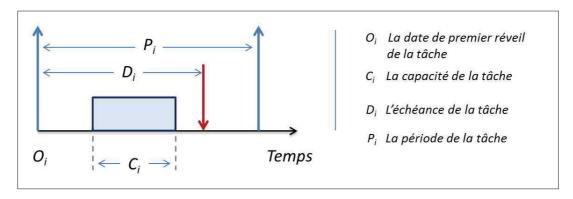

| 2.1 | Paramètres d'une tâche périodique. Une tâche périodique $\tau_i$ est représentée par cinq paramètres : une date de premier réveil $O_i$ , une capacité $C_i$ , une échéance $D_i$ , une période $P_i$ et une priorité $\pi_i$ .                                                                                                                                                                                                                                                                                                                                                                                              | 13 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

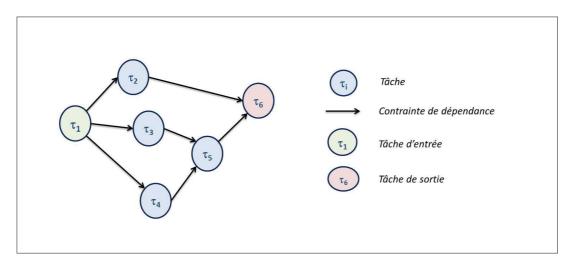

| 2.2 | Exemple d'un DAG. Dans un DAG, les nœuds représentent les tâches et les arcs représentent les relations de dépendance entre les tâches. Une tâche d'entrée (respectivement de sortie) dans un DAG est une tâche n'ayant pas de prédécesseur (respectivement de successeur) dans le graphe                                                                                                                                                                                                                                                                                                                                    | 14 |

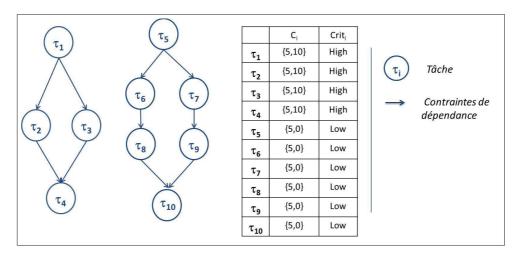

| 2.3 | Exemple d'un système à criticité mixte avec deux modes de criticité et deux niveaux de criticité. Les tâches $(\tau_1, \tau_2, \tau_3, \tau_4)$ sont des tâches ayant un niveau de criticité High. Les tâches $(\tau_5, \tau_6, \tau_7, \tau_8, \tau_9, \tau_{10})$ sont des tâches ayant un niveau de criticité Low. Chaque tâche possède deux valeurs de capacité. La première valeur est considérée sous le mode non critique. La deuxième valeur est considérée sous le mode critique.                                                                                                                                   | 18 |

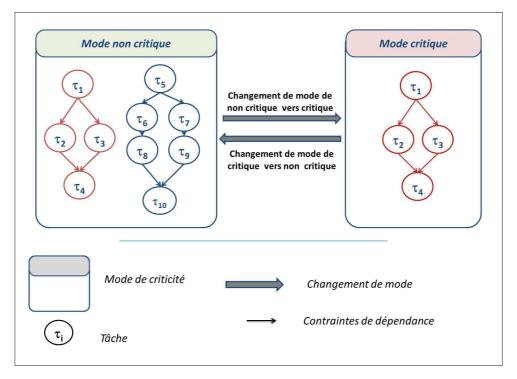

| 2.4 | Exemple d'un changement de mode de criticité. Nous considérons dans cet exemple deux modes de criticité : un mode critique et un mode non critique. Le protocole de changement de mode définit les seuils de transition d'un mode vers un autre                                                                                                                                                                                                                                                                                                                                                                              | 19 |

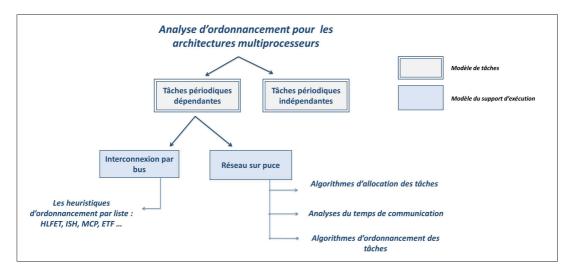

| 2.5 | Taxonomie des algorithmes d'ordonnancement multiprocesseur. Pour le modèle de tâche, nous considérons les tâches périodiques dépendante Concernant le modèle de support d'exécution, nous considérons les architectures multiprocesseurs et les architectures réseau sur puce. Pour les architectures multiprocesseurs il existe les heuristiques par liste. Dans le contexte de réseau sur puce, plusieurs travaux ont été proposés dans l'objectif d'ordonnancer ces systèmes temps réel : des analyses du temps de communication, des algorithmes d'ordonnancement des tâches et des algorithmes d'allocation des tâches. | 24 |

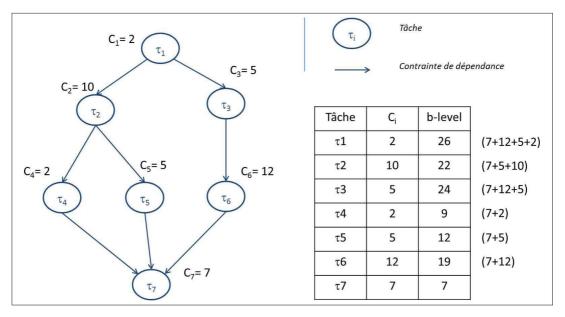

| 2.6 | Exemple HLFET: nous considérons 7 tâches périodiques dépendantes $(\tau_1, \tau_2, \tau_3, \tau_4, \tau_5, \tau_6, \tau_7)$ . La tâche $\tau_1$ est la tâche d'entrée. La tâche $\tau_7$ est la tâche de sortie. Dans la figure 2.7, nous calculons la valeur de b-level pour chaque tâche.                                                                                                                                                                                                                                                                                                                                  | 26 |

| 2.7 | Exemple HLFET : en se basant sur la valeur de b-level pour chaque tâche, HLFET construit la liste des tâches prêtes dans un ordre décroissant. Ensuite, il ordonnance la première tâche sur une unité de calcul disponible.                                                                                                                                                                                                                                                                                                                  | 26 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

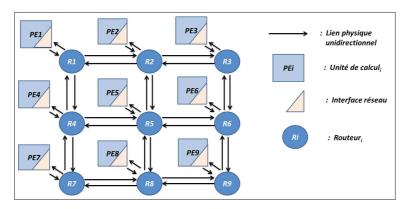

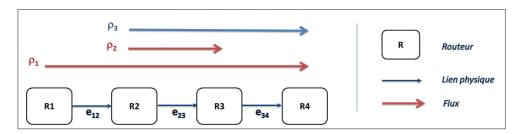

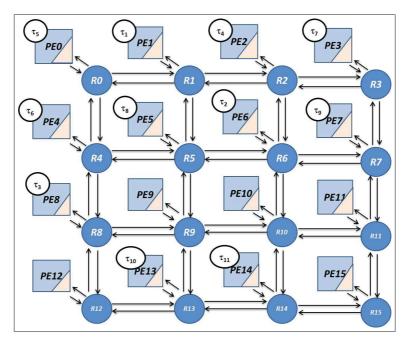

| 3.1 | Exemple d'un NoC $3x3$ en topologie grille Le réseau sur puce est composé des routeurs $R_i$ , des unités de calcul $PE_i$ , des interfaces réseau et des liens physiques $e_{RxRy}$ , $e_{RxPEy}$ ou $e_{PExRy}$ . $e_{RxRy}$ représente le lien qui transporte des données du routeur $R_x$ vers le routeur $R_y$ . $e_{PExRy}$ représente le lien qui transporte des données de l'unité de calcul $PE_x$ vers le routeur $R_y$ . $e_{RxPEy}$ représente le lien qui transporte des données du routeur $R_x$ vers l'unité de calcul $PE_y$ | 32 |

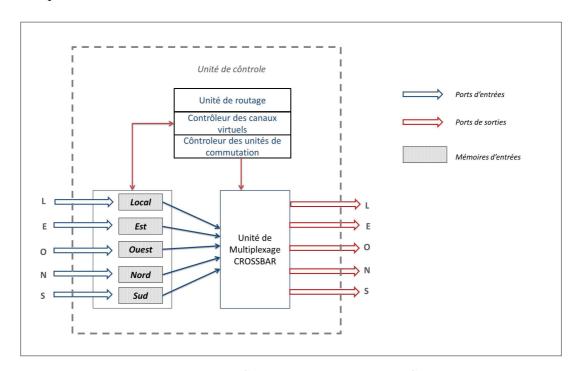

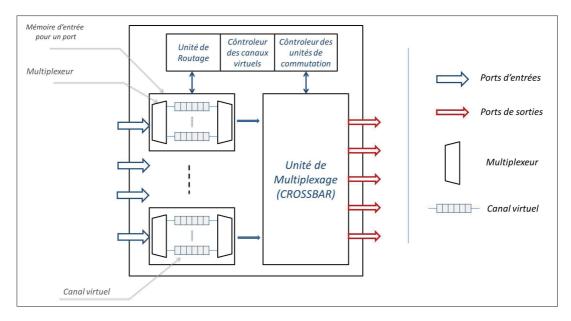

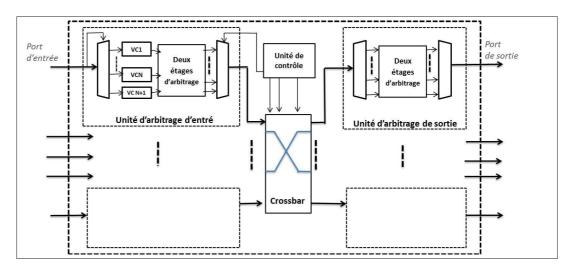

| 3.2 | Composition d'un routeur NoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33 |

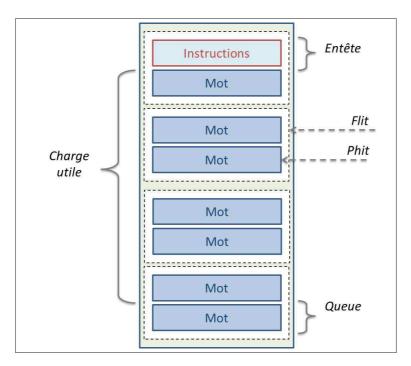

| 3.3 | Structure d'un paquet. La structure d'un paquet commence par<br>un entête, puis le corps du paquet et il se termine par une queue.                                                                                                                                                                                                                                                                                                                                                                                                           | 36 |

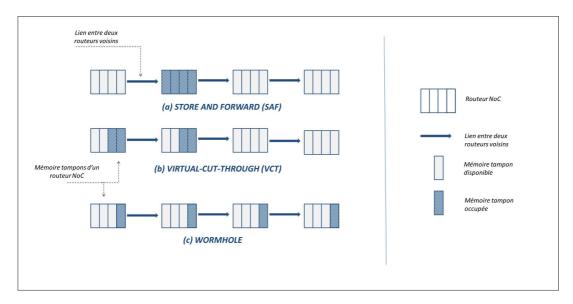

| 3.4 | Techniques de commutation. La commutation SAF exige la réception de la totalité du paquet pour la transmission au routeur suivant. La technique VCT réduit le temps de communication par rapport à SAF. Wormhole réduit la taille du tampon du routeur par rapport à VCT. Le paquet considéré dans cet exemple est de taille 4 flits                                                                                                                                                                                                         | 38 |

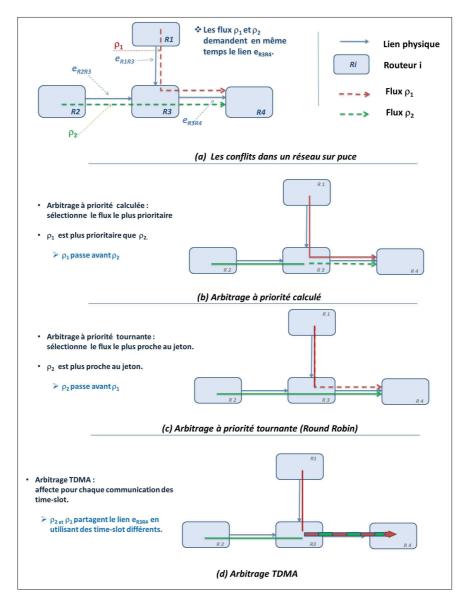

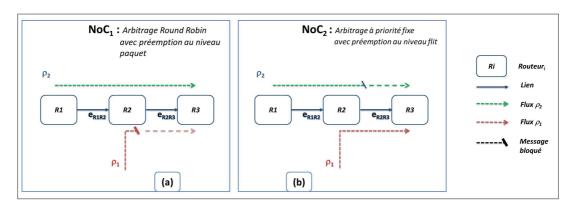

| 3.5 | Politiques d'arbitrage (a) présente un exemple d'interférence due au partage de ressources dans un réseau sur puce. Nous présentons dans (b) le comportement de l'arbitre à priorité tournante. (c) décrit le comportement de l'arbitre à priorité calculée. Le comportement de l'arbitre TDMA est illustré dans (d).                                                                                                                                                                                                                        | 41 |

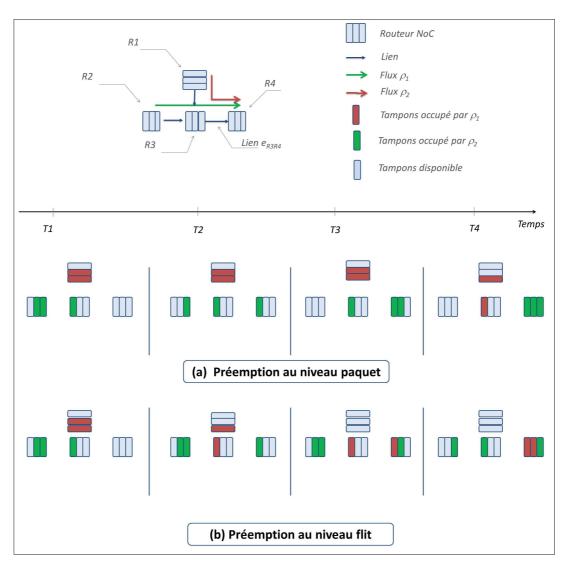

| 3.6 | Préemption dans le réseau sur puce. Les flux $\rho_1$ et $\rho_2$ partagent le lien $e_{R3R4}$ . Dans (a), $\rho_1$ attend le passage de $\rho_2$ . Dans (b), $\rho_1$ préempte $\rho_2$ au niveau flit                                                                                                                                                                                                                                                                                                                                      | 42 |

| 3.7 | Composition du routeur NoC avec canaux virtuels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44 |

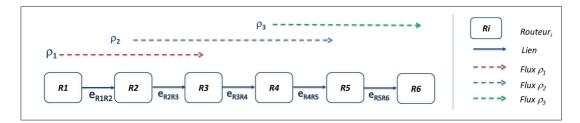

| 3.8 | Interférences des flux dans un NoC. Le flux $\rho_1$ utilise les liens $e_{R1R2}$ et $e_{R2R3}$ ; le flux $\rho_2$ utilise les liens $e_{R2R3}$ , $e_{R3R4}$ et $e_{R4R5}$ ; le flux $\rho_3$ utilise les liens $e_{R4R5}$ et $e_{R5R6}$ .                                                                                                                                                                                                                                                                                                   | 50 |

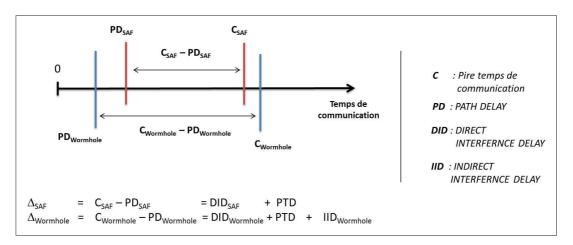

| 3.9 | Temps de communication pour une situation d'interférence directe                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51 |

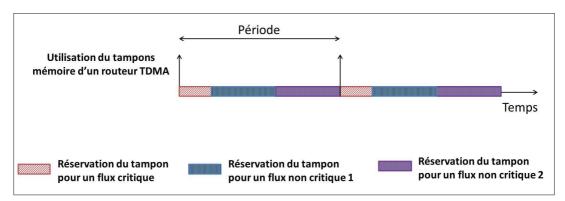

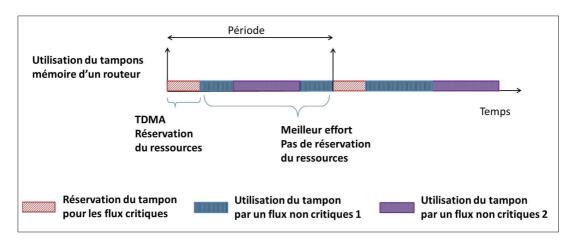

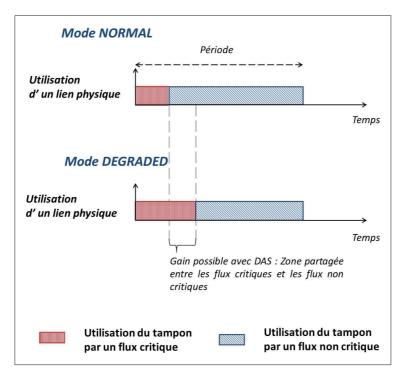

| 4.1 | Réservation des ressources dans un routeur TDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59 |

| 4.2 | Utilisation des ressources dans un routeur hybride                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 60 |

| 4.3 | Utilisation des ressources dans DAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66 |

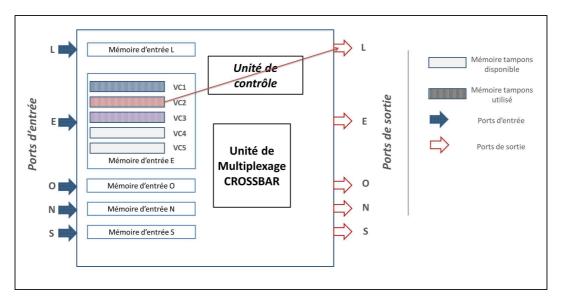

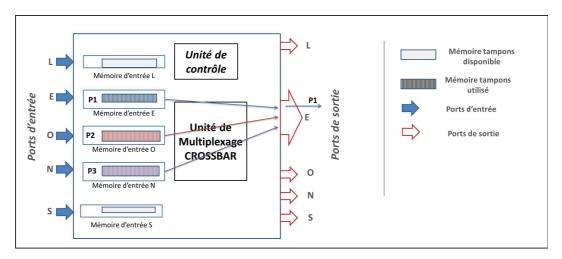

| 5.1  | Architecture du routeur DAS                                                                                                                                                                                                                                                                                                            | 73  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

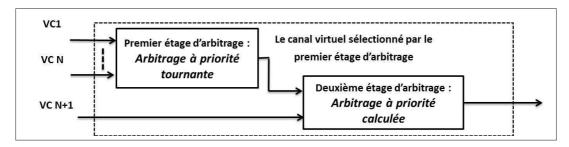

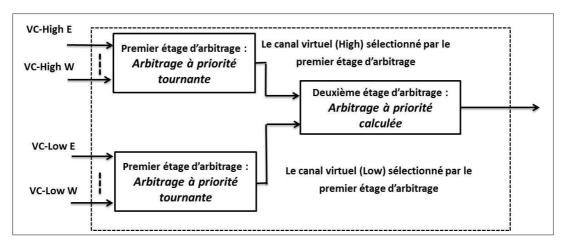

| 5.2  | Unité d'arbitrage d'entrée implanté dans DAS                                                                                                                                                                                                                                                                                           | 75  |

| 5.3  | Unité d'arbitrage de sortie implanté dans DAS                                                                                                                                                                                                                                                                                          | 75  |

| 5.4  | Rôle de l'unité d'arbitrage d'entrée                                                                                                                                                                                                                                                                                                   | 76  |

| 5.5  | Rôle de l'unité d'arbitrage de sortie                                                                                                                                                                                                                                                                                                  | 77  |

| 5.6  | Changements de mode de criticité pour chaque port d'E/S $$                                                                                                                                                                                                                                                                             | 79  |

| 5.7  | Analyse du pire temps de communication                                                                                                                                                                                                                                                                                                 | 81  |

| 5.8  | Temps de communication pour les techniques SAF et Wormhole .                                                                                                                                                                                                                                                                           | 86  |

| 6.1  | Temps de communication pour un flux ${\tt HIGH}$ - $3$ liens physiques $$ .                                                                                                                                                                                                                                                            | 95  |

| 6.2  | Temps de communication pour un flux ${\tt HIGH}$ - $4$ liens physiques $$ .                                                                                                                                                                                                                                                            | 95  |

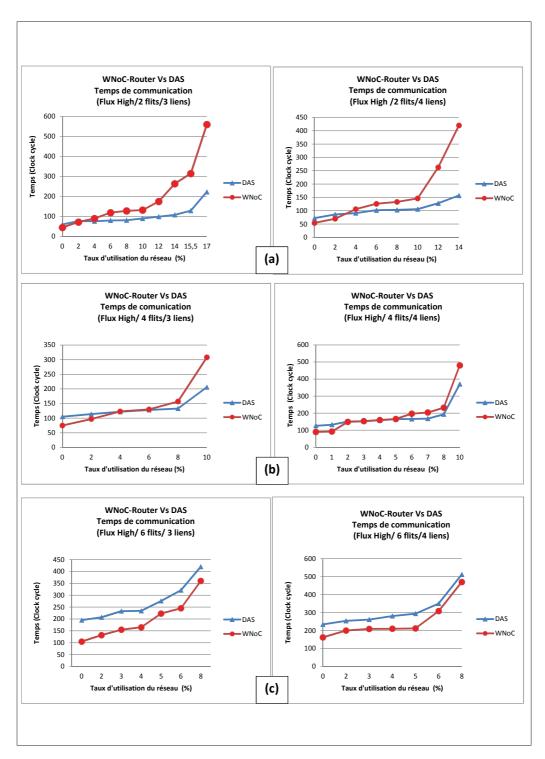

| 6.3  | Temps de communication pour FirstHigh (a) Taille $= 2$ flits (b) Taille $= 4$ flits (c) Taille $= 6$ flits $\dots \dots \dots \dots \dots$                                                                                                                                                                                             | 97  |

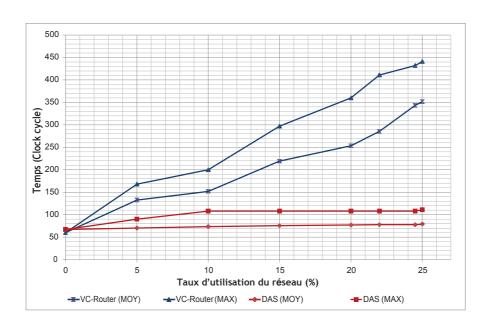

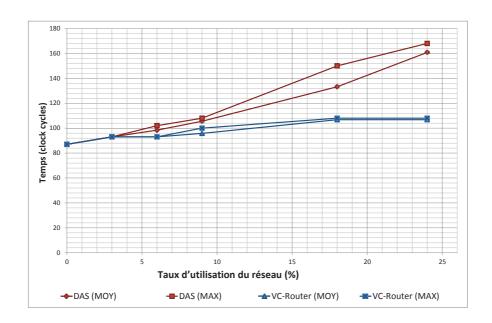

| 6.4  | Temps de communication pour les flux ${\tt LOW}$ - trafic uniforme                                                                                                                                                                                                                                                                     | 98  |

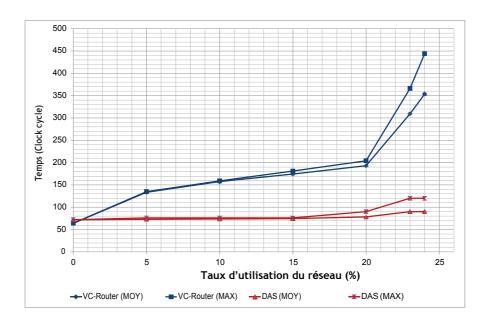

| 6.5  | Temps de communication pour les flux ${\tt LOW}$ - trafic All-To-One $$ .                                                                                                                                                                                                                                                              | 99  |

| 6.6  | Rosace : graphe de tâches                                                                                                                                                                                                                                                                                                              | 100 |

| 6.7  | Rosace : Allocation des tâches                                                                                                                                                                                                                                                                                                         | 101 |

| 6.8  | Impact du temps de communication des flux sur l'ordonnancement du système                                                                                                                                                                                                                                                              | 103 |

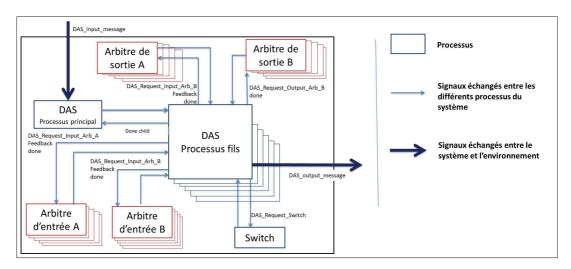

| 6.9  | L'architecture globale du modèle de DAS avec le langage IF                                                                                                                                                                                                                                                                             | 107 |

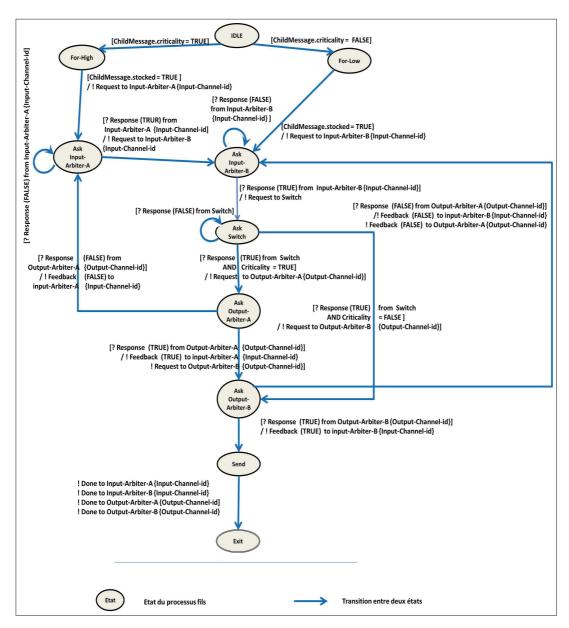

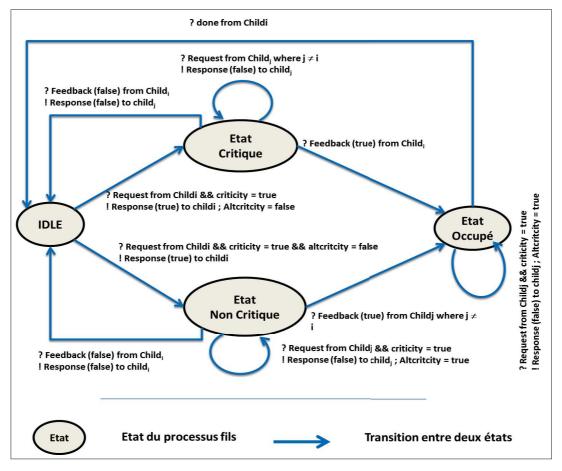

| 6.10 | Processus fils - Machine d'état                                                                                                                                                                                                                                                                                                        | 108 |

| 6.11 | Arbitre d'entrée B - Machine d'état                                                                                                                                                                                                                                                                                                    | 110 |

| 6.12 | The IF Cut Observer of the Property 3                                                                                                                                                                                                                                                                                                  | 113 |

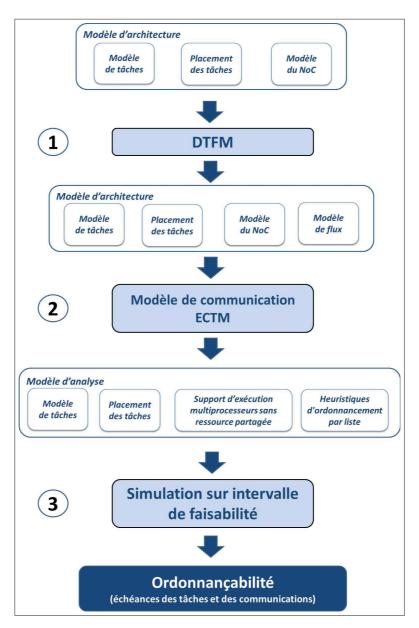

| 7.1  | Approche générale pour l'analyse d'ordonnancement d'un NoC - Objectif                                                                                                                                                                                                                                                                  | 117 |

| 7.2  | Approche générale pour l'analyse d'ordonnancement d'un NoC - Moyens                                                                                                                                                                                                                                                                    | 119 |

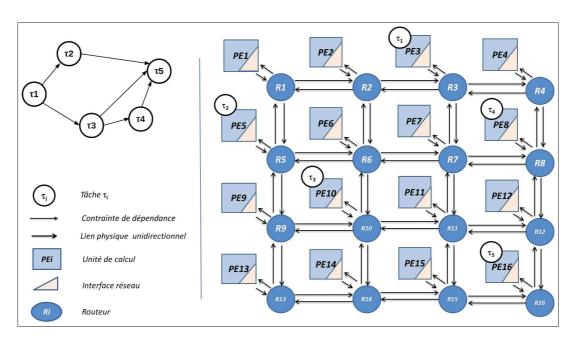

| 7.3  | Dual Task and Flow Model (DTFM) Exemple - Modèle de tâches et modèle de NoC. L'unité de calcul PE3 exécute la tâche $\tau_1$ . L'unité de calcul PE5 exécute la tâche $\tau_2$ . L'unité de calcul PE8 exécute la tâche $\tau_4$ . L'unité de calcul PE10 exécute la tâche $\tau_3$ . L'unité de calcul PE16 exécute la tâche $\tau_5$ | 123 |

| 7.4  | Modèle de communication pour les architectures NoC - Approche                                                                                                                                                                                                                                                                          |     |

|      | générale                                                                                                                                                                                                                                                                                                                               | 125 |

#### Table des figures

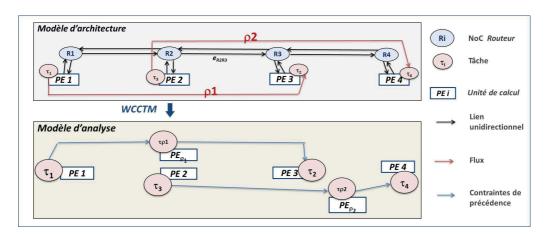

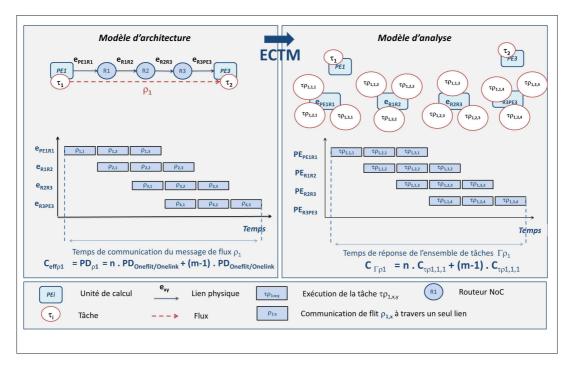

| 7.5  | Worst Case Communication Time Model (WCCTM) - Exemple de transformation          |

|------|----------------------------------------------------------------------------------|

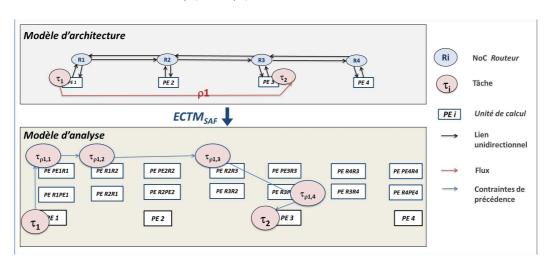

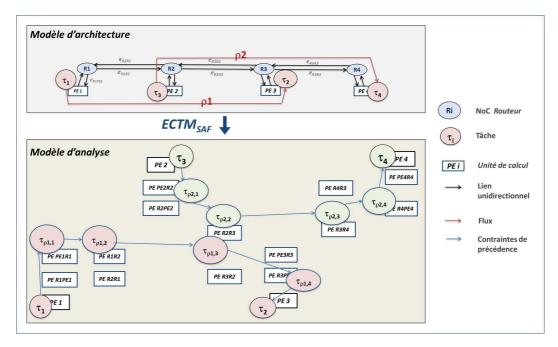

| 7.6  | $ECTM_{SAF}$ - Exemple de transformation - 1 flux (2 flits) 130                  |

| 7.7  | $ECTM_{SAF}$ - Exemple de transformation - 2 flux (2 flits) $$ 131               |

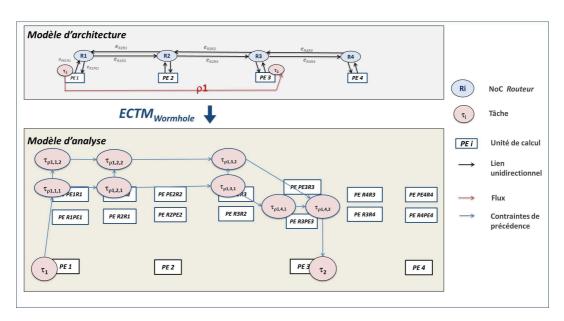

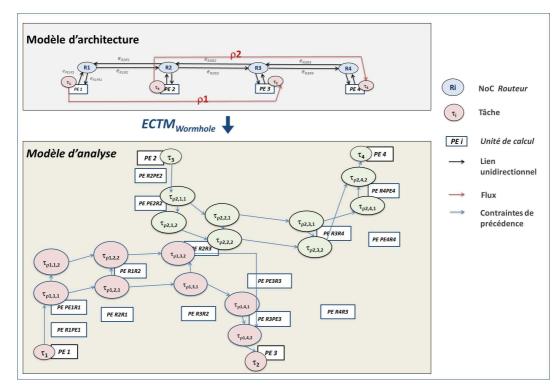

| 7.8  | $ECTM_{Wormhole}$ - Exemple de transformation - 1 flux 133                       |

| 7.9  | $ECTM_{Wormhole}$ - Exemple de transformation - 2 flux $\ \ldots \ \ldots \ 133$ |

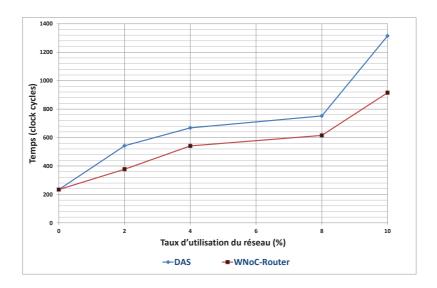

| 7.10 | $ECTM_{Wormhole}$ - Validation                                                   |

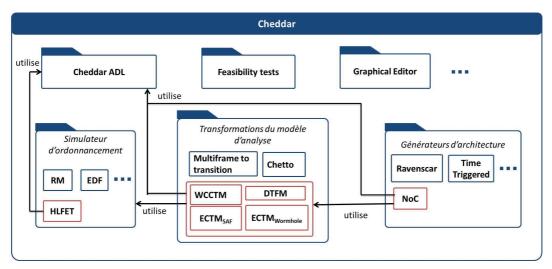

| 7.11 | Implantation de DTFM, ECTM et WCCTM dans Cheddar $142$                           |

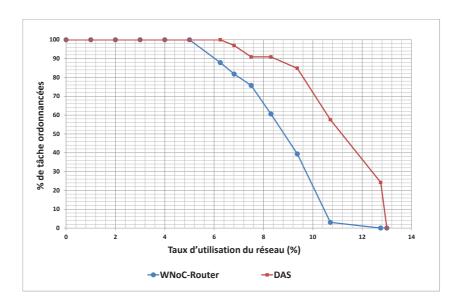

| 7.12 | Taux d'ordonnançabilité pour le modèle All-To-One                                |

| 7.13 | Taux d'ordonnançabilité pour le modèle One-To-One $\ \ldots \ \ldots \ 145$      |

| 7.14 | Temps de calcul pour les modèles de communications                               |

## Liste des tableaux

| 17 |

|----|

| 44 |

| 52 |

| 81 |

| 82 |

| 92 |

| 02 |

| 11 |

| 12 |

| 23 |

| 23 |

| 25 |

|    |

# Introduction

Dans le contexte des systèmes temps réel, le respect des contraintes temporelles est aussi important que l'exactitude du résultat. Autrement dit, la validité d'un système temps réel ne dépend pas seulement des résultats logiques des traitements mais également de la date de livraison du résultat [1]. Aujourd'hui, les systèmes temps réel sont de plus en plus présents autour de nous. Ils sont présents dans de nombreux secteurs d'activités comme les transports (contrôleurs pour les avions, les voitures, . . .), les systèmes de détection (radars, sonars, . . .), et le multimédia (lecteurs vidéo, téléphones, . . .).

Suivant l'importance accordée aux contraintes temporelles, nous distinguons les systèmes temps réel strict ou dur et les systèmes temps réel mou ou souple [1]. Dans les systèmes temps réel dur, nous devons respecter les contraintes temporelles même dans la pire des situations d'exécution possibles. Un dépassement d'échéance peut conduire à des situations critiques, voire catastrophiques [2]. Le contrôle de commande d'un avion et les applications de surveillance sont des exemples d'applications temps réel dur. Contrairement aux systèmes temps réel dur, les systèmes temps réel mou peuvent tolérer certains dépassements d'échéance [2]. Les applications de visioconférence et les jeux en réseau sont des exemples de systèmes temps réel mou.

Ces dernières années, il y a eu un intérêt accru pour l'intégration de plusieurs applications temps réel sur la même plate-forme d'exécution dans le but de réduire le coût, le poids et la consommation d'énergie. Cette intégration a conduit à la conception des systèmes à criticité mixte. Dans la communauté temps réel, les systèmes à criticité mixte sont constitués d'applications avec des niveaux de criticité différents qui s'exécutent sur la même plateforme d'exécution [3, 4].

La conception d'architectures multiprocesseurs est une autre tendance qui a suscité une attention toute particulière ces dernières années. Les réseaux sur puce (ou en anglais Network-on-Chip (NoC)) sont devenus un composant essentiel des architectures multiprocesseurs. Son adoption a été motivée par la nécessité de trouver une alternative aux communications par bus qui ne peuvent offrir le débit requis par un nombre croissant de processeurs, de mémoires et autres composants devant échanger concurremment des données. Un NoC est une méthode d'interconnexion qui simplifie l'intégration de composants complexes sur des systèmes sur puce (ou en anglais System-on-Chip (SoC)) [5] et permet de résoudre, dans une certaine mesure, le problème de saturation constaté avec les systèmes à base de bus. Les NoC présentent de nombreux avantages tels que l'augmentation des débits d'échanges, la réduction des temps de latence, l'extensibilité et la flexibilité [5].

Au regard de ces avantages, l'intégration des systèmes à criticité mixte sur des architectures NoC présente une solution prometteuse en termes de performance, coût, taille, poids et puissance [6].

Nous supposons dans ce travail que l'exécution des systèmes à criticité mixte sur des architectures NoC exige l'assurance des contraintes temporelles pour les applications critiques tout en minimisant l'impact du partage de ressources sur les applications non critiques.

Nous nous intéressons dans le cadre de ce travail au challenge consistant à déployer des systèmes à criticité mixte sur des architectures NoC. Dans la suite, nous détaillons les problématiques étudiées dans le cadre de cette thèse.

#### 1.1 Motivations et objectifs

Nous pouvons rencontrer plusieurs obstacles lors du déploiement des systèmes à criticité mixte sur les architectures NoC. Ces obstacles sont principalement :

## 1. L'incompatibilité des routeurs NoC existants avec les exigences des systèmes à criticité mixte

Le partage de ressources dans un NoC tel que les liens physiques et les routeurs introduit des interférences et des délais de communications supplémentaires, ce qui complique l'analyse d'ordonnancement du système.

Ces dernières années, divers routeurs pour les systèmes temps réel ont été proposés pour les architectures NoC. La plupart de ces routeurs sont capables de réduire et borner le temps de communication et de satisfaire les exigences temporelles pour les applications temps réel dur et mou [5].

Toutefois, pour déployer des systèmes à criticité mixte sur des architectures NoC, nous avons besoin d'un routeur NoC qui assure à la fois les contraintes

temporelles des communications critiques et limite la réservation des ressources pour les communications non critiques.

L'incompatibilité des routeurs NoC existants avec les exigences des systèmes à criticité mixte est une des raisons du non déploiement de ce genre du système sur les architectures NoC [7].

#### 2. Des modèles de tâches et de flux incomplets

Les modèles de tâches et les modèles de flux existants dans la littérature ne sont pas applicables immédiatement avec les architectures NoC. De nombreux modèles de tâches et de flux ont été proposés pour traiter les applications temps réel [8, 6] pour les NoC. Toutefois, les modèles de tâches proposés ne prennent pas en compte les communications à travers le NoC, l'affectation des tâches et les latences introduites par ce nouveau type de ressources partagées [6]. De même, les modèles de flux proposés pour les NoC ignorent l'ordonnancement des tâches [8]. Ainsi, ces modèles ne sont pas suffisants pour modéliser intégralement un système temps réel déployé sur un NoC.

## 3. Absence d'analyse des communications dans les techniques d'analyses d'ordonnancement temps réel

Les architectures NoC introduisent des nouvelles interférences variables en fonction de la configuration du NoC, de l'affectation des tâches et de l'état du réseau [5, 9]. Les délais de communication produits suite à ces nouvelles interférences doivent être considérés dans l'analyse d'ordonnancement du système.

Toutefois, les techniques d'analyse d'ordonnancement existantes ignorent ces interférences [10]. Ne pas tenir compte des interférences introduites par les architectures NoC fausse l'analyse d'ordonnancement du système.

#### 1.2 Contributions

Pour résoudre les problèmes mentionnés précédemment, nous avons proposé plusieurs contributions sous la forme d'un routeur, de modèles de tâches, de flux et de communications pour les NoC.

Nous avons proposé un nouveau routeur NoC dans le but d'exécuter des systèmes à criticité mixte sur un NoC. Afin de prédire l'ordonnancement des systèmes à criticité mixte sur un NoC, nous avons proposé un modèle de tâches et de flux ainsi qu'un modèle de communication. Dans la suite, nous détaillons nos contributions.

#### • DAS, un routeur pour les systèmes à criticité mixte

Afin de répondre à la première problématique, nous avons proposé un routeur NoC appelé *Double Arbiter and Switching Router* (DAS). DAS est un routeur conçu pour déployer un système temps réel à criticité mixte sur des architectures NoC. DAS assure les contraintes temporelles pour les communications critiques tout en limitant la réservation des ressources par les communications critiques. Afin de répondre aux exigences des systèmes à criticité mixte, DAS implante deux modes de fonctionnement, deux niveaux de préemption, deux techniques de contrôle de flux et deux étages d'arbitrage.

Nous avons évalué le routeur proposé sur 3 niveaux d'abstraction différents (circuit, transaction et système).

#### • Dual Task And Flow Model (DTFM)

Afin de répondre à la deuxième problématique, nous avons proposé DTFM. DTFM est une méthode conçue pour modéliser les systèmes temps réel déployés sur des architectures NoC. À partir du modèle de tâches, du modèle de NoC et du placement des tâches, DTFM calcule automatiquement le modèle de flux correspondant. DTFM prend en compte la technique de commutation adoptée par le NoC. Il supporte les techniques Wormhole [11] et Store And Forward (SAF) [12].

#### • Exact Communication Time Model (ECTM)

Pour tenir compte des communications lors de l'analyse d'ordonnancement des tâches, nous avons proposé ECTM. ECTM est un modèle de communication pour les architectures NoC. Nous montrons qu'ECTM peut conduire à une analyse d'ordonnancement efficace. Il supporte les techniques Wormhole et Store and Forward. Il modélise les communications par des graphes de tâches tout en tenant compte du modèle de NoC utilisé.

Afin de répondre à la troisième problématique, nous proposons de combiner DTFM et ECTM. D'abord, DTFM calcule le modèle de flux. Ensuite, ECTM applique ses transformations sur le modèle de flux calculé par DTFM afin de conduire une analyse d'ordonnancement avec des méthodes classiques de la littérature.

Nous avons utilisé DTFM lors de l'évaluation de DAS. Par contre, le modèle de communication ECTM n'est pas directement applicable au routeur proposé. En effet, DAS requiert un modèle de communication supportant conjointement SAF et Wormhole alors que nous avons proposé ECTM pour ces deux modes de commutation séparément. L'adaptation d'ECTM pour les caractéristiques de DAS est l'un de nos futurs travaux pour cette thèse.

#### 1.3 Plan

Ce document est divisé en huit chapitres. Les deux premiers chapitres exposent les notions de base nécessaires à la compréhension de nos travaux ainsi que des travaux connexes aux nôtres. Le chapitre 2 présente les systèmes à criticité mixte. Le chapitre 3 présente les architectures NoC.

Nous discutons des motivations, des objectifs et des contributions de cette thèse dans le chapitre 4. Ensuite, les chapitres 5, 6 et 7 présentent les contributions de cette thèse. Dans le chapitre 5, nous détaillons l'architecture et le fonctionnement de DAS. Puis, dans le chapitre 6, nous discutons de l'évaluation de DAS sur plusieurs niveaux d'abstraction. Nous décrivons DTFM et le modèle de communication pour les architectures NoC proposées dans le chapitre 7. Finalement, nous terminons cette thèse par une conclusion.

Première partie

Contexte - État de l'art

# 2

## Les systèmes temps réel à criticité mixte

| mmaiı | re    |                                                               |           |

|-------|-------|---------------------------------------------------------------|-----------|

| 2.1   | Syst  | tèmes temps réel                                              | 10        |

|       | 2.1.1 | Systèmes temps réel dur                                       | 11        |

|       | 2.1.2 | Systèmes temps réel mou                                       | 11        |

|       | 2.1.3 | Modèle de tâches                                              | 12        |

|       |       | 2.1.3.1 Tâche périodique, apériodique et sporadique           | 12        |

|       |       | 2.1.3.2 Caractéristiques d'une tâche temps réel               | 13        |

|       |       | 2.1.3.3 Dépendance                                            | 14        |

|       | 2.1.4 | Modèle de support d'exécution                                 | 15        |

| 2.2   | Syst  | tèmes à criticité mixte                                       | <b>15</b> |

|       | 2.2.1 | Modèle de tâches                                              | 17        |

|       | 2.2.2 | Changement de mode de criticité                               | 17        |

| 2.3   |       | oduction à l'analyse d'ordonnancement des systèmes<br>ps réel | <b>20</b> |

|       | 2.3.1 | Algorithme d'ordonnancement                                   | 20        |

|       |       | 2.3.1.1 Ordonnancement avec ou sans préemption .              | 20        |

|       |       | 2.3.1.2 Ordonnancement hors ligne ou en ligne                 | 21        |

|       |       | 2.3.1.3 Ordonnancement global ou par partitionnement          | 21        |

|       | 2.3.2 | Analyse d'ordonnancement                                      | 22        |

|       |       | 2.3.2.1 Approche analytique                                   | 22        |

|       |       | 2.3.2.2 Approche par simulation de l'ordonnancement           | 22        |

| 2.4 Ordonnancement temps réel multiprocesseur de tâches dépendantes |          |                                                       |    |

|---------------------------------------------------------------------|----------|-------------------------------------------------------|----|

| 2.4.1                                                               |          | onomie des algorithmes d'ordonnancement mul-<br>seurs | 23 |

| 2.4.2                                                               | Heuristi | iques d'ordonnancement par liste                      | 24 |

| 2.4.3                                                               | Réseau   | sur puce                                              | 27 |

|                                                                     | 2.4.3.1  | Algorithmes d'allocation des tâches                   | 27 |

|                                                                     | 2.4.3.2  | Analyse du temps de communication                     | 27 |

|                                                                     | 2.4.3.3  | Algorithmes d'ordonnancement des tâches $$ .          | 27 |

| 2.5 Cor                                                             | nclusion |                                                       | 28 |

#### Introduction

Exécuter des systèmes à criticité mixte sur des architectures multiprocesseurs est une solution prometteuse en terme de performance de calcul et de consommation énergétique [6]. L'ordonnancement des systèmes à criticité mixte sur des architectures multiprocesseurs a connu un regain d'intérêt ces dix dernières années ce qui s'est traduit par un grand nombre de propositions [6].

La première partie de ce chapitre présente les concepts de base de l'analyse d'ordonnancement des systèmes à criticité mixte. Nous présentons brièvement les systèmes temps réel. Ensuite, nous discutons de la définition des systèmes à criticité mixte. Nous expliquons aussi le rôle des algorithmes d'ordonnancement et les différentes techniques d'analyse d'ordonnancement.

Dans la deuxième partie de ce chapitre, nous proposons une taxonomie des algorithmes d'ordonnancement multiprocesseurs. Puis, nous présentons un état de l'art des algorithmes d'ordonnancement temps réel multiprocesseurs pour les tâches dépendantes. Ensuite, nous abordons les algorithmes multiprocesseurs qui s'intéressent aux systèmes à criticité mixte.

#### 2.1 Systèmes temps réel

#### Définition 1. (Système temps réel)

Un système temps réel est défini comme un système dont le comportement dépend de l'exactitude des traitements effectués et de la date où les résultats sont produits [1]. En d'autres termes, dans le contexte d'un système temps réel, nous devons satisfaire deux contraintes importantes :

- Exactitude logique : le système produit des résultats logiquement corrects.

- Exactitude temporelle : le système produit les résultats au bon moment (avant les échéances du système).

Les systèmes temps réel sont de plus en plus présents autour de nous [1]. Nous pouvons les trouver dans de nombreux domaines : aéronautique, militaire, robotique, télécommunication, etc.

Les systèmes temps réel sont généralement classés en plusieurs catégories suivant le niveau de sûreté temporelle demandé. Les deux catégories principales sont les systèmes temps réel dur (ou en anglais HARD REAL-TIME SYSTEM) et les systèmes temps réel mou (ou en anglais SOFT REAL-TIME SYSTEM) [13].

Dans la suite, nous définissons les systèmes temps réel dur et mou.

#### 2.1.1 Systèmes temps réel dur

#### Définition 2. (Système temps réel dur)

Les systèmes dits temps réel dur sont ceux pour lesquels le système doit impérativement garantir le respect des échéances fixées pour l'exécution des tâches [13].

Le respect de toutes les contraintes temporelles est indispensable pour le bon fonctionnement d'un système temps réel dur. Dans le contexte d'un système temps réel dur, une échéance non respectée peut endommager le système et conduire à des situations catastrophiques. Un système temps réel dur doit impérativement respecter toutes les contraintes temporelles même dans la pire des situations d'exécution possibles [2]. Le pilote automatique d'un avion et le système de surveillance d'une centrale nucléaire sont des exemples des systèmes temps réel dur.

#### 2.1.2 Systèmes temps réel mou

#### Définition 3. (Système temps réel mou)

Un système temps réel mou est un système où l'on tolére que certaines contraintes temporelles ne soient pas satisfaites. Ces violations peuvent dégrader l'expérience utilisateur du système sans compromettre le fonctionnement global [2].

Contrairement au système temps réel dur, le système temps réel mou peut tolérer un certain nombre de dépassements d'échéance sans que cela ait des conséquences catastrophiques. Les applications multimédia sont des exemples de systèmes temps réel mou [2].

Dans la suite nous présentons les concepts classiques des modèles de tâches pour un système temps réel.

#### 2.1.3 Modèle de tâches

#### Définition 4. (Tâche)

Une tâche est un ensemble d'instructions destinées à être exécutées sur une unité de calcul [14].

La caractérisation d'une tâche peut varier d'un modèle de tâches à un autre.

Divers modèles de tâches ont été proposés [6]. Dans la suite, nous introduisons la notion de tâche périodique. Puis, nous détaillons les paramètres les plus utilisés dans les modèles de tâches classiques. Ensuite, nous discutons des dépendances.

#### 2.1.3.1 Tâche périodique, apériodique et sporadique

Dans cette partie, nous définissons les tâches périodiques, les tâches sporadiques et les tâches apériodiques.

#### Définition 5. (Tâche périodique)

Une tâche périodique est une tâche dont le réveil est régulier et le délai entre deux réveils successifs est constant [14].

#### Définition 6. (Tâche sporadique)

Une tâche sporadique est une tâche caractérisée par un délai minimum entre deux réveils successifs [14].

#### Définition 7. (Tâche apériodique)

Les tâches apériodiques sont réveillées à des instants aléatoires. Elles sont généralement activées sur un événement extérieur [14].

Les tâches périodiques et les tâches sporadiques se répètent indéfiniment. Les instances de réveil d'une tâche périodique sont séparées par une période constante. Par contre, les tâches sporadiques se caractérisent par un délai minimum entre deux réveils. Contrairement aux tâches périodiques et sporadiques, les tâches apériodiques s'exécutent une seul fois.

#### 2.1.3.2 Caractéristiques d'une tâche temps réel

Nous considérons un ensemble de n tâches  $\Gamma = \{\tau_1, \tau_2, \dots, \tau_n\}$ . Chaque tâche  $\tau_i$  est caractérisée par :

- $O_i$  (Offset) : date de premier réveil d'une tâche  $\tau_i$ . Elle représente la date à laquelle la tâche  $\tau_i$  peut commencer son exécution.

- $C_i$  (Capacity) : capacité de la tâche  $\tau_i$ . Elle représente la durée d'exécution d'une tâche  $\tau_i$ . Dans la majorité des travaux d'ordonnancement temps réel, ce paramètre est considéré comme le pire temps d'exécution (ou en anglais WORST CASE EXECUTION TIME (WCET)) [6].

- $D_i$  (Deadline) : échéance de la tâche  $\tau_i$ . Elle représente l'instant auquel l'exécution d'une tâche doit être terminée et dont le dépassement provoque une violation de la contrainte temporelle.

- $P_i$  (Period) : période qui représente la durée séparant deux instants de réveils successifs.

- $\pi_i$  (Priority) : priorité de la tâche.

Tous ces paramètres sont illustrés dans la figure 2.1.

FIGURE 2.1 – Paramètres d'une tâche périodique.

Une tâche périodique  $\tau_i$  est représentée par cinq paramètres : une date de premier réveil  $O_i$ , une capacité  $C_i$ , une échéance  $D_i$ , une période  $P_i$  et une priorité  $\pi_i$ .

Dans la suite, nous discutons des contraintes de dépendance et de précedence entre les tâches.

#### 2.1.3.3 Dépendance

**Définition 8.** (Précédence) Une précédence désigne un ordre partiel d'exécution des tâches sans qu'il y ait nécessairement un transfert de données entre ces tâches [15].

#### Définition 9. (Dépendance)

Une dépendance désigne un ordre partiel d'exécution des tâches avec un transfert de données entre ces tâches [15].

En d'autres termes, la dépendance entre deux tâches impose une précédence entre la tâche qui produit des données et celle qui en consomme. Nous appelons la tâche qui produit les données la tâche source et la tâche qui consomme les données la tâche destination [15].

Plusieurs modèles de tâches ont été proposés pour les tâches dépendantes. Les dépendances entre les tâches peuvent être modélisées par des graphes acycliques orientés (ou en anglais DIRECTED ACYCLIC GRAPH (DAG)) [16].

#### Définition 10. (Directed Acyclic Graph (DAG))

Un DAG est un graphe  $G = (\Gamma, \Psi)$ , orienté et acyclique, où  $\Gamma$  représente les tâches, et  $\Psi$  les dépendances entre les tâches [16].

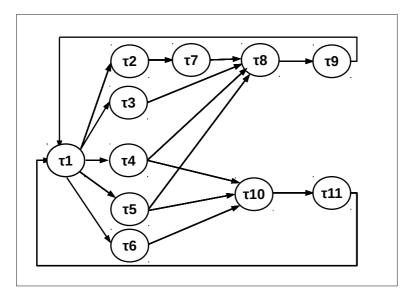

La figure 2.2 présente un exemple de DAG.

FIGURE 2.2 – Exemple d'un DAG.

Dans un DAG, les nœuds représentent les tâches et les arcs représentent les relations de dépendance entre les tâches. Une tâche d'entrée (respectivement de sortie) dans un DAG est une tâche n'ayant pas de prédécesseur (respectivement de successeur) dans le graphe.

#### 2.1.4 Modèle de support d'exécution

Après avoir présenté les modèles de tâches temps réel, nous décrivons dans cette partie le support d'exécution pour ces systèmes. Nous pouvons distinguer deux types de supports d'exécution : les systèmes monoprocesseurs et les systèmes multiprocesseurs. Dans les systèmes multiprocesseurs, nous trouvons les réseaux sur puce.

#### Définition 11. (Système monoprocesseur)

Un système monoprocesseur fournit une seule unité de calcul pour exécuter les applications [5].

#### Définition 12. (Système multiprocesseur)

Un système multiprocesseurs fournit au même moment plusieurs unités de calcul pour exécuter les applications [5].

Contrairement aux systèmes monoprocesseurs, sur les supports multiprocesseurs, les applications disposent de plusieurs unités de calcul simultanément pour s'exécuter.

#### Définition 13. (Réseau sur puce)

Le réseau sur puce (en anglais Network-On-Chip (NoC)) est un paradigme de connexion entre les unités de calcul qui sont intégrées dans un système sur puce [17].

Dans un NoC, les messages sont acheminés de l'émetteur vers une ou plusieurs destinations via des routeurs [5]. Nous détaillerons l'architecture, le mode de fonctionnement et les caractéristiques des NoC dans le chapitre suivant.

Dans la suite, nous définissons les systèmes à criticité mixte.

#### 2.2 Systèmes à criticité mixte

Aujourd'hui, les supports d'exécution sont de plus en plus performants et fournissent des capacités de calcul plus importantes qu'avant. En effet, les plateformes actuelles comportent plusieurs unités de calcul. Par la suite, les possibilités matérielles ont fortement augmenté et la consommation énergétique est devenue un enjeu primordial [6]. L'exécution d'une application par support d'exécution n'est plus rentable car l'unité de calcul est sous-utilisée.

Il est donc primordial de pouvoir tirer parti de ces capacités de calcul et de minimiser le gaspillage d'énergie. Afin de répondre aux besoins d'intégrer des applications avec des niveaux de criticité différents sur le même support d'exécution, les systèmes temps réel à criticité mixte ont été proposés.

Dans le domaine avionique, nous pouvons trouver des applications avec des niveaux de criticité différentes. Les normes de sécurité et les pratiques de l'industrie avionique ont une définition particulière des systèmes à criticité mixte [18, 19, 20]. Nous pouvons citer à titre d'exemple les normes CEI 61508, DO-178B et ISO 26262 [21]. Dans ces normes industrielles, une isolation spatiale et temporelle entre les fonctions de niveaux de criticité différents est requis.

Cependant, la définition de système à criticité mixte proposée pour la première fois par Vestal [3] et ultérieurement par Burns et Davis [4] précise que les plates-formes d'exécution doit fournir des modes de fonctionnement différents pour les applications avec des niveaux de criticité différents [3]. Cette définition fait que le défi du MCS est de garantir les contraintes temporeeles des applications critiques, tout en minimisant l'impact du partage de ressources sur les applications non critiques.

#### Définition 14. (Systèmes temps réel à criticité mixte)

Les systèmes temps réel à criticité mixte sont des systèmes temps réel ayant la particularité d'avoir plusieurs modes de criticité (au moins deux) et des tâches avec des niveaux de criticité différents (au moins deux niveaux) [3, 4, 22].

Dans les systèmes ayant deux niveaux de criticité, nous distinguons deux types de tâches : les tâches critiques et les tâches non critiques.

#### Définition 15. (Tâches critiques)

Les tâches critiques (ayant un niveau de criticité élevé) sont des applications temps réel dur. Les échéances de ces applications doivent être respectées [3].

#### Définition 16. (Tâches non critiques)

Les tâches non critiques (ayant un niveau de criticité faible) sont des applications temps réel mou. Elles peuvent tolérer certains dépassements de leurs échéances [3].

En outre, un système à criticité mixte doit fonctionner sous plusieurs modes de criticité (au minimum deux modes) selon l'état du système [22].

#### Définition 17. (Mode de criticité)

Dans le contexte des systèmes à criticité mixte, le mode de criticité définit les paramètres d'exécution du système tels que les capacités et les périodes des tâches [22].

Dans cette partie, nous présentons le modèle des systèmes à criticité mixte proposé par Vestal [3]. Puis, nous décrivons le mécanisme de changement de mode.

#### 2.2.1 Modèle de tâches

D'après Vestal [3], un système est composé d'un ensemble de n tâches périodiques  $(\Gamma = \{\tau_1, \tau_2, \dots, \tau_n\})$  ayant k niveaux de criticité différents [3]. Nous notons ici que le système à criticité mixte fonctionne sous j modes de criticité avec  $j \geq 2$  et  $k \geq 2$ .

Chaque tâche  $\tau_i$  de l'ensemble  $\Gamma$  est caractérisée par un ensemble de paramètres :  $\tau_i = \{ O_i, C_i(a), D_i P_i, Crit_i \}$

avec:

- $O_i$  représente la date du premier réveil de la tâche  $\tau_i$ .

- C<sub>i</sub>(a) représente le pire temps d'exécution de la tâche τ<sub>i</sub> sous le mode de criticité a avec 1 ≤ a ≤ j. Nous notons ici que C<sub>i</sub> est une fonction. La valeur de C<sub>i</sub> est déterminée en fonction du niveau de criticité de la tâche et du mode de criticité actuel du système [3].

TABLE 2.1 – Capacité d'une tâche pour un système à criticité mixte. La tâche  $\tau_i$  possède plusieurs valeurs de capacité en fonction du mode de criticité.  $C_i(1)$  est la capacité de  $\tau_i$  dans le mode 1.  $C_i(j)$  est la capacité de  $\tau_i$  dans le mode j.

| Mode de criticité | Mode 1   | <br>Mode a   | <br>Mode j   |

|-------------------|----------|--------------|--------------|

| $C_i$             | $C_i(1)$ | <br>$C_i(a)$ | <br>$C_i(j)$ |

- $D_i$  représente l'échéance de la tâche  $\tau_i$ .

- $P_i$  représente la période de la tâche  $\tau_i$ .

- $Crit_i$  représente le niveau de criticité de la tâche  $\tau_i$ .