# Adapting a HPC runtime system to FPGAs Georgios Christodoulis

## ▶ To cite this version:

Georgios Christodoulis. Adapting a HPC runtime system to FPGAs. Operations Research [math.OC]. Université Grenoble Alpes, 2019. English. NNT: 2019GREAM061. tel-02948338

# HAL Id: tel-02948338 https://theses.hal.science/tel-02948338v1

Submitted on 24 Sep 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique Arrêté ministériel : 25 mai 2016

Présentée par

# **Georgios CHRISTODOULIS**

Thèse dirigée par **Frédéric DESPREZ** et codirigée par **François Broquedis** et **Olivier MULLER**, MCF, Grenoble INP

préparée au sein du Laboratoire d'Informatique de Grenoble dans l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique

# Adaption d'un système HPC pour intégrer des FPGAs

# Adapting a HPC runtime system to FPGAs

Thèse soutenue publiquement le **5 décembre 2019**, devant le jury composé de :

#### Monsieur FREDERIC DESPREZ

DIRECTEUR DE RECHERCHE, INRIA CENTRE DE GRENOBLE RHÔNE-ALPES. Directeur de thèse Monsieur CHRISTIAN PEREZ DIRECTEUR DE RECHERCHE, INRIA CENTRE DE GRENOBLE RHÔNE-ALPES, Rapporteur Monsieur SMAÏL NIAR PROFESSEUR, UNIV. POLYTECHNIQUE DES HAUTS-DE-FRANCE, Rapporteur **Monsieur FRANÇOIS BROQUEDIS** MAITRE DE CONFERENCES, GRENOBLE INP, Examinateur Monsieur OLIVIER MULLER MAITRE DE CONFERENCES, GRENOBLE INP, Examinateur Monsieur RAYMOND NAMYST PROFESSEUR, UNIVERSITE DE BORDEAUX, Président Monsieur DAVID NOVO CHARGE DE RECHERCHE, CNRS DELEGATION OCCITANIE EST, Examinateur

## Abstract

Along with the traditional CPU cores, processing units of different architectures are now employed by the High Performance Computing (HPC) community in order to obtain improved efficiency and performance. A Field Programmable Gate Array (FPGA), is a hardware fabric composed of interconnected re-programmable logic and memory blocks. This type of processing unit, is considered a promising candidate to amplify the efficiency and the computational power of heterogeneous HPC platforms since it comes with massive parallelism and a reduced amount of abstraction layers between the application and the actual hardware.

However, exploiting FPGA requires an in-depth knowledge of low-level hardware design and high expertise on vendor-provided tools, which is not aligned with the skills of high performance computing application programmers. In the scope of this thesis, we have designed a framework that allows straightforward development of scientific applications over heterogeneous platforms enhanced with FPGA. Using this framework requires only a limited knowledge of the underlying architecture, and an FPGA can be used in the same way as any other type of processing unit. At the core of the proposed framework there is the StarPU heterogeneous runtime system, that was extended to support this new type of accelerator, hiding from the programmer complex operations deriving from the complexity of the underlying architecture while it allows fine control of the performance through different scheduling strategies. For the communication part, we created Conor, a communication library based on RIFFA, that enforces consistency in scenarios with concurrent accesses to the FPGA.

The approach proposed by our framework is evaluated across two directions. The first one corresponds to programmability, while the second one concerns the performance overhead imposed by the additional components attached to the FPGA. Both the programmability and overhead of the framework are evaluated using a basic blocked version of matrix multiplication showing the ease of development and the negligible overhead imposed by FPGA management to the rest of the framework. In addition to our experiments on matrix multiplication, we created an efficient hardware design of *GEMM*, that will allow the execution of more complex and interesting applications like the Cholesky decomposition.

# Contents

| 1        | Intr | oducti | ion        |                                                          | 1  |

|----------|------|--------|------------|----------------------------------------------------------|----|

| <b>2</b> | Bac  | kgrou  | nd And     | Problem Statement                                        | 4  |

|          | 2.1  | Parall | elism Is E | Everywhere                                               | 5  |

|          | 2.2  | HPC S  | Systems    |                                                          | 7  |

|          |      | 2.2.1  | Hardwar    | re Organization                                          | 8  |

|          |      |        | 2.2.1.1    | Parallelism Inside A CPU                                 | 8  |

|          |      |        | 2.2.1.2    | From Processors To Nodes                                 | 11 |

|          |      |        | 2.2.1.3    | From Nodes To Clusters                                   | 13 |

|          |      | 2.2.2  | How To     | Program An HPC System?                                   | 13 |

|          |      |        | 2.2.2.1    | Extracting Parallelism In An Application                 | 14 |

|          |      |        | 2.2.2.2    | Parallel Programming Models                              | 15 |

|          | 2.3  | FPGA   |            |                                                          | 16 |

|          |      | 2.3.1  | FPGA:      | Architecture                                             | 17 |

|          |      | 2.3.2  | How To     | Program An FPGA Chip?                                    | 20 |

|          |      | 2.3.3  | FPGA:      | Memory                                                   | 21 |

|          |      | 2.3.4  | FPGA:      | Communication With Its Environment                       | 22 |

|          | 2.4  | Perfor | mance Re   | esults Of FPGAs On HPC Applications                      | 23 |

|          | 2.5  | Proble | em Staten  | nent                                                     | 26 |

| 3        | Rel  | ated W | Vork       |                                                          | 29 |

|          | 3.1  | Hetero | ogeneous   | Programming Approaches From The HPC Community            | 31 |

|          |      | 3.1.1  | Low-Lev    | vel Device Programming Libraries: OpenCL and CUDA        | 32 |

|          |      | 3.1.2  | High-Le    | vel Heterogeneous Programming Environments               | 36 |

|          |      |        | 3.1.2.1    | <b>OPENACC</b> - An Industrial Specification For Hetero- |    |

|          |      |        |            | geneous Computing                                        | 37 |

|          |      |        | 3.1.2.2    | Runtime Support For Heterogeneous Task Execution         |    |

|          |      |        |            | Using Charm++                                            | 37 |

|     |        | 3.1.2.3  | OmpSs - Runtime Support Of FPGA For SoC               | 39 |

|-----|--------|----------|-------------------------------------------------------|----|

|     |        | 3.1.2.4  | ANTHILL - Runtime Support For Large Heterogeneous     |    |

|     |        |          | Distributed Environments                              | 40 |

|     |        | 3.1.2.5  | StarPU - A Runtime System For Heterogeneous Plat-     |    |

|     |        |          | forms                                                 | 41 |

|     |        | 3.1.2.6  | HARMONY- Runtime Support For Heterogeneous Many       |    |

|     |        |          | Core Systems                                          | 41 |

|     |        | 3.1.2.7  | QILIN - Adaptive Workload Mapping For Heteroge-       |    |

|     |        |          | neous Machines With CPUs And GPUs                     | 42 |

| 3.2 | FPGA   | Accessit | bility From The Hardware Community                    | 43 |

|     | 3.2.1  | Thread   | Based Approaches                                      | 43 |

|     |        | 3.2.1.1  | HTHREADS - Hybrid Threads; A POSIX Compliant          |    |

|     |        |          | Thread Based Abstraction For Reconfigurable Com-      |    |

|     |        |          | puting                                                | 44 |

|     |        | 3.2.1.2  | SPREAD - A Thread Based Approach For Streaming        |    |

|     |        |          | Applications                                          | 45 |

|     |        | 3.2.1.3  | FUSE - Front-End USEr Framework To Utilize Hard-      |    |

|     |        |          | ware Accelerators Under An OS Abstraction             | 46 |

|     |        | 3.2.1.4  | <b>RECONOS-</b> Multithreaded Programming Environment |    |

|     |        |          | For Computers With Reconfigurable Components          | 47 |

|     | 3.2.2  | Dataflov | v Based Approaches                                    | 47 |

|     |        | 3.2.2.1  | FOSFOR - A Model For Dataflow Applications On         |    |

|     |        |          | Architectures With Reconfigurable Components          | 48 |

|     |        | 3.2.2.2  | <b>RECONFIGME -</b> An Operating System For Reconfig- |    |

|     |        |          | urable Computing                                      | 49 |

|     |        | 3.2.2.3  | FLEXTILES- Flexible Tiles For An Heterogeneous Many-  |    |

|     |        |          | core Architecture                                     | 50 |

|     | 3.2.3  | Process  | Based Approaches                                      | 50 |

|     |        | 3.2.3.1  | BORPH - Berkeley Operating System For RePro-          |    |

|     |        |          | grammable Hardware                                    | 51 |

|     |        | 3.2.3.2  | SPORE- Simple Parallel Platform For Reconfigurable    |    |

|     |        |          | Environment                                           | 51 |

| 3.3 | Bridgi | ng The G | Sap : Heterogeneous Programming With FPGA             | 52 |

|     | 3.3.1  | OpenCI   | Support For FPGA                                      | 52 |

|     | 3.3.2  | FCUDA    | A                                                     | 54 |

|     | 3.3.3  | OpenA    | CC Support For FPGA                                   | 55 |

|          |     | 3.3.4  | OMPSS Support For FPGA E                                             | 55 |

|----------|-----|--------|----------------------------------------------------------------------|----|

|          | 3.4 | Discus | ssion                                                                | 56 |

| 4        | An  | Heter  | ogeneous HPC Framework Integrating FPGA 5                            | 58 |

|          | 4.1 | The P  | Proposed Framework                                                   | 59 |

|          |     | 4.1.1  | Inside StarPU                                                        | 61 |

|          |     |        | 4.1.1.1 The Task Model                                               | 61 |

|          |     |        | 4.1.1.2 The Memory Model                                             | 64 |

|          |     |        | 4.1.1.3 Task Scheduling And Performance Models                       | 64 |

|          |     | 4.1.2  | The StarPU FPGA worker                                               | 66 |

|          |     | 4.1.3  | Conor: A Communication Library Based On RIFFA                        | 69 |

|          |     |        | 4.1.3.1 RIFFA                                                        | 69 |

|          |     |        | 4.1.3.2 Channel Allocation                                           | 72 |

|          |     |        | 4.1.3.3 IP Mapping                                                   | 73 |

|          |     |        | 4.1.3.4 Performance Reports                                          | 74 |

|          |     | 4.1.4  | Hardware Level Integration                                           | 74 |

|          |     |        | 4.1.4.1 IO Protocol For The IPs                                      | 75 |

|          |     |        | 4.1.4.2 Description Of The Connector                                 | 75 |

|          |     |        | 4.1.4.3 Overview Of The Entire Design                                | 78 |

|          | 4.2 | Evalua | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 80 |

|          |     | 4.2.1  | Blocked Matrix Multiplication                                        | 80 |

|          |     | 4.2.2  | The Programmers' Side                                                | 81 |

|          |     |        | 4.2.2.1 The StarPU Application                                       | 81 |

|          |     |        | 4.2.2.2 Writing Hardware Tasks                                       | 84 |

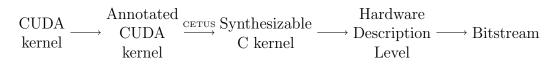

|          |     |        | 4.2.2.3 Generating The Bitstream                                     | 85 |

|          |     | 4.2.3  | Results                                                              | 85 |

|          | 4.3 | Concl  | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 90 |

| <b>5</b> | Het | erogen | neous Scheduling                                                     | 91 |

|          | 5.1 | Hetero | ogeneous Matrix Multiplication                                       | 92 |

|          | 5.2 | Choles | sky Decomposition                                                    | 95 |

|          | 5.3 | Analy  | sis On The Implementation Of The Cholesky Decomposition.             | 96 |

|          | 5.4 | Develo | oping A Hardware Design Of GEMM                                      | 98 |

|          |     | 5.4.1  | Hardware Design Optimizations Of GEMM.                               | 99 |

|          |     | 5.4.2  | Hardware GEMM - Performance Evaluation                               | 03 |

|          | 5.5 | Discus | ssion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $10$     | 05 |

| 6            | 6 Conclusion and Future Work |        |                              |     |

|--------------|------------------------------|--------|------------------------------|-----|

|              | 6.1                          | Conclu | sion                         | 107 |

|              | 6.2                          | Future | Work                         | 109 |

|              |                              | 6.2.1  | Heterogeneous Experiments    | 109 |

|              |                              | 6.2.2  | Interconnect Version Upgrade | 110 |

|              |                              | 6.2.3  | Dynamic Reconfiguration      | 111 |

|              |                              | 6.2.4  | Multi-Board Experiments      | 112 |

|              |                              | 6.2.5  | Use On-Board DDR             | 112 |

| $\mathbf{A}$ | App                          | endix  |                              | 114 |

| Bi           | bliog                        | raphy  |                              | 121 |

# List of Figures

| 2.1 | Overview of the GoldmontPlus CPU architecture by Intel [2]. The                                   |    |

|-----|---------------------------------------------------------------------------------------------------|----|

|     | architecture is used as a reference to demonstrate how parallelism is                             |    |

|     | employed in the design of a modern CPU.                                                           | 9  |

| 2.2 | Reference structure of a typical heterogeneous processing node. The                               |    |

|     | node is constructed by a set of CPU accessing the same main memory                                |    |

|     | (host), and a series of accelerators connected to the host via a PCIe                             |    |

|     | bus. Typically, accelerators do not share the same memory as CPU                                  |    |

|     | cores, hence they have their own privates memories                                                | 12 |

| 2.3 | Overview of the internal architecture of FPGAs. Configurable logic                                |    |

|     | blocks (CLB) are connected with embedded memory (BRAM) and                                        |    |

|     | dedicated processing elements (DSPs and FPUs), in an array-like ar-                               |    |

|     | rangement.                                                                                        | 18 |

| 2.4 | Overview of the internal structure of a CLB for the ZYNQ 7000 family $% \mathcal{T}_{\mathrm{T}}$ |    |

|     | of FPGAs by Xilinx [7]. Every block is assembled by two slices, that                              |    |

|     | can put through either purely logic operations, or logic operations along $% \mathcal{L}^{(n)}$   |    |

|     | with storage. The logic operations are provided via logical function                              |    |

|     | generators implemented by LUT and can simulate the behavior of any                                |    |

|     | Boolean function.                                                                                 | 19 |

| 2.5 | Block design of our experiment board - VC709, a member of the $Z_{YNQ}$                           |    |

|     | 7000 family from Xilinx [6]. The design is used to present the envi-                              |    |

|     | ronment of the chip on the board. Among with the DDR3 blocks, the                                 |    |

|     | Differential Clock, the DIP Switches the UART and the JTAG inter-                                 |    |

|     | faces, we highlight the 8-lane PCIe Edge Connector that allows the                                |    |

|     | communication of the chip with the host node. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$        | 22 |

27

30

53

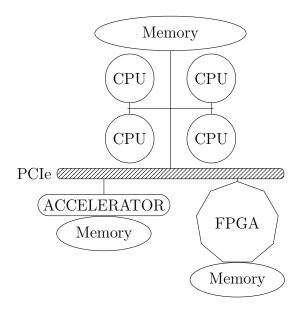

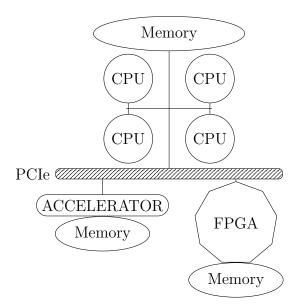

- 2.6 Paradigm of our reference heterogeneous platform. A typical node of our focus is assembled by a series of CPU cores accessing the same physical memory (host), coupled with an accelerator (typically a GPU) and an FPGA. The devices assembling the node are connected over PCIe with the host. They have their own physical address space, hence they are represented with their own private memories in the design.

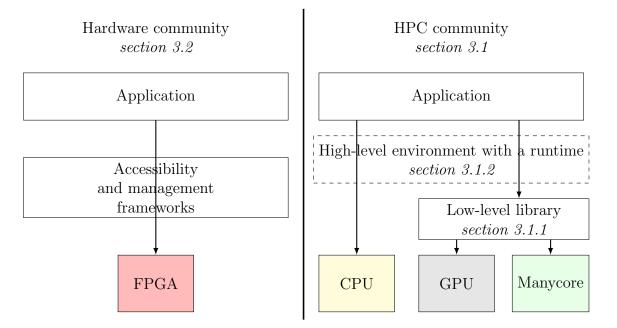

- 3.1 An overview of the related work on programming environments for heterogeneous platforms. On the high performance computing community side (section: 3.1), we first introduce low-level libraries that allow the execution of code on accelerators (section 3.1.1) and then higher-level runtime environments (section 3.1.2). On the hardware community side, we introduce frameworks that ease the accessibility and management of FPGAs (section 3.2). Our taxonomy distinguishes three classes of works: the thread based ones (section 3.2.1), the task based approaches (section 3.2.2) and the process based ones (section 3.2.3).

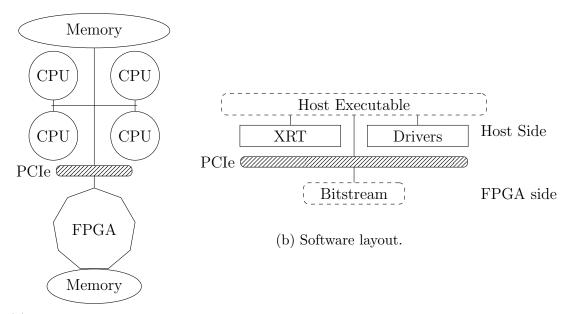

- 3.2 SDACCEL reference architecture and software layout. The reference architecture is similar to our heterogeneous reference architecture. A series of CPU cores connected with a FPGA over a PCIe bus. The FPGA is configured using a bitstream. The host executable is linked with the Linux drivers and the runtime system of Xilinx (XRT). . . .

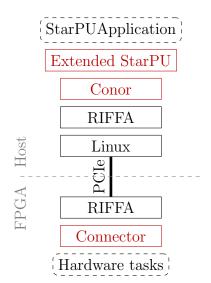

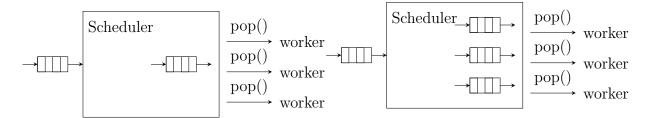

# 4.1 Figures 4.1a and 4.1b present the software stack and the reference architecture of our approach. 4.2 Reference architectures of a StarPU scheduler. A scheduling policy is responsible to determine the mapping between ready tasks and the available processing units. The source of the scheduler is a FIFO queue holding the tasks with satisfied dependencies, represented by the left side FIFO on figures 4.2a,4.2b. On the other side there is the amount of the available processing units represented by their workers, performing popping operations on the scheduler so they can proceed to task execution.

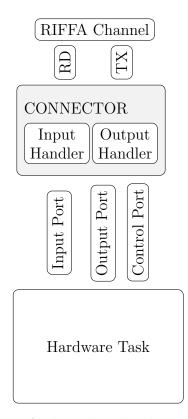

| 4.3 | Connector: a RIFFA channel to hardware task adapter. The connector                                             |    |

|-----|----------------------------------------------------------------------------------------------------------------|----|

|     | is assembled by two individual components the Input and the Output                                             |    |

|     | handler. The input handler is responsible to drive the RD direction of                                         |    |

|     | the RIFFA channel to the input port of the hardware task. The output                                           |    |

|     | handler is responsible to drive the output port of the hardware task to                                        |    |

|     | the TX direction of the RIFFA channel, using information provided by                                           |    |

|     | the control port of the task. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 77 |

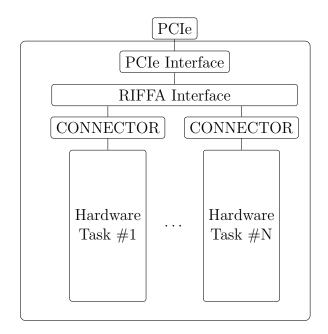

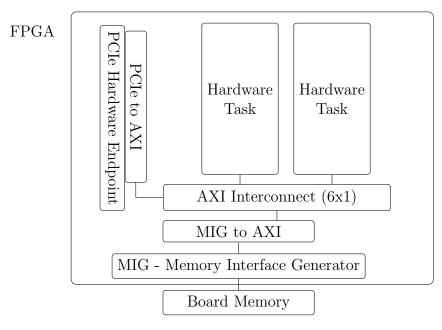

| 4.4 | Hardware Design Overview: This is a complete layout of a FPGA con-                                             |    |

|     | figuration compatible with our framework. The objective is to provide                                          |    |

|     | accessibility to a number of hardware tasks from the software (host)                                           |    |

|     | side. The link between the host and the device is the PCIe bus, on                                             |    |

|     | top of which the hardware interface of RIFFA is synthesized (using the                                         |    |

|     | PCIe interface from the FPGA vendors). Every synthesized hardware                                              |    |

|     | task is coupled with a connector component which is associated to a                                            |    |

|     | RIFFA channel                                                                                                  | 78 |

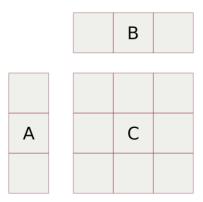

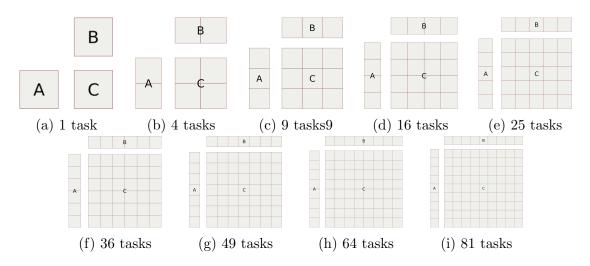

| 4.5 | Overview of our evaluation algorithm: Blocked version of matrix mul-                                           |    |

|     | tiplication. Figure 4.5a shows the partitioning of the input and output                                        |    |

|     | matrices while figure 4.5b shows the data blocks associated to a single                                        |    |

|     | task                                                                                                           | 80 |

| 4.6 | We conducted a series of experiments with a varying matrix size. We                                            |    |

|     | kept the task granularity constant across the experiments, modifying                                           |    |

|     | the number of tasks launched on every execution by adjusting the size                                          |    |

|     | of a matrix dimension and the number of partitions per dimension. For                                          |    |

|     | every set-up (configuration displayed in figures 4.6a through 4.6i) we                                         |    |

|     | run a case for the heavy weight task and another for the light weight                                          |    |

|     | one                                                                                                            | 87 |

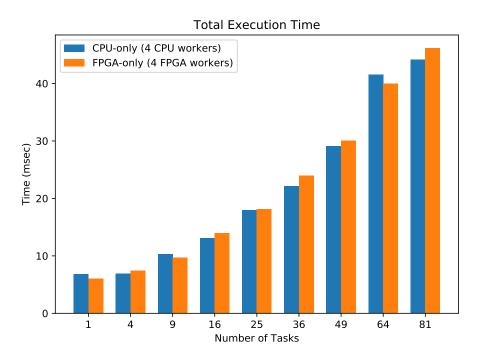

| 4.7 | Performance results on homogeneous execution scenarios of blocked                                              |    |

|     | matrix multiplication for block sizes of $64x64$ (figure 4.7a) and $256x256$                                   |    |

|     | (figure 4.7b). An execution can happen completely on the CPU cores                                             |    |

|     | (CPU-only bars) or the FPGA (FPGA-only bars). In the case of small                                             |    |

|     | granularity, the execution time for both architectures is similar while                                        |    |

|     | in the heavy-weight tasks, the FPGA impelmentation outperforms the                                             |    |

|     | CPU one. In both cases, the increase in the number of tasks shows no                                           |    |

|     | performance overhead imposed to the execution time.                                                            | 89 |

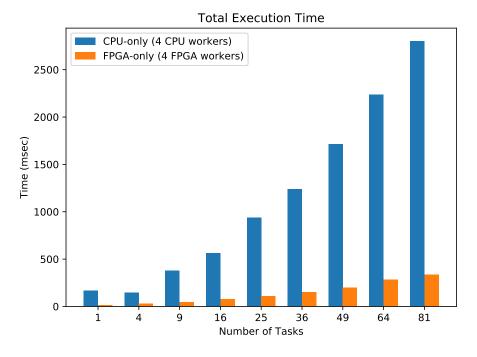

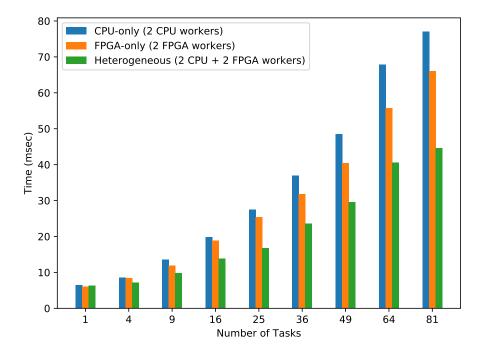

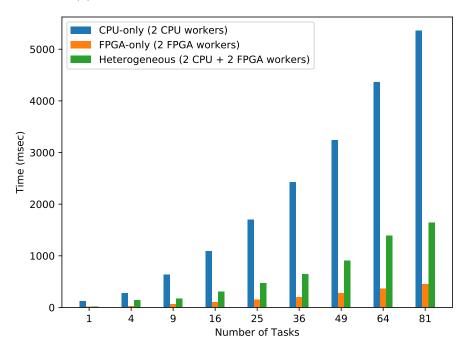

| 5.1 | Performance results on heterogeneous execution scenarios of blocked                                                             |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------|-----|

|     | matrix multiplication for block sizes of $64x64$ (figure 5.1a) and $256x256$                                                    |     |

|     | (figure 5.1b) $\ldots \ldots \ldots$ | 94  |

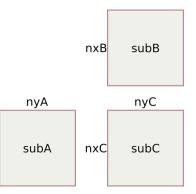

| 5.2 | Demonstration of memory mapping of a 3 by 3 matrix $X$ and its trans-                                                           |     |

|     | pose $X^T$                                                                                                                      | 98  |

| 6.1 | A design of an extended version of the framework able to exploit the                                                            |     |

|     | on-board FPGA memory                                                                                                            | 113 |

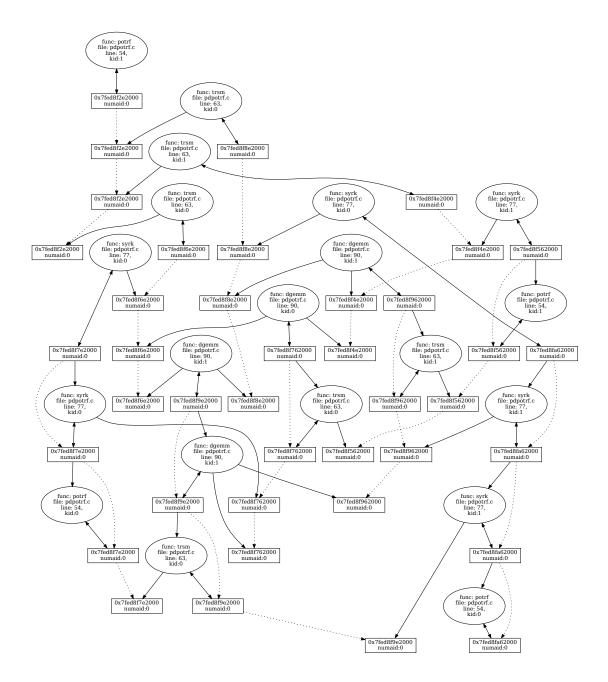

| A.1 | Task Graph of Cholesky decomposition                                                                                            | 120 |

# Chapter 1 Introduction

The evolution of technology has lead to computing systems of tremendous performance capabilities coupled with a fair amount of complexity. As an example, the IBM Summit super-computer reaches a theoretical peak performance of  $200 \,\mathrm{Pflop \, s^{-1}}$ , at the expense of a great increase in both architectural complexity and energy consumption. In order to overcome the complexity associated with such machines, researchers have developed models and tools that provide clean interfaces to developers bridging the gap between a common modern computer and such a system.

To overcome the energy demands required for this amount of computations, the community has oriented itself towards heterogeneous processing resources. The first example of truly high performing heterogeneous computations was the one of the GPU, that showed orders of magnitude of performance increase in certain kinds of computation compared to the traditional CPU. The idea behind heterogeneity is to identify and decompose an application into different parts with similar demands and bottlenecks and assign them to the type of processing unit that corresponds best to their characteristics. FPGA are re-configurable pieces of fabric, that lately gained the interest of the high performance computing community for their low energy consumption and potential for augmented performance. From a high level point of view, those properties derive by the fact that in an FPGA, the description of the application and its actual hardware implementation are closer (reduced amount of abstraction layers) than a traditional architecture like the CPU.

The trade-off of utilizing FPGA for general purpose processing is the complexity of hardware design. Despite the fact that hardware vendors have invested a lot of effort to enable the configuration of those devices using a higher-level language, there are still plenty of challenges to overcome in order to obtain efficient implementations. Those challenges are mainly due to the massively parallel nature of the hardware, as well as the fact that development happens in the inverse way compared to a traditional CPU. The fundamental processing units of an FPGA are very primitive, yet in the order of thousands and hundreds of thousands, so the level of parallelism exceeds by far the one that software developers are used to. On top of that, in the process of hardware design, it is the processing unit that is being adapted to the algorithm, and not the other way around.

All things considered, only a fraction of the high performance computing community considers programming FPGA for now. Besides the requirements for fine lowlevel control of hardware design, programmers need to handle mechanisms associated to the management of the device. The main objective of this thesis is to improve the accessibility of heterogeneous architectures containing FPGA accelerators to parallel application programmers. To do so, we propose a framework which enables developers to use FPGA as another accelerator within a traditionally heterogeneous high performance computing platform. We focused on ease of development and portability without sacrificing performance, to position this work as a first step towards bridging the gap between the hardware and high performance computing communities. Our solution relies on an extension of the StarPU heterogeneous runtime system and a new communication library called Conor that facilitates the communication between the software side and the device through PCIe. On the hardware side, we provided the control units responsible for the integration of the hardware tasks that will be provided by the developer This complexity has been the challenging, motivating and rewarding part of this thesis along with the fact that the product of this work is directly applicable to real large scale systems.

This manuscript is organized as follows:

- Chapter 2 provides the essential information about the background required for the understanding of this work. Section 2.1 introduces the concept of parallelism and its twofold nature, the spatial and the temporal one. Section 2.2 explains the different levels of complexity of a modern high performance computing system, and how parallelism is exploited in every one of them, while section 2.3 introduces FPGA as an accelerator to such system.

- Chapter 3 provides the different approaches associated to this work by the software (3.1) and hardware (3.2) community respectively.

- Chapter 4 introduces our framework as well as the first series of its evaluation. More precisely, section 4.1 focuses on both the software and hardware level

integration we went through during this thesis. In this chapter, we also evaluate the behavior of our framework on homogeneous execution scenarios, using a blocked version of matrix multiplication (4.2). The evaluation is across two dimensions, one being the programming effort that our framework requires for the support of FPGA (section 4.2.2), as well as the performance overhead of our integration (section 4.2.3).

- Chapter 5 presents our work towards truly heterogeneous experiments. On the first part of the chapter (in section 5.1) we present a series of experiments, where we used the same blocked version of matrix multiplication used in chapter 4, that multiplication tasks are executed simultaneously on the CPU and the FPGA. For a more complete example of heterogeneous execution, we introduce Cholesky decomposition, an application that is assembled by four different kernels, one of which (*GEMM*), we have chosen to optimize and synthesize in hardware (section 5.4).

- Lastly, chapter 6 presents a summary of this study as well as its possible perspectives.

# Chapter 2

# Background And Problem Statement

#### Contents

| 2.1 Par | allelism Is Everywhere                                          | <b>5</b>  |

|---------|-----------------------------------------------------------------|-----------|

| 2.2 HP  | C Systems                                                       | 7         |

| 2.2.1   | Hardware Organization                                           | 8         |

| 2.2.2   | How To Program An HPC System?                                   | 13        |

| 2.3 FP  | GA                                                              | 16        |

| 2.3.1   | FPGA: Architecture                                              | 17        |

| 2.3.2   | How To Program An FPGA Chip?                                    | 20        |

| 2.3.3   | FPGA: Memory                                                    | 21        |

| 2.3.4   | FPGA: Communication With Its Environment $\ldots \ldots \ldots$ | 22        |

| 2.4 Per | formance Results Of FPGAs On HPC Applications                   | <b>23</b> |

| 2.5 Pro | blem Statement                                                  | <b>26</b> |

The core of this PhD stands across two well-established research areas: high performance computing and hardware design using FPGAs. This chapter introduces the reader to the notions and concepts of both, that are necessary for the further comprehension of the contribution and the results of the work. Section 2.1 is an introduction to the concept of parallelism highlighting both its spatial and temporal nature. Section 2.2 introduces high performance computing systems presenting their hardware organization and the way they are programmed today. Section 2.3 is dedicated to FPGAs and provides details on both their architecture and how to exploit them from the programmers' point of view. Section 2.4 then presents a taxonomy of high performance computing applications and a suitability analysis of FPGAs to each class, based on the literature. The chapter ends with section 2.5 that provides an analysis of the challenges and our positioning regarding the integration of FPGAs in HPC.

# 2.1 Parallelism Is Everywhere

Once the capabilities of a single core reached a ceiling because of physical limits of the matter, mainly its ability to drain off heat, parallelism was employed in order to further augment the performance of computing platforms. The purpose of high performance computing is to deliver fast computational solutions to problems and algorithms of multiple fields. Often, those problems are by nature parallel, meaning there are parts of the computational load that can be executed independently and hence simultaneously with others. It is of vital importance to identify these parts in order to exploit the underlying processing resources to reach the best possible performance. Fundamentally parallelism has a twofold nature, the temporal and the spatial one. In the following analysis, we present two generic techniques to capitalize on its both aspects: pipelining for the temporal parallelism and resource duplication for spatial parallelism. Those two universal concepts can be applied to almost every problem. To demonstrate them we use the example of clothes-washing. Along with the concepts of pipelining and resource duplication, we introduce fundamental performance evaluation metrics like the throughput and the latency.

**Problem description: the laundry** Assume a given set of dirty t-shirts that needs to be delivered clean and well folded. The standard procedure involves:

- Step a: doing the actual washing (processing unit: washing machine)

- Step b: drying the clothing (processing unit: drier)

- Step c: ironing and folding (processing unit: ironing table)

The latency metric corresponds here to how much time it is required in order to get one t-shirt clean. Throughput refers to how many t-shirts per time unit we can deliver (assuming we have more than one t-shirt to process). In a completely sequential paradigm, we would wait for a t-shirt to pass from all the three stages (washing, drying, ironing and folding) before getting the next one into the procedure. **Pipelining** The first optimization technique that comes immediately in mind is that we can overlap washing with drying and ironing among different t-shirts. This is the idea of pipelining that exploits temporal parallelism. The concurrent utilization of the three different processing units on different t-shirts is possible because the three procedures are independent and can operate individually. In other words, the effort that is needed in order to perform the entire execution can be split into a set of individual and well defined steps.

We can at this point evaluate the impact of pipelining using the latency and throughput metrics introduced above. This will lead to a series of observations and remarks regarding the parameters that effect the behavior and the effectiveness of the method. Let step k requires  $t_k$  units of time for its completion. First by evaluating the sequential version of the laundry we obtain a latency and a throughput of:

Sequential latency =

$$t_a + t_b + t_c$$

Sequential throughput =  $\frac{1}{t_a + t_b + t_c}$

By evaluating the pipelined version we obtain:

Pipelined latency =

$$t_a + t_b + t_c$$

Pipelined throughput =  $\frac{1}{max(t_a, t_b, t_c)}$

The first observation here is that pipelining does not effect the latency. In other words pipelining is a technique that aims to increase the throughput. The second observation is that the effect on the throughput is correlated with the balance among the time spent on each one of the steps. On the one hand, if the steps are well balanced in terms of time demands, the gain in throughput is proportional to the number of steps. On the other hand, if the majority of the processing is spent during one of the steps, then the throughput of the pipelined version converges to the throughput of the sequential one. Said differently, the effectiveness of pipelining is determined by the delay of the slowest step compared to the average step delay.

**Resource duplication** The second intuitive optimization technique is to get equipped with multiple units of each stage (laundry machines, driers and ironing tables) so that we can perform the same step multiple times concurrently, exploiting the spatial nature of parallelism. This optimization technique is called resource duplication and by default is also a throughput optimization strategy. For our laundry problem, as well as for any problem where every workload will be processed by every step, resource

duplication can increase the throughput proportionally to the number of duplicates if we have an equal amount of duplicates for every stage. In a laundry with three washing machines, three dryers and one iron table, the throughput is the same than the one of a laundry with one single processing unit per stage. This is because all the t-shirts will have to serialize on the ironing step.

Assuming a facility with x processing units per step, the latency and the throughput are the following ones:

Duplicates

$$latency(x) = t_a + t_b + t_c$$

Duplicates  $throughput(x) = \frac{x}{t_a + t_b + t_c}$

Resource duplication is also technique to increase the throughput, by adding supplementary processing units. The bottleneck of the throughput increase lies at the step of the procedure with the least amount of resources.

**Combining the two techniques** As one could expect, the above two techniques can be combined together in order to exploit both temporal spatial parallelism. In our laundry problem, the facility can be equipped with a series of machines for every stage, and the operation on the machinery can occur in a pipelined fashion. This would increase the overall throughput in two ways, the amount of t-shirts processed per time unit will be proportional to the number of available resources per unit, and the time per new t-shirt will be decreased to the maximum delay per processing step. The final throughput for this combined approach where pipelining is combined with x duplicates is the following one:

$$Throughput(x) = \frac{x}{max(t_a, t_b, t_c)}$$

## 2.2 HPC Systems

The size and the computational power delivered by modern supercomputers are now tremendous. The highest ranked computer system of today, in the TOP500 list called *Summit*, according to the last published data of November 2018, holds 2,397,284 IBM POWER9 22C cores at 3.07 GHz and 2.8 PB of main memory [119]. The system is also equipped with NVIDIA Volta GV100 GPUs and connected with Dual-rail Mellanox EDR Infiniband. Its theoretical peak performance is  $200 \text{ Pflop s}^{-1}$ , and its submitted power consumption is 9,8 MW. This tremendous power of computation comes with very complex hardware and memory layouts that HPC application developers need to

fully comprehend in order to exploit such platforms at their full potential. This section first presents the hardware architecture of HPC systems. Moreover, it demonstrates how an algorithm can be decomposed and transformed in order to adapt to the underlying parallel infrastructure, from the point of view of the HPC programmer. Finally, this section classifies from a very high level, existing programming models currently used in order to implement a parallel algorithm.

#### 2.2.1 Hardware Organization

This section presents the typical hardware organization of an HPC system such as the *Summit* one mentioned above. It decomposes the system to different levels, and highlights the hardware parallelism on every one of them. Our analysis will start at the CPU level in section 2.2.1.1. In section 2.2.1.2 we present how several CPUs are combined together assembling a node, while in section 2.2.1.3 we present how a several nodes are combined together to form a cluster.

#### 2.2.1.1 Parallelism Inside A CPU

A CPU is a processing unit responsible for the execution of streams of instructions of a fixed architecture that are called programs. An instruction is a set of bits, that combined with an architecture called the Instruction Set Architecture (ISA), performs a specific operation that can be of various types such as integer or floating point arithmetic operation, branching or memory access. In most of the cases, this set of bits can be decomposed in two fields, the operation code (opcode) and the operands. From the programmers point of view, a stream of instructions is executed sequentially. That is, instructions are executed one after the other.

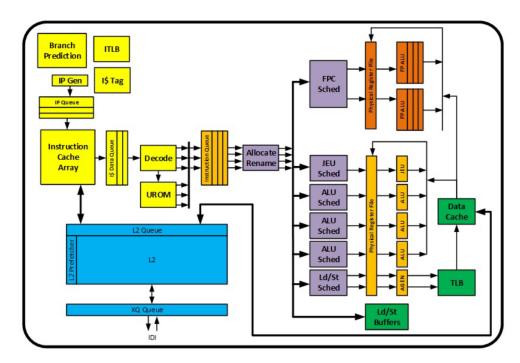

In practice, a CPU employs both pipelining and resource duplication to increase throughput when executing a stream of instructions. For the better understanding of how these two techniques are employed in a modern CPU, we will use the architecture of figure 2.1 as a reference. The architecture is called GoldmontPlus and is used in modern low-power x86-64 CPUs by Intel.

Figure 2.1: Overview of the GoldmontPlus CPU architecture by Intel [2]. The architecture is used as a reference to demonstrate how parallelism is employed in the design of a modern CPU.

Program's instructions live in memory, and are fetched as the execution progresses according to a program counter, a CPU register pointing to the next instruction to execute. Between memory and the processor there are several layers of caches.What we see in figure 2.1 (yellow part) though is that an instruction is fetched from a dedicated cache (Instruction Cache Array) and then passed to a queue in order to be further executed.

The next step is the decoding of the instruction. It corresponds to the procedure of the instruction's identification by its opcode and fetching of its operands. In the GoldmontPlus architecture, the decoding phase corresponds to a control operation, during which the instruction passes from the Instruction Cache Array to the Instruction Queue (orange part). At that time, the control unit also specifies which execution path will later be followed during the execution phase.

The next step that we see in figure 2.1 is related to the register renaming (purple part), which is a technique related to the out-of-order execution of instructions, and goes beyond the scope of this analysis. Nevertheless,[110] provides a complete presentation of register renaming techniques.

The next phase in the lifetime of an instruction is the execution. According to its type, an instruction associated to an arithmetic operation will be forwarded to the appropriate processing unit that can be either a floating point unit (FP ALU) or an integer arithmetic and logic unit (ALU).

Once the result of the corresponding operation is available, it will be written in the physical register file (the same series of registers that hold the input of the instruction).

The paths exploited so far correspond mainly to instructions with computational nature. There other types of instructions, like those responsible for the interaction with memory (loading and storing) or control oriented ones (branches). Although, what is important to keep for the rest of the analysis is the fact that the life of an instruction can be decomposed to the phases of fetching, decoding, execution, interaction with memory and write back.

**Instruction Pipelining** In our laundry example of section 2.1 we saw that pipelining is a technique that allows to exploit temporal parallelism and obtain increased throughput. It is the same very same basic idea, that has been employed by CPU designers, in order to deliver better performance, and in that scope is called *instruction pipelining*. In the presentation of the GoldmontPlus architecture, we observed that simply put, the lifetime of an instruction can be decomposed in five phases: fetching, decoding, execution, memory accessing and writing back. Instruction parallelism allows the overlapping of execution of different stages of different instructions at a given time. This can happen since every stage is independent, and there are different units responsible for its execution.

Overlapping the execution of instructions have some side effects that require some additional control to ensure the correctness of the computations. Consider a scenario according to which two consecutive instructions are pipelined, where the output of the first is used as an input on the second one. Such phenomenon if often referred to as *data dependency conflict*, and is usually handled by stalling a part of the pipeline so that by the input reading phase of the second instruction the output of the first one is the valid one. In such cases, the performance of the processor can converge down to the performance of a non-pipelined one, but this only depends on the dependencies of the instructions' stream.

**Super-Scalar Pipelines** The second technique of our laundry example of section 2.1 was resource duplication, that gives the ability of simultaneous execution of multiple workloads of the same kind. In the example architecture of figure 2.1 we see multiple execution units for basic arithmetic (ALUs) operations. A pipeline including such duplicates is called *superscalar*, since multiple instructions can be in the same pipeline stage concurrently, the same way multiple t-shirts can be washed at the same time in a laundry with several washing machines.

Exploiting parallelism in the processor with the aforementioned techniques allows an execution throughput greater that one instruction per cycle, which is the case for nearly every modern CPU. Because of the level that this parallelism is exploited, it is often referred to as *Instruction Level Parallelism* (ILP).

In processor with super-scalar pipelines, specific attention should be paid to minimize the amount of time that processing units remain idle. Techniques like outof-order issue, branch prediction, speculative execution, register renaming and out of order execution have been developed, but exceed the scope of this study, whose main purpose is to highlight the role of parallelism in a modern high performance computing system at every level.

**Multi-core CPU** The previous paragraphs presented how parallelism is expressed inside a CPU made of single processing unit, referred to as a *core*. To further exploit spatial parallelism, several cores are combined together in modern CPU. The CPU cores have access to the same shared main memory. In such a multi-core CPU, several instruction streams can be executed concurrently, and they can communicate through the shared memory.

#### 2.2.1.2 From Processors To Nodes

The previous section linked the fundamental concepts of parallelism introduced in section 2.1 to a typical modern CPU architecture. This section focuses on the introduction of the next level of complexity of modern parallel computers, which is the node level.

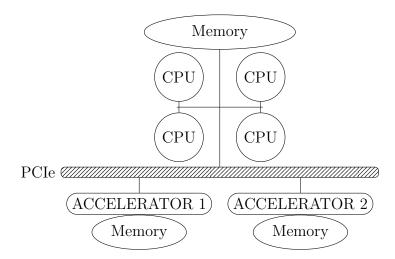

To further exploit spatial parallelism, several processing units are combined together to make a *node*. Along with the CPUs, other kind of processing units have been employed in order to enhance the processing capabilities of the node. Figure 2.2 shows a typical node design. The so called *host* part of the node is made of one or more multi-core CPU (4 in the example) accessing the same main memory. The other part of the node contains a series of accelerators often connected to the host via a PCIe bus. In this design, accelerators do not share the same memory as CPU cores, hence they have their own privates memories.

The number of CPU cores can greatly vary in modern processing nodes, depending on computing needs. Typical sizes are four (e.g. a single 4-core CPU) to thirty-two

Figure 2.2: Reference structure of a typical heterogeneous processing node. The node is constructed by a set of CPU accessing the same main memory (host), and a series of accelerators connected to the host via a PCIe bus. Typically, accelerators do not share the same memory as CPU cores, hence they have their own privates memories.

cores (e.g. four 8-core CPU). In a node with a single CPU all the cores access the same single shared memory as already stated. In other words they have uniform memory access at the same memory banks.

The increasing amount of CPU cores, is shown to throttle the performance of memory operations for the uniform memory accessing scenarios. To solve this issue hardware designers introduced architectures where all the CPU cores share a physically distributed memory. In this case the access to memory is no more uniform. Such architectures are called Non Uniform Memory Access (NUMA) architectures. There is a dedicated circuitry responsible for the exchange of data between the CPU cores and the different parts of the memory. The size of such architectures can increase significantly, with usual cases of nodes having a total of 256 cores (e.g. sixteen 16core CPU) or more. Fine control over the location of data when performing memory accesses is then crucial to obtain the best performance that can be delivered by such architecture. The deeper understanding of their structure and behavior though, lies beyond the focus of this work.

On the accelerators side, a typical node is coupled with one or two GPUs. Manycore processors, such as the Intel Xeon Phi, are also nowadays used as accelerator. The parts of the computation that are more efficiently executed on an accelerator than on a CPU are offloaded from the host side to the accelerator one. These accelerators come with there own private memories as already stated. The consistency between the host memory and the private memories of the accelerators is not handled by the hardware. Considering as an example the architecture presented in figure 2.2, and assuming that initially data lie in main memory, we can study the hypothetical scenario according to which a part of the execution will occur in one of the GPUs. The corresponding data need to be transferred from the main memory to the private memory of the accelerator. Meanwhile, an authority needs to ensure which of the two copies is valid at a given moment of the execution, as well as to synchronize the non-valid copies when needed.

#### 2.2.1.3 From Nodes To Clusters

Like multiple processing units can be put together to form a parallel, possibly heterogeneous compute node, the same approach can be followed to design large-scale clusters of nodes, an extreme -in terms of capabilities- instance of which is Summit introduced in section 2.2. The building block of a cluster is the node and nodes are connected using a network, like ETHERNET or INFINIBAND.

The interconnection of multiple nodes brings enormous processing power that comes to the theoretically unlimited scalability of such a system, although there are challenges to overcome deriving from the interconnection itself, along with the management of the underlying resources.

From the software point of view, there was a need to establish a protocol for the communication of execution units that are being processed on different nodes. This communication's overhead usually varies according to the distance of the processing units in the cluster. Another major concern in order to obtain the desired performance is the load balancing between the different nodes; in other words, we need to ensure that the workload will be distributed to the available processing nodes in a way that the variance of the completion time for every node is minimal as well as the communication overhead required for the exchange of data between nodes. Along with load balancing, another development concern is to set the proper affinity of execution units to nodes or cores (usually ensuring that an execution unit will remain close to the data that is associated with, making a better use of data locality). In other words, the developer needs to create and maintain a mapping between the processing load to a node, or more even more specifically to a core, in order to obtain a minimal overhead deriving from data movement.

#### 2.2.2 How To Program An HPC System?

In the preceding part of the chapter, one could obtain a global view of the hardware architecture of a modern high performance computing platform. It is of vital importance for the programmer to capitalize on the amount of computational power provided by such systems, that mainly derives from the underlying parallelism. To do so, one needs to adopt strategies, concepts and methodologies that would allow the concurrent execution of a formerly sequential algorithm or of a new one. Programming models and associated infrastructures are then needed for this parallel algorithm to be expressed and executed.

#### 2.2.2.1 Extracting Parallelism In An Application

Given a reference architecture, the entry point for the development of high performing application is the analysis and understanding of the algorithm that will later be expressed in the form of a program. In order to take advantage of a massively parallel platform like the ones described in section 2.2.1, it is essential that the nature of the computations is also heavily parallel. If not, the entire workload will be processed by a single processing unit while the rest of the resources will remain idle.

**Finding Concurrency** In the case the application contains parallelism, it is not always trivial to identify it in order to design a parallel version of the algorithm. Task and data decomposition, defined as follows, can be used to decompose the problem into pieces that can execute concurrently:

- The task decomposition dimension views the problem as a stream of instructions that can be broken down into sequences called *tasks* that execute simultaneously. For the computation to be efficient, the operations that make up the task should be largely independent of the operations taking place inside other tasks.

- The data decomposition dimension focuses on the data required by the tasks and how they can be decomposed into distinct chunks. Strong computational dependencies among the different chunks make the overall computation inefficient.

Task and data decomposition are tightly coupled, since one implies the other, although by making them distinct, we make the design emphasis explicit. In some cases the problem will naturally break down into a collection of tasks, hence the task-based approach is easier. In most cases though, the tasks are difficult to isolate and the decomposition of the data is a better starting point. Regardless of whether the starting point is a task or a data-based approach, a parallel algorithm ultimately needs individual work loads that will execute concurrently, so the tasks must be identified. In the case only data-parallelism is used, the tasks will all perform the same computation, but on different chunks of data.

#### 2.2.2.2 Parallel Programming Models

Many parallel programming models have been proposed and are in used to implement a parallel algorithm on an High Performance Computinghardware architecture. The evolution and proposal of these models have been following the evolution of hardware architectures. Combinations of these models are often used in order to exploit the hardware parallelism at all the levels.

**Shared memory programming models** In a shared memory programming model, the programmer specifies parallel activities communicating through writes and reads in a shared memory. Depending on the particular programming model, the proper synchronization between the activities is handle by the programmer or automatically. Among many others, POSIX threads and OpenMP are two widely used shared memory programming models. They are described in the next two paragraphs.

**POSIX threads** In the POSIX threads programming model, several independently controlled execution paths, called threads are created by the programmer. POSIX threads are implemented as a library with functions for creating, destroying and coordinating thread activities. This model is especially appropriate for the fork/join parallel programming pattern, according to which several execution flows are instantiated and then merged when everyone is completed. Threads are sharing the dynamically allocated heap memory causing programming difficulties regarding synchronization. When multiple threads access shared data, they must be properly synchronized by the programmer to avoid race conditions and deadlocks. That corresponds to a task oriented parallel programming model for shared memory architectures. The number of threads is not necessarily related to the number of processors.

**OpenMP** OpenMP is a shared memory programming model providing a higher level abstraction than Posix threads. Said differently, it eases the creation and management of threads from the programmers point of view. It is a portable application programming interface (API) implemented as a combination of a set of compiler directives (thread creation, synchronization, memory management), pragmas, and runtime providing both management of the thread pool and a set of library routines. Parallel regions enables a set of instructions to be replicated across a set of threads. OpenMP is specially suited for the loop parallel program structure pattern, although the Single Program Multiple Data (SPMD) and fork/join patterns also benefit from this programming environment.

Message passing programming models In message passing programming models, several entities are evolving in separate memory address spaces and communicate via explicit message exchanges. This is a natural model for a distributed memory system, where communication cannot be achieved directly by sharing variables.

Message Passing Interface (MPI) is the most used standard in this category. It defines a portable message passing interface designed to function on a wide variety of parallel computing architectures. It is a library that specifies the names, calling sequences and results of the subroutines or functions to be called. In MPI, work load partitioning and task mapping are assigned to the developer. In addition to point to point exchanges, MPI supports collective communications.

**Programming models for heterogeneous architectures** The previously described programming models focused on programming homogeneous architectures. The introduction of GPUs by Nvidia and their exploitation to non-graphic uses, that is General Purpose GPU (GPGPU), led to programming models explicitly dedicated to heterogeneous architectures including GPUs. CUDA from Nvidia, and the OpenCL standard are the two most used programming models in this category but many other solutions such as OPENMP target construct [25], OPENACC [76] or HMPP [33] have been proposed to ease the programming of architectures with GPUs.

In contrast with shared-memory, with these programming models, the programmer needs to offload some data to and from accelerators private memories. Also, because parts of the application are offloaded to accelerators, the programmer needs to write the code to be executed there. In CUDA for example, this done by writing C code which is compiled to GPU binary with the Nvcc compiler provided by Nvidia.

Because programming heterogeneous architectures is the main focus of this thesis, we extensively describe programming models for heterogeneous architecture in the related work chapter 3.

## 2.3 FPGA

In the previous section we explained how and why processing elements of different architectures were employed for general purpose computing in order to enhance the performance of high performance computing platforms. Our work has focused on incorporating FPGAs in such platforms. From that point of view, FPGAs can be considered as reprogrammable integrated circuits. In other words, they are hardware fabrics, with interconnected basic elements of logic and memory, whose content can change dynamically according to the configuration.

In order to explore the behavior and characteristics of FPGAs we will go along the natural process one will follow to integrate such an accelerator to a given heterogeneous platform. There is a series of fundamental questions to be answered:

- How to program the device?

- How is memory organized?

- How does the device communicate with the rest of the platform?

In order to understand how an FPGA is programmed, we need to understand its architecture which is presented in section 2.3.1. Then, section 2.3.2 presents the process of low level hardware design, as well as the utility of higher level synthesis tools that can be used in order to program the accelerator. In section 2.3.3 we present the different types of memory a modern FPGA chip and board are equipped with, and how they are used by modern vendor tools. Lastly, section 2.3.4 describes how an FPGA is connected with its environment to assemble an heterogeneous execution platform.

#### 2.3.1 FPGA: Architecture

When asked to integrate an FPGA, understanding its architecture is crucial, since it is not similar to the one of a traditional CPU that can be programmed using an ISA like x86. For the configuration of FPGAs, programming happens at a much lower level, that in practice it is no longer considered software development but hardware design.

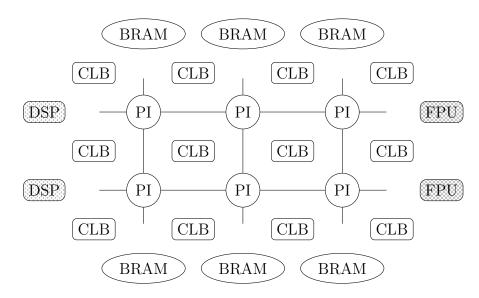

Figure 2.3 shows a high level overview of an FPGA. It is composed by Configurable Logic Blocks (CLB), memory blocks (BRAM) and an interconnection network (PI). In this section we will dive into the CLB components of the chip, while memory will be analyzed in section 2.3.3.

Figure 2.3: Overview of the internal architecture of FPGAs. Configurable logic blocks (CLB) are connected with embedded memory (BRAM) and dedicated processing elements (DSPs and FPUs), in an array-like arrangement.

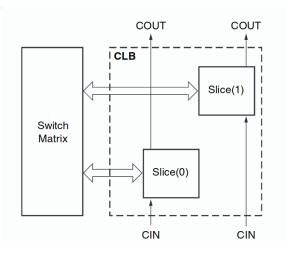

As a reference of a CLB we will use the ZYNQ 7000 FPGA family from Xilinx [1], since this is the FPGA family we conducted our experiments on. Figure 2.4 shows that a CLB is composed out of two disconnected slices. Each slice has an input and an output port (CIN and COUT respectively), and is also connected to the interconnection network (marked as Switch Matrix). A simple slice contains *function generators, storage elements, carry logic* and *multiplexers*, and is called SLICEL. Along with SLICEL slices, there are also SLICEM, that can additionally provide data storing functionalities through distributed RAM elements. A CLB can be either assembled by two SLICEL slices, or by one SLICEL and one SLICEM.

Figure 2.4: Overview of the internal structure of a CLB for the ZYNQ 7000 family of FPGAs by Xilinx [7]. Every block is assembled by two slices, that can put through either purely logic operations, or logic operations along with storage. The logic operations are provided via logical function generators implemented by LUT and can simulate the behavior of any Boolean function.

Function generators are the building blocks of logic, and are implemented using *look-up tables* (LUT). Every slice contains four function generators, every such generator is implemented by a LUT and can behave as an arbitrary Boolean function.

Along with the logic, a CLB is associated with some control signals like set/reset, write-enable, clock and clock-enable. Set/reset initialize the internal state of the LUT, so that we can obtain the output of the Boolean functions given the current inputs. Write enable is used in order to enable writing on the memory elements of the CLB. The clock is a signal that is used to synchronize the lower level hardware components like the flip-flops used to compose the LUT or the memory elements.

Along with the traditional reconfigurable logic, provided by the LUT, FPGA vendors have tried to augment the capabilities of the chips on dedicated computations. In order to deliver high performance on basic arithmetic operations Digital Signal Processors (DSPs) are added, while some modern FPGAs come also with dedicated logic for floating point (FPU) operations.

It is useful at this point to provide an order of magnitude of the amount of logic elements of a chip, and for that we will use our experimentation platform (7VX690T) as a reference. There are  $\sim 108$  k CLB slices out of which  $\sim 65$  k slices are of type SLICEL and the rest ( $\sim 43$  k) are of type SLICEM. To implement those slices  $\sim 400$  k LUT have been utilized. This particular chip is not equipped with a dedicated unit for floating point operations, although it holds 3.6 k DSP slices organized in 18 columns of 200 slices per column.

### 2.3.2 How To Program An FPGA Chip?

In section 2.3.1 we introduced a reference architecture of an FPGA, that we described as an integrated circuit that can be reconfigured. A configuration of the chip, is a hardware design that determines the contents of the CLB, the memory as well as the way that those components are connected via the interconnection network. The default languages for hardware design are called hardware description languages, Verilog and VHDL being the two representative examples of the category. Programming in such language is happening in very low level, justifying the existence of two distinctive communities: software developers and hardware designers. In appendix A and listing 20 one can see a template code of a single bit-adder module written in Verilog. The purpose of this template code is to demonstrate how low-level hardware design is compared to software development even for a language like C, that is particularly known for the fine control it gives to the programmer.

Given a hardware description of a design, there is a series of steps to be followed so that we have an FPGA circuit behaving accordingly. First the hardware design needs to be synthesized, which involves the procedures of syntactic checking and optimizations to the given FPGA chip. Next step is placement and routing, which is the procedure of mapping the synthesized design to the logic blocks and memory elements of the given chip, as well as determining the behavior of the interconnection network. Once placement and routing is finished, we can obtain the hardware design in a bitstream file, that will be flashed in the device and will give the requested behavior. All those functionalities, are provided by vendor tools that are proprietary, allowing very limited flexibility to the designers. This flexibility mainly relies on the ability of the designer to determine the exhaustiveness of the heuristics used by the algorithms (that by default are NP-complete).

In order to ease the accessibility of FPGA, so that they become usable for general purpose computing, researchers from both communities have created synthesis tools that bridge the gap between higher level languages (C, C++, python) and the hard-ware description level. Such tools are called High Level Synthesis (HLS) tools, and have become a matter of study for many years in an academic and industrial level. Nowadays, HLS tools can deliver augmented performance, providing fine control of the design in the form of compiler directives, that allow the programmer to exploit the massive parallelism of the FPGA, increasing their popularity and usability.

#### 2.3.3 FPGA: Memory

Memory is a fundamental component of every processing unit, including FPGAs. From a high level view there are three types of storage associated to an FPGA chip, the memory units inside a CLB, the block memory (BRAM) and the on board memory (external to the chip). Every type of the above comes at a different level of integration, and has different capacity and accessibility overhead.

Block level memory, has already been introduced in the presentation of the CLB in section 2.3.1. Data here are mainly stored in the LUT and in one bit registers. LUT memory is a versatile kind of storage, although when selected to store big memory structures the final design will be huge (in spatial terms). This will make the rest of the synthesis process (place and design and routing) very hard in terms of complexity and hence time consuming. Nevertheless, it is the selected memory type to store simple variables by most of the synthesis tools.

The block memory (BRAM) is a series of blocks of RAM, coupled with CLB, in most FPGAs in order to host large data structures. This is the type of memory that will concern developers the most, because most of the currently used High Level Synthesis tools map by default complex structures like arrays to this type of storage. BRAM memory is organized into single or dual port blocks, resulting in a reading throughput of one or two words per cycle respectively. Developers using HLS tools are equipped with a series of optimization directives that allow the fine control of how data are mapped to BRAM. Efficient block memory control combined with the massive amount of parallel resources available can deliver impressive performance increase. The capacity of the available BRAM memory will be a factor that indicates the granularity of the kernels, and should be taken into account from the beginning of the design process.

On top of the memory structures mentioned above, most of the modern FPGA boards, allow a memory extension with a DDR3 or DDR4 RAM sets. The characteristics of those memory blocks are similar to those used for conventional systems like laptops and barebones. In order to communicate with this external board memory, vendors provide a series of control designs, that should be manually tuned and incorporated to the rest of the design. This task used to be complicated for people without a certain amount of expertise on hardware design. Nowadays vendors have worked a lot to make the design process much simpler on more recent versions of the synthesis tools.

To provide an insight on the difference in capacity between the different storage elements of an FPGA we will use again as a reference the chip we conducted our experiments on (7VX690T). Inside the CLBs there are  $\sim 10$  Mb of distributed memory and  $\sim 5$  Mb of shift registers. With the BRAM blocks, the chip reaches a storage capacity of  $\sim 53$  Mb. Regarding the on board memory, we can slot two blocks of 4 GB external DDR3 memory, enabling the hosting of much bigger structures.

#### 2.3.4 FPGA: Communication With Its Environment

In order to use FPGAs in the context of general purpose processing, they need to be connected with their environment, so that they can receive computations' input and propagate their output. Modern FPGAs are usually delivered into boards with a rich amount of IO ports. The fabric itself can be directly coupled with a processor (most of the times a single or dual core ARM processor) via an AXI bus, where the FPGA chip and the CPU cores co-exist on the same chip, that is they make up a System on Chip (SoC). As an alternative to that, the FPGA chip can be connected to a host machine via one of the available buses, typically the PCIe bus.

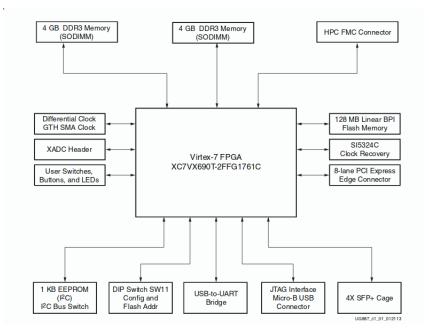

The block diagram of figure 2.5 shows the peripherals accompanying the FPGA chip, which the board we conducted our experiments on (VC709-7VX690T) is equipped with.

Figure 2.5: Block design of our experiment board - VC709, a member of the ZYNQ 7000 family from Xilinx [6]. The design is used to present the environment of the chip on the board. Among with the DDR3 blocks, the Differential Clock, the DIP Switches the UART and the JTAG interfaces, we highlight the 8-lane PCIe Edge Connector that allows the communication of the chip with the host node.

A PCIe based communication facilitates fundamental principles of high performance computing like the scalability and modularity. Building a system based on the SoC approach mentioned earlier, restricts the developers to a small amount of CPU cores and a single FPGA chip. On the other hand, utilizing the PCIe as the connection mean, allows a greater level of complexity on the node level. A node is not limited to a single FPGA device.

# 2.4 Performance Results Of FPGAs On HPC Applications

Despite the effort from the hardware community to bridge the gap between software development in HPC and hardware design required in order to exploit reprogrammable hardware, one could infer from the previous sections that there is still a fair amount of complexity associated to the usage of FPGAs in that context. The motivation to overcome this complexity barrier is associated to the ability of FPGAs to deliver noticeable performance with very low energy requirements. The energy consumption of an FPGA is significantly lower than the one of a typical CPU a fact that derives from the overhead imposed by the levels of abstraction between the CPU and the software languages utilized. Performance wise, according to the literature FPGAs can deliver comparable if not greater performance compared to a typical CPU, for certain applications.

HPC applications are scattered among a wide spectrum of application domains from commercial to financial, medical or scientific fields. Nevertheless, Asanovic et al. [16] has sorted them in different classes, putting together applications with similar behavior and bottlenecks, in a taxonomy called Berkeley categorization. The initiative of the following analysis is to present reported artifacts of the behavior of FPGA in every such category, following the analysis of Escobar et al. [38]. Roughly, in the aforementioned study, HPC applications are classified in the following categories:

• Dense Linear Algebra

One of the most popular category, that includes decomposition and factorization methods (Cholesky, LU, QR). BLAS, CUBLAS, LAPACK are libraries widely adopted by developers, offering outstanding performance using block and tile algorithms to perform the aforementioned calculations. State of the art FPGA implementations of applications from this group, have shown impressive performance results, although CPU-GPU combination is still more than an order of a magnitude faster [116, 128, 130]. • Sparse Linear Algebra

In this category we get the same group of applications as before, though in this cases matrices have few non-zero elements. We observe irregular memory accesses, low data reuse and low number of floating operations per access. Efforts to implement Sparse Matrix Vector (SpMV) multiplication in FPGAs have shown promising results, comparable with the performance of CPU-GPU platforms [34, 81, 88, 101].

• Spectrum Methods

This class of applications contains arithmetic computations on the frequency domain, partial or ordinary differential equation solvers being the two most representative candidates. Most of the algorithms employ a Fast Fourier Transform. The most promising results for this class are coming from the 3D-FFT version, where studies show that an FPGA implementation can outrun a GPU-CPU combination [61, 121].

• N-Body Methods

It is the set of algorithms describing the interactions of the particles due to gravitational forces between each other. The CPU profiles appear irregular memory accesses and scalability issues. CPU-GPU solutions increased a lot the performance over CPU only solutions, although they consume up to fifteen times more power per floating operation [58, 70, 109] than FPGA solutions.

• Structured Grids

It is the class of problems where data can be arranged into arrays with interacting neighboring elements. They are characterized by regular memory accesses. Studies have shown acceleration potentials using FPGAs for this class of applications, although most of the times it is a theoretical estimation of the expected performance [72, 107].

• Unstructured Grids

Here applications are characterized by irregular memory accesses due to their natural inability to be formatted in a structured representation. Techniques like data compression and encoding have been used to tolerate the bandwidth bottleneck between the host and the FPGA, but the results are comparable to a middle class CPU [10]. • Map Reduce

It is a set of distributed algorithms without strong dependencies allowing maximum parallelism. The most significant paradigm of this set is Hadoop which assumes a full dedicated cluster control, which makes it not the best candidate for HPC. There are several attempts to combine Map Reduce algorithms but each one of them requires a careful analysis to evaluate the results [120, 131].

• Combinational Logic

It is a class of application with extensive work in FPGAs invested in. It includes cryptographic algorithms like AES, DES, RC4, SHA-1, RSA. In multiple studies optimization techniques have been suggested, with results close to the ones obtained by CPUs [39, 86, 112].

• Graph Traversal