# Tracking haute fréquence pour architectures SIMD: optimisation de la reconstruction LHCb

Florian Lemaitre

### ▶ To cite this version:

Florian Lemaitre. Tracking haute fréquence pour architectures SIMD : optimisation de la reconstruction LHCb. Algorithme et structure de données [cs.DS]. Sorbonne Université, 2019. Français. NNT : 2019SORUS221. tel-02969497

### HAL Id: tel-02969497 https://theses.hal.science/tel-02969497v1

Submitted on 16 Oct 2020

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE DE DOCTORAT DE SORBONNE UNIVERSITÉ

### Spécialité

### Informatique

École doctorale Informatique, Télécommunications et Électronique (Paris)

### Présentée par

### Florian Lemaitre

Pour obtenir le grade de

### DOCTEUR de SORBONNE UNIVERSITÉ

Sujet de la thèse :

# Tracking haute fréquence pour architectures SIMD: optimisation de la reconstruction LHCb

présentée le 13 Février 2019

devant le jury composé de :

| [Directeur de thèse] | Lionel   | LACASSAGNE | LIP6   | (Sorbonne Université)    |

|----------------------|----------|------------|--------|--------------------------|

| [Rapporteur]         | Albert   | COHEN      | Google |                          |

| [Rapporteur]         | Daniel   | Menard     | IETR   | (Université de Rennes)   |

| [Examinateur]        | Emmanuel | CHAILLOUX  | LIP6   | (Sorbonne Université)    |

| [Examinateur]        | Michèle  | Gouiffès   | LIMSI  | (Université Paris-Sud)   |

| [Examinateur]        | Bertrand | LE GAL     | IMS    | (Université de Bordeaux) |

### Remerciements

J'aimerais remercier toutes les personnes qui ont participé de près ou de loin à cette thèse :

Albert Cohen et Daniel Menard pour leurs précieux conseils et remarques rapportés suite à la lecture de mon manuscrit de thèse.

Emmanuel Chailloux, Michèle Gouiffès et Bertrand Le Gal pour avoir accepté de prendre de leur temps pour faire partie de mon jury de thèse.

Lionel Lacassagne pour son aide déterminante et son soutien durant ces 3 années de thèse, et ce malgré la distance et les complications administratives.

Benjamin Couturier, Sébastien Ponce, Marco Clemencic et Paul Seyfert avec qui j'ai beaucoup (trop) discuté de mes travaux au sein de l'équipe LHCb.

Luis Granado, Joao Barbosa et Flavio Pisani pour m'avoir supporté pendant 3 ans dans le même bureau.

Toute l'équipe LHCb pour m'avoir accueilli et permis de réaliser cette thèse dans un tel environnement.

Ma compagne Charlotte à qui je dois désormais de nombreuses nuits de sommeil.

## Table des matières

| 1 | Intr | roduct               | ion                                  | 7  |  |  |  |  |

|---|------|----------------------|--------------------------------------|----|--|--|--|--|

|   | 1.1  | Préser               | ntation du CERN et du LHC            | 7  |  |  |  |  |

|   | 1.2  | Présentation de LHCb |                                      |    |  |  |  |  |

|   | 1.3  | LHCb                 | <i>Upgrade</i> pour 2020             | 10 |  |  |  |  |

|   | 1.4  | Enjeu                | x de la thèse                        | 12 |  |  |  |  |

|   | 1.5  | Plan o               | de la thèse                          | 12 |  |  |  |  |

| 2 | Opt  | imisat               | ions                                 | 15 |  |  |  |  |

|   | 2.1  | Archit               | secture                              | 15 |  |  |  |  |

|   |      | 2.1.1                | SIMD                                 | 15 |  |  |  |  |

|   |      | 2.1.2                | Cache                                | 28 |  |  |  |  |

|   |      | 2.1.3                | Scalarisation                        | 34 |  |  |  |  |

|   |      | 2.1.4                | Déroulage de boucle                  | 34 |  |  |  |  |

|   | 2.2  | Précis               | ion des calculs                      | 39 |  |  |  |  |

|   |      | 2.2.1                | Rappels sur le calcul flottant       | 39 |  |  |  |  |

|   |      | 2.2.2                | Racine carrée inverse                | 41 |  |  |  |  |

|   | 2.3  | Génér                | ation de code                        | 49 |  |  |  |  |

|   |      | 2.3.1                | Déroulage total                      | 49 |  |  |  |  |

|   |      | 2.3.2                | Dérouler-entrelacer et scalarisation | 50 |  |  |  |  |

|   |      | 2.3.3                | SIMD                                 | 53 |  |  |  |  |

|   | 2.4  | Synth                | èse                                  | 55 |  |  |  |  |

| 3 | Étu  | des pr               | éliminaires : calcul de paraboles    | 57 |  |  |  |  |

|   | 3.1  | Préser               | ntation des algorithmes              | 57 |  |  |  |  |

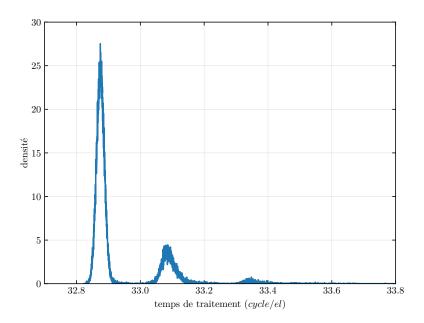

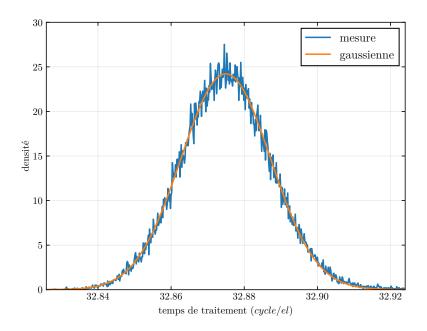

|   | 3.2 | Étude     | sur la mesure du temps                | ) |

|---|-----|-----------|---------------------------------------|---|

|   |     | 3.2.1     | Utilitaires de mesure du temps        | ) |

|   |     | 3.2.2     | Distribution du temps de traitement   | 2 |

|   | 3.3 | Analys    | se des performances                   | 3 |

|   |     | 3.3.1     | Comparaison des memory layouts        | 3 |

|   |     | 3.3.2     | Influence de la taille des données    | 7 |

|   |     | 3.3.3     | Impact de la précision                | ) |

|   |     | 3.3.4     | Multithreading                        | ) |

|   | 3.4 | Analys    | se de la précision                    | 3 |

|   | 3.5 | synthè    | se                                    | 1 |

| 4 | Fac | torisat   | ion de Cholesky 75                    | 5 |

|   | 4.1 | Algori    | thme                                  | 5 |

|   |     | 4.1.1     | Factorisation                         | 5 |

|   |     | 4.1.2     | Résolution                            | 3 |

|   | 4.2 | ormations | 3                                     |   |

|   |     | 4.2.1     | Traitement par lot                    | 7 |

|   |     | 4.2.2     | Déroulage et scalarisation            | 3 |

|   |     | 4.2.3     | Racine carrée inverse                 | 1 |

|   | 4.3 | Analys    | se des résultats                      | 1 |

|   |     | 4.3.1     | Protocole                             | 1 |

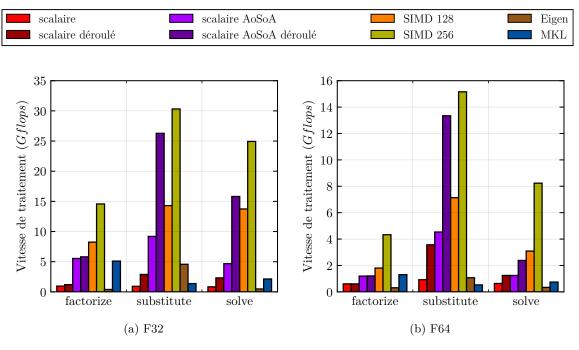

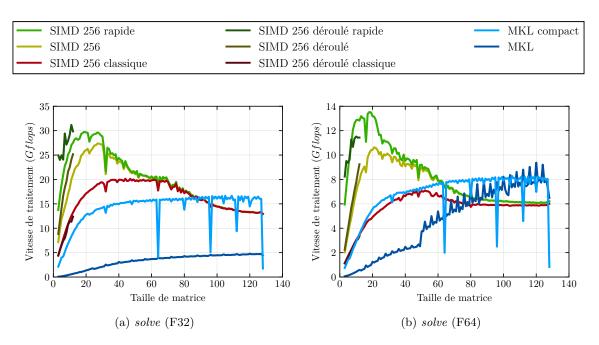

|   |     | 4.3.2     | Performance des différentes fonctions | 3 |

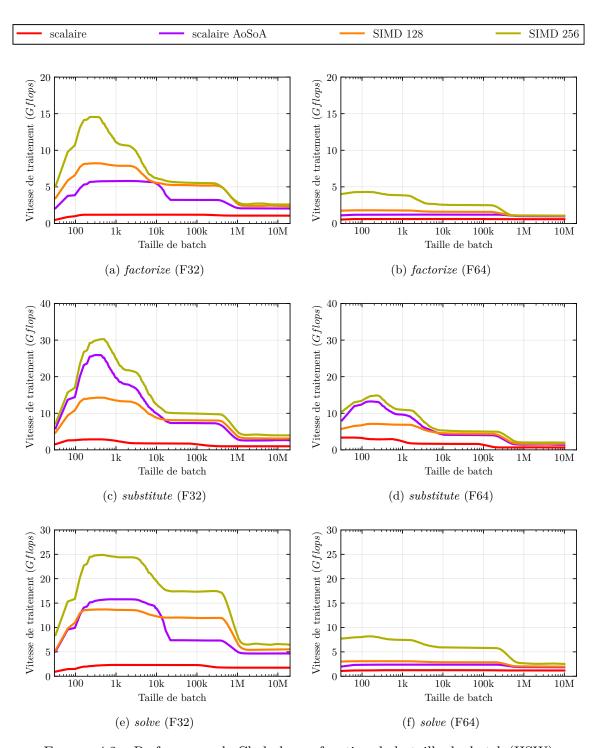

|   |     | 4.3.3     | Influence de la taille des données    | 1 |

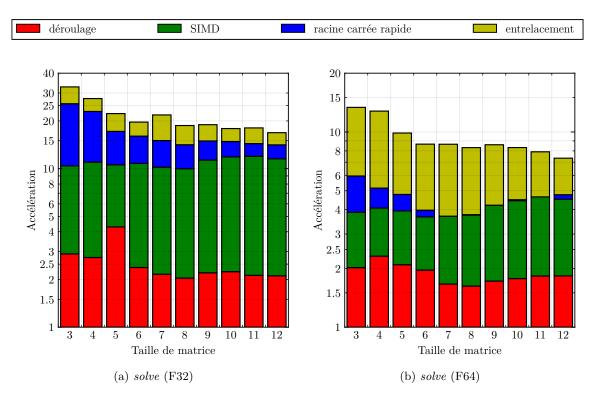

|   |     | 4.3.4     | Influence des optimisations           | 3 |

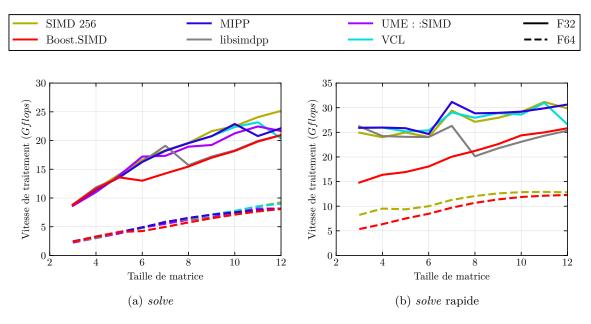

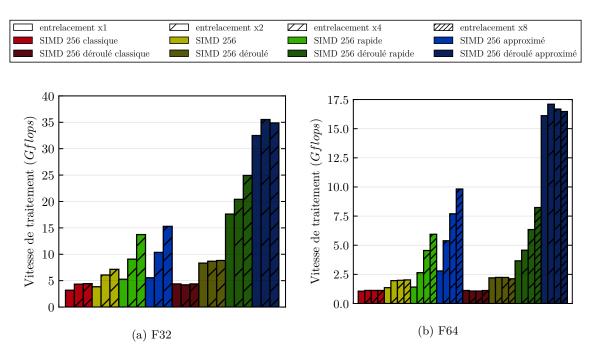

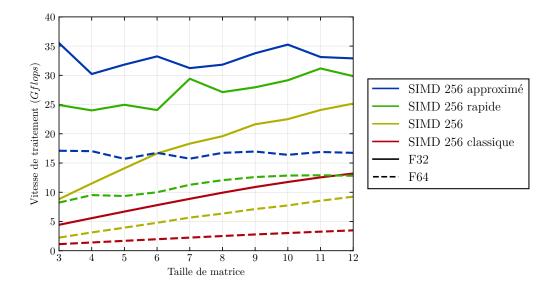

|   |     | 4.3.5     | Comparaison avec les wrappers SIMD    | 7 |

|   |     | 4.3.6     | Comparaison avec la MKL               | 3 |

|   |     | 4.3.7     | Influence du déroulage                | ) |

|   |     | 4.3.8     | Influence de la taille des matrices   | ) |

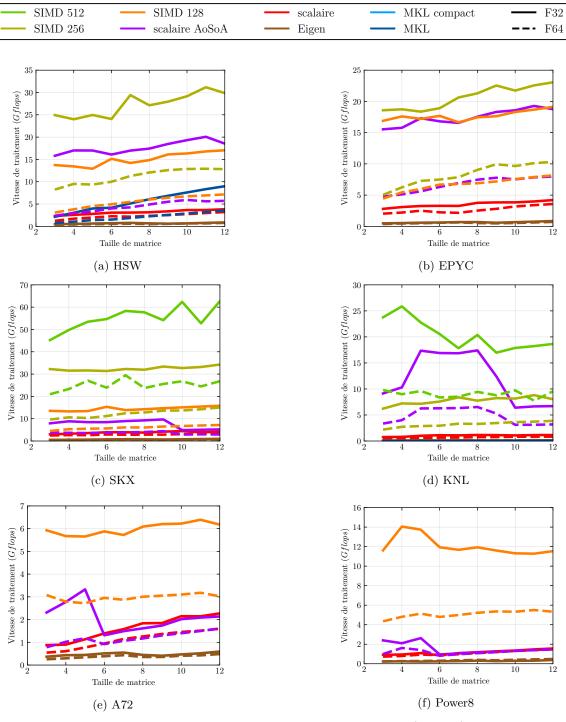

|   |     | 4.3.9     | Autres architectures                  | ) |

|   |     | 4.3.10    | Passage à l'échelle : OpenMP          | 3 |

|   | 1.1 | Synthe    | 94                                    | 1 |

| <b>5</b>     | $\mathbf{Filt}$ | re de l                                  | Kalman                                          | 95    |

|--------------|-----------------|------------------------------------------|-------------------------------------------------|-------|

|              | 5.1             | Algori                                   | thme                                            | . 95  |

|              | 5.2             | Transf                                   | formations                                      | . 98  |

|              |                 | 5.2.1                                    | Optimisation des accès aux matrices symétriques | . 98  |

|              |                 | 5.2.2                                    | Transformations algébriques                     | . 98  |

|              |                 | 5.2.3                                    | Heuristique de réordonancement                  | . 100 |

|              | 5.3             | Analy                                    | se des résultats                                | . 101 |

|              |                 | 5.3.1                                    | Protocole                                       | . 101 |

|              |                 | 5.3.2                                    | Influence des optimisations                     | . 101 |

|              |                 | 5.3.3                                    | Performance totale                              | . 103 |

|              | 5.4             | de Kalman spécifique à LHCb (LHC-Beauty) | . 106                                           |       |

|              |                 | 5.4.1                                    | Algorithme                                      | . 106 |

|              |                 | 5.4.2                                    | Algorithmes alternatifs                         | . 108 |

|              |                 | 5.4.3                                    | Résultats                                       | . 110 |

|              | 5.5             | Synthe                                   | èse                                             | . 114 |

| 6 Conclusion |                 |                                          |                                                 |       |

| Bi           | Bibliographie   |                                          |                                                 | 117   |

| $\mathbf{G}$ | lossa           | ire                                      |                                                 | 127   |

### Chapitre 1

### Introduction

### 1.1 Présentation du CERN et du LHC

Le CERN (Organisation Européenne pour la Recherche Nucléaire) est un pilier de la recherche fondamentale depuis sa création en 1954. Situé à la frontière Franco-Suisse et comptant 22 États membres, le CERN est devenu le plus gros laboratoire de physique des particules du monde. À présent, plus de 10 000 physiciens et ingénieurs travaillent ensemble à l'étude du monde sub-atomique.

Le CERN a aussi permis des avancées en dehors du monde de la physique avec par exemple la création du World Wide Web au début des années 90 : le premier site web fut activé en 1991, et le 30 Avril de la même année, le CERN annonce que le web sera gratuit et libre pour tout le monde.

Afin d'étudier les particules élémentaires (les composants de toute forme de matière), le CERN a mis au point l'appareil scientifique le plus grand et le plus complexe jamais réalisé : le LHC (*Large Hadron Collider*). Le Grand Collisionneur de Hadron est un accélérateur de particule circulaire de 27 km de circonférence enterré à presque 175 mètres sous le sol. Il a permis aux chercheurs du CERN et du monde entier de faire des découvertes majeures en physique des particules. La plus connue est la découverte de la dernière pièce manquante du Modèle Standard : le boson de Brout-Englert-Higgs.

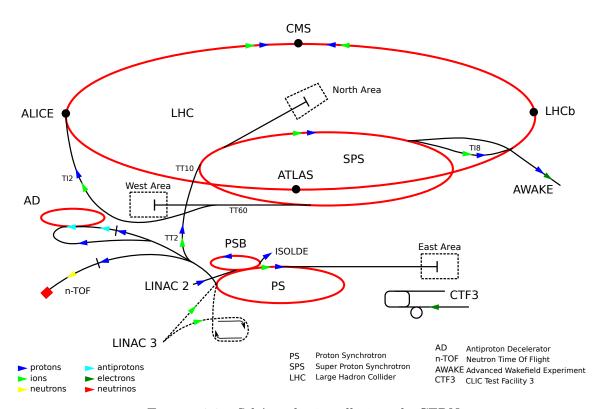

Sur la figure 1.1, on peut voir tout le complexe du CERN avec les différents accélérateurs de particules.

Le LHC comporte 4 expériences principales : Alice (A Large Ion Collider Experiment), Atlas (A Toroidal LHC Appartus), CMS (Compact Muon Solenoid) et LHCb. Chaque expérience consiste en un point de collision entre les deux faisceaux de protons du LHC, un détecteur pour mesurer les particules générées par la collision, ainsi qu'une ferme de calculs de plusieurs milliers de machines pour filtrer et analyser les données en sortie du détecteur.

FIGURE 1.1 – Schéma des installations du CERN

### 1.2 Présentation de LHCb

LHCB est l'une des 4 expériences principales du LHC et est conçu pour explorer et analyser les différences entre la matière et l'anti-matière. Plus précisemment, le but est de répondre au problème de l'anti-matière manquante en analysant les propriétés fondamentales de l'anti-matière.

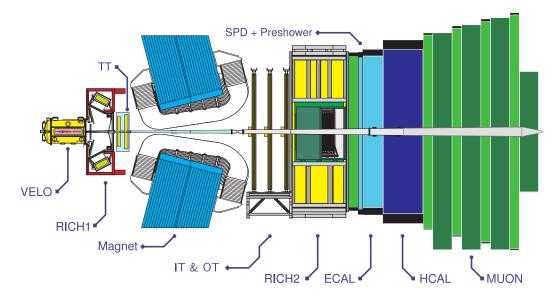

Le détecteur est composé d'un aimant tordant la trajectoire des particules chargées, ainsi que de plusieurs sous-détecteurs (figure 1.2) :

**VeLo :** Le *Vertex Locator* est un petit détecteur de particule extrêmement précis. Il est le plus proche possible du point de collision.

**RICH1 :** Le premier détecteur à effet Cherenkov (*Ring Imaging Cherenkov*) se situe juste après le VeLo et permet d'identifier et de mesurer la vitesse des particules lentes.

**Tracker Turencis :** Ce sous-détecteur est un *tracker* : il permet de déduire la position et la direction des particules le traversant. Celui-ci est situé juste avant l'aimant et possède 2 stations (plans de détections)

Tracker principal: Ce tracker est situé juste après l'aimant et possède 3 stations.

RICH2: Ce deuxième détecteur à effet Cherenkov permet de mesurer la vitesse des particules rapides

Calorimètres: Les calorimètres, situés après le *tracker* principal et le RICH2, permettent de mesurer l'énergie des particules rapides. Ils permettent aussi de détecter les évènements potentiellement intéressants avant la reconstruction.

Chambres à muons: Les chambres à muons permettent de détecter les muons: des particules lourdes, n'intéragissant que peu avec la matière. Ces détecteurs permettent de classifier la nature de la collision avant la reconstruction.

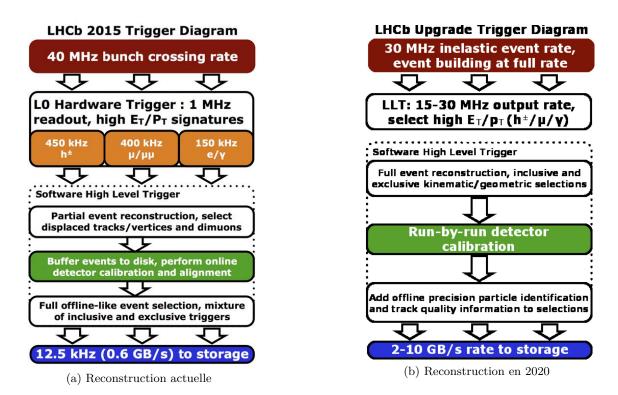

L'expérience LHCb détecte 40 000 000 de collisions par seconde, lorsque le LHC est en route. Cela produit une quantité phénoménale de données qui ne peut pas être analysée ni même stockée aussi vite. Juste en sortie du détecteur se trouvent 350 FPGA formant le LLT (Low Level Trigger) qui permettent de filtrer les évènements pour ne conserver que les évènements potentiellement intéressants. Les données filtrées sont ensuite transmises au HLT (High Level Trigger) constitué de 2000 serveurs.

Le traitement du HLT est séparé en deux étapes (HLT1 et HLT2). La première étape permet de reconstruire les trajectoires des particules. Le deuxième étape rassemble toutes les données du HLT1 afin de reconstruire l'évènement dans sa globalité. Ces deux étapes agissent également comme un filtre et ne conservent que les évènements jugés potentiellement intéressants.

Les données sont mises dans un tampon avant d'être traitées. En considérant le nombre de collisions et les pauses entre les *batchs* de collisions (pour réinjecter des protons par exemple), il faut en moyenne qu'un évènement soit traité en 10 ms par cœur.

FIGURE 1.2 – Schéma du détecteur LHCb

Les données sont ensuite envoyées à la surface où elles seront stockées sur bandes magnétiques et également envoyées sur un réseau de calculs mondial appelé la Grille. Les évènements envoyés sur la Grille sont analysés plus profondément et les résultats sont aggrégés sur plusieurs millions d'évènements.

Tout le code de reconstruction et d'analyse est écrit en C++ et utilise un framework interne appelé Gaudi.

### 1.3 LHCb Upgrade pour 2020

Le détecteur LHCb va être amélioré pour 2020, date de la prochaine mise en route du LHC. Beaucoup de sous-détecteurs seront changés et leur architecture différente nécessite de réécrire une partie des algorithmes de reconstruction [1].

En outre, la chaine de traitement va également changer : le filtre matériel LLT disparaitra et sera intégré au HLT (figure 1.3). La conséquence directe est que le HLT1 dans sa globalité devra traiter 30 fois plus d'évènement à la seconde. L'achat de machines plus récentes permettra d'augmenter considérablement la puissance de calcul de la ferme. Cela ne sera toutefois pas suffisant pour arriver au facteur 30 requis. Les estimations indiquent qu'il faut accélérer le code de la reconstruction d'un facteur 6 [2]. C'est pourquoi il est crucial d'accélérer le code de reconstruction. Le filtre de Kalman permettant de filtrer les traces reconstruites représente presque la moitié du temps d'exécution de la séquence complète, et est donc un candidat privilégié pour l'accélération de la reconstruction.

FIGURE 1.3 – Schéma de la reconstruction des évènements au sein de LHCb

### 1.4 Enjeux de la thèse

Les algorithmes de la reconstruction LHCb sont embarrasingly parallel. En effet, la reconstruction d'un évènement est complètement indépendante de la reconstruction des autres évènements, et il y a 30 000 000 d'évènements à la seconde à traiter. De plus, chaque évènement nécessite le traitement de plusieurs centaines à plusieurs milliers de traces.

L'algèbre linéaire requise pour le traitement de ces traces est de faible dimension : typiquement de  $2\times2$  à  $5\times5$ . Les bibliothèques d'algèbre linéaire telles que Eigen [3], Magma [4] ou MKL [5] sont optimisées pour de très grandes matrices, et ne sont pas donc adaptées à ces toutes petites matrices. Les petites matrices sont encore assez peu étudiées, mais leur grand nombre pose problème et nécessite des optimisations spécifiques. La communauté scientifique commence cependant à étudier des tels problèmes [6–10]. Les matrices de petites tailles ne sont pas utilisées qu'en physique des hautes énergies, mais aussi en vision par ordinateur [11,12].

La latence des transferts de données entre CPU et GPU étant trop grande pour ce genre de problème lors du début de cette thèse, nous avons décidé de nous concentrer sur les architectures CPU SIMD.

Cette thèse a pour but d'améliorer la vitesse de traitements de problèmes à faible dimension dans un contexte embarrasingly parallel.

Ces contributions sont multiples : l'identification d'un manque d'optimisations en faible dimension dans l'État de l'Art, la mise au point d'un assemblage de transformations connues efficace en faible dimension, l'élaboration d'une méthode et d'un générateur de code portable permettant l'application de ces transformations, ainsi que des implémentations rapides pour les algorithmes de la factorisation de Cholesky et du filtre de Kalman.

### 1.5 Plan de la thèse

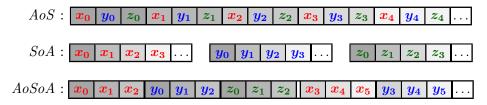

Nous verrons dans le chapitre 2 plusieurs transformations et optimisations relatives à l'architecture des processeurs telles que les agencements mémoires (Array of Structures, Structure of Arrays, Array of Structures of Array), la scalarisation et le déroulage de boucle (déroulage total, déroulage avec entrelacement). Nous ferons quelques rappels sur le calcul flottant, et comment accélérer la racine carrée inverse. Puis nous présenterons un générateur de code implémentant la plupart de ces transformations.

Dans le chapitre 3, nous utiliserons des algorithmes simples de la reconstruction LHCb afin de mettre au point une méthode pour mesurer de manière fiable les temps d'exécutions, d'appliquer et d'analyser les transformations vues précédemment sur ces algorithmes, et de faire une analyse de la précision des résulats.

1. Introduction 1.5. Plan de la thèse

Dans le chapitre 4, nous appliquerons la méthode ainsi que les transformations précédentes afin d'accélérer la factorisation de Cholesky pour de petites matrices. La factorisation de Cholesky est un algorithme classique d'algèbre linéaire qui est utilisé notamment pour inverser des matrices symétriques comme dans le filtre de Kalman.

Dans le chapitre 5, nous appliquerons une fois de plus ces transformations afin d'accélérer le filtre de Kalman, pièce maîtresse de la reconstruction LHCb. L'étude portera tout d'abord sur la formulation générale du filtre de Kalman avec des matrices  $4\times4$ , où de nouvelles transformations seront testées. Puis nous aborderons la formulation spécifique à LHCb du filtre de Kalman que nous comparerons en termes de vitesse à l'implémentation actuelle.

### Chapitre 2

### **Optimisations**

Cette partie traite des optimisations utilisées. Les optimisations présentées ici sont largement répandues dans la littérature [13]. Leurs combinaisons sont en revanche peu approfondies, mais sont importantes pour augmenter la vitesse de traitement [14]. Nous proposons ici des explications poussées de ces optimisations, ainsi que leurs implémentations au sein de cette thèse.

Le but de cette partie est de comprendre et d'assimiler plusieurs transformations et optimisations relatives à l'architecture des processeurs telles que les agencements mémoires (Array of Structures, Structure of Arrays, Array of Structures of Array), la scalarisation et le déroulage de boucle (déroulage total, déroulage avec entrelacement). Mais aussi l'accélération de la racine carrée inverse par des considérations arithmétiques. La plupart de ces transformations sont ensuites regroupées au sein d'un générateur de code qui sera utilisé dans la suite de cette thèse.

### 2.1 Architecture

### 2.1.1 SIMD

Afin d'accélérer les calculs, les processeurs actuels possèdent des unités fonctionnelles spécifiques qui sont capables d'effectuer une opération arithmétique comme une addition ou une multiplication sur des données différentes en parallèle. L'intérêt est le suivant : une telle instruction nécessite le même temps que la même instruction scalaire, mais traite plus de données dans le même laps de temps.

Ce paradigme est désigné par l'acronyme anglais SIMD de la classification Flynn [15] : Single Instruction Multiple Data. Les architectures SIMD les plus courantes sont SSE, AVX et AVX512 sur x86, Neon sur ARM ainsi que Altivec et VSX sur Motorola et IBM.

Cela se présente sous la forme d'un jeu de registres de taille fixes (typiquement 128 bits), et d'instructions spécifiques afin de manipuler ces registres. Les instructions disponibles se regroupent en plusieurs catégories usuelles comme les accès mémoires, les opérations arithmétiques et logiques; mais aussi des catégories plus spécifiques au SIMD comme le mélange ou le masquage des éléments du vecteur.

Les instructions disponibles dépendent fortement de l'architecture ciblée. Il est donc nécessaire d'avoir une connaissance approfondie de l'architecture afin d'utiliser pleinement les unités SIMD.

Il existe plusieurs manières d'utiliser le SIMD :

- Assembleur

- *Intrinsics* : extension du langage C permettant un accès direct aux registres SIMD ainsi qu'aux instructions associées par le biais de types natifs et de fonctions.

- Bibliothèques SIMD: fonctionne comme les *intrinsics*, mais avec une interface abstraite identique entre les architectures: Boost.SIMD [16], Cyme [17], libsimdpp [18], MIPP [19], UME::SIMD [20], Vc [21], Vcl [22]...

- Paradigmes de programmation parallèle [23] : ISPC [24], OpenACC [25], OpenCL [26], OpenMP [27], #pragmas...

- Vectorisation par le compilateur : ce dernier abstrait les opérations arithmétiques scalaires afin de les regrouper en opérations parallèles qu'il pourra alors convertir en instructions SIMD.

L'assembleur ainsi que les *intrinsics* sont particulièrement difficiles à écrire et à maintenir, et n'offrent aucune portabilité. Chaque architecture possède ses propres instructions et ses propres *intrinsics*, même si les capacités sont similaires.

Les bibliothèques SIMD avec leur abstraction permettent de s'affranchir des problèmes de portabilité, mais restent difficiles à programmer et requièrent tout de même une bonne compréhension de l'architecture afin d'avoir de bonnes performances.

Les paradigmes de programmation parallèle ainsi que la vectorisation offrent une portabilité maximale à moindre effort, mais perdent le contrôle requis pour des performances optimales.

Les accès mémoires en SIMD doivent être alignés avec la taille du registre. Par exemple, si un registre SIMD fait 16 octets, il faut que l'adresse soit un multiple de 16. Cette contrainte est imposée par l'implémentation matérielle afin d'être efficace.

Sur la plupart des architectures, il existe également des instructions pouvant faire des accès non-alignés, mais celles-ci sont moins efficaces : elles sont souvent implémentées avec deux accès alignés. Les architectures x86 supportent les accès non-alignés aussi rapides que les accès alignés depuis Nehalem chez Intel et depuis Bulldozer chez AMD.

C'est pourquoi il est préférable d'aligner les données en mémoire afin de pouvoir utiliser les accès alignés plus efficaces. Pour ceci, il est nécessaire de recourir à des fonctions d'allocations mémoires spécifiques comme posix\_memalign [28, pp. 1448-1449], \_mm\_malloc [29, pp. 657] ou bien aligned\_alloc [30, chapitre 7.22.3.1] en C11.

### 2.1.1.1 Historique

Les premiers travaux sur des architectures vectorielles remontent au début des années 60 avec le projet "Solomon" de Westinghouse. Ce projet fut rapidement arrêté, mais servit de base pour le projet ILLIAC IV [31]. Sorti en avril 1972, ILLIAC IV est ainsi la première machine vectorielle et comptait 64 FPU (Floating Point Unit) à 64 bits. Toutes les FPU sont indépendantes et possèdent leur propre mémoire, mais exécutent la même instruction. Cette approche fait de l'ILLIAC IV la première machine SIMD. Elle n'est cependant stable qu'à partir de 1975.

Entre-temps, deux autres machines vectorielles apparurent en 1974 : le ASC [32] (Advanced Scientific Computer) de Texas Instruments, et le STAR-100 [33] de CDC (Control Data Corporation). Sur ces machines, une instruction vectorielle "crée" un pipeline alimentant des unités scalaires. Les données sont lues et écrites en mémoire directement. Du fait que les éléments d'un vecteur ne sont pas calculés en parallèle, ces machines ne sont pas considérées comme des machines SIMD, mais des machines vectorielles.

Ces premières machines seront vite détrônées par les machines Cray-1 en 1975 [34]. Cette architecture a une approche vectorielle similaire à l'ASC et au STAR-100, mais ajoute des registres vectoriels. Ces registres permettent de stocker les résultats temporaires des opérations vectorielles, ce qui permet de chaîner les instructions et ainsi commencer l'instruction suivante alors même que la précédente n'a pas terminé de traiter le vecteur complet. Cette approche permet aussi de s'affranchir des accès mémoires entre deux instructions travaillant sur les mêmes données. En revanche, ces registres imposent une taille maximale aux vecteurs traités (64 éléments de 64 bits).

Les machines Cray sont des machines phares des années 80 et beaucoup portent une grande estime pour ces machines aujourd'hui encore. Par la suite, les autres fabricants utiliseront également une approche vectorielle pour leurs supercalculateurs.

Cette période voit également l'arrivée de machines SIMD massivement parallèles possédant plusieurs milliers de petites ALU (*Arithmetic and Logic Unit*) indépendantes nommées PE (*Processing Element*). Le DAP [35] (Distributed Array Processor) d'ICL (International Computers Limited) en est le précurseur avec un premier prototype en 1974 et une sortie officielle en 1979. Il possède 4096 PE de 1 bit.

Plusieurs constructeurs suivent cette voie jusqu'aux années 90. Le représentant le plus connu de ce type de machines est la "Connection Machine" [36] sortie en 1985 avec ses 65 536 PE de 1 bit, connectés selon un hypercube.

L'intérêt pour les architectures vectorielles et SIMD dédiées aux supercalculateurs s'essoufle dans les années 90 au profit d'architectures multi-cœurs et surtout multi-processeurs. Par la suite, les supercalculateurs, bénéficiant des avancées des microprocesseurs, disposent de nouvelles architectures SIMD.

Du côté des microprocesseurs, un intérêt pour le SIMD commence à apparaître au milieu des années 90 afin d'accélérer les applications multimedia (comme le décodage vidéo). Par simplicité, les architectures existantes sont étendues pour supporter de nouvelles instructions SIMD. L'approche utilisée est de stocker un vecteur en registre (comme les machines Cray), et d'utiliser autant d'unités fonctionnelles que nécessaire pour traiter tous les éléments en parallèle. On parle ainsi de SWAR [37] (SIMD Within A Register). Selon les opérations, il est possible d'utiliser des unités fonctionnelles plus grosses et d'en modifier légèrement le circuit : ainsi, deux additionneurs 16 bits peuvent être implémentés en utilisant un additionneur 32 bits où la retenue du 16ème bit n'est pas propagée au 17ème bit, séparant ainsi le traitement en deux sans nécessiter d'unités fonctionnelles spécifiques. On parle dans ce cas de Sub-Word Parallelism.

La première architecture à se voir doter d'une telle extension SIMD est PA-RISC avec les jeux d'instructions MAX-1 en 1994, puis MAX-2 en 1995, d'une largeur respective de 32 et 64 bits. Les autres architectures suivent avec VIS pour SPARC en 1995, MDMX pour MIPS-V en 1996, MVI pour Alpha en 1996 et MMX pour x86 en 1997, toutes avec une largeur de 64 bits. Ces extensions étant orientées multimedia, elles ne supportent que des données de type entier. La plupart de ces jeux d'instructions n'introduisent pas de nouveaux registres et réutilisent des registres existants : par exemple, MMX utilise les registres flottants du coprocesseur x87, ce qui pose problème lors de l'utilisation simultanée d'instructions scalaires et SIMD.

Sur MIPS-V, le jeu d'instructions "paired-single" sorti en 1994 permet d'étendre le SIMD au calcul flottant simple précision. AMD développe 3DNow! en 1998 qui permet lui aussi le support des nombres flottants simple précision sur x86. 3DNow! est une extension de MMX.

En 1998, Apple, IBM, et Motorola développent conjointement un jeu d'instructions SIMD 128 bits pour l'architecture Power. Ce jeu d'instructions est appelé "Velocity Engine" par Apple, VMX (Vector Media Extension) par IBM et enfin Altivec par Motorola. Le nom Altivec est désormais préféré, et le nom "Velocity Engine" a complètement disparu. Ce jeu d'instructions supporte l'arithmétique flottante simple précision, et peut donc traiter jusqu'à 4 flottants en parallèle. Contrairement à ses prédecesseurs, Altivec introduit 32 registres de 128 bits. Il est utilisé pour accélérer les applications Apple comme QuickTime ou iTunes, mais aussi des applications tierces telles qu'Adobe Photoshop. Il est considéré, aujourd'hui encore, comme l'un des meilleurs jeux d'instructions SIMD de par sa souplesse.

En 1999, Intel présente SSE, un jeu d'instructions SIMD 128 bits. Il introduit 8 registres de 128 bits (XMM0-XMM7). SSE ne supporte pas les types entiers et est donc restreint au calcul flottant simple précision. Il faut donc utiliser MMX afin d'utiliser du SIMD avec des entiers.

ARM spécifie un premier jeu d'instructions vectoriel en 2001 : VFP (Vector Floating-Point). Ce jeu d'instructions définit 16 registres 64 bits pouvant également être interprétés comme 32 registres 32 bits. Plusieurs registres consécutifs peuvent être combinés pour former un vecteur de taille maximale 256 bits. À l'instar des machines Cray, les instructions vectorielles ne traitent pas les éléments du vecteur en parallèle, mais séquentiellement au travers d'un pipeline. Ce jeu d'instructions ne supporte que les opérations flottantes (en simple et double précision).

L'année suivante, ARM spécifie un jeu d'instructions SIMD afin d'accélérer les applications multimedias. Ce dernier n'a pas de nom officiel. Il est souvent désigné par "SIMD extensions for multimedia". Tout comme les premières architectures SWAR, il n'introduit aucun registre et permet d'effectuer des opérations entières sur  $2\times16$  bits ou  $4\times8$  bits (largeur totale : 32 bits).

Au début des années 2000, les premières cartes graphiques programmables apparaissent avec une architecture similaire à ILLIAC IV.

En 2001, une nouvelle version de SSE voit le jour. SSE2 ajoute le support des flottants double précision, des entiers 8, 16 et 32 bits, ainsi qu'un support partiel des entiers 64 bits. Les opérations sur les entiers sont inspirées des opérations existantes sur MMX. SSE comme SSE2 supportent des instructions scalaires sur les registres vectoriels (qui ne traitent donc que le premier élément). Cela permet de s'affranchir du coprocesseur x87 pour le calcul flottant, et ainsi avoir un support des flottants selon la norme IEEE 754 [38]. Dès lors, les compilateurs n'utilisent plus x87 pour compiler du code en float ou en double lorsque SSE2 est disponible, et ce même pour du code scalaire non-vectorisé. Le coprocesseur x87 reste utilisé si le code utilise du long double (précision étendue).

Plusieurs versions de SSE se suivront avec des légères améliorations jusqu'en 2008 : SSE3 (2004), SSSE3 (2006), SSE4.1 (2007), SSE4a (2007) et SSE4.2 (2008).

En 2008, le jeu d'instructions AVX est spécifié par Intel et AMD. Il faudra attendre 2011 pour que les premiers processeurs le supportent. L'apport principal de l'AVX est une largeur de 256 bits. AVX n'introduit pas de nouveau registre, mais augmente la taille des registres SSE. En outre, le nouvel encodage VEX des instructions autorise trois opérandes par instructions, ce qui peut réduire la pression de registres.

Un support amélioré des entiers (notamment 64 bits) et de nouvelles instructions de mélange voient le jour en 2013 avec la version suivante : AVX2. Le support des FMA (Fused Multiply-Add) apparaitra en même temps.

En 2008, ARM définit un nouveau jeu d'instructions SIMD remplaçant l'ancien : Neon (ou "Advanced SIMD"). Neon définit 16 registres 128 bits. Ces registres peuvent être accédés également comme 32 registres 64 bits, et sont partagés avec la vfp. Neon supporte les entiers 8, 16, 32 et 64 bits, les flottants simple précision, mais également les polynômes booléens de degrés 8 et 16.

En 2009, le jeu d'instructions VSX complémente Altivec. VSX apporte le support des entiers 64 bits, de la double précision, ainsi que la division et la racine carrée précise.

En 2012, IBM créé le jeu d'instructions SIMD QPX de 256 bits. Ce jeu d'instructions est prévu pour le calcul scientifique et ne supporte que les flottants double précision.

En 2013, Intel propose une version étendue à 512 bits d'AVX : AVX512. Mise à part des registres plus larges, AVX512 apporte plusieurs nouveautés :

- un nombre accru de registres (32 registres de 512 bits),

- les instructions sont masquables : le traitement d'un élément en particulier peut être ignoré par le masque,

- 8 registres spécifiques aux masques,

- d'avantages d'instructions spécialisées comme la détection de conflit qui permet de supporter plus d'algorithmes.

AVX512 est une version améliorée du jeu d'instructions des Xeon Phi Knights Corner (déjà en 512 bits).

Fujitsu et ARM annoncent en 2017 un nouveau jeu d'instructions : SVE [39] (Scalable Vector Extension). SVE se démarque des autres architectures SWAR par une largeur de registre non fixée. En effet, chaque machine SVE peut implémenter une taille de registre différente. Le code assembleur pour cette architecture est donc agnostique à la taille des vecteurs. Tout comme AVX512, les instructions sont masquables.

Début 2018, NEC propose des machines vectorielles sous la forme de cartes accélératrices avec le SX-Aurora TSUBASA [40]. Cette machine adopte une approche hybride entre le SIMD, et le vectoriel (l'exécution séquentielle via un pipeline à la Cray). Les registres vectoriels ont une largeur de  $16\,384$  bits  $(256\times64)$ . Ces registres sont découpés en tranches de 32 éléments : tous les éléments d'une même tranche sont traités en parallèle, et chaque tranche est traitée séquentiellement au sein d'un pipeline spécifique.

Le tableau 2.1 retrace l'évolution des processeurs vectoriels et SIMD depuis ILLIAC IV jusqu'au SX-Aurora TSUBASA de NEC.

Table 2.1 – Évolution des architectures CPU vectorielles et SIMD

| Machine                   | Année | Type Largeur              |   |

|---------------------------|-------|---------------------------|---|

| ILLIAC IV                 | 1972  | SIMD $64 \times 64$       |   |

| CDC STAR-100              | 1974  | vectoriel N/A             |   |

| TI ASC                    | 1974  | vectoriel N/A             |   |

| Cray-1                    | 1975  | vectoriel 64×64           |   |

| ICL DAP                   | 1979  | SIMD $4096 \times 1$      |   |

| Goodyear MPP              | 1983  | SIMD 16384×1              | 1 |

| Cray-2                    | 1985  | vectoriel 64×64           |   |

| NEC SX-2                  | 1985  | vectoriel 256×64          |   |

| Connection Machine 1      | 1985  | SIMD $65536\times1$       | 1 |

| CDC ETA10 [41]            | 1987  | vectoriel ?               |   |

| NEC SX-3 [42]             | 1990  | vectoriel $256 \times 64$ |   |

| Connection Machine 5 [43] | 1991  | MIMD $4\times64$          |   |

| Architecture | extension       | Année | Type      | Largeur    | I8 I16 I32 I64 | F32 F64      |

|--------------|-----------------|-------|-----------|------------|----------------|--------------|

| PA-RISC      | MAX-1           | 1994  | SIMD      | 32         | 11             |              |

| PA-RISC      | MAX-2           | 1995  | SIMD      | 64         | 111            |              |

| SPARC        | VIS             | 1995  | SIMD      | 64         | 111            |              |

| MIPS-V       | MDMX            | 1996  | SIMD      | 64         | 111            |              |

| MIPS-V       | paired-single   | 1996  | SIMD      | 64         |                | $\checkmark$ |

| Alpha        | MVI             | 1996  | SIMD      | 64         | 111            |              |

| x86          | MMX             | 1997  | SIMD      | 64         | 111            |              |

| x86          | 3DNow!          | 1998  | SIMD      | 64         |                | ✓            |

| PowerPC      | Altivec         | 1998  | SIMD      | 128        | 111            | ✓            |

| x86          | SSE             | 1999  | SIMD      | 128        |                | ✓            |

| ARM          | VFP             | 2001  | vectoriel | 32 - 256   |                | / /          |

| x86          | SSE2            | 2001  | SIMD      | 128        | / / / ~        | / /          |

| ARM          | media extension | 2002  | SIMD      | 32         | <b>/</b> /     |              |

| x86          | SSE3            | 2004  | SIMD      | 128        | <b>✓ ✓ ✓</b> ~ | / /          |

| x86          | SSSE3           | 2006  | SIMD      | 128        | <b>✓ ✓ ✓</b> ~ | / /          |

| x86          | SSE4.1          | 2007  | SIMD      | 128        | <b>✓ ✓ ✓</b> ~ | / /          |

| x86          | SSE4.2          | 2008  | SIMD      | 128        | 111            | / /          |

| ARM          | Neon            | 2008  | SIMD      | 128        | / / / ~        | $\checkmark$ |

| PowerPC      | VSX             | 2009  | SIMD      | 128        | 111            | / /          |

| x86          | AVX             | 2011  | SIMD      | 256        | 111            | / /          |

| Power        | QPX             | 2012  | SIMD      | 256        |                | ✓            |

| x86          | AVX2            | 2013  | SIMD      | 256        | 111            | / /          |

| ARM          | Neon (64 bits)  | 2013  | SIMD      | 128        | 111            | / /          |

| x86          | AVX512          | 2017  | SIMD      | 512        | 111            | / /          |

| ARM          | SVE             | 2017* | SIMD      | 128 – 2048 | 111            | ✓ ✓          |

| NEC          | TSUBASA         | 2018  | hybride   | 16384      | ? ? ? ?        | / /          |

$<sup>\</sup>ast$  : Date d'annonce

### 2.1.1.2 Métriques

De par sa nature, le SIMD nécessite un plus gros débit des bus et des mémoires. En effet, ces instructions traitent plus de données dans le même laps de temps que les instructions scalaires équivalentes. Il faut donc plus de données afin de garder les unités fonctionnelles occupées.

On mesure généralement la performance brute d'une machine en comptant le nombre d'opérations flottantes que celle-ci peut effectuer en une seconde : flops. On utilise généralement le préfixe giga (10<sup>9</sup>) pour des ordres de grandeurs plus appréciables : Gflops. On distingue deux types de performance brutes : la performance théorique déduite des spécifications du processeur, et la performance pic soutenue mesurée grâce à des benchmarks normalisés dont le plus connu est Linpack [44]. La performance pic se situe généralement entre 80 et 90 % de la performance théorique, et reflète mieux ce qu'il est possible de tirer de la machine.

En ce qui concerne le débit des accès mémoires, on parle de bande passante qui s'exprime en octets par seconde (o/s). A l'instar de la performance, le préfixe giga est très souvent utilisé : Go/s.

Contrairement à la performance brute, il existe une hiérarchie mémoire avec plusieurs caches, chacun ayant une bande passante différente. Les benchmarks les plus utilisés normalisent les motifs d'accès mémoires. Le plus connu est STREAM TRIAD [45] (listing 2.1). Il est possible de mesurer la bande passante de la mémoire externe (RAM), des différents niveaux de caches ou bien entre deux processeurs. Nous nous intéresseront principalement à la bande passante des caches et de la mémoire externe. La bande passante théorique n'est que très rarement considérée dans ce contexte.

Il peut être intéressant de regarder le rapport entre les deux métriques précédentes. On peut ainsi définir le rapport calcul/bande passante ainsi : Le produit de la performance brute (pic ou théorique) par la taille d'un élément (4 octet/élément pour un float) divisé par la bande passante.

Le point intéressant d'une telle métrique est qu'elle ne dépend pas de la taille des

Listing 2.1 Implémentation naïve de STREAM TRIAD

```

void stream_triad(float* A, float* B, float* C, long n) {

float alpha = 1.2345f;

for (long i = 0; i < n; i++) {

C[i] = alpha * A[i] + B[i];

}

}</pre>

```

éléments dès lors que l'architecture supporte le SIMD. En effet, la très grande majorité des instructions SIMD prend le même nombre de cycles pour les calculs en simple précision qu'en double (la division et la racine carrée en sont des contre-exemples). Si l'instruction d'addition en float prend 3 cycles pour calculer 4 éléments, alors l'instruction d'addition en double prendra 3 cycles pour calculer 2 éléments. En d'autres termes, 4 additions en float nécessiteront 3 cycles, alors que 4 additions en double nécessiteront 6 cycles.

Cette métrique est à mettre en parallèle avec l'Intensité Arithmétique (IA) qui est le rapport entre le nombre d'opérations arithmétiques et le nombre d'accès mémoire d'une fonction ou d'un noyau de calcul. Ainsi, si l'IA est largement supérieure au rapport calcul/bande passante, alors le problème sera généralement limité par la puissance de calcul (compute bound). Dans le cas opposé, le problème sera généralement limité par les accès mémoires (memory bound). Quand les deux rapports sont proches, le programme aura, en pratique, de grandes chances d'être limité par d'autres facteurs comme le sparse addressing ou plus rarement le décodage des instructions par le processeur.

Comme la bande passante dépend de la mémoire qui est accédée, il en est de même pour le rapport calcul/bande passante. Ainsi, il est possible que le problème soit compute bound lorsque les données sont dans le cache L1, tout en étant memory bound lorsque les données sont en mémoire externe. Ce rapport dépend aussi, bien évidemment, de la machine considérée.

#### 2.1.1.3 Array of Structures

Considérons un ensemble de points dans l'espace (3D) dont on souhaite calculer le barycentre. La manière la plus simple de représenter ceci en mémoire est d'avoir un tableau de quadruplets (listing 2.2). Ainsi, pour calculer le barycentre, il suffit d'itérer sur l'ensemble des points, et de calculer la moyenne de chaque coordonnée : listing 2.3. Cet agencement mémoire s'appelle AoS (Array of Structures) signifiant littéralement tableau de structures.

Un tel code n'est pas trivialement vectorisable. En effet, bien que notre type Point soit un quadruplet de floats qui rentre donc parfaitement dans un registre SIMD de 128 bits, le rôle de chaque composante n'est pas identique. Le poids est différent et nécessite un

**Listing 2.2** Tableau de points (AoS)

```

struct Point {

float x, y, z; // coordonées

float w; // masse

};

Point points[N];

```

**Listing 2.3** Calcul de barycentre : scalaire (AoS)

```

Point center = {0.f, 0.f, 0.f, 0.f};

for (int i = 0; i < N; i++) {

center.x += points[i].w * points[i].x;

center.y += points[i].w * points[i].y;

center.z += points[i].w * points[i].z;

center.w += points[i].w;

}

center.x /= center.w;

center.y /= center.w;

center.z /= center.w;</pre>

```

traitement particulier. À noter que la division finale peut être effectuée en scalaire afin de faciliter la vectorisation sans que cela n'impacte les performances d'une telle fonctions (si N est suffisamment grand).

Pour résoudre ce problème, il existe principalement deux approches :

- vectorisation verticale : chaque vecteur correspond à même un point (ou une partie d'un point pour des problèmes plus gros),

- vectorisation horizontale : chaque vecteur correspond à une même composante de points différents.

La vectorisation verticale est généralement privilégiée lorsque les composantes d'un problème sont nombreuses et partagent le même rôle : vecteur ou matrice de grande dimension. Mais celle-ci ne passe pas bien à l'échelle lorsque la taille des objets manipulés est petite, d'autant plus, si la taille de ces objets n'est pas une puissance de 2. De plus, les opérations à effectuer sur ces vecteurs peuvent être difficiles à exprimer lorsque les composantes ne partagent pas le même rôle.

La vectorisation horizontale résout ces problèmes, mais a un coût lors de la lecture/écriture des données. Il faut en effet transposer les données afin que chaque registre traite la même composante de plusieurs points. De plus, la vectorisation horizontale requiert généralement plus de registres actifs : un registre par composante, là où la vectorisation verticale traite plusieurs composantes avec un seul registre.

Dans le cas présent, les deux approches donnent des résultats légèrement différents en pratique : les sommes ne sont pas calculées dans le même ordre.

Toutefois, la vectorisation horizontale ne peut s'appliquer que si le nombre d'itérations de la boucle est un multiple du cardinal d'un registre SIMD (4 floats dans le cas présent). Dans le cas contraire, il ne sera pas possible d'utiliser la version SIMD pour l'intégralité de la boucle. Il faudra en effet traiter la fin de la boucle (qui ne tiendrait pas dans un

**Listing 2.4** Calcul de barycentre : vectorisation verticale (AoS)

```

typedef float __attribute__((__vector_size__(16))) vec4f;

__attribute__((__vector_size__(16))) vec4i;

typedef int

Point center of mass(const Point* pts, int n) {

vec4f center;

vec4i mask = {true, true, true, false};

vec4f ones = \{1.f, 1.f, 1.f, 1.f\};

for (int i = 0; i < n; i++) {

vec4f p = {pts[i].x, pts[i].y, pts[i].z, pts[i].w};

vec4f wheight = {p[3], p[3], p[3], p[3]};

center += (mask ? weight : ones) * p;

}

vec4f wheight = {center[3], center[3], center[3]};

center /= mask ? wheight : ones;

return {center[0], center[1], center[2], center[3]};

}

```

registre SIMD entier) de manière différente : soit en repassant en scalaire, soit en utilisant des masques SIMD pour ne traiter que les éléments nécessaires.

De plus, dans cet exemple, le code applique une réduction qui nécessite un traitement particulier non-nécessaire en scalaire.

#### 2.1.1.4 Structure of Arrays

En pratique, il est possible de s'affranchir du coût de la transposition tout en conservant les avantages de la vectorisation horizontale [46]. Il suffit d'avoir en mémoire les données prêtes à être exploitées. Au lieu de stocker un tableau de quadruplets, on stocke quatre tableaux de scalaires (listing 2.6). Ainsi, une composante aura un adressage contigu en mémoire pour l'ensemble des points. Tous les xs sont à la suite des autres et peuvent être chargés en registre trivialement. Cet agencement mémoire se nomme SoA (Structue of Arrays) et est l'agencement par défaut en Fortran 77.

Il faut adapter légèrement le code scalaire afin de bénéficier de cet agencement mémoire (listing 2.7). La vectorisation horizontale de ce code est désormais triviale et peut être laissée au compilateur. Il faudra cependant l'autoriser à effectuer des optimisations sur les nombres à virgule flottante pouvant changer les résultats (à cause de la réduction flottante).

Avec un tel agencement mémoire, le corps de boucle SIMD est écrit de manière identique au corps de boucle scalaire : toute la complexité du SIMD semble avoir disparue. Les

**Listing 2.5** Calcul de barycentre : vectorisation horizontale (AoS)

```

typedef float __attribute__((__vector_size__(16))) vec4f;

Point center_of_mass(const Point* pts, int n) {

Vec4f sX = \{0, 0, 0, 0\};

Vec4f sY = \{0, 0, 0, 0\};

Vec4f sZ = \{0, 0, 0, 0\};

Vec4f sW = \{0, 0, 0, 0\};

for (int i = 0; i < n - 4; i += 4) {

// transposition des éléments

Vec4f x = {pts[i].x, pts[i+1].x, pts[i+2].x, pts[i+3].x};

Vec4f y = {pts[i].y, pts[i+1].y, pts[i+2].y, pts[i+3].y};

Vec4f z = \{pts[i].z, pts[i+1].z, pts[i+2].z, pts[i+3].z\};

Vec4f w = \{pts[i].w, pts[i+1].w, pts[i+2].w, pts[i+3].w\};

// calcul identique au cas scalaire

sX += w*x;

sY += w*y;

sZ += w*z;

sW += w;

}

// réduction (vecteurs -> scalaires)

Point center;

center.x = sX[0] + sX[1] + sX[2] + sX[3];

center.y = sY[0] + sY[1] + sY[2] + sY[3];

center.z = sZ[0] + sZ[1] + sZ[2] + sZ[3];

center.w = sW[0] + sW[1] + sW[2] + sW[3];

// reste

for (int i = (n/4)*4; i < n; i++) {

center.x += pts[i].w * pts[i].x;

center.y += pts[i].w * pts[i].y;

center.z += pts[i].w * pts[i].z;

center.w += pts[i].w;

}

center.x /= center.w;

center.y /= center.w;

center.z /= center.w;

return center;

}

```

### Listing 2.6 Tableau de points (SoA)

```

struct Points {

float *x, *y, *z;

float *w;

};

```

### **Listing 2.7** Calcul de barycentre : scalaire (SoA)

```

Point center_of_mass(Points points, int n) {

Point center = {0, 0, 0, 0};

for (int i = 0; i < n; i++) {

center.x += points.w[i] * points.x[i];

center.y += points.w[i] * points.y[i];

center.z += points.w[i] * points.z[i];

center.w += points.w[i];

}

center.x /= center.w;

center.y /= center.w;

center.z /= center.w;

return center;

}</pre>

```

performances, au contraire, sont bien meilleures qu'en scalaire ou en AoS. Les unités SIMD sont utilisées plus efficacement.

Si l'on compare les vitesses de traitement des différentes approches sur un processeur Intel Xeon E5-2683 v3 (tableau 2.2), on observe des performances différentes. La vectorisation verticale peut donner une version plus lente que la version scalaire si elle est mal implémentée. La vectorisation verticale n'est pas adaptée à ce problème avec une accélération maximale de  $\times 1.6$ . La vectorisation horizontale en AoS permet d'atteindre une accélération de  $\times 2.0$ . À noter que le compilateur applique la vectorisation horizontale ici.

Dès lors que l'on passe en SoA, les performances augmentent avec une accélération de  $\times 3.99$ . Cette accélération est très proche de l'optimale pour du SSE ( $\times 4$  en simple précision).

#### 2.1.2 Cache

Une autre partie importante des processeurs est le cache [47]. Le cache permet d'accélérer les accès mémoires, lorsque ceux-ci sont réguliers. Son rôle devient crucial avec le SIMD en faisant persister les données au plus près du processeur, permettant ainsi d'avoir des débits soutenus élevés.

L'idée est la suivante : si un élément en mémoire est chargé, le cache va alors stocker cet élément, ainsi que des éléments spatialement proches (localité spatiale). Les éléments sont groupés en blocs appelés lignes de cache. Lorsqu'un des ces éléments est accédé à nouveau, il n'est pas nécessaire de lire la mémoire externe, et l'élément peut être lu directement depuis le cache qui possède un débit plus important et une latence plus faible. Si un élément en mémoire externe est accédé et qu'il n'y a plus d'emplacement libre pour cet élément, il faut alors vider une ligne de cache pour mettre le nouvel élément. La ligne de cache éliminée est généralement une ligne qui n'a pas été utilisée récemment. On garde ainsi les éléments accédés fréquemment en cache (localité temporelle).

TABLE 2.2 – Vitesse de traitement du calcul de barycentre en SSE4 simple précision (Intel Xeon E5-2683 v3)

| version            | AoS  | SoA  |

|--------------------|------|------|

| scalaire           | 2.67 | 2.67 |

| vectorisée         | 1.34 | 0.67 |

| SIMD vertical naïf | 3.17 | N/A  |

| SIMD vertical      | 1.67 | N/A  |

| SIMD horizontal    | 1.34 | 0.67 |

Vitesses de traitement en cycle/point

Les contraintes matérielles empêchent un cache d'être à la fois gros et rapide. C'est pourquoi les architectures actuelles utilisent une hiérarchie de caches permettant d'avoir des caches extrêmement rapides, tout en ayant également des caches de grosse tailles.

Voici une configuration de caches typique à 3 niveaux :

- L1i : entre 32 Ko et 64 Ko pour les instructions (le programme),

- L1d : entre 32 Ko et 64 Ko pour les données,

- L2 : entre 256 Ko et 1 Mo,

- L3 : entre 1 Mo et 4 Mo par cœur, partagé entre les cœurs.

Les processeurs avec beaucoup de cœurs peuvent ainsi avoir un cache L3 de plus de 64 Mo.

#### 2.1.2.1 Sortie de cache : taille des données

La mémoire externe et les différents caches ayant des bandes passantes différentes, la performance d'un programme dépend de la localisation des données utilisées. Si celles-ci sont dans le L1, le programme pourra accéder aux données beaucoup plus vite que si les données sont dans le L3 (voire en mémoire externe). C'est d'ailleurs l'intérêt premier des caches.

On dit que le cache est chaud lorsque les données qui vont être utilisées sont déjà en cache. Lorsque le cache est chaud, la localisation des données dépend seulement de leur taille. Si elles sont suffisamment petites pour tenir dans le L1, elles seront dans le L1.

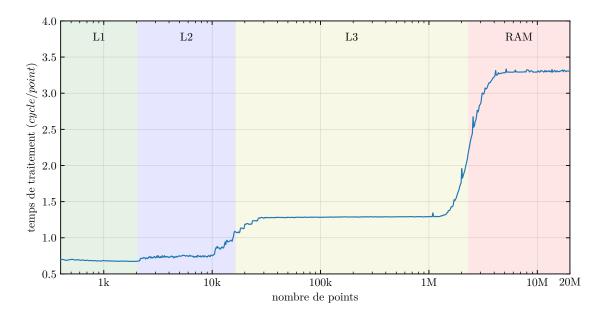

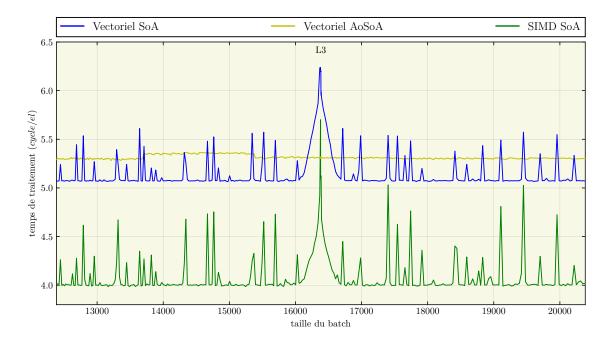

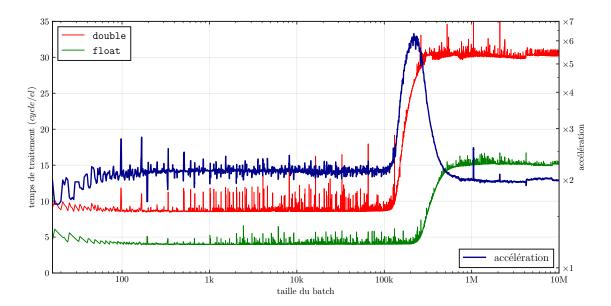

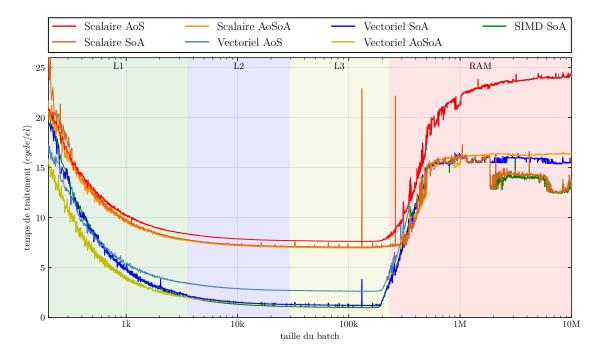

La performance d'un noyau de calcul en fonction de la taille des données avec un cache chaud permet de visualiser la performance d'un noyau de calcul lorsque les données sont en cache (figure 2.1). On peut alors voir des chutes de performance lorsque les données ne tiennent plus en cache (si le problème est memory bound). Ces chutes de performance sont des sorties de caches.

Pour éviter de sortir des caches, il est intéressant d'utiliser des objets plus petits. Par exemple, on peut utiliser des floats au lieu de doubles. L'ensemble des données prendra alors deux fois moins de place, il sera donc possible de traiter des problèmes plus gros tout en gardant les données en cache.

### 2.1.2.2 Évictions systématiques de cache : AoSoA

Le matériel a besoin d'une méthode de correspondance entre adresse en mémoire et position dans le cache. Il en existe principalement trois :

- correspondance directe: une adresse possède une unique position dans le cache,

- associativité complète : une adresse peux être localisée n'importe où dans le cache,

- associativité par ensembles : approche hybride, une adresse peut être localisée dans un unique ensemble de taille fixe.

FIGURE 2.1 – Calcul de barycentre en SoA simple précision : sorties de caches (Intel Xeon E5-2683 v3)

### Listing 2.8 Tableau de points (AoSoA)

```

const int K = /* typiquement la taille d'une ligne de cache */;

struct __Points {

float x[K], y[K], z[K];

float w[K];

};

typedef __Points* Points;

```

**Listing 2.9** Calcul de barycentre : scalaire (AoSoA)

```

Point center_of_mass(Points points, int n) {

Point center = \{0, 0, 0, 0\};

const int N = n / K;

// n doit être un multiple de K

for (int I = 0; I < N; I++) {

for (int i = 0; i < K; i++) {

center.x += points[I].w[i] * points[I].x[i];

center.y += points[I].w[i] * points[I].y[i];

center.z += points[I].w[i] * points[I].z[i];

center.w += points[I].w[i];

}

}

center.x /= center.w;

center.y /= center.w;

center.z /= center.w;

return center;

}

```

Les caches à associativité complète sont en pratique trop gros à implémenter pour des tailles supérieures à quelques Ko.

Les caches à correspondance directe sont les plus simple à implémenter et plus rapides. Du fait que chaque adresse a une unique position dans le cache, et que le cache est plus petit que la mémoire externe, il faut nécessairement que plusieurs adresses mémoires correspondent à une position dans le cache. Ainsi, le cache ne pourra contenir qu'une seule donnée correspondant à ces adresses conflictuelles : charger une de ces adresses supprimera automatiquement la donnée qui était présente. On parle d'évictions systématiques dans ce cas : peut importe l'usage du reste du cache, même "vide", si l'ancienne adresse est très souvent utilisée, la donnée sera évincée.

En pratique, la plupart des caches sont associatifs par ensemble. Un cache N-associatif disposera de plusieurs "ensembles" (set en anglais) pouvant contenir chacun jusqu'à N lignes. Il existe une correspondance directe entre adresse et ensemble, mais plusieurs adresses peuvent cohabiter au sein d'un même ensemble. Ce procédé ne résout pas le problème des évictions systématiques, mais l'atténue fortement en autorisant plusieurs adresses dans le même ensemble.

Afin de déterminer l'ensemble associé à une adresse, il est commun d'utiliser les bits de poids faibles de l'adresse comme position de l'ensemble. Dans une telle configuration, si plusieurs adresses partagent les mêmes bits de poids faibles, elles seront associées au même

ensemble. Ceci survient lorsque les adresses sont distantes d'une grande puissance de 2. S'il y a plus de données accédées que l'associativité du cache, on observera des évictions systématiques de cache. Celles-ci se traduisent par des chutes de performances localisées aux puissances de 2.

Si le noyau de calcul utilise plus de pointeurs ou de tableaux (références actives) que l'associativité du cache, le programme risque de subir des évictions systématiques de cache. Ce problème est fortement accentué avec le *multi-threading* où chaque *thread* possède ses propres références actives alors que le cache L3 est partagé entre les *threads*.

De par sa nature, l'agencement mémoire SoA requiert plusieurs références actives. Il est ainsi sensible à l'associativité du cache. En revanche, AoS n'ayant qu'une seule référence active, il n'a pas cette sensibilité.

Un agencement mémoire hybride est possible, permettant de conserver les avantages de SoA concernant la vectorisation tout en n'utilisant qu'une seule référence active comme AoS [48]. Un tel agencement est appelé AoSoA: il consiste en un tableau de "SoA". Pour garder une vectorisation facile et efficace, il faut que le nombre d'éléments en SoA soit un multiple de la taille du SIMD. Afin de ne pas tomber dans le même biais que SoA, il faut également peu d'éléments en SoA. Généralement, une ligne de cache par composante donne de bon résultats.

AoSoA est généralement plus performant, mais est plus difficile à manipuler de par sa nature à plusieurs étages. En effet, une boucle simple écrite en AoS ou en SoA devra être remplacée par deux boucles imbriquées. De plus, si le nombre d'éléments n'est pas un multiple de la taille des blocs SoA, il faut dupliquer le corps de boucle afin de gérer les derniers éléments. Une autre solution est de traiter tous les éléments du dernier bloc inconditionnellement. Les accès mémoires dans ce dernier ne sont pas problématiques car ce bloc est alloué entièrement quoiqu'il arrive. Il faut cependant que les données inutiles soient dans un état valide.

### 2.1.2.3 Agencements mémoire : récapitulatif

Nous avons vu trois agencements mémoire différents, avec chacun des propriétés différentes (figure 2.2): AoS, SoA et AoSoA.

AoS est le plus simple d'utilisation (en C). Il n'a qu'une seule référence active, et limite donc les évictions systématiques de cache. De plus, si des éléments du tableau n'ont pas besoin d'être chargés, ceux-ci ne pollueront pas le cache.

En revanche, les composantes non-utilisées des éléments pollueront le cache car à proximité des composantes utilisées. Si notre objet a plusieurs membres qui ne sont pas utilisés par la fonction, comme ceux-ci sont contigus en mémoire (sur la même ligne de

FIGURE 2.2 – Agencements mémoire : AoS, SoA, AoSoA

cache), ils seront également chargés bien qu'inutiles. Le cache sera donc rempli plus vite car une fraction non-négligeable des éléments qui sont en cache ne sera pas utilisée.

Cet agencement n'est pas adapté à la vectorisation horizontale, il sera donc plus difficile de tirer partie du SIMD.

SoA est un peu plus compliqué à utiliser en C, mais correspond à l'agencement mémoire par défaut en Fortran. Les composantes non-utilisées ne sont jamais mis en cache. Celles-ci sont physiquement éloignées des autres composantes et ne seront donc pas sur les même lignes de cache : ces éléments ne seront jamais chargés en cache. De plus, cet agencement mémoire est particulièrement adapté à la vectorisation horizontale.

Par contre, si tous les objets du tableau ne sont pas accédés, SoA va charger la composante de plusieurs objets en cache, même si certains objets ne seront jamais utilisés. En outre, SoA requiert plus de références actives (une par composante accédée) et est donc d'avantage sensible aux évictions systématiques de cache. Ce point est d'autant plus important avec l'utilisation du multithreading : plusieurs threads se partageront le même cache, et donc les ensembles associatifs de ce cache.

AoSoA est un agencement mémoire hybride combinant les caractéristiques du AoS et du SoA. Il consiste principalement en un tableau de blocs de taille fixe en SoA. Tout comme AoS, il ne requiert qu'une seule référence active et est donc peu sensible aux évictions systématiques de cache. Tout comme SoA, il est particulièrement adapté à la vectorisation horizontale, et permet donc de tirer pleinement partie du SIMD. De la même manière, les composantes non-utilisées ne polluent pas le cache.

Cependant, cet agencement mémoire est plus difficile à manipuler du fait de sa structure à deux niveaux. A l'instar de SoA, les éléments non-accédés peuvent polluer le cache.

Ainsi, AoSoA a les mêmes propriétés que SoA, excepté en ce qui concerne le nombre de références actives qui est réduit à 1 comme en AoS. Il est également plus difficile à écrire.

Listing 2.10 Exemple de scalarisation de la multiplication matrice-vecteur

```

(a) sans scalarisation

// Y += L * X

for (i = 0; i < N; i++) {

for (j = 0; j <= i; j++) {

for (j = 0; j < x[j];

}

}

Y[i] += L[i][j] * X[j];

}

Y[i] = y;

}</pre>

(b) avec scalarisation

// Y += L * X

for (i = 0; i < N; i++) {

float y = Y[i];

for (j = 0; j <= i; j++) {

y += L[i][j] * X[j];

}

Y[i] = y;

}

```

#### 2.1.3 Scalarisation

La scalarisation consiste à faire persister des données fréquemment utilisées dans des registres. Pour cela, on remplace les expressions avec des accès mémoires par des expressions entre variables, favorisant ainsi leur mise en registre.

La scalarisation peut être effectuée automatiquement par un compilateur optimisant [49], par un optimiseur source à source [50], ou manuellement.

Cette optimisation s'applique particulièrement bien après avoir déroulé complètement une boucle. En effet, une fois qu'une boucle est déroulée complètement, comme le compteur de boucle est devenue une constante, les accès indirects peuvent être calculés directement. On peut dès lors attribuer une variable locale à chaque emplacement mémoire. Les accès intermédiaires ou redondants ne seront donc plus nécessaires. On réduit ainsi fortement les accès mémoire. Cette approche est très similaire au blocage par registres.

Le principal problème de cette technique est l'augmentation drastique de l'utilisation de registres : la pression de registres est importante. Un compilateur risque fortement de générer du *spill code* s'il n'y a pas assez de registres disponibles. L'idée est que le *spill code* utilisera moins souvent et plus efficacement le cache que le code non-scalarisé.

### 2.1.4 Déroulage de boucle

Le déroulage de boucle est une transformation consistant à répéter le corps de boucle plusieurs fois. Cela peut avoir plusieurs avantages comme diminuer le coût du branchement ou permettre d'augmenter le nombre d'accumulateurs lors des réductions.

Il existe plusieurs types de déroulage de boucles, avec des avantages différents. Nous nous intéresserons à deux déroulages particuliers : le déroulage total (unwinding en anglais), et le déroulage avec entrelacement (unroll&jam en anglais).

Algorithme 2.1 Exemple de déroulage simple de boucle

```

(a) Boucle non déroulée

(b) Boucle déroulée d'un facteur 4

1 pour i = 0 : N faire

1 pour i = 0 : 4 : N faire

P_i \leftarrow A_i \cdot B_i

P_{i+0} \leftarrow A_{i+0} \cdot B_{i+0}

R_i \leftarrow \sqrt{P_i}

R_{i+0} \leftarrow \sqrt{P_{i+0}}

3

P_{i+1} \leftarrow A_{i+1} \cdot B_{i+1}

4

R_{i+1} \leftarrow \sqrt{P_{i+1}}

\mathbf{5}

P_{i+2} \leftarrow A_{i+2} \cdot B_{i+2}

R_{i+2} \leftarrow \sqrt{P_{i+2}}

6

7

P_{i+3} \leftarrow A_{i+3} \cdot B_{i+3}

8

R_{i+3} \leftarrow \sqrt{P_{i+3}}

```

Il existe également d'autres transformations de boucles. On notera ainsi les modèles polyhédriques [51] permettant de réorganiser automatiquement l'ordre des itérations sur des boucles imbriquées. De tels modèles sont déjà implémentés dans les compilateurs comme gcc [52,53].

### 2.1.4.1 Déroulage simple de boucle

Le déroulage simple consiste à répéter le corps de boucle plusieurs fois (algorithme 2.1). Ainsi, une itération de la nouvelle boucle sera équivalente à plusieurs itérations de la boucle d'origine.

#### 2.1.4.2 Dérouler-Entrelacer : unroll&jam

Les processeurs disposent d'un pipeline d'instructions : ils peuvent lancer une instruction avant que la précédente ne soit terminée, si celle-ci ne dépend pas du résultat de la précédente. Il faut donc différencier la latence d'une instruction de son débit. La latence définit le temps (en cycles) qu'il faut attendre avant que le résultat puisse être utilisé par une autre instruction. Le débit (throughput en anglais) définit la fréquence à laquelle une instruction peut être exécutée. Par exemple, sur Haswell, une addition flottante a une latence de 3 cycles, et un débit de 1 instr/cycle. Le débit d'une instruction dépend du nombre d'unités fonctionelles pouvant l'exécuter et peut donc être supérieur à 1. Ainsi, une multiplication flottante sur Haswell a un débit de 2 instr/cycle.

De plus, les processeurs peuvent exécuter effectivement plusieurs instructions par cycle tant que ces instructions sont indépendantes et utilisent des unités fonctionnelles différentes (processeurs superscalaires). Pour tirer partie de toute la puissance de tels processeurs, il

2. Optimisations 2.1. Architecture

Algorithme 2.2 Exemple de déroulage avec entrelacement (unroll&jam)

Ce type de déroulage est à comparer avec le déroulage simple (algorithme 2.1)

#### (a) Boucle non déroulée (b) Boucle déroulée-entrelacée d'un facteur 4 1 pour i = 0:4:N faire 1 pour i = 0 : N faire $\begin{array}{c|c} P_i \leftarrow A_i \cdot B_i \\ R_i \leftarrow \sqrt{P_i} \end{array}$ $P_{i+0} \leftarrow A_{i+0} \cdot B_{i+0}$ $P_{i+1} \leftarrow A_{i+1} \cdot B_{i+1}$ $P_{i+2} \leftarrow A_{i+2} \cdot B_{i+2}$ 4 $P_{i+3} \leftarrow A_{i+3} \cdot B_{i+3}$ $R_{i+0} \leftarrow \sqrt{P_{i+0}}$ 6 $R_{i+1} \leftarrow \sqrt{P_{i+1}}$ $R_{i+2} \leftarrow \sqrt{P_{i+2}}$ 7 8 $R_{i+3} \leftarrow \sqrt{P_{i+3}}$

faut donc que les instructions soient les plus indépendantes possibles, au moins localement. Pour atteindre ce but, les compilateurs réordonnent les instructions d'après le graphe de dépendance. La plupart des processeurs sont également capables de réordonner les instructions dans le même but. On parle d'exécution dans le désordre (*Out-of-Order execution* en anglais).

Toutefois, le réordonnancement d'instructions optimal est NP-difficile [54], et la fenêtre de réordonnancement des processeurs est "petite" : 192 entrées sur Haswell et Ryzen. De par l'utilisation d'heuristique et la visibilité limitée, l'ordre d'exécution est sous-optimal, et le sera d'autant plus que le le chemin critique sera long.

Dérouler-Entrelacer consiste à dérouler partiellement une boucle et à entrelacer les itérations : algorithme 2.2. Si les itérations sont indépendantes, les opérations entrelacées sont également indépendantes les unes des autres. On a donc un graphe de dépendance beaucoup plus large (plus de parallélisme).

Ainsi, on peut augmenter le débit d'instructions grâce à l'indépendance entre les instructions, chaque nouvelle instruction étant prête à être exécutée immédiatement. La performance de la boucle sera donc limitée par le débit des instructions et non leur latence. Cette optimisation est particulièrement intéressante si la latence des instructions est grande alors que leur débit est important : les instructions sont pipelinées. Plus le produit latence×débit des instructions sera haut, plus l'entrelacement sera intéressant. Il en est de même avec la longueur du chemin critique au sein d'une itération.

2. Optimisations 2.1. Architecture

#### 2.1.4.3 Déroulage total de boucle : loop unwinding

Le déroulage total consiste à prendre toutes les itérations d'une boucle, et les mettre à plat, les unes à la suite des autres. Il n'y a ainsi plus aucun branchement, et le compteur de boucle est maintenant une constante différente pour chaque "itération".

Ce déroulage n'est possible que si le nombre total d'itérations de la boucle est petit et connu à la compilation. Comme cela créé autant de copies du corps de boucle que d'itérations au total, il n'est pas conseillé de l'appliquer sur des boucles avec trop d'itérations.

Avec cette optimisation, il est possible de considérer le compteur de boucle comme une constante, et ainsi, de le propager pour réduire la complexité des calculs. Comme la propagation de constantes est une optimisation bien maîtrisée par les compilateurs, de très bons résultats sont obtenus lorsque ce déroulage est appliqué, soit à la main, soit directement par le compilateur.

Cela permet aussi d'éliminer tout branchement lié à la boucle. Ceci peut donner des gains importants sur des boucles imbriquées avec de petits corps de boucles (coût des branchements non-négligeables).

Après déroulage, comme toutes les adresses mémoires sont connues à la compilation (à un décalage près), il est facile d'appliquer la scalarisation. Ainsi, tous les accès mémoire intermédiaires seront supprimés, et seule une lecture unique des données d'entrée et une écriture unique des données de sorties seront nécessaires (listing 2.11). Ces deux transformations se combinent bien avec la fusion d'opérateurs, permettant d'éliminer encore plus d'accès mémoires [55].

2. Optimisations 2.1. Architecture

# Algorithme 2.3 Exemple de déroulage total de boucle (a) Boucle non déroulée

#### .,,

$$\begin{array}{c|c} \mathbf{1} \ \mathbf{pour} \ i = 0 : 3 \ \mathbf{faire} \\ \mathbf{2} \ \ \middle| \ \ P_i \leftarrow A_i \cdot B_i \\ \mathbf{3} \ \ \middle| \ \ R_i \leftarrow \sqrt{P_i} \end{array}$$

#### (b) Boucle totalement déroulée

$$\begin{array}{ccc}

\mathbf{1} & P_0 \leftarrow A_0 \cdot B_0 \\

\mathbf{2} & R_0 \leftarrow \sqrt{P_0} \\

\mathbf{3} & P_1 \leftarrow A_1 \cdot B_1 \\

\mathbf{4} & R_1 \leftarrow \sqrt{P_1} \\

\mathbf{5} & P_2 \leftarrow A_2 \cdot B_2 \\

\mathbf{6} & R_2 \leftarrow \sqrt{P_2} \\

\mathbf{7} & P_3 \leftarrow A_3 \cdot B_3 \\

\mathbf{8} & R_3 \leftarrow \sqrt{P_3}

\end{array}$$

Listing 2.11 Déroulage total du produit matrice triangulaire—vecteur avec scalarisation

```

(a) non déroulé

(b) déroulé et scalarisé

for (i = 0; i < 3; i++) {

// Chargement de X et Y

for (j = 0; j \le i; j++) {

float x0 = X[0], y0 = Y[0];

Y[i] += L[i][j] * X[j];

float x1 = X[1], y1 = Y[1];

}

float x2 = X[2], y2 = Y[2];

}

// Calcul

y0 += L[0][0] * x0;

y1 += L[1][0] * x0;

y1 += L[1][1] * x1;

y2 += L[2][0] * x0;

y2 += L[2][1] * x1;

y2 += L[2][2] * x2;

// Enregistrement de Y

Y[0] = y0;

Y[1] = y1;

Y[2] = y2;

```

#### 2.2 Précision des calculs

#### 2.2.1 Rappels sur le calcul flottant

Il est impossible pour un ordinateur de manipuler des nombres réels. Il faut donc recourir à une approximation des réels. L'approximation la plus utilisée par les ordinateurs est l'arithmétique flottante : [56, 57].

L'ensemble des flottants  $\mathbb{F}$  est un sous-ensemble fini des réels  $\mathbb{R}$ . Afin de représenter  $x \in \mathbb{R}$ , il faut trouver une approximation  $\hat{x} \in \mathbb{F}$  telle qu'il n'existe aucun flottant entre x et  $\hat{x}$ . Cette contrainte ne garantit pas l'unicité de l'approximation. Si  $x \notin \mathbb{F}$ , il y a 2 valeurs possibles. On peut ainsi définir un mode d'arrondi (une fonction  $\mathbb{R} \to \mathbb{F}$ ) respectant la propriété précédente, et permettant l'unicité de l'approximation. Pour chaque fonction  $\hat{f}: \mathbb{R} \to \mathbb{R}$ , il est possible de définir son approximation  $\hat{f}: \mathbb{F} \to \mathbb{F}$  telle que  $\forall \hat{a} \in \mathbb{F}, \hat{f}(\hat{a}) = \hat{f}(\hat{a})$ .

Une telle approximation ne peut cependant pas garantir  $\forall x \in \mathbb{R}, \hat{f}(\hat{x}) = \widehat{f(x)}$ : le résultat de la fonction approximante est la meilleure approximation possible uniquement si l'entrée n'est pas déjà une approximation  $(x = \hat{x})$ . Dans le cas contraire, il n'y a aucune garantie sur la qualité de l'approximation.

La norme IEEE 754 spécifie entièrement une telle arithmétique en définissant le format binaire, les opérations, leur précision... Cette norme définit 3 valeurs spéciales qui ne correspondent à aucun réel :  $\{-\infty, +\infty, \text{NaN}\} \subset \mathbb{F}$ . Elle définit également 4 modes d'arrondi : vers 0 (troncature), vers  $+\infty$ , vers  $-\infty$  et au plus près. Plusieurs précisions sont supportées : tableau 2.3.

Le terme français "précision" est ambigu et regroupe 2 notions distinctes. La précision des données représente la quantité d'information utilisée pour représenter la valeur (en anglais : precision), La précision de calcul désigne la proximité du résultat à la valeur réelle (en anglais : accuracy).

Par la suite, le terme "précision" sera utilisé pour désigner la précision des données, et le terme "exactitude" pour désigner la précision de calcul. L'exactitude en bits est donnée par la formule  $-\log_2\left(\frac{|\hat{x}-x|}{x}\right)$ . On peut également définir l'erreur en bits comme étant la

| Préci       | sion               | demi       | simple      | double       | étendue       | quad          |

|-------------|--------------------|------------|-------------|--------------|---------------|---------------|

| type C      | usuel              |            | float       | double       | long double   |               |

| précision ( | bits)<br>chiffres) | 11         | 24          | 53           | 64            | 113           |

| precision ( | chiffres)          | 3.3        | 7.2         | 15.9         | 19.3          | 34.0          |

|             |                    | $2^{15}$   | $2^{127}$   | $2^{1023}$   | $2^{16383}$   | $2^{16383}$   |

| exposant r  | naximum            | $10^{4.5}$ | $10^{38.2}$ | $10^{307.9}$ | $10^{4931.7}$ | $10^{4931.7}$ |

Table 2.3 – Précision des formats flottants IEEE 754

différence entre la précision et l'exactitude. Par ailleurs, l'erreur peut aussi s'exprimer en ulp avec la formule suivante :  $\frac{|\hat{x}-x|}{x} 2^p$  où p est la précision flottante.

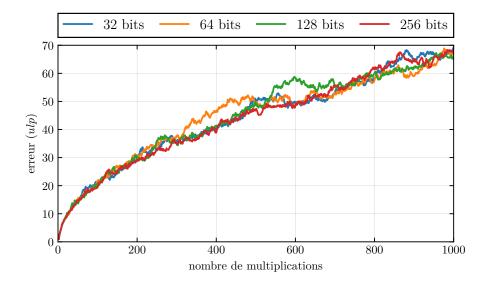

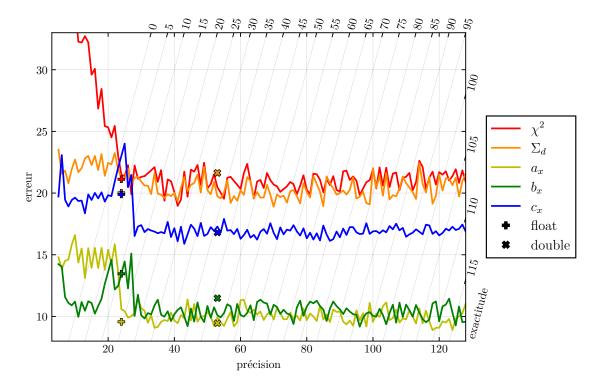

Analyser l'exactitude des résultats en fonction de la précision permet de relâcher les contraintes sur la précision à utiliser afin d'avoir des résultats corrects. Si un calcul en simple précision donne un résultat suffisamment correct (dépendant de l'application), alors il n'est pas nécessaire de recourir à une précision plus haute. On peut donc ainsi accélérer les calculs en utilisant des floats plutôt que des doubles. L'impact sera encore plus important si des flottants plus précis sont utilisés (tel que long double), ceux-ci n'étant pas supportés par les instructions SIMD des architectures actuelles.

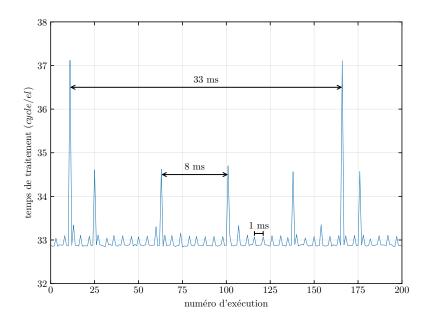

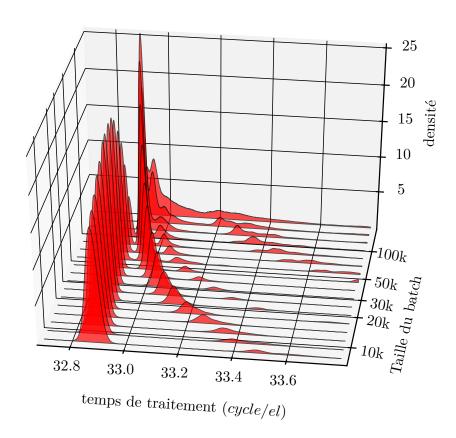

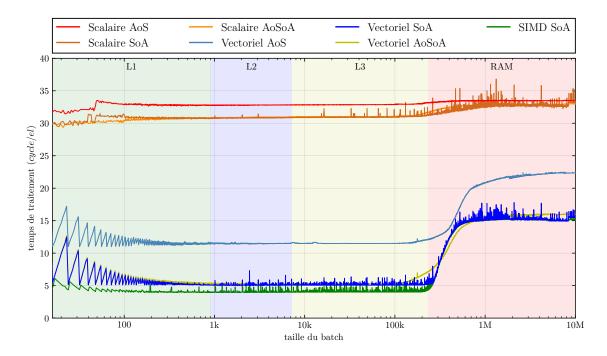

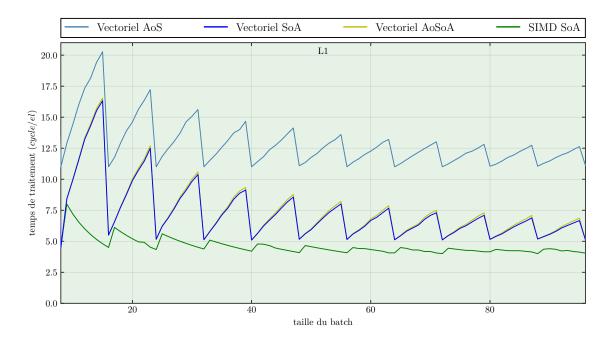

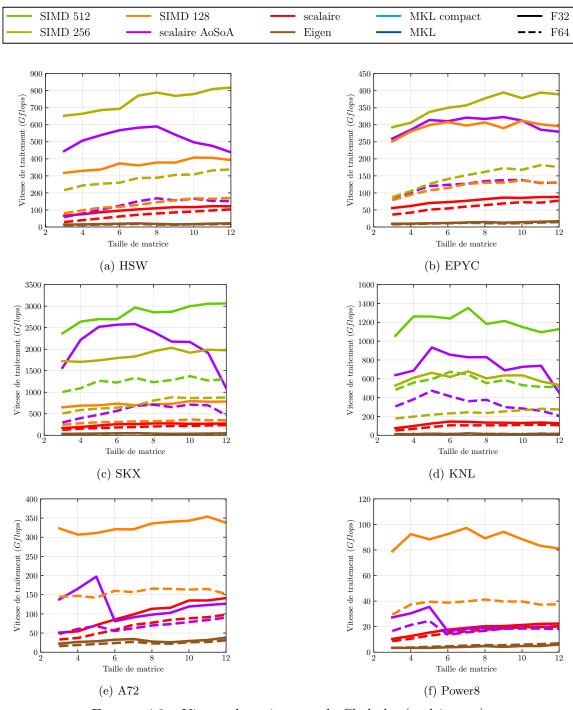

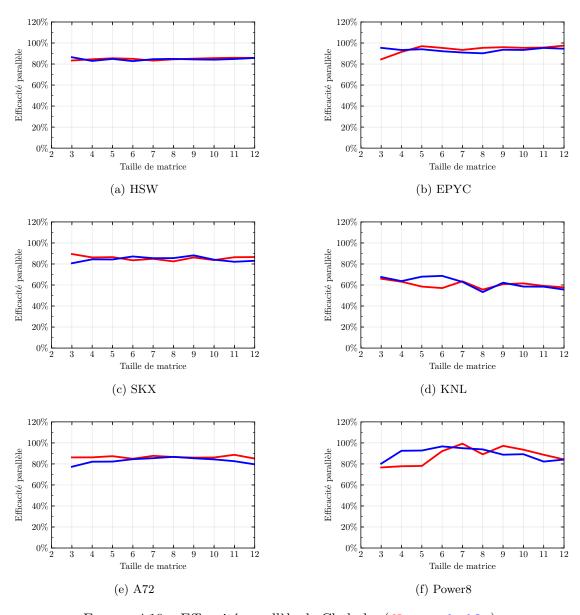

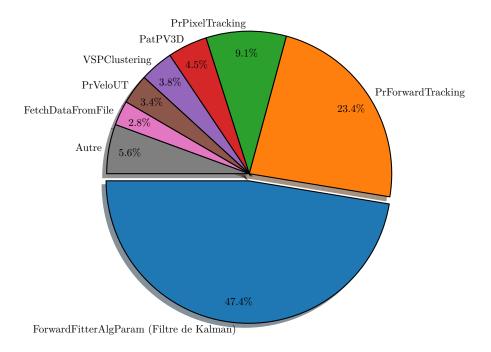

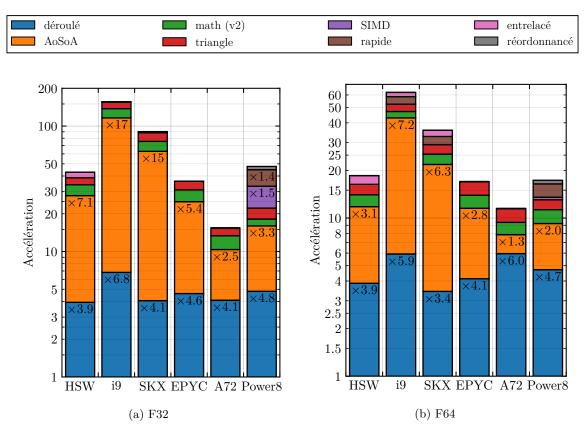

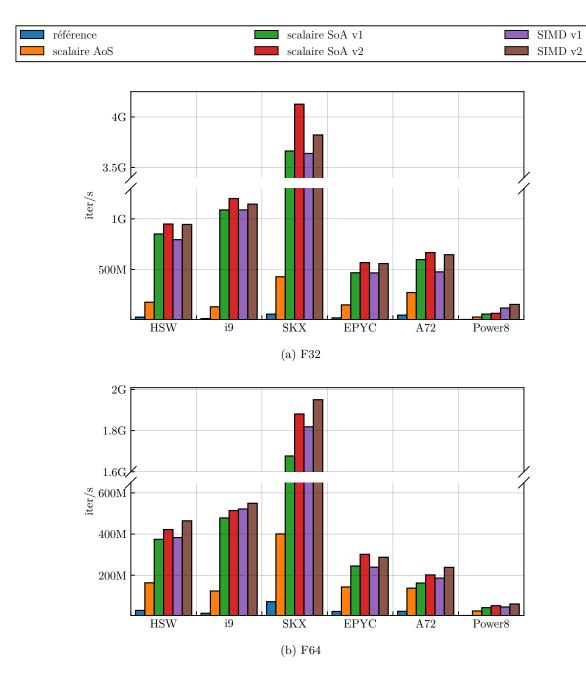

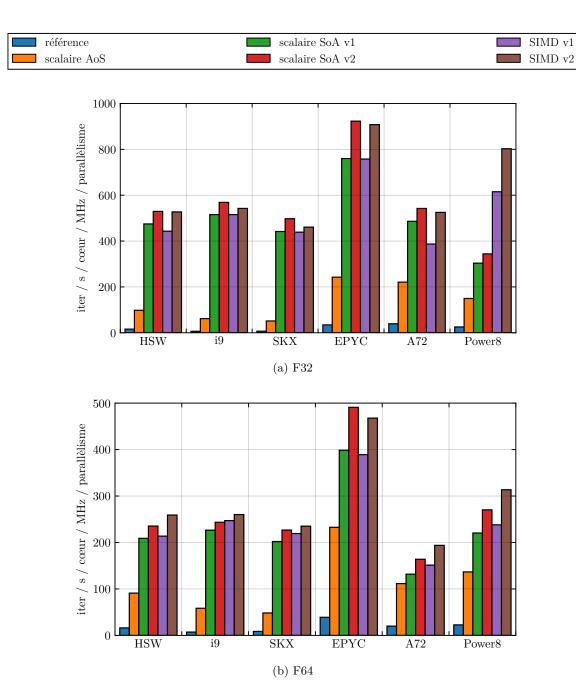

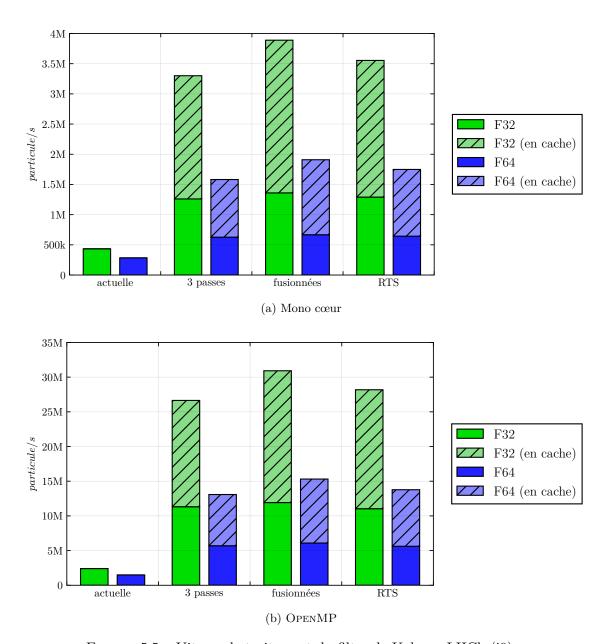

La question de la reproductibilité des résultats se pose également [58,59]. En effet, les compilateurs sont capables de faire des transformations qui changent les résultats flottants, mais n'auraient aucun effet en arithmétique réelle. Des options sont disponibles pour activer ou désactiver de telles transformations. Afin d'avoir un code plus rapide, il peut être intéressant d'assouplir les contraintes numériques : augmenter la capacité du compilateur à optimiser au détriment de la reproductibilité.