## Advanced speculation to increase the performance of superscalar processors

Kleovoulos Kalaitzidis

#### ▶ To cite this version:

Kleovoulos Kalaitzidis. Advanced speculation to increase the performance of superscalar processors. Performance [cs.PF]. Université Rennes 1, 2020. English. NNT: 2020REN1S007. tel-03033709

## HAL Id: tel-03033709 https://theses.hal.science/tel-03033709

Submitted on 1 Dec 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE

#### L'UNIVERSITÉ DE RENNES 1

ÉCOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Informatique

Par

#### « Kleovoulos KALAITZIDIS »

« Advanced Speculation to Increase the Performance of Superscalar Processors »

Thèse présentée et soutenue à Rennes, le 06 Mars 2020 Unité de recherche : Inria Rennes - Bretagne Atlantique Thèse N° :

#### Rapporteurs avant soutenance:

Pascal Sainrat Professeur, Université Paul Sabatier, Toulouse

Smail Niar Professeur, Université Polytechnique Hauts-de-France, Valenciennes

Composition du Jury :

Président : Sebastien Pillement Professeur, Université de Nantes

Examinateurs : Alain Ketterlin Maître de conférence, Université Louis Pasteur, Strasbourg

Angeliki Kritikakou Maître de conférence, Université de Rennes 1

Dir. de thèse : André Seznec Directeur de Recherche, Inria/IRISA Rennes

Computer theorists invent algorithms that solve important problems and analyze their asymptotic behavior (e.g. O(NlogN)). Computer architects set the constant factors for these algorithms.

Christos Kozyrakis

## TABLE OF CONTENTS

| Re  | sum   | é de Th | lèse                                            | 11 |

|-----|-------|---------|-------------------------------------------------|----|

| Int | trodu | ction   |                                                 | 17 |

| 1   | The   | Archite | ecture of a Modern General-Purpose Processor    | 25 |

|     | 1.1   | Funda   | mentals of Processor Architecture               | 25 |

|     |       | 1.1.1   | General Definition                              | 25 |

|     |       | 1.1.2   | Instruction Set Architecture - ISA              | 25 |

|     |       | 1.1.3   | Instruction Formats                             | 26 |

|     |       | 1.1.4   | Architectural State                             | 27 |

|     | 1.2   | Simple  | Pipelining                                      | 27 |

|     |       | 1.2.1   | Key Idea                                        | 27 |

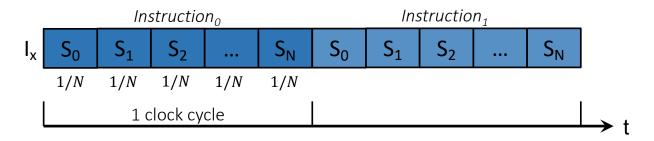

|     |       | 1.2.2   | Stage Breakdown                                 | 29 |

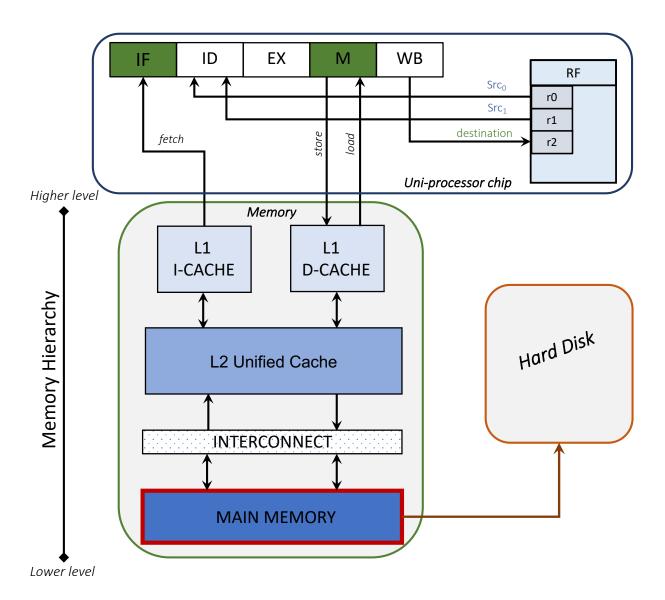

|     |       |         | 1.2.2.1 Instruction Fetch - IF                  | 30 |

|     |       |         | 1.2.2.2 Instruction Decode - ID                 | 30 |

|     |       |         | 1.2.2.3 Execution - EX                          | 30 |

|     |       |         | 1.2.2.4 Memory - M                              | 31 |

|     |       |         | 1.2.2.5 Write-back - WB                         | 32 |

|     |       | 1.2.3   | Limitations                                     | 33 |

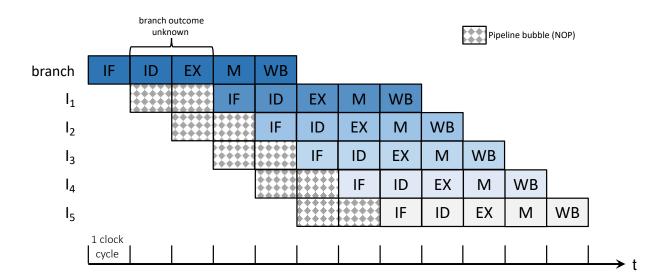

|     |       |         | 1.2.3.1 Control Hazards                         | 33 |

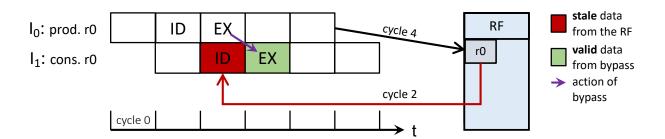

|     |       |         | 1.2.3.2 Data Hazards                            | 34 |

|     | 1.3   | Critica | I Pipelining Developments                       | 35 |

|     |       | 1.3.1   | Branch Prediction                               | 35 |

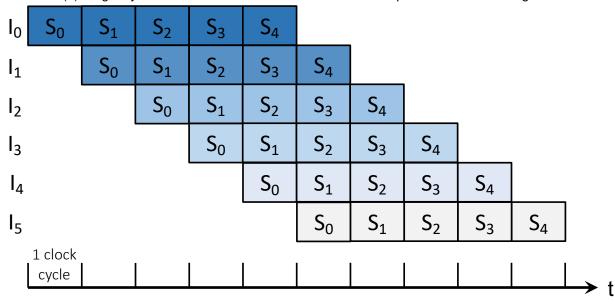

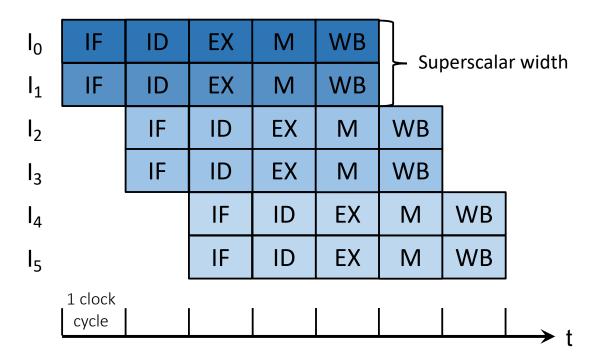

|     |       | 1.3.2   | Superscalar Pipelining                          | 35 |

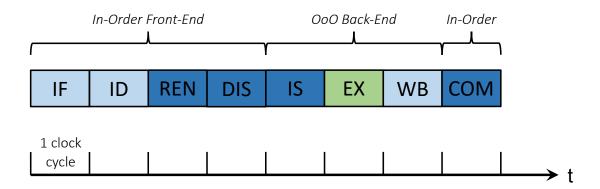

|     | 1.4   | Out-of  | -Order Execution                                | 37 |

|     |       | 1.4.1   | Basic Idea                                      | 37 |

|     |       | 1.4.2   | The In-Order Aspects of the Pipeline            | 38 |

|     |       |         | 1.4.2.1 Register Renaming - REN                 | 38 |

|     |       |         | 1.4.2.2 Instruction Dispatch & Commit - DIS/COM | 40 |

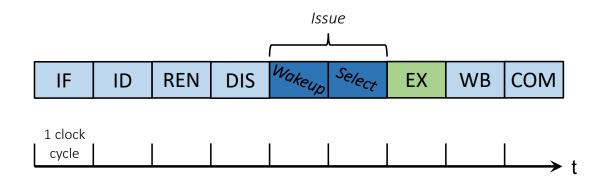

|     |       | 1.4.3   | The Out-Of-Order Execution Engine               | 40 |

|     |       |         | 1.4.3.1 Issue, Execute and Write-back           | 40 |

|     |       |         | 1.4.3.2 Manipulation of Memory Instructions     | 42 |

#### TABLE OF CONTENTS

|   |         | 1.4.4                                                                                    | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                                   |

|---|---------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 2 | Adv     | anced                                                                                    | Speculation in Out-Of-Order Superscalar Processors                                                                                                                                                                                                                                                                                                                                                                                                                               | 47                                                                   |

|   | 2.1     | Introd                                                                                   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47                                                                   |

|   | 2.2     | Value                                                                                    | Prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48                                                                   |

|   |         | 2.2.1                                                                                    | Key Idea                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48                                                                   |

|   |         | 2.2.2                                                                                    | Constant Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49                                                                   |

|   |         |                                                                                          | 2.2.2.1 Detection of Predictable Value Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49                                                                   |

|   |         |                                                                                          | 2.2.2.2 Increase of Coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                                   |

|   |         | 2.2.3                                                                                    | Principles of a Realistic Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                                                   |

|   |         | 2.2.4                                                                                    | Main Prediction Models                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52                                                                   |

|   |         |                                                                                          | 2.2.4.1 Context-Based Predictors                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52                                                                   |

|   |         |                                                                                          | 2.2.4.2 Computation-Based Predictors                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57                                                                   |

|   |         |                                                                                          | 2.2.4.3 Hybrid Predictors                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59                                                                   |

|   | 2.3     | Addre                                                                                    | ss Prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60                                                                   |

|   |         | 2.3.1                                                                                    | Overview of Possible Use Cases                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60                                                                   |

|   |         | 2.3.2                                                                                    | Data Speculation through Load-Address Prediction                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61                                                                   |

|   |         |                                                                                          | 2.3.2.1 Prediction Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61                                                                   |

|   |         |                                                                                          | 2.3.2.2 Critical Design Aspects                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 62                                                                   |

|   |         |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

| 2 | Oni     | the Inte                                                                                 | practions Potween Value Prediction and ISA Level Intrincies                                                                                                                                                                                                                                                                                                                                                                                                                      | 65                                                                   |

| 3 |         |                                                                                          | eractions Between Value Prediction and ISA-Level Intrinsics                                                                                                                                                                                                                                                                                                                                                                                                                      | 65                                                                   |

| 3 | 3.1     | Introd                                                                                   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                                   |

| 3 |         | Introd<br>Basic                                                                          | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65<br>66                                                             |

| 3 | 3.1     | Introd                                                                                   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65<br>66<br>66                                                       |

| 3 | 3.1     | Introd<br>Basic                                                                          | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65<br>66<br>66<br>67                                                 |

| 3 | 3.1     | Introd<br>Basic                                                                          | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65<br>66<br>67<br>67                                                 |

| 3 | 3.1     | Introde<br>Basic<br>3.2.1                                                                | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65<br>66<br>67<br>67<br>68                                           |

| 3 | 3.1     | Introd<br>Basic                                                                          | uction  ISA Properties Meaningful to Value Prediction  x86_64  3.2.1.1 Primary Data Types of Operations  3.2.1.2 Basic Program Execution Registers  3.2.1.3 Instruction Classes  Aarch64                                                                                                                                                                                                                                                                                         | 65<br>66<br>67<br>67<br>68<br>70                                     |

| 3 | 3.1     | Introde<br>Basic<br>3.2.1                                                                | uction  ISA Properties Meaningful to Value Prediction  x86_64  3.2.1.1 Primary Data Types of Operations  3.2.1.2 Basic Program Execution Registers  3.2.1.3 Instruction Classes  Aarch64  3.2.2.1 Supported Data Types                                                                                                                                                                                                                                                           | 65<br>66<br>67<br>67<br>68<br>70<br>71                               |

| 3 | 3.1 3.2 | Introde<br>Basic<br>3.2.1                                                                | uction  ISA Properties Meaningful to Value Prediction  x86_64  3.2.1.1 Primary Data Types of Operations  3.2.1.2 Basic Program Execution Registers  3.2.1.3 Instruction Classes  Aarch64  3.2.2.1 Supported Data Types  3.2.2.2 Register & Instruction Classes                                                                                                                                                                                                                   | 65<br>66<br>67<br>67<br>68<br>70<br>71                               |

| 3 | 3.1     | Introde<br>Basic<br>3.2.1<br>3.2.2                                                       | uction  ISA Properties Meaningful to Value Prediction  x86_64  3.2.1.1 Primary Data Types of Operations  3.2.1.2 Basic Program Execution Registers  3.2.1.3 Instruction Classes  Aarch64  3.2.2.1 Supported Data Types  3.2.2.2 Register & Instruction Classes  Prediction in the Studied ISAs                                                                                                                                                                                   | 65<br>66<br>67<br>67<br>68<br>70<br>71<br>71                         |

| 3 | 3.1 3.2 | Introde<br>Basic<br>3.2.1<br>3.2.2<br>Value<br>3.3.1                                     | ISA Properties Meaningful to Value Prediction  x86_64  3.2.1.1 Primary Data Types of Operations  3.2.1.2 Basic Program Execution Registers  3.2.1.3 Instruction Classes  Aarch64  3.2.2.1 Supported Data Types  3.2.2.2 Register & Instruction Classes  Prediction in the Studied ISAs  ISA-aware Definition of Value-Predictable Instructions                                                                                                                                   | 65<br>66<br>67<br>67<br>68<br>70<br>71<br>71<br>73                   |

| 3 | 3.1 3.2 | Introde<br>Basic<br>3.2.1<br>3.2.2<br>Value<br>3.3.1<br>3.3.2                            | ISA Properties Meaningful to Value Prediction  x86_64  3.2.1.1 Primary Data Types of Operations  3.2.1.2 Basic Program Execution Registers  3.2.1.3 Instruction Classes  Aarch64  3.2.2.1 Supported Data Types  3.2.2.2 Register & Instruction Classes  Prediction in the Studied ISAs  ISA-aware Definition of Value-Predictable Instructions  Deriving Flags from Predicted Results                                                                                            | 65<br>66<br>67<br>67<br>68<br>70<br>71<br>71<br>73<br>74             |

| 3 | 3.1 3.2 | Introde<br>Basic<br>3.2.1<br>3.2.2<br>Value<br>3.3.1<br>3.3.2<br>3.3.3                   | ISA Properties Meaningful to Value Prediction  x86_64  3.2.1.1 Primary Data Types of Operations  3.2.1.2 Basic Program Execution Registers  3.2.1.3 Instruction Classes  Aarch64  3.2.2.1 Supported Data Types  3.2.2.2 Register & Instruction Classes  Prediction in the Studied ISAs  ISA-aware Definition of Value-Predictable Instructions  Deriving Flags from Predicted Results  Arbitration on Instructions with Multiple Destination Registers                           | 65<br>66<br>67<br>67<br>68<br>70<br>71<br>71<br>73<br>74<br>75       |

| 3 | 3.1 3.2 | Introde<br>Basic<br>3.2.1<br>3.2.2<br>Value<br>3.3.1<br>3.3.2<br>3.3.3<br>Exper          | ISA Properties Meaningful to Value Prediction  x86_64  3.2.1.1 Primary Data Types of Operations  3.2.1.2 Basic Program Execution Registers  3.2.1.3 Instruction Classes  Aarch64  3.2.2.1 Supported Data Types  3.2.2.2 Register & Instruction Classes  Prediction in the Studied ISAs  ISA-aware Definition of Value-Predictable Instructions  Deriving Flags from Predicted Results  Arbitration on Instructions with Multiple Destination Registers  imental Setup            | 65<br>66<br>67<br>67<br>68<br>70<br>71<br>71<br>73<br>74<br>75<br>75 |

| 3 | 3.1 3.2 | Introde<br>Basic<br>3.2.1<br>3.2.2<br>Value<br>3.3.1<br>3.3.2<br>3.3.3<br>Exper<br>3.4.1 | ISA Properties Meaningful to Value Prediction  x86_64  3.2.1.1 Primary Data Types of Operations  3.2.1.2 Basic Program Execution Registers  3.2.1.3 Instruction Classes  Aarch64  3.2.2.1 Supported Data Types  3.2.2.2 Register & Instruction Classes  Prediction in the Studied ISAs  ISA-aware Definition of Value-Predictable Instructions  Deriving Flags from Predicted Results  Arbitration on Instructions with Multiple Destination Registers  imental Setup  Simulator | 65<br>66<br>67<br>67<br>68<br>70<br>71<br>71<br>73<br>74<br>75<br>76 |

| 3 | 3.1 3.2 | Introde<br>Basic<br>3.2.1<br>3.2.2<br>Value<br>3.3.1<br>3.3.2<br>3.3.3<br>Exper          | ISA Properties Meaningful to Value Prediction  x86_64  3.2.1.1 Primary Data Types of Operations  3.2.1.2 Basic Program Execution Registers  3.2.1.3 Instruction Classes  Aarch64  3.2.2.1 Supported Data Types  3.2.2.2 Register & Instruction Classes  Prediction in the Studied ISAs  ISA-aware Definition of Value-Predictable Instructions  Deriving Flags from Predicted Results  Arbitration on Instructions with Multiple Destination Registers  imental Setup            | 65<br>66<br>67<br>67<br>68<br>70<br>71<br>71<br>73<br>74<br>75<br>75 |

|   |       | •                                                                          | 78 |

|---|-------|----------------------------------------------------------------------------|----|

|   |       | 3.4.2.3 Simulating Fully Derivation of Flags                               | 79 |

|   |       | 3.4.3 Benchmark Slicing for Inter-ISA Comparable Simulations               | 79 |

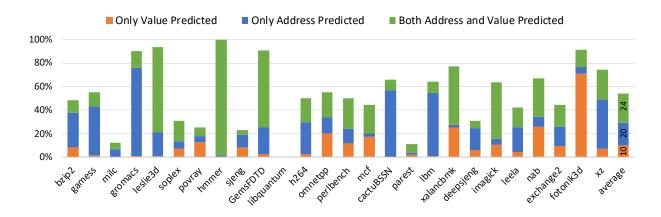

|   | 3.5   | Simulation Results                                                         | 31 |

|   |       | 3.5.1 ISA Effect on Value Predictability                                   | 31 |

|   |       | 3.5.2 Analysis of Value-Prediction Impact per ISA                          | 33 |

|   |       | 3.5.3 Influence of Vector Optimizations                                    | 36 |

|   | 3.6   | Conclusion                                                                 | 37 |

| 4 | Intro | oducing the Binary Facet of Value Prediction: VSEP                         | 39 |

|   | 4.1   | Introduction & Motivations                                                 | 39 |

|   | 4.2   | Value Speculation through Equality Prediction - VSEP                       | 91 |

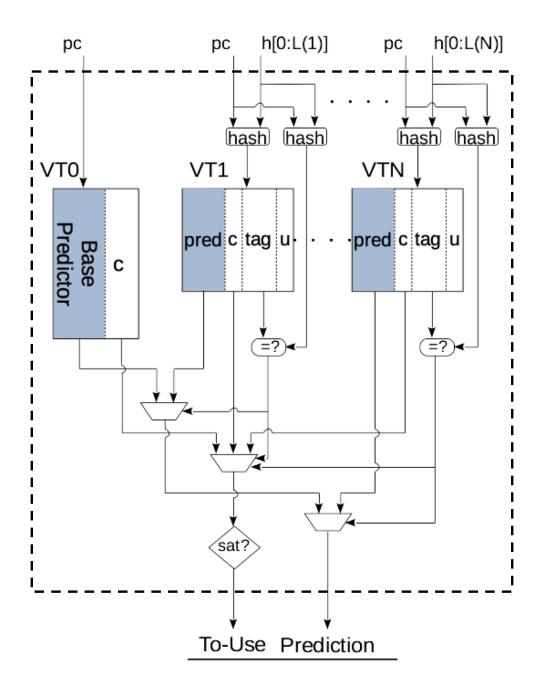

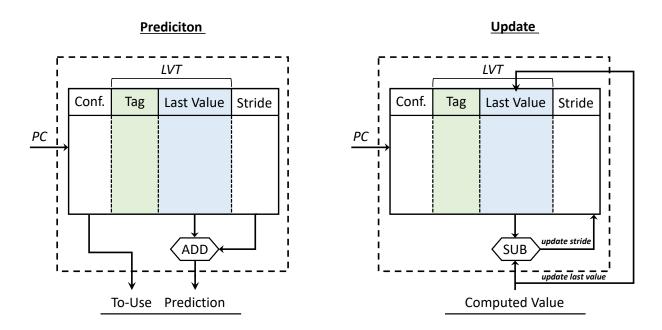

|   |       | 4.2.1 Value Prediction using ETAGE                                         | 92 |

|   |       | 4.2.1.1 Prediction                                                         | 92 |

|   |       | 4.2.1.2 Training                                                           | 92 |

|   |       | 4.2.1.3 Pipeline Details                                                   | 93 |

|   |       | 4.2.2 Dissecting the Prediction scenario of VSEP                           | 94 |

|   | 4.3   | Evaluation Methodology                                                     | 96 |

|   |       | 4.3.1 Examined Predictors                                                  | 96 |

|   |       | 4.3.2 Benchmarks                                                           | 96 |

|   |       | 4.3.3 Simulator                                                            | 97 |

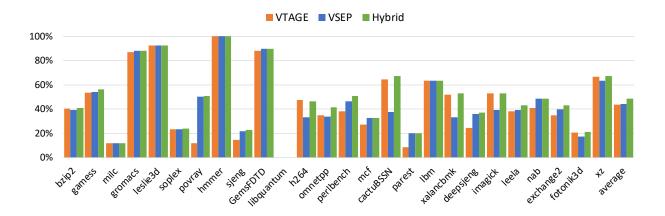

|   | 4.4   | Experimental Results and Analysis                                          | 98 |

|   |       | 4.4.1 VSEP vs VTAGE and LVP                                                | 98 |

|   |       | 4.4.1.1 Performance Analysis                                               | 98 |

|   |       | 4.4.1.2 Coverage Analysis                                                  | 01 |

|   |       | 4.4.2 Combining VSEP with VTAGE                                            | 03 |

|   | 4.5   | Conclusion                                                                 | 04 |

| 5 | Red   | lucing Load Execution Latency Radically through Load Address Prediction 10 | )7 |

|   | 5.1   | Introduction & Motivations                                                 | 07 |

|   | 5.2   | Using the Hybrid VSEP/VTAGE for Load-Address Prediction                    | 09 |

|   | 5.3   | The Use Case of Load-Address Prediction                                    |    |

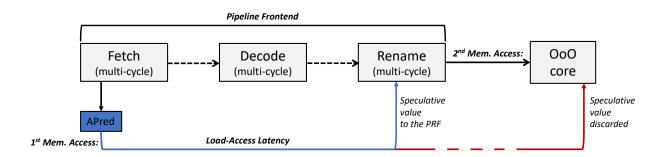

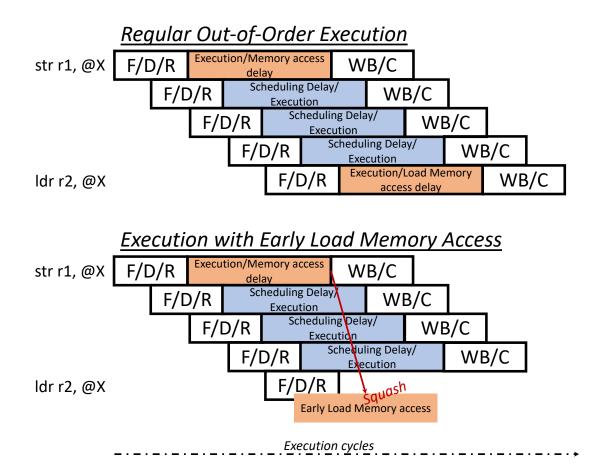

|   | 5.4   | LAPELE: Load-Address Prediction for Early Load Execution                   | 11 |

|   |       | 5.4.1 The Anatomy of Early Load Execution                                  | 11 |

|   |       | 5.4.1.1 Speculative Memory Accesses                                        |    |

|   |       | 5.4.1.2 Late Address Generation & Execution Validation                     |    |

|   |       | 5.4.2 Memory-Order Issues                                                  |    |

|   |       | 5.4.2.1 Ordering Limitations in Early Load Execution 1:                    | 14 |

#### TABLE OF CONTENTS

|         |                         | 5.4.2.2 Early-style Memory Dependence Speculation           | 114 |  |

|---------|-------------------------|-------------------------------------------------------------|-----|--|

|         |                         | 5.4.2.3 Guarantee of Memory Disambiguation                  | 117 |  |

|         | 5.4.3                   | Cache-port Contention                                       | 118 |  |

|         | 5.4.4                   | The Early Memory Access Engine                              | 118 |  |

|         |                         | 5.4.4.1 Transmission of Early Memory Requests               | 118 |  |

|         |                         | 5.4.4.2 Propagation of Speculative Values                   | 119 |  |

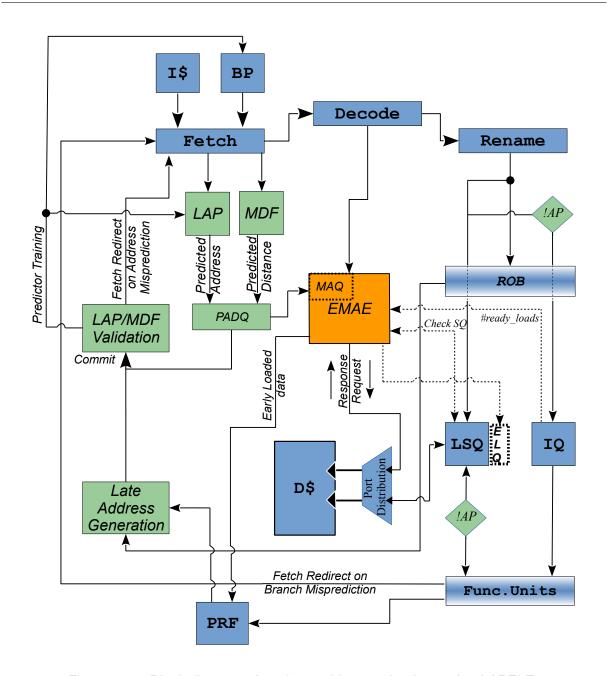

| 5.5     | Microa                  | rchitectural Overview                                       | 120 |  |

| 5.6     | Evalua                  | ation Methodology                                           | 122 |  |

|         | 5.6.1                   | Simulator                                                   | 122 |  |

|         | 5.6.2                   | Benchmarks                                                  | 122 |  |

| 5.7     | Experi                  | mental Results and Analysis                                 | 122 |  |

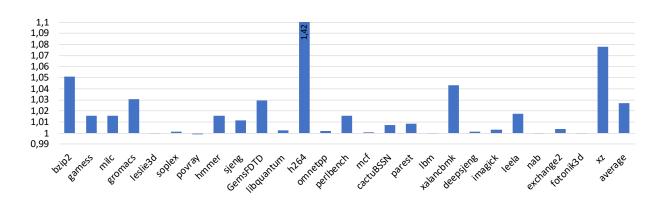

|         | 5.7.1                   | Performance Analysis                                        |     |  |

|         |                         | 5.7.1.1 Speedup                                             |     |  |

|         |                         | 5.7.1.2 Memory Order Violations                             | 124 |  |

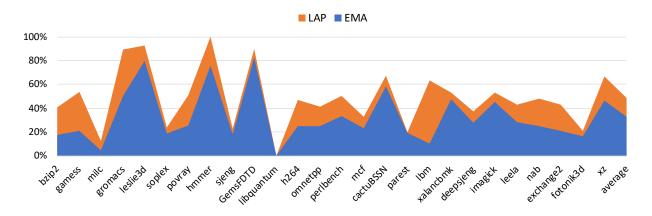

|         |                         | 5.7.1.3 Existing Potential and Limitations                  |     |  |

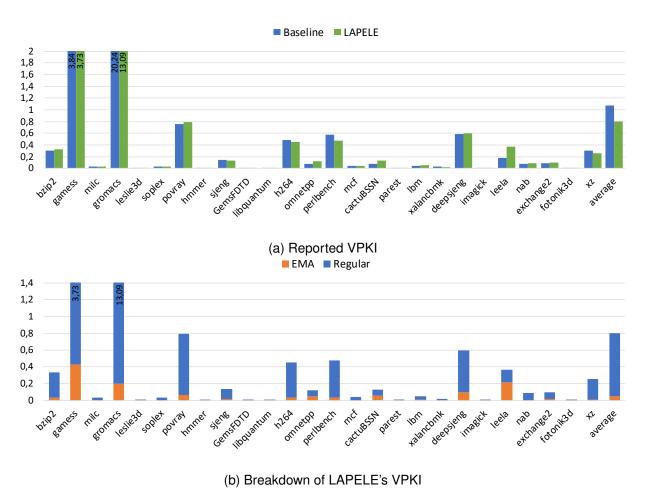

|         | 5.7.2                   |                                                             |     |  |

|         |                         | 5.7.2.1 Load-Address vs Load-Value Validation               |     |  |

|         |                         | 5.7.2.2 Early Load Execution vs Prediction of Loaded Values |     |  |

| 5.8     | Concl                   | usion                                                       | 130 |  |

| Conclu  | sion                    |                                                             | 133 |  |

| Bibliog | raphy                   |                                                             | 137 |  |

| List of | Figures                 | •                                                           | 145 |  |

| List of | ist of Publications 147 |                                                             |     |  |

## RESUMÉ DE THÈSE

À l'ère moderne de la numérisation, où presque tout est traité par les ordinateurs, les exigences de calcul sont croissantes. Aussi les processeurs doivent continuer à augmenter leurs performances, quelle que soit la complexité de la conception. Ainsi, même si les processeurs polyvalents modernes offrent déjà des performances élevées, il y a un besoin constant d'amélioration, en termes de latence d'exécution et de consommation énergétique. En réalité, ceux-ci représentent les deux défis constants de l'architecture de processeur.

À cette fin, les concepteurs de circuits, qui agissent au niveau du transistor, tentent de fournir des optimisations qui visent généralement à raccourcir le chemin critique électrique pour une transmission plus rapide des informations. D'un autre côté, les architectes de processeurs opèrent à un niveau supérieur qui est toujours proche du circuit des portes logiques. La responsabilité d'un architecte est de définir l'organisation du processeur, qui comprend la description de chacun de ses composants. Afin d'atteindre ces objectifs de performance, les architectes peuvent concevoir de nouveaux composants, en supprimer d'autres des modèles traditionnels ou modifier leurs fonctionnalités et leurs connexions, tout en garantissant l'orchestration efficace de toutes les différentes unités de traitement entre elles. Cependant, ils doivent toujours être conscients de la technologie actuelle des circuits, afin de fournir des solutions terre-à-terre, c'est-à-dire des conceptions qui peuvent être mises en œuvre sur du vrai silicium. En d'autres termes, les architectes informatique pourraient être considérés comme des architectes traditionnels qui dessinent leurs conceptions en respectant l'état de l'art des techniques de constructions, afin que les fabricants (c'est-à-dire les concepteurs de circuits) puissent les réaliser dans la pratique.

Depuis l'introduction du tout premier processeur informatique largement utilisé, l'Intel 8080 en 1974 [74], les fabricants de matériel tentent traditionnellement de placer de plus en plus de transistors sur une surface finie de silicium. En particulier, les processeurs généralistes actuels comportent des centaines de millions à des milliards de transistors. De manière évidente, plus de transistors (blocs de construction du processeur) signifie plus d'unités disponibles pour le traitement des instructions du programme et peut naturellement conduire à une vitesse de traitement plus élevée. Le nombre croissant de transistors dans les processeurs avait été empiriquement observé par *la loi de Moore*, qui déclarait que "*le nombre de transistors sur une puce doublerait tous les 2 ans*" [Moo98]. Cela signifie qu'environ tous les 24 mois, un transistor ne prendrait plus que la moitié de sa taille actuelle, de sorte que le double du nombre de transistors pourrait tenir dans une puce de taille égale. Bien qu'elle ne soit pas une loi au sens

mathématique, la loi de Moore s'est révélée être un indicateur assez précis de cette tendance depuis plus de 40 ans. Cependant, depuis 2001 environ, le passage à l'échelle de la technologie a ralenti alors que la miniaturisation des transistors atteint ses limites et la courbe de la loi de Moore est désormais difficile à suivre.

De plus, comme des processeurs de plus en plus complexes sont conçus et fabriqués selon des tolérances de l'ordre du nanomètre, les performances des processeurs ont augmenté en raison de l'escalade de la vitesse d'horloge. L'horloge d'un processeur se déclenche périodiquement et définit le temps minimum nécessaire pour terminer une étape de calcul particulière. Ainsi, en augmentant la fréquence d'horloge, plus de tâches peuvent être accomplies dans un certain intervalle de temps. La fréquence d'horloge est liée à la vitesse à laquelle les transistors d'un circuit peuvent être activés et désactivés de manière fiable. Au fur et à mesure que les transistors rétrécissaient, leur vitesse de commutation augmentait suivant une loi inverse, permettant l'émergence de processeurs à hautes fréquences, allant aujourd'hui de 2 GHz à 5 GHz. Pourtant, la fréquence des CPU est intrinsèquement limitée par les contraintes de puissance crête de la puce, êgalement connue sous le nom de Power Wall [Bos11]. En conséquence, les vitesses d'horloge ont stagné pendant plus d'une décennie car, il semblerait qu'une augmentation spectaculaire de la fréquence peut nécessiter un changement dans les lois de la physique.

Néanmoins, le grand nombre de transistors dans les processeurs a permis l'émergence de nouvelles méthodes de conception, telles que le pipeline, l'exécution superscalaire et l'exécution dans le désordre [AA93], qui ont montré que les performances des processeurs peuvent augmenter même si la fréquence d'horloge atteint un plateau. Ces techniques améliorent les performances des processeurs monocœurs, c'est-à-dire les performances séquentielles, en parallélisant l'exécution des instructions, une caractéristique qui est généralement appelée parallélisme d'instructions ou ILP (Instruction Level Parallelism). Bien que ces mécanismes aient été l'épine dorsale de l'architecture des processeurs jusqu'à aujourd'hui, il était devenu très difficile de continuer à augmenter les performances séquentielles au même rythme que l'augmentation du nombre de transistors. Par conséquent, afin de soutenir l'augmentation des performances, les concepteurs de puces et les fabricants ont adopté le principe de "diviser pour mieux régner", en passant progressivement à la mise en œuvre de puces multiprocesseurs ou multicœurs. En 2001, IBM a introduit POWER4 [War+02], la première puce multiprocesseur disponible dans le commerce qui comprenait 2 cœurs sur une seule puce, suivie par le Pentium D d'Intel et l'Athlon 64 x2 d'AMD vers 2005 [Man+06; Lu +07]. Aujourd'hui, le calcul haute performance est essentiellement dominé par des processeurs multicœurs composés de 2, 4, 8 cœurs ou plus.

Dans un processeur multicœur, l'exécution globale d'un programme peut être accélérée en le divisant en plusieurs programmes plus petits qui sont exécutés simultanément dans différents cœurs. Cette "mentalité de serveur" améliore les performances en termes de débit

(c'est-à-dire que plus de travail peut être traité dans une unité de temps donnée), contrairement aux monoprocesseurs qui ciblent la latence d'exécution (c'est-à-dire l'achèvement plus rapide d'une tâche particulière). Pourtant, les performances d'un processeur multicœur sont limitées par la nature du programme, car le calcul parallèle ne peut pas s'appliquer aux composants algorithmiques qui doivent être traités séquentiellement. En d'autres termes, certains programmes sont intrinsèquement séquentiels et ne peuvent pas du tout être parallélisés, tandis que d'autres peuvent posséder de longues parties séquentielles et ne peuvent être que partiellement parallèles. Finalement, comme le suggère la loi d'Amdahl [Amd67], le gain de performance qui peut être obtenu en parallélisant un programme est régi par ses aspects séquentiels. En d'autres termes, si l'on pouvait séparer un programme en ses parties parallèle et séquentielle, alors, en supposant un nombre infini de cœurs qui exécutent simultanément la fraction parallèle, l'accélération totale serait limitée par l'exécution des éléments séquentiels. Par exemple, si une application a besoin de 4 heures de calcul et que seulement 2 d'entre elles peuvent être parallélisées, le temps d'exécution final peut être réduit au maximum d'un facteur 2. Par conséquent, même à l'ère multicœur, rendre les cœurs plus rapides dans un contexte monocœur est primordial pour obtenir de hautes performances de calculs [HM08].

Les cœurs de processeur haute performance actuels utilisent des techniques de nature spéculative qui s'appuient sur des observations empiriques sur le comportement des programmes afin de devenir "plus intelligents" à l'exécution du programme. La principale observation qui motive à utiliser ces techniques est que les programmes ordinaires, pour la plupart, ne se comportent pas de manière aléatoire. Ils ont plutôt tendance à présenter une certaine régularité dans le flux d'instructions et dans les résultats de leurs opérations. Ainsi, en isolant ces comportements récurrents de programme, il est possible de concevoir des automates capables de deviner des informations d'exécution liées au programme. Ces aspects peuvent être mieux compris en considérant deux techniques de spéculation largement utilisées qui sont renforcées par le comportement des programmes: la prédiction de branchement et la prédiction de dépendances mémoire. La prédiction de branchement exploite la régularité trouvée dans les chemins de flux de contrôle que les programmes ont tendance à suivre, tandis que la prédiction de dépendances mémoire repose sur la régularité trouvée dans les interactions entre les instructions de lecture mémoire et de stockage. Ces deux techniques sont utilisées par pratiquement tous les cœurs haute performance modernes pour faciliter le flux d'instructions dans le cœur (c'est-à-dire la récupération ou fetch et la planification ou scheduling) et, par conséquent, augmenter les performances séquentielles.

Un autre niveau de spéculation plus avancé exploite la régularité sous-jacente des données brutes produites par les programmes ou des adresses mémoire d'où proviennent des données particulières. Deux techniques principales de ce type sont *la prédiction de valeur* (VP pour value prediction) et *la prédiction d'adresse des lectures mémoire* (LAP pour load-address

prediction). VP et LAP sont deux techniques en développement et très prometteuses de spéculation de données, dans le sens où elles offrent encore beaucoup de potentiel pour l'exploration et l'optimisation.

VP rompt les véritables dépendances de données entre les instructions en permettant aux "consommateurs" de lancer leur exécution de manière spéculative avant que leurs "producteurs" respectifs ne soient exécutés. VP est permis par le fait que différentes instances dynamiques de la même instruction statique produisent des résultats qui suivent souvent un modèle prédictible. Par conséquent, une structure matérielle peut être utilisée pour suivre ces instructions et prédire leur résultat. Lorsqu'une instruction est prédite, celles qui en dépendent peuvent s'exécuter simultanément en utilisant la valeur prédite sans avoir à se bloquer. Ainsi, lorsqu'une prédiction est correcte, le temps d'exécution total diminue. Dans le cas contraire, certaines actions de récupération doivent être mise en place pour garantir la ré-exécution des instructions dépendantes avec la bonne entrée. L'essentiel est que les performances séquentielles augmentent à mesure que le processeur peut extraire plus d'*ILP*.

LAP est assez similaire à VP; plutôt que de prédire les résultats des lectures mémoire, les mécanismes LAP prédisent les adresses mémoire à partir desquelles les instructions de lecture mémoire récupèrent leurs données. Ces mécanismes sont basés sur l'observation que les adresses des lectures mémoire peuvent également tomber dans des modèles prédictibles. La prédiction de l'adresse mémoire d'un lecture mémoire permet d'anticiper l'accès aux données chargées et de générer une valeur spéculative pour cette lecture mémoire. Cette valeur n'est pas nécessairement prédictible par un mécanisme VP. Comme dans VP, les valeurs spéculatives des lectures mémoire sont propagées aux instructions dépendantes et leur permettent de s'exécuter en avance. En tant que tel, LAP initie une forme similaire d'exécution spéculative basée sur les données et nécessite aussi une validation.

Dans l'ensemble, ces deux techniques de spéculation visent à augmenter l'*ILP* et à réduire la latence d'exécution des instructions dans le cœur. En partageant les mêmes objectifs, nous apportons dans cette thèse les principales contributions suivantes.

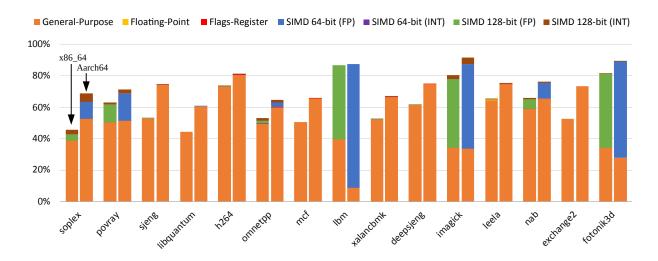

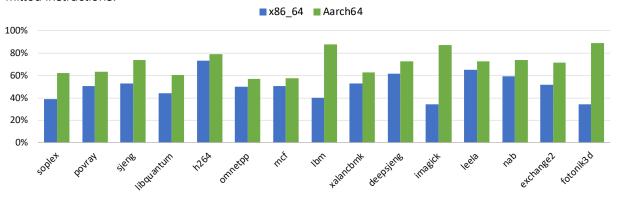

Premièrement, nous effectuons une exploration inter-jeux d'instructions (ou ISA pour Instruction Set Architecture) de la prédiction de valeur. Depuis la toute première introduction de la prédiction de valeur, il y a eu une pléthore de différents prédicteurs qui prétendent avoir des améliorations particulières indépendamment de l'ISA. Cependant, comme les techniques de VP dépendent essentiellement de la nature et du comportement du code des programmes, il est essentiel de détecter l'existence d'interactions entre les particularité d'une ISA et la prédiction de valeur. Dans notre étude, nous comparons soigneusement l'accélération apportée avec VP dans les binaires d'application compilés symétriquement pour x86\_64 et Aarch64 ISA. Notre exploration montre que, en effet, certaines particularités de l'ISA, telles que la quantité de registres disponibles dans l'ISA, peuvent avoir un impact significatif sur le gain de performance

qui peut être obtenu via VP. De plus, étant donné que les prédicteurs de valeur supposent conventionnellement des entrées de 64 bits pour suivre l'exécution, les instructions vectorielles qui produisent des valeurs d'au moins 128 bits ne sont pas couvertes, c'est-à-dire ni suivies ni prédites. Plus précisément, la prédiction d'instructions vectorielles peut entraîner un prédicteur assez grand, car elle nécessite d'agrandir la longueur des entrées en fonction de la longueur maximale de la valeur qui doit être prédite (par exemple, 128 bits par entrée pour couvrir les instructions de 128 bits). À cet égard, dans notre exploration au niveau de l'ISA, nous considérons également l'influence des optimisations vectorielles dans l'accélération réalisée avec VP, montrant leur impact sévère.

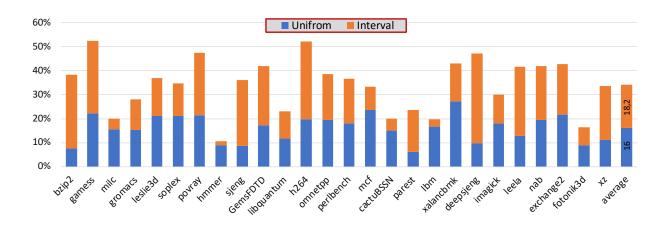

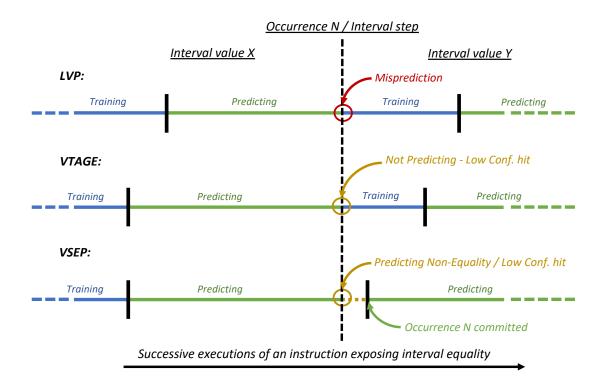

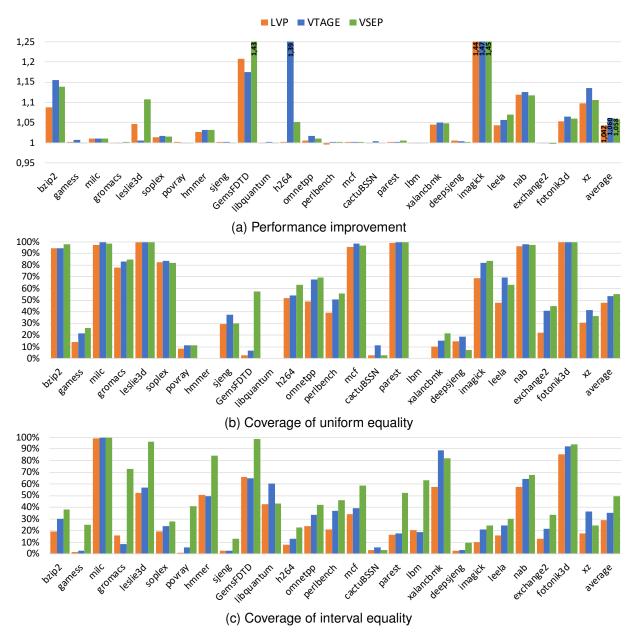

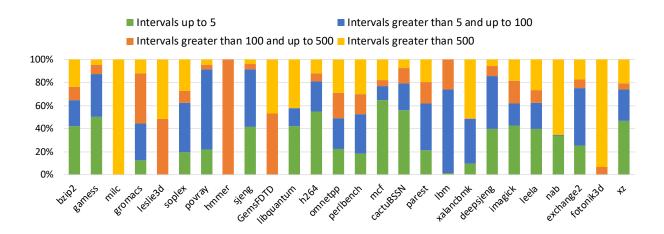

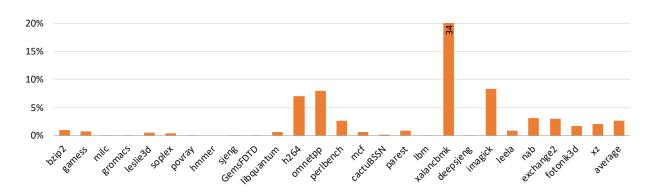

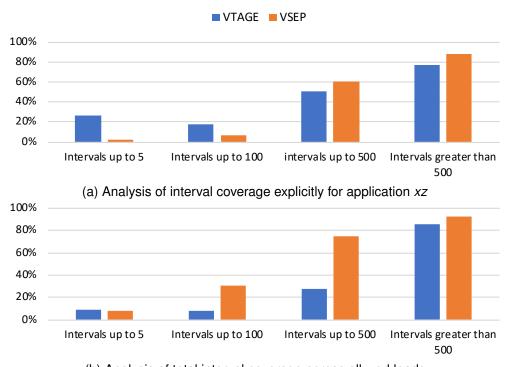

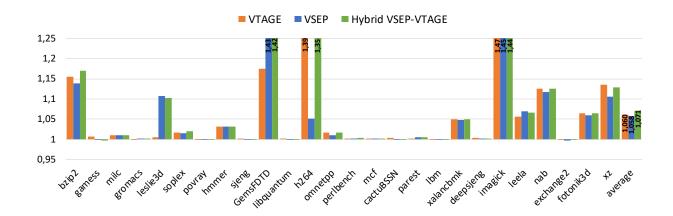

Deuxièmement, nous détectons un motif de valeurs inexploré, à savoir l'égalité d'intervalle, qui caractérise cependant une partie substantielle des instructions (plus de 18% en moyenne). Un tel motif de valeur n'est pas efficacement capturé par les prédicteurs précédemment proposés qui conservent généralement les valeurs suivies (c'est-à-dire qui seront potentiellement utilisées pour la prédiction) et leur confiance en la prédiction dans la même entrée. Afin de supprimer cette limitation, nous introduisons le prédicteur VSEP, qui est basé sur un schéma de décision binaire et dissocie fortement les valeurs de leur confiance en la prédiction. VSEP atteint une accélération qui se situe dans la même plage que le VTAGE [PS14b] proposé précédemment, mais en exploitant des motifs de valeur non capturés auparavant. En d'autres termes, VSEP complète efficacement la façon établie dont VP est effectuée en augmentant considérablement la fraction des instructions prédites qui exposent [de] l'égalité d'intervalle (15% supplémentaires en moyenne). Essentiellement, lorsqu'il est combiné avec VTAGE, VSEP améliore l'accélération obtenue de 19% en moyenne. De plus, avec VSEP, nous pouvons obtenir des performances comparables à celles d'un VTAGE à l'état de l'art, en utilisant environ 58% d'entrées en moins (3K entrées de valeur dans VSEP contre 7K entrées de valeur dans VTAGE) avec le même budget de stockage. De cette façon, VSEP peut réduire considérablement le coût de la prise en compte de la prédiction de valeurs pour des valeurs supérieures à 64 bits.

Troisièmement, et enfin, nous proposons un mécanisme basé sur LAP, à savoir LAPELE, qui fait des lectures mémoire anticipés avant la partie out-of-order du cœur. Pour ce faire, nous changeons l'objectif de notre prédicteur hybride VSEP/VTAGE afin d'effectuer LAP. Avec un tel prédicteur, nous réussissons à prédire les adresses mémoire de 48% des lectures mémoire en moyenne. Pour éviter une éventuelle explosion de violations d'ordre de mémoire, nous proposons l'utilisation d'un prédicteur auxiliaire à petite échelle pour "filtrer" les lectures mémoire qui présentent des conflits de mémoire. Finalement, avec ce schéma, nous pouvons exécuter en avance 32% des instructions de lecture mémoire validées en moyenne en les sortant complètement de le partie out-of-order du cœur. Du point de vue des performances, LAPELE atteint une accélération moyenne dans la même plage qu'un prédicteur de valeur de taille égale qui est réglé pour spéculer uniquement sur les valeurs des lectures mémoire. En réalité, les

mécanismes basés sur le LAP ne peuvent pas systématiquement atteindre ou dépasser les performances de la prédiction de valeur généraliste. Cependant, avec LAPELE, nous montrons que LAP peut être un catalyseur nécessaire des futures architectures à grande fenêtre efficaces en complexité pour tolérer la latence de la mémoire.

## INTRODUCTION

In his 1937 paper, Alan Turing [Tur37], the father of computer science, stated that "it is possible to invent a single machine which can be used to compute any computable sequence". The Turing machine or the a-machine (automatic machine) is a mathematical model that defines an abstract machine capable of implementing any given computer algorithm. In automata theory, an "abstract machine" is the theoretical model or the specification of a computing system. In the field of computer science, this abstraction simply represents the model of a processing unit. Indeed, the Turing principle is considered to be the general example of a Central Processing Unit (CPU) that carries out all computations within a computer. Traditionally, the term "CPU" refers to the processor, distinguishing it from external components, such as the main memory.

In essence, computers are designed to process, store, and retrieve data. Processors are fairly called the "brains" of computers, since they enable all basic arithmetic, logical, control and input/output(I/O) operations specified by a computer program. As such, they basically set the limits of computers processing capacity and they are reasonably considered the cornerstone of computer science. Image processing, bioinformatics, machine learning and artificial intelligence are only few aspects of computer science that could not simply exist without machines with sufficiently high computational capabilities. Moreover, both the miniaturization and standardization of CPUs has increased the presence of digital devices in modern life, far beyond the limited application of dedicated computing machines. Modern microprocessors appear in electronic devices ranging from automobiles to cellphones and from domestic appliances to critical medical devices. As a result, processor architecture is considered as one of the most important types of hardware design.

The word "architecture" typically refers to the design and construction of buildings. Similarly, in the computing world, computer architecture respectively describes the design of computer systems. More specifically, the architecture of a processor chip, known as microarchitecture, is the detailed description of its basic components, their functionalities and their interconnections, as well as the operations that they can effectuate. All these diverse features are fully expressed by the instructions that the processor supports, which all together represent the *Instruction Set Architecture* (ISA) of the processor. Different processor "families", such as Intel, IBM, PowerPC and ARM, can employ different categories of ISAs. For that reason, a program that is constructed by the compiler in a particular type of ISA, can not be executed on a machine that does not implement the same ISA. On the other hand, a single ISA may be implemented by different models of processors that remain compatible at the ISA level. For instance, popular

families, such as x86, have processors supplied by multiple manufacturers. In other words, the ISA provides a conceptual level of abstraction between compiler writers, who only need to know the available machine instructions and their encoding, and processor designers, who build machines that execute those instructions. Overall, the ISA together with the microarchitecture form what is called *computer architecture*.

From a microscopic point of view, *transistors* are the atomic parts of typical microprocessor chips, in the same sense that bricks are the major components of buildings. Transistors are arranged in certain ways in order to form electric circuits that are capable of carrying out all fundamental binary functions, such as OR and AND. Thereafter, the sophisticated combination of these functions can provide devices that enable higher-level operations, such as additions and multiplications. By solely considering the inarguably high complexity of designing such circuits, one can easily infer how perplexing is the actual procedure of "building" a processor.

In the modern age of digitalization, where almost everything is processed by computers, the computational demands are in an ascending orbit. In order to sustain the pace in computer-science research and quality-of-life improvement, processors have to keep increasing their performance, regardless of the design complexity. Thus, even if modern general-purpose processors already provide high performance rates, there is a continuous need of improvement, in terms of execution latency and power consumption. In reality, these represent the two constant challenges of processor architecture.

To that end, circuit designers, that act at the transistor level, attempt to provide optimizations that generally aim to shorten the electric critical path for the faster transmission of the information. On the other hand, computer architects operate on a higher level which is still close to the logic gates circuit. An architect's responsibility is to give a blueprint of the processor's organization, which includes the description of all its distinct components. In order to reach the respective performance goals, architects may design new components, remove some others from mainstream models or modify their functionality and their connections, by always guaranteeing the effective orchestration of all the different processing parts together. However, they have to always be aware of the current circuit technology, in order to provide down-to-earth solutions, i.e. designs that can be implemented on a real silicon. In other words, computer architects could be considered regular architects who draw their designs with respect to the state-of-the-art constructing principles, so that manufacturers (i.e., circuit designers) can carry them out in practice.

Since the introduction of the very first widely-used computer processor, the Intel 8080 in 1974 [74], hardware manufacturers traditionally attempt to cram more and more transistors onto a finite silicon surface. In particular, current general-purpose processors feature hundreds of millions to billions of transistors. Evidently, more transistors (processor building blocks) means more units available for processing program instructions and can naturally lead to higher pro-

cessing speed. The increasing number of transistors in processor chips had been empirically observed by *Moore's law*, which stated that "the transistor count on a chip will double every 2 years" [Moo98]. This meant that about every 24 months a transistor would be half of its current size so that double number of transistors could fit in an equally-sized chip. While not a law in the mathematical sense, Moore's Law has proved a fairly accurate predictor of this trend for more than 40 years. However, since around 2001, technology scaling has been slowing down as transistors shrinking is reaching its limits and Moore's Law curve is henceforth difficult to follow.

Moreover, as increasingly complex CPUs are designed and manufactured to tolerances on the order of nanometers, processors performance has been growing due to the escalation of the processors clock speed. A processor's clock ticks periodically and defines the minimum time needed for completing a particular computation step. Thus, by increasing the clock frequency more tasks can be completed within a certain interval of time. The clock frequency practically resembles the speed at which the transistors in a circuit can be reliably switched on and off. As transistors have been progressively shrinking, their switching speed has been inversely increasing, allowing the emergence of processors with high frequencies, nowadays ranging from 2GHz to 5GHz. Yet, CPUs frequency is inherently limited by the peak power constraints of the chip, also known as the Power Wall [Bos11]. As a result, clock speeds have stagnated for more than a decade because, as it appears, a dramatic increase in frequency may require a change in the laws of physics.

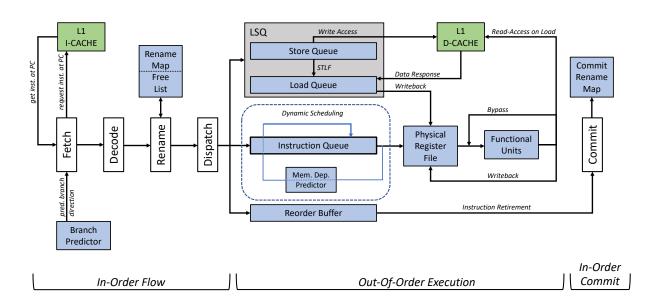

Nonetheless, the large number of transistors in processor chips enabled the emergence of novel design methods, such as *pipelining*, *superscalar* and *out-of-order* execution [AA93], which showed that processors performance can increase even if the clock frequency plateaus. Such techniques improve the performance of a single or uni-processor, i.e. *sequential performance*, by parallelizing instruction execution, a feature that is typically referred as *Instruction Level Parallelism* or *ILP*. Although these mechanisms have been the backbone of processor architecture till today, it had become very hard to keep increasing sequential performance in the same pace that the number of transistors was growing. Therefore, in order to sustain the augmentation of performance, chipmakers and manufacturers adopted the principle of "*divide and conquer*", by progressively shifting to the implementation of multiprocessor or multicore chips. In 2001 IBM introduced POWER4 [War+02], the first commercially available multiprocessor chip that featured 2 cores on a single die, followed by Intel's Pentium D and AMD's Athlon 64 x2 in around 2005 [Man+06; Lu +07]. Today, high-performance computing is essentially enabled by multicore processors that are composed by 2, 4, 8 or even more cores.

In a multicore processor the overall execution of a program can be sped up by dividing it into several smaller programs that are executed concurrently in different cores. This "server mentality" improves performance in terms of throughput (i.e., more work can be processed within

a given unit of time), as opposed to uni-processors that target execution latency (i.e., faster completion of a particular task). Still, the performance of a multicore processor is limited by the program nature, since parallel computing can not apply to algorithmic components that need to be processed sequentially. In other words, some programs are intrinsically sequential and they can not be parallel at all, while some others may possess long sequential parts and they can only be partly parallel. Eventually, as Amdahl's Law [Amd67] suggests, the performance gain that can be obtained by parallelizing a program is governed by its sequential aspects. In other words, if one could separate a program to its parallel and sequential parts, then, by assuming an infinite number of cores that execute concurrently the parallel fraction, the total speedup would be bounded by the execution of the sequential elements. For instance, if an application needs 4 hours of computing and only 2 of them can be parallelized, the final execution time can be reduced at most by a factor of 2. Consequently, it appears that even in the *multicore era*, making single cores faster is paramount to achieve high-performance computing [HM08].

Current leading-edge processor cores employ speculative-nature techniques that rely on empirical observations about programs behavior in order to become effectively "smarter" about program execution. The main observation that works as the enabling incentive of these techniques is that ordinary programs, for the most part, do not behave randomly. Rather, they tend to exhibit a certain regularity in the flow and in the products of their operations. As such, by isolating these program "idiosyncrasies", there is the ability to devise automata capable of guessing program-related execution information. These aspects can be understood better by considering two widely-used speculation techniques that are empowered by programs behavior: *branch prediction* and *memory dependence prediction*. Branch prediction exploits the regularity found in the control-flow paths that programs tend to follow, while memory dependence prediction relies on the regularity found in the interactions between load and store instructions. Both these techniques are employed by virtually all modern high-performance cores to facilitate the flow of instructions in the core (i.e. fetching and scheduling, respectively) and therefore, to increase sequential performance.

Another more advanced level of speculation leverages the underlying regularity in either the raw data that programs produce or the memory addresses from where particular data originate. Two major techniques of this kind are *value prediction* (VP) and *load-address prediction* (LAP). VP and LAP are two developing and highly-promising *data-speculative* techniques, in the sense that they still feature plenty of room for exploration and optimization. To this respect, this thesis proposes certain speculative-nature mechanisms that are based on value and load-address prediction in order to effectively improve the sequential performance of contemporary general-purpose processors. These mechanisms are devised on-top of the architecture of a single-core processor and are totally independent from the higher-level parallelism that multicore designs exploit. Therefore, they can be seamlessly adopted by the different cores of

a multicore processor and potentially scale also its performance. Additionally, when this thesis introduces modifications in the internal core-design, the current technology constraints are faithfully respected. That is, the proposed techniques rely on hardware structures that can be practically implemented on a real processor.

#### **Contributions**

The mechanisms that are introduced by this thesis are related with two main classes of advanced speculation: *value prediction* and *load-address prediction*.

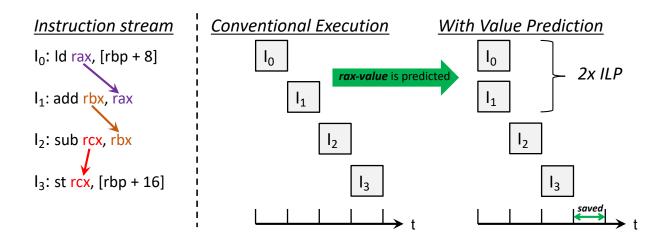

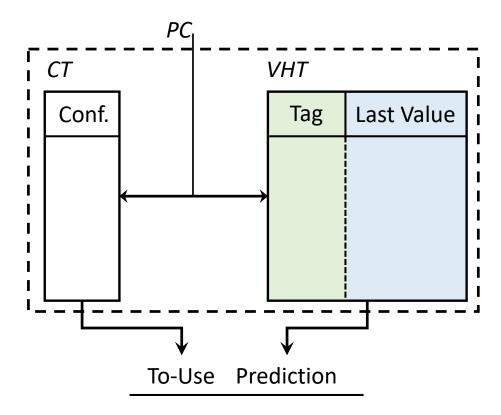

Value Prediction is a technique that breaks true data dependencies between instructions by allowing "consumers" to initiate their execution speculatively before their respective "producers" have executed. VP is enabled by the fact that different dynamic instances of the same static instruction produce results that often follow a predictable pattern. Consequently, a hardware structure can be used to track these instructions and predict their result. When an instruction is predicted, its dependents can execute concurrently by using the predicted value without needing to stall. As such, when a prediction is correct, the total execution time decreases. On the opposite case, certain recovery actions must be taken to guarantee the re-execution of dependents with the correct input. The bottom line is: sequential performance increases as the processor can extract more *ILP*.

Load-Address Prediction is fairly similar to VP; rather than predicting the results of load instructions, LAP-mechanisms predict the memory addresses from which loads fetch their data. Such mechanisms are based on the observation that load addresses may also fall into predictable patterns. Predicting a load's memory address allows to anticipate the access to the loaded data and to generate a speculative value for the particular load instruction. That value is not necessarily predictable by a VP-mechanism. Like in VP, the speculative values of load instructions are propagated to dependents and allow them to execute ahead of time. As such, LAP initiates a similar form of data-speculative execution that respectively requires validation.

Overall, both of these speculation techniques aim to boost *ILP* and to reduce the execution latency of instructions in the core. By sharing the same objectives, this dissertation makes the following main contributions:

1. Analysis of the ISA impact on the performance of value prediction:

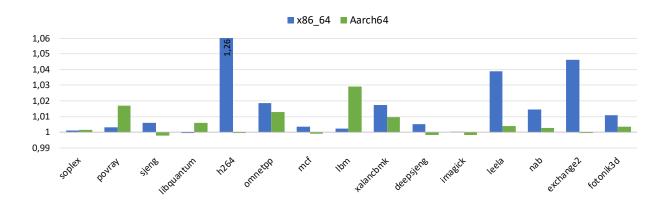

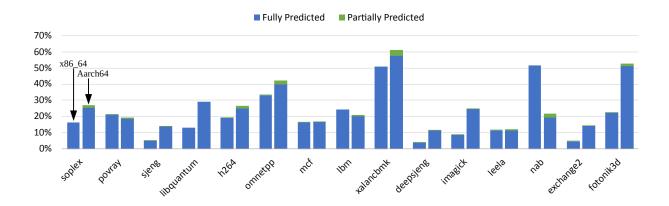

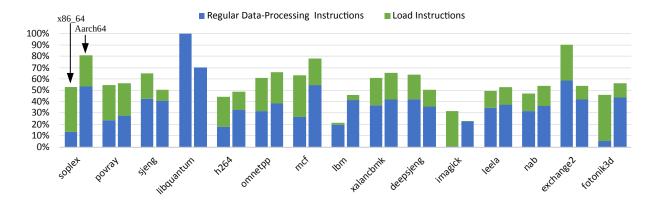

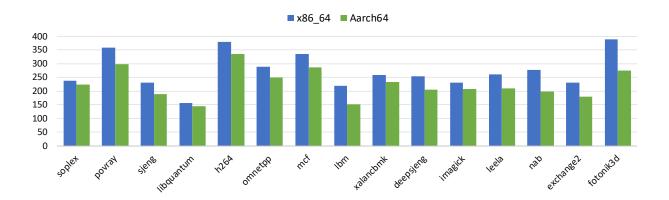

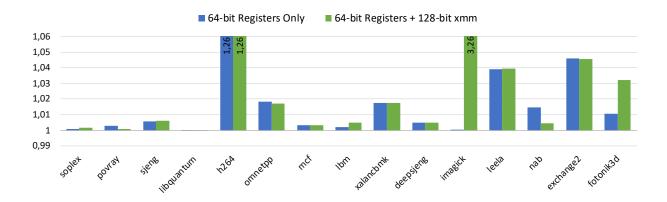

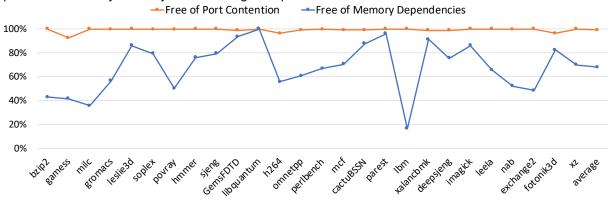

Our first contribution makes the case that certain ISA particularities have a significant impact on the performance gain that can be obtained with value prediction. In particular, we carefully studied and compared the performance of value prediction in the context of two widely-used 64-bit ISAs in high-end cores, namely the *x86\_64* and the *Aarch64* ISA. What we basically discovered from our inter-ISA exploration of value prediction is that the obtained speedup is consistently higher in x86\_64, with the speedup-gap being up to

26% in the interest of x86\_64. The main reason is that, compared to Aarch64, x86\_64 contains less architectural registers that lead to program-code with higher concentration of load instructions that are eventually predicted. In essence, our general observation is that by virtue of this registers-related particularity, in x86\_64, the code-regions that induce substantial execution delays due to data dependencies between instructions, are more frequent but at the same time more predictable. In addition, we isolated the influence of vector optimizations in the VP performance. Such optimizations have introduced instructions producing results longer than the 64 bits that the current technology assumes. Conventionally, these instructions are not considered for value prediction, since tracking their fairly wide values scales prohibitively the size of value predictors. In practice, current value predictors are typically limited to speculate on up to 64-bit values. However, our study reveals that this convention limits considerably the corresponding performance benefit. This issue is partly addressed by our second contribution.

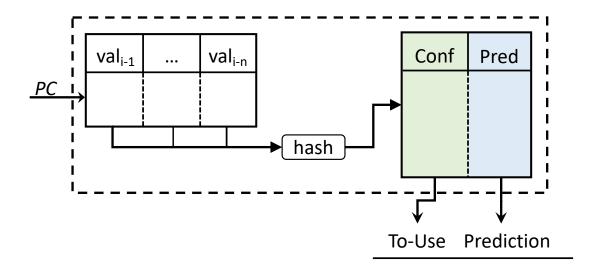

#### 2. VSEP [KS19], a binary-nature VP model:

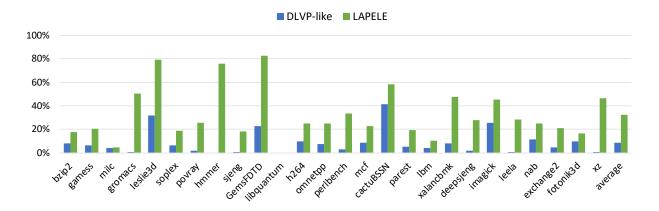

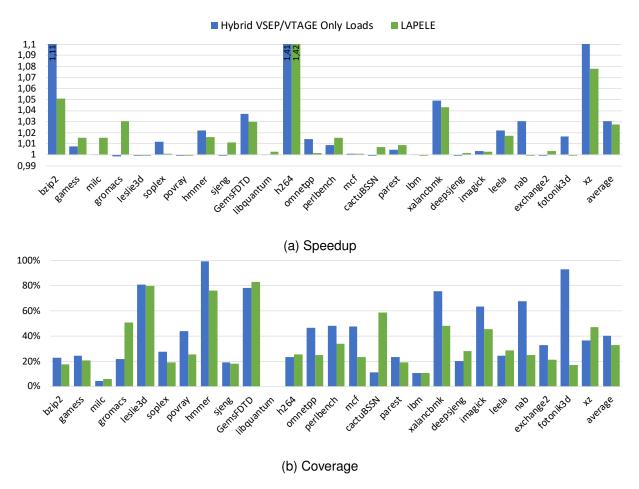

Our second contribution relates to the design of a value predictor that exploits an unexplored value pattern that is, however, substantially followed by instruction results. In essence, the driving force of value prediction is the existence of certain predictable patterns exposed by instruction values. In that sense, the constant challenge of contemporary value predictors is to sufficiently capture these patterns and exploit the predictable execution paths. To do so, existing techniques tightly associate recurring values with instructions and distinctive contexts by building confidence upon them after a plethora of repetitions. What we found is that execution monotony of an instruction can exist in the form of intervals and not only uniformly. That is, dynamic instances of the same static instruction may not only constantly produce a particular value, but also in intervals of successive executions. Nonetheless, previous VP-schemes have not been devised with total awareness of this interval-style pattern, but rather of the uniform one. As such, these intervals limit the potential fraction of predicted instructions (coverage), since in a conventional value predictor, confidence is reset at the beginning of each new interval. We address this challenge by introducing the notion of Equality Prediction (EP), which represents the binary facet of value prediction. By following a twofold decision-scheme (similar to branch prediction), EP makes use of control-flow history to determine equality between the last committed result read at fetch time, and the result of the fetched occurrence. When equality is predicted with high confidence, the read value is used. VSEP, our value predictor that makes use of EP, obtains the same level of performance as previously proposed state-of-the-art predictors. However, by virtue of exploiting value patterns not previously captured, our design complements the established way that value prediction is performed, and when combined with contemporary prediction models, improves the benefit of value prediction by 19% on average. Moreover, VSEP mitigates significantly the cost of predicting values that are wider than 64 bits, as it is by construction highly independent from the values width.

#### 3. LAPELE, a LAP-based design for data-speculative execution:

Our third and last contribution focuses particularly on reducing the total execution latency of load instructions. We propose LAPELE, a comprehensive design that leverages loadaddress prediction for data speculative execution. More specifically, in LAPELE we use a load-address predictor, namely ATAGE-EQ, which is directly derived from the VSEP value predictor of our second contribution and the previously-proposed VTAGE [PS14b]. In this way, we practically explore load-address predictability by capitalizing on recent advances in value prediction, having the intuition that load-addresses follow similar patterns. Indeed, ATAGE-EQ allows us to predict the addresses of 48% of the committed loads on average. The uniqueness of LAPELE is that loads that predict their address, use it to perform their memory access from the early pipeline frontend (early execution) and then bypass the out-of-order execution core. That is, no second repairing execution takes place. To do so, LAPELE employs some additional logic in charge of computing the actual address of address-predicted loads before Commit, similarly to the EOLE architecture [PS14a]. The data-speculative execution is then validated by verifying the predicted address before removing the instruction from the pipeline. However, such a flow is highly sensitive to memory hazards. To avoid a prohibitive increase of memory-order violations, we propose to use MDF, an auxiliary predictor of fairly low size and complexity, in order to "filter" the loads that use their predicted address for early execution. Eventually, LAPELE achieves to execute beyond the out-of-order engine, i.e. in the early frontend, 32% of the committed load instructions, achieving an average speedup in the same range with load-value prediction. This is in contrast with previous schemes where address-predicted loads were normally dispatched for execution in the out-of-order core.

### Organization

This dissertation is organized as follows. Chapter 1 serves as a comprehensive analysis of general-purpose processors architecture. We start from describing simple pipelining and we conclude to modern superscalar processors of out-of-order execution. In this way, readers may infer from the beginning the benefits that advanced speculation can have on the sequential performance of modern processors. In Chapter 2, we present the two speculation techniques we consider, namely *value prediction* and *load-address prediction*. We describe their logic and we provide the state-of-the-art models, as well as related work in general. Chapter 3 focuses on our first contribution. We first provide a basic analysis of the two employed ISAs and the tailored

framework we use to enable inter-ISA comparison, then we analyze our findings. In Chapter 4, we introduce our VSEP predictor (i.e. second contribution). First, we present the new value pattern we have detected. Then, we analyze how typical predictor and how VSEP interacts with it, before we provide an experimental analysis and comparison of VSEP with previous recent work. Chapter 5, concerns our third and last contribution. We analyze how we choose to use ATAGE-EQ as our load-address predictor. Then, we analyze the arising issues related with LAPELE and we present its microarchitectural model. We eventually evaluate VSEP considering prior relevant work. Finally, we conclude this dissertation summarizing our findings and offering suggestions on how this work can be extended.

# THE ARCHITECTURE OF A MODERN GENERAL-PURPOSE PROCESSOR

"The term architecture is used here to describe the attributes of a system as seen by the programmer, i.e., the conceptual structure and functional behavior as distinct from the organization of the dataflow and controls, the logic design, and the physical implementation."

Gene Amdahl, April 1964 [ABB64]

#### 1.1 Fundamentals of Processor Architecture

#### 1.1.1 General Definition

Processor or computer architecture is the science of designing, selecting, and interconnecting hardware components in order to create computing systems that meet functional, performance, power consumption, cost, and other specific goals. Even more precisely, according to the recognized computer architect Frederick P. Brooks Jr., "Computer architecture, like other architecture, is the art of determining the needs of the user of a structure and then designing to meet those needs as effectively as possible within economic and technological constraints" [Buc62]. General-purpose processors form the core of such computing systems and as such, terminology-wise, computer architecture typically refers to processors internal design and to their intrinsics.

#### 1.1.2 Instruction Set Architecture - ISA

Essentially, processors are programmable, and thus, they provide a specific interface for the communication between the software and the hardware, known as the *Instruction Set Architecture* or the *ISA*. That is, the ISA includes all those instructions that a processor is designed to "comprehend" and accordingly to execute. In that sense, a processor is said to implement a specific ISA. For instance, Intel and AMD processors implement the x86 ISA, while Qualcomm processors implement the ARM ISA. Although two processors may use the same ISA, the way

they implement it may be different. The term *microarchitecture* <sup>1</sup> is used to describe the specific way that an ISA is implemented by a processor and should not be confused with the ISA. Along with the set of instructions, the ISA also defines a specific collection of registers, i.e. memory locations where the operands of instructions can reside. In particular, registers are the closest and the fastest-to-access memory unit in a processor. These two, *instructions* and *registers*, are considered the primitives of a given ISA and both of them are visible to the software level.

Based on the nature of their instructions, existing ISAs are distinguished into two categories: the *Reduced Instruction Set Computing* (RISC) and the *Complex Instruction Set Computing* ISAs [Col+85]. In the former category, instructions are mostly simple operations (such as simple arithmetics or binary logic), while in the latter category, as its name suggests, instructions can perform more complicated tasks. As it follows, RISC ISAs usually contain more instructions in order to be able to eventually carry out equivalent tasks to CISC ISAs. But on the other hand, CISC ISAs are considered more perplexing in their implementation due to the higher complexity of their instructions, i.e. the microarchitecture of a processor implementing a CISC ISA is relatively more complicated. Furthermore, ISAs are also defined by the number or bits that their instructions use to probe memory. As a note, current technology allows processors to implement up to 64-bit ISAs, meaning that they can actually address 2<sup>64</sup> memory locations.

#### 1.1.3 Instruction Formats