# 5G 28 GHz high efficiency integrated phased array transceivers

Thibaut Despoisse

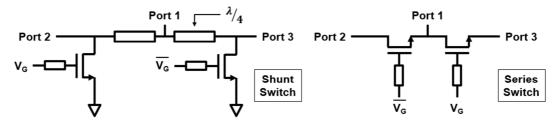

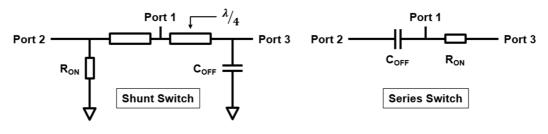

#### ► To cite this version:

Thibaut Despoisse. 5G 28 GHz high efficiency integrated phased array transceivers. Electronics. Université de Bordeaux, 2020. English. NNT: 2020BORD0151. tel-03053715

## HAL Id: tel-03053715 https://theses.hal.science/tel-03053715

Submitted on 11 Dec 2020  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE PRÉSENTÉE

#### POUR OBTENIR LE GRADE DE

## **DOCTEUR DE** L'UNIVERSITÉ DE BORDEAUX

SCIENCES PHYSIQUES ET DE L'INGÉNIEUR

SPÉCIALITÉ ÉLECTRONIQUE

Par Thibaut DESPOISSE

## 5G 28 GHz High Efficiency Integrated **Phased Array Transceivers**

From System-Level Specifications to CMOS SOI Front-End Module Circuits

Sous la direction de : Nathalie DELTIMPLE (Co-directeur : Anthony GHIOTTO, co-encadrant : Pierre BUSSON)

Soutenue le 23 octobre 2020

Membres du jury :

| Mme      | Patricia DESGREYS               | Professeur               |

|----------|---------------------------------|--------------------------|

| М.<br>М. | Serge VERDEYME<br>Eric KERHERVE | Professeur<br>Professeur |

| M.       | Bernard JARRY                   | Professeur               |

| M.       | Alain KARAS                     | Ingénieur                |

| Mme.     | Nathalie DELTIMPLE              | Maître de conférence     |

| M.       | Anthony GHIOTTO                 | Maître de conférence     |

| М.       | Pierre BUSSON                   | Ingénieur                |

Telecom Paris Université de Limoges Rapporteur Bordeaux INP Université de Limoges Examinateur Safran DS e Bordeaux INP ce Bordeaux INP ce Bordeaux INP STMicroelectronics Co-encadrant

Rapporteur Président Examinateur Directrice de thèse Co-directeur

« Faites que votre tableau soit toujours une ouverture au monde »

Léonard de Vinci

## Remerciements

Avant toute chose, je remercie sincèrement Madame Patricia Desgreys, professeur à Telecom Paris, et Monsieur Serge Verdeyme, professeur à l'Université de Limoges, d'avoir accepté d'être les rapporteurs de mes travaux de thèse. Je remercie également Messieurs Bernard Jarry et Alain Karas, respectivement professeur à l'Université de Limoges et ingénieur chez Safran Data Systems, d'avoir examiné mon travail et pris part au jury de la soutenance. Enfin, Monsieur Eric Kerherve, professeur à Bordeaux INP et directeur du laboratoire commun « ST – IMS », d'avoir présidé de ce jury.

Je tiens à exprimer toute ma gratitude à la directrice de cette thèse, Nathalie Deltimple, pour m'avoir convaincu de prendre part à cette aventure et pour son aide tout au long de ces presque quatre années. A Anthony Ghiotto, co-directeur de cette thèse, pour la confiance qu'il m'a accordé dès ma première année à l'ENSEIRB MATMECA, où il était mon enseignant. A Pierre Busson, co-encadrant industriel, pour avoir su trouver le sujet qui m'a séduit, et pour sa disponibilité tout au long de cette thèse.

Cette thèse s'est déroulée au sein du laboratoire commun « ST – IMS ». Je remercie donc chaleureusement Monsieur Yann Deval, directeur du laboratoire IMS, de m'avoir accueilli dans ses locaux. Je remercie également tous les membres du groupe Conception et de l'équipe Circuits et Systèmes Hyperfréquence (CSH) pour leur aide, tant technique qu'humaine; et particulièrement Magali sans qui nos circuits ne pourraient pas être mesurés, Manuel qui a donné beaucoup de son temps pour que lesdits circuits fonctionnent, et Simone pour son aide précieuse. Enfin, je remercie les doctorants du laboratoire qui ont fait de ces années une expérience très enrichissante. Je pense notamment à John et à mes compagnons d'organisation de conférences : David et Samuel (Dr. Redois).

Je remercie également mes collègues de STMicroelectronics Grenoble et Crolles, qui m'ont toujours apporté leur aide lors de mes séjours Isérois : Pascal, Joël, Jérôme, Patrice, Jocelyn, Andreia, Fréderic ; et bien sûr mes voisins de box : Jean-Yves, Vincent et Jérémie qui m'ont beaucoup soutenu lors de la conception des différents circuits.

Enfin, un très grand merci à ma famille et à mes amis qui me soutiennent depuis toujours, et qui ont continué à le faire pendant ces années de travail. Ils m'ont aidé à prendre du recul lors des moments difficiles. J'ai également une pensée émue pour toi, papi, dont la curiosité, la culture et la rigueur ont toujours été des exemples pour moi. Merci.

Je terminerai par remercier ma compagne, Camille, pour son aide quotidienne précieuse et pour la patience exemplaire dont elle a fait preuve. Merci de m'avoir épaulé chaque jour. Je t'aime.

Thibaut Despoisse

## Contents

| Contents      |         |          |                                                             | 9  |

|---------------|---------|----------|-------------------------------------------------------------|----|

| Glossary      |         |          |                                                             | 13 |

| Introduction  |         |          |                                                             | 17 |

| Chapter 1: Fr | om 5G E | xpectati | ons to Front-End Module Specifications                      | 19 |

| I.            | On th   | e Road   | towards the Wireless Communication Paradigm Shift           | 20 |

|               | 1.      | Lega     | cy and Current Telecommunication Networks                   | 20 |

|               |         | a.       | 1G – The Foundation of Mobile Communications                | 20 |

|               |         | b.       | 2G – The Beginning of Digital Telecommunications            | 21 |

|               |         | c.       | 3G – Towards Broadband Mobile Communications                | 22 |

|               |         | d.       | 4G – Towards a Unique Mobile Communication Standard         | 23 |

|               | 2.      | 5G O     | verview                                                     | 24 |

|               |         | a.       | The Emergence of 3 Standards                                | 24 |

|               |         | b.       | EMBB Spectrum and Network                                   | 25 |

|               |         | c.       | Beamforming: a Key Enabler                                  | 27 |

|               |         | d.       | The 5G Standardization Timeline                             | 29 |

| ١١.           | From    | 5G EME   | 3B Expectations to System-Level Specifications              | 30 |

|               | 1.      | Thesi    | s Use Case: Definition & Challenges                         | 30 |

|               |         | a.       | Chosen Scenarios                                            | 30 |

|               |         | b.       | First 5G Standard                                           | 31 |

|               |         | c.       | Challenges                                                  | 31 |

|               | 2.      | Sizing   | g Methodology for mm-Wave 5G Small Cells                    | 31 |

|               |         | a.       | Step 1 – Introduction                                       | 31 |

|               |         | b.       | Step 2 – Signal Properties                                  | 32 |

|               |         | c.       | Step 3 – Propagation Channel Modeling                       | 33 |

|               |         | d.       | Step 4 – Receiver Characteristics                           | 35 |

|               |         | e.       | Step 5 – Link Budget                                        | 35 |

|               |         | f.       | Step 6 – Front-End Module Features for mm-Wave Access Point | 36 |

|               |         | g.       | Step 7 – Array Sizing Issues                                | 38 |

|               |         | h.       | Preliminary Step 8 – Beamforming Topologies Overview        | 41 |

|               |         |          |                                                             |    |

#### Table of Contents

| 111.           | Phased   | l Array A | ntenna Transmitter Comparison                    | 43 |

|----------------|----------|-----------|--------------------------------------------------|----|

|                | 1.       | Ka-ban    | d 5G Phased Array Transceiver State of the Art   | 43 |

|                |          | a.        | RF Phased Arrays                                 | 43 |

|                |          | b.        | Other Phased Array Topologies                    | 44 |

|                |          | c.        | Phased Array Figure of Merit                     | 44 |

|                |          | d.        | Phased Array Comparative Table                   | 45 |

|                | 2.       | Transce   | eiver Power Consumption Estimation               | 46 |

|                |          | a.        | Power Consumption Model                          | 46 |

|                |          | b.        | Phased Array Transmitter Architecture Comparison | 48 |

|                |          | c.        | Prospects of Improvement                         | 49 |

| IV.            | Conclu   | sion      |                                                  | 50 |

| ٧.             | Refere   | nces      |                                                  | 51 |

| Chapter 2: Sta | ndalone  | Ka-Band   | Front-End Module Circuit Design                  | 56 |

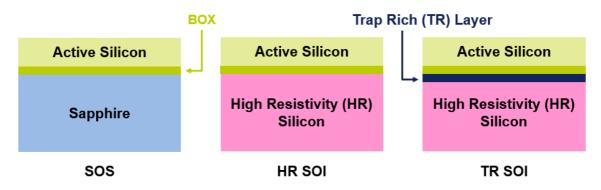

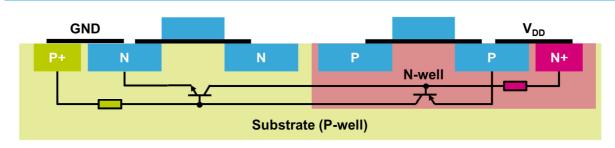

| I.             | The ST   | C65SOIF   | EM Technology                                    | 56 |

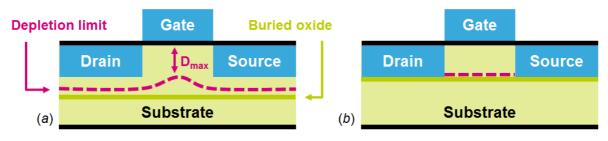

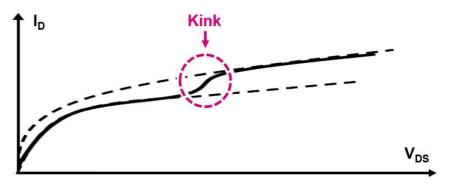

|                | 1.       | Substra   | ate on Insulator Technologies                    | 56 |

|                |          | a.        | From Bulk CMOS to SOI Technologies               | 56 |

|                |          | b.        | Comparison between PD SOI and FD SOI             | 58 |

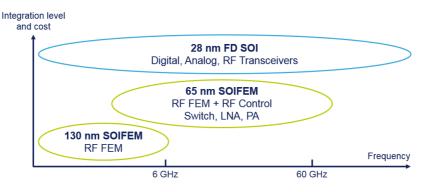

|                |          | с.        | Overview of ST SOI Technologies                  | 60 |

|                | 2.       | The ST    | C65SOIFEM Technology                             | 61 |

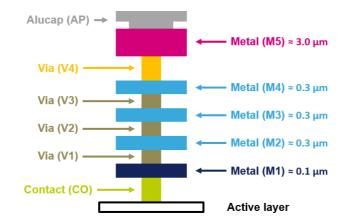

|                |          | a.        | Overview of the Technology Features              | 61 |

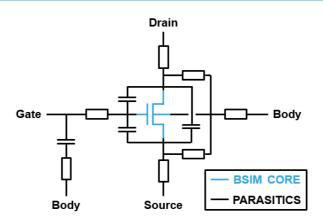

|                |          | b.        | Device Models                                    | 61 |

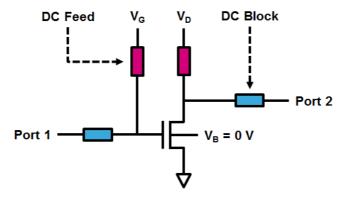

|                |          | c.        | First Simulation Results                         | 62 |

|                |          | d.        | Electromagnetic Simulations of the Passives      | 67 |

|                |          | e.        | De-embedding Method                              | 68 |

|                |          | f.        | Measurement Results                              | 69 |

| II.            | Single I | Pole Dou  | ible Throw RF Switches                           | 72 |

|                | 1.       | Introdu   | iction                                           | 72 |

|                |          | a.        | The Need of RF Switches                          | 72 |

|                |          | b.        | Ka-Band Semiconductor Switches                   | 73 |

|                | 2.       | Series-   | Shunt SPDT Switches                              | 76 |

|                |          | a.        | Operating Principle                              | 76 |

|                |          | b.        | Series-Shunt Switch Sizing Method                | 78 |

#### Table of Contents

|                |          | с.         | Circuit Layouts and Transistors' Figure of Merit Measurements | 80  |

|----------------|----------|------------|---------------------------------------------------------------|-----|

|                |          | d.         | SPDT Switch Measurement Results                               | 82  |

| III.           | Standa   | alone Ka-  | Band Low Noise Amplifier Design                               | 85  |

|                | 1.       | Ka-Bar     | d Low Noise Amplifier Overview                                | 85  |

|                |          | a.         | Noise Considerations in RF Microelectronics                   | 85  |

|                |          | b.         | Low Noise Amplifier Topologies                                | 86  |

|                |          | с.         | Ka-Band Low Noise Amplifier State of the Art                  | 88  |

|                | 2.       | Standa     | lone Ka-Band Low Noise Amplifier Design                       | 90  |

|                |          | a.         | Targeted Features                                             | 90  |

|                |          | b.         | Design of a Standalone LNA with Inductive Degeneration        | 90  |

|                |          | С.         | Circuit Measurements                                          | 94  |

| IV.            | Conclu   | usion      |                                                               | 97  |

| ۷.             | Refere   | ences      |                                                               | 98  |

| Chapter 3: Tov | vards an | n Integrat | ed Ka-Band Front-End Module                                   | 101 |

| I.             | Impro    | ved Ka-B   | and SPDT Switch                                               | 101 |

|                | 1.       | Introdu    | uction                                                        | 101 |

|                |          | a.         | Limitations of Usual SPDT Switches                            | 101 |

|                |          | b.         | Prospects of Improvements                                     | 102 |

|                | 2.       | Integra    | ated Hybrid Coupler                                           | 103 |

|                |          | a.         | Overview of RF Couplers                                       | 103 |

|                |          | b.         | Couplers in 5G Front-End Modules                              | 104 |

|                |          | с.         | Design of an Integrated Ka-Band Hybrid Coupler                | 105 |

|                |          | d.         | Measurement Results                                           | 108 |

|                | 3.       | SPDT S     | witch Based on Hybrid Couplers                                | 108 |

|                |          | a.         | Principle of Operations                                       | 108 |

|                |          | b.         | Circuit Design                                                | 110 |

|                |          | с.         | Measurement Results                                           | 112 |

|                |          | d.         | Perspectives for Future Designs                               | 114 |

| ١١.            | New L    | ow Noise   | e Amplifier and Co-Integration Perspectives                   | 115 |

|                | 1.       | Improv     | ved Ka-Band LNA                                               | 115 |

|                |          | a.         | Limitations of the First LNA                                  | 115 |

|                |          | b.         | Design of the Second LNA                                      | 116 |

|                |          |            |                                                               |     |

#### Table of Contents

|               |            | C.      | Circuit Measurements              | 119 |

|---------------|------------|---------|-----------------------------------|-----|

|               |            | d.      | Conclusions                       | 122 |

|               | 2.         | Towar   | ds an Integrated Front-End Module | 123 |

|               |            | a.      | Overview                          | 123 |

|               |            | b.      | Perspectives for Co-Integration   | 123 |

| III.          | Conclu     | usion   |                                   | 124 |

| IV.           | Refere     | ences   |                                   | 125 |

| Conclusion an | d Perspe   | ctives  |                                   | 127 |

| I.            | Summ       | ary     |                                   | 127 |

| ١١.           | Perspe     | ectives |                                   | 128 |

| III.          | Publica    | ations  |                                   | 129 |

| Résumé and A  | Abstract . |         |                                   | 130 |

**1G = First generation of mobile communications** 2G = Second generation of mobile communications 3G = Third generation of mobile communications 4G = Fourth generation of mobile communications 3GPP = 3G partnership project 5G = Fifth mobile communication generation AMPS = Advanced mobile phone system AP = Access point BB = Base band **BC = Body Contact BEOL = Back end of line BOX = Buried Oxide** BSIMSOI = Berkley short-channel IGFET model SOI CAGR = Compound annual growth rate **CAPEX = Capital expenditure** CDMA-One = Code division multiple access one CG = Common gate CMOS = Complementary metal oxide semiconductor **CRAN = Cloud radio access network** DAC = Digital to analog converter D-AMPS = Digital – advanced mobile phone system DCS = Digital cellular system **DIBL = Drain-induced barrier lowering** DMBA = Digital multi-beam antenna EDGE = Enhanced data rates for GSM evolution eMBB = Enhanced mobile broadband ESAR = Electronically steered array radar ETSI = European telecommunication standards institute E-UTRAN = Evolved universal terrestrial radio access network

| EVM = Error vector magnitude                  |

|-----------------------------------------------|

| FB = Floating body                            |

| FD = Fully depleted                           |

| FDD = Frequency division duplex               |

| FDMA = Frequency division multiple access     |

| FEM = Front-end module                        |

| FET = Field effect transistor                 |

| FoM = Figure of merit                         |

| FSPL = Free space path loss                   |

| GND = Ground                                  |

| GPRS = General packet radio service           |

| GSG = Ground-signal-ground                    |

| GSM = Groupe speciale mobile                  |

| HBT = Heterojunction bipolar transistor       |

| HLC = Home location register                  |

| HR = High resistivity                         |

| HSDPA = High-speed downlink packet access     |

| HSPA = High-speed packet access               |

| HSUPA = High-speed uplink packet access       |

| IC = Integrated circuit                       |

| IF = Intermediate frequency                   |

| IGFET = Insulated gate FET                    |

| IL = Insertion loss                           |

| IMS = IP multimedia system                    |

| IoT = Internet of things                      |

| IP = Internet protocol                        |

| IS-95 = Interim standard 95                   |

| IMT = International mobile telecommunications |

| ISD = Inter site distance                     |

| ITU = International telecommunication union   |

| ITU-R = ITU radio-communication sector        |

| KPI = Key performance indicator               |

|                                               |

| LNA = Low noise amplifier                             |  |

|-------------------------------------------------------|--|

| LO = Local oscillator                                 |  |

| LOS = Line of sight                                   |  |

| LP = Low power                                        |  |

| LTE = Long term evolution                             |  |

| LTE-A = Long term evolution – advanced                |  |

| MBA = Multi-beam antenna                              |  |

| MBPAA = Multi-beam phased array antenna               |  |

| MCS = Modulation and coding scheme                    |  |

| MEMS = Micro electro-mechanical systems               |  |

| MHC = Measurement to hardware correlation             |  |

| MIMO = Multiple-input multiple-output                 |  |

| mMTC = Massive machine type communications            |  |

| MOM = Metal-oxide-metal                               |  |

| NF = Noise figure                                     |  |

| NLOS = Non-line of sight                              |  |

| NMT = Nordic mobile telephone                         |  |

| NYU = New York university                             |  |

| O2I = Outdoor to indoor                               |  |

| OFDMA = Orthogonal frequency division multiple access |  |

| OPEX = Operational expenditure                        |  |

| OS = Open-short                                       |  |

| PA = Power amplifier                                  |  |

| PAE = Power added efficiency                          |  |

| PAPR = Peak to average power ratio                    |  |

| PBO = Power back-off                                  |  |

| PD = Partially depleted                               |  |

| QAM = quadrature amplitude modulation                 |  |

| QoS = Quality of service                              |  |

| QPSK = Quadrature phase shift keying                  |  |

| RFFE = Radio frequency front-end                      |  |

| RTPS = Reflection-type phase shifter                  |  |

|                                                       |  |

5G 28 GHz High Efficiency Integrated Phased Array Transceivers

| RX = Reception / | / Receiver |

|------------------|------------|

|------------------|------------|

- SDMA = Spatial division multiple access

- SMS = Short message service

- SNR = Signal to noise ratio

- **SOI = Substrate on insulator**

- SOS = Substrate on sapphire

- SPDT = Single pole double throw

- TACS = Total access communication system

- **TDD = Time division duplex**

- TDMA = Time division multiple access

- TL = Thru-line

- TR = Trap-rich

- TRL = Thru-reflect-line

- TRx = Transceiver

- TX = Transmission / Transmitter

- UE = User equipment

- ULA = Uniform linear array

- UMi = Urban micro

- UMTS = Universal mobile communication system

- URA = Uniform rectangular array

- URLLTC = Ultra-reliable and low latency communications

- UTBB = Ultra-thin body and BOX

- WCDMA = Wideband code division multiple access

- WRC-19 = 2019 world radio conference

### Introduction

The limitations of the current mobile communication generation (4G) are being reached. Indeed, the available bandwidth in the sub 6 GHz spectrum is no longer sufficient to cope with the increasing needs of higher data rates and more simultaneous users. Thus, a new generation is being developed: 5G. It will target different use cases from internet of things to high data rate communications, including critical applications such as autonomous vehicles and remote surgery. To cope with these highly demanding needs, innovative solutions are being studied. This thesis work focuses on the high data rate use case. The expected improvements to meet the specifications are the use of the millimeter-wave spectrum, network densification, and spatial multiplexing. This leads to degraded circuit performances, and to the need of many more components. Indeed, the number of required front-end modules may be a hundred times higher due to network densification and up to a thousand times higher due to the implementation of phased array transceivers. Consequently, this leads to drastic increases of the network deployment cost and the global power consumption. However, the use of phased arrays enables to relax the system requirements, and therefore its power consumption. Besides, it also enables to move from III-V circuits to less expensive advanced CMOS technologies. Hence, the aim of this thesis is twofold: determine the best suitable system architecture, meeting high data rate 5G requirement while minimizing the power consumption; and design millimeter-wave circuits using an advanced CMOS technology. It is targeted to implement RF switches and low noise amplifiers for 5G base station front-end modules

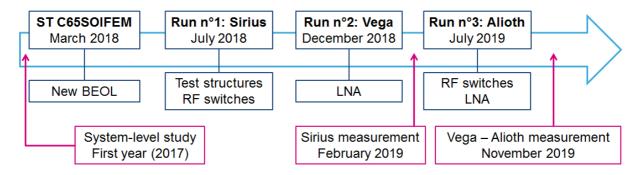

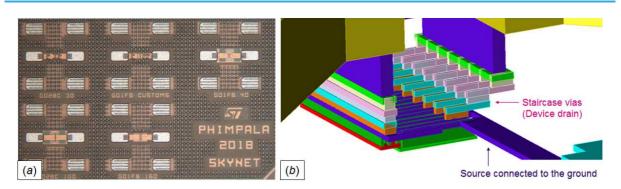

The first chapter is dedicated to the system-level study. Firstly, a use case is defined among the different 5G scenarios: high data rate communications in crowded urban environment. Then, a methodology to derive the system-level specifications from the standard early requirements is implemented. It is applied to the selected use case. Thus, several base station architectures meeting the specifications have been identified. Finally, a new methodology has been developed in order to estimate the power consumption of the different solutions. This enables to determine the best suitable topology in terms of performances and costs for a defined use case. Finally, it is applied to the selected scenario. However, both developed methodologies may be extended to other 5G scenarios, since they are easily scalable. The following chapters detail the design of millimeter-wave switches and low noise amplifiers for 5G front-end modules. The selected advanced CMOS technology is also presented. Besides, several runs have been achieved during this thesis work. They are depicted in Figure 0.

*Figure 0: Overview of the runs achieved during the thesis work*

The second chapter presents the circuits implemented in the first two runs (Sirius and Vega). The first aims are to characterize the new *ST C65SOIFEM* technology and to validate its suitability for the design of millimeter-wave front-end modules. Thus, several test structures and series-shunt RF switches are implemented and measured. A Ka-band low noise amplifier is also designed. These first steps enable to test the technology model accuracy and to validate the design methodology.

In the third chapter, improved versions of the RF switches and the Ka-band low noise amplifier are presented. Indeed, several drawbacks of the first designed circuits have been highlighted by accurate retro-simulations. A new asymmetrical RF switch is therefore designed, offering both low insertion loss and high power handling. The low noise amplifier is also improved to provide lower noise figure and higher gain, with consistent power consumption. These circuits are implemented in the third run, known as Alioth. After the analysis of the measurement results, some co-integration perspectives are discussed.

## Chapter 1: From 5G Expectations to FEM Specifications

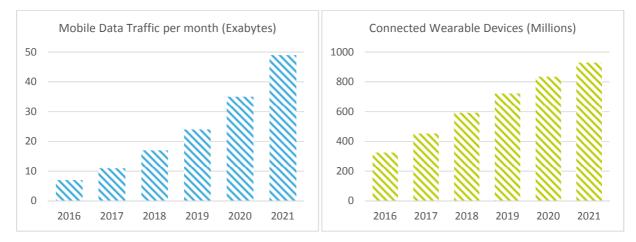

Daily life is increasingly a connected life. From the smartphone massive adoption to the rapid emergence of the internet of things (IoT), people have ever more connected objects, which require ever more data rate. In [1], Cisco expects 47% compound annual growth rate (CAGR) for mobile data traffic between 2016 and 2021. It is assumed that more than 80% of these data will be spent through smartphones. Moreover, 23% CAGR is expected for connected wearable devices as shown in Figure 1.

Figure 1: Mobile data traffic per month and global connected wearable devices, from [1]

To cope with the exponential number of connections and the rise of many new applications, an innovative solution is needed. That's why the fifth mobile communication generation (5G) is being developed. As detailed in [2], this new standard is willing to unify the different medium of wireless communication. From connected health, to virtual reality, through autonomous vehicles, the challenges are diverse and complex. In order to clearly explain why 5G is a paradigm shift in the telecommunication world, this chapter starts with an overview of the previous generations from the beginning of mobile communications to the current long-term evolution advanced (LTE-A) network. Then, the different 5G key performance indicators (KPI's) and the main expected solutions are presented and discussed. The deployment timeline and the main market actors are also introduced.

Secondly, the scope of the thesis is defined choosing practical use cases among prospective scenarios. The main challenges for system design are highlighted, and the system-level specifications are determined depending on the chosen use case KPI's. A new flexible methodology is set up to size and compare topologies which fill the defined requirements. A key metric is introduced: system power consumption.

This chapter ends with a state of the art of 5G Ka-band transceivers for high data rate wireless communications. Then, the system power consumption model is detailed, and the best suitable architecture for the given scenarios is highlighted. Finally, some perspectives are given as the power consumption estimation refining, and the Ka-band integrated circuit design.

#### I. On the Road towards the Wireless Communication Paradigm Shift

#### 1. Legacy and Current Telecommunication Networks

#### a. 1G – The Foundation of Mobile Communications

The first generation of mobile communications (1G) was launched in the early 80's. It consisted in the analog modulation of user's voice, transmitted thanks to base stations, as presented in [3]. The major innovation was the ability to move while communicating. Even if 1G has disappeared today, the first mobile communication network laid the foundations for all the next generations.

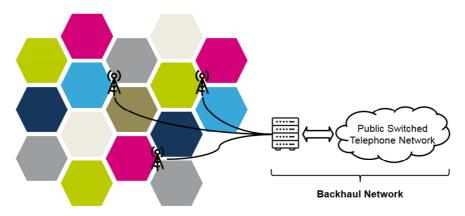

The main feature in 1G is the emergence of a cellular network. It is composed of base stations which defines the cells, and the backhaul network which coordinates the communications. The base stations are spread out over the territory. Each one operates at a defined frequency to avoid interferences between neighboring cells. The number of different frequencies used to mesh the area is called the cluster size. It is used to choose a cluster size about 7 to limit the inter-cell interferences with a minor number of reused frequencies. A cellular network with a cluster size of 7 is presented in Figure 2. Moreover, a base station usually operates at 3 different frequencies. It enables to cover 3 cells simultaneously.

Figure 2: Sectorized cellular network with a cluster size of 7 and connection to the backhaul network

In a given cell, the frequency band is divided in 30 kHz sub-channels. Each one could only handle one mobile communication. As users are accessing the spectrum, at the same time, with different frequencies, it is frequency division multiple access (FDMA). Moreover, large guard bands are necessary between sub channels to avoid user interferences. Consequently, the spectrum efficiency is very poor. Moreover, the mobility is limited due to the difficulty to manage the move from a cell to another, as known as hard handoff. The lack of security is also a major concern for 1G. Indeed, the analog voice modulation makes the communications easy to be intercepted and deciphered.

Besides, it is the emergence mobile communication standards. It defines the frequency bands dedicated to mobile communications, the sub-channel and guard band sizes, and the inter site distances. However, each world region has set up its rules without any compatibility between them. The best know are the Nordic mobile telephone (NMT) for Nordic countries, the advanced mobile phone system (AMPS) for North America and Australia, and the total access communication system (TACS) for the United Kingdom [**3**]. Nowadays, this standard has disappeared. It has been replaced by digital mobile technologies.

#### b. 2G – The Beginning of Digital Telecommunications

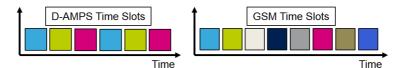

As it was the case for 1G, the second generation of mobile communications (2G) is composed of different standards, including, digital AMPS (D-AMPS) and *groupe speciale mobile* (GSM), which are improvements of AMPS and NMT, respectively. Their working principles are very similar. Both are based on time division multiple access (TDMA). With this new spectrum access technique, several users could share a sub-channel using different time slots. As shown in Figure 3, GSM sub-channels are split in 8 time slots. It could be shared by 7 different users. The last slot is dedicated to time synchronization, and short message service (SMS), whereas, D-AMPS slots could only be shared by 3 users. That's why the GSM standard, established by the European Telecommunications Standards Institute (ETSI) in 1990, has been quickly adopted in a great part of the world. Actually, it is made by 3 standards: GSM 900, GSM 1800, also known as digital cellular system (DCS), and GSM 1900. They respectively operate at 900, 1800, and 1900 MHz.

Figure 3: Sub-channel splitting in time slots for D-AMPS and GSM standards

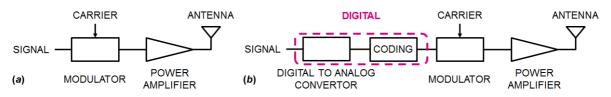

The main change compared with 1G is the shift from analog to digital modulation. It provides more security and flexibility. However, the transmitter and receiver architectures are more complex since an analog to digital conversion stage is needed as shown in Figure 4 for transmitters. It may be highlighted that 2G is the generation of mass mobile adoption thanks to technology scalability which reduces user terminal cost.

Figure 4: (a) Analog transmitter architecture; (b) Digital transmitter architecture

Moreover, up to [4], 2G has been improved twice to enable data transmissions. Firstly, with the general packet radio service (GPRS). The data rate is only between 9, and 21 kbps per time slot, and is limited to 40 kbps per user. GPRS is also called 2.5G as it is the first step towards the third generation (3G). Secondly, there is the enhanced data rates for GSM evolution (EDGE) which offers a data rate up to 60 kbps per time slot. This standard, sometimes known as 2.75G, could provide up to 200 kbps per user.

Figure 5: Transmission and reception of CDMA telecommunications

5G 28 GHz High Efficiency Integrated Phased Array Transceivers

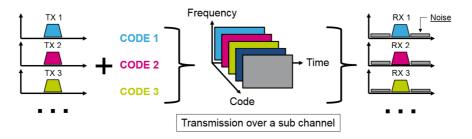

Finally, 2G laid another foundation for next generations with a less well-known standard: interim standard 95 (IS-95) also called code division multiple access one (CDMA One). First of all, this option was left behind due to GSM standardization. Then, its capacity, more than 4 times higher than GSM, makes it the favorite candidate for 3G. Actually, CDMA enables users to share the same time and spectrum resource thanks to a code assigned to each user in a sub channel. Consequently, the spectrum efficiency is considerably improved as shown in [3]. Figure 5 depicts the principle of CDMA standard. First of all, data for each user are coded independently before the transmission (TX). The signals are transmitted over a unique sub channel at the same time. Finally, each receiver (RX) deciphers the signal with its corresponding code. Thus, desired data are received and the others are dissolved in the noise.

#### c. 3G – Towards Broadband Mobile Communications

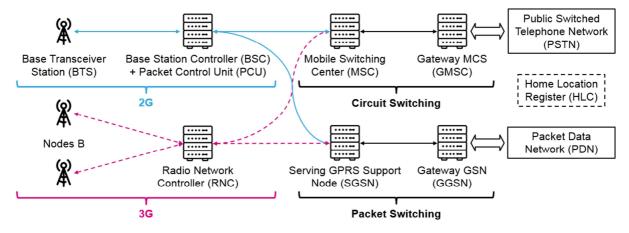

Due to its popularity, 2G quickly reached its limitations. So, a new standard has been launched to cope with the significant demand: the universal mobile communication system (UMTS). Firstly, 3G has been standardized by ETSI. Then the *IMT-2000* project defined the standard rules. It was led by the 3G partnership project (3GPP) forum, and the international telecommunication union (ITU). Initially, two candidates, both inspired by CDMA One, were competing. The most popular is wideband code division multiple access (WCDMA), which was then replaced by high-speed packet access (HSPA) as mentioned in [3]. It is also known as "Release 5". It is important to notice that 3G is complementary with the previous generation. The new base stations (known as Node B) are deployed in crowded areas to provide broadband communications and enhanced internet access. Whereas 2G still covers large part of the territory with reliable communications. Even if new base stations are deployed, the core network is shared by the two co-existing standards, as presented in Figure 6. Voice and data from both 2G and 3G base stations are respectively split towards circuit and packet switching. This kind of network implies the deployment of an expensive backhaul, based on optical fiber. Finally, the home location register (HLC) manages mobile authentication on the network, and route signals towards the proper nodes. It is the emergence of the signal control plane.

Figure 6: Presentation of the co-existing 2G and 3G networks

HSPA has evolved twice. Firstly, with high speed downlink packet access (HSDPA) to improve data rates from the base station to the user terminals up to 63 Mbps. Secondly, with high-speed uplink packet access (HSUPA) to enhance uploading from mobile phones [4]. The merge of these two standards is known as HSPA+.

#### d. 4G – Towards a Unique Mobile Communication Standard

Today, 3G is widely deployed and provides a reliable data rate. However, the use of 5 MHz channels is mandatory with HSPA+. Consequently, flexibility is limited [5]. Moreover, the theoretical channel capacity limit, defined by C. Shannon in 1948, has been reached. It is given by *Equation (1)*, where C (bit/s) is the channel capacity limit, B (Hz) is the available spectrum, and S/N is the signal to noise ratio before the demodulation, i.e. at the end of the receiving chain.

$$C = B \cdot \log_2\left(1 + \frac{S}{N}\right) \tag{1}$$

The emergence of the fourth generation of mobile communications (4G), also known as Long Term Evolution (LTE), is therefore motivated by the needs of higher capacity and flexibility. To face these challenges, several innovations are implemented. Firstly, a new spectrum access technique is used: orthogonal frequency division multiple access (OFDMA). It consists in splitting the signal over different sub-carriers, which are orthogonal to avoid interferences. It is combined with carrier aggregation, that is, several distinct sub-carriers could be used for the same user. Consequently, the sharing of time and frequency domains is very flexible. Secondly, LTE has introduced the use of several antennas, whereas previous generations had only one antenna broadcasting the signal for its whole cell. These kinds of systems are called multiple-input multiple-output (MIMO). It could operate in different modes, providing higher reliability, or improving the channel capacity. The Shannon's law is updated as in Equation (2), with M the number of transmitting antennas [4].

$$C = M.B.\log_2\left(1 + \frac{S}{N}\right) \tag{2}$$

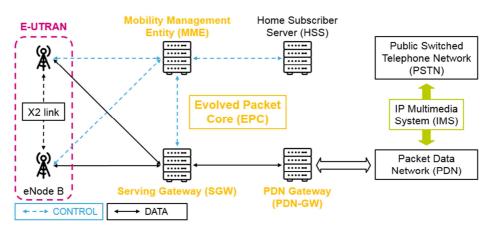

Furthermore, LTE introduces major changes in network architectures. As presented in Figure 7, the base stations (named eNode B) are now connected between them thanks to X2 links. This new radio interface is called evolved universal terrestrial radio access network (E-UTRAN). The core network has also evolved. Data and control planes are split in order to highly reduce network latency. Finally, the IP (internet protocol) multimedia system (IMS) enables to merge voice and data. This unification into a single communication protocol makes a break, since previous generations started with different standards. However, LTE and its enhanced version (LTE-A) have to face spectrum congestion [6], as shown in Figure 8.

Figure 7: Presentation of the LTE network

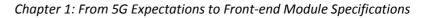

Figure 8: Simplified view of frequency spectrum users in France, from 800 MHz to 5.8 GHz

Finally, LTE-A provides high data rates, and improves network capacity. Network latency is also highly reduced. However, the mobile communications are still concentrated in the crowded sub-6 GHz spectrum. Moreover, the current standard is, as for previous generations, cell-phone focused. Thus, it is no longer appropriated regarding to the emerging applications such as IoT. LTE-A is also requiring more energy than the previous standards. In [7], it is shown that LTE-A power efficiency is 23 times worse than Wi-Fi, and even worse than 3G. To conclude, reducing the network power consumption while including the emerging mobile uses will be the major concern of the next mobile communication generations.

#### 2. 5G Overview

#### a. The Emergence of 3 Standards

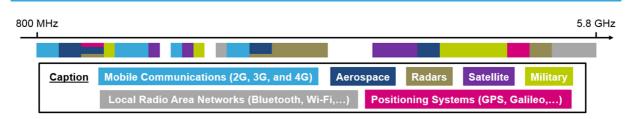

The upcoming 5G standard aims to reach unprecedented performance levels, as 20 Gbps peak data rate, or 10 million connections per km square. These targets have been defined by the radio-communication sector of international telecommunication union (ITU-R) in [8]. They launched the international mobile telecommunications (IMT) 2020 project, capitalizing on IMT 2000 (i.e. 3G), and IMT-Advanced (i.e. 4G), to set up 8 KPI's for 5G. Figure 9 presents these indicators, and gives a comparison with current levels. As these targets are too high to be reached simultaneously, 3 usage scenarios are defined.

Figure 9: 5G KPI for 3 Different Scenarios

• <u>Enhanced mobile broadband (eMBB)</u>: This first scenario is focused on high data rate communications for mobile user terminals. Consequently, high requirements are set on peak data rate, and area capacity. To reach the targets, spectrum efficiency has to be improved 3 times compared with LTE-A.

The implementation of a new network architecture is also scheduled. It will improve the user experience, including at cell edges. Besides, it is expected to severely reduce the global power consumption and increase the user mobility.

- <u>Ultra-reliable and low latency communications (URLLTC)</u>: This second scenario is designed for critical applications such as health robotics, energy infrastructures, or factory processes. High reliability and extremely low latency are required. Up to [2], some use cases may also require important mobility (autonomous cars), or high data rates (collaborative gaming).

- <u>Massive machine type communications (mMTC)</u>: Finally, the last case is tailored for large IoT networks, including wearable and e-health devices, or home and factory sensors. Consequently, massive connection density is needed in addition to good energy efficiency to ensure adequate operating time.

In a nutshell, 5G is pursuing the telecommunication standard unification as shown in [4]. On the one hand, it tends to build a whole connected world, but on the other hand, the demanding KPI's imply a splitting into three less demanding scenarios, which are closer to the usual mobile standard vision.

#### b. EMBB Spectrum and Network

This thesis work focuses on the EMBB scenario. Particularly, it is about providing extreme data rates into highly populated areas, while reducing the network latency, and the global power consumption. Furthermore, these researches are concentrated around the base station, i.e. on the radio interface (communications with the user), and on the backhaul (communication between base stations, and the core network). Consequently, mobility is not an EMBB targeted KPI here.

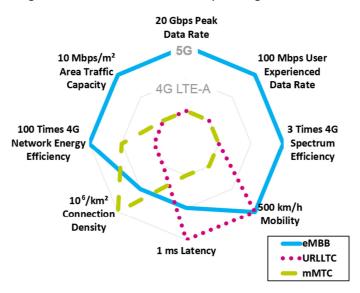

The first way to obtain higher data rates and network capacity is to use larger frequency bands, as shown by *Equation (2)*. But, as shown previously in Figure 8, the sub-6 GHz spectrum is very crowded. Even if a wide frequency band has been booked between 3.4 and 3.8 GHz for 5G, it is not enough to cope with the demanding requirements. Consequently, it is expected to move towards millimeter-wave [6]. Several bands, presented in Figure 10, have been identified during the 2019 world radio conference (WRC-19).

Figure 10: Millimeter-wave frequency bands (in GHz) selected at WRC-19

However, the use of higher frequencies for mobile communications also implies serious challenges. Firstly, as presented by *Equation (3)*, the wireless channel free space path loss (FSPL) increases with the signal frequency and the link length. In this equation, also known as Friis formula, *FSPL* is in dB, and the propagation distance (*R*) and signal wave length ( $\lambda$ ) are both given in meters. The additional FSPL between usual LTE ( $f_1$  = 2600 MHz) and 5G ( $f_2$  = 28 GHz) communications is computed in *Equation (4)*. Considering the same range for both links, the additional losses are 20.6 dB. It should be noticed that the path loss given in *Equation (3)* is a negative value in dB, since it accounts for power attenuation.

$$FSPL = 20.\log\left(\frac{\lambda}{4\pi R}\right) \tag{3}$$

5G 28 GHz High Efficiency Integrated Phased Array Transceivers

Chapter 1: From 5G Expectations to Front-end Module Specifications

$$FSPL_1 - FSPL_2 = 20.\log\left(\frac{\lambda_1}{\lambda_2}\right) = 20.6 \text{ dB}$$

(4)

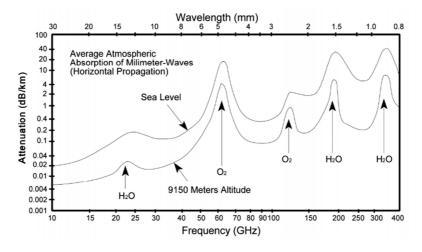

Secondly, as shown in Figure 11, the losses due to the atmospheric absorption are also stronger at higher frequencies. Actually, signal absorption increases with the frequency for the usual materials (air, water, glass, concrete, and wood) [9]. The additional atmospheric losses are not significant, but they are much stronger for other materials. For example, glass and concrete penetration losses are respectively 5.1 dB and 101.6 dB higher at 28 GHz compared with LTE (2600 MHz), for a typical building wall. Channel modeling is also more challenging at higher frequencies.

Figure 11: Average atmospheric absorption, from everythingrf.com

An accurate model for 5G communication channels is given in [9]. It includes the distinction between line of sight (LOS) and non-line of sight (NLOS) propagation within different environments. For the urban use case; the probability to have direct LOS between the access point (AP) and the user equipment (UE) is about 60% at 50 m, and decreases below 15% from 200 m. The associated NLOS propagation penalties are respectively 39 dB, and 53 dB. Consequently, it has a major impact on the communication reliability.

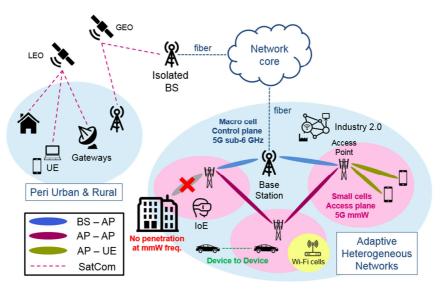

Figure 12: 5G Network, including small cells, and control and user plane splitting

To cope with the limited range of mm-wave communications, and to deal with the significant rise of user density, a new network architecture is needed. Several expected innovations are introduced in [10]. The first improvement is the implementation of many mm-wave small cells which provide high data rates in very crowded areas. This enables to shift from a base station centric to a user-centric network. Actually, the adaptive cells could change their configuration to fit properly with user density and to offer high quality of service (QoS) even at cell edges. Secondly, the split between control and user planes is stronger than previously. It is expected to route mm-wave signals from base stations to the core network. Consequently, the baseband processing is pushed out of the access point. This reduces both deployment complexity and network latency. The centralization of processing steps into virtual baseband unit pools is called cloud radio access network (CRAN). Finally, 5G also expects to benefit from the existing Wi-Fi network, particularly indoor, to offload outdoor facilities. The expected 5G network is shown in Figure 12.

To conclude, small cell densification enables to reduce the inter site distance to cope with high path loss but it also implies higher costs for mobile operators. In fact, more base stations have to be deployed and connected with the others so the capital expenditure (CAPEX) is increased. However, this cost is reduced thanks to CRAN and mm-wave backhauling. Actually, it replaces the usual fiber links which are very expensive. The global power consumption is also more important. Thus, the operational expenditure (OPEX) rises. Low-power small cell transceivers are required to minimize the operating costs. Finally, high interoperability with current LTE-A, and Wi-Fi standards is needed to optimize user quality of experience.

#### c. Beamforming: a Key Enabler

The use of mm-wave frequencies unlocks vast amounts of bandwidth but it also brings major drawbacks as propagation issues and lower circuit performances. However, the smaller wavelength is, the smaller the antennas are. Thus, it is possible to simultaneously use many antennas to improve the transceiver ranges, and support the network densification. This is the so-called beamforming. As proven in [11] with *Equation (5)*, the maximum antenna array directivity ( $D_{max}$ ) depends on the signal wave length ( $\lambda$ ) and array area (A). Thus, for a given transmitting antenna area, the frequency increase offers more advantages than drawbacks.

$$(D_{max})_{dB} = 20 \cdot \log\left(4. \pi \cdot \frac{A}{\lambda^2}\right)$$

(5)

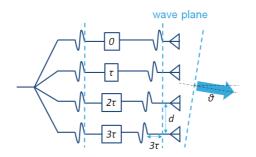

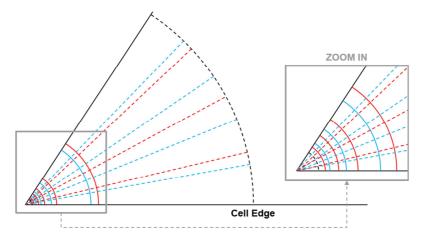

In addition to a significant directivity increase, beamforming enables to dynamically modify the direction of the beam. As shown by Figure 13, the signal is divided among several paths. Then, it is delayed, and emitted through the antennas. Finally, the transmitted signals are combined over the air to form a focused beam. In uniform linear arrays (ULA), as illustrated in Figure 13, elements are equally spaced. Thus, the delays vary proportionally, from a line to the nearby one. For a ULA composed of  $N_{el}$  half wavelength spaced elements, the beam steering ( $\vartheta$ ) is given by *Equation (6)*. It depends on the element spacing (d), the wave speed (c), and the set delay ( $\tau$ ). Moreover, the 3 dB beam width ( $\vartheta_3$ ) is defined in *Equation (7)* for this kind of array. Consequently, larger arrays allow establishing more directive communications. This introduces spatial division multiple access (SDMA), i.e. the ability to spatially separate different users. Finally, for narrow band signals, i.e. if bandwidth is much lower than the carrier frequency, the time delay could be approximate by phase shifting ( $\varphi$ ) as in *Equation (8)*.

Figure 13: Beamforming operating principle

$$\vartheta = \sin^{-1}\left(\frac{c.\tau}{d}\right) \tag{6}$$

$$\vartheta_3 = \frac{1.772}{N_{el} - 1} \tag{7}$$

$$\varphi = \tau \cdot \left(\frac{2\pi \cdot c}{\lambda}\right) \tag{8}$$

The beamforming principle is applicable for both the transmitting and receiving arrays. *Equations (9)* and (10), respectively from [12] and [13], demonstrate the benefits of these topologies. The received signal on each antenna is delayed and then combined to increase the signal-to-noise ratio (SNR) and filter uncorrelated noise. As a result, the receiving array noise figure ( $NF_{array}$ ) is improved compared with the noise figure of a single element ( $NF_{el}$ ). Likewise, the array effective isotropic radiated power ( $EIRP_{array}$ ) is improved regarding to the elementary antenna radiated power ( $EIRP_{el}$ ).

$$NF_{array}(dB) = NF_{el}(dB) - 10.\log(N_{el})$$

<sup>(9)</sup>

$$EIRP_{array}(dB) = EIRP_{el}(dB) + 20.\log(N_{el})$$

<sup>(10)</sup>

In a nutshell, larger arrays enable to overcome mm-wave communication drawbacks. Also, it introduces a new spectrum access technique. However, larger systems imply many more circuits. Depending on the chosen topology, overall power consumption and system complexity may increase in varying degrees. Indeed, several architectures are able to achieve beamforming. Up to [14], the first ones had been introduced in the early 1900's by K. F. Braun, for radar purpose. It consisted in a fixed beam, generated by a bulky and lossy passive phase shifter network. Then, the beam could be steered mechanically.

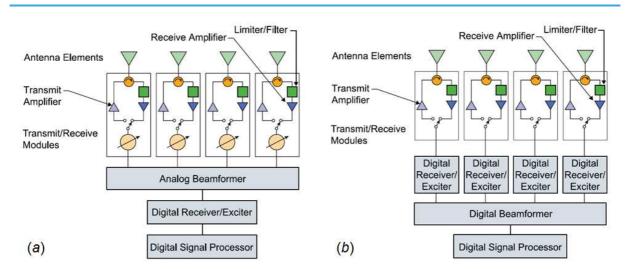

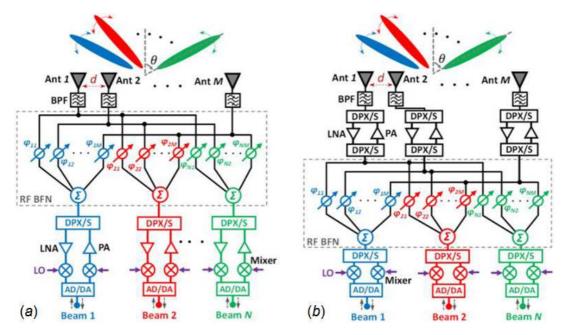

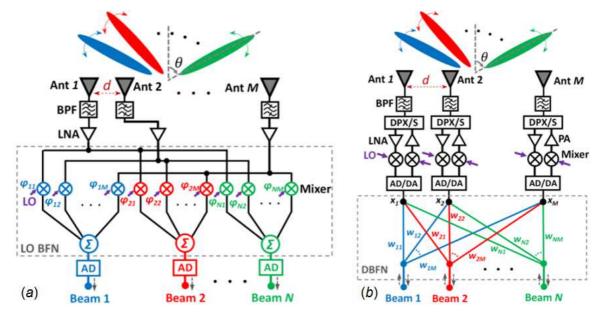

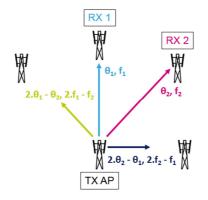

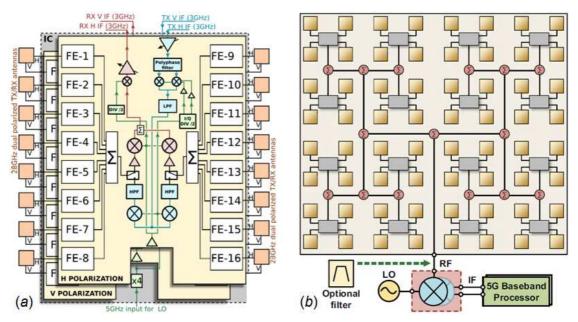

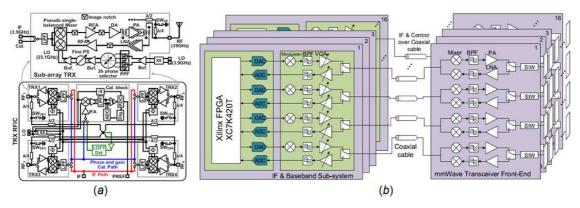

Since the 1940's, the beam could be steered changing the phase shift electronically. But the beamforming network is always behind the power amplification stage. Consequently, much power is lost causing power dissipation. A famous example is the electronically steered array radar (ESAR) designed in 1958. It has only been in the 1980's that phased array technology shifts from passive to active systems, thanks to circuit scaling. Actually, it was possible to integrate phase shifters or time delays before the amplifier to design more compact systems with better energy efficiency. This topology is illustrated in Figure 14 (*a*). Another consequence on phase shifter integration is the opportunity to move it towards lower frequencies, i.e. before the transmitter up conversion. It is also possible to operate the phase shifting in the local oscillator path. By the way, it is the case for the first fully integrated CMOS phased array receiver and transmitter introduced in [12] and [13], respectively. By now, phased arrays are going to become more digital thanks to the scaling of silicon technology nodes, significantly increasing the processing capabilities, as illustrated in Figure 14 (*b*).

#### Chapter 1: From 5G Expectations to Front-end Module Specifications

Figure 14: (a) Modern analog transceiver architecture; (b) Digital phased array transceiver architecture

#### d. The 5G Standardization Timeline

Following the general mobile standardization trend, 5G is expected to be released around 2020. Whereas previous generations have led the market, the 5G advent is triggered by the emergence of new uses. It could explain the large gap between current mobile networks and the next generation requirements. As shown in Figure 15, the deployment is expected to be very progressive, to cope with this large step. Since WRC-15, which has set the first 5G requirements, directions for below 6 GHz standardization, and recommendations for mm-wave frequency bands, many trials have been conducted. Up to [15], 40% of these trials are performed below 6 GHz, and 31% in the 24 – 29.5 GHz frequency band.

Figure 15: 5G Deployment Timeline, based on ARCEP Expectations [2]

As summarized in [10], market players have different targets. For example, *Qualcomm's* vision is focused on enabling new uses and improving user experience, while *Samsung* is focused on multimedia experience and IoT, and *Huawei* on massive capacity and network deployment. Moreover, the mobile terminal market is split between sub 6 GHz, and mm-wave system vendors. There are few actors able to provide mm-wave circuits. Up to [16], *Qualcomm* leads the market with the *QTM525* radio frequency front-end (RFFE), and the *Snapdragon X55* modem. More recently, *Qualcomm* have introduced the *Snapdragon X60* [17]. This 5G modem-RF system based on the 5 nm process node enables to aggregate the sub 6 GHz and mm-wave spectrums. Then, some players are focused on modems, as *Samsung* with its *Exynos 5100*, and *Intel* with its *XMM 8160*. Others provide RFFE's as *Qorvo*, or *SkyWorks*.

However, the big 5G challenge is to ensure high network capacity. In this context, *Ericsson* has presented the first integrated mm-wave phased array antenna module in [18]. *Anokiwave* is also an early actor in mm-wave phased arrays [19]. For now, they exhibit a complete offer including beamforming ICs and

front-ends, for macro cells and small cells operating in the 28 GHz and 39 GHz frequency bands. They have developed advanced features such as the *zero-cal* technology and the *kinetic-green* functionality which reduce respectively the system complexity and power consumption [20]. Besides, *Movandi* has designed the *BeamX* module, including amplifiers and frequency converters. It is used with a repeater (*BeamXR*) to optimize NLOS communications. Finally, *SatixFy* has developed the first fully digital commercial beamformer, which confirms the digitalization of such systems [20]. For now, their 256 element array is only dedicated to satellite communications in the Ku-band (12 – 18 GHz). These first 5G developments are advertised by major public events, as 2018 Winter Olympics in PyeongChang and 2021 Olympics in Tokyo.

To summarize this overview, 5G is expected to be a paradigm shift in the wireless communication world, led by the ever more connected society. To fill the demanding requirements, the network will firstly be deployed in the current sub 6 GHz spectrum. At the same time, mm-wave trials are performed to prepare the move to higher frequencies.

#### II. From 5G EMBB Expectations to System-Level Specifications

1. Thesis Use Case: Definition & Challenges

#### a. Chosen Scenarios

Since 5G is a broad standard, with a lot of applications and as many frequency bands, it is necessary to bound the study with clear use cases. This work focuses on mm-wave frequency bands, as the sub 6 GHz network is currently being deployed. Consequently, the main target is providing high data rates in very crowded areas. As presented in Figure 9, based on ITU-R recommendations [8], it is expected to provide a 10 Tbps/km<sup>2</sup> network capacity. Moreover, the data rate offered to each user has to be at least 10 Mbps, and should reach 20 Gbps in optimum cases. These requirements are consistent with current population densities. For cities like Paris or West New York, it is about 20 000 people per km<sup>2</sup> [21].

One of the key principles of 5G radio access network is significant access point densification. Consequently, it is important to determine how many users will be related to each small cell. The cell different radiuses are detailed in [22]. Results are reported in Table 1.

| Cell Type  | Radius       | Number of Users | Location |

|------------|--------------|-----------------|----------|

| Femto Cell | 10 to 100 m  | Up to 30        | Indoor   |

| Pico Cell  | 100 to 200 m | From 30 to 100  | Indoor & |

| Micro Cell | 0.2 to 2 km  | 100 to 2000     | Outdoor  |

Table 1: Mobile cell features for different kind of cells

To conduct an accurate study, the following work is limited to pico cells. However, the system sizing methodology is suitable for other scenarios. Considering an inter site distance (ISD) of 100 m, the cell density is about 100 cells/km<sup>2</sup>. It implies a 100 Gbps/cell capacity, i.e. simultaneously providing 1 Gbps to 100 users in a single cell. Likewise, cells with ISD of 200 m have to deal with 400 concurrent users. These use cases are reported in Table 2, considering 6 sectors per access point.

| Inter Site<br>Distance | Cell Density | Users / Cell | User Data Rate | User / Sector |

|------------------------|--------------|--------------|----------------|---------------|

| 100 m                  | 100 /km²     | 100          | 1 Gbps         | 17            |

| 200 m                  | 25 /km²      | 400          | 0.3 Gbps       | 67            |

Table 2: Identified 5G scenarios

Finally, the chosen operating frequency, among available mm-wave bands, is 28 GHz. This allows taking benefit from the many recent developments. Based on previous parts, the mm-wave access point is mainly composed of the phased array transceiver. It both provides data for users, and ensures low-cost backhaul with fast deployment. Consequently, this work also takes into account AP to AP links.

#### b. First 5G Standard

The 5G standardization has been started in 2017 by the ETSI, with Release 15 [23]. The aim of this first release is to meet the crucial market needs thanks to existing technologies. Thus, it includes detailed guidelines for the sub 6 GHz spectrum and sparse directions for mm-wave frequencies (24.25 – 27.5, 26.5 – 29.5, and 37 – 40 GHz). Indeed, mm-wave system requirements are only given over the air, i.e. after the transmitting antenna array. These partial guidelines include the maximum channel bandwidth (400 MHz), the receiver sensitivity (from -86 to -109 dBm), and the maximum error vector magnitude (EVM) depending on the signal modulation (17.5% for QPSK, 12.5% for 16-QAM, and 8% for 64-QAM). But some requirements are missing, as the maximum EIRP for the different kinds of small cells. This lack of information is expected to be bridged with Releases 16 (June 2020) and 17 (September 2021). They should target respectively the mm-wave use cases and the mMTC applications.

#### c. Challenges

The design of mm-wave systems for 5G small cells implies several challenges. Firstly, the requirements are very demanding, whereas the standardization is only at the beginning. It is therefore necessary to set up a sizing methodology to determine the system-level specifications. Then, the many studied solutions have to be compared. It enables to select the best suited solution for 5G small cell deployment. Finally, the significant densification implies high CAPEX and OPEX which have to be reduced. Thus, the design of 5G systems require a particular care about the overall power consumption.

#### 2. Sizing Methodology for mm-Wave 5G Small Cells

#### a. Step 1 – Introduction

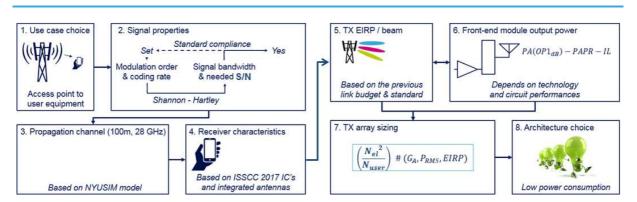

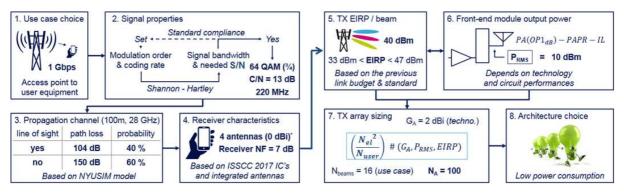

5G requirements are expected to be as broad as demanding. Thus, a new sizing methodology has been developed in this work. It enables to derive the system-level specifications from the early requirements. This methodology is summed up in Figure 16. It starts with the use case definition. Here, the previously presented use case is chosen. However, the sizing method may be applied to different requirements. The next steps are detailed in the following sections: the analysis of signal properties (modulation order, coding rate, and bandwidth) and propagation channels. Then, a link budget is performed. It is based on the performances of recently reported circuits, and it leads to the array sizing. Finally, the overall power consumption of the different phased array architectures is estimated to select the best suitable.

#### Chapter 1: From 5G Expectations to Front-end Module Specifications

Figure 16: Main steps of the 5G access point sizing methodology

#### b. Step 2 – Signal Properties

This step consists in determining the optimal modulation and coding scheme (MCS), i.e. the modulation order, and the coding rate, which are respectively represented by M, and  $C_R$  in the following equations. It is important to notice that antenna arrays are supposed to operate in beamforming mode. So, the network capacity is only increased due to higher SNR. Actually, this kind of transceiver does not bring diversity as it is the case with previously presented MIMO systems. Consequently, the Shannon's law is applied using *Equation (1)*, not *Equation (2)*. It is reminded that these equations are valid for additive white Gaussian noise channels. Finally, the communication channels are supposed to be independent for each user, as it is the case in [24] with the use of orthogonal beamforming. Consequently, the maximum data rate per user, termed  $R_{USER}$ , is equivalent to the channel capacity. This is expressed in *Equation (11)*. Moreover, *Equation (12)* gives the relation between the signal bandwidth, the data rate, and the MCS.

$$R_{USER} = B * \log_2\left(1 + \frac{S}{N}\right) \tag{11}$$

$$B = \frac{R}{C_R * \log_2(M)} \tag{12}$$

These equations enable to compute the required signal to noise ratio (*S/N*) and bandwidth (*B*) to ensure the targeted user data rate. The results for different MCS are reported in Table 3. This includes communications up to 2 Gbps for backhauling. The first remarkable result is that *S/N* only depends on the MCS. This could be shown thanks to *Equation (13)*, which is a combination of *Equation (11)*, and *Equation (12)*. Moreover, a lower coding rate implies a higher reliability but also a higher bandwidth. Consequently, the *S/N* requirements are relaxed. It stresses the tradeoff between signal bandwidth and required *S/N*, which both impact the system power consumption.

$$\log_2\left(1+\frac{S}{N}\right) = C_R * \log_2(M) \tag{13}$$

Based on prior 5G specifications, which expected channel bandwidths about 100, 200, and 400 MHz, the 16-QAM modulation has been chosen for 300 Mbps communications, with 7/8 coding rate. It enables to minimize the occupied bandwidth, with relaxed EVM requirements regarding to 64-QAM. Likewise, higher data rates could be reached using the same coding rate, with higher modulation orders. However, the latest specifications suggest using lower *CR* to improve reliability [23]. Consequently, the coding rate is reduced to 3/4 for 300 Mbps communications, using 16-QAM. For higher data rates, i.e. higher

modulation orders, it is chosen to decrease  $C_R$  to 2/3. Thus, the maximum throughput per beam is 1.6 Gbps to respect the 400 MHz bandwidth limitation. Based on this knowledge, several beams may be required for backhaul. As these links should often be in LOS, the coding rate may be increased to reduce the occupied bandwidth.

| R <sub>USER</sub> = 3 | 00 Mbps         | QPSK | 16-QAM | 64-QAM |

|-----------------------|-----------------|------|--------|--------|

| C 7/9                 | <i>S/N</i> (dB) | 3.75 | 10.1   | 15.7   |

| $C_R = 7/8$           | <i>B</i> (MHz)  | 171  | 85.7   | 57.1   |

| $C_{R} = 3/4$         | <i>S/N</i> (dB) | 2.62 | 8.5    | 13.4   |

| $C_R = 5/4$           | B (MHz)         | 200  | 100    | 66.7   |

| $C_{R} = 2/3$         | <i>S/N</i> (dB) | 1.82 | 7.24   | 11.8   |

| $C_R = 2/3$           | B (MHz)         | 225  | 113    | 75     |

| R <sub>USER</sub> =   | 1 Gbps          | QPSK | 16-QAM | 64-QAM |

| C 7/9                 | <i>S/N</i> (dB) | 3.75 | 10.1   | 15.7   |

| $C_{R} = 7/8$         | <i>B</i> (MHz)  | 570  | 286    | 190    |

| C - 2/4               | <i>S/N</i> (dB) | 2.62 | 8.5    | 13.4   |

| $C_R = 3/4$           | <i>B</i> (MHz)  | 667  | 333    | 222    |

| C = 2/2               | <i>S/N</i> (dB) | 1.82 | 7.24   | 11.8   |

| $C_R = 2/3$           | B (MHz)         | 750  | 375    | 250    |

| R <sub>USER</sub> =   | 2 Gbps          | QPSK | 16-QAM | 64-QAM |

| C 7/9                 | <i>S/N</i> (dB) | 3.75 | 10.1   | 15.7   |

| $C_{R} = 7/8$         | <i>B</i> (GHz)  | 1.14 | 0.57   | 0.38   |

| C - 2/4               | <i>S/N</i> (dB) | 2.62 | 8.5    | 13.4   |

| $C_R = 3/4$           | <i>B</i> (GHz)  | 1.33 | 0.67   | 0.44   |

| C = 2/2               | <i>S/N</i> (dB) | 1.82 | 7.24   | 11.8   |

| $C_R = 2/3$           | <i>B</i> (GHz)  | 1.50 | 0.75   | 0.50   |

Table 3: Signal to noise ratio and signal bandwidth for different MCS's and data rates

#### c. Step 3 – Propagation Channel Modeling

As discussed previously, the selected operating frequency is 28 GHz. This implies many new challenges, as rain and atmospheric attenuation, specular reflection on buildings, and channel modeling. A lot of channel modeling studies have been gathered in [9]. This is supported by the New York University (NYU) Wireless mm-wave channel simulator: NYUSIM 2.01 [25]. It enables accurate modeling for wireless mm-wave links, as it is based on many field studies.

Input parameters are divided in 4 sections. The main objective of this part is to determine the channel path loss, in order to perform the link budget. Thus the *channel parameters* section is of particular interest. The simulator may take into account atmospheric features (pressure, humidity, temperature), environmental constraints (rain, foliage, building penetration), and the transceiver localization. Moreover, different scenarios could be tested. The chosen use case corresponds to the urban micro (UMi) environment. Finally, the simulator also includes LOS probability. The other sections are related to *antenna properties, signal consistency*, and *human blockage*. These features are optional for path loss computing. Thus, they are not considered in this work.

| Range (m)        | Pressure (hPa) | Freq. (GHz)  | Humidity (%)   | Bandwidth (MHz) |

|------------------|----------------|--------------|----------------|-----------------|

| 10 - 500         | 1013           | 28           | 50             | 400             |

|                  |                |              |                |                 |

| Temperature (°C) | Scenario       | Polarization | TX Power (dBm) | Number of RX    |

Table 4: NYUSIM default channel parameters

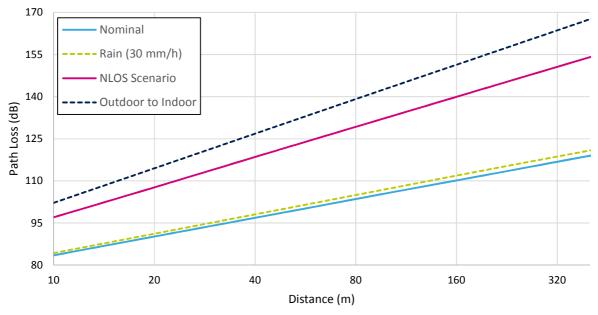

All the channel parameters reported in Table 4 are set to their default values, and the base station height is set to 10 m. The *Signal consistency* and *Human blockage* sections are disabled. The path loss has been computed using these settings. The effects of environmental constraints and NLOS scenario have been highlighted. Results are plotted in Figure 17. It is shown that heavy rains have low impact on the path loss. The main issues are NLOS scenario and outdoor to indoor (O2I) penetration losses. They respectively lead to 27 dB and 37 dB penalties. It is reminded that the LOS probability is between 15% and 60 % in the 50 to 200 m range. Finally, as shown in [9], the base station height also impacts the path loss from a certain distance. Indeed, it modifies the limit between the LOS and NLOS scenario.

Figure 17: UMi path loss at 28 GHz, for different scenarios

To conclude the path loss estimation, some relevant values are reported in Table 5.

5G 28 GHz High Efficiency Integrated Phased Array Transceivers

| Distance (m)           | 50  | 100 | 200 |

|------------------------|-----|-----|-----|

| Nominal path loss (dB) | 99  | 106 | 112 |

| NLOS path loss (dB)    | 122 | 133 | 158 |

| O2I path loss (dB)     | 131 | 143 | 172 |

Table 5: Path loss relevant values at 28 GHz

#### d. Step 4 – Receiver Characteristics

To establish the link budget of the whole mobile communication system, it is necessary to determine the receiver (i.e. the user equipment) characteristics. Based on recent state of the art, mobile receivers may be composed with small antenna arrays. As it is highly integrated, its gain per element is expected to be about 0 dBi, as shown in [26]. Moreover, circuit performances depend on the chosen technology, the operating frequency and the integration level. For example, the CMOS integrated receiver designed in [27] exhibits a noise figure (NF) lower than 4 dB and a maximum output power about 14.5 dBm. For cost and integration issues, SiGe or CMOS technologies may be preferred to GaAs and GaN. The expected user equipment characteristics are summed up in Table 6.

| Freq. (GHz) | NF (dB) | Antenna Gain (dBi) | Number of Antenna | Technology  |

|-------------|---------|--------------------|-------------------|-------------|

| 28          | 4       | 0                  | 4                 | SiGe / CMOS |

| Table 6: | Expected | user | equipment | features |

|----------|----------|------|-----------|----------|

|----------|----------|------|-----------|----------|

Finally, the base station receiver will be sized depending on the transmitter properties (front-end module features and array size). The current methodology may be used, after the base station transmitter sizing.

#### e. Step 5 – Link Budget

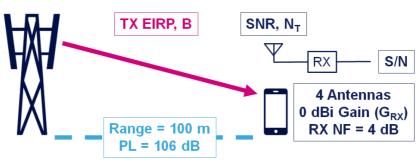

Thanks to the previous parts, transmitted signal, mm-wave channel, and receiver characteristics have been determined. Thus, the transmitter EIRP could be derived from a link budget. The wireless link is pictured in Figure 18.

Figure 18: Wireless link in the chosen use case

Firstly, the SNR is determined thanks to *Equation (14)*. It gives the relation between the required S/N, the receiver *NF*, and the *SNR* (all expressed in dB). Then, the link budget is completed with *Equation (15)*.

Chapter 1: From 5G Expectations to Front-end Module Specifications

$$SNR = \frac{S}{N} + NF - 10.\log_{10}(N_{el})$$

(14)

$$EIRP = SNR + PL - G_{RX} + N_T$$

<sup>(15)</sup>

$$N_T = 10.\log_{10}(k_B * T * B) \tag{16}$$

Finally, *Equation (16)* enables to compute the thermal noise,  $N_T$ . It depends on the Boltzmann constant  $k_B$ , which value is 1.3806 \* 10<sup>-23</sup> J.K<sup>-1</sup> and the temperature *T*. It also depends on the signal bandwidth. As it is much higher than it was for the previous standards, wireless systems are no longer interference limited, but noise limited. Results for the targeted use cases are reported in Table 7.

| Range (m) | PL (dB)   | LOS (%) | S/N (dB) | B (MHz) | Т (К) | N <sub>T</sub> (dB) | EIRP (dBm)  |

|-----------|-----------|---------|----------|---------|-------|---------------------|-------------|

| 100       | 106 - 143 | 40      | 11.8     | 250     | 298   | - 119.9             | 25.9 - 62.9 |

| 200       | 112 – 172 | 15      | 8.5      | 100     | 298   | - 123.9             | 24.6 - 84.6 |

Table 7: Link budget results for the chosen use cases

Up to these results, O2I and NLOS scenarios seem highly demanding due to their high path loss. Actually, the current specifications for sub 6 GHz pico-cells limit the base station EIRP to 33 or 47 dBm [23]. Fortunately, the expected network densification should increase the LOS probability. The use of signal repeaters is also expected [20]. It enables to cope with the large path loss penalty. As well, indoor coverage will be provided thanks to dedicated networks and offloading.

### f. Step 6 – Front-End Module Features for mm-Wave Access Point

This part focuses on the base station front-end module (FEM) performances in the TX mode, i.e. on the power amplifier (PA) properties and the way it is connected to each antenna. As the EIRP has been determined, FEM features will enable to size the antenna array. The choice of the FEM topology mainly depends on the standard requirements, and the chosen technology.

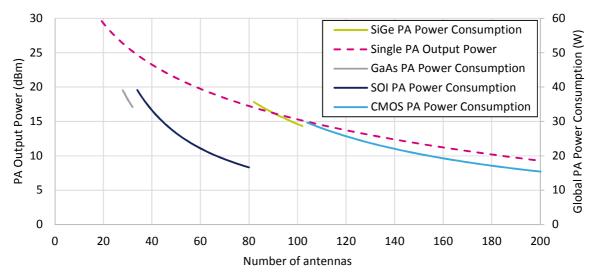

Firstly, 5G PA's will probably operate at an important power back-off (PBO). This means that the input power is much lower than the one corresponding to the PA saturation. Actually, the use of the OFDM modulation implies high peak to average power ratio (PAPR). Thus, the back-off is necessary to ensure adequate linearity. As discussed in [28], the input PBO is about 9.6 dB. Consequently, the power added efficiency (PAE) of the reported PA drops from 35.5 to 10 %. It is possible to save efficiency thanks to dedicated PA architectures [29], [30], or using PAPR reduction techniques, which lower the required PBO. The technology choice has also a significant impact on the PAE, as shown by the results from [31], reported in Table 8. It is shown that CMOS may achieve slightly higher PAE than SiGe, but it drops faster with the increase of  $P_{SAT}$ . Moreover, GaAs and GaN exhibit PAE up to 40% for  $P_{SAT}$  above 30 dBm.

| P <sub>SAT</sub> (dBm) | PAE <sub>SiGe</sub> (%) | PAE <sub>cmos</sub> (%) |  |

|------------------------|-------------------------|-------------------------|--|

| 20                     | 43                      | 47                      |  |

| 30                     | 20                      | 10                      |  |

Table 8: Reported PAE depending on the technology and P<sub>SAT</sub>, from [31]

Then, in order to choose the best suitable technology, several recently designed Ka-band PA's have been reported in Table 9. The PAE at PBO is reported with a 6 dB output PBO which is often equivalent to the required 9.6 dB input PBO [26]. The first remarkable result is that GaAs and GaN technologies enable to reach high P<sub>SAT</sub> with good PAE performances. However, the use of such technologies leads to high area penalties and challenging digital integration. Thus, CMOS and SiGe seem to be more suitable for the design of energy and cost efficient FEM's. For now, these technologies exhibit comparable features.

| Reference               | [32]              | [29]              | [33]           | [34]              | [30]    | [35]           |

|-------------------------|-------------------|-------------------|----------------|-------------------|---------|----------------|

| Technology              | 90 nm<br>CMOS     | 45 nm SOI<br>CMOS | 250 nm<br>SiGe | 65 nm<br>CMOS     | GaN-Si  | 150 nm<br>GaAs |

| Freq. (GHz)             | 28                | 26                | 27.5           | 38                | 28      | 28             |

| P <sub>SAT</sub> (dBm)  | 26                | 25                | 17.1           | 24.8              | 32      | 26.5           |

| PAE <sub>peak</sub> (%) | 34.1              | 31                | 26.5           | 24.3              | 30      | 42             |

| РАЕ <sub>РВО</sub> (%)  | ≈ 10 <sup>*</sup> | 24 – 27           | 11.6           | ≈ 10 <sup>*</sup> | 30      | 31             |

| Area (mm²)              | 0.401             | 0.63              | 0.36           | 0.146             | 6       | 2.86           |

| P <sub>DC</sub> (mW)    | 1083 **           | 286**             | 83.3 **        | 1035 **           | 1350 ** | 375 **         |

\*: graphically estimated; \*\*: graphically estimated with a 6 dB output PBO Table 9: Ka-band power amplifier state of the art

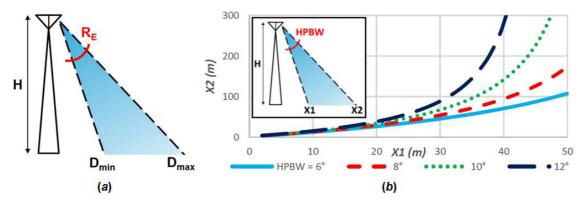

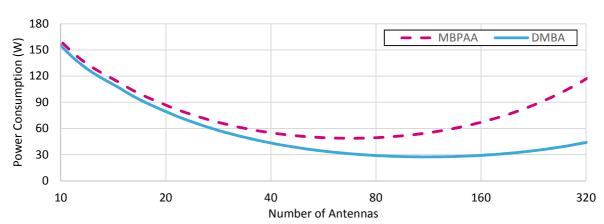

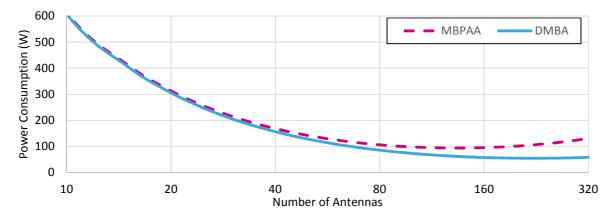

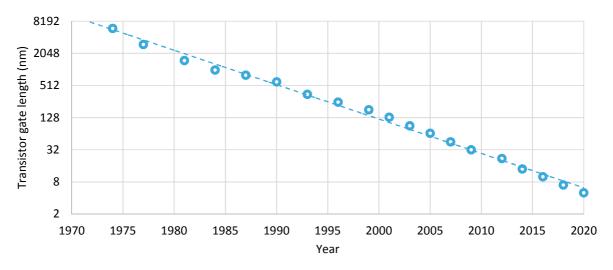

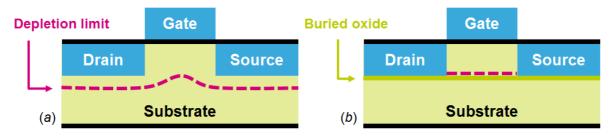

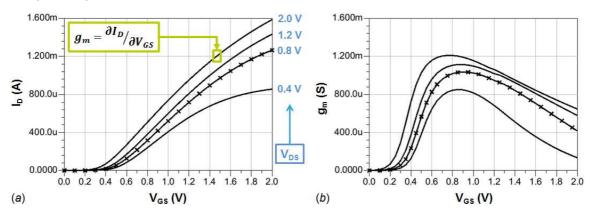

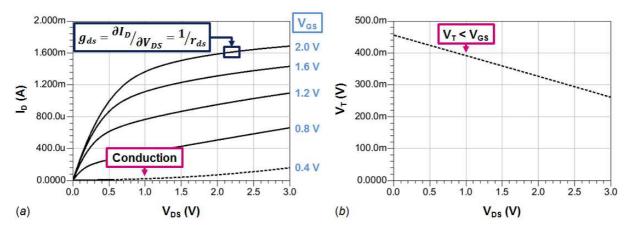

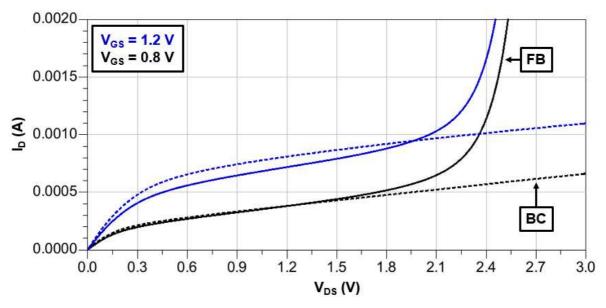

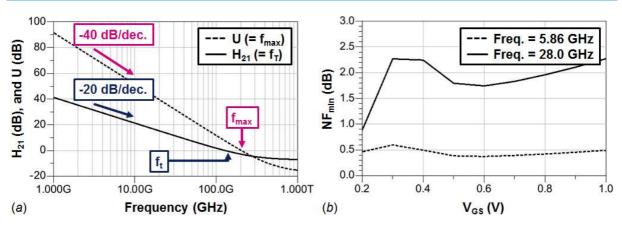

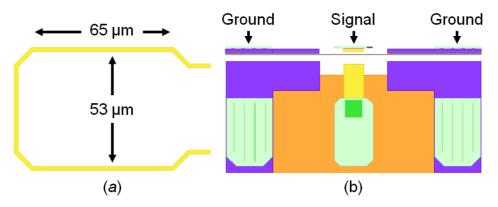

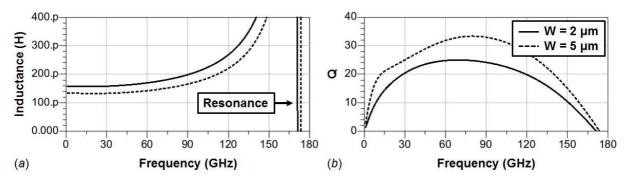

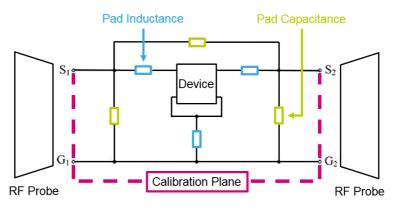

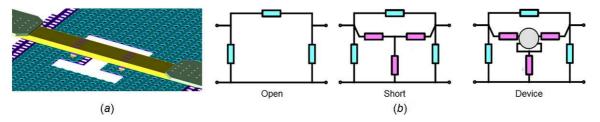

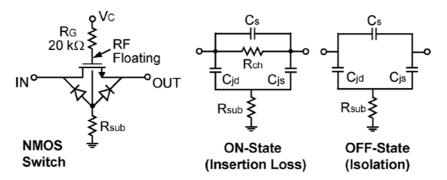

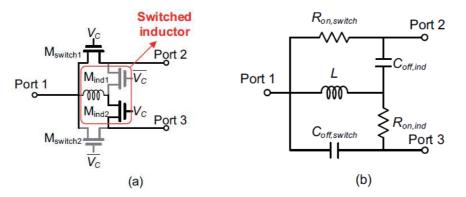

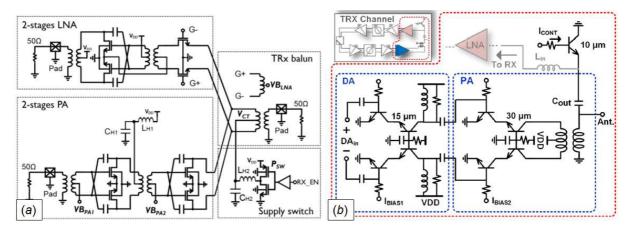

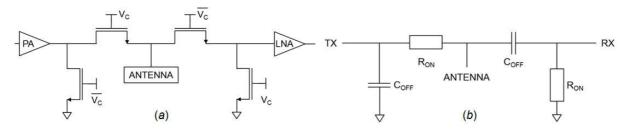

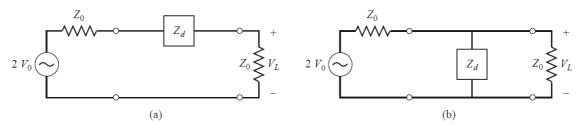

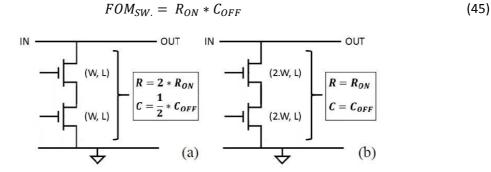

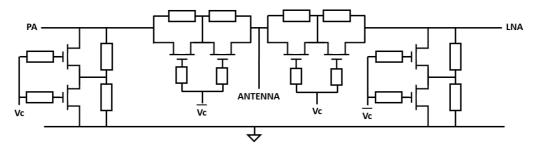

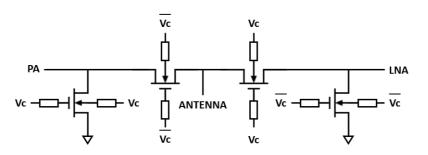

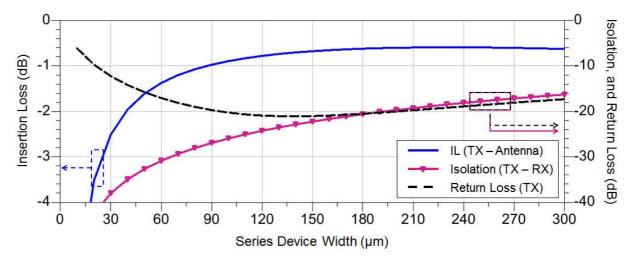

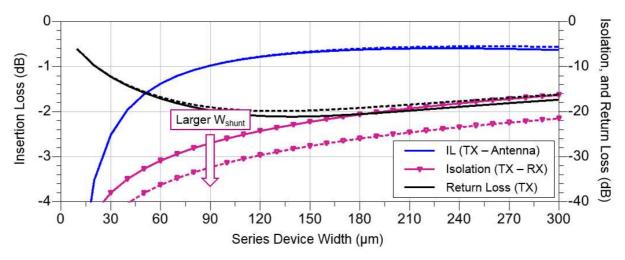

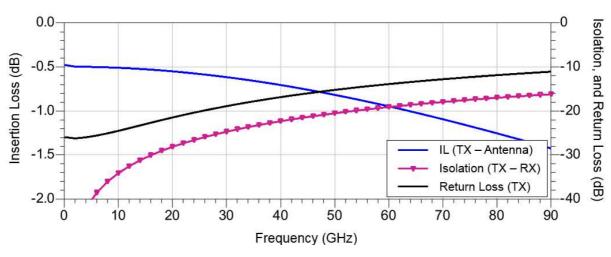

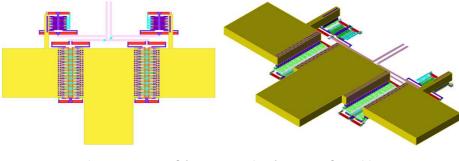

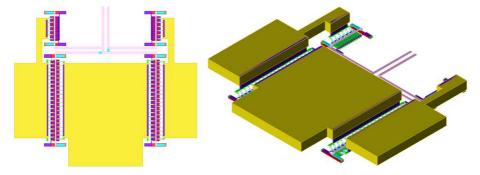

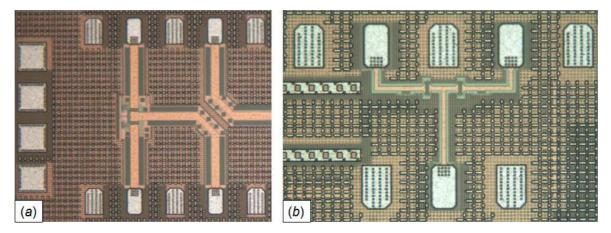

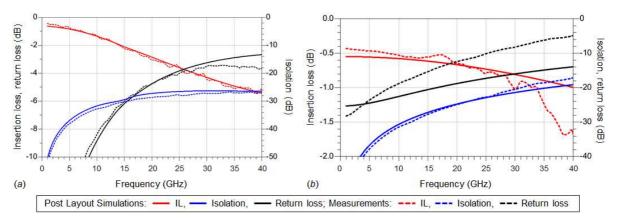

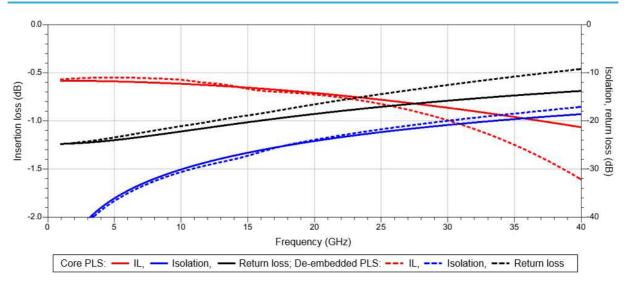

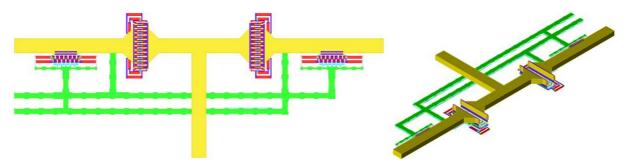

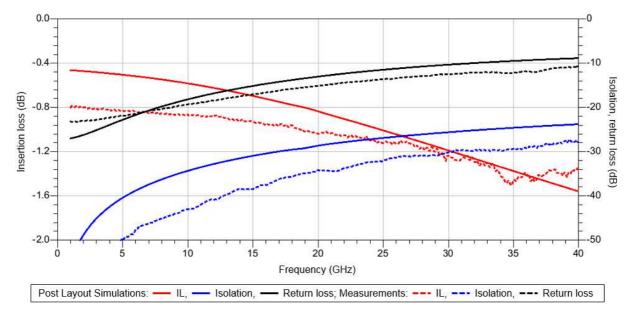

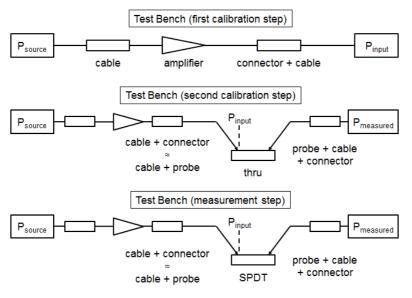

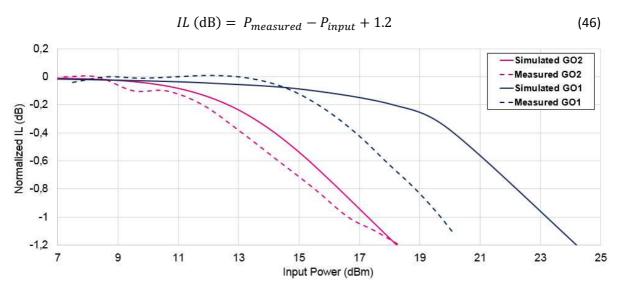

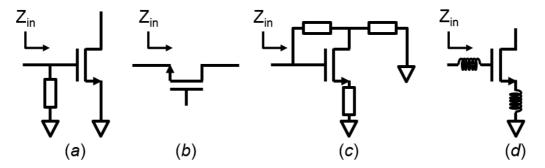

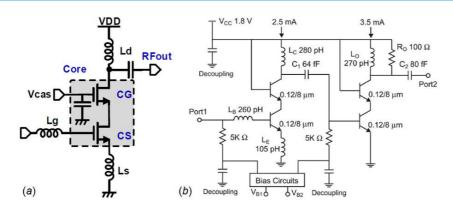

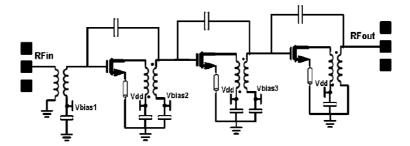

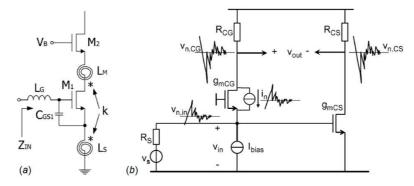

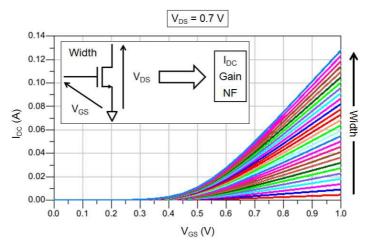

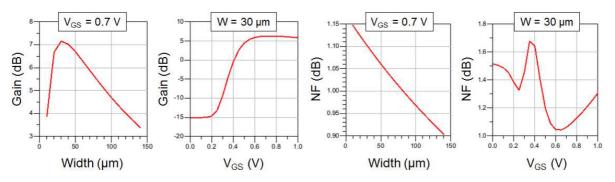

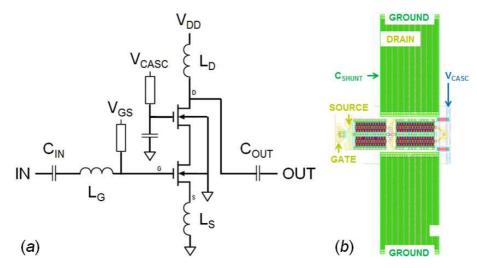

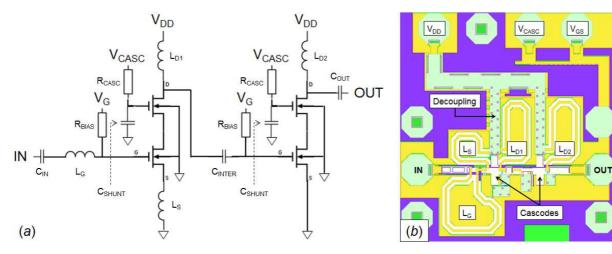

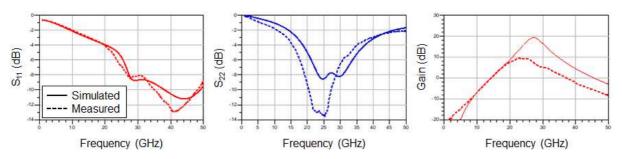

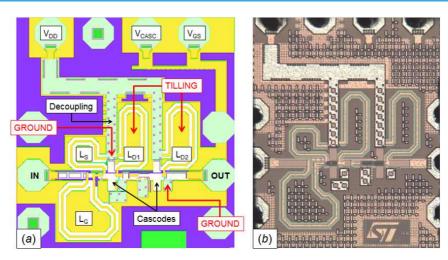

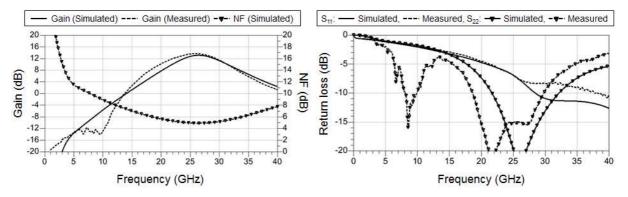

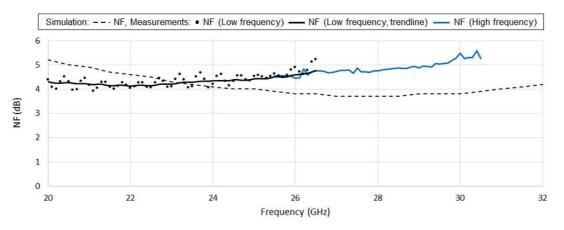

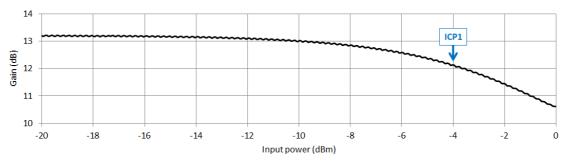

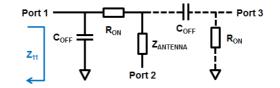

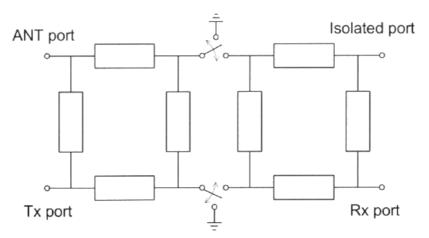

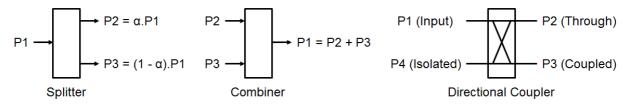

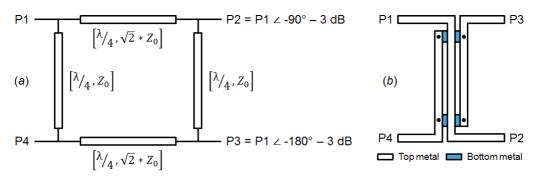

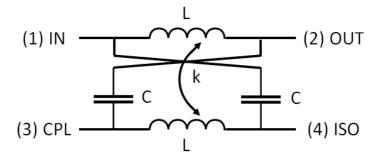

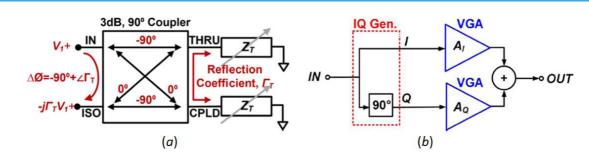

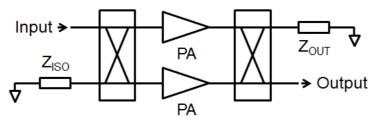

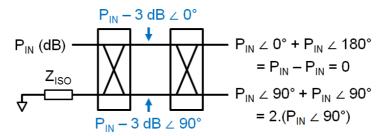

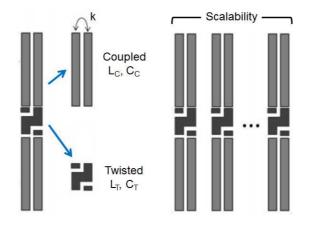

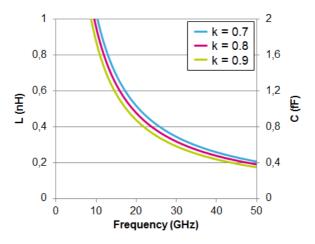

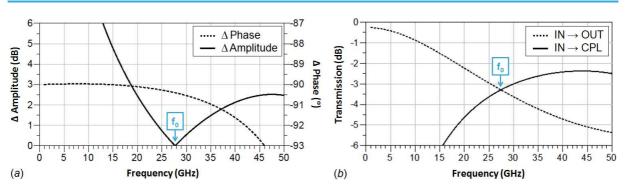

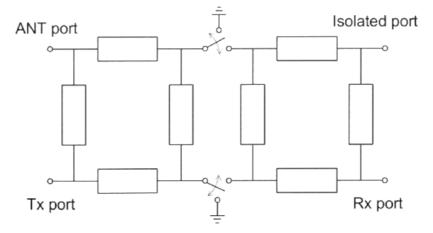

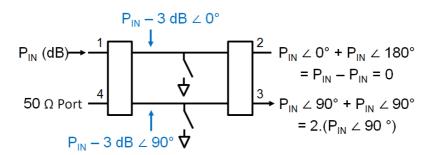

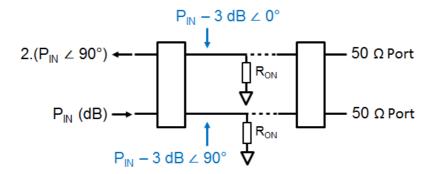

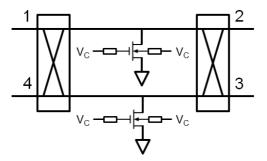

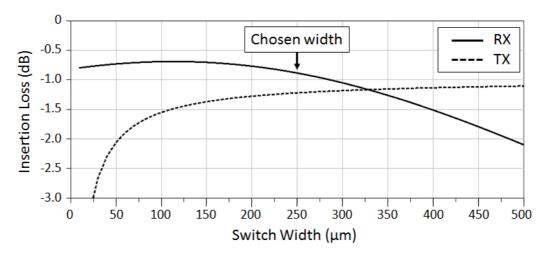

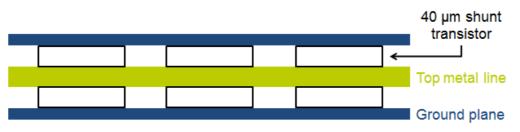

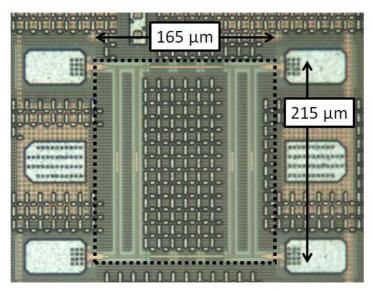

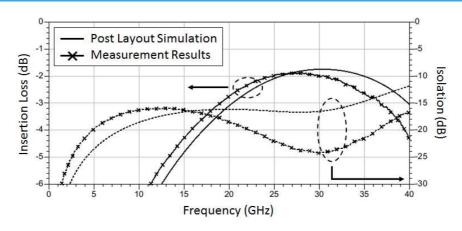

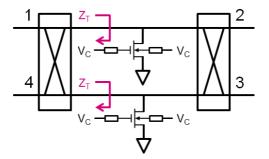

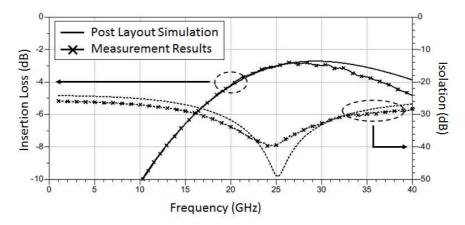

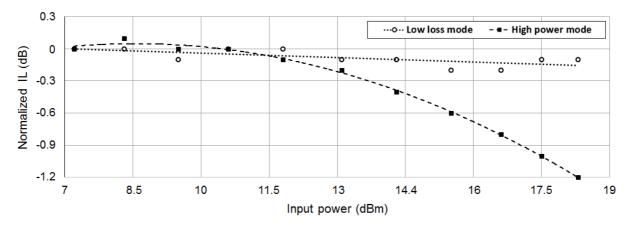

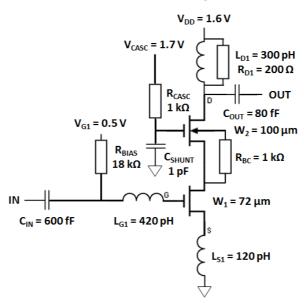

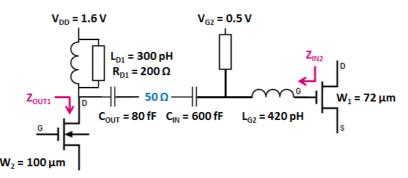

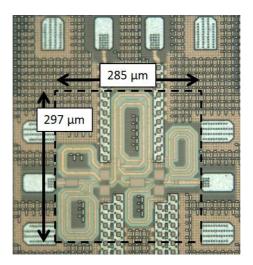

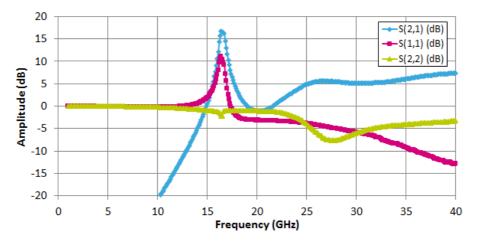

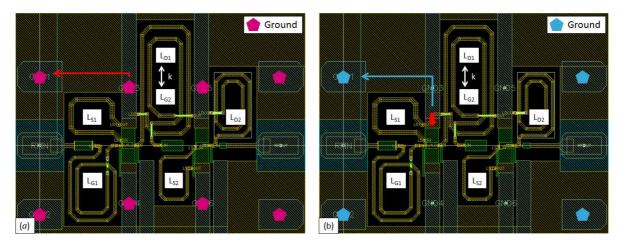

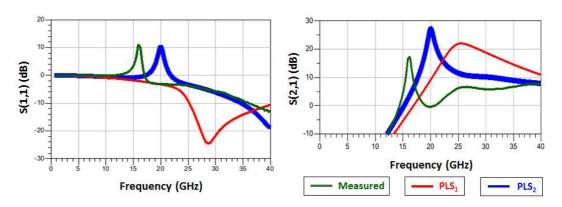

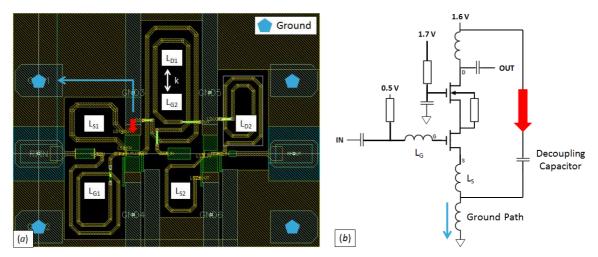

Moreover, MIMO and beamforming systems require an accurate and complex channel coding. To reduce the processing cost, time division duplex (TDD) is preferred to frequency division duplex (FDD). Actually, TDD enables to use the same frequency for both transmitting and receiving operations. Consequently, the channel coding only has to be realized once. This step may also be completed at the base station to reduce the constraints on user equipment. TDD implies the use of antenna switches. Several circuits designed in different technologies are reported in [36]. The comparison highlights the benefits of SOI CMOS in regards with bulk CMOS and SiGe. Actually, SOI CMOS switches may exhibit insertion losses lower than 1 dB, high power handling, and high integration level. Bulk CMOS and SiGe circuits have higher insertion losses, about 1.5 dB. Moreover they are often larger due to the implementation of bulky improvement techniques.