## Protections des processeurs contre les cyber-attaques par vérification de l'intégrité du flot d'exécution Michaël Timbert

### ▶ To cite this version:

Michaël Timbert. Protections des processeurs contre les cyber-attaques par vérification de l'intégrité du flot d'exécution. Cryptographie et sécurité [cs.CR]. Institut Polytechnique de Paris, 2020. Français. NNT : 2020IPPAT028 . tel-03066435

## HAL Id: tel-03066435 https://theses.hal.science/tel-03066435v1

Submitted on 15 Dec 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Protections of Processors against Cyber Attacks by Control Flow Checking

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à Télécom Paris

École doctorale n°626 École doctorale de l'Institut Polytechnique de Paris (ED IP Paris) Spécialité de doctorat : Informatique, données, IA

Thèse présentée et soutenue à Paris 75015, le 15 Septembre 2020, par

## MICHAËL TIMBERT

Composition du Jury :

| David Naccache<br>Professeur, ENS (Information Security Group)            | Rapporteur, Président |

|---------------------------------------------------------------------------|-----------------------|

| Marie-Laure Potet<br>Professeur, Grenoble INP (Ensimag)                   | Rapporteur            |

| Philippe Maurine<br>Maître de conférences/HDR, LIRMM                      | Examinateur           |

| Annelie Heuser<br>Chargée de recherche, CNRS (TAMIS)                      | Examinateur           |

| Jean-Luc Danger<br>Directeur d'études, Télécom Paris (COMELEC)            | Directeur de thèse    |

| Sylvain Guilley<br>Professeur, Télécom Paris (COMELEC), CTO (Secure-IC)   | Co-directeur de thèse |

| Karine Heydemann<br>Maître de conférences/HDR, Sorbonne Université (LIP6) | Invitée               |

| Ulrich Kühne<br>Maître de conférences, Télécom Paris (COMELEC)            | Invité                |

Thèse de doctorat

# Contents

| Li           | st of | Figur         | es                                        | 7         |

|--------------|-------|---------------|-------------------------------------------|-----------|

| Li           | st of | Table         | s                                         | 9         |

| R            | emer  | cieme         | nts                                       | 11        |

| $\mathbf{A}$ | bstra | $\mathbf{ct}$ |                                           | 13        |

| 1            | Intr  | oduct         | ion                                       | 27        |

|              | 1.1   | Today         | 's processors                             | . 27      |

|              |       | 1.1.1         | Common architecture of today's processors | . 27      |

|              |       | 1.1.2         | RISC Processors                           |           |

|              | 1.2   | Contr         | ol Flow Graph                             |           |

|              | 1.3   |               | ol Flow Hijacking                         |           |

|              | 1.4   |               | ol Flow Integrity                         |           |

|              | 1.5   |               | luction                                   |           |

| <b>2</b>     | Stat  | te-of-t       | he-art                                    | <b>37</b> |

|              | 2.1   | Softwa        | are weaknesses and associated attacks     | . 37      |

|              |       | 2.1.1         | Introduction                              | . 37      |

|              |       | 2.1.2         | Program architecture                      | . 37      |

|              |       |               | Static structures                         |           |

|              |       |               | Dynamic structures                        |           |

|              |       |               | Dynamic Loading of Libraries              |           |

|              |       | 2.1.3         | Vulnerable points                         |           |

|              |       | -             | Spatial errors                            |           |

|              |       |               | Temporal errors                           |           |

|              |       | 2.1.4         | Vulnerability exploitation                |           |

|     |       | Data only attack                                           |

|-----|-------|------------------------------------------------------------|

|     |       | Stack overflow                                             |

|     |       | Heap overflow                                              |

|     |       | Data and bss overflow                                      |

|     | 2.1.5 | Payload creation method                                    |

|     |       | Code injection                                             |

|     |       | Code Reuse Attack                                          |

|     | 2.1.6 | Synthesis                                                  |

| 2.2 | Hardw | vare countermeasure                                        |

|     | 2.2.1 | Existing Hardware Protections                              |

|     |       | Data Execution Prevention                                  |

|     |       | Control-flow Enforcement Technology                        |

|     |       | Memory Protection Extension                                |

|     |       | Pointer Authentication                                     |

|     |       | Trusted Execution Environment                              |

|     |       | TrustZone                                                  |

|     |       | Software Guard Extensions                                  |

|     |       | Secure Memory Encryption                                   |

|     |       | Virtual-Machine Extensions                                 |

|     |       | Secure Virtual Machine                                     |

|     |       | Silicon Secure Memory                                      |

|     | 2.2.2 | Academic studies                                           |

|     |       | Secure-Call                                                |

|     |       | HCODE                                                      |

|     |       | Project CHERI                                              |

|     |       | Processor SAFELite: Low fat pointer                        |

|     |       | HardBound                                                  |

|     |       | Compilation-Enforced Temporal Safety                       |

|     |       | Architectural Support for Instruction Set Randomization 95 |

|     |       | Software and Control Flow Integrity Architecture 96        |

|     |       | Hardware-Assissted Fine-Grained Control-Flow Integrity:    |

|     |       | Towards Efficient Protection of Embedded Sys-              |

|     |       | tems Against Software Exploitation                         |

|     | 2.2.3 | CFI                                                        |

|     |       | ECCA                                                       |

|     |       | CFCSS                                                      |

|     |       | HAFGCFI                                                    |

|     |       | HCFI                                                       |

4

| 3        | $\operatorname{Thr}$ | eat Model 10                                                                                                                                                      | 1        |

|----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|          | 3.1                  | Statement of threat model                                                                                                                                         | 1        |

|          | 3.2                  | Mitigation of the threat                                                                                                                                          | 2        |

|          | 3.3                  | Offered security                                                                                                                                                  | 2        |

|          |                      | 3.3.1 Fine-grain security $\ldots \ldots \ldots$  | 2        |

|          |                      | 3.3.2 Reactive vs infective strategies                                                                                                                            | 3        |

|          | 3.4                  | Comparison with SOA                                                                                                                                               | 4        |

| <b>4</b> | Fun                  | ctional Mechanism of Control Flow Integrity 10                                                                                                                    | <b>5</b> |

|          | 4.1                  | Formalism                                                                                                                                                         | 5        |

|          |                      | 4.1.1 Definitions and security property                                                                                                                           | 5        |

|          |                      | 4.1.2 Concept of seamless verification of security property $P_{-10}$                                                                                             |          |

|          |                      | 4.1.3 Basic-block based seamless verification of property $P$ . 10                                                                                                | 9        |

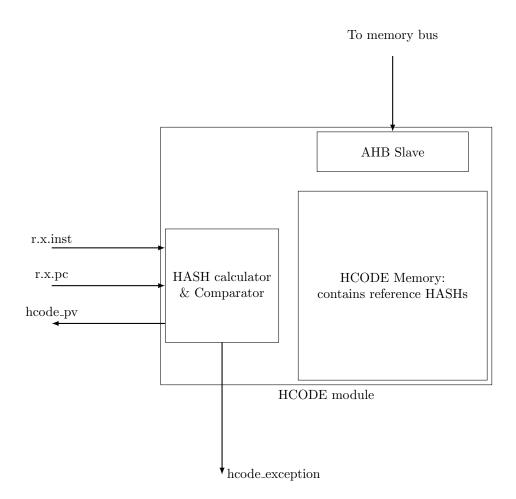

|          | 4.2                  | HCODE Operating Principle                                                                                                                                         | 4        |

|          |                      | 4.2.1 Big picture                                                                                                                                                 | 4        |

|          |                      | 4.2.2 Overview                                                                                                                                                    | 4        |

|          | 4.3                  | Software implementation                                                                                                                                           | 5        |

|          |                      | 4.3.1 Adding jump                                                                                                                                                 | 6        |

|          |                      | 4.3.2 The new '.HCODE' section                                                                                                                                    | 7        |

|          |                      | 4.3.3 Hardware module                                                                                                                                             | 8        |

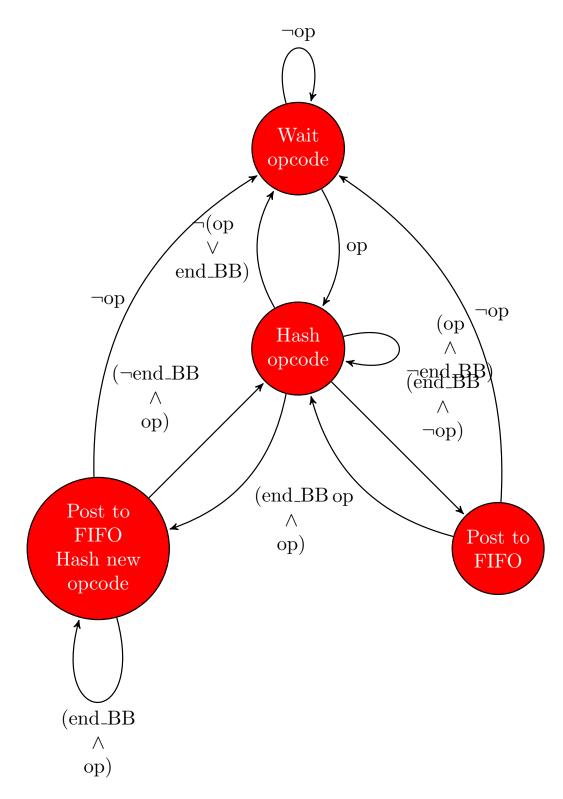

|          |                      | HCODE FSM                                                                                                                                                         | 9        |

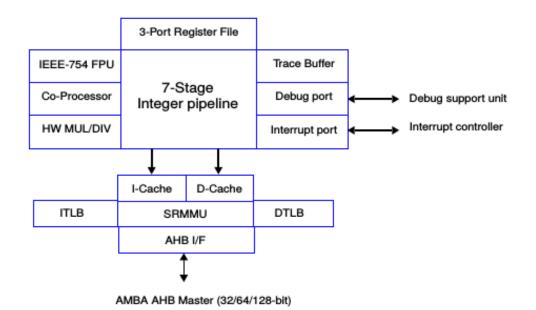

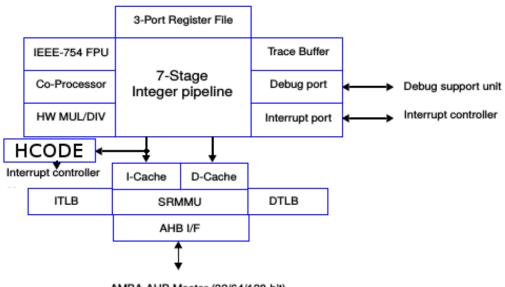

|          |                      | 4.3.4 LEON 3                                                                                                                                                      | 0        |

|          |                      | 4.3.5 Software OS                                                                                                                                                 | 1        |

|          |                      | HCODE verification                                                                                                                                                | 1        |

|          |                      | Kernel context                                                                                                                                                    | 1        |

|          | 4.4                  | Performance estimation                                                                                                                                            | 2        |

|          |                      | 4.4.1 Hardware performance                                                                                                                                        | 2        |

|          |                      | 4.4.2 Software performance $\ldots \ldots \ldots$ | 3        |

|          | 4.5                  | Conclusion                                                                                                                                                        | 3        |

| <b>5</b> | CCI                  | FI: Code and Control Flow Integrity 12                                                                                                                            | 9        |

|          | 5.1                  | Solution $\ldots$                                                                |          |

|          |                      | 5.1.1 Architecture Overview                                                                                                                                       |          |

|          |                      | 5.1.2 Metadata                                                                                                                                                    |          |

|          |                      | 5.1.3 CFI Verification                                                                                                                                            |          |

|          |                      | 5.1.4 Attack Model and Security Guaranties                                                                                                                        |          |

|          | 5.2                  | Implementation                                                                                                                                                    |          |

|          | 5.3                  | Performance                                                                                                                                                       |          |

|          |                      |                                                                                                                                                                   |          |

|   | 5.4   | Conclusion                                                                                                                         |

|---|-------|------------------------------------------------------------------------------------------------------------------------------------|

| 6 | Inte  | erruption and Speculative Execution 143                                                                                            |

|   | 6.1   | Solution                                                                                                                           |

|   |       | 6.1.1 Hardware                                                                                                                     |

|   |       | 6.1.2 Software                                                                                                                     |

|   |       | Metadata                                                                                                                           |

|   |       | Toolchain                                                                                                                          |

|   | 6.2   | Speculative execution                                                                                                              |

|   | 6.2   | -                                                                                                                                  |

|   |       | Interruptions                                                                                                                      |

|   | 6.4   | Implementation $\dots \dots \dots$ |

|   | 6.5   | Performance                                                                                                                        |

|   | 6.6   | Conclusion                                                                                                                         |

| 7 | Cor   | clusion 155                                                                                                                        |

| 8 | Per   | spectives 157                                                                                                                      |

|   | 8.1   | Limitation of our approach                                                                                                         |

|   | 8.2   | Interface with the processor                                                                                                       |

|   | 8.3   | Metadata alignment                                                                                                                 |

|   | 8.4   | Cache                                                                                                                              |

|   | 8.5   | Basic Block Optimisation                                                                                                           |

|   |       | -                                                                                                                                  |

| A | crony | vms 161                                                                                                                            |

| 9 | Bib   | liography 163                                                                                                                      |

6

# List of Figures

| 1    | Représentation simplifiée du graphe d'un programme                       | 16  |

|------|--------------------------------------------------------------------------|-----|

| 2    | Vue simplifiée de l'architecture de base du CCFI                         | 21  |

| 3    | Vue simplifiée de l'architecture de la solution CCFI prenant en          | 0.0 |

|      | compte l'exécution spéculative                                           | 23  |

| 1.1  | Example of program and associated flow graph (from [34]) $$              | 29  |

| 2.1  | Typical data structure on the stack $\ldots \ldots \ldots \ldots \ldots$ | 40  |

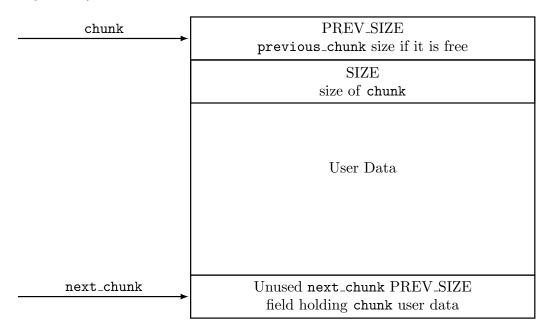

| 2.2  | Structure of an allocated memory <i>chunk</i>                            | 42  |

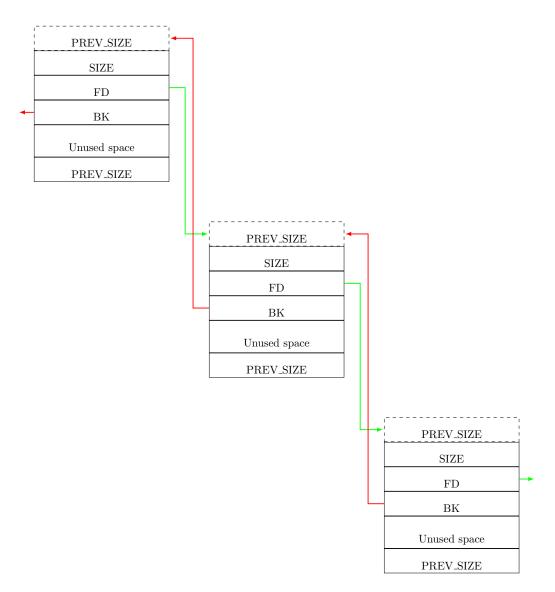

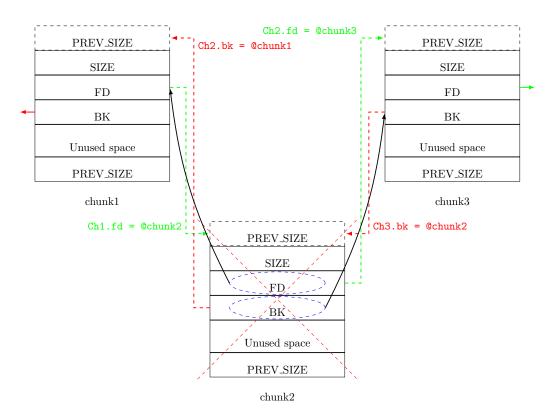

| 2.3  | Linked list of "free" memory <i>chunks</i>                               | 43  |

| 2.4  | Structure of a "free" memory <i>chunk</i>                                | 44  |

| 2.5  | Compilation and execution cycle of a program                             | 45  |

| 2.6  | 2 ways of realizing <i>buffer overflows</i>                              | 48  |

| 2.7  | Overflow in the stack                                                    | 52  |

| 2.8  | Example of a $bin$                                                       | 54  |

| 2.9  | chunk modification in the heap                                           | 56  |

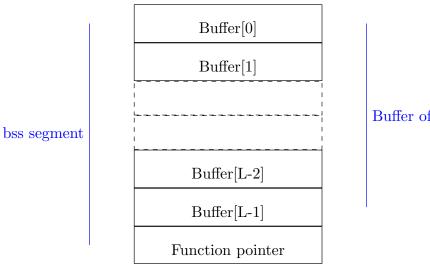

| 2.10 | bss segment                                                              | 57  |

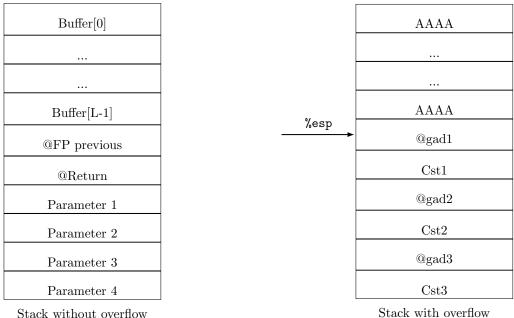

| 2.11 | Stack before and after a ROP attack                                      | 62  |

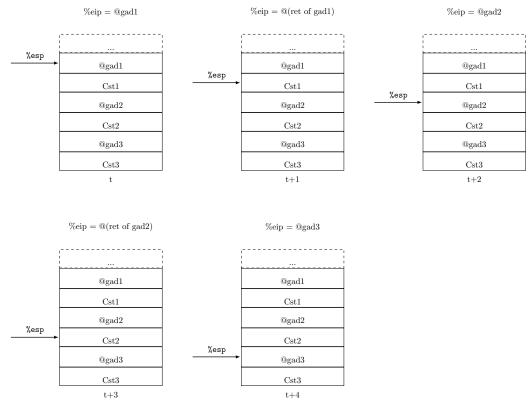

| 2.12 | Stack during a ROP attack                                                | 63  |

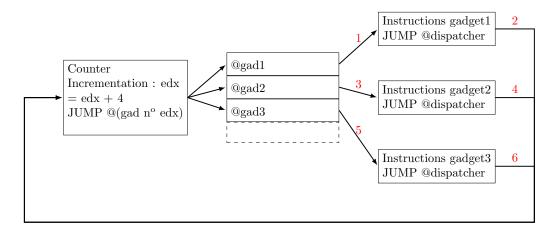

| 2.13 | JOP example                                                              | 64  |

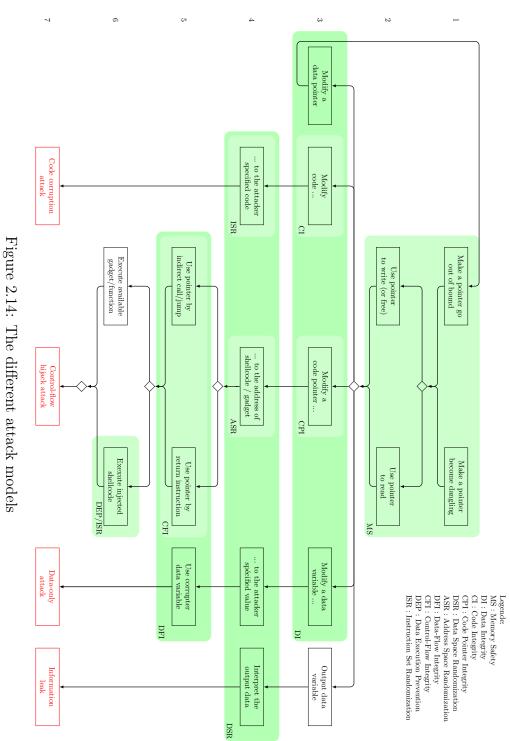

| 2.14 | The different attack models                                              | 66  |

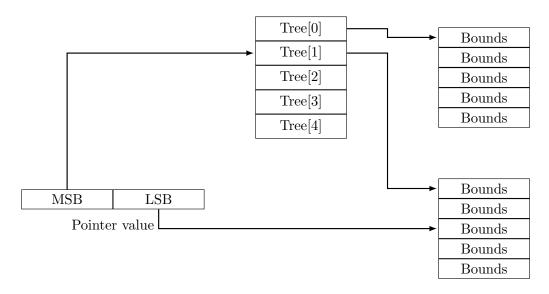

| 2.15 | Example of 2-level Lookup-Tree                                           | 71  |

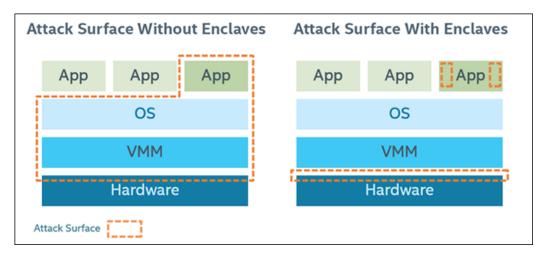

| 2.16 | Attack surface with and without the SGX protection (diagram              |     |

|      | extracted from Intel website)                                            | 79  |

| 2.17 | Remote attestation (diagram from the Intel website)                      | 80  |

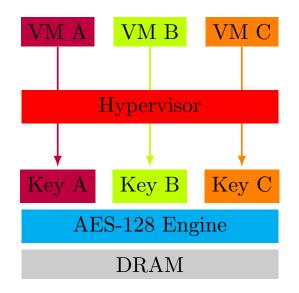

| 2.18 | SEV Architecture (diagram inspired by the AMD website)                   | 81  |

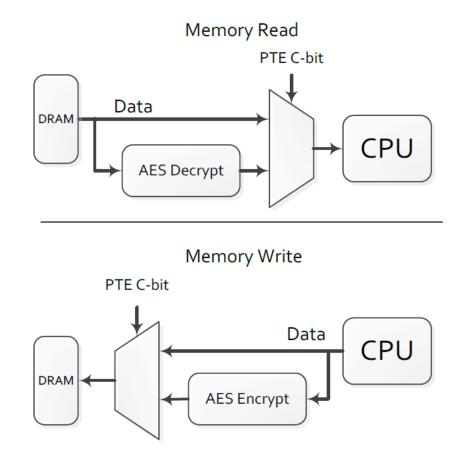

| 2.19 | Read and DWrite in SME mode (diagram from the AMD web-                   |     |

|      | site)                                                                    | 82  |

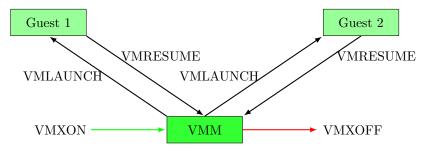

| 2.20 | Schematic representation of VMX                                          | 84  |

|      |                                                                          |     |

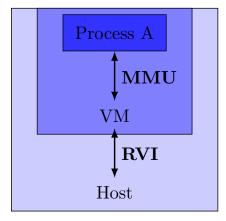

| 2.2 | 1 SVM protection representation                                          |

|-----|--------------------------------------------------------------------------|

|     | 2 SSM representation                                                     |

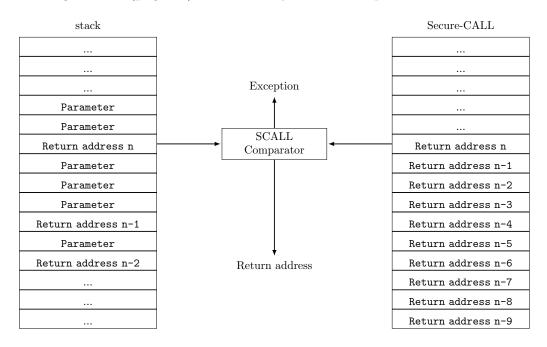

| 2.2 | 3 Schematic representation of the countermeasure SCALL 88                |

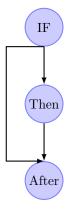

|     | 4 Example of <i>Basic Block (BB)</i> without jump in the end 89          |

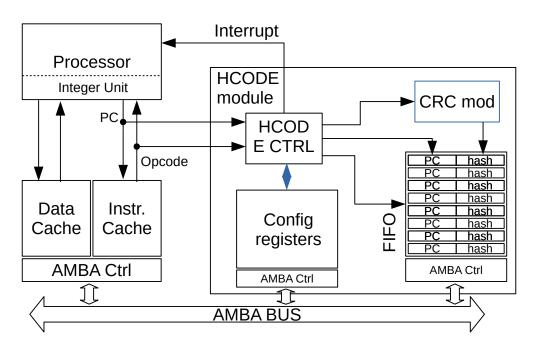

| 2.2 | 5 HCODE hardware module                                                  |

|     | 6 fat pointer representation                                             |

| 2.2 | 7 Diagram of a BIMA type counter                                         |

| 2.2 | 8 Example of <i>low fat pointer</i> 93                                   |

| 2.2 | 9 CETS schematic operation                                               |

| 2.3 | 0 SOFIA operation diagram (extracted from [27]) 97                       |

| 2.3 | 1 Basic Block allowing two predecessors (diagram extracted from          |

|     | $[27])  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |

| 0.1 |                                                                          |

| 3.1 | Attack vectors addressed by our CCFI technology 102                      |

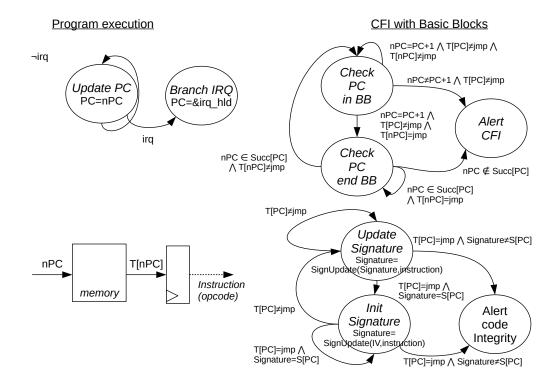

| 4.1 | Program state machine $(left)$ and CFI state machine $(right)$ . 108     |

| 4.2 |                                                                          |

| 4.3 |                                                                          |

|     | optimized to take into account basic blocks                              |

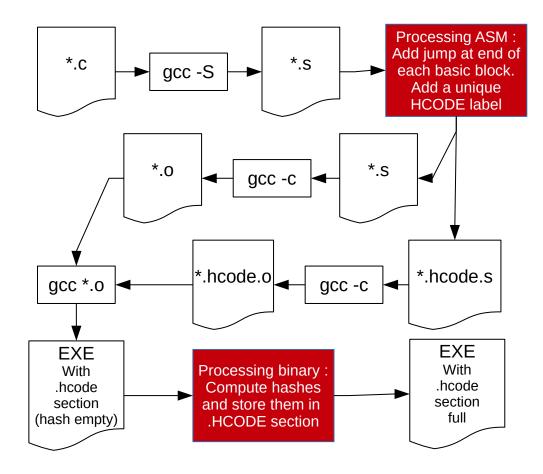

| 4.4 | •                                                                        |

| 4.5 |                                                                          |

| 4.6 |                                                                          |

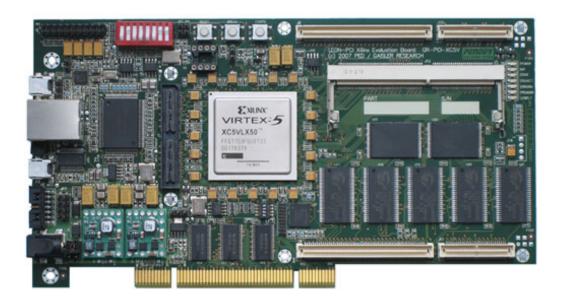

| 4.7 | Gaisler board used for the LEON3 prototype                               |

| 4.8 | LEON 3 internal                                                          |

| 4.9 | LEON 3 internal with HCODE module                                        |

|     |                                                                          |

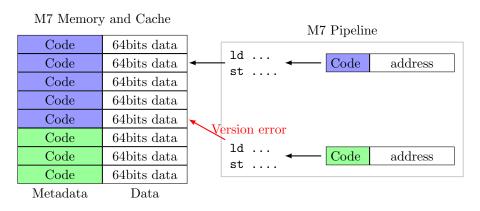

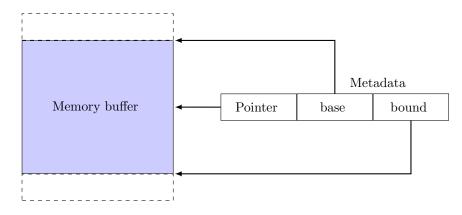

| 5.1 | 1 1                                                                      |

| 5.2 | 1                                                                        |

| 5.3 |                                                                          |

| 5.4 |                                                                          |

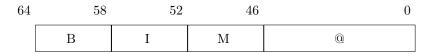

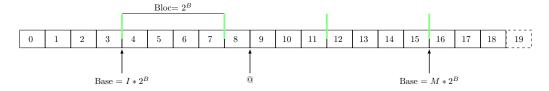

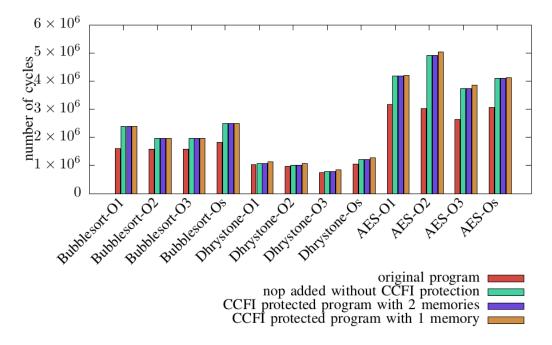

| 5.5 | Overhead on execution time                                               |

| 6.1 | Overview of the proposed architecture                                    |

| 6.2 |                                                                          |

| 6.3 |                                                                          |

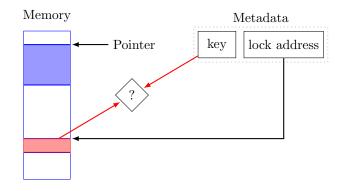

| 6.4 | 1                                                                        |

| 6.5 |                                                                          |

| 0.0 |                                                                          |

# List of Tables

| 1   | Comparaison de certaines des protections les plus importantes 17                                        |

|-----|---------------------------------------------------------------------------------------------------------|

|     | Comparison of some of the most prominent protections 32<br>Mapping between CCFI protections and threats |

|     | Code and metadata correspondence                                                                        |

| 6.1 | Hardware cost                                                                                           |

| 6.2 | Hardware cost of caches                                                                                 |

| 6.3 | Benchmark on A <sup>*</sup> processor in number of cycle                                                |

| 6.4 | Software modification                                                                                   |

## Remerciements

Je dédie cette thèse à mon père qui a su me transmettre avec passion le goût de l'informatique, de l'électronique et qui m'a transmis sa soif de connaissance.

Je remercie ma famille pour sa présence, son aide et son indéfectible soutien.

J'aimerai remercier Télécom Paris et Secure-IC qui m'ont accueilli pour réaliser cette thèse CIFRE financée par l'ANRT.

J'aimerai remercier mes directeurs de thèse, Jean-Luc Danger et Sylvain Guilley, qui m'ont donné l'opportunité de faire cette thèse, qui m'ont prodigué de nombreux conseils et ont été présents pour me motiver dans les moments difficiles.

Je remercie aussi mes encadrants, Thibault Porteboeuf et Adrien Facon qui m'ont soutenu durant cette période, avec qui j'ai aimé travailler et qui m'ont beaucoup appris.

Je tiens particulièrement à remercier Karine Heydemann, Ulrich Kühne ainsi qu'Abdelmalek Si merabet pour leur grande aide, leur soutien, leurs conseils avisés et pour tout le temps qu'ils m'ont consacré.

Je remercie tous les enseignants-chercheurs avec qui j'ai eu de nombreuses discussions passionnées et de sympathiques moments de détente.

Je remercie mes amis Céline Brunel, Jérémie Brunel, Boris Ploujoux, Xuan Thuy Ngo, Alexander Schaub, Sébastien Carre, Nicolas Bruneau et Margaux Dugardin pour leur présence et leur soutien dans les moments difficiles et surtout pour les bons moments passés ensemble.

Je remercie mes collègues de Secure-IC qui m'ont aidé en me prodiguant de nombreux conseils techniques, partagé avec moi leur expertise et pour leur bienveillance.

Merci, à toutes ces personnes et à toutes celles que j'aurai pu oublier

## Abstract

## Summary

In this thesis, we propose a new hardware Control Flow Integrity (CFI) protection implementation called Code and Control Flow integrity. Current CFI protection implementations, either software or hardware, are actually limited to a coarse-grain coverage, or feature an overhead cost which is prohibitive. The latter cost can concern the running time execution or directly impacts the hardware footprint.

We start in chapter 1 by introducing the security problem inherent of today's processors. This security flaw can affect all kinds of systems and constitutes a major problem for system continuity and person safety. The processors variability is discussed in order to understand the field of application of our solution. We present the concept of Control Flow Graph as the basic structure of a program. This allows us to explain on the one hand to what extent CFI is able to protect programs against corruption, and on the other hand what are the advantages and limitations of this protection.

Then we explore in chapter 2 the state-of-the-art of today's protections. This is presented as a list of existing CFI implementations, either software or hardware, academic or industrial. This allows us to distinguish coarse-grain and fine-grain protections, their limitations and advantages as well as their cost. We also propose an overview of historical protections to understand their history and why some protections have been adopted by industrialists while others have been ignored.

Then, in chapter 3, the threat model is exposed to explain the attacker capabilities. This describes what the attacker is able to perform on the targeted processor, and highlights the requirement for efficient protections.

The next three chapters (4 & 5 & 6) present our innovative solution with a top-down approach. We start by setting definition of a program structure and security property of CCFI. Then, each level of security is detailed, from functions call and return, called inter-procedural, to control flow checking between basic block inside a function, called intra-procedural. The chapter 4 leads to a simple implementation of CCFI and explain each aspect of its security. In the following chapter 5 we describe an implementation deployable on microcontroller and small processor. This presents the minimal hardware implementation needed to offer CCFI protection. The last chapter 6 describes a more advanced implementation, able to deal with complex processors using speculative execution and branch prediction. We also address the mangement of interruptions and propose a flexible solution to prevent false positive and protect code during an interruption.

In chapter 7 we summarize all benefits of the CCFI approach to provide efficient CFI. Its capacity of adaptation on many platforms and its low impact on performance and hardware cost makes it a good candidate to be adopted by the industry. Some perspectives on how this solution can be improved are discussed. It is notably pointed out that CCFI can be implemented in many different ways allowing an adaptation to many different architectures. We also discuss the possibility to use CCFI when an operating system or an hypervisor are used. In this case we show how our solution can be adapted to support context switch.

## Contributions

The premise of this thesis was a publication in 2014 at PPREW [25]. These four years of research gave rise to three publications. The first one was published in "The New Codebreakers" book in 2016 [24], the second was in 2018 at DSD conference under the name "CCFI-Cache: A Transparent and Flexible Hardware Protection for Code and Control-Flow Integrity" [22], and the last one, "Processor Anchor to Increase the Robustness against Fault Injection and Cyber Attacks", has been accepted for presentation at COSADE [70], in october 2020. This thesis also led to a patent for Secure-IC based on our technique to synchronize metadata and code.

## Résumé long en Français

Dans cette thèse, nous proposons une nouvelle implémentation matérielle pour le Contrôle d'Intégrité du Flot d'exécution (CFI: Control Flow Integrity) nommée Code and Control Flow Integrity (CCFI). Les implémentations actuelles, logicielles ou matérielles, implémentant la protection CFI sont actuellement limitées à une protection à gros grain ou ont un surcoût en temps d'exécution ou en terme d'empreinte matérielle trop coûteuse pour être déployée.

Nous commençons par introduire dans le chapitre 1 les problèmes de sécurité inhérents aux processeurs modernes. Ces failles de sécurité peuvent affecter toutes sortes de systèmes et constituent un problème majeur pour la continuité des systèmes et la sécurité des personnes. Les différences entre les processeurs sont discutées pour comprendre les différents champs d'application de notre solution. Nous y présentons le concept Graphe de Flot de Contrôle (CFG: Control Flow Graph).

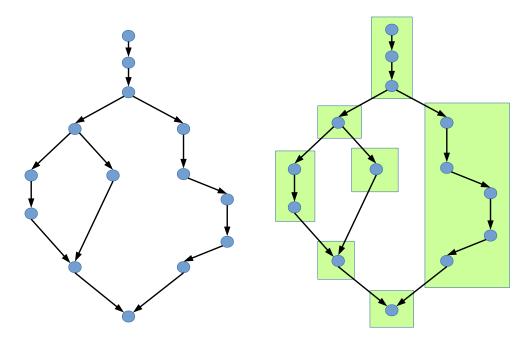

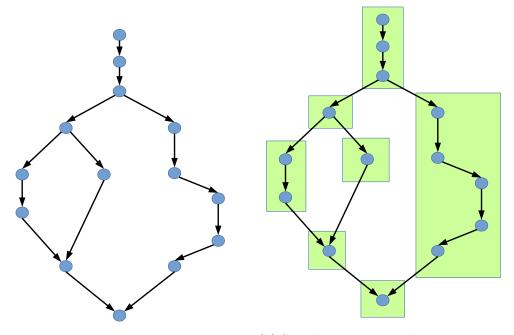

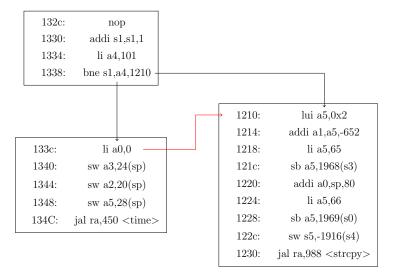

Un CFG est la représentation graphique du flux d'exécution d'un programme. Les CFG sont principalement utilisés dans l'analyse statique ainsi que dans les applications de compilation. Sur la figure 1a chaque point bleu représente une instruction assembleur et chaque flèche une transition autorisée pendant l'exécution du programme. Afin de simplifier le CFG de la figure 1a, nous pouvons utiliser le principe de Bloc de Base (BB: Basic Bloc) qui définit un ensemble d'instructions assembleurs toujours exécutées ensemble et dont le seul point d'entrée est la première instruction du BB et que le seul point de sortie est la dernière instruction de ce BB. Ainsi nous pouvons réduire le CFG de 14 nœuds à 7 nœuds (voir figure 1b).

Le principal problème de sécurité des processeurs modernes vient du fait que les processeurs n'ont pas connaissance du partitionnement mémoire. Les différentes zones mémoire utilisées par les programmeurs comme la pile, le tas et les pages mémoires de code ou de données ne sont que des constructions faites par les programmeurs afin de faciliter la conception de programme. Mais le processeur n'est pas informé de cette structure, ce qui permet à des attaquants de modifier l'exécution du programme ciblé. Plusieurs exemples sont présentés dans la section 2.1.3. Un exemple significatif est l'attaque de type dépassement de tampon (buffeur overflow) où le programme accède à des données à partir d'un pointeur de tableau mais ces données se trouvent au-delà de la plage mémoire destinée à ce tableau. Ce type de vulnérabilité est présent dans beaucoup de langage bas niveau comme le C.

(a) Représentation simplifiée du CFG

(b) Représentation simplifiée du CFG

d'un programme avec son équivalent avec des blocs de base (rectangle vert)

Figure 1: Représentation simplifiée du graphe d'un programme

D'autres attaques consistent à directement injecter du code dans l'application. Par exemple, en utilisant un champ de données destinées à contenir des informations de l'utilisateur pour y stocker du code binaire. Ensuite l'attaquant n'a plus qu'à dévier l'exécution du programme sur le code injecté pour finir son attaque. Ce genre d'attaque est maintenant arrêtée par des protections du type  $W^X$ . Mais cette protection n'est pas présente sur tous les processeurs, en particulier sur les microcontrôleurs. De plus, il existe maintenant des attaques de type réutilisation de code (code reuse) qui permettent d'achever le même type d'attaque sans avoir à injecter le code. Ce qui met à mal les protections de type  $W^X$ .

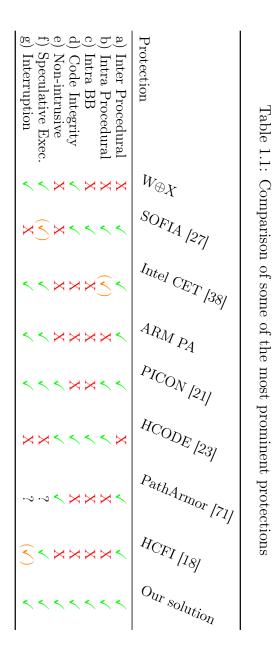

Le tableau 1 (pages 17 et 32) résume les différentes protections existantes ainsi que leur niveau de sécurité.

Dans le chapitre 2 nous explorons l'état de l'art des protections existantes. Nous y détaillons la liste des implémentations de la protection CFI, Table 1: Comparaison de certaines des protections les plus importantes

| Our solution                  |                  | >                | >       | >                | >            | >                | <b>,</b>    |

|-------------------------------|------------------|------------------|---------|------------------|--------------|------------------|-------------|

| 0 <sup>112</sup><br>HCEI [18] |                  | V                | V       | V                | V            |                  |             |

| HCP1 .                        | >                | $\sim$           | $\sim$  | $\sim$           | $\sim$       | `                | <u>&gt;</u> |

| PathArmor /71                 | >                | X                | X       | X                | >            | <i>د</i> .       | .∽          |

| HCODE [53]                    | Χ                | >                | >       | >                | >            | X                | Х           |

| PICON (21)                    | >                | >                | X       | X                | >            | >                | >           |

| APM PA                        | >                | X                | X       | X                | X            | >                | >           |

| Intel CET 1381                | >                | 5                | X       | Х                | Х            | >                | >           |

| SOFIA 127                     | >                | >                | >       | >                | X            | 5                | X           |

| XOM                           | Х                | ×                | ×       | >                | ×            | >                | >           |

| ection                        | iter-Procedurale | ntra-Procedurale | utra-BB | ntégrité du Code | on intrusive | xec. Spéculative | iterruption |

| Prot                          | a) Ir            | b) Ir            | c) In   | d) Ir            | e) N         | f) E:            | g) Ir       |

qu'elles soient logicielles ou matérielles, académiques ou industrielles. Cela nous permet de distinguer les protections à gros grain de celles à grain fin et d'en déduire leurs avantages et leurs inconvénients ainsi que leur coût respectif. Nous proposons ainsi une vue d'ensemble de l'historique des protections implémentées dans les systèmes pour comprendre leur histoire et définir pourquoi certaines protections ont été adoptées par l'industrie tandis que d'autres ont été ignorées.

L'état de l'art nous permet de distinguer plusieurs familles de sécurité. La première famille se base sur la gestion de la segmentation de la mémoire. Le principe est de segmenter la mémoire en pages et d'attribuer à chaque page des droits spécifiques. Par exemple des droits d'écriture, de lecture ou d'exécution. Cette technique est poussée plus loin avec les protections implémentant les fat-pointers. L'idée est d'offrir un niveau plus fin de gestion de la mémoire, par exemple être capable de délimiter la zone mémoire pour un tableau.

Le principe de protection des pages mémoire a en premier été implémenté en logiciel mais est maintenant répandu dans tout processeur moderne. Par contre, les techniques de fat-pointer ont encore beaucoup de mal à être déployées en milieu industriel. Principalement en raison de leur surcoût, en terme de mémoire, de temps d'exécution mais également car certaines protections nécessitent des changements au niveau de la chaîne de compilation.

La seconde famille de protections qui nous intéresse est celle implémentant des protections du type CFI. Les implémentations logicielles souffrent d'une vitesse d'exécution fortement réduite empêchant alors toute utilisation concrète. Les implémentations logicielles réussissant à avoir des performances correctes le font en réduisant le niveau de sécurité, par exemple en vérifiant le respect du CFG uniquement au niveau des appels des fonctions. Les implémentations matérielles quant à elles sont généralement plus rapides mais nécessitent une modification du processeur pour fonctionner. Or, dans un contexte industriel, il n'est pas possible de modifier les processeurs, soit parce que l'accès au code source du processeur n'est pas disponible, soit parce que le temps d'intégration et de validation du processeur est trop long.

Le modèle d'attaquant est discuté dans le chapitre 3. Cela décrit ce que l'attaquant est capable de faire sur le système et souligne la nécessité d'une protection efficace.

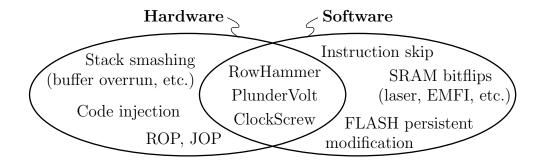

Nous considérons qu'un attaquant puissant est capable d'exécuter des attaques logicielles et/ou matérielles. En d'autres termes, le vecteur d'attaque peut être soit l'exploitation d'une faille existante (qui permet de corrompre

#### ABSTRACT

l'état du programme) ou une altération causée par un stress externe qui modifie l'état interne comme les attaques par injection électromagnétique. Les attaques matérielles sont détectées si la perturbation vise le code ou des pointeurs de code. Notez que certaines attaques récentes (telles que RowHammer et PlunderVolt) sont des modifications matérielles déclenchées par le logiciel et sont donc considérées comme des attaques logicielles et matérielles.

Comme les attaques physiques sont capables de modifier un mot en mémoire sans passer par le gestionnaire de mémoire, elles sont capables de contourner les protections matérielles comme W^X. L'attaquant est ainsi en mesure de modifier les instructions ou de sauter une instruction. En tant qu'attaque logicielle, il est capable d'utiliser toute vulnérabilité présente dans le logiciel Cela comprend l'utilisation de dépassement de tampon sur la pile pour modifier l'adresse de retour et de changer des pointeurs de fonction.

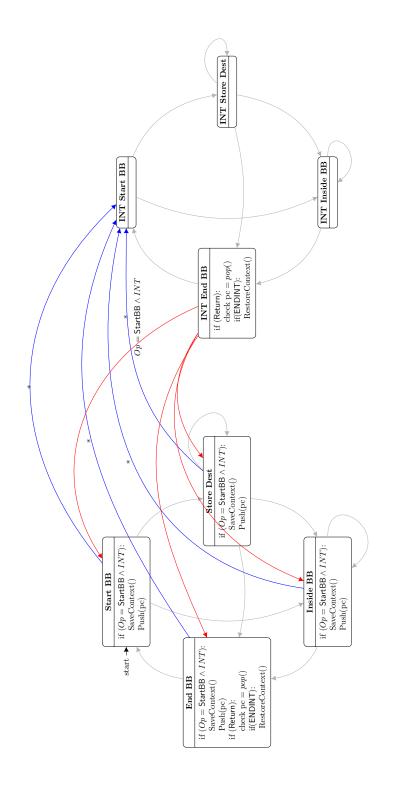

Les chapitres 4, 5 & 6 présentent notre solution innovante par une approche top-down. Nous commençons par définir la structure d'un programme et les propriétés de sécurité du CCFI. Chaque niveau de sécurité est détaillé. La protection des appels et des retours des fonctions est appelée inter-procédurale. La protection du flux d'exécution entre les BB est appelée intra-procédurale. Enfin la protection du flux d'exécution au sein du BB est appelée intra-BB.

Comme l'objectif est de fournir une implémentation d'une protection CFI capable de fonctionner sur une grande variété de processeurs, nous voulons que cette dernière ne soit pas intrusive et ne nécessite pas la modification du processeur protégé. Il est aussi nécessaire de prévoir la possibilité de protéger des codes utilisant des mécanismes d'interruptions, car cela peut s'apparenter à une déviation du CFG si cela n'est pas pris en compte. La solution doit aussi être capable de protéger des processeurs plus avancés utilisant potentiellement de l'exécution spéculative. Ainsi nous retrouvons tous les niveaux de sécurité que doit satisfaire notre solution CCFI dans le tableau 1

Le chapitre 4 conduit à une mise en œuvre simple du CCFI et explique chaque aspect de sa sécurité. Dans le chapitre 4, nous décrivons une mise en œuvre sur microcontrôleur et petit processeur. Cela présente le matériel minimal nécessaire pour assurer la protection CCFI.

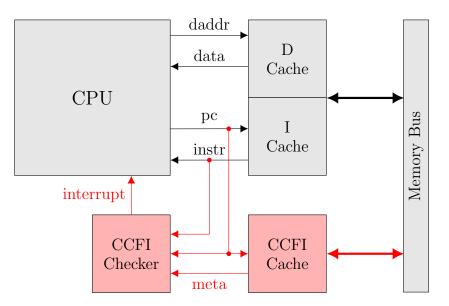

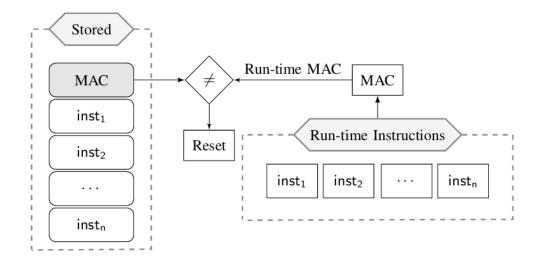

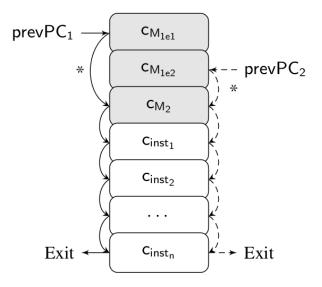

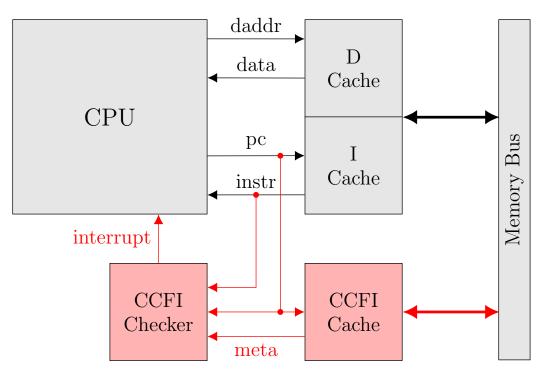

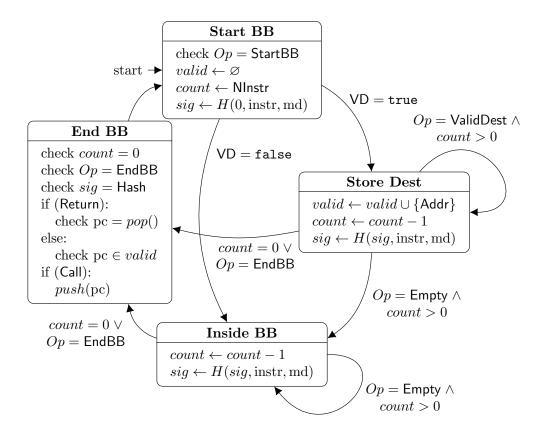

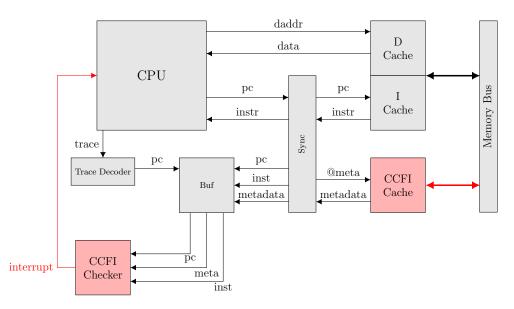

La figure 2 représente l'architecture de base de la solution CCFI. Elle est assurée par deux modules matériels supplémentaires (indiqué en rouge) : Le CCFI-cache récupère les métadonnées qui ont été calculées au moment de la compilation. Ces métadonnées contenant toutes les informations relatives au flot de contrôle. Ces informations sont utilisées au moment de l'exécution par le second module matériel, le CCFI-checker. Pour suivre et contrôler l'exécution du processeur, le CCFI-checker est connecté aux signaux d'interface entre le processeur et le cache d'instructions.

Le CCFI-cache a les mêmes caractéristiques (largeur, taille, associativité, politique de remplacement, etc...) que le cache d'instructions. Pour chaque bloc de base du programme, il y a un bloc de métadonnées correspondant. Chaque bloc de métadonnées est parfaitement aligné en mémoire sur le BB de code correspondant, avec un décalage constant. Pour chaque accès au cache d'instructions, une requête est émise au CCFI-cache. Grâce à l'utilisation d'un décalage constant entre les instructions et les métadonnées, le calcul d'adresses complexes est évité. En outre, les données du cache d'instructions et du CCFI-cache seront toujours cohérentes, c'est-à-dire que si un BB de code est présent dans le cache d'instructions alors ses métadonnées sont présentes dans le CCFI-cache.

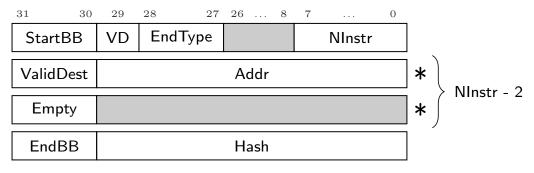

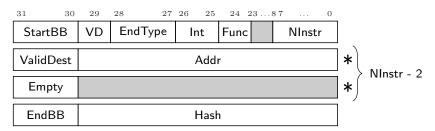

Les métadonnées pour chaque BB contiennent trois informations cruciales pour la vérification du flot d'exécution:

- Le nombre d'instructions contenues dans le BB

- Les adresses de destinations valides comme successeurs du BB

- Une signature calculée à partir des instructions et des metadonnées du BB

La vérification proprement dite est réalisée par le CCFI-checker. A la fin de chaque BB, il vérifie la validité de l'adresse suivante en la comparant avec les adresses valides contenues dans les métadonnées, assurant ainsi que le CFI intra-procédural est respecté. En cas d'appel ou de retour de fonction, une copie de la pile d'appels (shadow stack) est utilisée pour vérifier le CFI interprocédural. Cette pile d'appels est intégrée dans le CCFI-Checker et n'est pas accessible depuis le processeur principal. La cohérence intra-BB est assurée par un compteur qui contrôle le nombre d'instructions exécutées avant un transfert de contrôle. Enfin, l'intégrité du code et des métadonnées est assurée par une signature pré-calculée stockée dans les metadonnées. Cette signature est comparée à une valeur calculée durant l'exécution du BB par le CCFI-checker. En cas de violation, une interruption est déclenchée. Les détails du CCFI-checker sont présentés à la section 5.1.3.

#### ABSTRACT

Figure 2: Vue simplifiée de l'architecture de base du CCFI

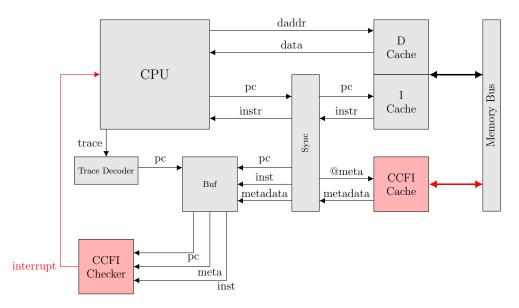

Le dernier chapitre 6 décrit une mise en œuvre plus avancée, capable de protéger des processeurs complexes utilisant l'exécution spéculative et la prédiction de branchement. Nous abordons également la gestion des interruptions et proposons une solution souple pour éviter les faux positifs et protéger le code durant l'exécution du code de l'interruption.

Lorsqu'une interruption se produit, le processeur détermine l'adresse mémoire du vecteur d'interruption et saute dessus. Il y a deux façons principales pour un processeur d'exécuter le gestionnaire d'interruption. La première est d'avoir un code statique en dur dans le processeur, quelle que soit l'interruption il exécutera ce code. La distinction du type d'interruption et l'appel du bon gestionnaire d'interruption sont laissés au programmeur. La seconde est d'avoir une zone de mémoire dédiée à un tableau de pointeurs de code. Pour chaque interruption, le processeur va chercher le pointeur de code correspondant et exécute le code relatif. Dans tous les cas, il en résulte un saut direct à la sous-routine d'interruption à tout moment et de n'importe où. Ce comportement, vu de l'extérieur, est considéré comme une violation du CFG. Pour être agnostique sur le type d'interruption, notre solution consiste à ajouter un drapeau **Int** dans l'en-tête des métadonnées du premier et du dernier BB de la fonction du gestionnaire afin de détecter le début et la fin de l'interruption. Cela permet de détecter les interruptions déclenchées à la volée, indépendamment de la la mise en œuvre du processeur. En cas d'interruption, le CCFI-checker détecte la discontinuité du flux de contrôle, mais les métadonnées indiqueront que la destination est à la fois un Start BB et Int signifiant que cette fonction est appelée à cause d'une interruption. Dans ce cas le CCFI-Checker sauvegarde son contexte d'exécution actuel dans une mémoire interne et la shadow stack est utilisée pour sauvegarder le PC actuel. Une fois la sauvegarde du contexte fait le CCFI-Checker saute à un autre FSM dédié à suivre l'exécution du gestionnaire d'interruption. Cette machine à états est la même que l'état normal, sauf pour l'état END BB où le drapeau ENDINT est vérifié. Si l'indicateur ENDINT est présent, alors le précédent contexte sauvegardé est restauré. Une fois le contexte restauré, le CCFI-checker peut poursuivre la vérification du BB là où elle a été interrompue.

Pour réussir à protéger les processeurs utilisant de l'exécution spéculative, il faut faire la distinction entre l'instruction récupérée par le processeur et l'instruction exécutée. Pour cela chaque instruction extraite est stockée dans un tampon circulaire avec ses métadonnées correspondantes. Ce tampon circulaire est aussi profond que nécessaire pour reproduire la latence du pipeline entre l'étage de la collecte (fetch) et l'étage de l'interface de traçabilité (voir figure 3). Pour chaque instruction récupérée par le processeur, une ligne est stockée dans le module Buf. Chaque ligne dans le module Buf contient l'instruction, son adresse et les métadonnées associées. Ainsi, lorsque la sortie de l'interface de trace expose une adresse, cette adresse est envoyée au module Buf pour sélectionner l'entrée correspondante. Le module Trace Decoder est présent pour assurer la récupération de l'adresse du PC à partir de l'interface de trace. Par construction, il n'est jamais possible pour le processeur de sortir un PC à partir de l'interface de trace sans que les métadonnées correspondantes soient présentes dans le module Buf. Une fois la ligne sélectionnée, le module Buf envoie les informations (PC, instruction et les métadonnées) au CCFI-Checker. Ce faisant, le CCFI-Checker est en mesure de suivre l'exécution du processeur, étape par étape, sans erreur, et cela même avec un processeur utilisant l'exécution spéculative.

Dans le chapitre 7, nous résumons tous les avantages de l'approche du CCFI pour fournir un CFI efficace. Sa capacité d'adaptation sur de nombreuses plateformes et son faible impact sur les performances et le coût matériel, en font un bon candidat à l'adoption par l'industrie. Quelques perspectives sur la manière dont cette solution peut être améliorée sont discutées. Il est notamment souligné que le CCFI peut être adapté de différentes

#### ABSTRACT

Figure 3: Vue simplifiée de l'architecture de la solution CCFI prenant en compte l'exécution spéculative

manières afin de permettre une adaptation à des architectures différentes. Nous discutons également de la possibilité d'utiliser le CCFI lorsqu'un système d'exploitation est utilisé. Dans ce cas, nous montrons comment notre solution peut être adaptée pour soutenir le changement de contexte et les modifications à apporter au système d'exploitation.

La vérification de l'intégrité du code et du flux de contrôle en parallèle avec l'exécution du logiciel est de la plus haute importance pour les applications de sécurité et de sûreté. L'idée de base d'utiliser un cache pour récupérer les métadonnées en même temps que le code a montré son efficacité en terme de performance, sans pour autant diminuer le niveau de sécurité. En effet, l'alignement des métadonnées avec la structure du code a été une bonne idée, tant pour simplifier le calcul de l'emplacement des métadonnées à partir de l'adresse du code que pour utiliser au mieux le cache de métadonnées. Nous avons prouvé qu'il est possible de développer une solution de CFI à grain fin tout en maintenant de bonnes performances. Un avantage majeur de notre solution est sa taille réduite en coût silicium et indépendante de la puissance de calcul du processeur utilisé.

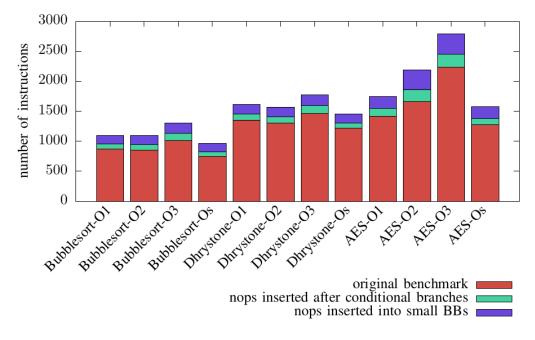

Néanmoins, certaines IPs spécialisées sont nécessaires en plus de la conception de base pour travailler avec les processeurs complexes, par exemple ceux qui utilisent l'exécution spéculative. Le surcoût mémoire lié à l'ajout des métadonnées, doublant la taille mémoire nécessaire pour le code, peuvent faire l'objet de controverses parmi les industriels et les universitaires. Cependant, nous pouvont considérer que c'est un prix raisonnable à payer pour ce niveau de sécurité et qu'aujourd'hui la mémoire est relativement bon marché. En outre, lorsque le code est compilé efficacement, il reste dans le cache et donc la vitesse d'exécution n'est pas impactée. Dans d'autres cas d'utilisation, doubler la taille mémoire est difficile surtout lorsque cette mémoire est intégrée dans un SoC (System-On-Chip). Comme nous l'avons vu, lors du développement de la solution CCFI, un des défis principal est de pouvoir détecter le début et la fin des blocs de base (BB) au cours de l'exécution. En effet, lors de l'exécution, seules les instructions qui modifient le flux de contrôle donnent un aperçu du CFG, mais cela ne suffit pas pour déduire l'ensemble du CFG. Nous avons intelligemment contourné ce problème en ajoutant ces informations directement dans nos métadonnées. Nous soulignons que la solution garantit le CFI au niveau des BB, ce qui le rend efficace et capable de détecter toutes les attaques modifiant le déroulement de l'exécution du programme. L'impact de la solution sur les performances est prometteur avec une variation de 2 à 30% selon le type de programme et le type d'architecture mis en place, ce qui est très raisonnable et industriellement viable.

Avant démontré son efficacité, la solution CCFI ouvre toutefois un certain nombre de perspectives en terme d'amélioration. La première piste d'amélioration est de lever la restriction forte de l'implémentation actuelle qui requiert que les métadonnées soient alignées avec le code. Ce qui implique que les métadonnées requièrent autant de place que le code. Or une grande partie des métadonnées ne contiennent pas d'informations utiles et certains BB du code sont artificiellement agrandis ce qui impacte les performances du programme. Il serait donc intéressant d'explorer la possibilité d'assouplir cette contrainte afin de réduire l'empreinte mémoire et d'améliorer les performances. Toute la difficulté étant de trouver un algorithme qui permet de déterminer l'adresse des métadonnées aussi rapidement que possible. Une possibilité serait de stocker l'adresse des métadonnées du BB suivant à côté de l'adresse du code au sein même des métadonnées. Nous pouvons aussi explorer la possibilité d'améliorer les performances de façon globale en modifiant le compilateur pour générer des BB de base suffisamment grands pour contenir toutes les métadonnées au prix, par exemple, de dupliquer du code. Une dernière optimisation concerne le CCFI-cache que nous pouvons intégrer

### ABSTRACT

directement au cache d'instructions pour alléger le nombre de requêtes sur le bus de mémoire et factoriser la logique du CCFI-cache avec celle du cache d'instructions.

ABSTRACT

26

## Chapter 1

## Introduction

## 1.1 Today's processors

#### 1.1.1 Common architecture of today's processors

Today processor are everywhere, inside computer, smartphone, smartwatch, calculator, TV box, toys and a lot more with the IOT devices. For all these purposes different kinds of processors have been developed from small microcontroller able to operate at few dozen of Mhz to powerful processor containing multiple cores, each operating at over 3.0 Ghz. This gap of performance is due to architectural differences, while microcontrollers have only a 3 stage pipeline and limited caches or none at all, big processors have around 14 stage pipeline and large caches. Advanced processors also have advanced prediction system to guess which part of the program while be executed. This in order to keep the pipeline full and to keep the number of instructions executed per cycle high. This complexity comes with a physical size and cost increase.

While it is relatively easy to follow the execution of a program from the outside of the processor by looking at which address it fetch instruction. It is more difficult, event impossible, to follow the execution path of the program for more complex processors. This can be because of prefetch mechanism which add a hidden cache inside the processor to speculative execution. During speculative execution the processor will guess the next jump before it had computes the destination. If this guessing was right it is time saved but in case of miss prediction the processor will make an internal rollback to previous state and take the right one. From the outside of the processor it

is hazardous to guess if the processor has make a wrong prediction or if it was an unexpected behavior. This can be theoretically possible if we know exactly the internal functioning of of the prediction mechanism. But this is rarely the case for most of the processor. It would come back to recreate a part of the processor to be able to follow processor execution. This will become more and more expensive as the processor have complex and multiple predictions.

#### 1.1.2 **RISC** Processors

CISC processors can have a large number of possible instructions, to minimize the code size and its impact on the necessary size of the instruction cache, these instructions have various length. This particularity makes harder to detect the beginning of an instruction in memory. It's also a risk for the security because instruction can be misinterpreted if they are fetched with one byte of offset. RISC processors feature constant size instruction which facilitates code instrumentation and lower the complexity of their pipeline. This is easier to detect misaligned fetch and to detect the beginning of an instruction. Their execution is also much more deterministic, for these reasons we focus on RISC processor in the rest of this PhD.

## 1.2 Control Flow Graph

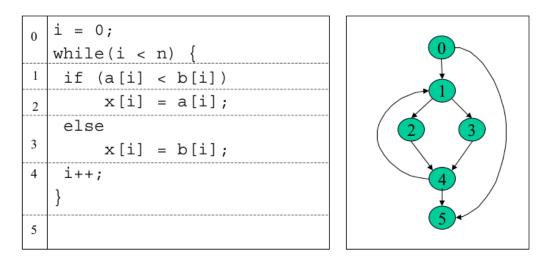

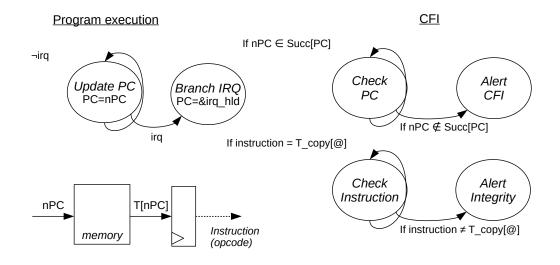

At the level of the machine code, a program is composed of multiple functions which in turn can be decomposed into basic blocks. A *Basic Block* (BB) is a straight-line sequence of instructions with a unique entry point and a unique exit point, i.e. if the control flow enters a BB, it will execute all of its instructions in sequence until leaving the BB at the exit point. A control flow transfer can only take place at the last instruction. This means that a basic block begins by an instruction that is the destination of a jump instruction (typically: branch, jump, call or return), and finishes by a jump instruction (idem: branch, jump, call or return) or by an instruction whose next instruction is the beginning of a new basic block. Each function can be represented as a *control-flow graph* (CFG), where each node corresponds to a BB, and edges represent the control transfers between the BBs. For example, Figure 1.1 illustrates a program along with its flow graph. These CFGs of function always have only one BB to enter the function and only

Figure 1.1: Example of program and associated flow graph (from [34])

one BB to exit the function. This constraint is set by the compiler during compilation. A whole program is composed of the CFG of each function linked by edges representing function calls and returns. It is noted that it is common in compilation world to consider that a BB can contain a call to a function without ended it. In our case we consider a call automatically set the end of the BB.

During a nominal program execution the flow remains on the CFG. However due to no memory safety of low level language it can happen that the program executes outside of the CFG. This behavior can be caused by software bug or physical disruption. Such behavior can be exploited by an attacker to leak date or take control over the machine. It is therefor extremely important to guarantee execution integrity. Technique to perform are referred to as Control Flow Integrity.

## 1.3 Control Flow Hijacking

There are multiple ways to an attacker can hijack the program execution to take over the machine. In many cases, buffer overflows – due to bad programming – offer an entry point for an attacker. They can be exploited to inject code and/or to compromise return addresses stored on the stack to divert the execution flow.

Executing injected code can be mitigated by DEP which prevents written data to be executed. This protection can be circumvented by *code reuse* attacks that rely on (stubs of) existing functions in libraries, so-called gadgets. Known variants of this type of attacks are return-oriented programming (ROP), jump-oriented programming (JOP) or call-oriented programming (COP) [17]. As shown in [68], all such attacks rely on code pointer corruption. In this way, only legitimate code of the application is executed, but the CFG of the program is not respected anymore. Executing injected code can be mitigated by Data Execution Prevention (DEP)/W<sup>X</sup> which prevents written data to be executed. This protection can be circumvented by *code reuse attacks* that rely on (stubs of) existing functions in libraries, so-called *gadgets*. Known variants of this type of attacks are *return-oriented* programming (ROP), jump-oriented programming (JOP) or call-oriented programming (COP) [17]. As shown in [68], all such attacks rely on code pointer corruption. In this way, only legitimate code of the application is executed, but the CFG of the program is not respected anymore.

Another threat – invalidating DEP protections – are fault attacks, where memory contents are altered by physical means [43, 73]. Using the *RowHammer* attack [44], a dynamic RAM cell can be changed by rapidly reading neighboring cells before a refresh. Its stealthiness makes this threat extremely dangerous: Even trusted firmware code with a digital signature can be corrupted when residing in RAM. Some examples of attacks enabled by such modifications are Shamir's bug attack [12] (e.g., on RSA) or Sbox tampering attacks [6] (e.g., on AES). Fault attacks are difficult to master, but can be used to change instructions, to manipulate access rights, to skip an instruction, or to directly change the current program counter, in some cases without violating the CFG.

### **1.4** Control Flow Integrity

Control-Flow Integrity (CFI) refers to protections against control-flow hijacking and was introduced in Abadi's [3] [4] seminal papers. In the paper of 2005 Abadi et al. present a software implementation of CFI. In theory CFI limit all control-flow transfers to those who are intended by the programmer. This prevent the use of code injection, ROP and JOP. CFI is divided in 2 phases, first phase is an analysis phase of the source code to extract the CFG of the programme. This phase can be done on the generated assembly code

#### 1.4. CONTROL FLOW INTEGRITY

but it will be less precise due to the fact we lose information on indirect jump. This is why it is preferable to directly extract the CFG from the source code. The second phase is an enforcement of the CFI by checking the current path of execution against the CFG data extracted during the previous phase.

To prevent control flow hijacking and fault attacks, it is necessary to ensure that control transfer instructions execute as expected, i.e. any control transfer originates from an address that corresponds to a control transfer instruction and targets a valid destination address for this specific instruction. For direct jumps and conditional branches, the valid destinations can be determined at compile-time. Verifying the integrity of these control transfers boils down to checking that for each executed jump or branch, there is a corresponding edge in the function's CFG. We refer to this check as *intraprocedural CFI*.

A different treatment is needed for function calls and returns. Since common functions – such as printf – are called from many sites, just checking that the function returns to one of these call sites does not provide a reasonable protection against ROP attacks. Instead, the correct pairing of call and return addresses needs to be ensured. We refer to this as *inter-procedural CFI*.

It should be noted that indirect jumps and calls pose a special problem for CFI as the set of destination addresses can be significant. However, in many cases – such as a switch statement which has been compiled to an indirect jump – the set of target addresses is usually small and can often be determined at compile-time.

Otherwise, either manual code changes are necessary or these specific instructions must remain unprotected.

While these checks only consider control transfer instructions, it is necessary to ensure that *inside a BB*, all instructions are executed in-order, thereby preventing instruction skips. This verification, which is hard to implement in software, is called *intra-BB CFI*. Finally, *Code integrity* (CI) refers to verifying that all instructions have been executed *unaltered*. This prevent physical injection to to modify an instruction in memory to change the result of computation, to bypass some verification.

In summary, a combined CFI and CI protection must ensure basic block integrity and verify both intra-procedural and inter-procedural control transfers.

### 1.5 Introduction

Software are know to contains unsolicited behavior called bugs. These bugs are present in all kinds of systems ranging from personal computer and cellphone to cloud-servers via industrial control systems. This bug can be a risk for people, environment and also for infrastructures. In fact these bugs are exploited by malicious attackers to extract sensitive data or to take control over the device. While these vulnerabilities can be eliminated by using technique or tools like technical code review, static analysis, usage of memory-safe programming languages or mechanically proved programs, in reality it is difficult to do. This can be due to the complexity and the time needed to use expert tools to prove lack of vulnerabilities. There are also many already existing programs use today which have been written long time ago that have vulnerabilities. One solution would be to rewrite these code in memory safe language but the investment in cost in time is too high the fault to by time-to-market constraints, legacy code reuse, and high competition.

Cyber-attacks exploit these bugs in different ways. There is another threat that can overcome some protection: fault injection. The software attacks exploit bugs or wrong configurations in order to hijack the control flow. In practice, such cyber-attacks mainly operate in two distinct manners. Attacks such as Return-Oriented-Programming (ROP) consist in corrupting the stack such that it calls carefully picked pieces of code called gadgets, which altogether form the attack payload. ROP attacks are thus "code-based". The second type of cyber-attacks exploit contamination of data to force pointers to different locations. Such "data-based" attacks exploit improperly checked user-inputs, which can lead to control-flow contamination. In this article, we focus on "code-based" attacks, including their protection.

*Control-flow integrity* (CFI) refers to protections against control-flow hijacking and was introduced in Abadi's seminal paper [4]. The idea is to verify at run-time by a monitor process or by dedicated hardware that the correct control flow is respected. A common specification of the control flow is given by the static *control flow graph* (CFG) of the application, which can be determined at compile-time.

Since [4] was published many CFI implementation was proposed. There is two main approaches to implement the CFI, software or hardware. Software CFI solutions are convenient mainly because they can be deployed on existing equipment. These solutions rely on instrumenting the software to add self verification or by using an external monitor to check the behavior of the monitored thread. The flexibility of the software solution is at the cost of performance slow down or to only ensure coarse grained CFI, like [21]. On the another hand, hardware solutions are generally proposed in academic papers and rely on hardware monitor to follow the execution of the processor. Or by using cryptographic primitive with core modification to ensure CFI and more. These hardware solution have generally less impact on processor performance but needs modification of the internal of the processor, which is a very high price to pay in the industrial world, like SOFIA implementation [27].

Most CFI approaches assume that the code cannot be modified, due to the presence of widely used *data execution prevention* (DEP) protections. Such a protection is commonly present on high performance processors but rarely deployed on embedded platforms or micro-controllers. Furthermore, different threats may invalidate this assumption: There exist physical attacks able to perform fault injections that result in a modification of the executed code [43, 73]. Since the discovery of the *RowHammer* attack [44], it is known that changes in write protected DRAM can even be induced by software. Hence, *code integrity* (CI) is also to be targeted in order to protect systems against a large body of attacks that disrupt the execution.

Hardware-based solutions range from lightweight solutions – ensuring only some types of control transfer (such as a so-called *shadow stack*) or reducing the amount of reusable code by marking valid call/jump destinations – to solutions covering all control transfers that can be determined statically at compile-time, at link-time, or at load-time of the application [23, 27]. Unfortunately, such approaches either offer coarse-grained protection or does not allow indirect jump or they require a significant modification of the CPU, which prevents them from being deployed in practice due to either the huge amount of work required for validating a modified processor or the use of off-the-shelf processor cores. This is why we target a *non-intrusive* solution that does not modify the CPU core.

Another technical point generally not addressed by CFI implementation is how to handle interruptions. Interruption can happen at any time, and can be seen as a violation of the CFG from an external point of view. It is also necessary that the hardware implementation of CFI addresses the speculative execution or branch prediction. This adds another complexity level to the CFG verification as unused predicted instruction should not be checked by CFI.

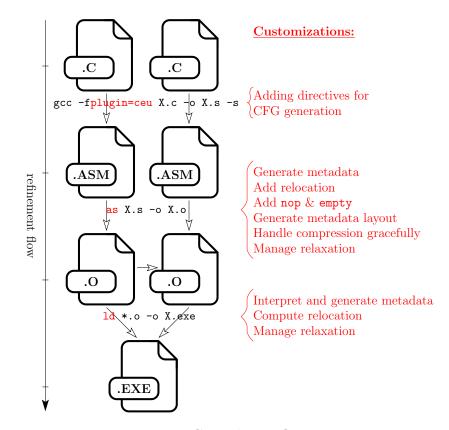

We present a hardware-based solution that combines CFI with CI, while being non-intrusive. The *Code and Control-Flow Integrity* (CCFI) checks are performed at runtime by a dedicated hardware module outside the processor core. The control flow information – referred to as *metadata* – is stored in a dedicated section in memory and is aligned with the instructions. These metadata are fetched by a cache named CCFI-cache. Whenever a new instruction is requested by the processor, the corresponding metadata is fetched transparently and in parallel, so as not to disrupt or slow down the execution flow. The *CCFI-checker* verifies the integrity of execution flow changes by checking the effective target addresses. Function calls and returns are protected by an integrated shadow stack. Additionally, we ensure code and metadata integrity by computing a signature based on the executed instructions and metadata fetched by validating it against a precomputed signature contained in the metadata.

The proposed *CCFI* solution architecture has been implemented on a RISC-V [11] platform, without modifying the processor core and without adding sanity check code within the program. Our experiments show that the run-time overhead is acceptable for different benchmarks. The price to pay for this very flexible solution is a two-fold increase in instruction memory.

In summary, the contribution of this work is a novel hardware-based CFI scheme that:

- is non-intrusive, since the CPU core remains untouched,

- implemented code integrity (CI),

- is fine-grained, in that it enforces intra- and inter-procedural CFI,

- has low run-time overhead, and

- only requires very minor code modifications from the application code side.

The aforementioned protections, namely code integrity check and intraand inter-procedural CFI, address hardware and software threats, to various extents, as depicted in Tab. 1.2. The code integrity is granted by various system-level mechanisms already ( $W^X$ , etc.), but the code is very fragile with respect to hardware-level modifications. On the contrary, control flow hijacking can be achieved more reliabily by the exploitation of software issues. A complete analysis is provided in chapter 3.

Table 1.2: Mapping between CCFI protections and threats

|                        | Hardware attack | Software attack |

|------------------------|-----------------|-----------------|

| Code Integrity         | +++             | +               |

| Control Flow Integrity | +               | +++             |

# Chapter 2

# State-of-the-art

# 2.1 Software weaknesses and associated attacks

# 2.1.1 Introduction

This section first introduces the general structure of a program. Particularly, in the case of Executable Link Format (ELF) format, the static and dynamic structures are described in detail, followed by the vulnerabilities induced by the use of of these representations in memory and how they can be exploited. Finally, different methods for payload creation are reviewed.

## 2.1.2 Program architecture

This section is about the general structure of a program in memory, although some aspects specific to the ELF (Executable Linkable Format) format are mentioned. This format is used by numerous systems, especially GNU/Linux systems (embedded or not). The ELF format specifications are openly available ([20]).

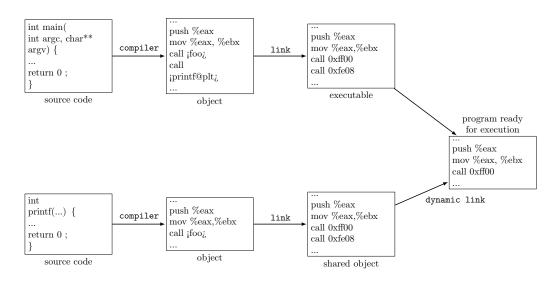

First we present static structures which are declared at compilation time and are allocated inside the ELF file. Secondly we introduce dynamic structures allocated during the execution of the program. Finally we introduce dynamic linking mechanisms for libraries.

#### Static structures

The structure of a program in memory is divided into sections, in order to make memory management easier for the programmer. It is mainly composed of the following sections:

- .text containing the program instructions.

- .rodata containing read-only data.

- .data containing the initialized data, which is accessible for reading and writing.

- .bss containing non initialized data, or data initialized with 0, which is also accessible for reading and writing.

These sections allow to sort the different types of information in memory. For example, the .text and .rodata sections can be read from a non-volatile memory, for example a Flash memory, and the .data section can be copied into Random Access Memory (RAM) to increase performance.

Additionally, some ELF binaries are endowed with .init, .fini .ctors and .dtors sections, which serve to call initialization code (.init, .ctors) or termination code at the program exit (.fini, .dtors).

It is important to note that microprocessors have no knowledge of the semantic that the developer choose to assign to each of the sections. To be more precise, the microprocessor does not even consider the notion of section at hardware level, as it is actually a generic calculation module. The data semantic and the breakdown into sections are defined by the developer for convenience. The attacks introduced later in this document are linked to the genericity property of the microprocessor, viewed as a general execution module.

It is interesting to note that the control of sections such as .text, .fini or .dtors may give an attacker the control of the instruction flow during the execution or at the program termination. These sections are therefore sensitive areas. Also, the possibility to execute code from the .data section is an ideal attack mean, as it is explained in the next sections.

After this introduction about the main big "static" structures of a program, the next section covers "dynamic" structures, namely the heap and the stack.

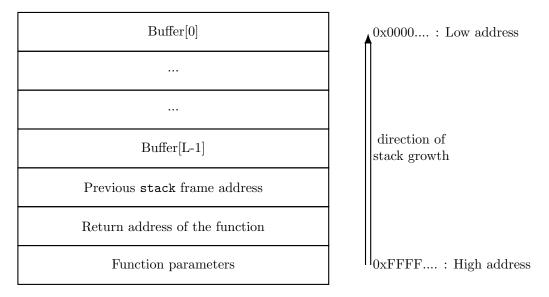

#### Dynamic structures

The heap and stack are also stored in RAM. These structures allow the user to perform dynamic allocation during the program execution, unlike the others sections previously presented which are statically allocated (even though their content changes dynamically).

**Function calls and stack:** For programming flexiblity, programs are organized in functions. This allows to reuse code at several locations in the program, and also to use recursive procedures.

Each function needs resources to be functional, particularly local variables. Moreover, it is necessary to store the parameters of a function call, as well as the state of the registers of a calling function in order to resume the previous computation after the called function was correctly executed.

The microprocessor registers, being limited in number (16 on Intel x86 architectures), dynamic allocation is necessary to satisfy the memory needs of functions. To store all these data (local variables, registers, parameters and return address), we use a stack structure. This stack is a dynamic structure allocated during the execution of program. Each time a function is called, it is used to save the current state of registers and store the address where to return once the called function has finished. A function can also store their local variables on the stack to be able to manage more data than the number of available registers.

At hardware level, the stack is generally addressed by at least one register which serves to identify its top position, as seen in the microprocessor address space.

Function call conventions, and therefore the organisation of data on the stack, may vary depending on the considered microprocessor architecture, the compiler, and the Operating System. For example, some microprocessors have both a register to store the stack current top position, called stack pointer, and a register to save the stack top position before the last function call. This register is generally called frame pointer and is frequently used as a reference to locate data on the stack more easily, in particular the function call parameters. A frame is a memory section of the stack where data of the current function is stored. In a normal behavior the function must not access to other sections of the stack. frame pointer is used to access local variables more easily than by using the stack pointer.

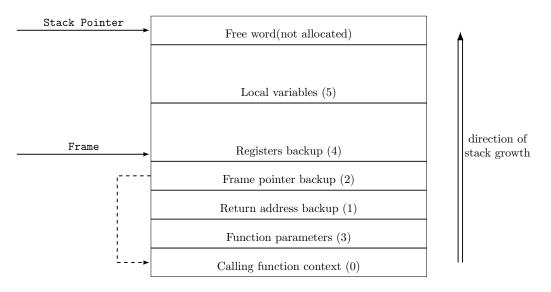

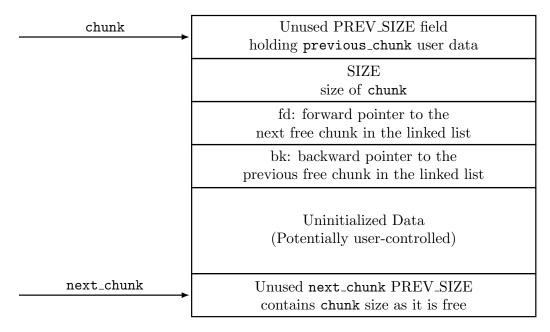

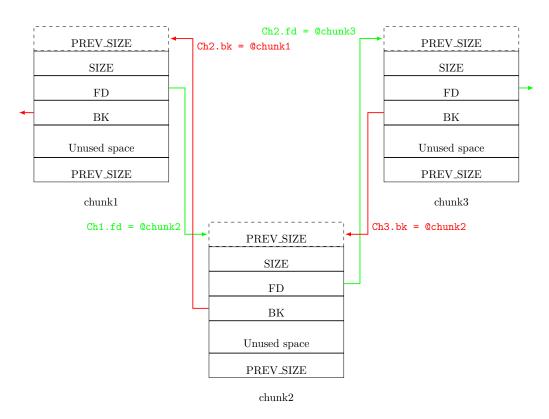

Figure 2.1 (page 40) shows how the various items are saved on the stack

Figure 2.1: Typical data structure on the stack

when a function is called, including at least a return address (1) to get back to the calling function, and optionally the **frame pointer** (2). The function arguments (3) can be passed partially by the registers (e.g. on SPARC architecture) or fully on the stack. Finally, the called function starts its execution by saving the processor registers that will be used (4), and by allocating the necessary space for local variables (5) that cannot be saved into registers. These registers used by the function are then restored to their original state before resuming the calling function.