# Optimization and parallelization methods for software-defined radio

Adrien Cassagne

#### ▶ To cite this version:

Adrien Cassagne. Optimization and parallelization methods for software-defined radio. Networking and Internet Architecture [cs.NI]. Université de Bordeaux, 2020. English. NNT: 2020BORD0231. tel-03118420v2

## HAL Id: tel-03118420 https://theses.hal.science/tel-03118420v2

Submitted on 6 Sep 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE PRÉSENTÉE POUR OBTENIR LE GRADE DE

# DOCTEUR DE L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE MATHÉMATIQUES ET INFORMATIQUE SPÉCIALITÉ : INFORMATIQUE

par Adrien Cassagne

# Méthodes d'optimisation et de parallélisation pour la radio logicielle

Co-directeurs de thèse : Denis Barthou

Christophe Jégo

Co-encadrants de thèse: Olivier Aumage

Camille Leroux

préparée au Centre de Recherche Inria Bordeaux - Sud-Ouest et au Laboratoire de l'Intégration du Matériau au Système (IMS)

soutenue le 8 décembre 2020

#### Jury:

Professeur des Universités Sorbonne Université Lionel LACASSAGNE -Rapporteur Université de Rennes 1 Matthieu Gautier Maître de Conférences, HDR RapporteurMichel Jezequel - Professeur des Universités IMT Atlantique Président Cédric Bastoul Directeur Scientifique, HDR Huawei Paris ExaminateurCamille Leroux - Maître de Conférences Bordeaux INP Examinateur Olivier Aumage Chargé de Recherche, HDR Inria Examinateur Christophe Jégo Professeur des Universités Bordeaux INP Co-directeur Denis Barthou Professeur des Universités Bordeaux INP Co-directeur

Thèse réalisée au Centre de Recherche Inria Bordeaux - Sud-Ouest, au sein de l'équipe projet STORM.

Université de Bordeaux Centre de Recherche Inria Bordeaux - Sud-Ouest 200 Avenue de la Vieille Tour 33405 Talence

Thèse réalisée au Laboratoire de l'Intégration du Matériau au Système (IMS) de Bordeaux, au sein de l'équipe CSN du groupe Conception.

Université de Bordeaux, Laboratoire IMS UMR 5218 CNRS - Bordeaux INP 351 Cours de la Libération Bâtiment A31 33405 Talence Cedex

## Remerciements

Je tiens en premier lieu à remercier les membres du jury pour l'intérêt qu'ils ont porté à ces travaux. Je remercie donc chaleureusement Monsieur Lionel LACASSAGNE, professeur de Sorbonne Université et Monsieur Matthieu GAUTIER, maître de conférences de l'Université de Rennes 1 de m'avoir fait l'honneur de rapporter ce travail de thèse. Je remercie aussi Monsieur Michel JEZEQUEL, professeur de l'Institut Mines-Télecom Atlantique d'avoir présidé le jury ainsi que Monsieur Cédric BASTOUL, directeur scientifique chez Huawei, d'avoir accepté d'examiner ma thèse.

Je remercie sincèrement mes encadrants qui ont été exceptionnels, chacun sur des aspects différents. Camille, merci pour tes explications claires et imagées, pour ta croyance sans faille dans le projet, et bien sûr pour les moments passés en dehors. Olivier, merci pour ton expertise précieuse, ton soutient lors des changements de direction et pour ta patience et ton aide lors des phases de rédaction. Christophe, merci de m'avoir toujours soutenu, en commençant par le réagencement de notre espace de travail jusqu'au soutient infaillible dans le projet. Dans ces conditions il était naturel de pouvoir évoluer sereinement. Denis, merci de m'avoir fait confiance et de m'avoir donné l'opportunité de pouvoir intégrer le monde de la recherche. Merci d'avoir su me guider dans ce projet, ton recul et tes conseils avisés m'ont beaucoup apporté.

Merci à tous mes collègues de l'équipe CSN d'avoir contribué à l'excellente ambiance de travail. Je pense à Baptiste, Bertrand, Camilo, Dominique, Guillaume B., Guillaume D., Imen, Jérémie, Jonathan, Logan, Malek, Mathieu, Olivier, Thibaud, Vincent, Yann et Yassine.

Et, pour les mêmes raisons, aussi un grand merci à tous mes collègues de l'équipe STORM. Je pense à Alexis, Amina, Baptiste, Célia, Chiheb, Corentin, Emmanuelle, Hugo, Jean-Marie, Kun, Léo, Maël, Marie-Christine, Mariem, Mehdi, Nathalie, PAW, Philippe, Pierre, Raymond, Romain, Sabrina, Samuel et Yanis.

Je tiens à remercier tout particulièrement le noyau dur de l'équipe AFF3CT avec qui nous avons partagé des moments forts. Romain, merci pour tes nombreuses explications, ta motivation sans faille et tes qualités humaines, ça a été un réel plaisir de pouvoir travailler avec toi. Olivier, merci d'avoir autant accroché au projet, d'avoir toujours su proposer des nouvelles idées et de m'avoir supporté. Tu es incontestablement un des plus grand contributeur et une personne avec qui j'ai adoré travailler. Mathieu, que dire, merci d'avoir toujours cru au projet, de l'avoir adopté et d'avoir été le premier doctorant à prouver qu'il était possible d'en tirer parti et de l'enrichir. Je suis aussi extrêmement fier du travail accompli ensemble.

Pour terminer, je veux dire un mot à tous les gens qui me sont chers en dehors du travail et qui se reconnaîtront. Vous avez joué un rôle déterminant dans le bon déroulement de cette thèse, à différents moments et à différents niveaux. Pour cela je vous remercie infiniment et j'espère avoir la chance de vous avoir à mes côtés encore longtemps.

## Résumé

Une radio logicielle (en anglais Software-Defined Radio ou SDR) est un système de communications numériques reconfigurable utilisant des techniques de traitement du signal sur des architectures numériques programmables. Avec l'émergence de nouveaux standards de communications complexes et la puissance de calcul grandissante des processeurs généralistes, il devient intéressant d'échanger l'efficacité énergétique des architectures dédiées contre la souplesse et la facilité d'implémentation sur processeurs généralistes.

Même lorsque l'implémentation d'un traitement numérique est finalement faite sur une puce dédiée, une version logicielle de ce traitement s'avère nécessaire en amont pour s'assurer des bonnes propriétés de la fonctionnalité. Cela est généralement réalisé via la simulation. Les simulations sont cependant souvent coûteuses en temps de calcul. Il n'est pas rare de devoir attendre plusieurs jours voire plusieurs semaines pour évaluer les performances du modèle fonctionnel d'un système.

Dans ce contexte, cette thèse propose d'étudier les algorithmes les plus coûteux en temps de calcul dans les chaînes de communication numériques actuelles. Ces algorithmes sont le plus souvent présents dans des décodeurs de codes correcteurs d'erreurs au niveau récepteur. Le rôle du codage canal est d'accroître la robustesse vis à vis des erreurs qui peuvent apparaître lorsque l'information transite au travers d'un canal de transmission. Trois grandes familles de codes correcteurs d'erreurs sont étudiées dans nos travaux, à savoir les codes LDPC, les codes polaires et les turbo codes. Ces trois familles de codes sont présentes dans la plupart des standards de communication actuels comme le Wi-Fi, l'Ethernet, les réseaux mobiles 3G, 4G et 5G, la télévision numérique, etc. Les décodeurs qui en découlent proposent le meilleur compromis entre la résistance aux erreurs et la vitesse de décodage. Chacune de ces familles repose sur des algorithmes de décodage spécifiques. Un des enjeux principal de cette thèse est de proposer des implémentations logicielles optimisées pour chacune des trois familles. Des réponses sont apportées de façon spécifique puis des stratégies d'optimisation plus générales sont discutées. L'idée est d'abstraire des stratégies d'optimisation possibles en étudiant un sous-ensemble représentatif de décodeurs.

Enfin, la dernière partie de cette thèse propose la mise en œuvre d'un système de communications numériques complet à l'aide de la radio logicielle. En s'appuyant sur les implémentations rapides de décodeurs proposées, un émetteur et un récepteur compatibles avec le standard DVB-S2 sont implémentés. Ce standard est typiquement utilisé pour la diffusion de contenu multimédia par satellite. À cette occasion, un langage dédié à la radio logicielle est développé pour tirer parti de l'architecture parallèle des processeurs généralistes actuels. Le système atteint des débits suffisants pour être déployé en condition opérationnelle.

Les différentes contributions des travaux de thèse ont été faites dans une dynamique d'ouverture, de partage et de réutilisabilité. Il en résulte une bibliothèque à code source ouvert nommée AFF3CT pour A Fast Forward Error Correction Toolbox. Ainsi, tous les résultats proposés dans cette thèse peuvent aisément être reproduits et étendus. Cette philosophie est détaillée dans un chapitre spécifique du manuscrit de thèse.

Mots clefs : Radio logicielle, Simulation fonctionnelle, Codes correcteurs d'erreurs, Implémentation logicielle, Optimisation, Parallélisation, Code source ouvert

## Abstract

A software-defined radio is a radio communication system where components traditionally implemented in hardware are instead implemented by means of software. With the growing number of complex digital communication standards and the general purpose processors increasing power, it becomes interesting to trade the energy efficiency of the dedicated architectures for the flexibility and the reduced time to market on general purpose processors.

Even if the resulting implementation of a signal processing is made on an application-specific integrated circuit, the software version of this processing is necessary to evaluate and verify the correct properties of the functionality. This is generally the role of the simulation. Simulations are often expensive in terms of computational time. To evaluate the global performance of a communication system can require from few days to few weeks.

In this context, this thesis proposes to study the most time consuming algorithms in today's digital communication chains. These algorithms often are the channel decoders located on the receivers. The role of the channel coding is to improve the error resilience of the system. Indeed, errors can occur at the channel level during the transmission between the transmitter and the receiver. Three main channel coding families are then presented: the LDPC codes, the polar codes and the turbo codes. These three code families are used in most of the current digital communication standards like the Wi-Fi, the Ethernet, the 3G, 4G and 5G mobile networks, the digital television, etc. The resulting decoders offer the best compromise between error resistance and decoding speed known to date. Each of these families comes with specific decoding algorithms. One of the main challenge of this thesis is to propose optimized software implementations for each of them. Specific efficient implementations are proposed as well as more general optimization strategies. The idea is to extract the generic optimization strategies from a representative subset of decoders.

The last part of the thesis focuses on the implementation of a complete digital communication system in software. Thanks to the efficient decoding implementations proposed before, a full transceiver, compatible with the DVB-S2 standard, is implemented. This standard is typically used for broadcasting multimedia contents via satellite. To this purpose, an embedded domain specific language targeting the software-defined radio is introduced. The main objective of this language is to take advantage of the parallel architecture of the current general purpose processors. The results show that the system achieves sufficient throughputs to be deployed in real-world conditions.

These contributions have been made in a dynamic of openness, sharing and reusability, it results in an open source library named AFF3CT for A Fast Forward Error Correction Toolbox. Thus, all the results proposed in this thesis can easily be reproduced and extended. This philosophy is detailed in a specific chapter of the thesis manuscript.

Keywords: Software-Defined Radio, Functional Simulation, Error Correcting Codes, Software Implementation, Optimization, Parallelization, Open Source Code

## Résumé étendu

### Chapitre 1 - Contexte et objectifs

#### Organisation

Ce chapitre présente le contexte des systèmes de communications numériques. Il a pour but de définir les notions qui seront réutilisées dans le manuscrit et de donner une vue globale. Il définit aussi les principaux objectifs de cette thèse. La première partie présente le principe des systèmes de communications numériques avec ses différentes composantes : l'émetteur, le canal et le récepteur. Les métriques les plus couramment utilisées dans les communications numériques sont présentées avec notamment la définition du taux d'erreur binaire (Bit Error Rate, BER) et du taux d'erreur trame (Frame Error Rate, FER). La deuxième partie détaille le modèle de canal qui correspond à un ajout d'un bruit blanc gaussien (Additive White Gaussian Noise, AWGN) et la modulation numérique binaire par changement de phase (Binary Phase-Shift Keying, BPSK) utilisés tout au long du manuscrit. Une caractérisation du rapport signal sur bruit (Signal-to-Noise Ratio, SNR) est donnée ainsi que la notion de probabilité à la sortie du canal et du démodulateur. La troisième partie présente les familles de code correcteur d'erreurs considérées dans ce manuscrit, à savoir les codes LDPC, les codes polaires et les turbo-codes. Les traitements de codage (situé au niveau de l'émetteur) et de décodage (situé au niveau du récepteur) correspondants sont détaillés pour chaque famille de code. Ces familles de code sont utilisées dans la plupart des standards de télécommunication actuels et engendrent une complexité calculatoire élevée. Par conséquent, ce sont de bons candidats d'étude. Dans la dernière partie, deux contextes applicatifs majeurs sont détaillés pour les familles de code considérées. La "simulation fonctionnelle" permet la conception et la validation d'un schéma de codage. La "radio logicielle" (Software-Defined Radio, SDR) est un système de communication radio où tous les composants sont implémentés avec des blocs logiciels (par opposition à des implémentations matérielles plus couramment utilisées dans ce domaine).

#### Objectifs de la thèse

À l'aube de la cinquième génération des standards pour la téléphonie mobile (5G), le défi consiste maintenant à concevoir des systèmes de communication capables de transmettre une grande quantité de données en peu de temps, à un faible coût énergétique et dans des environnements très variés. Les chercheurs s'efforcent d'affiner encore les schémas de codage existants, afin d'obtenir de faibles taux d'erreur résiduels grâce à des processus de décodage rapides, souples et aussi peu complexe que possible.

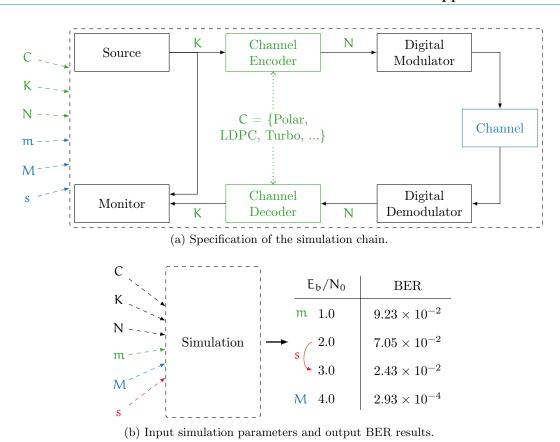

Simulation fonctionnelle La validation d'un système de codage nécessite d'estimer son taux d'erreur. En général, il n'existe pas de modèle mathématique simple pour décrire ce type de performance. La seule solution pratique consiste à effectuer une simulation de type Monte Carlo de l'ensemble de la chaîne de transmission. Cela signifie que certaines données sont générées,

encodées, modulées, bruitées, décodées de manière aléatoire, et que les performances sont ensuite estimées en mesurant le taux d'erreur binaire (BER) et le taux d'erreur trame (FER) à la fin de la chaîne de communication (après décision du décodeur). Ce processus a l'avantage d'être universel mais il entraîne également trois problèmes principaux :

- 1. Temps de simulation : ~ 100 trames erronées doivent être simulées pour estimer avec précision les BER/FER. Ainsi, la mesure d'un FER de 10<sup>-7</sup> nécessite la simulation de la transmission de ~ 100 × 10<sup>7</sup> = 10<sup>9</sup> trames. En supposant une trame de 1000 bits, le simulateur doit alors traiter la transmission de 10<sup>12</sup> bits. En gardant à l'esprit que la complexité de calcul de l'algorithme de décodage peut être importante, plusieurs semaines voire plusieurs mois peuvent être nécessaires pour estimer avec précision les BER/FER d'un schéma de codage (en particulier si le taux d'erreur est faible).

- 2. Hétérogénéité algorithmique: un grand nombre de codes correcteurs d'erreurs ont été conçus au fil des années. Pour chaque famille de code, plusieurs configurations de décodage sont possibles. Si il est simple de décrire un schéma de codage unique, il est plus difficile d'avoir une description logicielle unifiée qui prenne en charge tous les schémas de codage et les algorithmes de décodage associés. Cette difficulté provient de l'hétérogénéité des structures de données nécessaires pour décrire les différents schémas de codage canal : les turbo-codes sont basés sur des treillis, les codes LDPC sont bien définis par des graphes bipartis et les codes polaires sont décodés efficacement à l'aide d'arbres binaires.

- 3. Reproductibilité: il est généralement fastidieux de reproduire des résultats issus de la littérature. Cela peut s'expliquer par la grande quantité de paramètres empiriques nécessaires pour définir un système de communication, et par le fait que tous ne sont pas toujours rapportés dans les publications. En outre, le code source des simulateurs est rarement accessible au public. Par conséquent, beaucoup de temps est passé à "réinventer la roue" juste pour pouvoir comparer de nouveaux résultats avec l'état de l'art.

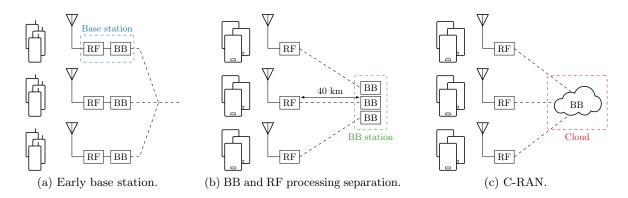

Radio logicielle Le paradigme de la radio logicielle (Software-Defined Radio, SDR) est désormais considéré pour des systèmes de communications numériques réels. Pour répondre aux contraintes posées par les systèmes temps réel, voici les principaux défis à relever :

- 1. **Haut débit :** les nouvelles applications comme le *streaming* vidéo, peuvent être très gourmandes en données. Par conséquent, les tâches de calcul intensif au sein de l'émetteur et du récepteur doivent être bien optimisées pour atteindre des niveaux de performance comparables à des implémentation matérielles.

- 2. Faible latence : atteindre un débit élevé n'est pas toujours la contrainte majeure, par exemple, dans les applications d'audio-conférence, il est inconfortable de percevoir un retard lorsque les gens parlent.

- 3. Flexibilité: les implémentations logicielles doivent pouvoir s'adapter à diverses configurations. Par exemple, lorsque le rapport signal sur bruit (SNR) change, le décodeur doit être capable se s'adapter "à la volée" à de nouveaux taux de codage.

- 4. **Portabilité :** les solutions proposées peuvent être déployées sur des serveurs haut de gamme ainsi que dans des systèmes embarqués à faible consommation énergétique. De plus, de nombreux systèmes d'exploitation coexistent et il est important de pouvoir supporter les plus communs comme Windows, macOS et Linux.

### Chapitre 2 - Stratégies d'optimisation

#### Organisation

Ce chapitre se concentre sur les stratégies d'optimisation dédiées aux algorithmes de communications numériques. Nos contributions sont divisées en deux parties : 1) les stratégies génériques et 2) les optimisations spécifiques. La première partie décrit les stratégies génériques que nous avons proposées pour optimiser les algorithmes présents dans les récepteurs de systèmes de communications numériques. Il s'avère que la vectorisation est une des clefs pour implémenter des solutions logicielles efficaces. Une bibliothèque dédiée ainsi que des niveaux de parallélisme génériques sont proposés. La seconde partie est consacrée à l'implémentation logicielle efficace d'un sous-ensemble représentatif de décodeurs pour les trois grandes familles de code abordées plus tôt, à savoir : les codes LDPC, les codes polaires et les turbo-codes.

#### Principaux résultats

En premier lieu, des stratégies génériques pour l'implémentation efficace d'algorithmes sur processeurs généralistes (CPUs) sont présentées. Une contribution majeure dans ce chapitre est la proposition de MIPP: une bibliothèque qui encapsule les instructions vectorielles. L'idée est d'abstraire les types de données et les multiples jeux d'instructions vectoriels existants afin de proposer des implémentations logicielles "universelles" et efficaces des algorithmes présents dans les récepteurs de systèmes de communications numériques. Nous montrons que MIPP n'introduit presque pas de surcoût par rapport aux fonctions intrinsèques (ou du code assembleur). MIPP fonctionne aussi bien sur des représentations en virgule flottante et que sur des représentations en virgule fixe. Pour les algorithmes présents dans les récepteurs de systèmes de communications numériques, les représentations en virgule fixe sont très intéressantes car elles permettent de traiter un plus grand nombre d'éléments dans les registres vectoriels, avec un impact modéré sur les performances de décodage. Pour résumer, MIPP améliore la flexibilité et la portabilité du code source tout en conservant un même niveau de performance. Notez que la bibliothèque MIPP a été valorisée suite à une publication dans une conférence scientifique internationale [7].

Dans une deuxième partie, deux grandes stratégies de vectorisation sont explicitement définies et présentées. La stratégie intra-trame fonctionne sur une seule trame en s'appuyant sur le parallélisme inhérent à l'algorithme. La stratégie inter-trames fonctionne quant à elle sur plusieurs trames en même temps. La stratégie intra-trame peut à la fois augmenter le débit et diminuer la latence. Au contraire, la stratégie inter-trames n'améliore pas la latence. Elle s'accompagne cependant d'une efficacité vectorielle potentiellement plus élevée et peut conduire à des débits très élevés. Ces deux stratégies peuvent être appliquées à tous les blocs de traitement des chaînes de communications numériques. Les stratégies intra-trame et inter-trames constituent donc un point clé pour résoudre le problème de l'hétérogénéité algorithmique.

Les dernières parties du chapitre se concentrent sur la conception d'implémentations logicielles efficaces des algorithmes de décodage présentés dans le chapitre précédent. Les décodeurs LDPC, les décodeurs polaires et le turbo-décodeur sont compatibles avec la stratégie inter-trames, tandis que les décodeurs polaires sont aussi compatibles avec la stratégie intra-trame. En fonction des familles de codes, nous nous concentrons sur différentes contraintes. Les décodeurs LDPC ont été mis en œuvre pour prendre en charge de nombreuses variantes et donc pour maximiser la flexibilité au prix de débits plus faibles et de latences plus élevées par rapport à d'autres

travaux. Ce choix permet d'évaluer les performances de décodage de nombreuses combinaisons algorithmiques. Dans les décodeurs polaires, la flexibilité ainsi que des optimisations agressives sont considérées et comparées. Ces dernières permettent d'atteindre de très faibles latences. Enfin, le turbo-décodeur se concentre sur l'obtention de débits les plus élevés possibles. Certaines spécialisations sont faites pour le standard LTE. Il est à noter que la plupart des implémentations logicielles proposées ont fait l'objet de publications dans des conférences et des revues scientifiques internationales [2, 3, 4, 5, 6].

### Chapitre 3 - AFF3CT : une boîte à outils pour le codage canal

#### Organisation

Ce chapitre est consacré à la présentation de notre boîte à outils open-source nommée AFF3CT. La première partie décrit les principaux prérequis en fonction de quatre objectifs : l'implémentation d'un logiciel hautement performant, la prise en charge de l'hétérogénéité algorithmique, la portabilité et la reproductibilité. Dans la deuxième partie, AFF3CT est comparé aux autres bibliothèques logicielles de codage canal C/C++ existantes. La troisième partie présente AFF3CT comme une bibliothèque dédiée aux algorithmes de communications numériques. L'architecture et les fonctionnalités du logiciel sont décrites. Ensuite, des exemples d'utilisation de la bibliothèque sont donnés en C++ et en MATLAB®. La quatrième partie se concentre sur le simulateur AFF3CT qui est livré dans la boîte à outils. Un aperçu des explorations possibles est donné et notre comparateur de BER/FER est présenté. À la fin, la stratégie de test d'AFF3CT est expliquée. Une dernière partie est consacrée à l'impact d'AFF3CT dans les contextes industriels et universitaires. Une revue des publications scientifiques qui ont utilisé AFF3CT est donnée.

#### Principaux résultats

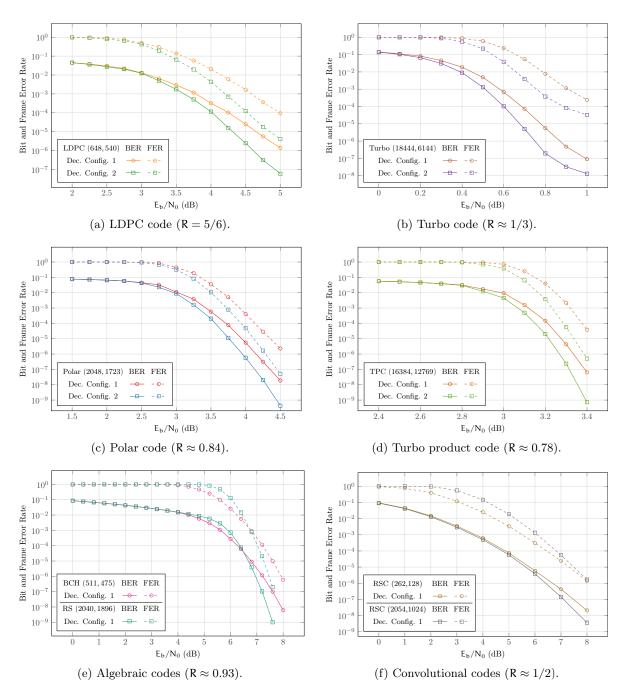

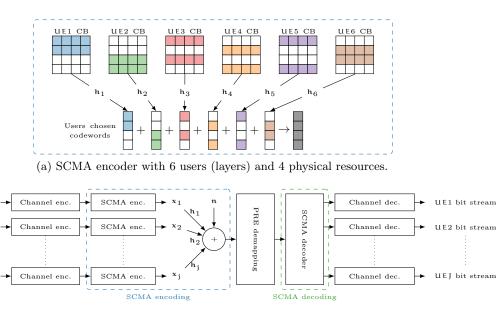

Tout d'abord, l'accent est mis sur la bibliothèque AFF3CT qui vient avec une architecture logicielle qui permet l'hétérogénéité algorithmique. De nombreuses familles de code correcteur d'erreurs sont supportées comme les codes LDPC, les codes polaires, les turbo-codes, les turbo-codes produit, les codes convolutifs, les codes BCH, les codes Reed-Solomon, etc. À notre connaissance, AFF3CT est la bibliothèque qui offre le support le plus complet pour les algorithmes associés au codage canal. AFF3CT est également livré avec de multiples modèles de canaux (AWGN, Rayleigh, BEC, BSC, etc.) et différents schémas de modulation numérique (PSK, QAM, PAM, OOK, CPM, SCMA, etc.). Toutes ces implémentations logicielles efficaces d'algorithmes peuvent être utilisées à partir d'interfaces. Des exemples d'utilisation de la bibliothèque sont donnés en C++ natif ou en utilisant l'encapsulation MATLAB®. La boîte à outils AFF3CT a fait l'objet de publications dans une conférence et une revue scientifique internationale [8, 1].

AFF3CT est également fourni avec un simulateur fonctionnel de BER/FER. Toutes les caractéristiques précédemment énumérées peuvent être simulées sur différents paramètres. Sa capacité à explorer une grande variété de paramètres est démontrée. De nombreux paramètres peuvent être modifiés comme le nombre d'itérations de décodage, les approximations dans l'implémentation des algorithmes, la quantification des données dans les décodeurs, etc. Certains de ces paramètres sont présentés pour les décodeurs introduits dans les chapitres précédents. Ce sujet a été valorisé par un article dans une conférence nationale [9].

AFF3CT est conçu pour permettre la reproductibilité des résultats scientifiques. Un outil de comparaison des performances de décodage (BER/FER) a été ajouté pour permettre une recherche facile dans une base de données d'environ 500 références pré-simulées. Toutes ces références sont des résultats simulés avec AFF3CT qui peuvent être aisément reproduits. À cette fin, une suite de tests a été mis en place. Chaque fois qu'il y a une modification du code source, la base de données des références est rejouée pour éviter des problèmes de régression. Ces tests sont également effectués sur plusieurs architectures (x86 et ARM®) et systèmes d'exploitation (Windows, macOS et Linux) afin de garantir que la portabilité soit toujours conservée.

La dernière partie du chapitre traite de l'impact d'AFF3CT dans la communauté. Il est montré que de plus en plus d'utilisateurs adoptent la boîte à outils AFF3CT aussi bien dans l'industrie que dans les milieux académiques. Les contextes applicatifs sont variés et vont de la validation des performances de décodage à l'utilisation de sous-parties spécifiques de la bibliothèque. Les contributions externes sont cependant encore rares.

### Chapitre 4 - Évaluation et comparaison des performances

#### Organisation

Ce chapitre propose d'évaluer les différentes contributions exposées dans les chapitres précédents. Les trois premières parties se concentrent sur les implémentations logicielles efficaces de décodeurs LDPC, de décodeurs polaires et d'un turbo-décodeur. Le débit, la latence et l'efficacité énergétique sont étudiés et comparés avec d'autres travaux de la littérature. La quatrième partie résume les implémentations de décodeurs logiciels les plus efficaces que nous avons trouvées dans la littérature. Cet état de l'art est décomposé en trois catégories distinctes : une pour les décodeurs LDPC, une pour les décodeurs polaires et une pour les turbo-décodeurs. Certaines métriques sont spécifiées afin de faciliter la comparaison entre les différentes publications. La dernière partie est consacrée à une analyse des performances du simulateur AFF3CT. Une chaîne de communications numériques représentative est définie et évaluée en séquentiel et en parallèle. Cette chaîne utilise un décodeur polaire rapide évalué plus tôt dans le chapitre.

#### Principaux résultats

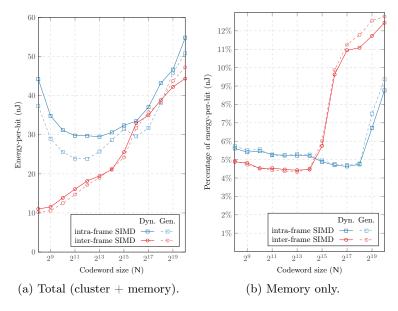

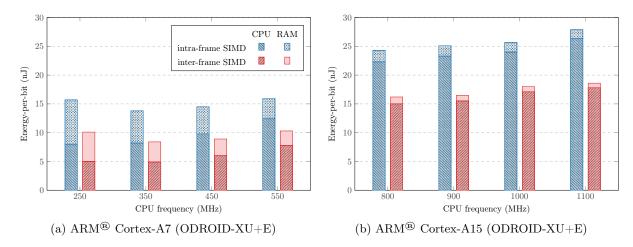

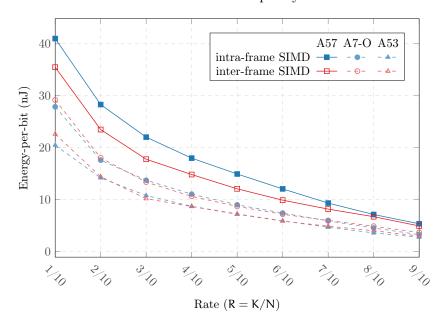

Pour les décodeurs LDPC et les turbo-décodeurs, la stratégie inter-trames a été appliquée. Elle permet d'obtenir des débits comparables aux meilleurs travaux de la littérature. Toutefois, les latences ne sont pas compétitives avec les meilleures implémentations de type intra-trame que l'on trouve dans la littérature. L'implémentation inter-trames proposée est alors davantage orientée vers la simulation ou vers des applications en temps réel qui ne nécessitent pas une faible latence comme le streaming vidéo, par exemple. Pour les décodeurs polaires, les stratégies inter-trames et intra-trame ont été implémentées. Il en résulte un framework complet qui peut s'adapter à de nombreux contextes applicatifs. Les décodeurs proposés sont parmi les plus rapides de la littérature. Ils peuvent également être très flexibles avec les implémentations dynamiques ou spécialisés pour des performances maximales avec la technique de génération de code source. Pour tous les décodeurs proposés (code LDPC, code polaire et turbo-code), le niveau de généricité est l'une de nos principales contributions. Les implémentations sont capables de s'adapter à différentes architectures de CPU ainsi que de supporter de nombreuses variantes algorithmiques. De plus, chacune des implémentations présentées est capable de travailler à un niveau proche des performances de

décodage de référence. La plupart des résultats obtenus ont été publiés dans des conférences et des revues scientifiques internationales [2, 3, 4, 5, 6].

Les "Temples de la renommée" (Hall of Fames, HoFs) des décodeurs logiciels sont ensuite présentés. Ces HoFs représentent des états de l'art complets de chaque famille de code correcteur d'erreurs. Les implémentations de décodeur proposées dans la thèse sont comparées avec les autres travaux de la littérature. Ces HoFs permettent de comparer les implémentations CPU et GPU. Certaines mesures telles que le débit normalisé, le TNDC et la consommation d'énergie sont définies. Les résultats montrent que ces dernières années, les implémentations CPU sont plus efficaces que les implémentations GPU en termes de débit, de latence et d'efficacité énergétique. L'un des principaux problèmes des implémentations basées sur GPU est le temps de transfert nécessaire entre le CPU et le GPU. Un autre problème majeur vient de l'architecture intrinsèque des GPUs qui nécessite un parallélisme très élevé pour être efficace. Il n'est pas toujours possible de tirer parti de ce niveau élevé de parallélisme dans les algorithmes de décodage de code correcteur d'erreurs. Par conséquent, en général, les CPUs sont plus adaptés pour des implémentations logicielles à faible latence que les GPUs.

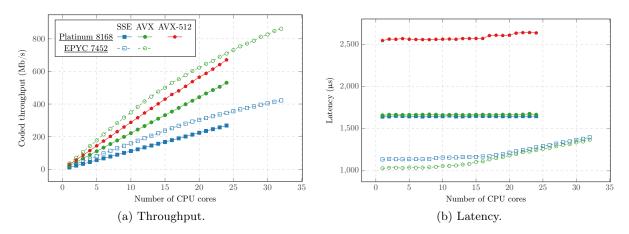

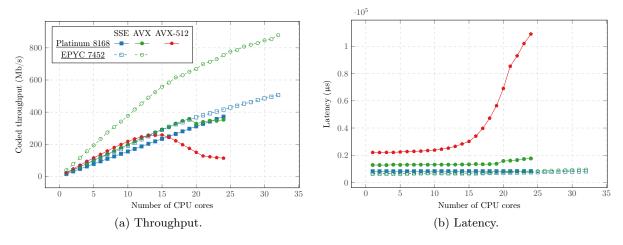

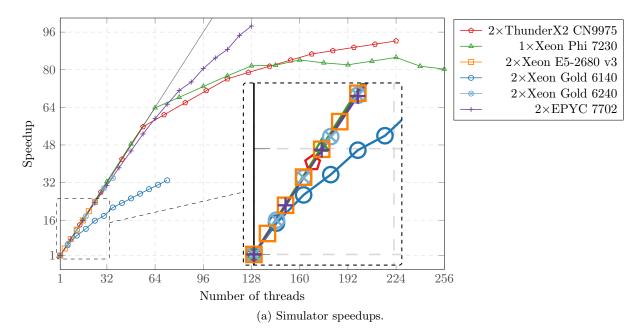

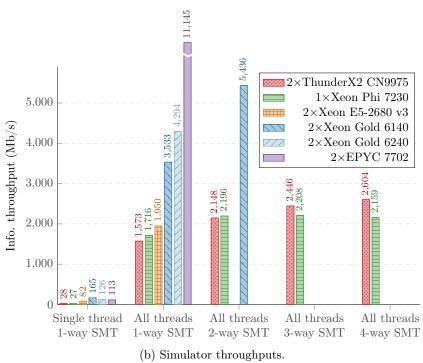

La dernière partie de ce chapitre est consacrée aux performances du simulateur AFF3CT. Une chaîne de communications numériques entièrement vectorisée est proposée pour l'évaluation. Des performances sur un seul cœur de calcul CPU sont d'abord présentées. Il en résulte qu'AFF3CT fonctionne le plus rapidement sur les derniers processeurs Intel<sup>®</sup> Gold qui supportent le jeu d'instructions vectorielles "AVX-512". Ensuite, les performances sur plusieurs cœurs de calcul sont mises à l'épreuve. Dans ce cadre, les processeurs AMD<sup>®</sup> EPYC s'avèrent être les plus performants : le débit utile de la chaîne atteint 11 Gb/s. Même si les processeurs AMD<sup>®</sup> EPYC ne prennent en charge que les instructions de type "AVX", il semble que l'architecture Zen 2 soit bien équilibrée entre la puissance de calcul et la vitesse de la mémoire. Enfin, la capacité multi-nœuds du simulateur AFF3CT est testée et une accélération linéaire est observée sur 32 nœuds. Le débit de pointe en multi-nœuds est de 32 Gb/s. Ces débits élevés permettent l'exploration de nombreuses combinaisons à un niveau de taux d'erreur très faible. Une partie de ces résultats ont été publiés dans une revue scientifique internationale [1]. À l'heure actuelle et à notre connaissance, AFF3CT est l'un des simulateurs de codes correcteurs d'erreurs le plus rapide.

### Chapitre 5 - Langage embarqué et dédié à la radio logicielle

#### Organisation

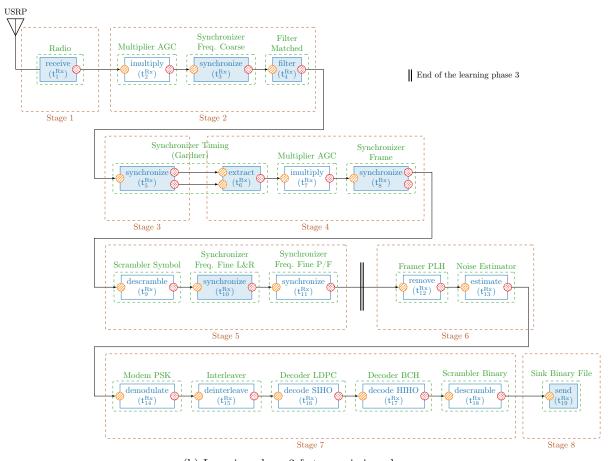

Ce chapitre présente un nouveau langage embarqué et dédié (embedded Domain Specific Language, eDSL) à la radio logicielle (SDR). La première partie décrit les modèles et solutions existants. Elle motive également le besoin d'un nouveau langage dédié à la radio logicielle. Dans une deuxième partie, une description de l'eDSL proposé est donnée et détaillée en deux sous-parties. Dans un premier temps, les composants élémentaires sont présentés, puis, dans un second temps, les composants parallèles sont décrits. La troisième partie se concentre sur l'implémentation des composants présentés précédemment. Entre autres, la technique de duplication des séquences et l'implémentation du pipeline sont discutées. Enfin, la dernière partie présente un cas concret d'utilisation de l'eDSL sur un standard bien répandu dans les communications numériques : la norme DVB-S2. Un émetteur-récepteur entièrement numérique a été conçu en logiciel. La norme DVB-S2 est présentée d'un point de vue applicatif (émetteur et récepteur) et est ensuite évaluée sur une cible CPU spécifique.

#### Principaux résultats

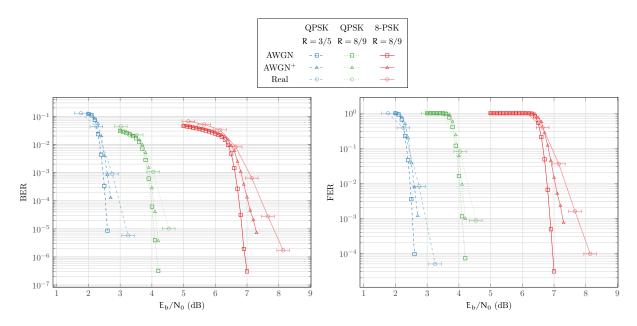

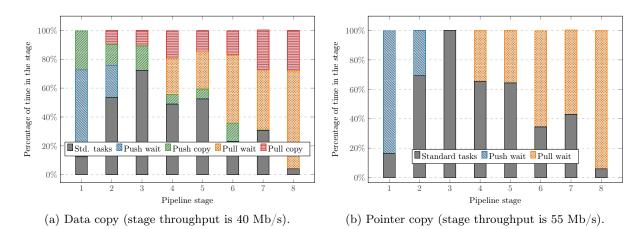

Les principaux composants de l'eDSL ont été conçus pour répondre aux besoins de la SDR en termes 1) d'expressivité avec des séquences, des tâches et des boucles ; 2) de performance avec la technique de duplication de séquences et la stratégie de pipeline. Nous avons évalué l'eDSL proposé dans un contexte applicatif : l'implémentation logicielle de la norme DVB-S2. Les résultats démontrent l'efficacité de l'eDSL d'AFF3CT. En effet, la solution proposée répond aux contraintes de temps réel des satellites (30  $\sim$  50 Mb/s). Ceci est la conséquence de deux facteurs principaux : 1) les optimisations au niveau des tâches, par exemple un décodeur LDPC rapide a été utilisé ; 2) l'eDSL a un très faible surcoût à l'utilisation. Cela est notamment possible grâce à une implémentation efficace de la technique du pipeline.

# Contents

| A                         | ckno   | wledgments in French                      |  |       | 1     |

|---------------------------|--------|-------------------------------------------|--|-------|-------|

| A                         | bstra  | acts                                      |  |       | ii    |

| E                         | xtend  | ded Abstract in French                    |  |       | iv    |

| Li                        | ist of | Figures                                   |  |       | xiv   |

| Li                        | ist of | Tables                                    |  |       | xvi   |

| Li                        | ist of | Algorithms and Source Codes               |  |       | xvii  |

| $\mathbf{L}_{\mathbf{i}}$ | ist of | Acronyms                                  |  | 3     | cviii |

| Ir                        | atrod  | uction                                    |  |       | 1     |

| 1                         | Cor    | ntext and Objectives                      |  |       | 5     |

|                           | 1.1    | Digital Communication Systems             |  |       | 6     |

|                           | 1.2    | Channel Model                             |  |       | 7     |

|                           | 1.3    | Channel Codes                             |  |       | 8     |

|                           |        | 1.3.1 Prerequisites                       |  |       | 9     |

|                           |        | 1.3.2 Low-density Parity-check Codes      |  |       | 9     |

|                           |        | 1.3.3 Polar Codes                         |  |       | 12    |

|                           |        | 1.3.4 Turbo Codes                         |  |       | 17    |

|                           | 1.4    | Applicative Contexts                      |  |       | 22    |

|                           |        | 1.4.1 Functional Simulation               |  |       | 22    |

|                           |        | 1.4.2 Software-defined Radio              |  |       | 25    |

|                           |        | 1.4.3 Sparse Code Multiple Access         |  |       | 26    |

|                           | 1.5    | Problematics                              |  | <br>• | 29    |

| 2                         | Opt    | imization Strategies                      |  |       | 31    |

|                           | 2.1    | MIPP: A C++ Wrapper for SIMD Instructions |  |       | 32    |

|                           |        | 2.1.1 Low Level Interface                 |  |       | 32    |

|                           |        | 2.1.2 Medium Level Interface              |  |       | 33    |

|                           |        | 2.1.3 Software Implementation Details     |  |       | 34    |

|                           |        | 2.1.4 Related Works                       |  |       | 35    |

|                           | 2.2    | Vectorization Strategies                  |  |       | 39    |

|                           |        | 2.2.1 Intra-frame SIMD Strategy           |  |       | 39    |

|                           |        | 2.2.2 Inter-frame SIMD Strategy           |  |       | 40    |

|                           |        | 2.2.3 Intra-/inter-frame SIMD Strategy    |  |       | 41    |

|                           | 2.3    | Efficient Functional Simulations          |  |       | 41    |

|                           |        | 2.3.1 Box-Muller Transform                |  |       | 42    |

|                           |        | 2.3.2 Quantizer                           |  |       | 43    |

|   | 2.4   | LDPC Decoders                                                      | 45           |

|---|-------|--------------------------------------------------------------------|--------------|

|   |       | 2.4.1 Generic Belief Propagation Implementation                    | 45           |

|   |       | 2.4.2 Specialized Belief Propagation Implementation                | 47           |

|   | 2.5   | Polar Decoders                                                     | 47           |

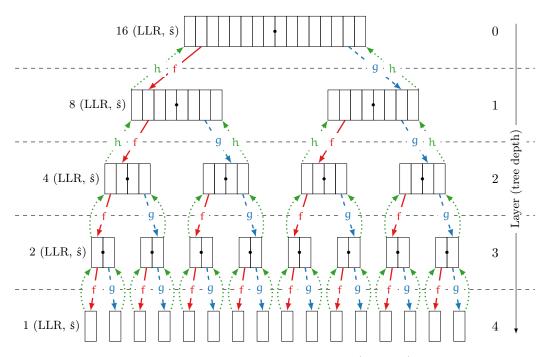

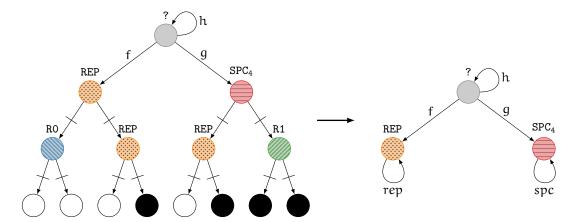

|   |       | 2.5.1 Tree Pruning Strategy                                        | 48           |

|   |       | 2.5.2 Polar Application Programming Interface                      | 51           |

|   |       | 2.5.3 Successive Cancellation Decoders                             | 52           |

|   |       | 2.5.4 Successive Cancellation List Decoders                        | 56           |

|   | 2.6   | Turbo Decoders                                                     | 59           |

|   |       | 2.6.1 Inter-frame Parallelism on Multi-core CPUs                   | 60           |

|   |       | 2.6.2 Software Implementation of the Turbo Decoder                 | 61           |

|   | 2.7   | SCMA Demodulators                                                  | 63           |

|   |       | 2.7.1 Flattening Matrices to Reduce Cache Misses and Branch Misses | 63           |

|   |       | 2.7.2 Adapting the Algorithms to Improve Data-level Parallelism    | 63           |

|   | 2.8   | Conclusion                                                         | 67           |

| 0 | A 101 |                                                                    | 0.0          |

| 3 | 3.1   | F3CT: A Fast Forward Error Correction Toolbox  Prerequisites       | <b>69</b> 70 |

|   | 0.1   | 3.1.1 High Performance Implementations                             | 70           |

|   |       | 3.1.2 Support for Algorithmic Heterogeneity                        | 70           |

|   |       | 3.1.3 Portability                                                  | 71           |

|   |       | 3.1.4 Reproducibility                                              | 71           |

|   | 3.2   | Related Works                                                      | 71           |

|   | 3.3   | Library of Digital Communication Algorithms                        | 72           |

|   | ა.ა   | 3.3.1 Software Architecture                                        | 72           |

|   |       |                                                                    | 74           |

|   |       | 1                                                                  | 76           |

|   |       |                                                                    |              |

|   | 2.4   |                                                                    | 77           |

|   | 3.4   | Simulation of Digital Communication Algorithms                     | 79           |

|   |       | 3.4.1 A Simulator Application on Top of the Library                | 79           |

|   |       | 3.4.2 In-depth Parameter Exploration                               | 80           |

|   |       | / 1                                                                | 83           |

|   | 2.5   | 3.4.4 Continuous Integration and Continuous Delivery               | 84           |

|   | 3.5   | Impact and Community                                               | 84           |

|   | 3.6   | Conclusion                                                         | 85           |

| 4 | Per   | formance Evaluations and Comparisons                               | 86           |

|   | 4.1   | LDPC Decoders                                                      | 87           |

|   |       | 4.1.1 Experimentation Platforms                                    | 87           |

|   |       | 4.1.2 Throughput and Latency Performance on Multi-core CPUs        | 87           |

|   |       | 4.1.3 Comparison with State-of-the-art BP Decoders                 | 89           |

|   | 4.2   | Polar Decoders                                                     | 90           |

|   |       | 4.2.1 Successive Cancellation Decoders                             | 90           |

|   |       | 4.2.2 Successive Cancellation List Decoders                        | 97           |

|   | 4.3   | Turbo Decoders                                                     | 99           |

|   |       | 4.3.1 Experimentation Platforms                                    | 100          |

|   |       | 4.3.2 Throughput Performance on Multi-core CPUs                    | 100          |

|   |       | 4.3.3 Energy Efficiency on a Multi-core CPU                        | 101          |

|   |       | 4.3.4 Comparison with State-of-the-art Turbo Decoders              | 101          |

|    | 4.4   | FEC Software Decoders Hall of Fame                                 | 102 |

|----|-------|--------------------------------------------------------------------|-----|

|    | 4.5   | SCMA Demodulators                                                  | 107 |

|    |       | 4.5.1 Experimentation Platforms                                    | 107 |

|    |       | 4.5.2 Throughput, Latency and Energy Efficiency on Multi-core CPUs | 107 |

|    | 4.6   | Analysis of the Simulator Performance                              | 109 |

|    |       | 4.6.1 Experimentation Platforms                                    | 110 |

|    |       | 4.6.2 Mono-threaded Performances                                   | 110 |

|    |       | 4.6.3 Multi-threaded and Multi-node Performances                   | 111 |

|    | 4.7   | Conclusion                                                         | 113 |

| 5  | Eml   | bedded Domain Specific Language for the Software-defined Radio     | 115 |

|    | 5.1   | Related Works                                                      | 116 |

|    |       | 5.1.1 Dataflow Model                                               | 116 |

|    |       | 5.1.2 Dedicated Languages                                          | 116 |

|    |       | 5.1.3 GNU Radio                                                    | 117 |

|    | 5.2   | Description of the Proposed Embedded Domain Specific Language      | 117 |

|    |       | 5.2.1 Elementary Components                                        | 117 |

|    |       | 5.2.2 Parallel Components                                          | 120 |

|    | 5.3   | Implementation Strategies                                          | 121 |

|    |       | 5.3.1 Implicit Rules                                               | 121 |

|    |       | 5.3.2 Sequence Duplication                                         | 121 |

|    |       | 5.3.3 Processes                                                    | 121 |

|    |       | 5.3.4 Pipeline                                                     | 122 |

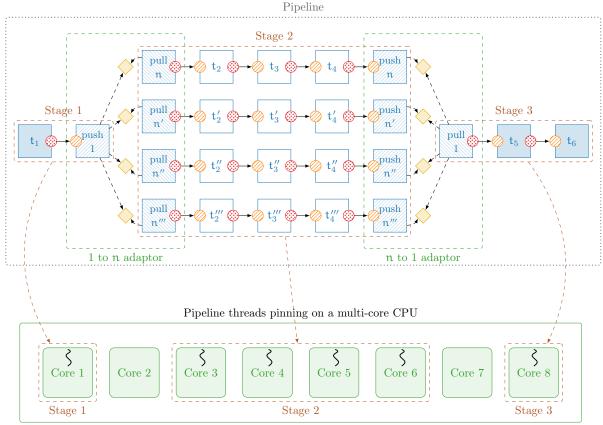

|    | 5.4   | Application on the DVB-S2 Standard                                 | 125 |

|    |       | 5.4.1 Transmitter Software Implementation                          | 125 |

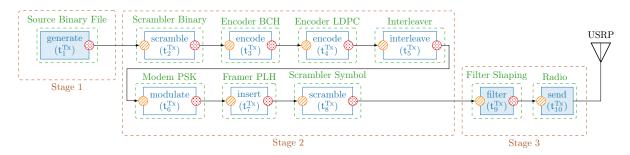

|    |       | 1                                                                  | 126 |

|    |       | 5.4.3 Evaluation                                                   | 128 |

|    |       | 5.4.4 Related Works                                                | 132 |

|    | 5.5   | Conclusion                                                         | 132 |

| Co | onclu | sions and Perspectives                                             | 134 |

| Bi | bliog | graphy                                                             | 138 |

| Pe | rson  | al Publications                                                    | 150 |

# List of Figures

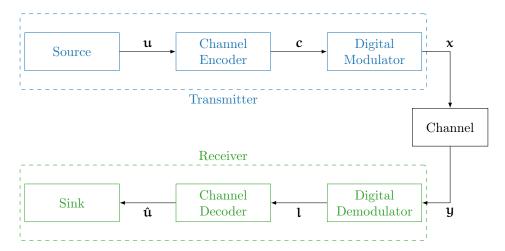

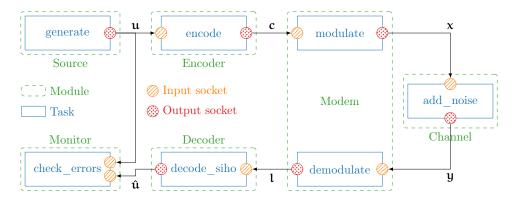

| 1.1  | Digital communication chain                                                              | 6  |

|------|------------------------------------------------------------------------------------------|----|

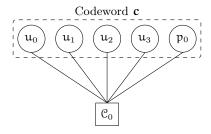

| 1.2  | Representation of the $C_0$ parity-check constraint on a Tanner graph                    | 10 |

| 1.3  | Parity-check constraints of an LDPC code on a Tanner graph                               | 10 |

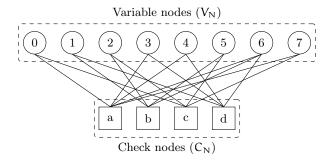

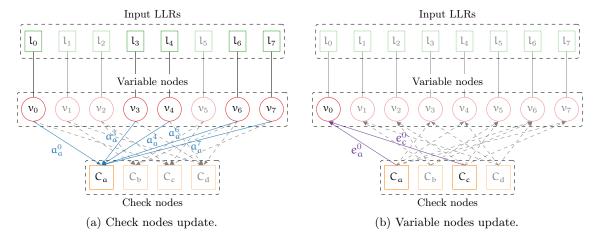

| 1.4  | Illustration of the belief propagation algorithm on a Tanner graph                       | 11 |

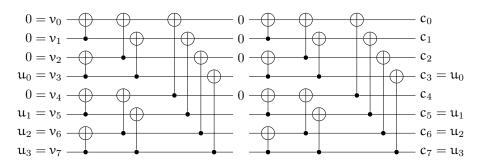

| 1.5  | Polar encoding process for $N \in \{2,4,8\}$ and $R = 1/2$                               | 13 |

| 1.6  | Systematic polar encoder for $N=8$ and $R=1/2.$                                          | 13 |

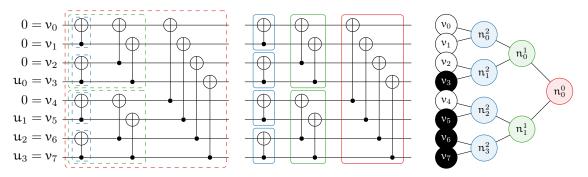

| 1.7  | Tree representation of a polar encoder for $N=8$ and $R=1/2.$                            | 14 |

| 1.8  | Full SC decoding tree $(N = 16)$                                                         | 14 |

| 1.9  | Example of polar tree pruning on a small binary tree $(N = 8)$                           | 17 |

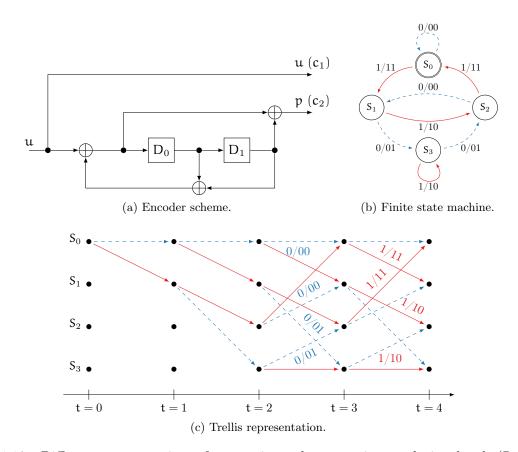

| 1.10 | Different representations of a recursive and systematic convolutional code $(R = 1/2)$ . | 18 |

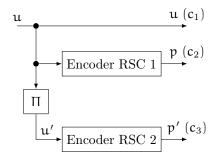

| 1.11 | Turbo code $(R = 1/3)$ with two convolutional sub-encoders and a $\Pi$ interleaver       | 19 |

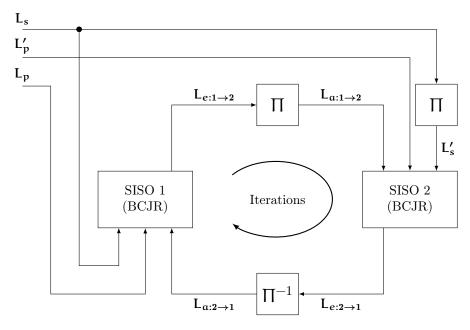

| 1.12 | Information exchanges in turbo decoding process                                          | 19 |

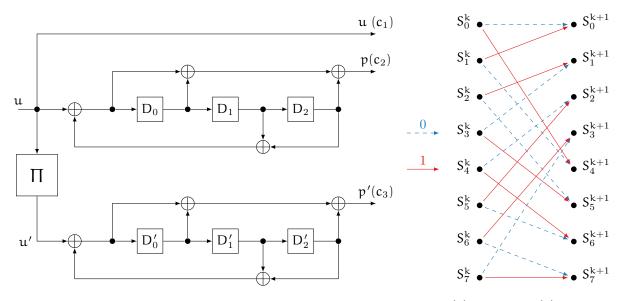

| 1.13 | Turbo LTE encoder and its associated 8-state trellis                                     | 20 |

| 1.14 | Description of a digital communication system simulation                                 | 23 |

| 1.15 | BER and FER simulation results on various code families                                  | 24 |

| 1.16 | Base stations evolution in mobile networks                                               | 25 |

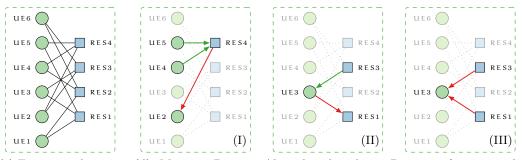

| 1.17 | SCMA system model, encoding and decoding schemes                                         | 27 |

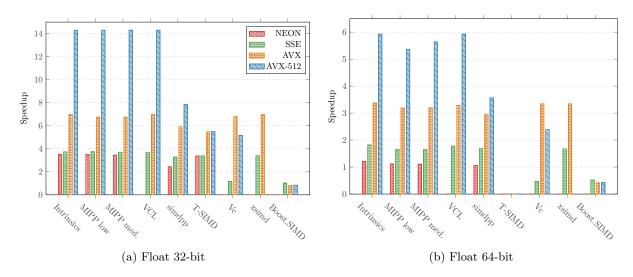

| 2.1  | Speedups over the Mandelbrot naive auto-vectorized implementation                        | 38 |

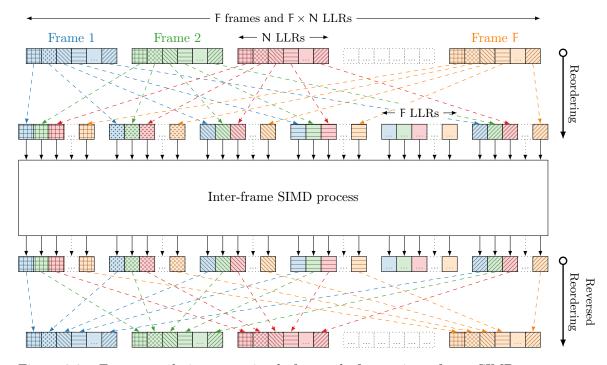

| 2.2  | Frame reordering operation before and after an inter-frame SIMD process                  | 40 |

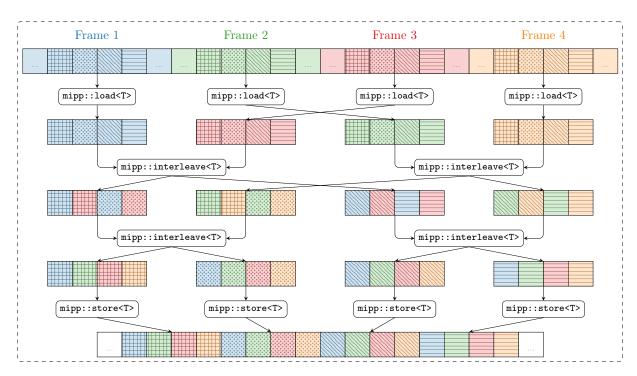

| 2.3  | MIPP implementation of the SIMD frame reordering process for $p_{SIMD}=4$                | 41 |

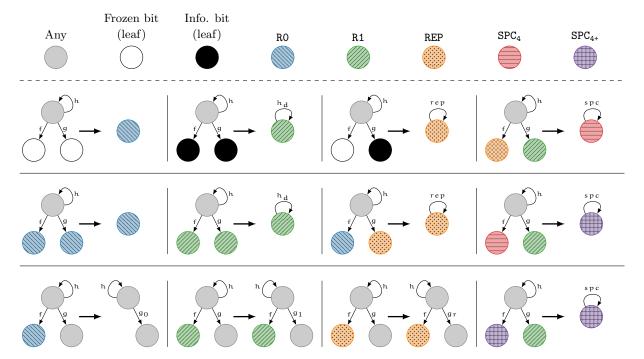

| 2.4  | Polar sub-tree rewriting rules for processing specialization                             | 48 |

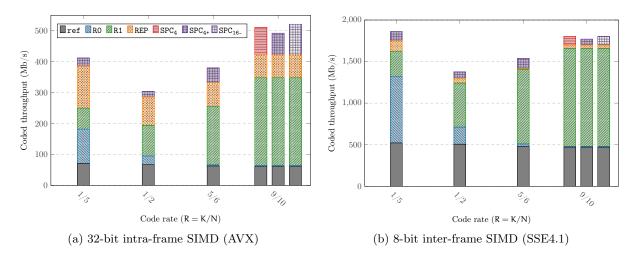

| 2.5  | Throughput of the SSC decoder depending on the different optimizations                   | 49 |

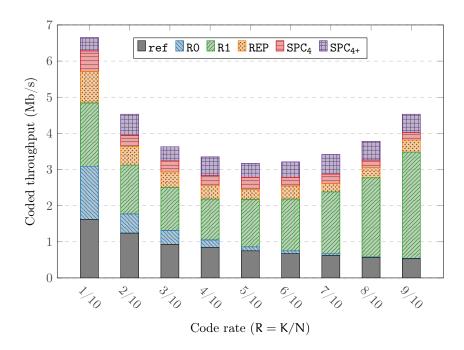

| 2.6  | Impact of the specialized nodes on the SSCL coded throughput                             | 50 |

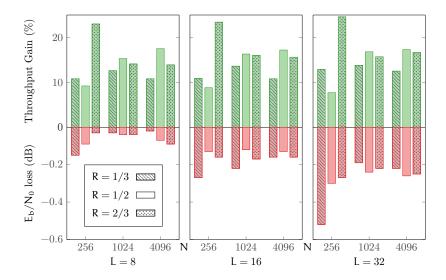

| 2.7  | Effects of the SPC <sub>4+</sub> nodes on the CA-SSCL decoder @ $10^{-5}$ FER            | 51 |

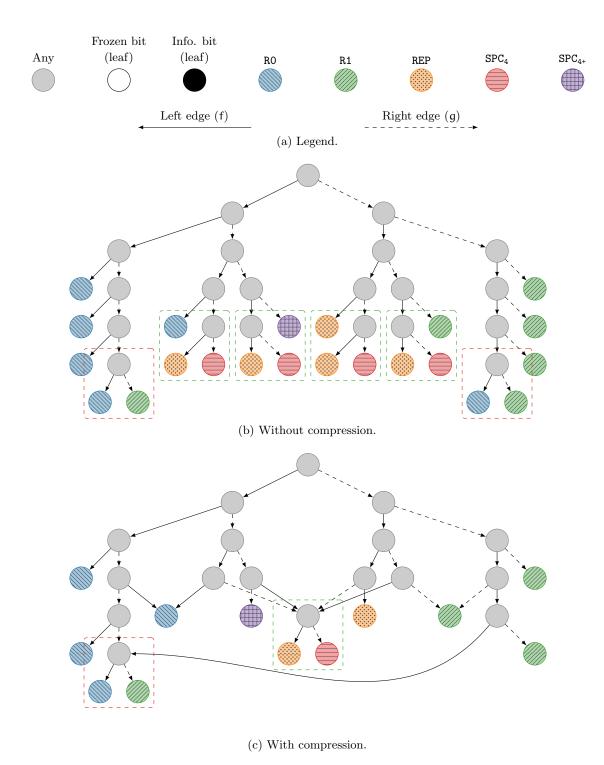

| 2.8  | Pruned polar decoding tree representation without and with compression                   | 55 |

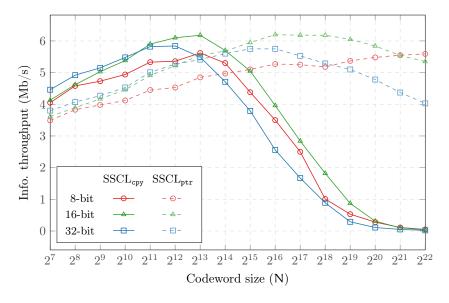

| 2.9  |                                                                                          | 58 |

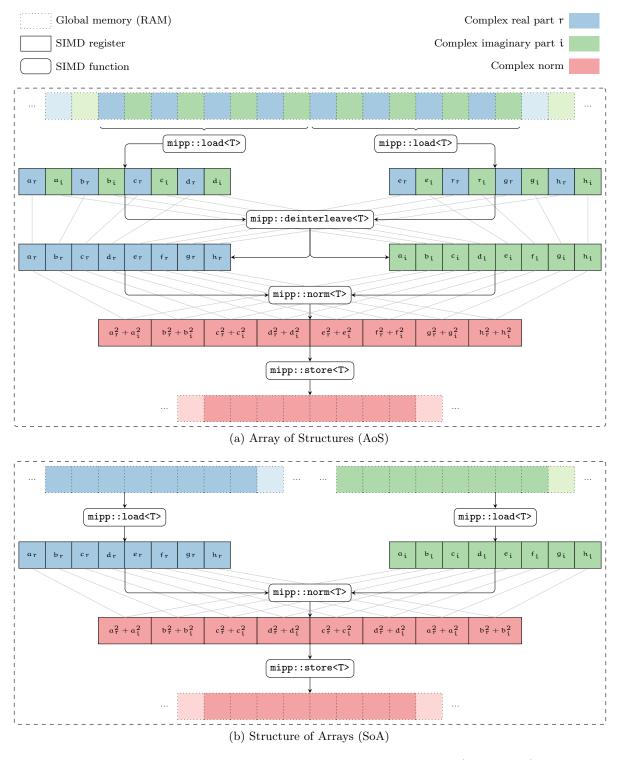

| 2.10 | MPA vectorized complex norm computations                                                 | 64 |

|      | •                                                                                        | 65 |

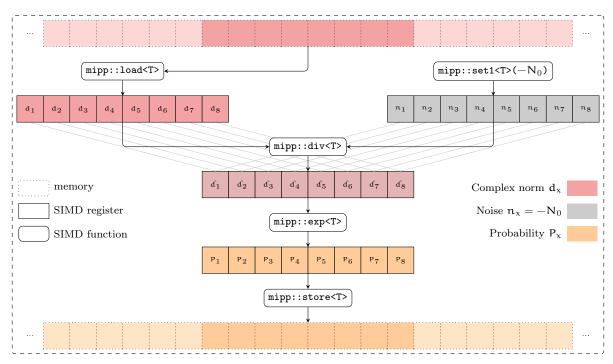

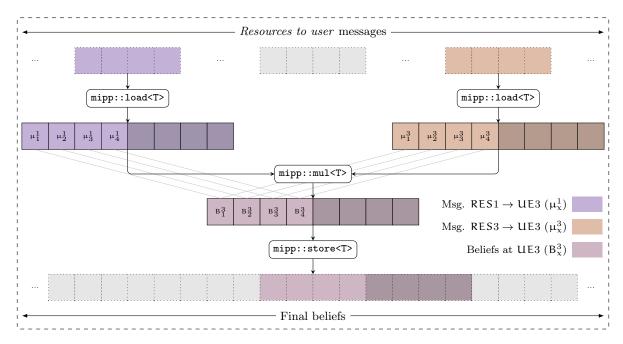

| 2.12 | MPA vectorized computations of final beliefs                                             | 66 |

| 3.1  | Q V                                                                                      | 74 |

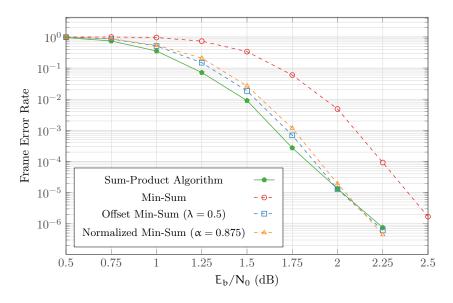

| 3.2  | Decoding performance of the LDPC BP algorithm depending on the update rules.             | 80 |

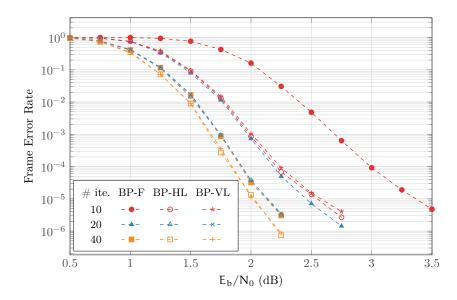

| 3.3  | Decoding performance of the LDPC BP algorithm depending on the scheduling                | 81 |

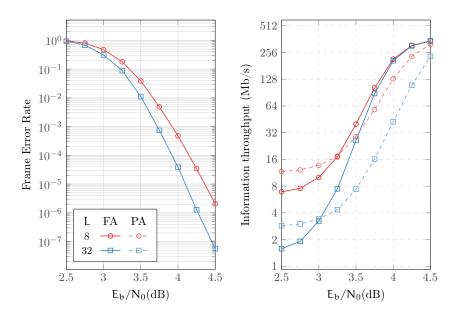

| 3.4  | FER and throughput of the polar fully and partially adaptive SSCL decoders               | 82 |

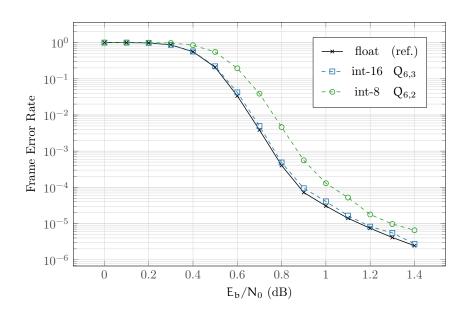

| 3.5  | FER of the turbo decoder for $K=6144$ (6 iterations) and $R=1/3.\ldots$                  | 82 |

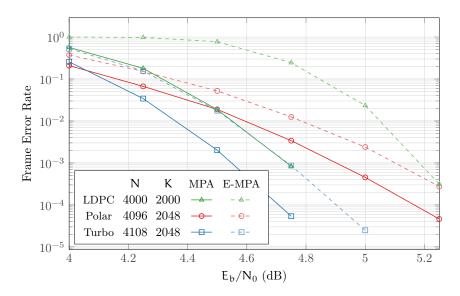

| 3.6  | FER evaluation of the SCMA MPA and E-MPA demodulators                                    | 83 |

| 3.7  | AFF3CT continuous integration and continuous delivery pipeline                           | 84 |

| 4.1  | LDPC decoder throughput and latency depending on the number of cores (WiMAX).            | 88 |

| 4.2  | LDPC decoder throughput and latency depending on the number of cores (DVB-S2).           | 88 |

| 4.3  | SC variation of the <i>energy-per-bit</i> for different frame sizes and implementations. | 92 |

| 4.4  | SC variation of the <i>energy-per-bit</i> depending on the cluster frequency      | 93  |

|------|-----------------------------------------------------------------------------------|-----|

| 4.5  | SC evolution of the <i>energy-per-bit</i> depending on the code rate              | 93  |

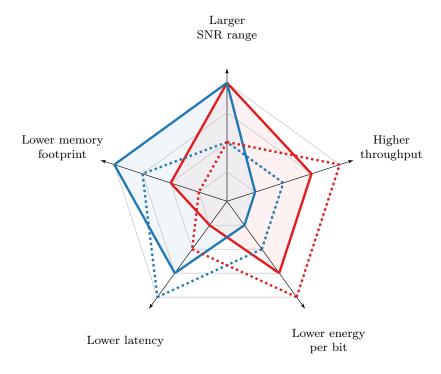

| 4.6  | SC ranking of intra-/inter-frame SIMD approaches along 5 metrics                  | 94  |

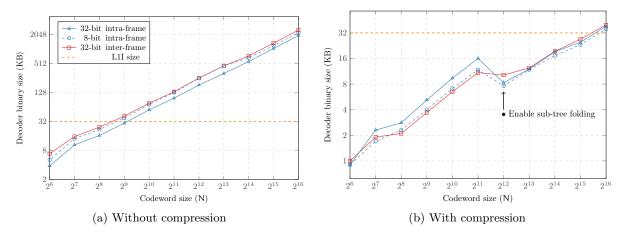

| 4.7  | Generated SC decoder binary sizes depending on the frame size $(R=1/2)$           | 95  |

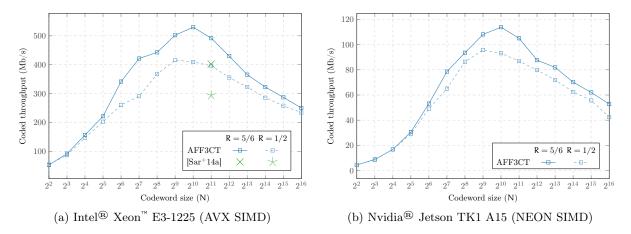

| 4.8  | SC performance comparison between two code rates (intra-frame vectorization)      | 96  |

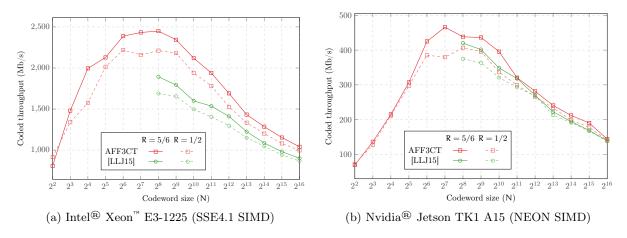

| 4.9  | SC performance comparison between several code rates (inter-frame vectorization). | 97  |

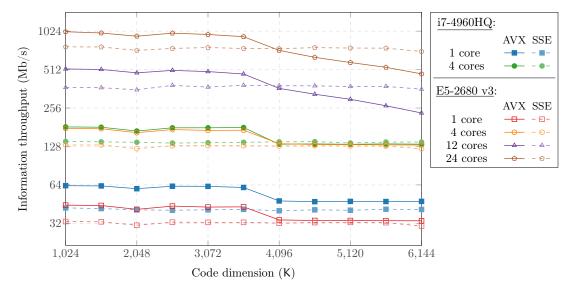

| 4.10 | Information throughput of the turbo decoder depending on $K$                      | 100 |

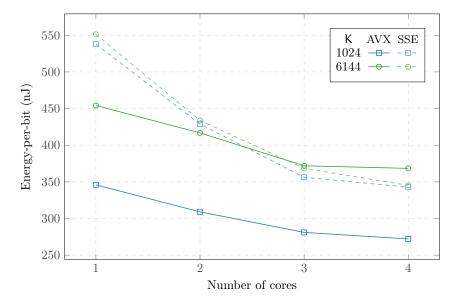

| 4.11 | Turbo decoder <i>energy-per-bit</i> depending on the number of cores              | 101 |

| 4.12 | AFF3CT simulator chain                                                            | 109 |

| 4.13 | AFF3CT simulation results of a (2048,1723) Polar code, FA-SSCL decoder $L=32$ .   | 112 |

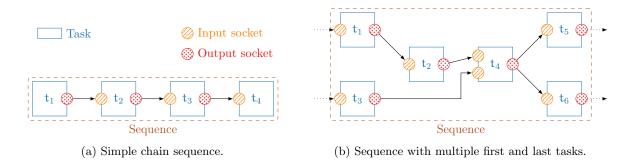

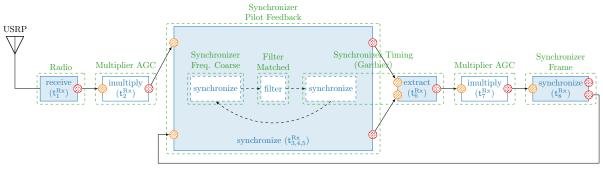

| 5.1  | Example of sequences                                                              | 118 |

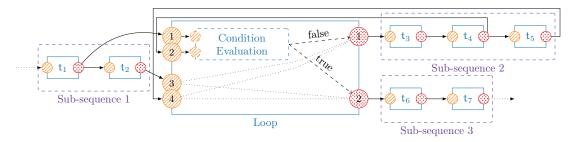

| 5.2  | Example of a sequence of tasks with a loop                                        | 119 |

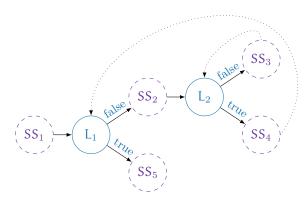

| 5.3  | Nested loops                                                                      | 119 |

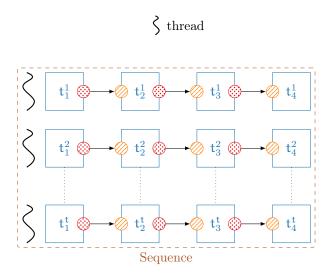

| 5.4  | Sequence duplication for multi-threaded execution                                 | 120 |

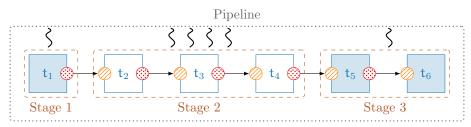

| 5.5  | Example of a pipeline description and the associate transformation with adaptors. | 122 |

| 5.6  | DVB-S2 transmitter software implementation                                        | 125 |

| 5.7  | DVB-S2 receiver software implementation                                           | 126 |

| 5.8  | DVB-S2 BER and FER decoding performance                                           | 128 |

| 5.9  | Comparison of the two pipeline implementations in the receiver                    | 130 |

# List of Tables

| 1.1                      | Elementary operations in $Gr_2$ (logical exclusive or and logical ana)                                                                                                                                  | 9                    |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2.1<br>2.2<br>2.3<br>2.4 | Comparison of various SIMD wrappers: General Information and Features Comparison of various SIMD wrappers: Supported ISA and Data Type Specifications of the target processors for the MIPP experiments | 36<br>36<br>37<br>43 |

| 2.5<br>2.6               | Quantizer throughputs and speedups of the MIPP implementation Polar decoders memory complexity                                                                                                          | 44<br>59             |

| 3.1<br>3.2               | C/C++ open source channel coding simulators/libraries                                                                                                                                                   | 72<br>77             |

| 3.3                      | List of the modulations/demodulations (modems) supported in AFF3CT                                                                                                                                      | 78                   |

| 3.4                      | List of the channel models supported in AFF3CT                                                                                                                                                          | 78                   |

| 4.1                      | Specifications of the target processors for the LPDC decoder experiments                                                                                                                                | 87                   |

| 4.2                      | Comparison of the proposed BP decoder with the state-of-art                                                                                                                                             | 89                   |

| 4.3<br>4.4               | Specification of the x86 platforms for the polar decoders experiments                                                                                                                                   | 90<br>90             |

| 4.4                      | Throughput, latency and <i>energy-per-bit</i> of the dynamic SC decoders                                                                                                                                | 91                   |

| 4.6                      | Binary code size (in KB) of the generated SC decoders                                                                                                                                                   | 95                   |

| 4.7                      | Comparison of 8-bit fixed-point dynamic SC decoders (intra-frame SIMD)                                                                                                                                  | 96                   |

| 4.8                      | Comparing SC generated software decoder with the state-of-art (intra-frame SIMD).                                                                                                                       | 96                   |

| 4.9                      | Throughput comparisons between floating-point and fixed-point A-SSCL decoders.                                                                                                                          | 98                   |

| 4.10                     | Throughput and latency comparisons with state-of-the-art SCL decoders                                                                                                                                   | 99                   |

| 4.11                     |                                                                                                                                                                                                         | 100                  |

|                          |                                                                                                                                                                                                         | 101                  |

|                          |                                                                                                                                                                                                         | 103                  |

|                          |                                                                                                                                                                                                         | 104                  |

|                          |                                                                                                                                                                                                         | 105<br>107           |

|                          |                                                                                                                                                                                                         | 107<br>108           |

|                          | 9 1 7 07 1                                                                                                                                                                                              | 110<br>110           |

|                          | Average throughput and latency performance per simulated task (single-threaded). 1                                                                                                                      |                      |

|                          | THE                                                                                                                                                                 | 112                  |

| 5.1                      |                                                                                                                                                                                                         | 125                  |

| 5.2                      | 1 0 1                                                                                                                                                                                                   | 129                  |

| 5.3                      | Throughput performance depending of the selected DVB-S2 configuration 1                                                                                                                                 | 131                  |

# List of Algorithms and Source Codes

| 1.1  | SCL decoding algorithm                                                                      | 16 |

|------|---------------------------------------------------------------------------------------------|----|

| 1.2  | Pseudo-code of the BCJR decoding algorithm                                                  | 20 |

| 2.1  | MIPP medium level interface encapsulation                                                   | 33 |

| 2.2  | Box-Muller Transform SIMD kernel with MIPP                                                  | 42 |

| 2.3  | Sequential implementation of the quantizer                                                  | 43 |

| 2.4  | SIMD implementation of the quantizer with MIPP                                              | 44 |

| 2.5  | LDPC BP-HL scheduling implementation                                                        | 46 |

| 2.6  | LDPC MS update rules implementation                                                         | 46 |

| 2.7  | Example of a $C++$ SIMD polar API $(f, g \text{ and } h \text{ functions are implemented})$ | 52 |

| 2.8  | Generated polar SC decoder source code                                                      | 54 |

| 2.1  | Loop fusion BCJR implementation                                                             | 60 |

| 2.9  | Generic implementation of the BCJR $\alpha^k$ computations                                  | 62 |

| 2.10 | Unrolled implementation of the BCJR $\alpha^k$ computations                                 | 62 |

| 3.1  | Example of modules allocation with the AFF3CT library                                       | 75 |

| 3.2  | Example of sockets binding with the AFF3CT library                                          | 75 |

| 3.3  | ı                                                                                           | 75 |

| 3.4  | Example of the AFF3CT MATLAB® wrapper                                                       | 76 |

| 3.5  | Example of an AFF3CT simulator command                                                      | 79 |

| 3.6  | Example of an AFF3CT simulator output                                                       | 79 |

| 5.1  | AFF3CT C++ eDSL source code of the pipeline described in Figure 5.5 1                       | 23 |

# List of Acronyms

Third Generation of Mobile Phone Networks

Fourth Generation of Mobile Phone Networks

Fifth Generation of Mobile Phone Networks

A-SCL Adaptive SCL

A-SSCL Adaptive SSCL

AFF3CT A Fast Forward Error Correction Toolbox

AGC Automatic Gain Control

AMS Approximate Min-star

AoS Array of Structures

API Application Programming Interface

AR Augmented Reality

ASIC Application-Specific Integrated Circuits

AVX Advanced Vector Extensions

AVX-512 Advanced Vector Extensions (512-bit)

AWGN Additive White Gaussian Noise

BCJR Bahl, Cocke, Jelinek & Raviv Decoding Algorithm

BB Base Band

BCH Bose, Ray-Chaudhuri & Hocquenghem Channel Codes Family

BE Bit Error

BEC Binary Erasure Channel

BER Bit Error Rate

BP Belief Propagation

BP-F BP with Flooding Scheduling

BP-HL BP with Horizontal Layered Scheduling

BP-VL BP with Vertical Layered Scheduling

BPSK Binary Phase-shift Keying

BSC Binary Symmetric Channel

C-RAN Cloud Radio Access Network

CA-SCL CRC-aided SCL CRC-aided SSCL

CCSDS Consultative Committee for Space Data Systems

CD Continuous Delivery

CI Continuous Integration

CPM Continuous Phase Modulation

CPU Central Process Unit

CRC Cyclic Redundancy Check

DSL Domain Specific Language

DSP Digital Signal Processor

DVB-RCS Digital Video Broadcasting - Return Channel via Satellite

DVB-S2 Digital Video Broadcasting for Satellite (Second Generation)

E-MPA Estimated-MPA

ECC Error Correcting Code

eDSL Embedded Domain Specific Language

EML-MAP

FA-SCL

FA-SSCL

Enhanced ML-MAP

Fully Adaptive SCL

Fully Adaptive SSCL

FE Frame Error

FEC Forward Error Correction

FER Frame Error Rate

FPGA Field Programmable Gate Arrays

GA Gaussian Approximation

GCC GNU C Compiler GNU GNU's Not UNIX

GPP General Purpose Processor

GPU Graphical Process Unit

HIHO Hard Input Hard Output

HoF Hall of Fame

HPC High Performance Computing

ICPC Intel<sup>®</sup> C++ Compiler

IEEE Institute of Electrical and Electronics Engineers

Internet of Mission Critical Things

Internet of Things

ISA Instruction Set Architecture

KNC Knights Corner

KNCI Knights Corner Instructions

KNL Knights Landing

LDPC Low Density Parity Check Channel Codes Family

LLC Last Level Cache

LLR Log Likelihood Ratio

LTE Long Term Evolution

MAP Maximum a Posteriori

MIPP My Intrinsics Plus Plus

ML Maximum Likelihood

ML-MAP Max-log-MAP

MODCOD Modulation and Coding

MPA Message Passing Algorithm

MPI Message Passing Interface

MS Min-sum

MSVC Microsoft® Visual Compiler

MT19937 Mersenne Twister 19937

NMS Normalized Min-sum

NOMA Non-orthogonal Multiple Access

NUMA Non Uniform Memory Access

OFDM Orthogonal Frequency-division Multiplexing

OMS Offset Min-sum

OOK On-off Keying

OOP Object-oriented Programming

P-EDGE Polar ECC Decoder Generation Environment

PA-SCL Partially Adaptive SCL

PA-SSCL Partially Adaptive SSCL

PAM Pulse Amplitude Modulation

PLH Pay Load Headers

PRNG Pseudo Random Number Generator

PSK Phase-shift Keying

QAM Quadrature Amplitude Modulation QPSK Quadrature Phase-shift Keying

$egin{array}{ll} {

m R0} & {

m \bf Rate} \ {

m \bf 0} \\ {

m \bf R1} & {

m \bf Rate} \ {

m \bf 1} \\ \end{array}$

RAM Random Access Memory

REP Repetition

RF Radio Frequency

RS Reed & Solomon Channel Codes Family

RSC Recursive Systemactic Convolutionnal

SCSuccessive CancellationSCLSuccessive Cancellation ListSCMASparse Code Multiple Access

SDR Software-defined Radio

SIMD Single Instruction Multiple Data

SISO Soft Input Soft Output

SMT Simultaneous Multi-threading

SNR Signal-to-noise Ratio

SoA Structure of Arrays

SoC System on a Chip

SPA Sum-product Algorithm

SPC Single Parity Check

SPMD Single Program Multiple Data

SSC Simplified SC SSCL Simplified SCL

SSE Streaming SIMD Extensions

TDP Thermal Design Power

TNDC Throughput under Normalized Decoding Cost

TPC Turbo Product Codes

TTA Transport Triggered Architecture

USRP Universal Software Radio Peripheral

VLIW Very Long Instruction Word

Wi-Fi Wireless Fidelity

WiMAX Worldwide Interoperability for Microwave Access

WRAN Wireless Regional Area Networks

XOR Exclusive Or

## Introduction

#### **Digital Communications**

Man has sought to communicate from time immemorial. Since then, man has always been seeking for more efficient ways to extend his communication possibilities. Nowadays, with the advent of the Internet, the digital communications represent the last technology advances to communicate world-wide. For instance, digital communications enable both live video transmission and the use of a messaging system. With the growing number of users and needs, the digital communication systems are the subject of an important area of research. New digital communication systems have to be able to match high throughput and low latency constraints as well as acceptable energy consumption levels.

Traditionally, digital communication transmitters and receivers are implemented in hardware, on dedicated chips. The required signal processing algorithms are often very specific and repetitive. Thus, they are good candidates for specialized architectures. However, with the growing number of use cases and telecommunication standards, these algorithms are evolving and are becoming more and more heterogeneous. In this context, it becomes interesting to consider software implementations on generic architectures. This type of programmable architectures is available in computers and is commonly referred as the Central Process Unit (CPU). The CPUs are General Purpose Processors (GPP) that can adapt to various types of algorithms.

#### Computer Architecture

Improving the computational and the energy efficiency of these processors is one of the main concern in computer science. As they are largely adopted for many use cases, the CPUs take advantage of the best manufacturing processes. Thanks to their pipelined architecture they are able to reach very high processing frequencies ranging from 1 to 4 GHz. They also come with dedicated memory caches that enable efficient spatial and temporal reuse of data. Nowadays, the computational efficiency of the CPUs relies on two main parallel techniques. The first one is the multi-core architecture: it consists in duplicating the hardware of the "CPU" in multiple instances called cores. These cores are mostly independent from each other. They are packaged together in the same chip (called the CPU) and generally they share a fast memory: the last level cache. The second parallel technique is the vectorized instructions. These types of instructions are available in each core and are able to perform the same operation on a chunk of data. This is also known as the Single Instruction Multiple Data (SIMD) architectural model.

From an energy point of view, it is clear that CPUs are not directly competitive compared to dedicated architectures. Their large number of instructions enables efficient implementations of many algorithms but this is also a limitation when targeting specific applications. Many transistors are unused and consume a non-negligible amount of energy. On the other hand, the main strength of the GPP architectures comes from their abilities to be used programmatically

with high level languages. Consequently, the time required to implement new algorithms is much shorter on GPPs than on dedicated hardwares. However, even with reduced implementation time, it is still challenging to design algorithms that take effectively advantage of the CPUs parallelism levels.

#### Hardware Abstraction and Software

The ever growing complexity of processors motivates new hardware description level abstractions. Even if it is still possible to write assembly codes, one should agree that this is not adapted to real-size applications. Moreover, in general the designers of an application are not familiar with the specificities of the CPU architectures. Thus, it becomes important to propose new models (or abstractions) on top of the hardware. It enables the efficient use of processors to the largest number of people. To this purpose, dedicated compilers, languages and libraries are an important research area in computer science.

In the design of digital communication systems, it is now common to rely on software implementations for the evaluation and the validation of signal processing algorithms. These evaluation and validation steps consist in the simulation of the whole communication system. Generally these type of simulations are implemented by signal processing experts with high level programing languages like MATLAB® or Python. However, with the growing complexity of the digital communication systems, these simulations are becoming more and more compute intensive. Using high level programming languages is a limiting factor because it can lead to large restitution times (from days to weeks). Thus, high performance implementations based on lower level programming languages are considered.

Moreover, software implementations are also considered for real-time uses. Their flexibility and reduced time to market are becoming more and more attractive. Indeed, dedicated hardware solutions require specific skills and are achieved by electronics specialists. In general, signal processing experts do not focus on implementing efficient software or hardware solutions. The dialog between the two communities is not always simple as they have different concerns.

The purpose of this thesis is to ease the overall design of digital communication systems, from the conception to the implementation. Dedicated tools and interfaces are proposed to help the signal processing experts to design fast software implementations. In general, this type of software implementations are a good start to better understand the algorithms hotspots. From this point, electronics specialists can improve proposed software solutions and, if necessary, design adapted hardware implementations.

### Contributions

In this thesis we propose to study the most time consuming algorithms of digital communication systems, to adapt and optimize them on General Purpose Processors (GPPs) like the CPUs. Most of the current digital communication standards require the implementation of such algorithms. The long simulation times and the real-world application requirements make it desirable to have portable, flexible, high throughput and low latency implementations. The proposed high performance implementations are shown to be competitive with the state-of-the-art ones. Contrary to the previous works, this thesis strives to extract generic methodologies and strategies common to the majority of the signal processing algorithms. The proposed implementations try to be as flexible as possible without sacrificing too much the performance.

The signal processing algorithms come with various characteristics. Thus, it is of interest to be able to manage this algorithmic heterogeneity. In this work, to enable code reuse, similarities are identified into this zoo of algorithms. The various implementations have been packaged, categorized and organized in one single software library, namely AFF3CT. These implementations cohabit together thanks to well-defined interfaces and an adapted software architecture based on the Object-Oriented Programming (OOP) paradigm.

Another important concern of this work is the ability to reproduce the scientific results. Indeed, all the proposed implementations are regrouped in AFF3CT which is an open-source software. Specific strategies have been operated to minimize the possible regressions based on the digital communication systems characteristics. These non-regression strategies are automated. They ensure that the source code remains stable even if many contributors are working together.

These contributions have been the topic of several scientific publications in both the computer science and the signal processing communities. They are listed at the end of the manuscript in the "Personal Publications" section. As a convention in the document, the numeric citations are contributions of this thesis while the alphabetic citations refer to other works in the literature.

#### **Dissertation Organization**

This dissertation is organized in five chapters. The first chapter describes the context and details the objectives. The next chapters present our contributions.

In Chapter 1, the digital communication systems are detailed. Then, the most time consuming part of these systems is presented, namely the channel decoders. After that, the applicative contexts of this thesis are defined. The two main ones are the functional simulation and the Software-Defined Radio (SDR). The functional simulation enables the evaluation and the validation of different digital communication systems while the SDR corresponds to the real-time execution of these systems in software. Finally, the main problematics are exposed.

In Chapter 2, new efficient implementations of the decoders are proposed. First, an overall portable methodology is detailed to meet the high throughput constraint required by both the simulations and the real-time systems. This methodology is based on the Single Instruction Multiple Data (SIMD) model implemented in most of the current CPUs. Depending on how the CPU SIMD instructions are used, it is possible to maximize the throughput or the latency of the implemented decoding algorithms. Then, specific optimized implementations are detailed for each decoding algorithm. These implementations focus on maximizing the flexibility, high throughput and low latency. Depending on the implementations, some compromises have to be made and some of these characteristics can be maximized unbeknownst to others.

In Chapter 3, AFF3CT, our toolbox dedicated to the forward error correction (FEC) algorithms is presented. AFF3CT is unique in the domain and it is composed by many algorithm implementations (including those presented in Chapter 2). AFF3CT is the software that enables the signal processing algorithms heterogeneity thanks to a robust software architecture based on well-defined and coherent interfaces. It enables reproducibility of the results as it is open-source and extensively tested. AFF3CT also contains a parallel functional simulator and enables extensive exploration/validation of existing or new algorithms on a large combination of parameters.

In Chapter 4, the efficient algorithm implementations proposed in Chapter 2 are evaluated and compared with the state-of-the-art. The FEC software decoders hall of fame is introduced to summarize and to compare the proposed contributions with previous works in the literature. Some metrics are defined for ease of comparison. These metrics focus on normalized throughput, proper use of hardware and energy efficiency. Finally, the AFF3CT simulator efficiency is demonstrated on various multi-core CPUs and on a multi-node cluster.

In Chapter 5, a new embedded Domain Specific Language (eDSL) for the SDR is presented. The AFF3CT software suite is enriched with new blocks dedicated to the efficient implementation of real-time digital communication systems on multi-core CPUs. These blocks enable automatic parallelism. As an example of use, a full physical layer of the DVB-S2 standard has been implemented. All the digital processing are performed with AFF3CT while the radio frequency communications is achieved with Universal Software Radio Peripherals (USRPs). The results match the satellite real-time constraints.

# 1 Context and Objectives