# Approaches, Strategies, and Implementations of Memory Safety Defenses in Critical and Constrained Embedded Systems

Cyril Bresch

### ► To cite this version:

Cyril Bresch. Approaches, Strategies, and Implementations of Memory Safety Defenses in Critical and Constrained Embedded Systems. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2020. English. NNT: 2020GRALT043. tel-03118575

## HAL Id: tel-03118575 https://theses.hal.science/tel-03118575v1

Submitted on 22 Jan 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES

Arrêtée ministériel : 25 mai 2016

Présentée par **Cyril BRESCH**

Thèse dirigée par **loannis Parissis**, Université Grenoble Alpes et codirigéee par **David Hély**, Maitre de Conférence, Université Grenoble Alpes

et Stéphanie Chollet, Maitre de Conférence, Université Grenoble Alpes

préparée au sein du Laboratoire de Conception et d'Intégration des Systèmes (LCIS)

dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Approches, Stratégies, et Implémentations de Protections Mémoire dans les Systèmes Embarqués Critiques et Contraints.

Approaches, Strategies, and Implementations of Memory Safety Defenses in Critical and Constrained Embedded Systems.

Thèse soutenue publiquement le **16 noctobre 2020**, devant le jury composé de:

### Monsieur AURELIEN FRANCILLON PROFESSEUR, EURECOM - SOPHIA-ANTIPOLIS, Rapporteur

Monsieur SEBASTIEN PILLEMENT PROFESSEUR, UNIVERSITE DE NANTES, Rapporteur

Madame MARIE-LAURE POTET PROFESSEUR, GRENOBLE-INP, Examinateur

Monsieur GIORGIO DI NATALE DIRECTEUR DE RECHERCHE, CNRS DELEGATION ALPES, Président

Monsieur ROMAN LYSECKY PROFESSEUR, UNIVERSITE D'ARIZONA, Invité

"To my family, and all my friends around the world, for all the love and support."

# Acknowledgements

The existence of this work would probably require the writing of a second manuscript to thank all the people who supported it. It is thanks to them, over a time span of three amazing years, that I could complete this work.

First of all, I would like to thank my thesis' jury: Mr. Giogio Di Natale, Mrs. Marie-Laure Potet, Mr. Aurélien Francillon, and Mr. Sébastien Pillement for willing to serve on my thesis committee. They carefully attended my defense, listened to my vision regarding my research, evaluated it, recognized it, and finally, awarded me with the degree of doctor. Their insightful comments, suggestions, and challenging questions have helped me make significant improvements to this thesis and beyond. We had memorable discussions and interesting debates during the defense that will contribute to continuing my education as a young researcher.

This thesis would not have been possible without the dedication of my thesis directors, David Hély and Ioannis Parissis, as well as my co-supervisor Stéphanie Chollet. I am delighted to have worked with them, they encouraged me to pursue my interests and provided me the freedom and guidance to explore my topic. Besides their scientific support, they have always been there for support and helpful advice. I particularly appreciated Stéphanie's rigor and her approach regarding my research. She taught me the skills of a professional researcher such as exposing a scientific problem and approaching it from different perspectives. I obviously can't forget David's openness, good mood, and support in all my ideas. He approved my desire to go to the United States and collaborate with other researchers. Besides, I will never forget our sparkling meetings, full of ideas and ambitions during these moments. Working with him has been inspiring.

I would also like to thank Roman Lysecky, professor at the University of Arizona in Tucson. He hosted me in his research team during my international exchange in the United States. He treated me as one of his Ph.D. students, and I am immensely grateful for his guidance and assistance during my stay in the United States, and after, while collaborating on various research papers. We've accomplished a lot and I'm very happy about that.

I also want to take this opportunity to thank the SERENE-IoT project, the Laboratoire de Conception et d'Integration des Systèmes (LCIS) Laboratory, the Grenoble EEATS doctoral school, Grenoble Alpes Cybersecurity Institute, and IDEX for financially supporting this work, the conferences, and all travel.

Last but not least, I would like thanks to all my friends, my colleagues, and my labmates. I would like to give a special thanks to both Baptiste Pestourie and Luc Perard, my two friends who spent a lot of time with me in Valence. Thank you Soraya Zahouily and Louise Constant for supporting me, even in the most difficult moments. Finally, I would not forget my family for their continuous love and support throughout all these years.

i

# Contents

|          |      | cknowledgements |                                                              |           |

|----------|------|-----------------|--------------------------------------------------------------|-----------|

|          | 140  |                 |                                                              | 111       |

| In       | trod | uction          |                                                              | 1         |

| 1        | Bac  | kgrou           | nd                                                           | 7         |

|          | 1.1  | _               | Iemory Safety Issue in Life-Critical Systems                 | 8         |

|          |      | 1.1.1           | C a prominent programming language in critical systems       | 8         |

|          |      | 1.1.2           | The C programming language weaknesses                        | 9         |

|          |      | 1.1.3           | Critical systems programming rules                           | 15        |

|          | 1.2  | Exploi          | tation Techniques                                            | 17        |

|          |      | 1.2.1           | Control-flow attacks                                         | 17        |

|          |      | 1.2.2           | Data-oriented attacks                                        | 23        |

|          |      | 1.2.3           | Real-world exploits                                          | 24        |

|          | 1.3  | Existi          | ng Defenses                                                  | 26        |

|          |      | 1.3.1           | Control-flow integrity                                       | 27        |

|          |      | 1.3.2           | Heuristic defenses                                           | 40        |

|          |      | 1.3.3           | Software diversity                                           | 43        |

|          |      | 1.3.4           | Data-flow integrity                                          | 46        |

|          | 1.4  | State           | of the Art Synthesis                                         | 55        |

|          |      | 1.4.1           | Control-flow integrity discussion                            | 55        |

|          |      | 1.4.2           | Heuristic defenses discussion                                | 56        |

|          |      | 1.4.3           | Software diversity discussion                                | 57        |

|          |      | 1.4.4           | Data-flow integrity discussion                               | 58        |

|          |      | 1.4.5           | State-of-the-art discussion                                  | 59        |

| <b>2</b> | Арр  | oroach          |                                                              | 62        |

|          | 2.1  | Proble          | em statement                                                 | 63        |

|          |      | 2.1.1           | Why critical medical devices are insecure?                   | 63        |

|          |      | 2.1.2           | Why current defenses are not implemented in medical devices? | 64        |

|          | 2.2  | Impor           | tant memory safety criteria for medical devices              | 68        |

|          | 2.3  | Appro           | aches                                                        | 70        |

| 3        | Sec  | Pump            |                                                              | <b>74</b> |

|          | 3.1  | Motiva          | ation                                                        | 75        |

|          | 3.2  | Open            | Source Medical Devices                                       | 77        |

|          | 3.3  | SecPu           | mp                                                           | 81        |

|          |      | 3.3.1           | wireless pump model                                          | 81        |

|          |      | 3.3.2           | SecPump software model                                       | 82        |

|          |      | 3.3.3           | SecPump variants                                             | 88        |

|    | 3.4               | Security Assessments                                                                                                                                             | 0 |

|----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    |                   | 3.4.1 Software Threats                                                                                                                                           | 0 |

|    |                   | 3.4.2 Hardware Threats                                                                                                                                           | 1 |

|    | 3.5               | Comparison with other works                                                                                                                                      | 3 |

|    | 3.6               | Conclusion                                                                                                                                                       | 5 |

| 4  | Tru               | tFlow 94                                                                                                                                                         | 8 |

|    | 4.1               | Motivation                                                                                                                                                       | 9 |

|    | 4.2               | Approach                                                                                                                                                         | 2 |

|    |                   | 4.2.1 A trusted environment                                                                                                                                      | 4 |

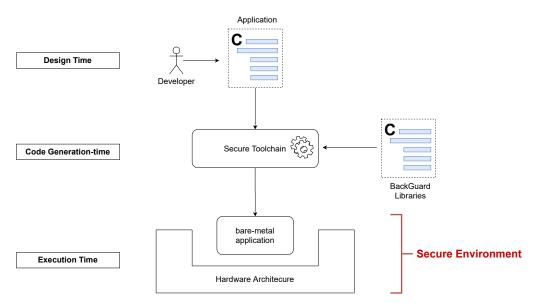

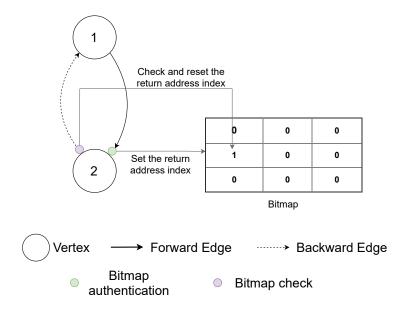

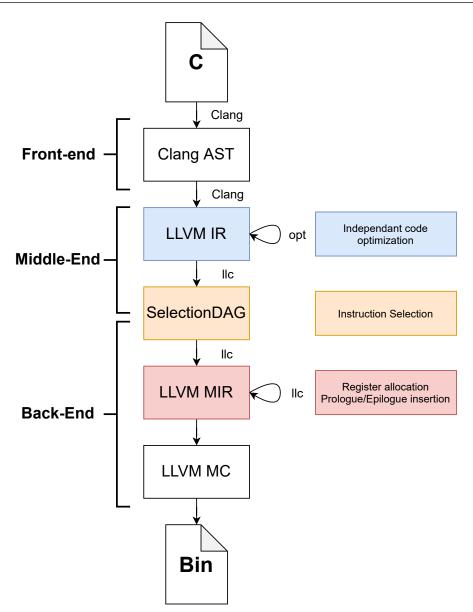

|    |                   | 4.2.2 A secure toolchain                                                                                                                                         | 5 |

|    | 4.3               | Implementation $\ldots \ldots \ldots$            | 8 |

|    |                   | 4.3.1 Environment Implementation                                                                                                                                 | 8 |

|    |                   | 4.3.2 Toolchain implementation                                                                                                                                   |   |

|    | 4.4               | Evaluation                                                                                                                                                       |   |

|    |                   | 4.4.1 Security evaluation $\ldots \ldots \ldots$ |   |

|    |                   | 4.4.2 Environment evaluation                                                                                                                                     |   |

|    | 4.5               | Discussion                                                                                                                                                       |   |

|    | 4.6               | Comparison with related work                                                                                                                                     |   |

|    | 4.7               | Conclusion                                                                                                                                                       |   |

| 5  | Dee               | Guard 12                                                                                                                                                         | 0 |

| 9  | <b>Бас</b><br>5.1 | Motivation $\dots \dots \dots$                                   | ~ |

|    | $5.1 \\ 5.2$      | Approach                                                                                                                                                         |   |

|    | 0.2               | 5.2.1 Protection concept $\ldots \ldots \ldots$  |   |

|    |                   | *                                                                                                                                                                |   |

|    |                   | ······································                                                                                                                           |   |

|    | 5.9               | 5.2.3 Implementation challenges $\dots \dots \dots$              |   |

|    | 5.3               | $Implementation \dots \dots$                               |   |

|    |                   | 5.3.1 Compiler implementation strategy                                                                                                                           |   |

|    |                   | 5.3.2 Additional passes $\dots \dots \dots$                      |   |

|    | <b>-</b> ,        | 5.3.3 Boot sequence $\dots \dots \dots$                          |   |

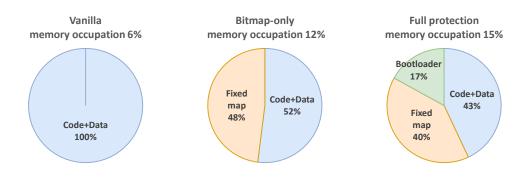

|    | 5.4               | $Evaluation \dots \dots$                                   |   |

|    |                   | 5.4.1 Security evaluation $\ldots \ldots \ldots$ |   |

|    |                   | 5.4.2 Costs $\ldots \ldots \ldots$               |   |

|    | 5.5               | Discussion                                                                                                                                                       |   |

|    | 5.6               | Comparison with related work                                                                                                                                     |   |

|    | 5.7               | Conclusion                                                                                                                                                       | 6 |

| Co | onclu             | sion 15                                                                                                                                                          | 9 |

|    |                   |                                                                                                                                                                  |   |

| Pe | erspe             | tives 16                                                                                                                                                         | 2 |

| Bi | bliog             | raphy                                                                                                                                                            | Ι |

| Li | st of             | Figures XV                                                                                                                                                       | V |

| Li | st of             | Tables XVII                                                                                                                                                      | т |

|    | 50 01             |                                                                                                                                                                  | * |

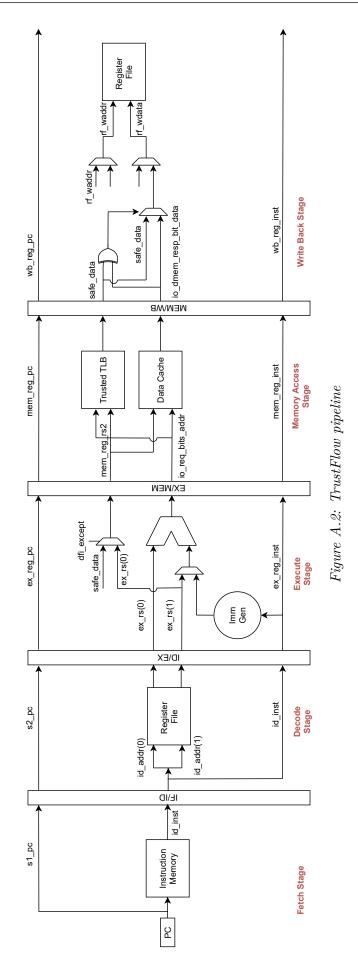

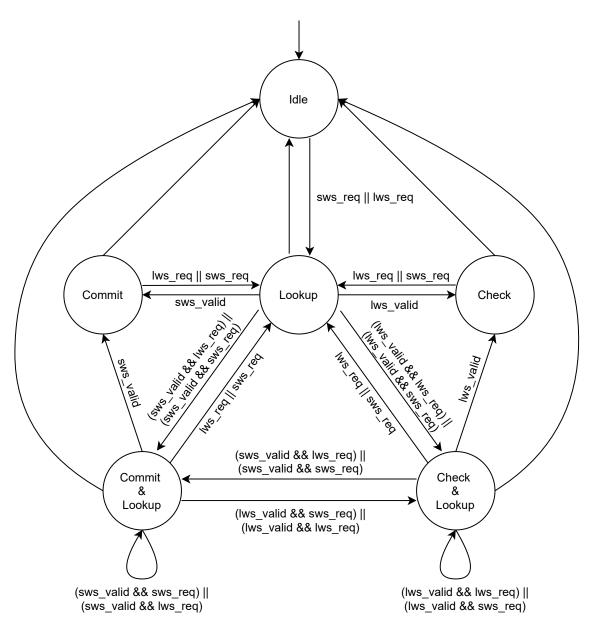

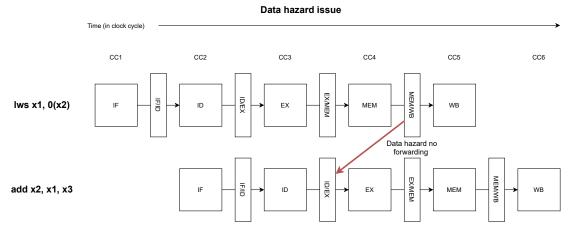

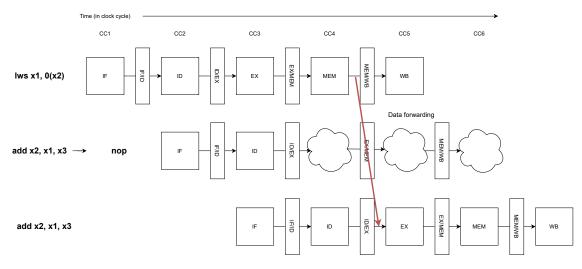

| A            | Annex 1: TrustFlow pipelineA.1 Trusted memory integrationA.2 Trusted memory controllerA.3 Data restoration | XXIII |

|--------------|------------------------------------------------------------------------------------------------------------|-------|

| в            | Annexe 2 : RISC-V prologue and epilogue insertion                                                          | XXVII |

| $\mathbf{C}$ | Annexe 3 : LLVM ARM backend bitmap pass                                                                    | XXX   |

### Introduction

With the emerging technologies in several domains such as artificial intelligence, communication, sensors, and processing power, manufacturers are increasingly developing new ubiquitous connected devices identified as the "Internet of Things" –IoT–. According to Forbes [1], the IoT is a fast-growing market that may even double before 2021. As a result, manufacturers see in IoT a genuine business opportunity that encourages them to increasingly release new smart devices over the coming years.

The prime purpose of IoT devices is to operate in an environment by collecting, processing, and sharing data over the network with other computers without any human-to-human or human-to-computer interaction. From the consumers' perspective, smart devices are technological innovations that aim at improving their daily life. One of the most common applications example of the "Internet of Things" is the smart home. In a smart home, a user can monitor some equipment such as the lights, the temperature, and the appliances by only using a smartphone. However, the "Internet of Things" is not limited to smart homes. Several sectors [2] such as agriculture, transport, healthcare, and the military are heavily invested in the development of innovative IoT infrastructures to improve their quality of life and quality of service.

This thesis unfolds within the European project SERENE-(IoT Secured & EneRgy EfficieNt hEalth-care solutions for IoT market). SERENE-IoT project is labeled within the framework of PENTA, the EUREKA Cluster for Application and Technology Research in Europe on NanoElectronics. The project contributes to developing high quality connected care services and diagnostic tools based on advanced smart health-care IoT devices. SERENE-IoT leverages the emergence of the "Internet of Medical Things" -IoMT-to prototype new devices, fully manufactured in Europe, that increases the healthcare quality of service for patients remotely followed by caregivers at a much lower cost than the traditional care.

Unfortunately, connecting medical devices to the network is a concern. It raises relevant questions especially in the areas of privacy, security, and safety [3]. The main purpose of this thesis performed within the CTSYS team of the Laboratoire de Conception et d'Intération des Systèmes (LCIS) in Valence and collaboration with the University of Arizona in Tucson is to focus on the embedded system application security of the next generation of IoMT. However, before digging into the security concerns that impact medical devices, it is important to define what is a medical device. According to the Food and Drug Administration (FDA) [4], a medical device is "an instrument, apparatus, implement, machine, contrivance, implant, in vitro reagent, or other similar or related article, including a component part or accessory which is: recognized in the official National Formulary, or the United States Pharmacopoeia, or any supplement to them, intended for use in the diagnosis of disease or other conditions, or in the cure, mitigation, treatment, or prevention of disease, in man or other animals, or intended to affect the structure or any function of the body of man or other animals, and which does not achieve its primary intended purposes through chemical action within or on the body of man or other animals and which is not dependent upon being metabolized for the achievement of any of its primary intended purposes". For instance, two medical devices are shown in Figure 1. On the left, a pacemaker used in the treatment of heart diseases. On the right, an insulin pump commonly used in the treatment of diabetes.

Figure 1: Off-the-shelf medical devices

In consistence with healthcare manufacturers, the main purpose of connecting these two medical devices is to improve the quality of service. It may help healthcare professionals in the prevention, diagnosis, and treatment of patients' disease. From the patient perspective, wireless medical devices improve the quality of life. For instance, it is much less restrictive to update a pacemaker using the Bluetooth<sup>TM</sup> [5] protocol rather than performing surgery. Thus, healthcare manufacturers see IoMT as a way to revolutionize and improve patient care. Thanks to connectivity many medical devices may help healthcare professionals to identify early disease at the lowest cost but also to monitor and adjust the progress of a patients' treatment over time [3].

A representative example of a wireless medical device is a connected insulin pump. Insulin pumps are commonly used in the treatment of diabetes. Today, according to the World Health Organization (WHO) [6] it is more than 8% of the worldwide population that suffers from diabetes. To stay alive, these people must regularly inject themselves manually with insulin to keep their blood sugar at a reasonable threshold. Although this practice is necessary, it remains very binding for patients. Thanks to new IoMT devices such as wireless insulin pump [7,8] the process of measuring and self-injecting the insulin is automated and even remotely controlled. As a result, the quality of life and comfort of patients significantly improved.

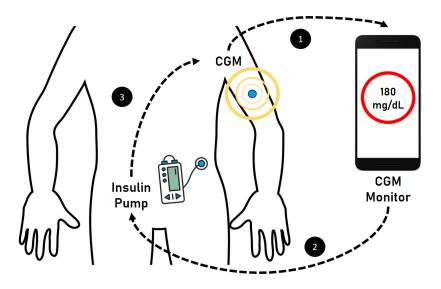

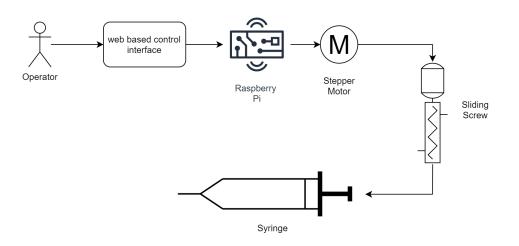

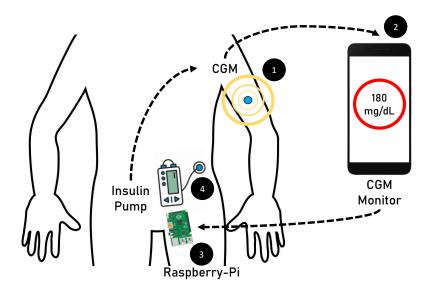

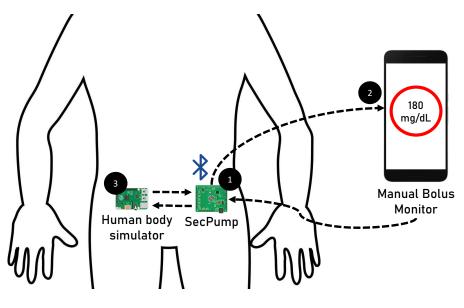

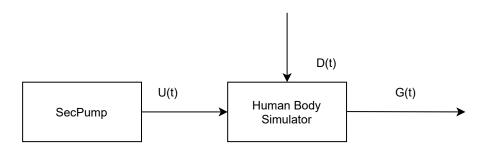

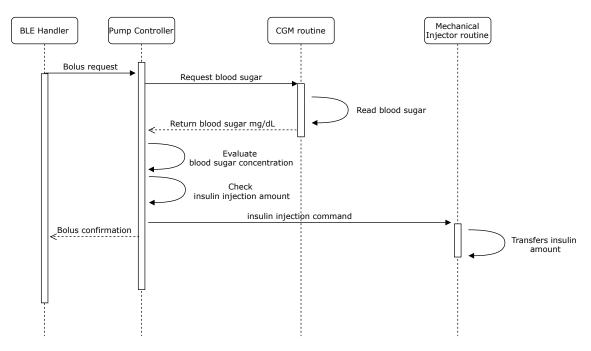

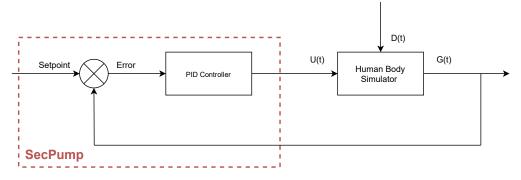

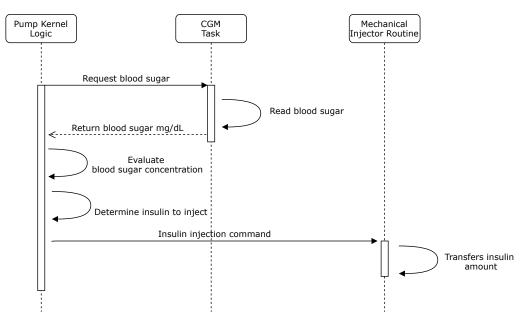

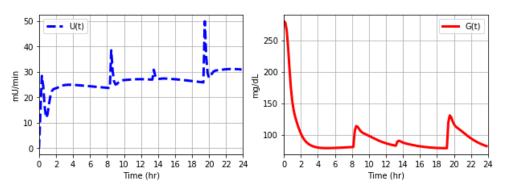

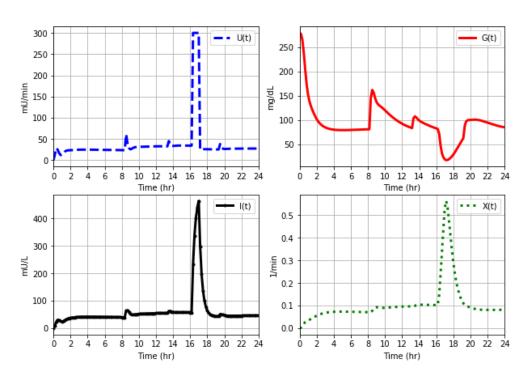

Figure 2 displays an overview of a closed-loop wireless insulin pump. Three major

Figure 2: Insulin pump closed-loop

components are identified. The Continuous Glucose Monitor (CGM) is a tiny sensor implanted under the skin that measures glycemia at regular intervals. These measurements are sent to a remote smartphone application that computes and determines whether the blood glucose is too high (1 in Figure 2). If the glycemia is too high, a bolus injection command is sent from the smartphone to the insulin pump (2 on Figure 2). Usually, these commands are sent using a low-energy radio protocol such as Bluetooth<sup>TM</sup> [5]. Once received, the command is processed and injects an insulin bolus to the patient. Finally, the injected insulin maintains the glycemia of the patient that is again measured by the CGM forming the closed-loop system (3 on Figure 2).

The extension of connected devices such as insulin pumps in the healthcare industry is a promising innovation and will undoubtedly bring many benefits to both caregivers and patients. However, as previously stated, connecting medical devices to the network is a concern. Indeed, a large majority of medical devices such as pacemakers, insulin pumps, defibrillators are considered life-critical systems. In other words, these devices are in direct interaction with the human body and may harm in the event of a hazard or even worse, a security breach. Of course, healthcare manufacturers are well trained about safety issues and various hazards in medical devices for decades. Many medical devices on the market have been validated by recognized institutions such as the FDA [4] and to date are considered very safe. However, it appears that manufacturers are less aware of cybersecurity issues [9]. This is because connecting a medical device to the network is a relatively recent trend. Consequently, these devices are more exposed to new threats that manufacturers were not confronted with in the past.

According to recent studies [9], it seems that basic security features such as integrity, authenticity, privacy, and defense-in-depth are missing in medical devices. One possible explanation for this is that manufacturers lack security experts [10]. Thus, security issues are left to non-security experts. Knowing that the integration of security in critical devices is a difficult task, without security expertise, the design and the integration of the latter are usually poorly achieved. Furthermore, advanced vulnerability research should be part of the development life cycle of a medical device. However, this is rarely the case, advanced security tests are time and budget consuming making them regularly neglected.

For hackers, this lack of robust security trends is profitable. In recent years, many new attacks have appeared on various life-critical systems. For instance, security researchers were able to maliciously modify the firmware of a real infusion pump [11] and pacemakers [12] because there were not properly signed by the manufacturers. As a result, these researchers were able to implement malware directly in the device. Also, many wireless medical devices do not verify the authenticity and the identity of the host with whom they interact. Hence, a malicious hacker can easily craft a fake application [13] and send malicious commands to the critical device. Many medical devices use a proprietary protocol for communication. Unfortunately, these protocols do not use proper or standard ciphers leaving the data in plain text passing through the network [13]. As these devices are connected to the network, they can also be remotely accessed. Unfortunately, once again, the accesses are often poorly secured, and even sometimes, there is no security at all [14]. On top of that, medical devices are vulnerable to zero-day vulnerabilities such as memory safety issues that result from code and design mistakes [15]. These vulnerabilities can be exploited by hackers to remotely execute malicious code on the device. The seriousness of this type of attack is extreme, it can be achieved without requiring any physical access to the system. In an era of ransomware [16], such poor security devices are profitable to hackers that look for a quick return on investment. Since these critical-devices keep patients alive, it's even easier for hackers to pressure them to pay a ransom.

As it appears, there are various vulnerabilities in medical devices. Countermeasures against these vulnerabilities cover many areas of software and hardware security. This thesis focuses on embedded software security. More, specifically the thesis studies the memory safety issue in life-critical devices. When exploited, memory safety issues allow attackers to take control of a device and make it execute arbitrary malicious actions. While the criticality of these vulnerabilities is severe, and even more when it can be performed remotely, it seems that efficient protections are currently not deployed in medical devices [9,17,18].

To address these concerns, this manuscript proposes the following steps. The first chapter covers the state-of-the of various attacks and defenses regarding memory safety. It highlights the particularities of critical embedded systems such as medical devices, why they are exposed to memory safety issues, how memory safety vulnerabilities are exploited, and finally, what are the existing defenses. Chapter 2 confronts the state of the art with the requirements of life-critical medical devices. More specifically, this transitional chapter identifies why current medical devices do not benefit from existing defenses. Then, it exposes the problem: How to implement **practical** and **efficient** defense against memory safety defenses in safety-critical devices while respecting their constraints? The thesis proposes to deal with this problem using two approaches and a life-critical demonstrator to assess them. Chapter 3 exposes SecPump, a wireless insulin pump security system workbench used to model memory safety threats and tailored for further security assessments. Chapter 4 presents TrustFlow, the first approach of the thesis. This approach assumes that memory safety defenses can be implemented using both hardware and software. As a whole, TrustFlow is a framework that ensures low-level software protection specifically for memory-constrained embedded systems. Conversely, Chapter 5 presents BackGuard, the second approach of the thesis. Unlike the first approach, this approach assumes that most critical embedded applications are running on a fixed microprocessor that cannot be modified to implement security features. As a result of this assumption, this second approach aims to demonstrate and study the feasibility of memory safety defenses using only software primitives.

# Background

#### Summary of the Chapter

This Chapter surveys the memory-safety issue in embedded systems. As this thesis unfolds in the medical area, a brief introduction to life-critical devices is given at the beginning of the Chapter. This introduction describes how these systems work, how they are designed, and why they are currently facing memory safety issues. The Chapter offers an overview of the various attack techniques that are leveraged by an attacker to execute malicious code on a system. Then, it exhibits the state-of-art regarding the existing countermeasures. This state-of-the-art regroups the countermeasures in four categories exposing their benefits, costs, and weaknesses. Finally, synthesis of the state of the art prepares the gap exposure and the thesis approach outlined in Chapter II.

### Contents

| 1.1 The Memory S               | Safety Issue in Life-Critical Systems                                                                                |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 1.1.1 C a promin               | nent programming language in critical systems 8                                                                      |

| 1.1.2 The C pro                | gramming language weaknesses                                                                                         |

| 1.1.3 Critical sys             | stems programming rules                                                                                              |

| 1.2 Exploitation T             | echniques $\dots \dots 17$ |

| 1.2.1 Control-flo              | w attacks                                                                                                            |

| 1.2.2 Data-orien               | ted attacks $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 23$                               |

| 1.2.3 Real-world               | exploits                                                                                                             |

| 1.3 Existing Defen             | ses $\ldots \ldots 26$                                |

| 1.3.1 Control-flo              | w integrity $\ldots \ldots 27$                                                                                       |

| 1.3.2 Heuristic d              | lefenses                                                                                                             |

| 1.3.3 Software d               | iversity                                                                                                             |

| 1.3.4 Data-flow                | integrity $\ldots \ldots 46$     |

| 1.4 State of the Art Synthesis |                                                                                                                      |

| 1.4.1 Control-flo              | w integrity discussion                                                                                               |

| 1.4.2 Heuristic d              | lefenses discussion                                                                                                  |

| 1.4.3 Software d               | iversity discussion                                                                                                  |

| 1.4.4 Data-flow                | integrity discussion                                                                                                 |

| 1.4.5 State-of-th              | e-art discussion $\ldots \ldots 59$                   |

### 1.1 The Memory Safety Issue in Life-Critical Systems

### 1.1.1 C a prominent programming language in critical systems

Life-critical systems such as wireless insulin pumps described are governed by both hardware and software components. One of the fundamental aspects of these components is that they should meet high performance and deterministic real-time constraints to deliver the patients' perfect dose of insulin at the right time. Also, for patient-worn systems, the components must be small in order not to be too invasive. The logical and deterministic actions performed by cyber-physical systems are driven by thousands of lines of code that are executed by microcontrollers. Microcontrollers are often considered as the brain of smart devices. They execute instructions that control and deliver input/output to external components. These external components include drug reservoirs, screens that establish physical contact between the user and the embedded system, sensors, and radio components. Finally, the set of lines of code that lead the logic of the system constitutes the firmware. Its main purpose is to monitor the behavior of the device throughout its lifetime.

According to a recent study made by the IEEE Spectrum 2017 [19], the C programming language is the dominant language in the context of embedded system programming. Most of the existing critical devices' firmware on the market are developed using the C programming language [18]. This popularity can be explained by several advantages that this C offers to critical embedded systems manufacturers over other programming languages:

- Maturity: The C programming language has been created more than 40 years ago to provide an alternative to writing code in assembly. Since then it has been widely used in companies and academia. Compared to much newer programming languages [20, 21], the C programming language has the advantage of being supported by a large and experienced community.

- *Readability*: C is considered a high-level programming language in comparison with assembly. It has been created to write data structures and algorithms without relying on complex assembly knowledge.

- Toolchain support: Many free C compilers [22], [23], and libraries are available for a wide range of microcontrollers. This means that the C programming language can be easily translated into efficient machine-independent code. On top of that, the current C compilers are very mature and offer a lot of features such as detecting programming errors during compilation and/or code coverage [22]. Also, many free open-source and well-maintained toolchains are available to perform either static [23,24], and/or dynamic [25,26] verification of C programs.

- *Modularity*: The C programming language is very modular, thanks to header files it allows developers to export functionality from a C source file and import it in another

file. Consequently, by using modularity it is very easy for a programmer to break a complex program into multiple sub-modules that achieve specific functionalities.

- *Portability*: Many free C compilers are available for a wide range of Instruction Set Architecture (ISA). This means that the C programming language enables developers to write convenient processor independent code that ensures low-level tasks while retaining portability.

- Efficiency: The C programming language can easily interface with other programming languages such as assembly. In embedded system programming, it is very common to see routines that are completely written in assembly to efficiently use the hardware. Secondly, one of the most powerful features offered by the C programming language is full control over memory management thanks to pointers. Indeed, by using pointers, embedded system developers can directly read/write from/to memory or allocate it in an efficient, machine-independent way. Consequently, embedded systems programmers can customize the memory usage of embedded systems applications making it inherently fast and optimized in size. Finally, as most of the embedded systems have input/output devices that are directly mapped into the memory, the use of pointers allows instant access to these memory locations.

- *Real-time operating system support*: On the market, the most popular real-time operating systems [27–30] are written in the C programming language. The C programming language is very fast and efficient; it can easily meet real-time constraints. Besides, these real-time operating systems provide C APIs enforcing the use of this language by developers.

- *Determinism*: C programs can be written to be deterministic. This means that it is formally possible to determine the behavior of a program knowing its current state, the previous events, and the environment. Determinism is a very strong feature for critical systems because it allows manufacturers to develop very accurate programs.

- *Standard*: The C programming language is compliant with safety-critical standards such as the DO-178C [31] and MISRA C [32].

It turns out that the C programming language is a perfect language for critical systems. The language is close to the hardware, allowing developers to tune specific routines and memory allocation. This programming language can be used to develop lightweight applications that are very **fast**, **deterministic**, **safe**, and **portable**.

Unfortunately, these benefits come at a certain price. The C programming language does not provide any specific security support against memory access mistakes. This can lead to several security breaches covered in the following section.

### 1.1.2 The C programming language weaknesses

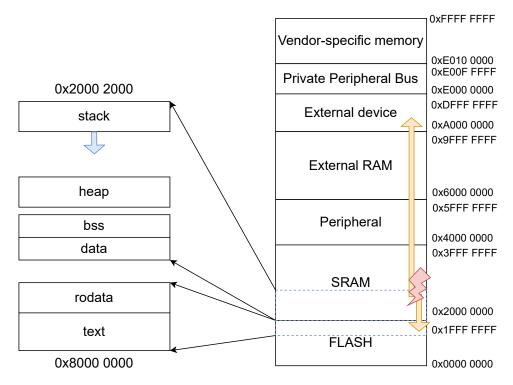

While the C programming language provides many benefits to embedded system developers, it is often the source of numerous in-memory security flaws due to the misuse of pointers. To understand the origin of in-memory security flaws, it is important to introduce the basic memory layout of a C program.

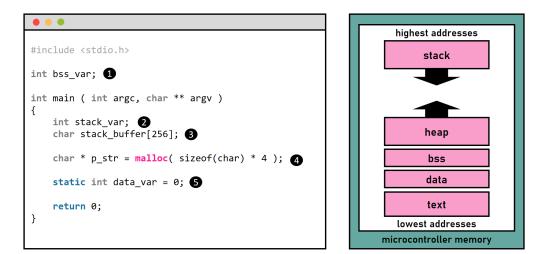

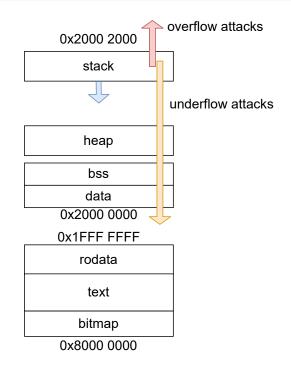

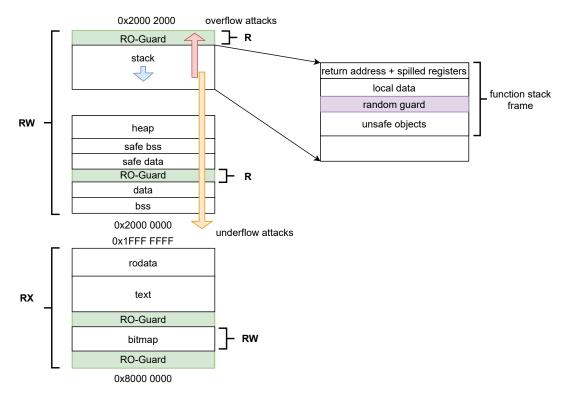

A simplified example of a C program is displayed in Figure 1.1.

Figure 1.1: C program memory layout

Several variables in the displayed program are annotated with bullets. When compiled into instructions, the program is mainly stored on the "text" memory section of the microcontroller. When executed, this program performs computations using variables that are stored in several areas of the memory.

The variable (1) is an uninitialized global variable. It is stored in the Block Started by Symbol (BSS) area of the memory. This global variable can be accessed throughout the entire lifetime of the program by any function. If it turned out that the variable was initialized it would be placed in the data section.

Both variable (2) and (3) are used within a function, their scope is limited to the life span of the main function. Regarding the microcontroller memory, these temporary variables are placed in the stack area. The stack is a memory structure that follows the Last-In-First-Out (LIFO) concept. In Figure 1.1, the stack is ascending downwards. The stack memory structure is addressed by the stack pointer register of the microprocessor core. This register always points to the memory address of the top of the stack. Two main operations manage the stack: push and pop. When data is pushed, the stack pointer moves to the lowest adjacent address, and the corresponding data is stored. When data is popped, the data stored at the stack pointer address is returned and the pointer moves to the highest adjacent address. Considering our example, when the main function executes, (2) and (3) are pushed on the stack and destroyed when the function returns.

The variable (4) is slightly different from the variable (2) and (3). Indeed, the variable (4) is a pointer stored on the stack but points on a freshly allocated memory which is located in the heap area thanks to a memory allocation function. In Figure 1.1, the heap memory area is increasing upwards. The heap is governed by specific memory allocation algorithms that depend on the "malloc" implementation. Each memory chunk allocated in the heap is accessible by a program through the use of pointers. Besides, allocated

memory chunks can be freed thanks to the "free" function.

Finally, the variable (5), is a static initialized variable. This variable is placed into the data memory section and its value is preserved even when the main function returns. However, this variable is considered private and can only be accessed by the main function.

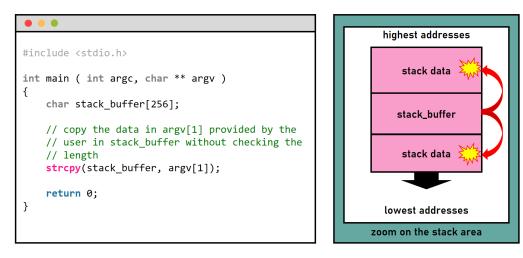

Knowing the structure of a C program in memory, it is now possible to point out its weaknesses. Unlike high level and/or interpreted programming languages [33, 34], the C programming language does not provide any extra features for spatial and temporal memory safety. The C programming language is thus considered unsafe. Spatial memory safety is defined as the property that all memory objects are always accessed within their bounds. In other words, the C programming language does not ensure that the data copied into a buffer will no longer be larger than the buffer can hold. It follows, that if a developer does not explicitly check for oversized input, an attacker can intentionally provide large enough data that will write past the end of a buffer. As a result, adjacent memory areas that do not belong to the buffer will be overwritten, leaving the program in an erratic state. The most prominent example of a spatial memory error is a stack buffer overflow/underflow. A classical stack buffer overflow is displayed in Figure 1.2. In such a situation, an attacker overflows a local buffer on the stack and overwrites useful buffers' adjacent data of the program. In Figure 1.2, the "stack\_buffer" buffer is in the stack area and the "strcpy" function copies a buffer coming from "argy [1]" which is controlled by an attacker. Unfortunately, the "strcpy" function does not check the size of "argy [1]" before copying it to the "stack buffer" buffer. Consequently, an attacker can exploit this feature to modify some data in the memory that does not belong to the buffer. Thus, if this data is reused later, the behavior of the program may be modified. It should be mentioned that spatial vulnerabilities are nowadays much more complex than the straightforward example displayed in Figure 1.2 [35].

Figure 1.2: Spatial memory issue

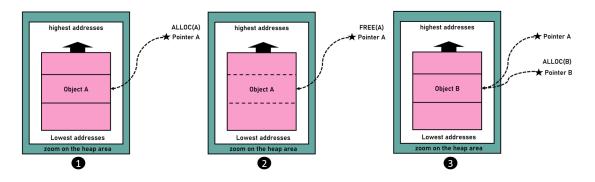

Temporal memory safety is defined as the property that ensures that all memory objects are valid at the time they are dereferenced by a pointer. Like spatial memory safety, the C programming language does not prevent any attempts to read or write an object after it has been deallocated. It follows that, after deallocating an object in memory, if the developer does not explicitly invalidate all pointers on this object, some will still point to the freed memory location. These pointers are called dangling pointers; they can dereference invalid memory location. By leveraging dangling pointers, an attacker can intentionally reallocate the previously freed memory, fill it with malicious data, and dereference a dangling pointer to this location. As a result, the previously deallocated object is reused thanks to the dangling pointer with invalid data causing unexpected memory corruption.

Figure 1.3: Temporal memory issue

A typical dangling pointer scenario is displayed in Figure 1.3. This example assumes that an attacker can use object A and free it thanks to the pointer A. Also, it assumes that object A has previously been allocated by the application (1) and cannot be modified by an attacker. However, the example assumes that an attacker can fully allocate an object B and modify it. By leveraging this dangling pointer issue, an attacker can launch a memory attack in three steps. First, the attacker makes the application free object A in memory (2). Due to the vulnerability, pointer A is still pointing to invalid memory object A. Then, the attacker allocates a new object B and fills it with custom data (3). Finally, the attacker makes the application reuse the pointer A which is pointing on an invalid controlled object B. As a result, the application executes code that belongs to object A but with object B values. As spatial attacks, dangling pointers can be maliciously manipulated by attackers to make an application execute invalid data.

The incorrect verification of oversized input and the usage of freed memory are common programming vulnerabilities related to the usage of the C programming language [36]. Nowadays, buffer overflows and dangling pointers, represent a significant part of the low-level security bugs [15, 37]. Their exploitation has many consequences from crashing a target application to executing user-supplied malicious code. This thesis is chiefly concerned about malicious code execution on critical devices. Indeed, the ability of an attacker to induce faulty behavior into a critical system is a significant threat that can lead to disastrous consequences.

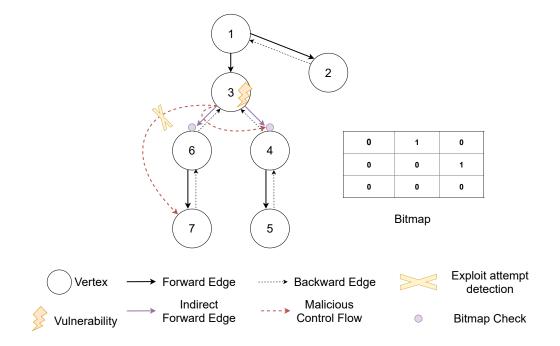

To understand arbitrary code execution on embedded devices, Figure 1.4 exposes the concept of control-flow graphs.

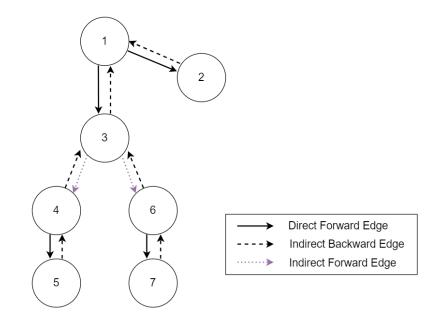

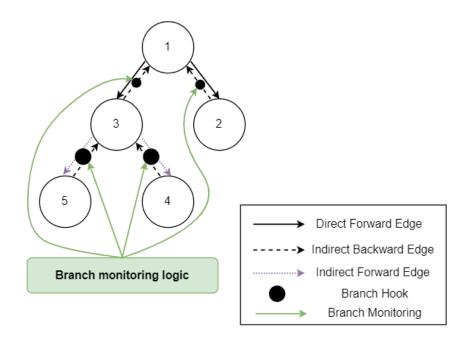

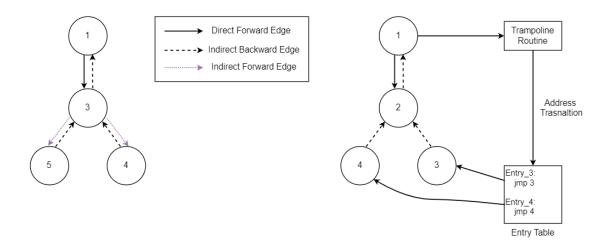

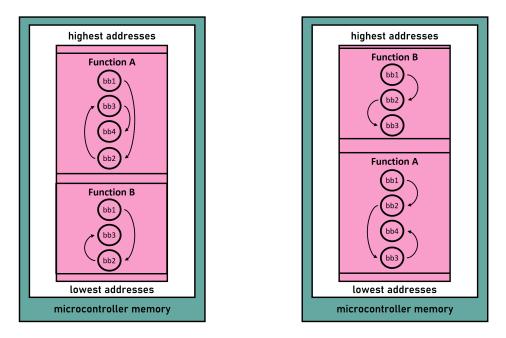

Figure 1.4: Control-flow graph

A typical embedded system application written in C can be represented by a controlflow graph such as Figure 1.4. All vertex in such a graph usually represents a basic block of code. However, to simplify the study the present work considers that each vertex in this graph represents a function. Of course, each function is composed of basic blocks and has an internal control-flow graph as well. Vertices are linked with each other using edges. These edges represent transitions between functions in the graph such as function calls and function returns. A function call is denoted as a forward-edge and is represented in green in Figure 1.4. A forward-edge can either be direct, or indirect through a function pointer. Conversely, a function return is denoted as a backward-edge and is represented in purple in Figure 1.4. Most of the time, a backward-edge is indirect and uses the return address of the caller function that is already pushed in the stack or a register according to the microcontroller architecture calling convention.

It turns out that every function transition in an application is governed by control-flow information. This control-flow information is either immutable in the source code (direct forward-edge) or calculated at run-time through a function pointer (indirect forwardedge) and/or function return address (indirect backward-edge). Unlike fixed control-flow information, indirect control-flow transitions are usually computed at run-time and stored in either registers or memory. Thus, from the moment control-flow information is stored in memory it can be tamper through the exploitation of one of the previously exposed vulnerabilities such as buffer overflows or dangling pointers.

A typical control-flow attack is performed at run-time when data is exchanged between a malicious user and the application. The main goal of a control-flow attack is to hijack the execution flow of an application and make it execute malicious actions. For instance, a spatial memory vulnerability can be exploited by an attacker to write past beyond the limit of a buffer. Thus, the attacker possesses an arbitrary write in memory that may overwrite control-flow information located close to the buffer. By replacing in-memory control-flow information, an attacker can divert the execution flow on a destination of his choice.

Nowadays, every embedded system written in C can be vulnerable to memory corruption bugs. Even with extremely accurate and advanced tests, the time proved that some memory bugs remain undetected [18, 35]. However, these memory bugs can potentially threaten the security of a system after being discovered by attackers. Unfortunately, there are still a lot of reasons why the memory safety issue is far from being solved in critical IoT devices:

- Device complexity: Connected devices especially life-critical devices in healthcare are becoming increasingly complex. These devices have to deal with hard real-time constraints and deterministic behavior in any condition. For instance, an infusion pump in its intended operating mode had to deliver the perfect amount of insulin when needed without misbehaving due to physical external factors. Besides, some embedded software may control physical devices. These physical devices can be the source of high pressure or X-ray control and therefore extremely difficult to debug when controlled by software. Finally, the combination of several physical elements controlled by software increases the complexity of a system, its safety analysis, and the implementation of accurate tests that cover all functionalities without unwanted bugs.

- The number of lines of code: There are no existing metrics that give the average bugs per line of code. However, it is often considered that there are between 15 and 50 bugs per 1000 lines of code [38]. Applied to a pacemaker which is around 80,000 lines of code [39], an infusion pump which is around 170,000 lines of code [39] or a magnetic resonance imaging which is around 7 million lines of code [39], there is a high probability that some memory bugs remains undetected after tests and attackers are looking for them.

- *Third-party services*: When developing a critical application, it may require the use of libraries or third-party code. Although it is possible to test these third-party codes before integrating them, this operation may require non-trivial reverse engineering skills due to the unavailability of the source codes.

- Increased attack surface: From the three previous points it follows that the attack surface of a system is directly proportional to its complexity, its number of lines of code, and its number of integrated third-party code. Hence, the more complex the system proves to be, the more likely it is that attackers will find vulnerabilities. Also, with the Internet of Things trend, more and more manufacturers are connecting devices to the Internet and critical medical systems are no exception [9]. Unfortunately, the connectivity sharply increases the attack surface. Indeed, with a memory vulnerability, an attacker is now able to remotely control a critical system.

Finally, while the C programming language offers fine control over embedded systems,

this section demonstrated that it comes with a certain security cost. As extensively discussed, the C programming language does not provide any safeguard against memory safety issues. One can argue that the exploitation of memory corruption bugs is not new and the ways to overcome it have been studied over the past twenty years [40]. Unfortunately, it seems that critical devices are still vulnerable to it [15,37].

#### 1.1.3 Critical systems programming rules

The usage of the C programming language in critical embedded systems differs from traditional desktop applications. Life-critical medical devices can mean the difference between life and death. To release medical devices on the market, manufacturers closely follow important standards such as the IEC 62304 [41], a functional safety standard that specifies the software requirements for medical devices, the ISO 14971 [42] for the risks managements, the ISO 13485 [43], a set of procedures guaranteeing the quality monitoring, and finally, the FDA regulations [44] concerning medical records and device traceability. These certification standards assess the quality and the safety of medical devices software based on the development process [45]. Regarding the implementation, the IEC 62304 [41] strongly enforces the use of coding standards such as MISRA [32] to enforce safety. By respecting these guidelines, manufacturers reduce the likeliness of software hazards and they allow certification of their products. While these standards ensure quality, reliability, and safety, it should be mentioned that they do not remove security issues related to memory safety [15, 17, 37].

To avoid the use of long and complex (sometimes vague) coding standards, the Jet Propulsion Laboratory (JPL) of NASA proposes the "The Power of Ten – Rules for Developing Safety Critical Code" [46]. This paper summarizes some strict development rules to write safety-critical applications using the C programming language. The JPL argues that 10 rules are not all-inclusive but it is enough to achieve measurable effects on software reliability. These 10 rules mostly summarize the highest coding standards such as MISRA [32].

This thesis considers that most life-critical medical devices enforce these rules. Consequently, the security contributions detailed in the following thesis are designed in accordance with [46]. More specifically, the security contributions will at a minimum be able to protect systems that comply with the 10 rules enforced by the JPL. Not all the rules are mentioned in this manuscript. Some of them encourage the improvement of code quality in safety-critical applications. For in-depth details, the thesis refers the reader to "The Power of Ten – Rules for Developing Safety Critical Code" paper [46]. However, bellow is three important rules that have an impact on the outcome.

• Use of simple control-flow structures: No "setjmp", "longjmp", "goto" or direct/indirect recursion: By respecting simple control-flow structures developers improve the clarity of an application and make debugging easier. Moreover, the use of recursion introduces cycles into control-flow graphs that complicate the verification task of static analyzers. Besides, it is not an easy matter to cover all the tests to determine the upper bound of a recursive function. As a consequence, recursion can induce prohibitive unexpected large usage of stack memory in life-critical systems. Finally, according to [38], a recursive function can always be translated into iterative function.

• No dynamic memory allocation after initialization: According to [38,46] and most of the references in critical software development [31,32], the use of dynamic memory allocation using "malloc" introduces memory pool fragmentation and potential memory leakage (dangling pointers).

It follows that the usage of dynamic memory allocation is not deterministic and thus cannot be safe.

• No more than one level of pointer dereferencing: The use of pointers is one of the major sources of programming errors, safety, and security issues. Although their use may be practical, it must be minimized and restricted to the smallest scope as possible. Moreover, according to [46], the use of function pointers should be justified and even prohibited. Indeed, when checking an application, the use of a function pointer prevents static analysis tools from determining a call destination and the absence of recursion. However, after being reviewed 10 years later [38], it seems that the JPL considers that "constant function pointers, for instance, stored in lookup tables, pose no risk to safe execution or code analysis".

Considering the previous rules and with section 1.1.2, life-critical application mostly consumes static memory. Consequently, most memory vulnerabilities are located in static regions such as the stack, the data, and the BSS. In critical embedded systems, temporal memory safety issues are restricted by the non-use of dynamic memory allocation.

### **1.2** Exploitation Techniques

A successful memory attack results from the exploitation of a spatial and/or temporal memory issue. The main goal of a memory exploit is to divert the execution flow of an application to make it trigger malicious actions. This section highlights the various exploitation techniques used by both attackers and researchers to hijack the behavior of a program. The state-of-the-art is carried out in two parts: control-flow attacks and dataoriented attacks. Control-flow attacks aim at diverting the execution flow of a program by violating its control-flow graph whereas data-oriented attacks break the logical behavior of an application without necessarily violating the control-flow graph.

### 1.2.1 Control-flow attacks

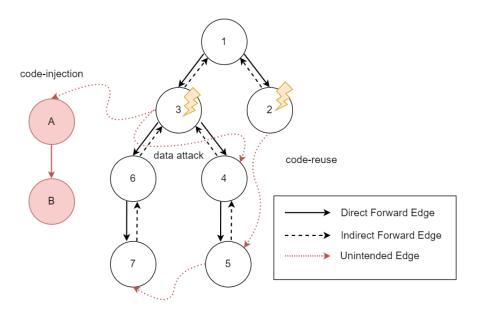

This section discusses various control-flow attacks. More specifically, control-flow attacks mostly rely on malicious code injection and/or code-reuse techniques.

### 1.2.1.1 Code-injection attacks

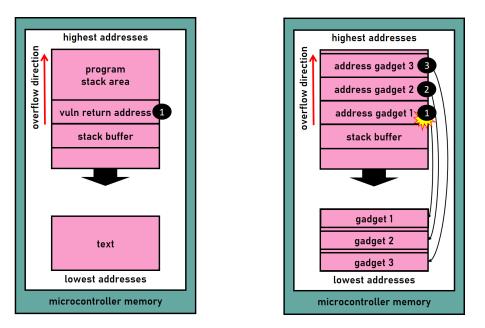

Historically, the first control-flow attacks were based on code injection [47]. To illustrate the code-injection process this section refers to Figure 1.5.

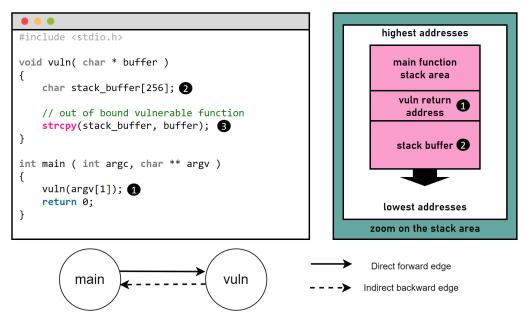

Figure 1.5: Stack-based buffer overflow issue

A trivial example of a buffer overflow vulnerability is displayed on the code part of the Figure. A primary function "main" is calling a "vuln" function with a buffer argument. Such code can be easily represented by a basic control-flow graph with two vertices (on the bottom in Figure 1.5). The zoom on the stack memory area is particularly interesting in this example because this is exactly where an attacker achieves his attack. First, the "vuln" function (1) is called by the "main" function. This has the effect of saving the return address (1) of the "vuln" function in the stack. Indeed, after its execution, the

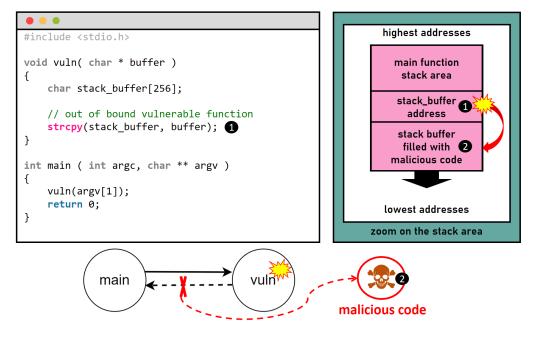

"vuln" function must return to the "main" function to continue execution. To achieve this, the "vuln" function needs control-flow information stored in memory such as the saved return address. Then, a buffer (2) is also stored in the stack area (2) of the "vuln" function. According to Figure 1.5, the buffer is close to the return address stack. Finally, the "strcpy" function is used to copy data controlled by an attacker in the stack buffer (2). As the "strcpy" does not perform any bounds checking while copying the attacker data in the stack buffer, a spatial memory vulnerability can be exploited. Such a spatial attack is shown in Figure 1.6. First, an attacker injects a malicious code (shellcode) in the stack buffer. Such shellcode is a string of hexadecimal characters that correspond to instruction opcodes that can be executed by a processor. When executed, the main purpose of shellcode is to manipulate registers, functions, or syscalls of a program (originally, the term shellcode was derived from the action of spawning a root shell when executed on a target). Then, the attacker exploits the out-of-bound vulnerability (1) to overwrite the "vuln" return address in memory and replace it with the address of the buffer which contains the shellcode (2).

Figure 1.6: Stack-based buffer overflow exploit

As a result, when the "vuln" function returns, its return address is popped from the top of the stack to the program counter register that points on the next instruction to execute. Consequently, instead of returning to the "main" function, the "vuln" function returns to the shellcode previously injected by the attacker (2). Finally, the behavior of the target application is controlled by the injected shellcode.

Code injection attacks were very popular around the 2000s on desktops computers. For instance, the SQL Slammer worm [48] was exploiting a buffer overflow in Microsoft's SQL servers to infect computers. Likewise, the Morris worm [49] exploited a vulnerability in the Fingerd protocol to spread over the network and paralyze hundreds of thousands of computers. Since then, several countermeasures have been proposed to protect applications against memory safety exploits. Three very famous buffer overrun protections such as Address Space Layout Randomization (ASLR) [50], Data Execution Prevention (DEP), and Stack Smashing Protector [51] are currently widely deployed in most personal computer application. These countermeasures are summarized in Figure 1.7.

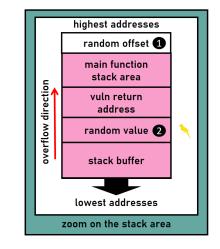

Figure 1.7: Common exploits mitigations

The Address Space Layout Randomization (ASLR) is managed by a classic operating system such as Linux or Windows. It has the effect of placing the stack at different memory offset (1) each time an application is executed. As a result, it is much more difficult for an attacker to predict the address of an injected malicious code in randomized memory areas. To push it further, various types of ASLR are currently available and deeply exposed hereafter.

The Data Execution Prevention (DEP) is a hardware feature that can be managed by operating systems with MMU and/or MPU support. The main purpose of DEP is to define non-code memory regions as not executable. Consequently, any malicious code injected into the stack, in particular, will no longer be treated as instructions.

The Stack Smashing Protector (SSP) is a compiler feature that requires a Random Number (RN). This feature enforces the return address protection of function that manages stack frame objects subject to overflow issues. Each time an application is executed, a random value is placed in a function's stack frame between the return address and the local variables (2). Then, before a function returns, the value of the Stack Protector is checked to ensure that no out-of-bounds write modified the return address.

With the ASLR, DEP, and the SSP, memory corruptions are much harder to exploit on desktop computers. However, there are imperfect. For instance, the ASLR applies to both 32-bit and 64-bit systems. Regarding 32 bits systems, the entropy of the ASLR is very low (up to 8 bits). This means that a maliciously injected code position can be brute-forced in a reasonable time. Also, there is a downside to using canaries. At first, the compiler does not instrument all functions (around 20,5% functions for the Linux kernel [52]), so some of them remain unprotected. Besides, checking a canary value for each protected function introduce extra code that often results in performance degradation. Finally, DEP prevents attackers from executing malicious code in the data memory areas. Although DEP is effective against code injection attacks, new attacks such as code-reuse attacks [53] completely overcome it.

Regarding embedded systems, it seems that the ASLR, DEP, and the SSP are not well-suited. Unlike desktop computers, embedded systems do not always benefit from an operating system with full MMU support nor Truly-/Pseudo-Random Generators [54]. Hence, embedded applications cannot be effectively protected by the ASLR and the SSP. On top of that, many embedded systems are based on 32 bits' microcontroller systems. As previously discussed, the 32 bits ASLR is weak. Finally, some embedded systems with a Memory Protection Unit [55] (MPU) can define non-executable memory regions to thwart data-execution. However, the MPU does not enforce DEP by default on major embedded systems [54]. The configuration of the latter is left to developers, a task that is not always trivial. As a consequence, classical defenses against code injections are very limited when applied to embedded systems. It is therefore currently still easy to exploit software vulnerabilities on embedded systems using simple code injections [18, 37, 56].

#### 1.2.1.2 Code-reuse attacks

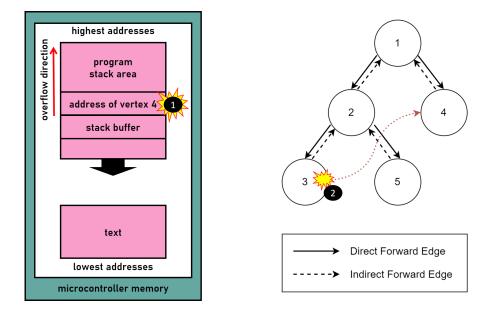

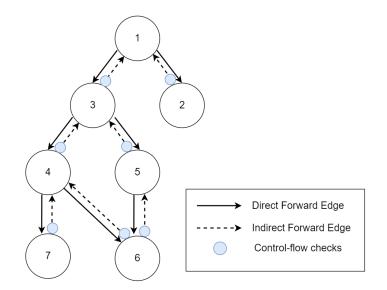

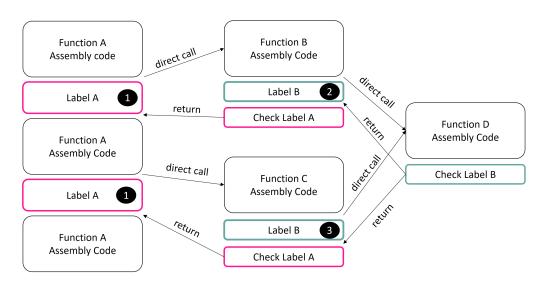

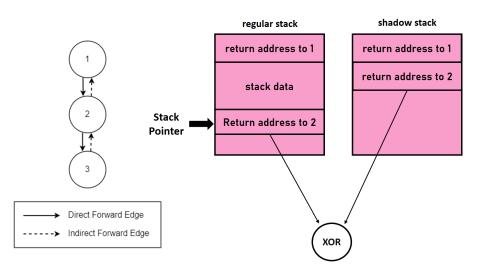

With the emergence of Data Execution Prevention (DEP), code injection attacks became less powerful. Given this, attackers rapidly demonstrated new attacks based on code-reuse to circumvent DEP. These attacks force unexpected executable control-flow paths in an application avoiding any malicious code execution in data areas. A simple code-reuse attack is displayed in Figure 1.8. The stack memory area is snapshotted in vertex 3 which suffers from a memory vulnerability.

Figure 1.8: Control-flow diversion

First, the attacker replaces the return address (previously pointing to the return location in vertex 2) of the vertex 3 by the address of the vertex 4. Hence, when vertex 3 returns, the execution-flow is redirected in vertex 4 instead of vertex 2. Such a controlflow violation attack overcome DEP. No malicious shellcode is executed in the stack. The attacker only reuses the application code already located in the executable text memory area.

An exploit technique called Return-to-Libc [57] uses the presented scheme to bypass DEP. The main purpose of the Return-to-Libc attack is to gain execution-flow and chain multiple returns on security-critical functions located in the application libraries. Of course, the purpose of these attacks is to force an application to execute malicious actions. Many "return-into" attacks such as [58] have been inspired by the Return-to-Libc scheme. However, "return-into" attacks suffer from minor limitations. Indeed, such an attack reuse functions that are part of the program or its libraries. Thus, an attacker may not find the functions he wants to execute his payload. Besides, for embedded systems that rely on a complex operating system such as Linux, the loaded shared libraries are often located in an executable area of the stack. Consequently, due to the Address Space Randomization (ASLR), the position of function libraries may change over time limiting the capabilities of exploits. Finally, bare-metal systems use statically linked libraries. It is frequent that compilers embed whole libraries without removing dead code, giving leeway to the attacker to build a working payload.

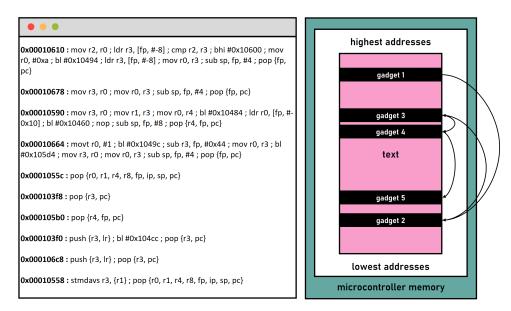

To circumvent the limitation of "ret-into" attacks, S. Krahmer introduced a new exploit technique [59] which consists of redirecting the execution flow of a program on short sequences of instructions instead of functions. Later, this innovative exploit technique is generalized by Shacham [53] into the so-called Return-Oriented Programming (ROP) attack. The main purpose of ROP attacks is to divert the execution-flow of a target application on a short sequence of instructions that end with an indirect branch. These short sequences are called "gadgets" and are located in the code of the application itself. The general idea is to make an application executing a gadget and use the branch at the end of the instruction sequence to transfer the execution-flow on another gadget. Consequently, given a large application with many instructions, an attacker may find enough gadgets to mount a Turing-complete language. By using this language, the attacker may be able to make the application successfully executes any malicious action he wants. It worth mentioning that the term Return-Oriented Programming comes from the fact that the first attacks used gadgets ending with a "ret" instruction. This instruction allows popping the top of the stack in the program counter register and transfers the control-flow to another gadget. An overview of a ROP attack is represented in Figure 1.9.

First, an attacker exploits a vulnerable buffer (stack-based in Figure 1.9). Then, the attacker injects a sequence of pointers (1), (2), (3). In Figure 1.9, this sequence first overwrites the return address of the vulnerable function (1) on other data higher up in the stack (2)(3). These pointers dereference gadgets located in the text section of the program. When the vulnerable function returns, the execution-flow of the application is redirected to the address pointed by the first gadget pointer(1). Then, when the first gadget returns, it transfers the execution to the next gadget (2) higher up in the stack using a "branch" [60, 61] or "ret" instruction. Finally, the process is repeated for (3), as well as all gadget addresses potentially injected by an attacker. In conclusion, by chaining

Figure 1.9: Return-Oriented Programming attack

gadgets into a so-called "ROPchain" an attacker can trigger any arbitrary code execution.

Although the return-oriented programming attack was initially introduced on the x86 architecture [53], the technique has been quickly extended by researchers to target many other architectures such as ARM [53], SPARC [61], Atmel [56], PowerPC [62] that are widely used in embedded systems. As a result, small Internet of Things devices based on exotic architectures are no exception to code-reuse attacks.

The major issue with code-reuse attacks and ROP, in particular, is that it overcomes the common protections against code injection attacks (ASLR, DEP, SSP). First of all, ROP is based on gadgets found in the executable text section of a program. Thus, no malicious code is executed on the stack bypassing the DEP protection. Secondly, many systems only benefit from a partial ASLR. This means that the text sections of programs are fixed from one application run to the next. As a direct consequence, the position of the gadgets in memory is fixed, allowing adversaries to deploy large scale exploits. Concerning systems that benefit from the full ASLR (randomization of the entire memory space of an application), it is often found that vulnerability is associated with a memory disclosure [42]. From this memory leak, an attacker can derandomize the vulnerable application memory layout and therefore, compute on-the-fly-all the memory addresses of the gadgets to achieve a successful attack [42]. It is worth reminding here that all embedded systems do not benefit from ASLR. Therefore, these systems are even weaker at mitigating ROP attacks. Finally, under certain conditions, A. Bittau et al. [57] demonstrated through the blind Return-Oriented Programming technique that the stack canary can be bruteforced. The blind return-oriented programming attack works particularly well against an application that handles several processes. According to [57], the crash of a process does not always cause the crash of the whole application as well as a reset of the canary value. As a result, if the vulnerable process restarts, it is, therefore, possible to replay the exploit several times and brute force the canary value byte by byte. While this technique is noisy, it demonstrates the non-infallibility of stack canaries. Of course, the protection offered by a stack canary requires the support of a TRNG/PRNG [63] which is not always acquired for embedded systems [54].

That concludes the discussion on code-reuse attacks. Of course, this section does not tackle all the advanced exploitation techniques in the literature. They would be exposed when evaluating the state-of-the-art of existing memory safety defenses.

#### 1.2.2 Data-oriented attacks

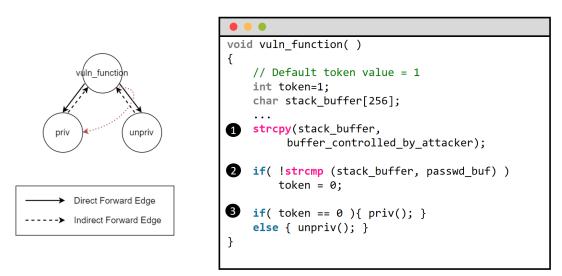

This section introduces the data-oriented programming attacks, a powerful class of attacks that exploits memory vulnerabilities to modify the behavior of an application without violating its control-flow graph. Indeed, diverting the control-flow graph is not the only way to achieve a successful attack. Usually, an attacker aims at modifying the behavior of an application to unlock security restrictions or gain more control. Consider, for instance, the code snippet with its the control-flow graph in Figure 1.10.

Figure 1.10: Data-oriented attack

There is an obvious out-of-bound vulnerability in (1). Also, the "vuln\_function" is calling both the "priv" or the "unpriv" according to the providing password. The token variable is placed in the stack memory, very closed to the vulnerable buffer. As a result, an attacker can maliciously set the token variable to zero by exploiting the spatial vulnerability in (1). Of course, in this case, the comparison in (2) may fail. However, as the token has been maliciously set to one in (1), the comparison in (3) succeeds allowing the attacker to reach the privileged function. The important point is that a successful attack can be achieved without necessarily violating the control graph. Besides, data-oriented attacks such as the one presented in Figure 1.10 are very silent. They don't induce unexpected control-flow path and they can be very effective just by modifying a couple of bytes in memory.

In their paper, S. Chen et al. [64] demonstrated that data flow attacks targeting security-critical non-control data are realistic. Through their work, they identified many

security-critical data in real-world software that can be tampered resulting in compromises equivalent to control-flow attacks. According to [64] this critical data includes configuration data, user input, user identity data, and decision making data such as in Figure 1.10. In the case of an insulin pump, the amount of medication to be delivered to a patient is critical data.

According to the previous description, it seems that the expressiveness of data-oriented attacks is more limited than control-flow attacks. However, H. Hu and al. [65] demonstrated that data flow attacks are Turing-complete. They introduced a generic exploitation method called data-oriented programming. This technique requires two elements: data-oriented gadgets and a gadget dispatcher. Data-oriented gadgets are sequences of instructions that manipulate and perform operations between registers and either load or store their results in/from the memory. These gadgets should respect the control-flow graph of the program and operate on data location controlled by an attacker thanks to a memory error. The purpose of the gadget dispatcher is to connect the data-oriented gadgets. To achieve this, the gadget dispatcher is composed of both a loop and a selector. At each loop turn, the selector is used by the attacker to select and activate gadgets that perform operations on the data. Thus by chaining several loops and activating different gadgets, [65] demonstrated that they could build a Turing complete language allowing them to perform any operation on any data in memory. According to their results, 8 out of 9 real-world programs contained data-oriented gadgets, and 2 were fully exploitable using data-oriented programming. These results demonstrate that attacks on data flow becomes increasingly practicable and empower more and more attackers.

So far, data-oriented attacks [64,66,67] are powerful enough to bypass DEP, ASLR, and SSP. Protecting systems against data flow attacks is thus a complex problem. First, dataoriented attacks do not violate the control-flow graph of an application. Consequently, it is difficult to distinguish legitimate access to resources from illegitimate ones. Then, as applications are becoming increasingly complex, the amount of critical data increases proportionally. For performance reasons, it is impractical to protect every critical data within an application. Finally, during the software development phase of a program, it is extremely difficult to determine which data is critical or not. Some data may appear noncritical, however, in the hands of an attacker, it can become devastating. According to [65] it seems that a simple loop iteration data can be reused for malicious purposes. Nowadays, most of the countermeasures against data-oriented attacks are still at the research stage and are discussed later in this thesis.

### 1.2.3 Real-world exploits

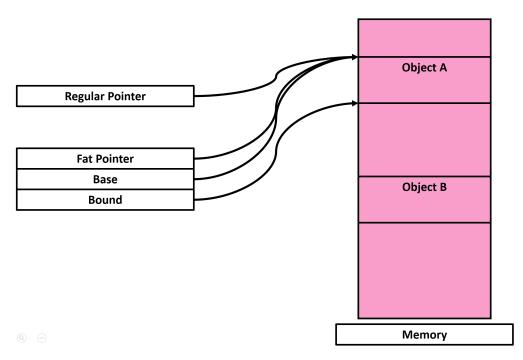

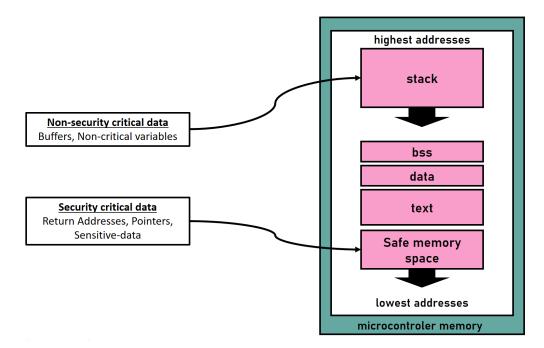

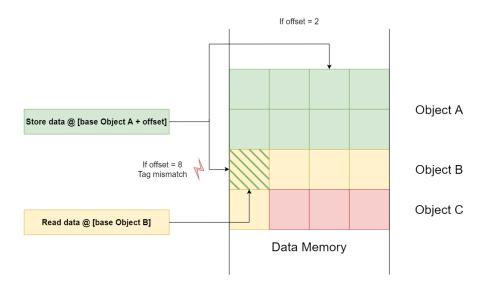

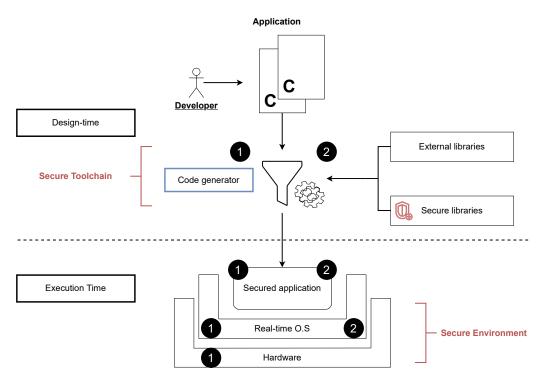

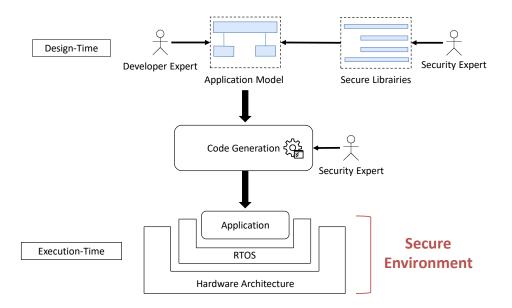

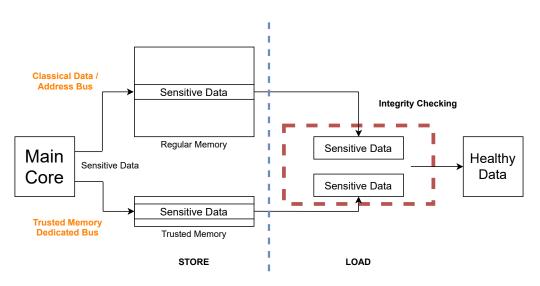

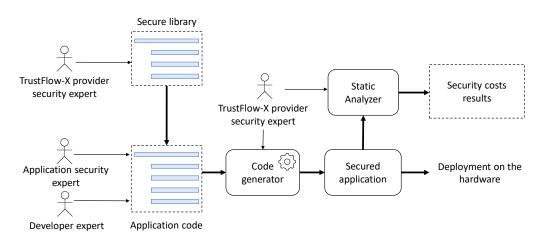

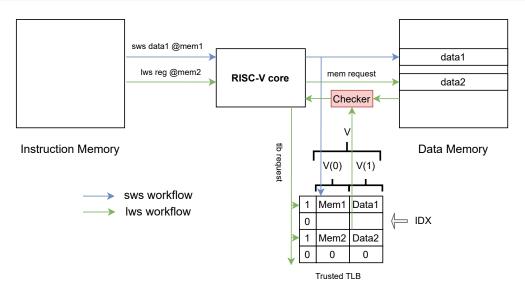

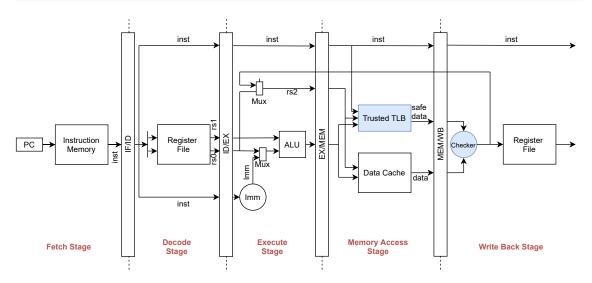

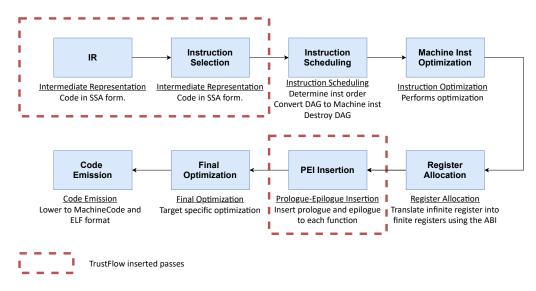

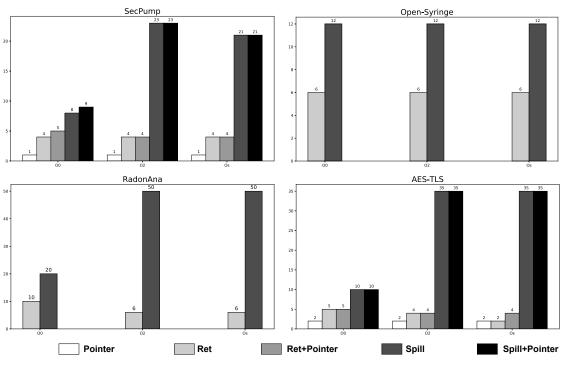

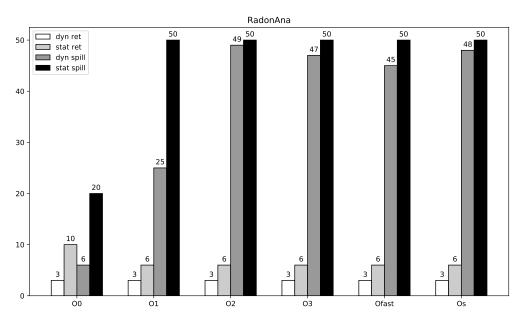

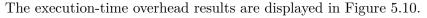

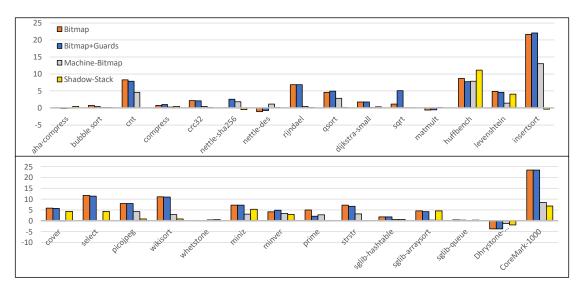

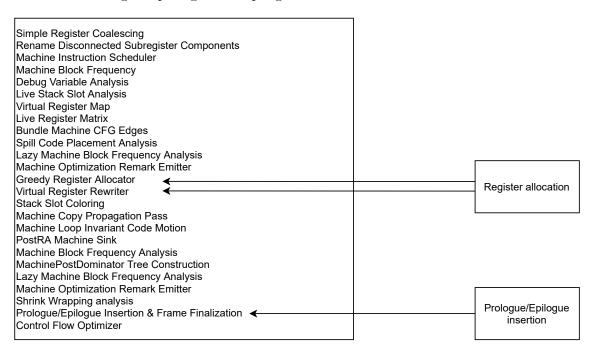

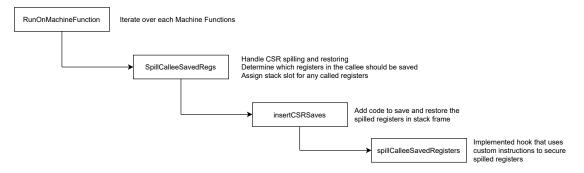

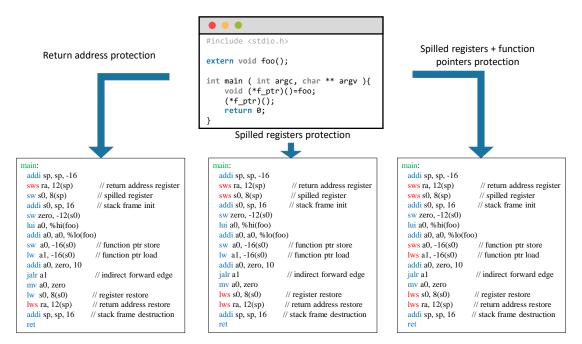

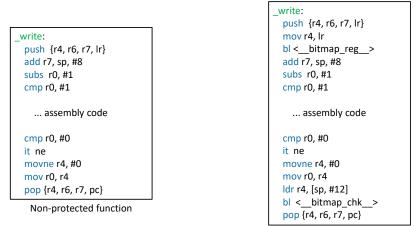

The preceding sections highlight the various techniques used by attackers to hijack a vulnerable program. While several exploit examples were given, it is not discussed whether control-flow or data-oriented attacks have already been applied to critical medical devices. Also, do these exploits exist in the wild on real applications? Which exploit technique is the most commonly used? The purpose of this section is to demonstrate that medical devices are no exception to memory vulnerabilities. Unfortunately, threats such as attacks on control-flow or security-critical data are awfully real on critical medical devices. Recent research on Smiths Medical Medfusion 4000 pumps [18] has uncovered several stack buffer overflows in the real-time operating system of the device. Such critical vulnerabilities allow an attacker to remotely take control of the pump. This research uncovered an embedded system that does not benefit from the ASLR, DEP, and SSP. As a result, a successful complete exploit is achieved with a simple code injection attack. This vulnerability also underlines what was previously exposed in section 1.1. Indeed, the root cause of the vulnerability is the use of a third-party real-time system, itself having a certain complexity and a consequent number of lines of code. It must be stressed that this example of memory corruption is only one among others. By digging on different Common Vulnerability Exposure (CVE) databases it is straightforward to find many critical vulnerabilities on medical systems [15, 17, 18]. Another important point is that the exploitation techniques explained in the previous sections are very categorical. In reality, the exploitation techniques of the attackers are hybrid. Real-world exploits combine code-reuse, code injection, and data-oriented attacks to bypass the defenses of a device. For instance, in the presence of an extremely protected system, an attacker tends to combine techniques such as codereuse, and/or data-oriented programming to first overcome the system protections such as DEP. Then, in a second time, the attacker performs a code injection attack to execute its malicious shellcode.