# Failure mechanisms implementation into SiGe HBT compact model operating close to safe operating area edges

Marine Couret

#### ▶ To cite this version:

Marine Couret. Failure mechanisms implementation into SiGe HBT compact model operating close to safe operating area edges. Electronics. Université de Bordeaux, 2020. English. NNT: 2020BORD0265. tel-03121111

### HAL Id: tel-03121111 https://theses.hal.science/tel-03121111

Submitted on 26 Jan 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE PRÉSENTÉE POUR OBTENIR LE GRADE DE

#### DOCTEUR DE L'UNIVERSITÉ DE BORDEAUX

### ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGÉNIEUR SPÉCIALITÉ ÉLECTRONIQUE

présentée et soutenue publiquement par

#### Marine COURET

le 15 décembre 2020

# FAILURE MECHANISMS IMPLEMENTATION INTO SIGE HBT COMPACT MODEL OPERATING CLOSE TO SAFE-OPERATING-AREA EDGES

Directrice de thèse : Cristell MANEUX

#### Membres du jury:

| M. ANIEL Frédéric,         | Professeur, C2N, Université Paris-Sud      | Rapporteur          |

|----------------------------|--------------------------------------------|---------------------|

| M. PASCAL Fabien,          | Professeur, IES, Université de Montpellier | Rapporteur          |

| M. CÉLI Didier,            | Ingénieur, STMicroelectronics              | Examinateur         |

| Mme DELTIMPLE Nathalie,    | MCF HDR, IMS, Bordeaux INP                 | Examinatrice        |

| M. FISCHER Gerhard,        | Ingénieur, IHP Microelectronics            | Examinateur         |

| M. MARC François,          | MCF HDR, IMS, Université de Bordeaux       | Examinateur         |

| M. BEGUERET Jean-Baptiste, | Professeur, IMS, Université de Bordeaux    | Président           |

| Mme MANEUX Cristell,       | Professeur, IMS, Université de Bordeaux    | Directrice de thèse |

|                            |                                            |                     |

Université de Bordeaux Laboratoire de l'Intégration du Matériau au Système UMR CNRS 5218, F-33400 Talence, France

### Abstract - EN

In an ever-growing terahertz market, BiCMOS technologies have reached cut-off frequencies beyond 0.5 THz. These dynamic performances are achieved thanks to the current technological improvements in SiGe hetero-junction bipolar transistors (HBTs). However, these increased performances lead to a shift of the transistors bias point closer to, or even beyond, the conventional safe-operating-area (SOA). As a consequence, several parasitic physical effects are encountered such as impact-ionization or self-heating which can potentially activate failure mechanisms, hence limiting the long-term reliability of the electronic device. In the framework of this thesis, we develop an approach for the description and the modeling of hot-carrier degradation occurring in SiGe HBTs when operating near the SOA edges. The study aims to provide an in-depth characterization of transistors operating under static and dynamic operating conditions. Based on these measurements results, a compact model for the impactionization and the self-heating has been proposed, ultimately allowing to extend the validity domain of a commercially available compact model (HiCuM). Considering the operation as close as possible to the SOA, an aging campaign was conducted to figure out the physical origin behind such failure mechanism. As a result, it has been demonstrated that hot-carrier degradation leads to the creation of trap densities at the Si/SiO<sub>2</sub> interface of the emitter-base spacer which induces an additional recombination current in the base. A compact model integrating aging laws (HiCuM-AL) was developed to predict the evolution of the transistor/circuit electrical parameters through an accelerated aging factor. For ease of use in computer-aided design (CAD) tools, the aging laws have been scaled according to the geometry and architecture of the emitter-base spacer. The model has demonstrated its robustness and its accuracy for different SiGe HBT technologies under various aging conditions. In addition, a study on the reliability of several integrated circuits has been performed leading to a precise location of the most sensitive regions to the hot-carrier degradation mechanism. Thus, the HiCuM-AL model paves the way to perform circuit simulations optimizing the mm-wave circuit design not only in terms of sheer performances but also in terms of long-term reliability.

**Keywords:** SiGe HBT - Reliability - Compact model - Hot-carriers

### Résumé - FR

Afin de répondre au marché florissant des applications térahertz, les filières BiCMOS atteignent désormais des fréquences de coupure supérieures à 0,5 THz. Ces performances dynamiques sont obtenues grâce aux améliorations technologiques apportées aux transistors bipolaires à hétérojonction (TBH) SiGe. Toutefois, cette montée en fréquence à entraîner un décalage du point de polarisation des transistors au plus proche, voir au-delà, de l'aire de sécurité de fonctionnement (SOA). En conséquence, de nombreux effets physiques parasites sont déclenchés tel que l'ionisation par impact ou bien l'auto-échauffement pouvant potentiellement activer des mécanismes de défaillance et ainsi limiter la fiabilité à long terme du transistor. Dans le cadre de cette thèse, nous proposons une approche pour la description et la modélisation de la dégradation par porteurs chauds au sein des TBH SiGe fonctionnant aux frontières de la SOA. L'étude est basée sur une caractérisation approfondie en conditions statiques et dynamiques des transistors. Du fait de ses résultats de mesures, une modélisation de l'ionisation par impact et de l'auto-échauffement a été proposé permettant d'étendre, avec précision, le domaine de validité des modèles compact commerciaux (HiCuM). Au-vu du fonctionnement aux limites de la SOA, une campagne de vieillissement a été mise en place afin de mieux cerner l'origine physique de ce mécanisme de défaillance. De ce fait, il a été démontré que la dégradation par porteurs chauds entraîne la création de densités de pièges au niveau de l'interface Si/SiO2 de l'espaceur émetteur-base induisant un courant de recombinaison supplémentaire dans la base. Un modèle compact intégrant des lois de vieillissement (HiCuM-AL) a été développé prédisant l'évolution des paramètres électriques d'un transistor ou d'un circuit au travers d'un facteur de vieillissement accéléré. Afin de facilier son utilisation dans des outils de conception assistée par ordinateur (CAO), les lois de vieillissement ont été adaptées en fonction de la géométrie et de l'archictecture de l'espaceur émetteur-base. Le modèle a démontré sa robustesse et sa précision pour plusieurs technologies de TBH SiGe et, ce, pour différentes conditions de vieillissement. De plus, une étude de la fiabilité de plusieurs architectures de circuits intégrés a été réalisé menant à une localisation précise des régions les plus sensibles au mécanisme de dégradation par porteurs chauds. Le modèle HiCuM-AL ouvre ainsi la voie à des simulations optimisées pour la conception de circuits millimétriques en termes de performances, mais aussi de fiabilité à long terme.

Mots-clés: TBH SiGe - Fiabilité - Modèle compact - Porteurs chauds

# Acknowledgments

Je souhaiterais tout d'abord remercier ma directrice de thèse, Dr Cristell Maneux, sans qui ce manuscrit n'aurait pas vu le jour. A coup de corrections roses, tu m'as donné l'envie, tout au long de cette thèse, de me surpasser et de produire un travail dont je suis fière. Merci!

Mes sincères remerciements vont au Dr François Marc et Dr Chhandak Mukherjee qui ont ardemment participé et contribué au succès de cette thèse. Au même titre, je tiens à présenter mes remerciements à Magali De Matos pour sa bienvieillance et son dynamisme. Tu as fait de la salle de caractérisation un lieu de partage et de convivialité.

A special thanks to Gerhard Fischer who was a great support from the beginning of this journey. I particularly appreciated our exchanges and your warm welcome during my visit to Frankfurt. I retain of this visit, an excellent souvenir.

Je tiens aussi à remercier les autres membres du groupe Nanoélectronique. Plus particulièrement Dr Thomas Zimmer, pour sa justesse et ses conseils. Mais également Dr Patrick Mounaix, pour nos échanges piquants, mais toujours respectueux (enfin, je crois).

Mes chaleureux remerciements au Dr Marina Deng qui m'a soutenu dans mes premiers pas dans l'enseignement. J'ai, grâce à toi, eu des opportunités que peu de doctorants ont la chance d'avoir. Merci au Dr Frédéric Darracq pour la supervision de mes enseignements à l'UF Sciences de l'Ingénieur. Je remercie aussi toute l'équipe pédagogique du CREEA qui m'a accompagné en tant qu'étudiante puis en tant qu'enseignante. Je pense notamment à Myriam, Luc, Didier, Stéphane et Xavier.

Une reconnaissance particulière au Dr Jean-Baptiste Begueret pour sa bienveillance durant ces dernières années. Je te remercie de m'avoir accompagné jusqu'à la fin de ce parcours en présidant ma soutenance de thèse.

Il ne me faut pas oublier mon collègue, mon coéquiper, mon compère d'aventure, le Dr Mathieu Jaoul. Comme tu l'as si bien écrit, nos thèses ont été étroitement liées soldant ainsi une solide amitié entre nous.

Mes pensées à ma seconde famille, mes amis, pour la plupart rencontrés tout au long de cette thèse ou lors de nos années d'étude. A toutes nos sorties, nos soirées, nos bouffes, nos escapades, nos discussions, nos rires qui ont, à jamais, gravés dans ma mémoire de merveilleux souvenirs. Pour ses moments, je me dois de remercier Matthieu, Quentin, Ming Ming, Adrien, Margaux, Djeber, Jean-Baptiste, Marco, Florent M., Florent A., Nolwenn, Romain, Isabel, Olivia, Claire et Fanny.

Comment ne pas remercier Ghyslain, passé de camarade, voisin, collègue à meilleur ami. Malgré ton absence, tu n'as jamais manqué de me soutenir et de me conseiller dans mes périodes de doutes.

Je tiens aussi à remercier mes beaux-parents d'avoir fait de leur maison, un lieu où je pouvais me ressourcer. Merci également à Sonia, Adrien et l'espiègle Pénélope pour les bons moments passés en famille.

Mes pensées vont à mes parents, pour leur affection, leur confiance et leur support, sans lesquels, tout ce travail n'aurait jamais été réalisable. Il en va de même pour mes soeurs, Virginie et Aurélie, pour qui je suis toujours une petite chipie.

Finalement, et non des moindes, j'aimerais exprimer ma reconnaissance à mon conjoint, Thomas, pour son affection, son empathie, sa patience et, surtout, son indéfectible soutien. Tel un superhéros, tu as su me préserver durant ces années et je te dois une grande partie de ma réussite.

## **Contents**

| A  | bstrac | ct - EN                                      | i    |

|----|--------|----------------------------------------------|------|

| R  | ésum   | é - FR                                       | iii  |

| A  | cknov  | wledgments                                   | v    |

| Li | st of  | Figures                                      | ix   |

| Li | st of  | Tables                                       | xvii |

| G  | enera  | l Introduction                               | 1    |

| 1  | Stat   | e-of-the-art of SiGe HBTs                    | 5    |

|    | 1.1    | Introduction                                 | 6    |

|    | 1.2    | Terahertz radiations                         | 6    |

|    | 1.3    | Technology                                   | 9    |

|    | 1.4    | Device operation                             | 14   |

|    | 1.5    | Compact modeling                             | 19   |

|    | 1.6    | Reliability issue                            | 21   |

|    | 1.7    | Technologies under analysis                  | 23   |

|    | 1.8    | Conclusion                                   | 26   |

| 2  | Con    | npact Modeling of High Biases Mechanisms     | 27   |

|    | 2.1    | Introduction                                 | 28   |

|    | 2.2    | Limitations of HiCuM compact model           | 28   |

|    | 2.3    | DC characterization of self-heating effect   | 32   |

|    | 2.4    | Compact modeling of avalanche effect         | 36   |

|    | 2.5    | AC characterization of self-heating effect   | 43   |

|    | 2.6    | Physics-based electrothermal compact model   | 49   |

|    | 2.7    | Time domain validation                       | 54   |

|    | 2.8    | Conclusion                                   | 58   |

| 3  | Phy    | sics and Modeling of Hot-Carrier Degradation | 61   |

|    | 3.1    | Introduction                                 | 62   |

|    | 3.2    | Physics of hot-carrier degradation           | 62   |

|    | 2 2    | Accelerating factors                         | 68   |

| 3.4                        | Compact modeling                                                             | 73                                                                                                                                                                                                                                                         |

|----------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.5                        | Scaled formulation                                                           | 81                                                                                                                                                                                                                                                         |

| 3.6                        | Parameter extraction                                                         | 87                                                                                                                                                                                                                                                         |

| 3.7                        | Simulation results                                                           | 91                                                                                                                                                                                                                                                         |

| 3.8                        | Conclusion                                                                   | 94                                                                                                                                                                                                                                                         |

| Hot                        | -Carrier Degradation Impact on Integrated Circuits                           | 97                                                                                                                                                                                                                                                         |

| 4.1                        | Introduction                                                                 | 98                                                                                                                                                                                                                                                         |

| 4.2                        | Current mirrors                                                              | 98                                                                                                                                                                                                                                                         |

| 4.3                        | Ring oscillator                                                              | 108                                                                                                                                                                                                                                                        |

| 4.4                        | A test vehicle: a broadband amplifier                                        | 113                                                                                                                                                                                                                                                        |

| 4.5                        | Conclusion                                                                   | 121                                                                                                                                                                                                                                                        |

| enera                      | l Conclusion                                                                 | 123                                                                                                                                                                                                                                                        |

| Author Publication List 12 |                                                                              |                                                                                                                                                                                                                                                            |

| bliog                      | raphy                                                                        | 129                                                                                                                                                                                                                                                        |

|                            | 3.5<br>3.6<br>3.7<br>3.8<br>Hot-<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>enera | 3.6 Parameter extraction 3.7 Simulation results 3.8 Conclusion  Hot-Carrier Degradation Impact on Integrated Circuits 4.1 Introduction 4.2 Current mirrors 4.3 Ring oscillator 4.4 A test vehicle: a broadband amplifier 4.5 Conclusion  eneral Conclusion |

# **List of Figures**

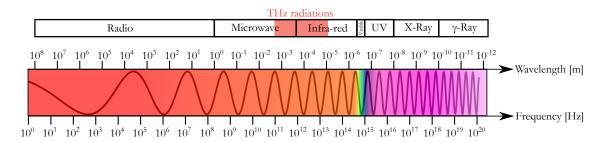

| 1.1  | Location of the terahertz radiations within the electromagnetic spectrum                                               | 6  |

|------|------------------------------------------------------------------------------------------------------------------------|----|

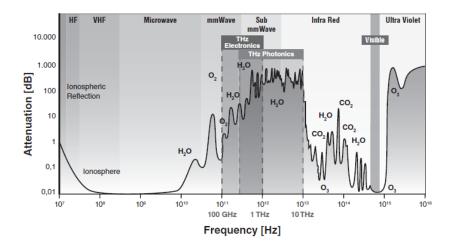

| 1.2  | Atmospheric absorption as a function of the signal frequency taken from [4]                                            | 7  |

| 1.3  | Potential applications for silicon integrated mm-wave and THz circuits taken                                           |    |

|      | from [5]                                                                                                               | 8  |

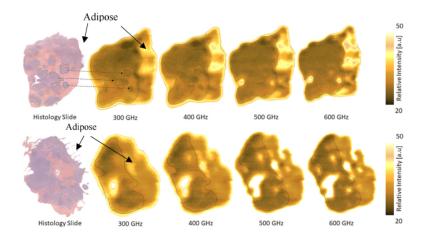

| 1.4  | Histology image and terahertz image of breast cancer taken from [20]                                                   | 9  |

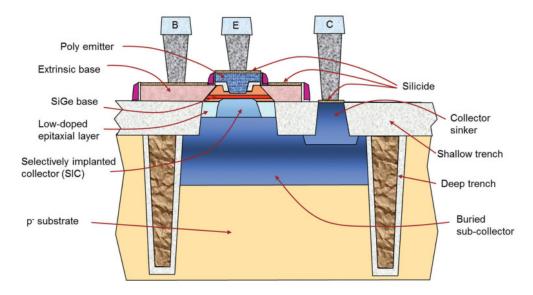

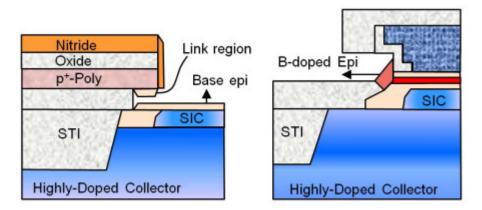

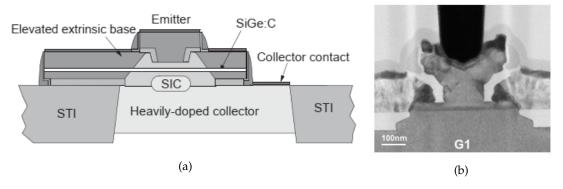

| 1.5  | Schematic cross-section of a high-speed SiGe HBT taken from [5]                                                        | 11 |

| 1.6  | Schematic flow of the selective epitaxial growth of the base link region in both                                       |    |

|      | DSPA (left) and EBL (right) processes taken from [22]                                                                  | 12 |

| 1.7  | Schematic cross section of an NSEG HBT with elevated extrinsic base (EEB) re-                                          |    |

|      | gions taken from [5]                                                                                                   | 13 |

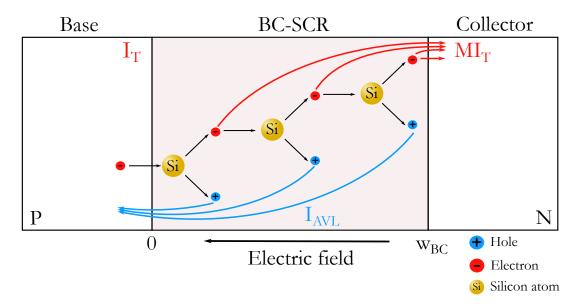

| 1.8  | Creation of electron-hole pairs within the BC-SCR due to the impact ionization                                         |    |

|      | mechanism.                                                                                                             | 14 |

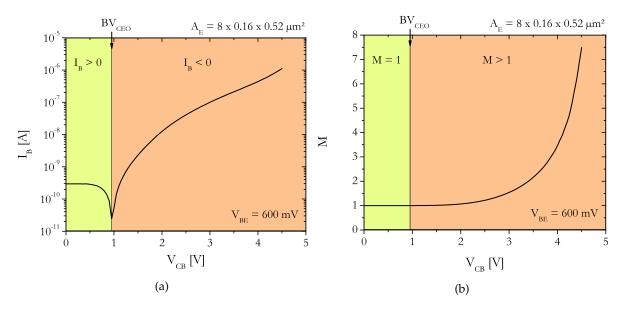

| 1.9  | (a) $I_B$ and (b) M evolution according to $V_{CB}$ highlighting the avalanche behavior.                               | 15 |

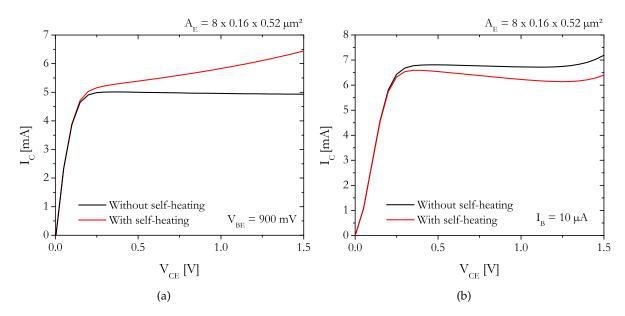

| 1.10 | Output characteristics under (a) a constant $V_{\textit{BE}}$ bias and (b) a constant $I_{\textit{B}}$ bias            |    |

|      | with and without self-heating effect                                                                                   | 16 |

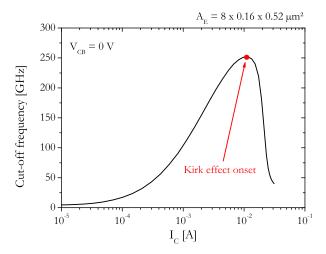

| 1.11 | Evolution of the transit frequency according to the collector current depicting                                        |    |

|      | the Kirk effect onset at high current densities                                                                        | 16 |

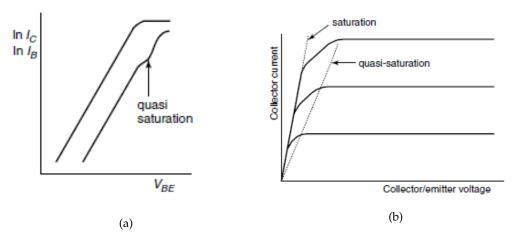

| 1.12 | (a) Forward Gummel and (b) output characteristic showing the quasi-saturation                                          |    |

|      | effect taken from [21]                                                                                                 | 17 |

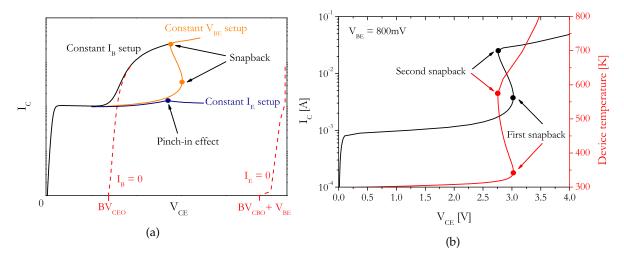

| 1.13 | (a) Influence of the measurements configurations on a HBT output characteristic                                        |    |

|      | and (b) Device junction temperature for a constant $V_{\textit{BE}}$ setup                                             | 18 |

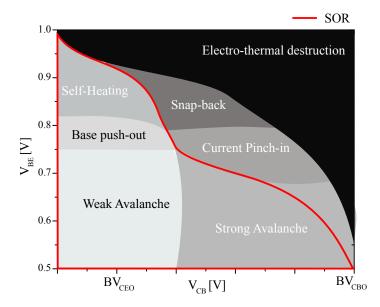

| 1.14 | Stable Operation Regime for a constant $V_{\textit{BE}}$ setup on a high-speed SiGe HBT                                | 19 |

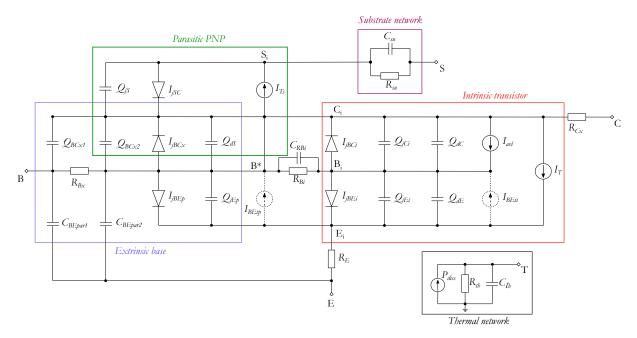

| 1.15 | Equivalent electrical circuit of HiCuM/L2 including the electro-thermal node.                                          |    |

|      | Not shown are the networks for NQS effects and correlated noise                                                        | 21 |

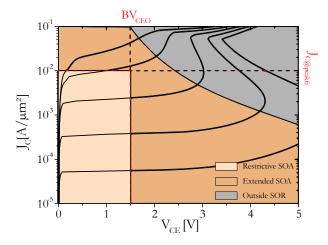

| 1.16 | Safe Operating Area boundaries for a constant $V_{\textit{BE}}$ setup on a high-speed SiGe                             |    |

|      | HBT                                                                                                                    | 22 |

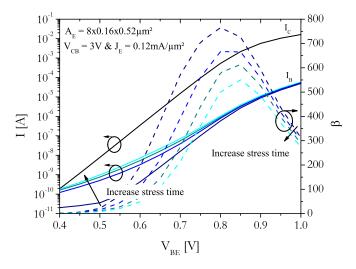

| 1.17 | Base current and current gain $\beta$ as a function of $V_{BE}$ for a mixed-mode stress of                             |    |

|      | $V_{CB}$ =3V and $J_E$ =0.12mA/ $\mu$ m <sup>2</sup> on a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> device corresponding to |    |

|      | SG13S technology from IHP Microelectronics                                                                             | 22 |

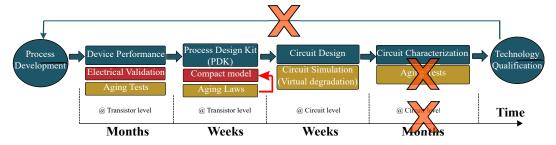

| 1.18 | Methodology for circuit reliability prediction                                                                         | 23 |

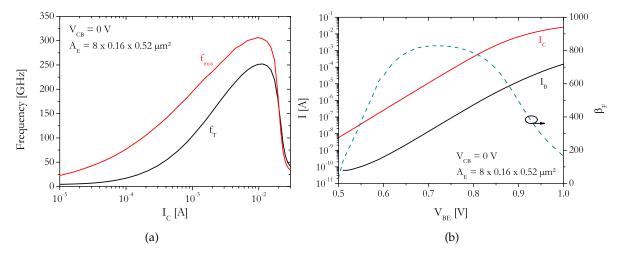

| 1.19 | (a) $f_t$ and $f_{max}$ as a function of the collector current and (b) Gummel character-                               |    |

|      | istics for a high-speed transistor corresponding to SG13S technology from IHP                                          |    |

|      | Microelectronics                                                                                                       | 24 |

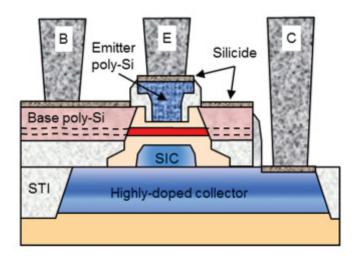

| 1.20 | (a) Schematic [64] and (b) TEM cross-section [62] for a high-speed transistor from SG13S technology                                                                                                                                                                                                                                                                          | 24         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

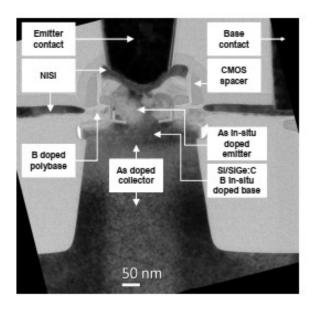

| 1.21 | TEM cross-section of a 0.1 x 4.9 $\mu$ m <sup>2</sup> HS SiGe HBT from B55 technology [23]                                                                                                                                                                                                                                                                                   | 25         |

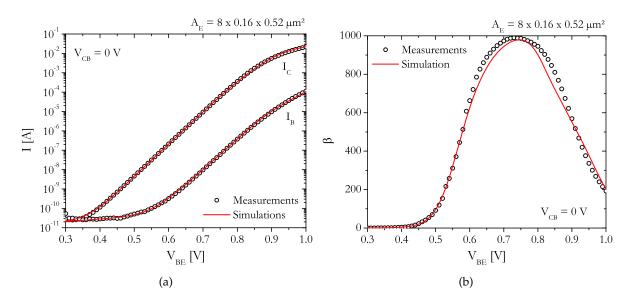

| 2.1  | Comparison between measurements (symbols) and HiCuM/L2 simulation v2.34 (solid lines) for (a) the forward Gummel characteristic and (b) the current gain at $V_{CB} = 0$ V on a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> device corresponding to SG13S technology from IHP Microelectronics                                                                                      | 28         |

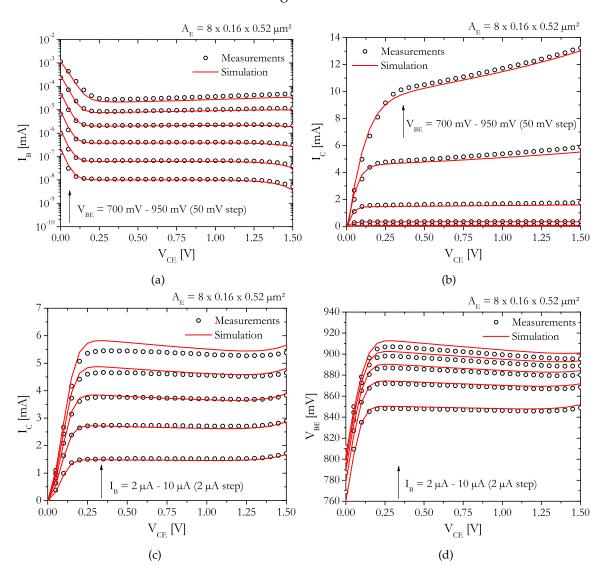

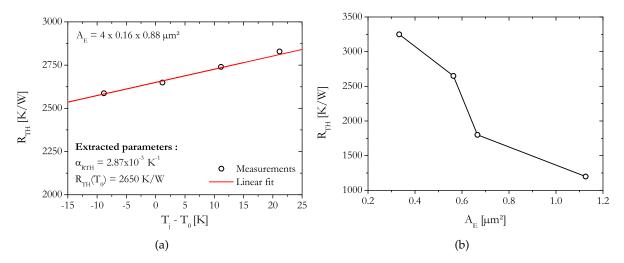

| 2.2  | Comparison between measurements (symbols) and HiCuM/L2 v2.34 simulation (solid lines) for (a) $I_B$ and (b) $I_C$ as function of $V_{CE}$ under constant $V_{BE}$ 's bias and for (c) $I_C$ and (d) $V_B$ as function of $V_{CE}$ under constant $I_B$ 's bias on a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> device corresponding to SG13S technology from IHP Microelectronics. | 29         |

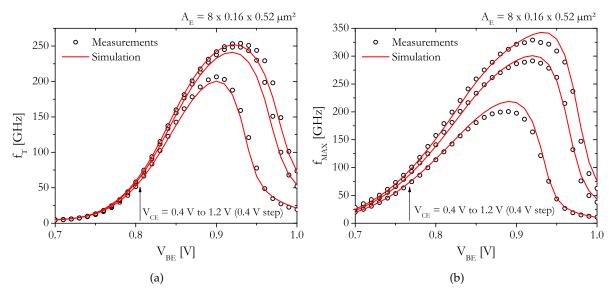

| 2.3  | Comparison between measurements (symbols) and HiCuM/L2 simulation (solid lines) for (a) $f_T$ and (b) $f_{MAX}$ as function of $V_{BE}$ at various $V_{CE}$ 's bias on a 8 x 0.16                                                                                                                                                                                            | <b>4</b> 9 |

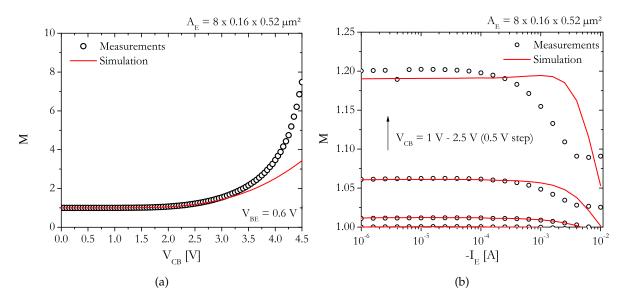

| 2.4  | $\times$ 0.52 $\mu m^2$ device corresponding to SG13S technology from IHP Microelectronics. Comparison between measurements (symbols) and HiCuM/L2 simulation v2.34 (solid lines) for the multiplication factor, M, at (a) various $V_{CB}$ under a constant                                                                                                                 | 30         |

| 2.5  | $V_{BE}$ and (b) various $I_E$ under constant $V_{CB}$ 's on a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> device corresponding to SG13S technology from IHP Microelectronics                                                                                                                                                                                                       | 31         |

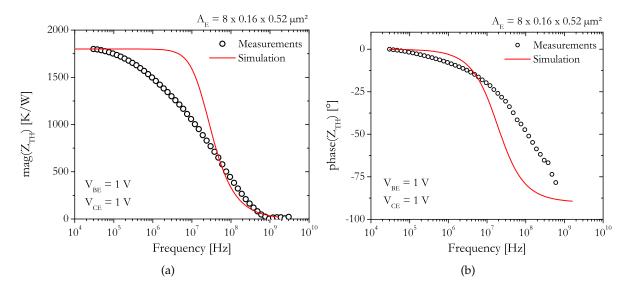

|      | (solid lines) for the thermal impedance (a) magnitude and (b) phase evolution according to the frequency on a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> device corresponding to                                                                                                                                                                                                   | 22         |

| 2.6  | SG13S technology from IHP Microelectronics                                                                                                                                                                                                                                                                                                                                   | 32         |

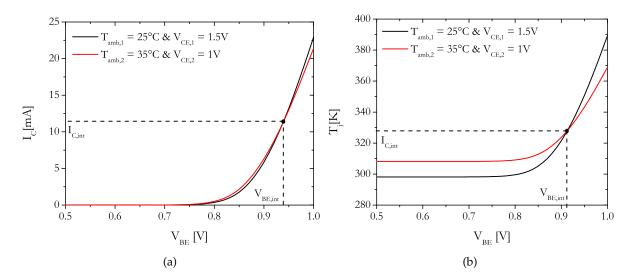

| 2.7  | $\mu$ m <sup>2</sup> device corresponding to SG13S technology from IHP Microelectronics Thermal resistance evolution according to (a) the device temperature and (b) the emitter area for SG13S technology from IHP Microelectronics. The extraction is                                                                                                                      | 33         |

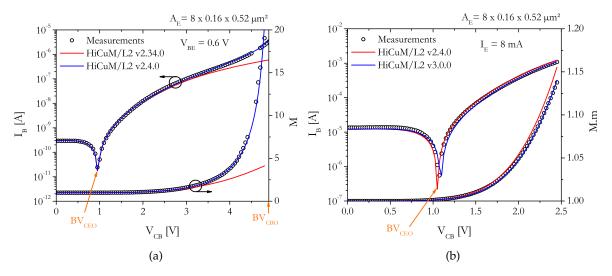

| 2.8  | performed based on the intersection technique                                                                                                                                                                                                                                                                                                                                | 35         |

|      | results (solid lines) of (a) HiCuM/L2 v2.34 (in red) and v2.4.0 (in blue) at $V_{BE}$ = 0.6 V and (b) HiCuM/L2 v2.4.0 (in red) and v3.0.0 (in blue) at $I_E$ = 8 mA for                                                                                                                                                                                                      |            |

|      | the base current and the multiplication factor on a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> device corresponding to SG13S technology from IHP Microelectronics                                                                                                                                                                                                                  | 38         |

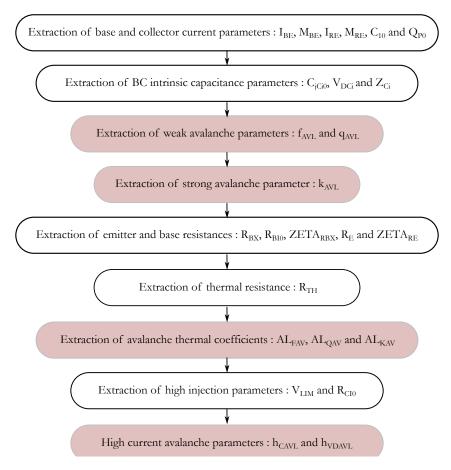

| 2.9  | Extraction flow the avalanche related parameters reproduced from [31]                                                                                                                                                                                                                                                                                                        | 39         |

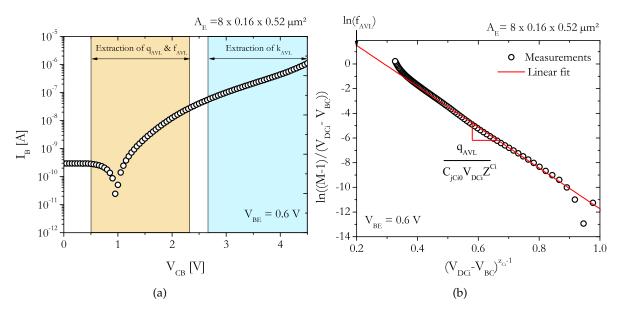

|      | Illustration of the extraction (a) range and (b) methodology for the weak avalanche parameters ( $f_{AVL}$ and $q_{AVL}$ ) on a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> device corresponding to                                                                                                                                                                                 |            |

|      | SG13S technology from IHP Microelectronics                                                                                                                                                                                                                                                                                                                                   | 40         |

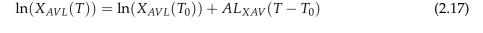

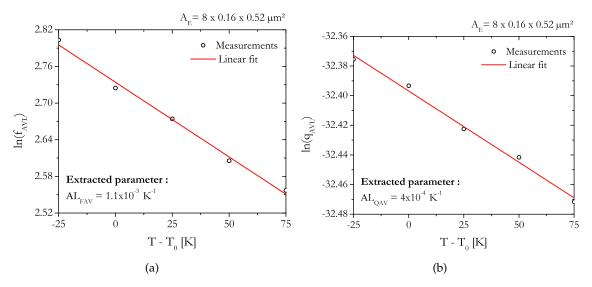

| 2.11 | Thermal coefficient extraction for (a) $f_{AVL}$ and (b) $q_{AVL}$ parameters for a 8 x 0.16                                                                                                                                                                                                                                                                                 |            |

|      | $\times$ 0.52 $\mu$ m <sup>2</sup> device corresponding to SG13S technology from IHP Microelectronics.                                                                                                                                                                                                                                                                       | 40         |

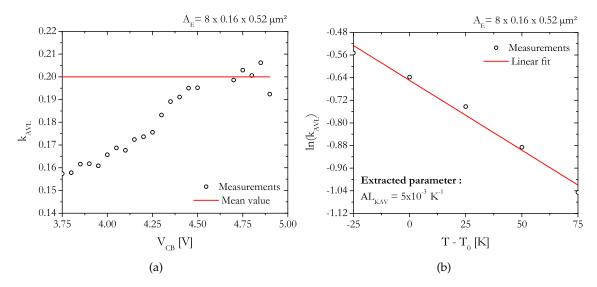

| 2.12 | (a) $k_{AVL}$ extraction result and (b) associated thermal coefficient for a 8 x 0.16 x                                                                                                                                                                                                                                                                                      |            |

|      | $0.52 \ \mu\text{m}^2$ device corresponding to SG13S technology from IHP Microelectronics.                                                                                                                                                                                                                                                                                   | 41         |

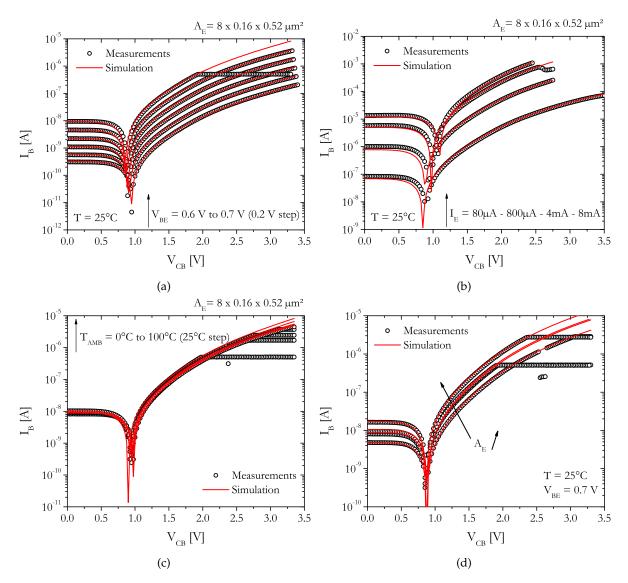

| 2.13        | Compact model simulations results (solid lines) vs measurements (symbols) for                                                                                                       |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | $I_B$ evolution according to $V_{CB}$ at (a) various $V_{BE}$ values, (b) various $I_E$ values,                                                                                     |    |

|             | (c) various $T_{AMB}$ and (d) various emitter dimensions corresponding to SG13S                                                                                                     |    |

|             | technology from IHP Microelectronics. A current compliance is used to avoid                                                                                                         |    |

|             | the transistor destruction                                                                                                                                                          | 42 |

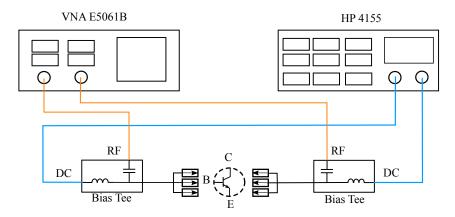

| 2.14        | Low-frequency S-parameters measurement bench                                                                                                                                        | 46 |

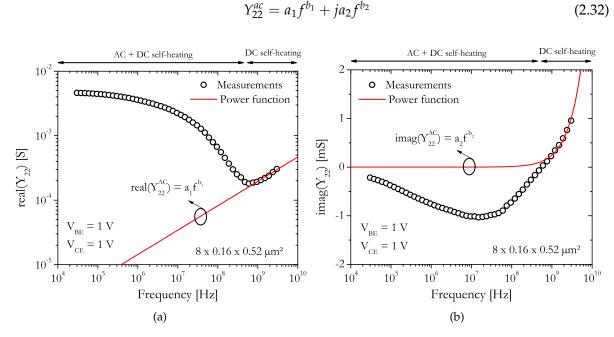

| 2.15        | (a) Real and (b) imaginary part of $Y_{22}$ with the corresponding extrapolation to extract the isothermal values using a power function for a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> |    |

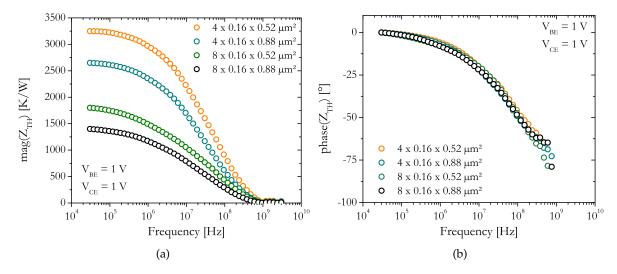

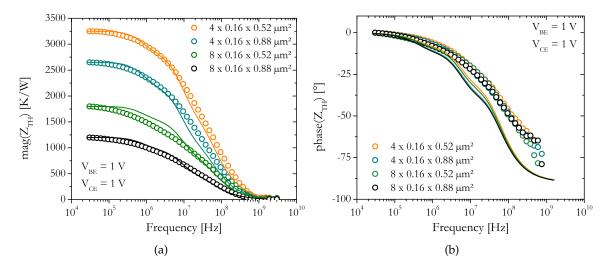

| 2 16        | device corresponding to SG13S technology from IHP Microelectronics Extraction results for (a) the magnitude and (b) the phase of $Z_{TH}$ for different                             | 46 |

| 2.10        | emitter geometries corresponding to SG13S technology from IHP Microelectronics.                                                                                                     | 17 |

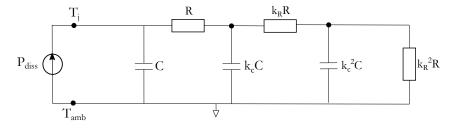

| 7 17        | Electrical equivalent circuit of the recursive electrothermal network                                                                                                               | 47 |

|             | Comparison between measurements (symbols) and recursive network simula-                                                                                                             | 4/ |

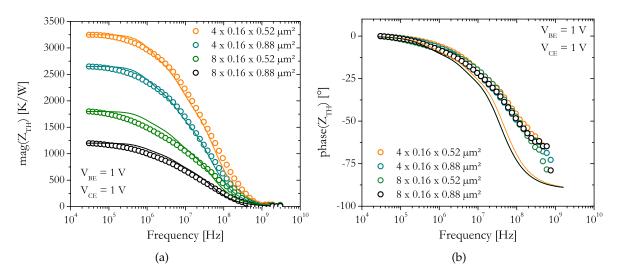

| 2.10        |                                                                                                                                                                                     |    |

|             | tion (solid lines) for (a) the magnitude and (b) the phase of $Z_{TH}$ for different                                                                                                |    |

|             | emitter geometries corresponding to SG13S technology from IHP Microelectron-                                                                                                        | 10 |

| <b>3</b> 10 |                                                                                                                                                                                     | 48 |

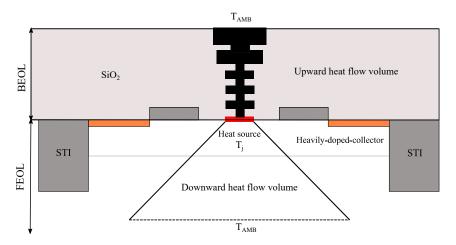

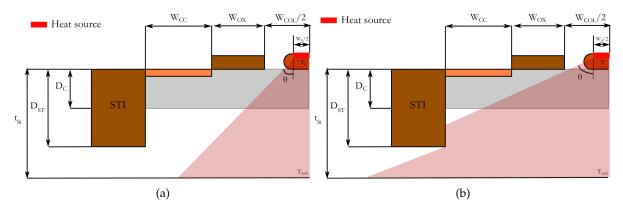

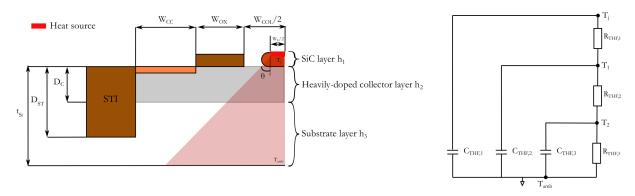

| 2.19        | Illustration of the heat flow volume in a SiGe HBT architecture considering the                                                                                                     |    |

|             | BEOL metal layers. Note that the heat source is assumed to be located at the                                                                                                        |    |

|             | base-collector junction and the contributions from the emitter and the neutral                                                                                                      |    |

|             | base are neglected.                                                                                                                                                                 | 49 |

| 2.20        | Downward heat diffusion for (a) $\theta < \theta_C$ and (b) $\theta > \theta_C$ corresponding to a half                                                                             |    |

|             | cross-section corresponding to SG13S technology from IHP Microelectronics                                                                                                           | 50 |

| 2.21        | Electrical equivalent circuit of the downward heat flow for a SG13S technology                                                                                                      |    |

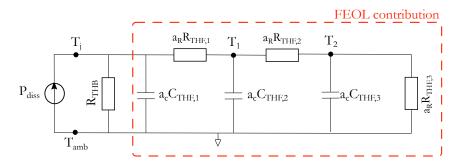

|             | from IHP Microelectronics                                                                                                                                                           | 52 |

|             | Electrical equivalent circuit of the physics-based electrothermal network                                                                                                           | 53 |

| 2.23        | Comparison between measurements (symbols) and physics-based electrother-                                                                                                            |    |

|             | mal model simulation (solid lines) for (a) the magnitude and (b) the phase of                                                                                                       |    |

|             | $Z_{TH}$ for different emitter geometries corresponding to SG13S technology from                                                                                                    |    |

|             | IHP Microelectronics                                                                                                                                                                | 54 |

| 2.24        | Comparison between measurements (symbols) and physics-based electrother-                                                                                                            |    |

|             | mal model simulation (solid lines) for $Y_{12}$ (a) magnitude and (b) phase, on a 8 $\times$                                                                                        |    |

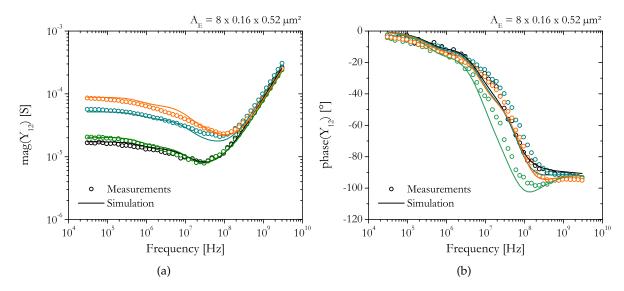

|             | $0.16 \times 0.52 \ \mu\text{m}^2$ corresponding to SG13S technology from IHP Microelectronics                                                                                      | 55 |

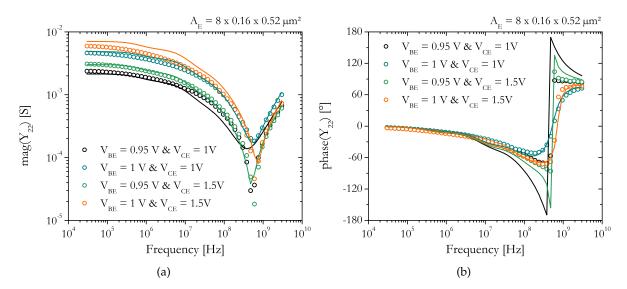

| 2.25        | Comparison between measurements (symbols) and physics-based electrother-                                                                                                            |    |

|             | mal model simulation (solid lines) for $Y_{22}$ (a) magnitude and (b) phase, on a 8 x                                                                                               |    |

|             | $0.16 \times 0.52 \; \mu\text{m}^2$ corresponding to SG13S technology from IHP Microelectronics.                                                                                    | 55 |

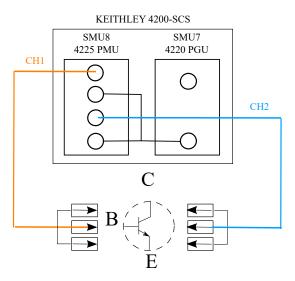

| 2.26        | Experimental setup for pulse measurements                                                                                                                                           | 56 |

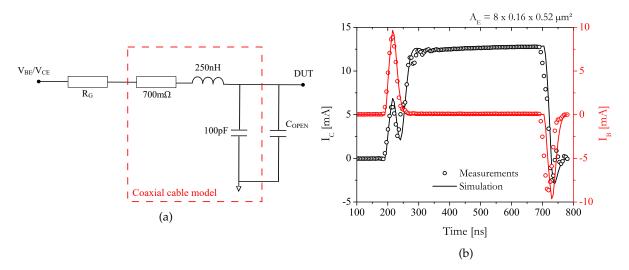

| 2.27        | (a) Equivalent circuit model of the coaxial cables consisting of passive elements,                                                                                                  |    |

|             | the generator resistance $R_G$ and device open capacitance $C_{\mathit{OPEN}}$ and (b) Compact                                                                                      |    |

|             | model simulation results on the base and collector current using the coaxial cable                                                                                                  |    |

|             | model at $V_{BE}$ = 0.95 V and $V_{CE}$ = 1.5 V                                                                                                                                     | 56 |

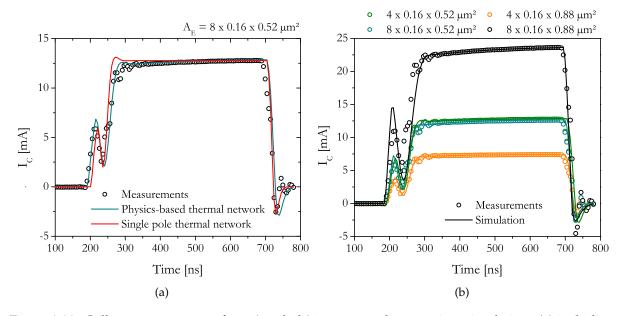

| Collector current waveform (symbols) is compared to transient simulations (a) including the single pole (solid red lines) and the physics-based (solid blue lines) thermal model for a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> device and (b) including the physics-based (solid lines) thermal model for the four DUTs geometries corresponding to SG13S technology from IHP Microelectronics. Both figures are obtained at an operating condition of $V_{BE} = 0.95$ V and $V_{CE} = 1.5$ V | 57                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

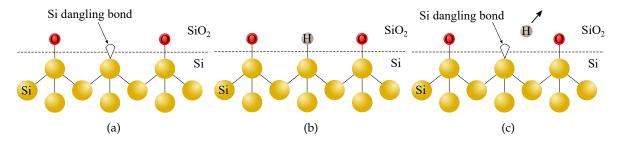

| (a) Si dangling bond creation at the Si/SiO <sub>2</sub> interface, (b) Incorporation of hydrogen atoms for passivation of dangling bonds and (c) Interface trap carrier                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                  |

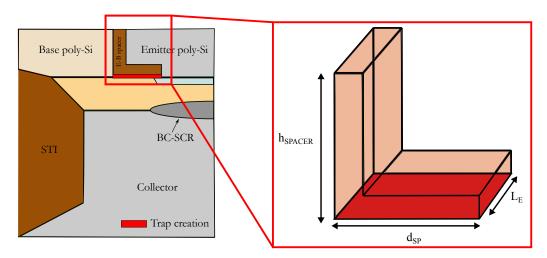

| Schematic cross section of a SiGe HBT showing the Si/SiO <sub>2</sub> interfaces likely sub-                                                                                                                                                                                                                                                                                                                                                                                               | 62                                                                                                                                                                                                                                                                                                                                                                                               |

| mitted to HCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63                                                                                                                                                                                                                                                                                                                                                                                               |

| sponding to B55 technology from ST Microelectronics                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64                                                                                                                                                                                                                                                                                                                                                                                               |

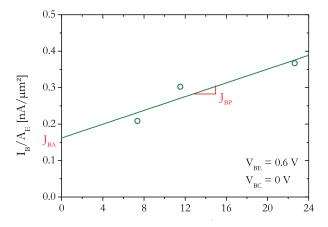

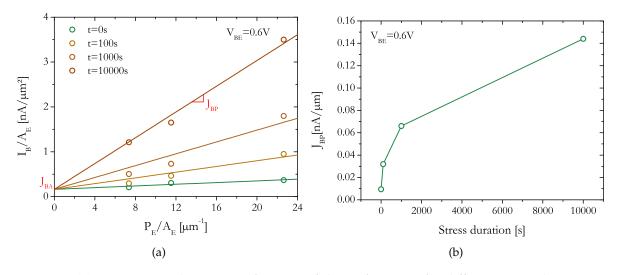

| (a) Base current density as a function of the $P_E/A_E$ ratio for different stress duration extracted at $V_{BE} = 0.6 \text{ V}$ and (b) Peripheral contribution of the base current                                                                                                                                                                                                                                                                                                      | 65                                                                                                                                                                                                                                                                                                                                                                                               |

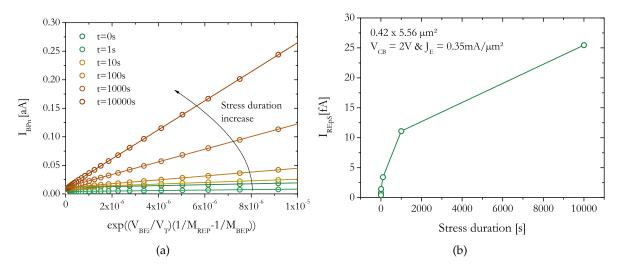

| = 0.6 V corresponding to B55 technology from ST Microelectronics (a) Normalized peripheral part of the base current, $I_{BPn}$ , extracted from the measurements in figure 3.3a for various stress duration and (b) $I_{REpS}$ evolution extracted from figure 3.6a with increasing mixed-mode stress time ( $V_{CB} = 2 V$ and                                                                                                                                                            | 65                                                                                                                                                                                                                                                                                                                                                                                               |

| from ST Microelectronics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66                                                                                                                                                                                                                                                                                                                                                                                               |

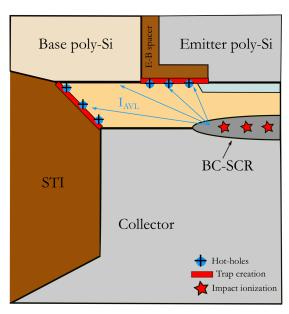

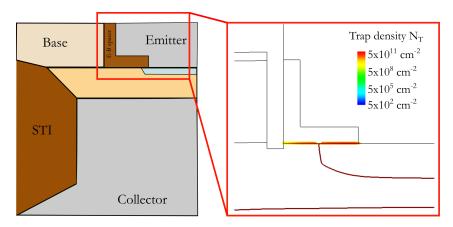

| on the E-B spacer oxide where traps have been added at the $\mathrm{Si}/\mathrm{SiO}_2$ interface                                                                                                                                                                                                                                                                                                                                                                                          | 67                                                                                                                                                                                                                                                                                                                                                                                               |

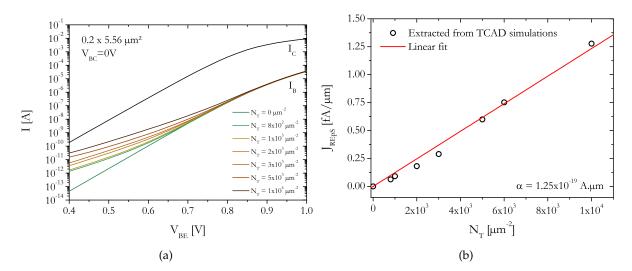

| (a) TCAD simulation results for various trap densities and (b) corresponding $J_{REpS}$ evolution allowing to extract the proportionality coefficient $\alpha$ representative of the relationship between the density of defects at the interface and the base recombination current density value on a B55 technology from ST Micro-                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                  |

| electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68                                                                                                                                                                                                                                                                                                                                                                                               |

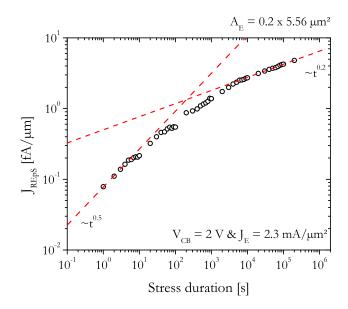

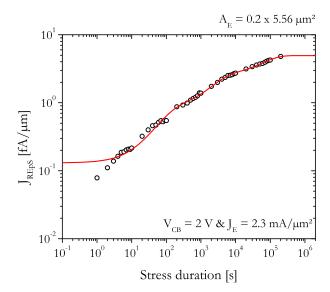

| Time-exponent evolution of $J_{REpS}$ parameter for a mixed-mode stress of $V_{CB}$ = 2 $V$ and $J_E$ = 2.3 mA/ $\mu$ m <sup>2</sup> on a 0.2 x 5.56 $\mu$ m <sup>2</sup> device corresponding to B55 technol-                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                  |

| ogy from ST Microelectronics                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69                                                                                                                                                                                                                                                                                                                                                                                               |

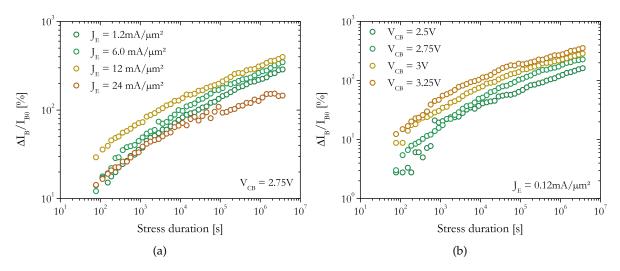

| 2.75 V and various $J_E$ and (b) $J_E$ = 0.12 mA/ $\mu$ m² and various $V_{CB}$ on a 8 x 0.16 x 0.52 $\mu$ m² device corresponding to SG13S technology from IHP Microelectronics                                                                                                                                                                                                                                                                                                           | 70                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | including the single pole (solid red lines) and the physics-based (solid blue lines) thermal model for a 8 × 0.16 × 0.52 $\mu$ m² device and (b) including the physics-based (solid lines) thermal model for the four DUTs geometries corresponding to SG135 technology from IHP Microelectronics. Both figures are obtained at an operating condition of $V_{BE} = 0.95$ V and $V_{CE} = 1.5$ V |

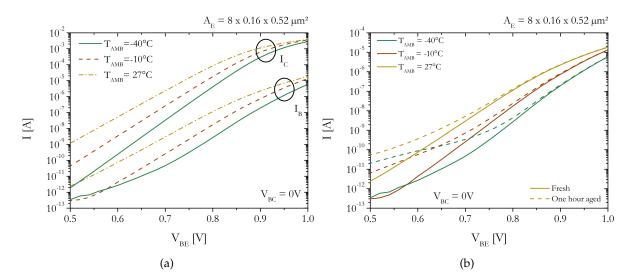

| 3.11         | Gummel characteristics (a) without any aging procedure and (b) after one hour of mixed-mode stress ( $V_{CB} = 3 \text{ V}$ and $I_E = 180 \mu\text{A}$ ) at different ambient temperatures (-40°C;-10°C and 27°C) on a 8 x 0.16 x 0.52 $\mu\text{m}^2$ device corresponding to |     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | SG13S technology from IHP Microelectronics                                                                                                                                                                                                                                      | 71  |

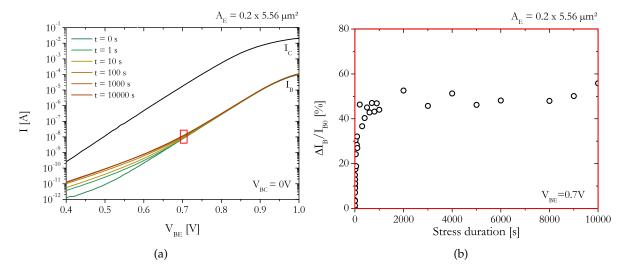

| 3.12         | (a) Gummel characteristic and (b) relative base current evolution for a mixed-                                                                                                                                                                                                  |     |

|              | mode stress ( $V_{CB} = 2.7 \text{ V}$ and $I_E = 20 \text{ mA}$ ) at high junction temperature ( $T_i =$                                                                                                                                                                       |     |

|              | 315°C) applied on a 0.2 x 5.56 μm² device corresponding to B55 technology from                                                                                                                                                                                                  |     |

|              | ST Microelectronics                                                                                                                                                                                                                                                             | 71  |

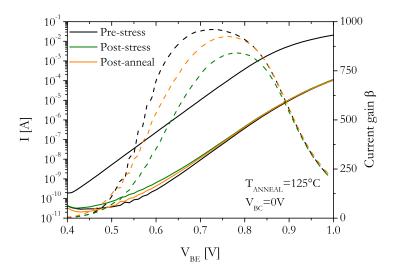

| 3.13         | Gummel characteristics before/after an annealing treatment at 125°C on a former aged transistor corresponding to SG13S technology from IHP Microelec-                                                                                                                           |     |

|              | tronics                                                                                                                                                                                                                                                                         | 72  |

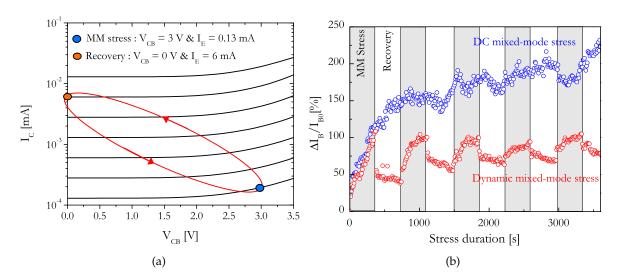

| 3.14         | (a) Bias conditions for dynamic mixed-mode stress and (b) relative base current                                                                                                                                                                                                 |     |

|              | evolution for this particular stress mode compared to a DC mixed-mode stress                                                                                                                                                                                                    |     |

|              | on a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> device corresponding to SG13S technology from IHP                                                                                                                                                                                     |     |

|              | Microelectronics                                                                                                                                                                                                                                                                | 73  |

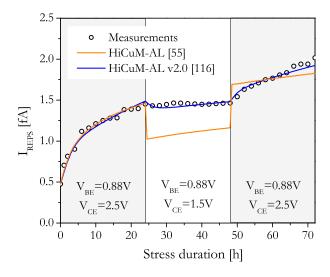

| 3.15         | Comparison between measurements (symbols) and simulations (solid line) of                                                                                                                                                                                                       |     |

|              | the aging model proposed in [54] for a dynamic stress on a 8 x $0.16$ x $0.52$ $\mu m^2$                                                                                                                                                                                        |     |

|              | device corresponding to SG13S technology from IHP Microelectronics                                                                                                                                                                                                              | 74  |

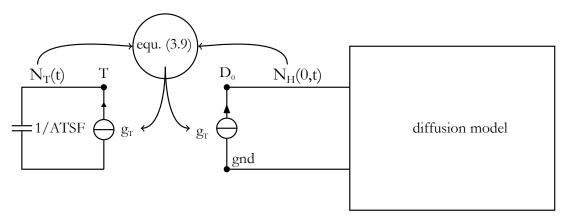

|              | Implementation schematic of the reaction-diffusion model                                                                                                                                                                                                                        | 75  |

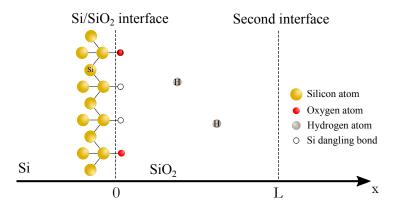

| 3.17         | Schematic of the hydrogen diffusion considering the creation of traps at the                                                                                                                                                                                                    |     |

|              | Si/SiO <sub>2</sub> interface                                                                                                                                                                                                                                                   | 76  |

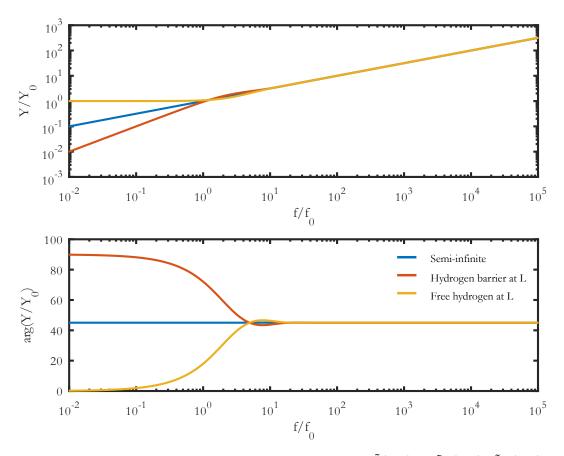

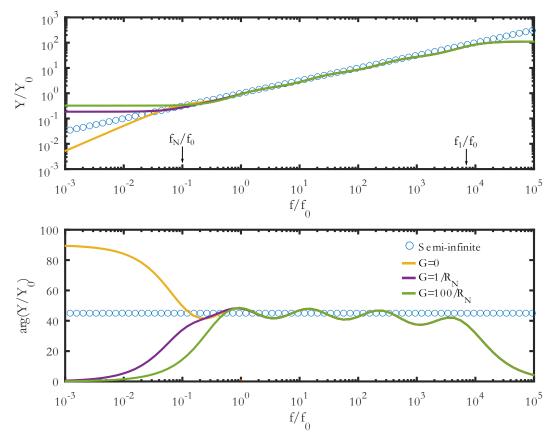

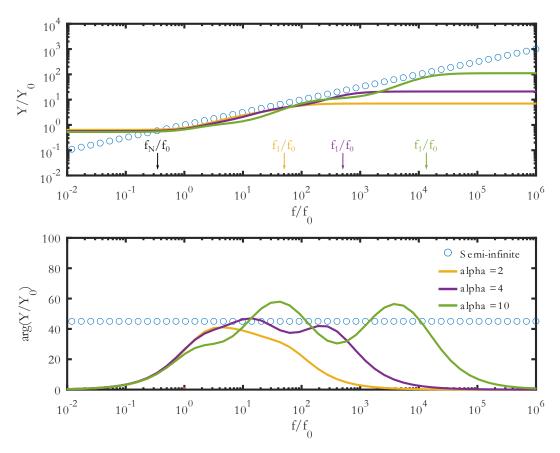

| 3.18         | Bode-like representation of normalized admittance $\tilde{Y}(0,f) = \tilde{\phi}_H(0,f)/\tilde{N}_H(0,f)$                                                                                                                                                                       |     |

|              | of diffusion for the three cases of second interface properties                                                                                                                                                                                                                 | 78  |

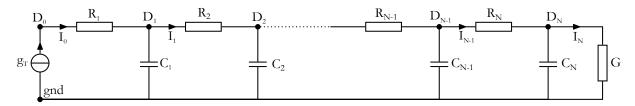

|              | Architecture of the R-C ladder model of diffusion equation system                                                                                                                                                                                                               | 78  |

| 3.20         | Bode-like representation of normalized admittance $\tilde{Y}(0,f) = \tilde{\phi}_H(0,f)/\tilde{N}_H(0,f)$                                                                                                                                                                       |     |

|              | of the R-C ladder model for $\alpha_R$ =4 and N=5 compared to the semi-infinite theory.                                                                                                                                                                                         | 80  |

| 3.21         | Comparison between measurements (symbols) and simulations (solid line) of                                                                                                                                                                                                       |     |

|              | the previous [54] and newly proposed [115] aging compact model for a dynamic                                                                                                                                                                                                    |     |

|              | stress on a 8 x $0.16$ x $0.52$ $\mu$ m <sup>2</sup> device corresponding to SG13S technology from                                                                                                                                                                              | 0.4 |

| 2 22         | IHP Microelectronics                                                                                                                                                                                                                                                            | 81  |

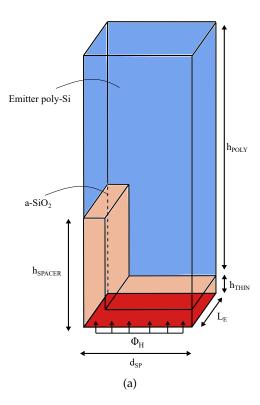

| 3.22         | Side view of the E-B spacer corresponding to B55 technology transistor architec-                                                                                                                                                                                                | 00  |

| 2.22         | ture from ST Microelectronics                                                                                                                                                                                                                                                   | 82  |

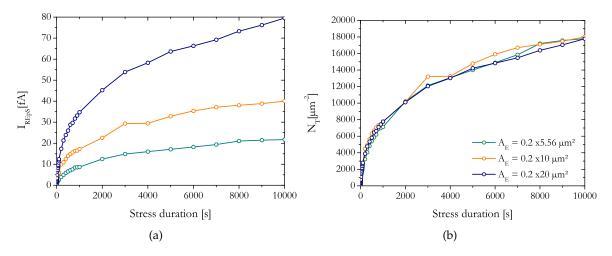

| 3.23         | (a) Extracted $I_{REpS}$ parameter and (b) Calculated $N_T$ following equation (3.8)                                                                                                                                                                                            |     |

|              | from Gummel measurements for a stress condition of $V_{CB} = 2.4 \text{ V}$ and $J_E = 231$                                                                                                                                                                                     | വ   |

| 2 24         | $\mu$ A/ $\mu$ m <sup>2</sup> and for three B55 technology devices from ST Microelectronics                                                                                                                                                                                     | 83  |

| 3.24         | Schematic of the hydrogen diffusion volume taking into account the E-B spacer                                                                                                                                                                                                   |     |

|              | oxide and the emitter poly-Si thickness for B55 technology from ST Microelectronics                                                                                                                                                                                             | Q A |

| 2 75         | tronics                                                                                                                                                                                                                                                                         | 84  |

| <b>3.</b> ∠3 | R-C ladder network for hydrogen diffusion modeling                                                                                                                                                                                                                              | 85  |

| 3.26 | Bode-like representation of normalized admittance $Y(0, f) = \phi_H(0, f)/N_H(0, f)$ of the R-C ladder model for N = 3, G = 1/R <sub>N</sub> and various recursive factors $\alpha$                                                                                                                                                                                            | 0.0 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.27 | Evolution of $J_{REpS}$ for a static condition of $V_{CB} = 2 \text{ V}$ and $J_E = 2.3 \text{ mA/µm}^2$ on a $0.2 \times 5.56 \text{ µm}^2$ device corresponding to B55 technology from ST Microelectronics. The data were fitted with a three poles exponential decay function to extract the                                                                                | 86  |

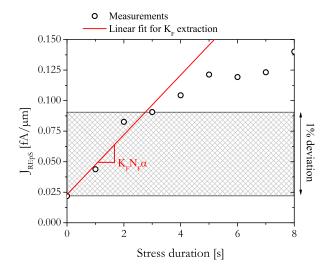

| 3.28 | $K_F$ extraction example for a static stress condition of $V_{CB}=2$ V and $J_E=4.6$ mA/ $\mu$ m <sup>2</sup> on a 0.2 x 5.56 $\mu$ m <sup>2</sup> corresponding to B55 technology from ST Micro-                                                                                                                                                                              | 87  |

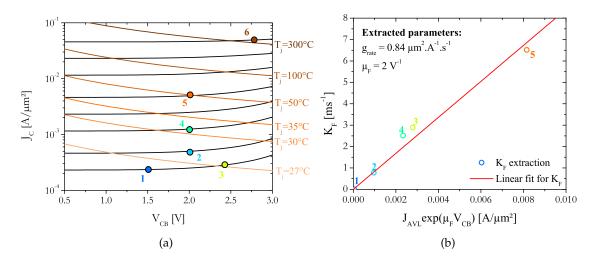

| 3.29 | (a) $J_C$ - $V_{CB}$ curves illustrating the stress conditions for $K_F$ extraction and (b) $K_F$ extraction results with corresponding linear fit leading to equation (3.38) for five stress conditions (see figure 3.29a) on a 0.2 x 5.56 $\mu$ m <sup>2</sup> corresponding to B55                                                                                          | 89  |

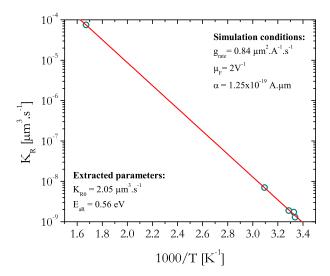

| 3.30 | $K_R$ extraction results for a 0.2 x 5.56 $\mu$ m <sup>2</sup> device corresponding to B55 technology                                                                                                                                                                                                                                                                          | 90  |

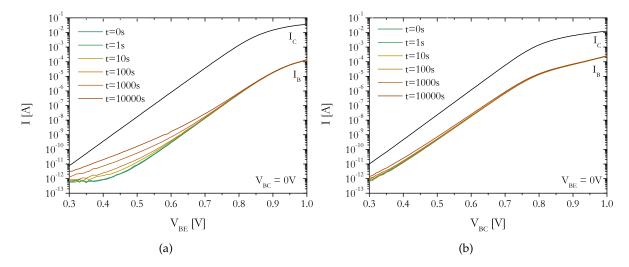

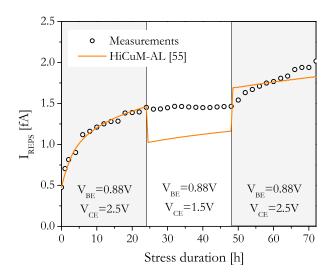

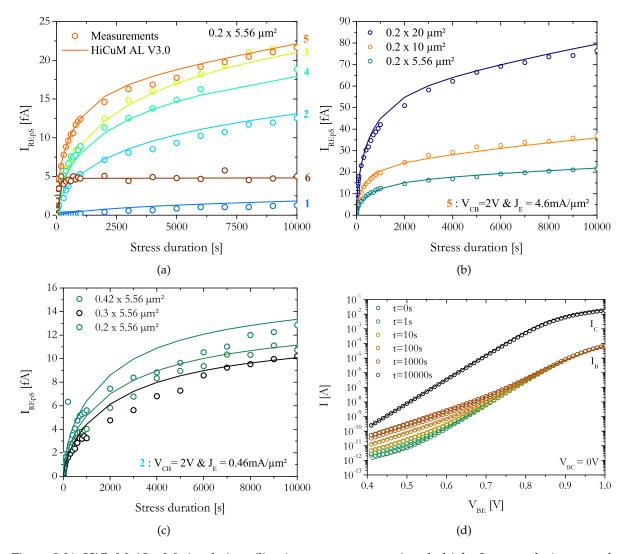

| 3.31 | HiCuM-AL v3.0 simulations (lines) vs measurements (symbols) for $I_{REpS}$ evolution according to the stress duration at (a) various stress conditions (see figure 3.29a), (b) various $L_E$ , (c) various $W_E$ and (d) Gummel evolution for a static stress condition of $V_{CB} = 2 \text{ V}$ and $J_E = 4.6 \text{ mA/}\mu\text{m}^2$ on devices corresponding to B55     | 91  |

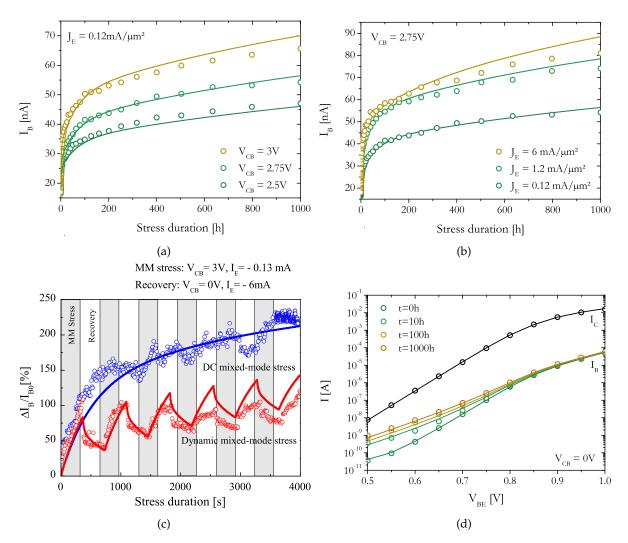

| 3.32 | HiCuM-AL v3.0 simulations (lines) vs measurements (symbols) for $I_B$ evolution according to the stress duration at (a) various $V_{CB}$ , (b) various $J_E$ , (c) under a dynamic stress condition and (d) Gummel Gummel evolution for a static stress condition of $V_{CB} = 3$ V and $J_E = 0.12$ mA/ $\mu$ m <sup>2</sup> on a 8 x 0.16 x 0.52 $\mu$ m <sup>2</sup> device | 94  |

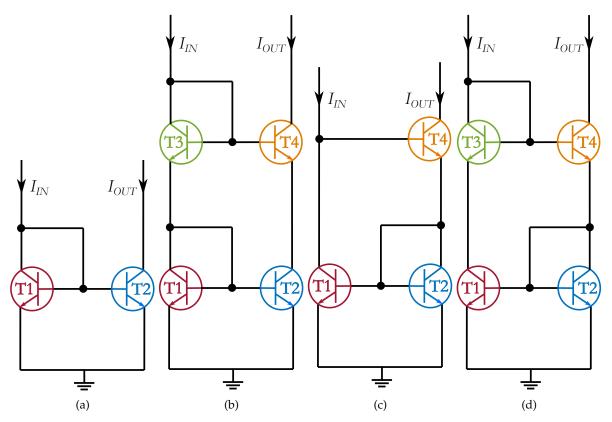

| 4.1  | Schematic of (a) the simple, (b) the cascode, (c) the Wilson and (d) the balanced Wilson current mirrors                                                                                                                                                                                                                                                                       | 99  |

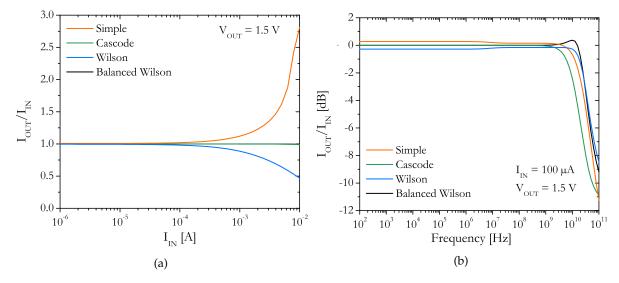

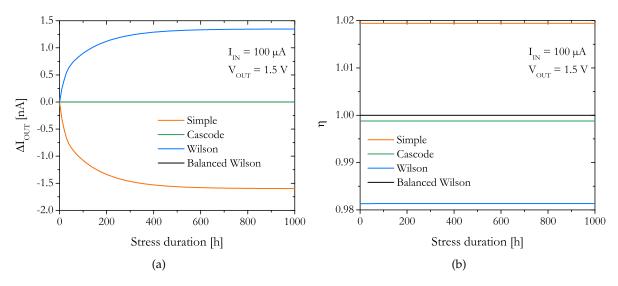

| 4.2  | Transfer ratio evolution for $V_{OUT} = 1.5$ V according to (a) the input current and (b) the frequency at $I_{IN} = 100 \mu\text{A}$                                                                                                                                                                                                                                          |     |

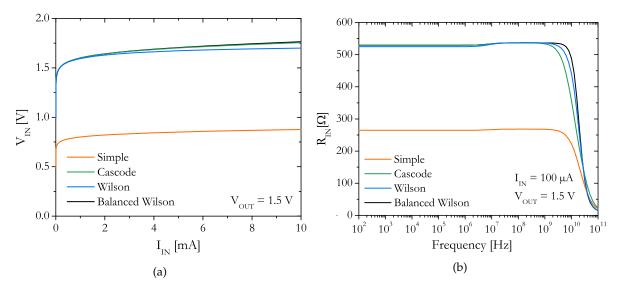

| 4.3  | (a) Input voltage evolution according to the input current for $V_{OUT}$ = 1.5 V and (b) Input resistance evolution according to the frequency for $V_{OUT}$ = 1.5 V and                                                                                                                                                                                                       |     |

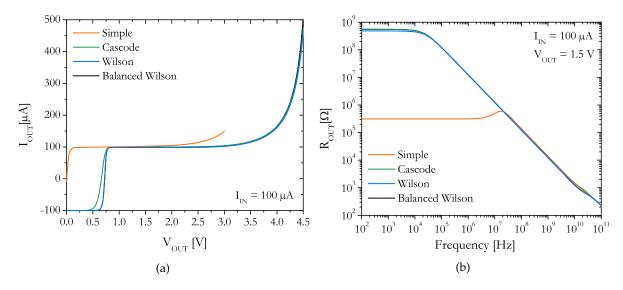

| 4.4  | $I_{IN}$ = 100 $\mu$ A                                                                                                                                                                                                                                                                                                                                                         |     |

| 4.5  | and $I_{IN}$ = 100 $\mu$ A                                                                                                                                                                                                                                                                                                                                                     |     |

| 4.6  | for each current mirror configurations at $V_{OUT} = 1.5 \text{ V}$ and $I_{IN} = 100 \mu\text{A}$                                                                                                                                                                                                                                                                             |     |

|      | tion for $I_{IN} = 100 \mu\text{A}$ and $V_{OUT} = 1.5 \text{V}$                                                                                                                                                                                                                                                                                                               | U4  |

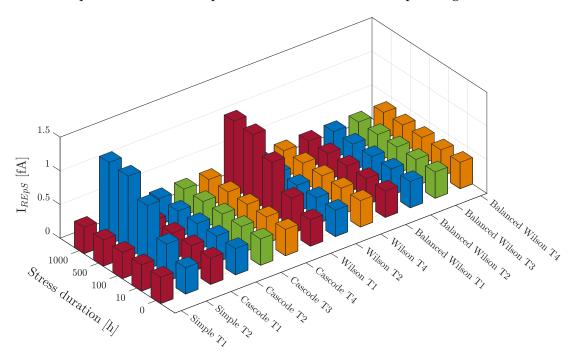

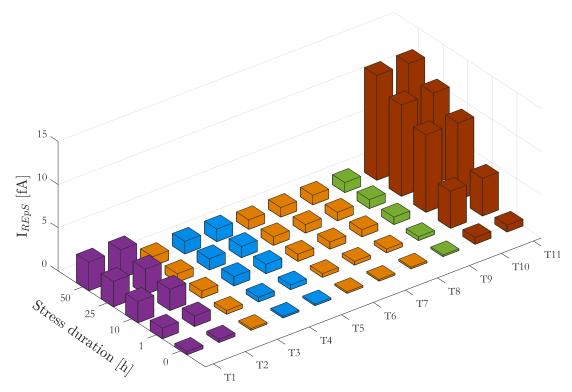

| 4.7   | Evolution of $I_{REpS}$ parameter according to the stress duration for the different transistors and current mirror configurations for $I_{IN} = 100 \mu\text{A}$ and $V_{OUT} = 1.5 \text{V}$ . | 05  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

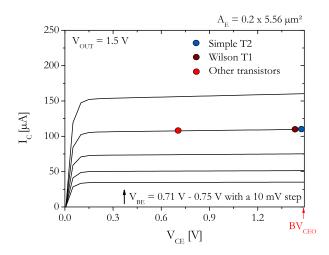

| 1 Q   | $I_C$ vs $V_{CE}$ output characteristics highlighting the transistors operating conditions                                                                                                       | UU  |

| 4.8   |                                                                                                                                                                                                  | Ω6  |

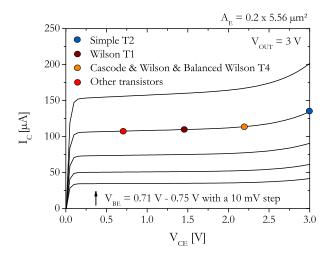

| 4.0   | for each current mirror configurations at $V_{OUT} = 3 \text{ V}$ and $I_{IN} = 100 \mu\text{A}$                                                                                                 | JO  |

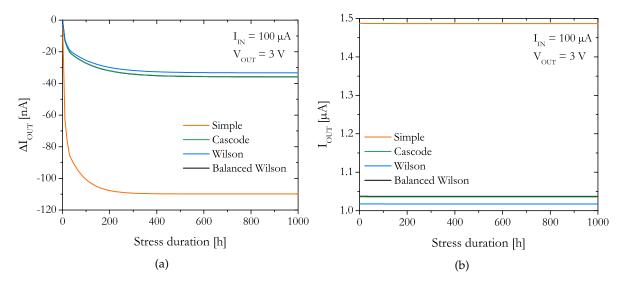

| 4.9   | (a) Output current and (b) transfer ratio evolution according to the stress duration for L = 100 vA and W = 2 V                                                                                  | 07  |

| 1.10  | tion for $I_{IN} = 100 \mu\text{A}$ and $V_{OUT} = 3 \text{V}$                                                                                                                                   | Jb  |

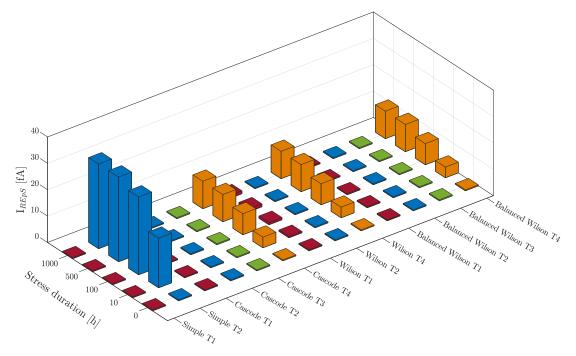

| 4.10  | Evolution of $I_{REpS}$ parameter according to the stress duration for the different                                                                                                             | 05  |

| 1 1 1 | transistors and current mirror configurations for $I_{IN}$ = 100 $\mu A$ and $V_{OUT}$ = 3 $V_{OUT}$ = 1.                                                                                        | J/  |

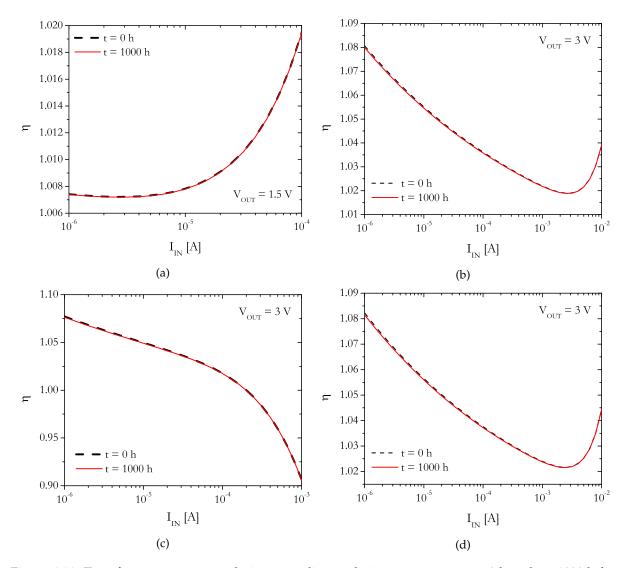

| 4.11  | Transfer current ratio evolution according to the input current at $t = 0$ h and t                                                                                                               |     |

|       | = 1000 h for (a) the simple, (b) the cascode, (c) the Wilson and (d) the balanced                                                                                                                | 0.0 |

|       | Wilson current mirror                                                                                                                                                                            | U8  |

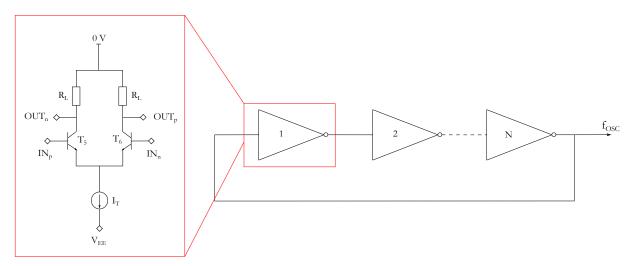

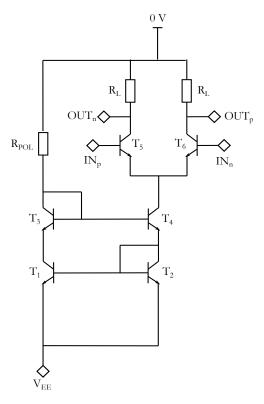

| 4.12  | Schematic of the ring oscillator equivalent circuit together with the CML inverter                                                                                                               |     |

|       | architecture                                                                                                                                                                                     | 09  |

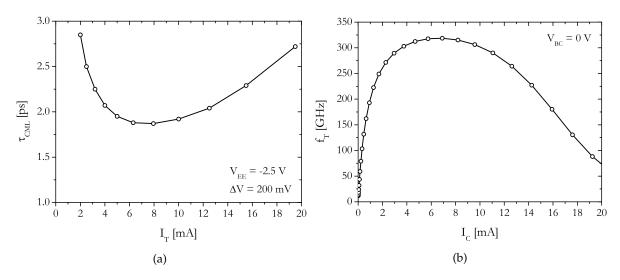

| 4.13  | (a) Propagation gate delay $\tau_{CML}$ as a function of the tail current $I_T$ using an ideal                                                                                                   |     |

|       | current source and (b) transit frequency $f_T$ evolution according to the collector                                                                                                              |     |

|       | current $I_C$ for a 0.2 x 5.56 $\mu$ m <sup>2</sup> SiGe HBT device                                                                                                                              | 10  |

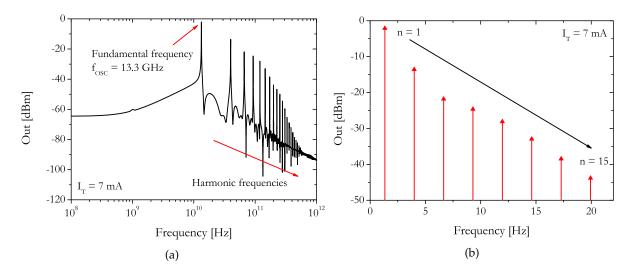

| 4.14  | (a) Frequency power spectrum and (b) corresponding harmonic frequencies up                                                                                                                       |     |

|       | to n = 15 of the ring oscillator for $I_T = 7$ mA                                                                                                                                                |     |

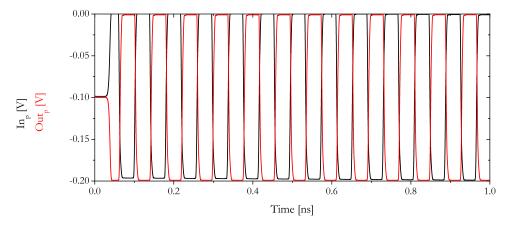

|       | Transient evolution of the input and the output of one inverter stage                                                                                                                            | 11  |

| 4.16  | Schematic view of the CML architecture with a balanced Wilson current mirror                                                                                                                     |     |

|       | to provide the tail current                                                                                                                                                                      | 12  |

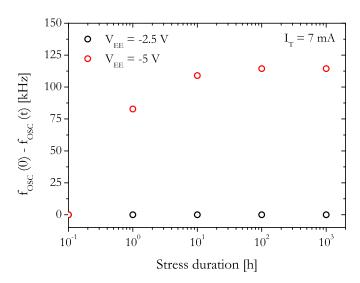

| 4.17  | Oscillation frequency evolution according to the stress duration for $V_{EE}$ = -2.5 V                                                                                                           |     |

|       | (in black symbols) and $V_{EE}$ = -5 V (red symbols)                                                                                                                                             |     |

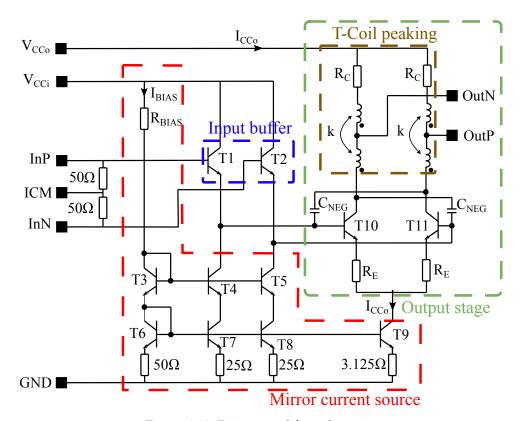

|       | Driver amplifier schematic                                                                                                                                                                       |     |

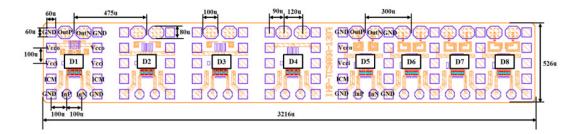

|       | Top layout of the driver array [149]                                                                                                                                                             |     |

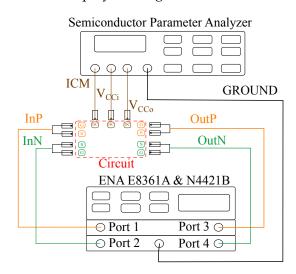

| 4.20  | 4-port S-parameters measurement bench                                                                                                                                                            | 15  |

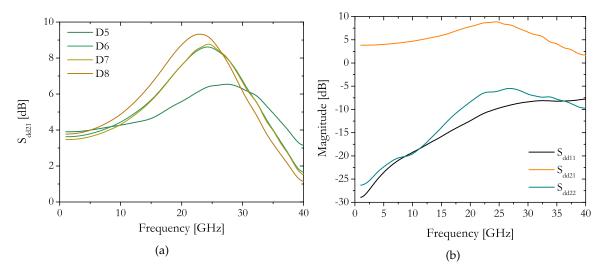

| 4.21  | (a) Differential gain $S_{dd21}$ for the different driver configurations (D5-D8) and (b)                                                                                                         |     |

|       | Differential parameters measurement results for D6 circuit configuration 1                                                                                                                       | 16  |

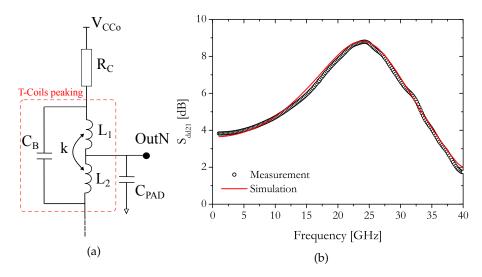

| 4.22  | (a) T-Coils structures modeling which includes a mutual inductance with a cou-                                                                                                                   |     |

|       | pling factor k, an output pad capacitance, $C_{pad}$ , and a bridge capacitance, $C_B$ ,                                                                                                         |     |

|       | and (b) Comparison between measurements (symbols) and simulation (red solid                                                                                                                      |     |

|       | line) for $S_{dd21}$ parameter of D6 circuit configuration using HiCuM compact model. 1                                                                                                          | 17  |

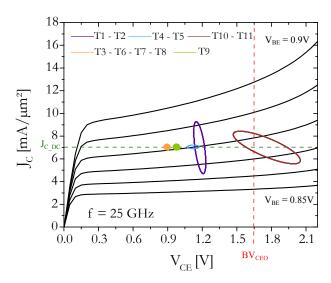

| 4.23  | $J_{\text{C}}$ vs $V_{\text{CE}}$ output characteristics highlighting the transistors operating conditions. $1$                                                                                  | 18  |

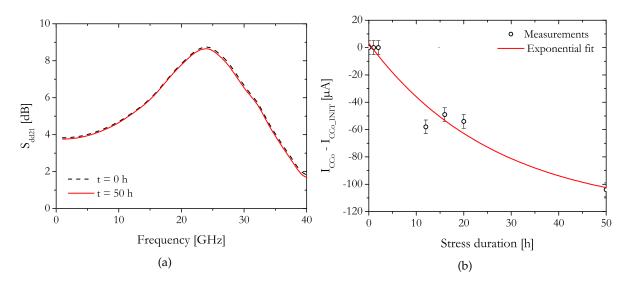

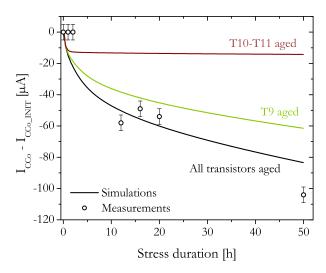

| 4.24  | Evolution of (a) the differential gain, $S_{dd21}$ , at $t = 0$ h and $t = 50$ h and (b) the                                                                                                     |     |

|       | output supply current, $I_{CCo}$ , according to the stress duration under RF stress 1                                                                                                            | 19  |

| 4.25  | $I_{REpS}$ parameter evolution according to the stress duration for the 11 transistors                                                                                                           |     |