# Development of Built-In Self-Test solutions for RF/mm-wave integrated circuits

Florent Cilici

## ► To cite this version:

Florent Cilici. Development of Built-In Self-Test solutions for RF/mm-wave integrated circuits. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2019. English. NNT: 2019GREAT072. tel-03132469

# HAL Id: tel-03132469 https://theses.hal.science/tel-03132469

Submitted on 5 Feb 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Communauté UNIVERSITÉ Grenoble Alpes

## THÈSE

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES Arrêté ministériel : 25 mai 2016

Présentée par

## **Florent CILICI**

Thèse dirigée par **Salvador MIR**, Directeur de recherche , CNRS et codirigée par **Sylvain BOURDEL** , Enseignant-chercheur préparée au sein du **Laboratoire Techniques de l'Informatique** et de la Microélectronique pour l'Architecture des systèmes intégrés

dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

## Développement de solutions BIST (Built-In Self-Test) pour circuits intégrés radiofréquences/millimétriques

# Development of Built-In Self-Test solutions for RF/mm-wave integrated circuits

Thèse soutenue publiquement le **17 décembre 2019**, devant le jury composé de :

Monsieur Philippe Ferrari Professeur, Université Grenoble Alpes, Président

Monsieur Serge Bernard Directeur de Recherche, LIRMM, Université Montpellier, Rapporteur

Madame Nathalie Deltimple Maître de Conférences, Bordeaux INP, Laboratoire IMS, Rapporteur

Monsieur Benoît Poussard Ingénieur, NXP Semiconductors, Toulouse, Examinateur

Monsieur Thierry Parra Professeur, Université de Toulouse III Paul Sabatier, LAAS, Examinateur

Monsieur Manuel Barragan Chargé de Recherche, TIMA, Grenoble, Co-encadrant de thèse

Madame Estelle Lauga-Larroze Maître de Conférences, Université Grenoble Alpes, RFIC-Lab, Grenoble Co-encadrant de thèse, Invité

Monsieur Sylvain Bourdel Professeur, Grenoble INP, RFIC-Lab, Grenoble, Co-directeur de thèse Monsieur Salvador Mir

Directeur de Recherche, TIMA, Grenoble, Directeur de thèse

ii

# Acknowledgements

First, I want to thank my supervisors Salvador Mir, Manuel Barragan, Sylvain Bourdel and Estelle Lauga-Larroze. Their human and technical qualities greatly helped me in making my Ph.D. a successful and most enriching adventure. In this line, I want to sincerely thank Gildas Leger from the Institute of Microelectronics of Seville for his ideas, work and welcome during my stay in Seville. I also want to thank all the researchers, professors, engineers and other colleagues whose support was of immense value: Antonio, Jean-Daniel, Philippe, Florence and Emmanuel from the RFIC Lab, Jean-Michel, Ekta, Walid and Abdelhaziz from IMEP-LAHC and Ayssar from CEA Leti.

I want to especially thank the jury for reviewing my doctoral dissertation and for their involvement my Ph.D. defense: Philippe Ferrari, Serge Bernard, Nathalie Deltimple, Benoît Poussard, Thierry Parra.

I want to especially acknowledge the precious help and efficiency of Alejandro, Mohamed, Frédéric and Ahmed with any computer, design kit or software-related problem.

Circuit fabrication by ST Microelectronics has been funded by the TARANTO project. In this regard, I acknowledge the contribution of P. Ferrari from RFIC-Lab laboratory, D. Gloria, and C. Durand from ST Microelectronics. All the measurements I had to perform would not have been possible without Loïc from CIME Nanotech, Nicolas from IMEP-LAHC and Fabrice from TIMA, I therefore warmly thank them.

I thank Youness, Anne-Laure, Laurence from TIMA, Lorraine from CIME Nanotech and Isabelle from IMEP-LAHC for the administrative support.

Of course thank you to all my close colleagues: Guisseppe, Lisinius, Dimitris, Mahdi, Ekta, Jing, Edouard from IMEP-LAHC, Halim, Renato, Marc, Ghislain, Hani, Rshdee from TIMA, Serge, Jordan from RFIC Lab, and everyone who has shared some time and took part in creating a warm work atmosphere.

During the last three years I had the opportunity to teach several classes, especially in Phelma engineering school. This was a most enriching time, so thank you to all my colleagues: Laurent, Fatah, Daniel, Renato, Sylvain, Jean-Michel, Nicolas, Marc and Pierre.

Finally, I want to thank my fiancé, my family and my friends for their invaluable support.

iv

# Contents

| 1 | Intro | oduction to RF/mm-wave test                                                                         | 1 |

|---|-------|-----------------------------------------------------------------------------------------------------|---|

|   | 1.1   | Introduction                                                                                        | l |

|   | 1.2   | Production testing                                                                                  | 2 |

|   |       | 1.2.1 Characterization and production testing                                                       | 2 |

|   |       | 1.2.2 Required equipment                                                                            |   |

|   |       | 1.2.3 Wafer probing                                                                                 | 2 |

|   |       | 1.2.4 Calibration                                                                                   | 3 |

|   |       | 1.2.5 Accuracy, repeatability, correlation                                                          | 3 |

|   |       | 1.2.6 Test cost                                                                                     | 3 |

|   | 1.3   | Measures to be performed                                                                            | 1 |

|   |       | 1.3.1 Small signal measurements                                                                     | 1 |

|   |       | 1.3.2 Large signal measurements                                                                     | 5 |

|   |       | 1.3.3 Power efficiency                                                                              | 7 |

|   | 1.4   | Alternatives to conventional test                                                                   | 7 |

|   |       | 1.4.1 Structural test                                                                               | 3 |

|   |       | 1.4.2 Built-Off Test                                                                                | 3 |

|   |       | 1.4.3 Built-In Test                                                                                 | 3 |

|   |       | 1.4.4 Machine Learning Indirect Test                                                                | ) |

|   |       | 1.4.5 Conclusion                                                                                    | 3 |

|   | 1.5   | Calibration against process variations 13                                                           | 3 |

|   |       | 1.5.1 Introduction                                                                                  | 3 |

|   |       | 1.5.2 One-shot statistical calibration                                                              | 1 |

|   | 1.6   | Conclusion                                                                                          | 5 |

| 2 | Stat  | e of the art                                                                                        | 7 |

| 4 | 2.1   | Built-In Self-Test                                                                                  |   |

|   | 2.1   | 2.1.1         Intrusive methods         17                                                          |   |

|   |       | 2.1.1         Intrusive methods         17           2.1.2         Non-intrusive methods         21 |   |

|   | 2.2   |                                                                                                     |   |

|   | 2.2   |                                                                                                     |   |

|   |       |                                                                                                     | - |

|   |       | 2.2.2 One-shot strategies                                                                           |   |

|   | • •   | 2.2.3 Towards self-healing                                                                          |   |

|   | 2.3   | Conclusions                                                                                         | ) |

| CONTENTS |

|----------|

|----------|

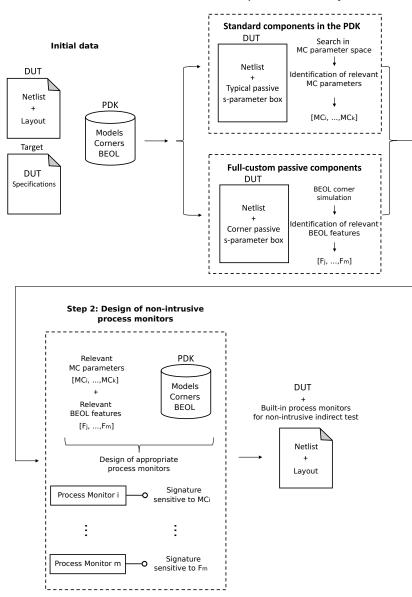

| 3 | Assi | isted test design for non-intrusive MLIT                                            | 29  |

|---|------|-------------------------------------------------------------------------------------|-----|

|   | 3.1  | Introduction                                                                        | 29  |

|   | 3.2  | Proposed approach                                                                   | 29  |

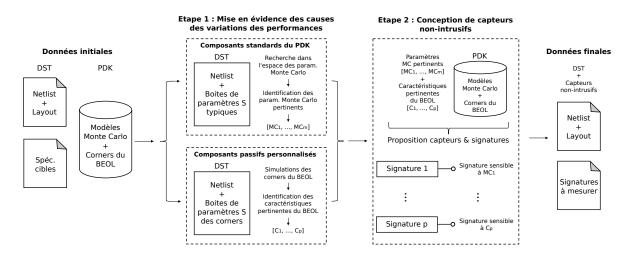

|   |      | 3.2.1 Step 1: Unveiling the root causes of parametric performance variation         | 30  |

|   |      | 3.2.2 Step 2: Assisted design of non-intrusive process variation sensors            | 32  |

|   | 3.3  | Case study                                                                          | 33  |

|   |      | 3.3.1 Basics of linear power amplifier design                                       | 33  |

|   |      | 3.3.2 Design of a mm-wave power amplifier                                           | 36  |

|   |      | 3.3.3 Applying the proposed methodology to the designed PA                          | 43  |

|   | 3.4  | Conclusions                                                                         | 53  |

| 4 | Assi | isted MLIT design of mm-wave ICs with custom passives                               | 55  |

|   | 4.1  |                                                                                     | 55  |

|   | 4.2  | Non-intrusive test program generation for generic mm-wave ICs                       | 56  |

|   |      | 4.2.1 Problem statement                                                             | 56  |

|   |      | 4.2.2 Step 1: Assessment of the root causes of the parametric performance variation | 56  |

|   |      | 4.2.3 Step 2: Design of non-intrusive process variation sensors                     | 58  |

|   | 4.3  | Case Study                                                                          | 59  |

|   | 1.5  | 4.3.1 Device Under Test                                                             | 59  |

|   |      | 4.3.2 Step 1: Assessment of parametric performance variation root causes            | 63  |

|   |      | 4.3.3 Step 2: Design of non-intrusive process variation sensors                     | 68  |

|   | 4.4  | Experimental results                                                                | 69  |

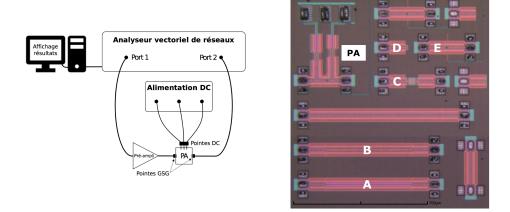

|   |      | 4.4.1 Measurement setup                                                             | 70  |

|   |      | 4.4.2 Fabricated set of chips                                                       | 71  |

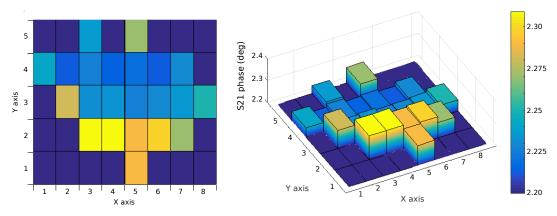

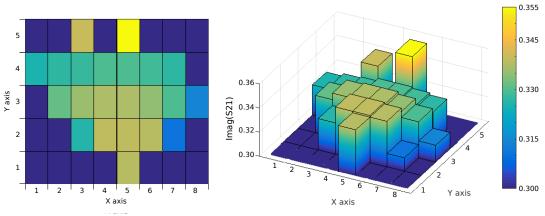

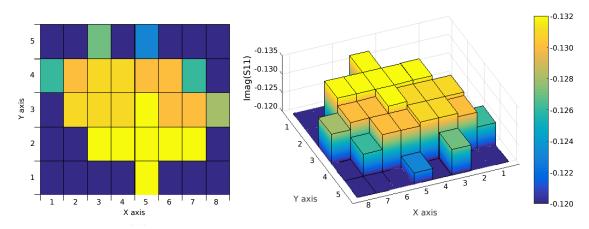

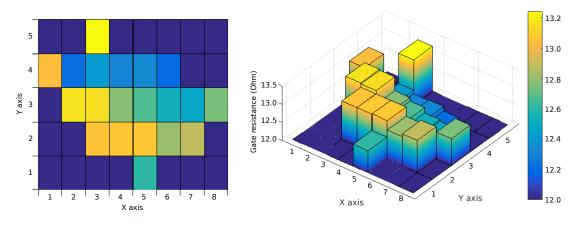

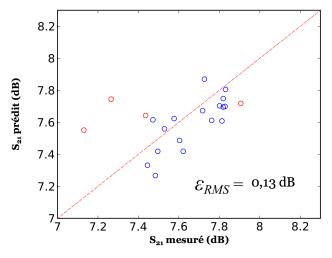

|   |      | 4.4.3 Signature measurement                                                         | 71  |

|   |      | 4.4.4 PA measurement results                                                        | 78  |

|   |      | 4.4.5 General results                                                               | 81  |

|   | 4.5  | Conclusions                                                                         | 82  |

| 5 | One  | e-shot calibration against process variation                                        | 85  |

| U | 5.1  |                                                                                     | 85  |

|   | 5.2  | Design of a power amplifier with calibration capabilities                           | 85  |

|   | 0.2  | 5.2.1 Power amplifier design                                                        | 85  |

|   |      | 5.2.2 Tuning knobs design                                                           | 87  |

|   | 5.3  | A novel data generation method                                                      | 92  |

|   | 5.5  | 5.3.1 Previous work                                                                 | 93  |

|   |      | 5.3.2 Data generation for training calibration models                               | 93  |

|   |      | 5.3.3 Proposed random sampling results                                              | 95  |

|   |      | 5.3.4 Practical implementation                                                      | 97  |

|   |      | 5.3.5 Conclusions                                                                   | 98  |

|   | 5.4  | Calibration procedure and results                                                   | 99  |

|   |      | 5.4.1 Calibration procedure and implementation                                      | 99  |

|   |      | 1 1                                                                                 | 102 |

|   | 55   |                                                                                     | 104 |

| CONTENTS     | vii |

|--------------|-----|

| Conclusions  | 107 |

| Publications | 109 |

| Bibliography | 111 |

| Appendices   | 117 |

| Résumé       | 123 |

#### CONTENTS

# **List of Figures**

| 1.1  | Illustration of incident and reflected waves for a two-port network.                      | 5  |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | Definition of 1 dB compression point.                                                     | 6  |

| 1.3  | Definition of IP3 (for voltage quantities).                                               | 7  |

| 1.4  | Machine learning example: price versus area.                                              | 10 |

| 1.5  | Machine learning example: predicted price versus real price                               | 11 |

| 1.6  | Machine learning indirect test principle.                                                 | 12 |

| 1.7  | Generic test flow for machine learning indirect test.                                     | 12 |

| 1.8  | a) Iterative calibration using external ATE, b) Iterative calibration using low-cost ATE. | 14 |

| 1.9  | One-shot calibration principle.                                                           | 14 |

| 2.1  | Direct loopback setup for integrated transceiver test.                                    | 19 |

| 2.2  | Block diagram showing the required modifications to convert a DUT into an oscillator.     | 20 |

| 2.3  | Block diagram of a generic non-intrusive indirect test based on process-aware sensors.    | 22 |

| 2.4  | Self-calibration/self-healing using on-chip ressources                                    | 26 |

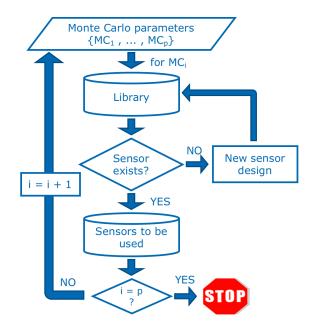

| 3.1  | Assisted design of non-intrusive process variation sensors - Exploiting the sensors       |    |

|      | reusability by means of a library.                                                        | 32 |

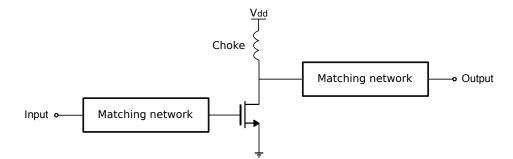

| 3.2  | Basic diagram of a common source NMOS power amplifier.                                    | 33 |

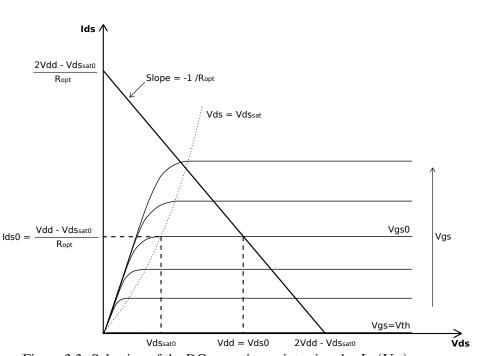

| 3.3  | Selection of the DC operating point using the $I_{ds}(V_{ds})$ curves                     | 34 |

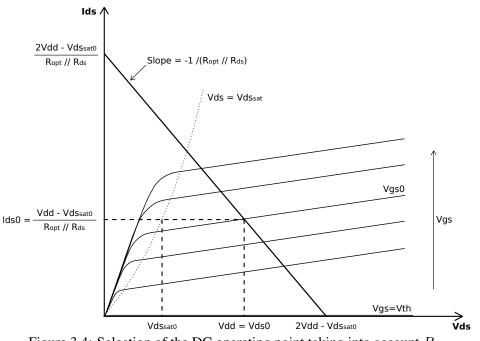

| 3.4  | Selection of the DC operating point taking into account $R_{ds}$ .                        | 35 |

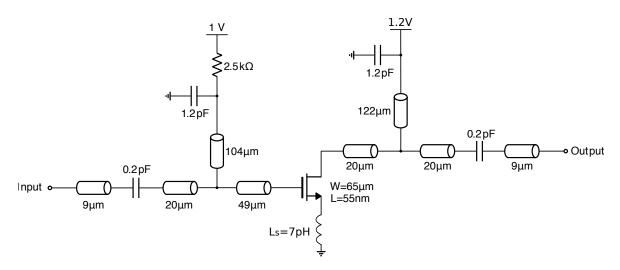

| 3.5  | Transistor level schematic of the power amplifier under test.                             | 37 |

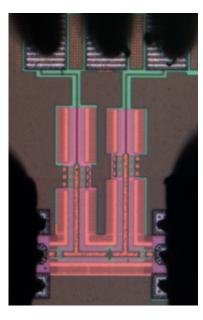

| 3.6  | Layout of the power amplifier under test                                                  | 38 |

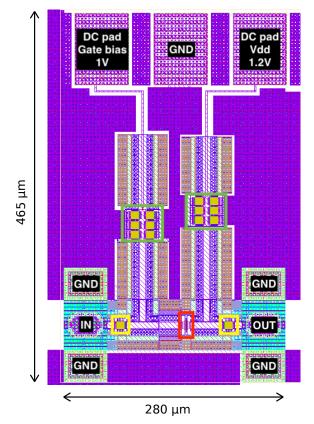

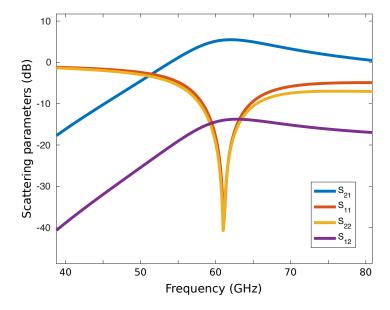

| 3.7  | Scattering parameters obtained though post-layout simulations                             | 39 |

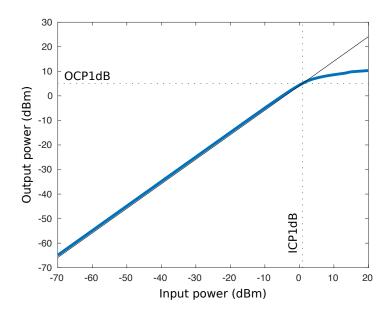

| 3.8  | Output power versus input power at 60 GHz - Compression point and saturation              | 39 |

| 3.9  | 3D view of the MOS transistor connections.                                                | 40 |

| 3.10 | Top and 3D views of a 50 $\Omega$ microstrip line                                         | 41 |

| 3.11 | T-junction layout and model.                                                              | 41 |

|      | 3D view of the decoupling cell                                                            | 42 |

|      | Top view and model of the decoupling cell.                                                | 42 |

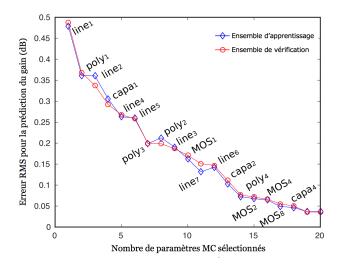

| 3.14 | Exploration of the MC process parameter space for finding the root causes of gain         |    |

|      | parametric variation for the PA                                                           | 44 |

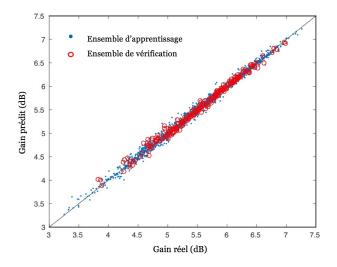

| 3.15 | Scatterplot of predicted versus actual gain of the PA using the 18 most relevant MC       |    |

|      | parameters as signatures.                                                                 | 45 |

|      |                                                                                           |    |

#### LIST OF FIGURES

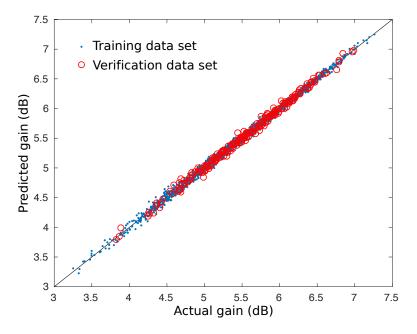

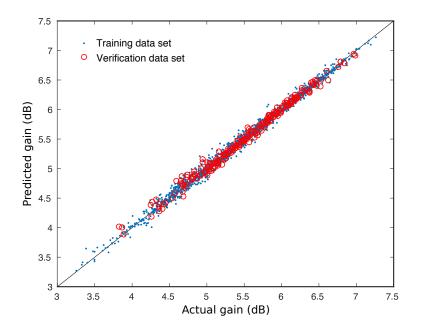

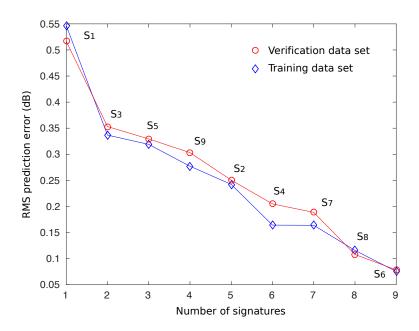

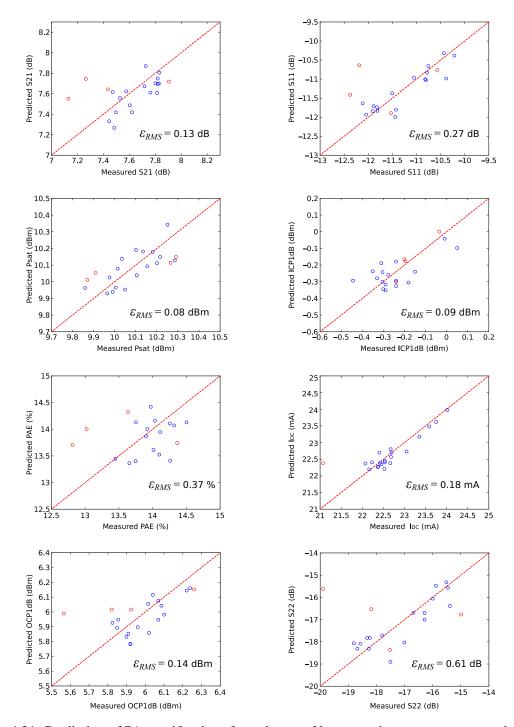

| 3.16  | Scatterplot of predicted versus actual gain of the PA using the generated indirect test program with the 9 non-intrusive signatures of Table 3.3. | 49 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.17  | RMS error for gain prediction versus the number of signatures.                                                                                    | 49 |

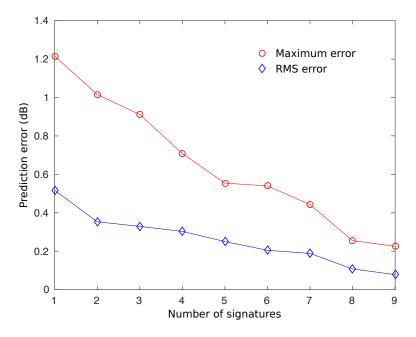

|       | Maximum and RMS error for gain prediction versus the number of signatures                                                                         | 50 |

|       | Scatterplot of predicted versus actual specification of the PA using the generated indi-                                                          |    |

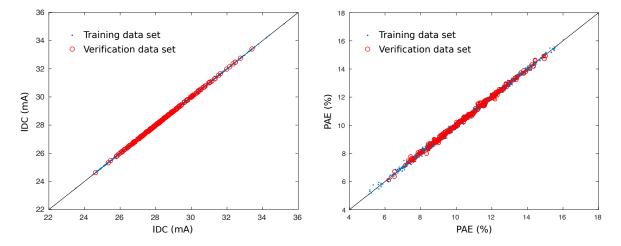

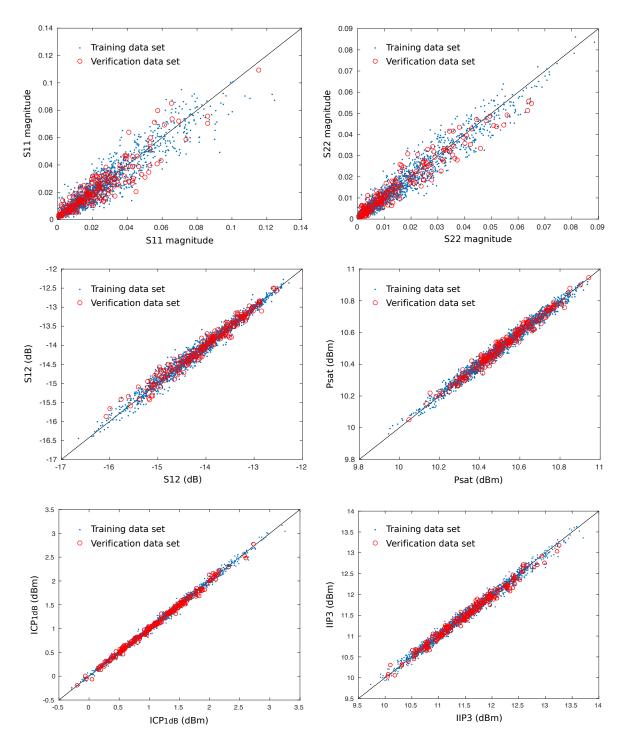

| 0.127 | rect test program with the 9 non-intrusive signatures of Table 3.3                                                                                | 51 |

| 3 20  | Scatterplot of predicted versus actual specification of the PA using the generated indi-                                                          |    |

| 0.20  | rect test program with the 9 non-intrusive signatures of Table 3.3 (continued).                                                                   | 52 |

|       |                                                                                                                                                   |    |

| 4.1   | Conceptual block diagram of the proposed methodology for the generation of non-                                                                   |    |

|       | intrusive indirect test for a generic mm-wave integrated circuit                                                                                  | 57 |

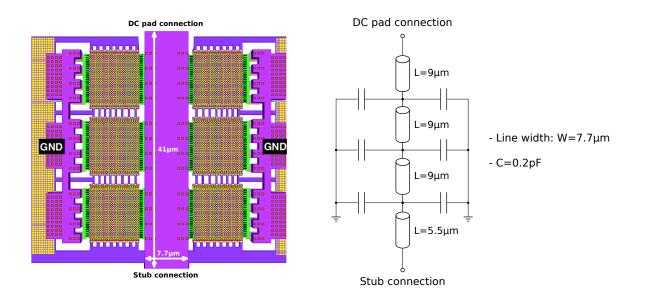

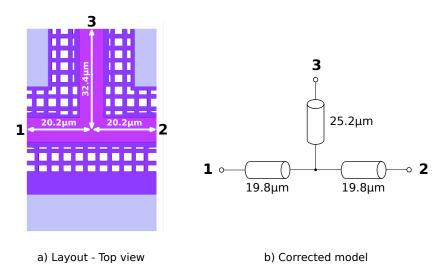

| 4.2   | Top view and corrected model of the T-junction.                                                                                                   | 60 |

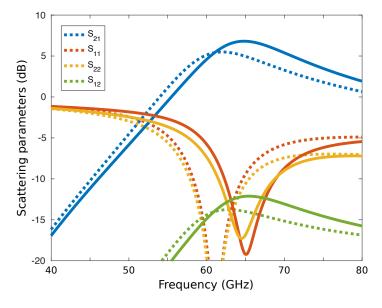

| 4.3   | Expected S-parameters with the initial (dotted lines) and corrected (solid lines) models.                                                         | 61 |

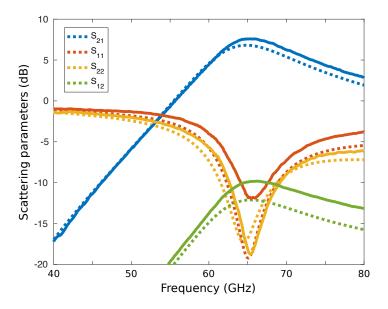

| 4.4   | Expected S-parameters with the corrected model (dotted lines) and measured S-parameter                                                            | s  |

|       | (solid lines)                                                                                                                                     | 62 |

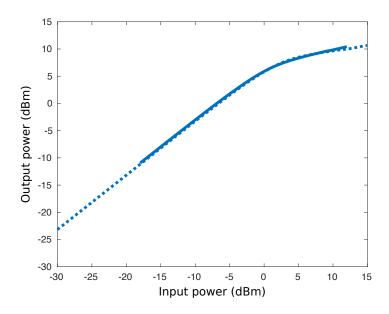

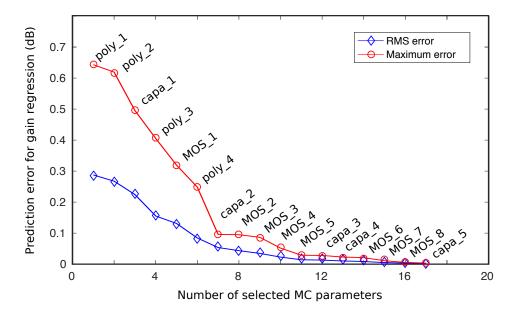

| 4.5   | Expected output power with the corrected model (dotted lines) and measured output                                                                 |    |

|       | power (solid lines).                                                                                                                              | 62 |

| 4.6   | Expected PAE with the corrected model (dotted lines) and measured PAE (solid lines).                                                              | 63 |

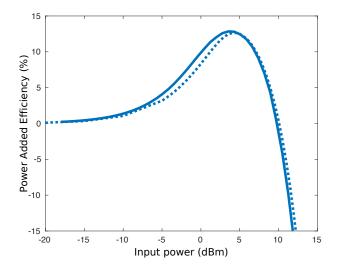

| 4.7   | Transistor level schematic of the PA under test with typical S-parameters boxes for                                                               |    |

|       | passive custom components.                                                                                                                        | 64 |

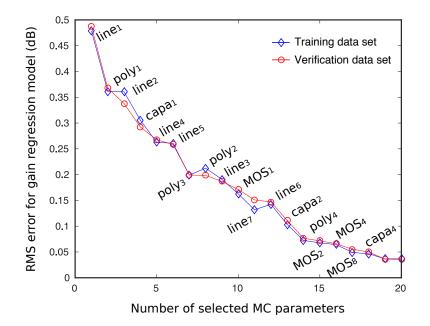

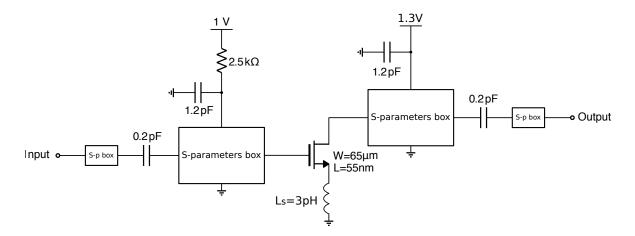

| 4.8   | RMS and maximum error for the prediction of the PA small signal gain as a function                                                                |    |

|       | of the number of selected MC parameters                                                                                                           | 65 |

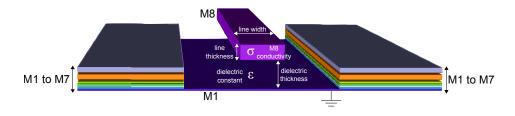

| 4.9   | Full-custom microstrip line and relevant BEOL features                                                                                            | 65 |

| 4.10  | Microphotograph of the PA under test with the proposed non-intrusive process moni-                                                                |    |

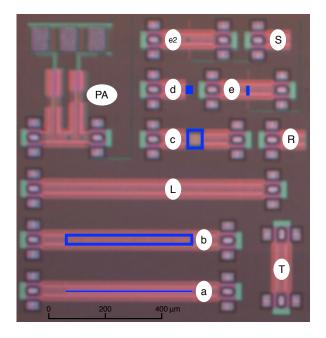

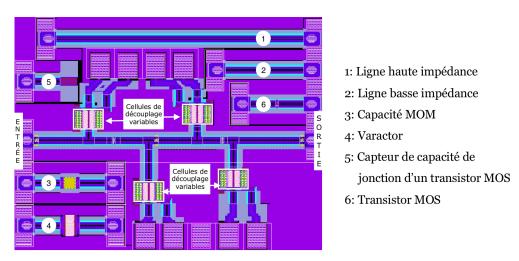

|       | tors and de-embeding structures.                                                                                                                  | 71 |

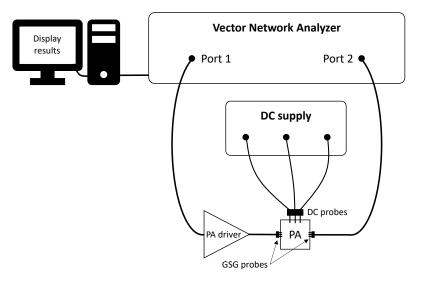

|       | General diagram of the measurement setup.                                                                                                         | 72 |

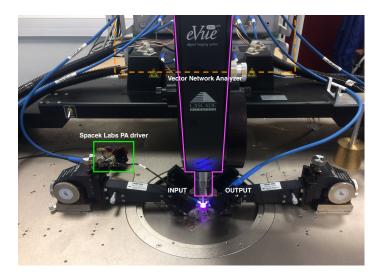

|       | Photography of the test bench for large signal measurements                                                                                       | 72 |

|       | Photography of the PA being measured.                                                                                                             | 73 |

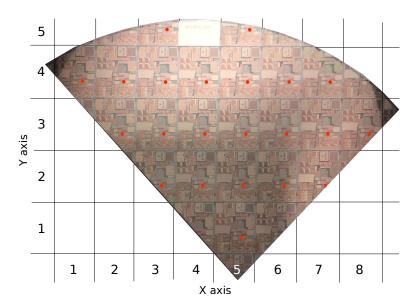

| 4.14  | Photography of the wafer with the circuits position (red dots) and mapping to the wafer                                                           |    |

|       | reticle                                                                                                                                           | 73 |

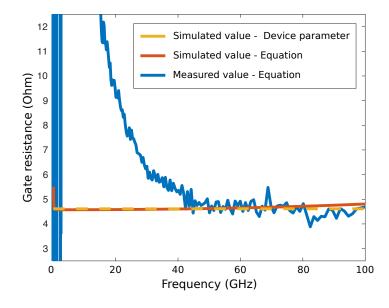

|       | Gate resistance extraction - Simulation versus measurement.                                                                                       | 74 |

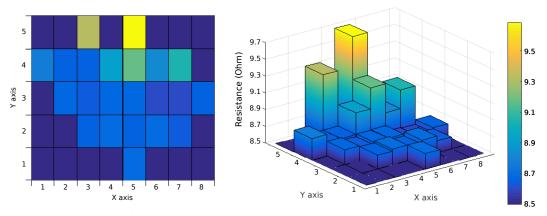

| 4.16  | Measurement results on the thin lines, wide lines and MOM capacitors - Signatures                                                                 |    |

|       | $S_1, S_2$ and $S_4, \ldots, \ldots, \ldots, \ldots, \ldots, \ldots, \ldots, \ldots, \ldots, \ldots$                                              | 76 |

| 4.17  | Measurement results on the MOS junction capacitance sensors and MOS transistors -                                                                 |    |

|       | Signatures $S_5$ , $S_6$ and $S_7$                                                                                                                | 77 |

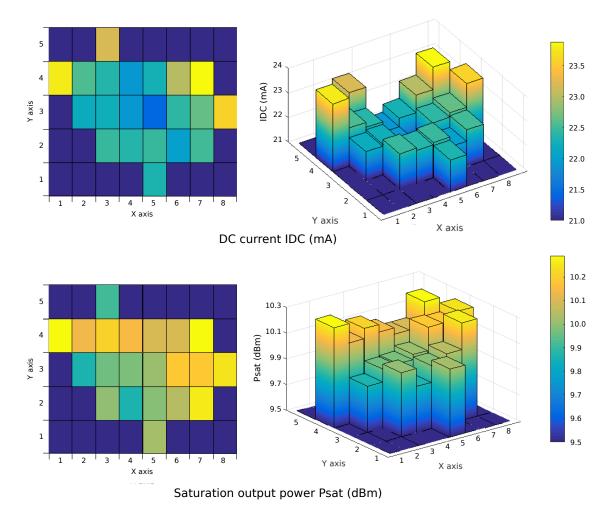

|       | Measurement results of the PA performance - $I_{DC}$ , $P_{sat}$                                                                                  | 78 |

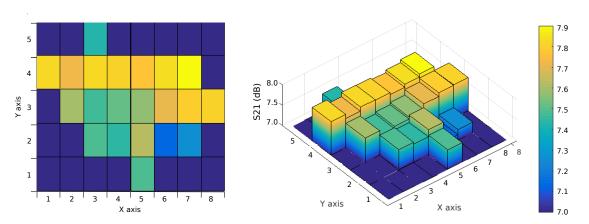

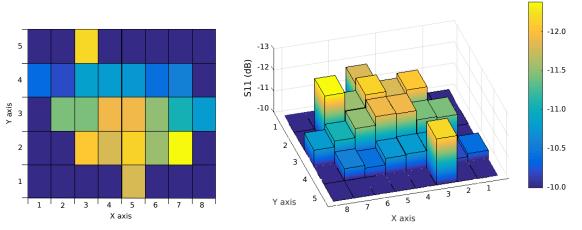

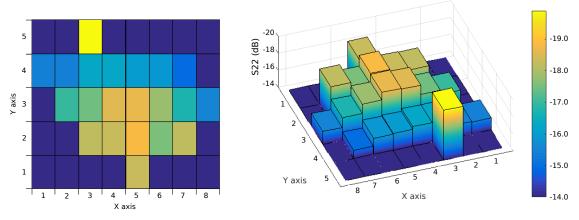

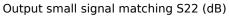

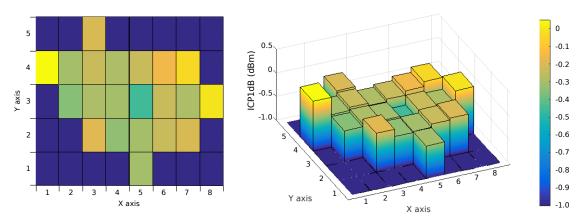

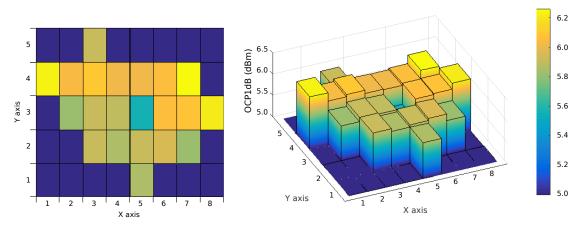

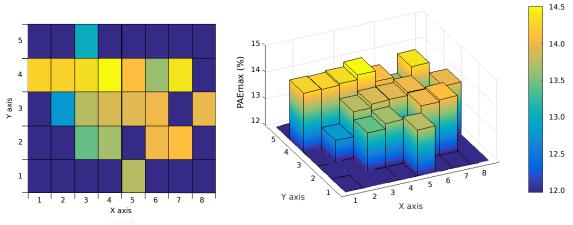

|       | Measurement results of the PA performance - $S_{21}$ , $S_{11}$ and $S_{22}$                                                                      | 79 |

|       | Measurement results of the PA performance - $ICP_{1dB}$ , $OCP_{1dB}$ , $PAE_{max}$                                                               | 80 |

| 4.21  | Prediction of PA specifications from the set of low-cost signatures versus standard                                                               |    |

|       | mm-wave functional measurements.                                                                                                                  | 83 |

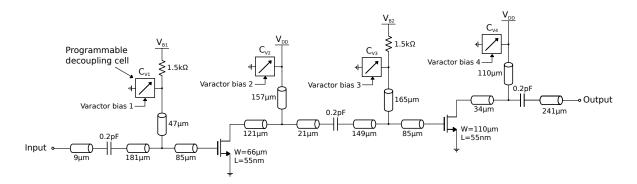

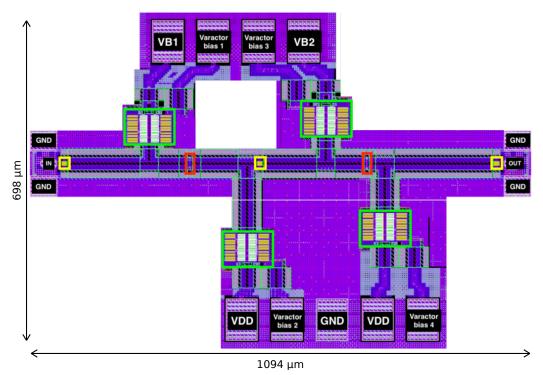

| 5.1   | Transistor-level schematic of the power amplifier under study.                                                                                    | 87 |

| 5.2   | Layout of the power amplifier under study.                                                                                                        | 87 |

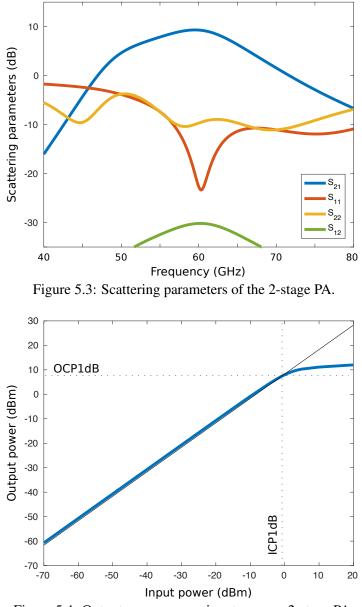

| 5.3   | Scattering parameters of the 2-stage PA.                                                                                                          | 88 |

#### LIST OF FIGURES

| 5.4  | Output power versus input power - 2-stage PA.                                           | 88  |

|------|-----------------------------------------------------------------------------------------|-----|

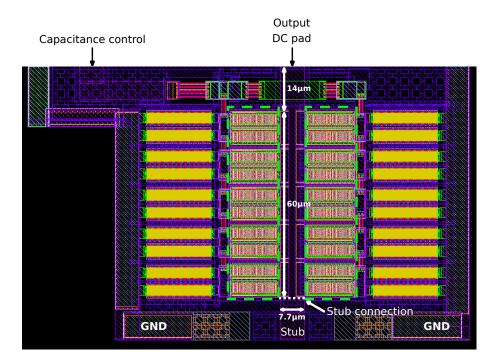

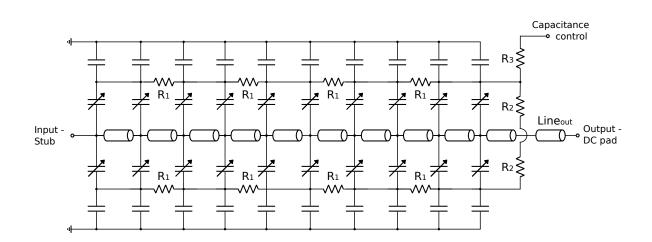

| 5.5  | Layout of the proposed variable decoupling cell                                         | 90  |

| 5.6  | Model of the proposed variable decoupling cell.                                         | 90  |

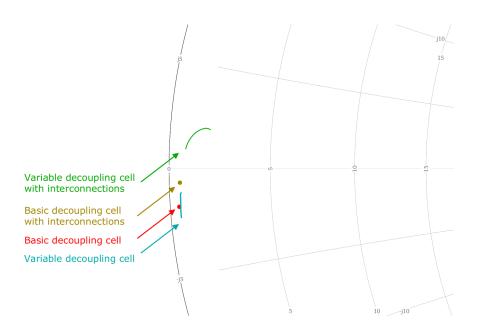

| 5.7  | Impact of the interconnection model for fixed and variable decoupling cells             | 91  |

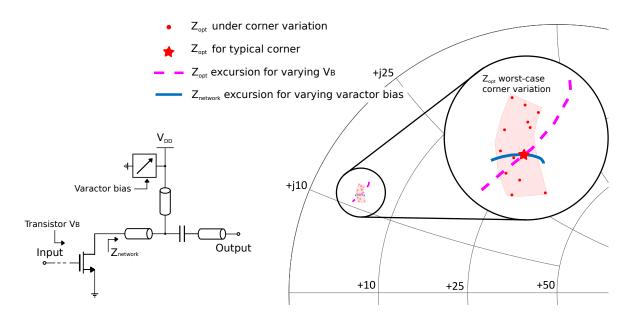

| 5.8  | Simplified example for illustrating the effect of the tuning knobs on a node impedance. | 92  |

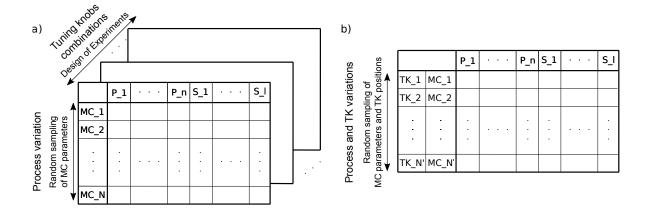

| 5.9  | Generation of training data sets using a) full factorial DOE and b) random sampling.    | 94  |

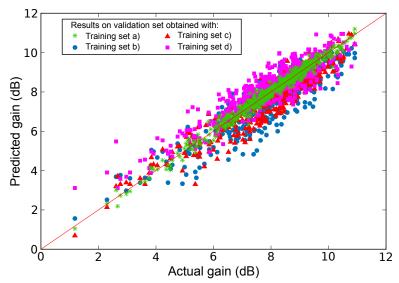

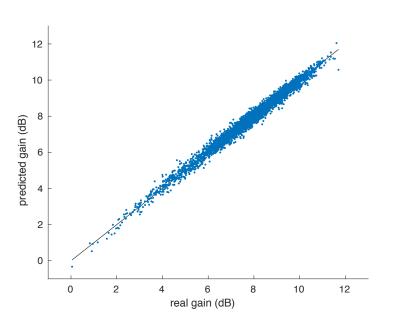

| 5.10 | Scatterplot of predicted versus actual PA gain for the samples in the validation set    | 96  |

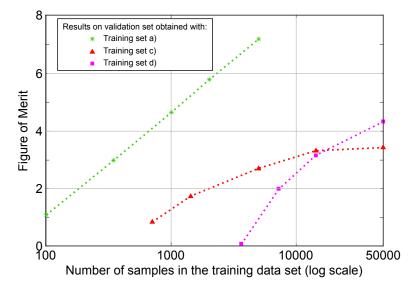

| 5.11 | Figure of merit for the prediction of the PAE as a function of the size of the training |     |

|      | data set                                                                                | 97  |

|      | OCEAN script used to simulate the circuit with the calibrated tuning knob values        | 98  |

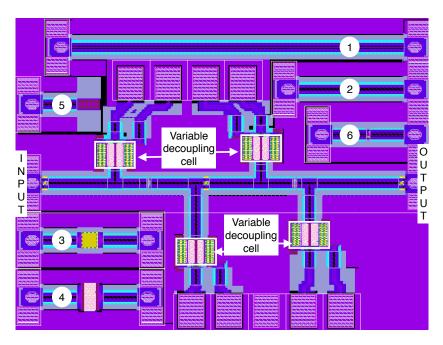

| 5.13 | Layout of the power amplifier with variable decoupling cells and non-intrusive process  |     |

|      | monitors                                                                                | 99  |

|      | Predicted versus actual gain using the regression function used for the calibration     | 100 |

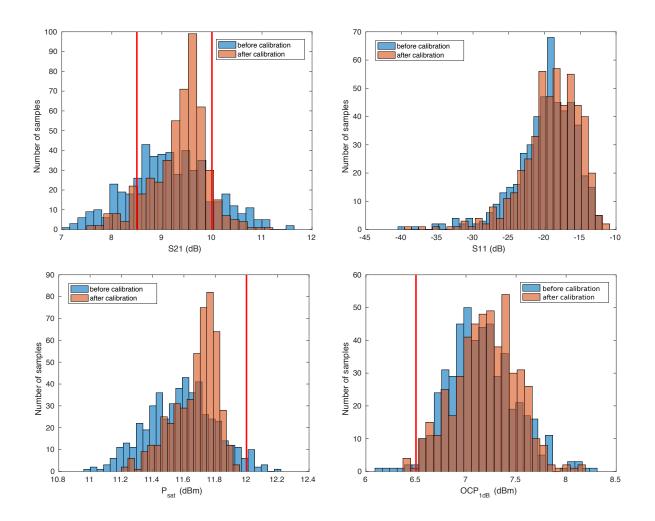

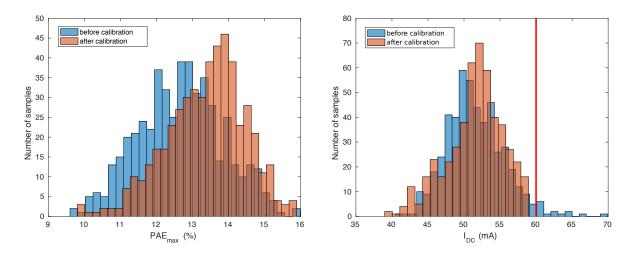

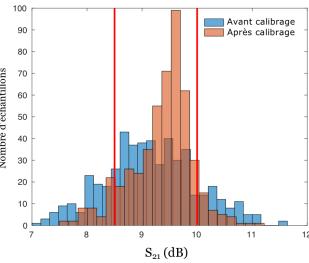

| 5.15 | Histograms of the main performances of the PA simulated both before and after cali-     |     |

|      | bration.                                                                                | 103 |

| 5.16 | Histograms of the main performances of the PA simulated both before and after cali-     |     |

|      | bration (continued).                                                                    | 104 |

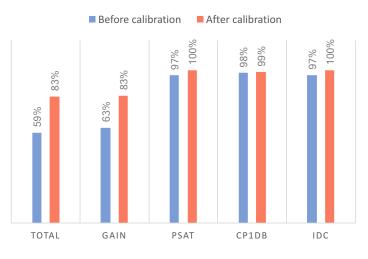

| 5.17 | Yield before and after calibration.                                                     | 104 |

xi

#### LIST OF FIGURES

# **List of Tables**

| 3.1 | Performances of the PA under test.                                                      | 38  |

|-----|-----------------------------------------------------------------------------------------|-----|

| 3.2 | $50\Omega$ transmission line main features                                              | 41  |

| 3.3 | Proposed library of non-intrusive sensors and their associated signatures for gain pre- |     |

|     | diction.                                                                                | 47  |

| 3.4 | Identified relevant MC parameters for the prediction of the PA specifications.          | 51  |

| 3.5 | Prediction of PA performances using the generated indirect test program                 | 53  |

| 4.1 | Identified relevant MC parameters for the prediction of the PA specifications           | 66  |

| 4.2 | Transmission line main performances for the seven selected corners                      | 68  |

| 4.3 | Identified relevant BEOL features for the prediction of the PA specifications           | 68  |

| 4.4 | Proposed library of non-intrusive sensors and signatures for gain prediction            | 70  |

| 4.5 | Measured performances of the PA and prediction results                                  | 82  |

| 5.1 | Performance and design parameters of the PA                                             | 89  |

| 5.2 | Variable decoupling cell model features.                                                | 91  |

| 5.3 | Comparison of PA performances figures of merit for different training sets              | 96  |

| 5.4 | Performances of the PA before and after calibration.                                    | 102 |

#### LIST OF TABLES

# Chapter 1

# **Introduction to RF/mm-wave test**

## **1.1 Introduction**

The market of Systems on Chip (SoC) and Systems in Package (SiP) is continuously growing, pulled by sectors such as automotive, biomedical or 4.0 industry. This is possible especially thanks to advanced nanometric CMOS technologies, which allow the use of high frequencies and the integration of complex functions within tiny SoCs or SiPs.

Nevertheless, such technologies are prone to imperfections which can noticeably alter the devices performances. Process variations during the fabrication of the circuits are the most prominent source of faulty devices. Several kind of parametric process variations can be distinguished: lot-to-lot, wafer-to-wafer, die-to-die, within-die. The first three correspond to global variations whereas the last one corresponds to local random discrepancies, also known as mismatch. Catastrophic defects, also called spot-defects, are another possible source of faulty devices. They are caused by open/short circuits and most of the time, translate into faults.

Today a cleanroom can deliver a circuit for a fraction of the price it cost a few years ago. However, the test of the fabricated circuits still represents a bottleneck in the production line. As a matter of fact, the use of highly integrated and various types of circuits (digital, memory, analog, mixed-signal, RF, ...) makes it difficult or even impossible to access internal nodes for test purposes. Moreover, the test of analog, mixed-signal, RF and mm-wave circuits usually relies on specification-based test. The time and equipment required to perform these tests still represent an important part of the test cost and, therefore, a major challenge.

In [1], the test of a mobile phone SoC is thoroughly studied. It is estimated that the digital and memory test only represents 13% of the overall test time, while these parts account for more than half of the silicon area. This well illustrates the efficiency of test approaches for digital circuits and the possible progression margin for their analog counterparts.

This Chapter is structured as follows. Section 1.2 gives an insight into production testing while Section 1.3 details the classical measurements that are performed to ascertain device performances.

Section 1.4 reviews the main approaches that are suitable to replace the conventional test procedures and Section 1.5 introduces calibration techniques that can be used to improve the performances of a suboptimal device. A special focus is given on one-shot strategies, that will be further developed in this thesis.

## **1.2** Production testing

#### 1.2.1 Characterization and production testing

In order to sort out good and bad fabricated samples, a circuit can be tested in several ways. During the early stages of pre-production and production runs, a thorough characterization of the devices is typically performed to ensure their performances. However, several of the measurements that are performed may be redundant and therefore not mandatory to ensure the device behavior. Thus, during the production stage, the number of tests is minimized as far as possible. Nevertheless, even when the product is mature enough, an extensive characterization of each n-th die can be performed [2].

#### 1.2.2 Required equipment

Rack-and-stack configurations are similar to laboratory test equipment and are suited to characterization. They can be specifically optimized for the target Device Under Test (DUT). For optimal test time during the production stage, Automated Test Equipment (ATE) are provided by large testequipment manufacturers. They are especially suited to large volume production, can test several parts in parallel and are flexible enough to be reconfigured for another DUT in another test campaign. Different kinds of equipment are used depending on the DUT. For high frequency tests, they can consist in Vector Network Analyzer (VNA), spectrum analyzer, RF/mm-wave source, handler, load boards, contactor sockets, wafer prober, probe card, probes, etc. The ATE cost and complexity is highly dependent on the DUT, the tests to perform and the number of devices that are to be tested in parallel.

#### **1.2.3** Wafer probing

In this thesis we only focus on wafer-level test. The interested reader is referred to [2] for testing of packaged circuit. For prototyping and characterization, bench top wafer probing equipment is used. The probes are typically contacted to the wafer using a manual or semi-automatic wafer prober, and measurements are performed using external equipment (VNA, ...). For production testing, a probe card is required in addition to bench top equipment. "A probe card, serving the purpose of the load board and contactor (in an analogy to packaged testing), is a complex printed circuit board that contains a customized arrangement of probe needles or probe tips to allow all of the necessary tester ressources to contact all of the bond pads on one or more chips simultaneously" [2].

#### 1.2.4 Calibration

For the measurements to truly reflect the DUT specifications, calibration procedures have to be set up and performed regularly. The losses introduced by the different elements that are used to connect the DUT to the measurement equipment (cable, connector, probes, etc) are especially critical for RF and mm-wave DUTs. A de-embedding procedure, typically a SOLT calibration, is used to remove their effect on the measured data [3]. It is based on 4 measurements: a Short, an Open, a 50  $\Omega$  Load and a Thru, hence the name SOLT. Power sources are also key elements that need to be calibrated, typically using a power-meter.

#### **1.2.5** Accuracy, repeatability, correlation

The accuracy of a test procedure translates how far the test results are from the truth and seems to be the first feature that need to be accounted for. However, repeatability is of paramount importance, often far more than accuracy since the go/no-go decision must be consistent over time. It is also critical to ascertain the correlation, the consistency of the test results with measurements provided by bench top equipment, especially if the test is outsourced to a test house [2].

#### 1.2.6 Test cost

The overall Cost Of Test (COT) is an extremely critical feature of testing. Several parameters are worth considering to compute it. A simple expression is given by the following Equation.

$$COT = \frac{Fixed \ costs \times Recurring \ costs}{Lifetime \times Yield \times Utilization \times Throughput}$$

(1.1)

Fixed costs refer mainly to the ATE capital, while recurring costs are implied by the use of the test equipment. The lifetime and utilization (percentage of the time) of the equipment is also taken into account to compute the COT. The yield refers to the percentage of circuits that pass the test and the throughput to the number of circuits that are tested per time unit. The yield is a topic of paramount importance. It is impacted by the process quality of course but also by the ATE accuracy which imposes to take guard-band in the go/no-go decision. Two kinds of error related to yield can imply a revenue loss: false negative and wrong positive. A false negative is a circuit that is thrown away because the ATE failed it, although is was good. These undesirable events are accounted for to compute the yield loss. A wrong positive is a bad circuit that is nevertheless passed by the ATE. This is typically the case with insufficient guard-banding and can be much more costly than a false negative [2]. The metric that accounts for this event is the test escape.

To alleviate the test cost, several possibilities are worth considering [1]: a) increase ATE throughput and b) reduce ATE capital and operational cost (human intervention, energy). The throughput is limited by the test time, the handling time and the number of parallel tests. On the one hand, parallelization and handling time are elements that should not be neglected, but they are greatly dependent on the ATE capabilities and thus must be considered by the ATE suppliers and users. On the other hand, test time can be reduced by proposing alternate solutions to the classical functional tests. As a matter of fact, they can be particularly long as it is the case with Error Vector Magnitude (EVM) or Bit Error Rate (BER) to name but a few. As the technologies scale down, the available frequencies increase and so does the price of the associated test equipment. In addition to being less time-consuming, test procedures would greatly benefit from using low-cost ATE. This implies lowering the test frequencies and thus, devising new test procedures.

Next section focuses on the classical measurements that are used to ascertain DUT specifications.

### **1.3** Measures to be performed

Several measurements can be performed depending on the circuit and the target specifications. In this work we have decided to use Power Amplifiers (PA) as case study. Thus, the following subsections review the main kinds of measurement that are typically performed on a power amplifier. They can be classified into three main categories:

- a. Small signal measurements in order to characterize the linear behavior of the circuit.

- b. Large signal measurements in order to characterize the non-linear behavior of the amplifier under large signal stimuli.

- c. Power measurements for quantifying the energy-wise performances of the circuit.

Other types of measurements can be performed on PAs, such as modulated wave measurements to compute the Adjacent Chanel Power Ratio (ACPR) for instance. This will not be discussed in this thesis since we do not target any specific modulation.

We could have used other circuits with other specifications such as Low Noise Amplifier (LNA), Voltage Controlled Oscillator (VCO), mixer or Phased Locked-Loop (PLL) as case study. Since we focus on PAs, their specifications are not discussed in this section.

#### **1.3.1** Small signal measurements

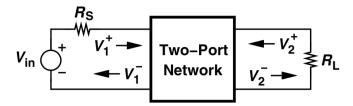

Microwave theory generally uses power quantities instead of voltages and currents [4]. This is due to two main reasons: a) traditionally microwave designs aim at transmitting power between stages and b) high frequency powers are much more easy to measure compared to voltages and currents. To quantify the power transfer, parameters called "scattering parameters" (S-parameters) have been introduced. Let us consider a two-port network with an incident input wave  $V_1^+$ , a reflected input wave  $V_1^-$ , and the same for the output  $V_2^+$  and  $V_2^-$ , as illustrated in Figure 1.1 [4].  $S_{11}$  and  $S_{22}$  respectively represent the accuracy of the input and output matching.  $S_{21}$  represents the gain and  $S_{12}$  the reverse isolation. Their definitions are given by the expressions 1.2.

$$S_{11} = \frac{V_1^-}{V_1^+} \bigg|_{V_2^+=0} S_{12} = \frac{V_1^-}{V_2^+} \bigg|_{V_1^+=0} S_{22} = \frac{V_2^-}{V_2^+} \bigg|_{V_1^+=0} S_{21} = \frac{V_2^-}{V_1^+} \bigg|_{V_2^+=0}$$

(1.2)

Figure 1.1: Illustration of incident and reflected waves for a two-port network [4].

#### 1.3.2 Large signal measurements

For memoryless linear devices, such as passive components, the output voltage y(t) can be expressed as a function of the input x(t) using the following equation [4]:

$$y(t) = \alpha x(t) \tag{1.3}$$

For a memoryless non-linear device, such as a MOS transistor, the input/output characteristic can be approximated by:

$$y(t) = \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t)$$

(1.4)

For a sinusoidal input,  $x(t) = Acos(\omega t)$ , Equation 1.4 can be expressed as,

$$y(t) = \alpha_1 A \cos(\omega t) + \alpha_2 A^2 \cos^2(\omega t) + \alpha_3 A^3 \cos^3(\omega t)$$

(1.5)

$$y(t) = \frac{\alpha_2 A^2}{2} + (\alpha_1 A + \frac{3\alpha_3 A^3}{4})\cos(\omega t) + \frac{\alpha_2 A^2}{2}\cos(2\omega t) + \frac{\alpha_3 A^3}{4}\cos(3\omega t)$$

(1.6)

Under large signal stimuli, the circuit behavior can thus be noticeably different from its small-signal operation. A device non-linearity has various impacts such as harmonic distortion, gain compression, cross modulation or intermodulation. For power amplifiers, gain compression and intermodulation are effects that are typically quantified as part of their specifications.

#### Gain compression

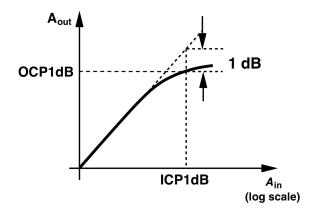

Gain compression phenomenon is highlighted by Equation 1.6, where the gain of the device is  $\alpha_1 + (3\alpha_3 A^2)/4$  at the fundamental frequency. With  $\alpha_1\alpha_3 < 0$  (which is typically the case for common source amplifiers), the gain is reduced as A increases. This gain compression phenomenon is quantified by the 1 dB compression point, which corresponds to the signal amplitude at which the gain is 1 dB below its nominal value. The 1 dB compression point can be input or output referred, respectively shortened  $ICP_{1dB}$  and  $OCP_{1dB}$ . The following expression is used to calculate the  $ICP_{1dB}$ .

$$ICP_{1dB} = \sqrt{0.145 \left| \frac{\alpha_1}{\alpha_3} \right|} \tag{1.7}$$

Figure 1.2 shows the output signal  $A_{out}$  as a function of the input signal  $A_{in}$  in logarithmic scale [4]. This theoretical analysis has been carried out with voltages quantities, but the concept is the same with powers.

Figure 1.2: Definition of 1 dB compression point.

#### Third intercept point

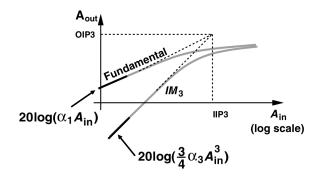

Intermodulation (IM) is a phenomenon that must be taken into account for wireless communications. Let us consider a signal of interest at  $\omega_0$  and two interferes at  $\omega_1$  and  $\omega_2$  applied to a non-linear system. According to 1.4, third order intermodulation products (IM3) will appear at  $2\omega_1 \pm \omega_2$  and  $2\omega_2 \pm \omega_1$ . If the angular frequency of one of this four IM3 products equals  $\omega_0$ , it will corrupt the signal of interest.

A typical way to quantify this phenomenon is the "two-tone" test. Two sinusoidal signals of same amplitude are applied to the device input. The amplitude of the IM3 products are thus

$$A_{IM3} = 20 \log(\frac{3}{4} \frac{\alpha_3}{\alpha_1} A^2) \ dBc, \tag{1.8}$$

where the unit dBc denotes that the IM3 product amplitude is normalized and relative to the one of the carrier (A).

Thus, as the input amplitude increases ( $\propto A$ ), the relative IM increases even more ( $\propto A^3$ ). The third intercept point (IP3) is the amplitude at which the IM3 products signal levels are as high as the fundamental. It is based on an extrapolation of the device small signal behavior, without any gain compression. It can be input (IIP3) or output (OIP3) referred and is calculated using the expression 1.9. However, due to gain compression, it is actually impossible to directly measure a device IP3. It is extrapolated using a "two-tone" test as illustrated in Figure 1.3 [4].

$$IIP3 = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|} \tag{1.9}$$

Figure 1.3: Definition of IP3 (for voltage quantities).

Using 1.7 and 1.9, we obtain a most useful formula (1.10). It is only true if the third-order approximation stands for the system since higher-order terms have been neglected.

$$IIP3 \approx ICP_{1dB} + 9.6 \ dB. \tag{1.10}$$

#### **1.3.3** Power efficiency

Power amplifiers are usually the circuits that consume the main part of a transmitter power. Two metrics can be used to quantify the power consumption. The efficiency is defined as

$$\eta = \frac{P_{load}}{P_{supply}},\tag{1.11}$$

where  $P_{load}$  is the power delivered to the amplifier load (the antenna) and  $P_{supply}$  is the power drawn from the power supply. The power added efficiency (PAE) takes into account the input power  $P_{in}$  that is provided to the PA. It is defined as

$$PAE = \frac{P_{load} - P_{in}}{P_{supply}}.$$

(1.12)

### **1.4** Alternatives to conventional test

As already mentioned, the test equipment cost is a major limitation for RF/mm-wave circuits. Moreover, testing high frequency devices can require long test times and complex setups. Thus, several solutions have been proposed to tackle these issues. They can be classified in four main tendencies: structural test, built-off test, built-in test and machine learning indirect test. Their principle is explained in the next subsections.

#### 1.4.1 Structural test

The structural test approach is similar to digital test procedure and relies on fault modeling. However, such models are difficult to build for analog and RF circuits [5]. This is due to the variety of components that can be used, their complex interactions and the faults that are modeled: catastrophic faults which correspond to short/open circuits and parametric faults which correspond to excessive process variations. The main difficulty for analog circuits is that process variations combinations can result in a specification violation, especially for demanding specifications. In this line, authors in [6] propose a suitable solution for RF circuits.

#### 1.4.2 Built-Off Test

The versatility of ATEs may not be required in high volume production phase as it is the case during the development phase [7]. As a matter of fact, the needs are very different for these two steps. During the development phase, testers must handle wide ranges of powers and frequencies to allow changes in the way the test is performed. On the contrary, during the production phase, only specific combinations of frequencies and powers are needed since the test procedure is well set up. In this line, built-off test proposes to move some of the test equipment features on a custom board. The involvement of the ATE in the test procedure can vary depending on the board abilities, the DUT and the ATE itself. In certain cases a low cost ATE can be used as in [8].

#### 1.4.3 Built-In Test

Built-In Test (BIT) or Built-In Self-Test (BIST) proposes to go even further and embed test features on-chip, with the DUT. This can drastically simplify the test procedure and required equipment. However, several drawbacks of analog BIST techniques still limit their adoption. In [7], the authors especially point out the extra die area required for the BIST circuitry and the extra package cost due the dedicated pins and wire-bondings for test purposes. The need to co-design the DUT with its BIST circuitry is also an important limiting point since this may be time-consuming, costly and may degrade the DUT performances. Moreover, the BIST must be accurate enough to provide relevant information about the DUT.

Thus, for a BIST technique to be really appealing, it must (a) provide a simpler and cheaper way to test the circuit compared to classical functional tests while it should (b) not imply a noticeable area overhead, (c) avoid the need to co-design and (d) be accurate enough.

A large number of BIST techniques have already been proposed. The main methods may use: DC sensing, envelope detector, loopback test, Oscillation Based Test (OBT), embedded VNA, thermal measurement or non-intrusive dummy circuits. These techniques are further discussed in Chapter 2.

#### 1.4.4 Machine Learning Indirect Test

Before presenting machine learning indirect test, the following subsection briefly introduces basics of machine learning knowledge.

#### Introduction to machine learning

Machine learning is a subfield of computer science and more specifically of artificial intelligence. The term refers to algorithms written in such a way that they can learn how to solve a problem without being explicitly programmed for it. One of the first consequent works in this field was a program designed to learn how to play a game of checkers better than the person who coded it [9]. Nowadays the term "machine learning" is used to describe a wide variety of algorithms with various purposes such as email filtering, web-page ranking in search engines, pattern recognition (face, hand-written characters, etc) or financial market analysis to name but a few. Typically, there is a systematic two-step procedure to use a machine learning algorithm. In the first stage, the algorithm learns from the data it has been given. It is said that the algorithm is learning or is being trained, hence the name learning or training stage. Then, when the algorithm has been trained, it can be used for the purpose it was conceived for. Two main kinds of algorithms can be distinguished depending on the way the learning is performed, in a supervised or unsupervised manner.

**Supervised algorithms** They are devised to learn on both input and output data. Once the algorithm has been trained, it is able to predict the output based solely on input data.

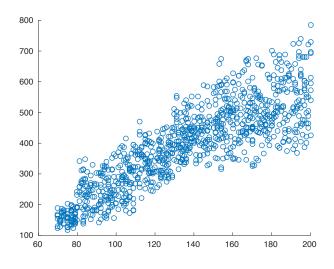

Let us consider a simple example where we have a data base of houses with their price and area. The problem we wish to solve here is getting the price of a house knowing only its area, which is a typical regression problem. To this end, the data base is fed into the algorithm for it to learn the link that exists between the price and the area. The trained algorithm is basically a regression function/model. It can be used to predict the price of an other house, that is not in the initial data base, knowing only its area. In other words, the model is used to regress the output(s) from the input(s), that is the price from the area in this example.

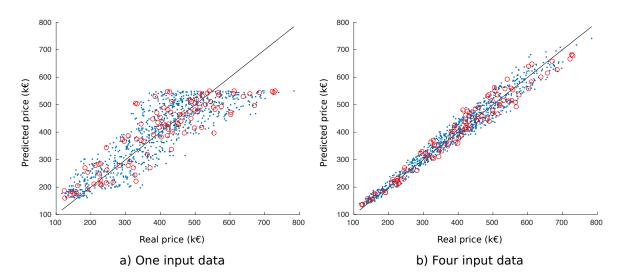

The problem here has only two dimensions, so it is quite straightforward to represent it visually. In this line, Figure 1.4 displays the price versus the area of a few houses. Now if we train a machine learning algorithm on this data in order to build a regression model, we can plot Figure 1.5.a that shows the predicted value of the houses versus their actual price. Blue dots correspond to the data that are used to train the machine learning algorithm and red circles to the data set appart and used to ascertain its accuracy. This scatter plot is an excellent visual way to represent the model accuracy. It is all the more convenient when the problem dimensionality increases. Suppose for instance that we have other relevant information about the houses such as their age, the garden area and the presence of a swimming pool. In this case, we can leverage four variables to predict the price of the house. This five dimension regression problem would be impossible to represent in a similar way as in Figure 1.4. However, the scatter plot of the predicted versus the real price of the house would be a really good indicator of the prediction accuracy. With this extra *relevant* data we can expect a more accurate

prediction, visually represented by Figure 1.5.b. The relevance of the information is crucial. Imagine for instance that instead of the age, the garden area and the presence of a swimming pool, we provide a non relevant information, let us say the hair color of the previous owner. This data is clearly useless for the price prediction and may disturb the learning, leading to a degraded accuracy. Quantitatively speaking, we can compute the Root Mean Square (RMS) error of the model that corresponds to the average distance between the predicted and the real output target, the price of the house in this example. Mathematically speaking, the RMS error  $\epsilon_{RMS}$  can be computed using Equation 1.13 where *n* is the size of the data (the number of houses in this example) and  $T_{real}$  and  $T_{predicted}$  respectively refer to the real and predicted target values (the price of the house).

$$\epsilon_{RMS} = \sqrt{\frac{\sum_{i=1}^{n} \left(T_{real \, i} - T_{predicted \, i}\right)^2}{n}} \tag{1.13}$$

The RMS error of the regression function can be computed on the data that are used for the training to check that the algorithm is learning correctly. However, the model accuracy in itself must be evaluated on independent data i.e. data that was not used to train the algorithm (corresponding to the red circles). Thus, in this work, when we mention the model RMS error, or simply the model error, we refer to the RMS error that is computed on independent data, set appart for verification purposes.

Figure 1.4: Machine learning example: price versus area.

Supervised machine learning algorithms can also be used to solve classification problems, such as spam email filtering. In this case, the algorithm learns on a data base composed of emails with associated boolean values representing whether they are spam or not. Once the algorithm has been trained, it is able to sort out incoming new emails and directly trash the spams. Overall, supervised machine learning algorithms are especially flexible and can be easily implemented to solve a large variety of complex non-linear problems.

In this thesis we will use a classical supervised machine learning algorithm for regression purposes.

Figure 1.5: Machine learning example: predicted price versus real price.

**Unsupervised algorithms** Also referred as clustering algorithms, they are aimed at finding categories, patterns in large data bases, without any idea of the output result. This technique is especially leveraged in biology, medicine, genomics or in advertising for market segmentation. We will not use this kind of algorithm in this work.

#### Machine learning indirect test

Machine learning indirect test (MLIT), first introduced as the so-called alternate test strategy in [10], is a possible solution to alleviate the complexity and cost associated to testing mm-wave circuits. The aim of machine learning indirect test is to replace the measurement of complex functional specifications by a set of simpler measurements, also called signatures. This is a multivariate regression problem, so in mathematical terms, this means we need to build a regression function  $f_{S \to P}$  between the signatures space  $\{S_1, S_2, \ldots, S_l\}$  and the performances space  $\{P_1, P_2, \ldots, P_N\}$  as

$$f_{S \to P} : [S_1, \dots, S_l] \to [P_1, \dots, P_N].$$

(1.14)

This function can be easily obtained by training a supervised machine learning algorithm to map the signatures to the specifications.

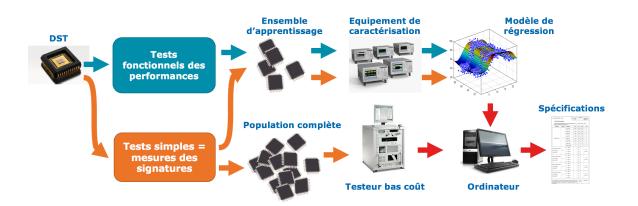

The usual approach to machine learning indirect test is illustrated in Figure 1.6. The procedure is developed in two stages: a learning stage, and a testing stage. During the learning stage, both performances (blue path) and signatures (orange path) are measured from a set of training devices. Then, a machine learning algorithm is trained over the two sets of measurements to build a mapping model. This function,  $f_{S \rightarrow P}$  as it is defined in equation 1.14, can be used to predict the performances based on the signatures. In the production/testing stage, signatures are measured for each DUT, and performances are simply inferred using the mapping model obtained in the previous stage. This indirect test

framework has the benefit of a simple interpretation of the test outcome since the estimated specifications are directly compared to their test acceptance windows in a conventional manner. Moreover, indirect measurements are devised to be cheaper than the direct measurement of functional specifications.

Figure 1.6: Machine learning indirect test principle.

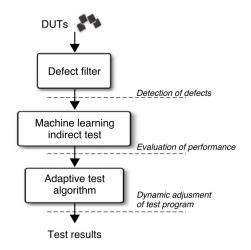

For a practical use of machine learning indirect test, some extra steps should be added to the procedure. Figure 1.7 shows a typical flow for this test paradigm [11]. The first step aims at screening out outliers, circuits that have undergone a catastrophic spot defect. Then, regression models can be trained to learn the correlation between the signatures and the DUT specifications, as explained in the previous paragraph. A third phase would be to propose adaptive algorithms which would reduce even more the test time and cost.

Figure 1.7: Generic test flow for machine learning indirect test [11].

#### 1.5. CALIBRATION AGAINST PROCESS VARIATIONS

#### 1.4.5 Conclusion

To tackle the complexity and cost associated with testing RF/mm-wave circuits, a great variety of techniques exist. The choice of one above the others depends on the DUT and the conventional test methods that are to be replaced. Overall, there is not yet a generic method that may work for any kind of RF/mm-wave circuit. In our opinion, BIST and machine learning indirect test offer great possibilities that can be combined to automate the implementation of a low-cost test procedure on a variety of circuits.

A complete test method should be able to detect catastrophic faults, that may cause a functional failure, as well as process variations that can induce suboptimal performances. In addition to providing the go/no-go decision, the test outcome can further be used to make up for suboptimal performances. This refers to calibration methods, that are introduced in the next section.

## 1.5 Calibration against process variations

#### 1.5.1 Introduction

Generally speaking, calibration methods aim at tuning a device after its fabrication to improve its performances. The goal may be to improve the fabrication yield, to obtain the best performance tradeoff or to compensate for aging or environmental effects. The calibration relies on dedicated tunable elements, usually called tuning knobs, that allow the trimming of the device.

In [12], authors distinguish three categories of such techniques:

- Calibration that can compensate for static variations: catastrophic or parametric defaults.

- Healing that can compensate for static variations and quasi-static ones: aging, environment.

- Adaptation that can compensate for static, quasi-static and dynamic variation such as fast modifications of the operating conditions, the channel quality, etc.

Such procedures can be implemented off-chip or on-chip with a great variety of approaches which lead to many calibration/healing/adaptation methods. Whatever the selected method, the first step is to quantify the phenomenon that is to be compensated for (process variations, temperature, impedance variation, aging, ...). Once this has been done, calibration/healing/adaptation can be performed.

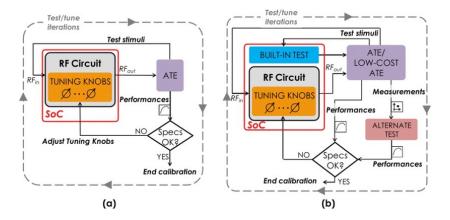

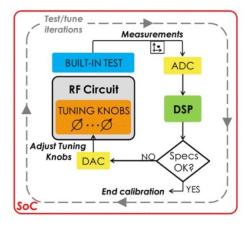

Calibration methods can be divided into iterative test & tune and one-shot approaches [13]. Iterative approaches are more straightforward. The simpler implementation would be a tunable circuit without any test capabilities. The ATE would be used to test & tune the circuit, but obviously this would require prohibitive long test times. Providing BIST capabilities and/or alternate measurements to the device seems to be a more reasonable choice, thus allowing to use low-performances ATE. These two approaches are illustrated in Figures 1.8 a) and b) [14].

In this thesis, we focus on calibration for process variations and more precisely on one-shot methods which are appealing possibilities, easily compatible with machine learning indirect test.

Figure 1.8: a) Iterative calibration using external ATE, b) Iterative calibration using low-cost ATE [14].

#### 1.5.2 One-shot statistical calibration

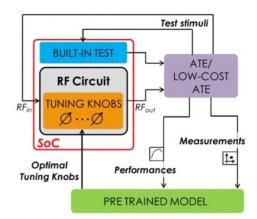

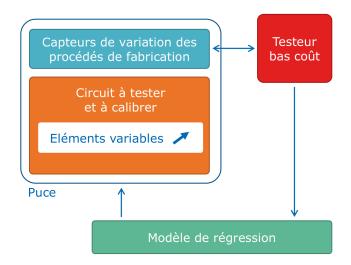

This subsection provides a brief review of the operation of a generic one-shot statistical calibration strategy which operation principle is illustrated in Figure 1.9 [14].

Figure 1.9: One-shot calibration principle [14].

Let us consider a circuit under calibration with a set of N specifications  $\{P_1, P_2, \ldots, P_N\}$  and k tuning knobs  $\{T_1, T_2, \ldots, T_k\}$ . The main goal of statistical calibration techniques is to find a set of simple measurements (i.e. signatures)  $\{S_1, S_2, \ldots, S_l\}$  such that a regression function  $f_{T,S\to P}$  can be built as

$$f_{T,S \to P} : [T_1, \dots, T_k, S_1, \dots, S_l] \to [P_1, P_2, \dots, P_N].$$

(1.15)

Once such a regression function has been determined, and by measuring vector  $\{S_1, \ldots, S_l\}$  on a fabricated sample, function  $f_{T,S\to P}$  can be used for exploring the space of  $\{T_1, \ldots, T_k\}$  and maximize the performances  $\{P_1, \ldots, P_N\}$ . The regression function  $f_{T,S\to P}$  is typically obtained using a supervised machine learning algorithm.

#### 1.6. CONCLUSION

This procedure is divided into two stages: in a first stage –the training stage– for a population of circuits (the training set) both the performances and the signatures under different combinations of tuning knobs are extracted. A machine learning algorithm is then trained to regress the circuit performances from the signatures and tuning knob states. Once the training has been performed, we can take advantage of this regression model (function  $f_{T,S\rightarrow P}$  referred to as "pre-trained model" in green in Figure 1.9) to actually perform the calibration to circuits in the production line. During the second stage –the calibration stage– only the set of signatures is measured (typically for the typical tuning knobs combination) and the machine learning model previously obtained is used to determine the best combination of tuning knobs. The process has the advantage of avoiding iterative calibration loops, since the regression function allows finding the optimum calibration point in one shot. Moreover, it is clear that this calibration approach is based on the machine learning indirect test paradigm.

### 1.6 Conclusion

In this chapter we have introduced RF/mm-wave test. The classical approaches of production testing have been reviewed and the main challenges pointed out. The cost of test equipment and the test time are two major hurdles when trying to reduce the overall test cost. Consequently, alternate solutions such as structural test, built-off test, built-in self-test or machine learning indirect test have been presented. We have also given an insight into calibration strategies to enhance DUT performances after fabrication and more especially into one-shot statistical calibration. Next chapter reviews BIST and calibration approaches that have been proposed in the litterature.

# Chapter 2

# State of the art

Continuous demand for high data-rate transmissions and high-speed systems has led the industry towards mm-wave frequencies. This trend is supported by the continuous scaling of CMOS technologies that enables the fabrication of transistors with transition frequencies higher than 200 GHz. While such advanced fabrication processes allow the integration of mm-wave circuits, they are also especially prone to large process variations that may result in substantial performance degradation and low fabrication yield. Hence, integrated RF and mm-wave circuits require extensive production testing to evaluate the performance of the fabricated parts. However, testing such circuits in the production line is especially demanding since test procedures often involve complex at-speed measurements that require costly dedicated ATE and long test times. Possible solutions to tackle these issues have been proposed and are reviewed in this chapter. In this sense, we have organized the existing literature on the topic in two sections. The first one focuses on BIST while the second one reviews calibration techniques.

### 2.1 Built-In Self-Test

Built-in self-test strategies for analog and RF circuits are as diverse as the DUTs they target. This section summarizes the main contributions in this prolific research topic. They are presented in two groups whether they are intrusive or non-intrusive methods.

#### 2.1.1 Intrusive methods

Many works have addressed intrusive BIST. In most cases the test circuitry uses one or several of the following elements: envelope detector, DC voltage probe, current sensor, loopback method or oscillation based test. These approaches are reviewed in the followings subsections.

#### Envelope detector, DC probes and current sensor

These kinds of sensors provide DC or low frequency signals that are easy to understand and process. Envelope detectors can be used to monitor the RF/mm-wave power in critical nodes. In [15], the gain of a 5 GHz LNA is extracted thanks to envelope detectors. The principle is quite simple: one detector senses the input RF signal while another monitors the output signal. The latter can then be variably attenuated and compared to the input envelope. A comparator is thus used to determine whether the gain of the attenuator is low enough to compensate for the LNA gain. The implementation of this approach has a very low overhead of only 7.6% of the overall active area and the gain extraction error is less than 1 dB in measurement. Moreover, the envelope detectors do not imply any design modification for the DUT due their high input impedance at the working frequency. In [16], the authors present a broadband (900 MHz to 2.4 GHz) amplitude detector that can be used for gain and  $ICP_{1dB}$  prediction. Measurements performed on a 1.6 GHz LNA show an accuracy better than 1 dBm for  $ICP_{1dB}$  extraction. The detector has a low area and it is estimated that 10 detectors would account for less than 5% of the area of a complete transceiver.

Several architectures of envelope detectors exist, depending on the technology, the target performances and the frequency band. Detectors for mm-wave frequencies are difficult to design within a limited surface and may negatively impact the DUT performances. Though, in [17] a small RMS Schottky diode detector is detailed. It allows measurements in the 80-110 GHz band for an area overhead of just 340  $\mu m^2$ . To avoid the co-design of the DUT alongside with the envelope detector, which may be necessary for mm-wave DUTs, low-coupling coefficient couplers can be leveraged as in [18]. The authors use -20 dB couplers at the input and output nodes of a 28 GHz PA to take off a very small amount of power and quantify it. Aside from removing the need to co-design the detectors with the PA, this approach provides immunity against load impedance mismatch.

Envelope detectors can also be used as part of a more thorough test framework including voltage and current sensors. DC probes or current sensors are used to check the DC operating point of the DUT. Since a good DC operating point is not a sufficient condition for the DUT to work properly, tests at its operating frequency have to be carried out. This is the role of envelope detectors and dynamic current sensors. A dynamic current sensor is used to extract a signature of the power supply dynamic current. These sensors have been used successfully in [5] to predict the conversion gain, compression point, third order intercept point and noise factor of an RF front-end (LNA and VCO). Performance prediction made use of machine learning algorithms to build mapping models between the sensors output and the target performances. In [19], a similar technique is applied to a 2.4 GHz QPSK transceiver to implement a low cost EVM BIST. 3 DC voltage probes, 2 envelope detectors and 1 dynamic current sensor are used to predict the EVM with a 5.8% error. This kind of approach have a very low area overhead and give very good results in simulations. However, they require to co-design the test circuitry with the DUT, which can be a major blocking point for mm-wave devices. Moreover, DC probes or current sensors are not straightforward to implement. DC probes basically consist in a large resistor connected to an internal node, but as the frequency increases it becomes far less ideal and can affect the circuit behavior. Current sensors can also affect the device performances and their design can be a complex task [5, 18].

Another paradigm exploiting an envelope detector is the signature based test. In [20], two high-

#### 2.1. BUILT-IN SELF-TEST

frequency close tones are fed into a 2.45 GHz LNA which output is connected to an envelope detector. The signal is processed to extract the main specifications: S-parameters, input and output impedances, noise factor, intermodulation, compression point. A machine learning algorithm is used to learn the correlation between the envelope detector output and the performances. The envelope detector adds a real improvement compared to a traditional signature based approach since the output signal is low frequency, and thus much more easy to process.

An important point for these kind of approaches is the RF/mm-wave signal source. In [15, 16] external sources are used, which is suitable for RF DUTs, but can be much more costly for mm-wave ones. Other works in the same field have led to different solutions. For instance in [21], the authors take advantage of a local oscillator to feed an integrated millimeter-wave radar receiver. In [22], a 60 GHz LNA is tested using the loopback technique which alleviates the need of RF/mm-wave sources as discussed next.

envelope detectors, alone or together with DC probes and DC current sensors, have been successfully leveraged in many works to predict various performances of devices. Overall, these sensors provide DC information that are easy to extract, the results accuracy is good and the area overhead is not too critical, especially for RF DUTs. Nevertheless, although co-design is not mandatory for all RF circuits, it is unlikely to be the same for mm-wave ICs. The use of low-coupling coefficient couplers with envelope detectors can partially alleviate this drawback, but requires extra area.

#### Loopback

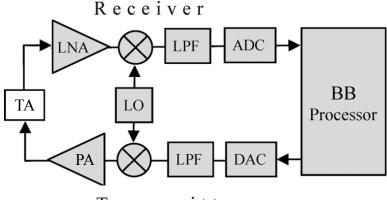

A simple idea for testing transceivers is to connect the transmitter (TX) to the receiver (RX). In this configuration, the need of an RF source is removed and a whole set of functional tests can be easily performed. Recent works still focus on this topic, such as [23], [24] where the concept is used for mm-wave transceivers BIST or to test and calibrate a 2.4 GHz transceiver [25]. Figure 2.1 shows the diagram of a basic direct loopback implementation [26].

Transmitter

Figure 2.1: Direct loopback setup for integrated transceiver test.

This is a very appealing method and yet it implies several problems. Despite its apparent simplicity,

it may incur a noticeable area overhead, require co-design and may not be able to fully differentiate transmitter and receiver impact in the overall performance. Besides, the absence of radio channel implies to find a way to reduce the signal power at the input of the RX chain to be in the dynamic range of the LNA. A test attenuator (TA in Figure 2.1) can be inserted but its design may be challenging. Another option is to remove the PA in order to reduce the power at the LNA input, but of course the PA is not tested. An extra mixer can also be inserted between TX and RX for certain types of transceivers [26].

The loopback configuration can be setup along side with envelope detectors at critical nodes for a more complete test procedure as in [22]. Performances such as gain, gain compression, intermodulation, I/Q mismatch can be easily extracted.

#### **Oscillation Based Test**

Oscillation Based Test (OBT), first introduced in [27] for analog and mixed-signal circuits, proposes to use the DUT to create an oscillating system. Defects will cause drift in the oscillation frequency (and amplitude) making it a convenient way to test a circuit. Figure 2.2 presents a block diagram which illustrates this method [28].

Figure 2.2: Block diagram showing the required modifications to convert a DUT into an oscillator [28].

In [29], a practical implementation of this technique is presented for a 2.4 GHz LNA. The authors take advantage of a frequency-selective on-chip power detector to sense the operating frequency as well as the output power. They achieve a 60 % fault coverage in simulation. However, the BIST circuitry implies performance degradations that cannot be neglected of around 0.5 dB for the noise factor and 2 dB for the gain. OBT can also be applied to mm-waves circuits such as in [30] where the concept has been implemented as a BIST solution for a 60 GHz phase shifter. In this work, the phase shifter is used as the resonant element of a 14-17 GHz VCO, whose output frequency is an image of the phase shift.

OBT is an interesting solution for testing RF and millimeter-wave ICs since the test output is sensitive to the performance degradation mechanisms and is simple to exploit. Nevertheless, the extracircuitry and design modification that may be required represent major challenges that may limit the adoption of OBT for high frequency circuits.

#### Embedded VNA and spectrum analyzer

Some works propose to design on-chip miniature VNA or spectrum analyzer. The area overhead can be important but they offer a great flexibility and variety of test possibilities. A key advantage for mm-wave circuits is that it alleviates the need of de-embedding procedures. In [31], authors present a 33 MHz - 3 GHz spectrum analyzer which can be used for on-chip PLL characterization. It presents a dynamic range of 60 dB and a resolution of 30 kHz with an area of around 0.27 mm<sup>2</sup>. [32] introduces a dual-port 50-100 GHz VNA that can be used to perform measurements on a wide variety of mm-wave circuits or to provide BIST capabilities. The presented VNA achieves a dynamic range of 55 - 72.5 dB at an IF RBW of 100 kHz and a 3  $\sigma$  phase error of 0.3°. The work in [33] proposes a dedicated BIST circuitry for evaluating the S-parameters of phased-arrays with an accuracy better than 1 dB in amplitude and 7° in phase. Although promising silicon results have been reported, the complexity and area overhead of the on-chip instrumentation is high and careful co-design with the DUT is necessary. Overall, this kind of approaches have a great potential but suffer from their complexity and area. They are not suited for all kind of integrated devices though they can be relevant for specific cases.

#### 2.1.2 Non-intrusive methods

Though really relevant, most intrusive BIST techniques suffers from a major drawback: they require to co-design the test circuitry with the DUT and are architecture-dependent. An exception would be embedded VNAs, but the extra area they require may be a stumbling block for most DUTs. Several works thus target non-intrusive test approaches.

#### **Thermal measurement**

Non-intrusive temperature sensors can be used to detect defects within a DUT. A major advantage of temperature sensors is that they are able to detect catastrophic defects in the components they monitor in a non-intrusive way. When the DUT is powered on, part of the electric power is dissipated thermally by Joule effect and conducted through the substrate. Sensors can thus monitor the thermal evolution of several locations of the DUT. In [34], thermal sensing is applied to a 2.4 GHz LNA to monitor its DC operating point and RF behavior. In [35], temperature sensors are used to evaluate the thermal noise level of a 60 GHz LNA. In [18], they are used to measure the DC power dissipation of a 28 GHz PA. This approach is especially interesting but it needs to be used together with another test technique to provide a thorough test outcome.

#### **Dummy circuits**

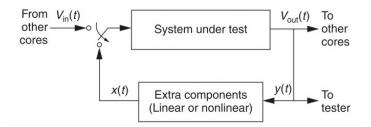

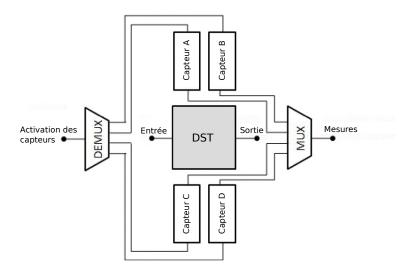

This approach is sensitive to parametric process variations (lot-to-lot, wafer-to-wafer, die-to-die). The idea is to monitor these variations by means of dummy analog elements, similar to the ones used in the DUT. By placing them next to their kind, they would undergo the same process quality. The choice of the duplicate analog elements is the crucial point in this approach. A monitor can be a

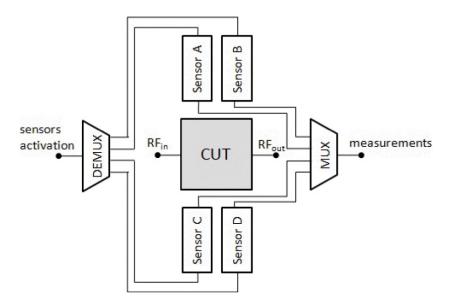

complete analog stage or simple components called Process Control Monitors (PCM). Then, DC and low frequency measurements on these sensors, that are not electrically connected to the DUT, are used as test signatures for training machine learning regression models. This method is thus part of the so-called "non-intrusive indirect test" and relies on process-aware sensors. The concept was first proposed in [36] for mixed-signal test applications, and later extended to the RF and mm-wave domain in [37, 38]. Figure 2.3 illustrates this test paradigm [37].

Figure 2.3: Block diagram of a generic non-intrusive indirect test based on process-aware sensors [37].

In [37], several analog stages and PCMs are used successfully to predict the gain, NF, 1 dB compression point and IIP3 of 2.4 GHz LNA. The average prediction error is excellent: less than 0.1 dB for gain and NF, less than 0.2 dB for the compression point and IIP3. In [38], the approach is applied to a 60 GHz LNA. Considering the different sensitive elements in the DUT, several dummies are chosen: common source stage, cascode stage, N+ polysilicium resistor, MOM capacitor, transistor and micro-strip transmission line. They allow the prediction of S-parameters, noise factor and third order intercept point. In simulation the results are good for most specifications with a RMS error of 0.5 dB for  $S_{21}$  and  $S_{11}$ , 0.1 dB for NF and 0.3 dB for IIP3. Results for  $S_{22}$  are not as good as for the other specifications with a RMS error of 1.7 dB and a maximum error of 4.1 dB.

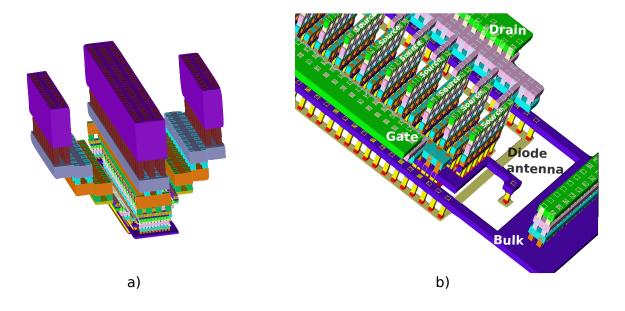

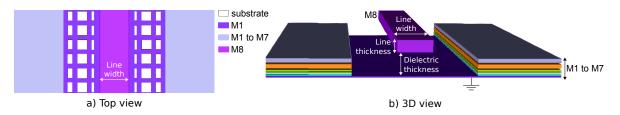

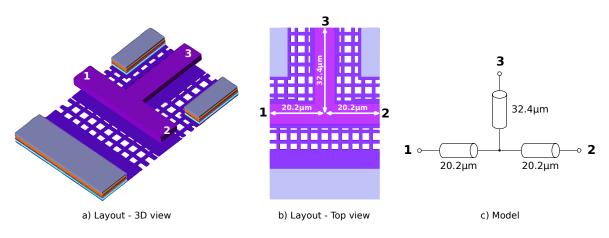

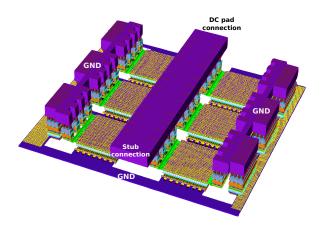

Another approach, based on the same paradigm, is presented in [39] where a 80 GHz LNA is tested by the intermediate of a ring oscillator. Since the oscillator undergoes the same process variations as the transistors it is designed next to, any drift in the size of the transistors results in a drift in the oscillating frequency. As the frequency varies almost linearly with the width of the MOS transistors, it is an excellent process variation monitor which output is easy to measure. However, in a fabrication process many of the transistor features can vary and not only its width, so this study is a little too simplistic.