# Time-to-Digital Conversion based on a Self-Timed Ring Oscillator

Assia El Hadbi

### ► To cite this version:

Assia El Hadbi. Time-to-Digital Conversion based on a Self-Timed Ring Oscillator. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes; Institut national des postes et télé-communications (Rabat), 2019. English. NNT: 2019GREAT071. tel-03132550

# HAL Id: tel-03132550 https://theses.hal.science/tel-03132550v1

Submitted on 5 Feb 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE

Pour obtenir le grade de

### DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

préparée dans le cadre d'une cotutelle avec l'Institut National des Postes et Télécommunications (INPT), Rabat, Maroc.

Spécialité : Nano Électronique & Nano Technologies

Arrêté ministériel : 25 mai 2016

Présentée par

# Assia EL HADBI

Thèse dirigée par Laurent FESQUET et codirigée par Oussama EL ISSATI

préparée au sein du Laboratoire Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intègres (TIMA) dans l'École Doctorale Électronique, Électrotechnique, Automatique & Traitement du Signal (EEATS),

et du Laboratoire Systèmes de Télécoms, Réseaux et Services (STRS) dans le Centre d'Étude Doctorales Télécoms et Technologies de l'Information (CEDoc 2TI).

# Time-to-Digital Conversion based on a Self-Timed Ring Oscillator

Thèse soutenue publiquement le 20 Novembre 2019, devant le jury composé de :

M. Skandar BASROUR Professeur des Universités, Université de Grenoble Alpes, Président M. Dominique DALLET Professeur des Universités, Bordeaux INP, Rapporteur Mme Patricia DESGREYS Professeur des Universités, TELECOM ParisTech, Rapporteur M. Wilfried UHRING Professeur des Universités, Université de Strasbourg, Rapporteur **M. Laurent FESQUET** Maître de Conférences HDR, Grenoble INP, Directeur de thèse M. Oussama EL ISSATI Professeur Habilité, INPT, Co-Directeur de thèse M. Abdelkarim CHERKAOUI Directeur Technique, HawAI.tech, Examinateur M. Olivier ROSSETTO Maître de Conférences HDR, Université de Grenoble Alpes, Invité

This thesis has been supported by "Région Auvergne Rhône-Alpes"

ISBN: 978-2-11-129258-1

To my family ...

ISBN : 978-2-11-129258-1

# Acknowledgments

"Même si je suis convaincue que les mots ne suffisent pas pour exprimer mes remerciements, je souhaite au moins laisser quelques lignes pour exprimer ma gratitude envers les gens qui m'ont aidé à accomplir ce travail.

Je tiens, tout d'abord, à remercier chaleureusement mes deux encadrants M. Laurent FES-QUET et M. Oussama EL ISSATI. Oussama, je te remercie d'avoir confiance en moi dès le premier jour. Tu n'étais pas seulement un encadrant mais aussi un coach, un ami et un frère. Je te remercie pour le temps que tu m'as accordé pour le travail de cette thèse. Laurent, je te remercie de m'avoir accueillir dans ton équipe et de m'offrir les moyens nécessaire pour la réalisation des travaux.

J'ai de la chance d'avoir ces deux encadrants car ils sont les meilleurs!

Je remercie également les membres du jury : M. Dominique DALLET, Mme. Patricia DES-GREYS et M. Wilfried UHRING qui m'ont fait l'honneur d'être les rapporteurs de cette thèse, ainsi que M. Skandar BASROUR, le président du jury et M. Olivier ROSSETO d'être notre invité.

Je remercie aussi M. Abdelkarim CHERKAOUI d'être l'examinateur de cette thèse mais aussi pour ses efforts d'encadrement et d'accompagnement pour les premiers pas du projet. Dans ce cadre, je tiens à remercier également, M. Jean SIMATIC, qui n'a pas hésité de venir en aide et de discuter pour avancer les travaux de recherche. Ensuite, j'adresse mes remerciements à tous mes collègues du travail, (doctorants, ingénieurs, stagiaires..) à TIMA, CIME NANOTECH et au CEDOC 2TI à l'INPT. Un grand merci à mes amis à Grenoble qui sont devenus ma famille en France.

Enfin, c'est difficile de remercier ma famille car ce n'est pas toujours suffisant. Un super grand merci à ma très chère famille! A ma mère, mon père, ma sœur et son mari, mon frère qui m'ont toujours supporté moralement pour faire face à la vie d'un thésard et qui ont contribué à aboutir à ce travail, de près ou de loin."

Merci à vous tous

# Table des matières

| 1 | Intr | oductio      | n           |                                                | 1  |  |  |  |

|---|------|--------------|-------------|------------------------------------------------|----|--|--|--|

|   | 1.1  | Contex       | t and Mot   | tivations                                      | 1  |  |  |  |

|   | 1.2  | Thesis       | contributi  | ons                                            | 2  |  |  |  |

|   | 1.3  | Thesis       | overview    |                                                | 4  |  |  |  |

| 2 | Stat | e-of-the     | -Art on T   | ime-to-Digital Converters                      | 5  |  |  |  |

|   | 2.1  | Introduction |             |                                                |    |  |  |  |

|   | 2.2  | Time-t       | o-Digital   | Converters : key performance metrics           | 7  |  |  |  |

|   |      | 2.2.1        | Main TD     | DC metrics                                     | 7  |  |  |  |

|   |      |              | 2.2.1.1     | Time resolution                                | 7  |  |  |  |

|   |      |              | 2.2.1.2     | Dynamic range                                  | 8  |  |  |  |

|   |      |              | 2.2.1.3     | Conversion time                                | 8  |  |  |  |

|   |      |              | 2.2.1.4     | Latency                                        | 8  |  |  |  |

|   |      | 2.2.2        | Linear a    | nd nonlinear imperfections                     | 9  |  |  |  |

|   |      |              | 2.2.2.1     | Offset error                                   | 9  |  |  |  |

|   |      |              | 2.2.2.2     | Quantization error                             | 9  |  |  |  |

|   |      |              | 2.2.2.3     | Differential non-linearity (DNL)               | 10 |  |  |  |

|   |      |              | 2.2.2.4     | Integral non-linearity (INL)                   | 10 |  |  |  |

|   | 2.3  | Analog       | g time-to-c | digital converters                             | 10 |  |  |  |

|   |      | 2.3.1        | Analog 7    | ΓDCs based on analog-to-digital converter      | 11 |  |  |  |

|   |      | 2.3.2        | Analog t    | ime-to-digital converters with time stretching | 12 |  |  |  |

|   |      |              | 2.3.2.1     | Single integrator stretching                   | 12 |  |  |  |

|   |      |              | 2.3.2.2     | Dual-slope conversion                          | 13 |  |  |  |

|   |      |              | 2.3.2.3     | Triple-pulse time stretching                   | 14 |  |  |  |

|   |      | 2.3.3        | Conclusi    | ion                                            | 14 |  |  |  |

|   | 2.4  | Fully I      | Digital Tin | ne-to-Digital Converters                       | 14 |  |  |  |

|   |      | 2.4.1        | TDC wit     | th gate-delay resolution                       | 15 |  |  |  |

|   |      |              | 2.4.1.1     | Delay-Line based TDC                           | 15 |  |  |  |

|   |      |              | 2.4.1.2     | Ring Oscillator                                | 16 |  |  |  |

|   |      |              | 2.4.1.3     | Gated Ring Oscillator                          | 18 |  |  |  |

|   |      |              |             |                                                |    |  |  |  |

|   |       | 2.4.2   | TDC with sub-gate-delay resolution        | 19 |

|---|-------|---------|-------------------------------------------|----|

|   |       |         | 2.4.2.1 Vernier based TDC                 | 19 |

|   |       |         | 2.4.2.2 TDC with interpolation technique  | 23 |

|   | 2.5   | Conclu  | usion                                     | 26 |

| 3 | Self- | Timed   | Ring Oscillators and Operation Principles | 29 |

|   | 3.1   | Introdu | uction                                    | 30 |

|   | 3.2   | Funda   | mental concepts of asynchronous logic     | 31 |

|   |       | 3.2.1   | Synchronous logic circuits                | 31 |

|   |       | 3.2.2   | Asynchronous logic circuits               | 32 |

|   |       | 3.2.3   | Handshake protocols                       | 33 |

|   |       |         | 3.2.3.1 Two-phase handshake protocol      | 33 |

|   |       |         | 3.2.3.2 Four-phase handshake protocol     | 33 |

|   |       | 3.2.4   | Asynchronous data encoding                | 34 |

|   |       | 3.2.5   | Micropipeline                             | 36 |

|   |       | 3.2.6   | Basic element : Muller gate (C-element)   | 36 |

|   |       |         | 3.2.6.1 Charlie effect                    | 39 |

|   |       |         | 3.2.6.2 Drafting effect                   | 40 |

|   | 3.3   | Archite | ectural and logical bvehavior             | 40 |

|   |       | 3.3.1   | Self-timed ring oscillator structure      | 40 |

|   |       | 3.3.2   | Tokens and Bubbles abstraction            | 41 |

|   | 3.4   | Tempo   | ral behavior                              | 43 |

|   |       | 3.4.1   | Propagation modes                         | 43 |

|   |       | 3.4.2   | Charlie and Drafting diagrams             | 44 |

|   | 3.5   | Freque  | ency model                                | 47 |

|   |       | 3.5.1   | Occupancy Ratio                           | 47 |

|   |       | 3.5.2   | Frequency curve                           | 47 |

|   |       | 3.5.3   | Oscillation frequency estimation          | 48 |

|   | 3.6   | STRO    | Phase distribution                        | 49 |

|   | 3.7   | Phase   | noise analysis in STRO                    | 51 |

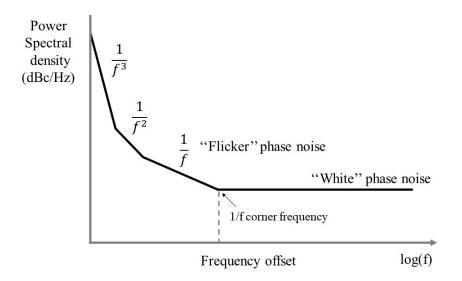

|   |       | 3.7.1   | Phase noise study for oscillators         | 51 |

|   |       | 3.7.2   | Phase noise in STRO                       | 52 |

|   |       | 3.7.3   | Jitter in STROs                           | 53 |

|   | 3.8   | Other t | features of the STRO                      | 54 |

|   |       | 3.8.1   | Robustness to PVT variations              | 54 |

|   |       | 3.8.2   | STRO as programmable oscillator           | 54 |

|   |       | 3.8.3   | STRO in other applications                | 55 |

|   | 3.9   | Conclu  | usion                                     | 55 |

|   |       |         |                                           |    |

| 4 | STR | O-base               | d TDC architecture and implementation               | 57       |  |

|---|-----|----------------------|-----------------------------------------------------|----------|--|

|   | 4.1 | Introdu              | uction                                              | 58       |  |

|   | 4.2 | Propos               | ed TDC                                              | 58       |  |

|   |     | 4.2.1                | STRO-based TDC principles                           | 58       |  |

|   |     | 4.2.2                | Global architecture                                 | 61       |  |

|   | 4.3 | STRO-                | -based TDC readout techniques                       | 63       |  |

|   |     | 4.3.1                | Asynchronous vs. synchronous counters               | 63       |  |

|   |     |                      | 4.3.1.1 The counter issues                          | 65       |  |

|   |     |                      | 4.3.1.2 STRO-based TDC counter implementations      | 67       |  |

|   |     | 4.3.2                | Hamming block                                       | 67       |  |

|   |     | 4.3.3                | M Parity block                                      | 70       |  |

|   |     | 4.3.4                | Computation algorithm                               | 71       |  |

|   | 4.4 | STRO-                | -based TDC simulations using 28 nm FDSOI technology | 71       |  |

|   |     | 4.4.1                | High-level validation                               | 71       |  |

|   |     |                      | 4.4.1.1 Behavioral model                            | 71       |  |

|   |     |                      | 4.4.1.2 Noisy environment                           | 73       |  |

|   |     | 4.4.2                | Analog simulations                                  | 76       |  |

|   |     |                      | 4.4.2.1 STRO results                                | 76       |  |

|   |     |                      | 4.4.2.2 TDC measurements                            | 79       |  |

|   |     | 4.4.3                | Linearity in a noisy environment                    | 80       |  |

|   | 4.5 | Conclu               |                                                     | 81       |  |

| 5 | FPC | - hasa               | d TDC validation                                    | 83       |  |

| 5 | 5.1 |                      |                                                     | 84       |  |

|   |     |                      | -based TDC literature                               | 84       |  |

|   | 5.2 | 5.2.1                | Carry chain                                         | 85       |  |

|   |     | 5.2.2                | Wave union                                          | 85       |  |

|   |     | 5.2.3                | Vernier RO-based TDC                                | 86       |  |

|   |     | 5.2.4                | Pulse shrinking method                              | 86       |  |

|   |     | 5.2.4                | Harmonic ring                                       | 80<br>87 |  |

|   |     | 5.2.6                | Conclusions and discussions                         | 87<br>87 |  |

|   | 5.3 |                      |                                                     | 87<br>88 |  |

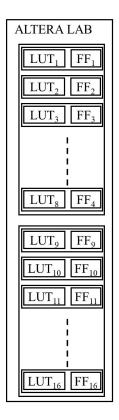

|   | 5.5 | 5.3.1                | EPC A implementation constraints                    | 88       |  |

|   |     | 5.3.2                | FPGA implementation constraints                     |          |  |

|   |     | 5.3.2<br>5.3.3       | STRO implementation                                 | 90<br>01 |  |

|   |     | 5.5.5                |                                                     | 91<br>92 |  |

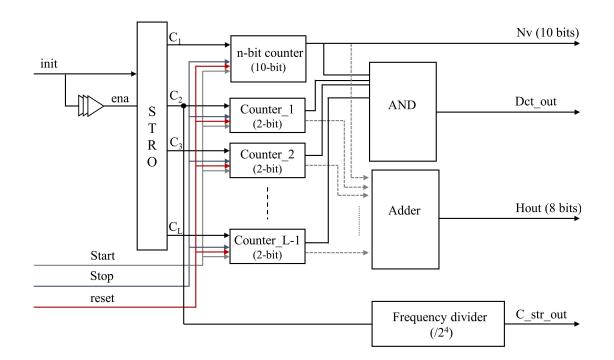

|   |     |                      | 5.3.3.1 Counter implementation                      |          |  |

|   | 5 1 | Even                 | 5.3.3.2 Hamming and M Parity blocks                 | 93<br>94 |  |

|   | 5.4 | Experimental results |                                                     |          |  |

|            |                                       | 5.4.1<br>5.4.2 | The measurement environment          | 94<br>94<br>94<br>96 |  |  |  |  |

|------------|---------------------------------------|----------------|--------------------------------------|----------------------|--|--|--|--|

|            | <i>E E</i>                            | Canala         | 5.4.2.3 Comparison with other TDCs   | 97                   |  |  |  |  |

|            | 5.5                                   | Conclu         | sion                                 | 98                   |  |  |  |  |

| 6          | STR                                   | O-based        | d TDC prototypes                     | 99                   |  |  |  |  |

|            | 6.1                                   | Introdu        | ction                                | 99                   |  |  |  |  |

|            | 6.2                                   | Layout         | of the TDC Prototype Chip            | 100                  |  |  |  |  |

|            |                                       | 6.2.1          | STRO-based TDC architecture          | 100                  |  |  |  |  |

|            |                                       |                | 6.2.1.1 STRO with analog C-element   | 101                  |  |  |  |  |

|            |                                       |                | 6.2.1.2 Counting unit implementation | 102                  |  |  |  |  |

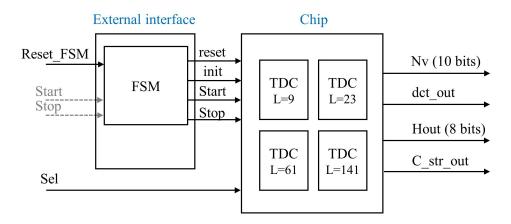

|            |                                       | 6.2.2          | Input/Output interfaces              | 102                  |  |  |  |  |

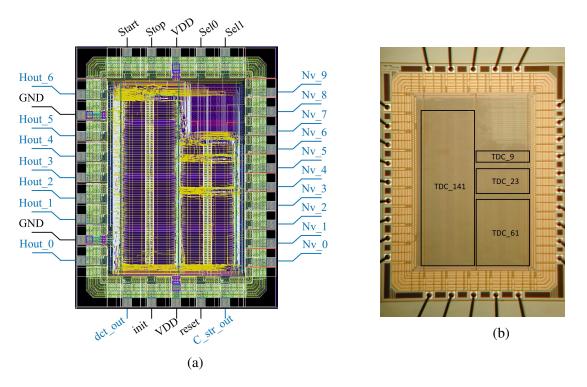

|            |                                       | 6.2.3          | Layout and circuit                   | 103                  |  |  |  |  |

|            | 6.3                                   | Measur         | rement results                       | 104                  |  |  |  |  |

|            |                                       | 6.3.1          | 9-stage STRO-based TDC               | 105                  |  |  |  |  |

|            |                                       | 6.3.2          | 23-stage STRO-based TDC              | 106                  |  |  |  |  |

|            |                                       | 6.3.3          | 61-stage STRO based TDC              | 107                  |  |  |  |  |

|            | 6.4                                   | Conclu         | sion                                 | 108                  |  |  |  |  |

| 7          | Cone                                  | clusions       | and Perspectives                     | 111                  |  |  |  |  |

|            | 7.1                                   | Thesis         | contributions                        | 111                  |  |  |  |  |

|            | 7.2                                   | Perspec        | ctives                               | 113                  |  |  |  |  |

| Gl         | Glossary                              |                |                                      |                      |  |  |  |  |

| Bil        | Bibliography of Author's Publications |                |                                      |                      |  |  |  |  |

| References |                                       |                |                                      |                      |  |  |  |  |

# **Table des figures**

| 1.1  | Digital time measurement principle                                                   | 3  |

|------|--------------------------------------------------------------------------------------|----|

| 2.1  | Example of TDC transfer curve in ideal case.                                         | 7  |

| 2.2  | Example of TDC transfer curve (number of bits 3), showing the offset and the         |    |

|      | dynamic range of a TDC.                                                              | 8  |

| 2.3  | The conversion time principle.                                                       | 9  |

| 2.4  | TDC nonlinearity example.                                                            | 11 |

| 2.5  | Analog TDC based on Analog-to-Digital converter : (a) Basic architecture, (b)        |    |

|      | timing diagram.                                                                      | 12 |

| 2.6  | Analog TDC with time stretching/amplification :(a) single-slope integrator ar-       |    |

|      | chitecture (b) timing diagram.                                                       | 12 |

| 2.7  | Analog TDC with time stretching/amplification :(a) dual-slope integrator archi-      |    |

|      | tecture (b) timing diagram.                                                          | 13 |

| 2.8  | Generic TDC architecture.                                                            | 15 |

| 2.9  | (a) Basic implementation of a delay-line based TDC, (b) the timing diagram           | 16 |

| 2.10 | Inverter Ring Oscillator based TDC example and its timing diagram                    | 17 |

| 2.11 | Gated Ring Oscillator based TDC.                                                     | 18 |

| 2.12 | A Vernier delay-line TDC structure.                                                  | 20 |

| 2.13 | operating principle of the Vernier TDC                                               | 21 |

| 2.14 | Vernier gated ring oscillator TDC                                                    | 22 |

| 2.15 | $3 \times 3$ 2-D Vernier gated ring oscillator TDC                                   | 23 |

| 2.16 | GRO creation of sub-gate-delay spacing using resistive ring interpolation [62]       | 24 |

| 2.17 | (a) implementation of the $i^{th}$ delay stage, (b) Schematic of the proposed multi- |    |

|      | path GRO in [63]                                                                     | 25 |

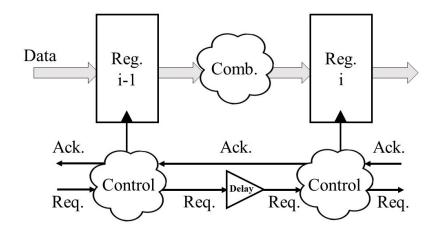

| 3.1  | Digital synchronous circuit : general architecture.                                  | 31 |

| 3.2  | Digital asynchronous circuit : general architecture.                                 | 32 |

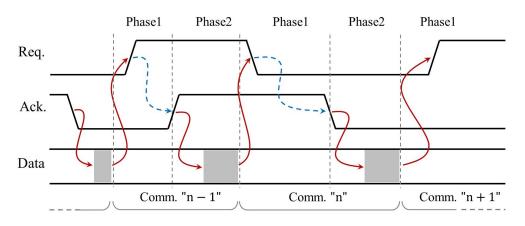

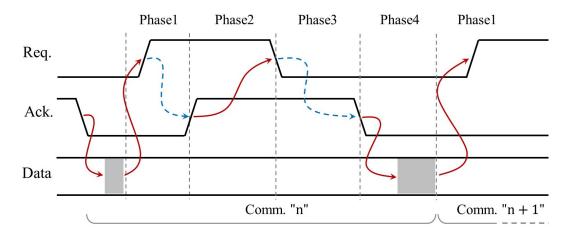

| 3.3  | Two-phase protocol diagram.                                                          | 34 |

| 3.4  | Four-phase protocol diagram.                                                         | 34 |

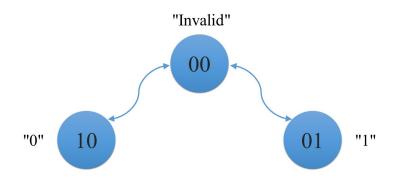

| 3.5  | Three-state encoding.                                                                | 35 |

|      |                                                                                      |    |

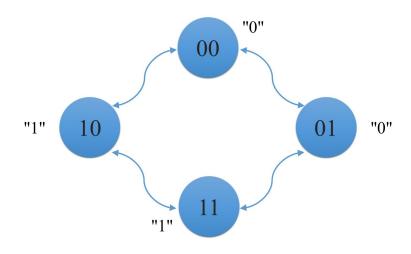

| 3.7                                                                                                                                | Four-state encoding                                                            | 35                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|                                                                                                                                    | General structure of Micropipeline circuit.                                    | 36                                                                                                         |

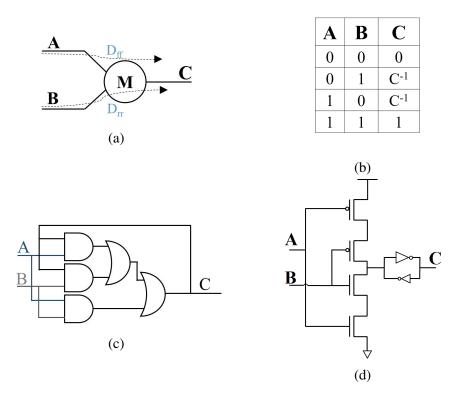

| 3.8                                                                                                                                | (a) the C-element symbol, (b) truth table of a C-element, (c) C-element im-    |                                                                                                            |

|                                                                                                                                    | plementation with standard digital gates, (d) transistor implementation of the |                                                                                                            |

|                                                                                                                                    | C-element                                                                      | 37                                                                                                         |

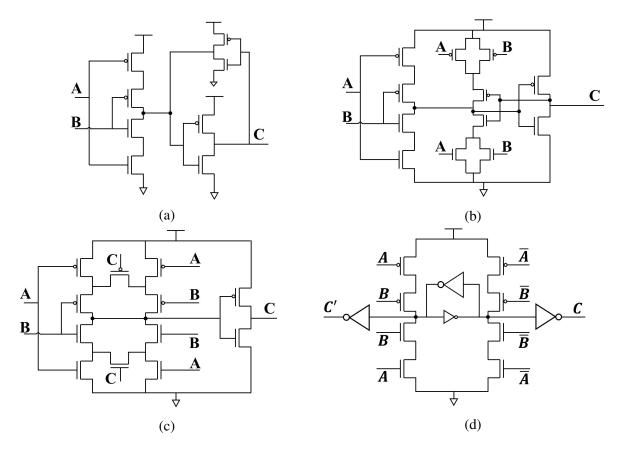

| 3.9                                                                                                                                | C-element implementations : (a) week-feedback, (b) conventional, (c) symme-    |                                                                                                            |

|                                                                                                                                    | tric, (d) differential.                                                        | 38                                                                                                         |

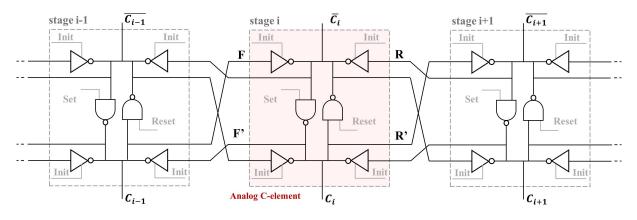

| 3.10                                                                                                                               | Analog C-element structure.                                                    | 39                                                                                                         |

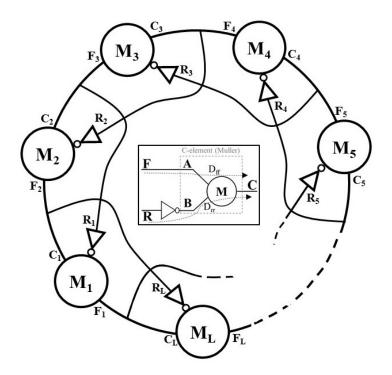

|                                                                                                                                    | Global architecture of a L-stage STRO oscillator.                              | 41                                                                                                         |

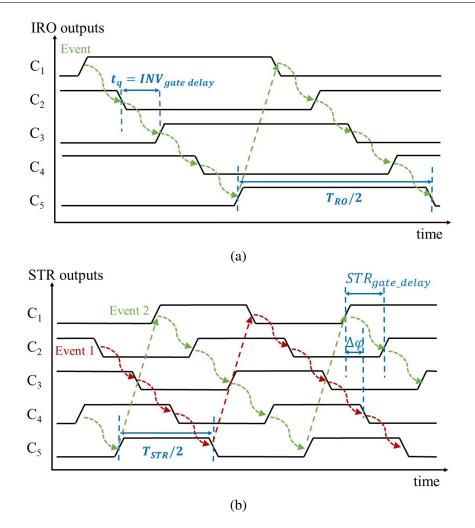

|                                                                                                                                    | 5-stages (a) IRO versus (b) STRO phases diagram showing events propagation     |                                                                                                            |

|                                                                                                                                    | in time (example of two events propagation in the 5-stages STRO)               | 42                                                                                                         |

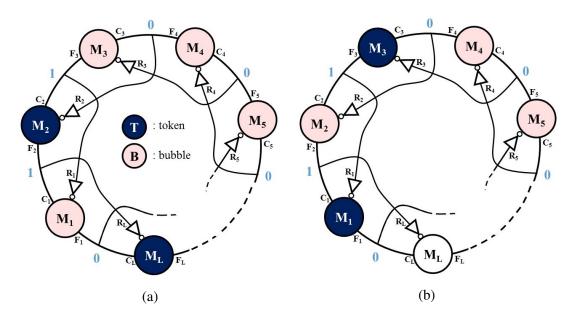

| 3.13                                                                                                                               | Tokens and bubbles propagation example : (a) a L-stage STRO state at time t,   |                                                                                                            |

| 0110                                                                                                                               | (b) the next state at time t+1                                                 | 43                                                                                                         |

| 3 14                                                                                                                               | Propagation modes of a STRO in its steady state.                               | 44                                                                                                         |

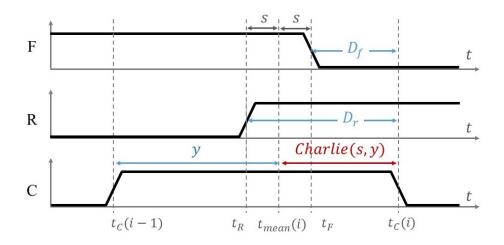

|                                                                                                                                    | Timing diagram example of a STRO stage.                                        | 45                                                                                                         |

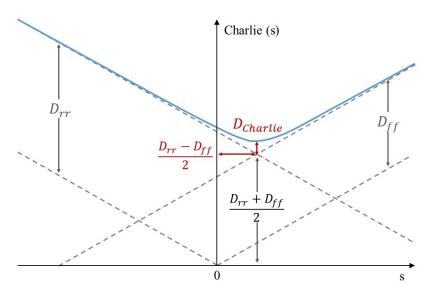

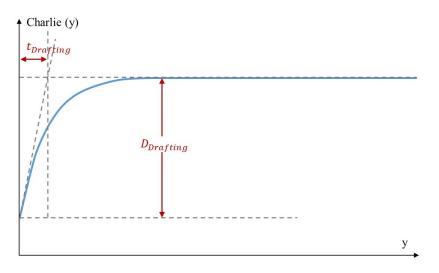

|                                                                                                                                    | 2D Charlie diagram.                                                            | 46                                                                                                         |

|                                                                                                                                    | Drafting diagram.                                                              | 46                                                                                                         |

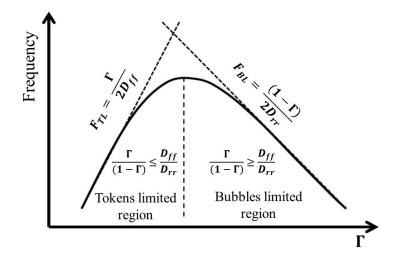

|                                                                                                                                    | Frequency curve of a STRO as a function of its occupancy.                      | 40<br>48                                                                                                   |

|                                                                                                                                    | Oscillator phase noise vs. frequency offset.                                   | 40<br>51                                                                                                   |

| 5.19                                                                                                                               |                                                                                | 51                                                                                                         |

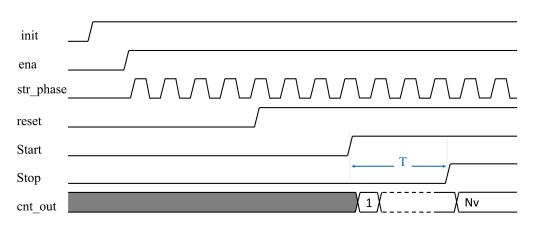

| 4.1                                                                                                                                | Re-arranged phases of a 9-stage STRO with 4 tokens                             | 59                                                                                                         |

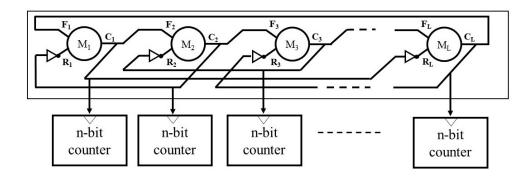

| 4.2                                                                                                                                | Basic architecture of the STRO-based TDC using only n-bit counters             | 60                                                                                                         |

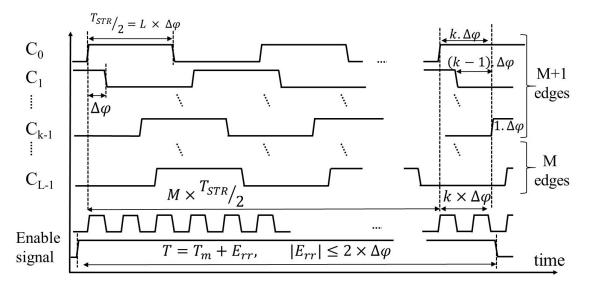

|                                                                                                                                    | Time measurement diagram.                                                      |                                                                                                            |

| 4.3                                                                                                                                | 6                                                                              | 60                                                                                                         |

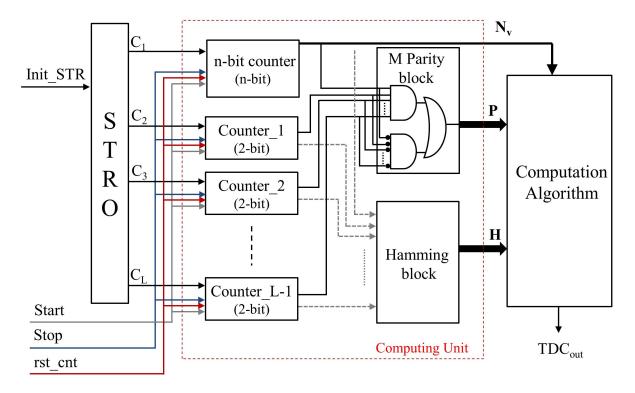

| 4.3<br>4.4                                                                                                                         | Proposed TDC architecture using an L-stage STRO                                | 60<br>62                                                                                                   |

|                                                                                                                                    | -                                                                              |                                                                                                            |

| 4.4                                                                                                                                | Proposed TDC architecture using an L-stage STRO                                |                                                                                                            |

| 4.4                                                                                                                                | Proposed TDC architecture using an L-stage STRO                                | 62                                                                                                         |

| 4.4<br>4.5                                                                                                                         | Proposed TDC architecture using an L-stage STRO                                | 62                                                                                                         |

| 4.4<br>4.5                                                                                                                         | Proposed TDC architecture using an L-stage STRO                                | 62                                                                                                         |

| 4.4<br>4.5                                                                                                                         | Proposed TDC architecture using an L-stage STRO                                | 62<br>63                                                                                                   |

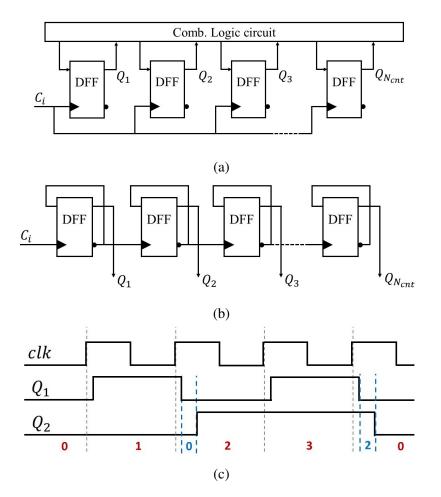

| 4.4<br>4.5<br>4.6                                                                                                                  | Proposed TDC architecture using an L-stage STRO                                | 62<br>63<br>64                                                                                             |

| <ul><li>4.4</li><li>4.5</li><li>4.6</li><li>4.7</li></ul>                                                                          | Proposed TDC architecture using an L-stage STRO                                | 62<br>63<br>64<br>66                                                                                       |

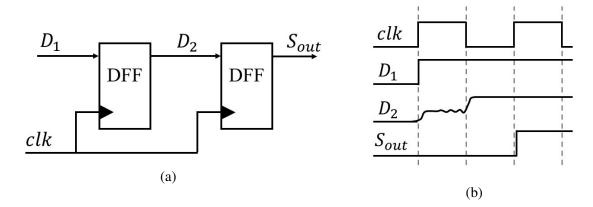

| <ul> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> </ul>                                                        | Proposed TDC architecture using an L-stage STRO                                | 62<br>63<br>64<br>66                                                                                       |

| <ul> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul>                                           | Proposed TDC architecture using an L-stage STRO                                | 62<br>63<br>64<br>66<br>66                                                                                 |

| <ul> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> </ul>                             | Proposed TDC architecture using an L-stage STRO                                | 62<br>63<br>64<br>66<br>66<br>68                                                                           |

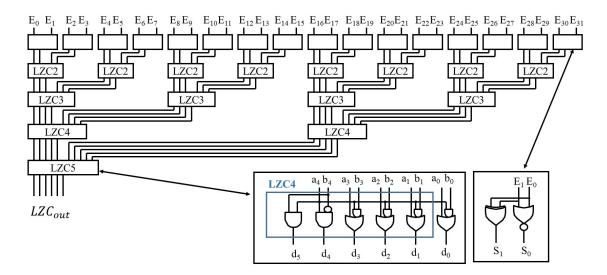

| <ul> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> <li>4.11</li> </ul>               | Proposed TDC architecture using an L-stage STRO                                | <ul> <li>62</li> <li>63</li> <li>64</li> <li>66</li> <li>66</li> <li>68</li> <li>68</li> </ul>             |

| <ul> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> <li>4.11</li> </ul>               | Proposed TDC architecture using an L-stage STRO                                | <ul> <li>62</li> <li>63</li> <li>64</li> <li>66</li> <li>66</li> <li>68</li> <li>68</li> </ul>             |

| <ul> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> </ul> | Proposed TDC architecture using an L-stage STRO                                | <ul> <li>62</li> <li>63</li> <li>64</li> <li>66</li> <li>66</li> <li>68</li> <li>68</li> <li>69</li> </ul> |

| 4.4<br>4.5                                                                                                                         | Proposed TDC architecture using an L-stage STRO                                | 62                                                                                                         |

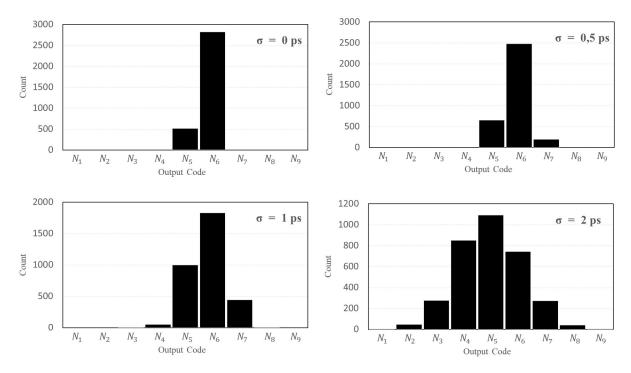

| 4.14 | The TDC output distribution for a fixed time interval $T$ with different values of                     |     |

|------|--------------------------------------------------------------------------------------------------------|-----|

|      | $Jitter_{var}$ (the TDC characteristics : $L = 9$ , $N_T = 4$ , and $Jitter_{seed} = 100$ ).           | 74  |

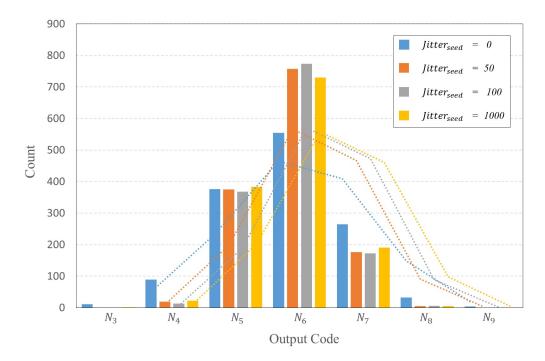

| 4.15 | The TDC output distribution for variable $Jitter_{seed}$ with their trend curves (                     |     |

|      | $Jitter_{var} = 1 \text{ ps}$ )                                                                        | 75  |

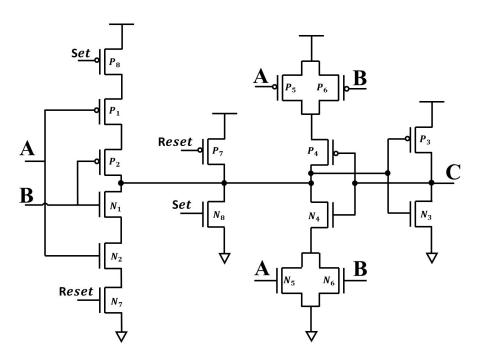

| 4.16 | CMOS implementation of the conventional C-element.                                                     | 76  |

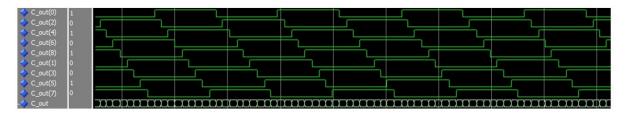

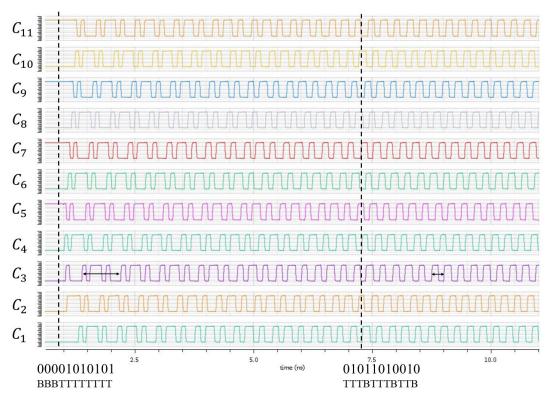

| 4.17 | 11-stage STRO outputs for an initialization of 8 tokens                                                | 77  |

| 4.18 | The phase signal for each possible configuration of an STRO with : $L = 9$ ,                           |     |

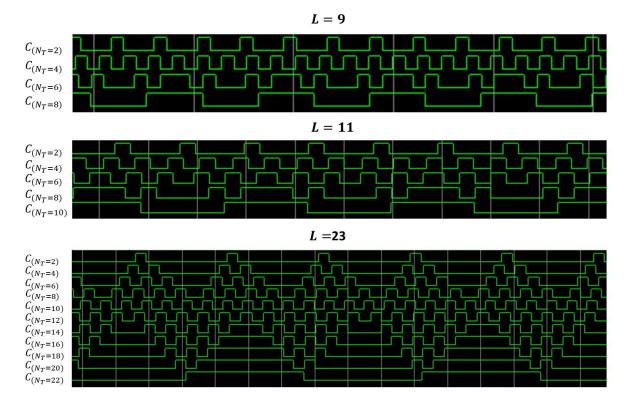

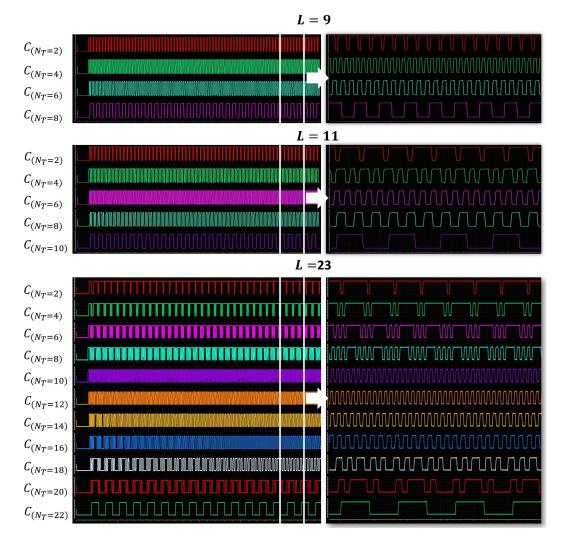

|      | L = 11, and $L = 23$                                                                                   | 78  |

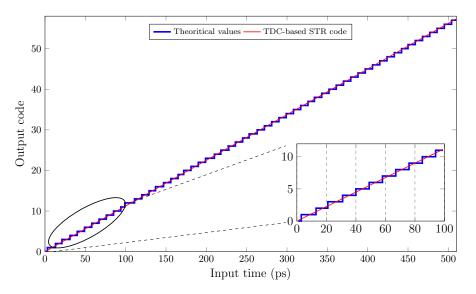

| 4.19 | Simulated TDC output versus input time.                                                                | 80  |

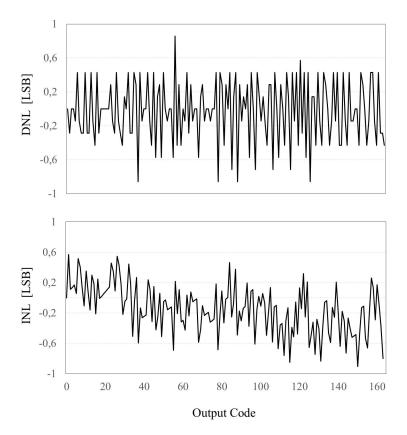

| 4.20 | Simulation results of DNL and INL in the presence of the jitter (standard devia-                       |     |

|      | tion of 1.00 ps                                                                                        | 81  |

| 5.1  | Block diagram of the TDC based on cyclic pulse shrinking                                               | 87  |

| 5.2  | (a) Architecture of a Vernier-TDC based on delay line loops with shrinking                             |     |

|      | method (b) timing diagram showing the operation principle of the shrinking TDC.                        | 88  |

| 5.3  | Intel Cyclone IV Logic Array Block (LAB) architecture.                                                 | 89  |

| 5.4  | The implementation of the C-element into a look up table (LUT) in Intel Cy-                            |     |

|      | clone IV showing the logical cell of the LAB.                                                          | 90  |

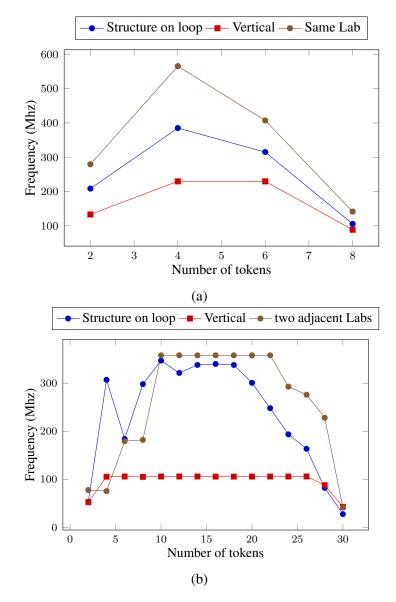

| 5.5  | Measured frequency with different structures implemented in Cyclone IV FPGA                            |     |

|      | for : (a) 9-stages STRO, and (b) 31-stages STRO                                                        | 92  |

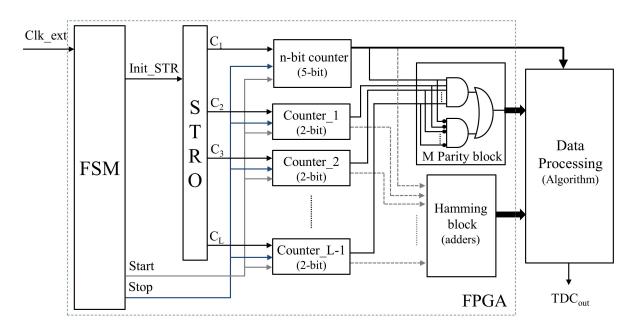

| 5.6  | Composition of the proposed TDC architecture using STRO of a $L$ stages                                | 93  |

| 5.7  | Implementation topology of a STRO of more than 16 stages (each stage on a                              |     |

|      | single LAB).                                                                                           | 94  |

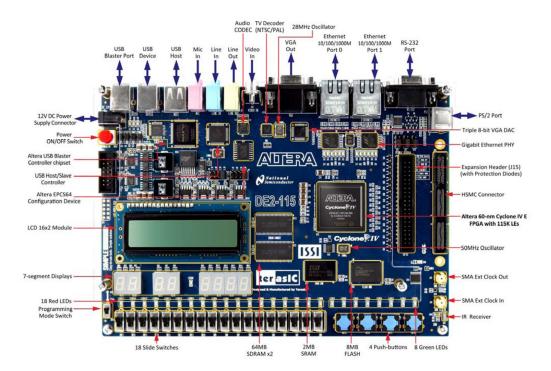

| 5.8  | The top view of the DE2-115 (EP4CE115F29C7) Intel Cyclone IV board (from                               |     |

|      | the user manual).                                                                                      | 95  |

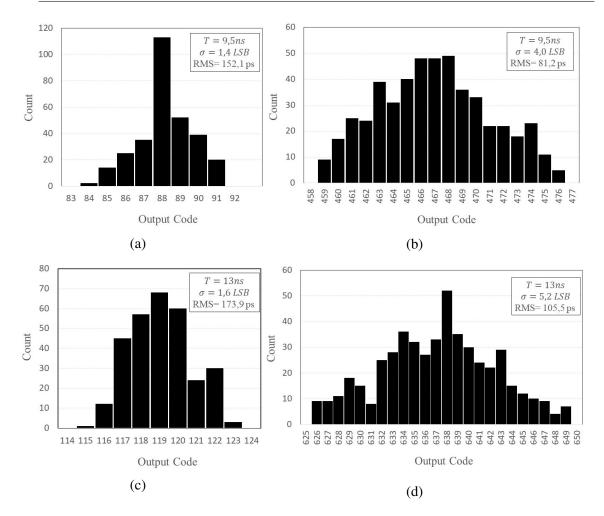

| 5.9  | Histograms of the time interval measurement : 23-STRO based TDC : (a) $9.5 \mathrm{ns}$                |     |

|      | and (c) $13.0 \text{ ns}$ / and $141$ -STRO based TDC : (b) $9.5 \text{ ns}$ and (d) $13.0 \text{ ns}$ | 96  |

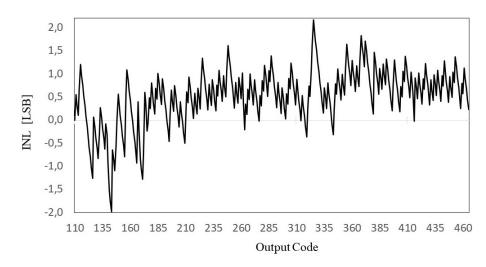

| 5.10 | The 23-stage STRO-based TDC integral nonlinearity (INL).                                               | 97  |

| 6.1  | The global architecture of L-stage TDC for 350 nm CMOS technology imple-                               |     |

|      |                                                                                                        | 100 |

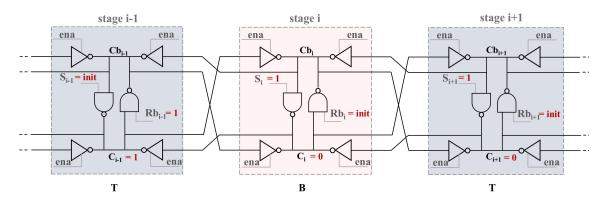

| 6.2  | Three stages example from a self-timed ring oscillator with Analog C-element                           |     |

|      |                                                                                                        | 101 |

| 6.3  |                                                                                                        | 103 |

| 6.4  |                                                                                                        | 103 |

| 6.5  | (a) the circuit layout with pads and input/output, (b) Microphotograph of the                          |     |

|      |                                                                                                        | 105 |

| 6.6  | -                                                                                                      | 106 |

|      |                                                                                                        |     |

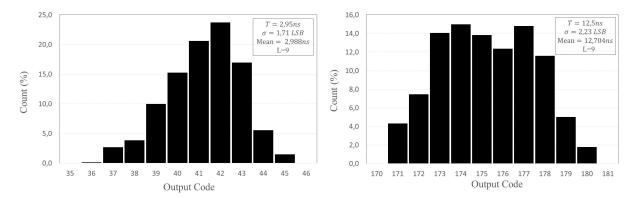

| 6.7 | Measured single-shot precision of the 9-STRO based TDC when input time  |     |  |  |  |

|-----|-------------------------------------------------------------------------|-----|--|--|--|

|     | intervals are respectively 2.95 ns and 12.5 ns                          | 106 |  |  |  |

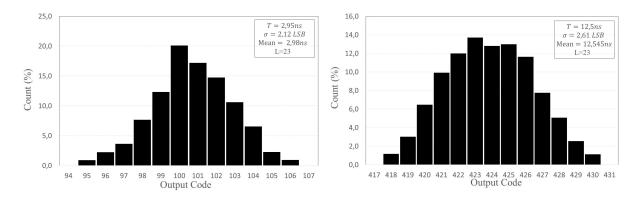

| 6.8 | Measured single-shot precision of the 23-STRO based TDC when input time |     |  |  |  |

|     | intervals are respectively $2.95 \text{ ns}$ and $12.5 \text{ ns.}$     | 107 |  |  |  |

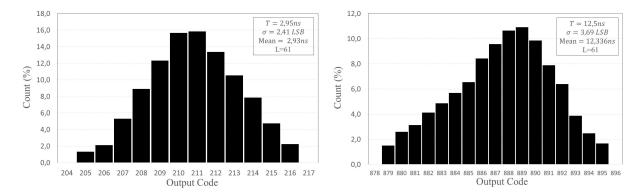

| 6.9 | Measured single-shot precision of the 61-STRO based TDC when input time |     |  |  |  |

|     | intervals are respectively 2.95 ns and 12.5 ns                          | 108 |  |  |  |

# Liste des tableaux

| 3.1 | Analog simulation results of different structure of STROs using 65 nm CMOS                                                                                          |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | technology                                                                                                                                                          | 50  |

| 4.1 | Possible states for the n-bit vectors $B_k = M$ and $M_k = M + 1$                                                                                                   | 61  |

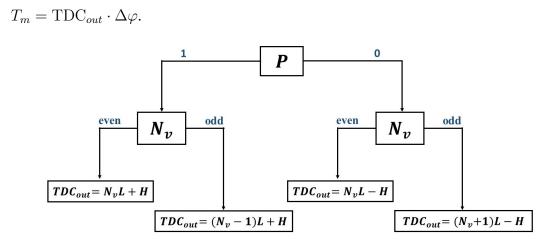

| 4.2 | The predicted value of $M$ and $k$ as a function of $N_v$ , $P$ and $H$                                                                                             | 62  |

| 4.3 | High-level simulation of a STRO-based TDC measuring a time interval $T =$                                                                                           |     |

|     | 500 ps in a noisy environment for different resolutions $\Delta \varphi$ , and for a fixed jitter                                                                   |     |

|     | standard deviation $\sigma = 1.00  \text{ps.} \dots \dots$                      | 75  |

| 4.4 | The frequency, time resolution, and the duty cycle for different STRO configu-                                                                                      |     |

|     | ration simulations in 28 nm FDSOI technology.                                                                                                                       | 79  |

| 4.5 | Analog simulation results of a 9-stage STRO-based TDC using $28\mathrm{nm}$ FDSOI                                                                                   |     |

|     | CMOS technology                                                                                                                                                     | 80  |

| 5.1 | Performance summary and comparison with state-of-the-art TDCs                                                                                                       | 98  |

| 6.1 | Input/ Output interfaces : Pins description.                                                                                                                        | 104 |

| 6.2 | Measurement summary of the 9-stage STRO based TDC presenting a time re-                                                                                             |     |

|     | solution of $\Delta \varphi = 72.5 \mathrm{ps.} \ldots \ldots$    | 105 |

| 6.3 | Post-layout simulation results for the 9-stage STRO based TDC                                                                                                       | 106 |

| 6.4 | Measurement summary of the 23-stage STRO based TDC presenting a time                                                                                                |     |

|     | resolution of $\Delta \varphi = 29.6 \text{ ps.} \dots \dots$ | 107 |

| 6.5 | Post-layout simulation results for the 23-stage STRO based TDC                                                                                                      | 107 |

| 6.6 | The test chip Measurements for the 61-stage STRO based TDC with a time                                                                                              |     |

|     | resolution of $\Delta \varphi = 13.9 \mathrm{ps.}$                                                                                                                  | 108 |

# **Chapitre 1**

# Introduction

#### Sommaire

| 1.1 | Context and Motivations | 1 |

|-----|-------------------------|---|

| 1.2 | Thesis contributions    | 2 |

| 1.3 | Thesis overview         | 4 |

### **1.1 Context and Motivations**

Continuous progress in electronic devices and technology enables us to makes our life comfortable and convenient. This progress is due mainly to CMOS scaling, which allows deploying more and more integrated functionalities into the same chip. One simple example is the use of sensors, which are pervasive and useful in several fields. They are embedded in cars, airplanes, cellular phones, radios and countless other applications. These applications are mostly based on the time measurement of time interval or pulse width corresponding to physical events. It is also used to measure the distance for some applications as radar and geolocation. This time measurement is generally performed by devices called time-to-digital converters (TDCs). These latter convert the time into a digital value, which facilitates the data processing and its integration in digital systems.

Time-to-digital converters (TDCs) are widely used for the time measurement. They quantify the measured time interval T and provides its digital value as a function of the time resolution, which often represents the time step of the digital clock or a gate delay. The time resolution is the most important parameter, which defines the time measurement performances. It presents the sampling step and the smallest time interval that can be measured. Otherwise, many parameters can characterize and take part in the TDC performances such as its dynamic range and latency. Many applications require precise time measurement in order to quantify physical or electrical events with a digital value such as high-energy physics, time-of-flight measurement, instrumentation and satellite positioning.

#### Introduction

The first TDCs have been designed in the 60s for time-of-flight applications in high energy physics [52]. This first generation was based on analog techniques initially developed for the time-to-amplitude converters (TAC). The second analog TDC category was based on the time stretching technique, which does not require the analog-to-digital converters (ADCs) previously used. The analog TDCs provide a high precision and a good linearity. They are suitable for short measurement ranges. Especially, they show high performances in term of time resolution.

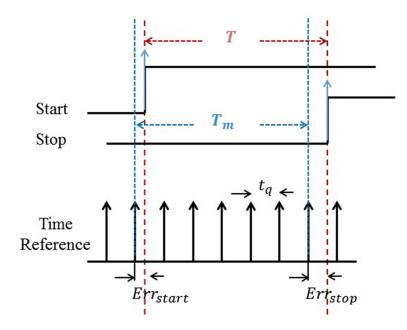

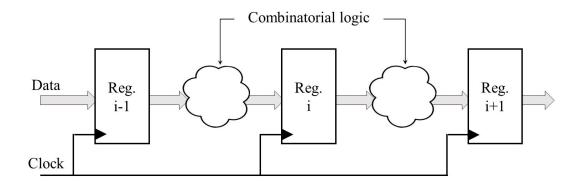

Today, fully digital approaches are mostly used for time measurement. Such an approach takes advantage of reduced die area, power and functional complexity. Moreover, digital TDCs can easily be integrated on-chip in CMOS technology. The simplest fully digital TDC architecture is based on counting the number of edges of a reference clock signal, as shown in Fig. 1.1. The converter starts counting the number of edges from the *Start* event to the arrival of the *Stop* event. Each measurement induces a quantification error at the beginning and at the end of measured time. The total error value is function of the time resolution of the converter. The smaller is the time resolution, the precise is the converter. So, the precision will depend on the achieved time resolution  $t_q$ .

TDC structures, with an effective time resolution of few picoseconds, are also presented. In the simplest TDC architecture, the time resolution is bounded by the CMOS gate delay. Many digital TDCs have been proposed dealing with time resolution improvement, which offer a sub-gate delay resolution. However, they generally present issues related to their limited dynamic range. Alternatively, in order to overcome this limitation, architectures using interpolation scheme or multi-quantization levels have been proposed to achieve wide measurement range with a fine time resolution. Therefore, repetitive measurement are mostly required in order to ensure high precise measurements without sacrificing the TDC linearity. Therefore on-the-fly measurements on fast non-periodic signals are particularly challenging in TDC designs.

A TDC structure, simultaneously propagating more than one event, has shown further performance improvement. In fact, the propagation of several events allows considering the phase difference as a time sampling step. Thus, the gate delay is subdivided into smallest time portions considered as the time resolution. Many structures dealing with this principle have been presented in the literature. They usually propose a full custom design of their delay gates, which integrate multiple inputs in order to couple together several oscillators. Consequently, the number of coupled oscillators is the ratio by which the time resolution is divided. Despite the high resolution and the wide measurement range provided by such topologies, they require a larger chip area and eventually more power consumption.

# **1.2** Thesis contributions

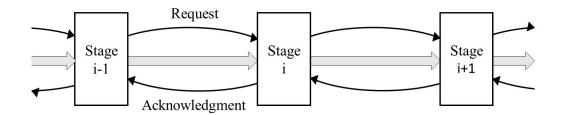

In this work, a new approach is presented for a fully digital TDC based on a self-timed ring oscillator (STRO). In such an oscillator, several events can be initialized and propagate without

FIGURE 1.1: Digital time measurement principle.

colliding thanks to a request/handshake protocol. Due to the STRO characteristics, a regular time base is generated by exploiting its equidistant phases. Exploiting the uniform distribution of phases, a TDC architecture, adopting the STRO as a clock reference, is proposed.

The time resolution of this TDC can be accurately tuned as fine as needed by simply increasing the number of STRO stages. Its time resolution can be lower than the propagation delay of the used gates. This resolution is only limited by the noise floor of the STRO stage. Furthermore, the implementation is simple and suitable for all digital circuits. Moreover, it easily support the technology shrink. For applications requiring on-the-fly measurements with a fine resolution, the STRO-based TDC offers interesting perspectives compared to the other TDCs.

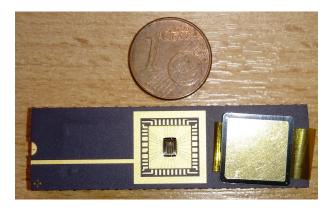

As a hardware proof-of-concept, our proposed architecture has been implemented in an Intel Cyclone IV. Then, an ASIC testchip has been designed and fabricated using CMOS AMS350 technology. The test of the circuit proves the validity of this new kind of TDCs.

This work is a first exploration of an architecture of time-to-digital converter based on selftimed ring oscillators. It is also a tight collaboration between the TIMA laboratory, *Université Grenoble Alpes (UGA)/CNRS* Grenoble, France and the STRS laboratory, *Institut National des Postes et Telecommunications (INPT)*, Rabat, Morocco. This collaboration has contributed demonstrating the efficiency of the architecture in terms of configurability. Thanks to the knowledge of the asynchronous circuits, a fully digital TDC architecture with sub-gate time resolution, wide dynamic range, for on-the-fly measurement, and without any calibration has been proposed. This work has been supported by the "Région Auvergne Rhône-Alpes" (France) grant  $n^{\circ}$  150054650.

### **1.3** Thesis overview

This thesis is organized as follows :

Chapter 2 presents a literature review of different TDC architectures. It brings a detailed information about the first TDC generations based on analog techniques. Then, the recent main architectures based on digital techniques dealing with the time resolution improvement have been described. In addition, key performance metrics are given in order to examine the TDC performances.

Chapter 3 deals with self-timed ring oscillators (STROs) which are a promising solution for designing multi-phase clock generators. In STROs, the phase resolution can be adjusted as fine as desired by simply increasing its number of stages without frequency drop. Moreover, this resolution is not limited by the gate delay. In addition, different oscillation frequencies can be obtained by the same STRO depending on its initialization. In addition, the STRO phase noise analysis is also presented; 1/N phase noise reduction is obtained at the cost of higher power consumption when the number of stages is increased by N, and while keeping the same oscillation frequency.

The proposed STRO based time-to-digital-converter architecture is detailed in Chapter 4. Thanks to the STRO characteristics, a regular time base is generated by equidistant phases. In addition, the proposed TDC architecture allows on-the-fly time measurement on fast non-periodic signals. This new TDC architecture has been validate using precise high-level model and analog simulations using the 28 nm FDSOI technology from *STMicroelectronics*.

InChapter 5 and Chapter 6, two hardware proof-of-concepts of the STRO-based TDC have been respectively implemented in an FPGA Intel Cyclone IV and as an ASIC using the AMS350 CMOS technology. TDCs with different number of stages have been implemented to demonstrate the time resolution enhancement with an increased number of stages. Measurement results points out the advantages of this new TDC in terms of measurement accuracy and simplicity of implementation.

Finally, the conclusion Chapter 7 discuss the directions for our future research and the potential applications for the STRO-based TDC.

# **Chapitre 2**

# State-of-the-Art on Time-to-Digital Converters

## Sommaire

| 2.1 | Intro | luction .  |                                                | 6  |

|-----|-------|------------|------------------------------------------------|----|

| 2.2 | Time- | to-Digital | Converters : key performance metrics           | 7  |

|     | 2.2.1 | Main TI    | DC metrics                                     | 7  |

|     |       | 2.2.1.1    | Time resolution                                | 7  |

|     |       | 2.2.1.2    | Dynamic range                                  | 8  |

|     |       | 2.2.1.3    | Conversion time                                | 8  |

|     |       | 2.2.1.4    | Latency                                        | 8  |

|     | 2.2.2 | Linear a   | nd nonlinear imperfections                     | 9  |

|     |       | 2.2.2.1    | Offset error                                   | 9  |

|     |       | 2.2.2.2    | Quantization error                             | 9  |

|     |       | 2.2.2.3    | Differential non-linearity (DNL)               | 10 |

|     |       | 2.2.2.4    | Integral non-linearity (INL)                   | 10 |

| 2.3 | Analo | g time-to- | digital converters                             | 10 |

|     | 2.3.1 | Analog     | ΓDCs based on analog-to-digital converter      | 11 |

|     | 2.3.2 | Analog t   | ime-to-digital converters with time stretching | 12 |

|     |       | 2.3.2.1    | Single integrator stretching                   | 12 |

|     |       | 2.3.2.2    | Dual-slope conversion                          | 13 |

|     |       | 2.3.2.3    | Triple-pulse time stretching                   | 14 |

|     | 2.3.3 | Conclusi   | ion                                            | 14 |

| 2.4 | Fully | Digital Ti | me-to-Digital Converters                       | 14 |

|     | 2.4.1 | TDC wit    | th gate-delay resolution                       | 15 |

|     |       | 2.4.1.1    | Delay-Line based TDC                           | 15 |

|     |       | 2.4.1.2    | Ring Oscillator                                | 16 |

| 2.5 | Conclu | ision    |                                  | 26 |

|-----|--------|----------|----------------------------------|----|

|     |        | 2.4.2.2  | TDC with interpolation technique | 23 |

|     |        | 2.4.2.1  | Vernier based TDC                | 19 |

|     | 2.4.2  | TDC with | n sub-gate-delay resolution      | 19 |

|     |        | 2.4.1.3  | Gated Ring Oscillator            | 18 |

# 2.1 Introduction

Time measurement between two events is a key technique used in many fields such as highenergy physics, time-of-flight measurement, instrumentation and satellite positioning [6, 34, 48, 56, 60]. Devices called time-to-digital converters (TDCs) are widely used for precise time measurement. The time interval T to be measured is generally defined with a *Start* signal, which indicates its beginning, and a *Stop* signal, which points the end. The time conversion into a digital word (binary output code) facilitates the data processing and its integration in digital systems. Such an approach takes advantage of integrated circuits because they provide a reduced die area, low power consumption and complex functionality. Moreover, TDCs can easily be integrated on-chip in CMOS technology in a lager system.

The first generation of TDCs was based on analog techniques. They have been designed to enhance the previous technique initially developed for time measurement based on the time-to-amplitude converters (TAC) [33, 55, 61]. Recently, fully digital approaches are mostly used for time measurement. The simplest architecture of TDC is based on a timer counting the number of edges of a reference clock signal. The precision depends on the timer resolution (sampling step) by which the measurement is performed. This can be carried out by low-power and compact circuits.

Many TDC principles have been proposed in the literature as second generation of TDCs for improving the time resolution. In the simplest TDC architectures, the time resolution is bounded by a CMOS gate delay. In order to overcome this technological limitation, sub-gate delay resolution solutions have also been proposed [12,42,63,68] corresponding to a TDC third generation. As a wide dynamic range of time measurement is required in many applications, dedicated architectures have been proposed. In order to achieve a wide measurement range with a fine time resolutions [76], several strategies can be employed such as interpolation schemes or multi-quantization levels. Nevertheless, while many of the proposed TDC architectures in the literature can achieve high measurement accuracy, they often require repetitive measurements. Therefore, on-the-fly measurements on fast non-periodic signals are really challenging for most of the TDCs.

This chapter provides a literature review of the main used architectures of TDCs [22]. In addition, key performance metrics are given in order to analyze the TDC performances. The chapter is organized as follows. The Section 2.2 exposes the main key performances metrics to

take into consideration in TDCs design. Section 2.3 and Section 2.4 respectively presents the main TDC architectures based on analog and digital techniques.

### 2.2 Time-to-Digital Converters : key performance metrics

Time-to-digital converters quantify the time between a *Start* and a *Stop* event and express their result as a digital value. Many parameters help to characterize the TDC performances. A set of parameters related to the TDC are firstly presented. Then, we discuss the linear and nonlinear imperfections of TDCs.

#### 2.2.1 Main TDC metrics

#### 2.2.1.1 Time resolution

The time resolution characterizes the measurement precision of a time interval T. It represents the minimal time that a TDC can correctly quantify. It is often referenced as the least significant bit (LSB). This parameter generally depends on the circuit characteristics, *i.e.*, the technology and the noise performances.

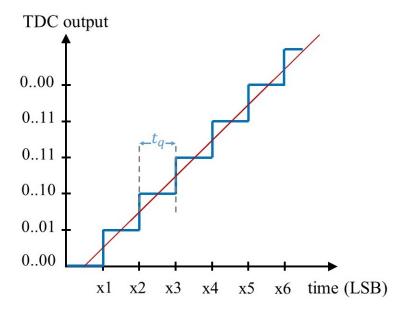

FIGURE 2.1: Example of TDC transfer curve in ideal case.

With an ideal TDC, a time equal to one LSB corresponds to the first non-zero code. Then, the TDC value is incremented for each time increment of 1 LSB. The resolution is in this case constant. The quantization characteristic is given on Fig. 2.1 for an ideal TDC in absence of any distortion. A variation lower than one LSB is coded by the same word. Thus, the transfer function is stepped curve with a step width of 1 LSB). In our study, the parameter  $t_q$  represents the time resolution.

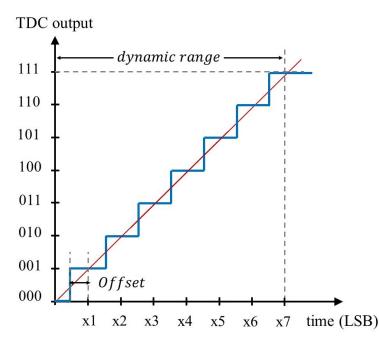

#### 2.2.1.2 Dynamic range

The dynamic range expresses the TDC maximal time input to correctly be quantified. For the structures using counters, this parameter is related to the number of bits of the counters. As illustration, a TDC with a 3-bit counter is presented in Fig. 2.2. The last code that this TDC is able to produce is . The time needed to show this code presents the TDC dynamic range, as shown in the figure. If we suppose that the number of bits of the TDC output is N, the dynamic range will be presented by the value  $2^N$ .LSB [34].

FIGURE 2.2: Example of TDC transfer curve (number of bits 3), showing the offset and the dynamic range of a TDC.

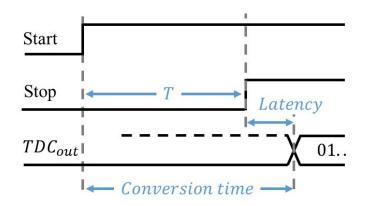

#### 2.2.1.3 Conversion time

The conversion time is a performance parameter applied to a single measurement representing the minimal time needed for a TDC to digitize a time input into a valid digital word. This time is counted from the *Start* event as illustrated in Fig. 2.3). This value is very important for the high-speed applications for which a specific time conversion should be respected. Another parameter is the counting rate, which demonstrates how fast is the TDC conversion process. It can be required for applications such as fast image sensors.

#### 2.2.1.4 Latency

This parameter gives information on the TDC rapidity to present a valid output. Indeed, the latency is the time needed after the *Stop* event to compute a valid digital word. This time is included in the conversion time as presented in Fig. 2.3.

FIGURE 2.3: The conversion time principle.

#### 2.2.2 Linear and nonlinear imperfections

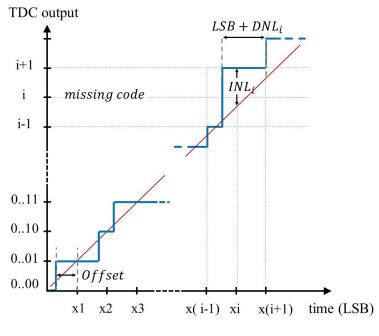

The TDC imperfections can be classified into two categories. Firstly, the linear imperfections are easily detectable and not too much difficult to compensate such as the offset [34]. Contrarily, the nonlinear imperfections require advanced calibration schemes and cannot always be completely removed. The Differential and Integral nonlinearities are the most important static errors to analyze. Furthermore, if the errors are large enough, the TDC should have missing codes. This is a crucial issue affecting TDCs as illustrated in Fig. 2.4 (code i is missing).

In addition to these imperfections, noise sources like the jitter and the thermal noise can also degrade the performances of the TDC.

#### 2.2.2.1 Offset error

The *Offset* represents a deviation of the TDC from the ideal first measurement which should be equal to 1 LSB. For  $0 \le t < LSB$ , the code should be 0 until reaching a time equal to one LSB, as displayed in Fig. 2.1. The time difference between the time,  $t_1$ , where the first code 0..01 appears and the LSB present the offset error. The normalized value of this error,  $E_{\text{Offset}}$ , is expressed by :

$$E_{\text{Offset}} = \frac{t_1 - t_q}{t_q} \tag{2.1}$$

#### 2.2.2.2 Quantization error

The conversion introduces a distortion between the digital output value and the original value. It is an inherent error related to any digital converter. Thus, the measured time interval is a function of the TDC output  $TDC_{out}$  given by :

$$T_m = \text{TDC}_{\text{out}} \times t_q + \varepsilon \tag{2.2}$$

where  $\varepsilon$  is the quantization error. The latter is generally modeled by a uniform random variable. The quantization error is the main error affecting the precision of a TDC.

#### 2.2.2.3 Differential non-linearity (DNL)

For a specific code, the differential non-linearity corresponds to the deviation of the step width from the theoretical LSB step width. As a result, the real step width is equal to LSB + DNL (DNL is a real number). The expression of the differential non-linearity value per one LSB describing the fluctuation effect for the code digit *i* is given by (2.3), where  $t_i$  represents the measured delay for the first appearance of the *i*<sup>th</sup> step.

$$DNL(i) = \frac{t_{i+1} - t_i}{LSB} - 1$$

(2.3)

#### 2.2.2.4 Integral non-linearity (INL)

The integral nonlinearity (INL) is a measurement of the gap between the transfer characteristic and the straight red line in Fig. 2.4. It represents at the same time the cumulative deviation of each step from an ideal value providing a measurement of the non-linearity [34]. The INL is obtained by integrating the DNL curve. Thus, the cumulative  $i^{th}$  INL is expressed by :

$$INL(i) = \sum_{k=0}^{i} DNL_k$$

(2.4)

The INL (as the DNL) can be presented by its maximal value or by its root mean square (rms) value over all steps. They are usually normalized to be expressed in LSB.

Many architectures have been proposed in the state-of-the-art for dealing with fine time resolution. They have to ensure a large dynamic range, on-the-fly measurement and, if possible, without requiring complex calibration. Generally, it is difficult to combine all these wished properties in the same structure especially because the TDCs handle with many other parameters affecting its performance.

# 2.3 Analog time-to-digital converters

The first proposed architectures of the time-to-digital converters were based on the analog techniques. They are suitable for the short measurement ranges since they provide a high precision and a good linearity. The traditional structure is based on the conversion of time interval to voltage. They show high performances in term of time resolution because they are able to reach a few picoseconds [42, 69]. Moreover, these measurements are usually requiring a calibration and/or an averaging process. This first category of analog TDCs requires the use of analog-to-digital converter (ADC). Thereafter, the ADC has been removed for the second category, which

FIGURE 2.4: TDC nonlinearity example.

basically implements time stretching techniques.

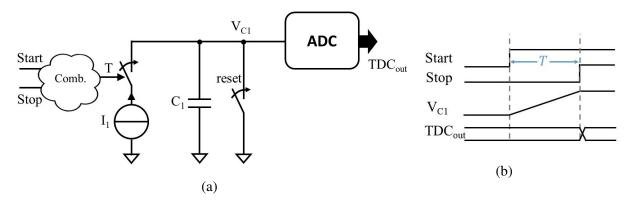

#### 2.3.1 Analog TDCs based on analog-to-digital converter

Based on a similar principle of ADCs, the classical analog approach converts into a voltage the time interval T [47,55,61,69]. Traditionally, one possible way to generate the corresponding voltage is to use an integrator, in which a capacitor is charged with a constant current source, as presented in Fig. 2.5. The integrator transforms the pulse into a voltage corresponding to the time intervals T. Then, this voltage is converted thanks to an ADC providing the digital output. The analog design constraints of the ADC limit the finest resolution  $t_q$ . Moreover, the trade-off between the resolution and the dynamic range (DR) should also be considered. A high resolution means a short time to sweep from ground to the supply voltage at the ADC input and, thus, limits the time DR. On the opposite, a large DR assumes to have a longer time to go from zero to the supply voltage ( the time step increases as well). Otherwise, the dependence between these parameters can be expressed mathematically by :

$$DR = 2^{N_{ADC}} \cdot t_q \tag{2.5}$$

where  $N_{ADC}$  is the number of bits of the ADC and DR is the dynamic range.

FIGURE 2.5: Analog TDC based on Analog-to-Digital converter : (a) Basic architecture, (b) timing diagram.

#### 2.3.2 Analog time-to-digital converters with time stretching

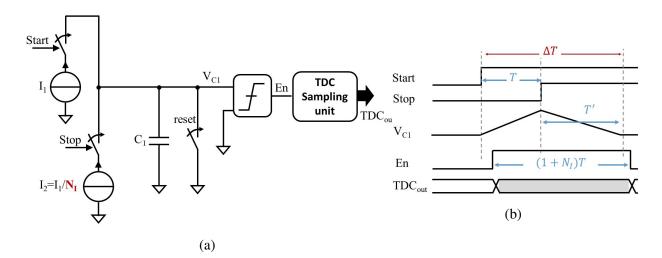

#### 2.3.2.1 Single integrator stretching

The most common structures of analog TDCs are based on the pulse-stretching techniques [28, 53]. In this case, no ADC is used and its limitation is eliminated. The principle is to charge the capacitor  $C_1$  with a first current source  $I_1$  and then to discharge it with a lower current source  $I_2 = I_1/N_I$ , as illustrated in Fig. 2.6a. A comparator is used to detect when the second integrator completes its discharge operation (time for zero-crossing), which corresponds to the time interval multiplied by the ratio  $N_I$  between the two current sources. A counter controlled with a stable clock reference records the number of cycles during this operation. Thanks to this architecture, as the capacitor  $C_1$  is discharged slowly ( $N_I$  times), capturing the time with a better resolution becomes easier as the time has been stretched.

FIGURE 2.6: Analog TDC with time stretching/amplification :(a) single-slope integrator architecture (b) timing diagram.

FIGURE 2.7: Analog TDC with time stretching/amplification :(a) dual-slope integrator architecture (b) timing diagram.

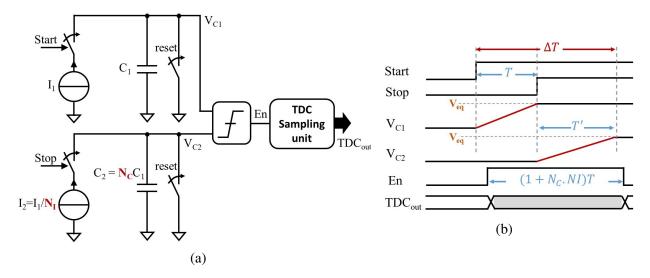

#### 2.3.2.2 Dual-slope conversion

Another type of the analog TDC is based on the dual-slope time stretching approach [10,56]. This TDC is inspired from the principle of dual-slop analog-to-digital converter (ADC) with a reversed operation, which defines a voltage and integrates the unknown time T without requiring an ADC [34].

Similarly to the single-slope, the principle is to charge the first capacitor  $C_1$  during time T with a first current source  $I_1$  when the *Start* event is presented. This capacitor becomes floating when the *Stop* event is arrived. This latter will command a second capacitor  $C_2 = N_C \cdot C_1$  to be charged with another current source  $I_2$  during the interval time T'. The equivalent circuit of this approach and its timing diagram are displayed in Fig. 2.7.

If  $I_2$  is  $N_I$  times smaller than  $I_1$  and  $C_2$  is  $N_C$  times greater than  $C_1$ , the time resolution will be reduced by  $N_I \times N_C$ , presenting the stretching factor of the dual-slope conversion. We can explain this differently by considering a second integrator. So, with the arrival of the *Stop* event, the other integrator starts to integrate the process with a factor of  $N_I \times N_C$  by considering the time interval  $T_2$ .

$$\Delta T = T + T' = \left(1 + \frac{C_2 I_1}{C_1 I_2}\right) T = \left(1 + N_I \times N_C\right) T$$

(2.6)

A comparator detects when the second integrator is equal to the first one because this happens exactly after  $N_I \times N_C \times T$ .

This approach is very attractive with a factor  $N_I \times N_C$  enough large since a TDC with moderate performances can be used. It is very interesting for the resolution enhancement. One advantage compared to the single-slope is that the absolute values of devices are not relevant against the ratios  $N_I$  and  $N_C$ . Thus, stretching the time with a factor  $N_I \times N_C$  is not requiring large device values that can be implemented with basic components as presented in [53]. For design facility, controlling the capacitance ratio is easier than controlling the current source ratio since it is adjusted by simply modifying the area. However, this architecture has high power consumption and is sensitive to a temperature drift [56].

#### 2.3.2.3 Triple-pulse time stretching

To further improve the time resolution, triple-slope stretching schemes have been proposed [41]. In this paper, a coarse counter, a single triple-slope stretcher, and a fine counter are used. In this structure, the analog approach is combined with the digital approach for time measurement. The triple-slope stretcher considers three-time intervals. In accordance with a clock reference, the interval T is divided to time interval  $T_m$  and the error quantification time intervals  $\Delta T_{Start}$  and  $\Delta T_{Stop}$ . A time splitter is used to feed the triple-slope stretcher with these intervals [41].

This structure has an area reduction of 40% compared with the dual-slope TDC presented in [10] since it just requires two capacitances and one comparator for its implementation. The TDC has been implemented in 350 nm CMOS technology. A 0.357 ns time resolution was obtained by using a 175 MHz reference clock. The structure has shown an achievement of a dynamic range of  $1.46 \,\mu\text{s}$ .

#### 2.3.3 Conclusion

The analog TDCs are able to reach a time resolution that can only be a few picoseconds [42]. Nevertheless, they suffer from several fundamental issues. Firstly, the used current sources are sensitive to a nonlinear output and a finite output resistance. Therefore, the linearity of the TDC can be degraded especially for large dynamic ranges since the analog TDCs are known to be sensitive to a temperature drift [34]. Secondly, they are not suitable for fast applications due to limitation related to the dead time [13]. Mostly, the measurements are not feasible without calibration schemes or an averaging process. Otherwise, these TDCs require a large area due to the use of capacitors which induce more power cosumption in comparison to the digital counter part [13]. Thus, they are few suitable for the technology shrink since they require complex adaptations.

### 2.4 Fully Digital Time-to-Digital Converters

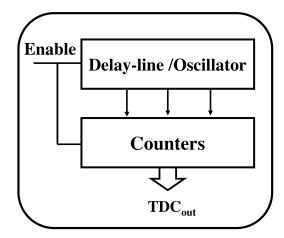

Fully digital techniques have been deployed to overcome the issues presented by the analog TDCs. These can be carried out by very small, low power and simple circuits. The usual architecture of a TDC is simply based on counting the number of edges on a reference clock signal or to propagate an event into a delay-line during the time interval to be measured, as illustrated in Fig. 2.8. Obviously, for an all-digital PLL (ADPLL), the analog TDC are not solicited. In this

case, the digital TDC offers a suitable solution that can be deployed as a digital phase detector [13, 34, 60]. A digital value of the phase error between the reference clock and the feedback signal is given with a configurable CMOS architecture benefiting from a small area and a low power consumption.

FIGURE 2.8: Generic TDC architecture.

#### 2.4.1 TDC with gate-delay resolution

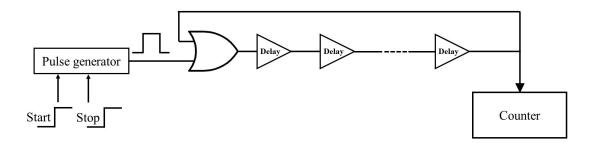

#### 2.4.1.1 Delay-Line based TDC

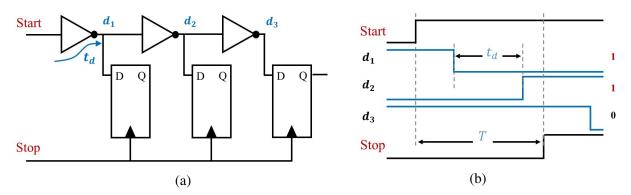

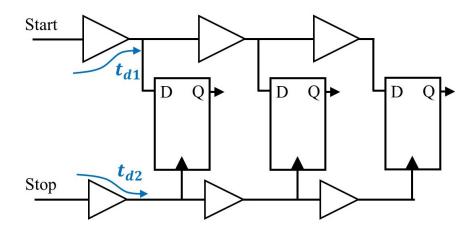

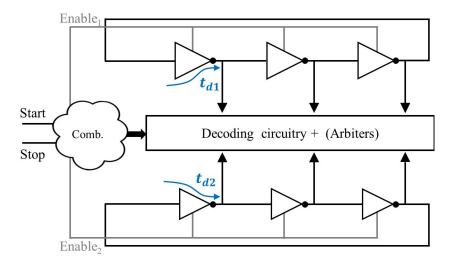

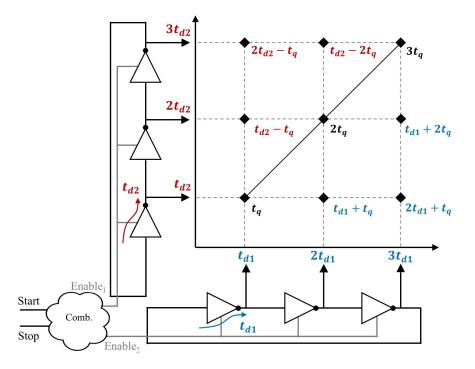

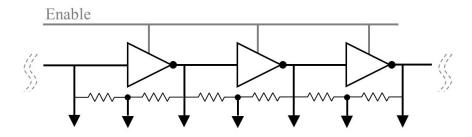

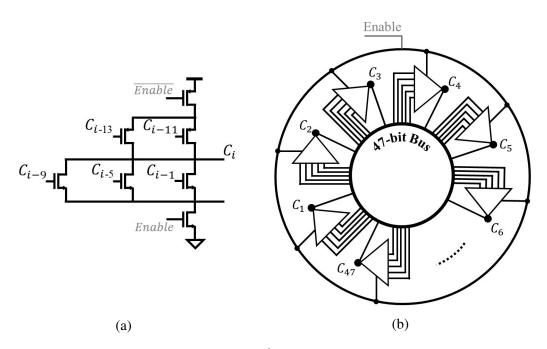

A TDC with gate-delay resolution, called delay-line based TDC, is depicted in Fig. 2.9a. It is a compact architecture that has been proposed as a first fully digital solution. The line is composed of many stages of buffers or inverters [4]. Globally, the Start signal polarity is respected more with buffers than for inverter delays [34]. In this architecture, the Start signal provides an event propagating along the delay line. The arrival of the Stop signal triggers the registers to start copying the state of each gate output. The interpretation of the flip-flop (FF) outputs gives the measured time interval  $T_m$ . In other words,  $T_m$  corresponds to the number of stages that have propagated the Start signal. The measured time is defined by the thermometer code given by the output registers. The process is more explicit in Fig. 2.9b. This topology is the basis for most of the other digital TDC architectures. Admittedly, this TDC is a simple structure that can easily be integrated into an ASIC or an FPGA but at the price of moderate performances. It presents a low latency because the output can be quickly available after the arrival of the *Stop* event. However, its resolution is bounded by the CMOS gate delays; it cannot be lower than the propagation delay of a logical gate. In addition, to cover a larger time interval, the number of stages must be duplicated as needed. Thus, the cost and power consumption will be increased. This concerns as well the maximal sampling rate, which is decreased when drastically expanding the clock tree.

Otherwise, the PVT variations affect the delay of the stages [34]. The jitter contributes to the measurement errors due to the temperature and supply voltage variations. With the accumulation of these random variations, the delay-line may present an important deviation at its end. Furthermore, the linearity could be affected by the random mismatch of the delay-line gates. Therefore, the delay-locked-lines (DLLs) are often deployed to calibrate the process variations [38]. The delay unit of the DLL is voltage-controllable, which allows locking its delay to a fraction of a reference clock whatever the variations [35].

FIGURE 2.9: (a) Basic implementation of a delay-line based TDC, (b) the timing diagram.

#### 2.4.1.2 Ring Oscillator

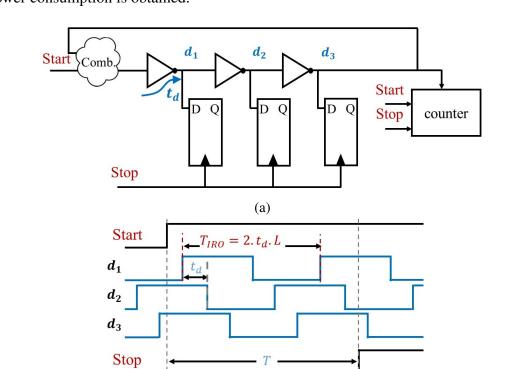

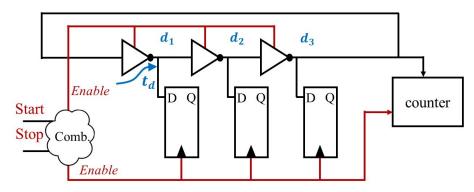

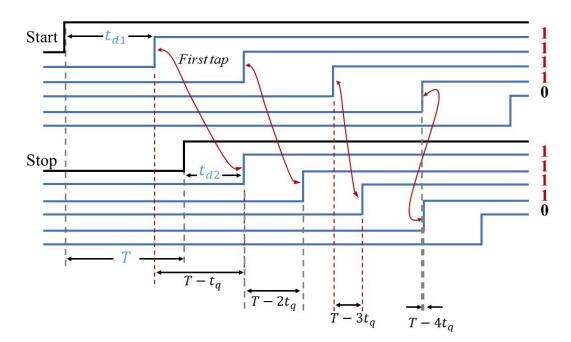

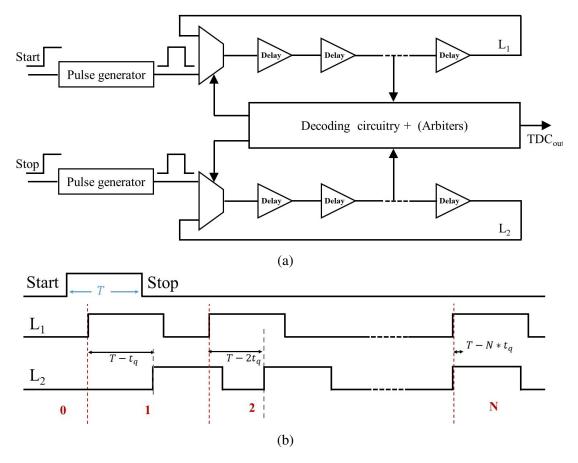

A simple way to overcome the limitation of the dynamic range of the delay-line TDC is to wrap the line into a ring [7,45,62,63]. This makes the inverter ring oscillator (IRO) as shown in Fig. 2.10a. Compared to the simple delay-line, each stage can be used several times. Therefore, the electrical event, which provides the time stamping, will propagate several times in the ring to cover large dynamic ranges. Moreover, a gain of power and area is obtained.

If double edge is considered, using CMOS inverters or buffers as delay gate is the same. Else, using inverters instead of buffers allows doubling the resolution [34]. However, the problem of the transition slope asymmetry related to the design of inverters, can affect the linearity of the TDC. This can be fixed via design but any process variation can produce similar problems [34].

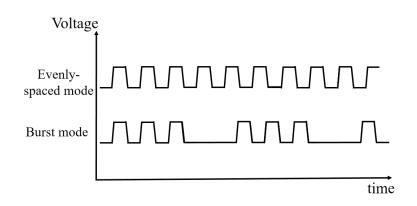

The *Start* and *Stop* signals can be replaced with one *Enable* signal provided by a digital logic block [63]. The multiplexers are used to feed the ring with the adequate signals. However, they are source of asymmetry in the delay-chain, which increases the mismatches and affects as well the linearity performances [34]. Thus, the multiplexer was replaced by NAND gates. Similarly, counters are replacing registers to determine how many times the event looped in the ring. Therefore, the TDC output is obtained by counting the number transitions occurring during T of each delay output and summing the result to express the binary code. In this TDC, high-power consumption occurs due to the free-running mode of the IRO [13]. Otherwise, to simplify the architecture, one counter can be connected to the final stage to measure the number of cycles, for which the event has looped back, providing a coarse evaluation of the time. The

other output registers can be used to evaluate the fine measurement. As a result, a gain in area and power consumption is obtained.

(b)

TDC<sub>out</sub>

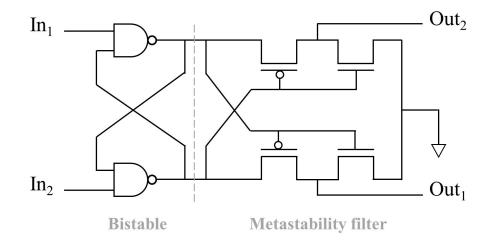

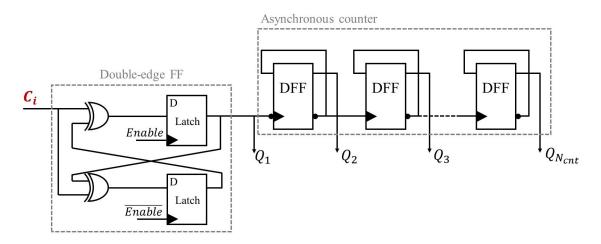

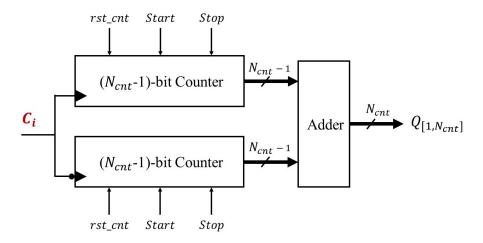

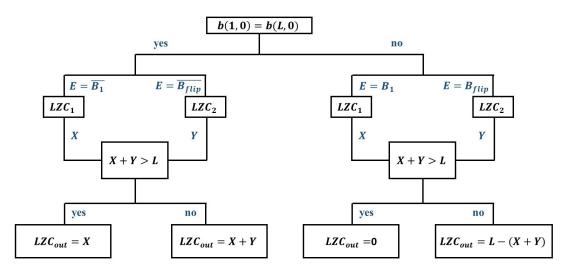

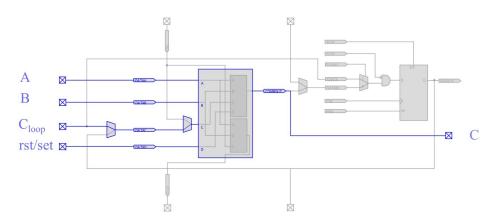

FIGURE 2.10: Inverter Ring Oscillator based TDC example and its timing diagram.