# Leveraging Logic Masking to Facilitate Hardware Trojan Detection Methods

Arash Nejat

#### ▶ To cite this version:

Arash Nejat. Leveraging Logic Masking to Facilitate Hardware Trojan Detection Methods. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2019. English. NNT: 2019 GREAT004. tel-03132626

# HAL Id: tel-03132626 https://theses.hal.science/tel-03132626

Submitted on 5 Feb 2021

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES

Arrêté ministériel : 25 mai 2016

Présentée par

#### **Arash NEJAT**

Thèse dirigée par **Vincent BEROULLE** , Enseignant-chercheur, Grenoble INP

et codirigée par **David HELY**, Maitre de Conférence, Grenoble INP préparée au sein du **Laboratoire Laboratoire de conception et d'intégration des systèmes**

dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

# Tirer parti du masquage logique pour faciliter les méthodes de détection des chevaux de Troie hardware

# Leveraging Logic Masking to Facilitate Hardware Trojan Detection Methods

Thèse soutenue publiquement le **22 janvier 2019**, devant le jury composé de :

#### **Monsieur VINCENT BEROULLE**

MAITRE DE CONFERENCES, GRENOBLE INP, Directeur de thèse **Monsieur DAVID HELY**

MAITRE DE CONFERENCES, GRENOBLE INP, Co-directeur de thèse

#### Monsieur JEAN-LUC DANGER

PROFESSEUR, TELECOM PARISTECH, Rapporteur

#### **Monsieur LIONEL TORRES**

PROFESSEUR, UNIVERSITE DE MONTPELLIER, Rapporteur

#### **Monsieur LILIAN BOSSUET**

PROFESSEUR, UNIVERSITE JEAN MONNET - SAINT-ETIENNE, Examinateur

#### **Monsieur GIORGIO DI NATALE**

DIRECTEUR DE RECHERCHE, CNRS DELEGATION LANGUEDOC-ROUSSILLON, Examinateur

# **Table of Contents**

| List of Acronyms                                                             | VII |

|------------------------------------------------------------------------------|-----|

| List of Figures                                                              | IX  |

| List of Tables                                                               | XII |

| Abstract                                                                     | XIV |

|                                                                              |     |

| Chapter 1 Introduction                                                       | 1   |

| 1.1. Hardware Trojan                                                         | 2   |

| 1.2. IP Piracy                                                               | 3   |

| 1.2.1. State Masking                                                         | 4   |

| 1.2.2. Logic Masking                                                         | 4   |

| 1.3. Major Contributions                                                     | 5   |

| 1.3.1. AMELIORATION                                                          | 6   |

| 1.3.2. ESCALATION                                                            | 7   |

| 1.3.3. RESTORATION                                                           | 8   |

| 1.4. Thesis Outline                                                          | 10  |

|                                                                              |     |

| Chapter 2 Background on Hardware Security                                    | 11  |

| 2.1. Introduction                                                            | 11  |

| 2.1.1. SoC Life Cycle                                                        | 12  |

| 2.1.2. Security Threat Models                                                | 14  |

| 2.2. IP Protection                                                           | 16  |

| 2.2.1. Passive IP Protection Methods: Watermark, Obfuscation, and Camouflage | 16  |

| 2.2.2. IP Piracy Prevention by Active IP Protection Methods                  | 19  |

| 2.2.3. IP Masking                                                                                                                                                                                                                                                           | 21                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 2.2.3.1. State Masking                                                                                                                                                                                                                                                      | . 21                                                                                           |

| 2.2.3.2. Logic Masking                                                                                                                                                                                                                                                      | 22                                                                                             |

| 2.2.3.3. Criteria for Logic Masking                                                                                                                                                                                                                                         | 25                                                                                             |

| 2.2.3.4. Hardware Requirements for IP Masking                                                                                                                                                                                                                               | 26                                                                                             |

| 2.3. Hardware Trojan Threat                                                                                                                                                                                                                                                 | 27                                                                                             |

| 2.3.1. Hardware Trojan Attributes and Taxonomies                                                                                                                                                                                                                            | 27                                                                                             |

| 2.3.2. Hardware Trojan Model                                                                                                                                                                                                                                                | 30                                                                                             |

| 2.3.3. Hardware Trojan Attack Model                                                                                                                                                                                                                                         | . 31                                                                                           |

| 2.3.4. Hardware Trojan Countermeasures                                                                                                                                                                                                                                      | . 34                                                                                           |

| 2.3.4.1. Hardware Trojan Detection                                                                                                                                                                                                                                          | . 35                                                                                           |

| 2.3.4.2. Design for Trust                                                                                                                                                                                                                                                   | 43                                                                                             |

| 2.5.4.2. Design for Trust                                                                                                                                                                                                                                                   |                                                                                                |

| 2.3.4.2. Design for Trust                                                                                                                                                                                                                                                   |                                                                                                |

| Chapter 3 Advantaging Logic Masking to Ameliorate Logic-Testing Based Trojan Detection                                                                                                                                                                                      | 47                                                                                             |

| Chapter 3 Advantaging Logic Masking to Ameliorate Logic-Testing Based                                                                                                                                                                                                       |                                                                                                |

| Chapter 3 Advantaging Logic Masking to Ameliorate Logic-Testing Based Trojan Detection                                                                                                                                                                                      | . 47                                                                                           |

| Chapter 3 Advantaging Logic Masking to Ameliorate Logic-Testing Based Trojan Detection  3.1. Introduction                                                                                                                                                                   | . 47<br>48                                                                                     |

| Chapter 3 Advantaging Logic Masking to Ameliorate Logic-Testing Based Trojan Detection  3.1. Introduction                                                                                                                                                                   | . 47<br>48<br>. 49                                                                             |

| Chapter 3 Advantaging Logic Masking to Ameliorate Logic-Testing Based Trojan Detection  3.1. Introduction                                                                                                                                                                   | . 47<br>48<br>. 49<br>51                                                                       |

| Chapter 3 Advantaging Logic Masking to Ameliorate Logic-Testing Based Trojan Detection  3.1. Introduction                                                                                                                                                                   | . 47<br>48<br>. 49<br>51<br>52                                                                 |

| Chapter 3 Advantaging Logic Masking to Ameliorate Logic-Testing Based Trojan Detection  3.1. Introduction                                                                                                                                                                   | . 47<br>48<br>. 49<br>51<br>52<br>. 57                                                         |

| Chapter 3 Advantaging Logic Masking to Ameliorate Logic-Testing Based Trojan Detection  3.1. Introduction  3.2. Contribution  3.3. Proposed Solution  3.3.1. Security Metric  3.3.2. Greedy Algorithm  3.4. Experimental System Setup and Results                           | <ul> <li>47</li> <li>48</li> <li>49</li> <li>51</li> <li>52</li> <li>57</li> <li>57</li> </ul> |

| Chapter 3 Advantaging Logic Masking to Ameliorate Logic-Testing Based Trojan Detection  3.1. Introduction  3.2. Contribution  3.3. Proposed Solution  3.3.1. Security Metric  3.3.2. Greedy Algorithm  3.4. Experimental System Setup and Results  3.4.1. Experiment setups | . 47<br>48<br>. 49<br>51<br>52<br>. 57<br>57                                                   |

| 3.4.2.3. Joint Evaluation of IP Piracy Protection and Trojan Avoidance                         | 63  |

|------------------------------------------------------------------------------------------------|-----|

| 3.4.2.4. Overhead Results                                                                      | 66  |

| 3.5. Logic Masking Effects on Sequential Circuits                                              | 69  |

| 3.6. Conclusions                                                                               | 73  |

| Chapter 4 Employing Logic Masking To Facilitate Path Delay Analysis-<br>Based Trojan Detection | 75  |

| 4.1. Introduction                                                                              | 75  |

| 4.2. Contributions                                                                             | 76  |

| 4.3. ESCALATION Based Algorithm                                                                | 77  |

| 4.3.1. Vulnerable points in path delay-based Trojan Detection                                  | 77  |

| 4.3.2. Motivations                                                                             | 78  |

| 4.3.3. Examples                                                                                | 79  |

| 4.3.4. Proposed Algorithm                                                                      | 84  |

| 4.3.5. Measuring ESCALATION Efficiency                                                         | 85  |

| 4.3.6. Masking Quality                                                                         | 85  |

| 4.3.7. TDP calculation                                                                         | 86  |

| 4.4. EXPERIMENTAL RESULTS                                                                      | 89  |

| 4.4.1. Experiment Setups and Assumptions                                                       | 89  |

| 4.4.2. TDP Results at Gate Level                                                               | 90  |

| 4.4.3. Masking quality                                                                         | 93  |

| 4.5. Layout Level Validation                                                                   | 96  |

| 4.6. Discussions                                                                               | 98  |

| 4.7. Conclusions                                                                               | 100 |

| Chapter 5 Restricting Switching Activity Using Logic Masking To Improve Power Analysis-Based Trojan Detection | 103 |

|---------------------------------------------------------------------------------------------------------------|-----|

| 5.1. Introduction                                                                                             | 103 |

| 5.2. Contributions                                                                                            | 104 |

| 5.3. RESORATION Based Algorithm                                                                               | 105 |

| 5.3.1. Partitioning Aware Input Vector Generation Method                                                      | 106 |

| 5.3.2. A New Logic Masking Method                                                                             | 108 |

| 5.3.3. Proposed Algorithm                                                                                     | 112 |

| 5.4. Experiments and Results                                                                                  | 116 |

| 5.4.1. Experiments Flow                                                                                       | 116 |

| 5.4.2. Results                                                                                                | 117 |

| 5.4.2.1. Circuit c432                                                                                         | 118 |

| 5.4.2.2. Circuit c880                                                                                         | 120 |

| 5.4.2.3. Other Circuits                                                                                       | 122 |

| 5.5. Conclusions                                                                                              | 123 |

|                                                                                                               |     |

| Chapter 6 Conclusion and Feature Work                                                                         | 125 |

| 6.1. Conclusion                                                                                               | 125 |

| 6.2. Ongoing and Feature Work                                                                                 | 128 |

| 6.2.1. A New AMELIORATION-Based Algorithm                                                                     | 128 |

| 6.2.2. Two New ESCALATION-Based Algorithms                                                                    | 128 |

| 6.2.3. A New RESTORATION-Based Algorithm                                                                      | 130 |

|                                                                                                               |     |

| Chanter 7 References                                                                                          | 133 |

# **List of Acronyms**

ADC Analog-Digital Converter

BEOL Back-End-Of-Line

BFS Breadth First Search

CAD Computer-Aided Design

COTS Commercial-Off-The-Shelf

CUTT Circuit Under Trojan Test

DAC Digital-Analog Converter

DfTr Design for Trust

DSP Digital Signal Processor

FBA Fault-Based Analysis

FEOL Front-End-Of-Line

FF Flip Flop

FPGA Field Programmable Gate Array

FPR False Positive Rate

FSM Finite State Machine

GDSII Graphic Database System

HD Hamming Distance

HDL Hardware Description Language

HDP Hardware Trojan Detection Probability

HT Hardware Trojan

I/O Input/ Output

IC Integrated Circuit

IDDq Leakage Current

IDDt Transient Current

IP Intellectual Property

IVG Input Vector Generation

KG Key-Gate

KI Key-Input

KL Kernighan–Lin

LOG SATT Logic Simulation, Security, And Trust Analysis Tool

MSP Maximum Shortest Path

MUX Multiplexer

PCA Power Consumption Analysis

PDA Path Delay Analysis

PDF Probability Distribution Functions

PI Primary Input

PO Primary Output

PSI Pseudo Input

PSO Pseudo Output

PUF Physical Unclonable Function

PV Process Variation

RO Ring Oscillator

RS Rare Signal

RTL Register Transfer Level

SAL Switching Activity Localization

SoC System On Chip

SSA Sum Of Switching Activity

TCA Trojan To Circuit Activity

TCP Trojan To Circuit Power

TDP Trojan Detection Probability

TDR Trust-Driven Retiming

TRNG True Random Number Generator

# **List of Figures**

| Figui | re                                                                                                                                         | Page |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | SoC including trusted, Trojan-infected, and suspicious IPs                                                                                 | 12   |

| 2.2   | Six periods of the SOC life cycle and possible security threats                                                                            | 12   |

| 2.3   | An embedded watermark that includes three states and is reachable in one state (S3) of the host circuit.                                   | 17   |

| 2.4   | An obfuscator that renames inputs, outputs, variables                                                                                      | 18   |

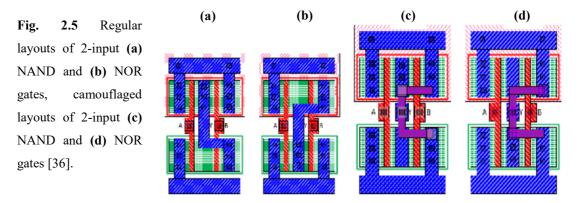

| 2.5   | Regular layouts of 2-input (a) NAND and (b) NOR gates, camouflaged layouts of 2-input (c) NAND and (d) NOR gates                           | 19   |

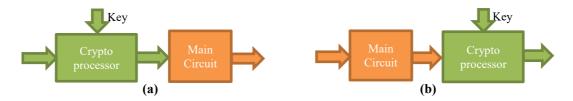

| 2.6   | Circuit encryption using a crypto processor in (a) inputs, (b) outputs                                                                     | 20   |

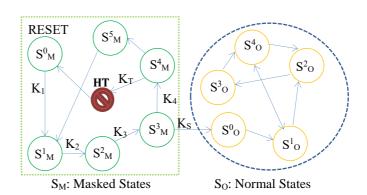

| 2.7   | FSM structure of a masked sequential circuit; an inserted Hardware Trojan will be active by a specific input (KT) in the added FSM         | 21   |

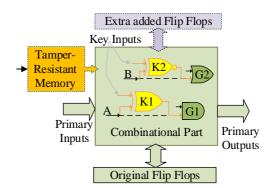

| 2.8   | Mealy machine view of a masked circuit, including two key-gates and key-inputs, and a tamper-resistant memory which drives key-inputs      | 23   |

| 2.9   | 2-to-1 multiplexer cell as a key-gate and its truth table                                                                                  | 24   |

| 2.10  | Four hardware Trojan taxonomies based on four Trojan attributes: insertion phase, abstraction level, intention, and location               | 28   |

| 2.11  | Trojan taxonomy based on physical characteristics                                                                                          | 29   |

| 2.12  | Trojan taxonomy based on activation characteristics                                                                                        | 30   |

| 2.13  | Abstract hardware Trojan model including the trigger and payload part                                                                      | 30   |

| 2.14  | Taxonomy of Trojan triggers and payloads                                                                                                   | 31   |

| 2.15  | Taxonomy of Trojan countermeasures                                                                                                         | 35   |

| 3.1   | A circuit with three AND gates, a numerical pair on the top of each signal shows the probability of being '0' and '1'                      | 51   |

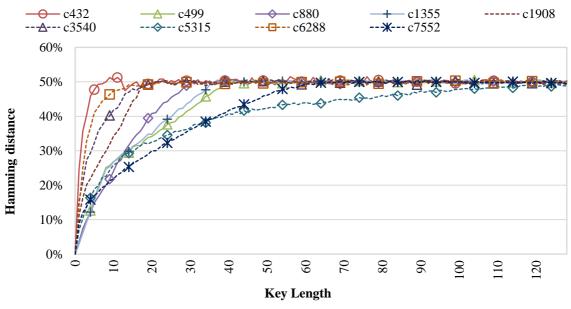

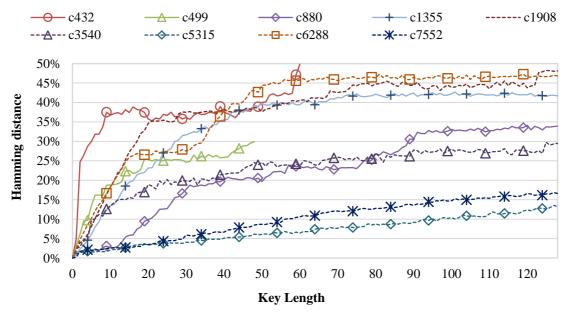

| 3.2   | Hamming distance of the output bits for each key length, using Security-Metric <sub>HAHB</sub> = HB, $(\omega 1, \omega 2) = (0, 1) \dots$ | 61   |

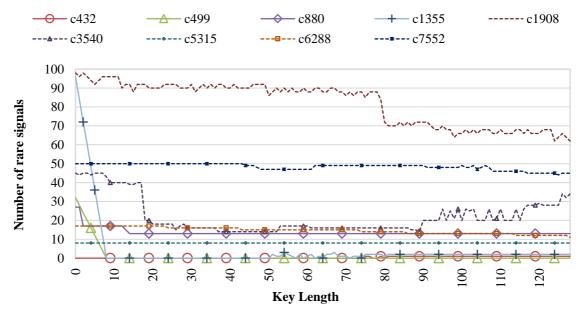

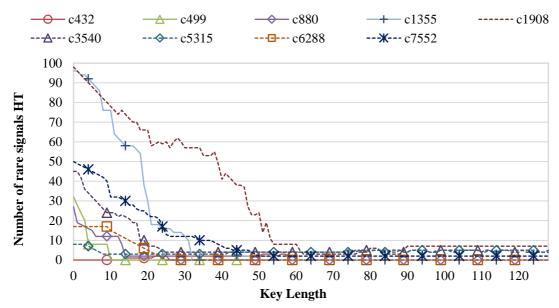

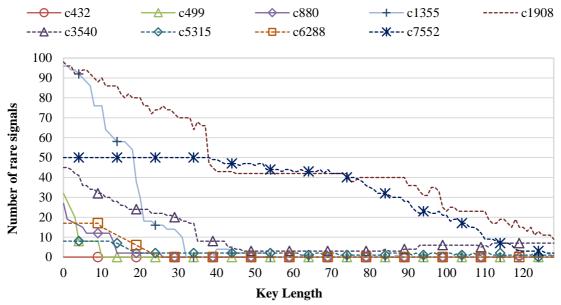

| 3.3   | The number of rare signals for each key length using Security-Metric <sub>HAHB</sub> = HB, $(\omega 1, \omega 2) = (0, 1) \dots$           | 61   |

| 3.4  | The number of rare signals for each key length using Security-Metric <sub>HAHB</sub> = HA, $(\omega 1, \omega 2) = (1, 0)$                                                                          | 02 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | Hamming distance of the output bits for each key length, using Security-Metric <sub>HAHB</sub> = HA, $(\omega 1, \omega 2) = (1, 0) \dots$                                                          | 62 |

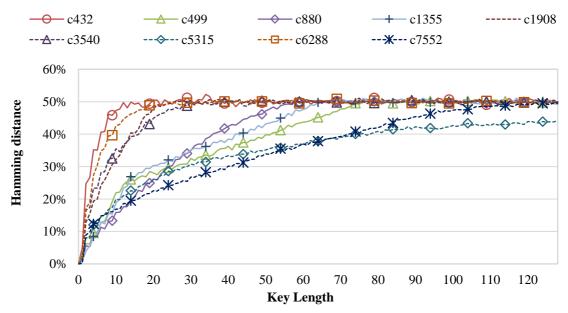

| 3.6  | Hamming distance of the output bits for each key length, using Security-Metric <sub>HAHB</sub> , $(\omega 1, \omega 2) = (0.5, 0.5)$                                                                | 63 |

| 3.7  | The number of rare signals for each key length using Security-Metric <sub>HAHB</sub> , $(\omega 1, \omega 2) = (0.5, 0.5)$                                                                          | 64 |

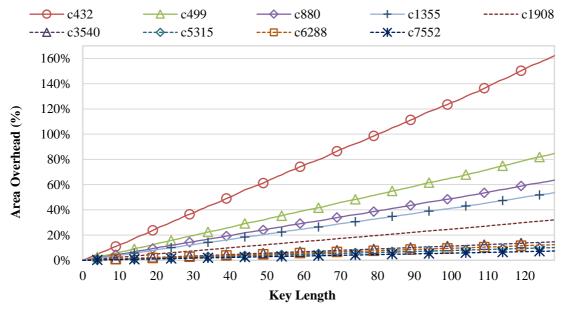

| 3.8  | Area overhead of the proposed algorithm for different key lengths                                                                                                                                   | 66 |

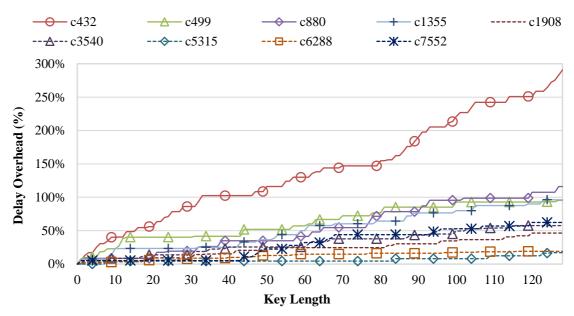

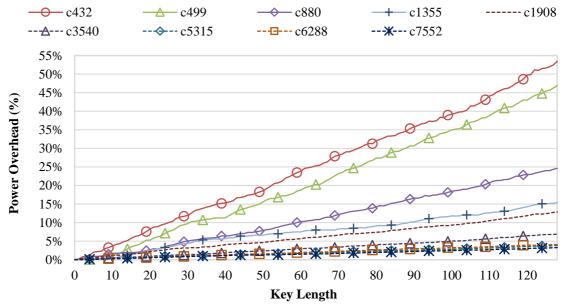

| 3.9  | Delay overhead of the proposed algorithm for different key lengths                                                                                                                                  | 67 |

| 3.10 | Power overhead of the proposed algorithm for different key lengths                                                                                                                                  | 67 |

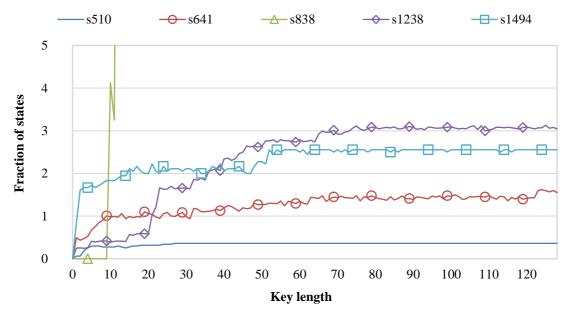

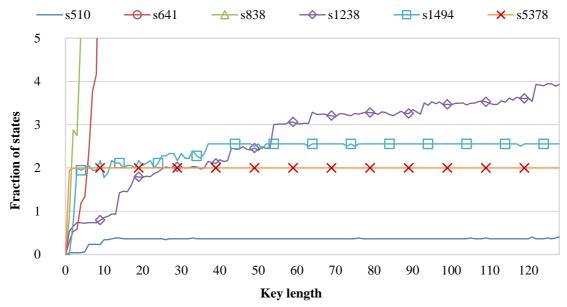

| 3.11 | The fraction of the number of states before and after performing the proposed logic masking algorithm along with Security-Metric <sub>HAHB</sub> for each key lengths                               | 71 |

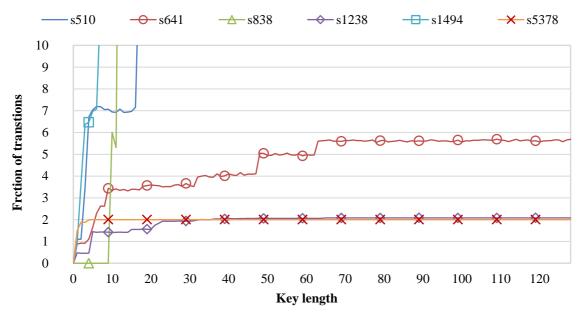

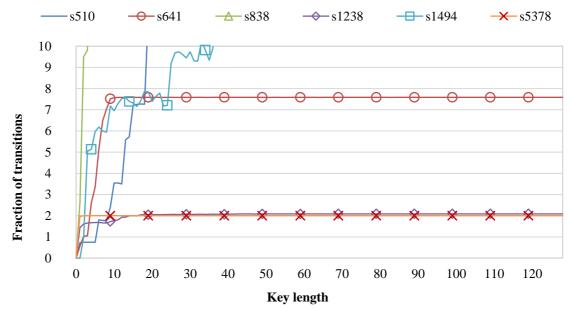

| 3.12 | The fraction of the number of transitions before and after performing the proposed logic masking algorithm along with Security-Metric <sub>HAHB</sub> for each key lengths                          | 72 |

| 3.13 | The fraction of the number of states before and after performing the random logic masking algorithm                                                                                                 | 72 |

| 3.14 | The fraction of the number of transitions before and after performing the random logic masking algorithm                                                                                            | 73 |

| 4.1  | Four paths from a primary input to a primary output                                                                                                                                                 | 80 |

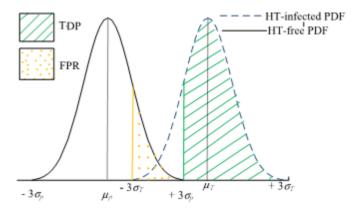

| 4.2  | The probability distribution functions of a path with a Trojan (dashed lines) and without any Trojan (solid lines). The area of the shaded part is equal to TDP with 0% FPR. The dotted area is FPR | 87 |

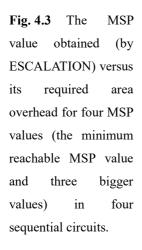

| 4.3  | The MSP value obtained (by ESCALATION) versus its required area overhead for four MSP values (the minimum reachable MSP value and three bigger values) in four sequential circuits                  | 91 |

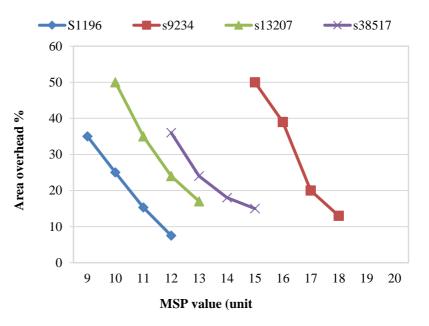

| 4.4  | Results of TDR and two executions of ESCALATION. ESCALATION1 (ESCALATION2) needs a bit less (more) area overhead than TDR. a: MSP values, b: area overheads                                         | 92 |

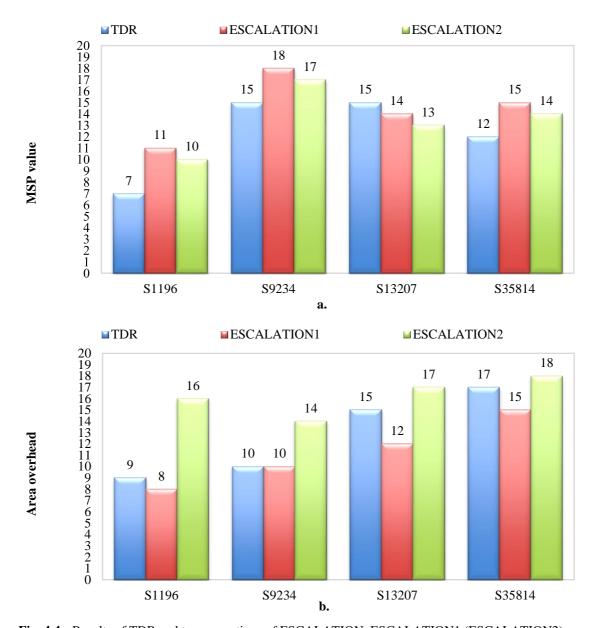

| 4.5  | Output failures versus area overhead for both HARPOON [6] and ESCALATION                                                                                                                            | 95  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

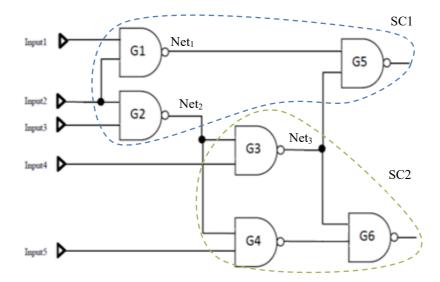

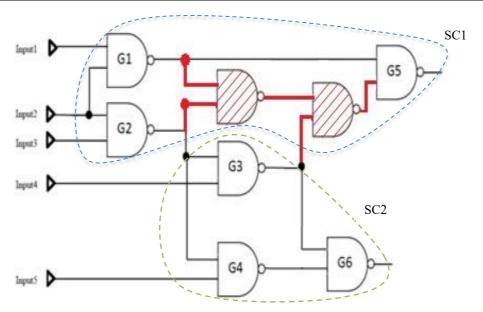

| 5.1  | Circuit c17 partitioned to the sub-circuits SC1 and SC2                                                                                                                                             | 107 |

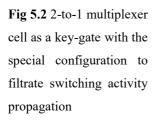

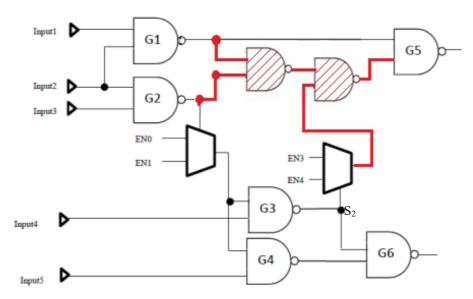

| 5.2  | 2-to-1 multiplexer cell as a key-gate with the special configuration to filtrate switching activity propagation                                                                                     | 109 |

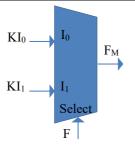

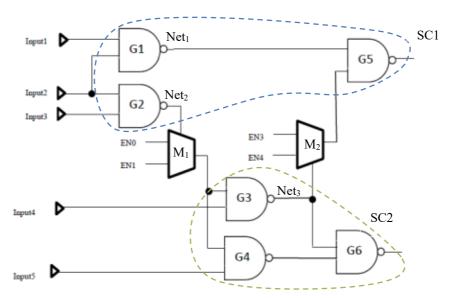

| 5.3  | The masked version of circuit c17 using two MUX key-gates inserted on two nets interconnecting sub-circuits SC1 and SC2 in order filtrate the switching propagation form a partition to another one | 109 |

| 5.4  | Circuit c17 infected by a hardware Trojan including two NAND gates and partitioned to the sub-circuits SC1 and SC2                                                                                  | 111 |

| 5.5  | Circuit c17 masked using two MUX key-gates and infected by a hardware Trojan including two NAND gates                                                                                               | 112 |

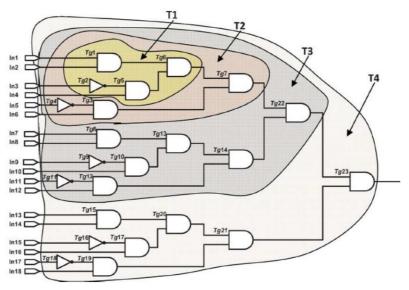

| 5.6  | Trojan benchmarks proposed in [14]                                                                                                                                                                  | 117 |

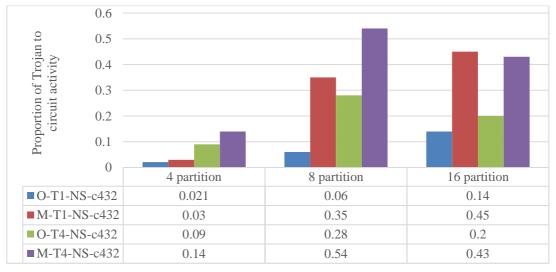

| 5.7  | Obtained TCA in four circuits O-T1-NS-c432, M-T1-NS-c432, O-T4-NS-c432, and O-T4-NS-c432 using the partition-based IVG methods                                                                      | 119 |

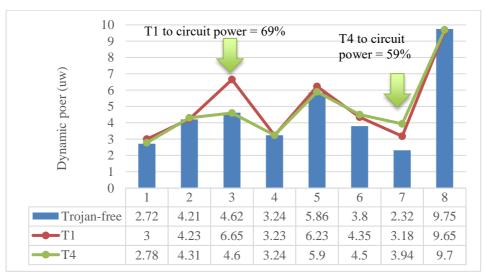

| 5.8  | PCA in circuits M-TF-S-c432, M-T1-S-c432, and M-T4-S-c432 using the partitioning aware IVG methods and individually targeting eight made partitions                                                 | 120 |

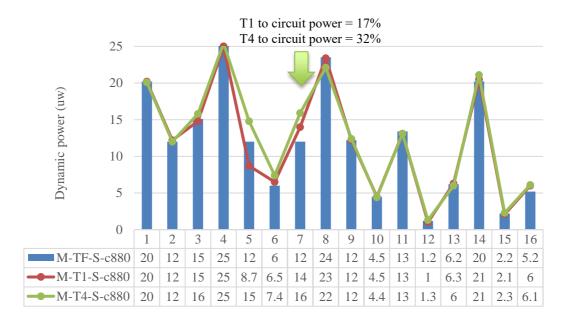

| 5.9  | PCA in circuits M-TF-S-c880, M-T1-S-c880, and M-T4-S-c880 using the partitioning-based IVG methods and individually targeting sixteen made partitions                                               | 122 |

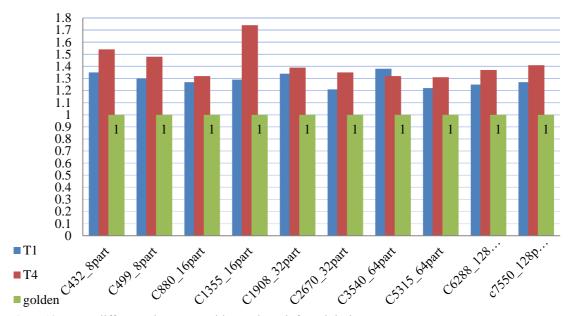

| 5.10 | nower difference between golden and HT infected designs                                                                                                                                             | 123 |

# **List of Tables**

| Tables                                                                                                                                                                                                                    | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1 Trojan attack model based on suspiciousness foundries that may insert hardware Trojans                                                                                                                                | 32   |

| 3.1 Details of the used benchmark circuits                                                                                                                                                                                | 58   |

| 3.2 HD achievement by the FAB [5] and the proposed algorithm using Security-Metric <sub>HB</sub> and Security-Metric <sub>HAHB</sub>                                                                                      | 65   |

| 3.3 Area, power, and performance overheads for each benchmark regarding the number of used key-gates to reach 50% hamming Distance                                                                                        | 68   |

| 4.1 MSP value, TDP, and required FPR to obtain 100% TDP before and after performing the proposed algorithm on sequential circuits, accepting 20% area overhead and assuming unit delay model and 60% cell delay variation | 94   |

| 4.2 Comparing HD results of random masking, ESCALATION, and FBA                                                                                                                                                           | 96   |

| 4.3 HDP of MSP in the original and masked circuits; performance and area overhead in layout level                                                                                                                         | 98   |

| <ul><li>5.1 The number and percentage of switching activity for each sub-circuit in Fig.</li><li>5.1 obtained by the circuit-partitioning aware IVG method</li></ul>                                                      | 108  |

| <ul><li>5.2 The number and percentage of switching activity for each sub-circuit in Fig.</li><li>5.3 obtained by the IVG based on the partitioning information</li></ul>                                                  | 110  |

| 5.3 TCA and the number of switching activity in the circuit of Fig. 5.4 and its hardware Trojan obtained by applying random input vectors to all the primary inputs and key-inputs                                        | 111  |

| 5.4TCA and the number and percentage of switching activity for each sub-circuit in Fig. 5.4 obtained by the circuit-partitioning aware IVG method                                                                         | 111  |

| 5.5 TCA and the number and percentage of switching activity for each sub-circuit in Fig. 5.4 obtained by the input vector generation based on the partitioning information                                                | 112  |

| 5.6 The number of transitions in circuit O-TF-NS-c432 using the random and partitioning aware IVG methods                                                                                                                 | 118  |

| 5.7 The power consumption in circuit O-TF-S-c432 using the random and partitioning aware IVG methods                                                                                                                      | 118  |

| 5.8 The number of transitions in circuit O-TF-NS-c880 using the random and   | 121 |

|------------------------------------------------------------------------------|-----|

| partitioning based IVG methods                                               |     |

| 5.9 The power consumption of the circuits synthesized from c880 "original or | 121 |

| masked" \ "Trojan-free or Trojan-infected                                    |     |

# **Abstract**

The ever-increasing complexity of integrated circuits (ICs) design and manufacturing has necessitated the employment of third parties such as design-houses, intellectual property (IP) providers and fabrication foundries to accelerate and economize the development process. The separation of these parties results in some security threats. Untrustworthy fabrication foundries are suspected of three security threats: hardware Trojans, IP piracy, and IC overproduction. Hardware Trojans are malicious circuitry alterations in IC layouts intended for sabotage objectives.

Some IC design modifications, known as Design-for-Trust (DfTr) have been proposed to facilitate Trojan detection methods or prevent Trojan insertion. In addition, key-based modifications, known as design masking or obfuscation, have been proposed to protect IPs/ICs from IP piracy and IC overproduction. They obscure circuits' functionality by modifying circuits such that they do not correctly work without being fed with a correct key.

In this thesis, we propose three DfTr methods based on leveraging the masking approach to hinder Trojan insertion. The first proposed DfTr method aims to maximize obscurity and simultaneously minimize the rare signal counts in circuits under masking. Rare signals barely have transitions during circuit operations and so the use of them causes hardware Trojans will not be easily activated and detected during circuit tests. The second proposed DfTr facilitates path delay analysis-based Trojan detection methods. Since the delay of shorter paths varies less than longer ones', the objective is to generate fake short paths for nets which only belong to long paths by repurposing the masking elements. Our experiments show that this DfTr method increases the Trojan detectability in modified circuits and also provides the advantages of masking methods. The aim of

the third DfTr method is to facilitate power-analysis-based Trojan detection. In a masked circuit by the proposed method, one has more control over the switching activity of the different circuit parts. For instance, one can target one part of the circuit, increase its switching activity, and simultaneously decrease the other parts' switching activity; consequently, if the target part includes an hardware Trojan, its switching activity and so power consumption rises, although the total power consumption of the circuit goes down due to low switching activity rates in most parts of the circuit. When the circuit consumes less power, the power measurement noise abates. The noise can disturb to observe Trojans' effects on the power consumption of Trojan-infected circuits.

In addition, in this thesis, we introduce a CAD tool that can run various masking algorithms on gate-level netlists. The tool can also perform logic simulation and estimate circuit area, power consumption, and performance at the gate level.

# **Chapter 1**

# Introduction

During the last two decades, a fabless business model has emerged into semiconductor industries due to costly fabrication processes of integrated circuits (ICs) [1]. In this model, semiconductor companies outsource the manufacturing part of their designs to third fabrication foundries, shortly called *fabs*. On the other hand, time-to-market and design complexity issues associated with today's system-on-chips (SoCs) have convinced design houses to employ predesigned circuit blocks, called *intellectual properties* (IPs) [1]. However, the separation of design houses, IP developers, and fabs in the fabless model has economic advantages, it entails serious security challenges. For instance, design houses may illegally sell IPs that they purchased from IP developers. Likewise, untrustworthy fabs can also extract IPs from their costumers' layouts and then pirate them. In addition, they can clone or overproduce the layouts [2]. In literature, this threat is known as IP piracy. Untrustworthy IP developers and fabs are suspected of another security threat in which malicious circuits, known as *hardware Trojans*, are added to IPs or fabricated ICs for sabotage objectives. These issues are some security threats in the fabless business model. For each threat, detection and prevention methods have been

2 1. Introduction

proposed in many research work [3]. The focus of this dissertation is on detecting and preventing hardware Trojan and IP piracy threats that may happen in untrustworthy fabrication foundries.

# 1.1 Hardware Trojan

Hardware Trojans can cause secret information leakage, malfunctions in specific circumstances, or performance downgrade in Trojan-infected ICs [4]. Regarding ICs' application, design, and fabrication technology, various hardware Trojans can be designed. Therefore, different detection methods have been proposed. These methods are based on either *side-channel analysis* or *logic testing*. The former one is the inspection of circuit parameters like power consumption, and logic testing is based on conventional functional/structural tests and includes generating and applying proper input patterns and then observing their results [5]. Any abnormality in measured side-channels or captured outputs can warn the presence of a hardware Trojan.

Side-channel-analysis-based detection methods face two important challenges: process and environmental variations. Process variations happen during IC manufacturing and cause variations in some transistor characteristics such as channel length and oxide-thickness. Environmental variations happen while a circuit is working and induce changes in the operating environment of the circuit such as temperature and supply voltage. Trojans effects on side-channels may be undetectable among effects of process and environmental variations. Logic-testing-based detection methods are also a challenging task because one must generate proper test vectors to catch Trojans effects on the outputs; and skillful Trojan attackers try to use low-controllable and low-

observable signals for Trojan activation and mission, respectively.

The challenges in Trojan detection impose some design modifications on designers to integrate security and trust into fabricated ICs. This approach is entitled Design-for-Trust (DfTr) [6]. Two main categories of DfTr approaches are 1) preventing Trojan insertion that hinders Trojan attackers for inserting hard-to-detect Trojans and 2) facilitating Trojan detection that boosts logic testing and side-channel analysis-based Trojan detection methods. More details and examples of Trojan characteristics, taxonomies, detection methods, and DfTr are presented in Section 2.

# 1.2 IP Piracy

Untrustworthy design houses and fabs are suspected of the IP piracy threat. One prevention approach for this threat is *design masking* that aims at obscuring the original functionality of a circuit by adding some inputs, gates, and flip-flops to the circuit. A masked circuit correctly functions only if it is fed with a correct specific value, like a correct key. In other words, if someone applies any incorrect key to a masked circuit, it malfunctions. Only authorized users (i.e., IP or IC owners) must have this correct key. Therefore, the piracy of a masked circuit is meaningless as long as the key is not revealed.

Authors have used different names for the mentioned approach, such as *obfuscation*, *encryption*, *locking*, and *masking*. The authors in [11] discussed that the term masking is more accurate than other ones. In this dissertation, hereafter, *state masking* and *logic masking* will be used to refer to the approach at register transfer level (RTL) and gate level, respectively.

4 1. Introduction

# 1.2.1 State Masking

The first step of design masking is *state masking* that modifies the finite state machine (FSM) of a circuit at RTL [7]. The modified FSM has the original states of the circuit plus some added fake ones. It starts from a new start state on power-up, and one needs to know a specific inputs sequence, as the key, to pass the fake (masked) states and reach the original start state.

In order to interlock the original and fake states, designers have to make several transitions from original states to fake ones, and vice versa [8]. For this aim, one can synthesize the modified FSM to a gate-level netlist (non-optimized and not technology-mapped netlist) and then perform logic masking on the combinational part.

# 1.2.2 Logic Masking

The design modifications in logic masking usually include adding some inputs and XOR/XNOR gates to the combinational part of a circuit at the gate level. These inputs and gates are usually called *key-input* and *key-gate* in the literature. Applying incorrect value (key) to the key-inputs results in faults at the output of some of the added key-gates. These faults may be propagated to the primary outputs, and then make failures.

Logic (and state) masking methods can hinder Trojan insertion as well, however, their first objective is to prevent IP piracy. Indeed, Trojan attackers cannot easily have enough knowledge about masked circuits. In other words, they need to know the correct key of a masked circuit in order to insert a well-designed hardware Trojan. For instance, without knowing the correct key, an attacker may insert a hardware Trojan in a masked circuit

somehow the Trojan may be activated only when the circuit is fed with an incorrect key [9].

# 1.3 Major Contributions

This doctoral dissertation presents discussions about IP piracy and Trojan insertion in untrustworthy fabs and how logic masking can counter Trojan threats. The basic objective and attitude in this work are to leverage logic masking to hinder Trojan insertion and facilitate Trojan detection methods based on logic-testing and side-channel analysis. Accordingly, the main contributions of this dissertation include three proposed approaches for three objectives, as follows:

- 1. Approach 1: Advantaging logic Masking to amELiorate functIOnal/stRuctural testing-bAsed Trojan detectION (*AMELIORATION*).

- 2. Approach 2: Employing logic maSking to faCilitate pAth deLay Analysis-based Trojan detectION (ESCALATION).

Approach 3: REstricting Switching acTivity using LOgic masking to improve power Analysis-based Trojan DetectION (*RESTORATION*).

For each proposed approach, logic masking methods and algorithms will be proposed and run on some circuit benchmarks and then the achievement will be measured by comparing both the masked and original circuits. In addition, the quality of masking in some circuits masked by different logic masking algorithms will be measured according to two main criteria: 1) the Hamming distance between correct and incorrect output bits of a masked circuit while applying correct and incorrect keys [12], 2) the number of

6 1. Introduction

mismatch points between an original circuit and its peer masked circuit [9]. First criteria can be measured by applying many input vectors and keys (to the primary inputs and key-inputs, respectively) and then comparing the output vectors of the masked and original circuit, for each applied input vectors. For the second criteria, formal verification tools can be used to compare the original circuit with its peer masked circuit. In the following, each proposed approach is briefly explained.

#### 1.3.1 AMELIORATION

The first proposed approach concerns rare (low-controllable) signals that barely have transitions during the circuit operation either in the normal mode or test mode. A masked circuit by the proposed approach has two challenges for Trojan attackers: 1) lack of knowledge about the original functionality of the being attacked circuit, 2) shortage of rare signals for design Trojan activation mechanisms. In normal circuits, Trojan attackers can easily find rare signals. The use of rare signals causes hardware Trojans will not be easily activated during the logic tests or normal operations [10]. In masked circuits, finding rare signals is difficult, because the key-gates and key-inputs affect the transition rate of the signals. Indeed, the transition rate (and controllability) of key-inputs, like that of the primary inputs, is máximum. Each key-input is directly connected to one input of a key-gate. Thus, the transition rate and controllability of some signals would increase if key-gates are preceded them.

AMELIORATION aims at mystifying circuit original functionality and removing rare signal, simultaneously. It checks all signals of a circuit to find the best ones, according to the aims, for inserting on XOR/XNOR key-gates. To find such signals, a security metric

is proposed that employs "high balanced Hamming distance achievement" and "rare signals elimination". It should be noted that if there is no rare signal in a circuit, the chance of the Trojans activation is increased. The more Trojan activation chance is, the more faults caused by the Trojan will be observed. To avoid this, a Trojan attacker must make rare signals by performing logic operations (such as AND or OR) on normal signals. This production of rare signals increases his Trojan size; therefore, the Trojan affects more on side-channel parameters, such as power consumption or paths' delay [3].

In this work, an algorithm based on approach AMELIORATION has been implemented; and its efficiency has been evaluated in a toolset has been designed and developed using c# programming language. It gets the gate-level netlist of a circuit, performs logic simulations, and applies the proposed approach. The simulation results on ISCAS-85 circuit benchmarks show that the proposed method offers high quality of logic masking while also significantly reduces the number of rare signals. Furthermore, the toolset extracts and reported the amount of area, power consumption, and delay overheads at the gate level.

#### 1.3.2 ESCALATION

The second proposed approach masks the circuit functionality while improving the efficiency of path delay-based Trojan detection methods. Such methods can detect a Trojan if its effects on the delay of the paths of the Trojan-infected circuit are perceivable from among process variation effects. Shorter paths have less delay variation that longer ones, proven in [13]. Thus, apart from logic masking benefits, the objective of ESCALATION is to generate short paths using key-gates and key-inputs for nets that only

8 1. Introduction

belong to long paths.

It should be noted that if all nets of a circuit at least belong to one enough-short path, it will be easier for defenders to detect any potential Trojans. In this condition, in order to hide Trojan delay effects, attackers can increase the drive strength and capacity load of the cells which are before and after the targeted Trojan. These changes increase the Trojan power consumption, and so increase the success of power-analysis-based Trojan detection methods.

An algorithm based on this approach will be implemented in this work. The masked circuits by this algorithm were also synthesized, placed, and routed in order to validate the Trojan detection efficiency of the proposed algorithm at the layout level. The obtained results show that ESCALATION can improve Trojan detection probability in path delay-based detection methods. In addition, the ability of the implemented algorithm to mask circuit functionality will be evaluated based on Hamming distance, as the meter. The results show that the implemented algorithm achieves better Hamming distance than the random masking, presented in Chapter 2.

#### 1.3.3 RESTORATION

The third proposed approach concerns the proportion of Trojan power to circuit power. The power consumption of hardware Trojans will be observable if they raise the power consumption of Trojan-infected circuits to a value more than the expected one. The expected power consumption is different in different states of the circuit. Moreover, the power of two instances of a circuit in two ICs and in the same circuit state are different due to process variations. In circuitry situations that a circuit uses more power (e.g.

because of more internal cells activities), the power variation is more than that of the circuit uses less power, proven in [14]. Thus, in order to increase the success chance of power-analysis-based Trojan detection methods, one has to increase Trojan power and simultaneously decrease circuit power.

Trojans power will probably rise by increasing the switching activity of their host circuit, but it increases the total power consumption of circuit, hence, the circuit power variations are increased. To solve this problem, one must localize switching activity; it means that the switching activity of one small part of IC must be increased while that of other IC parts simultaneously decreased [14].

To localize switching activity in special parts of a circuit, RESTORATION divides the circuit into regions, and then adds one key-gate to each one. In each region, all of the key gates are controlled by one key input, and so the number of key inputs is equal to the number of regions.

An algorithm based on RESTORATION approach was implemented in this work. The algorithm gets the gate-level netlist of a combinational circuit; since there is no physical information in this level, the algorithm runs a portioning algorithm and assigns one keygate to each partition. The experiment results in this level show that RESTORATION well localizes switching activity for each partition; consequently it can improve Trojan detection probability in power-analysis-based detection methods, as matter of fact that physical synthesis tools in the placement step try to place cells of a partition, which are highly logical-correlated, close to each other with the aim of decreasing costs of routing (wire lengths and so power and performance).

1. Introduction

# 1.4 Dissertation Outline

The rest of this dissertation is organized as follows: Section 2 reviews literature related on both IP piracy and hardware Trojan. Section 3 details the ALEMORATION approach and introduces a CAD tool. Section 4 presents and evaluates the ESCALATION approach and an algorithm based on it. Section 5 explains the RESTORATION approach and proposes a simple algorithm based on that. In addition, it presents the primary results of the algorithm. Finally, Section 6 summarizes the dissertation and discusses future perspectives.

# **Chapter 2**

# **Background on Hardware Security**

#### 2.1 Introduction

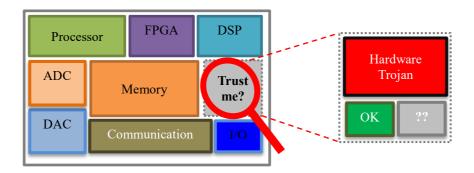

Due to the expensive production cost of today's SoCs, the fabless business model has progressively become the main model in the semiconductor industry over the last decade [1, 15]. In this model, semiconductor companies prefer to only design their SoCs layout and then outsource them to a third-party manufacturer, shortly called *fab* [16]. Moreover, semiconductor companies purchase IPs and use them in their SoCs design, in order to decrease the time-to-market and design complexities [16]. Fig. 2.1 shows a SoC including different blocks. These blocks may be purchased from different IP suppliers across various countries. Although the fabless model reduces the final cost of the SoCs production, it faces security challenges among its involved parties [17]. In the following sections, security threats that may happen by involved different third-parties during the SoC life cycle are presented.

Fig. 2.1 A SoC including trusted, Trojan-infected, and suspicious IPs [18, 19]

# 2.1.1 SoC Life Cycle

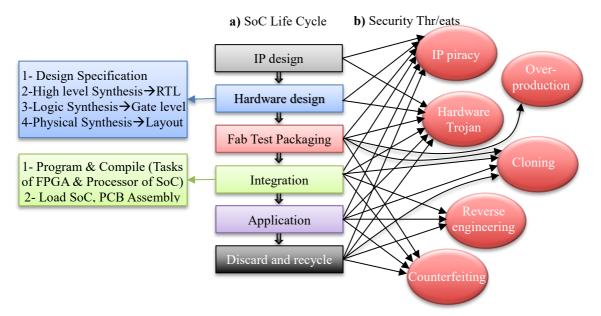

The life cycle of SoCs includes six periods [18, 19], shown in Fig. 2.2.a. In the first period, the IP design period, IP suppliers prepare IPs which could be further integrated into SoCs. During designing an IP, its developer may buy and use IPs from other suppliers. IPs are offered in three forms: 1) synthesizable RTL specifications, 2) generic gate-level netlists, and 3) placed and routed transistors in layout formats (like GDSII) [20].

Fig. 2.2 a) Six periods of the SOC life cycle and b) possible security threats [18-19]

The second period of the SoC life cycle is the hardware design period. In this period, a design house starts to design the hardware part of a SoC, from a high-level description to the layout level. The hardware design flow includes some usual steps, shown in the left side of Fig. 2.2.a [19]. At first, the design house specifies the description of the intended SoC. According to this specification, the design house needs to prepare different circuit blocks. They implement some of these blocks; the other blocks have to be purchased from IP suppliers. During the implementation of the blocks, the design house has to also decide about the required technology and perform logical and physical synthesis. As industrial logical/physical synthesis tools are expensive, they may decide to outsource the RTL/gate-level specifications of the intended blocks (besides the purchased IPs at these levels) to another company to generated technology-mapped netlists for each block [21]. Similarly, these netlists may be again outsourced to other third parties in order to perform physical syntheses and obtain their layouts, seen in Fig. 2.2.a. Finally, all the blocks are gathered to obtain the layout level specification of the SoC.

The third period of the SoC life cycle is the fabrication period in which a SoC layout and information for its tests are outsourced to a fab [22]. The fab may either test the fabricated instances (dies) of the SoC layout by own or ask another company to do it [23]. The goal of these tests is to find circuit defects, happened during the manufacturing, and separate the defective dies from the well-fabricated ones. Another third party probably contributed to the fabrication period is packaging companies. They package each the-tests-passed die into a complete chip. Finally, the fab delivers back the chips to the design house.

The fourth period is when a design house sells a SoC chip to their clients who ordered the SoC and intended to use it [24]. The clients program the processor and reconfigurable parts of the SoC and then integrated it in their board-level design as the final product, which offers services to end users, like a smartphone.

The fifth and sixth periods are the application and discard periods, respectively [25]. In the application period, a SoC works inside a final product. In the discard period, a final product is no longer useful and end users throw it away. However, in these periods, a SoC is one part of a final product and normal end users do not have direct access to the SoC, some security threats are possible from professional end users [26]. In the following, security threats may happen in various third parties in the different period of the SoC life cycle are briefly presented.

# 2.1.2 Security Threat Models

As discussed earlier, during the SoC life cycle, there are various security threats that may happen in involved third parties. Some of these threats are shown in Fig. 2.2.b.

Security threats begin from the first period of the SoC life cycle. In this period rogue IP designers are suspicious. Two threats in this period are hardware Trojan and IP piracy [2, 3, 17, 20]. Hardware Trojans are malicious circuitry components stealthily inserted in a circuit for sabotage objectives [4, 5, 22]. IP piracy happens if untrustworthy parties buy IPs, take advantage of the access to the purchased IPs, and illegally resell them.

In the hardware design period, any disloyal employee of the design house or employing CAD tools (in either the design house or third parties that perform logical and physical syntheses) may add hardware Trojans to the SoC design [21, 27]. In addition, untrustworthy design houses are suspected of IP piracy [28].

Other security-critical third parties are untrustworthy fab, test, and packaging

foundries. Fabs can overproduce a SoC that they receive its layout from their clients for fabrication [23]. They can also make *counterfeit* SoC using two components: (1) a new package different from the original ordered package and (2) the overproduced dies from the ordered SoC layout [25]. Fabs can sell overproduced and counterfeit SoCs in black markets under the original price because they have not paid any for designing the SoC [29]. They can also clone the whole SoC layout or extract and pirate some IPs from it. Fabs can make small changes into the layout of a SoC and insert hardware Trojans [4, 22].

The security threats of untrustworthy fabs exist in test and packaging foundries with small differences [23, 25]. Test and packaging foundries have access to the fabricated dies of a SoC received from a fab for testing and packaging; thus, in order to obtain the layout of the SoC, they need to perform reverse engineering (including delayering, imaging and image processing [26]) on the layout of the fabricated dies. They can clone the obtained layout or extract and pirate its IPs [28]. In addition, they can insert hardware Trojans into the obtained layout and send it for fabrication [4, 22]. Moreover, packaging foundries can insert hardware Trojans besides to the tested dies into the ordered package. In this case, they do not need to change the layout and fabricate the new one [30].

During the application period, end users can obtain the die of a SoC by encapsulating its package [26]. Thereafter, they can insert hardware Trojans besides the obtained die into a new package. Moreover, cloning and IP piracy will be possible if they can perfume reverse engineering on the obtained die [1, 31]. Alternatively, they can remark the packages of used, aged, or recycled SoCs and make counterfeit ones [25]. Similarly, all these threats are possible in the recycle period [25, 31].

For all these security threats, detection and prevention methods have been proposed.

in the followings sections in order to make the readers familiar with some related topics to this dissertation, more details about IP protection methods against IP piracy and hardware Trojans taxonomies, Trojan models, Trojan detection and prevention methods are presented.

# 2.2 IP Protection

IP piracy threat in the different periods of the SoC life cycle forces IP designers to use IP protection methods [7-10, 12, 31-43]. Researchers classify these methods in two categories, passive and active ones, based on whether or not they can prevent IP piracy [33]. Passive methods cannot prevent IP piracy because, unlike the active ones, they do not add the lock/unlock feature to IP design [33]. A protected IP incorporating this feature would correctly operate when a correct value, as a key, is applied to. Thus, pirates need to figure out the correct key in order to reach the correct functionality of the modified IP. In the following, some of the passive and active methods with their accurate terminology are presented and shown in the figures 2.3-2.9.

# 2.2.1 Passive IP Protection Methods: Watermark, Obfuscation, and Camouflage

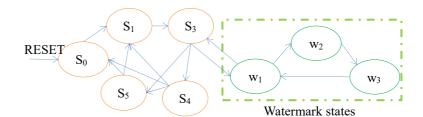

A digital *watermark* is a designer signature that is embedded into an IP in order to prove the designer's ownership [34]. Adding watermark to IP is a passive method because it cannot prevent IP piracy. Owners of such IPs can present the presence of their watermarks in pirated IPs and claim their rights. Figure 2.3 shows a watermark at RTL whose states

are added to the original states and reachable by specific input vectors. Note, if pirates can detect and then remove a watermark, its owners would not be capable to prove their ownership.

**Fig. 2.3** An embedded watermark that includes three states and is reachable in one state (S<sub>3</sub>) of the host circuit

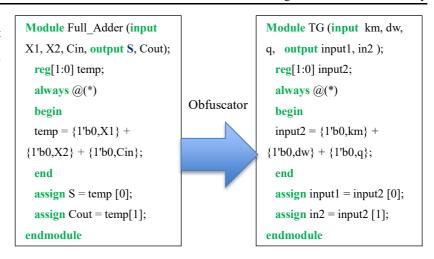

The term *obfuscation* refers to modify the design or specification of an IP without making any change in the IP functionality [11, 35]. For example, a designer can keep some redundant logic gates and don't-care inputs (which logic optimization algorithms usually remove) in a netlist, in order to make the understanding of the netlist functionality difficult. Another example is to modify an IP specification in order to reduce its readability, i.e. changing the name of variables and signals and clearing the comments in the Hardware Description Language (HDL) files of an IP specification. Figure 2.4 shows an obfuscator. As seen in the examples and figure, obfuscated IPs are piratable, and one can use them as a black box; thus, obfuscation is a passive IP protection method.

**Fig. 2.4** An obfuscator that renames inputs, outputs, variables.

Camouflage or look-alike gates protect protects ICs against chip-level reverse engineering [36]. The layout-level design of a camouflage gate has contacts in different layout layers; some of them are called *true contacts* that make the logic functions of the cell, other ones called *dummy contacts* and only make an identical layout-level appearance with other gates [36]. Dummy contacts in a camouflage gate are true ones for other gates. For example, Fig. 2.5.a and 2.5.b show a normal layout design of NAND and NOR gates, respectively. In addition, their camouflaged design is shown in Fig. 2.5.c and 2.5.d. As seen in these figures, the first two figures have a different design; however, the third and fourth figures look the same.

As mentioned, professional end users in the application period can perform reverse engineering on a SoC to obtain its layout (and then its IPs). It includes encapsulating the SoC package, delayering the SoC die, imaging each layer of the die, and then using the images to make the transistor level netlist of the SoC. If a SoC is designed using camouflage gates, the image of each layer, obtained from reverse engineering process, contains true and dummy contacts that appear the same look from the top and so make the logic functionality of the gates unknown.

# 2.2.2 IP Piracy Prevention by Active IP Protection Methods

As mentioned, active methods prevent IP piracy because they modify an IP such that it correctly functions when a correct key is applied to. According to the abstraction level of such methods, RTL or gate-level, authors have used different names for such as logic encryption [12], state/logic obfuscation [8, 9], logic locking [37], logic masking [38, 40]. Sometimes, these terms have been used interchangeably.

The use of the term *encryption* is accurate when design modifications include embedding a crypto processor into a design [11]. As shown in Fig. 2.6.a, the original inputs of a circuit under modifications are fed by the outputs of a crypto processor. Similarly, one can use a crypto-processor at the outputs of a circuit; thus, the original functionality of the circuit is encrypted, as shown in Fig. 2.6.b. Such IPs have wrong outputs if the crypto-processor gets incorrect keys. This method can protected IPs from end users in the application period; however, such IPs are piratable in untrustworthy fabs because attackers can either separate the embedded crypto-processor or write a known value, as the key, to a specific memory that is designed to keep the correct key of the crypto-processor. Figure 2.6 shows that if attackers write such a key, then they can easily use it to decrypt the functionality of the IP. The requirement hardware including a tamper-resistance memory is described in the following subsection.

Fig. 2.6 circuit encryption using a crypto processor in (a) inputs, (b) outputs.

The term *masking* refers to a prevention approach against IP piracy, which aims to obscure the original functionality of a circuit by adding some gates, state elements, and extra inputs. A masked circuit has two modes: a functional mode and a masked mode. It works like the one before masking modifications in the functional mode. In the masked mode, the masked circuit malfunctions. In order to reach the functional mode, one needs to apply a correct value(s) to the masked circuit inputs. In other words, this value acts like a key and so long as only authorized users (i.e., IP or IC owners) know this value, IP piracy prevention is achieved.

Masking modifications usually include 1) adding some fake states to the original FSM of a circuit at RTL and then 2) adding some gates to the combinational part of the circuit at the gate level. The modification at RTL is named *state obfuscation* in literature, i.e. in [7, 8]. According to the obfuscation definition, the term *state masking* specifies this modification better than that of state obfuscation. The modification at gate level has been referred in different ways such as *logic obfuscation*, *logic encryption*, *logic masking*, or *logic locking*. The authors in [11] discussed that these modifications do not have the features of encryption and obfuscation, thus, these terms cannot well indicate this modification; but, nonetheless, the term logic masking and logic locking are significant and have been used interchangeably in the literature. Hereafter, we use the term logic masking to refer to this modification. In the following state masking and logic masking are presented with more details.

# 2.2.3 IP Masking

#### 2.2.3.1 State Masking

State masking conjoins a fake FSM and the FSM of a circuit into a new one, at RTL [7-9]. Indeed, the new FSM represents a new circuit incorporating a functional and a mask (fake) mode in which the circuit functionality is the same as the original circuit and meaningless, respectively. Upon power-up, the new FSM starts from a fake start state; and one needs to know a specific inputs sequence to pass the circuit through the start state of the original FSM. An example is shown in Fig. 2.7, the circuit starts from  $S^0_M$  which belongs to the mask mode (fake FSM), and the start state of the original circuit ( $S^0_O$ ) is reachable from  $S^0_M$  by applying the key sequence  $K_1$ ,  $K_2$ ,  $K_3$ , and  $K_8$  to the circuit's inputs.

Fig 2.7 FSM structure of a masked sequential circuit; an inserted hardware Trojan (HT) will be active by a specific input  $(K_T)$  in the added FSM

It is noteworthy that if there is only one transition between the fake and the original FSM, like what is seen in Fig. 2.7, an attacker can infer the fake states; one can randomly apply many input vectors to the circuit and figure out that the circuit never goes to some states [8]. To tackle this issue, a designer must interlock the fake and original FSM such that the merged FSM has three features. First, there must be several

transitions between the fake and original FSM. Second, if the circuit goes to the original states using incorrect keys, it must generate incorrect outputs; and third, in such cases, the circuit must return to states of the fake mode [8].

In order to well interlock the fake and original FSM including the mentioned features, a designer must add some extra inputs and transitions between these two FSMs. It can be performed at RTL or gate level [41]. A designer should have accurate information about the states and transitions in the original FSM, at RTL. At gate level, these modifications are implementable using logic masking. The authors in [41] showed that the logic masking approach results in a higher level of integration in between the original and fake FSMs. Another advantage of logic masking is that there is no need to know about the original FSM and circuit behavior, thus, it can be performed by another design group.

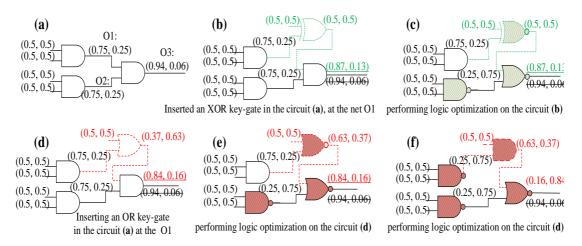

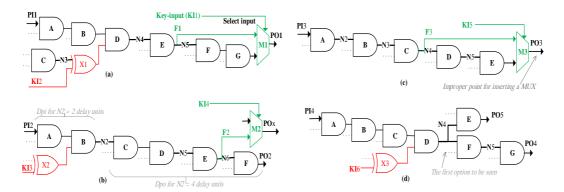

#### 2.2.3.2 Logic Masking

The majority of proposed logic masking methods modifies the combinational part of the circuit under masking at the gate level [40]. They are based on two steps. The first step, which is common in all methods, is a random selection between XOR and XNOR gate (the so-called *key-gate*). For each added key-gate, designers also add one input (the so-called *key-input*) and connect it to one input of the key-gate. The selected key-gate determines the correct key value. For XOR (XNOR) the correct key is 0 (1). The key-inputs increases the truth table size of the modified circuit and the key-gate produces wrong outputs while the key input is not derived by the correct key. A circuit including one XOR (K<sub>1</sub>) and one XNOR (K<sub>2</sub>) key-gate is shown in Fig 2.8; the correct key for key-gates K<sub>1</sub> and K<sub>2</sub> is '0' and '1', respectively.

Fig. 2.8 Mealy machine view of a masked circuit, including two key-gates and key-inputs, and a tamper-resistant memory which drives key-input

The second step is to choose a net from the combinational part of the circuit, then connect to another input of an added key-gate [40]. Instead of the selected net, the key-gate output derives the cell(s) that has (have) been derived by the net. Different algorithms can implement this selection process taking into account various objectives. Figure 2.8 shows two nets A and B selected for the logic masking modifications. In the original circuit, these nets (dashed lines) drive an input of gates  $G_1$  and  $G_2$ . The output of  $K_1$  and  $K_2$  drive these inputs, in the masked circuit.

For the first time, the authors of [42] proposed an algorithm for random net selection among circuit nets for inserting key-gates. This approach is termed random masking. Whereas this approach is easy-to-implement, the quality of logic masking is guaranteed.

In [9] the authors proposed a logic masking algorithm considering information about fan-in and fan-out cones of the circuit. Their objective is to maximize the mismatch points between the masked circuit and the original circuit when they are compared using formal methods.

In [43] the authors presented another logic masking method in which key-gates have more effect on each other. This method inserts key-gates such that attackers cannot use the circuit inputs to excite and propagate the effect of one key-gate and simultaneously prevent exciting and propagating the effect of other key-gates. Thus, this method hinders

attackers' efforts to reveal the key by feeding the circuit-specific inputs.

Using multiplexer primitive as a key-gate instead of XOR/XNOR has been proposed in [12, 40, 43, 44], as shown in Fig. 2.9. One of the two inputs of a multiplexer is randomly selected. This input defines the correct value of its key-input. Figure 2.9 shows the selected input is I<sub>1</sub> and so the correct key is '1'. Another input of the multiplexer must be connected to a net from the combinational part according to the masking algorithm. One can use the inversion of the selected net in the previous, as shown in Fig. 2.9. The multiplexer passes the correct input if its select input (the key-input) is fed by the correct value; otherwise, it passes a wrong value coming from another part of the circuit.

Fig 2.9 2-to-1 multiplexer cell as a key-gate and its truth table [43]

| $I_0$ | $I_1$ | S | $F_{M}$ |

|-------|-------|---|---------|

| $I_0$ | X     | 0 | $I_0$   |

| X     | F     | 1 | F       |

In all logic masking approaches, after key-gate insertion, designers must incrementally perform a logic optimization algorithm in order to solve key-gates in combinational parts [40]. For example, if one inverter gate, in the original circuit, is preceded by an XOR key-gate, a logic optimizer algorithm might convert them to an XNOR key-gate. As a result, the masked circuit has an XNOR key-gate which its correct key is '0', though the correct key value of an XNOR key-gate seems '1' at first glance. Thus, the reverse engineering of the masked layout cannot allow attackers to find the correct key value.

#### 2.2.3.3 Criteria for Logic Masking

Researchers have proposed different criteria to measure masking quality in a modified circuit by logic masking. First, the authors in [9] proposed to use the number of mismatch points between a masked circuit and its original one. A mismatch point makes an inversion at its place. If the inversion arrives at the circuit outputs, consequently it produces a wrong output. Obviously, the output failure might depend on input vectors. As a result, the proportion failed and succeeded input vectors can be used as a metric for the masking qualification.

The simplicity of the mismatch point number as a logic masking criteria can be misleading because it only concerns failed outputs even with one wrong bit failure. If the fab that fabricated a masked layout finds an activated IC of the masked layout in the market, they can guess the correct key by observing the masked-layout output bits (for different input vectors) and comparing it with the correct output bits of the activated IC [43]. The correct output bits, in each trial of the attack, lead the attacker to find the correct key [45].

For this reason, an effective masking approach must produce nearly equal numbers of the correct and incorrect output bits when it is driven by the wrong keys [12]. In other words, Hamming distance (HD) between the correct and incorrect output bits (when a circuit is fed by the incorrect keys) should be near to 50%. The more balance HD, the more masking is obtained [12]. In this situation, the attacker can hardly deduce the correct key by incrementally improving partial correct keys. The authors in [12] also proved mathematically that in case of having 50% HD the attacker faces the most difficult situation for the key guesses. In addition, 0% HD means the masked circuit outputs are always correct and independent of the key value. Moreover, 100% HD means the outputs

and the key-inputs are correlated, but it is not proper for masking [12]. The reason is that the wrong output bits always equal the inversion of the correct value while the key-inputs are applied by the wrong keys.

To obtain a highly balanced Hamming distance (50%), the authors of [12] have proposed to employ the concept of fault excitation/propagation analysis. If a fault in a signal can affect nearly 50% of all circuit outputs, the signal is called a high-fault-impact signal. The high-fault-impact signals are the best choices for key-gate insertion. This method has been applied to ISCAS-85 benchmark circuits and worked well but could not achieve a Hamming distance of 50% for all circuits.

#### 2.2.3.4 Hardware Requirements for IP Masking

Logic/state masking involves secure infrastructures (i.e. a tamper resistance memory to store the key, as shown in Fig. 2.8 [11]. The authors in [4] discussed even if the infrastructures are secure, the masking quality is an important security concern. For example, if the fab that fabricated a masked layout finds an activated IC of the masked layout in the market, the fab can guess the correct key by observing the masked-layout output bits (for different input vectors) and comparing it with the correct output bits of the activated IC [12]. The correct output bits, in each trial of the attack, lead the attacker to find the correct key [4]. For this reason, an effective masking approach must produce nearly equal numbers of the correct and incorrect output bits when it is driven by the wrong keys. In other words, Hamming Distance (HD) between the correct and incorrect output bits (when a circuit is fed by the incorrect keys) should be near to 50%. The more balance HD, the more masking is obtained [12]. In this situation, the attacker can hardly deduce the correct key by incrementally improving partial correct keys [12].

## 2.3 Hardware Trojan

## 2.3.1 Hardware Trojan Attributes and Taxonomies

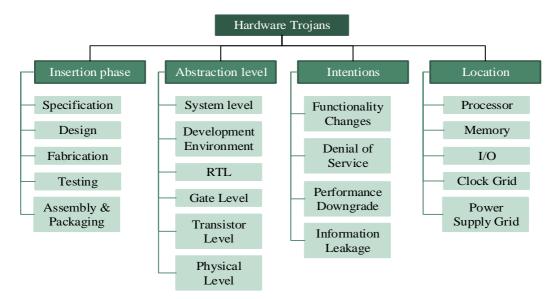

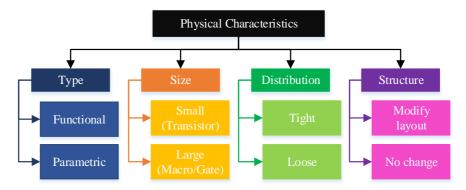

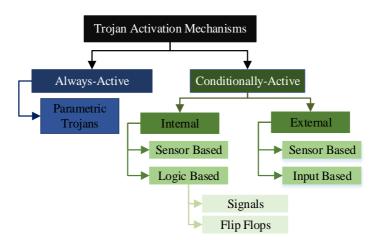

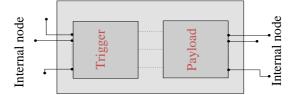

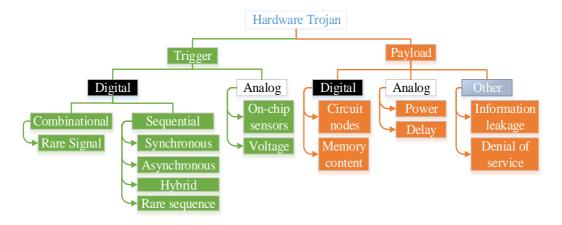

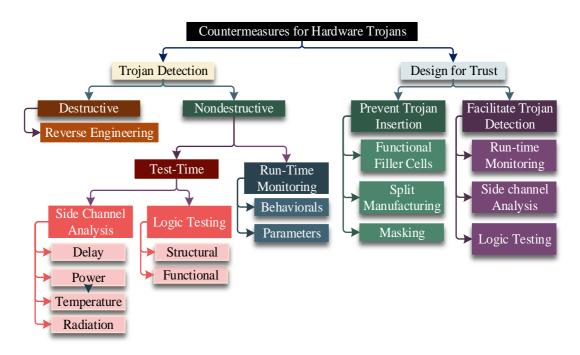

As previously mentioned, hardware Trojans are malicious alterations in circuits intended for sabotage purposes [4-5, 19, 22]. In order to model Trojan threats and counter them, awareness about Trojans attributes is vital, because Trojan attackers are smart, skillful, and able to design many different hardware Trojans for each circuit. As a result, many classifications have been proposed so that in each of them an attribute of hardware Trojans is concerned [4].