## Usuba, Optimizing Bitslicing Compiler

Darius Mercadier

### ▶ To cite this version:

Darius Mercadier. Usuba, Optimizing Bitslicing Compiler. Cryptography and Security [cs.CR]. Sorbonne Université, 2020. English. NNT: 2020SORUS180. tel-03133456v2

# HAL Id: tel-03133456 https://theses.hal.science/tel-03133456v2

Submitted on 19 Oct 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE DE DOCTORAT DE SORBONNE UNIVERSITÉ

### Spécialité

### Informatique

École doctorale Informatique, Télécommunications et Électronique (Paris)

Présentée par

### **Darius MERCADIER**

Pour obtenir le grade de

### DOCTEUR de SORBONNE UNIVERSITÉ

Sujet de la thèse :

# Usuba, Optimizing Bitslicing Compiler

soutenue le 20 novembre 2020 (hopefully)

devant le jury composé de :

M. Gilles MULLER Directeur de thèse M. Pierre-Évariste DAGAND Encadrant de thèse

M. Karthik BHARGAVAN

Mme. Sandrine BLAZY

Mme. Caroline COLLANGE

M. Xavier LEROY

M. Thomas PORNIN

Examinateur

M. Damien VERGNAUD

Examinateur

# **Abstract**

Bitslicing is a technique commonly used in cryptography to implement high-throughput parallel and constant-time symmetric primitives. However, writing, optimizing and protecting bitsliced implementations by hand are tedious tasks, requiring knowledge in cryptography, CPU microarchitectures and side-channel attacks. The resulting programs tend to be hard to maintain due to their high complexity. To overcome those issues, we propose Usuba, a high-level domain-specific language to write symmetric cryptographic primitives. Usuba allows developers to write high-level specifications of ciphers without worrying about the actual parallelization: an Usuba program is a scalar description of a cipher, from which the Usuba compiler, Usubac, automatically produces vectorized bitsliced code.

When targeting high-end Intel CPUs, the Usubac applies several domain-specific optimizations, such as interleaving and custom instruction-scheduling algorithms. We are thus able to match the throughputs of hand-tuned assembly and C implementations of several widely used ciphers.

Futhermore, in order to protect cryptographic implementations on embedded devices against side-channel attacks, we extend our compiler in two ways. First, we integrate into Usubac state-of-the-art techniques in higher-order masking to generate implementations that are provably secure against power-analysis attacks. Second, we implement a backend for SKIVA, a custom 32-bit CPU enabling the combination of countermeasures against power-based and timing-based leakage, as well as fault injection.

# Résumé

Le bitslicing est une technique utilisée pour implémenter des primitives cryptographiques efficaces et s'exécutant en temps constant. Cependant, écrire, optimiser, et sécuriser manuellement des programmes bitslicés est une tâche fastidieuse, nécessitant des connaissances en cryptographie, en microarchitecture des processeurs et en attaques par canaux cachés. Afin de remédier ces difficultés, nous proposons Usuba, un langage dédié permettant d'implémenter des algorithmes de cryptographie symétrique. Usuba permet aux développeurs d'écrire des spécifications de haut niveau sans se soucier de leur parallélisation: un programme Usuba est une description scalaire d'une primitive, partir de laquelle le compilateur Usuba, Usubac, produit automatiquement un code bitslicé et vectorisé.

Afin de produire du code efficace pour les processeurs haut de gamme, Usubac applique plusieurs optimisations spécialement conçues pour les primitives cryptographiques, telles que l'entrelacement et l'ordonnancement d'instructions. Ainsi, le code produit par notre compilateur offre des performances comparables du code assembleur ou C optimisé la main.

De plus, afin de générer des implémentations sécurisées contre des attaques par canaux cachés, nous proposons deux extensions de Usubac. Lorsque les attaques par analyse de courant sont un risque considérer, Usubac est capable de protéger les implémentations qu'il produit l'aide de masquage booléen. Si, additionellement, des attaques par injection de fautes doivent être prévenues, alors Usubac peut générer du code pour SKIVA, un processeur 32-bit offrant des instructions permettant de combiner des contre-mesures pour du code bitslicé.

# **Contents**

| 1 | Intr | oduction 1                                                            |

|---|------|-----------------------------------------------------------------------|

|   | 1.1  | Contributions                                                         |

|   | 1.2  | Background                                                            |

|   | 1.3  | Conclusion                                                            |

| 2 | Usu  | ba, Informally 4                                                      |

|   | 2.1  | Data Layout                                                           |

|   | 2.2  | Syntax & Semantics, Informally                                        |

|   | 2.3  | Types                                                                 |

|   | 2.4  | Applications                                                          |

|   | 2.5  | Conclusion                                                            |

| 3 | Usu  | ba, Greek Edition 7                                                   |

|   | 3.1  | Syntax                                                                |

|   | 3.2  | Type System                                                           |

|   | 3.3  | Monomorphization                                                      |

|   | 3.4  | Semantics                                                             |

|   | 3.5  | Usuba0                                                                |

|   | 3.6  | Translation to PseudoC                                                |

|   | 3.7  | Conclusion                                                            |

| 4 | Usu  | bac 8                                                                 |

|   | 4.1  | Frontend                                                              |

|   | 4.2  | Backend                                                               |

|   | 4.3  | Conclusion                                                            |

| 5 | Perf | formance Evaluation 12:                                               |

|   | 5.1  | Usuba vs. Reference Implementations                                   |

|   | 5.2  | Scalability                                                           |

|   | 5.3  | Polymorphic Cryptographic Implementations                             |

|   | 5.4  | Conclusion                                                            |

| 6 | Prot | ecting Against Power-based Side-channel Attacks 133                   |

|   | 6.1  | Masking                                                               |

|   | 6.2  | Tornado                                                               |

|   | 6.3  | Evaluation                                                            |

|   | 6.4  | Conclusion                                                            |

| 7 | Prot | ecting Against Fault Attacks and Power-based Side-channels Attacks 14 |

|   | 7.1  | Fault Attacks                                                         |

|   | 7.2  | SKIVA                                                                 |

|   | 73   | Evaluation 150                                                        |

|            | 7.4 Conclusion                                                        | 159            |

|------------|-----------------------------------------------------------------------|----------------|

| 8          | Conclusion 8.1 Future Work                                            | <b>161</b> 162 |

| Bi         | bliography                                                            | 173            |

| Ar         | opendix A Backend optimizations                                       | 193            |

|            |                                                                       |                |

|            |                                                                       |                |

| T          | ist of Eigenes                                                        |                |

| L          | ist of Figures                                                        |                |

|            |                                                                       |                |

| 1.1        | The RECTANGLE cipher                                                  | 17             |

| 1.2        | Skylake's pipeline                                                    | 21             |

| 1.3        |                                                                       | 23             |

| 1.4<br>1.5 |                                                                       | 25<br>26       |

| 1.6        | 0 1                                                                   | 27             |

| 1.7        |                                                                       | 28             |

| 1.8        | •                                                                     | 29             |

| 1.9        | Piccolo's round permutation                                           | 31             |

| 1.1        | 1                                                                     | 34             |

|            | 1 Data layout of vsliced RECTANGLE                                    | 36             |

|            | 2 Data layout of <i>h</i> sliced RECTANGLE                            | 37             |

|            | 3 A left-rotation using a shuffle                                     | 38<br>39       |

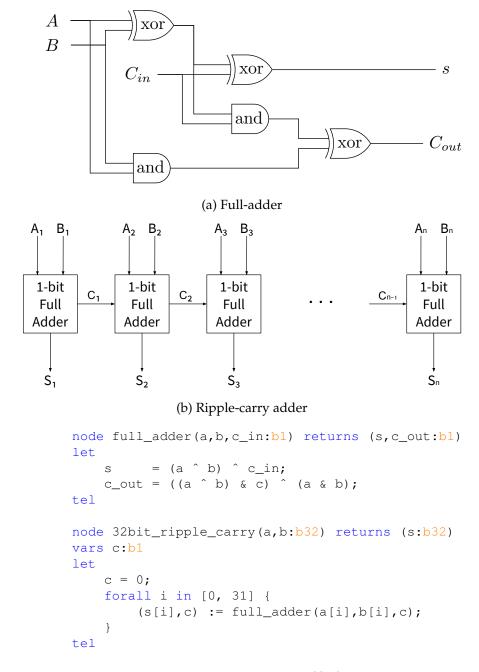

|            | 5 Circuits for some adders                                            | 41             |

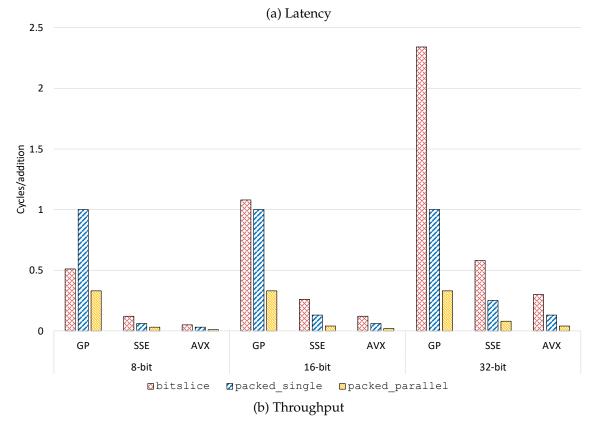

|            | 6 Comparison between bitsliced adder and native addition instructions | 42             |

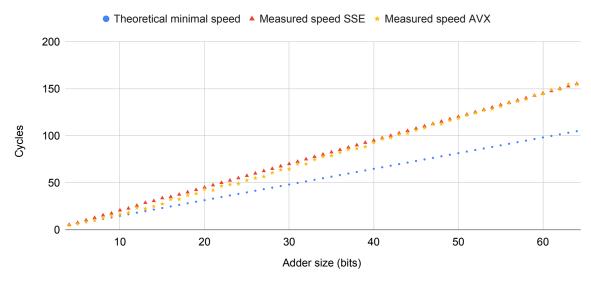

|            | 7 Scaling of bitsliced adders on SIMD                                 | 43             |

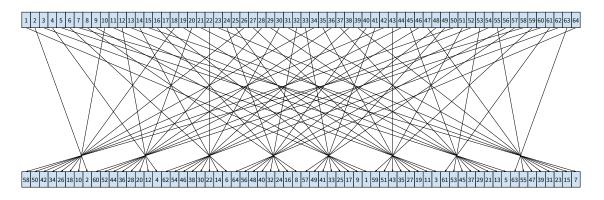

| 2.1        | DES's initial permutation                                             | 47             |

| 2.2        | 1                                                                     | 48             |

| 2.3        | RECTANGLE's sliced data layouts                                       | 49             |

| 2.4        | J 1                                                                   | 54             |

| 2.5        | 1                                                                     | 59             |

| 2.6        | 1                                                                     | 60             |

| 2.7        | 1                                                                     | 61<br>62       |

| 2.9        | •                                                                     | 63             |

| 2.1        |                                                                       | 64             |

| 2.1        | 1 Usuba implementation of SERPENT                                     | 65             |

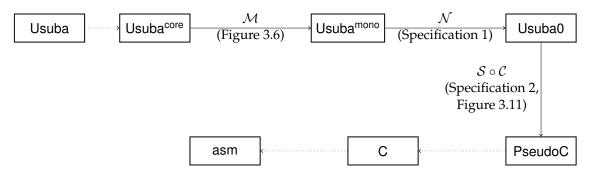

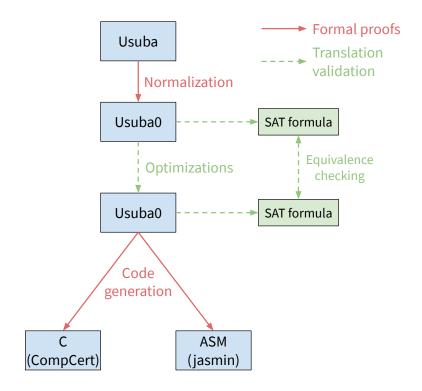

| 3.1        | Usuba's formal pipeline                                               | 71             |

| 3.2        | <b>-</b> -                                                            | 73             |

| 3.3        | B Elaboration of Usuba's syntactic sugar to Usuba <sup>core</sup>     | 74             |

| 3.4        | 7 71 0                                                                | 75<br>76       |

| 3.5        |                                                                       | 76             |

| 3.6        | Monomorphization of Usuba <sup>core</sup> programs                    | 77             |

|                                                             | Syntax of PseudoC                                                                                                                                                                                                                  | 83<br>84<br>84<br>86                              |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | Usubac's pipeline                                                                                                                                                                                                                  | 89<br>97<br>98<br>101<br>105<br>107<br>114<br>117 |

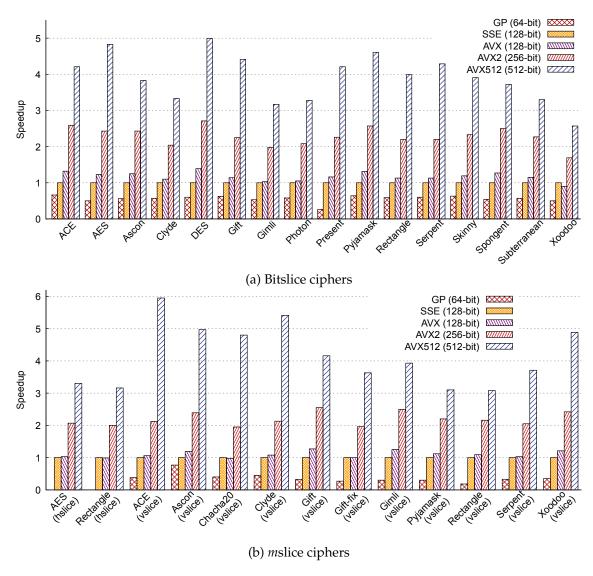

| 5.1<br>5.2                                                  | 0 1                                                                                                                                                                                                                                | 129<br>131                                        |

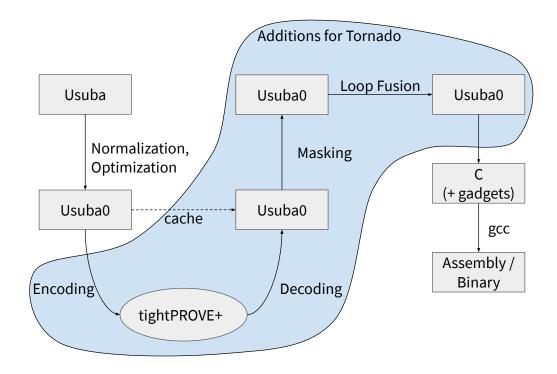

| 6.1<br>6.2<br>6.3                                           | ISW gadgets                                                                                                                                                                                                                        | 135<br>136<br>137                                 |

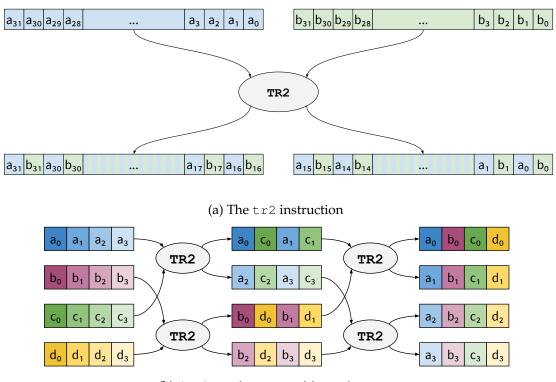

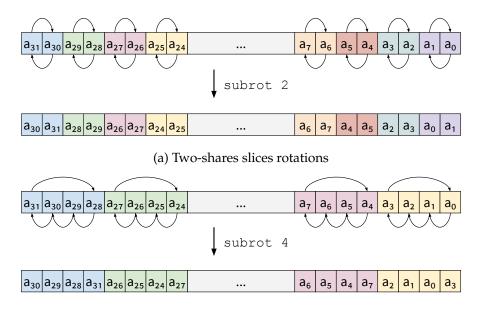

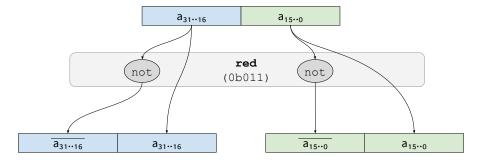

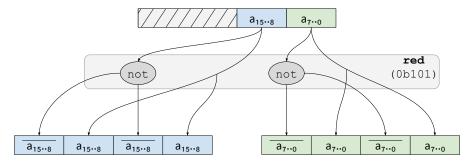

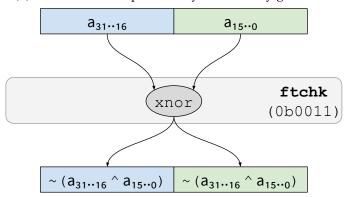

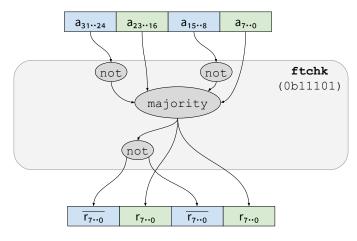

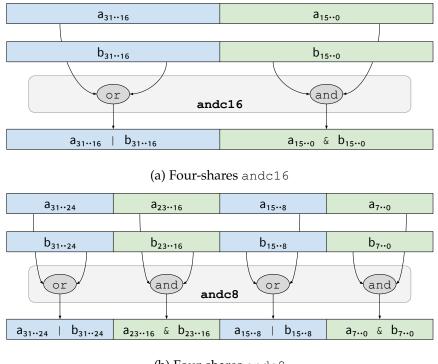

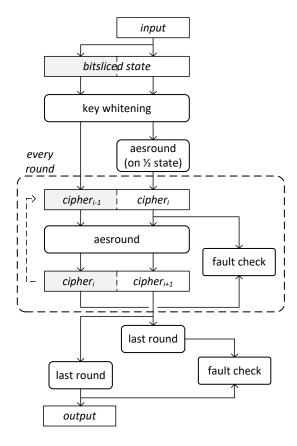

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6                      | SKIVA's tr2 instruction                                                                                                                                                                                                            | 151<br>152<br>153<br>155<br>156<br>157            |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8        | Left-rotation by 2 after packing data with _pdef_u64  CHACHA20's round  vslice CHACHA20's double round  CHACHA20 in hybrid slicing mode  AES's first round in CTR mode  Bitsliced DES scaling on Neon, AltiVec and SSE/AVX2/AVX512 | 163<br>164<br>165<br>166<br>168<br>169<br>170     |

| Li                                                          | ist of Tables                                                                                                                                                                                                                      |                                                   |

| 2.1                                                         | Operator instances                                                                                                                                                                                                                 | 55                                                |

Comparison between Usuba code & optimized reference implementations . . 125

4.1

4.2

4.3

5.1

10 List of Tables

| 5.2 | Comparison between Usuba code & unoptimized reference implementations              | 127 |

|-----|------------------------------------------------------------------------------------|-----|

| 6.1 | Overview of the primitives selected to evaluate Tornado                            | 139 |

| 6.2 | Comparison of Usuba vs. reference implementations on Intel                         | 140 |

| 6.3 | Performance of Tornado <i>m</i> sliced masked implementations                      | 142 |

| 6.4 | Throughput of Tornado bitsliced masked implementations                             | 144 |

| 6.5 | Speedups gained by manually implementing key routines in assembly                  | 145 |

| 7.1 | Exhaustive evaluation of the AES design space                                      | 158 |

| 7.2 | Experimental results of simulated instruction skips                                | 158 |

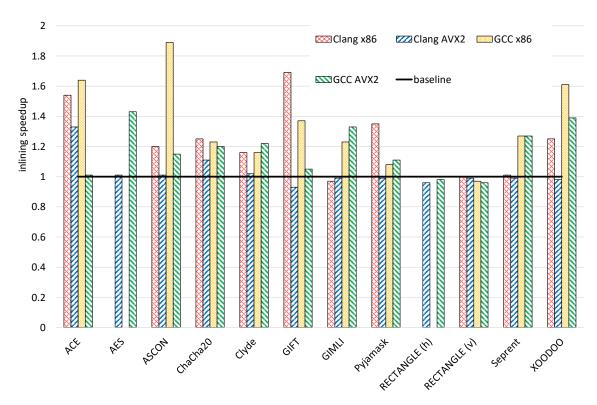

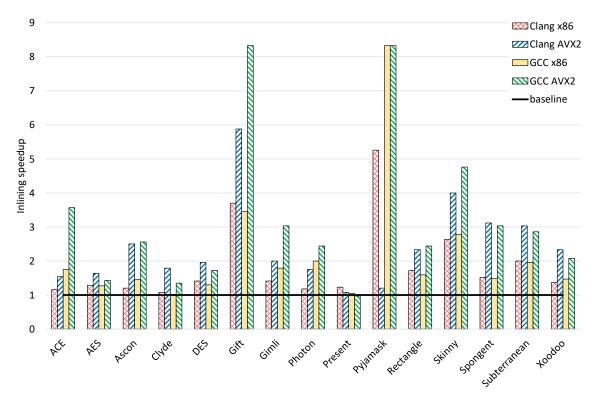

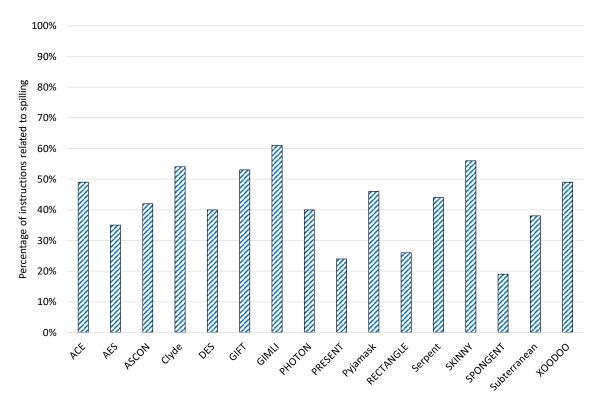

| A.1 | Impact of fully inlining msliced ciphers                                           | 193 |

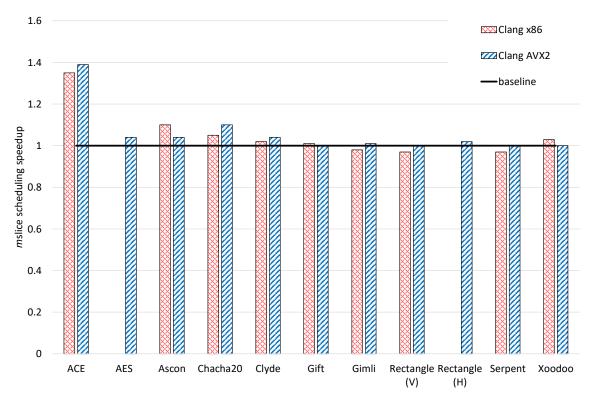

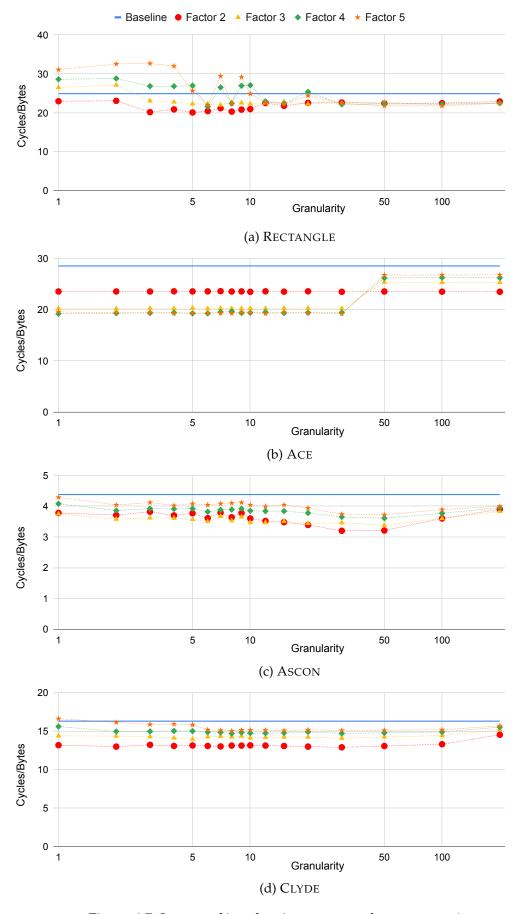

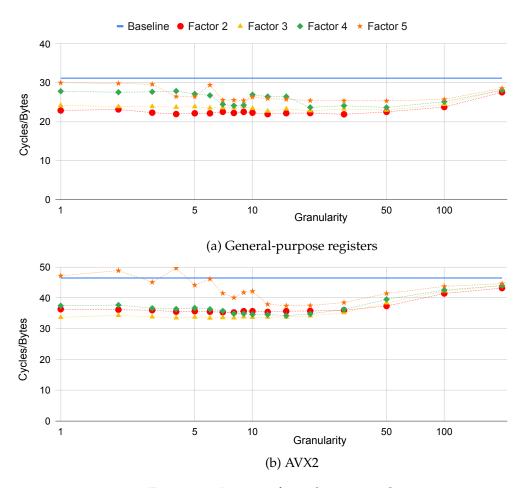

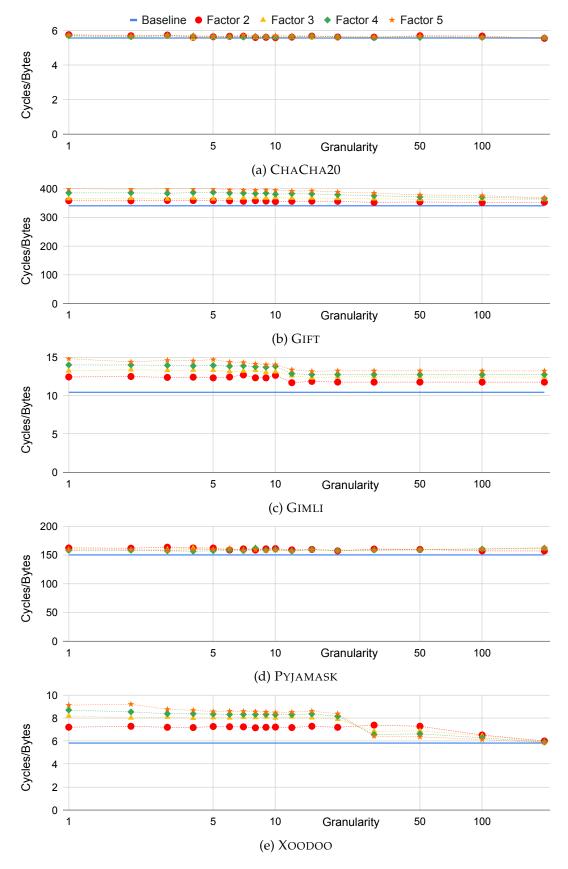

|     | Performance of the <i>m</i> slice scheduling algorithm (compiled with Clang 7.0.0) | 193 |

| A.3 | Impact of fully inlining bitsliced ciphers                                         | 194 |

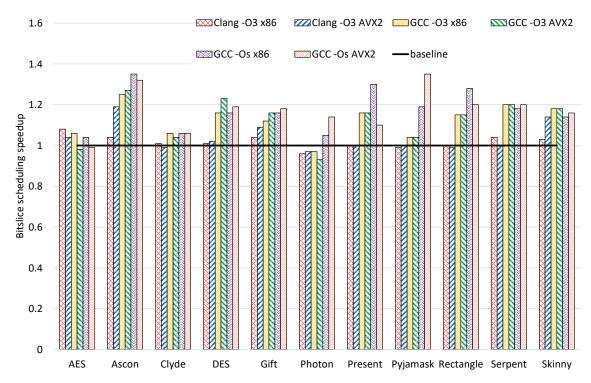

| A.4 | Performance of the bitslice scheduling algorithm                                   | 194 |

# Chapter 1

# Introduction

Cryptography, from the Ancient Greek *kryptos* "hidden" and *graphein* "to write", is the practice of securing a communication by transforming its content (the *plaintext*) into an unintelligible text (the *ciphertext*), using an algorithm called a *cipher*, which often takes as additional input a secret *key* known only from the people encrypting and decrypting the communication. The first known use of cryptography dates back to ancient Egypt, in 1900 BCE. Almost 2000 years later, Julius Caesar was notoriously using cryptography to secure his orders to his generals, using what would later be known as a Caesar cipher, which consists in replacing each letter by another one such that the  $i^{th}$  letter of the alphabet is replaced by the  $(n+i)^{th}$  one (for some fixed n between 1 and 25), wrapping around at the end of the alphabet. Throughout history, the military would continue to use cryptography to protect their communications, with the famous example of Enigma, used by Nazi Germany during World War II. Nowadays, in our increasingly digital and ever more connected world, cryptography is omnipresent, protecting sensitive data (*e.g.*, passwords, banking data) and securing data transfers over the Internet, using a multitude of ciphers.

The basic blocks of modern cryptography are called *cryptographic primitives*, and can be divided into three main categories:

- Asymmetric (or public-key) ciphers, which use two different keys for encryption and decryption: one is public and used for encryption, while the other one is private and used for decryption. Commonly used examples of asymmetric ciphers include RSA [265] and elliptic curves such as Curve25519 [59].

- Symmetric (or secret-key) ciphers, which use the same (secret) key for both encryption and decryption, and are subdivided into two categories:

- Stream ciphers, which generate a pseudo-random bit-stream and xor it with the plaintext. The most widely used stream cipher in software is CHACHA20 [61].

- Block ciphers, which only encrypt a single fixed-size block of data at a time. When the plaintext is longer than the block length, a block cipher is turned into a stream cipher using an algorithm called a *mode of operation*, which describes how to repeatedly call the block cipher until the whole plaintext is encrypted. The most used block cipher is the Advanced Encryption Standard [230] (AES), which replaces the now outdated Data Encryption Standard [229] (DES).

- Hash functions, which do not require a key, and are not reversible. They are typically used to provide data integrity or to irreversibly encrypt passwords. MD5 [264] and SHA-1 [283] are two well-known hash functions.

### 1.0.1 Secure Implementations

Cryptanalysis focuses on finding weaknesses in cryptographic primitives, either in their algorithms or in their implementations. For instance, the Caesar cipher, presented earlier, is easily broken by trying to shift all letters of the ciphertext by every possible n (between 1 and 25) until it produces a text that makes sense. Examples of more advanced attacks include related-key attack [79, 176, 54], which consists in observing similarities in the ciphertext produced by a cipher for a given plaintext with different keys, and differential cryptanalysis [73, 194], where several plaintexts are encrypted, and the attacker tries to find statistical patterns in the produced ciphertexts. A cipher is considered algorithmically secure if no practical attack exists, that is, no attack can be carried out in a reasonable amount of time or set up at a reasonable cost.

Even when cryptanalysis fails to break a cipher on an algorithmic level, its implementation might be vulnerable to *side-channel attacks*, which rely on physically monitoring a the execution of a cipher, in order to recover secret data. Side-channel attacks exploit physical vulnerabilities of the architecture a cipher is running on: executing a cipher takes time, consumes power, induces memory transfers, *etc.*, all of which could be attack vectors. A typical example is *timing attacks* [185, 95, 58], which exploit variations of the execution time of a cipher due to conditional branches depending on secret data. For instance, consider the following C code that checks if a provided password matches an expected password:

```

int check_password(char* provided, char* expected, int length) {

for (int i = 0; i < length; i++) {

if (provided[i] != expected[i]) {

return 0;

}

}

return 1;

}</pre>

```

If provided and expected start with different characters, then this function will quickly return 0. However, if provided and expected start with the same 10 characters, then this function will loop ten times (and therefore will take longer) before returning 0, thus informing an attacker monitoring the execution time of this function that they have the first characters right. This vulnerability could be fixed by decorrelating the execution time from secret inputs, making it *constant-time*:

```

int check_password(char* provided, char* expected, int length) {

int flag = 1;

for (int i = 0; i < length; i++) {

if (provided[i] != expected[i]) {

flag = 0;

}

}

return flag;

}</pre>

```

Timing attacks can also be possible in the absence of conditional execution based on secret data: the time needed to read some data from memory on a modern computer depends heavily on whether those data are in cache. An attacker could therefore design a *cache-timing attack*, *i.e.*, a timing attack based on cache accesses pattern.

By monitoring the power consumption of a cipher, an attacker can carry a *power analysis* [186, 213] to gain knowledge of secret data: power consumption can be correlated with the number of transistor switching state, which may itself depend on the value of the secret data [187].

Rather than being passive (*i.e.*, observing the execution without tampering with it), an attacker can be active and inject faults in the computation [75, 32, 20] (using, for example, ionizing radiation, electromagnetic pulses, or lasers). Consider the following C code, which returns some secret data if it is provided with the correct pin code:

```

char* get_secret_data(int pin_code) {

if (pin_code != expected_pin_code) {

return NULL;

}

return secret_data;

}

```

An attacker could inject a fault during the execution of this code in order to skip the return NULL instruction, which would cause this function to return the secret data even when provided with the wrong pin code.

Protecting code against faults requires a deep understanding of both the hardware and existing attacks. For instance, let us consider a function called <code>lookup</code>, which takes as input a 2-bit integer <code>index</code>, and returns the 2-bit integer at the corresponding index in a private array <code>table</code>:

```

int lookup(int index) {

int table[4] = { 3, 0, 1, 2 };

return table[index];

}

```

This code is vulnerable to cache-timing attacks (or rather, would be, if executed on a CPU where a cache line is 4 bytes wide), since table[index] might hit or miss in the cache depending on the value of index. To make lookup resilient to such attacks, we can transform it to remove the table and only do constant-time bitwise operations instead:

```

int lookup_ct(int index) {

// Extracting the index's 2 bits

bool x0 = (index >> 1) & 1;

bool x1 = index & 1;

// Computing the lookup through bitwise operations

bool r1 = ~x1;

bool r0 = ~(x0 ^ x1);

// Recombining the result's bits together

return (r0 << 1) | r1;

}</pre>

```

lookup\_ct is functionally equivalent to lookup. Its code does not perform any memory accesses depending on secret data, and is thus resilient to cache-timing attacks.

However, lookup\_ct is still vulnerable to power analysis attacks: computing  $\tilde{x}1$ , for instance, might consume a different amount of power depending on whether x1 is 0 or 1. To thwart power-based attacks, we can use *boolean masking*, which consists in representing each bit b of secret data by n random bits (called *shares*) such that their xor is equal to the original secret bit:  $b = b1 \hat{b}2 \hat{b}2 \hat{b}1 \hat{b}1$  bn for each secret bit b. The idea is that an attacker needs to determine the value of n bits of data in order to know the value of a single secret bit, which increases exponentially (with n) the cost of an attack. Adding this protection to lookup\_ct would produce the following code (assuming that index has already been masked and is therefore now an array of shares):

```

int* lookup_ct_masked(int index[NUMBER_OF_SHARES]) {

// Extracting the index's 2 bits

bool x0[NUMBER_OF_SHARES], x1[NUMBER_OF_SHARES];

for (int i = 0; i < NUMBER_OF_SHARES; i++) {</pre>

x0[i] = (index[i] >> 1) & 1;

x1[i] = index[i] & 1;

}

// Computing the lookup

bool r0[NUMBER_OF_SHARES], r1[NUMBER_OF_SHARES];

// r1 = ~x1

r1[0] = x1[0];

for (int i = 1; i < NUMBER_OF_SHARES; i++) {</pre>

r1[i] = x1[i];

// r0 = (x0 ^ x1)

r0[0] = (x0[0] \cdot x1[0]);

for (int i = 1; i < NUMBER_OF_SHARES; i++) {</pre>

r0[i] = x0[i] ^ x1[i];

// Recombining the result's bits together

int result[NUMBER OF SHARES];

for (int i = 0; i < NUMBER OF SHARES; i++) {</pre>

result[i] = (r0[i] << 1) | r1[i]

// (pretending that we can return local arrays in C)

return result;

```

Note that computing a masked not only requires negating one of the shares (we arbitrarily chose the first one): negating a bit b shared as b0 and b1 is indeed (~b0) ^ b1 rather than (~b0) ^ (~b1). Computing a masked xor between two masked values, on the other hand, requires xoring all of their shares: (a0, a1, ..., an) ^ (b0, b1, ..., bn) = (a0^b0, a1^b1, ..., an^bn).

Protecting this code against fault injection could be done by duplicating instructions, which would add yet another layer of complexity. However, one must be careful about the interactions between countermeasures: adding protections against faults could undo some of the protections against power analysis [256, 257, 112]. Conversely, an attacker could combine fault injection and power analysis [19, 267, 135], which needs to be taken into account when designing countermeasures [260, 125].

### 1.0.2 High-Throughput Implementations

A paramount requirement on cryptographic primitive is high throughput. Ideally, cryptography should be completely transparent from the point of view of the end users. However, the increasing complexity of CPU microarchitectures makes it hard to efficiently implement primitives. For instance, consider the following C code:

```

int a, b, c, d;

for (int i = 0; i < 2000000000; i++) {

a = a + d;

b = b + d;

c = c + d;

}</pre>

```

An equivalent x86 assembly implementation is:

```

movl $200000000, %esi

.loop:

addl %edi, %r14d

addl %edi, %ecx

addl %edi, %eax

addl %edi, %r14d

addl %edi, %r2x

addl %edi, %ecx

addl %edi, %ex

addl %edi, %ex

addl %edi, %ex

addl %edi, %eax

addl %edi, %eax

```

The main loop of this code contains 7 additions and a jump. Since modern superscalar Intel CPUs can execute 4 additions per cycles, or 3 additions and a jump, one could expect the body of the loop to execute in 2 cycles. However, depending on the alignment of the jump instruction<sup>1</sup> (jne .loop), the loop will execute in 3 cycles rather than 2.

In order to achieve the best throughputs possible, cryptographers resort to various programming trick. One such trick, popularized by Matsui [206], is called interleaving. To illustrate its principle, consider for instance the following imaginary block cipher, written in C:

```

void cipher(int plaintext, int key[2], int* ciphertext) {

int t1 = plaintext ^ key[0];

*ciphertext = t1 ^ key[1];

}

void encrypt_blocks(int* input, int key[2], int* output, int length) {

for (int i = 0; i < length; i++) {

cipher(input[i], key, &output[i]);

}

}</pre>

```

The cipher function contains two instructions. Despite the fact that modern CPUs are superscalar and can execute several instructions per cycles, the second instruction (t1  $^k$  key[1]) uses the result of the first one (t1 = plaintext  $^k$  key[0]) and thus cannot be computed in the same cycle. The execution time of encrypt\_blocks can thus be expected to be length \* 2 cycles. Matsui's trick consists in unrolling once the main loop and interleaving two independent instances of cipher:

```

void cipher_inter(int plaintext[2], int key[2], int ciphertext[2]) {

int t1_0 = plaintext[0] ^ key[0];

int t1_1 = plaintext[1] ^ key[0];

ciphertext[0] = t1_0 ^ key[1];

ciphertext[1] = t1_1 ^ key[1];

}

void encrypt_blocks_inter(int* input, int key[2], int* output, int length) {

for (int i = 0; i < length; i+=2) {

cipher_inter(&input[i], key, &output[i]);

}

}</pre>

```

This new code is functionally equivalent to the previous one. cipher\_inter computes the ciphertexts of 2 plaintexts at the same time, and the main loop of encrypt\_blocks\_inter thus performs twice less iterations. However, since the first two (resp., last two) instructions of cipher\_inter have no data dependencies between them, they can be executed

<sup>&</sup>lt;sup>1</sup>See https://stackoverflow.com/q/59883527/4990392

during the same cycle. cipher\_inter thus takes as many cycles as cycle to be executed, but computes two ciphertexts instead of one. Overall, encrypt\_blocks\_inter is thus twice faster than encrypt\_blocks.

### 1.0.3 The Case for Usuba

Implementing high-throughput cryptographic primitives, or securing primitives against side-channel attacks are complicated and tedious tasks. Both are hard to get right and tend to obfuscate the code, thus hindering code maintenance. Trying to achieve both at the same time, performance and side-channel protection, is a formidable task.

Instead, we propose Usuba [212, 211], a domain-specific programming language designed to write symmetric cryptographic primitives. Usuba is a high-level programming language, enjoying a straightforward formal semantics, allowing to easily reason on program correctness. Usuba programs are constant-time by construction, and thus protected against timing attacks. Furthermore, Usuba can automatically insert countermeasures, such as Boolean masking, to protect against power-based side-channels. Finally, Usuba compiles to high-performance C code, exploiting SIMD extensions of modern CPUs when available (SSE, AVX, AVX512 on Intel), thus performing on par with hand-tuned implementations.

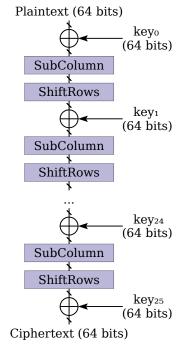

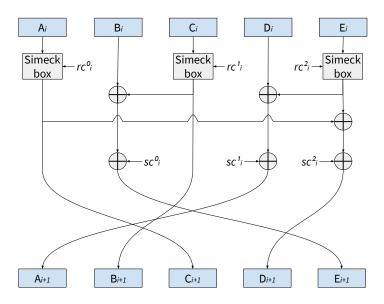

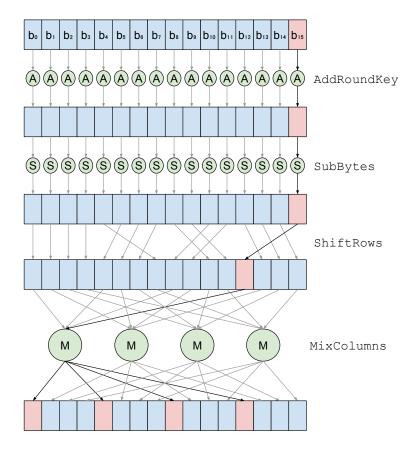

The design of Usuba is largely driven by the structure of block ciphers. A block cipher typically uses bit-permutations, bitwise operations, and sometimes arithmetic operations, and can therefore be seen as a stateless circuit. These basic operations are combined to form a *round*, and a block cipher is defined as *n* (identical) rounds, each of them taking the output of the previous round as well as a key as input. For instance, the RECTANGLE [309] block cipher takes as input a 64-bit plaintext and 25 64-bit keys, and produces the ciphertext through 24 rounds, each doing a xor, and calling two auxiliary functions: SubColumn (a lookup table), and ShiftRows (a permutation). Figure 1.1a represents RECTANGLE using a circuit.

Usuba aims at providing a way to write an implementation of a cipher which is as close to the specification (*i.e.*, the circuit) as possible. As such, RECTANGLE can be straightforwardly written in Usuba in just a few lines of code, as shown in Figure 1.1b. The code should be self-explanatory: the main function Rectangle takes as input the plaintext as a tuple of 4 16-bit elements, and the key as a 2D vector, and computes 25 rounds, each calling the functions ShiftRows, described as 3 left-rotations, and SubColumn, which computes a lookup in a table. This code is simple, and as close to the specification as can be. Yet, it compiles to a C code which is about 20% faster than the reference implementation (Section 5.1), while being much simpler and more portable: whereas the reference implementation explicitly uses SSE and AVX SIMD extensions, Usuba is not bound to a specific SIMD extension.

One of the other main benefits of Usuba is that the code it generates is constant-time by construction. To write constant-time code with traditional languages (e.g., C) is to fight an uphill battle against compilers [27], which may silently rewrite one's carefully crafted program into one vulnerable to timing attacks, and against the underlying architecture itself [216], whose undocumented, proprietary micro-architectural features may leak secrets through timing or otherwise. For instance, the assembly generated by Clang 9.0 for the following C implementation of a multiplexer:

```

bool mux(bool x, bool y, bool z) {

return (x & y) | (~x & z);

}

```

uses a cmove instruction, which is not specified to be constant-time [259]. Likewise, some integer multiplication instructions are known not to be constant-time, causing library

(a) RECTANGLE as a circuit

```

table SubColumn (in:v4) returns (out:v4) {

6 , 5, 12, 10, 1, 14, 7, 9,

11, 0, 3 , 13, 8, 15, 4, 2

node ShiftRows (input:u16[4]) returns (out:u16[4])

let

out[0] = input[0];

out[1] = input[1] <<< 1;

out[2] = input[2] <<< 12;

out[3] = input[3] <<< 13

tel

node Rectangle (plain:u16[4], key:u16[26][4])

returns (cipher:u16[4])

vars state : u16[4]

let

state = plain;

forall i in [0,24] {

state := ShiftRows(SubColumn(state ^ key[i]))

cipher = state ^ key[25]

tel

```

(b) RECTANGLE written in Usuba

Figure 1.1: The RECTANGLE cipher

developers to write their own software-level constant-time implementations of multiplication [247]. The issue is so far-reaching that tools traditionally applied to hardware evaluation are now used to analyze software implementations [259], treating the program and its execution environment as a single black-box and measuring whether its execution time is constant with a high enough probability. Most modern programming languages designed for cryptography have built-in mechanism to prevent non-constant-time operations. For instance, HACL\* [310] has the notion of *secure integers* that cannot be branched on, and forbids the use of non-constant-time operations like division or modulo. FaCT [99], on the other hand, takes the stance that HACL\* is too low-level, and that constant-timeness should be seen as a compilation problem: it provides high-level abstractions that are compiled down to constant-time idioms. Adopting yet another high-level approach, Usuba enforces constant-time by adopting (in a transparent manner from the developer's perspective) a programming model called *bitslicing*.

Bitslicing was first introduced by Biham [72] as an implementation trick to speed up software implementations of DES. Intuitively, the idea of bitslicing is to represent a *n*-bit value as 1 bit in n registers. In the case of 64-bit registers, each register therefore has 63-bit empty bit remaining, which can be filled in the same fashion by other independent values. To manipulate such data, the cipher must be reduced to bitwise logical operations (and, or, xor, not). On a 64-bit machine, a bitwise operation then effectively works like 64 parallel 1-bit operations. Throughput is thus achieved by parallelism: 64 instances of the cipher are computed in parallel. Consequently, bitslicing is especially good at exploiting vector extensions of modern CPUs, which offer large registers (e.g., 128-bit SSE, 256-bit AVX and 512-bit AVX-512 on Intel). Bitsliced implementations are constanttime by design: no data-dependent conditionals nor memory accesses are made (or, in fact, possible at all). Many record-breaking software implementations of block ciphers exploit this technique [189, 207, 174, 33], and modern ciphers are now designed from the ground up with bitslicing in mind [78, 309]. However, bitslicing implies an increase in code complexity, making it hard to write efficient bitsliced code by hand, as can be demonstrated by the following few lines of C code that are part of a DES implementation written by Matthew Kwan [192]:

```

s1 (r31 ^ k[47], r0 ^ k[11], r1 ^ k[26], r2 ^ k[3], r3 ^ k[13], r4 ^ k[41], &18, &116, &122, &130); s2 (r3 ^ k[27], r4 ^ k[6], r5 ^ k[54], r6 ^ k[48], r7 ^ k[39], r8 ^ k[19], &112, &127, &11, &117); s3 (r7 ^ k[53], r8 ^ k[25], r9 ^ k[33], r10 ^ k[34], r11 ^ k[17], r12 ^ k[5], &123, &115, &129, &15); s4 (r11 ^ k[4], r12 ^ k[55], r13 ^ k[24], r14 ^ k[32], r15 ^ k[40], r16 ^ k[20], &125, &119, &19, &10);

```

The full code goes on like this for almost 300 lines, while the Usuba equivalent is just a few lines of code, very similar to the RECTANGLE code shown in Figure 1.1b. The simplicity offered by Usuba does not come at any performance cost: both Kwan's and Usuba's implementations exhibit similar throughput.

The bitslicing model can sometimes be too restrictive as it forbids the use of arithmetic operations, and may fail to deliver optimal throughputs as it consumes a lot of registers. To overcome these issues, and drawing inspiration from Käsper & Schwabe's byte-sliced AES [174], we propose a generalization of bitslicing that we dub *m*slicing. *m*slicing preserves the constant-time property of bitslicing, while using less registers, and allowing to use SIMD packed arithmetic instructions (*e.g.*, vpaddb, vmuldp), as well as vector permutations (*e.g.*, vpshufb).

19

### 1.1 Contributions

We made the following contributions in this thesis:

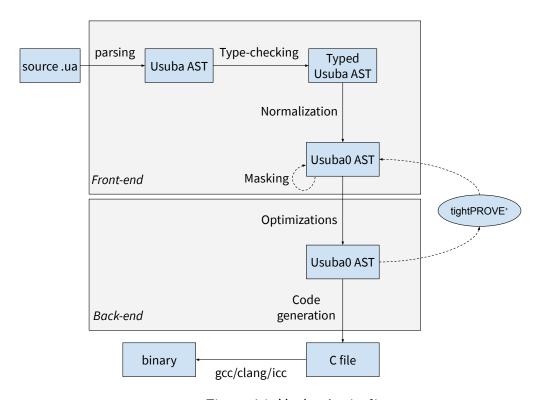

- We designed Usuba, a domain-specific language for cryptography (Chapter 2). Usuba enables a high-level description of symmetric ciphers by providing abstractions tailored for cryptography, while generating high-throughput code thanks to its slicing model. We demonstrated the expressiveness and versatility of Usuba on 17 ciphers (Section 2.4). Furthermore, we formalized Usuba's semantics (Chapter 3), thus enabling formal reasoning on the language, and paving the way towards a verified compiler for Usuba.

- We developed Usubac, an optimizing compiler translating Usuba to C (Chapter 4). It involves a combination of folklore techniques—such as inlining and unrolling—tailored to the unique problems posed by sliced programs (Section 4.2) and introduces new techniques—such as interleaving (Section 4.2.6) and sliced scheduling (Section 4.2.5)—made possible by our programming model. We showed that on high-end Intel CPUs, Usuba exhibits similar throughputs as hand-tuned implementations (Chapter 5).

- We integrated side-channel countermeasures in Usuba, in order to generate sidechannel resilient code for embedded devices. In particular, by leveraging recent progress in provable security [53], we are able to generate implementations that are provably secure against *probing* side-channel attacks (Chapter 6). We also implemented a backend for SKIVA, thus producing code resilient to both power-based side-channel attacks and fault injections (Chapter 7).

### 1.2 Background

Usuba has two main targets: high-end CPUs, for which it generates optimized code, and embedded CPUs, for which it generates side-channel resilient code. Several optimizations are specifically tailored for Intel superscalar CPUs (Section 4.2), and our main performance evaluation compares Usuba-generated ciphers against reference implementation on Intel CPUs (Chapter 5). In Section 1.2.1, we introduce the micro-architectural notions necessary to understand this platform, as well as our benchmarking methodology.

Section 1.2.2 and 1.2.3 present bitslicing and *m*slicing as data formats and their impact on code expressiveness, performance, and compilation.

Finally, Section 1.2.5 compares the throughputs of performing a bitsliced and a *m*sliced addition. We provide a detailed analysis of the performance of both implementations, which can be seen as a concrete example of the notions introduced in Section 1.2.1.

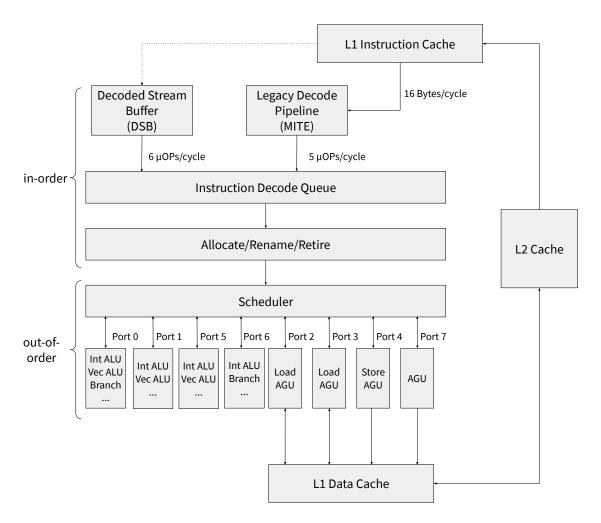

### 1.2.1 Skylake CPU

At the time of writing, the most recent Intel CPUs (Skylake, Kaby Lake, Coffee Lake) are derived from the Skylake microarchitecture. The Skylake CPU (Figure 1.2) is a deeply pipelined microarchitecture (*i.e.*, it can contain many instructions at the same time, all going through different execution phases). This pipeline consists of 2 main phases: the *frontend* retrieves and decodes instructions in-order from the L1 instruction cache, while the *out-of-order execution engine* actually executes the instructions. The instructions are finally removed in-order from the pipeline by the retiring unit.

Note that this is a simplified view of the Skylake microarchitecture, whose purpose is only to explain what matters to us, and to show which parts we will be focusing on when designing our optimizations, and when analyzing the performance of our programs.

### **Frontend**

The L1 instruction cache contains x86 instructions represented as a sequence of bytes. Those instructions are decoded by the Legacy Decode Pipeline (MITE). The MITE operates in the following way:

- up to 16 bytes of instructions are fetched from the L1 instruction cache, and predecoded into macro-ops.

- up to 6 macro-ops per cycle are delivered to the instruction queue (IQ), which performs macro-fusion: some common patterns are identified and optimized by fusing macro-ops together. For instance, an increment followed by a conditional jump, often found at the end of a loop, may fuse together in a single macro-op.

- the IQ delivers up to 5 macro-ops per cycle to the decoders. The decoders convert each macro-ops into one or several  $\mu$ ops, which are then sent to the Instruction Decode Queue (IDQ).

The MITE is limited by the fetcher to 16 bytes of instructions per cycle. This translates to 4 or 5  $\mu$ ops per cycle on programs manipulating integer registers, which is enough to maximize the bandwidth of the pre-decoder and decoders. However, SSE, AVX and AVX-512 instructions are often larger. For instance, an addition between two registers is encoded on 2 bytes for integer registers, 4 bytes on SSE and AVX, and 6 bytes on AVX-512. Therefore, on programs using SIMD extensions, the MITE tends to be limited by the fetcher. In order to overcome this, the Decoded Stream Buffer (DSB), a  $\mu$ op cache, can be used to bypass the whole MITE when dealing with sequences of instructions that have

Figure 1.2: Skylake's pipeline

already been decoded (for instance, in a tight loop). The DSB delivers up to 6  $\mu$ ops per cycles, directly to the IDQ.

### **Execution Engine**

The execution engine can be divided in 3 phases. The Allocate/Rename phase retrieves  $\mu$ ops from the IDQ and sends them to the Scheduler, which dispatches  $\mu$ ops to the execution core. Once  $\mu$ ops are executed, they are retired: all resources allocated to them are freed, and the  $\mu$ ops are effectively removed from the pipeline.

While assembly code can only manipulate 16 general purpose (GP) registers (e.g., rax, rdx) and 16 SIMD registers (e.g., xmm0, xmm1), the CPU has hundreds of registers available. The renamer takes care of renaming architectural registers (i.e., registers manipulated by the assembly) into micro-architectural registers (the internal registers of the CPU, also known as physical registers). The renamer also determines the possible execution ports for each instruction, and allocates any additional resources they may need (e.g., buffers for load and store instructions).

The execution core consists of several execution units, each able to execute some specific type of  $\mu$ ops, accessed through 8 ports. For instance:

- Arithmetic and bitwise instructions can execute on ports 0, 1 and 5 (and port 6 for general-purpose registers).

- Branches can execute on ports 0 and 6.

- Memory loads can execute on ports 2 and 3.

- Memory reads can execute on port 4.

The scheduler dispatches  $\mu$ ops out-of-order to the execution units of the execution core. When an instruction could be executed on several execution units, the scheduler chooses one (the algorithm making this choice is not specified).

The instructions are then removed from the pipeline in-order by the retiring unit. All resources allocated for them are freed, faults and exceptions are handled at that stage.

### **SIMD**

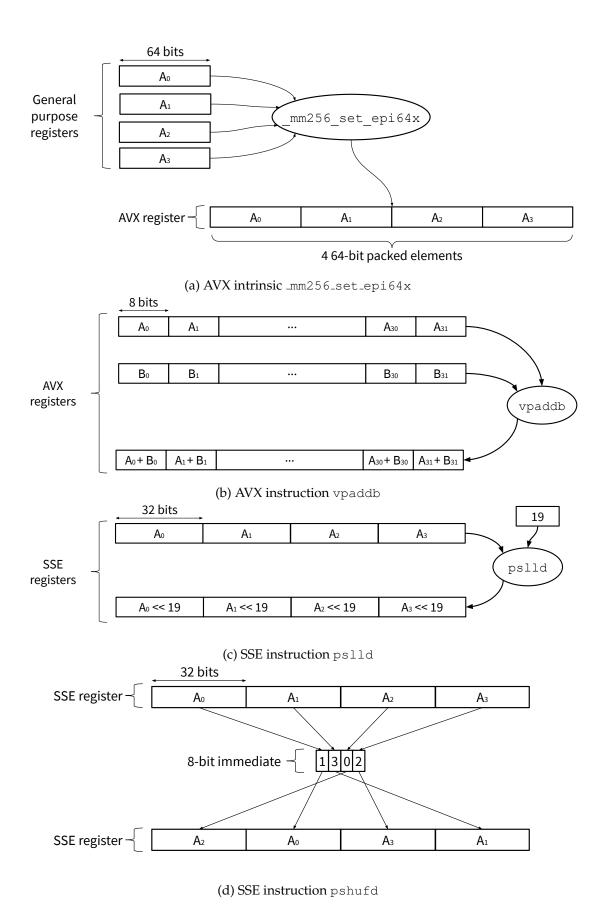

SIMD (*single instruction, multiple data*) are CPU extensions that offer registers and instructions to compute the same operations on multiple data at once. Intel provides 4 main classes of SIMD extensions: MMX with 64-bit registers, SSE with 128-bit registers, AVX with 256-bit registers and AVX-512 with 512-bit registers. For the purposes of bitslicing, MMX offers little to no benefits compared to general purpose 64-bit registers, and we shall ignore them.

SSE, AVX and AVX-512 provide instructions to pack several 8-bit, 16-bit, 32-bit and 64-bit words inside a single register of 128 bits, 256 bits or 512 bits, thus producing a *vector*. Figure 1.3a illustrates the function \_mm256\_set\_epi64x, which packs 4 64-bit integers in a 256-bit AVX register. The term *packed elements* is used to refer to the individual 64-bit integers in the AVX registers.

SIMD extensions then provide *packed instructions* to compute over vectors, which we divide in two categories. *vertical m*-bit instructions perform the same instruction over multiple packed elements in parallel. If we visually represent SIMD registers as aggregations of *m*-bit elements vertically stacked, vertical operations consist in element-wise computations along this vertical direction. For instance, the instruction vpaddb (Figure 1.3b) takes two 256-bit AVX registers as parameters, each containing 32 8-bit words, and computes 32 additions between them in a single CPU cycle. Similarly, the instruction pslld (Figure 1.3c) takes a 128-bit SSE register containing 4 32-bit words, and an 8-bit integer, and computes 4 left shifts in a single CPU cycle.

On the other hand, *horizontal* SIMD operations perform element-wise computations within a single register, *i.e.*, along the horizontal direction. For instance, the instruction pshufd (Figure 1.3d) permutes the 4 32-bit packed elements of a SSE register (according to a pattern specified by an 8-bit immediate).

Intel provides *intrinsic* functions that allow **C** code to use SIMD instructions. For instance, the \_mm256\_add\_epi8 intrinsic is compile into a vpaddb assembly instruction, and \_mm\_sll\_epi32 is compiled into a pslld assembly instruction.

One straightforward application of SIMD extensions is to *vectorize* programs, that is, to transform a program manipulating scalars into a functionally equivalent but faster program manipulating vectors. For instance, consider the following C function, which computes 512 32-bit additions between two arrays:

```

void add_512_integers(int* a, int* b, int* c) {

for (int i = 0; i < 512; i++) {

c[i] = a[i] + b[i];

}

}</pre>

```

Figure 1.3: Some SIMD instructions and intrinsics

This function can be transformed into the following equivalent one:

```

void add_512_integers_vec(__m256i* a, __m256i* b, __m256i* c) {

for (int i = 0; i < 64; i++) {

c[i] = _mm256_add_epi32(a[i],b[i]);

}

}</pre>

```

The second one (add\_512\_integers\_vec) manipulates 256-bit AVX registers (of type \_\_m256i), and uses the \_mm256\_add\_epi32 intrinsic to perform 8 32-bit additions in parallel. The second one should divide by 8 the number of cycles required to perform 512 additions. Most C compilers (*e.g.*, GCC, Clang, ICC) automatically try to vectorize loops to improve performance. Some code cannot be vectorized however. For instance, consider the following snippet:

```

void all_fibonacci(int* res, int n) {

res[0] = res[1] = 1;

for (int i = 2; i < n; i++) {

res[i] = res[i-1] + res[i-2];

}

}</pre>

```

Since each iteration depends on the number calculated at the previous iteration, this code cannot be computed in parallel. Similarly, table lookups cannot be vectorized. Consider, for instance:

```

void n_lookups(int* table, int* indices, int* res, int n) {

for (int i = 0; i < n; i++) {

res[i] = table[indices[i]];

}

}</pre>

```

Vectorizing this code would require a SIMD instruction to perform multiple memory lookups in parallel, but no such instruction exists.

As shown in Figure 1.2, ports 0, 1, 5 and 6 of the CPU can compute bitwise and arithmetic instructions, but only ports 0, 1 and 5 can compute SIMD instructions ("Vec ALU"). This limits the potential speedup offered by SIMD extensions:  $add_512_integers_vec should execute in <math>64/3 = 22$  cycles, whereas  $add_512_integers should execute in <math>512/4 = 128$  cycles, or 5.8 times more. AVX-512 restrict CPU usage even further: only 2 bitwise/arithmetic AVX-512 instructions can be executed per cycle.

New generations of SIMD offer more than simply twice larger registers. For instance, one of the additions of AVX extensions is 3-operand non-destructive instructions. SSE bitwise and arithmetic instructions take two registers as arguments, and override one of them with the result (*i.e.*, a SSE xor will compute x  $^{^\circ}$  y). On the other hand, AVX instructions set a third register with their output (*e.g.*, an AVX xor will compute x = y  $^\circ$  z). Another example is AVX512 extensions, which provide 32 registers, whereas AVX and SSE extensions only provide 16.

**Generations of SIMD.** Several generations of SSE extensions have been released by Intel (SSE, SSE2, SSSE3, SSE4.1, SSE4.2), each introducing new instructions. Similarly, the AVX2 extensions improve upon AVX by providing many useful operations, including 8/16/32-bit additions and shifts. Whenever we mention SSE (resp., AVX) without specifying which version, we refer to SSE4.2 (resp., AVX2).

### Micro-Benchmarks

Intel gives access to a Time Stamp Counter (TSC) through the rdtscp instruction. This counter is incremented at a fixed frequency, regardless of the frequency of the CPU core clock (and, in particular, is not affected by Turbo Boost, which increases the frequency of the core clock). On both Intel CPUs we used in this thesis (i5-6500 and Xeon W-2155), the TSC frequency is very close to the core frequency: on the i5-6500, the TSC frequency is 3192MHz and the core frequency is 3200Mhz, and on the W-2155, the TSC frequency is 3299MHz and the core frequency is 3300MHz. We can thus use this counter to approximate the number of clock cycles taken by a given code to execute. In order to keep the TSC frequency and core frequency correlated, we disabled Turbo Boost.

Figure 1.4a provides the C benchmark code we used throughout this thesis to benchmark some arbitrary function run\_bench. Some components of the CPU go through a warm-up phase during which they are not operating at peak efficiency. For instance, according to Fog [138], parts of the SIMD execution units are turned off when unused. As a result, the first instruction using AVX registers takes between 150 and 200 cycles to execute, and the following instructions using AVX registers are 4.5 times slower than normal for about 56.000 clock cycles. 2.7 million clock cycles after the last AVX instruction, parts of the SIMD execution units will be turned back off. In order to prevent those factors from impacting our benchmarks, we include a warm-up phase, running the target code without recording its run time. In Figure 1.4a, the warm-up loop performs 100.000 iterations, which ensures that SIMD extensions are fully powered.

```

1

extern void run_bench();

2

3

int main() {

4

// Warm-up

5

for (int i = 0; i < 100000; i++) {</pre>

6

run_bench();

7

8

9

// Actual benchmark

10

unsigned int unused;

11

uint64_t timer = __rdtscp(&unused);

for (int i = 0; i < 1000000; i++) {</pre>

12

13

run_bench();

14

15

timer = __rdtscp(&unused) - timer;

16

17

// Outputting result

18

printf("%.2f_cycles/iteration\n", timer/1000000);

19

(a) Core of our generic benchmark code (C)

for my $i (0 .. 29) {

$times_a[$i] = system "./bench_a";

$times_b[$i] = system "./bench_b";

printf "bench_a:_%.2f__//_bench_b:_%.2f\n",

average(@times_a), average(@times_b);

```

(b) Wrapper for our benchmarks (Perl)

Figure 1.4: Our benchmark code

Figure 1.5: Bitslicing example with 3-bit data and 4-bit registers

While the code from Figure 1.4a provides a fairly accurate cycle count for a given function, other programs running on the same machine may impact its run-time. In order to alleviate this issue, we repeated each measurement 30 times, and took the average of the measurements (Figure 1.4b).

To compare performance results, we use the Wilcoxon rank-sum test [300] (also called Mann-Whitney U test), which assesses whether two distributions are significantly distinct. Every speedup and slowdown mentioned in this thesis are thus statistically significant. For instance, Table A.4 (Page 194) shows some  $\times 1.01$  speedups and  $\times 0.99$  slowdowns, all of which are significant.

Intel provides hundreds of counters to monitor the execution of a program. For instance, the number of read and writes to the caches, the number of cache misses and hits, the number of cycles where 1, 2, 3 or 4  $\mu$ ops were executed, the number of cycles where the frontend did not dispatch  $\mu$ ops, the number of instructions executed each cycles (IPC). To collect such counters, we use the perf utility [4], and vtune software [164].

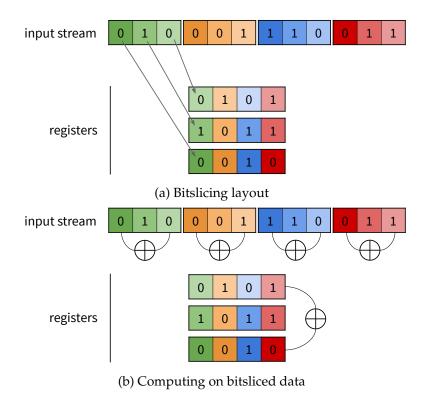

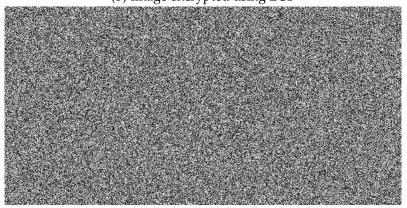

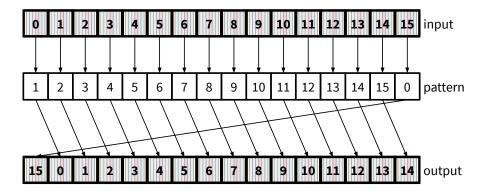

### 1.2.2 Bitslicing

The general idea of bitslicing is to transpose m n-bit data into n m-bit registers (or variables). Then, standard m-bit bitwise operations of the CPU can be used and each acts as m parallel operation. Therefore, if a cipher can be expressed as a combination of bitwise operations, it can be ran m times in parallel using bitslicing. A bitsliced program can thus be seen as a combinational circuit (i.e., a composition of logical operations) implemented in software.

Figure 1.5a illustrates bitslicing on 3-bit inputs, using 4-bit registers (for simplicity). 3 registers are required to bitslice 3-bit data: the first bit of each input goes into the first register; the second bit into the second register and the third bit into the third register. Once the data has this representation, doing a xor (or any other bitwise operation) between two registers actually computes 4 independent xors (Figure 1.5b).

1.2. BACKGROUND 27

### Scaling

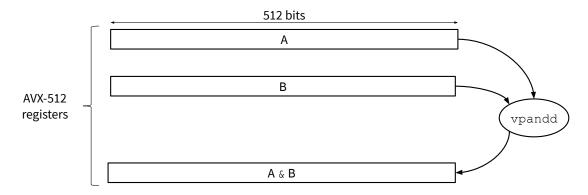

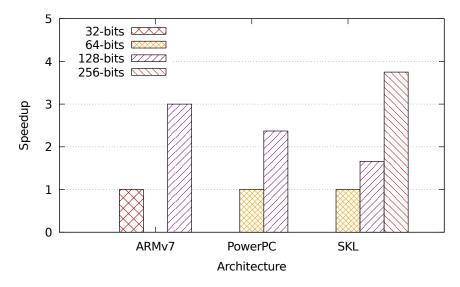

SIMD instructions, presented in Section 1.2.1, offer large registers (up to 512 bits) and operations to perform data-parallel computation on those registers. Bitslicing being parallel by construction, it is always possible to make use of SIMD instructions sets to increase the throughput of a bitsliced program. As for general-purpose registers, a bitsliced program will only require SIMD bitwise instructions, such as vpandd that computes 512 bitwise 1-bit ands in parallel (Figure 1.6).

Figure 1.6: The AVX-512 vpandd instruction

Executing a bitsliced program on 512-bit registers will compute the same circuit on 512 independent data in parallel, thus dividing by 8 the number of cycles compared to 64-bit registers. On the other hand, the overall time needed to execute the circuit, and thus the latency, remains constant no matter the registers used: encrypting 64 inputs in parallel on 64-bit registers, or encrypting 512 inputs in parallel on 512-bit registers will take roughly the same amount of time.

Finally, to make full use of SIMD extensions, hundreds of inputs must be available to be encrypted in parallel. For instance, on AES, which encrypts a 128-bit plaintext, 8 KB of data are required in order to fill 512-bit AVX-512 registers.

### **Modes of Operation**

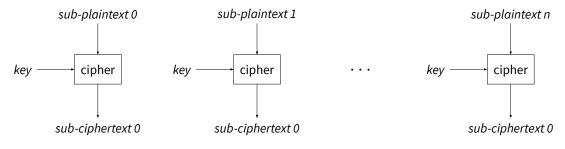

A block cipher can only encrypt a fixed amount of data (a block). The size of a block is generally between 64 and 128 bits (e.g., 64 bits for DES and 128 bits for AES). When the plaintext is longer than the block size, the cipher must be repeatedly called until the whole plaintext is encrypted, using an algorithm called a *mode of operation*. The simplest mode of operation is Electronic Codebook (ECB, Figure 1.7a). It consists in dividing the plaintext into sub-plaintexts (of the size of a block), encrypting them separately, and concatenating the resulting sub-ciphertext to produce the full ciphertext.

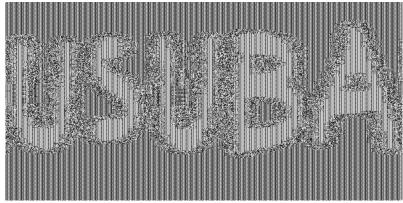

This mode of operation is considered insecure because identical blocks will be encrypted into the same ciphertext. This can be exploited by an attacker to gain knowledge about the plaintext. Figure 1.8 illustrates the weaknesses of ECB: the initial image (Figure 1.8a) encrypted using AES in ECB mode results in Figure 1.8b, which clearly reveals information about the initial image.

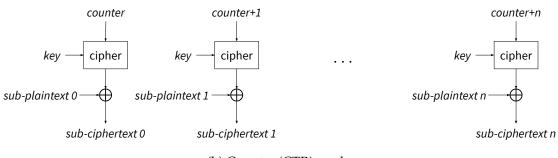

Counter mode (CTR) is a more secure parallel mode that works by encrypting a counter rather than the sub-plaintexts directly (Figure 1.7b). It then xors the encrypted counter with the sub-plaintext. Encrypting the image from Figure 1.8a with this mode produces a seemingly random image (Figure 1.8c). Incrementing the counter can be done in parallel using SIMD instructions:

(a) Electronic codebook (ECB) mode

(b) Counter (CTR) mode

(c) Cipher block chaining (CBC) mode

| Mode | Encryption | Decryption | Secure |

|------|------------|------------|--------|

| ECB  | parallel   | parallel   | Х      |

| CTR  | parallel   | parallel   | ✓      |

| CBC  | sequential | parallel   | ✓      |

(d) Qualitative comparison of ECB, CBC and CTR

Figure 1.7: Some common modes of operation

1.2. BACKGROUND 29

# USUBA

(a) Source image

(b) Image encrypted using ECB

(c) Image encrypted using CTR

The sources of this experiment are available at:

https://github.com/DadaIsCrazy/usuba/tree/master/experimentations/ecb\_vs\_ctr

Figure 1.8: ECB vs. CTR

```

// Load 4 times the initial counter in a 128-bit SSE register

__m128i counters = _mm_set1_epi32(counter);

// Load a SSE register with integers from 1 to 4

__m128i increments = _mm_set_epi32(1, 2, 3, 4);

// Increment each element of the counters register in parallel counters = _mm_add_epi32(counters, increments);

// |counters| can now be transposed and encrypted in parallel

```

CTR can thus be fully parallelized and therefore allows bitslicing to maximize parallelism and register usage.

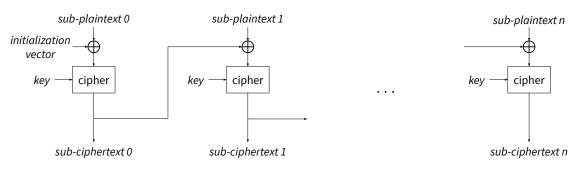

Another commonly used mode is Cipher Block Chaining (CBC, Figure 1.7c), which solves the weakness of ECB by xoring each sub-plaintext with the sub-ciphertext produced by the encryption of the previous sub-plaintext. This processed is bootstrapped by xoring the first sub-plaintext with an additional secret data called an *initialization vector*.

However, because bitslicing encrypts many sub-plaintexts in parallel, it prevents the use of CBC, as well as any other mode that would rely on using a sub-ciphertext as an input for encrypting the next sub-plaintext (like Cipher Feedback and Output Feedback). To take advantage of bitslicing in such sequential modes, we can multiplex encryptions from multiple independent data streams, at the cost of some management overheads [148].

### **Compile-time Permutations**

A desirable property of ciphers is *diffusion*: if two plaintexts differ by one bit, then statistically half of the bits of the corresponding ciphertexts should differ. In practice, this property is often achieved using permutations. For instance, Piccolo [277] uses an 8-bit permutation (Figure 1.9). A naive, non-bitsliced C implementation of this permutation would be:

A clever developer (or compiler) could notice that the three right-shifts by 2 can be merged together:  $((x \& 64) >> 2) \mid ((x \& 16) >> 2) \mid ((x \& 4) >> 2)$  can be optimized to  $(x \& (64 \mid 16 \mid 4)) >> 2$ . The same goes for the three left-shifts by 2, and the permutation can therefore be written as (with the masks written in binary for more simplicity):

In bitslicing, each bit is stored in a different variable, so this permutation consists in 8 static assignments:

31

Figure 1.9: Piccolo's round permutation

The C compiler can inline this function, and get rid of the assignments by doing copy propagation, effectively performing the permutation at compile time. This technique can be applied to any bit-permutation, as well as shifts and rotations, thus reducing their runtime cost to zero.

### **Lookup Tables**

Another important property of ciphers is *confusion*: each bit of a ciphertext should depend on several bits of the encryption key, so as to obscure the relationship between the two. Most ciphers achieve this property using functions called *S-boxes* (for substitution-boxes), often specified using lookup tables. For instance, RECTANGLE uses the following lookup table:

```

char table[16] = {

6, 5, 12, 10, 1, 14, 7, 9,

11, 0, 3, 13, 8, 15, 4, 2

};

```

This lookup table is said to be a  $4 \times 4$  table: it needs 4 bits to index its 16 elements, and returns integers on 4 bits (0 to 15). Such tables cannot be used in bitslicing, since each bit of the index would be in a different register. Instead, equivalent circuits can be used, as illustrated in Section 1.0.1. A circuit equivalent to the lookup table of RECTANGLE is:

```

void table(bool a0, bool a1, bool a2, bool a3,

bool* b0, bool* b1, bool* b2, bool* b3) {

bool t1 = ^{\sim}a1;

bool t2 = a0 \& t1;

bool t3 = a2 ^{\circ} a3;

*b0 = t2 ^t3;

bool t5 = a3 | t1;

bool t6 = a0 ^t5;

*b1

= a2 ^t t6;

bool t8 = a1 ^{\circ} a2;

bool t9 = t3 & t6;

*b3 = t8 ^t9;

bool t11 = *b0 | t8;

*b2 = t6 ^t11;

}

```

Using 64-bit variables (uint64-t in C) instead of bool allows this code to compute the S-box 64 times in parallel. Bitslicing then becomes more efficient than direct code: accessing to a value in the original table will take about 1 cycle (assuming a cache hit), while doing the 12 instructions from the circuit above should take 12 cycles (or even less on a superscalar CPU) to compute 64 times the S-box (on 64-bit registers), thus costing at most 0.19 cycles per S-box.

Converting a lookup table into a circuit can be easily done using Karnaugh maps [172] or binary decision diagrams [197]. However, this tends to produce large circuits. Bruteforcing every possibility is unlikely to yield any results, as even a small  $4\times4$  S-box usually requires a circuit of about 12 instructions, and hundreds of billions of such circuits exist. Heuristics can be added to the brute-force search in order to reduce the complexity of the search [234], but this does not scale well beyond  $4\times4$  S-boxes. For large S-boxes, like the  $8\times8$  AES S-box, cryptographers exploit the underlying mathematical structure of the S-boxes to optimize them [96, 91]. Such a task is hard to automate, yet it is essential to obtain good performance on bitsliced ciphers.

### Constant-time

Bitslicing makes it impossible to (efficiently) branch on secret data, since within a single register, each bit represents a different input. In particular, the branch condition could be, at the same time, true for some inputs, and false for others. Thus, both branches of conditionals need to be computed, and combined by masking with the branch condition. For instance, the following branching code (assuming x, a, b, c, d and e are all Boolean, for the sake of simplicity):

```

if (x) {

a = b;

} else {

a = c ^ d ^ e;

}

```

would be implemented in a bitsliced form as:

```

a = (x \& b) | (x \& (c d e));

```

If x is a secret data, the branching code is vulnerable to timing attacks: it runs faster if x is true than if it is false. An attacker could observe the execution time and deduce the value of x. On the other hand, the bitsliced code executes the same instructions independently of the value of x and is thus immune to timing attacks. For large conditionals, this would be expensive, since it requires computing both branches instead of one. However, this is

1.2. BACKGROUND 33

not an issue when implementing symmetric cryptographic primitives, as they rarely—if ever—rely on conditionals.

The lack of branches is not sufficient to make a program constant-time: memory accesses based on secret indices could be vulnerable to cache-timing attacks (presented in Section 1.0.1). However, as shown in the previous section, bitslicing prevents such memory accesses by replacing lookup tables by constant-time circuits.

Since they prevent both conditional branches based on secret data, and memory accesses based on secret data, bitsliced programs are constant-time by construction.

### **Transposition**

Transposing the data from a direct representation to a bitsliced one is expensive. Naively, this would be done bit by bit, using the following algorithm for a matrix of 64 64-bit registers (a similar algorithm can be used for any matrix size):

```

void naive_transposition(uint64_t data[64]) {

// transposing |data| in a local array

uint64_t transposed_data[64] = { 0 };

for (int i = 0; i < 64; i++) {

for (int j = 0; j < 64; j++) {

transposed_data[j] |= ((data[i] >> j) & 1) << i;

}

}

// copying the local array into |data|, thus transposing |data| in-place

memcpy(data, transposed_data, 64 * sizeof(uint64_t));

}</pre>

```

This algorithm does 4 operations per bit of data (a left-shift <<, a right-shift >>, a bitwise and & and a bitwise or  $|\cdot|$ ), thus having a cost in  $\mathcal{O}(n)$  where n is the size in bit of the input. Given that modern ciphers can have a cost as low as half a cycle per byte (CHACHA20 on AVX-512, for instance), spending 1 cycle per bit (8 cycles per byte) transposing the data would make bitslicing too inefficient to be used in practice. However, this transposition algorithm can be improved (as shown by Knuth [184], and explained in detail by Pornin [248]) by observing that the transpose of a matrix can be recursively written as:

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}^T = \begin{bmatrix} A^T & C^T \\ B^T & D^T \end{bmatrix}$$

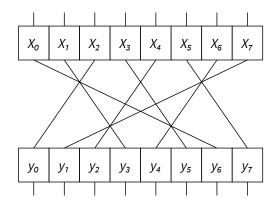

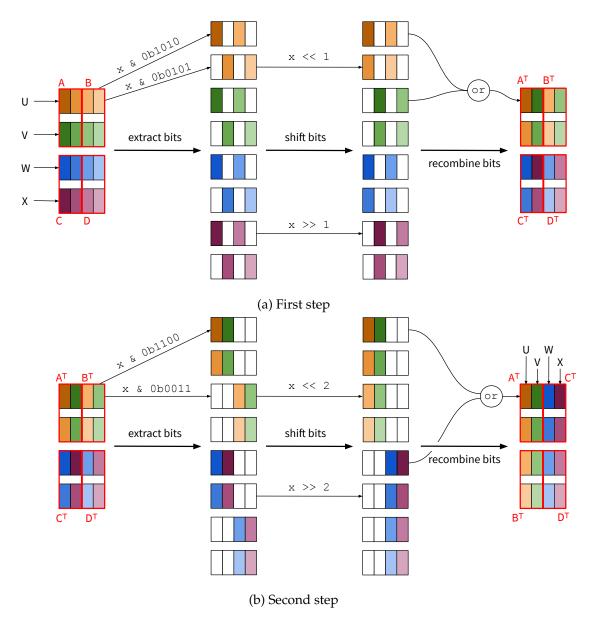

until we are left with matrices of size  $2 \times 2$  (on a 64x64 matrix, this takes 6 iterations). Swapping B and C is done with shifts, ors, and ands. The key factor is that when doing this operation recursively, the same shifts/ands/ors are applied at the same time on A and B, and on C and D, thus saving a lot of operations compared to the naive algorithm.

**Example 1.2.1.** Let us consider a  $4 \times 4$  matrix composed of 4 4-bit variables U, V, W and X. The first step is to transpose the  $2 \times 2$  sub-matrices (corresponding to A, B, C and D above). Since those are  $2 \times 2$  matrices, the transposition involves no recursion (Figure 1.10a). Transposing A and B is done with the same operations: & 0b1010 isolates the leftmost bits in both A and B at the same time; << 1 shifts the rightmost bits of both A and B at the same time, and the final or recombines both A and B at the same time. The same goes for C and D. The individual transpose of B and C can then be swapped in order to finalize the whole transposition (Figure 1.10b).

When applied to a matrix of size  $n \times n$ , this algorithm performs  $\log(n)$  recursive steps to get to  $2 \times 2$  matrices, each of them doing n operations to swap sub-matrices B and C. The total cost is therefore  $\mathcal{O}(n \log n)$  for a  $n \times n$  matrix, or  $\mathcal{O}(\sqrt{n \log n})$  for n bits. On a

Figure 1.10: Optimized transposition of a  $4 \times 4$  matrix

modern Intel CPU (*e.g.*, Skylake), this amounts to 1.10 cycles per bits on a 16x16 matrix, down to 0.09 cycles per bits on a 512x512 matrix [212].

Furthermore, in a setting where both the encryption and decryption are bitsliced, transposing the data can be omitted altogether. Typically, this could be the case when encrypting a file system [248].

### **Arithmetic Operations**

Bitslicing prevents from using CPU arithmetic instructions (addition, multiplication etc.), since each n-bit number is represented by 1 bit in n distinct registers. Instead, bitsliced programs must re-implement binary arithmetic, using solely bitwise instructions. As we will show in Section 1.2.5, using bitslicing to implement additions is 2 to 5 times slower than using native CPU add instructions, and multiplication would be much slower. We are not aware of any bitsliced implementation of a cipher that simulates arithmetic operations in this way.

### 1.2.3 *m*slicing

Bitslicing can produce high-throughput cipher implementations through data-parallelism. However, it suffers from a few limitations:

- bitslicing requires *a lot* of independent inputs to be efficient, since throughput is achieved by encrypting multiple inputs in parallel (*m* parallel inputs on *m*-bit registers).

- bitsliced code uses hundreds of variables, which puts a lot of pressure on the registers, which causes spilling (moving data back-and-forth between registers and memory), thus reducing performance.

- bitslicing cannot efficiently implement ciphers which rely heavily on arithmetic operations, like CHACHA20 [61] and THREEFISH [136].

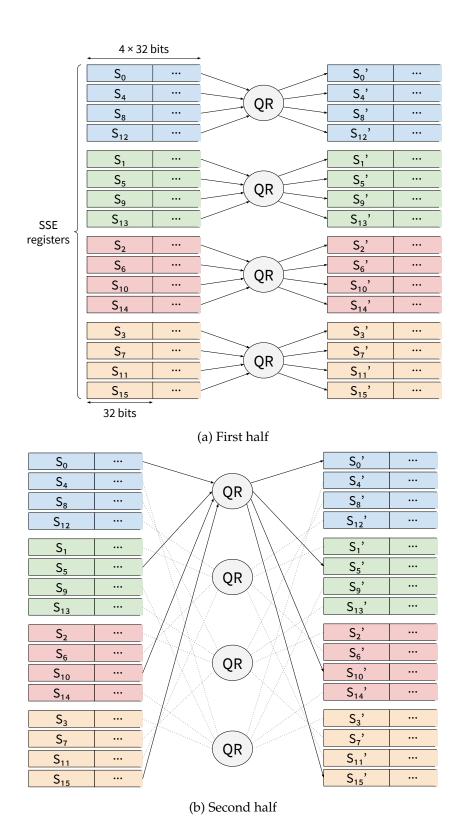

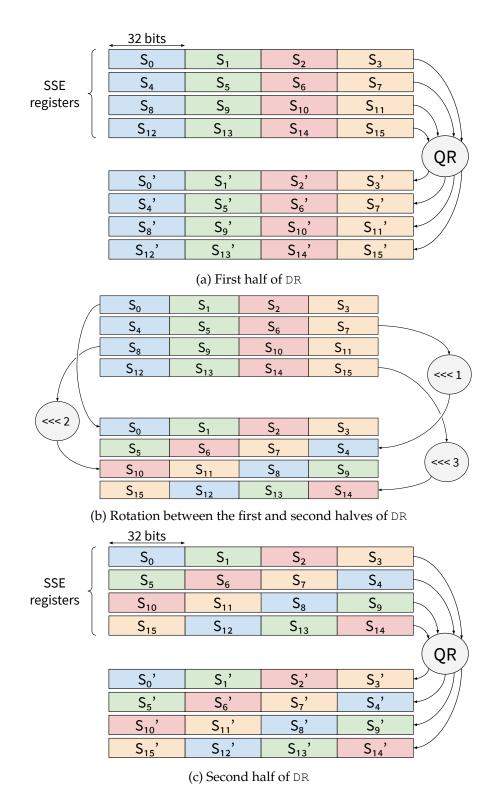

To overcome the first two issues, Käsper and Schwabe [174] proposed a "byte-sliced" implementation of AES. Bitslicling would represent the 128-bit block of AES as 1 bit in 128 registers. Instead, Ksper and Schwabe proposed to represent the 128-bit block as 16 bits in 8 registers. Using only 8 registers greatly reduces register pressure and allows AES to be implemented without any spilling. Furthermore, this representation requires fewer inputs to fill the registers and thus maximize throughput: only 8 parallel AES inputs are required to fill up 128-bit SSE registers (against 128 with bitslicing).

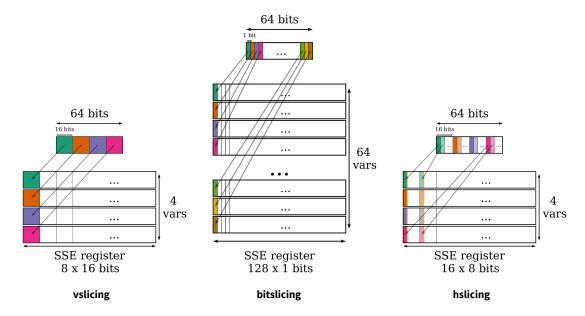

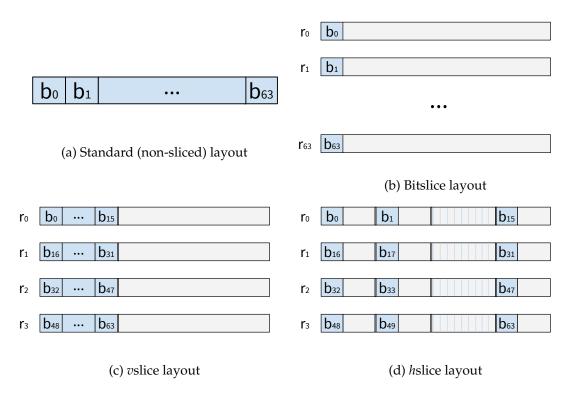

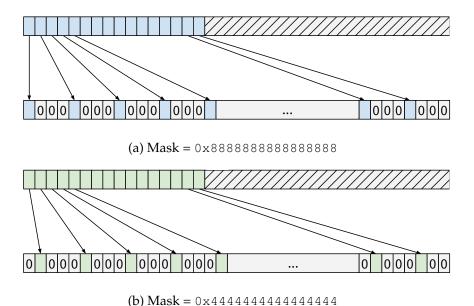

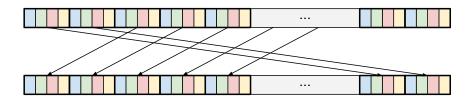

We define mslicing as a generalization of bitslicing, where a n-bit input is split into k bits in m registers (such that  $k \times m = n$ ). The special case m = 1 corresponds to bitslicing. When k (the number of bits in each register) is greater than one, there are two possible ways to arrange the bits within each register: they can either be stored contiguously, or they can be spread across each packed element. The first option, which we call vslicing, will enable the use of vertical instructions (e.g., 16-bit addition), while the second option, which we call hslicing, will enable the use of permutation instructions (e.g., pshufb).

### **Vertical Slicing**

Rather than considering the bit as the atomic unit of computation, one may use m-bit words as such basis (m being a word size supported by the SIMD architecture). On Intel (SSE/AVX/AVX512), m can be 8, 16, 32, or 64. We can then exploit vertical m-bit SIMD instructions to perform logic as well as arithmetic in parallel.

This technique, which we call vertical slicing (or vslicing for short), is similar to the notion of *vectorization* in the compilation world. Compared to bitslicing, it puts less pressure on registers, and requires less parallel data to fill the registers. Furthermore, it can be used to implement arithmetic-based ciphers (like CHACHA20), which cannot be implemented efficiently in bitslicing.

However, permutations are costly in *v*slicing. Applying an arbitrary bit-permutation to the whole block requires using shifts and masks to extracts bits from the registers and recombine them, as shown in Section 1.2.2.

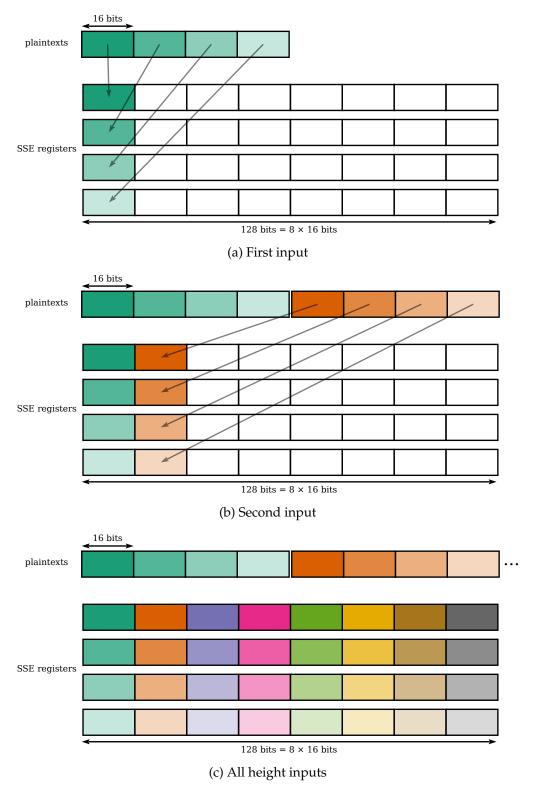

**Example 1.2.2** (*v*sliced RECTANGLE). The RECTANGLE cipher [309] (Figure 1.1, Page 17) encrypts a 64-bit input. We can split this input into 4 16-bit elements, and store them in the first 16-bit packed elements of 4 SSE registers (Figure 1.11a). Then, applying the same principle as bitslicing, we can fill the remaining empty elements of these SSE registers with independent inputs (Figures 1.11b and 1.11c), until the registers are full (in the case of RECTANGLE on 128-bit SSE registers, this is achieved with 8 inputs).

vsliced RECTANGLE can be efficiently computed in parallel. The S-box is a sequence of bitwise and, xor, not and or between each of these SSE registers, and is thus efficient

Figure 1.11: Data layout of vsliced RECTANGLE

Figure 1.12: Data layout of hsliced RECTANGLE

Figure 1.13: A left-rotation using a shuffle

in bitslicing and *v*slicing. The permutation can be written as three left-rotations, each one operating on a different SSE register. While the SSE extension does not offer a rotation instruction, it can be emulated using two shifts and an or. This is slightly more expensive than the bitsliced implementation of RECTANGLE, which can perform this permutation at compile time. However, the reduced register pressure more than compensate for this loss, as we shall demonstrate in our evaluation (Section 5.3).

#### **Horizontal Slicing**

Rather than considering a m-bit atom as a single packed element, we may also dispatch its m bits into m distinct packed elements, assuming that m is less or equal to the number of packed elements of the architecture. Using this representation, we lose the ability to perform arithmetic operations but gain the ability to perform arbitrary shuffles of our m-bit word with a single instruction (Figure 1.3d, Page 23). This style exploits on horizontal SIMD operations.

We call this technique *horizontal* slicing, or *h*slicing for short. Like *v*slicing, it lowers register pressure compared to bitslicing, and requires fewer inputs to fill the registers. While *v*slicing shines where arithmetic operations are needed, *h*slicing is especially useful to implement ciphers that rely on intra-register permutations, since those can be performed in a single shuffle instruction. This includes RECTANGLE's permutations, which can be seen as left-rotations, or Piccolo's permutation (Figure 1.9, Page 31).

Permutations mixing bits from distinct registers, however, will be expensive, as they will require manually extracting bits from different registers and recombining them.

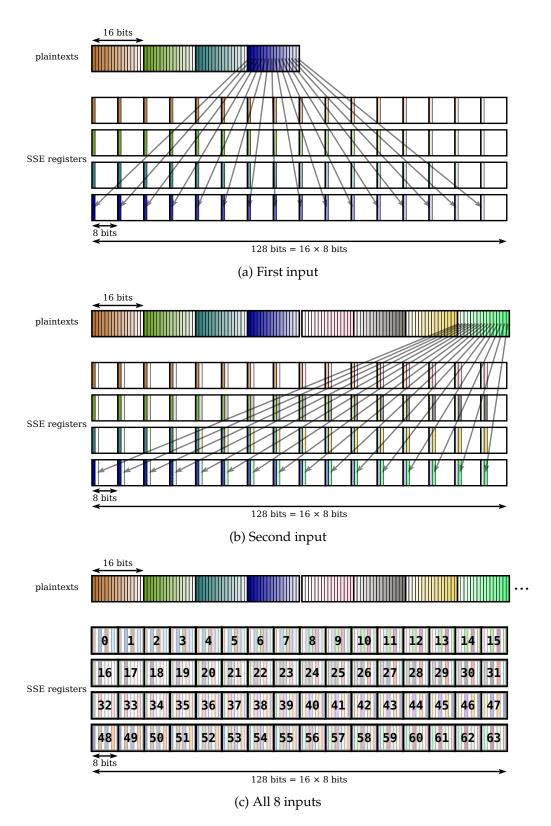

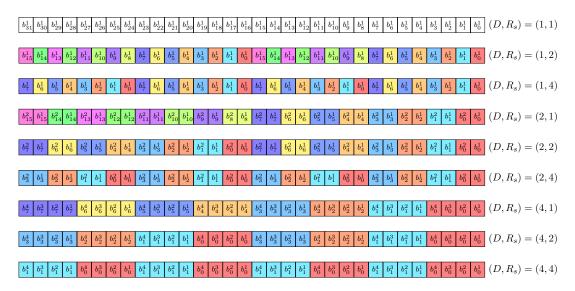

**Example 1.2.3** (*h*sliced RECTANGLE). On RECTANGLE, the 64-bit input is again seen as 4 times 16 bits, but this time, each bit goes to a distinct packed element (Figure 1.12a). Once again, there are unused bits in the registers, which can be filled with subsequent inputs. The second input would go into the second bits of each packed element (Figure 1.12b). Like for *v*slicing, this is repeated until the registers are full, which in the case of RECTANGLE on SSE requires a total of 8 inputs. Numbering the bits from 0 (most significant) to 63 (least significant) can help visualize the *h*slicing data layout (Figure 1.12c): the 8-bit element labeled *i* contains the *i*-bit of each of the 8 inputs.

RECTANGLE's S-box, composed solely of bitwise instructions, can be computed using the same instructions as the *v*sliced implementation. The permutation, however, can be done even more efficiently than in *v*slicing, using shuffle instructions. For instance, Figure 1.13 shows how a shuffle can perform the first left-rotation of RECTANGLE's linear layer: given the right pattern, the pshufb instruction acts as a byte-level rotation of a SSE register.

Figure 1.14: Slicing layouts

## 1.2.4 Bitslicing vs. vslicing vs. hslicing

**Terminology.** Whenever the slicing direction (*i.e.*, vertical or horizontal) is unimportant, we talk about mslicing (assuming m > 1) and we call slicing the technique encompassing both bitslicing and mslicing.

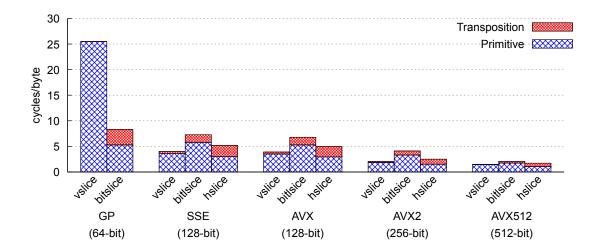

Figure 1.14 provides a visual summary of all slicing forms using RECTANGLE as an example. All these slicing forms share the same basic properties: they are constant-time, they rely on data-parallelism to increase throughput, and they use some sort of transposition to convert the data into a layout suitable to their model. However, each slicing form has its own strengths and weaknesses:

- transposing data to *h*slicing or *v*slicing usually has a cost almost negligible compared to a full cipher, while a bitslice transposition is much more expensive.

- bitslicing introduces a lot of spilling, thus reducing its potential performance, unlike *h*slicing and *v*slicing.

- only *v*slicing is a viable option on ciphers using arithmetic operations, since it can use SIMD arithmetic instructions. As shown in Section 1.2.5, trying to implement those instructions in bitslicing (or *h*slicing) is suboptimal.