# Impact of aging on the behaviour of wild band gap power transistors, application to the efficiency of DC-DC converters

Al Mehdi Bouchour

## ► To cite this version:

Al Mehdi Bouchour. Impact of aging on the behaviour of wild band gap power transistors, application to the efficiency of DC-DC converters. Electronics. Normandie Université; Université Abdelmalek Essaâdi (Tétouan, Maroc), 2020. English. NNT: 2020NORMR045. tel-03137632

# HAL Id: tel-03137632 https://theses.hal.science/tel-03137632

Submitted on 10 Feb 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE EN CO-TUTELLE INTERNATIONALE

# Pour obtenir le diplôme de doctorat

## Spécialité Génie électrique, électronique, photonique et systèmes

Préparée au sein de Université de Rouen Normandie et de Université de Abdelmalek Essaadi Tetouan

# Impact du vieillissement sur le comportement des transistors de puissance grand gap, application à l'efficacité des convertisseurs d'énergie

# Présentée et soutenue par AL MEHDI BOUCHOUR

|                          | Thèse soutenue publiquement le 01/12/2020<br>devant le jury composé de                                |                     |

|--------------------------|-------------------------------------------------------------------------------------------------------|---------------------|

| M. Zoubir KHATIR         | Directeur de recherche IFSTTAR, France                                                                | Rapporteur          |

| M. Jamal ZBITOU          | Professeur, Université Hassan Premier, Faculté des Sciences et Techniques de Settat, Maroc            | Rapporteur          |

| M. Abdeljabbar CHERKAOUI | Professeur, Université Abdelmalek Essaadi, ENSA de Tanger, Maroc                                      | Rapporteur          |

| M. Yassin LAAZIZ         | Professeur de l'enseignement supérieure, Université<br>Abdelmalek Essaadi, ENSA de Tanger, Maroc      | Examinateur         |

| Mme. Mounira BERKANI     | Maître de conférences à l'Université Paris Est Créteil<br>UPEC, ESPE de l'académie de Créteil, France | Examinateur         |

| M. Olivier LATRY         | Professeur, GPM, Université de Rouen Normandie, France                                                | Directeur France    |

| M. Ahmed EL OUALKADI     | Professeur de l'enseignement supérieure, Université<br>Abdelmalek Essaadi, ENSA de Tanger, Maroc      | Directeur Maroc     |

| M. Pascal DHERBECOURT    | Maitre de conférences - HDR, Université de Rouen<br>Normandie, France                                 | Co-directeur France |

Thèse dirigée par :

M. Ahmed El Oualkadi M. Olivier Latry M. Pascal Dherbécourt

UNIVERSITÉ DE ROUEN N D R M A N D I E Université Abdelmalek Essaadi Tétouan, Maroc Université de Rouen Normandie, France Université de Rouen Normandie, France

Centre des Etudes Doctorales : « Sciences et Techniques de l'ingénieur »

# Acknowledgments

First of all, I would like to thank my supervisors Mr. Ahmed El Oualkadi, Mr. Pascal Dherbécourt and Mr. Olivier Latry for their assistance and support in this thesis. I would like also to thank my supervisors for all the interesting scientific discussions. Each of you have given of his time, energy, and expertise and I am grateful for it.

I would like to thank Mr. Yassin Laaziz, director of the LabTIC and Mr. Philipe Pareige director of the GPM, for allowing me to conduct my research work in excellent conditions.

I have also to thank PHC TOUBKAL project for funding this thesis.

Special thanks to Mr. Ahmed El Oualkadi for sharing with me his expertise. You were my teacher in ENSAT for 5 years and then my thesis supervisors for 3 years. I learned many things from you so thank you.

I must thank M. Pascal Dherbécourt for being not only my thesis supervisor but also my second family in France. I am very grateful to him for being very patient and for all his time that he spent in discussing the various subjects of this thesis, and for going through the numerous versions of this dissertation.

Thank you Mr. Olivier Latry for accepting me in the ERDEFI team and for offering me all the support to conduct my work in excellent conditions.

I would also like to extend my thanks to the GPM laboratory for providing materials and resources for my experiment measurements. Also, many thanks to the ERDEFI team in the GPM laboratory for their help.

This journey would not have been possible without the support of my family. I am especially grateful to my father Allal Bouchour and my mother Hafida Guerouat, who supported me emotionally. I always knew that you believed in me and wanted the best for me. Thank you for teaching me that my job in life was to learn and to be happy.

To my sister Safe Bouchour, thank you for encouraging me in all of my pursuits and inspiring me to follow my dreams. Thank you to my brother Reda Bouchour and my sister Salma Bouchour for their support and the joyful moments we have spent together.

# Table of contents

| Acknowledgments                                                   |    |

|-------------------------------------------------------------------|----|

| Table of contents                                                 | 4  |

| List of figures                                                   |    |

| List of tables                                                    |    |

| List of symbols                                                   |    |

| List of acronyms                                                  |    |

| Abstract                                                          |    |

| Résumé                                                            |    |

| Chapter 1: Introduction                                           |    |

| 1.1 GaN HEMT for power converter applications                     | 24 |

| 1.1.1. Normally-off challenge                                     | 24 |

| 1.1.2 Power losses estimation                                     |    |

| 1.1.3. Gate driver                                                |    |

| 1.1.4. Reliability challenges                                     |    |

| 1.2. Thesis project description                                   |    |

| 1.3. Objectives of this research work                             |    |

| 1.4. Outline of the thesis                                        |    |

| 1.5. References                                                   |    |

| Chapter 2: Context and state of art of GaN HEMT power transistors | 29 |

| 2.1. Introduction                                                 |    |

| 2.2. Context of the study                                         | 29 |

| 2.2.1. Improving energy efficiency through GaN technology         | 29 |

| 2.2.2. GaN power converters market                                |    |

| 2.2.3. GaN power converter applications                           |    |

| 2.3. GaN and SiC power devices comparison                         |    |

| 2.3.1. Static characteristics                                     |    |

| 2.3.2. Switching characteristics                                  |    |

| 2.4. Physical properties of the power GaN HEMT                    | 41 |

| 2.4.1. Physical properties of GaN                                 |    |

| 2.4.2. GaN HEMT normally-on structure                             | 45 |

| 2.4.3. GaN HEMT normally-off                                      | 46 |

| 2.5. Aging of the GaN HEMT power transistors                      |    |

| 2.5.1. Short circuit stress                                       |    |

| 2.5.2. Static stresses: HTGB, HTRB                                |    |

| 2.5.3. Switching stress                                                | 49 |

|------------------------------------------------------------------------|----|

| 2.6. GaN HEMT power losses modeling                                    | 50 |

| 2.6.1. Power losses in DC power converter                              | 51 |

| 2.6.2. Estimation of GaN power losses                                  | 52 |

| 2.7. Conclusion                                                        | 55 |

| 2.8. References                                                        | 55 |

| Chapter 3: GaN HEMT power losses estimation for switching applications | 61 |

| 3.1. Introduction                                                      | 61 |

| 3.2. Static characterization of GaN HEMT                               | 61 |

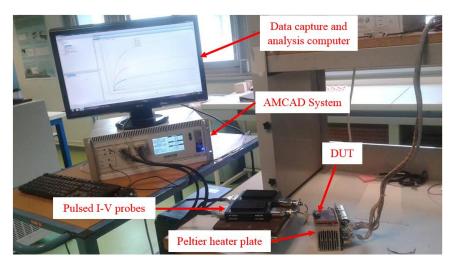

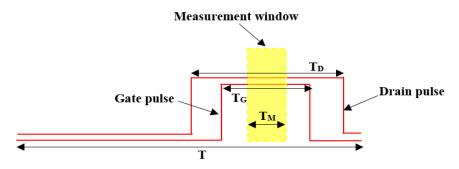

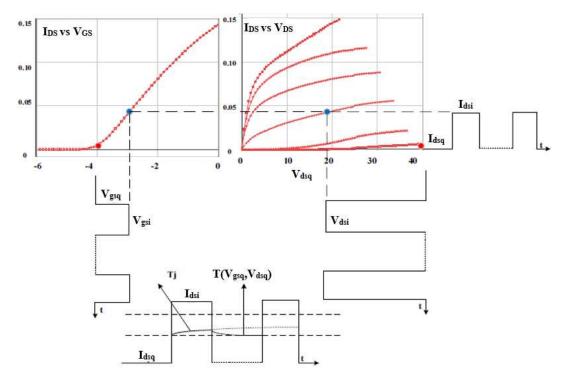

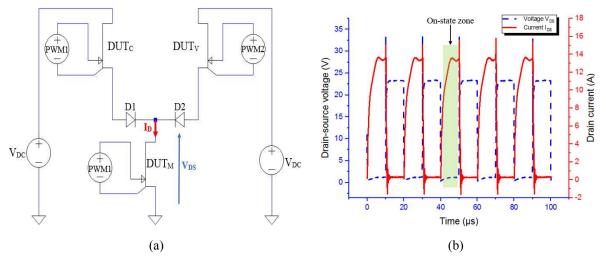

| 3.2.1. Pulsed I-V Experiment setup                                     | 62 |

| 3.2.2. Temperature dependency of GaN HEMT static characteristics       | 64 |

| 3.2.2.1. On-state resistance R <sub>DS(ON)</sub>                       | 65 |

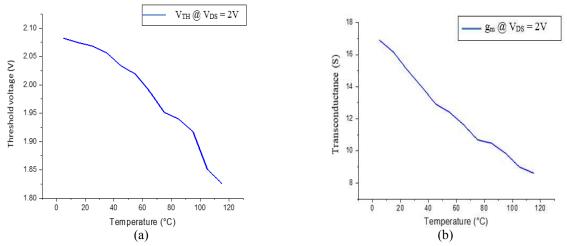

| 3.2.2.2 Threshold voltage (V <sub>TH</sub> )                           | 66 |

| 3.2.2.3 Transconductance (g <sub>m</sub> )                             | 67 |

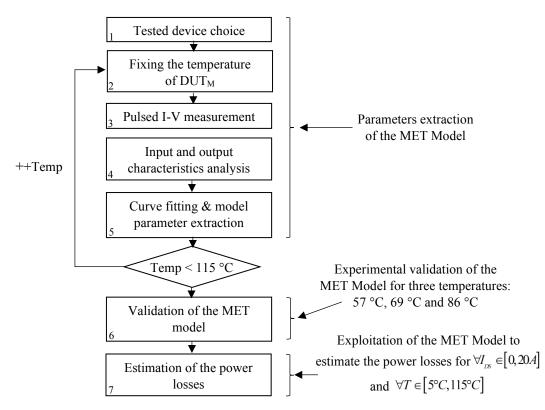

| 3.2.3. Modeling GaN HEMTs Power Transistors                            | 67 |

| 3.2.3.1. Modeling methodology                                          | 67 |

| 3.2.3.2. Results and discussions                                       | 70 |

| 3.3. Dynamic characterization of GaN HEMT                              | 77 |

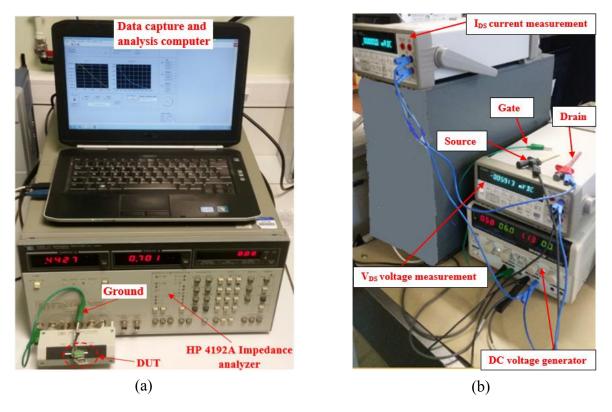

| 3.3.1. C-V experimental setup                                          | 77 |

| 3.3.1.1. Calibration                                                   | 77 |

| 3.3.1.2. Initialization                                                | 77 |

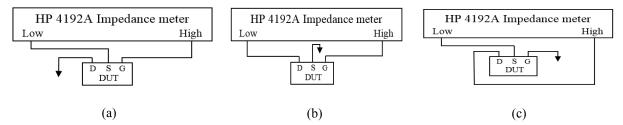

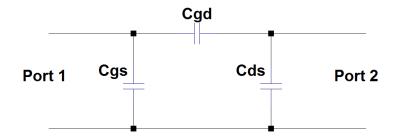

| 3.3.1.3. Measurement circuits for CGS, CGD and CDS                     |    |

| 3.3.2. Temperature-dependent capacitance-voltage measurements          | 79 |

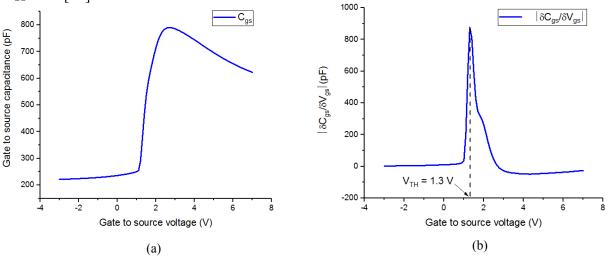

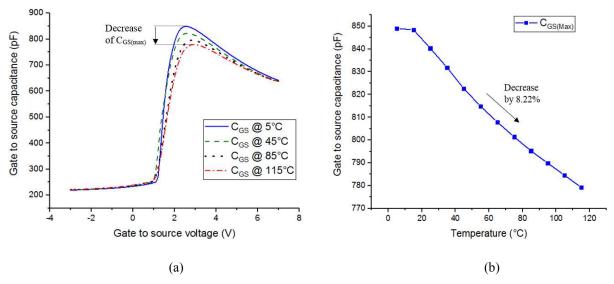

| 3.3.2.1. C <sub>GS</sub> -V <sub>GS</sub> characteristic               | 79 |

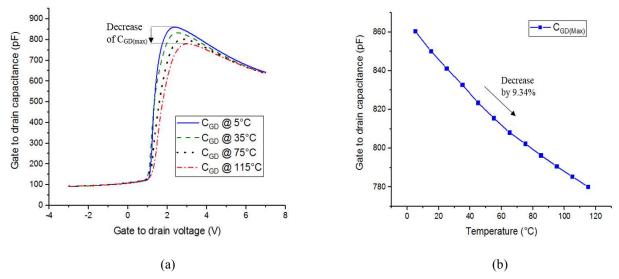

| 3.3.2.2. C <sub>GD</sub> -V <sub>GD</sub> characteristic               | 80 |

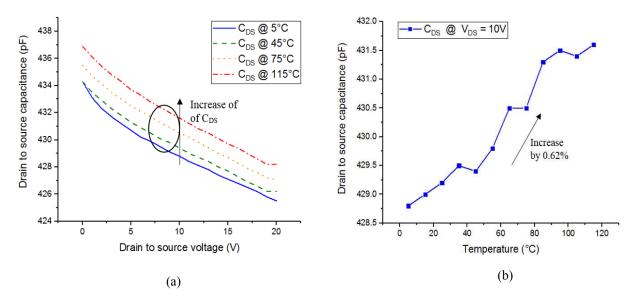

| 3.3.2.3. C <sub>DS</sub> -V <sub>DS</sub> characteristics              | 81 |

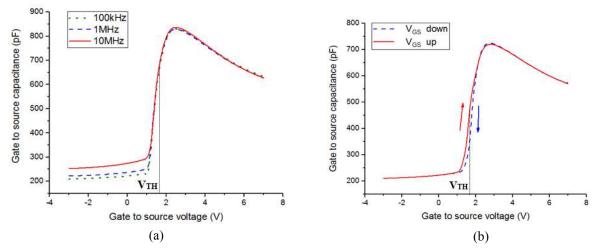

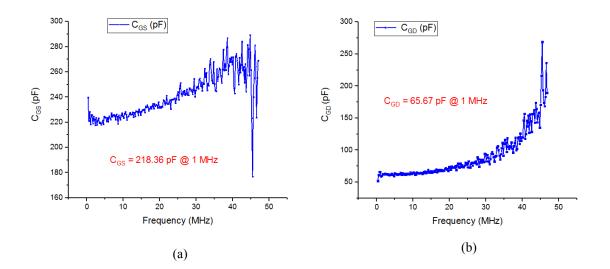

| 3.3.3. Frequency dependent of C-V measurements                         | 82 |

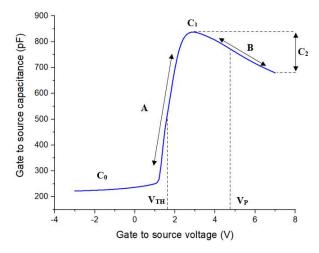

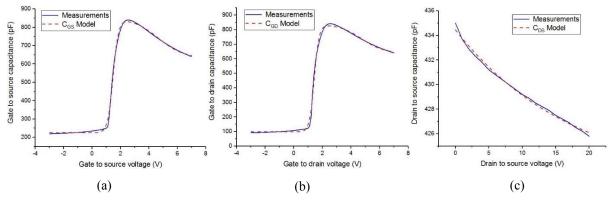

| 3.3.4. C-V modeling methodology                                        | 83 |

| 3.4. Leakage current characteristics                                   | 86 |

| 3.4.1. Low current experiment setup                                    | 86 |

| 3.4.2. Gate leakage current temperature dependency                     | 86 |

| 3.4.3. Gate leakage current power estimation                           | 87 |

| 3.5. Estimation of the GaN HEMT power converters efficiency            | 88 |

| 3.6. Conclusion                                                        | 90 |

| 3.7. References                                                        | 91 |

| Chapter 4: Extraction of the power GaN HEMTs intrinsic and extrinsic elements | -   |

|-------------------------------------------------------------------------------|-----|

| 4.1. Introduction                                                             |     |

| 4.2. Small signal model of power GaN HEMT                                     |     |

| 4.3. S-parameters experimental setup at the cold state                        |     |

| 4.4. Measurement verification                                                 |     |

| 4.4.1. Measurement repeatability                                              |     |

| 4.4.2. Passive component test                                                 |     |

| 4.5. The proposed extraction methodology                                      | 100 |

| 4.6. GaN HEMT S-parameters extraction                                         | 101 |

| 4.6.1. Parasitic inductances                                                  | 103 |

| 4.6.2. Intrinsic capacitances                                                 | 105 |

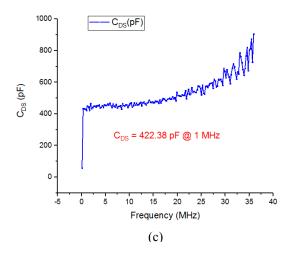

| 4.6.3. Parasitic resistances                                                  | 107 |

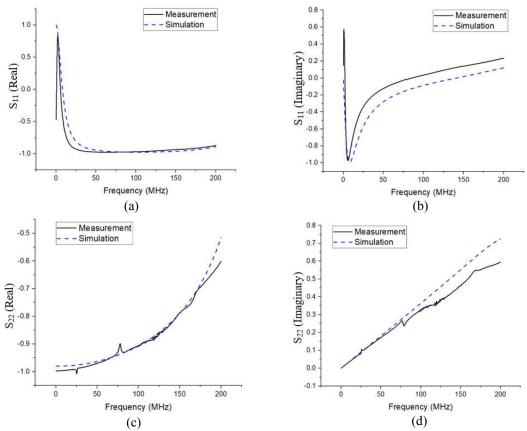

| 4.6.4. Measurement methodology verification                                   | 109 |

| 4.7. Multiple bias model extraction                                           | 110 |

| 4.7.1. Multiple bias experiment setup                                         |     |

| 4.7.2. Linear model extraction methodology                                    |     |

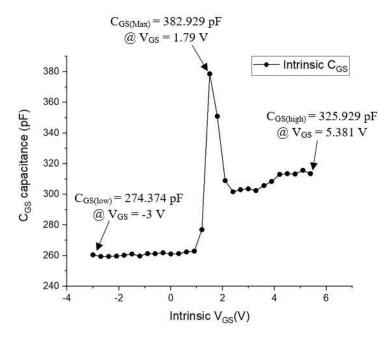

| 4.7.3. Non-linear intrinsic capacitance extraction                            | 113 |

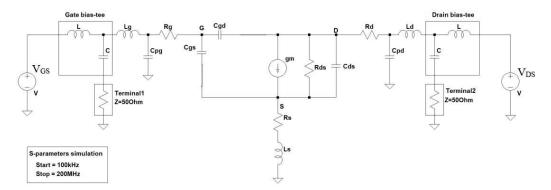

| 4.8. S-parameter modelling and simulation                                     |     |

| 4.9. Conclusion                                                               |     |

| 4.10. References                                                              |     |

| Chapter 5: Aging of the GaN HEMT under safe operational conditions            | 120 |

| 5.1. Introduction                                                             | 120 |

| 5.2. Aging methodology                                                        | 120 |

| <b>5.2.1.</b> $I_D$ current and $V_{DS}$ voltage limitations                  |     |

| 5.2.2. Junction temperature limit                                             |     |

| 5.3. Impact of aging on static characteristics                                | 122 |

| 5.3.1. Static parameters degradation                                          | 122 |

| 5.3.2. Static characteristics aging modeling                                  |     |

| 5.4. Impact of aging on dynamic characteristics                               | 125 |

| 5.4.1. Parasitic capacitances degradation                                     | 125 |

| 5.4.1.1. C <sub>GS</sub> -V <sub>GS</sub> characteristic                      | 125 |

| 5.4.1.2. C <sub>GD</sub> -V <sub>GD</sub> characteristic                      | 126 |

| 5.4.1.3. C <sub>DS</sub> -V <sub>DS</sub> characteristic                      | 127 |

| 5.4.2. Dynamic characteristics aging modeling                                 | 128 |

| 5.5. Impact of aging on S-parameters characteristics                          | 129 |

| 5.5.1. S-parameters degradation                                         | 129 |

|-------------------------------------------------------------------------|-----|

| 5.5.2. S-parameters aging modeling                                      | 131 |

| 5.6. Step stress tests                                                  | 132 |

| 5.6.1. Frequency stress                                                 | 132 |

| 5.6.2. On-state stress                                                  | 133 |

| 5.6.3. Off-state stress                                                 | 134 |

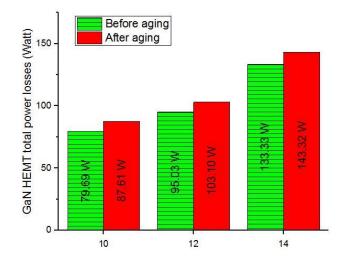

| 5.7. Effect of aging the GaN HEMT on the efficiency of power converters | 136 |

| 5.7.1. Conduction power losses aging effect                             |     |

| 5.7.2. Switching power losses aging effect                              | 139 |

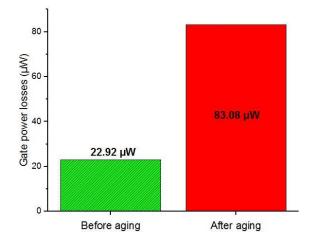

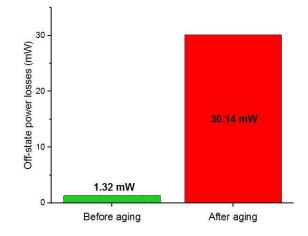

| 5.7.3. Gate leakage current losses aging effect                         | 139 |

| 5.7.5. Efficiency aging impact                                          |     |

| 5.8. Conclusion                                                         | 142 |

| 5.9. References                                                         | 142 |

| Chapter 6: Summary, conclusions and future work                         | 148 |

| 6.1 Summary                                                             | 148 |

| 6.2 Conclusion                                                          | 149 |

| 6.3 Thesis contribution                                                 | 149 |

| 6.4 Future work                                                         | 150 |

| List of publications and communications                                 | 151 |

# List of figures

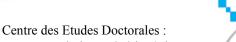

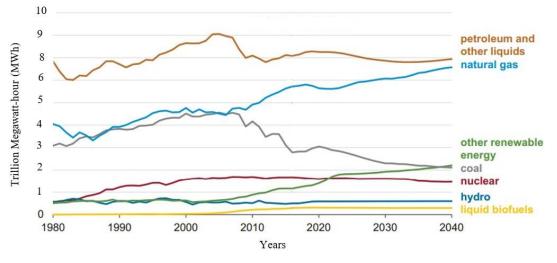

| Fig. 2.1: Change in oil and electricity consumption outlook 2000-2040 [2-3].                                                              | . 29 |

|-------------------------------------------------------------------------------------------------------------------------------------------|------|

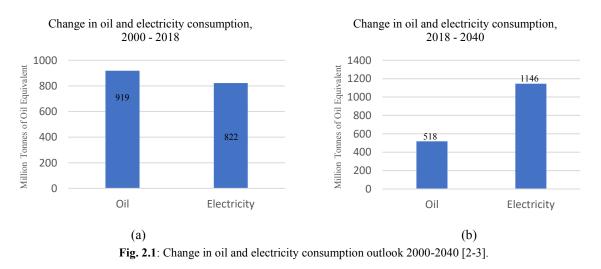

| Fig. 2.2: Electric energy losses during the consumption flow [4].                                                                         | . 30 |

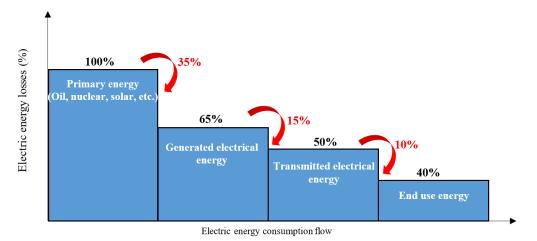

| Fig. 2.3: Power losses in synchronous buck converter [5]                                                                                  |      |

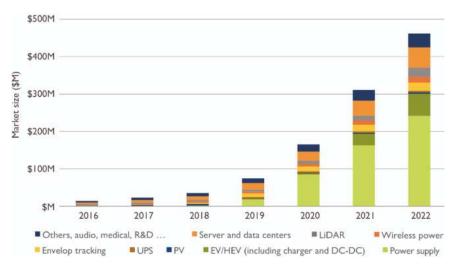

| Fig. 2.4: GaN power device market by application (\$M) [6]                                                                                | . 31 |

| Fig. 2.5: GaN size equipment compared to Si [13]: (a) 65 W AC power adapter, (b) 1 kW ESS                                                 |      |

| converter, (c) 3-Phase AC power conversion modules.                                                                                       | . 32 |

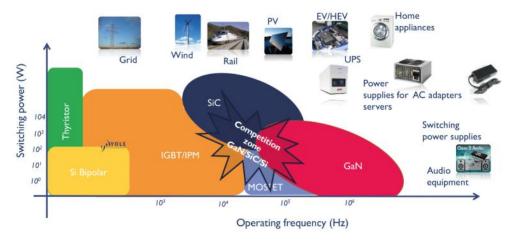

| Fig. 2.6: Power vs Frequency on electronics: technology positionning in 2018 [6]                                                          | . 33 |

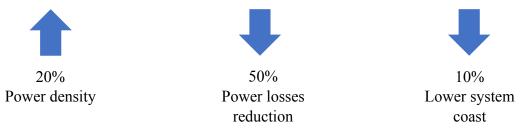

| Fig. 2.7: GaN advantages in automotive applications compared to Si [18]                                                                   | . 33 |

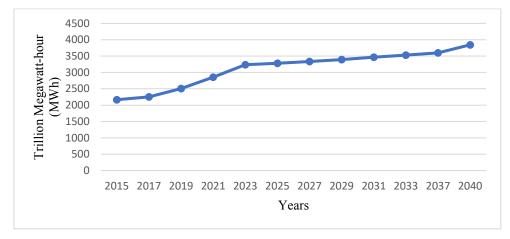

| Fig. 2.8: Total renewable energy consumption outlook 2015-2040 [19]                                                                       | . 34 |

| Fig. 2.9: GaN advantages in renewable energy applications [20]                                                                            | . 34 |

| Fig. 2.10: World Energy Consumption [11].                                                                                                 |      |

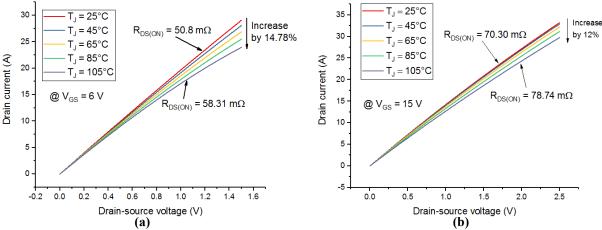

| Fig. 2.11: Simulated output characteristic at various temperatures varying from 25 °C to 105 °C : (a                                      | ι)   |

| GaN HEMT (GS66508P) ; (b) SiC MOSFET (SCT2120AF)                                                                                          |      |

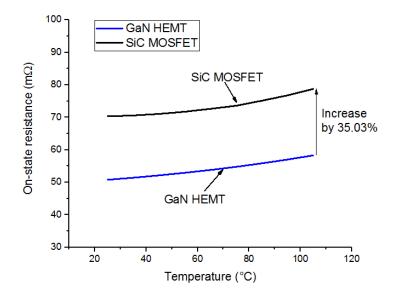

| Fig. 2.12: Simulated R <sub>ON</sub> comparison between GaN HEMT (GS66508P), SiC MOSFET                                                   |      |

| (SCT2120AF)                                                                                                                               | . 37 |

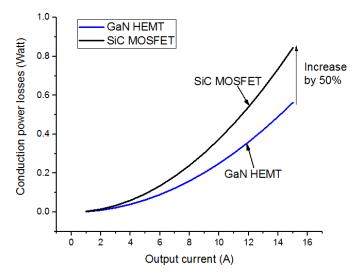

| Fig. 2.13: Simulated conduction power losses comparison between GaN HEMT (GS66508P), SiC                                                  |      |

| MOSFET (SCT2120AF).                                                                                                                       | . 37 |

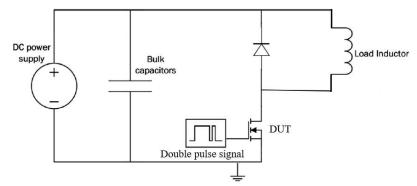

| Fig. 2.14: Double-pulse setup with inductive load [28]                                                                                    | . 38 |

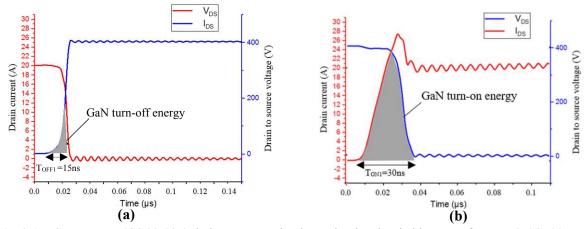

| Fig. 2.15: GaN HEMT (GS66508P) drain current and voltage simulated switching waveforms at                                                 |      |

| 25°C: (a) turn-off; (b) turn-on.                                                                                                          |      |

| Fig. 2.16: SiC MOSFET (SCT2120AF) Drain current and voltage simulated switching waveforms a                                               |      |

| 25°C: (a) turn-off; (b) turn-on.                                                                                                          | . 39 |

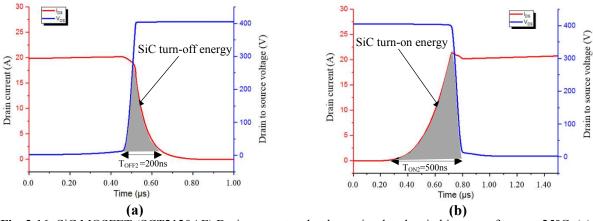

| Fig. 2.17: GaN HEMT (GS66508P) and SiC MOSFET (SCT2120AF) simulated switching energy                                                      |      |

| losses versus the temperature: (a) turn-on ( $E_{ON}$ ); (b) turn-off ( $E_{OFF}$ ).                                                      | . 39 |

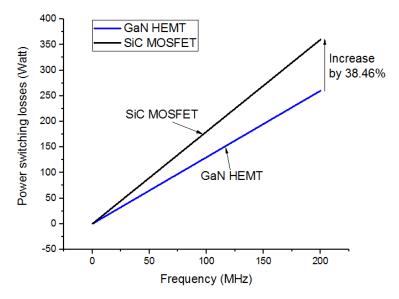

| Fig. 2.18: Simulated power switching losses comparison between GaN HEMT (GS66508P), SiC                                                   |      |

| MOSFET (SCT2120AF).                                                                                                                       | . 40 |

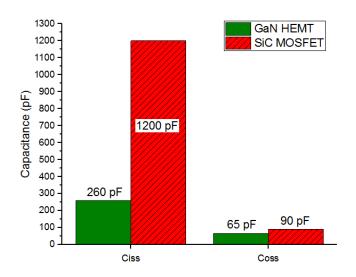

| <b>Fig. 2.19:</b> Ciss and Coss capacitances comparison between GaN HEMT (GS66508P) and SiC                                               | • •  |

| MOSFET (SCT2120AF) [24-25].                                                                                                               |      |

| <b>Fig. 2.20:</b> Comparison of GaN power performances limits: (a) R <sub>DS(ON)</sub> versus BV (b) BV versus cuto                       |      |

| frequency [30]                                                                                                                            |      |

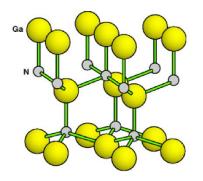

| Fig. 2.21: Schematic of the wurzite GaN [32].                                                                                             |      |

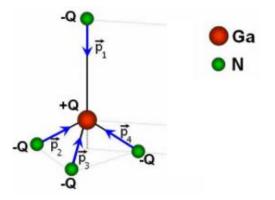

| <b>Fig. 2.22:</b> Generation of the GaN spontaneous polarization [35].                                                                    |      |

| <b>Fig. 2.23:</b> Generation of the GaN piezoelectric polarization [36]                                                                   |      |

| <b>Fig. 2.24:</b> AlGaN/GaN heterostructure: (a) cross section (b) Band diagram [37].                                                     |      |

| Fig. 2.25: Cross section of the GaN HEMT structure.                                                                                       | . 45 |

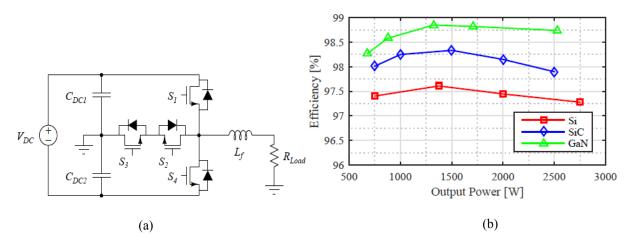

| <b>Fig. 2.26:</b> Power converter efficiency comparison between Si IGBTs, SiC MOSFETs and GaN                                             | 50   |

| HEMTs: (a) T-type inverter topology (b) Efficiency comparison at 32 kHz [83].                                                             |      |

| <b>Fig. 2.27:</b> GaN HEMT package and comparison to Si MOSFET parasitic elements [84].                                                   |      |

| <b>Fig. 2.28:</b> Boost DC/DC converter: (a) Circuit schematic (b) representation of the different operation                              | •    |

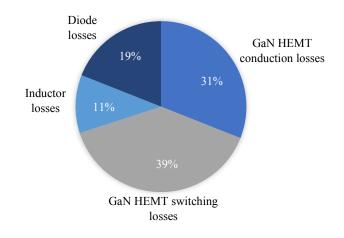

| regimes of the transistor in a boost converter                                                                                            | . 51 |

| <b>Fig. 2.29:</b> Distribution of power losses in Boost DC/DC converter with $V_{IN} = 16$ V; $V_{OUT} = 34$ V and $P_{OUT} = 15$ W [89]. | 50   |

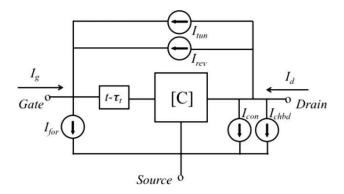

| Fig. 2.30: GaN HEMT SPICE model [93]                                                                                                      |      |

| Fig. 2.30: Compact physical GaN HEMT model [94].                                                                                          |      |

| Fig. 2.51: Compact physical Gal Field 1 model [94]                                                                                        |      |

| <b>Fig. 3.2:</b> I-V pulse chronogram                                                                                                     |      |

| <b>1 12. 3.2.</b> 1- v puise chitohogram                                                                                                  | . 05 |

| Fig. 3.3: Principle of pulsed I-V measurements                                                                                            | 64              |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

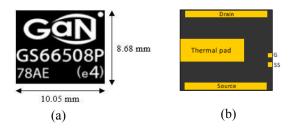

| Fig. 3.4: GS66508P package [7]: (a) Top view; (b) bottom view                                                                             | 64              |

| Fig. 3.5: Schematic illustration of the tested GaN HEMT power transistor structure [6].                                                   |                 |

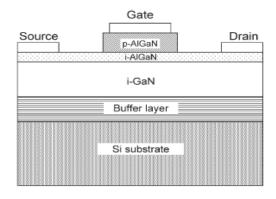

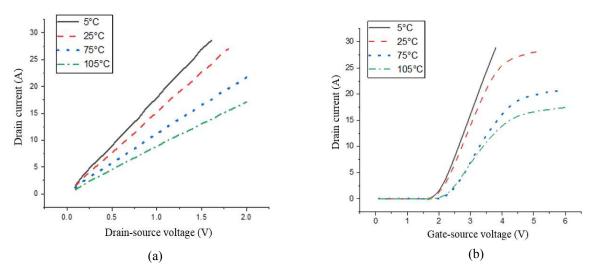

| Fig. 3.6: Measured (a) Output characteristics at $V_{GS} = 6V$ ; (b) Transfer characteristics at $V_{DS} = 2V$                            | of              |

| GaN HEMT for various temperatures: 5 °C, 25 °C, 75 °C and 105 °C.                                                                         | 66              |

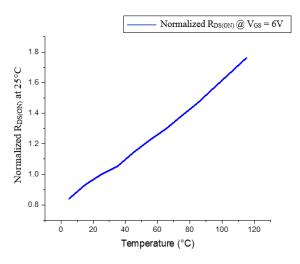

| Fig. 3.7: Normalized $R_{DS(ON)}$ as a function of temperature at $V_{GS} = 6V$                                                           |                 |

| Fig. 3.8: (a) Threshold voltage; (b) Transconductance as a function of temperature at $V_{DS} = 2 V$                                      |                 |

| Fig. 3.9: Proposed methodology for estimating the GaN HEMT power losses                                                                   | 68              |

| Fig. 3.10: (a) Schematic of the switching bench; (b) Current and voltage waveforms on $DUT_M$ for                                         |                 |

| switching conditions: 50 kHz, duty-cycle = 50 %, and 14 A / 24 V operating conditions                                                     | 69              |

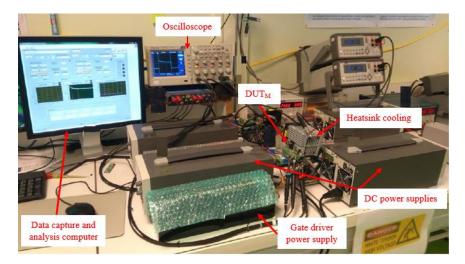

| Fig. 3.11: Switching bench platform and associated instruments.                                                                           | 70              |

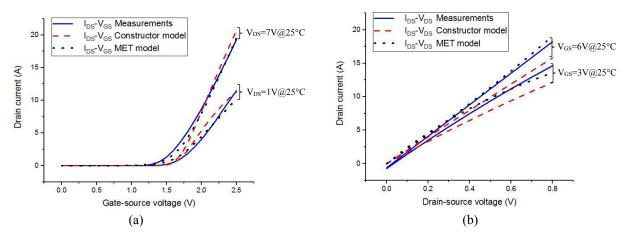

| Fig. 3.12: Comparison between measurements, Constructor model and MET model: (a) Transfer                                                 |                 |

| characteristics (b) Output characteristics                                                                                                | 71              |

| Fig. 3.13: Comparisons of Mean Relative Error between constructor model and MET model for both                                            | h               |

| transfer and output static characteristics                                                                                                | 72              |

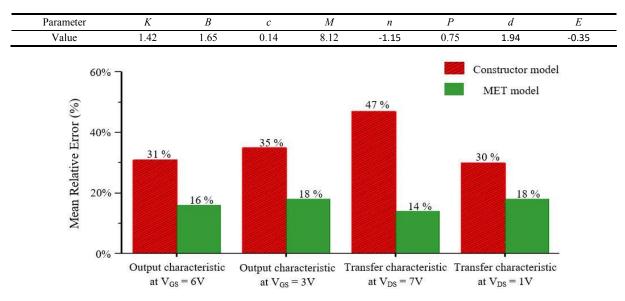

| Fig. 3.14: Comparisons of Mean Relative Error between MET model, constructor static model and                                             |                 |

| literature for the output characteristic at $V_{GS}$ = 3 V and 25 °C                                                                      | 72              |

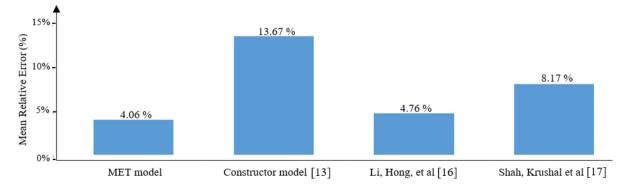

| Fig. 3.15: Comparisons between MET model (dot), constructor model (dashed) and measurements                                               |                 |

| (solid): (a) Transfer characteristic for $V_{DS}$ = 7 V at 55 °C and 115 °C; (b) Output characteristic for V                              | / <sub>GS</sub> |

| = 6 V at 55 °C and 115 °C                                                                                                                 | 73              |

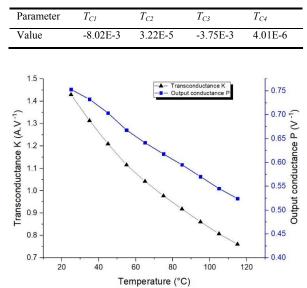

| Fig. 3.16: Evolution of the device parameters K and P when varying temperature from 25 °C to 115                                          |                 |

| °C                                                                                                                                        |                 |

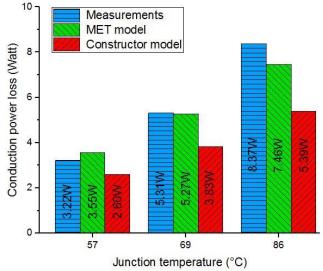

| Fig. 3.17: Comparisons of conduction power loss between measurements, MET model and construct                                             |                 |

| model for three values of TJ: 57 °C, 69 °C and 86 °C.                                                                                     |                 |

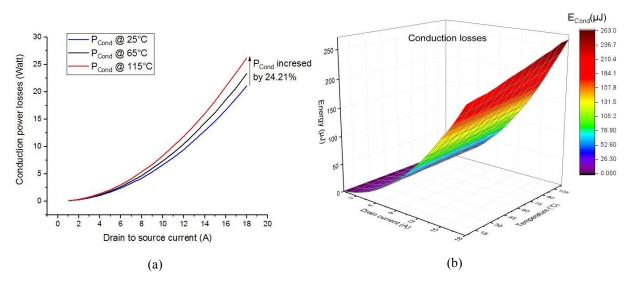

| Fig. 3.18: Conduction losses estimation: (a) power losses at three temperatures: 25 °C, 65 °C and 11                                      |                 |

| °C; (b) energy losses at $f = 50 \text{ kHz}$ , Duty-cycle = 50 %, $V_{DS} = 200 \text{ V}$ .                                             |                 |

| Fig. 3.19: C-V experimental setup: (a) CV bench; (b) detrapping setup.                                                                    |                 |

| Fig. 3.20: Measurement circuit for the C-V characteristics: (a) $C_{GS}$ - $V_{GS}$ ; (b) $C_{GD}$ - $V_{GD}$ ; (c) $C_{DS}$ - $V_{DS}$ . | 78              |

| Fig. 3.21: (a) Gate to source capacitance C <sub>GS</sub> ; (b) Derivative of C <sub>GS</sub> -V <sub>GS</sub> plot                       | 79              |

| <b>Fig. 3.22:</b> (a) C <sub>GS</sub> -V <sub>GS</sub> characteristics for various temperatures: 5°C, 45°C, 85°C and 115 °C. (b)          |                 |

| C <sub>GS(Max)</sub> as a versus temperature                                                                                              | 80              |

| <b>Fig. 3.23:</b> (a) C <sub>GD</sub> -V <sub>GD</sub> characteristics for various temperatures: 5°C, 45°C, 85°C and 115 °C. (b)          |                 |

| C <sub>GD(Max)</sub> as a versus temperature.                                                                                             |                 |

| Fig. 3.24: (a) $C_{DS}$ - $V_{DS}$ characteristics for various temperatures: 5°C, 45°C, 85°C and 115 °C. (b) $C_{D}$                      |                 |

| versus temperature at V <sub>DS</sub> equals 10 V                                                                                         | 82              |

| Fig. 3.25: (a) C-V-f measurements; (b) Measured C <sub>GS</sub> -V <sub>GS</sub> characteristics at 1 MHz and at room                     |                 |

| temperature. Solid curves correspond to the voltage sweep from negative to positive values of $V_{\text{GS}}$ a                           |                 |

| dashed curves correspond to the opposite sweep direction.                                                                                 | 83              |

| Fig. 3.26: C <sub>GS</sub> capacitance model parameters.                                                                                  | 84              |

| Fig. 3.27: Comparison between measured and modelled capacitances at 25 °C: (a) C <sub>GS</sub> -V <sub>GS</sub> ; (b) C <sub>GD</sub>     | )-              |

| $V_{GD}$ ; (c) $C_{DS}$ - $V_{DS}$                                                                                                        |                 |

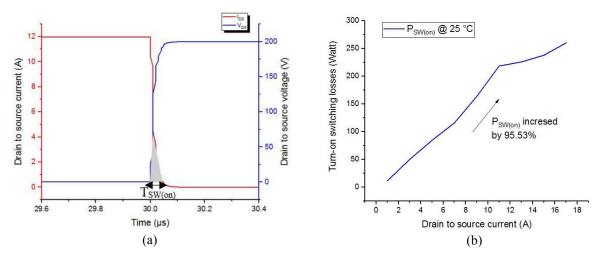

| Fig. 3.28: Turn-on switching losses estimation at 25 °C, $f = 50$ kHz, Duty-cycle = 50 % and $V_{DS} = 2$                                 | 200             |

| V: (a) switching times, (b) power losses.                                                                                                 |                 |

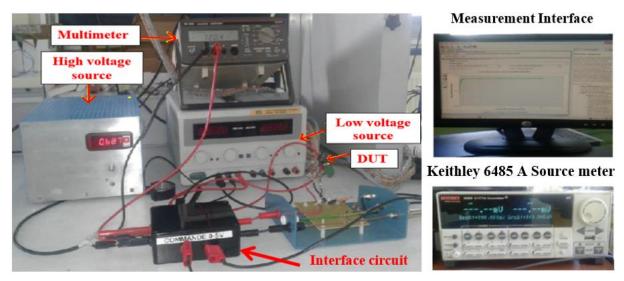

| Fig. 3.29: Leakage current measurement bench                                                                                              |                 |

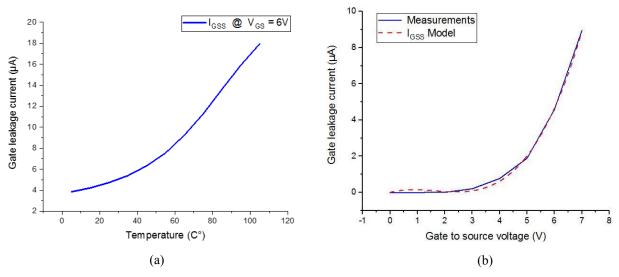

| Fig. 3.30: Gate leakage current: (a) temperature dependency at $V_{GS} = 6V$ ; (b) $I_{GSS}$ Model as a function                          |                 |

| of $V_{GS}$ at 25 °C.                                                                                                                     | 87              |

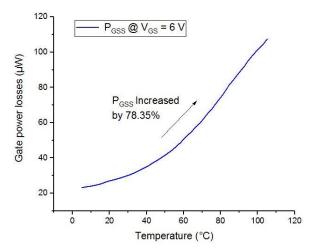

| Fig. 3.31: Gate power losses estimation versus temperature at $V_{GS} = 6 V_{}$                                                           |                 |

| Fig. 3.32: Solar energy application with a 30V/200V DC-DC converter stage                                                                 | 88              |

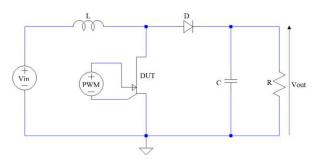

| Fig. 3.33: DC-DC boost converter, with L = 170 mH, C = 850 $\mu$ F and R = 20 $\Omega$ , at 50 kHz switching                                                                                     | ~ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| frequency, 30 V input voltage and 200 V output voltage                                                                                                                                           |   |

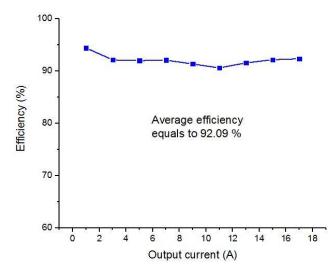

| <b>Fig. 3.34:</b> Efficiency estimation of a GaN HEMT 30 V/ 200 V DC-DC boot converter versus I <sub>out</sub> at 50 kHz and 25 °C.                                                              |   |

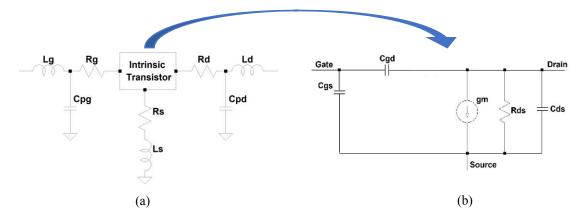

| <b>Fig. 4.1:</b> GaN HEMT package [9]: (a) extrinsic parameters, (b) intrinsic parameters                                                                                                        |   |

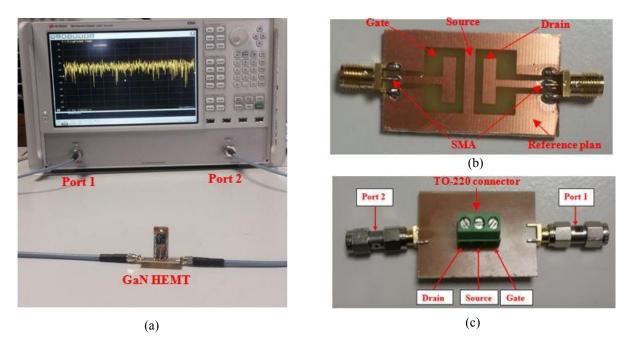

| <b>Fig. 4.2:</b> (a) VNA measurement setup for GaN HEMT; (b) DUT test fixture; (c) Test fixture using                                                                                            | , |

| TO-220 connector                                                                                                                                                                                 | 8 |

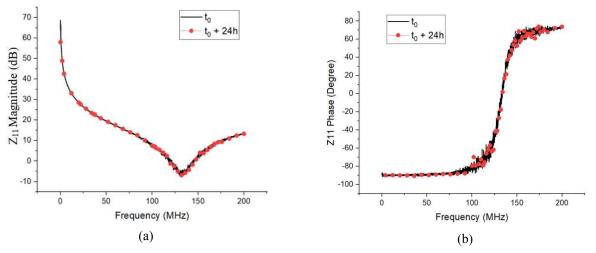

| <b>Fig. 4.3:</b> Measured GaN HEMT $Z_{11}$ coefficient before and after 24 hours VNA measurement session:                                                                                       |   |

| (a) Z <sub>11</sub> Magnitude and (b) Z <sub>11</sub> Phase                                                                                                                                      |   |

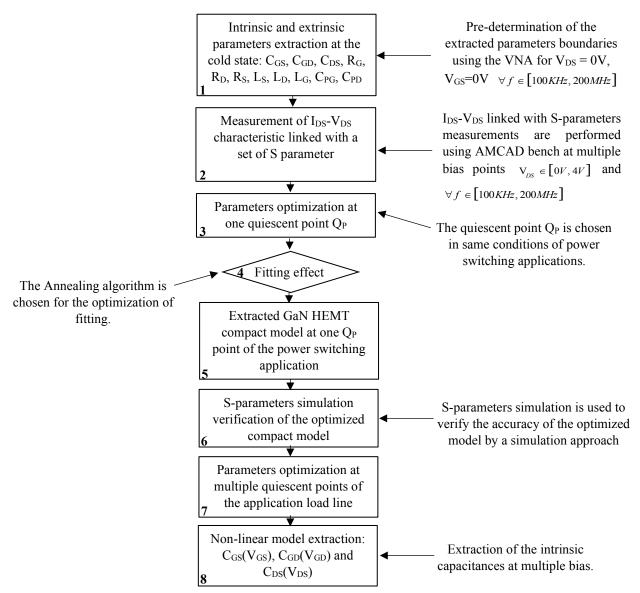

| Fig. 4.4. GaN HEMT small signal model extraction methodology                                                                                                                                     | 1 |

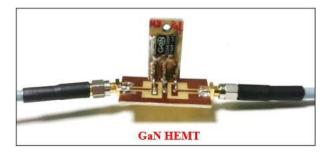

| Fig. 4.5: Tested 650 V / 30 A GaN HEMT 102                                                                                                                                                       | 2 |

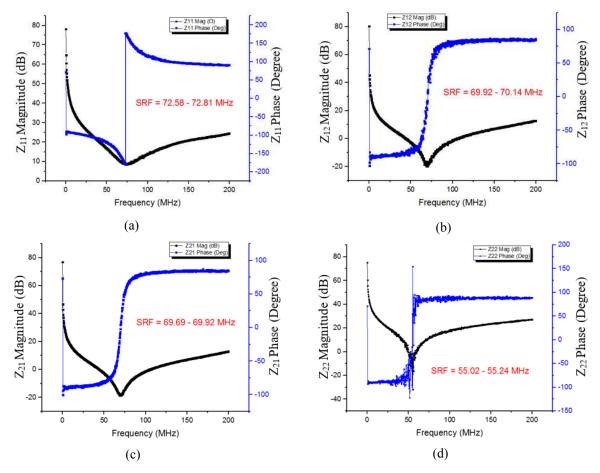

| <b>Fig. 4.6:</b> Frequency responses of the tested power GaN HEMT for 100 kHz $\leq$ f $\leq$ 200 MHz: (a) Z <sub>11</sub> ,                                                                     |   |

| (b) $Z_{12}$ , (c) $Z_{21}$ and (d) $Z_{22}$ Magnitudes and phases                                                                                                                               |   |

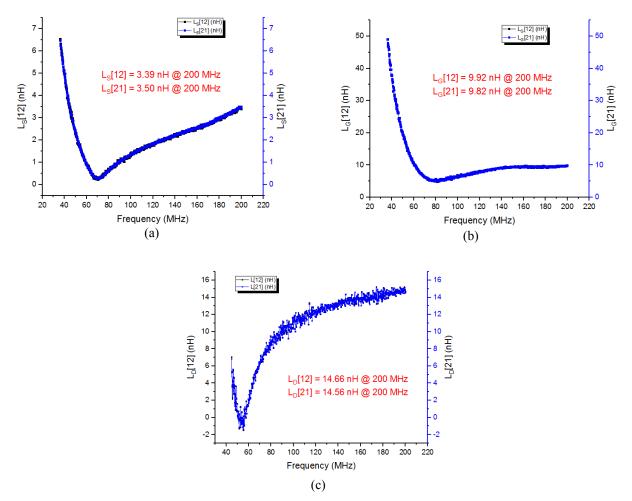

| Fig. 4.7: Equivalent circuit of the DUT at high frequency [27] 103                                                                                                                               | 3 |

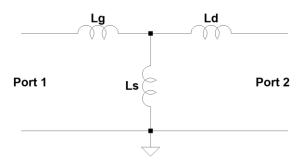

| <b>Fig. 4.8:</b> Inductances extraction of the tested power GaN HEMT: (a) L <sub>S</sub> , (b) L <sub>G</sub> and (c) L <sub>D</sub> frequency responses.                                        | 4 |

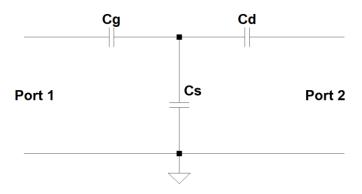

| <b>Fig. 4.9:</b> Equivalent circuit of the DUT at high frequency using star connection [30]: C <sub>G</sub> , C <sub>S</sub> and C <sub>D</sub> .                                                |   |

|                                                                                                                                                                                                  | 5 |

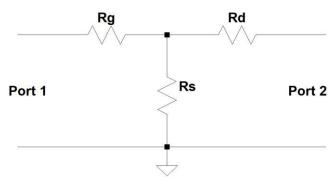

| Fig. 4.10: Delta connection of the extracted capacitances [31]: C <sub>GS</sub> , C <sub>GD</sub> and C <sub>DS</sub> 106                                                                        | 6 |

| Fig. 4.11: Capacitances extraction of the tested power GaN HEMT: (a) $C_{GS}$ , (b) $C_{GD}$ and $C_{DS}$                                                                                        |   |

| frequency responses                                                                                                                                                                              |   |

| Fig. 4.12 : Equivalent circuit of the DUT at SRF frequency [34]: R <sub>G</sub> , R <sub>S</sub> , R <sub>D</sub> 107                                                                            |   |

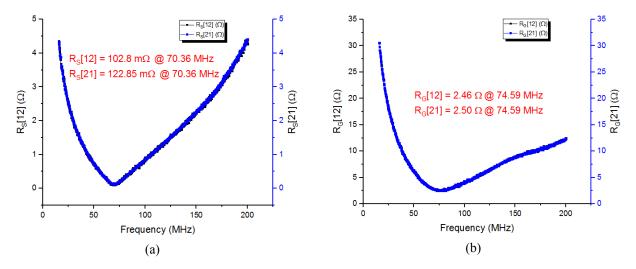

| <b>Fig. 4.13:</b> Resistances extraction of the tested power GaN HEMT: (a) R <sub>S</sub> , (b) R <sub>G</sub> and (c) R <sub>D</sub> frequency                                                  |   |

| 109                                                                                                                                                                                              |   |

| Fig. 4.14: Tested 1200 V SiC MOSFET                                                                                                                                                              |   |

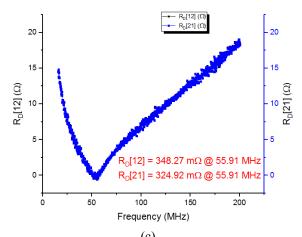

| Fig. 4.15: GaN HEMT load line I <sub>DS</sub> -V <sub>DS</sub> characteristic                                                                                                                    |   |

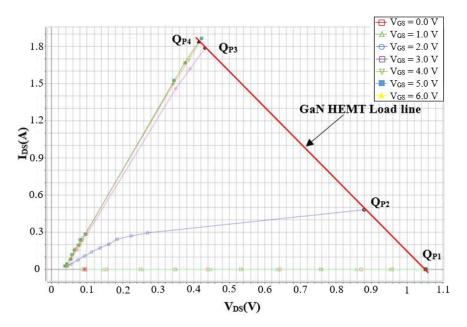

| Fig. 4.16: Multiple bias S-parameters bench                                                                                                                                                      |   |

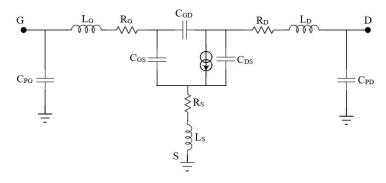

| Fig. 4.17: Small signal equivalent circuit model of GaN HEMTs [51]                                                                                                                               |   |

| <b>Fig. 4.18:</b> Evolution of GaN HEMT $C_{GS}$ intrinsic capacitance                                                                                                                           |   |

| <b>Fig. 4.19:</b> S-parameter simulation setup at $Q_{P4}$ bias point                                                                                                                            | 4 |

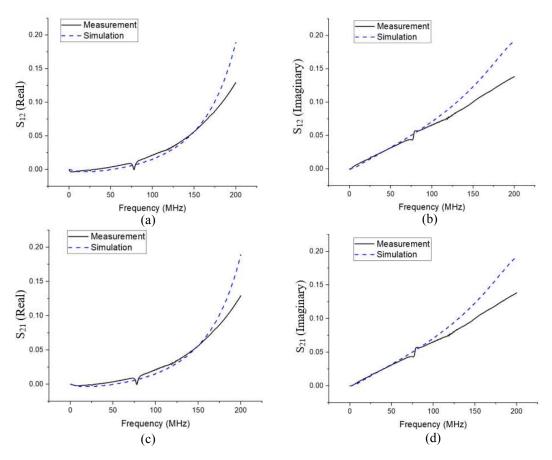

| (b) $S_{11}$ imaginary, (c) $S_{22}$ Real, (d) $S_{22}$ imaginary                                                                                                                                | Δ |

| <b>Fig. 4.21</b> : Optimized $S_{12}$ and $S_{21}$ parameters for the tested GaN HEMT at $Q_{P4}$ bias point: (a) $S_{12}$ Real,                                                                 |   |

| (b) $S_{12}$ imaginary, (c) $S_{21}$ Real, (d) $S_{21}$ imaginary. 115                                                                                                                           |   |

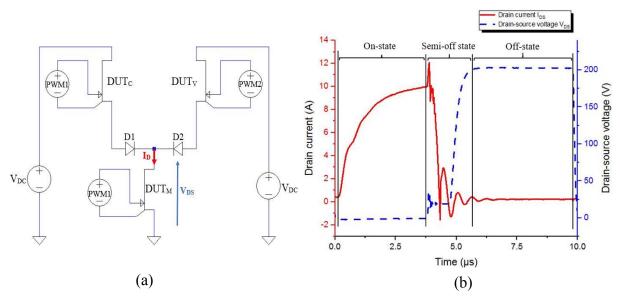

| <b>Fig. 5.1.</b> (a) Aging switching bench; (b) $I_D$ and $V_{DS}$ waveforms of DUT <sub>M</sub> over one period for switching                                                                   |   |

| conditions: 100 kHz, duty-cycle = 50 %, and 10 A / 200 V operating conditions. $122$                                                                                                             |   |

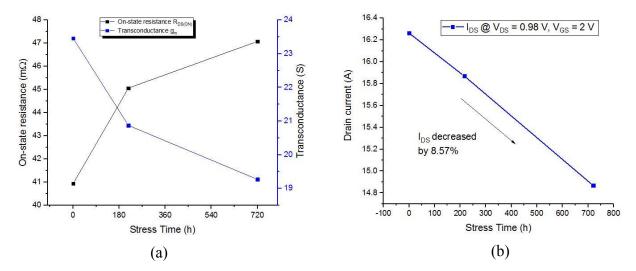

| <b>Fig. 5.2.</b> Evolution of the static parameters during 720 h of aging: (a) $R_{DS(ON)}$ and $g_m$ ; (b) $I_{DS}$ at $V_{GS} = 6$ V and $V_{DS} = 0.76$ V.                                    | 5 |

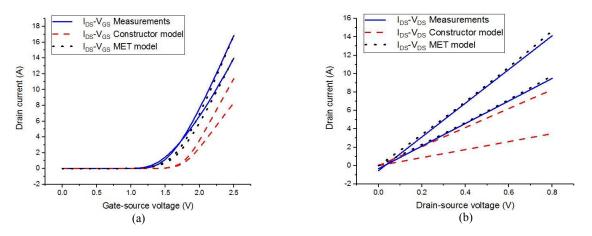

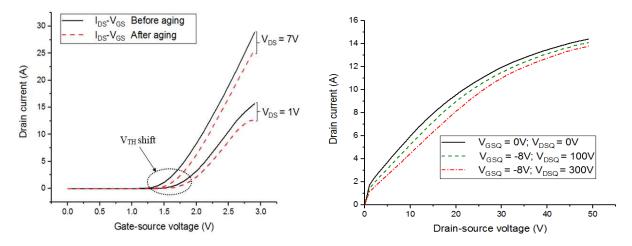

| <b>Fig. 5.3.</b> (a) $I_{DS}$ - $V_{GS}$ characteristics measured at $V_{DS}$ equals to 1V and 7V; (b) $I_{DS}$ - $V_{DS}$ characteristics for various quiescent bias points at 25°C in the dark |   |

| <b>Fig. 5.4.</b> Experiment and model: (a) Output characteristics $I_{DS}$ - $V_{DS}$ ; (b) transfer characteristics $I_{DS}$ - $V_{GS}$                                                         |   |

| before and after 720 h of aging                                                                                                                                                                  |   |

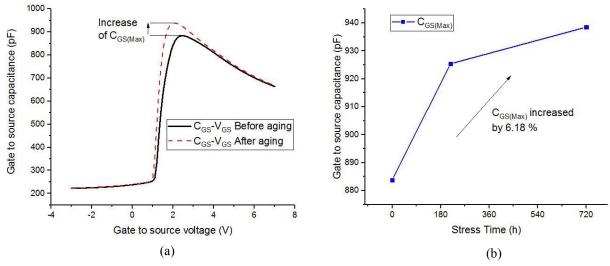

| Fig. 5.5: (a) Evolution of $C_{GS}$ - $V_{GS}$ characteristic before and after aging; (b) Evolution of $C_{GS(Max)}$                                                                             |   |

| during aging                                                                                                                                                                                     | 6 |

| Fig. 5.6: (a) Evolution of $C_{GD}$ -V <sub>GD</sub> characteristic before and after aging; (b) Evolution of $C_{GD(Max)}$                                                                       |   |

| during aging                                                                                                                                                                                     |   |

| Fig. 5.7: (a) Evolution of $C_{GD}$ - $V_{GD}$ characteristic before and after aging; (b) Evolution of $C_{DS}$ @ $V_{DS}$ =                                                                     |   |

| 10 V during aging                                                                                                                                                                                | 8 |

|                                                                                                                                                                                                  |   |

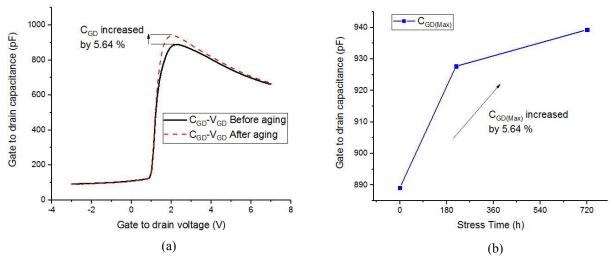

| Fig. 5.8: Experiment and model before and after 720 h of aging: (a) $C_{GS}$ - $V_{GS}$ characteristics; (b) $C_{GD}$ -                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{GD}$ characteristics; (c) $C_{DS}$ - $V_{DS}$ characteristics                                                                                                                |

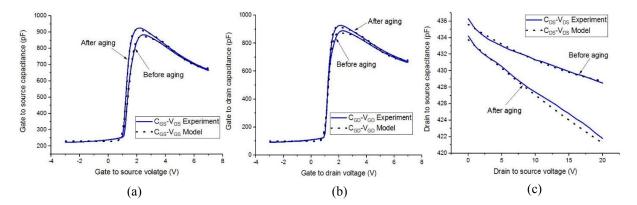

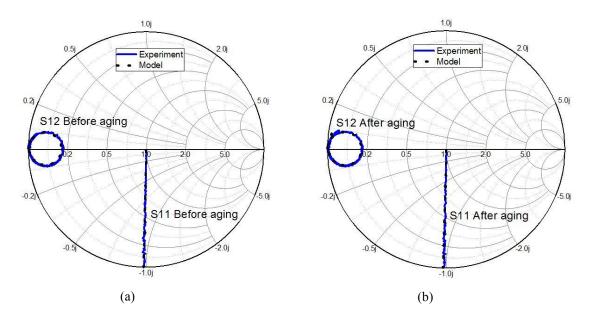

| <b>Fig. 5.9:</b> Evolution of the S parameters during 720 h of aging: (a) S <sub>11</sub> Magnitude, (b) S <sub>11</sub> Phase,                                                  |

| (c) S <sub>12</sub> Magnitude, (d) S <sub>12</sub> Phase, (e) S <sub>21</sub> Magnitude, (f) S <sub>21</sub> Phase, (g) S <sub>22</sub> Magnitude, (h) S <sub>22</sub> Phase.130 |

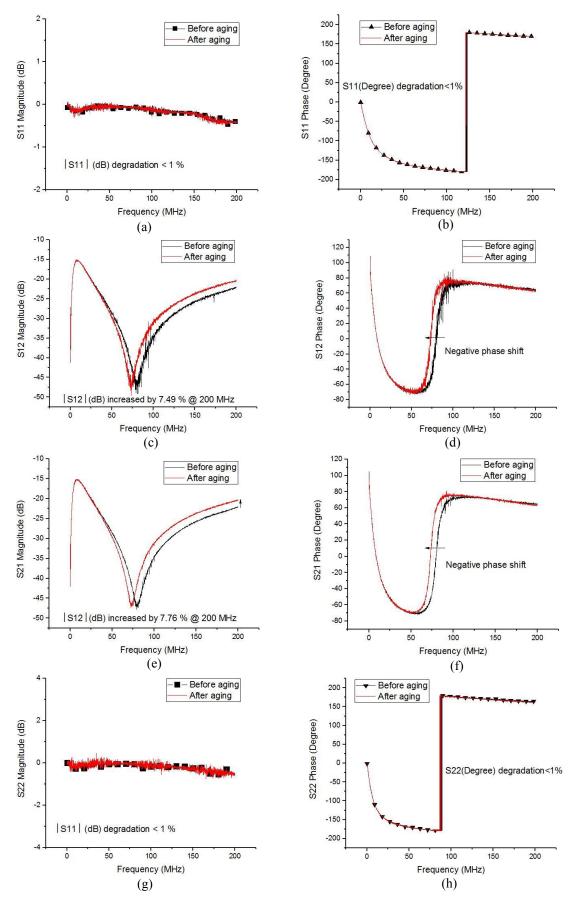

| Fig. 5.10: Experiment and model of S11 and S12 parameters: (a) Before aging; (b) after 720 h of                                                                                  |

| aging                                                                                                                                                                            |

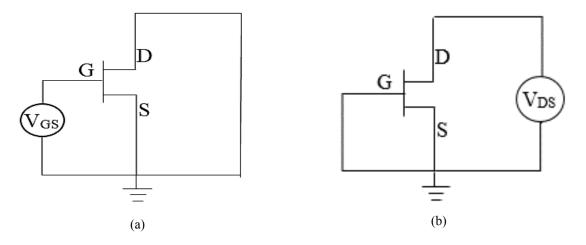

| Fig. 5.11: (a) On-state stepp stress bench, (b) Off-state step stress bench [73]                                                                                                 |

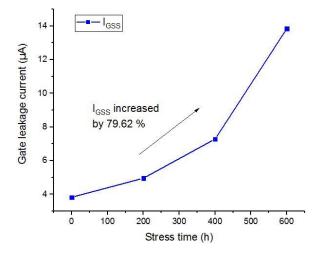

| Fig. 5.12: Evolution of $I_{GSS}$ current at $V_{GS} = 6$ V during on-state stress                                                                                               |

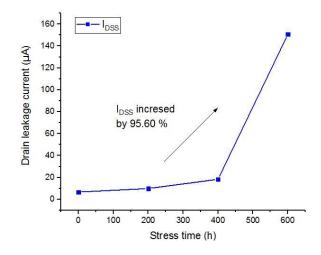

| Fig. 5.13: Evolution of $I_{DSS}$ current at $V_{DS} = 200$ V during off-state stress                                                                                            |

| Fig. 5.14: Wind energy application with a 200 V/ 24 V DC-DC converter stage for electric vehicle                                                                                 |

| charging stations                                                                                                                                                                |

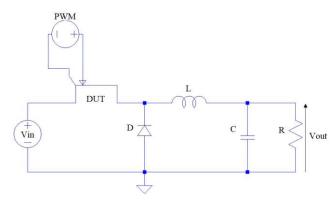

| <b>Fig. 5.15:</b> DC-DC buck converter, with L = 170 mH, C = 850 $\mu$ F and R = 20 $\Omega$ , at 100 kHz switching                                                              |

| frequency, 200 V input voltage and 24 V output voltage                                                                                                                           |

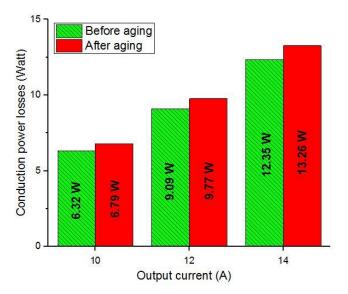

| Fig. 5.16. Conduction power losses of DC-DC buck converter before and after 720 h of aging for                                                                                   |

| different output current: 10 A, 12 A and 14 A                                                                                                                                    |

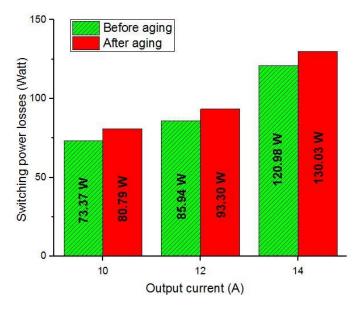

| Fig. 5.17: Switching power losses of DC-DC buck converter before and after 720 h of aging for                                                                                    |

| different output current: 10 A, 12 A and 14 A                                                                                                                                    |

| Fig. 5.18: Estimated gate power losses before and after 720 h of on-state step stress aging 140                                                                                  |

| Fig. 5.19: Estimated gate power losses before and after 720 h of off-state step stress aging                                                                                     |

| Fig. 5.20: GaN HEMT total power losses of DC-DC buck converter before and after 720 h of aging                                                                                   |

| for various output current: 10 A, 12 A and 14 A 141                                                                                                                              |

# List of tables

| Table 2.1: Comparison of the investigated transistors characteristics of GaN HEMT and SiC                                                            |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| MOSFET [24-25]                                                                                                                                       | 36  |

| <b>Table 2.2:</b> Simulated switching time T <sub>ON</sub> and T <sub>OFF</sub> of GaN HEMT (GS66508P) and SiC MOSFET (SCT2120AF).                   | 28  |

| Table 2.3: Material properties of Si, GaN and SiC [31].                                                                                              |     |

| Table 2.3: Material properties of Si, GaN and SiC [51].         Table 2.4: GaN HEMT substrate comparison: Si, SiC and GaN.                           |     |

| Table 2.4: Gain Field 1 substate comparison. Si, SiC and Gain.         Table 2.5: Comparison of Gan HEMT structures.                                 |     |

| Table 2.5: Comparison of Gal HEMT structures.         Table 2.6: The most critical failure mode and effects analysis of the GaN HEMT.                |     |

|                                                                                                                                                      |     |

| Table 2.7: Comparison of available GaN SPICE models [97].         Table 2.1: LX makes time in a                                                      |     |

| Table 3.1: I-V pulse timing.                                                                                                                         |     |

| Table 3.2: Static parameters comparison between measurements, constructor model and MET mode                                                         |     |

| Table 3.3: Extracted MET model parameters at 25°C.                                                                                                   |     |

| Table 3.4: Extracted MET thermal model temperature coefficients.                                                                                     |     |

| <b>Table 3.5:</b> Switching conditions applied to $DUT_M$ at: $V_{DS(OFF)} = 24$ V, f = 50 kHz and Duty-cycle = 1                                    |     |

| %                                                                                                                                                    |     |

| Table 3.6: Measurements, MET model and constructor model comparisons of conduction power                                                             |     |

| losses                                                                                                                                               |     |

| Table 3.7: Extracted parameters of the estimated conduction power losses $P_{Cond}(I_{DS},T)$ .                                                      |     |

| Table 3.8: Extracted values of CGS, CGD and CDS at 25°C.                                                                                             |     |

| Table 3.9: Extracted I <sub>GSS</sub> model parameters at 25°C.                                                                                      | 87  |

| <b>Table 3.10 :</b> Total losses in DC-DC boost converter with GaN HEMT at 25°C and $I_{out} = 10 A$                                                 | 90  |

| Table 4.1: Comparison between impedance meter and S-parameter measurements of the tested                                                             |     |

| passive component at 1 MHz: capacitance, inductance and resistance.                                                                                  | 99  |

| Table 4.2: Self resonance frequency of the tested power GaN HEMT 1                                                                                   | 103 |

| Table 4.3: GaN HEMT extracted parasitic inductances Ls, LG and LD at 200 MHz 1                                                                       | 105 |

| Table 4.4: GaN HEMT extracted parasitic capacitances C <sub>GS</sub> , C <sub>GD</sub> and C <sub>DS</sub> at 1 MHz1                                 | 107 |

| Table 4.5: GaN HEMT extracted parasitic resistances R <sub>s</sub> , R <sub>G</sub> and R <sub>D</sub> at SRF frequency1                             | 109 |

| Table 4.6: GaN HEMT extracted pad parasitic capacitances C <sub>pg</sub> and C <sub>pd</sub> at 1 MHz Error! Bookma                                  | ark |

| not defined.                                                                                                                                         |     |

| Table 4.7: Tested SiC MOSFET parasitic elements extraction results summarization                                                                     | 10  |

| <b>Table 4.8:</b> Load line bias points $Q_{P1}$ , $Q_{P2}$ , $Q_{P3}$ and $Q_{P4}$                                                                  |     |

| Table 4.9: linear model parameters of the GaN HEMT at multiple quiescent points: QP1, QP2, QP3 and                                                   | nd  |

|                                                                                                                                                      | 12  |

| Table 4.10: Comparison between measured and simulated extracted parasitic elements of the GaN         VID (T) (0) (0) (0) (0) (0) (0) (0) (0) (0) (0 |     |

| HEMT at Q <sub>P4</sub> bias point                                                                                                                   |     |

| Table 5.1: Applied switching conditions on DUT <sub>M</sub> .       1                                                                                |     |

| Table 5.2: 720 hours aging results for DUT <sub>M</sub>                                                                                              |     |

| <b>Table 5.3:</b> Extracted Static Model Parameters at 25 °C for the Fresh State ( $t = 0$ ) and Aged State ( $t = 0$ )                              |     |

| 720 h) 1                                                                                                                                             |     |

| <b>Table 5.4:</b> Extracted values of $C_{GS}$ , $C_{GD}$ and $C_{DS}$ model before and after 720 h of aging.1                                       |     |

| Table 5.5: Extracted values of parasitic parameters before and after 720 h of aging                                                                  |     |

| Table 5.6: Failure mode and effects analysis (FMEA) of the GaN HEMT during 1000 h of step stress                                                     |     |

| aging1                                                                                                                                               |     |

| Table 5.7: DC-DC buck converter conduction power losses, before and after 720 h of aging for output                                                  |     |

| current: 10 A, 12 A and 14 A 1                                                                                                                       | 138 |

Table 5.8: Total losses in DC-DC buck converter with GaN HEMT at 25°C, 10 A. ..... 141

# List of symbols

C: Capacitance of the supercapacitor [F] C<sub>0</sub>: Initial value of C [F] ESR: Equivalent Series Resistance of the supercapacitor  $[\Omega]$ ESR0: Initial value of ESR  $[\Omega]$ Ciss: Input capacitance [F] Coss: Output capacitance [F] Crss: Reverse transfer capacitance [F] C<sub>GS</sub>: Gate to source capacitance [F] C<sub>GD</sub>: Gate to drain capacitance [F] C<sub>DS</sub>: Drain to source capacitance [F] D: Duty cycle DC: Direct current fs: Switching frequency [Hz] I<sub>DS</sub>: Drain to source current [A] I<sub>GSS</sub>: Gate leakage current [A] I<sub>DSS</sub>: Drain leakage current [A] I<sub>OUT</sub>: Inverter output current [A] L: Output filter inductance [H] P<sub>GaN</sub>, P<sub>SiC</sub>, P<sub>Si</sub>: Device power losses [Watt] P<sub>g</sub>: Gate power losses [Watt] Q<sub>g</sub>: Gate charge [C]  $R_{DS(on)}$ : Drain to source on-state resistance [ $\Omega$ ] g<sub>m</sub>: Transconductance [S] n<sub>s</sub>: 2DEG carrier density [cm] P<sub>PZ</sub>: Piezoelectric polarization [C.cm<sup>-2</sup>]  $P_{SP}$ : Spontaneous polarization [C.cm<sup>-2</sup>] q: elementary charge [C]

$\sigma_{2DEG}$ : 2DEG charge density [cm<sup>-2</sup>]  $\sigma_{AIGaN/GaN}$ : Polarization charge density at the interface [cm<sup>-2</sup>]  $\sigma_{SURF}$ : Surface charge density [cm<sup>-2</sup>]  $T_a$ : Ambient temperature [°C]  $T_j$ : Junction temperature [°C]  $V_{GS}$ : Gate to source voltage [V]  $V_{DS}$ : Drain to source voltage [V]  $V_{TH}$ : Threshold voltage [V]

# List of acronyms

2D: Two dimensions 2DEG: Two-dimensional electron gas GaN: Gallium nitride AlGaN: Aluminum gallium nitride HEMT: High-electron-mobility transistor III-V: Material being formed by elements from the 3<sup>rd</sup> and 5<sup>th</sup> column of the table of elements DUT: Device under test IGBT: Insulated-gate bipolar transistor JFET: Junction gate field-effect transistor MOSFET: Metal oxide semiconductor field-effect transistor Si: Silicon SiC: Silicon carbide WBG: Wide-bandgap SPICE: Simulation Program with Integrated Circuit Emphasis SOA: Safe Operating Area IGBT: Insulated-gate bipolar transistor JFET: Junction gate field-effect transistor MOSFET: Metal oxide semiconductor field-effect transistor FMECA: Failure Modes, Effects and Criticality Analysis PWM: Pule width modulation **RF:** Radio frequency

# Abstract

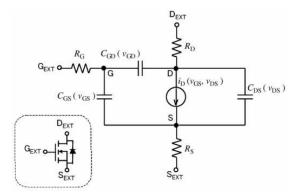

In this thesis, we have studied the impact of aging the GaN HEMT on the power converter efficiency. For that, we have developed an experimental methodology to estimate the power losses of the GaN HEMT for switching circuit applications. The estimation of the power losses is performed by a SPICE simulation approach using a non-segmented Electro-thermal model. The developed methodology enables the estimation of both the static and dynamic power losses in power converter applications.

Additionally, we have implemented an accurate method for extracting both the intrinsic and extrinsic elements of the GaN HEMT power transistors. The experimental setup includes: Vector Network Analyzer, IVCAD measurement modules, drain and gate bias tees. The developed S-parameter setup enables the extraction of the parasitic elements of the power GaN HEMT at multiple bias conditions. The Annealing algorithm is chosen for the optimization of the model parameters. This method enables to study the effect of aging on both the parasitic elements of the GaN HEMT.

Moreover, we have investigated the aging of a 650 V, 30 A GaN HEMT power transistor under operational switching conditions. The switching stress respects the Safe Operation Area (SOA) of the tested transistor. Various types of stress are performed, such as: continuous operational switching stress, on-state, off-state and frequency step stresses. The aging campaigns lasted 1000 h and was carried out through a developed switching application with high power efficiency. During aging, several electrical characterizations were performed for monitoring both the dynamic and static characteristics of the device under test, including: pulsed I-V, leakage current, C-V, S-parameters, temporal switching measurements. The effects of this degradation on power converters are studied for both the static and dynamic characteristics of the aged GaN HEMT. Using the developed SPICE model, the conduction power losses, switching power losses, leakage current gate and drain power losses are estimated before and after of aging. The accuracy and consistent convergence of the developed SPICE model provide a good way to investigate the reliability of GaN HEMTs by simulation.

Keywords: GaN, HEMT, S-parameter, DC-DC power converters, aging, SOA, power losses.

## Résumé

Ce travail de recherche s'inscrit dans la problématique de l'efficacité énergétique des convertisseurs de puissance à base des transistors GaN-HEMTs, cette thématique représente une importance primordiale pour des domaines tels que les transports, les énergies renouvelables ou encore les télécommunications.

Les travaux développés dans cette thèse se déroulent en cotutelle entre l'Université Abdelmalek Essaadi de Tétouan-Maroc et l'Université de Rouen Normandie-France, ce travail représente un intérêt réel pour les industriels internationaux et pour l'agence marocaine pour l'énergie durable au Maroc, puisqu'il traite une problématique actuelle qui est celle de la fiabilité et l'efficacité énergétique des convertisseurs de puissance. Notre travail s'inscrit donc dans le développement de la technologie électronique dans le cadre d'un partenariat Maroc-France.

Actuellement, les composants de puissance de nouvelle génération de technologie GaN (nitrure de gallium) ou SiC (carbure de silicium) remplacent peu à peu les technologies usuelles à base silicium. Des modèles électriques rencontrés en littérature sont adaptés à ces composants, cependant leur intégration dans les systèmes de conversion d'énergie nécessite de connaitre avec précision l'évolution de ces modèles face au stress subi, en premier lieu thermique et électrique.

Ce travail de recherche consiste dans un premier temps à étudier l'impact des dégradations sur les éléments du modèle du composant à l'étude. Puis, dans un second temps, à partir du modèle, nous analysons l'impact des dégradations sur les performances d'un convertisseur de puissance.

Concernant les applications mobiles alimentées par batterie comme les véhicules électriques, les avions « plus électriques » ou les applications photovoltaïques, une haute efficacité énergétique combinée à un poids faible et une conception compacte sont des exigences clés.

En utilisant des semi-conducteurs à grand gap comme le GaN, il est possible de travailler avec des fréquences de commutation plus élevées. Par conséquent, le volume et le poids des composants magnétiques et des condensateurs peuvent être réduits de manière significative.

17

En raison de leurs caractéristiques, les composants de technologie GaN constituent un choix crucial pour les convertisseurs DC-DC fonctionnants à des fréquences de commutation allant au-delà de quelques centaines de100 kHz jusqu'au MHz.

Malgré les nombreux avantages qu'apporte la technologie GaN comparée par la technologie Si, la fiabilité doit encore être démontrée. Cela est dû d'une part à l'évolution continue du processus technologique adopté, et d'autre part en raison du manque d'information concernant les modes et les mécanismes de défaillance.

La contribution de ce travail de recherche se situe essentiellement au niveau de l'étude de l'impact du vieillissement d'un composant GaN HEMT commercial sur l'efficacité énergétique des convertisseurs DC-DC. L'étude consiste à la réalisation des tests de vieillissement en commutation dans des conditions opérationnelles de fonctionnement. Les pertes dynamiques et statiques du composant sont estimées avant et après les tests du vieillissement. Par conséquent, l'impact du vieillissement sur le rendement du convertisseur DC-DC est déterminé.

Afin de réaliser ce travail, le banc de mesure des caractéristiques courant-tension (I-V) pulsé est exploité afin d'estimer les pertes de puissance de conduction à l'état passant d'un composant GaN HEMT commercial. La caractérisation I-V en mode pulsé permet de placer le transistor sous test dans un mode de fonctionnement très proche de celui de son utilisation réelle.

La caractérisation expérimentale constitue un atout indéniable pour réussir ce projet de thèse. A ce sujet, le banc de mesure des caractéristiques capacité-tension (C-V) est exploité afin d'estimer les pertes de commutation du GaN HEMT.

La technologie des transistors GaN HEMTs représente une importance primordiale pour les applications de convertisseurs de puissance. Cependant, comme toute technologie émergente, la question de la fiabilité des transistors GaN HEMTs s'impose, car il y a peu de retour d'expérience sur cette technologie et une instabilité sur la maîtrise des processus de fabrication, notre étude s'intègre dans cette démarche de fiabilité.

Pour aborder cette problématique, nous avons réalisé des tests de vieillissement en commutation dans des conditions opérationnelles. Le comportement statique et dynamique du transistor est impacté par les dégradations physiques causées par le stress thermique et électrique.

Les objectifs de cette thèse sont :

- Étudier le vieillissement du transistor GaN HEMT 650V, 30A en conditions opérationnelles de fonctionnement.

- Réaliser plusieurs campagnes de vieillissement dans diverses conditions opérationnelles.

- Suivre l'évolution des caractéristiques dynamiques et statiques du transistor de test pendant 1000 h de vieillissement.

- Étudier les indicateurs de défaillance du GaN HEMT à partir des caractérisations expérimentales et comparer les résultats obtenus avec la littérature.

- Pour aider à répondre à ces objectifs, mettre en place au sein du laboratoire un banc expérimental d'extraction automatique des éléments parasites de transistors de puissance en utilisant des paramètres S à multiples points de polarisation.

- Mettre en œuvre une méthodologie expérimentale de mesure des caractéristiques C-V des transistors GaN HEMT.

- Concevoir un modèle SPICE précis de GaN HEMT de puissance pour les applications de convertisseurs de puissance.

- Identifier l'impact du vieillissement du GaN HEMT sur l'efficacité des convertisseurs de puissance. Ceci est d'un très grand intérêt pour les concepteurs de circuits de commutation, car il est alors possible de prendre en compte les effets de la dégradation des transistors GaN de puissance sur leurs systèmes.

Pour répondre aux objectifs, cette thèse est organisée en six chapitres :

Le chapitre 1 présente l'introduction générale. Dans ce chapitre, les challenges majeurs de la technologie GaN HEMT dans les applications de convertisseurs de puissance sont présentés. Aussi, les objectifs de ce projet de thèse sont définis et une description du plan de ce rapport de thèse est donnée.

Le chapitre 2 présente l'état de l'art des transistors de puissance GaN HEMT. Une étude du marché des convertisseurs du puissance est présentée afin de justifier le besoin des nouvelles technologies de transistors à base du GaN. De plus, ce chapitre décrit les propriétés physiques du matériau GaN ainsi que les avantages et les principales applications du GaN HEMT. Les limites des composants au Silicium et le besoin de technologies émergentes telles que : le GaN

et le SiC sont analysées dans ce chapitre. Les avantages et les principales applications des GaN HEMTs sont présentés.

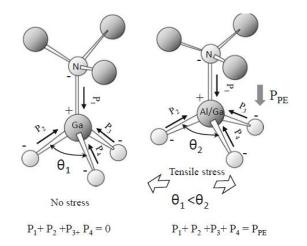

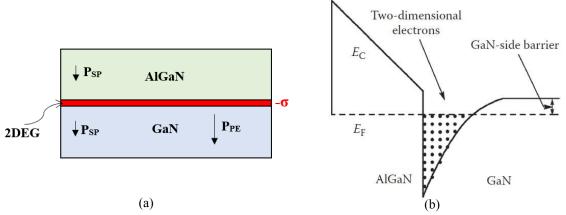

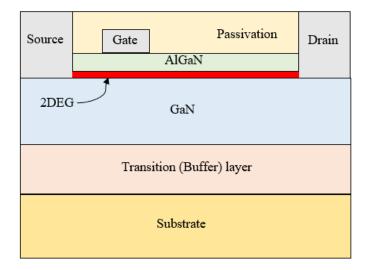

Ensuite, une comparaison des performances statiques et dynamiques entre le GaN et son concurrent SiC est développée en utilisant une approche de simulation SPICE. Cette étude est suivie par la présentation des propriétés physiques du matériau GaN. La formation du gaz d'électrons bidimensionnel (2DEG) est expliquée sur la base de l'interaction d'une couche de GaN avec une couche mince de l'AlGaN.

Une description de la structure physique GaN HEMT est développée. Une étude comparative des différentes technologies du GaN HEMTs est présentée. De même, les différentes modes de défaillance du GaN HEMT dans des conditions de commutation sont synthétisées suivant une analyse AMDEC. En outre, les diverses techniques de vieillissement pour évaluer la fiabilité des GaN HEMT de puissance sont discutées. Aussi, pour l'estimation des pertes du puissance du GaN HEMT selon une approche de simulation, plusieurs modèles du GaN HEMT sont comparés aux données issues de la littérature.

Le chapitre 3 présente une méthodologie complète pour l'estimation des pertes de puissance du GaN HEMT basée sur des mesures expérimentales. Le banc de commutation et les bancs de mesure I-V et C-V sont présentés. Les caractérisations I-V pulsé, C-V et le courant de fuite sont réalisées à différentes températures variant de 5 ° C à 115 ° C par pas de 10 ° C. L'effet de la température sur les caractéristiques statiques et dynamiques du GaN HEMT est étudié et comparé aux données présentes dans la littérature. L'effet de la fréquence sur les mesures C-V est étudié.

Le modèle SPICE choisi pour le GaN HEMT présente des faibles erreurs par rapport aux mesures expérimentales. Une étude comparative du modèle électrothermique utilisé avec d'autres modèles de la littérature est réalisée. Le modèle utilisé montre une bonne convergence avec les mesures expérimentales. Aussi, le modèle prend en considération l'effet de la température ce qui permet l'estimation des pertes de puissances avec une grande précision.

Les pertes de puissance du transistor sous test sont estimées sur la base d'une approche de simulation SPICE pour les applications de convertisseur de puissance. L'évolution des pertes de conduction et de commutation est modélisée en fonction de la température variant entre 5°C et 115 °C et pour un courant de sortie variant de 0 à 20A.

Sur cette base, nous avons construit un modèle précis de pertes de puissance du GaN HEMT basé sur des mesures expérimentales. Le rendement d'un convertisseur de puissance DC-DC 30 V / 200 V à base du GaN HEMT est estimé pour une application d'énergie solaire. La méthodologie proposée pour l'estimation des pertes de puissance sera exploitée dans le chapitre 5 pour étudier l'impact du vieillissement du GaN HEMT en condition de commutation opérationnelle sur le rendement des convertisseurs de puissance.

Le chapitre 4 présente une méthodologie expérimentale pour extraction des éléments intrinsèques et extrinsèques du GaN HEMT de puissance sur une large gamme de fréquences : de 100 kHz à 200 MHz par un pas de 100 kHz. La méthodologie de mesure des paramètres S est vérifiée sur des composants passifs, tels que : un condensateur, une inductance, une résistance et sur des composants actifs, comme : les transistors GaN HEMT et SiC MOSFET.

Après description de la procédure de calibration, l'étude de la répétabilité des mesures est effectuée. Ensuite, la mesure des résistances d'accès et des inductances ainsi que des capacités est présentée. La mesure des paramètres S est effectuée sur le GaN HEMT à la fois à l'état froid et à de multiples points de polarisation.

Le banc de mesure des paramètres S réalisé permet l'extraction automatique des paramètres parasites d'un transistor à multiples points de polarisations et utilisant l'algorithme d'optimisation « Annealing ».

La modélisation des éléments parasites de GaN HEMT est donc réalisée en utilisant l'approche de simulation des paramètres S. L'extraction des éléments parasites du GaN HEMT est réalisée avec une grande précision. Cette méthode est utilisée dans le chapitre 5 pour étudier l'effet du vieillissement du GaN HEMT dans des conditions de commutation opérationnelle sur les éléments parasites du GaN HEMT.

Dans le chapitre 5, nous présentons les effets du vieillissement du transistor de puissance GaN HEMT dans des conditions de commutation opérationnelles à fort courant et à haute tension. De telles études sont d'une grande importance, car le GaN HEMT est soumis à des conditions similaires à ce qui serait vécu dans une application réelle de convertisseurs de puissance.

De plus, pour classifier les mécanismes de dégradation du GaN HEMT pour les applications de convertisseur de puissance, nous avons réalisé plusieurs campagnes de vieillissement, à savoir : stress en commutation continue, step-stress sur la grille, sur le drain et en fréquence de commutation.

Aussi, une analyse des modes de défaillance et de leurs effets (AMDEC) du GaN HEMT pendant 1000 h de vieillissement en commutation est présentée. Au cours des campagnes de vieillissement, nous avons surveillé les changements des caractéristiques I-V, C-V et des paramètres S. Les caractéristiques électriques statiques et dynamiques du GaN HEMT sont mesurées en fonction du temps de stress et sont modélisées. L'impact du vieillissement sur l'efficacité énergétique des convertisseurs de puissance à base du GaN HEMT est estimé pour une application d'énergie renouvelable. Les pertes de conduction et commutation sont calculées avant et après vieillissement.

Le chapitre 6 présente une conclusion générale de la thèse et les études futures possibles sur les transistors GaN HEMT de puissance. Aussi, les contributions majeures de la thèse sont définies et présentées comme suit :

- Développement d'une méthodologie d'estimation des pertes de puissance statiques et dynamiques du GaN HEMT. Cette méthode est basée sur des caractérisations expérimentales I-V pulsé, C-V et du courant de fuites. La précision et la convergence cohérente du modèle SPICE utilisé fournissent un bon moyen d'étudier l'impact du vieillissement du GaN HEMT sur le rendement des convertisseurs de puissance par une approche de simulation.

- Développement d'un banc expérimental de caractérisation des paramètres S. Ce banc permet l'extraction des éléments parasites du GaN HEMT automatiquement et à multiples points polarisation. La méthode développée pour l'extraction des paramètres intrinsèques et extrinsèques est générique et peut être appliquée à plusieurs types de composants de puissance.

- La plupart des études existantes dans la littérature concernent la fiabilité du GaN HEMT dans des conditions statiques. Ce travail étudie le vieillissement du GaN HEMT de puissance dans les conditions de commutation opérationnelles des convertisseurs de tension DC-DC.

- Le banc de vieillissement proposé permet d'étudier l'impact des électrons chauds sur le GaN HEMT à haute courant et tension avec une faible consommation d'énergie.

- Les divers types de vieillissement réalisés permettent de classifier les modes de défaillance du GaN HEMT pour chaque mode de fonctionnement dans les applications de convertisseur de puissance.

**Mots clés :** GaN, HEMT, paramètres S, convertisseurs de puissance DC-DC, vieillissement, SOA, pertes de puissance.

## **Chapter 1: Introduction**

Investigating the impact of aging the power GaN HEMTs under operational switching conditions is receiving an increasing interest from research laboratories worldwide. The attention of academics and industrials on the power converters efficiency is accelerated by the impressive growth of GaN HEMTs market, due to their high superior performances compared to those of Silicon power transistors. Their applications are in various domains, such as renewable energy and high-power engineering.

The estimation of power losses with high convergence to measurements is necessary to design efficient power converters using GaN transistors. The authors in [1] have proposed an estimation of power losses based on a look-up tables of energy losses to estimate the switching losses of IGBTs. Also, the authors in [2] have estimated and compared the switching power losses of GaN HEMTs to equivalent Si devices such as IGBT and MOSFETs.

For that, an accurate model is necessary. In the literature, several behavioral models of GaN transistor have been proposed. References [3] and [4] show a simple and accurate segmented behavioral model, which include the important static parameters of the GaN HEMTs. However, these models suffer from the discontinuity of the simulated curves, because the used equations are divided into three segments according to cutoff, linear and saturation regions.

In this work, we estimate both the static and dynamic losses of power GaN HEMTs. Moreover, we used a smooth and continuous behavioral model to estimate the efficiency of DC-DC power converter circuits before and after operational switching aging.

Moreover, to validate the robustness of power GaN HEMTs, JEDEC standardized tests for Si power transistors are used [5]. However, the standardized tests for Si are not enough to guarantee the robustness of GaN transistors when they are used in power converter applications, because the reliability of GaN under switching operation is different from that of Si transistors [6]. Therefore, running GaN HEMTs power transistors under accelerated conditions would cause many non-GaN failures.

In the literature, the reliability of GaN HEMTs has been improved. Reference [7] classifies the degradation modes of GaN HEMT in switching mode DC power converter into three classes: on-state, off-state and semi-off state. According to [8], one of the major disadvantages limiting the reliability of GaN HEMTs for switching power applications is hot electron effects that occurs during the switching state. In [9], this degradation result in decreased DC and RF performance.

According to [10], it is important to study the reliability of GaN HEMT for power conversion circuits. This work presents a developed reliability methodology under operational switching conditions. The proposed aging switching bench presents high power efficiency. The effects of aging GaN HEMT transistor on a power converter application are studied by SPICE simulation approach.

The devices investigated on this thesis are based on the gallium nitride (GaN) material. GaN is a III-V compound semiconductor with various physical properties such as wide band gap, large breakdown electric field, strong mechanical and thermal stability and good heat conductivity. In this first chapter, a general overview of the GaN power devices is given. Therefore, the objectives and the outline of this research work are presented.

#### **1.1 GaN HEMT for power converter applications**

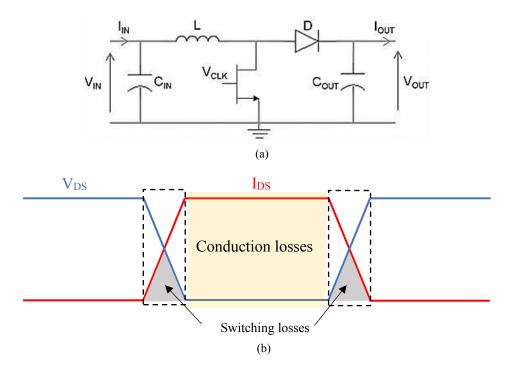

Power switching devices are used in DC-DC converters to convert voltages. In order to provide an efficient conversion, an ideal switching device should guarantee zero static and dynamic losses. The static losses are due to the parasitic resistance of the device ( $R_{ON}$ ) when it is in the on-state and due to the leakage current when is in the off-state. However, the dynamic power loss is induced during the switching from the on-state to the off-state and vice versa.

Furthermore, the possibility of having a power switching device able to operate at high switching frequencies would allow to reduce the size of passive components present in today DC-DC converts, this can significantly reduce the overall converter size. Nowadays, the Si MOSFET technology is reaching the limit [11]. Hence, emergent technologies have to be considered to go beyond the limit of Si devices.

Due to the large critical electric field, the GaN material is considered to replace Si technology. The large critical electric field of the GaN is combined with the high twodimensional electron gas (2DEG) density, which is spontaneously generated at the AlGaN/GaN heterostructure interface, hence, with intrinsically low resistivity.

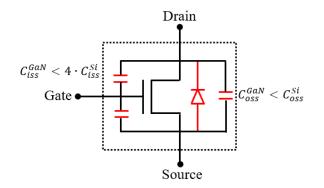

As a result, due to the high-density and low-resistivity 2DEG in comparison to the Si technology for the same current target value, AlGaN/GaN HEMTs guarantee a smaller on-resistance with smaller overall device area. Moreover, a smaller parasitic capacitance compared to other Si devises. Only the SiC based devices appear to be able to compete with the GaN. However, the GaN has lower dynamic losses, highest density and switching frequency.

Despite the high performances of the GaN HEMT in power converter applications, this technology still has various challenges to overcome for both a wide use and highly confident in the power converter market. The GaN HEMT challenges are presented in the following.

#### 1.1.1. Normally-off challenge

One of the challenges that the GaN technology had to overcome in order to enhance its performances on the power switching market was the creation of the GaN normally-off devices. In fact, naturally GaN transistors are normally-on devices and most of the advantages of this technology are due to the spontaneous formation of the 2DEG channel without applying any gate voltage. However, for switching applications normally-off devices are required for safety reasons. Today, various companies have commercialized normally-off devices with high operating voltage (1000 V). Their performances in term of dynamic and static losses are better than the Si devices for the same operating voltage. According to the power GaN HEMT roadmap [12], it is recommended to study the normally-off GaN HEMT technology for power converter circuits. This thesis fulfils the recommendation of the GaN power roadmap. For that, we have investigated both the reliability and the power efficiency of the p-GaN normally-off technology as required in the power converter market.

#### 1.1.2 Power losses estimation

The estimation of the GaN HEMT losses offers to the power converter designers the possibility to estimate the power losses of GaN HEMT with high accuracy without the use of

the complex switching bench, which reduces the time to market and cost. To accurately design a power converter with GaN HEMT, it is important to calculate the power losses of the device. For that, we have presented in chapter 3 an experimental methodology for the estimation of both the static and dynamic power losses of the GaN HEMT using C-V and I-V measurement. The impact of the GaN HEMT losses on the efficiency of power converts are modelled using SPICE simulation approach. This accurate methodology enables to identify the impact of aging the GaN HEMT on the efficiency of power converts.

### 1.1.3. Gate driver