# MOSFETs SiC connectés en série: un nouveau concept de packaging et nouvelles configurations d'alimentation de commande rapprochée

Luciano Francisco Sousa Alves

### ▶ To cite this version:

Luciano Francisco Sousa Alves. MOSFETs SiC connectés en série : un nouveau concept de packaging et nouvelles configurations d'alimentation de commande rapprochée. Electric power. Université Grenoble Alpes [2020-..], 2020. English. NNT : 2020GRALT050 . tel-03139963

# HAL Id: tel-03139963 https://theses.hal.science/tel-03139963

Submitted on 12 Feb 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Ph. D. THESIS

To acquire the degree of

### **DOCTOR AT GRENOBLE ALPES UNIVERSITY**

Major: Electrical Engineering

Ministerial law from: August 7th 2006

Presented by

### Luciano FRANCISCO SOUSA ALVES

Thesis supervised by:

Pierre LEFRANC, Chair Pierre-Olivier JEANNIN, Co-supervisor Benoît Sarrazin, Co-supervisor

Completed at:

**Grenoble Electrical Engineering Laboratory (G2ELab)**

Under the:

**Doctoral School of Electronics, Electrical Engineering, Automatics and Signal Treatment (EEATS)**

# Series-Connected SiC-MOSFETs: A Novel Multi-Step Packaging Concept and New Gate Drive Power Supply Configurations

Thesis defended publicly «November, 5<sup>th</sup> 2020», in front of the jury composed by:

### M. Nadir IDIR

Professor at Université de Lille, HDR, L2EP Laboratory: President

### M. Nicolas ROUGER

Research Scientist, CNRS, HDR, Laplace Laboratory: Reviewer

### M. Cyril BUTTAY

Research Scientist, CNRS, HDR, Ampère Laboratory: Reviewer

### M. Nicolas GINOT

Professor at IUT Nantes, HDR, IETR Laboratory: Member

### M. Jean-Christophe CREBIER

Research Scientist, CNRS, HDR, G2Elab laboratory: Member

### M. Pierre LEFRANC

Associate Professor at Grenoble-INP, HDR: Supervisor

### **Pierre-Olivier JEANNIN**

Associate Professor at UGA: Co-supervisor

### **Benoît SARRAZIN**

Research engineer at Grenoble-INP: Co-supervisor

# **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITE GRENOBLE ALPES

Spécialité : GENIE ELECTRIQUE

Arrêté ministériel : 25 mai 2016

Présentée par

### Luciano FRANCISCO SOUSA ALVES

Thèse dirigée par **Pierre LEFRANC** et codirigée par **Pierre-Olivier JEANNIN** et **Benoît SARRAZIN**

préparée au sein du Laboratoire de Génie Electrique de Grenoble (G2ELab) dans l'École Doctorale Electronique, Electrotechnique, Automatique et Traitement du Signal (EEATS)

# Association en Série de MOSFETs SiC: Un Nouveau Concept de Packaging et Nouvelles Configurations d'Alimentation de Commande Rapprochée

Thèse soutenue publiquement le « 05/11/2020 », devant le jury composé de :

### M. Nadir IDIR

Professor à l'Université de Lille, HDR, Laboratoire L2EP: Président

#### M. Nicolas ROUGER

Directeur de Recherche CNRS, HDR, Laboratoire LAPLACE: Rapporteur

### M. Cyril BUTTAY

Directeur de Recherche CNRS, HDR, Laboratoire AMPERE: Rapporteur

### M. Nicolas GINOT

Professeur à l'IUT de Nantes, HDR, Laboratoire IETR: Examinateur

### M. Jean-Christophe CREBIER

Directeur de Recherche CNRS, HDR, Laboratoire G2Elab: Examinateur

#### M. Pierre LEFRANC

Maître de Conférences Grenoble-INP, HDR: Directeur de thèse

### Pierre-Olivier JEANNIN

Maître de Conférences UGA: Co-encadrant

### **Benoît SARRAZIN**

Ingénieur de Recherche Grenoble-INP: Co-encadrant

# Acknowledgements

I would like to start this manuscript by expressing a special thanks to all the persons who accompanied me during these three years of Ph.D. work.

First of all, I sincerely thank my advisors, Pierre Lefranc, Pierre-Olivier Jeannin and Benoit Sarrazin who accompanied, advised and guided me as best we could imagine. Their motivation for research as well as their willingness to teach and an unlimited availability, made this thesis a really enjoyable work (without forgetting the moments of human interaction (coffee break, apero, etc.)). It was surely pleasing to work with them. Also, I would like to give a special thanks to Jean-Christophe Crebier for being been part of this Ph.D. His advice and proposals highly contributed to this work. Furthermore, I would like to thank all members of the jury committee that carefully read this work, proposed improvements and made a very productive discussion during the defence day: M. Nadir Idir, M. Nicolas Rouger, M. Cyril Buttay, M. Nicolas Ginot et M. Jean-Christophe Crebier. I also address a special thought to all the persons that I met at the laboratory; with whom I could work, drink, have a coffee or simply share a place full of life; Andre Andreta, Lucas Souza, Nisith Bhowmick, Soleiman Galeshi, Nasreddine Kesbia, Uyen, Adrien Voldoire, Theo Lamorelle, Aurelien Marechal, Gaetan Perez, Beatriz de Luca, Arhur Kazuiti, Glauber de Freitas, Fadel Bikinga, Pawel-bogdan, Antoine Bulteau, Blazei-De-Bulteau, Damien Lemaitre, Boubakr Rahmani and Nicolas Botter.

Finally, I sincerely thank my family because nothing would have been possible without them. I would like to give a special thanks to my parents Maria de Lourdes Sousa Alves and Francisco de Assis Alves Guerra, my brother, my sister and my nephew; but also, my partner Jennifer Ly Tham and my friends.

Thank you all very much.

# Abstract

This work investigates new gate drive power supply configurations and a novel multi-step packaging concept in order to improve the performances of series-connected SiC-MOSFETs. The new gate drive configurations are proposed in order to reduce noise currents that circulate in the control part of the electrical system. Furthermore, a new gate drive power supply is proposed to increase the dv/dt of the switching cell. These improvements, i.e., noise current reduction and dv/dt boosting, are achieved by modifying the impedance of the gate drive circuitry. The novel multi-step packaging concept is proposed in order to improve the voltage sharing performances. The proposed package geometry considers optimal dielectric isolation for each device leading to a multi-step geometry. It has a significant impact on the parasitic capacitances introduced by the packaging structure that are responsible for voltage unbalances. The new gate driver configurations and the proposed multi-step packaging concepts are introduced and analysed thanks to equivalent models and time domain simulations. Then, experimental set-ups are performed to confirm that the proposed concepts are better than traditional ones in terms of voltage balancing, switching speed and conducted EMI reduction.

# Contents

| Al       | ostra  | ct         |                                                                      | 5  |

|----------|--------|------------|----------------------------------------------------------------------|----|

| C        | onte   | ${ m nts}$ |                                                                      | 1  |

| ${f L}$  | ist of | f Table    | es                                                                   | 3  |

| ${f L}$  | ist of | f Figui    | res                                                                  | 4  |

| 1        | Ger    | neral I    | ntroduction                                                          | 1  |

|          | 1.1    | Medi       | um-Voltage High-Power Converter Applications                         | 1  |

|          | 1.2    | Metho      | ods for Achieving Higher Voltage Capability                          | 2  |

|          |        | 1.2.1      | Wide Band Gap Devices                                                | 2  |

|          |        | 1.2.2      | Series-Connected Devices and Multi-level Converters                  | 2  |

|          | 1.3    | Challe     | enges of Series-Connected Devices                                    | 3  |

|          |        | 1.3.1      | Voltage Balancing Problems                                           | 3  |

|          |        | 1.3.2      | Common Mode Conducted EMI                                            | 3  |

|          | 1.4    | Resea      | rch Motivation and Objectives                                        | 5  |

|          | 1.5    | Thesis     | s Organization                                                       | 5  |

| <b>2</b> | Sta    | te-of-t    | he-Art                                                               | 6  |

|          | 2.1    | Si, Si     | $C, GaN, Ga_2O_3$ and $Diamond \dots \dots \dots \dots \dots \dots$  | 6  |

|          | 2.2    | Silico     | on Carbide MOSFETs                                                   | 8  |

|          |        | 2.2.1      | Turn-ON Procedure                                                    | 9  |

|          |        | 2.2.2      | Turn-OFF Procedure                                                   | 10 |

|          |        | 2.2.3      | SiC-MOSFETs: Important Characteristics                               | 12 |

|          | 2.3    | Series     | -Connected SiC-MOSFETs                                               | 13 |

|          |        | 2.3.1      | Device Parameter Tolerances, Package and Layout Parasitic Components | 15 |

|          |        | 2.3.2      | Gate Signal Timing Delays                                            | 17 |

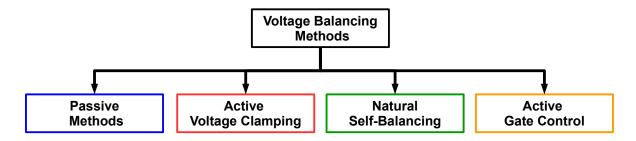

|          | 2.4    |            | ge Balancing Techniques                                              | 18 |

|          |        | 2.4.1      | Passive Methods                                                      | 18 |

|          |        | 2.4.2      | Active Voltage Clamping                                              | 22 |

|          |        | 2.4.3      | Natural Self-Balancing                                               | 26 |

|          |        | 2.4.4      | Active Gate Control                                                  | 29 |

|          |        | 2.4.5      | Common Mode Conducted EMI                                            | 37 |

| 3        | Nev    | w Gate     | e Driver Architectures                                               | 39 |

|          | 3.1    | Comn       | non Mode Conducted EMI Reduction                                     | 39 |

|          |        | 3.1.1      | Traditional Gate Driver Configuration (TGD)                          | 41 |

|          |        | 3.1.2      | New Modified Gate Driver Configurations                              | 45 |

|          |                                                                           | 3.1.3 Experimental Results                                                                                                                                                   |

|----------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 3.2                                                                       | Impact of the gate driver parasitic capacitances on the switching cell $dv/dt$ . 59                                                                                          |

|          |                                                                           | 3.2.1 Electrical Transient Simulations                                                                                                                                       |

|          |                                                                           | 3.2.2 Experimental validations                                                                                                                                               |

|          | 3.3                                                                       | Impact of the Gate Driver Configuration on Voltage Balancing: A Brief Dis-                                                                                                   |

|          |                                                                           | cussion                                                                                                                                                                      |

|          |                                                                           | 3.3.1 Experimental Results                                                                                                                                                   |

|          | 3.4                                                                       | Conclusion                                                                                                                                                                   |

| 4        | $\mathbf{A}$                                                              | Novel Multi-Step Packaging Concept for Series-Connected Devices . 78                                                                                                         |

|          | 4.1                                                                       | Impact of Power Module Parasitic Capacitances on Voltage Balancing 78                                                                                                        |

|          |                                                                           | 4.1.1 Theoretical Analyses                                                                                                                                                   |

|          | 4.2                                                                       | Multi-Step Packaging/Layout Concept: 1st Proposition                                                                                                                         |

|          | 4.3                                                                       | Multi-Step Packaging/Layout Concept: 2nd Proposition                                                                                                                         |

|          |                                                                           | 4.3.1 Comments About Thermal Management                                                                                                                                      |

|          |                                                                           | 4.3.2 Conclusion                                                                                                                                                             |

|          |                                                                           |                                                                                                                                                                              |

| _        |                                                                           |                                                                                                                                                                              |

| 5        |                                                                           | Novel Active Gate Driver for Series-Connected SiC-MOSFETs: A                                                                                                                 |

| 5        | $\mathbf{Pro}$                                                            | position                                                                                                                                                                     |

| 5        | <b>Pro</b> 5.1                                                            | position                                                                                                                                                                     |

| 5        | Pro<br>5.1<br>5.2                                                         | positionIntroductionA Novel Active Gate Driver with a Double Active Control                                                                                                  |

| 5        | <b>Pro</b> 5.1                                                            | position                                                                                                                                                                     |

| <b>5</b> | 9.1 5.2 5.3                                                               | positionIntroductionA Novel Active Gate Driver with a Double Active Control                                                                                                  |

|          | 9.1 5.2 5.3                                                               | position118Introduction118A Novel Active Gate Driver with a Double Active Control120Conclusion129                                                                            |

|          | Pro<br>5.1<br>5.2<br>5.3<br>Rés                                           | Introduction                                                                                                                                                                 |

|          | Pro<br>5.1<br>5.2<br>5.3<br>Rés<br>6.1                                    | Introduction                                                                                                                                                                 |

|          | Pro<br>5.1<br>5.2<br>5.3<br>Rés<br>6.1<br>6.2                             | position118Introduction118A Novel Active Gate Driver with a Double Active Control120Conclusion129umé en Français134Introduction134Motivation et objectifs de la recherche134 |

|          | Pro<br>5.1<br>5.2<br>5.3<br>Rés<br>6.1<br>6.2<br>6.3                      | Introduction                                                                                                                                                                 |

|          | Pro<br>5.1<br>5.2<br>5.3<br>Rés<br>6.1<br>6.2<br>6.3<br>6.4               | Introduction                                                                                                                                                                 |

|          | Pro<br>5.1<br>5.2<br>5.3<br><b>Rés</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5 | Introduction                                                                                                                                                                 |

# List of Tables

| 2.1        | Physical Properties of Silicon (Si), Silicon Carbide (4H-SiC), Gallium Nitride (GaN), Ga <sub>2</sub> O <sub>3</sub> , and Diamond [14–19] | 7   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1        | Gate drive circuitry elements presented in Fig. 3.2                                                                                        | 41  |

| 3.2        | Element values of the equivalent impedance network circuits                                                                                | 44  |

| 3.3        | Elements of the equivalent circuit shown in Fig. 3.34                                                                                      | 60  |

| 3.4        | Element values of the HF equivalent circuit                                                                                                | 66  |

| <i>4</i> 1 | Parasitic canacitances network values                                                                                                      | 105 |

# List of Figures

| 1.1  | Medium-voltage applications [1]                                                                      | 1  |

|------|------------------------------------------------------------------------------------------------------|----|

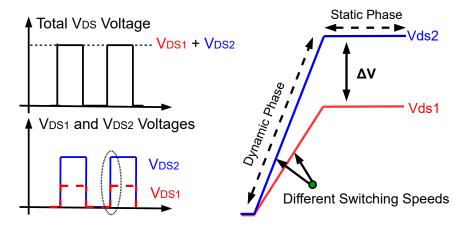

| 1.2  | Unbalanced voltages during dynamic and static phases                                                 | 3  |

| 1.3  | Gate driver circuitry                                                                                | 4  |

| 2.1  | Material properties comparison between Si, 4H-SiC, GaN, Ga <sub>2</sub> O <sub>3</sub> , and Diamond | 7  |

| 2.2  | SiC-MOSFET device model                                                                              | ç  |

| 2.3  | Ideal turn-ON process for SiC-MOSFETs                                                                | 10 |

| 2.4  | Ideal turn-OFF process for SiC-MOSFETs                                                               | 11 |

| 2.5  | Behavior of Vth = $f(Vgs)$ after 500h of operation [14,25]                                           | 12 |

| 2.6  | $V_{ds}-I_{ds}$ characteristic for a SiC-MOSFET, Si-SJMOS and a Si-IGBT at 25 °C and 125 °C [25]     | 13 |

| 2.7  | On-resistance comparison between Si-MOSFET, Si-Super-Junction and SiC-DMOSFET [26]                   | 14 |

| 2.8  | Two series-connected SiC-MOSFETs operated as a single switch                                         | 14 |

| 2.9  | Voltage Balancing Problem                                                                            | 15 |

| 2.10 | Two series-connected SiC-MOSFETs and their parasitic elements                                        | 16 |

| 2.11 | Equivalent electrical scheme of two series-connected SiC-MOSFETs and their                           |    |

|      | parasitic elements.                                                                                  | 17 |

| 2.12 | Unbalanced voltage caused by gate signal timing delays                                               | 18 |

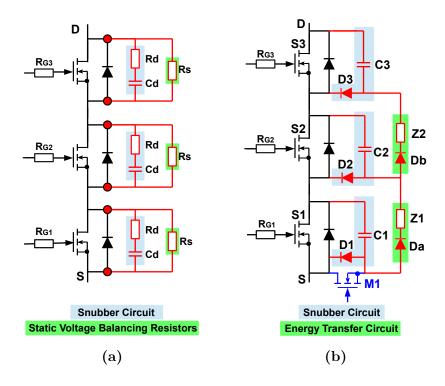

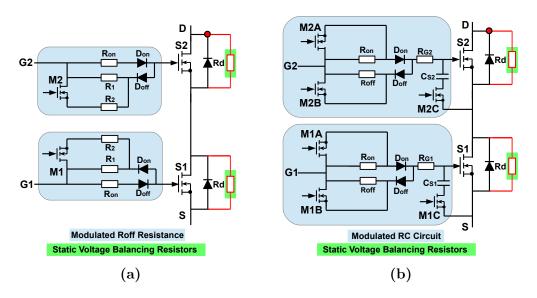

| 2.13 | Classical voltage balancing techniques                                                               | 18 |

| 2.14 | Simple RC snubber method (a) [33–35] ,and snubber circuits with energy recovery capability (b) [38]  | 19 |

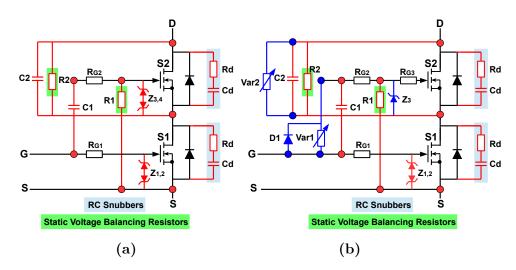

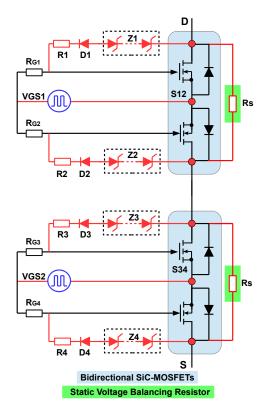

| 2.15 | Proposed series-connected topology (a) [40,41], and its adaptation for SSCB application (b) [42]     | 21 |

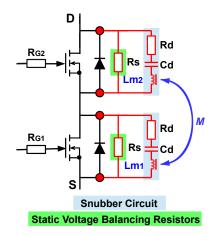

| 2 16 | Voltage balancing circuit realized by mutual inductance [44]                                         | 22 |

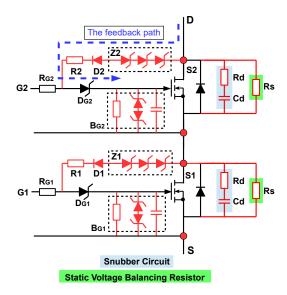

|      | Active voltage clamping method proposed in [47]                                                      | 23 |

|      | Active voltage clamping method proposed in [48] for SSCB applications                                | 24 |

|      | Active voltage clamping method with a single external driver proposed in [39].                       | 25 |

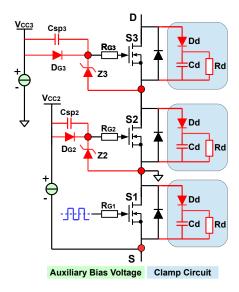

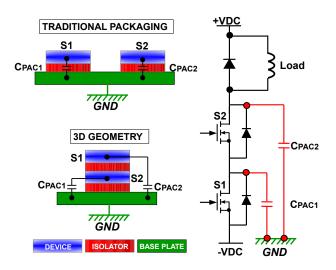

|      | 3D-geometry layout proposed in [50,51]                                                               | 26 |

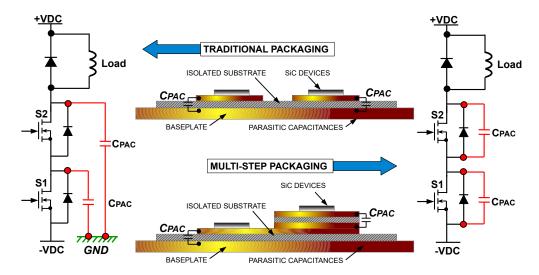

|      | Multi-step packaging concept proposed in [10]                                                        | 27 |

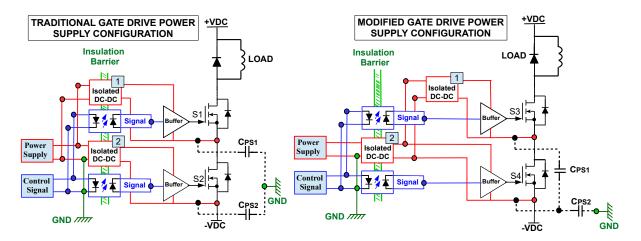

|      | Modified gate drive power supply configuration proposed in [9]                                       | 27 |

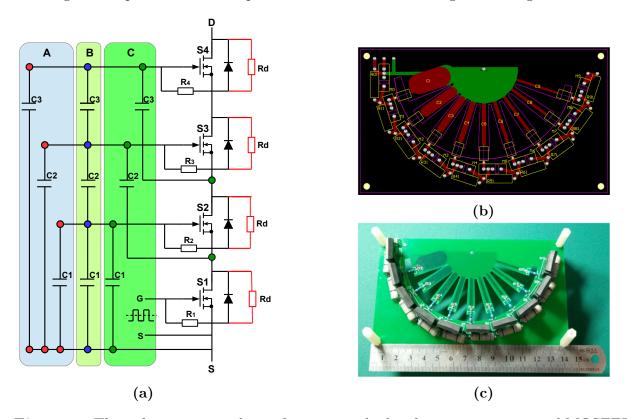

|      | Three derivative topologies for compact high voltage series-connected MOS-                           |    |

|      | FETs module (a), PCB layout for the A-configuration (b), and prototype of                            |    |

|      | 10 kV power module (c) [8]                                                                           | 28 |

| 2.24 | Active $dv/dt$ control method for balancing voltages across stacked SiC-MOSFETs                      |    |

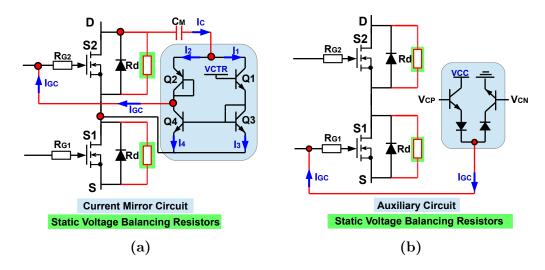

|      | proposed in [52,53](a), and similar active gate control proposed in [54](b).                         | 30 |

| 2.25 | Active control methods for balancing voltages across stacked SiC-MOSFETs       |

|------|--------------------------------------------------------------------------------|

|      | proposed in $[55-57](a)$ , and in $[45](b)$                                    |

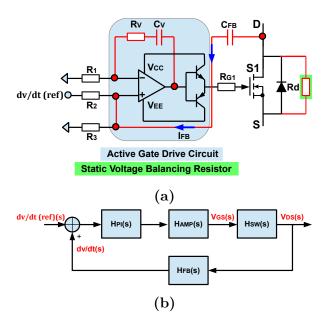

| 2.26 | Proposed closed loop active gate driver circuit (a), and its closed-loop block |

|      | diagram (b) [58]                                                               |

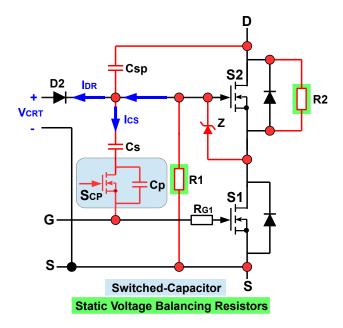

| 2.27 | Capacitive coupling method proposed in [59]                                    |

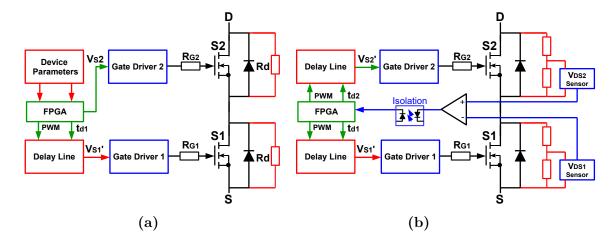

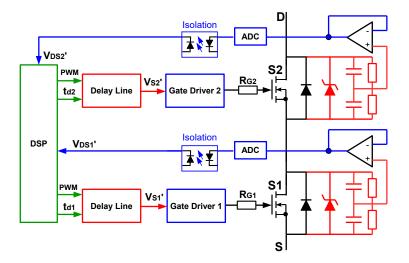

| 2.28 | Time-delay control for series-connected devices. Open-loop control [61](a),    |

|      | and closed loop [62](b)                                                        |

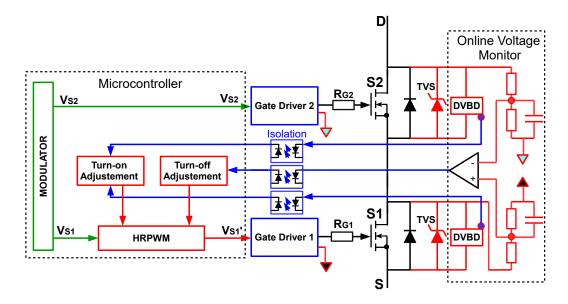

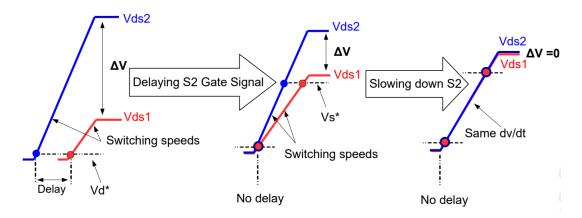

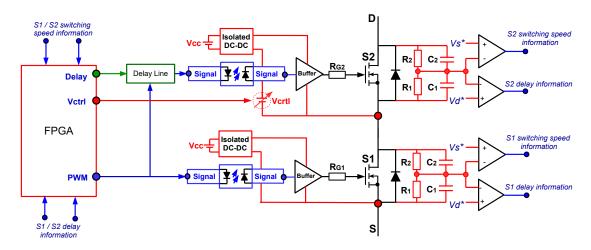

| 2.29 | Time-delay closed-loop control proposed in [63]                                |

| 2.30 | Time-delay closed-loop control proposed in [64]                                |

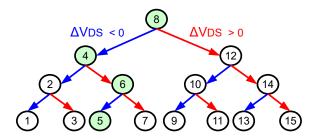

| 2.31 | Binary searching algorithm proposed in [65]                                    |

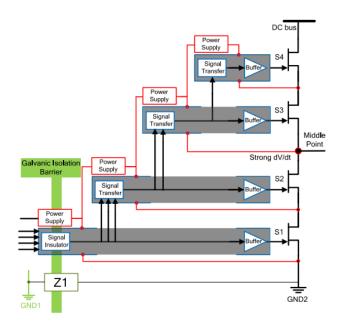

| 2.32 | Modified gate drive architecture proposed in [72]                              |

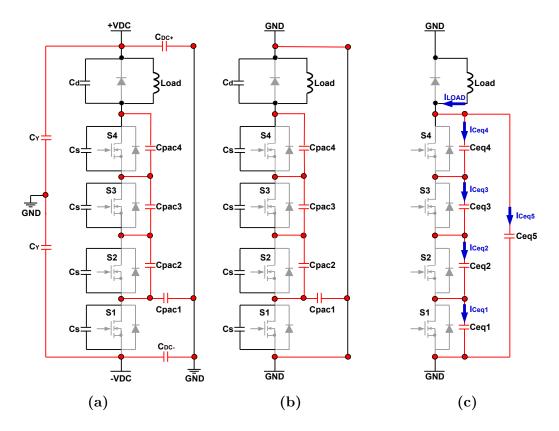

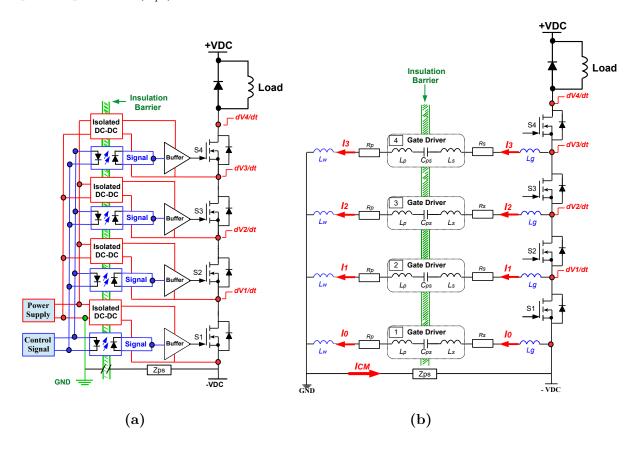

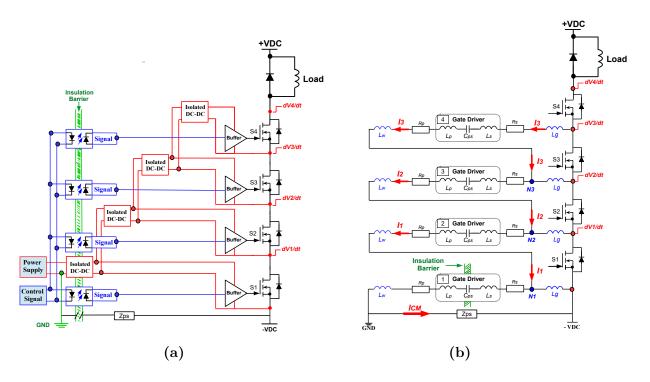

| 3.1  | Gate drive power supply and signal isolation unit parasitic capacitances 4     |

| 3.2  | Parasitic elements of the gate drive power supply and its connections 4        |

| 3.3  | TGD configuration (a) and its electrical circuit (b)                           |

| 3.4  | Equivalent switching cell model for the TGD configuration                      |

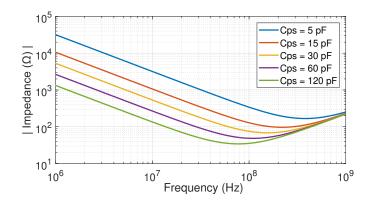

| 3.5  | Gate drive power supply impedance for different values of $C_{ps}$             |

| 3.6  | 1MGD configuration (a) and its electrical circuit (b)                          |

| 3.7  | Gate drive power supply impedances                                             |

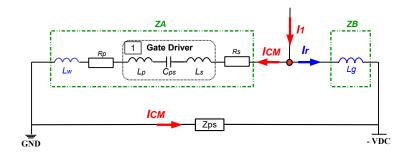

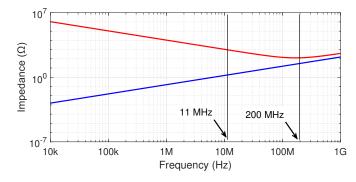

| 3.8  | $Z_A$ and $Z_B$ impedances of as a function of the frequency                   |

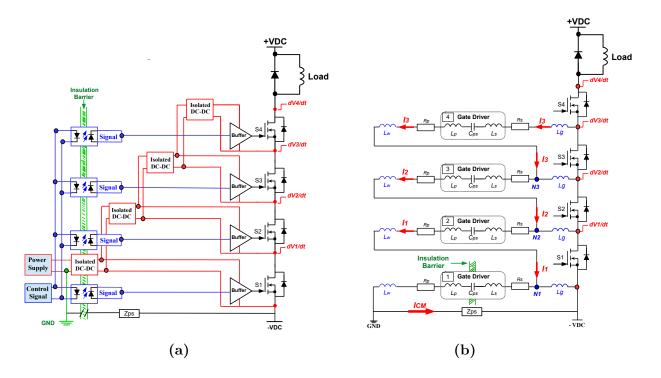

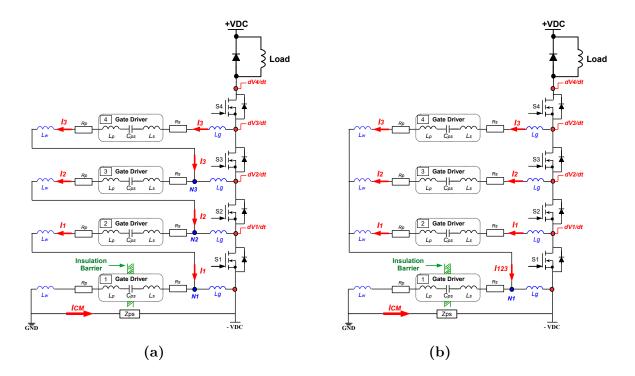

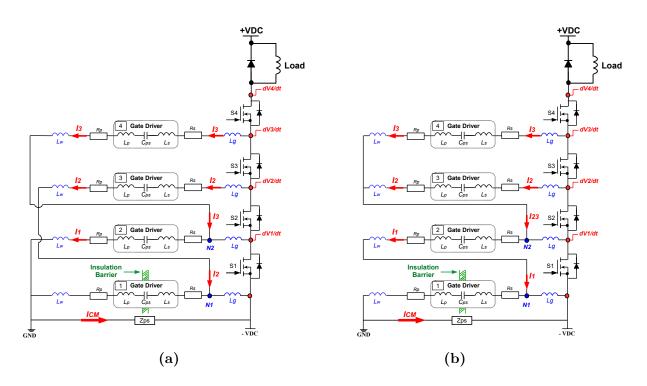

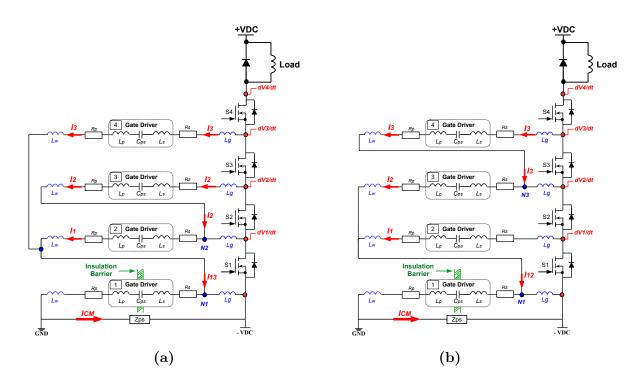

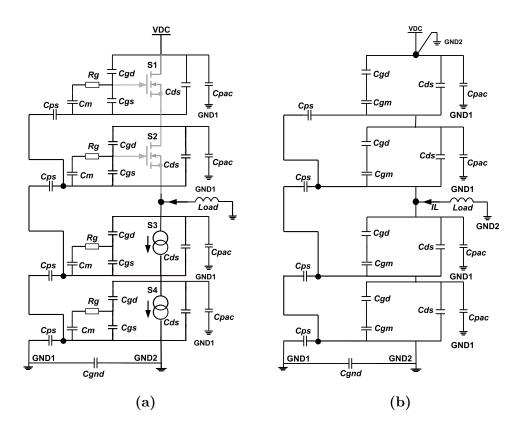

| 3.9  | Electrical schematic of 1MDG (a) and 2MGD (b) configurations                   |

| 3.10 | Electrical scheme of 3MDG (a) and 4MGD (b) configurations                      |

| 3.11 | Electrical circuits of 5MDG (a) and 6MGD (b) configurations                    |

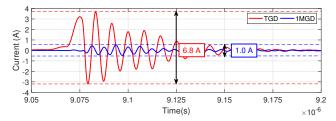

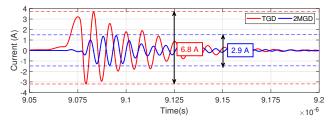

| 3.12 | CM current comparison between TGD and 1MDG configurations. Simulation          |

|      | Results                                                                        |

| 3.13 | CM current comparison between TGD and 2MDG configurations. Simulation          |

|      | Results                                                                        |

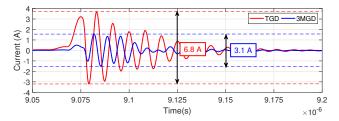

| 3.14 | CM current comparison between TGD and 3MDG configurations. Simulation          |

|      | Results                                                                        |

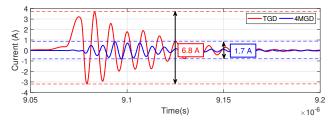

| 3.15 | CM current comparison between TGD and 4MDG configurations. Simulation          |

|      | Results                                                                        |

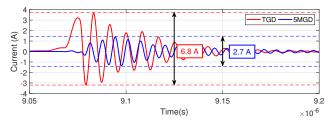

| 3.16 | CM current comparison between TGD and 5MDG configurations. Simulation          |

|      | Results                                                                        |

| 3.17 | CM current comparison between TGD and 6MDG configurations. Simulation          |

|      | Results                                                                        |

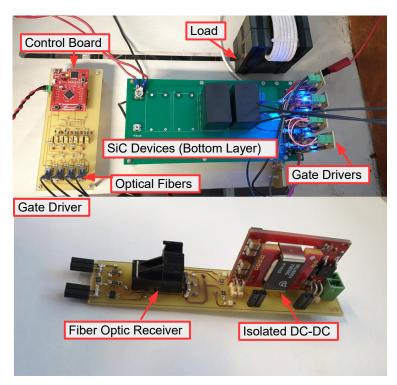

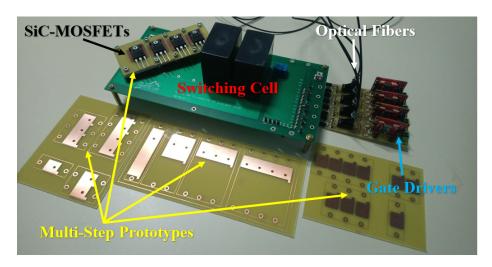

| 3.18 | Switching cell prototype of four series-connected SiC-MOSFETs                  |

|      |                                                                                |

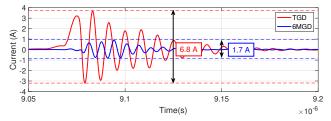

|      | CM current waveforms with and without $ZM$                                     |

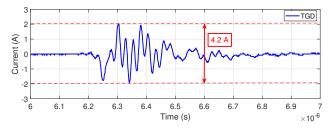

|      | CM current in the TGD configuration. Experimental Result                       |

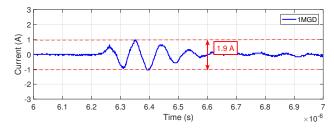

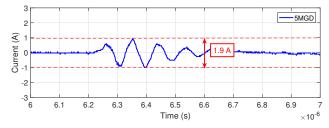

|      | CM current in the 1MDG configuration. Experimental Result 5                    |

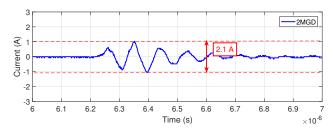

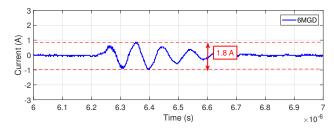

| 3.23 | CM current in the 2MDG configuration. Experimental Result                       | 55            |

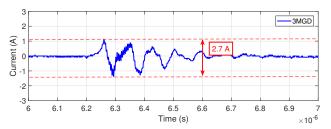

|------|---------------------------------------------------------------------------------|---------------|

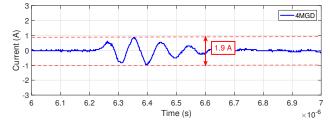

| 3.24 | CM current in the 3MDG configuration. Experimental Result                       | 55            |

| 3.25 | CM current in the 4MDG configuration. Experimental Result                       | 55            |

| 3.26 | CM current in the 5MDG configuration. Experimental Result                       | 56            |

| 3.27 | CM current in the 6MDG configuration. Experimental Result                       | 56            |

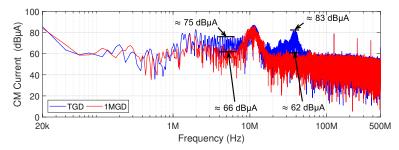

| 3.28 | Spectral CM current comparison between TGD and 1MDG configurations.             |               |

|      | Experimental Results                                                            | 57            |

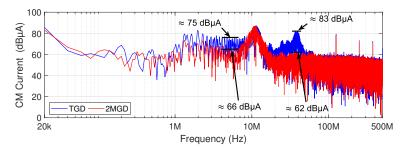

| 3.29 | Spectral CM current comparison between TGD and 2MDG configurations.             |               |

|      | Experimental Results                                                            | 57            |

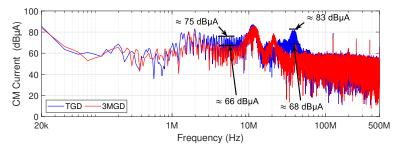

| 3.30 | Spectral CM current comparison between TGD and 3MDG configurations.             |               |

|      | Experimental Results                                                            | 57            |

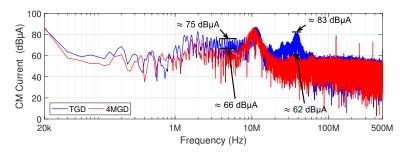

| 3.31 | Spectral CM current comparison between TGD and 4MDG configurations.             |               |

|      | Experimental Results                                                            | 58            |

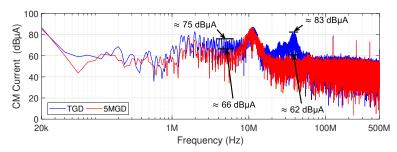

| 3.32 | Spectral CM current comparison between TGD and 5MDG configurations.             |               |

|      | Experimental Results                                                            | 58            |

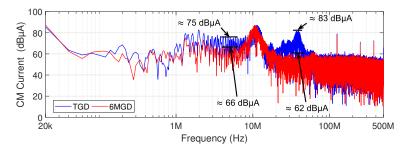

| 3.33 | Spectral CM current comparison between TGD and 6MDG configurations.             |               |

|      | Experimental Results                                                            | 58            |

| 3.34 | Simplified capacitive model with the main parasitic capacitances                | 59            |

| 3.35 | Traditional Gate Driver Architecture Configuration (TGD) 6                      | 31            |

|      |                                                                                 | 32            |

| 3.37 | Equivalent switching cell model (TGD)                                           | 32            |

| 3.38 | Cascaded Gate Driver Configuration (CGD)                                        | 33            |

|      |                                                                                 | 34            |

| 3.40 | Equivalent switching cell model (CGD)                                           | 35            |

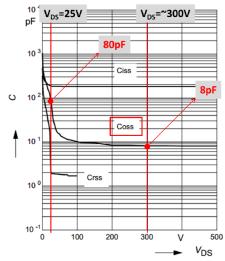

| 3.41 | $C_{oss}$ Capacitance variation as a function of drain-source voltage 6         | 66            |

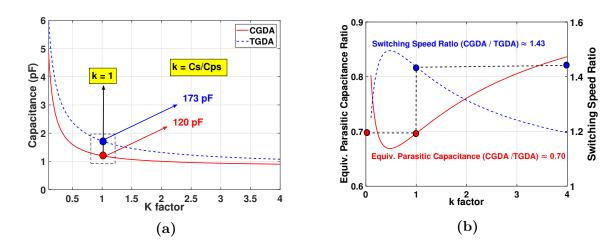

| 3.42 | Equivalent capacitances (a) and switching speed middle point and equivalent     |               |

|      | parasitic capacitance rates (b) as a function of the $k$ factor for TGD and CGD |               |

|      |                                                                                 | <sup>37</sup> |

| 3.43 | Switching speed middle point as function of the gate driver architecture; si-   |               |

|      |                                                                                 | 38            |

| 3.44 | Experimental Vds voltage balancing waveforms for the TGD (a) and CGD (b)        |               |

|      |                                                                                 | <b>3</b> 9    |

|      | ( ) ( ) (                                                                       | 70            |

| 3.46 | Experimental pulse train waveforms (a) and measured $dv/dt$ for TGD and         |               |

|      |                                                                                 | 71            |

| 3.47 | ,                                                                               |               |

|      | • • •                                                                           | 71            |

| 3.48 | Electrical circuit of two SiC-MOSFETs connected in series (a) and equivalent    |               |

|      | electrical circuit (b)                                                          | 73            |

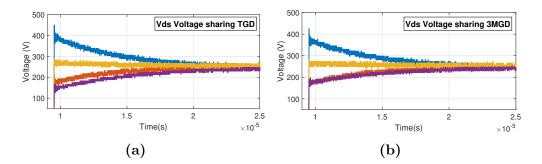

| 3.49       | Experimental voltage balancing waveforms for (a) TGD and (b) 1MGD configurations                                                                                   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.50       | Experimental voltage balancing waveforms for (a) TGD and (b) 2MGD configurations                                                                                   |

| 3.51       | Experimental voltage balancing waveforms for (a) TGD and (b) 3MGD configurations                                                                                   |

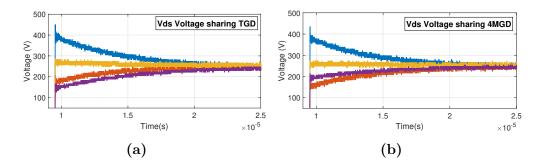

| 3.52       | Experimental voltage balancing waveforms for (a) TGD and (b) 4MGD configurations.                                                                                  |

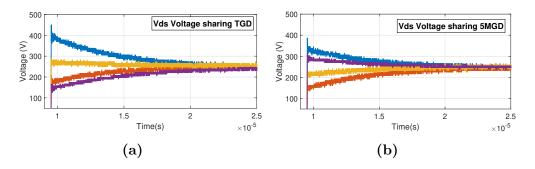

| 3.53       | Experimental voltage balancing waveforms for (a) TGD and (b) 5MGD configurations.                                                                                  |

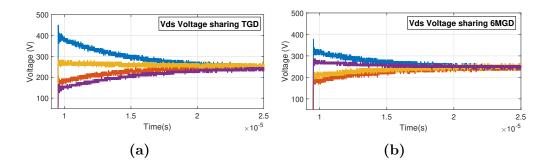

| 3.54       | Experimental voltage balancing waveforms for (a) TGD and (b) 6MGD configurations.                                                                                  |

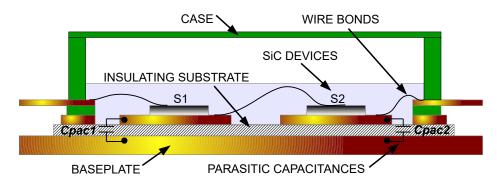

| 4.1        | Cross-section of a simplified standard 2D planar package with two dies connected in series                                                                         |

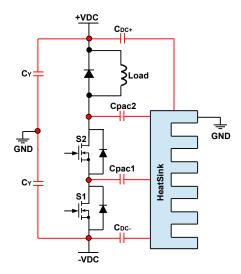

| 4.2        | Equivalent electrical circuit of two SiC-MOSFETs connected in series in a 2D planar package                                                                        |

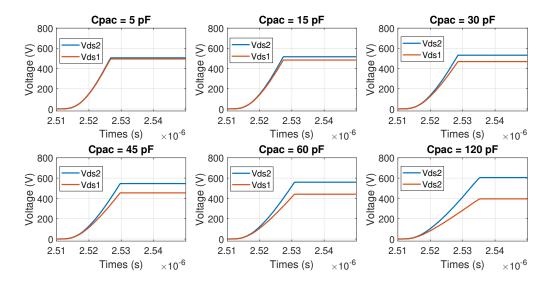

| 4.3        | Electrical circuit of two SiC-MOSFETs connected in series in a 2D planar package (a), high frequency circuit (b) and simplified electrical scheme (c).             |

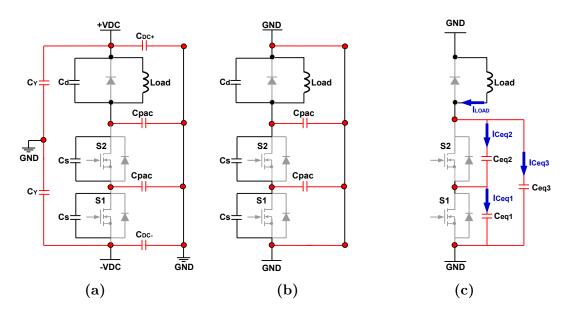

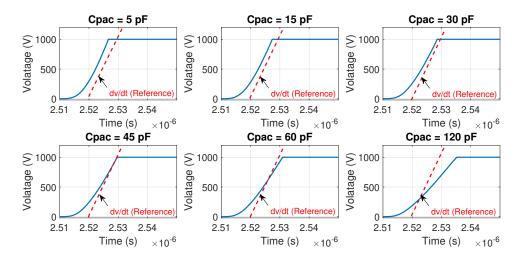

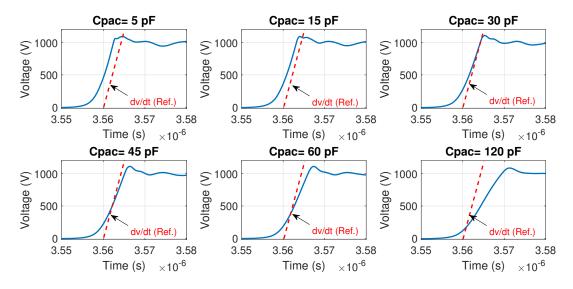

| 4.4        | Simulation results: voltage sharing between two series-connected devices as a function of $C_{pac}$                                                                |

| 4.5        | Simulation results: middle point switching speed as a function of $C_{pac}$                                                                                        |

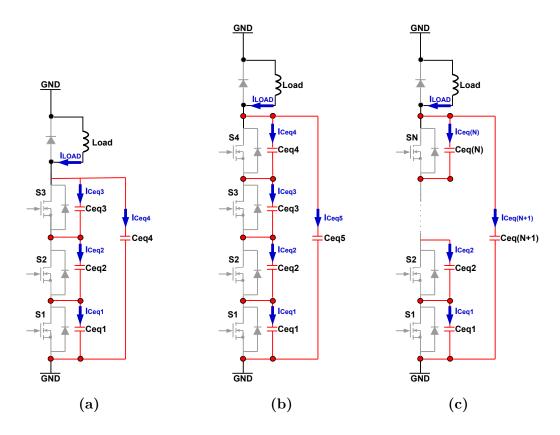

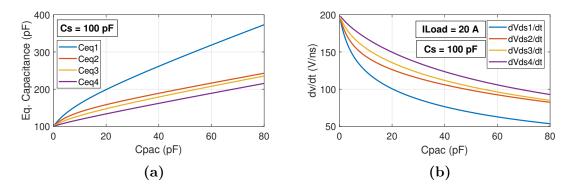

| 4.6<br>4.7 | Equivalent electrical circuits for 3(a), 4(b), and N-series-connected devices(c). Equivalent parasitic capacitances (a) and middle point $dv/dt$ (b) as a function |

| 1.1        | of $C_{pac}$                                                                                                                                                       |

| 4.8        | Multi-Step Package concept for four series-connected SiC-MOSFETs                                                                                                   |

| 4.9        | Electrical circuit of four SiC-MOSFETs connected in series in the MSP package (a), high frequency circuit (b) and simplified electrical scheme (c)                 |

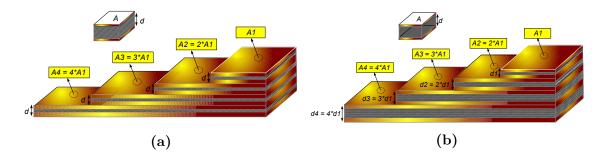

| 4.10       | 3D view of the proposed package concept with the same distance $d$ (a), and different distances $d$ (b)                                                            |

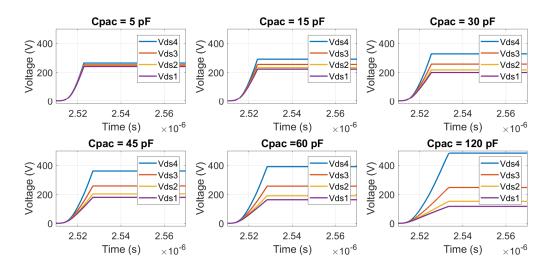

| 4.11       | TRP simulation results: voltage Sharing between four series-connected SiC-MOSFETs                                                                                  |

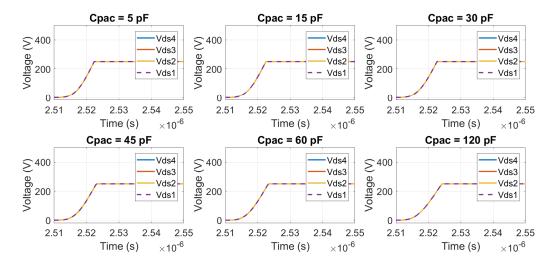

| 4.12       | MSP simulation results: voltage Sharing between four series-connected SiC-MOSFETs                                                                                  |

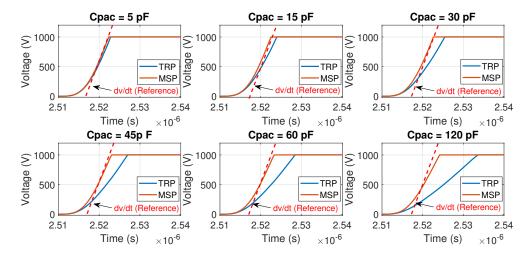

| 4.13       | Simulation results: $dv/dt$ as a function of $C_{pac}$ for TRP and MSP packages/layouts                                                                            |

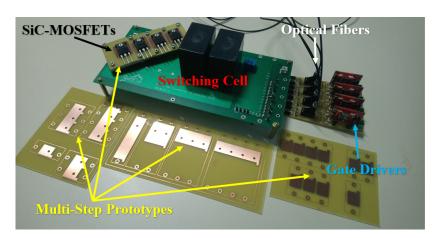

| 4.14       | Switching cell and package prototypes                                                                                                                              |

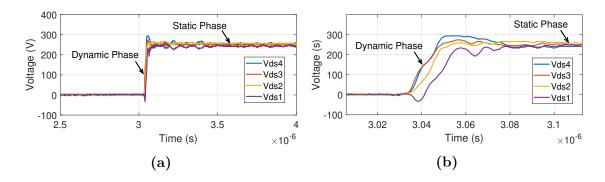

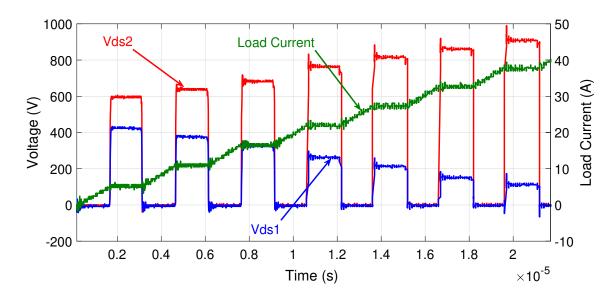

|            | Experimental results: voltage balancing achieved by the calibration process without FR4 package (a) and its zoomed view (b); CASE 1                                |

|            |                                                                                                                                                                    |

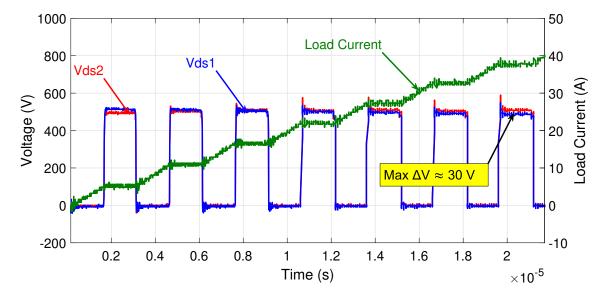

| 4.16 | Experimental results: voltage balancing after adding the traditional planar                     |     |

|------|-------------------------------------------------------------------------------------------------|-----|

|      | package (a) and its zoomed view (b); CASE 2                                                     | 92  |

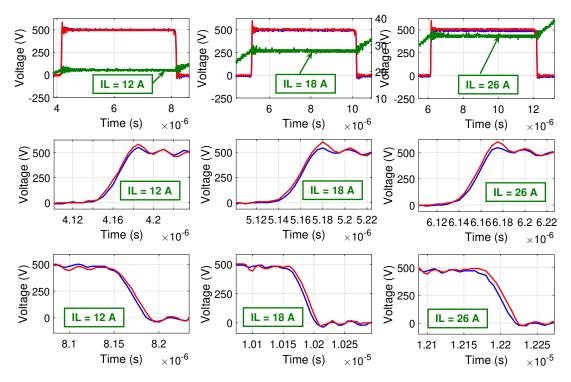

| 4.17 | Experimental results: voltage balancing after adding the proposed MSP pac-                      |     |

|      | kage (a) and its zoomed view (b); CASE 3                                                        | 93  |

| 4.18 | Intrinsic capacitance variations as a function of drain-source voltage of SiC-                  |     |

|      | MOSFETs C2M0160120 (1200V, 19A) [92]                                                            | 94  |

| 4.19 | Simplified SiC-MOSFET model                                                                     | 94  |

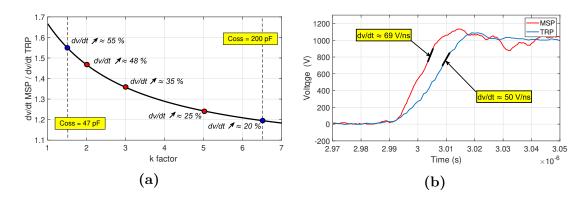

| 4.20 | Predicted $dv/dt$ improvement as a function of k factor $(C_{oss}/C_{pac})$ (a), and            |     |

|      | measured $dv/dt$                                                                                | 96  |

| 4.21 | Classical gate driver (a), and its parasitic elements (b)                                       | 97  |

| 4.22 | Electrical circuit of classical packaging and gate drive circuitry (a), and its                 |     |

|      | simplified high frequency circuit (b)                                                           | 98  |

| 4.23 | Simplified electrical circuit of classical packaging and gate drive circuitry                   | 99  |

| 4.24 | Electrical circuit of MSP packaging and gate drive circuitry (a), and its sim-                  |     |

|      | plified high frequency circuit (b)                                                              | 100 |

| 4.25 | Current distribution in the MSP electrical circuit                                              | 101 |

| 4.26 | Novel Proposed Multi-Step Packaging                                                             | 103 |

| 4.27 | Simulation results: voltage sharing between four series-connected as a function                 |     |

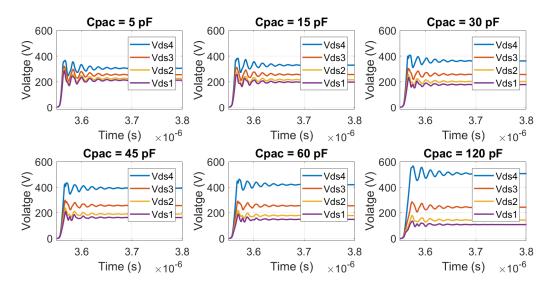

|      | of $C_{pac}$ (classical planar package)                                                         | 105 |

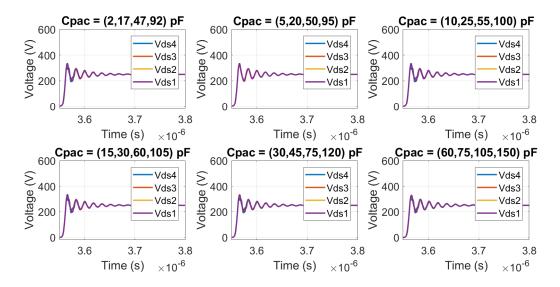

| 4.28 | Simulation results: voltage sharing between four series-connected as a function                 |     |

|      | of $C_{pac}$ (proposed MSP package)                                                             | 106 |

| 4.29 | Simulation results: middle point switching speed as a function of $C_{pac}$ (clas-              |     |

|      | sical planar package)                                                                           | 106 |

| 4.30 | Simulation results: middle point switching speed as a function of $C_{pac}$ (pro-               |     |

|      | posed MSP package)                                                                              | 107 |

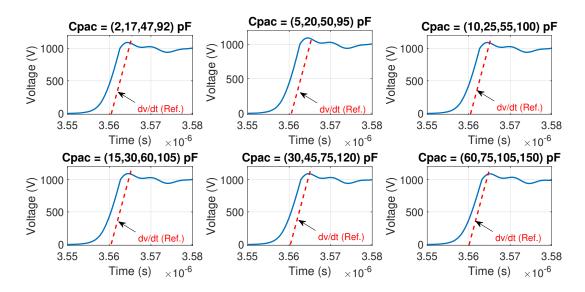

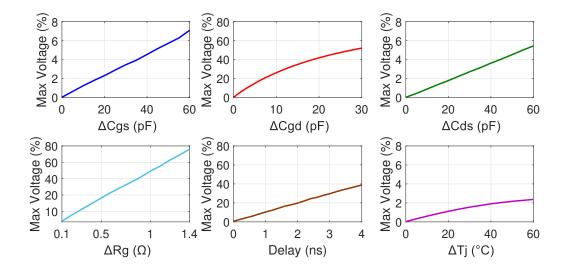

| 4.31 | Sensitive analysis results                                                                      | 108 |

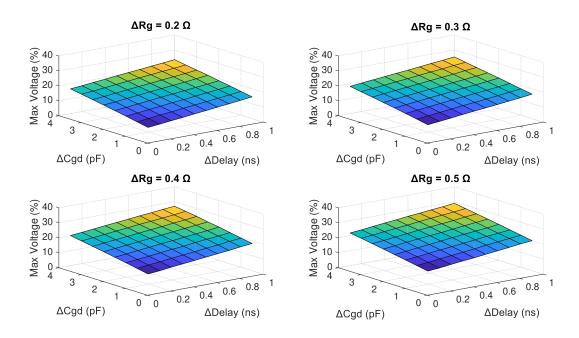

|      | Parametric analysis results as a functions of $\Delta R_g$ , $\Delta C_{gd}$ and $\Delta delay$ | 110 |

|      | Switching cell and package prototypes                                                           | 111 |

|      | Experimental results: voltage unbalancing across two series-connected SiC-                      |     |

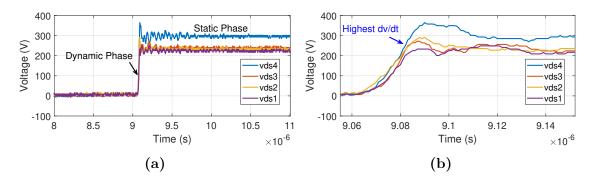

| 1.01 | MOSFETS; classical planar package.                                                              | 112 |

| 4 35 | Experimental results: voltage balancing across two series-connected SiC-MOSFI                   |     |

| 1.00 | proposed MSP package                                                                            | 112 |

| 4 36 | Experimental results: voltage balancing across two series-connected SiC-MOSFI                   |     |

| 4.00 | as a function of the load current; proposed MSP package                                         |     |

| 1 27 | Experimental results: output waveforms (a) and middle point switching speed                     | 110 |

| 1.J1 | (b) as a function of the load current; proposed MSP package                                     | 114 |

| 190  | . ,                                                                                             |     |

| 4.00 | Experimental results: voltage sharing performance between two series-connected                  |     |

| 4.90 | at light loads.                                                                                 |     |

| 4.39 | MSP thermal resistance 1D model                                                                 | GII |

| 4.40 | Junction temperature increase among the series-connected devices as a func-            |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | tion of the thermal conductivity(a) and its zoomed view (b) for $P_s = 60 \text{ W}$ , |     |

|      | $T_j = 110$ °C, $T_a = 25$ °C and $R_{thjc} = 0.1$ °C/W                                | 116 |

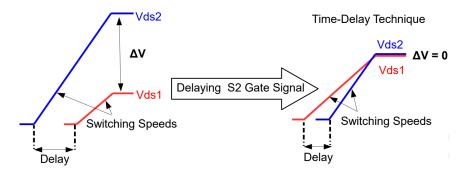

| 5.1  | Classical time-delay control technique                                                 | 119 |

| 5.2  | Classical active gate current driver technique                                         | 120 |

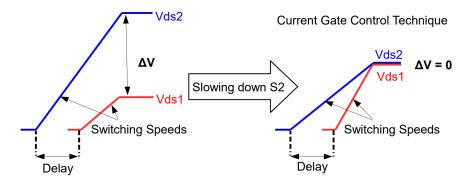

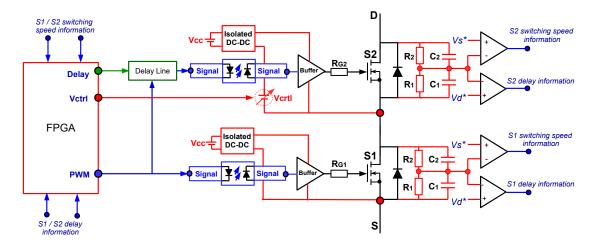

| 5.3  | Proposed active gate driver concept                                                    | 121 |

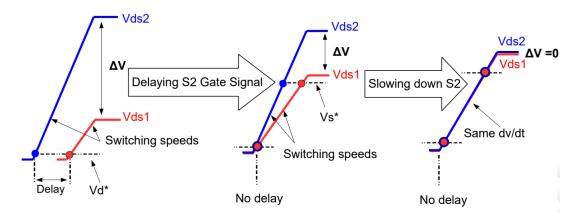

| 5.4  | Active gate driver with a double active control                                        | 122 |

| 5.5  | Ideal turn-OFF process for SiC-MOSFETs                                                 | 123 |

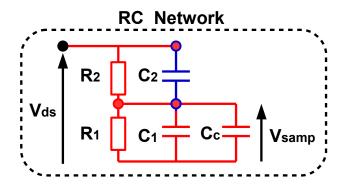

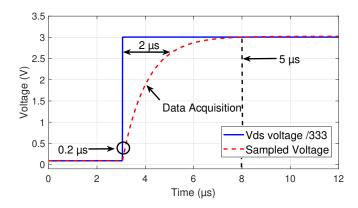

| 5.6  | RC network circuit.                                                                    | 124 |

| 5.7  | Delay on the RC circuit response                                                       | 124 |

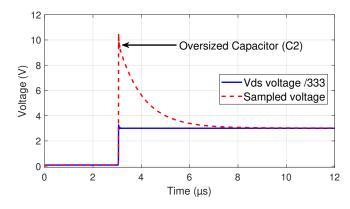

| 5.8  | RC circuit response when $C_2$ is oversized                                            | 125 |

| 5.9  | Ideal RC circuit response                                                              | 125 |

| 5.10 | Delay and $dv/dt$ control strategies                                                   | 126 |

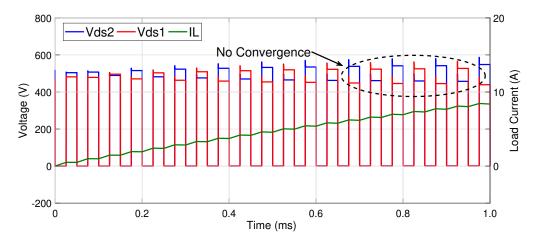

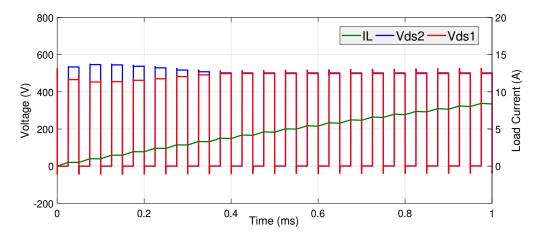

| 5.11 | Simulation result of voltage sharing performance without AGD control tech-             |     |

| 5.12 | nique                                                                                  | 127 |

| J.1_ | trol technique when $Delay = 0.1 \ ns$ and $v_i = 0.1 \ V. \ldots$                     | 128 |

| 5.13 | Simulation result of voltage sharing performance with th proposed AGD con-             |     |

|      | trol technique when $Delay = 0.5 \ ns$ and $v_i = 0.5 \ V.$                            | 128 |

| 5.14 |                                                                                        |     |

|      | trol technique when $Delay = 0.25 \ ns$ and $v_i = 0.25 \ V$                           | 129 |

| 6.1  | Configuration traditionnelle de commande rapprochée (a) et son schéma élec-            |     |

|      | trique (b)                                                                             | 136 |

| 6.2  | Une nouvelle configurations de commande rapprochée (a) et son schéma élec-             |     |

|      | trique(b)                                                                              | 137 |

| 6.3  | Impédance du circuit de la commande rapprochée.                                        | 138 |

| 6.4  | Packaging classique                                                                    | 139 |

| 6.5  | Première nouvelle proposition de packaging                                             | 139 |

| 6.6  | Deuxième nouvelle proposition de packaging                                             | 139 |

| 6.7  | Concept du driver actif proposé                                                        | 141 |

| 6.8  | Diagramme du driver actif proposé                                                      | 141 |

# Chapter 1 General Introduction

# 1.1 Medium-Voltage High-Power Converter Applications

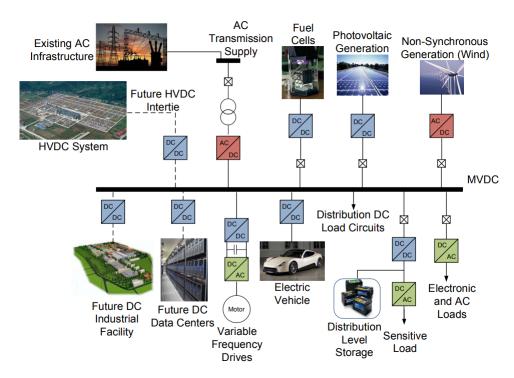

The energy transition with grid integration of distributed energy resources, motor drive systems, and data centers leads to new challenges for power generation, transmission and distribution. Hence, the medium-voltage grid and direct medium-voltage applications are becoming increasingly important. As shown in Fig. 1.1, medium-voltage high-power converters have great potential for a wide variety of medium-voltage applications, such as high-voltage direct current (HVDC), medium-voltage direct current (MVDC), smart/super/micro-grids, drives for electrical machines, medium-voltage pulse generators for plasma applications, etc [1].

The common characteristic of the mentioned applications is the search for maximizing the efficiency and output power capability of these critical systems, which can be achieved by increasing the blocking voltage of the devices or by increasing the converter output voltage. To this end, advancements in power electronic technology areas such as semiconductor devices and converter topologies have been investigated to improve the blocking voltage, power density, and efficiency, which can lower overall system cost and electricity consumption.

Fig. 1.1. Medium-voltage applications [1]

# 1.2 Methods for Achieving Higher Voltage Capability

## 1.2.1 Wide Band Gap Devices

Silicon (Si) power devices have dominated the world of power electronics in the last years, and they have proven to be efficient in a wide range of applications. But high power, high frequency and high temperature applications require more than Si can deliver. Wide Band-Gap (WBG) materials such as Silicon Carbide (SiC), Gallium Nitride (GaN), Gallium Oxide (Ga<sub>2</sub>O<sub>3</sub>) and diamond material have been intensively developed for power electronics applications due to the substantial advantages that their inherent material properties could realize at device level, such as high-breakdown voltage, high-operating electric field, high-operating temperature, high-switching frequency and low losses. In the last years, Silicon Carbide MOSFETs (Metal Oxide Semiconductor Field Effect Transistor) have started gaining significant importance in application areas of power electronics for medium-voltage, high efficiency, high switching frequencies and high temperatures applications. It is expected that the emergence of SiC-MOSFETs will allow power electronics to meet the increasing demand in utility or grid-scale applications [2]. However, today, the maximum voltage ratings of the existing commercial SiC-MOSFET are still only 1.7kV. Some higher voltage ratings, (10kV-15kV) SiC devices are tested in research laboratories [3,4]. Nowadays, series-connected and multi-level converter topologies are used to increase the blocking voltage capability for medium-voltage applications (up to 30 kV).

Maybe in the future, in the medium voltage range (up to 30 kV), WBG devices will be used to build compact and efficient power electronic converters without the need to use series-connected or multi-level converter topologies. However, it will open up new possibilities for series-connected and multi-level converter topologies in high-voltage applications over 30 kV. Single-phase and three-phase inverters will be operate directly at high and medium-voltage without the need to use a transformer.

### 1.2.2 Series-Connected Devices and Multi-level Converters

Series-connected devices and multilevel converter topologies are two effective ways of reaching higher voltage with low-voltage devices. Multilevel topologies offer outstanding features such as low common-mode voltage, low dv/dt stress, and lower propagated electromagnetic interference [5]. On the other hand, using individual semiconductors in series will result in lower cost and higher efficiency. Furthermore, according to the study presented in [6], using two or more medium-voltage semiconductors in series features better on-resistance and higher current density than using a single higher voltage device. Therefore, series-connected SiC-MOSFETs is an effective way to increase the blocking voltage capabilities to answer application constraints above  $1.7 \mathrm{kV}$ .

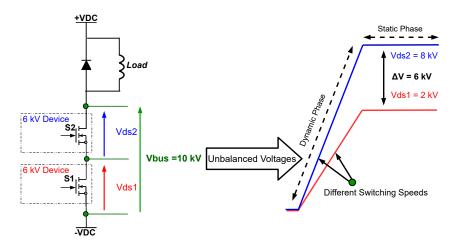

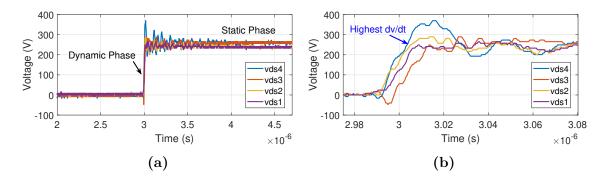

Fig. 1.2. Unbalanced voltages during dynamic and static phases.

## 1.3 Challenges of Series-Connected Devices

As explained in the previous section, using two or more medium-voltage semiconductors in series is an affective way of reaching higher breakdown voltage with low-voltage devices, which features better on-resistance and higher current density than using a single higher-voltage device. However, the two main problems related to the series association of power devices are the unequal voltage sharing among them, and the Common Mode current caused by the faster switching speed of the power devices. If these problems are not mitigated, it can result in damage to the switches in the stack and to the control system.

## 1.3.1 Voltage Balancing Problems

The majority of literature have attributed the unequal voltage sharing among stacked power devices to the tolerance in device parameters, package/layout parasitic components and gate signal timing delays [7–9]. If the device turn-off speeds are significantly different, the devices in the series stack that turn off faster will block more of the total dc bus voltage. For example, Fig. 1.2 shows two 6 kV series-connected devices operating under a 10 kV bus voltage. In an ideal case, the devices operate normally and safely, since during the turn-off switching each device blocks 5 kV. However, the drain-source voltages ( $V_{ds1}$  and  $V_{ds2}$ ) are unbalanced (dynamic and static phases) due to the causes mentioned above. In this case, the voltage  $V_{ds2}$  across the device S2 exceeds its nominal value. Consequently, the device S2 could be damaged.

### 1.3.2 Common Mode Conducted EMI

The Common Mode (CM) currents that circulate in power converters can be divided in two categories: 1) the CM currents that circulate in the power part through the power

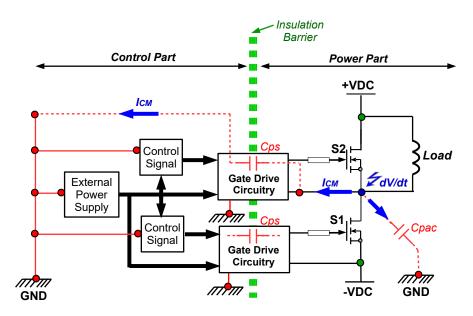

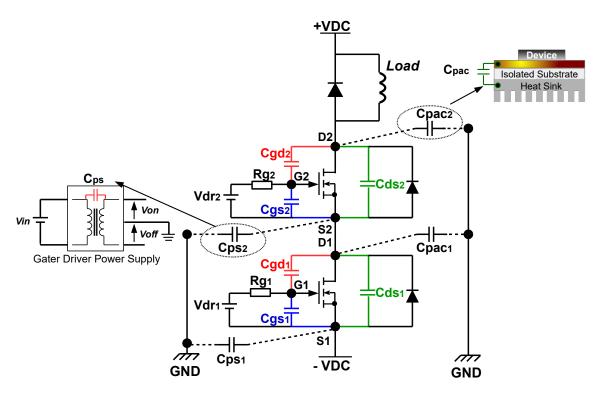

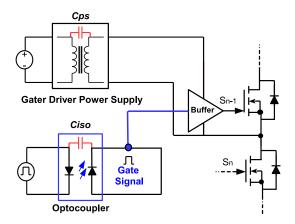

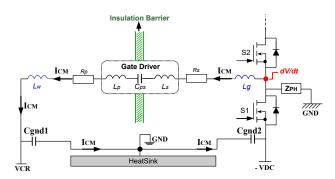

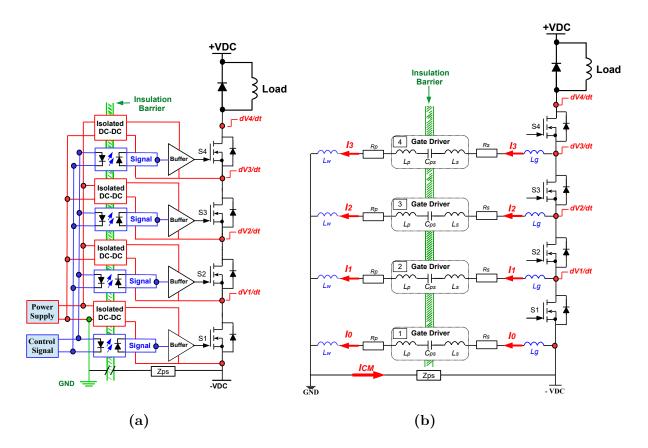

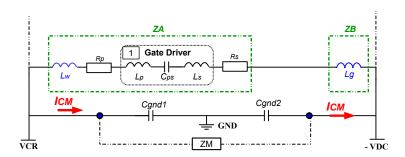

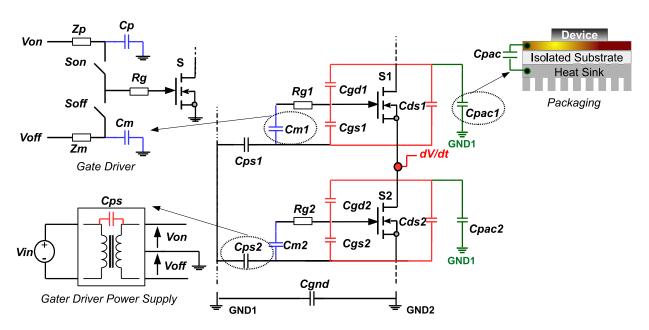

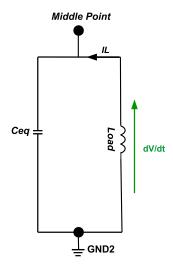

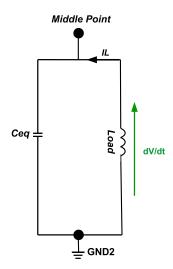

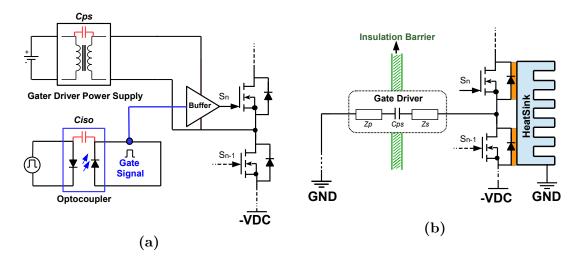

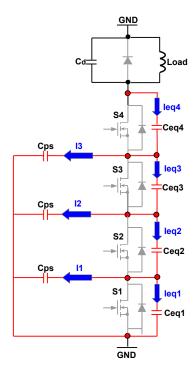

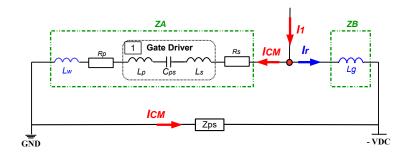

devices and the ground (through the dielectric barrier of the package) [10,11], and 2) the CM currents that circulate in the control part through the isolation barriers of the DC-DC power supplies and signal transmission functions of the gate drivers [12,13]. Focusing on the second category, i.e., on the CM currents that circulate through the parasitic capacitances introduced by DC-DC power supplies and signal transmission functions of gate drivers, in Fig. 1.3 is defined the parasitic capacitance induced by the driver power supply, which is noted  $C_{ps}$ .

Fig. 1.3. Gate driver circuitry.

As can be seen, an isolated gate driver power supply is implemented in order to isolate the control part from the power part. However, isolated gate driver power supplies introduce primary to secondary parasitic capacitances  $(C_{ps})$  due to the insulation barrier of the isolated DC-DC converters presented in the gate drive circuitry. As shown in Fig. 1.3, the gate driver parasitic capacitance  $(C_{ps})$  has a direct connection to the middle point of the power leg that corresponds to a dV/dt source. Therefore, as expressed by Eq. (1.1), the dV/dt source generates CM currents that propagate to the control part through the parasitic capacitance  $C_{ps}$ .

$$I_{CM} = C_{ps} \frac{dV}{dt} \tag{1.1}$$

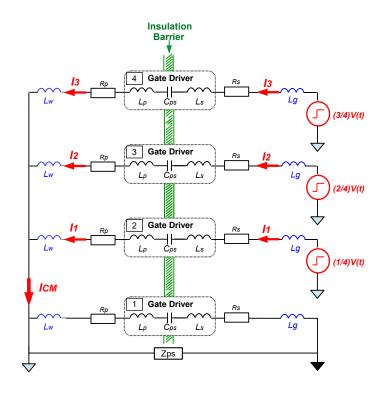

In series-connected device topologies, this problem is aggravated, since for N-devices connected in series, there are N-floating points that correspond to N-dV/dt sources. Consequently, if several isolated power supplies in the driver circuitry are used, they will introduce several primary to secondary parasitic capacitances, and as a consequence several common mode currents will circulate in the control part, which can seriously disrupt and perhaps damage the system.

### 1.4 Research Motivation and Objectives

Based upon the motivations and technological challenges of series-connected devices presented in this chapter, this work proposes a comprehensive study and new solutions to solve the main problems related to the higher voltage capability achieved by series-connected low voltage SiC MOSFETs (1.2 kV nominal voltage rating per device) for medium-voltage converter applications.

In order to study the viability and effectiveness of a series-connected converter topology, one objective of this work is to propose, develop and test natural passive solutions, such new gate driver power supply and packaging configurations in order to reduce the CM current in the control side and voltage balancing problems. Finally, this research aims to investigate a novel active gate drive method in order to improve the voltage balancing across series-connected SiC-MOSFETs. To investigate the passive and active methods proposed in this work, voltage balancing, CM current reduction, and switching speed performance are experimentally tested up to four discrete 1.2 kV SiC MOSFETs in series under a total blocking voltage of 1 kV.

# 1.5 Thesis Organization

Based upon the research objectives described above, this thesis is organized as follows:

In **Chapter 2**, it is presented a comprehensive overview of series-connected SiC-MOSFETs. The factors that can influence the voltage sharing performance and the existent voltage balancing techniques are presented.

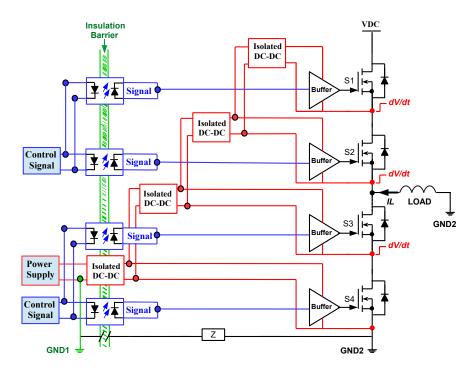

In **Chapter 3**, new gate drive power supply configurations are analysed in order to mitigate the conducted common mode (CM) currents in series-connected SiC-MOSFET applications. Furthermore, a new gate driver configuration is proposed in order to increase the dv/dt of the switching cell middle point.

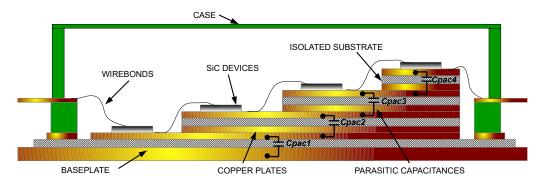

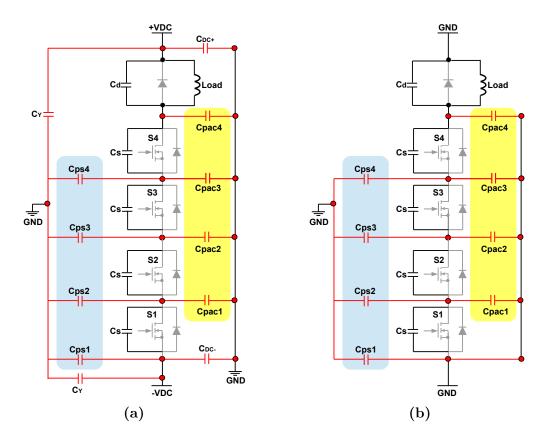

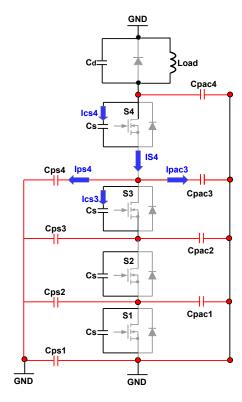

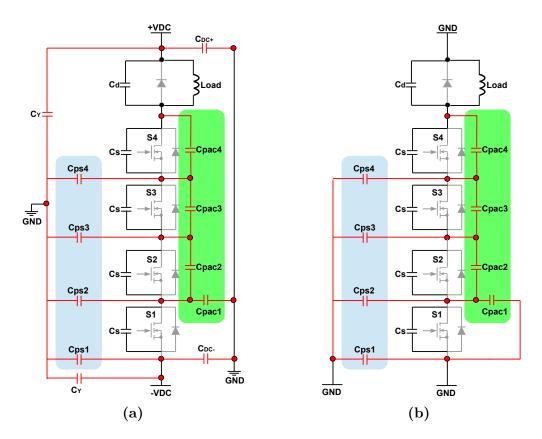

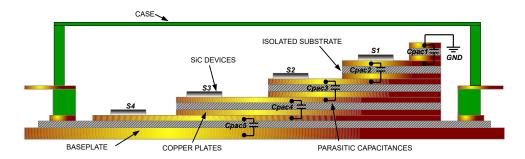

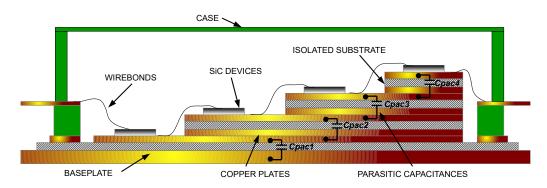

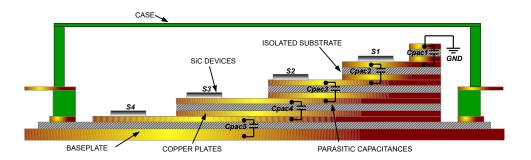

In **Chapter 4**, a Novel Multi-Step Packaging (MSP) concept for series-connected SiC-MOSFETs is analysed. The proposed package geometry considers optimal dielectric isolation for each device leading to a multi-step geometry. It has a significant impact on the parasitic capacitances introduced by the packaging structure that are responsible for voltage unbalances.

In **Chapter 5**, a novel active gate driver with a double active control is introduced. The proposed gate driver is based on the analysis of the state of the art presented in Chapter 2. The proposition is validated by numerical simulations. Some practical aspects are then proposed to go towards the experimental verifications.

# Chapter 2 State-of-the-Art

In this chapter, a comprehensive overview of series-connected SiC-MOSFETs is presented. The fundamentals of the SiC-MOSFET and its switching process are essential for understanding the principles behind any natural voltage mismatch between series-connected devices. Then, an overview of factors that can influence voltage sharing performance and the existent voltage balancing techniques are discussed in the next sections.

# 2.1 Si, SiC, GaN, Ga<sub>2</sub>O<sub>3</sub> and Diamond

In power electronics, improving the efficiency of electronic devices is crucial to reduce switching losses. Nowadays, Silicon (Si) is by far the most widely used semiconductor material for power devices. However, the intrinsic physical properties of silicon have limitations that in some domains will prevent devices based on Si material from being the candidates for the future of power electronics. As Si-based power devices are approaching their material limits, engineers and researchers have prompted a lot of efforts to find alternatives to Si-based power devices for better performances [14–16].

The search for a solution to the limitations of silicon leads to investigations of wide bandgap (WBG) semiconductors, such as Silicon Carbide (SiC), Gallium Nitride (GaN), Gallium Oxide ( $Ga_2O_3$ ) and Diamond power devices.

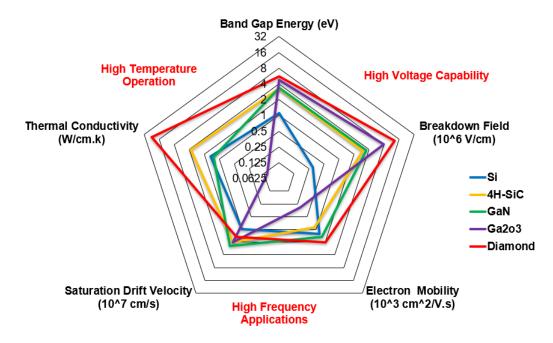

Some semiconductors are classified as wide-bandgap semiconductors because of their wider bandgap. Silicon has a bandgap of 1.1 eV and is not considered as a wide bandgap semiconductor. The bandgaps of WBG semiconductors are about three times or more that of Si as can be seen in Table 2.1.

As shown in Fig. 2.1, WBG means larger breakdown field and high band gap. It results in power devices with higher breakdown voltage capabilities. With a high electric breakdown field, much higher doping levels can be achieved; thus, device layers can be made thinner at the same breakdown voltage levels. The resulting WBG semiconductor-based power have smaller drift region resistances. This means for the same breakdown voltage WBG devices offer significantly less on-resistance than Si-based devices [14, 15, 17–19].

The high-frequency switching capability or switching speed of a semiconductor is directly proportional to its drift velocity. The drift velocities of WBG materials are more than twice the drift velocity of Si; therefore, it is expected that WBG semiconductor-based power devices could be switched at higher frequencies than their Si counterparts. Moreover, higher

Table 2.1 Physical Properties of Silicon (Si), Silicon Carbide (4H-SiC), Gallium Nitride (GaN),  $Ga_2O_3$ , and Diamond [14–19].

| Propriety                               | Si  | 4H-SiC | GaN | $Ga_2O_3$ | Diamond |

|-----------------------------------------|-----|--------|-----|-----------|---------|

| Band Gap Energy $(eV)$                  | 1.1 | 3.2    | 3.4 | 4.7       | 5.50    |

| Breakdown Field ( $10^6\ V/cm)$         | 0.3 | 3.0    | 3.5 | 8.0       | 13.0    |

| Electron Mobility $(10^3 cm^2/V.s)$     | 1.3 | 0.9    | 1.5 | 0.3       | 2.00    |

| Saturation Drift Velocity $(10^7 cm/s)$ | 1.0 | 2.0    | 2.5 | 2.0       | 1.50    |

| Thermal Conductivity $(W/cm.k)$         | 1.5 | 3.7    | 1.3 | 0.1       | 22.9    |

Fig. 2.1. Material properties comparison between Si, 4H-SiC, GaN, Ga<sub>2</sub>O<sub>3</sub>, and Diamond.

drift velocity allows charge in the depletion region of a diode to be removed faster; therefore, the reverse recovery current of WBG semiconductor based diodes is smaller, and the reverse recovery time is shorter [14, 15, 17–19].

WBG semiconductors have the advantage of high-temperature operation and more radiation hardening. As the temperature increases, the thermal energy of the electrons in the valence band increases. At a certain temperature, they have sufficient energy to move to the conduction band. This is an uncontrolled conduction that must be avoided. The temperature at which this happens is around 150°C for Si [15]. For WBG semiconductors, the bandgap energy is higher; therefore, electrons in the valence band need more thermal energy to move to the conduction band. For example, this intrinsic temperature for SiC is around 900°C. As a result, WBG semiconductors can withstand more heat and radiation without

losing their electrical characteristics. In other words, they can be used in extreme conditions where Si-based devices cannot be used.

Among the presented wide bandgap semiconductor, in the mid power range application field, GaN devices offer a higher break down field than Si devices and a better high frequency performance. The current GaN devices market is mainly dominated by devices less than 200V. 600V GaN devices are expected to take off and keep growing. While SiC is used for high-voltage applications, GaN is mainly used for low voltage.

The  $Ga_2O_3$  is a currently hardly recognized wide bandgap semiconductor for power electronic application. It targets the mid to high power range. Its future development is still uncertain. Compared to SiC, the lower heat conductivity of  $Ga_2O_3$  is a drawback [20].

Diamond is the wide bandgap semiconductor with the best physical properties in almost every sense with respect to power electronics. Although Diamond technology is more developed than  $Ga_2O_3$ , Diamond is still in maturation process [21]. Maybe in future high power applications that push all power densities and operation voltages to the upper limit, the semiconductor diamond would be the best choice.

SiC devices already offer a mature device processing technology. Its major application lies in the field of high power electronics where reliability plays a major role. In the last years, SiC-MOSFETs have been used in medium-voltage applications due to its higher voltage capability and switching performances. Nowadays, SiC-MOSFETs are the best candidate to replace Si-based IGBTs in the medium-voltage high-power converter applications [14].

### 2.2 Silicon Carbide MOSFETs

When switch mode operation of the SiC-MOSFET is considered, the goal is to switch between the ON and OFF states of the device in the shortest time possible in order to reduce switching losses. Since the practical switching times of the SiC-MOSFETs are very fast, a very small discrepancy between the switching speed of the series-connected SiC-MOSFETs can generate considerable voltage balancing problems. Therefore, to better understand the voltage sharing behaviour across the series-connected devices, it is important to understand the SiC-MOSFET fundamentals.

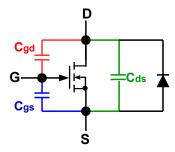

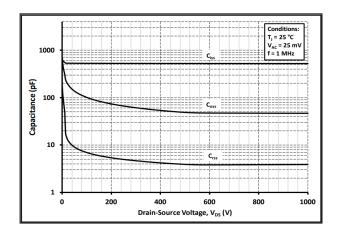

In Fig. 2.2 is shown a model that represents a SiC-MOSFET. As can be seen, it includes three capacitors connected between the three terminals of the device. Two of these capacitors, the  $C_{gs}$  and  $C_{gd}$  capacitors correspond to the actual geometry of the device while the  $C_{ds}$  capacitor is the capacitance of the drain source diode of the transistor (body diode). None of the above mentioned capacitance values are defined directly in the transistor data sheets. Their values are given indirectly by the input capacitance  $(C_{iss})$ , reverse transfer capacitance  $(C_{rss})$ , and output capacitance  $(C_{oss})$  values and must be calculated as shown in Eqs. (2.1),

Fig. 2.2. SiC-MOSFET device model.

(2.2) and (2.3), respectively. Ultimately, the switching performance of the transistor is determined by how quickly the voltages can be changed across these capacitors.

$$C_{iss} = C_{qd} + C_{qs} \tag{2.1}$$

$$C_{rss} = C_{gd} (2.2)$$

$$C_{oss} = C_{ad} + C_{ds} \tag{2.3}$$

The turn-ON/OFF procedures for Si and SiC MOSFETs are similar. However, there are some important specific characteristics of the SiC-MOSFETs that have to be taken into account, especially for switching control optimization and calculation methods for switching losses.

### 2.2.1 Turn-ON Procedure

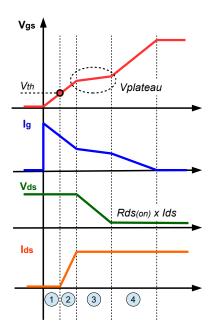

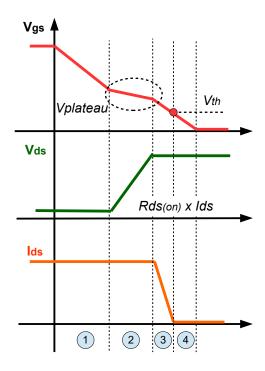

The turn-ON event of the SiC-MOSFET can be divided into four intervals as depicted in Fig. 2.3.

**Time-interval 1:** in the first step, the input capacitance of the device is charged from 0 V to  $V_{TH}$ . During this interval most of the gate current is charging the  $C_{gs}$  capacitor. A small current is flowing through the  $C_{gd}$  capacitor, too. As the voltage increases at the gate terminal, the voltage across  $C_{gd}$  has to be slightly reduced. This period is called the turn-on delay, because both the drain current and the drain voltage of the device remain unchanged [22, 23].

**Time-interval 2:** once the gate is charged to the threshold level  $(V_{th})$ , the drain current starts to conduct through the SiC-MOSFET. More current continues to rise through the SiC-MOSFET as  $V_{gs}$  increases. The SiC-MOSFET is in the saturation region during this period since  $V_{ds}$  is still blocking voltage [22, 23].

**Time-interval 3:** entering into the third period of the turn-on procedure the gate is already charged to the sufficient voltage (*V plateau*) to carry the entire load current and the rectifier diode is turned off. That now allows the drain voltage to fall. Almost all the gate

current available from the driver is diverted to discharge the  $C_{gd}$  capacitor to facilitate the rapid voltage change across the drain-to-source terminals. The drain current of the device stays constant since it is now limited by the DC current source [22, 23].

Miller-plateau: as shown in Figs. 2.3 and 2.4, an important characteristic feature of few SiC-MOSFETs is their non-flat miller plateau voltage as observed in typical silicon MOSFETs and IGBTs, which means the gate-source voltage of the SiC-MOSFET changes during the drain-source voltage fall and rise transitions instead of remaining constant. This is due to the low transconductance  $(g_m)$  of SiC-MOSFETs [24]. In other words, a relatively small amount of gate voltage is needed to cause a large change in the drain current.

Fig. 2.3. Ideal turn-ON process for SiC-MOSFETs.

Time-interval 4: the last stage of the turn-on is to fully enhance the conducting channel of the SiC-MOSFET by applying a higher gate drive voltage. The final amplitude of  $V_{gs}$  determines the ultimate on-resistance of the device during its on-time. Therefore, in this fourth interval,  $V_{gs}$  is increased from Vplateau to its final value. This is accomplished by charging the  $C_{gs}$  and  $C_{gd}$  capacitors, thus gate current is now split between the two components. While these capacitors are being charged, the drain current is still constant, and the drain-to-source voltage is slightly decreasing as the on-resistance of the device is being reduced [22, 23]. A drop voltage  $(R_{ds(on)}.I_{DS})$  across the drain to source terminals is still present due the specific on-resistance.

### 2.2.2 Turn-OFF Procedure

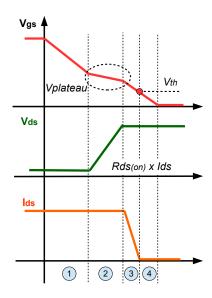

As shown in Fig. 2.4, the description of turn-off procedure for the SiC-MOSFET transistor is similar to the turn-on steps.

Fig. 2.4. Ideal turn-OFF process for SiC-MOSFETs.

**Time-interval 1:** the first time interval is required to discharge the  $C_{iss}$  capacitance from its initial value to the Miller plateau level. During this time, the gate current is supplied by the  $C_{iss}$  capacitor itself and it is flowing through the  $C_{gs}$  and  $C_{gd}$  capacitors of the SiC-MOSFET [22, 23].

**Time-interval 2:** during this time period, which corresponds to the Miller plateau in the gate voltage waveform, the  $V_{ds}$  voltage rises from  $R_{ds(on)}.I_{DS}$  to the final value of  $V_{ds}$ . The drain current of the device remain unchanged [22, 23].

Miller-plateau: it is important to highlight once again that an important characteristic feature of few SiC MOSFETs is their non-flat miller plateau voltage, which means the gate-source voltage of the SiC-MOSFET changes during the drain-source voltage fall and rise transitions instead of remaining constant [24].

**Time-interval 3:** the beginning of the third time interval is signified by the turn-on of the diode, thus providing an alternative path to the load current. The gate voltage resumes falling from Vplateau to  $V_{TH}$ . The SiC-MOSFET is in linear operation and the declining gate-to-source voltage causes the drain current to decrease and reach near zero by the end of this interval [22, 23].

**Time-interval 4:** the last step of the turn-off procedure is to fully discharge the input capacitors of the device.  $V_{gs}$  is further reduced until it reaches 0 V. The drain current and the drain voltage in the device are unchanged [22,23].

As can be seen, the SiC-MOSFET switching behaviour is a function of the parasitic capacitance values, the required voltage change across them and the available gate drive current. This emphasizes that, in a switching cell with series-connected SiC-MOSFETs, even a very small discrepancy between the device characteristics can drastically impacts

the switching speed behaviour of each SiC-MOSFET, and consequently, the voltage sharing among them.

### 2.2.3 SiC-MOSFETs: Important Characteristics

Gate-to-source voltage: SiC-MOSFETs have a relatively low transconductance compared to Si-MOSFETs. The result is a higher gate-to-source voltage required to achieve the lowest  $V_{ds}$  saturation voltage at high drain current. Si-MOSFETs achieve low  $V_{ds}$  saturation at 8 V to 10 V on the gate to source. On the other hand, SiC-MOSFETs typically require a  $V_{gs}$  voltage between 15 V to 20 V to achieve low  $V_{ds}$  saturation. The turn-on threshold voltage of SiC-MOSFETs requires larger  $V_{gs}$  transition when the SiC-MOSFET is operating as a variable resistance. The fast switching speed and low turn-on threshold of SiC-MOSFETs require a negative  $V_{gs}$  level during turn-off. Depending on the device, -2 V to -5 V drive is recommended for SiC devices. Although the SiC-MOSFET parasitic  $C_{gd}$  is very low, the high  $V_{ds} \ dV/dt$  during turn-off can result in coupling enough charge from the drain-to-gate capacitance to reach the threshold voltage if negative drive is not in place [14, 15].

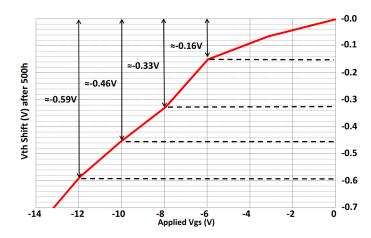

Shift in threshold voltage: the good stability of gate threshold voltage, when positive gate voltage is applied for an extended period of time is an attractive feature of the SiC-MOSFET. The shift in threshold voltage is very small and it remains stable after several hours. However, when continuous negative voltage is applied to the gate for an extended period of time, the threshold shift can be larger than that caused by positive gate voltage, e.g., the threshold drops by 0.5V or more. In other words, extensive negative gate voltage can cause a significant drop in the threshold as can be seen in Fig. 2.5, where a ROHM Semiconductor SiC-MOSFET was submitted to different negative gate-to-source voltages [14,25]. This characteristic varies from one SiC device to another.

Fig. 2.5. Behavior of Vth = f(Vgs) after 500h of operation [14, 25].

$V_{ds}$ - $I_{ds}$  characteristics: another characteristic of SiC-MOSFET devices is their no threshold voltage (knee) compared to IGBT devices, and their low conduction loss throughout

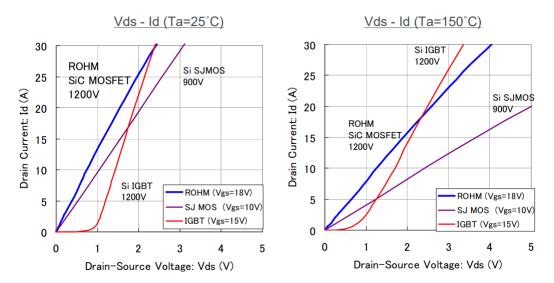

the entire current range when compared to Si-devices. For example, as shown in Fig. 2.6, Si-MOSFET on-resistance at 150 °C is more than twice that at room temperature, whereas SiC-MOSFET on-resistance increases only at a relatively low rate. This positive characteristic facilitates the thermal design for SiC-MOSFETs and provides low on-resistance at high temperatures [25]. This characteristic varies from one SiC device to another.

**Fig. 2.6.**  $V_{ds} - I_{ds}$  characteristic for a SiC-MOSFET, Si-SJMOS and a Si-IGBT at 25 °C and 125 °C [25].

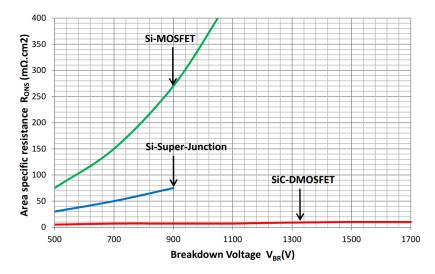

**Specific on-resistance**: SiC-MOSFET is an attractive device especially for medium power applications due to its lower conduction resistance compared to Si-MOSFET, its higher switching speed and its ability to operate at elevated temperatures [26]. In Fig. 2.7 is shown the comparison between Si and SiC-MOSFETs in terms of the specific on-resistance as a function of the breakdown voltage. The body diode of the SiC-MOSFET is a PiN diode that has 3V forward voltage drop, about 5 times that of a Si PN junction diode. However, the reverse recovery time is much smaller compared to a Si PN diode [27].

SiC-MOSFET devices present excellent characteristics and performances to be implemented in medium-voltage power converters. However, fast switching in high voltage applications may cause considerable surge voltages, spike currents, high-frequency leakage currents, and various electromagnetic interference (EMI) issues, due to high dV/dt and/or di/dt.

In series-connected SiC-MOSFET topologies, these problems are also present. Voltage balancing and EMI reduction methods applied to Si-MOSFETs/Si-IGBTs in series require new considerations for series-connected SiC-MOSFETs.

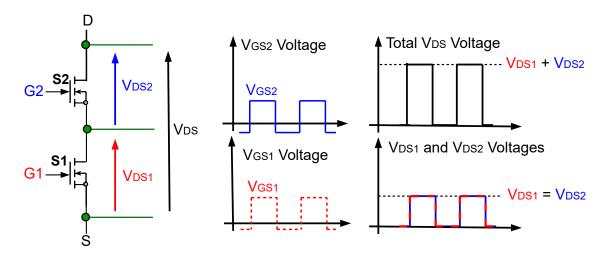

### 2.3 Series-Connected SiC-MOSFETs

Series connection is an attractive way of reaching higher breakdown voltage with low-voltage devices as shown in Fig. 2.8, where two devices are connected in series, and driven

**Fig. 2.7.** On-resistance comparison between Si-MOSFET, Si-Super-Junction and SiC-DMOSFET [26].

by the same gate signal timing. As can be seen, the two devices operate as a single device, which has a total blocking voltage  $V_{ds} = V_{ds1} + V_{ds2}$ . Note that, the  $V_{ds1}$  and  $V_{ds2}$  voltages are perfectly balanced.

Fig. 2.8. Two series-connected SiC-MOSFETs operated as a single switch.

The basic principle shown in Fig. 2.8 is a completely ideal case scenario of two series-connected devices without mismatch between device leakage currents, device parameter to-lerances, package and layout parasitic components, and gate signal timing delays [28–30]. In real experiments, these problems are present, which generate voltage balancing problems as shown in Fig. 2.9.

The unbalanced voltage problem during the static phase can be easily solved by placing a static resistor in parallel with each device at the drain-to-source terminals. However, some considerations have to be taken into account in the static resistor design:

Fig. 2.9. Voltage Balancing Problem.

- The current through the static resistor has to be very dominant when compared to the maximum leakage current of the device provided in the device's datasheet. Otherwise, the resistor has no influence on voltage balancing.

- The switching period for the series-connected MOSFETs has to be very predominant when compared to the time constant of the parallel association between each device's output capacitance  $C_{oss}$  and the static resistors. Otherwise, the  $V_{ds}$  voltage of each devices will not reach the ideal static voltage before the end of the switching period.

- The power dissipation of each resistor placed in parallel with each device needs to be considered.

As mentioned, the voltage balancing problems during the dynamic switching can be caused by several different factors, such mismatched device parameter tolerances, package and layout parasitic components, and gate signal timing delays. Unlike the static phase, the dynamic phase requires more complex methods to ensure acceptable voltage sharing across the series-connected devices.

# 2.3.1 Device Parameter Tolerances, Package and Layout Parasitic Components

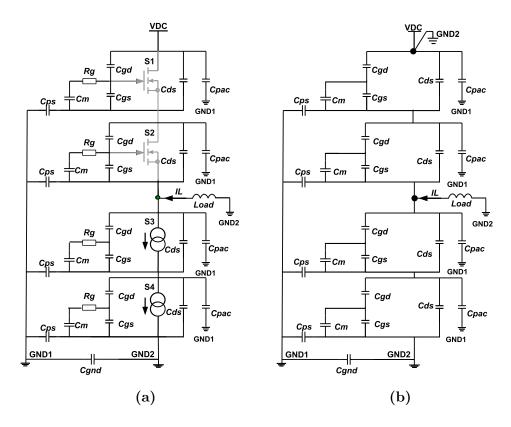

In Fig. 2.10 is shown an electrical scheme for two series-connected devices. The main elements that contribute to voltage balancing problems are presented as follows (for i = 1, 2):

- The intrinsic parasitic capacitances of the devices:  $C_{gdi}$ ,  $C_{gsi}$  and  $C_{dsi}$ .

- The gate resistances:  $R_{qi}$ .

- The gate drive voltages:  $V_{dri}$ .

• The parasitic capacitances introduced by the gate drive circuitry:  $C_{psi}$ .

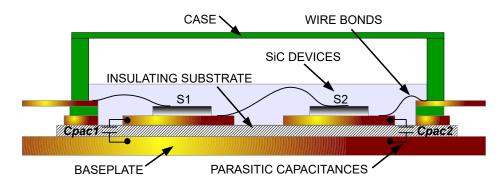

• The parasitic capacitances of the packaging :  $C_{paci}$ .

Fig. 2.10. Two series-connected SiC-MOSFETs and their parasitic elements.

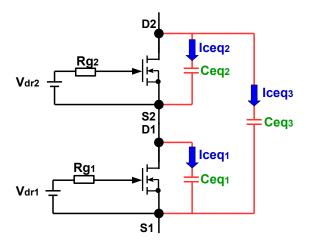

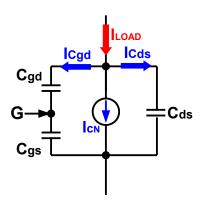

Regarding Fig. 2.10, a simplification allows better understanding the causes of unbalanced voltages across the series-connected devices. As shown in Fig. 2.11, the parasitic capacitances shown in Fig. 2.10 can be reduced to three equivalent capacitors [31], which are expressed by Eqs. (2.4), (2.5) and (2.6). Note that, to facilitate the analysis, the gate behavior is not taken into account.

$$C_{eq1} = \frac{C_{gs1} \cdot C_{gd1}}{C_{gs1} + C_{gd1}} + C_{ds1} + C_{pac1} + C_{ps2}$$

(2.4)

$$C_{eq2} = \frac{C_{gs2}.C_{gd2}}{C_{as2} + C_{ad2}} + C_{ds2}$$

(2.5)

$$C_{eq3} = C_{pac2} \tag{2.6}$$

The capacitor current  $I_{ceqi}$  is a function of the load current and gate driver i ( $V_{gsi}$  and  $R_{gi}$ ), for i=1,2. Therefore, supposing that the gate drivers are identical, and the current  $I_{ceq1}$  is equal to the current  $I_{ceq2}$ , the following equations can be written:

Fig. 2.11. Equivalent electrical scheme of two series-connected SiC-MOSFETs and their parasitic elements.

$$\frac{d_{Vds2}}{dt}.C_{eq2} = \frac{d_{Vds1}}{dt}.C_{eq1}$$

(2.7)

$$\frac{d_{Vds2}}{dt} \cdot \left(\frac{C_{gs2} \cdot C_{gd2}}{C_{gs2} + C_{gd2}} + C_{ds2}\right) = \frac{d_{Vds1}}{dt} \cdot \left(\frac{C_{gs1} \cdot C_{gd1}}{C_{gs1} + C_{gd1}} + C_{ds1} + C_{pac1} + C_{ps2}\right)$$

(2.8)

As can be seen in Eq. (2.8), the series-connected devices have different dv/dt behaviours, which generate unbalanced voltages. Even though the gate drivers are perfectly identical, and there is no mismatch between the intrinsic capacitances of the devices, they have different switching speeds due the packaging/layout parasitic capacitance  $C_{pac1}$ , and the gate drive circuitry parasitic capacitance  $C_{ps2}$ . In other words, according to Eq. (2.8), the only way to achieve perfectly balanced voltages (without any compensation method) across the series-connected devices is to ensure that the following conditions are satisfied: 1) the series-connected devices have to be identical, and 2) the gate drivers/packaging/layout have to introduce no parasitic capacitances. In this case, the voltages across the devices will be perfectly balanced, unless there are gate signal timing delays, as it will be explained in the next section.

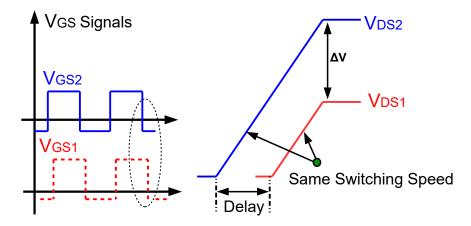

## 2.3.2 Gate Signal Timing Delays

When compared with Si-IGBTs, whose switching process lasts for several microseconds, SiC-MOSFET can finish its switching process within tens of nano-seconds [31]. However, the fast switching process means high voltage difference of  $V_{ds}$  when time delay mismatch occurs between gate signals. Fig. 2.12 shows a hypothetical case where the series-connected devices have the same switching speed. However, as can be seen, the  $V_{ds}$  voltages are unbalanced due the gate signal timing delays. In [32] is demonstrated that 20ns gate drive signal time

deviation of two SCT3120AL SiC-MOSFETs (650V, 21A) can trigger over 400V voltage difference under 800V DC bus voltage.

Fig. 2.12. Unbalanced voltage caused by gate signal timing delays.

In real experiments, all the previously mentioned causes of voltage balancing problems are present. The series-connected devices have different switching speeds and time delays between gate signals. Therefore, advanced techniques are required to mitigate voltage balancing problems in series-connected SiC-MOSFET topologies.

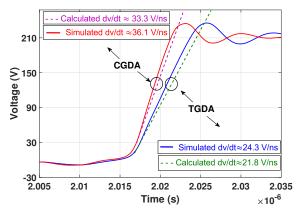

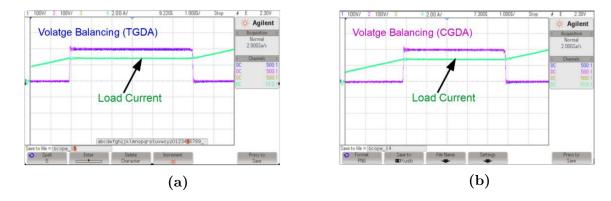

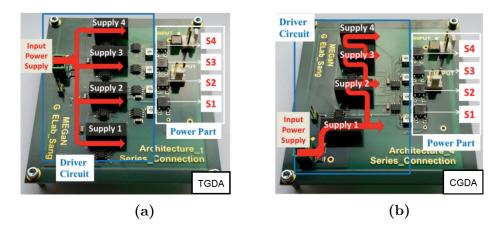

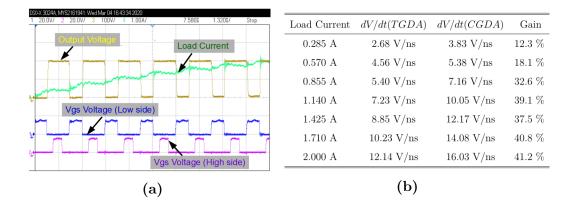

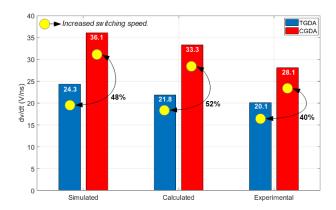

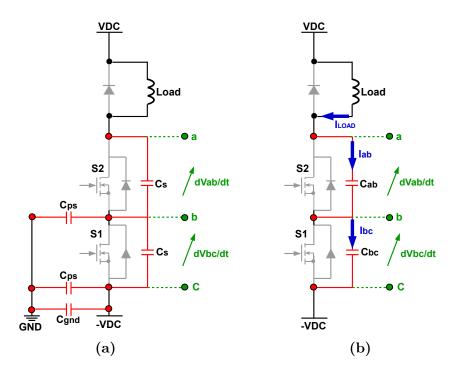

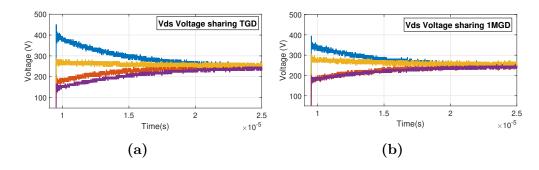

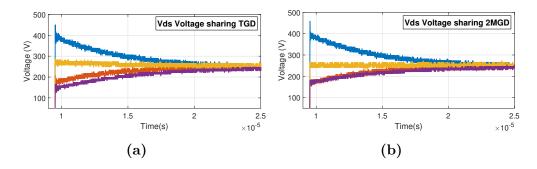

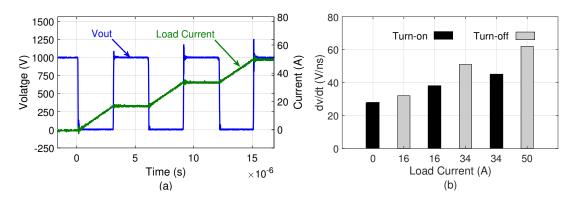

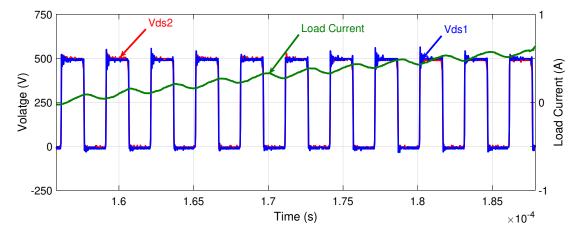

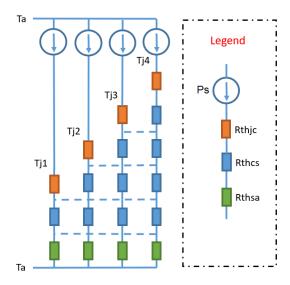

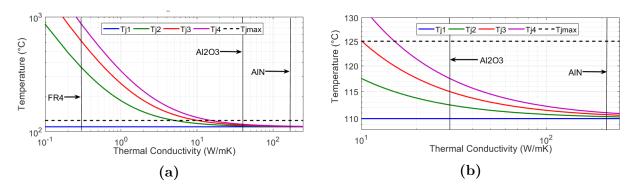

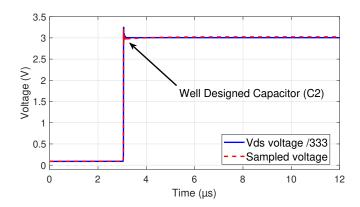

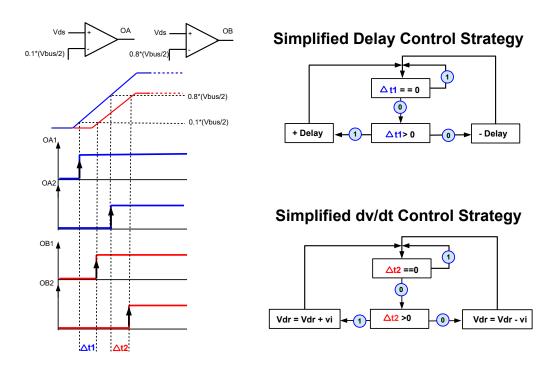

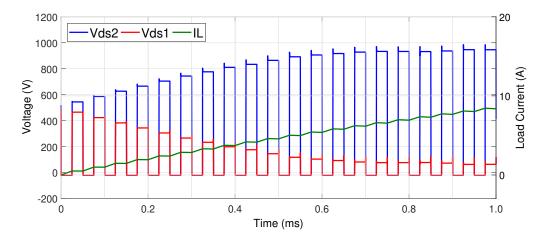

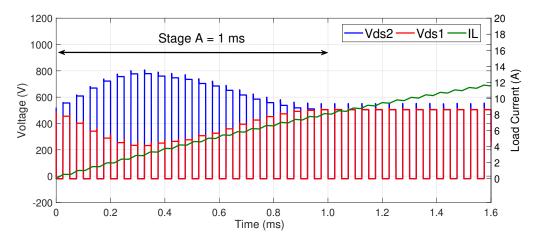

# 2.4 Voltage Balancing Techniques