# Response time analysis of parameterized dataflow applications on heterogeneous SW/HW systems

Claudio Rubattu

#### ▶ To cite this version:

Claudio Rubattu. Response time analysis of parameterized dataflow applications on heterogeneous SW/HW systems. Embedded Systems. INSA de Rennes, 2020. English. NNT: 2020 ISAR 0005. tel-03157774

# HAL Id: tel-03157774 https://theses.hal.science/tel-03157774

Submitted on 3 Mar 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

L'INSTITUT NATIONAL DES SCIENCES APPLIQUEES RENNES

ÉCOLE DOCTORALE Nº 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Signal, Image, Video

Par

# « Claudio RUBATTU »

# « Response time analysis of parameterized applications on heterogeneous HW/SW systems »

Thèse présentée et soutenue à Rennes, le 02.12.2020

Unité de recherche: IETR, UMR CNRS 6164

Thèse Nº: 20ISAR 22 / D20 - 22

## Rapporteurs avant soutenance:

Abdoulaye Gamatié Directeur de Recherche CNRS - LIRMM - UMR 5506 CNRS & UM (France)

Stéphane Mancini Maître de conférences - Laboratoire TIMA / CDSI (France)

**Composition du Jury:**

Dir. de thèse :

Président : Luigi Raffo Professeur - Università degli Studi di Cagliari (Italie)

Examinateurs: Shuvra S. Bhattacharyya Professeur - University of Maryland (USA)

Jeronimo Castrillon Professeur - Technische Universität Dresden (Allemagne)

Eduardo Juárez Martínez Professeur Agrégé - Universidad Politécnica de Madrid (Espagne)

Francesca Palumbo Professeur Agrégé - Università degli Studi di Sassari (Italie)

Maxime Pelcat Maître de conférences - IETR UMR CNRS 6164 (France)

# Response time analysis of parameterized applications on heterogeneous HW/SW systems

Claudio RUBATTU

Document protégé par les droits d'auteur

# **TABLE OF CONTENTS**

| A            | ckno            | wledge | ements                                                     | g  |

|--------------|-----------------|--------|------------------------------------------------------------|----|

| $\mathbf{A}$ | bstra           | ıct    |                                                            | 11 |

| 1            | Intr            | oducti | ion                                                        | 13 |

| 2            | HW              | //SW   | Design of Reconfigurable Systems for Signal Processing Ap- |    |

|              | plic            | ations |                                                            | 19 |

|              | 2.1             | Design | n of Signal Processing Applications                        | 20 |

|              |                 | 2.1.1  | Overview of the Main System Simulation Methods             | 20 |

|              |                 | 2.1.2  | Dataflow Model of Computations                             | 23 |

|              |                 | 2.1.3  | Timing-focused Tools in the Dataflow Context               | 25 |

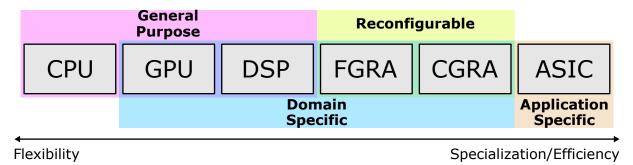

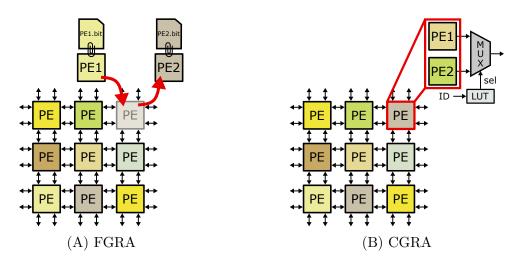

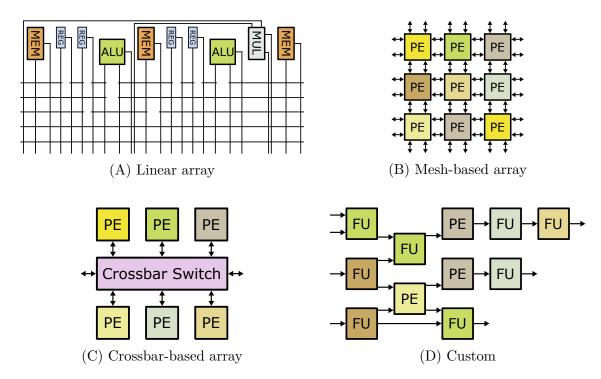

|              | 2.2             | Design | n of Coarse-Grained Reconfigurable Architectures           | 27 |

|              |                 | 2.2.1  | Coarse-Grained Reconfigurable Architectures                | 30 |

|              |                 | 2.2.2  | State-of-the-art Tools for CGRA Design                     | 32 |

|              | 2.3             | Timin  | g Analysis on MPSoCs                                       | 34 |

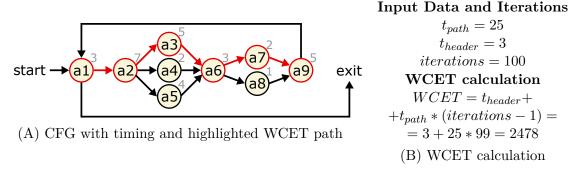

|              |                 | 2.3.1  | Fundamental Concepts in Timing Analysis                    | 35 |

|              |                 | 2.3.2  | Main Strategies in Timing Verification                     | 39 |

|              | 2.4             | Tools  | used in the Proposed Design Flows                          | 44 |

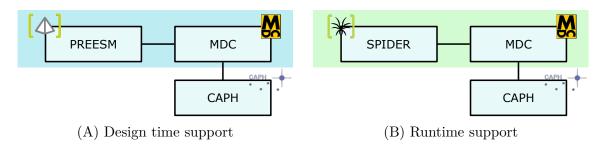

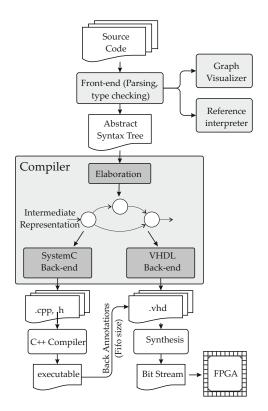

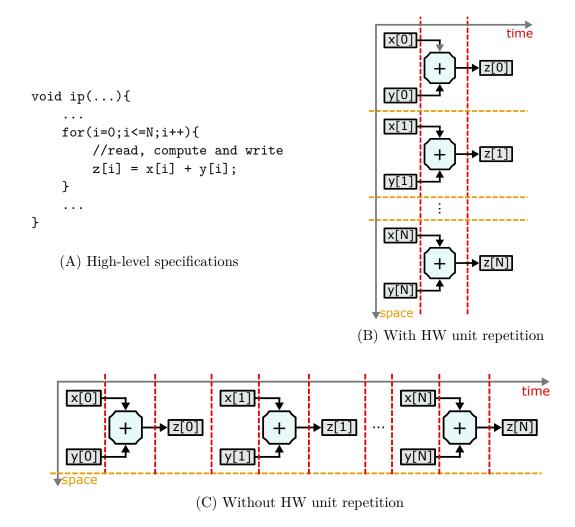

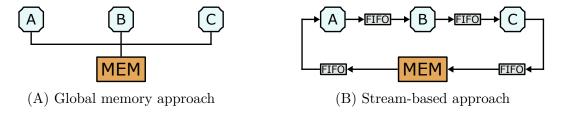

|              |                 | 2.4.1  | CAPH                                                       | 44 |

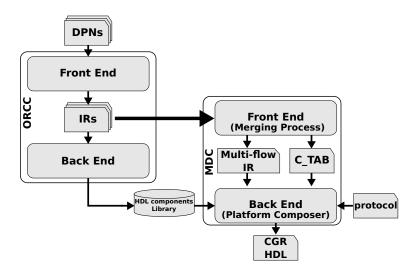

|              |                 | 2.4.2  | MDC                                                        | 45 |

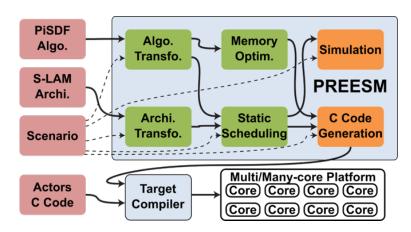

|              |                 | 2.4.3  | PREESM                                                     | 47 |

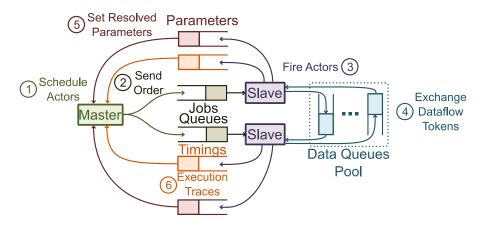

|              |                 | 2.4.4  | SPIDER                                                     | 48 |

|              | 2.5             | Chapt  | er Remarks                                                 | 49 |

| 3            | Lat             | ency E | Estimation in Hybrid Flexible HW/SW CPSs: Problem Defi-    |    |

|              | $\mathbf{niti}$ | on and | l Objectives                                               | 51 |

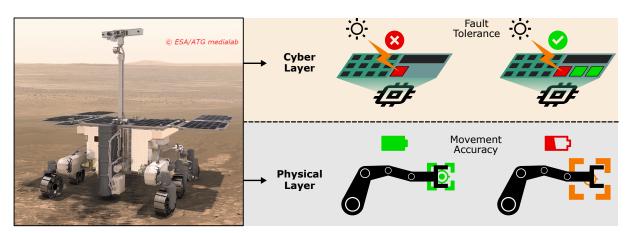

|              | 3.1             | Proble | em Definition in the CPS Hardware Context                  | 51 |

|              |                 | 3.1.1  | Discussion on Latency Information in CGR DSA Designs       | 54 |

|              |                 | 3.1.2  | Motivation on Creating DFF HLS CPS Hardware Design         | 56 |

# TABLE OF CONTENTS

|   |     | 3.1.3   | Objectives of this Thesis on Hardware Design Automation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57 |

|---|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 3.2 | Proble  | em Definition in the CPS Parallel Software Context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57 |

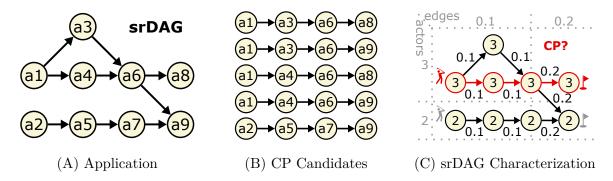

|   |     | 3.2.1   | Application Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58 |

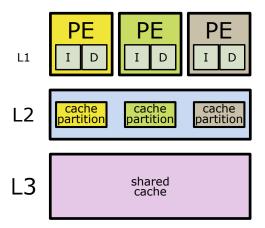

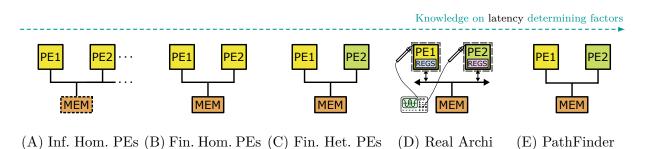

|   |     | 3.2.2   | Discussion on the Levels of Exploitable Architectural Information $$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60 |

|   |     | 3.2.3   | Motivating Example: Latency Evaluation of a DAET Tagged DAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|   |     |         | Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63 |

|   |     | 3.2.4   | Objectives on Software Latency Predictability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64 |

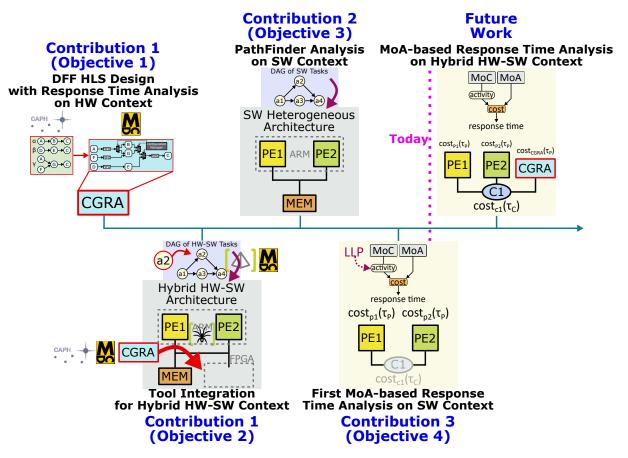

|   | 3.3 | Proble  | em Definition in the Hybrid Hardware-Software Context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65 |

|   |     | 3.3.1   | Motivation on Latency Estimation for Hardware-Software Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|   |     |         | Automation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66 |

|   |     | 3.3.2   | Objectives on Latency Evaluation Hardware-Software Hybrid Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69 |

|   | 3.4 | Chapte  | er Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69 |

| 4 | Con | tnibuti | ion 1. On Ruilding a Design Toolshoin for Florible vet Pre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 4 |     |         | ion 1: On Building a Design Toolchain for Flexible yet Pre- ${ m IW/SW~CPSs}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71 |

|   | 4.1 |         | ting Latency in CGR DSAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72 |

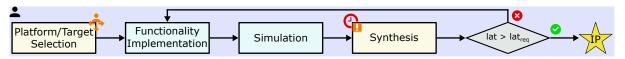

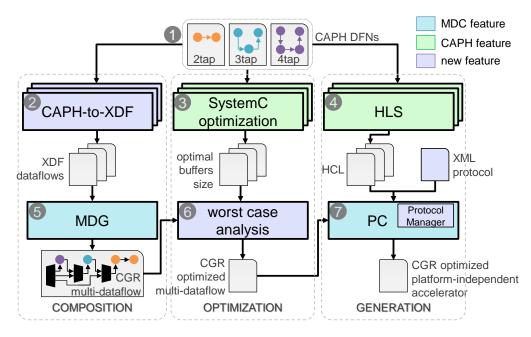

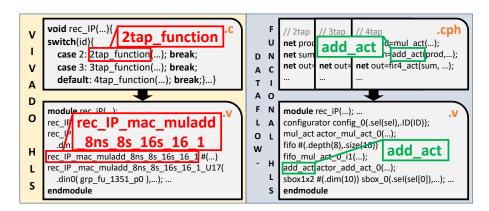

|   | 7.1 | 4.1.1   | DataFlow-Functional High-Level Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72 |

|   |     | 4.1.2   | Use-case Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 74 |

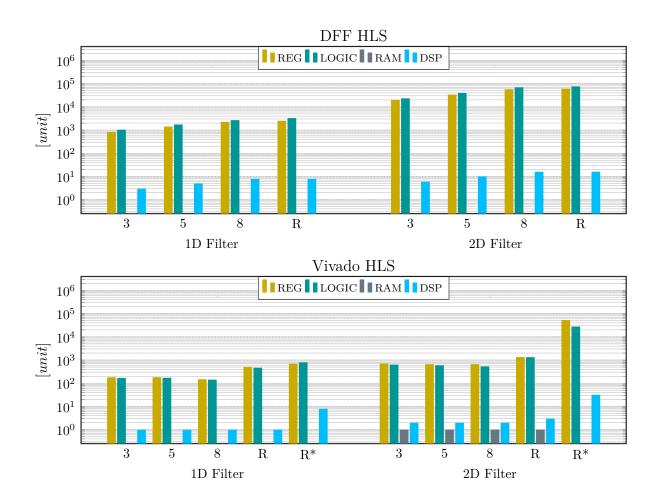

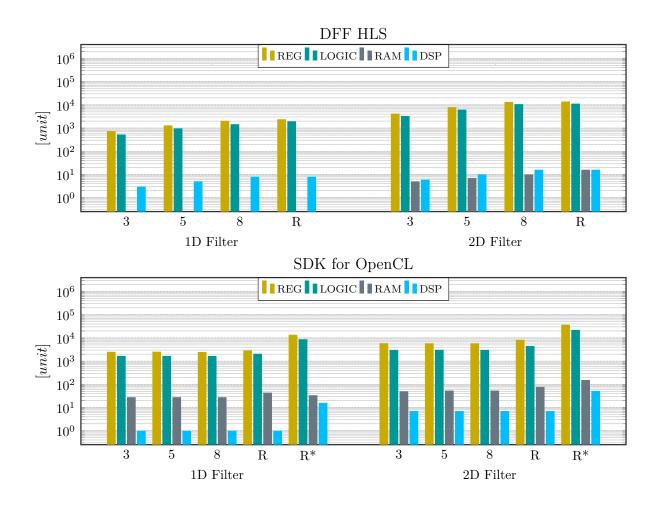

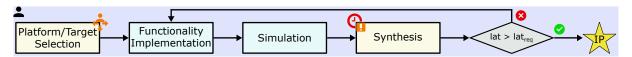

|   |     | 4.1.3   | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75 |

|   |     | 4.1.4   | Section Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77 |

|   | 4.2 |         | g Software in the Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 77 |

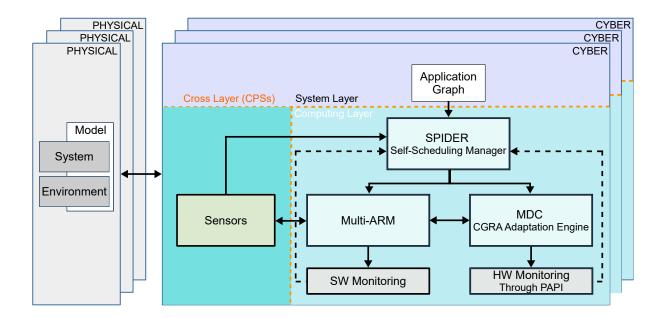

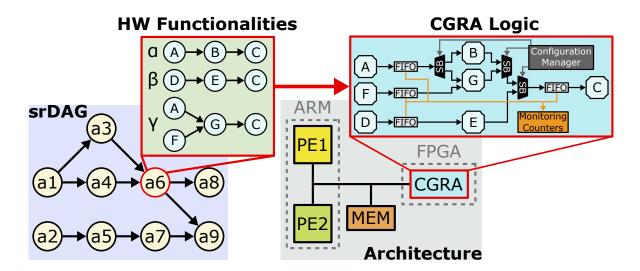

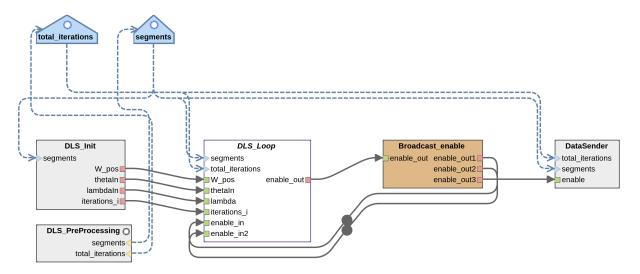

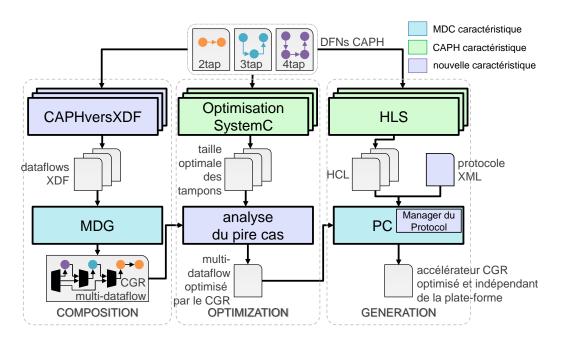

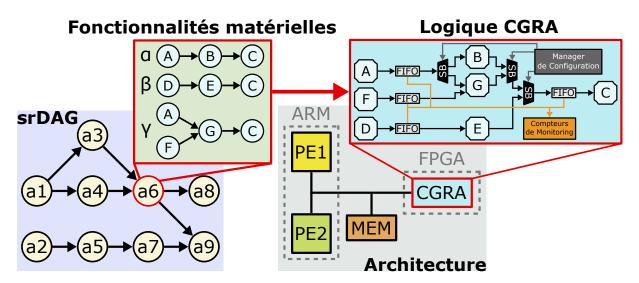

|   | 1.4 | 4.2.1   | CGR Adaptation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80 |

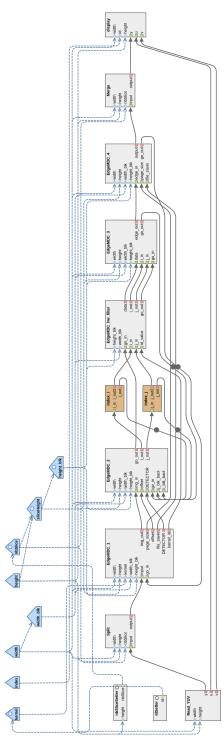

|   |     | 4.2.2   | Proof of Concept on Image Processing Application with DFF HLS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81 |

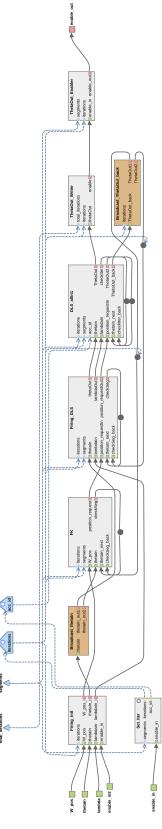

|   |     | 4.2.3   | Proof of Concept on an Inverse Kinematics Application with MDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83 |

|   |     | 4.2.4   | Section Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87 |

|   | 4.3 |         | er Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88 |

| _ | C   | .42123  | to a Deal Titule of the late o |    |

| 5 |     |         | ion 2: PathFinder: studying the application latency-causing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|   |     | vity    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89 |

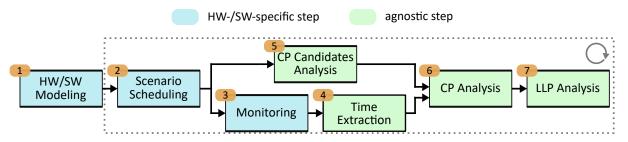

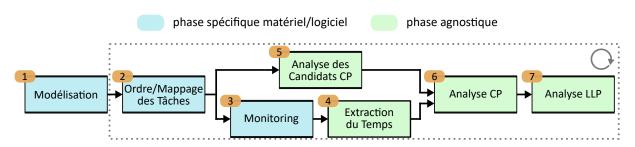

|   | 5.1 | _       | Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 90 |

|   |     | 5.1.1   | HW/SW Modeling for LLP Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 91 |

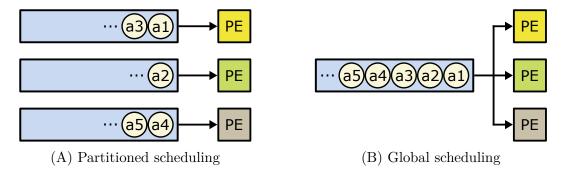

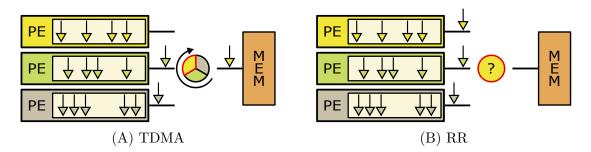

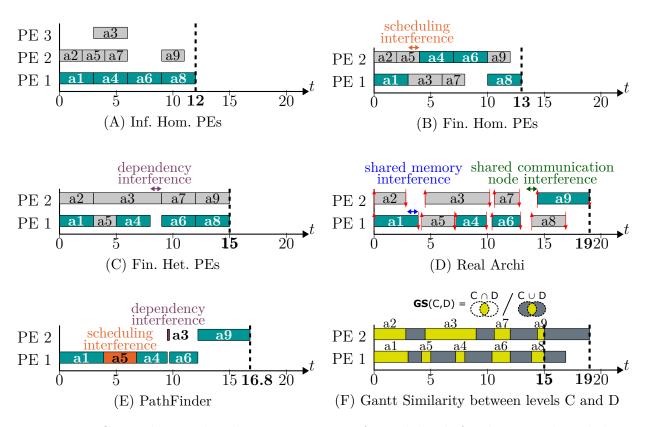

|   |     | 5.1.2   | Scheduling Scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 91 |

|   |     | 5.1.3   | Measuring Local Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91 |

|   |     | 5.1.4   | Latency Post-Characterization and Relevant Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 92 |

|   |     | 5.1.5   | Finding the Critical Path Candidates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 92 |

|              |      | 5.1.6   | Choosing the Most Probable CP                                       | . 93   |

|--------------|------|---------|---------------------------------------------------------------------|--------|

|              |      | 5.1.7   | Finding the LLP                                                     | . 95   |

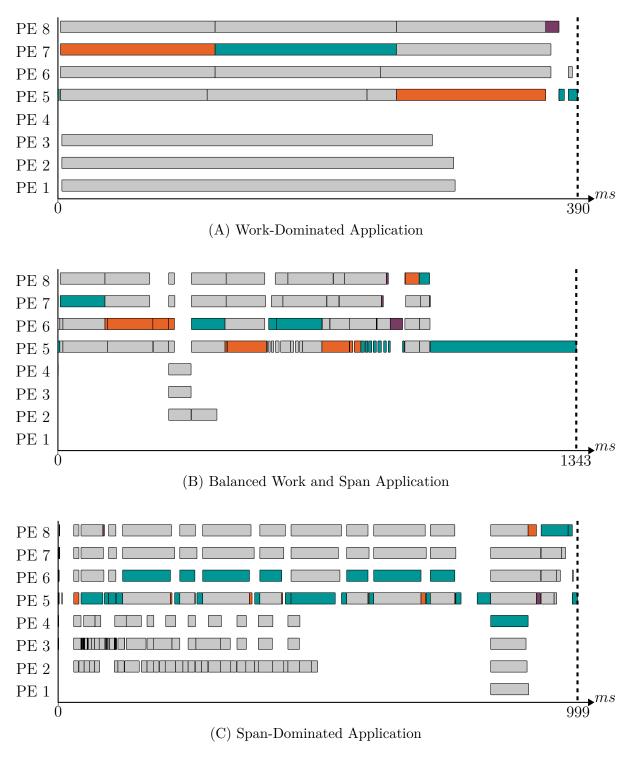

|              | 5.2  | Assess  | ment                                                                | . 98   |

|              |      | 5.2.1   | Use-case Applications                                               | . 98   |

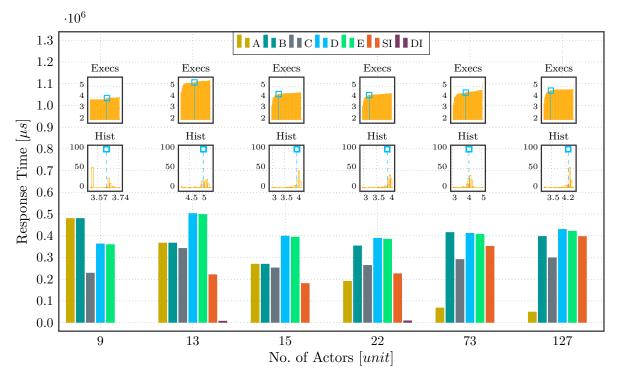

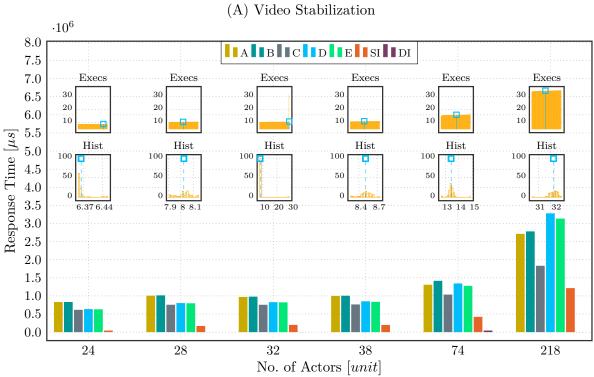

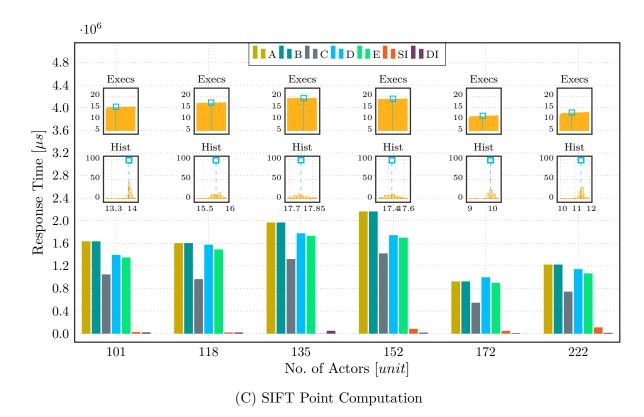

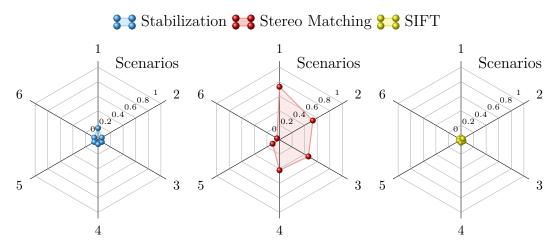

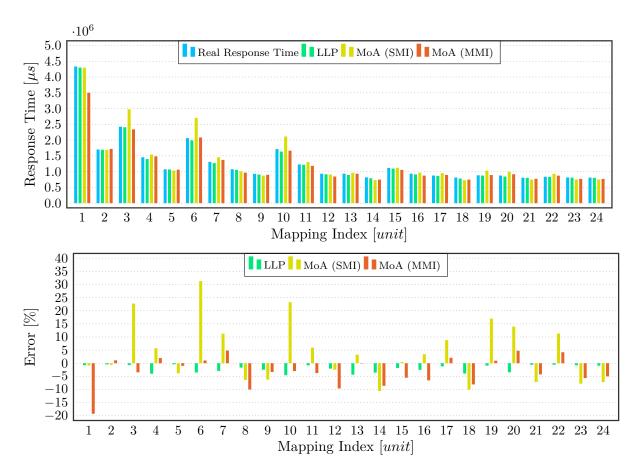

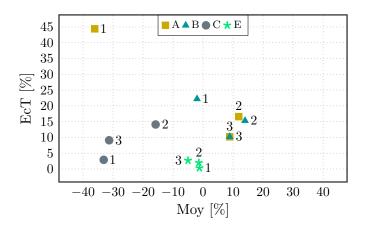

|              |      | 5.2.2   | Experimental Results                                                | . 104  |

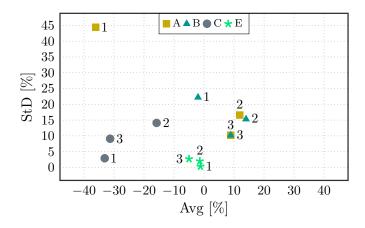

|              |      | 5.2.3   | Gantt Similarity Analysis                                           | . 108  |

|              |      | 5.2.4   | Analysis of the Interferences                                       | . 109  |

|              | 5.3  | Chapt   | er Remarks and Future Works                                         | . 110  |

| 6            | Con  | tribut  | ion 3: Response time estimation through LLP Activity and            | a      |

|              | Mod  | del of  | Architecture                                                        | 113    |

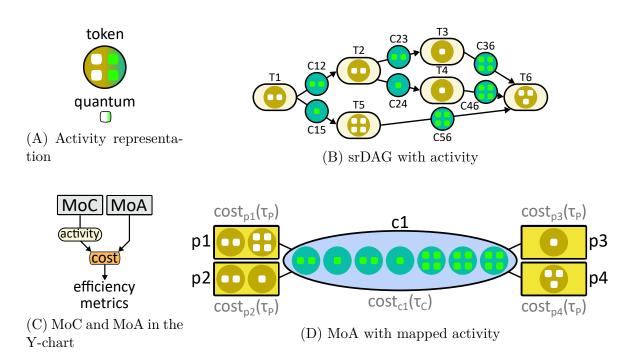

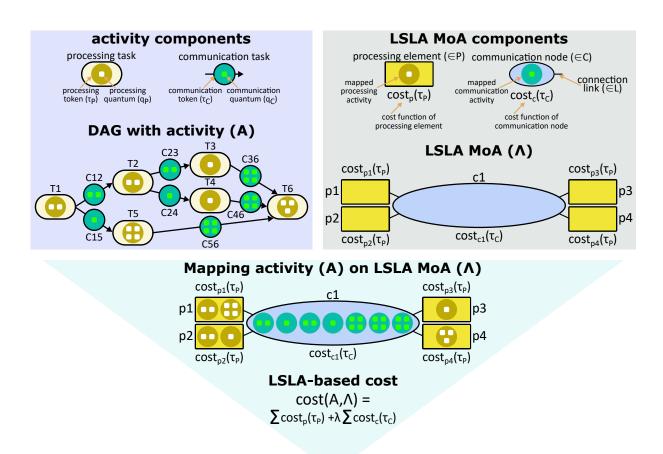

|              | 6.1  | Using   | the LSLA MoA for LLP-based Activity                                 | . 115  |

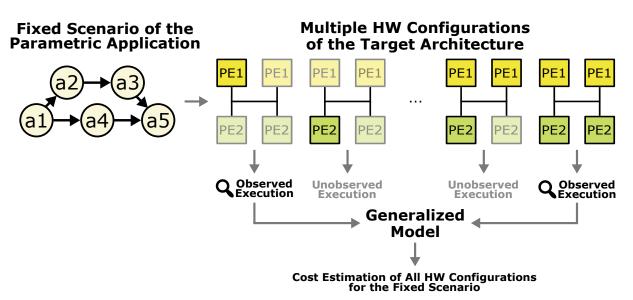

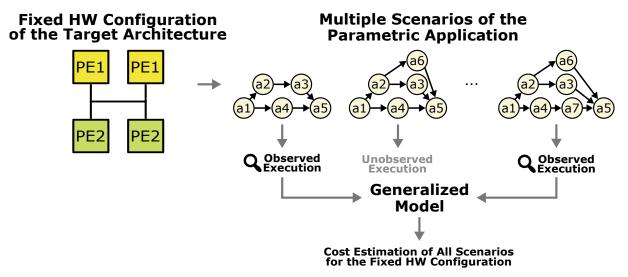

|              | 6.2  | The L   | ong Road Towards the Fully Generalized MoA                          | . 118  |

|              | 6.3  | Traini  | ng an MoA from System Platform Measurements                         | . 120  |

|              |      | 6.3.1   | Example of choice of the activity                                   | . 121  |

|              |      | 6.3.2   | A method for choosing the mappings                                  | . 122  |

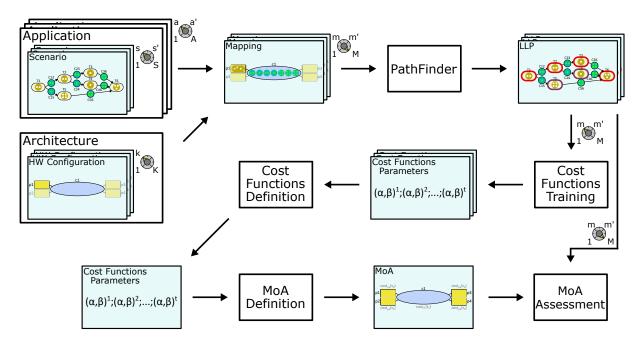

|              | 6.4  | Estima  | ation Flow through MoA with LLP-based Activity                      | . 123  |

|              | 6.5  | Assess  | ment of the Method                                                  | . 124  |

|              | 6.6  | Chapt   | er Remarks                                                          | . 126  |

| 7            | Con  | ıclusio | n                                                                   | 129    |

| $\mathbf{A}$ | Frei | nch Su  | mmary                                                               | 133    |

|              | A.1  | Introd  | uction                                                              | . 133  |

|              | A.2  | Etat d  | le l'Art                                                            | . 135  |

|              |      | A.2.1   | Conception d'applications de traitement du signal                   | . 136  |

|              |      | A.2.2   | Conception d'architectures reconfigurables à gros grains            | . 137  |

|              |      | A.2.3   | Analyse de temps sur les MPSoCs                                     | . 138  |

|              | A.3  | Définit | tion du Problème et Motivation                                      | . 139  |

|              |      | A.3.1   | Définition du problème dans le contexte du matériel du CPS          | . 139  |

|              |      | A.3.2   | Définition du problème dans le contexte du logiciel parallèle du CP | S 140  |

|              |      | A.3.3   | Définition du problème dans le contexte du matériel/logiciel hybrid | le 140 |