#### Security Techniques for Test Infrastructures

Emanuele Valea

#### ▶ To cite this version:

Emanuele Valea. Security Techniques for Test Infrastructures. Micro and nanotechnologies/Microelectronics. Université Montpellier, 2020. English. NNT: 2020MONTS042. tel-03161953

#### HAL Id: tel-03161953 https://theses.hal.science/tel-03161953

Submitted on 8 Mar 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

En SYAM – Systèmes Automatiques et Micro-électroniques

École doctorale : I2S – Information, Structures et Systèmes

Unité de recherche : LIRMM - Laboratoire d'Informatique, de Robotique et de Micro-électronique de Montpellier

# TECHNIQUES POUR LA SECURISATION DES INFRASTRUCTURE DE TEST

#### SECURITY TECHNIQUES FOR TEST INFRASTRUCTURES

#### Présentée par Emanuele VALEA Le 8 juillet 2020

Sous la direction de Giorgio DI NATALE et Bruno ROUZEYRE

#### Devant le jury composé de

| Bruno ROUZEYRE     | Professeur à l'Université de Montpellier, LIRMM, Montpellier            | Directeur de thèse    |

|--------------------|-------------------------------------------------------------------------|-----------------------|

| Giorgio DI NATALE  | Directeur de recherche au CNRS, TIMA, Grenoble                          | Co-directeur de thèse |

| Marie-Lise FLOTTES | Chargé de recherche au CNRS, LIRMM, Montpellier                         | Co-encadrant          |

| Jacques FOURNIER   | Ingénieur de recherche, CEA-Leti, Grenoble                              | Rapporteur            |

| Guy GOGNIAT        | Professeur à l'Université de Bretagne Sud, Lab-STICC, Lorient           | Rapporteur            |

| Bernd BECKER       | Professeur à l'Université de Fribourg, Allemagne                        | Examinateur           |

| Sophie DUPUIS      | Maître de conférences à l'Université de Montpellier, LIRMM, Montpellier | Examinateur           |

| Régis LEVEUGLE     | Professeur à l'Université de Grenoble Alpes, TIMA, Grenoble             | Président             |

# University of Montpellier Graduate School for Information, Structures and Systems (I2S)

## Security Techniques for Test Infrastructures

by Emanuele Valea

July 2020

Laboratory of Computer Science, Robotics, and Microelectronics of Montpellier (LIRMM)

#### **Abstract**

Test infrastructures are crucial to the modern Integrated Circuits (ICs) industry. The necessity of detecting manufacturing defects and preventing system failures in the field, makes their presence inevitable in every IC and its sub-modules. Unfortunately, test infrastructures also represent a security threat due to the augmented controllability and observability on the IC internals that they typically provide. In this thesis, we present a comprehensive analysis of the existing threats and the respective countermeasures, also providing a classification and a taxonomy of the state-of-the-art. Furthermore, we propose new security solutions, based on lightweight cryptography, for the design of test infrastructures. All proposed countermeasures belong to the category of *scan encryption* solutions and their purpose is to guarantee data confidentiality and user authentication. Each proposed solution is evaluated in terms of implementation costs and security capabilities. The results presented in this thesis, indicate that scan encryption is a promising solution for granting a secure design of test infrastructures.

#### Résumé

Le test est une étape fondamentale dans le développement des circuits intégrés modernes. Afin de pouvoir tester efficacement des circuits d'une grande complexité interne, il est nécessaire de concevoir des infrastructures de test appropriées au sein de ces circuits. Si ces infrastructures permettent des pratiques de test simples et efficaces et ce, tout au long du cycle de vie du produit, elles offrent également une porte dérobée qui peut être exploitée pour des attaques. C'est pourquoi il est nécessaire de concevoir des infrastructures de test en adoptant une approche axée sur la sécurité. De nombreuses techniques existantes utilisent des implémentations cryptographiques pour empêcher tout accès non autorisé, ou pour assurer la confidentialité et l'intégrité des données de test transmises entre l'utilisateur et le dispositif. Parmi toutes les contre-mesures existantes, l'une des plus prometteuses est le chiffrement des chaînes de scan ou scan encryption. Cette contre-mesure est basée sur le chiffrement des données de test, ce qui garantit la confidentialité des données et prévient d'une utilisation frauduleuse l'infrastructure de test. Dans cette thèse, nous abordons en détail les techniques de scan encryption. Les contributions de cette thèse peuvent être résumées comme suit:

- Nous proposons un examen approfondi de l'état de l'art en matière de sécurité des infrastructures de test. Nous proposons une nouvelle classification des menaces de sécurité et des contre-mesures. Sur la base de cette classification, nous effectuons une comparaison entre les contre-mesures existantes, et nous identifions la technique de scan encryption comme une approche prometteuse pour la sécurisation des infrastructures de test.

- 2. Nous analysons en profondeur les techniques de scan encryption les plus récentes, en identifiant deux approches différentes pour le chiffrement des données de test (c'est-à-dire, respectivement, le chiffrement par flot

- et le chiffrement par bloc). En outre, nous mettons en évidence une vulnérabilité affectant les implémentations existantes de scan encryption basées sur le chiffrement par flot.

- 3. Nous proposons des nouvelles techniques de scan encryption basées sur le chiffrement par flot, en surmontant la vulnérabilité présente dans les propositions les plus récentes. Les implémentations proposées visent différentes infrastructures de test. Leur coût est évalué en termes de surface et de temps de test.

- 4. Nous comparons les techniques proposées basées sur le chiffrement par flot, avec les techniques existantes basées sur le chiffrement par blocs. Nous soulignons les avantages et les inconvénients des deux implémentations, en fournissant des recommandations permettant aux concepteurs d'opter pour la technique de scan encryption la plus adaptée à leurs besoins.

- 5. Nous analysons la sécurité des techniques de scan encryption étudiées, et nous identifions une catégorie d'attaques qui peuvent être menées sur les circuits intégrés protégés par la scan encryption. Cette vulnérabilité affecte toutes les implémentations de scan encryption et provient d'un manque de vérification de l'intégrité des données.

- 6. Nous améliorons la scan encryption, en ajoutant un mécanisme de contrôle d'intégrité léger basé sur des codes de parité. Cette version améliorée de la scan encryption offre une protection complète contre toutes les menaces connues.

#### 1 Test des Systèmes Numériques

Le test numérique est une pratique fondamentale pour détecter la présence de défauts après production des circuits intégrés, il permet d'effectuer un tri entre circuits bons et défectueux. Les entreprises doivent faire face à des coûts élevés pour garantir un flot de tests efficace, mais cela ne peut être évité. C'est pourquoi les ingénieurs de test font de gros efforts pour garantir une détection maximale des fautes avec un coût de test minimal en termes de développement et d'application sur l'ensemble d'une production. La procédure de test de base consiste à stimuler le dispositif testé avec des séquences de test, qui stimulent la logique interne du circuit intégré

et propagent tout effet de fautes éventuelles vers les sorties. Ainsi, il est possible de détecter la présence d'une faute en comparant les réponses des tests obtenues sur un circuit avec celles dérivées des spécifications. L'objectif est de maximiser la couverture des fautes (c'est-à-dire le pourcentage de fautes détectées par rapport au total des fautes possibles), et de réduire au minimum la durée du test. Cependant, la génération des séquences de test et la mesure de la couverture des fautes sont des questions qui sont loin d'être négligeables.

La génération de séquences de test nécessite l'utilisation d'algorithmes spécifiques, appelés générateurs automatiques de séquences de test (en anglais Automatic Test Pattern Generator ou ATPG), qui sont capables de traiter la netlist des circuits et de générer un ensemble de vecteurs de test qui sont en mesure de fournir la couverture de fautes la plus élevée. Les algorithmes ATPG fonctionnent très bien et efficacement sur la logique combinatoire, mais il n'en va pas de même dans le cas de la logique séquentielle. C'est ici que les infrastructures de test entrent en jeu. Les concepteurs doivent employer la conception pour la testabilité (en anglais Design-for-Testability ou DfT) pour pouvoir générer et acheminer les vecteurs efficacement au sein du circuit. Il s'agit de modules supplémentaires qui sont ajoutés durant la conception du circuit intégré.

La technique de DfT la plus courante pour tester les circuits séquentiels est l'insertion des chaînes de scan. Dans ce scénario, les bascules du circuit sont remplacées par des bascules dit bascules scan. Ces bascules possèdent une entrée supplémentaire, appelée scan-in, qui est connectée à la sortie d'une autre bascule du circuit de façon créer un long registre à décalage appelé une chaîne de scan. Un signal scan-enable permet de faire passer toutes les bascules du mode fonctionnel (c'est-à-dire que le circuit fonctionne normalement et que les bascules fonctionnent de manière traditionnelle) au mode test (c'est-à-dire que toutes les bascules sont configurées en mode scan, et qu'elles sont déconnectées de la logique combinatoire). La première et la dernière bascule de la chaîne de scan sont connectées aux pins externes du circuit intégré par les pins scan-in et scan-out respectivement. Cette architecture permet au testeur de décaler directement les valeurs dans les registres internes du circuit en utilisant l'accès scan-in. De même, le pin de scan-out permet au testeur de décaler vers l'extérieur le contenu des registres internes.

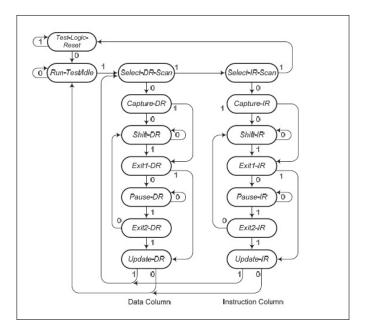

Des standards de test ont été élaborés par l'institut des ingénieurs en électricité et en électronique (IEEE) dans le but de fournir des interfaces et des procédures de test universelles. L'élaboration des normes de test de l'IEEE a commencé dans les années 1980 avec le groupe d'action conjointe sur le test (en anglais Joint Test Action Group ou JTAG), qui a commencé à développer la norme IEEE 1149.1, publiée en 1991 [1]. L'objectif du standard JTAG était le développement d'une interface de test pour les circuits intégrés qui peut être accessible lorsque les dispositifs sont soudés sur une carte électronique. Ce travail a abouti à la mise au point de la porte d'accès au test (en anglais Test Access Port ou TAP), qui représente aujourd'hui une interface universelle pour les infrastructures de test dans les circuits intégrés. Plus récemment, en 2005, la norme IEEE 1500 a été publiée [2]. Cette norme n'a pas eu la chance d'être associée à un acronyme pratique, c'est pourquoi tout le monde l'appelle encore simplement IEEE 1500. Cette norme a été développée afin de surmonter certaines limitations de la norme JTAG dans les applications liées aux systèmes sur puce (en anglais Systems on Chip ou SoC). Enfin, en 2014, la norme IJTAG (en anglais Internal JTAG) a été publiée [3]. Cette norme introduit un nouveau type d'infrastructure de test qui représente un réel progrès par rapport à la logique du JTAG. L'objectif est de fournir une infrastructure flexible permettant d'atteindre différents types de modules et d'instruments intégrés dans les SoC.

#### 2 Menaces pour la Sécurité des Infrastructures de Test

La DfT contraste de manière décisive avec la nécessité de confidentialité et de restriction d'accès qui est requise dans tout type de circuit intégré. L'infrastructure de test donne généralement à l'utilisateur une contrôlabilité et une observabilité accrues sur les détails internes du circuit. En outre, la configuration en chaîne, typique des infrastructures de test standard, garantit que plusieurs entités indépendantes à l'intérieur du système partagent la même connexion de données. Ce scénario peut entraîner de graves vulnérabilités, lorsque des données sensibles sont déplacées à travers le réseau scan. D'un point de vue général, les menaces impliquant l'infrastructure de test d'un circuit intégré appartien-

nent à deux grandes catégories:

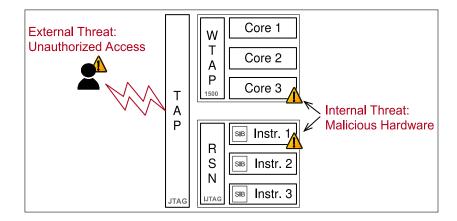

- ▶ Menaces externes: utilisateur non autorisé qui a le contrôle de l'interface TAP du dispositif.

- Menaces internes: dispositif malveillant ou cœur interne implanté dans le système par une entité tierce. Dans ce cas, le dispositif malveillant peut accéder à des données propagées par l'infrastructure à laquelle il est connecté.

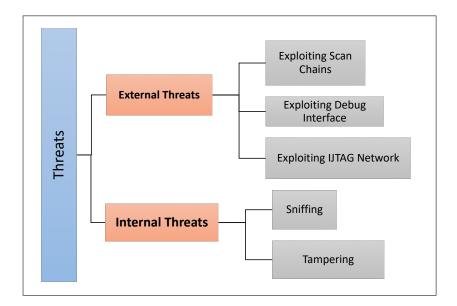

Les attaques externes et internes peuvent être classées en différentes catégories, selon le type d'action effectuée par l'attaquant et les ressources auxquelles il a accès.

Dans les menaces externes, tous les composants du système sont censés être fiables. Toutefois, si l'attaquant a un accès physique au dispositif, il est en mesure de se connecter à l'interface TAP et d'exploiter la contrôlabilité et l'observabilité mises en évidence sur le dispositif par l'infrastructure de test. En accédant à l'interface TAP, il est possible d'atteindre potentiellement chaque infrastructure qui y est connectée. Dans la littérature, nous avons identifié trois cibles différentes qui sont exploitées par les attaquants: les chaînes de scan, l'infrastructure de debug, le réseau reconfigurable IJTAG.

La tendance actuelle dans l'industrie des circuits intégrés est la globalisation de la conception et de la production. Pour cette raison, les produits finaux proviennent d'un flot de production qui implique de nombreuses entreprises différentes. Les entreprises de conception sans usine fournissent généralement des cœurs de propriété intellectuelle (IP) aux intégrateurs de SoC. Dans un flot de conception typique, l'intégrateur de SoC assemble tous les cœurs IP, provenant de différents fournisseurs, et conçoit les circuits au niveau du SoC pour garantir une intégration correcte. C'est au cours de cette phase, que l'infrastructure de test au niveau du SoC est insérée. L'infrastructure est connectée aux interfaces de test de chaque cœur IP (par exemple, le contrôleur TAP, l'enveloppe de test IEEE 1500). L'interaction entre toutes ces parties est d'une extrême importance pour la sécurité du matériel. Par exemple, l'intégrateur de SoC ne fait pas nécessairement confiance aux fournisseurs de cœur IP. De même, les vendeurs de cœur IP ne se font pas confiance entre eux. Cependant, les cœurs IP sont généralement connectés à l'infrastructure de test en chaîne. Lorsque le testeur envoie des données à un cœur IP cible par l'intermédiaire de l'interface TAP du SoC, celles-ci sont partagées avec d'autres cœurs IP. Le niveau de

confiance de l'intégrateur du SoC à l'égard des fournisseurs d'IP peut varier selon différents scénarios: 1) les cœurs IP sont vendus à l'intégrateur SoC sans enveloppes de test. Dans ce cas, l'intégrateur SoC doit lui-même envelopper les cœurs IP avec des interfaces de test fiables; 2) les cœurs IP sont vendus à l'intégrateur SoC avec des enveloppes de test. Dans ce cas, l'intégrateur SoC ne peut pas non plus faire confiance à la fonctionnalité correcte des cœurs IP, ce qui fait que les interfaces de test des dispositifs connectés à l'infrastructure de test sont considérées comme non fiables. Les mêmes considérations s'appliquent au niveau de carte électronique, où des circuits intégrés provenant de différents fournisseurs sont montés sur la même carte. En général, lorsque les données de test sont transférées par l'infrastructure de test d'un cœur IP non fiable, il n'est pas certain que celui-ci les traitera selon des règles prédéfinies. Deux menaces possibles ont été envisagées dans la littérature jusqu'à présent:

- ▶ le cœur IP non fiable *sniffs* espionne les données qui sont transférées et vole éventuellement des informations sensibles;

- ▶ le cœur IP non fiable falsifie les données de test pendant qu'elles sont transférées, et peut éventuellement corrompre leurs informations.

Pour autant que nous sachions, il n'y a aucune trace dans la littérature de dispositifs malveillants qui ont été réellement pris en train de saboter une infrastructure de test. Toutefois, certains auteurs ont publié plusieurs scénarios d'attaque impliquant des dispositifs malveillants exploitant leur connexion à l'infrastructure de test. Ces modèles de menace ont été largement utilisés par les chercheurs afin de motiver leurs contre-mesures.

#### 3 Contre-mesures de Sécurité pour les Infrastructures de Test

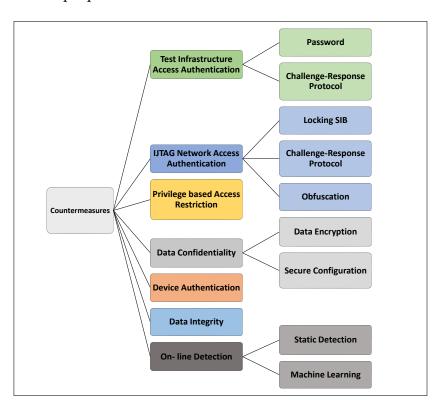

Nous nous intéressons dans ce paragraphe aux techniques de sécurité visant les infrastructures de test complexes basées sur les standards de test de l'IEEE. Une classification et une taxonomie de ces contre-mesures est proposée. Nous avons montré que les menaces affectant les infrastructures de test peuvent être divisées en menaces *externes* et *internes*. Dans la

littérature, nous pouvons trouver des propositions de contremesures concernant les deux catégories d'attaques: 1) les attaques externes sont principalement contrecarrées par les techniques de *l'authentification de l'utilisateur* et de *la détection des attaques*; 2) les attaques internes sont contrecarrées en accordant la *confidentialité des données*, *l'intégrité des données* et *l'authentification des dispositifs*.

Nous avons divisé ces contre-mesures en sept catégories différentes.

Authentification de l'Utilisateur Cette catégorie de contremesures vise à éviter que des entités non autorisées n'accèdent à l'infrastructure de test. Si l'utilisateur n'est pas autorisé, le contrôleur TAP est désactivé et les instructions JTAG ne peuvent pas être exécutées. De cette façon, il n'est pas possible d'accéder aux cœurs IP internes ou au réseau IJTAG reconfigurable. En conséquence, l'exploitation des chaînes de scan internes ou de l'infrastructure de debug est empêchée. Deux catégories de techniques d'authentification ont été identifiées. La première repose sur l'insertion d'un mot de passe à l'intérieur du contrôleur TAP afin de le verrouiller ou de le déverrouiller complètement. L'autre catégorie regroupe une série de techniques basées sur des protocoles de réponse aux défis mettant en œuvre des primitives cryptographiques.

#### Authentification des Utilisateurs pour les Réseaux IJTAG

Trois catégories de techniques d'authentification pour les réseaux IJTAG ont été identifiées dans la littérature. La première est basée sur des *SIB verrouillés* qui ouvrent l'accès aux régions privées du réseau. La connaissance d'un mot de passe secret est nécessaire pour ouvrir ces SIB. La deuxième catégorie est basée sur les *protocoles de questions/réponse*, ou *challenge/response* en anglais, qui permettent l'accès au réseau (ou à de plus petites parties de celui-ci) uniquement aux utilisateurs autorisés. La dernière catégorie vise à *obfusquer* la structure du réseau, en augmentant la complexité de sa rétro-ingénierie.

Authentification basée sur les Privilèges Les contremesures regroupées dans cette catégorie sont une extension des techniques d'authentification des utilisateurs. Dans ce cas, tous les utilisateurs n'ont pas le même type d'authentification, mais ils obtiennent des privilèges différents sur l'infrastructure de test en fonction du niveau de confiance dont ils disposent.

Confidentialité des Données Lorsque des données sensibles sont échangées entre l'utilisateur et l'appareil, la possibilité d'écoute ou sniffing à partir d'une troisième entité malveillante représente une menace. Ce risque est présent à la fois dans un environnement carte et dans un SoC, où l'entité malveillante est un cœur IP interne. En outre, les réseaux IJTAG doivent être protégés lorsque des données confidentielles pourraient être transférées par des instruments embarqués non fiables. Nous avons identifié deux catégories de contremesures qui assurent la confidentialité des données d'essai. La première catégorie repose sur le cryptage des séquences de test et peut être appliquée à toutes sortes d'infrastructures. Il s'agit des techniques dites de scan encryption. La deuxième catégorie est plus orientée vers la protection des réseaux IJTAG. La configuration du réseau re-configurable de scan (en anglais Reconfigurable Scan Network ou RSN) est correctement modifiée afin d'isoler les instruments non fiables lorsque des données confidentielles y sont transférées.

Authentification des Dispositifs L'authentification de l'appareil est fondamentale pour lutter contre la présence d'appareils non fiables. L'utilisateur qui communique avec un dispositif cible sur une infrastructure de test doit être sûr que la cible est un dispositif authentique et non un faux dispositif issu d'un processus de contrefaçon. Certaines contre-mesures de ce type ont été proposées dans la littérature.

Intégrité des Données Le fait de garantir l'intégrité de la communication permet à l'utilisateur et/ou à l'appareil de s'assurer que les données échangées n'ont pas été modifiées pendant la transmission. Une technique courante consiste à utiliser un code d'authentification de message (en anglais Message Authentication Code ou MAC) attaché à la fin de chaque message transmis. Le MAC est une signature unique qui est calculée en fonction du contenu du message. L'algorithme MAC le plus utilisé dans ce domaine est le Hash MAC (HMAC). Le HMAC est basé sur des fonctions de hachage, telles que SHA-256. Lorsqu'un message est reçu, l'appareil calcule en interne la signature HMAC du message. Si celle-ci est égale à la signature qui a été reçue en an-

nexe au message, cela signifie que le message est intact. Dans le cas contraire, cela signifie que le message a été altéré. La sécurité de cette primitive réside dans la clé secrète partagée utilisée à la fois par l'utilisateur et par le dispositif pour calculer la signature HMAC.

Détection des Attaques Toutes les contre-mesures présentées jusqu'à présent visent à éviter les attaques sur le système cible. Cependant, il est possible de trouver dans la littérature une catégorie de techniques visant à détecter l'exécution des attaques pendant qu'elles sont en cours. Ceci est réalisé par une surveillance du comportement de l'utilisateur sur la puce. Lorsque le comportement de l'utilisateur est considéré comme illégitime, le système détecte une attaque et passe en mode protection. Les techniques de détection peuvent être divisées en deux catégories. La première catégorie, comprend toutes les méthodes de détection basées sur des règles statiques. Dès que ces règles ne sont pas respectées, l'utilisateur est considéré comme un attaquant. La deuxième catégorie comprend les méthodes basées sur l'apprentissage automatique.

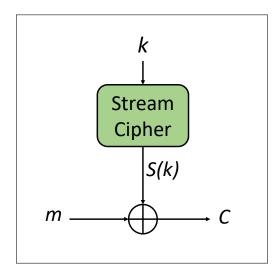

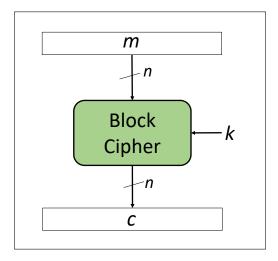

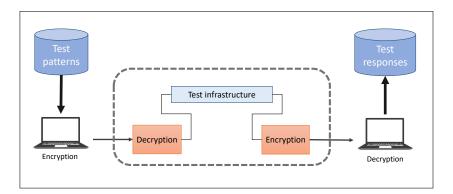

Les techniques de scan encryption ont connu un développement relativement récent en raison de leurs caractéristiques prometteuses. Du point de vue de la sécurité, elles reposent sur un chiffrement des données basé sur du chiffrement symétrique. Le chiffrement symétrique peut être facilement utilisé pour mettre en place un flot de test sécurisé. En fait, le processus de test peut être considéré comme une communication entre un testeur et un dispositif. Le testeur peut être un utilisateur autorisé accédant à l'infrastructure de test sur le terrain, ou un équipement de test automatique effectuant un test après fabrication. L'appareil cible peut être un circuit intégré ou un cœur IP spécifique à l'intérieur d'un SoC dont l'infrastructure de test interne est protégée. La technique de scan encryption fusionne l'authentification des utilisateurs et la confidentialité des données en une contre-mesure de sécurité unique. En fait, tout dispositif malveillant ou utilisateur malveillant qui tente de sniffer le canal de test n'est pas en mesure de comprendre le contenu du message transmis. En outre, un utilisateur non autorisé qui ne connaît pas la clé secrète qu'il a utilisée n'est pas en mesure de chiffrer avec succès les données de test. Il convient de souligner que le chiffrement du scan d'entrée est toujours présent. Par conséquent, sa fonction de déchiffrement ne peut pas être

évitée le long du canal de test. Pour cette raison, la seule façon de communiquer avec succès avec le dispositif cible est de connaître la clé secrète et de chiffrer correctement toutes les données qui sont introduites par le pin de scan-in.

# 4 Scan Encryption Sécurisé Basée sur le Chiffrement par Flot

Les techniques de scan encryption existantes sont toutes basées sur le chiffrement par flot TRIVIUM (en raison de sa faible empreinte silicium) et elles représentent apparemment une solution moins coûteuse que les techniques de scan encryption basées sur le chiffrement par blocs. Nous avons montré que les solutions basées sur le chiffrement par blocs doivent être accompagnées de circuits supplémentaires pour être compatible avec l'interface série des infrastructures de test. Ce surcoût est particulièrement évident lorsqu'il s'agit de chaînes de scan multiples. Les solutions basées sur des flots ne présentent pas ce problème, mais les implémentations existantes n'ont pas été développées de manière approfondie comme cela a été fait pour les solutions basées sur des blocs. Pour cette raison, nos recherches se sont orientées vers l'exploration de nouvelles possibilités d'utilisation de chiffrement par flot dans la scan encryption, mais, à notre surprise, certains problèmes ont été découverts. Le chiffrement par flot est considéré comme sûr si deux conditions sont remplies: 1) que le flot de clés ou *keystream* soit imprévisible par l'attaquant; 2) le même flot de données ne doit pas être utilisé plus d'une fois. Si l'une de ces conditions n'est pas respectée, il est possible d'effectuer une attaque, appelée two times pad. Les trois implémentations de la scan encryption basée sur les flots, présentes dans la littérature pour sécuriser les chaînes de scan, peuvent toutes être exploitées pour réaliser l'attaque two times pad. Dans la proposition de K. Rosenfeld et R. Karri [4], la clé du chiffrement TRIV-IUM est établie par l'utilisateur au moyen d'un protocole de défi-réponse. Le vecteur d'initialization (IV) est fixe. Cela signifie que si l'utilisateur envoie deux fois le même défi à l'appareil, il est sûr que la même clé est utilisée deux fois pour le chiffrement des données de test. Ainsi, l'attaquant peut forcer le dispositif à générer le même flot de clés, même sans connaître sa valeur. La technique décrite dans [5] permet

à l'utilisateur de définir directement la clé de chiffrement du flot. En fait, cette solution ne garantit pas l'authentification de l'utilisateur. Dans ce cas, on ne peut que supposer que l'attaque par scan pourrait être effectuée par un dispositif de sniffage. La vulnérabilité two times pad est présente si l'utilisateur ne modifie pas la clé avant d'envoyer un nouveau message au dispositif. La contre-mesure présentée dans [6] est basée sur un chiffrement par flots dont la clé secrète et le vecteur d'initialization sont soit câblées avec des fusibles, soit produites par une procédure de défi-réponse basée sur des fonctions physiques non clonables (en anglais Physically Unclonable Function ou PUF). Chaque appareil possède un ensemble unique de clés secrètes et de circuits intégrés attribués aux différents instruments du réseau reconfigurable IJTAG. Malheureusement, les auteurs ne précisent aucune précaution prise pour changer les valeurs des clés ou des IV entre les différentes sessions de chiffrement. Par conséquent, l'attaque two times pad peut être effectuée, détruisant l'effet du schéma de scan encryption. Il est clair que les mises en œuvre modernes du scan encryption par flots ont négligé le soin qui doit être apporté à la bonne gestion des clés qu'exige le chiffrement par flots. En revanche, la scan encryption par blocs ne souffre pas d'une telle faiblesse. En fait, le chiffrement par blocs peuvent réutiliser la même clé tout au long de la durée de vie du dispositif sans entraîner de problèmes de sécurité connus. C'est une première indication du fait que préférer la scan encryption basée sur le chiffrement par flots n'est pas aussi évident qu'il n'y paraît à première vue. Cependant, nous avons décidé de donner une autre chance au chiffrement par flot et nous avons proposé une nouvelle façon de mettre en œuvre la scan encryption basée sur le chiffrement par flots.

La contre-mesure proposée consiste à ajouter deux chiffrements de flot à l'entrée et à la sortie de la chaîne de scan respectivement. Un attaquant qui ne connaît pas la clé secrète utilisée pour le chiffrement des données de test n'est pas en mesure d'insérer les séquences de test souhaitées à l'intérieur du circuit. De plus, l'attaquant n'est pas en mesure de comprendre le contenu des données de test qui sont transférées hors de l'infrastructure de test. Seuls les utilisateurs ayant connaissance de la clé secrète sont autorisés à accéder aux chaînes de scan. En réutilisant la gestion de la clé du circuit d'origine, la solution n'introduit pas de nouveaux problèmes dans la manipulation de la clé secrète. Le dispositif fournit

une clé de scan encryption dédiée aux utilisateurs autorisés. L'IV utilisée pour initialiser le chiffrement de la chaîne est générée par un générateur de nombres aléatoires véritables (en anglais True Random Number Generator ou TRNG). Ce IV aléatoire est envoyé à l'utilisateur externe par l'intermédiaire du pin de scan-out. De cette façon, l'utilisateur est en mesure de chiffrer correctement les séquences de test. L'IV est totalement aléatoire et il est différent après chaque réinitialisation du circuit, mais il n'est pas secret. Le seul secret est la clé, qui n'est connue que des utilisateurs autorisés. Comme les chiffreurs par flots sont initialisés avec une IV différente à chaque initialisation du dispositif, le même flot de clés n'est jamais généré deux fois. Ainsi, cette solution n'est pas vulnérable à la faiblesse du two times pad, ce qui empêche tout attaquant d'effectuer des attaques de scan différentiel. La première étape de la nouvelle procédure de test consiste à générer des vecteurs de test pour le circuit testé, et à calculer les réponses de test attendues par simulation. Avant toute opération de scan, les chiffreurs par flots sont initialisés en générant un nombre aléatoire utilisé comme IV. Le testeur récupère l'IV aléatoire généré par le biais du pin scan-out, et il chiffre les vecteurs de test hors puce en utilisant l'IV aléatoire et la clé secrète. Une fois l'initialisation du chiffrement par flots terminée, le testeur peut transférer les vecteurs de test chiffrés dans l'infrastructure de test. Chaque vecteur de test chiffré est d'abord déchiffré à l'aide du flot de clés d'entrée généré par le chiffreur par flot. Ensuite, il est déplacé dans les chaînes de scan de l'appareil. Les vecteurs de test sont appliqués au circuit testé et des réponses de test sont obtenues. Pendant l'opération de décalage, les réponses de test sont chiffrées à l'aide du flot de clés généré par le chiffrement par flots placé à la sortie du scan. Les réponses de test chiffrées sont décalées hors du circuit afin d'être déchiffrées hors puce par le testeur. Une fois déchiffrées, les réponses au test peuvent être comparées avec les réponses attendues.

Nous avons montré que les solutions de scan encryption basées sur le chiffrement par flot sont un choix attrayant pour assurer la sécurité des infrastructures de test. Cela est vrai à condition de gérer correctement la génération des IV, contrairement à ce qui avait été proposé précédemment par d'autres auteurs. Cependant, la génération des IV aléatoires n'est pas gratuite. Dans les techniques présentées, nous avons proposé la mise en œuvre d'un TRNG pour générer un IV toujours différent. Comme les TRNG sont souvent

déjà présents à l'intérieur des circuits intégrés, nous ne considérons pas nécessairement cet élément comme un coût exclusivement dû à la présence de la scan encryption. À ce stade, nos recherches ont été guidées par le désir de donner une image claire aux ingénieurs intéressés par la mise en œuvre d'une contre-mesure de scan encryption. Nous résumons ici les conclusions que nous avons tirées de la comparaison des techniques de scan encryption par flot et en bloc :

Sécurité La scan encryption par flot et en bloc assure la sécurité contre les attaques externes et les attaques internes basées sur le sniffage de données de test. Dans le cas des attaques par scan différentiels, la solution proposée basée sur le flot est la seule solution de scan encryption sécurisée existante de ce type, car elle ne permet pas l'attaque two times pad. Les deux solutions nécessitent une clé secrète intégrée dans le dispositif cible, dont la gestion peut bénéficier de la politique de gestion des clés fournie par le dispositif cible.

**Testabilité** les deux techniques garantissent la testabilité complète du dispositif cible, tant à la fabrication que sur le terrain. Le test de fabrication n'est pas affecté par la perte de couverture des fautes induite par l'ajout de la solution de scan encryption. La scan encryption par flot a besoin d'une méthode permettant de contourner la génération aléatoire du IV lorsque le test in-wafer est effectué. Le test sur le terrain est accordé, car l'accès à l'infrastructure de test est laissé ouvert, même si seuls les utilisateurs autorisés peuvent communiquer avec succès avec l'infrastructure de test.

Coût en Surface la scan encryption par flot mis en œuvre avec le chiffrement par flot TRIVIUM est égal à la moitié du coût en surface induit par la scan encryption en bloc mise en œuvre avec le chiffrement par bloc SKINNY (c'est-à-dire le chiffrement par bloc le plus léger que nous avons utilisé dans nos expériences). En fait, il est possible d'observer qu'un chiffrement par blocs léger, tel que le chiffrement SKINNY, a la même empreinte de surface que le chiffrement TRIVIUM. Toutefois, dans le cas de scan encryption basée sur des flots, il est suffisant d'implémenter un seul chiffrement générant deux flots de clés, alors que dans le cas de chiffrement par blocs, il est obligatoire d'implémenter un chiffrement lors du scan-out. Il en

résulte que la scan encryption par flot coûte la moitié de la scan encryption en blocs. D'autre part, si l'on considère le coût du TRNG comme un coût induit par la mise en œuvre de la scan encryption par flot, son coût augmente considérablement et devient jusqu'à trois fois supérieur à celui d'une solution par blocs. Par conséquent, il est clair que la scan encryption par flot n'est pratique du point de vue du coût de la surface que si un TRNG est déjà disponible dans l'implémentation du dispositif cible.

Coût en Temps de Test la scan encryption par flot a un grand avantage du point de vue du temps. Cela est possible parce que le chiffrement par flot bénéficie de son adéquation naturelle avec l'interface série des infrastructures de test standard. Pour cette raison, la pénalité de temps de test induite par la solution basée sur le flot est un temps d'initialisation constant qui est négligeable par rapport au temps de test total du dispositif cible. Les solutions de scan encryption par blocs doivent adapter le chemin de données des chiffrages par blocs à l'interface série de l'infrastructure de test. Pour cette raison, la nécessité de compléter les vecteurs de test par des bits supplémentaires pénalise fortement le temps de test. Cette surcharge peut être réduite par l'ajout de points de test, modifiant ainsi l'infrastructure de test du dispositif cible.

Chaînes de Scan Multiple lorsque plusieurs chaînes de scan sont présentes, la scan encryption par flot peut bénéficier de sa capacité à générer plusieurs flots de clés à partir du même chiffrement par flot. Pour cette raison, il est possible de gérer jusqu'à 32 chaînes de scan mettant en œuvre un seul chiffrement de flot TRIVIUM. Dans le cas de la scan encryption en bloc, la gestion de plusieurs chaînes de scan est définitivement plus compliquée. En effet, les chiffrages par blocs doivent être pilotés par une fréquence d'horloge plus élevée que le reste de l'infrastructure de test. Cela entraîne une consommation d'énergie plus élevée et une modification plus profonde de la conception du circuit intégré.

#### 5 Sécurité de la Scan Encryption

La scan encryption offre une protection contre la plupart des attaques connues visant les infrastructures de test. D'une part, le chiffrement des données de test compromet la faisabilité des attaques basées sur le sniffage du canal de communication entre l'utilisateur et le dispositif cible. D'autre part, les attaques externes ne sont pas réalisables, car l'attaquant n'a pas de contrôle sur les données qui sont envoyées à l'infrastructure de test, il ne peut donc pas comprendre les résultats produits par le dispositif cible et lus par l'infrastructure de test. La sécurité de la scan encryption s'articule autour de deux points clés : confidentialité des données et authentification de l'utilisateur. La confidentialité des données transmises est une caractéristique clé du chiffrement en lui-même. En effet, lorsque l'utilisateur et l'appareil échangent des données cryptées avec une clé secrète, personne d'autre n'est en mesure de comprendre les informations transmises. Cela signifie que toute tentative d'attaque faite par des entités malveillantes au sein du système, et connectées à l'infrastructure de test, ne peut aboutir. En outre, toutes les attaques basées sur l'observation des états internes du circuit sont rendues impossibles par le fait que tout ce qui est déplacé hors de l'infrastructure de test est chiffré. L'authentification de l'utilisateur est obtenue grâce au fait que la connaissance de la clé secrète est fondamentale pour pouvoir communiquer efficacement avec le dispositif. Si l'utilisateur ne connaît pas la clé que le dispositif utilise pour le déchiffrement, il ne pourra pas prévoir la forme que prendront les données entrantes une fois qu'elles seront arrivées dans l'infrastructure de test. Il est donc impossible de forcer un état spécifique sur les registres internes du circuit. La seule possibilité qui reste à l'utilisateur non autorisé est d'entrer des données aléatoires dans l'infrastructure de test.

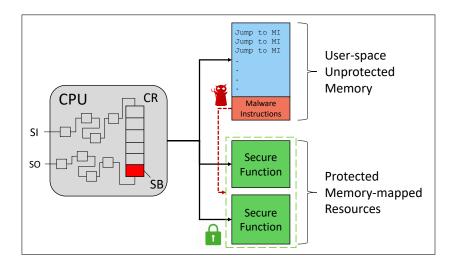

La seule capacité qui reste à l'attaquant est la possibilité de déplacer les données à travers des pins de scan, qui sont déchiffrées en interne, les rendant ainsi imprévisibles pour l'utilisateur non autorisé. La plupart des modèles de menaces que nous avons présentés sont basés sur l'hypothèse que l'attaquant peut insérer des modèles spécifiques à l'intérieur de l'infrastructure de test. Cependant, nous avons identifié certains scénarios dans lesquels même l'insertion de bits

aléatoires à l'intérieur de l'infrastructure de test pourrait constituer une menace pour la sécurité si des contre-mesures appropriées ne sont pas mises en œuvre. C'est le cas de certains systèmes à base de microprocesseurs, où des modes opérationnels protégés sont activés et désactivés en modifiant la valeur d'un seul bit dans un registre. Dans ce cas, même l'insertion de valeurs aléatoires à l'intérieur des chaînes de scan interne pourrait conduire à une attaque, rendant ainsi la contre-mesure de scan encryption inefficace. La scan encryption permet à l'attaquant d'entrer des données aléatoires dans l'infrastructure de test. Cela est possible car quelles que soient les informations que l'attaquant tente d'entrer par le pin de scan-in, elles seront corrompues de manière imprévisible par le chiffrement d'entrée. Malheureusement, les techniques de scan encryption n'offrent en aucune façon la possibilité d'empêcher un accès non autorisé, il est donc nécessaire de comprendre si l'insertion de contenu aléatoire dans l'infrastructure de test peut constituer une menace. Cela se produit dans les cas où, pour réaliser l'attaque, il suffit de forcer, au travers des chaînes de scan, un nombre limité de bascules à une valeur spécifique. Si le reste de l'attaque peut être effectué en mode fonctionnel, la présence de la scan encryption n'est pas suffisante pour empêcher l'attaquant d'entrer, après un certain nombre de tentatives, la valeur souhaitée à l'intérieur du dispositif. Dans cette thèse, nous avons émis l'hypothèse d'un tel scénario, en utilisant un microprocesseur équipé d'un environnement d'exécution de confiance (en anglais Trusted Execution Environment ou TEE) comme dispositif victime. En fait, dans ce type de microprocesseur, nous avons un seul bit contenant la valeur binaire qui détermine l'activation du TEE.

Nous avons montré plusieurs mécanismes d'authentification des utilisateurs visant à empêcher l'utilisation de l'infrastructure de test par des utilisateurs malveillants. Nous avons vu que ces techniques sont principalement basées sur l'insertion d'une clé secrète ou d'un mot de passe, et sur des protocoles de défi-réponse. De notre côté, nous avons identifié une opportunité offerte par le chiffrement, dans le but d'obtenir une forme d'authentification de l'utilisateur qui va au-delà des techniques standards traditionnelles. Plus précisément, il est possible de s'appuyer sur le dispositif qui déchiffre passivement les données d'entrée à l'aide d'une clé secrète. Par conséquent, en supposant qu'un attaquant n'ait aucun contrôle sur le processus de déchiffrement, il

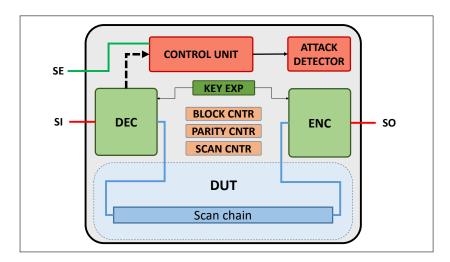

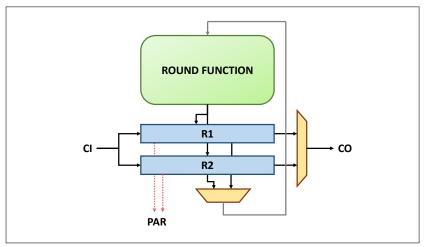

est possible d'imposer des règles de format que les données saisies doivent respecter pour être acceptées par le dispositif. Ce faisant, le dispositif est capable de reconnaître, après le déchiffrement, si les données ont été envoyées par un utilisateur en possession de la clé secrète, ou par un utilisateur malveillant qui tente d'entrer des données aléatoires. Dans cette thèse, nous présentons la technique de scan encryption avec contrôle de parité (en anglais Scan Encryption with Parity check ou SEP), afin de contrecarrer l'attaque par scan présentée. L'hypothèse clé qui sous-tend la faisabilité de l'attaque par scan proposée, est que les schémas de chiffrement symétrique manquent d'un mécanisme d'authentification, de sorte que le destinataire accepte toujours le message reçu. Avec la technique SEP, nous proposons d'améliorer la scan encryption en ajoutant une vérification légère de l'intégrité des données transférées dans l'infrastructure de test. L'idée de base consiste à encoder, avant le chiffrement, les vecteurs de test en texte clair avec un algorithme de codage connu du public. Le dispositif destinataire, après déchiffrement, décode les vecteurs de test obtenus et vérifie leur conformité avant de les appliquer à la logique du circuit. Dans la technique SEP, nous avons choisi d'utiliser un code de parité couplé à un chiffrement par blocs afin de mettre en œuvre ce schéma d'authentification. La sécurité de ce schéma repose sur l'hypothèse suivante: un utilisateur non autorisé n'est pas capable de créer un texte chiffré, de sorte qu'une fois déchiffré, le texte en clair qui en résulte est conforme au format souhaité. Dans la technique SEP, on a recours au calcul de code de parité sur chaque bloc de chiffrement. Le décodage de la parité est effectué en conjonction avec le mécanisme de déchiffrement de l'entrée du scan. Un attaquant qui ne connaît pas la clé de chiffrement n'est donc pas en mesure de produire des vecteurs de test chiffrés valides qui passent avec succès la vérification de parité après le déchiffrement. Dès que le module de déchiffrement détecte un mauvais bit de parité, il lève un drapeau à l'intérieur du circuit. Lorsque le chargement de la chaîne de scan est terminé et que l'attaquant fait passer le circuit en mode fonctionnel, la présence du drapeau fait passer le circuit en état de protection. La technique SEP garantit les exigences de sécurité suivantes:

1. Les utilisateurs non autorisés ne peuvent pas contrôler ou observer l'état interne du circuit. En héritant du chiffrement de la chaîne de scan, nous nous as-

- surons que toutes les données qui sont extraites par l'infrastructure de test ne sont pas compréhensibles par l'attaquant. En outre, après le déchiffrement des données d'entrée, l'exactitude des bits de parité est vérifiée. Cela empêche l'attaquant d'insérer des vecteurs de test avec un contenu aléatoire dans la chaîne de scan;

- 2. Les messages échangés par le biais de l'infrastructure de test ne doivent pas être compréhensibles par des tiers. Cette propriété est assurée par le chiffrement des données de test effectué par un chiffrement par blocs standard. Ainsi, la sécurité sémantique du chiffrement est garantie. Notamment, même si l'attaquant est capable d'interroger le chiffrement par blocs interne et de prendre plusieurs paires texte clair/texte chiffré (c'est-à-dire un attaque à texte clair connu), il n'est pas possible de trouver une corrélation entre eux, d'où la clé secrète.

#### 6 Conclusions

La nécessité d'un test conscient de la sécurité est une question urgente pour tous les systèmes électroniques modernes. Les infrastructures de tests invasifs sont obligatoires pour garantir la production de circuits intégrés à faible coût. Dans la plupart des applications, il n'est plus possible d'imaginer un système sans accès TAP. Dans cette thèse, nous montrons que la sécurité est un problème majeur qui affecte toutes les infrastructures de test. Pour cette raison, le flot DfT devrait prendre en considération la sécurité dès les premières étapes du développement des circuits intégrés. Dans cette thèse, nous avons montré que de nombreuses contre-mesures existantes pour les infrastructures de test sont basées sur l'ajout de modules cryptographiques pour l'authentification des utilisateurs. La plupart de ces mécanismes d'authentification sont basés sur un matériel cryptographique complexe, représentant un coût insupportable en dehors de certains marchés de niche spécifiques. De la même manière que la DfT a connu un processus d'automatisation au cours des dernières décennies, qui a permis son utilisation massive dans tous les segments du marché, nous voulons souligner que la nécessité d'une DfT sécurisé devrait également connaître une telle diffusion. Bien qu'il y ait maintenant de nombreuses propositions dans la littérature dans ce sens, le scénario est

encore trop fragmenté, et composé de techniques qui offrent une protection partielle et/ou dont la sécurité est difficile à prouver. Nous avons identifié la scan encryption comme une technique très prometteuse pour sécuriser facilement les infrastructures de test. La scan encryption est basée sur l'ajout de matériel cryptographique dont le coût peut être maintenu marginal selon le besoin du concepteur. Son déploiement est extrêmement simple et facile à automatiser. Le concepteur de la DfT établit les clés secrètes qui sont utilisées par le dispositif, et l'ensemble du flot de test est chiffré en conséquence. Cela empêche à la fois l'accès non autorisé par des utilisateurs malveillants et la fuite d'informations dans le canal de communication.

Dans cette thèse, nous avons analysé en profondeur les techniques de scan encryption et essayé de résoudre les problèmes qui ont été identifiés. Dans un premier temps, nous avons inspecté les techniques de pointe, en identifiant deux catégories : la scan encryption basée sur le chiffrement par flot et basée sur le chiffrement par blocs. Alors que la scan encryption par blocs avait déjà fait l'objet d'une analyse minutieuse et d'une activité expérimentale étendue, la scan encryption par flot a été proposée dans de nombreux travaux, mais n'a jamais fait l'objet d'une analyse de sécurité approfondie. C'est pourquoi nous avons proposé de nouvelles implémentations de scan encryption basées sur le chiffrement par flot, corrigeant ainsi certains problèmes de sécurité que nous avons trouvés dans l'état de l'art. La scan encryption proposée est basé sur la génération aléatoire d'un IV différent au début de chaque communication entre l'utilisateur et l'appareil. Bien que cela implique des coûts de mise en œuvre plus élevés également pour la scan encryption par flot, les deux techniques ont été amenées au même niveau de sécurité et peuvent toutes deux être envisagées sans risque pour le déploiement d'une DfT sécurisé. Nous avons largement comparé la nouvelle méthode de scan encryption par flot et la méthode de scan encryption par blocs déjà existante. Nous avons mis en évidence les avantages et les inconvénients des deux solutions, afin de fournir une ligne directrice aux concepteurs qui souhaitent utiliser la scan encryption pour sécuriser leur DfT.

La scan encryption, tant dans sa mise en œuvre par flot que par blocs, est capable de contrecarrer la plupart des attaques impliquant des infrastructures de test. En fait, tant la contrôlabilité que l'observabilité des ressources internes sont considérablement entravées. L'attaquant n'a aucun contrôle sur l'opération de déchiffrement qui est effectuée au niveau du port d'entrée. Ainsi, sa seule capacité est d'insérer des données aléatoires à l'intérieur de l'infrastructure de test. D'autre part, le chiffrement des données garantit la confidentialité des données de test en dehors des limites du dispositif cible. Ainsi, toutes les tentatives de piratage et d'accès illégal à le pin de sortie de scan n'entraînent aucune menace. Malgré la sécurité étendue offerte par la scan encryption, son absence de mécanisme de contrôle de l'intégrité des données la rend potentiellement vulnérable aux accès non désirés. Dans cette thèse, nous avons exploré les scénarios possibles dans lesquels un utilisateur malveillant peut exploiter la capacité d'insérer des données aléatoires dans l'infrastructure de test pour réaliser une attaque. Nous avons identifié une catégorie d'attaques, dans laquelle l'attaquant exploite les chaînes de scan interne afin de forcer un nombre très limité de bascules à une valeur spécifique. Dans ce cas, la contre-mesure de scan encryption ne suffit pas pour éviter un scénario similaire. Nous avons proposé un exemple d'attaque visant l'environnement d'exécution de confiance d'un microprocesseur. Si l'attaquant règle correctement la mémoire du microprocesseur, il est possible de déclencher l'exécution d'un code malveillant par l'insertion de données aléatoires dans les chaînes de scan. Pour cette raison, nous avons proposé une amélioration de la scan encryption comprenant un mécanisme de contrôle d'intégrité très léger. Dans cette technique, nous proposons d'inclure une règle de format aux données de test en texte clair que le dispositif cible peut facilement vérifier après le déchiffrement. Si ces règles sont respectées, les données reçues sont valides, sinon, elles sont considérées comme des données malveillantes envoyées par un attaquant. La sécurité de cette technique repose sur le fait qu'un attaquant ne peut pas produire un message valide qui résulterait en un format correct après décryptage, sans connaître la clé de scan encryption. Nous avons mis en œuvre cette technique en ajoutant des bits de parité dans les données de test. Au prix d'un léger surcoût en termes de temps et de surface de test, la scan encryption obtient une propriété de sécurité qui la rend robuste contre tout type d'accès non autorisé.

Nous pensons que la scan encryption est une technique très prometteuse pour protéger les infrastructures de test. Ses caractéristiques lui permettent de fournir une DfT consciente de la sécurité, même dans des appareils peu coûteux. Sa flexibilité et la variété des mises en œuvre sont des caractéristiques qui permettent d'adapter la contre-mesure à différents besoins de conception. Nous pensons également que le développement d'un standard de test conscient de la sécurité est inévitable à l'avenir, et la scan encryption pourrait être un point de départ prometteur pour raisonner à ce sujet.

## Acknowledgments

I would like to thank some people that, in different ways, contributed to this thesis. These acknowledgments have been redacted in different languages, according to the context and the people they are addressed to.

Grazie a Giorgio che, oltre a essere il mio direttore di tesi, è stato in questi anni anche un prezioso amico. Anche se le circostanze ci hanno portato a vivere in due città diverse, non ha mai smesso di motivarmi e di spingermi a cercare di arrivare sempre più lontano.

Merci à Bruno et Marie-Lise, pour leur soutien et leur patience pendant ces années de thèse.

Merci à Sophie pour ses précieux conseils et pour avoir participé au jury de thèse.

Merci a Guy Gogniat et Jacques Fournier pour avoir accepté d'être rapporteurs de ma thèse et pour avoir fait partie du jury.

Thanks to Regis Leveugle and Bernd Becker, for agreeing to join the thesis committee.

Grazie alla mia famiglia. Grazie a mio papà e a mia mamma, per avermi sempre motivato a fare meglio e per avermi sostenuto e permesso di arrivare fino alla fine del mio lungo percorso di studi. Grazie a Martina, per essermi sempre vicino nonostante la distanza geografica. Grazie a Gennaro, per essere entrato nelle nostre vite proprio durante questi ultimi anni e aver portato tante soddisfazioni.

Grazie a Cecilia, mia compagna di vita, che quotidianamente partecipa alla realizzazione dei miei sogni.

Merci à Mathieu, mon premier copain de bureau, pour m'avoir aidé beaucoup pendant ma première année à Montpellier.

Thanks to all the colleagues and friends, Bastien, Clement, Linh, Safa and all the others at LIRMM. They made my days at work a lot easier and funnier.

Merci à Caroline, pour son aide inestimable dans l'organisation des missions et dans la gestion des démarches bureaucratiques.

Thanks to all the colleagues and friends from the scientific community. Thanks to anyone that has shared professional advice (and drinks) with me during the conferences.

Grazie a Ilaria, mia collega e inseparabile amica in questa mia avventura a Montpellier. Grazie anche per essere sempre d'ispirazione per il mio lavoro e per spingermi ad astrarre i tecnicismi della mia ricerca.

Grazie a Marcello, per essere un caro amico. Ogni volta che sento qualche difficoltà, so che rivolgendomi a lui posso sempre trovare un saggio consiglio. I primi tempi a Montpellier sarebbero stati molto più difficili senza il suo supporto e i suoi suggerimenti.

Thanks to all the friends that I have found in Montpellier, Alina, Fernanda, Francesco, Cloé, Katherine, Sara, Umberto. They made my life in Montpellier a great experience.

Grazie a Matteo, per avermi fatto scoprire il LIRMM e condotto verso questa bella esperienza.

Grazie a Dizer, per farmi sempre ricordare il lato creativo della vita.

Grazie a Ler, amico del liceo, ritrovato a Montpellier. Grazie per essermi sempre vicino.

Grazie ad Aleandro, mio carissimo amico. Nonostante la distanza che ci separa, riesco sempre a sentirti vicino.

Grazie a Claudio, perché senza di lui questo dottorato non sarebbe neanche cominciato.

This thesis has been redacted during the lockdown period due to the COVID-19 outbreak. I want to thank every person that is taking part in the collective effort we are doing to counteract this disease.

## **Contents**

| <b>A</b> l | ostra | c <b>t</b>                                                  | i     |

|------------|-------|-------------------------------------------------------------|-------|

| Re         | esum  | e                                                           | iii   |

|            | 1     | Test des Systèmes Numériques                                | iv    |

|            | 2     | Menaces pour la Sécurité des Infrastructures de Test        | vi    |

|            | 3     | Contre-mesures de Sécurité pour les Infrastructures de Test | viii  |

|            | 4     | Scan Encryption Sécurisé Basée sur le Chiffrement par Flot  | xii   |

|            | 5     | Sécurité de la Scan Encryption                              | xvii  |

|            | 6     | Conclusions                                                 | XX    |

| A          | cknov | wledgments                                                  | xxv   |

| Co         | onten | ats                                                         | xxvii |

| Li         | st of | Abbreviations                                               | xxxv  |

| In         | trodu | action                                                      | xxxi  |

| 1          | Test  | t of Digital Systems                                        | 1     |

|            | 1.1   | Testing in the IC Production Flow                           | 2     |

|            | 1.2   | Design-for-Testability                                      | 4     |

|            |       | Scan Chains                                                 | 4     |

|            | 1.3   | IEEE Test Standards                                         | 7     |

|            |       | JTAG                                                        | 7     |

|            |       | IEEE 1500                                                   | 9     |

|            |       | IJTAG                                                       | 10    |

| 2          | Sec   | urity Threats in Test Infrastructures                       | 13    |

|            | 2 1   | Differential Scan Attack on AFS                             | 1/    |

|   | 2.2  | Classification of Threats                      | 17 |

|---|------|------------------------------------------------|----|

|   |      | External Threats                               | 18 |

|   |      | Internal Threats                               | 25 |

|   |      | Summary                                        | 29 |

|   |      |                                                |    |

| 3 | Seci | urity Countermeasures for Test Infrastructures | 31 |

|   | 3.1  | Classification of Countermeasures              | 31 |

|   |      | User Authentication                            | 32 |

|   |      | User Authentication for IJTAG Networks         | 37 |

|   |      | Privilege Based Authentication                 | 42 |

|   |      | Data Confidentiality                           | 43 |

|   |      | Device Authentication                          | 45 |

|   |      | Data Integrity                                 | 47 |

|   |      | Attack Detection                               | 48 |

|   |      | Summary                                        | 51 |

|   | 3.2  | Scan Encryption                                | 52 |

|   |      | Symmetric Encryption                           | 52 |

|   |      | Testing with Encrypted Data                    | 55 |

|   |      | Block Based Scan Encryption                    | 57 |

|   |      | Stream Based Scan Encryption                   | 59 |

|   |      | Summary                                        | 60 |

|   |      |                                                |    |

| 4 | Sect | ure Stream Based Scan Encryption               | 61 |

|   | 4.1  | Scan Encryption Vulnerability                  | 61 |

|   | 4.2  | New Secure Scan Encryption Solution            | 64 |

|   |      | Secure Scan Chain                              | 66 |

|   |      | Secure JTAG                                    | 72 |

|   | 4.3  | Stream vs Block based Scan Encryption          | 77 |

|   |      | Summary                                        | 83 |

| 5  | Scar   | n Encryption Security                                                 | 87  |

|----|--------|-----------------------------------------------------------------------|-----|

|    | 5.1    | Security analysis against different attacks from the state-of-the-art | 88  |

|    | 5.2    | Security Threat against Scan Encryption                               | 90  |

|    |        | Trusted Execution Environment                                         | 91  |

|    |        | Working Principle                                                     | 92  |

|    |        | Attack Implementation                                                 | 93  |

|    | 5.3    | Scan Encryption with Parity Check                                     | 96  |

|    |        | General Overview of the SEP Technique                                 | 97  |

|    |        | SEP Architecture                                                      | 98  |

|    |        | Security Analysis                                                     | 100 |

|    |        | DfT Flow with SEP Insertion                                           | 101 |

|    |        | Area and Test Time Overhead                                           | 102 |

|    |        | Discussion                                                            | 104 |

| 6  | Con    | clusions                                                              | 105 |

|    | 6.1    | Future Perspectives                                                   | 107 |

| Sc | ientif | ic Contributions                                                      | 111 |

| Bi | bliog  | raphy                                                                 | 115 |

# **List of Figures**

| 1.1 | Finite state machine implemented by the TAP controller of the IEEE Std. 1149                    |    |

|-----|-------------------------------------------------------------------------------------------------|----|

|     | (JTAG) [1]                                                                                      | 8  |

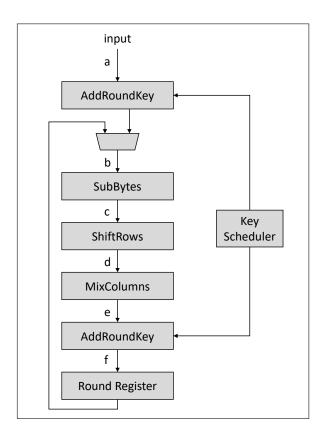

| 2.1 | Block diagram representing AES operations                                                       | 15 |

| 2.2 | Vulnerabilities in test infrastructures can be originated by (i) an external threat,            |    |

|     | caused by an unauthorized user accessing the IC; (ii) an internal threat, caused                |    |

|     | by malicious hardware planted inside the IC                                                     | 18 |

| 2.3 | Taxonomy of the known threats on standard test infrastructures                                  | 19 |

| 3.1 | $Taxonomy\ of\ the\ existing\ security\ countermeasures\ for\ standard\ test\ infrastructures.$ | 32 |

| 3.2 | High-level architecture of a generic stream cipher                                              | 54 |

| 3.3 | High-level architecture of a generic block cipher                                               | 55 |

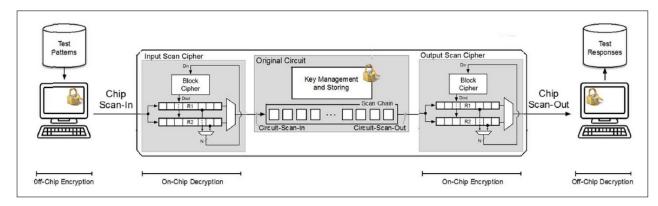

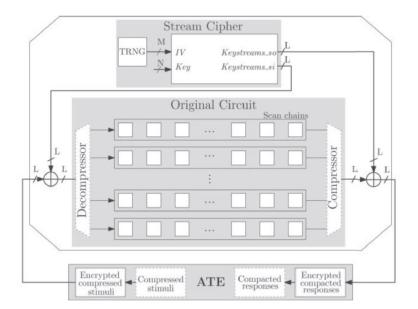

| 3.4 | Functional scheme of scan encryption                                                            | 56 |

| 3.5 | Scan encryption based on block ciphers [82]                                                     | 57 |

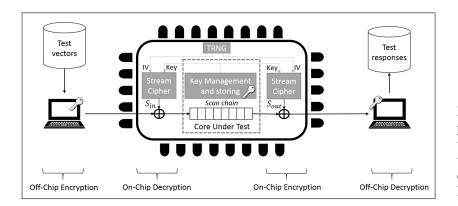

| 4.1 | Schematics of the proposed stream based scan encryption. A TRNG produces                        |    |

|     | the IV that is used to seed the stream cipher, together with the secret key                     | 65 |

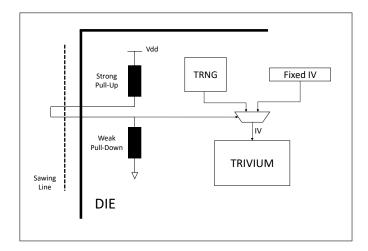

| 4.2 | Schematics of the saw bow technique for isolating the TRNG when the die is                      |    |

|     | still connected to the wafer                                                                    | 66 |

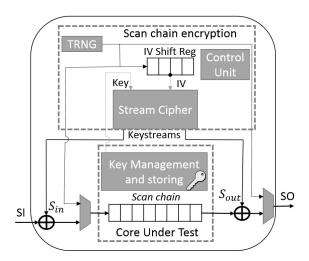

| 4.3 | Architecture of the stream based encryption based of a scan chain infrastructure.               | 67 |

| 4.4 | Stream based scan encryption applied to multiple scan chains supporting test                    |    |

|     | compaction                                                                                      | 7  |

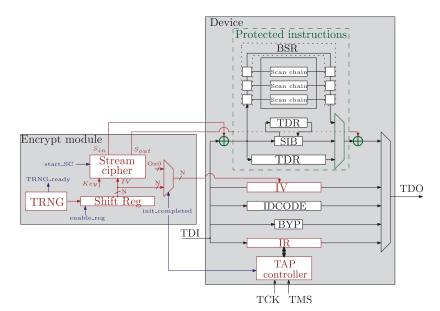

| 4.5 | High-level architecture of Secure JTAG                                                          | 72 |

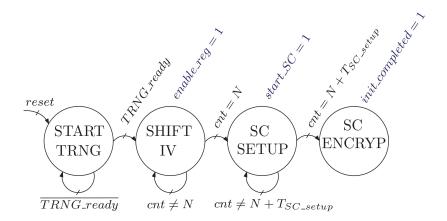

| 4.6 | Finite State Machine controlling the initialization procedure                                   | 73 |

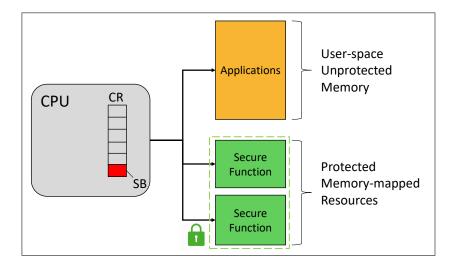

| 5.1 | Functional scheme of a generic microprocessor system implementing a Trusted             |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | Execution Environment. The Security Bit (SB) in the Configuration Register (CR)         |    |

|     | determines if applications executed from the user-space memory can access the           |    |

|     | protected resources                                                                     | 92 |

| 5.2 | Functional scheme of the architecture under attack. The user-space unprotected          |    |

|     | memory is filled with <i>jump</i> instructions redirecting to the malware instructions, |    |

|     | which access the protected resources if $SB=1$                                          | 94 |

| 5.3 | Schematics of the SEP architecture. SI and SO pins (in red) carry encrypted             |    |

|     | test data and responses. The dashed line represents the parity signal, which is         |    |

|     | asserted by the decryption unit to the control unit                                     | 99 |

| 5.4 | High-level schematic of the DEC and ENC units. Parity signals are not present           |    |

|     | in the FNC unit                                                                         | 99 |

# **List of Tables**

| 2.1 | Correlation between AES partial results and their plaintext [29]                   | 17  |

|-----|------------------------------------------------------------------------------------|-----|

| 3.1 | Analysis of the protection granted from each countermeasure against the known      |     |

|     | threats                                                                            | 52  |

| 4.1 | Cost of the submodules composing the proposed countermeasure                       | 69  |

| 4.2 | Benchmark ICs used to evaluate the implementation cost of the TRIVIUM based        |     |

|     | scan encryption                                                                    | 69  |

| 4.3 | Cost of the scan chain encryption with the TRIVIUM stream cipher on the chosen     |     |

|     | benchmarks                                                                         | 70  |

| 4.4 | Area cost of the proposed countermeasure compared to an unprotected JTAG           |     |

|     | wrapper                                                                            | 76  |

| 4.5 | Area overhead of different block and stream based scan encryption techniques.      | 80  |

| 4.6 | Test time overhead of different block and stream based scan encryption techniques. | 80  |

| 5.1 | Complexity of the scan attack performed on a secure microprocessor based on        |     |

|     | the MiniMIPS CPU                                                                   | 95  |

| 5.2 | Complexity of the scan attack on TEE performed on a secure microprocessor          |     |

|     | based on the MiniMIPS CPU protected with the SEP technique                         | 101 |

| 5.3 | Benchmarks Characteristics                                                         | 102 |

| 5.4 | SEP Insertion Overhead                                                             | 102 |

# List of Abbreviations

**3PIP** Third-Party Intellectual Property

**AD** Attack Detector

**AES** Advanced Encryption Standard

**AE** Authenticated Encryption

**ASIC** Application Specific Integrated Circuit

**ATE** Automatic Test Equipment

ATPG Automatic Test Patterns Generator

**BIST** Built-In Self-Test

**BSR** Boundary Scan Register

**CBC** Cipher Block Chaining

**CPU** Central Processing Unit

**CRP** Challenge-Response Pair

**CR** Configuration Register

**CU** Control Unit

**DEC** DEcryption Cipher

**DES** Data Encryption Standard

**DfT** Design for Testability

**DoS** Denial of Service

**DR** Data Register

**DUT** Device Under Test

**ECB** Electronic Codebook

**ECC** Elliptic Curve Cryptography

xxxvi

ECDSA Elliptic Curve Digital Signature Algorithm

**EDA** Electronic Design Automation

**ENC** ENcryption Cipher

**FeRAM** Ferromagnetic RAM

**FF** Flip-flop

**FPGA** Field Programmable Gate Array

FSM Finite State Machine

**HLSIB** Honeypot Locking SIB

**HMAC** Hashed Message Authentication Code

**IC** Integrated Circuit

**IEEE** Institute for Electrical and Electronics Engineers

**IJTAG** Internal JTAG

**IoT** Internet of Things

**IP** Intellectual Property

IR Instruction Register

**IV** Initialization Value

JTAG Joint Test Action Group

LFSR Linear Feedback Shift Register

**LSIB** Locking SIB

MAC Message Authentication Code

**NLFSR** Non-Linear Feedback Shift Register

**NVM** Non-Volatile Memory

**OCD** On-Chip Debugging

**OTP** One-Time Pad

PRG Pseudo-Random Generator

**PUF** Physically Unclonable Function

**RAM** Random Access Memory

**RSN** Reconfigurable Network

**SEP** Scan Encryption with Parity check

**SE** Scan-Enable

**SIB** Segment Insertion Bit

SI Scan-In

**SKMU** Secret Key Management Unit

SLFSR Secure Linear Feedback Shift Register

**SLSIB** Switching Locking SIB

**SoC** System on Chip

**SO** Scan-Out

SSC Secure Scan Chain

**SVM** Support Vector Machine

**TAP** Test Access Port

TCK Test Clock

**TDI** Test Data Input

**TDO** Test Data Output

**TDR** Test Data Register

**TEE** Trusted Execution Environment

TMS Test Mode Signal

**TRNG** True Random Number Generator

**TRST** Test Reset

WBR Wrapper Boundary Register

WDR Wrapper Data Register

xxxviii List of Abbreviations

WIR Wrapper Instruction Register

**WSP** Wrapper Serial Port

# Introduction

The test is a fundamental step in the development of modern integrated circuits (ICs). In order to be able to effectively test circuits with high internal complexity, it is necessary to design appropriate test infrastructures within them. While these infrastructures make lean and effective testing practices possible throughout the entire product life cycle, they also offer an unwanted security backdoor. For this reason, there is a need to design test infrastructures using a security-aware approach. Many existing techniques use cryptographic implementations to prevent unauthorized access, or to provide confidentiality and integrity to test data transmitted between the user and the device. Among all the existing countermeasures, one of the most promising is the scan encryption. This countermeasure is based on the encryption of test data, which guarantees the confidentiality of test data and does not allow unauthorized use of the test infrastructure. In this thesis, we extensively discuss scan encryption techniques.

The contributions made by this thesis can be summarized as follows:

- 1. We provide an **extensive review** of the state-of-the-art on the security of test infrastructures. We propose a new classification of the security threats and countermeasures. Based on this classification, we perform a comparison between the existing countermeasures, and we identify the scan encryption technique as a promising approach for securing test infrastructures.

- 2. We thoroughly analyze state-of-the-art scan encryption techniques, identifying two different approaches for the encryption of test data (i.e., stream cipher and block cipher encryption respectively). Furthermore, we point out a vulnerability affecting existing scan encryption implementations based on stream ciphers.

- 3. We propose **new scan encryption techniques** based on stream cipher encryption, overcoming the vulnerability present in the state-of-the-art implementations.

- The proposed implementations target different test infrastructures. Their cost is evaluated in terms of area and test time.

- 4. We compare the proposed techniques based on stream cipher encryption, with the existing techniques based on block cipher encryption. We highlight pros and cons of both implementations, providing a **guideline** to allow designers to opt for the most suitable scan encryption technique for their needs.

- 5. We analyze the security of the discussed scan encryption techniques, and we identify a **category of attacks** that can be carried out on ICs protected with scan encryption. This vulnerability affects all scan encryption implementations and stems from a lack of data integrity check in the scan encryption mechanism.

- 6. We enhance the scan encryption, adding a lightweight integrity check mechanism based on parity codes. This improved version of scan encryption offers a complete protection against all known threats.

This thesis is organized as follows. In Chapter 1, we provide a background on testing, and we describe the existing test infrastructures that are the object of the whole thesis. In Chapter 2, we review the existing security threats on test infrastructures. In Chapter 3, we describe the state-of-the-art security countermeasures for the test infrastructure design. We present a new classification of the existing techniques, and we focus on scan encryption techniques. In Chapter 4, we highlight a vulnerability affecting state-of-the-art scan encryption techniques based on stream ciphers. Furthermore, we present new scan encryption implementations based on stream ciphers overcoming the presented vulnerability. Finally, we compare stream and block based scan encryption techniques. In Chapter 5, we discuss the security properties of scan encryption techniques. We highlight the consequences of the lack of data integrity check, presenting an attack model on some secure microprocessors. Finally, we propose an enhanced scan encryption providing data integrity check based on parity coding. In Chapter 6, we draw the conclusions.

1

The development of test techniques for integrated circuits goes hand in hand with the innovations in semiconductor technology. The deployment of Moore's Law has been possible thanks to the constant reduction of the transistors size. However, this fast development has always been coupled with the presence of fabrication defects that necessarily affect cutting-edge semiconductor technologies. For this reason, digital testing is a fundamental practice for detecting the presence of defects on the production output and classifying ICs into good and faulty. Companies face high costs for guaranteeing an efficient test flow, but this cannot be avoided. For this reason, test engineers make big efforts in order to guarantee maximum fault detection with minimum test cost. The basic test procedure consists in stimulating the device under test (DUT) with test patterns, which stimulate the internal logic of the IC and propagate any possible fault effect on the outputs. Thus, it is possible to detect the presence of a defect comparing the test responses with reference results derived from the specifications. The objective is maximizing the *fault* coverage (i.e., the percentage of faults that are detected out of the total possible faults) while minimizing the test time. However, generating test patterns and measuring the fault coverage are issues that are far from trivial. In order to measure the fault coverage, it is necessary to determine a fault *model*, i.e., a model that correlates the physical defects with a logical behavior that can be represented and simulated at design time. The most popular fault model is the stuck-at fault model, where faults are represented as constant binary values imposed on the circuit interconnections. Generating test patterns requires the usage of specific algorithms, called automatic test patterns generators (ATPG), which are able to process the circuit netlist and generate a set of test vectors (i.e., input patterns for test purposes) that are able to provide the highest fault coverage. ATPG algorithms work very well and efficiently on combinational logic, but this is not the case for sequential logic. For this reason, test infrastructures come into play. Designers must employ design-for-testability (DfT) practices for efficiently generating test vectors. These are additional modules that are added to the IC design, in

[7]: Wang et al. (2006), VLSI Test Principles and Architectures [8]: Bushnell et al. (2002), Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits order to support the generation and the application of the test [7, 8].

In this chapter, we introduce the most common DfT techniques and the related test infrastructures, which play a crucial role in this thesis. At first, we describe the overall test flow and its configuration in the production model of a typical integrated circuit. Finally, we describe in more detail some test infrastructures that are implemented inside the device at design time allowing the overall feasibility of the test procedures.

# 1.1 Testing in the IC Production Flow