# Hardware design of spiking neural networks for energy efficient brain-inspired computing

Nassim Abderrahmane

### ▶ To cite this version:

Nassim Abderrahmane. Hardware design of spiking neural networks for energy efficient braininspired computing. Artificial Intelligence [cs.AI]. Université Côte d'Azur, 2020. English. NNT: 2020COAZ4082. tel-03185295

# HAL Id: tel-03185295 https://theses.hal.science/tel-03185295

Submitted on 30 Mar 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

SCIENCES ET

TECHNOLOGIES DE

L'INFORMATION ET DE

LA COMMUNICATION

# Impact du codage impulsionnel sur l'efficacité énergétique des architectures neuromorphiques

# **Nassim ABDERRAHMANE**

Laboratoire d'Electronique, Antennes et Télécommunications (LEAT)

Présentée en vue de l'obtention du grade de docteur en électronique d'Université Côte d'Azur

Dirigée par : Benoît Miramond Soutenue le : 16 décembre 2020

### Devant le jury, composé de :

Michel Paindavoine, Professeur, Université Bourgogne Franche-Comté

Timothée Masquelier, Chargé de recherche CNRS, Centre de Recherche Cerveau et Cognition

Benoît Miramond, Professeur, Université Côte d'Azur

Jean Martinet, Professeur, Université Côte d'Azur

Sébastien Bilavarn, Maître de conférences, Université Côte d'Azur

Olivier Bichler, Ingénieur chercheur, CEA LIST

# Impact du codage impulsionnel sur l'efficacité énergétique des architectures neuromorphiques

### Jury:

### Président

Jean Martinet, Professeur des universités, Université Côte d'Azur Rapporteurs

Michel Paindavoine, Professeur des universités, Université Bourgogne Franche-Comté

Timothée Masquelier, Chargé de recherche CNRS, Centre de Recherche Cerveau et Cognition, Toulouse

### Examinateurs

Benoît Miramond, Professeur des universités, Université Côte d'Azur Sébastien Bilavarn, Maître de conférences, Université Côte d'Azur Olivier Bichler, Ingénieur chercheur, Commissariat à l'Energie Atomique et aux Energies Alternatives - CEA LIST, Palaiseau

# Résumé

Dans le contexte actuel, l'Intelligence Artificielle (IA) est largement répandue et s'applique à de nombreux domaines tels que les transports, la médecine et les véhicules autonomes. Parmi les algorithmes d'IA, on retrouve principalement les réseaux de neurones, qui peuvent être répartis en deux familles : d'une part, les Réseaux de Neurones Impulsionnels (SNNs) qui sont issus du domaine des neurosciences; d'autre part, les Réseaux de Neurones Analogiques (ANNs) qui sont issus du domaine de l'apprentissage machine. Les ANNs connaissent un succès inédit grâce à des résultats inégalés dans de nombreux secteurs tels que la classification d'images et la reconnaissance d'objets. Cependant, leur déploiement nécessite des capacités de calcul considérables et ne conviennent pas à des systèmes très contraints. Afin de pallier ces limites, de nombreux chercheurs s'intéressent à un calcul bio-inspiré, qui serait la parfaite alternative aux calculateurs conventionnels basés sur l'architecture de Von Neumann. Ce paradigme répond aux exigences de performance de calcul, mais pas aux exigences d'efficacité énergétique. Il faut donc concevoir des circuits matériels neuromorphiques adaptés aux calculs parallèles et distribués.

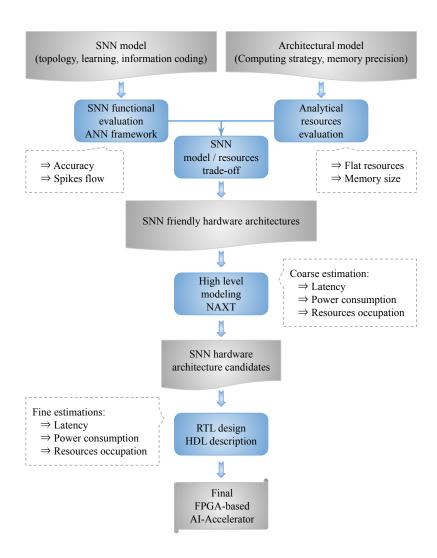

Dans ce contexte, nous avons établi un certain nombre de critères en termes de précision et de coût matériel pour différencier les SNNs et ANNs. Dans le cas de topologies simples, nous avons montré que les SNNs sont plus efficaces en termes de coût matériel que les ANNs, et ce, avec des précisions de prédiction quasiment similaires. Ainsi, dans ce travail, notre objectif est de concevoir une architecture neuromorphique basée sur les SNNs. Dans cette perspective, nous avons mis en place un flot de conception composé de trois niveaux, qui permet la réalisation d'une architecture neuromorphique dédiée et adaptée aux applications d'IA embarquée.

Dans un contexte d'efficacité énergétique, nous avons réalisé une étude approfondie sur divers paradigmes de codage neuronal utilisés avec les SNNs. Par ailleurs, nous avons proposé de nouvelles versions dérivées du codage fréquentiel, visant à se rapprocher de l'activité produite avec le codage temporel, qui se caractérise par un nombre réduit d'impulsions (spikes) se propageant dans le SNN. En faisant cela, nous sommes en mesure de réduire le nombre de spikes, ce qui se traduit par un SNN avec moins d'événements à

traiter, et ainsi, réduire la consommation énergétique sous-jacente. Pour cela, deux techniques nouvelles ont été proposées : "First Spike", qui se caractérise par l'utilisation d'un seul spike au maximum par donnée; "Spike Select", qui permet de réguler et de minimiser l'activité globale du SNN.

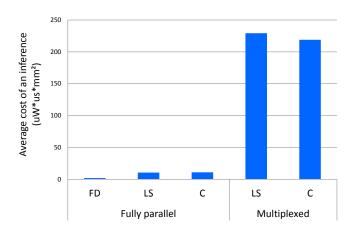

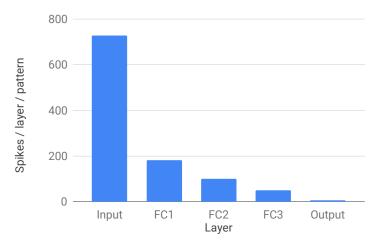

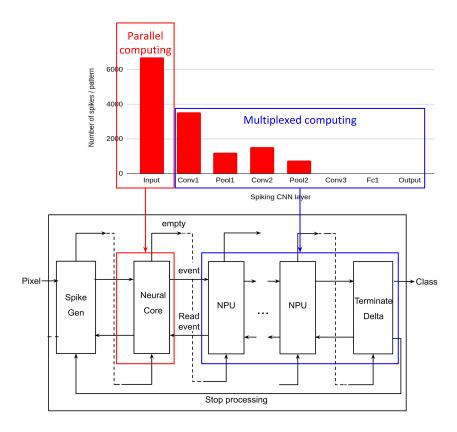

Dans la partie d'exploration RTL, nous avons comparé de manière quantitative un certain nombre d'architectures de SNN avec différents niveaux de parallélisme et multiplexage de calculs. En effet, le codage "Spike Select" engendre une régulation de la distribution des spikes, avec la majorité générée dans la première couche et peu d'entre eux propagés dans les couches profondes. Nous avons constaté que cette distribution bénéficie d'une architecture hybride comportant une première couche parallèle et les autres multiplexées. Par conséquent, la combinaison du "Spike Select" et de l'architecture hybride serait une solution efficace, avec un compromis efficace entre coût matériel, consommation et latence.

Enfin, en se basant sur les choix architecturaux et neuronaux issus de l'exploration précédente, nous avons élaboré une architecture évènementielle dédiée aux SNNs mais suffisamment programmable pour supporter différents types et tailles de réseaux de neurones. L'architecture supporte les couches les plus utilisées : convolution, pooling (mise en commun) et entièrement connectées. En utilisant cette architecture, nous serons bientôt en mesure de comparer les ANNs et les SNNs sur des applications réalistes et enfin conclure sur l'utilisation des SNNs pour l'IA embarquée.

*Mots clés*— Réseaux de Neurones Artificiels, Intelligence Artificielle, Réseaux de Neurones Impulsionnels, Codage Neuronal, Calcul Neuromorphique, Architecture Matérielle, Consommation d'Energie, Systèmes Embarqués

# **Abstract**

Nowadays, Artificial Intelligence (AI) is a widespread concept applied to many fields such as transportation, medicine and autonomous vehicles. The main AI algorithms are artificial neural networks, which can be divided into two families: Spiking Neural Networks (SNNs), which are bio-inspired models resulting from neuroscience, and Analog Neural Networks (ANNs), which result from machine learning. The ANNs are experiencing unprecedented success in research and industrial fields, due to their recent successes in many application contexts such as image classification and object recognition. However, they require considerable computational capacity for their deployment which is not adequate to very constrained systems such as 'embedded systems'. To overcome these limitations, many researchers are interested in brain-inspired computing, which would be the perfect alternative to conventional computers based on the Von Neumann architecture (CPU/GPU). This paradigm meets computing performance but not energy efficiency requirements. Hence, it is necessary to design neuromorphic hardware circuits adaptable to parallel and distributed computing.

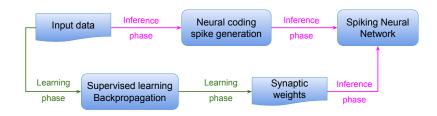

In this context, we have set criteria in terms of accuracy and hardware implementation cost to differentiate the two neural families (SNNs and ANNs). In the case of simple network topologies, we conducted a study that has shown that the spiking models have significant gains in terms of hardware cost when compared to the analog networks, with almost similar prediction accuracy. Therefore, the objective of this thesis is to design a generic neuromorphic architecture that is based on spiking neural networks. To this end, we have set up a three-level design flow for exploring and implementing neuromorphic architectures.

In an energy efficiency context, a thorough exploration of different neural coding paradigms for neural data representation in SNNs has been carried out. Moreover, new derivative versions of rate-based coding have been proposed that aim to get closer to the activity produced by temporal coding, which is characterized by a reduced number of spikes propagating in the network. In this way, the number of spikes can be reduced so that the number of events to be processed in the SNNs gets smaller. The aim in doing this approach is to reduce the hardware architecture's energy consumption. The

proposed coding approaches are: First Spike, which is characterized using at most one single spike to present an input data, and Spike Select, which allows to regulate and minimize the overall spiking activity in the SNN.

In the RTL design exploration, we quantitatively compared three SNN architectural models having different levels of computing parallelism and multiplexing. Using Spike Select coding results in a distribution regulation of the spiking data, with most of them generated within the first layer and few of them propagate into the deep layers. Such distribution benefits from a so-called 'hybrid architecture' that includes a fully-parallel part for the first layer and multiplexed parts to the other layers. Therefore, combining the Spike Select and the Hybrid Architecture would be an effective solution for embedded AI applications, with an efficient hardware and latency trade-off.

Finally, based on the architectural and neural choices resulting from the previous exploration, we have designed a final event-based architecture dedicated to SNNs supporting different neural network types and sizes. The architecture supports the most used layers: convolutional, pooling and fully-connected. Using this architecture, we will be able to compare analog and spiking neural networks on realistic applications and to finally conclude about the use of SNNs for Embedded Artificial Intelligence.

*Keywords*— Artificial Neural Networks, Artificial Intelligence, Spiking Neural Networks, Neural Coding, Neuromorphic Computing, Hardware Architecture, Energy Consumption, Embedded Systems

# Acknowledgements

I would like to first express my deepest gratitude to my thesis supervisor, Professor Benoît Miramond, for the support and trust in accepting the scientific directions of my research work. I would like to thank him for his expert advice all along this thesis, his kindness and his availability in challenging and difficult circumstances. I am very grateful for all these sharing moments.

I would like to thank all the researchers who accepted to be part of this thesis jury. I would like to express my gratitude to Michel Paindavoine and Timothée Masquelier for agreeing to report this thesis and for the time they devoted to reviewing my work. I would also like to thank Jean Martinet, Olivier Bichler and Sébastien Bilavarn for having accepted to be part of my thesis jury.

I would also like to sincerely thank the members of the ebrAIn group and the EDGE team. I particularly thank Lyes Khacef for the many discussions that we have had over the last three years and for his pleasure of sharing.

I do not forget, of course, all the staff and doctoral students of LEAT with whom I shared all these moments of uncertainty and pleasure. All those moments I shared over coffee or during soccer matches with them made the atmosphere of daily work so pleasant.

I would like to thank my family, especially my mother Ouardia and my father Abderrahmane, my brother Karim, my sisters Houria, Atika, Samira and Nassiba and my brothers-in-law, Nabyl and Nabil, and their children for sharing with me their happiness and supporting me in my efforts. I thank you for your presence regardless the distance. I thank all my friends, with a special thought for Alexis and his wife, 2 x Amine, Youcef and Said to whom I wish all the best.

A special thought goes to Yasmina with whom I have shared happy and memorable moments during the last years and for her numerous reviews of my thesis and scientific articles.

# **Contents**

| Al | bstrac | et                                            | vii |

|----|--------|-----------------------------------------------|-----|

| A  | cknov  | wledgements                                   | ix  |

| 1  | Gen    | eral introduction                             | 1   |

|    | 1.1    | Context                                       | 1   |

|    | 1.2    | Problematic                                   | 2   |

|    | 1.3    | Objectives                                    | 3   |

|    | 1.4    | Contributions                                 | 4   |

|    | 1.5    | Thesis outline                                | 5   |

| 2  | The    | oretical background                           | 7   |

|    | 2.1    | Introduction                                  | 7   |

|    | 2.2    | Neural network models                         | 7   |

|    |        | 2.2.1 Analog Neural Networks (ANNs)           | 10  |

|    |        | 2.2.2 Spiking Neural Networks (SNNs)          | 12  |

|    | 2.3    | Spiking neuron models                         | 13  |

|    | 2.4    | SNN's training                                | 16  |

|    |        | 2.4.1 Unsupervised learning with STDP         | 16  |

|    |        | 2.4.2 Supervised learning                     | 18  |

|    |        | 2.4.2.1 ANN-SNN conversion                    | 18  |

|    |        | 2.4.2.2 Learning in spiking domain            | 20  |

|    | 2.5    | Neural coding                                 | 21  |

|    |        | 2.5.1 Rate-based coding                       | 22  |

|    |        | 2.5.2 Time-based coding                       | 22  |

|    |        | 2.5.3 Contributions                           | 24  |

|    | 2.6    | Neuromorphic hardware                         | 25  |

|    |        | 2.6.1 Hardware targets                        | 25  |

|    |        | 2.6.2 Event-based computing                   | 27  |

|    |        | 2.6.3 Time-multiplexed and parallel computing | 28  |

|    | 2.7    | Related works: neuromorphic hardware chips    | 28  |

|    | 2.8    | Conclusion                                    | 34  |

| 3 | Des | ign Spa | ce Exploration Methodology             | 35 |

|---|-----|---------|----------------------------------------|----|

|   | 3.1 | Introd  | uction                                 | 35 |

|   | 3.2 | Design  | n flow framework description           | 35 |

|   | 3.3 | Prelim  | inary analytical exploration           | 36 |

|   |     | 3.3.1   | Spiking neural models exploration      | 37 |

|   |     | 3.3.2   | SNN architectural models exploration   | 39 |

|   | 3.4 | High-l  | evel SNN's architectural modeling      | 44 |

|   |     | 3.4.1   | Parallelism and distribution           | 46 |

|   |     | 3.4.2   | Memory organization                    | 47 |

|   |     | 3.4.3   | Latency, Power and Surface estimations | 48 |

|   |     | 3.4.4   | High-level modeling results            | 50 |

|   | 3.5 | Hardw   | vare architecture description of SNNs  | 52 |

|   | 3.6 | Conclu  | asion                                  | 54 |

| 4 | Neu | ral cod | ing                                    | 57 |

|   | 4.1 | Introd  | uction                                 | 57 |

|   |     | 4.1.1   | Rate-based coding                      | 58 |

|   |     | 4.1.2   | Time-based coding                      | 59 |

|   |     | 4.1.3   | Neural coding versus energy-efficiency | 60 |

|   | 4.2 | ANN-    | SNN conversion                         | 60 |

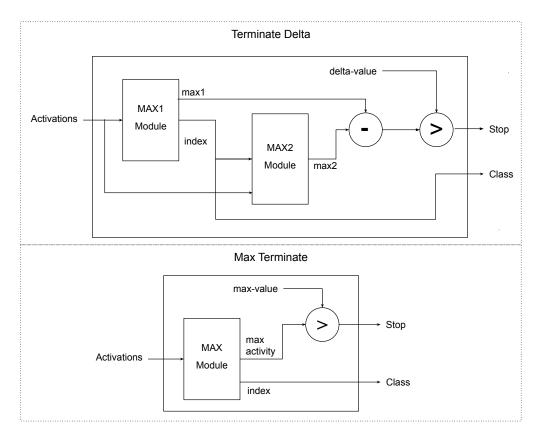

|   | 4.3 | SNNs    | classification policy                  | 62 |

|   | 4.4 | Spikes  | generation methodologies               | 64 |

|   |     | 4.4.1   | Rate-based coding                      | 64 |

|   |     | 4.4.2   | Temporal coding : Single Burst         | 65 |

|   |     | 4.4.3   | Temporal coding: First Spike           | 65 |

|   |     | 4.4.4   | Hybrid coding: Spike select            | 67 |

|   | 4.5 | Experi  | ments and results                      | 69 |

|   |     | 4.5.1   | Experiment setup                       | 69 |

|   |     | 4.5.2   | SNN classification policies            | 72 |

|   |     | 4.5.3   | ANN-SNN conversion versus accuracy     | 74 |

|   |     | 4.5.4   | State-of-the-art accuracy results      | 74 |

|   |     | 4.5.5   | Spikes generation                      | 75 |

|   | 4.6 | Discus  | ssions                                 | 82 |

|   | 4.7 | Conclu  | asion                                  | 84 |

| 5 | RTL | explor  | ation of neuromorphic architectures    | 87 |

|   | 5.1 | Introd  | uction                                 | 87 |

|   | 5.2 | Prelim  | inary SNN to ANN confrontation         | 88 |

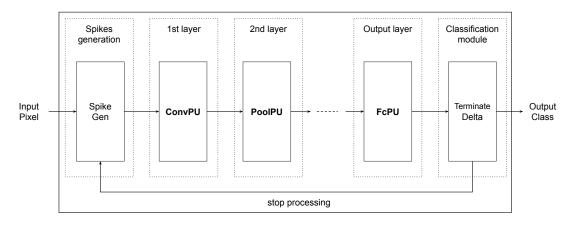

|   | 5.3 | Comp    | lete hardware architecture overview    | 91 |

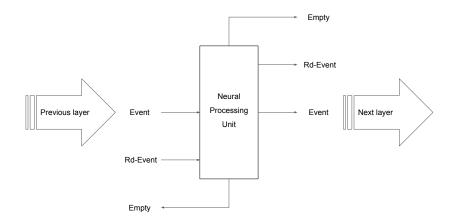

| 5.4   | Event-based communication protocol                           | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5   | Deep SNNs hardware implementation                            | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

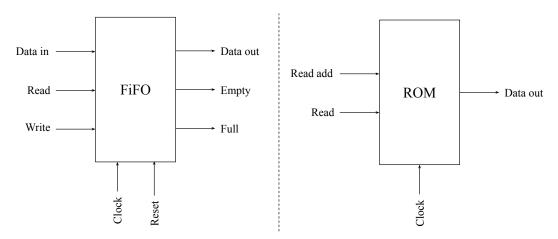

|       | 5.5.1 Elementary hardware modules                            | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 5.5.2 Fully-Parallel Architecture                            | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 5.5.3 Time-Multiplexed Architecture                          | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 5.5.4 Hybrid Architecture                                    | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.6   | Experiment and results                                       | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.7   | Discussions                                                  | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.8   | Conclusion                                                   | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Spil  | king CNN hardware architecture                               | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.1   |                                                              | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.2   |                                                              | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 1 0                                                          | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                              | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.3   | 1 0                                                          | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.4   |                                                              | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.5   |                                                              | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 6.5.1 Functional validation                                  | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 6.5.2 Hardware cost                                          | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.6   | Discussions                                                  | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.7   | Conclusion                                                   | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Con   | aclusion                                                     | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.1   | Restatement of the objectives                                | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.2   | ,                                                            | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.3   | •                                                            | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| bliog | raphy                                                        | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 5.5  5.6 5.7 5.8  Spil 6.1 6.2  6.3 6.4 6.5  Con 7.1 7.2 7.3 | 5.5 Deep SNNs hardware implementation 5.5.1 Elementary hardware modules 5.5.2 Fully-Parallel Architecture 5.5.3 Time-Multiplexed Architecture 5.5.4 Hybrid Architecture  5.6 Experiment and results 5.7 Discussions 5.8 Conclusion  Spiking CNN hardware architecture  6.1 Introduction 6.2 Convolutional processing unit – ConvPU 6.2.1 Control module 6.2.2 Computing core 6.3 Pooling Processing Unit – PoolPU 6.4 Fully-connected Processing Unit 6.5 Experiments and results 6.5.1 Functional validation 6.5.2 Hardware cost 6.6 Discussions 6.7 Conclusion  Conclusion  Conclusion  7.1 Restatement of the objectives 7.2 Summary and review of the work done |

# **List of Figures**

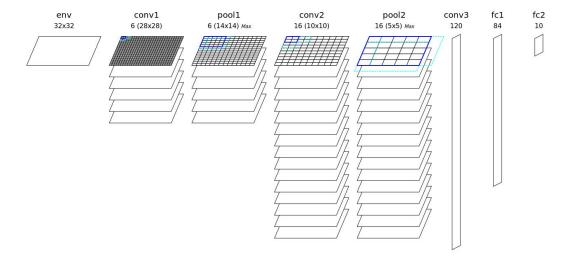

| 2.1  | LeNet CNN architecture used with MINIST dataset – gener-                       |    |

|------|--------------------------------------------------------------------------------|----|

|      | ated from the N2D2 framework (Bichler et al., 2017)                            | 8  |

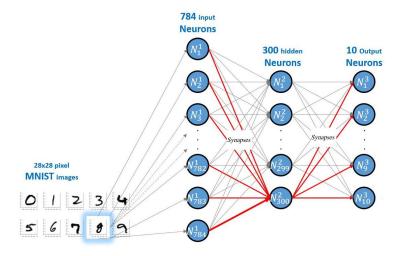

| 2.2  | A one hidden layer MLP network applied to MNIST dataset                        | 11 |

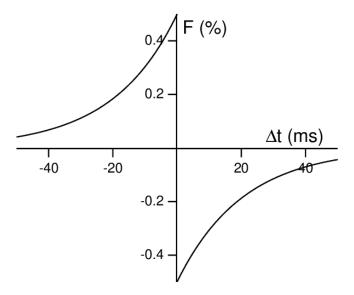

| 2.3  | Spike-time-dependent synaptic modification rule presented in                   |    |

|      | (Song, Miller, and Abbott, 2000)                                               | 17 |

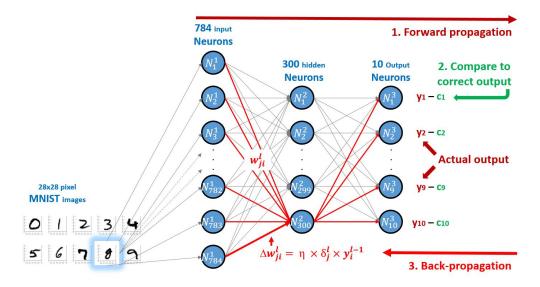

| 2.4  | Back-propagation algorithm applied to a one-hidden layer neu-                  |    |

|      | ral network                                                                    | 19 |

| 2.5  | ANN-SNN conversion mechanism                                                   | 20 |

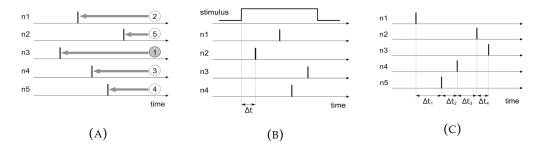

| 2.6  | Temporal coding: (A) rank order coding; (B) time-to-first-spike                |    |

|      | coding and (C) relative latency coding. Legend: $n1 - n5$ repre-               |    |

|      | sent the neurons labels; the vertical bars represent the neural                |    |

|      | firing times; the circled numbers indicate the arriving order of               |    |

|      | the spikes; $\Delta t$ is the latency between the stimulus onset and the       |    |

|      | first spike; $\Delta t1 - \Delta t4$ are the inter-spike latencies (from Ponu- |    |

|      | lak and Kasinski, 2011)                                                        | 23 |

| 3.1  | Design space exploration framework diagram                                     | 37 |

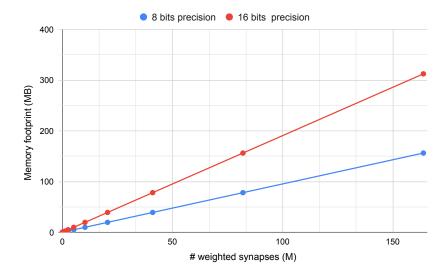

| 3.2  | Memory occupation of two encoding precisions (8 and 16 bits)                   |    |

|      | versus the number of weighted synaptic connections                             | 41 |

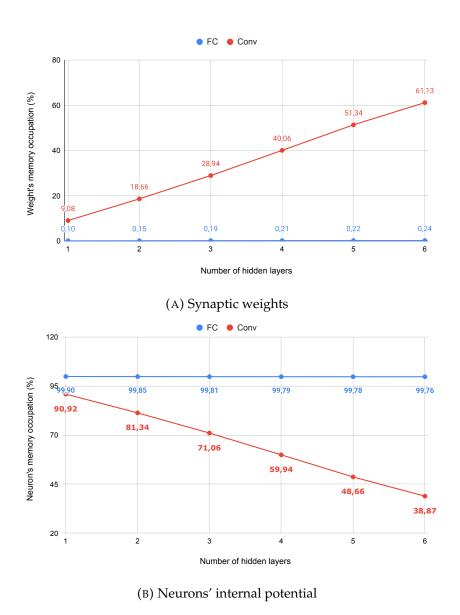

| 3.3  | Neuron and weight memory requirements versus the SNN size.                     | 42 |

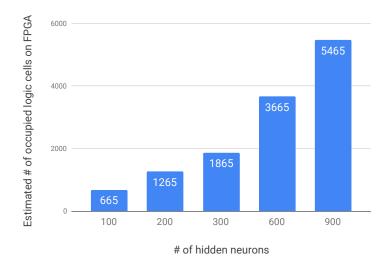

| 3.4  | Theoretical FPGA occupation versus hidden layer size – MNIST.                  | 44 |

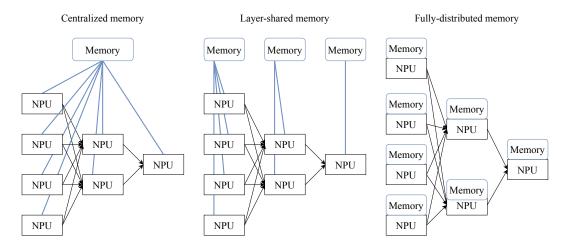

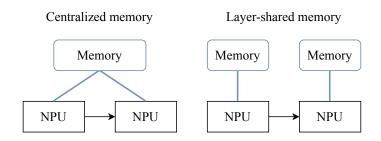

| 3.5  | Memory organizations for FPA architectures                                     | 48 |

| 3.6  | Memory organizations for TMA architectures                                     | 48 |

| 3.7  | Qualitative cost function for a 804-hardware-neurons SNN for                   |    |

|      | the different architectures available in NAXT                                  | 50 |

| 3.8  | Average number of spikes generated for one pattern per layer                   |    |

|      | – "784-3x(300)-10" SNN on MNIST                                                | 52 |

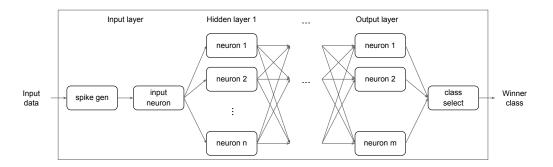

| 3.9  | FPA simplified representation                                                  | 53 |

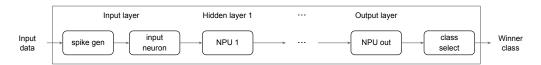

| 3.10 | TMA simplified representation                                                  | 54 |

| 3.11 | HA simplified representation                                                   | 55 |

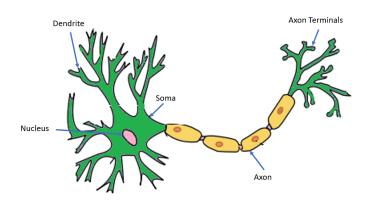

| 4.1  | Simplified representation of a biological neuron - from (Yu et     |     |

|------|--------------------------------------------------------------------|-----|

|      | al., 2014)                                                         | 58  |

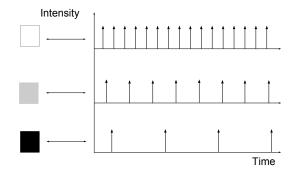

| 4.2  | Rate-based coding paradigm                                         | 59  |

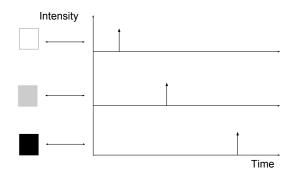

| 4.3  | Temporal coding paradigm                                           | 59  |

| 4.4  | Non-leaky Integrate-and-Fire neuron                                | 61  |

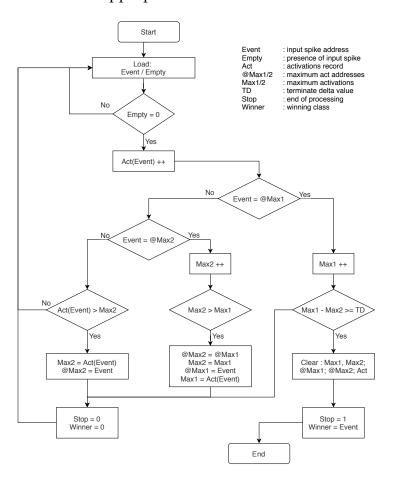

| 4.5  | Terminate Delta flowchart                                          | 63  |

| 4.6  | Max Terminate flowchart                                            | 64  |

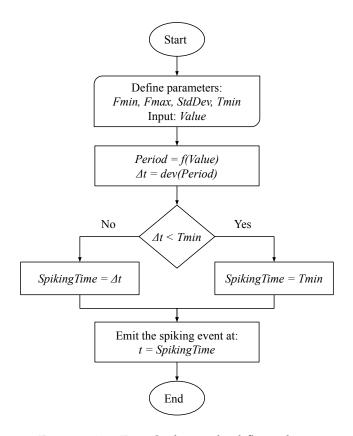

| 4.7  | First Spike method flow-chart                                      | 66  |

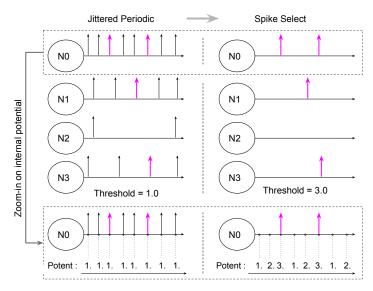

| 4.8  | Spike Select and Jittered Periodic codings effect on output spikes |     |

|      | of an integrate-and-fire neurons group                             | 68  |

| 4.9  | Pattern examples of the datasets used in this work                 | 71  |

| 4.10 | Terminate Delta and Max Terminate versus accuracy and spik-        |     |

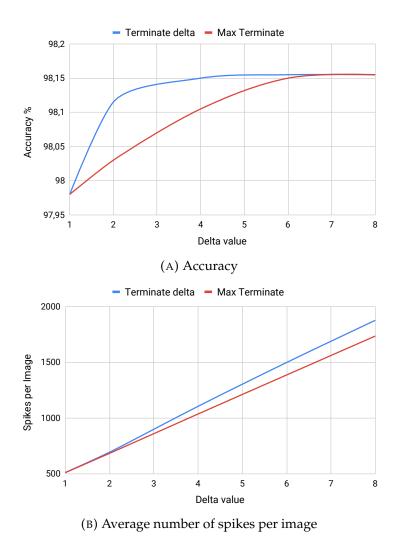

|      | ing activity - 784-3x(300)-10 - MNIST data-set                     | 73  |

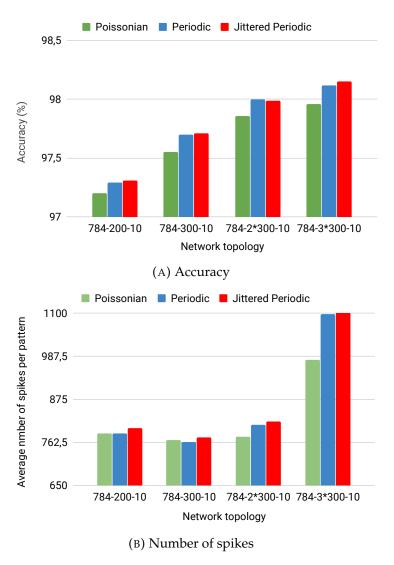

| 4.11 | Rate-based coding – MNIST                                          | 77  |

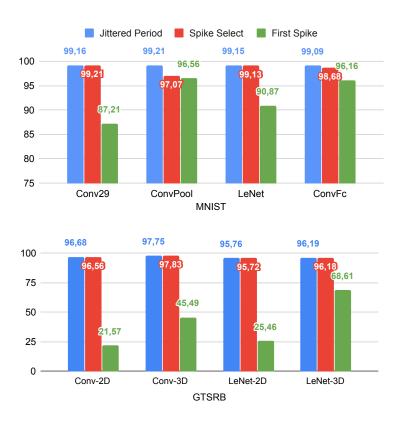

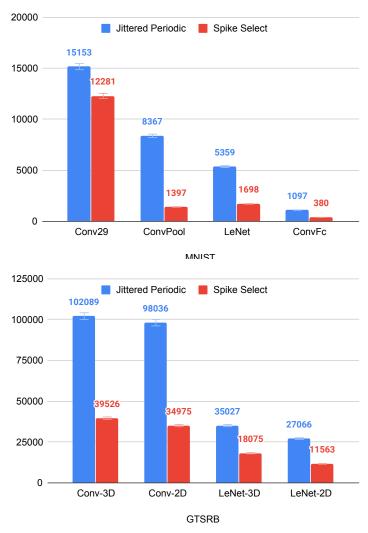

| 4.12 | Spike generation versus accuracy - MNIST & GTSRB                   | 79  |

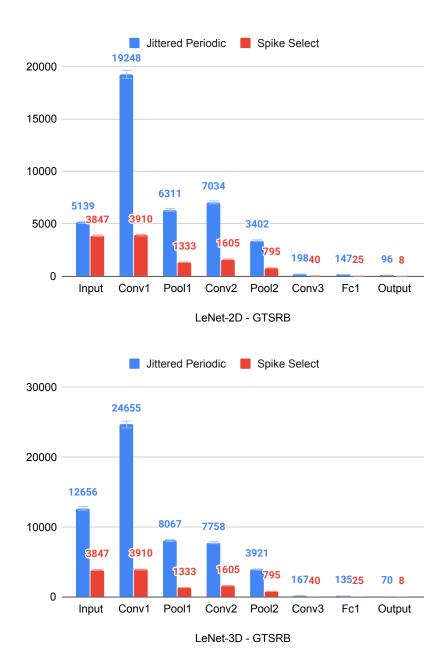

| 4.13 | Spike Select and Jittered Periodic versus total spiking data       | 81  |

| 4.14 | Spike Select and Jittered Periodic versus spiking data distribu-   |     |

|      | tion – GTSRB                                                       | 82  |

| 4.15 | Spike Select and Hybrid Architecture for embedded hardware         |     |

|      | classification                                                     | 84  |

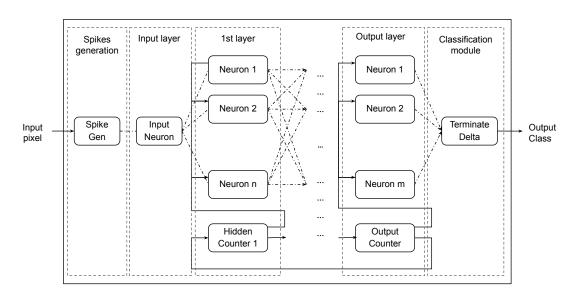

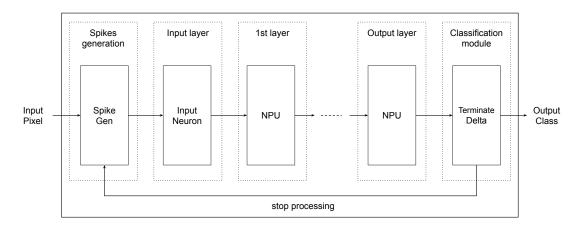

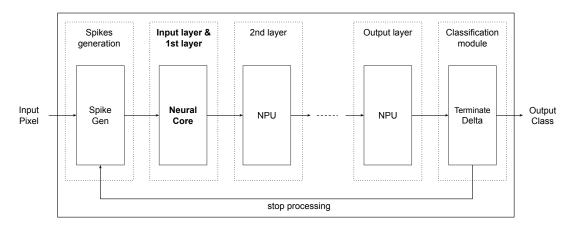

| 5.1  | Input-time-multiplexed SNN's architecture                          | 89  |

| 5.2  | Schematic diagram of proposed hardware architectures               | 92  |

| 5.3  | FiFo-based communication system used to link the architec-         |     |

|      | ture layers                                                        | 94  |

| 5.4  | I/O ports of FiFo and ROM memory blocks                            | 96  |

| 5.5  | Schematic diagram of the classification modules                    | 98  |

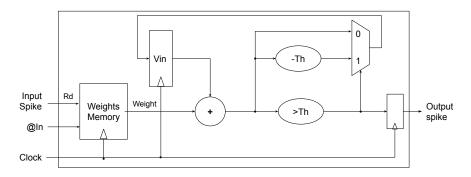

| 5.6  | IF neuron module's internal structure                              | 99  |

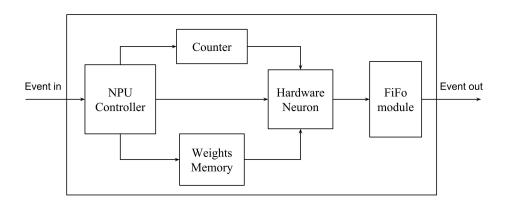

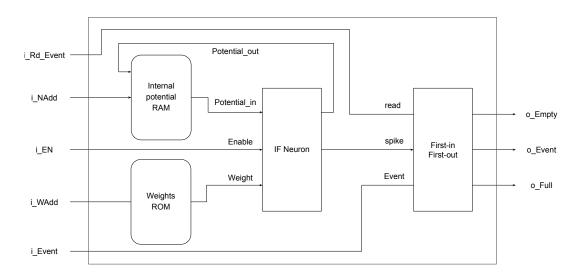

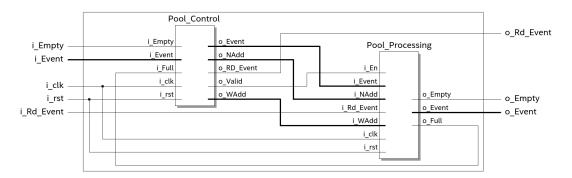

| 5.7  | Neural Processing Unit simplified block diagram                    | 99  |

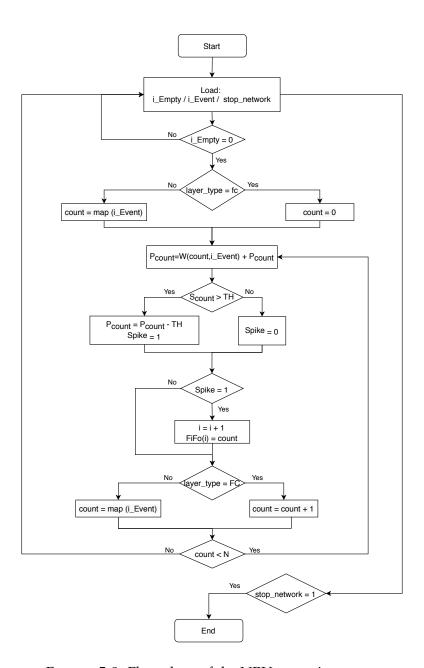

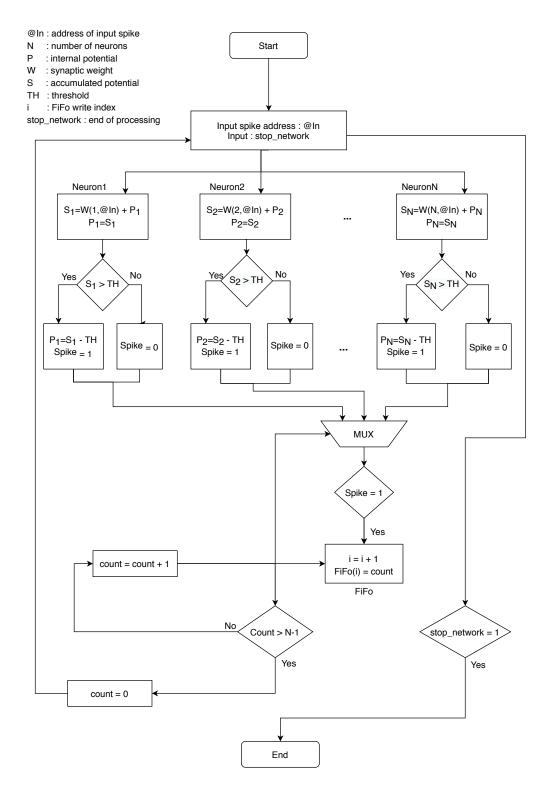

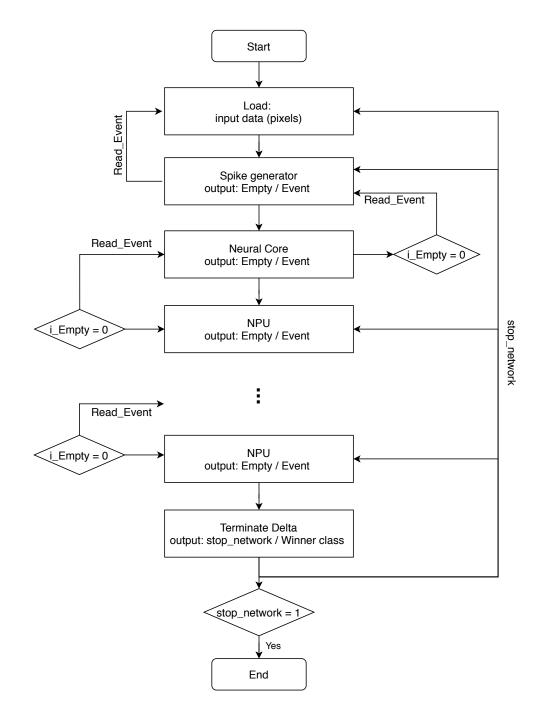

| 5.8  | Flow chart of the NPU operating steps                              | 101 |

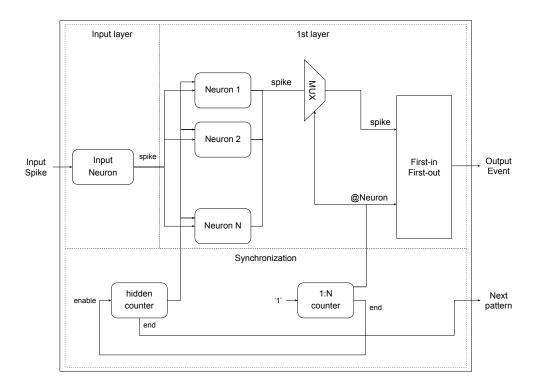

| 5.9  | Neural Core module schematic diagram                               | 102 |

| 5.10 | Flow chart of the Neural Core operating steps                      | 103 |

|      | FPA simplified schematic diagram                                   | 104 |

|      | TMA simplified schematic diagram                                   | 105 |

| 5.13 | HA simplified schematic diagram                                    | 106 |

|      | Operating steps of the Hybrid Architecture flow chart              | 107 |

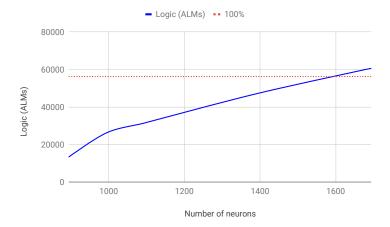

|      | FPA architecture: FPGA logic (ALM) utilization versus the SNN      |     |

|      | number of neurons; Different SNN topologies are used, refer        |     |

|      | to table 5.3                                                       | 109 |

| 5.16 | FPA architecture: FPGA registers occupation versus the SNN     |     |

|------|----------------------------------------------------------------|-----|

|      | number of neurons; Different SNN topologies are used, refer    |     |

|      | to table 5.3                                                   | 109 |

| 5.17 | Logic occupation of two SNNs by the three architectures: FPA,  |     |

|      | TMA and HA                                                     | 111 |

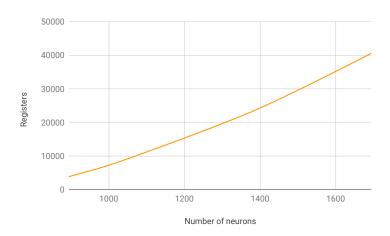

| 5.18 | Trade-off between logic and latency of the hardware architec-  |     |

|      | tures according to three neural coding schemes                 | 113 |

| 5.19 | Theoretical vs. experimental FPGA occupation with respect to   |     |

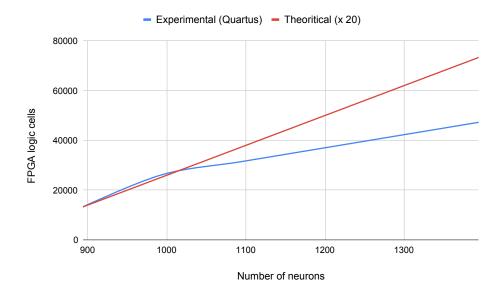

|      | the number of neurons – FPA                                    | 114 |

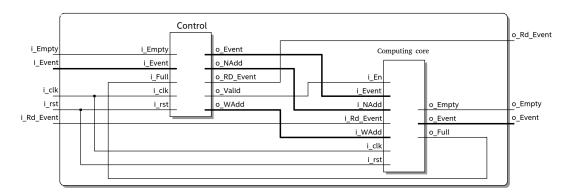

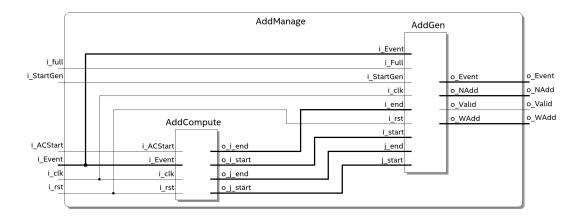

| 6.1  | Convolution Processing Unit schematic diagram                  | 118 |

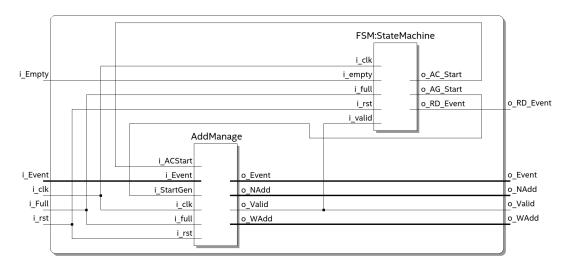

| 6.2  | Convolution control module schematic diagram                   | 119 |

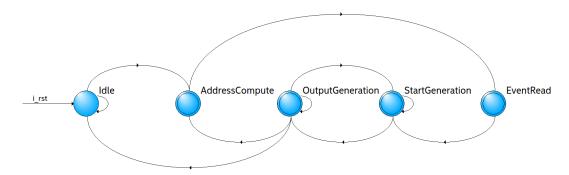

| 6.3  | Convolution control: finite state machine                      | 119 |

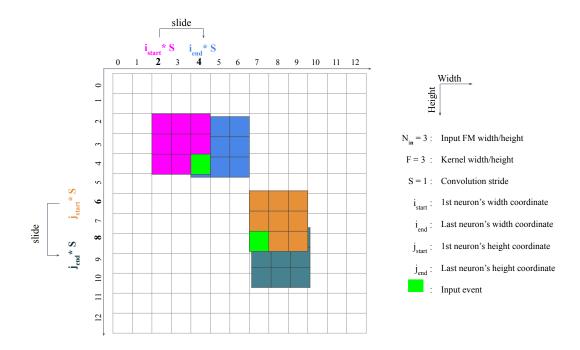

| 6.4  | Address management module's internal structure                 | 121 |

| 6.5  | Address compute: coordinates of the first and last convolu-    |     |

|      | tional neurons having input event in their receptive field     | 123 |

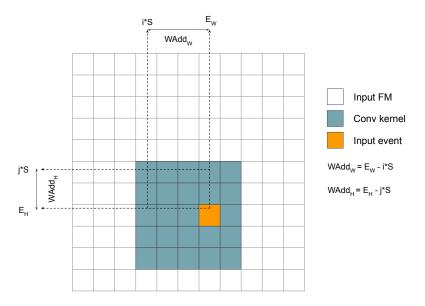

| 6.6  | A convolution filter covering an input event                   | 125 |

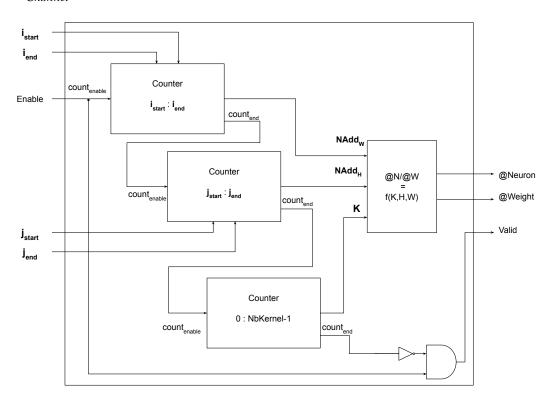

| 6.7  | Convolution address generator module                           | 125 |

| 6.8  | Convolution computing core schematic diagram                   | 126 |

| 6.9  | Pooling Processing Unit schematic diagram                      | 128 |

| 6.10 | Convolution versus pooling features mapping                    | 129 |

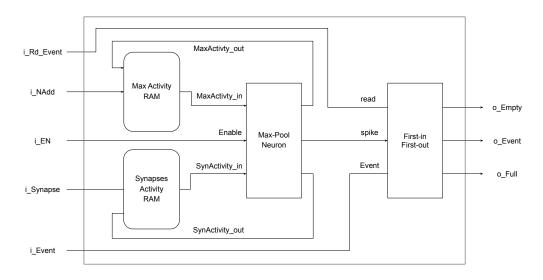

| 6.11 | Pooling computing core internal structure                      | 130 |

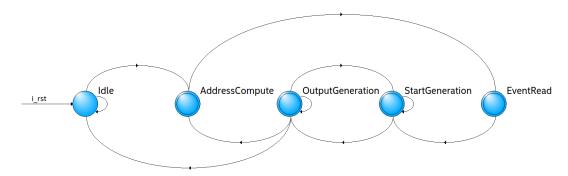

| 6.12 | A graph representation of the fully-connected finite state ma- |     |

|      | chine                                                          | 132 |

| 6.13 | Example of simulation under Modelsim tool of the architec-     |     |

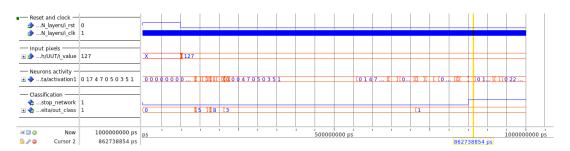

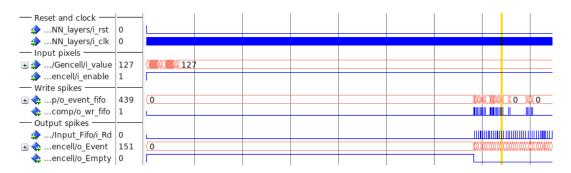

|      | ture showing the classification of the number "1"              | 134 |

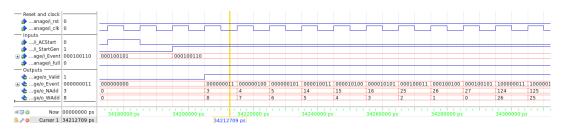

| 6.14 | Spike generation simulation                                    | 134 |

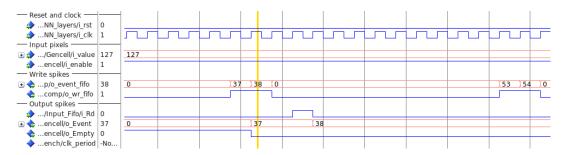

| 6.15 | Zoom-in on spike generation simulation                         | 135 |

| 6.16 | Convolution layer simulation                                   | 135 |

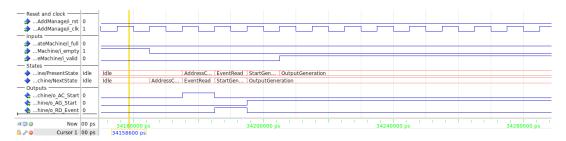

| 6.17 | FSM simulation                                                 | 136 |

| 6.18 | Address generation module simulation                           | 136 |

| 6.19 | Simulation of hardware neuron                                  | 137 |

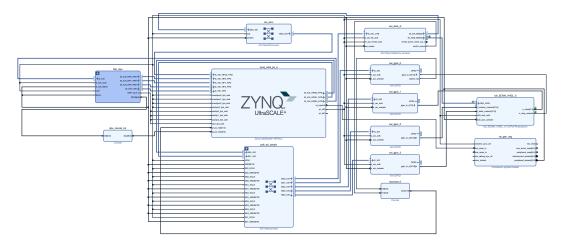

| 6.20 | On-chip validation platform structure (generated from Vivado   |     |

|      | tool)                                                          | 138 |

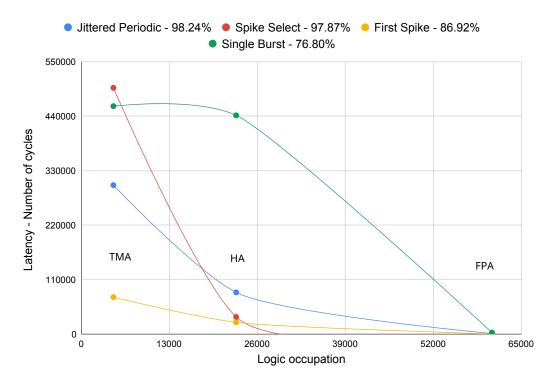

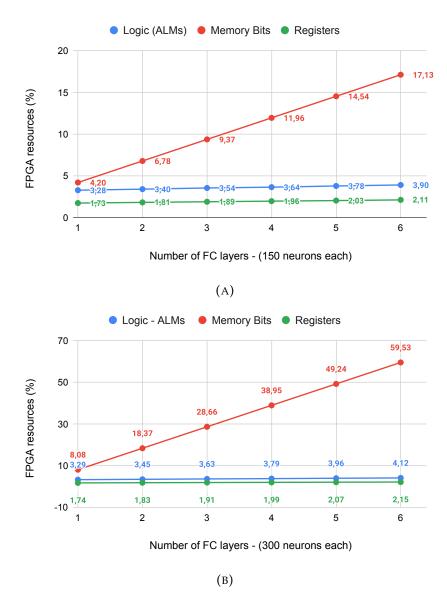

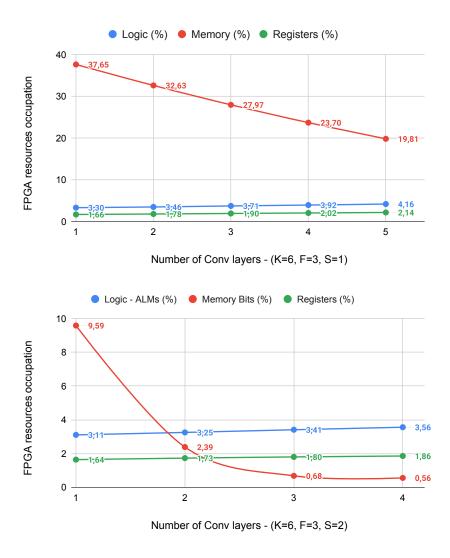

| 6.21 | FPGA resources occupations versus the number of FC layers.     | 140 |

|      | FPGA resources occupations versus the number of convolu-       |     |

|      | tional layers                                                  | 141 |

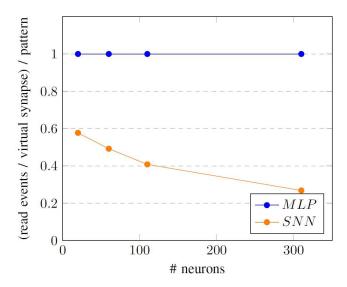

| 6.23 | A comparison between the number of events read per synapse     |     |

|      | in SNNs and ANNs.                                              | 142 |

# **List of Tables**

| 2.1 | Neuromorphic hardware architectures. Legend: "D" for digital, "A" for Analog, "On" for online learning and "off" for of- |            |

|-----|--------------------------------------------------------------------------------------------------------------------------|------------|

|     | fline learning.                                                                                                          | 29         |

| 3.1 | ANN's learning hyper-parameters used in this work. Legend                                                                | 20         |

| 3.2 | : LR stands for Learning Rate                                                                                            | 39         |

| J.Z | age versus the number of hidden conv. layers – 8 bits encoding                                                           |            |

|     | precision                                                                                                                | 41         |

| 3.3 | Neurons' internal potential and synaptic weights memory us-                                                              |            |

|     | age versus number of hidden FC layers – 8 bits encoding pre-                                                             |            |

|     | cision                                                                                                                   | 41         |

| 3.4 | Simulation results for a 784-10-10 SNN hardware for the avail-                                                           |            |

|     | able architectures in NAXT, with SRAM on-chip memories.                                                                  |            |

|     | Legend: LD: Layer Distributed; LS: Layer Shared; C: Central-                                                             |            |

|     | ized                                                                                                                     | 51         |

| 4.1 | ANN topologies used with MNIST and GTSRB data-sets. Leg-                                                                 |            |

|     | ends: "c" stands for convolution, "p" stands for max pooling,                                                            |            |

|     | "s" stands for stride and no letter means FC layer                                                                       | 72         |

| 4.2 | Terminate Delta and Max Terminate versus accuracy and spik-                                                              |            |

|     | ing activity on MNIST dataset. Neural coding: Jittered Peri-                                                             |            |

|     | odic; Topology: 784-3x(300)-10                                                                                           | 72         |

| 4.3 | Accuracy results of analog and spiking models                                                                            | 74         |

| 4.4 | Classification accuracy results of different SNNs on MNIST                                                               |            |

|     | data-set                                                                                                                 | 75         |

| 4.5 | Classification accuracy results of different network topologies                                                          |            |

| 1.6 | on GTSRB data-set                                                                                                        | <b>7</b> 5 |

| 4.6 | Rate-based coding versus accuracy - MNIST                                                                                | 76         |

| 4.7 | Rate-based coding versus spiking activity - MNIST                                                                        | 76         |

| 4.8 | Spike generation versus accuracy – MNIST dataset                                                                         | 78<br>70   |

| 4.9 | Spike generation versus accuracy – GTSRB dataset                                                                         | 78         |

| 4.10 | MNIST. Network: "FcNet2: 784-3x(300)-10"                                                                                                                                        | 79       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.11 | Spike Select and Jittered Periodic versus total spiking data – MNIST                                                                                                            | 80       |

| 4.12 | Spike Select and Jittered Periodic versus total spiking data – GTSRB                                                                                                            | 80       |

| 4.13 | Spike Select and Jittered Periodic versus spiking data distribution – GTSRB                                                                                                     | 80       |

| 5.1  | SNN vs. ANN comparison results on the topology: 784-300-10. The ASIC results correspond to a CMOS 65nm technology obtained using Synopsys Design Compiler. The FPGA device      | 0.0      |

| 5.2  | is an Intel Cyclone V (5CGXFC9E7F35C8)                                                                                                                                          | 90<br>90 |

| 5.3  | FPGA Logic ALMs and registers utilization by the FPA architecture.                                                                                                              | 109      |

| 5.4  | FPGA resource occupation of different SNNs by the TMA architecture.                                                                                                             | 110      |

| 5.5  | FPGA cyclone V resources occupation of different SNNs with by the HA architecture                                                                                               | 110      |

| 5.6  | Latency (number of cycles / image) of the three architectures using three neural coding schemes – SNN: 784-3x(300)-10                                                           | 111      |

| 6.1  | Convolution FSM states transitions                                                                                                                                              | 119      |

| 6.2  | Fully-connected FSM states transitions                                                                                                                                          |          |

| 6.3  | FPGA resources occupation of Spiking CNNs with different number of fully-connected layers. Topology: "28x28 - 6c3s2-6c3s2 - N(FC) - 10" with N the number of FC layers that are |          |

| 6.4  | composed of 150 or 300 neurons                                                                                                                                                  | 139      |

|      | F=3, S=1 or 2)                                                                                                                                                                  | 139      |

# List of Abbreviations

AI Artificial Intelligence

ALM Adaptive Logic Module

ANN Analog Neural Network

ASIC Application-Specific Integrated Circuit

AXI Advanced eXtensible Interface

CMOS Complementary Metal Oxide Semiconductor

CNN Convolutional Neural Network

DMA Direct Memory AccessDNN Deep Neural Network

DPU Deep Learning Processor Unit

DSP Digital Signal ProcessorDVS Dynamic Vision SensorEBS Event-Based Sensor

FNN Formal Neural Network

FiFo First in First out

FPA Fully-Parallel Architecture

**FPGA** Field-Programmable Gate Array

GTSRB German Traffic Sign Recognition Benchmark

**HA** Hybrid Architecture

HICANN High-Input Count Analog Neural Network

IP Intellectual Property

(L)IF (Leaky) Integrate-and-Fire

LUT Look-Up Table

MLP Multi-Layer Perceptron

MNIST Modified National Institute of Standards and Technology database

N2D2 Neural Network Design & Deployment

NPU Neural Processing UnitPL Programmable LogicPS Processing System

RAM Random-Access Memory

ROM Rread Only Memory

RTL Register Transfer Level

SDRAM Synchronous Dynamic RAM

SNN Spiking Neural Network

SOPS Synaptic Operation per Second

STDP Spike Timing Dependent Plasticity

TMA Time-Multiplexed Architecture

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrtaed Circtuis

# Author's publication list

# Journal papers

Nassim Abderrahmane, Edgar Lemaire, and Benoît Miramond (2020).

"Design Space Exploration of Hardware Spiking Neurons for Embedded Artificial Intelligence". In: Neural Networks 121, pp. 366 –386.

ISSN: 0893-6080. DOI: https://doi.org/10.1016/j.neunet.2019.09.024.

## **Patents**

— Nassim Abderrahmane and Benoît Miramond (2020b). *Hardware Architecture for Spiking Neural Networks and Method of Operating*. International Patent submitted to "Office européen des brevets".

# International conference papers

- Nassim Abderrahmane and Benoit Miramond (2020a). "Neural coding: adapting spike generation for embedded hardware classification".

In: *International Joint Conference on Neural Networks (IJCNN)*, pp. 1–8.

- Nassim Abderrahmane and Benoit Miramond (2019). "Information coding and hardware architecture of spiking neural networks". In: Euromicro Conference on Digital System Design (DSD), "1–8".

- Lyes Khacef, Nassim Abderrahmane, and Benoit Miramond (2018). "Confronting machine-learning with neuroscience for neuromorphic architectures design". In: *International Joint Conference on Neural Networks (IJCNN)*, pp. 1–8.

# Chapter 1

# General introduction

# 1.1 Context

Artificial neural networks are derived and inspired from the biological brain, and have become the most well-known and frequently used form of Artificial Intelligence. Even though these neural models have garnered a lot of interest in recent years, they stem from the 1940s with the apparition of the first computer. Subsequent work and advancements have led to the development of a wide variety of neural models. Convolutional Neural Network (CNN) is the most used one today. It is inspired from the biological visual perception mechanism of living beings. In 1959, Hubel and Wiesel have found that animals possess biological cells in their visual cortex which are detecting the light present in their receptive field (Hubel and Wiesel, 1959). In 1980, Fukushima was inspired by this finding and proposed what is considered as the CNN's predecessor: the neocognitron (Fukushima, 1980).

A decade later, LeCun et al. proposed the CNN revolutionary framework that is presented as a Deep Neural Network (DNN) composed of several layers of different types, called "LeNet-5" (LeCun et al., 1990). This DNN is specifically used to ensure the handwritten digits classification task. More than a decade later, several models have been proposed, they came with improvements and facilitations in training DNNs. Krizhevsky, Sutskever, and Hinton proposed one of them, the AlexNet model, it has a similar, but deeper, structure to LeNet-5 with more layers (Krizhevsky, Sutskever, and Hinton, 2017). This model was very successful, it brought out many methods and materials coming from other works that improved classification performances. Among them, we can cite VGGNet (Simonyan and Zisserman, 2014), ZFNet (Zeiler and Fergus, 2014), GoogleNet (Szegedy et al., 2015) and ResNet (He et al.,

2015). Recent advances on DNNs can be found in the paper proposed by Gu et al. in (Gu et al., 2015).

Meanwhile, these neural algorithms have become more popular with applications in several domains such as image and video recognition, image classification, medical image analysis, and natural language processing. This success can be awarded to two factors. First, the high-performance computing capabilities of modern CPU/GPU based computers that accelerated the implementation, the training and the inference stages. Second, the huge amount of available open source labeled data for training DNN algorithms, which increased the number of applications and contributed to the improvement of these algorithms.

These neural networks could be separated into three different generations, distinguished by the neural computation and coding. The first generation is composed of neural models based on the traditional McCulloch and Pitts neuron, which outputs discrete binary values (Schuman et al., 2017).

The second generation is characterized by the use of continuous activation functions within their neurons rising to more complex architectures, such as Boltzmann Machines (Ackley, Hinton, and Sejnowski, 1985), Hopfield Networks (Hopfield, 1982), Perceptrons, Multi-Layer Perceptrons (MLP) (Rumelhart, McClelland, and PDP Research Group, 1986) and Convolutional Neural Networks (Krizhevsky, Sutskever, and Hinton, 2017).

Finally, the third generation is composed of neural algorithms called Spiking Neural Networks (SNNs). In SNN models, the neural information is encoded into spikes or action potentials, inspired from neuroscience. Indeed, the spiking models and inter-neuron connections used with SNNs mimic biological neurons and synaptic communication mechanisms based on action potentials. According to this spike-based coding paradigm, SNNs are characterized by an event-based processing where spiking neuron computations are operated only when receiving input spikes.

# 1.2 Problematic

The recent performance of DNNs in terms of image classification has given them a major role in machine-learning field and AI research. After a first phase of offline experiments, these methods have started to proliferate in our daily life through autonomous applications everywhere and close to the user. 1.3. Objectives 3

Thus, an increasing number of applications such as smart devices, IoTs or autonomous vehicles are requiring an efficient embedded implementation.

However, the fact that these neural networks process analog and continuous data makes their computation more complex and requires to be executed on high-performance computing platforms. As a result, their initial implementation on classical Von-Neuman architectures (CPU/GPU) is too resource-and energy-intensive for such constraining systems (embedded systems). In addition to their computational complexity, these intrinsically parallel algorithms are not adapted to the general-purpose sequential processors. Therefore, it is essential to, first, reduce the computation complexity of these neural systems and, second, deploy them on dedicated neuromorphic systems. These architectures are designed to fit the parallel and distributed computing paradigm of ANNs, which allows their implementation on embedded systems.

# 1.3 Objectives

Recent literature considers the third generation of neural algorithms, i.e. Spiking Neural Networks (SNNs), as the alternative to Analog Neural Networks (ANNs) for embedded artificial intelligence applications. According to their spike-based coding paradigm, SNNs perform an event-based processing: computation is held by a spiking neuron when and only when it receives an input spike. Without any stimulation, the neuron remains idle. Hence, computation is strictly performed for relevant information propagation, in contrast to ANNs, where the states of every neuron are updated periodically. Moreover, the computation is usually much simpler in spiking neurons than in formal neurons. Hence, SNNs are much more promising for low-power embedded hardware implementations than ANNs, considering the advantages in terms of event-driven computation and resource consumption brought by the spiking neuron model. Consequently, the objective of this thesis is the hardware design of a generic neuromorphic computing architecture capable of running any embedded AI application based on SNNs. Indeed, the neural algorithm structure depends on the user-defined application data, where different types and sizes of the neural network models could be employed. Moreover, spiking data is naturally very sparse but using rate-coding a huge quantity is processed by the SNN, therefore, we explore novel coding schemes aiming to reduce this spiking activity.

# 1.4 Contributions

The thesis contribution consists in studying more precisely the question of the digital hardware design of spiking neural networks for energy-efficient implementation of embedded AI applications using static data. The SNNs are all the more advantageous as we plan to execute them in dedicated accelerators. Then they take full advantage of the event-driven nature of data flows, the simplicity of their elementary operators and their local and distributed computing and learning properties. Several specific hardware solutions have already been proposed in the literature, but they are only solutions isolated from the overall design space where network topologies are often constrained by the characteristics of the circuit architecture. We recommend the opposite approach, which consists in generating the architecture that best supports the network topology. This is done by: first, using a neural coding scheme generating, as little as possible, spiking events while keeping the desired accuracy; second, using an architectural model that optimally uses the available hardware resources to best fit the energy- and processing-efficiency requirements.

Through this study, we therefore propose an exploration framework that makes it possible to evaluate the impact of different spiking models on the effectiveness of their hardware implementation. With this framework, we start from a wide variety of hardware implementation choices to incrementally refine the scope to find the most suitable at the end.

Moreover, we focus on neural coding for spike generation with SNNs by studying its impact on neuromorphic system efficiency. Our intuition is that using time-based coding instead of rate-based coding leads to a system with reduced power consumption but with lower accuracy results. When using time-based coding a few numbers of spikes are used to encode data, whereas with rate-based coding a greater spiking activity is recorded in the network, thus increasing resource and energy intensiveness of the system. However, at the same time, higher accuracy results are obtained with rate coding than with temporal coding. Therefore, we explore additional spike coding methods attempting to mimic time-based coding paradigm in terms of spiking activity and rate-based coding in terms of accuracy performance.

In the context of hardware SNN implementation, we use a high-level neuromorphic architectural exploration simulator that provides rough energy

1.5. Thesis outline 5

consumption, latency and chip surface estimates for several built-in architectural configurations. This simulator, acting as a first evaluation tool, provides results helping the filtering of the large panel of architectural choices. Therefore, fewer architecture candidates appear at the output of this stage that are then described using VHDL to be tested at Register Transfer Level, thus delivering precise timings, logic resources and energy measures. Notably, we propose a novel Hybrid Architecture, which combines the advantages of both multiplexed and parallel hardware implementations.

### 1.5 Thesis outline

The remaining part of this thesis manuscript is composed of six chapters. First, in chapter 2 we describe the background and the context of spiking neural networks and neuromorphic computing. Then, in chapter 3, we present the design framework of the thesis and give high-level results of some architectural models for hardware SNNs. Then, we discuss neural coding and report the results of some explored coding schemes ranging from rate-based to time-based paradigms, in chapter 4. Then, in chapter 5, we describe a Register-Transfer-Level (RTL) exploration of different neuromorphic architectures for SNNs that are based on fully-connected layers. This RTL exploration comes up with a set of architectural choices that are used to design a generic hardware architecture supporting spiking CNNs. This spiking CNN architecture is described in chapter 6. Finally, we present the thesis conclusions and propose some future directions in the final chapter 7.

# Chapter 2

# Theoretical background

## 2.1 Introduction

The objective of this thesis is designing a neuromorphic architecture based on bio-inspired approaches to adapt to the embedded system constraints. Moreover, the architecture has to respect some criteria in terms of configurability, programmability, scalability and genericity.

In this chapter, we describe the theoretical concepts and methods that will serve for the selection of some technical choices for achieving our objectives. First, we introduce the neural network models found in literature and the ones we are dealing with. Second, we present some spiking neuron models that are the main computing units of the spiking neural network. Afterwards, we discuss the SNN's training and neural coding which are two important concepts in the construction of spiking neuromorphic systems. Then, we define the basic paradigms and architectural models for the implementation of neuromorphic hardware chips. Finally, we present some related works dealing with neuromorphic computing.

# 2.2 Neural network models

In this work, we deal with the design of embedded electronic systems capable of performing tasks commonly considered as AI applications such as image classification or object recognition. For performing such tasks, the most commonly used solution is based on artificial neural networks.

There are many types of neural network topology, such as recurrent, feedforward or self-organizing maps. In this work, we consider only feed-forward networks because they are the simplest for implementation in hardware and provide the state-of-the-art accuracy performance for many AI applications.

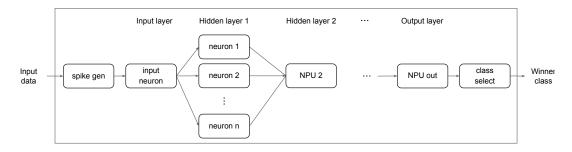

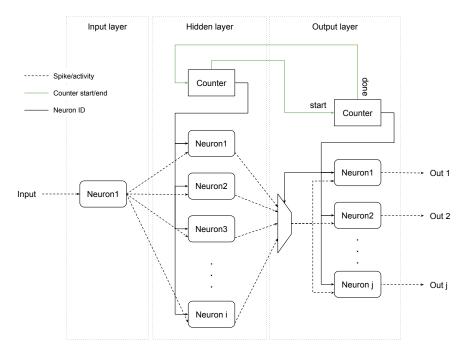

These feed-forward networks are composed of neurons that are connected between each other through synapses that conduct neural activities. Based on these neurons, networks can be formed by organizing them in layers connected to each other (Bebis and Georgiopoulos, 1994). An ANN consists of an input layer and an output layer and at least one hidden layer. The input layer consists of input neurons that only transmit the information to the rest of the network by acting as buffers. The output layer contains the neurons that represent the different classes of the data that the network is classifying (Sze et al., 2017). The hidden layers are connected to the input and output layers and may be of different types and sizes (number of neurons). In this work, we have considered the most commonly used layer types, these are: convolutional, pooling and fully-connected layers. Figure 2.1 shows an example of such a CNN composed of 6 layer hidden layers, with, two convolutional, two pooling and two fully-connected layers. This kind of ANN is called "Convolutional Neural Network" or simply "CNN" because it has convolutional layers. In the following, we give a brief description of its different layer types.

FIGURE 2.1: LeNet CNN architecture used with MNIST dataset – generated from the N2D2 framework (Bichler et al., 2017).

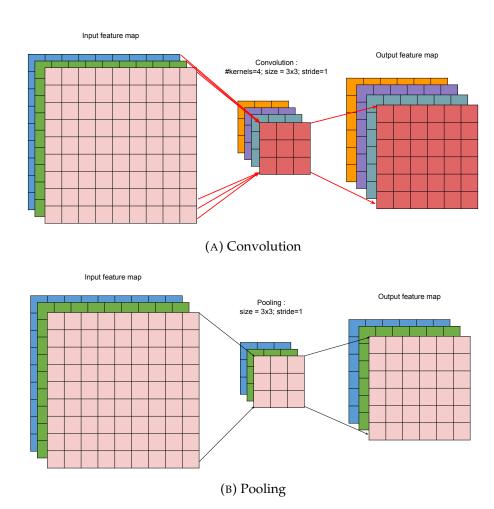

### Convolutional layer

The convolutional layer is composed of kernels or filters that are applied to an input image or Feature Map (FM) to extract specific features. To do so, each kernel has its unique weights that are defined after the learning process and applied at different positions of the input image or FM. The number of these positions correspond to the size of the convolution layer's output feature map that is computed using equations 2.1 and 2.2.

$$FM_{size} = N_{out} * N_{out} (2.1)$$

$$N_{out} = (N_{in} - F + 2 * P)/S + 1 \tag{2.2}$$

Where  $N_{out}$  is the width/height of the output feature map, F is the receptive field width (filter width), P is the padding, S is the stride and  $N_{in}$  is the input FM width/height. In figure 2.1 an illustration showing the network LeNet-5 when used for MNIST classification tasks. Here, there are three convolutional layers, one connected to the input and two others connected to the first and second pooling layers. The first layer is composed of 6 convolution kernels with the size of 5x5 that slide over the input image using a stride equal to 1 (the padding is equal to 0). This convolutional layer output is 6x28x28, i.e. 6 FMs of 28x28 size, this is obtained by applying the formulas in equations 2.1 and 2.2.

### Pooling layer

Pooling layers, also called sub-sampling layers, are used to reduce the size of input FMs. Actually, they are composed of average or maximum pooling kernels that are applied to input FMs using the similar sliding technique used with convolutional layers. Therefore, to compute the output feature map size, we use the same formulas found in equations 2.1 and 2.2. For example, in the third layer from the left in figure 2.1, applying 6 pooling kernels (of 2x2 size and with a stride of 2) on 6x28x28 FMs results in feature maps of 6x14x14 size.

### Fully-Connected layer

Fully-connected layers are generally located at the last stages of a CNN network. They come to process the output FM of the last CNN convolutional or pooling layer, they are considered as the network's classifier. These layers are composed of neurons connected to all previous layer nodes.

### Neural models

Indeed, there are many models of artificial neural networks that can be classified into two families according to the type of neurons and the method of communication between them. First, there are the Analog Neural Networks (ANNs) which are widely used in the field of Machine Learning. They are called Analog because the data flowing and processed by the network is analog data (real valued data). Second, we have Spiking Neural Networks (SNNs) that rise from the field of neuroscience.

# 2.2.1 Analog Neural Networks (ANNs)

The analog models (ANNs) constitute the first neural family that we are dealing with in this work. As mentioned before, they are composed of analog neurons organized in layers and connected in a feed-forward manner. The data flowing in the network between its nodes represent neural activities of the different neurons. These neural activities are output of neurons that have processed input data coming from weighted input synapses. In this thesis, we have used two different ANN models: Multi-Layer Perceptron (MLP) and Convolutional Neural Network (CNN).

### **Multi-Layer Perceptron**

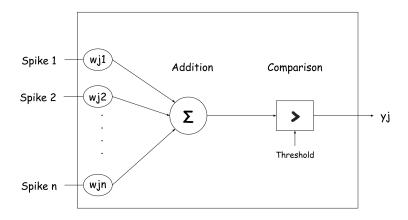

The best-known network model in the machine-learning field is the MLP, which is a feed-forward network that consists of only fully-connected layers. Each layer has a number of neurons called perceptrons that are totally connected to the neurons of the previous layer. The neuron j in layer l performs the computation shown in equations 2.3 and 2.4.

$$y_j^l(t) = f(s_j^l(t))$$

(2.3)

$$s_j^l(t) = \sum_{i=0}^{N_{l-1}-1} w_{ij} \times y_i^{l-1}(t)$$

(2.4)

Where  $y_j^l$  is the output of the neuron j in the layer l,  $N_l$  is the number of neurons in the layer l,  $w_{ij}$  is the synaptic weight between neuron i in layer l-1 and neuron j in layer l, and f() is the non-linear activation function. There are several activation functions that can be used with perceptrons such as Sigmoid (Narayan, 1997), hyperbolic tangent (TanH) (Lecun et al., 1998)

and Rectified Linear Unit (ReLU) (Hahnloser et al., 2000; Agarap, 2018). In this work, we use the ReLU function for two reasons: first, for its computing efficiency allowing the network to converge quickly and its prevention from over-fitting (Krizhevsky, Sutskever, and Hinton, 2017); second, when mapped to spiking domain, it results in a simple comparison with a threshold (Perez-Carrasco et al., 2013).

FIGURE 2.2: A one hidden layer MLP network applied to MNIST dataset.

The learning algorithm used to adapt the synaptic parameters of the MLP is back-propagation, this algorithm is described later in subsection 2.4.2.1. An example of an MLP with one hidden layer of 300 neurons applied to MNIST data-set is shown in figure 2.2.

### **Convolutional Neural Networks (CNNs)**

CNN is the most used deep learning architecture. It is inspired from the biological visual perception mechanism of living beings. Indeed, Hubel and Wiesel have found, in 1959, that animals have cells in their visual cortex that detect the light present in their receptive field (Hubel and Wiesel, 1959). Inspired by this finding, Fukushima proposed in 1980 the neocognitron, which is considered as the CNN's predecessor (Fukushima, 1980). A decade later, LeCun et al. proposed the revolutionary framework of CNN that is presented as an ANN of several layers of different types, called "LeNet-5". This ANN is specifically used to ensure the handwritten digits classification task (LeCun et al., 1990).

More than a decade later, several models have been proposed, they came with improvements and facilitation in training CNNs. Krizhevsky, Sutskever,

and Hinton proposed one of them, AlexNet, it has similar structure to LeNet-5 but with more layers (Krizhevsky, Sutskever, and Hinton, 2017). This model was very successful, it brought out many methods coming from other works that improved classification performances. Among them, we can cite VGGNet (Simonyan and Zisserman, 2014), ZFNet (Zeiler and Fergus, 2014), GoogleNet (Szegedy et al., 2015) and ResNet (He et al., 2015). Recent advances on CNNs can be found in the survey paper proposed by Gu et al. in (Gu et al., 2015).

Meanwhile, CNNs have become more popular with applications in several domains such as image and video recognition, image classification, natural language processing, and medical image analysis. This success can be awarded to two factors. First, computing capabilities of modern CPU/GPU based computers that accelerated learning and inference stages. Second, the huge amount of available open source labeled data for training CNNs, which increased the number of applications and contributed in the improvement of CNN models.

## 2.2.2 Spiking Neural Networks (SNNs)