# Operating system dedicated to NVRAM-based low power embedded systems

Gautier Berthou

#### ▶ To cite this version:

Gautier Berthou. Operating system dedicated to NVRAM-based low power embedded systems. Embedded Systems. Université de Lyon, 2021. English. NNT: 2021LYSEI021. tel-03192646v2

### HAL Id: tel-03192646 https://theses.hal.science/tel-03192646v2

Submitted on 17 Nov 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT: 2021LYSEI021

### THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de L'INSA de Lyon

# **Ecole Doctorale** N° 512 **Informatique et Mathématiques de Lyon**

#### Spécialité/ discipline de doctorat : Informatique

Soutenue publiquement le 29/03/2021, par : Gautier Berthou

# Operating system dedicated to NVRAMbased low power embedded systems

#### Devant le jury composé de :

| Puaut, Isabelle          | Professeur des<br>Universités | Université de<br>Rennes 1           | Président.e                |

|--------------------------|-------------------------------|-------------------------------------|----------------------------|

| Torres, Lionel           | Professeur des<br>Universités | Université de<br>Montpellier        | Rapporteur.e               |

| Lucia, Brandon           | Associate<br>Professor        | Carnegie Mellon<br>University       | Rapporteur.e               |

| Guérin Lassous, Isabelle | Professeur des<br>Universités | Université Claude<br>Bernard Lyon 1 | Examinateur.rice           |

| Sentieys, Olivier        | Professeur des<br>Universités | Université de<br>Rennes 1           | Examinateur.rice           |

| Miro-Panades, Ivan       | Docteur<br>Ingénieur          | CEA LETI                            | Examinateur.rice           |

| Risset, Tanguy           | Professeur des<br>Universités | INSA LYON                           | Directeur.rice de thèse    |

| Marquet, Kevin           | Maître de<br>Conférences      | INSA LYON                           | Co-directeur.rice de thèse |

### Département FEDORA – INSA Lyon - Ecoles Doctorales – Quinquennal 2016-2020

| SIGLE     | ECOLE DOCTORALE                                                                                                                                                                                           | NOM ET COORDONNEES DU RESPONSABLE                                                                                                                                                                                                                                                          |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СНІМІЕ    | CHIMIE DE LYON  http://www.edchimie-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage secretariat@edchimie-lyon.fr INSA: R. GOURDON                                                              | M. Stéphane DANIELE Institut de recherches sur la catalyse et l'environnement de Lyon IRCELYON-UMR 5256 Équipe CDFA 2 Avenue Albert EINSTEIN 69 626 Villeurbanne CEDEX directeur@edchimie-lyon.fr                                                                                          |

| E.E.A.    | ÉLECTRONIQUE,<br>ÉLECTROTECHNIQUE,<br>AUTOMATIQUE<br>http://edeea.ec-lyon.fr<br>Sec.: M.C. HAVGOUDOUKIAN<br>ecole-doctorale.eea@ec-lyon.fr                                                                | M. Gérard SCORLETTI École Centrale de Lyon 36 Avenue Guy DE COLLONGUE 69 134 Écully Tél: 04.72.18.60.97 Fax 04.78.43.37.17 gerard.scorletti@ec-lyon.fr                                                                                                                                     |

| E2M2      | ÉVOLUTION, ÉCOSYSTÈME, MICROBIOLOGIE, MODÉLISATION  http://e2m2.universite-lyon.fr  Sec.: Sylvie ROBERJOT  Bât. Atrium, UCB Lyon 1  Tél: 04.72.44.83.62  INSA: H. CHARLES  secretariat.e2m2@univ-lyon1.fr | M. Philippe NORMAND UMR 5557 Lab. d'Ecologie Microbienne Université Claude Bernard Lyon 1 Bâtiment Mendel 43, boulevard du 11 Novembre 1918 69 622 Villeurbanne CEDEX philippe.normand@univ-lyon1.fr                                                                                       |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-SANTÉ  http://www.ediss-lyon.fr Sec.: Sylvie ROBERJOT Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 INSA: M. LAGARDE secretariat.ediss@univ-lyon1.fr                            | Mme Sylvie RICARD-BLUM Institut de Chimie et Biochimie Moléculaires et Supramoléculaires (ICBMS) - UMR 5246 CNRS - Université Lyon 1 Bâtiment Curien - 3ème étage Nord 43 Boulevard du 11 novembre 1918 69622 Villeurbanne Cedex Tel: +33(0)4 72 44 82 32 sylvie.ricard-blum@univ-lyon1.fr |

| INFOMATHS | INFORMATIQUE ET MATHÉMATIQUES http://edinfomaths.universite-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage Tél: 04.72.43.80.46 infomaths@univ-lyon1.fr                                        | M. Hamamache KHEDDOUCI Bât. Nautibus 43, Boulevard du 11 novembre 1918 69 622 Villeurbanne Cedex France Tel: 04.72.44.83.69 hamamache.kheddouci@univ-lyon1.fr                                                                                                                              |

| Matériaux | MATÉRIAUX DE LYON http://ed34.universite-lyon.fr Sec.: Stéphanie CAUVIN Tél: 04.72.43.71.70 Bât. Direction ed.materiaux@insa-lyon.fr                                                                      | M. Jean-Yves BUFFIÈRE INSA de Lyon MATEIS - Bât. Saint-Exupéry 7 Avenue Jean CAPELLE 69 621 Villeurbanne CEDEX Tél: 04.72.43.71.70 Fax: 04.72.43.85.28 jean-yves.buffiere@insa-lyon.fr                                                                                                     |

| MEGA      | MÉCANIQUE, ÉNERGÉTIQUE, GÉNIE CIVIL, ACOUSTIQUE http://edmega.universite-lyon.fr Sec.: Stéphanie CAUVIN Tél: 04.72.43.71.70 Bât. Direction mega@insa-lyon.fr                                              | M. Jocelyn BONJOUR INSA de Lyon Laboratoire CETHIL Bâtiment Sadi-Carnot 9, rue de la Physique 69 621 Villeurbanne CEDEX jocelyn.bonjour@insa-lyon.fr                                                                                                                                       |

| ScSo      | ScSo* http://ed483.univ-lyon2.fr Sec.: Véronique GUICHARD INSA: J.Y. TOUSSAINT Tél: 04.78.69.72.76 veronique.cervantes@univ-lyon2.fr                                                                      | M. Christian MONTES Université Lyon 2 86 Rue Pasteur 69 365 Lyon CEDEX 07 christian.montes@univ-lyon2.fr                                                                                                                                                                                   |

Cette thèse est accessible à l'adresse, http://theses.insa-lyon/fr/oublication/2021+YSE1021/these pdf

© [G. Berthou], [2021], INSA Lyon, tous droits reservés

# Acknowledgments

Carrying out a PhD thesis is no easy task and there were helping hands in my close environment.

First, I would like to thank my advisors Kevin Marquet and Tanguy Risset for finding interesting conferences and journals to publish our work. They also enabled the fulfilment of my desire to formally prove systems by getting me in touch with Delphine Demange and Pierre-Évariste Dagand, whom I thank as well for their patience and for introducing me to formal methods. My colleagues at CITI lab offered me support and great memories, in particular Guillaume Salagnac, François Lesueur, Tristan Delizy, Guillaume Bono, David Kibloff, Jonathan Tournier, Yohann Uguen and others whom I shared laughs and scientific conversations with. The administrative personnel also did a great work at maintaining my ship afloat against procedures and prevented it from sinking down to the benthic floor. Special thanks to my thesis committee for their reviews and interesting discussions during the presentation and offline.

I would also like to thank friends and family, loving and supportive. In particular, I could have deep discussions with Jason Lecerf, we helped each other out in difficult moments and did live utter friendship regardless of the distance from one another. Gary Cottancin and Yannick Marion were supportive and had wholesome ideas, besides being available and always willing to go to gigs or on vacations together. I shared cheering freetime with expedition-comrades Pierre Godard, Douglas Raillard and Sergueï Lallement. Above all, we have had such nice moments together for almost ten years now, and it certainly helped the ship safely come ashore.

# Contents

| 1 | Intr | oducti        | on                                                         | <b>15</b>       |

|---|------|---------------|------------------------------------------------------------|-----------------|

| 2 | Pro  | blem S        | Statement and Related Works                                | 17              |

|   | 2.1  | Energy        | y Harvesting                                               | 17              |

|   |      | 2.1.1         | Energy Sources                                             | 17              |

|   |      | 2.1.2         | Power Outages                                              | 18              |

|   |      | 2.1.3         | Power Managers                                             | 18              |

|   | 2.2  | Tradit        | ional Platforms with Intermittent Power                    | 20              |

|   | 2.3  |               | dded Programming                                           | 20              |

|   |      | 2.3.1         | Programming Basics                                         | 20              |

|   |      | 2.3.2         | Intermittent Programming Paradigms                         | 21              |

|   | 2.4  | Embed         | dded Operating Systems                                     | 22              |

|   |      | 2.4.1         | Common Operating Systems                                   | 22              |

|   |      | 2.4.2         | Legacy Operating Systems for Constrained Platforms         | 23              |

|   |      | 2.4.3         | Operating Systems for Energy-Harvesting Systems            | $\frac{1}{24}$  |

|   | 2.5  | _             | olatile Memory                                             | $^{-24}$        |

|   |      | 2.5.1         | Traditional Non-Volatile Memory                            | 25              |

|   |      | 2.5.2         | Non-Volatile RAM                                           | 25              |

|   | 2.6  |               | nittent Computing Problematics                             | 27              |

|   | 2.0  | 2.6.1         | Checkpoint Definition                                      | 27              |

|   |      | 2.6.2         | P1 — Memory and CPU State Volatility                       | 28              |

|   |      | 2.6.3         | P2 — Handling Peripherals                                  | 28              |

|   |      | 2.6.4         | P3 — Timeliness and Atomicity                              | 31              |

|   |      | 2.6.5         | P4 — Using Non-volatile Memory as Main Memory              | 32              |

|   | 2.7  |               | vare Architecture for Intermittent Computing               | $\frac{32}{35}$ |

|   | 2.1  | 2.7.1         | Some Choices are not Deliberate                            | 35              |

|   |      | 2.7.1 $2.7.2$ | A1/A3 — Volatile Processor, SRAM and NVRAM                 | 36              |

|   |      | 2.7.2 $2.7.3$ | A2/A4 — Volatile Processor and NVRAM                       | 36              |

|   |      | 2.7.3 $2.7.4$ | A5 — Non-volatile Processor and NVRAM                      | 36              |

|   |      | 2.1.4         | A5 — Non-volathe i rocessor and ivviçam                    | 30              |

| 3 | Ope  | erating       | Systems for Transiently-Powered Systems                    | 39              |

|   | 3.1  | Applic        | eation Scenarios                                           | 39              |

|   |      | 3.1.1         | The Dilemma of Benchmarks for Transiently-Powered Systems  | 39              |

|   |      | 3.1.2         | Sense, Process and Possibly Send                           | 40              |

|   |      | 3.1.3         | Benchmarks and Testbenches for Transiently-Powered Systems | 41              |

|   | 3.2  | Softwa        | are Architecture                                           | 41              |

|   |      | 3.2.1         | Baseline: Bare-metal Applications                          | 41              |

|   |      | 3.2.2         | Qualitative Metrics of Programming Effort                  | 42              |

|   |      | 3.2.3         | M — Memory Organization                                    | 42              |

|   |      | 3.2.4         | E — Execution Model                                        | 44              |

|   | 3.3  | Design        | ning Platforms for Intermittent Computing                  | 44              |

|   |      | 3.3.1         | Platforms                                                  | 44              |

|   | 3 4  |               | ons Brought by Existing Approaches                         | 45              |

6 CONTENTS

|   |            | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5 | Solutions to P1                           | 45<br>50<br>52<br>54 |

|---|------------|-------------------------------------------|-------------------------------------------|----------------------|

| 4 | Syt        | are                                       | P.                                        | 57                   |

| - | 4.1        |                                           |                                           | 57<br>57             |

|   | 4.2        | 0                                         |                                           | 58                   |

|   |            | 4.2.1                                     |                                           | 58                   |

|   |            | 4.2.2                                     |                                           | 58                   |

|   | 4.3        | Solutio                                   |                                           | 58                   |

|   |            | 4.3.1                                     | Device Contexts                           | 59                   |

|   |            | 4.3.2                                     | Initialization Function                   | 60                   |

|   |            | 4.3.3                                     | Save Function                             | 60                   |

|   |            | 4.3.4                                     | Restore Function                          | 60                   |

|   |            | 4.3.5                                     | Interrupt Callback                        | 61                   |

|   |            | 4.3.6                                     | Driver Routine Wrappers                   | 61                   |

|   |            | 4.3.7                                     | Nested Driver Routines                    | 62                   |

|   | 4.4        | Solutio                                   | n to P3                                   | 62                   |

|   |            | 4.4.1                                     | Application and Kernel Stacks             | 63                   |

|   |            | 4.4.2                                     | Driver Organization                       | 63                   |

|   |            | 4.4.3                                     | Driver Routines                           | 63                   |

|   |            | 4.4.4                                     | Driver Routine Wrappers                   | 63                   |

|   | 4.5        | Integra                                   | tion                                      | 64                   |

|   | 4.6        | Perfor                                    | mance Evaluation                          | 69                   |

|   |            | 4.6.1                                     | Power Supply                              | 69                   |

|   |            | 4.6.2                                     | Benchmark applications                    | 69                   |

|   |            | 4.6.3                                     | Time Efficiency                           | 69                   |

|   |            | 4.6.4                                     | Kernel                                    | 72                   |

|   | 4.7        | ARMo                                      | rik: Towards new Architectures with NVRAM | 76                   |

|   |            | 4.7.1                                     | Hardware Design                           | 76                   |

|   |            | 4.7.2                                     | Software                                  | 78                   |

|   |            | 4.7.3                                     | ARM-related mechanisms                    | 78                   |

|   | 4.8        | Conclu                                    | sion                                      | 80                   |

| _ | -          | 3.6                                       | 11.67                                     |                      |

| 5 |            |                                           | v                                         | 33<br>34             |

|   | 5.1        |                                           | 30                                        | 34                   |

|   |            | 5.1.1                                     |                                           | 84                   |

|   |            | 5.1.2                                     |                                           | 34                   |

|   | <b>F</b> 0 | 5.1.3                                     |                                           | 85<br>00             |

|   | 5.2        | 0.                                        | V                                         | 86<br>26             |

|   |            | 5.2.1                                     | 1 0                                       | 86                   |

|   | <b>r</b> o | 5.2.2                                     | 11                                        | 87                   |

|   | 5.3        |                                           |                                           | 87<br>27             |

|   | 5.4        |                                           | v                                         | 87<br>20             |

|   |            | 5.4.1                                     | •                                         | 88                   |

|   |            | 5.4.2                                     |                                           | 39                   |

|   |            | 5.4.3                                     | 11 0                                      | 90                   |

|   | 5.5        |                                           | •                                         | 90                   |

|   | 5.6        |                                           |                                           | 92                   |

|   |            | 5.6.1                                     | $\Theta$                                  | 92                   |

|   |            | 5.6.2                                     |                                           | 93                   |

|   |            | 5.6.3                                     |                                           | 93                   |

|   |            | 5.6.4                                     | Integration in Simulation                 | 94                   |

CONTENTS 7

|              | 5.7   | 5.6.5 Benchmark Applications                                    | 95<br>95 |

|--------------|-------|-----------------------------------------------------------------|----------|

|              | 5.8   | Conclusion                                                      |          |

| 6            | MP    | U-Based Incremental Checkpointing                               | 97       |

|              | 6.1   | Towards Incremental Checkpointing                               | 98       |

|              |       | 6.1.1 Software-based Approaches                                 | 98       |

|              |       | 6.1.2 Hardware-based Approaches                                 |          |

|              | 6.2   | Incremental Checkpointing Design using an MPU                   | 100      |

|              |       | 6.2.1 Memory Protection Units                                   |          |

|              |       | 6.2.2 Leveraging an MPU for Incremental Checkpointing           | 100      |

|              | 6.3   | Analysis of the Energetic Benefits of Incremental Checkpointing |          |

|              |       | 6.3.1 Modeling MPU-based Incremental Checkpoint                 |          |

|              |       | 6.3.2 Comparison with Other Approaches                          |          |

|              | 6.4   | Validation through Simulation                                   |          |

|              | 0.1   | 6.4.1 Simulation Platform                                       |          |

|              |       | 6.4.2 Benchmark Applications                                    |          |

|              |       | 6.4.3 Checkpointing Layer                                       |          |

|              |       | - •                                                             |          |

|              | o =   | 6.4.4 Validation of Analytical Results                          |          |

|              | 6.5   | Validation on a Real Platform                                   |          |

|              | 6.6   | Conclusion                                                      | 112      |

| 7            | Fori  | mal Proof of Checkpointing-Based Intermittent Systems           | 115      |

|              | 7.1   | Proving Systems                                                 |          |

|              | 7.2   | Challenges of Intermittence                                     |          |

|              | 7.3   | Model and Definitions                                           |          |

|              | •••   | 7.3.1 Entity Definitions                                        |          |

|              |       | 7.3.2 Specification Under Continuous Power                      |          |

|              |       | 7.3.3 Execution Trace Under Intermittent Power                  |          |

|              |       | 7.3.4 Differences With the Original Model                       |          |

|              | 7 4   |                                                                 |          |

|              | 7.4   |                                                                 |          |

|              | 7.5   | Applications of the Model to Actual Systems                     |          |

|              | 7.6   | Conclusion                                                      | 122      |

| 8            | Con   | nglusion                                                        | 123      |

| 0            |       | nclusion                                                        |          |

|              | 8.1   | A Quick Glance at the Contributions                             |          |

|              | 8.2   | Perspectives                                                    |          |

|              |       | 8.2.1 Operating System                                          |          |

|              |       | 8.2.2 Worst-Case Energy Consumption                             |          |

|              |       | 8.2.3 Simulation                                                |          |

|              |       | 8.2.4 Formal Proof                                              | 126      |

|              |       | 8.2.5 Communication Protocol                                    | 127      |

|              | 8.3   | Transiently-Powered Systems of Tomorrow                         | 127      |

| Bi           | blioe | graphy                                                          | 129      |

|              |       |                                                                 |          |

| A            | Glo   | ssary                                                           | 139      |

| В            | List  | of Publications                                                 | 141      |

| $\mathbf{C}$ | Abs   | stract                                                          | 143      |

| D            | Rés   | gumé de la thèse                                                | 145      |

8 CONTENTS

# List of Figures

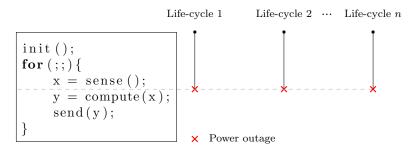

| 2.1   | Program counter volatility                                                                                                    | 28  |

|-------|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2   | CPU registers and memory volatility                                                                                           | 28  |

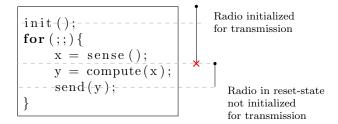

| 2.3   | Peripheral state volatility                                                                                                   | 29  |

| 2.4   | Comparison between (a) interrupt-less model and (b) interrupt support                                                         | 30  |

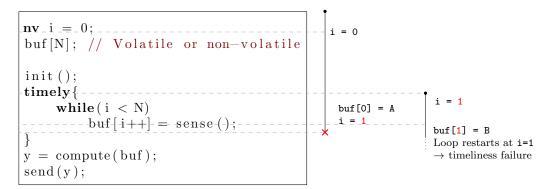

| 2.5   | Timeliness constraint.                                                                                                        | 31  |

| 2.6   | Non-idempotent access to non-volatile memory.                                                                                 | 33  |

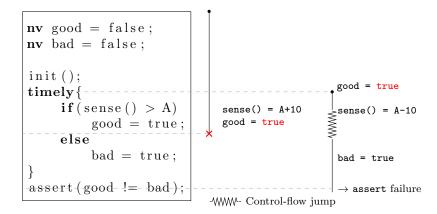

| 2.7   | Non-idempotent access to non-volatile memory due to the influence of peripherals on the                                       |     |

|       | control-flow                                                                                                                  | 34  |

| 2.8   | Non-idempotent access to non-volatile stack.                                                                                  | 34  |

| 2.9   | Non-idempotent access to non-volatile heap                                                                                    | 35  |

| 3.1   | Example of bare-metal application                                                                                             | 43  |

| 3.2   | Typical run-time of just-in-time checkpointing systems                                                                        | 51  |

| 4.1   | Overview of the hardware and software architectures Sytare is designed for                                                    | 57  |

| 4.2   | Examples of low-level and high-level drivers for the clock system of Texas Instruments'                                       |     |

|       | MSP430FR5739 micro-controller                                                                                                 | 59  |

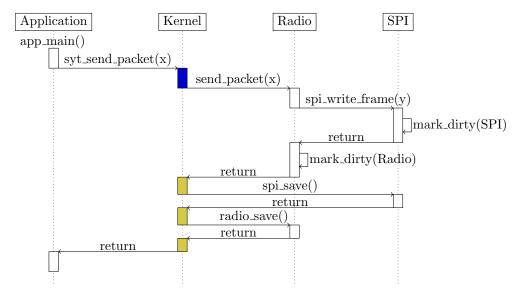

| 4.3   | Sequence diagram of a nested driver call, showing the interactions between Sytare, the                                        |     |

|       | drivers and the application                                                                                                   | 62  |

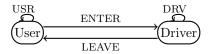

| 4.4   | Data structures and global variables of Sytare                                                                                | 64  |

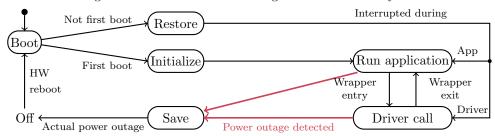

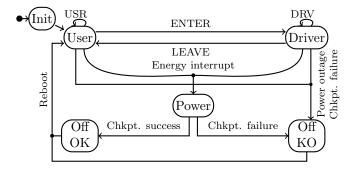

| 4.5   | Run-time state machine of Sytare, with interrupts left aside                                                                  | 64  |

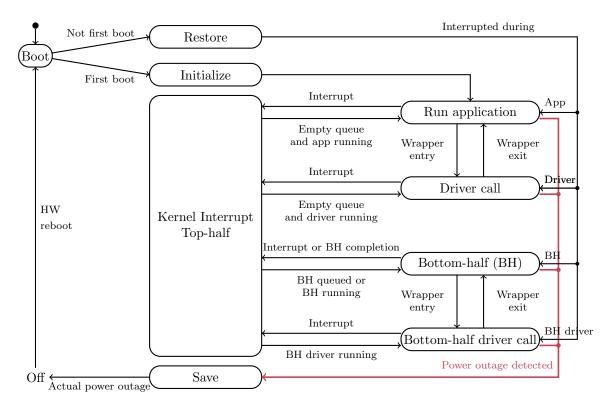

| 4.6   | Complete run-time state machine of Sytare                                                                                     | 67  |

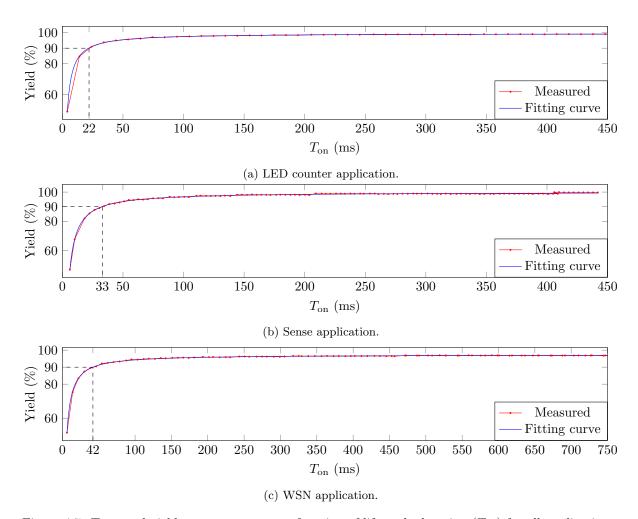

| 4.7   | Temporal yield measurements as a function of life-cycle duration $(T_{\rm on})$ for all applications.                         | 71  |

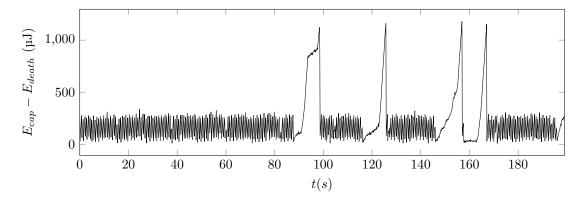

| 4.8   | Excerpt of the available energy in the storage capacitor, as the platform harvests solar                                      |     |

|       | energy                                                                                                                        | 75  |

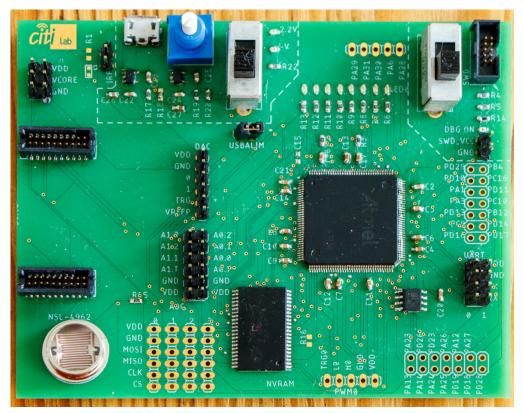

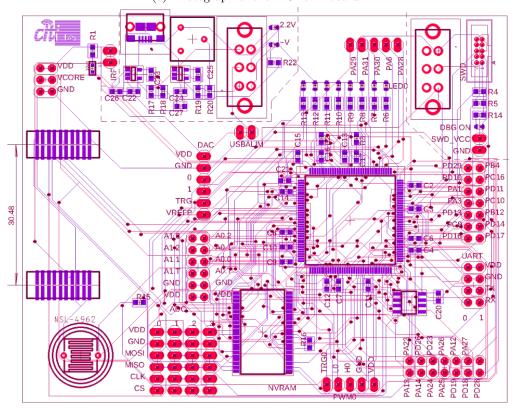

| 4.9   | Photograph and board design of ARMorik                                                                                        | 79  |

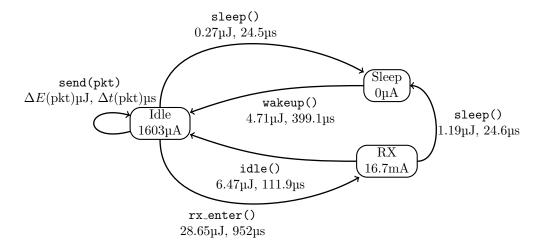

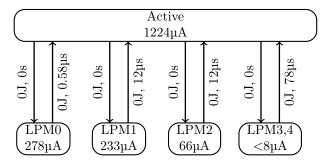

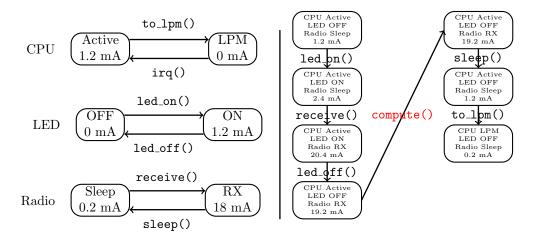

| 5.1   | Driver state machine of the driver for CC2500EMK radio daughter board                                                         | 88  |

| 5.2   | Power state machine of the MSP430FR5739 micro-controller                                                                      | 89  |

| 5.3   | Example showing how the platform's power state evolves with driver calls                                                      | 90  |

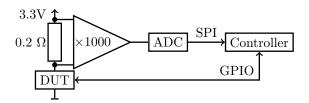

| 5.4   | Measurement circuit schematics                                                                                                | 91  |

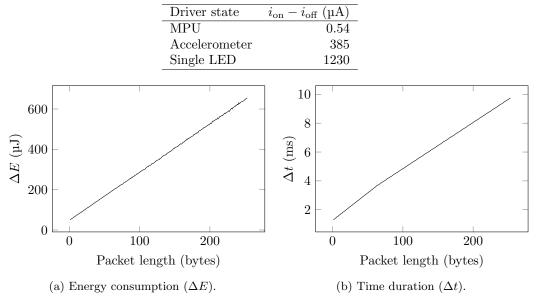

| 5.5   | Measured (a) energy consumption and (b) duration of radio emission for different packet                                       |     |

|       | lengths                                                                                                                       | 93  |

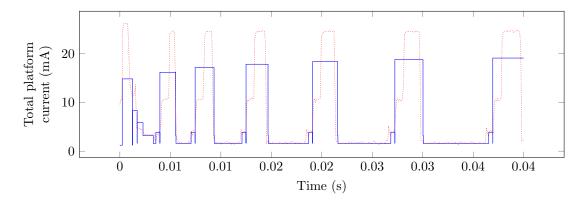

| 5.6   | Excerpt of simulation record of the first seven data batches of the Complete-WSN application.                                 |     |

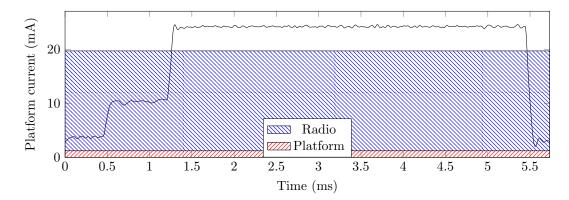

| 5.7   | Instantaneous current consumption for a transmission of a 128-byte long radio packet and                                      |     |

| • • • | its integral average                                                                                                          | 95  |

| 6.1   | Toy code that illustrates memory accesses to different MPU regions                                                            | 101 |

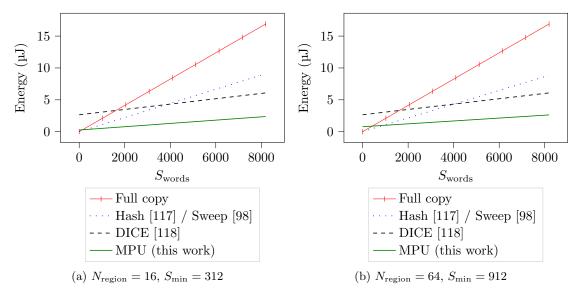

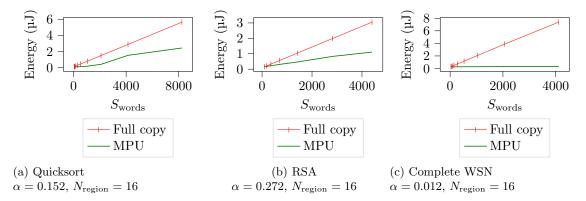

| 6.2   | Energy consumption of the checkpointing mechanisms with respect to size of RAM for                                            |     |

|       |                                                                                                                               | 107 |

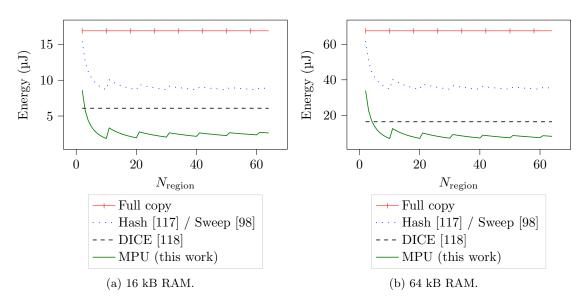

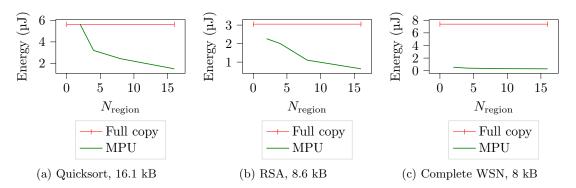

| 6.3   | Energy consumption of the checkpointing mechanisms with respect to the amount of MPU                                          |     |

|       | regions for different RAM sizes                                                                                               | 109 |

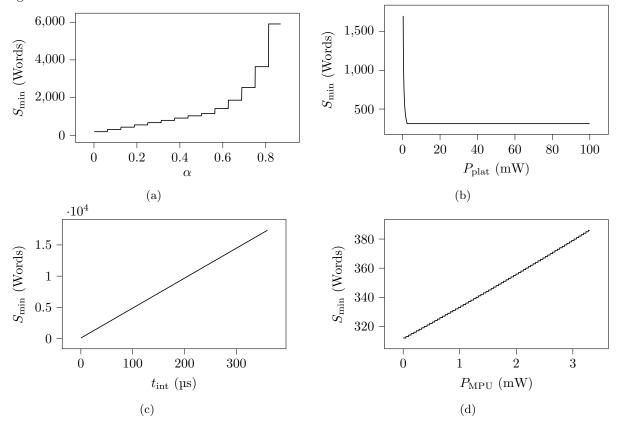

| 6.4   | Impact of $\alpha$ , $P_{\text{plat}}$ , $t_{\text{int}}$ and $P_{\text{MPU}}$ on the minimal amount of RAM words to make the |     |

|       |                                                                                                                               | 109 |

10 LIST OF FIGURES

| 6.5 | Checkpointing energy consumption with respect to size of RAM for different applications,   |     |

|-----|--------------------------------------------------------------------------------------------|-----|

|     | when the energy budget is 120 $\mu J.$                                                     | 111 |

| 6.6 | Checkpointing energy consumption with respect to the amount of MPU regions for different   |     |

|     | applications, when the energy budget is 120 $\mu J.$                                       | 112 |

| 7.1 | State machine of the system under continuous power                                         | 118 |

| 7.2 | State machine of the system under intermittent power                                       | 120 |

| 7.3 | Example of application code with timeliness constraints, alongside its specification and a |     |

|     | possible execution trace, showing that they match.                                         | 121 |

# List of Algorithms

| 4.1 | Imminent power outage interrupt handler                                                 | 65 |

|-----|-----------------------------------------------------------------------------------------|----|

| 4.2 | Restoration function.                                                                   | 66 |

| 4.3 | Wrapper entry, wrapper exit and a typical example of a wrapped driver routine           | 67 |

| 4.4 | A typical interrupt handler, distinct from the imminent power outage interrupt, and its |    |

|     | interactions with Sytare's scheduler                                                    | 68 |

LIST OF ALGORITHMS

# List of Tables

| 3.1        | Comparison between existing systems for transiently-powered systems, with respect to their ability to solve the identified problems                           | 45  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1        | wheely on it wheel                                                                                                                                            |     |

|            | $T_{\text{wired}}$ over a hundred samples                                                                                                                     | 71  |

| 4.2        | Booting sequence of WSN application                                                                                                                           | 73  |

| 4.3        | Temporal impact of driver routine wrappers                                                                                                                    | 73  |

| 4.4        | NVRAM requirements, in bytes, of some applications                                                                                                            | 74  |

| 4.5        | Kernel stack utilization, in bytes, for button and radio applications, under several runtime                                                                  |     |

|            | scenarios                                                                                                                                                     | 74  |

| 5.1        | Measurements of driver calls energy consumption and duration for the radio, temperature sensor and accelerometer as implemented in Sytare                     | 92  |

| 5.2        | Difference in measured current levels between on and off states of the Memory Protection                                                                      |     |

| 5.3        | Unit (MPU), accelerometer and LED                                                                                                                             | 93  |

| - 1        | applications on the MSP-EXP430FR5739 platform                                                                                                                 | 96  |

| 5.4        | Comparison, for energy consumption, between measurements and simulation of the benchmark applications on the MSP-EXP430FR5739 platform.                       | 96  |

| 6.1<br>6.2 | Characteristics of the MPUs from MSP430 and ARM Cortex-M architectures Model parameters and their default values, used in the models of the full copy and the | 100 |

|            | MPU-based incremental approaches                                                                                                                              | 103 |

14 LIST OF TABLES

## Chapter 1

### Introduction

Embedded systems are increasingly used and their application range swiftly grows. Many objects become equipped with computation and communication abilities, thus widening further the family of embedded devices. Cloth tags, crop plant sensors, wearables, medical implants and sensors for hard-to-reach areas are examples of such items. More generally, this thesis focuses on constrained devices. The greatest constraints are form factor, *i.e.*, the volume occupied by the object itself, and physical access to the device once deployed. Within the scope of the present thesis, the considered objects are small and subject to limited maintenance. Indeed, an individual would not want a massive medical implant, for the benefits brought by the implant might be diminished by the discomfort it would generate. In addition, when deploying sensors in closed environments or hostile to the human body, such as inside walls or in radiation-covered areas, physical access to the devices is problematic and thus, must be avoided. Embedding batteries is limited to some extent, for batteries take space and require the intervention of a human operator from time to time, thus reducing the autonomy of the object itself. That statement also stands for rechargeable batteries. One gets the insight that alternative power supplies must be investigated to supplant the usage of batteries.

Full autonomy is achieved when the device is capable of harvesting energy from its environment. There are many sources of energy, and as many kinds of energy harvesters: light, electromagnetic waves, temperature, mechanic movement, motion of the living, air flow, etc. Harvesters yield a variable power, depending on the nature of the phenomenon to harvest, on environmental conditions and on the harvester itself. A small solar panel typically delivers less power than a wider one, however some applications might need a small form factor and hence have to cope with small harvesters.

Apart from solar energy, that usually provides long time windows of stable power, other sources do not allow that comfort. Eventually, power fails and the platform shuts down until the environmental conditions are favorable again. With weak energy sources, such as harvesting radio waves from a distant low-power device, the off-times may last hours or even days. When the energy availability of a platform is constrained to that extent, it becomes crucial to stop fighting against power outages but, on the contrary, to compose with them and to integrate off-times as inherent parts of the life of the platform, for power outages are unavoidable at that point.

Widespread state-of-the-art approaches use Wireless Power Transfer, that consists in purposing an external device to beam energy into the platform, as seen for credit cards where the card reader beams energy to whatever card reaches inside its range. Wireless Power Transfer, however, creates an unnatural environment, for the energy source is made on purpose for that deed, while that energy field would not be observed in nature otherwise.

This thesis hence sides with alternative solutions, that actually harvest energy from a natural environment. Unlike Wireless Power Transfer, a natural environment probably cannot deliver as much energy and thus, on-times are expected to run shorter and to be less stable as the power demands of the platform evolve alongside application progress. Hence, applications designed for natural energy harvesting can no longer afford to restart from the very beginning every time the platform reboots. As a result, considering the energy constraints that complement the size and access constraints, compliant platforms can only embed low-power components. Computation capabilities cannot exceed that of low-power micro-controllers and accelerators, hence limiting possible applications to sensor-related and monitoring features, alongside

basic processing.

Forward progress grows into a key concept of platforms that harvest energy from a natural environment, whereas it is always discarded within the credit card model. There needs to be a way of storing and loading forward progress so that the application can go on after every power outage. This is correlated to the concept of checkpointing. It creates a need for embedding non-volatile memories, that are memories which do not lose their contents whilst not powered. Non-volatile memories are usually purposed to store the application instructions and the initial values of data sections, often in read-only memories. On the other hand, the last decades witnessed the emergence of non-volatile Random Access Memories, that are designed to be used as regular, volatile Random Access Memories. These non-volatile memories are byte-addressable and, more importantly, have similar read and write access times than their volatile counterparts. Although they are still behind volatile Random Access Memories in terms of performance and do not yet have an infinite endurance, they are the most promising hope that energy-harvesting devices have to establish a persistent data storage.

Considering power outages is not straightforward in common programming languages. It raises a core question: how to handle every outcome induced by power outages into a programming paradigm? That question could be addressed in sundry ways, notably language-wise. This thesis proposes to sand off the sharp edge by providing a lightweight operating system support for traditional embedded software programming under intermittent power conditions. Hence, the resulting programming paradigm feels really close to what was done in battery-equipped embedded systems, without the discomfort of manually managing power outage constraints and without throwing away decades of programming experience.

Providing operating system support to spread application execution across power outages comes along with its share of challenges and trade-offs. Indeed, operating systems provide useful services for applications, but the price of that model in comparison to *ad-hoc* bare-metal baselines is an overhead due to function calls and to the genericity of the proposed services. It is legitimate to wonder whether such overheads are acceptable given the energy scarcity. This works shows that a lightweight operating system layer is actually worth using, for a rigorous automated resource and power outage management is beneficial in terms of development effort, run-time execution and confidence in application robustness.

Confidence in the behavior of such applications is a major concern when it comes to transiently-powered systems. Beyond testing systems against a finite benchmark suite, it seems important to take a step back and retrospectively analyze the concepts developed by such operating systems. The world of transiently-powered systems clearly lacks proof material to underpin the assumptions that those persistence mechanisms work and maintain an overall consistency to spread an application across power outages.

The present thesis identifies problematics related to intermittent power and proposes mechanisms for operating systems to solve those issues. An implementation of the investigated mechanisms within a lightweight operating system is Sytare. This work further investigates optimizations of such systems, brings a proof of correctness under intermittent power and builds an accurate energy consumption estimation tool.

Chapter 2 states the general problem and explores related works. Chapter 3 extensively studies existing operating systems for transiently-powered systems and positions them with respect to the problems depicted in Chapter 2. Chapter 4 describes in detail Sytare, an operating system for transiently-powered systems developed and improved during the course of the present thesis. Chapter 5 exposes a novel peripheral-aware energy model for embedded systems that encompasses changes in platform power state, a simple power measurement platform to populate the model and an accurate simulator for such platforms. The simulator both reproduces the behavior of the platform in software and hardware and yields time- and energy-related metrics using the model. Chapter 6 proposes an incremental checkpointing scheme using a common micro-controller peripheral as an optimization of former checkpointing schemes. Chapter 7 lays the groundwork for the first formal proof of correctness of checkpointing schemes for intermittent systems. Finally, Chapter 8 concludes this work and discloses some of its perspectives.

## Chapter 2

# Problem Statement and Related Works

Systems supplied with intermittent power must face new challenges with respect to continuously-supplied systems. Power outages are a kind of failure that makes almost every part of the platform fail, but not necessarily at the same time. They add complexity to run-time conditions and thus, the correct execution of long-running applications is not trivial to establish. The present thesis addresses the global problematic of being able to execute long-running applications despite power outages.

This chapter first discusses energy harvesting, energy sources, power managers and the outcomes of solely using harvested energy without an additional energy provider. Then, usual platforms that run under intermittent power are presented. A brief introduction to embedded programming and to embedded operating systems follows. Non-volatile memories are described after. This chapter then exposes recurrent problems that arise with intermittent power, either from intermittent properties themselves, or from application specifications. Those problems lay a baseline in the domain of transiently-powered systems and are referred to throughout this thesis. Finally, a categorization of existing hardware architectures equipped with non-volatile RAM is given.

### 2.1 Energy Harvesting

Harvesting energy consists in transforming an ambient physical phenomenon into energy intended to be used by some device. The conversion from the physical phenomenon into an electric pulse is the role of the transducer. Transducers are devices that transform one kind of energy into another. An interesting property of transducers is that they often work conversely with almost no modification. For instance, a speaker can be used as a microphone, a Light-Emitting Diode (LED) as a light sensor or harvester, etc. In general, apart from large solar panels, the raw output of the transducer cannot directly supply a device. Rectifier circuits are often required. Indeed, depending on the phenomenon and on the transducer, the raw output voltage may be high but cannot stand a current load, or both voltage and currents are low. The usage of a rectifier enables to convert the raw output voltage of the transducer into another voltage, more stable and suited to the device. The nature of the harvested energy, the performance of the transducer and the efficiency of the rectifier are parameters to study when designing a platform supplied by energy harvesting. Hence, figures exposed hereafter are for indicative use only, enabling to reason about orders of magnitude. In addition, many experiments have been conducted, at different time periods, using different technologies and devices, under different experimental conditions. Some works report the power density surface-wise, others volume-wise and the last simply report power. It is nonetheless not necessary to get an exact value as the orders of magnitude speak for themselves.

#### 2.1.1 Energy Sources

There are many natural sources of energy and as many types of transducers to produce electric energy out of them.

Light Light is certainly the most popular natural source of energy. It may be harvested using photodiodes or photovoltaic cells and generate electrical power between 15 mW.cm<sup>-2</sup> and 100 mW.cm<sup>-2</sup> [1, 2, 3]. The light source may be natural as sunlight, or synthetic as indoor light or LEDs from another device. Visible Light Communication systems [4] could benefit from light harvesting using the same device for communicating and harvesting, *i.e.*, an LED. It was further shown that a red LED could deliver 133 μW under outdoor sunlight [5], however ambient light reduces light communication efficiency.

Radio and electromagnetic waves An important energy source is radio and other, non-visible electromagnetic waves. Energy is harvested using inductors and antennas. GSM can provide 0.1 mW.cm<sup>-2</sup> of electrical power, Wi-Fi delivers between 10 nW.cm<sup>-2</sup> and 10  $\mu$ W.cm<sup>-2</sup> [1, 2] and a vibrating magnet 40 pW.cm<sup>-2</sup> [6]. The sensitivity of the harvester, that is the minimal radio power required for the harvester to operate, is the most critical and the most constraining property. A plethora of works proposes different designs for radio energy harvesting. Most of them can deliver 1 V DC output when the incoming radio power is at least -22 dBm (6  $\mu$ W) to -14 dBm (40  $\mu$ W) [7]. As of light, it would be interesting to build platforms that use the same antenna for both energy harvesting and communication [8].

**Temperature** Spatial and temporal variations of temperature may also be used to generate energy. A 5 K difference in temperature generates up to 60 μW.cm<sup>-2</sup> [9, 1]. The applications are numerous and notably wearables can take advantage of temperature gradients of the living.

Mechanic movement While some mechanical energy can be managed using magnetic waves, such as a vibrating magnet or coil, another technology may be used to convert mechanical energy into electrical energy. Piezoelectric properties achieve such a deed and may provide power, when struck or twisted, in the order of magnitude of  $200 \,\mu\text{W.cm}^{-2}$  to  $500 \,\mu\text{W.cm}^{-2}$  [9]. People move and body movement can thus provide energy. For instance, a heel strike, a finger motion and even blood pressure.

**Air flow** The flow of gas, like any fluid, can generate energy using, for instance, an anemometer or a turbine. Wind turbines may produce 28.5 mW.cm<sup>-2</sup> [1]. Human breath can generate up to 0.4 W [3] with a face mask as energy harvester.

#### 2.1.2 Power Outages

Some energy sources are quite stable, for instance, when using large solar panels. This thesis addresses small objects with, among others, form factor constraints and thus, cannot embed large energy harvesters. As a consequence, regardless of the harvested energy source, the harvested power is expected to be low. More importantly, the harvested power is expected to be lower than the power consumption of the supplied platform in active mode. Active mode depicts an operating mode of the platform when it performs some operation, e.g., the micro-controller is computing or a piece of data is being sent over radio. Sleeping modes may consume less instantaneous power than harvested, but performing any useful operation would result in energy depletion as energy is consumed faster than harvested. Inevitably, that situation incurs power outages. Given that there is no degree of freedom regarding form factor, considering medical implants for example, the platform must then face and cope with power outages as an inherent part of its life. Furthermore, battery-less platforms are designed to overcome the limitations of replacing batteries over time, hence they are destined to be deployed once and never, or seldom, physically accessed again. Battery-less platforms are de facto on their own regarding energy supply and must thus accept power outages.

#### 2.1.3 Power Managers

Aside from the transducer itself, an energy harvester embeds some circuitry, including voltage rectifiers and power managers. The harvested energy may be used as is or be aggregated into a small storage such as a small-sized capacitor. A power manager may take responsibility for handling the energy storage: it dictates when to supply or not the platform. It also provides a befitted power supply to the platform.

#### **Energy Management Policy**

There are two major policies of powering the platform: harvest-use and harvest-store-use [10, 3, 11, 12, 13, 14. Under the harvest-use policy, the platform is directly wired onto the harvester. It is simple and may lead to the smallest form factor designs. However, the harvester must provide a high voltage, i.e., voltage above the operating threshold of the platform plus the voltage drop due to the current consumption of the platform. When the output of the harvester drops below that threshold, the platform is abruptly turned off. The other policy, harvest-store-use, introduces an energy storage, such as small capacitors or super-capacitors. The energy storage acts like a low-pass filter, it enables the platform to be powered more steadily than under the harvest-use policy. Using a harvest-store-use approach allows the usage of smaller harvesters and of lower harvested power levels. The downside of harvest-store-use is that the energy storage must charge up to a certain energy level to power the platform and, depending on the capacity of the energy storage, the charging phase may take time. The storage element is important for, in practice, it is not ideal and presents current leakage. Its capacity must be carefully chosen for the rate at which it charges and discharges is directly incurred to capacity. A trade-off between reactivity and the ability of being powered on during long times must be established [15]. UFoP [16] derives this methodology and proposes to decouple capacitance by using several smaller capacitors: one for the micro-controller and one for every single peripheral.

A hybrid between harvest-use and harvest-store-use has been designed to reconcile both approaches. Confusedly named either harvest-use(store) [17, 18], harvest-store(use) [19] or harvest-store-use [20], it tries to use the harvested energy in a harvest-use manner as much as possible and stores the potential exceeding harvested energy into an energy storage. Once the harvester can no longer provide sufficient power to the platform, the energy storage takes over so that powered periods are lengthened.

The three power management policies can be implemented in numerous ways. The bulk of existing works candidly wire the transient power source directly onto the platform to supply, regardless of the chosen policy [21, 22]. The platforms thus have to cope with a supply voltage that evolves over time. Fluctuating supply voltage impacts clock frequencies and current consumption [23]. Hence, while directly wiring a transient power source onto the platform still enables the execution of applications, there are some pitfalls to avoid. First, all electronic components on the same platform do not necessarily have the same voltage requirements and the scenario where the power supply is able to supply a given component but fails to supply another may happen. For instance, low-power micro-controllers usually operate at 1.8 V or even less, whereas radio chipsets might require at least 2 V. In that case, if the voltage of the power supply, in either of the harvest-use, harvest-store-use or harvest-use(store) modes, stays between 1.8 V and 2 V for some reason, the software application might think that the platform is working well since the micro-controller is able to execute instructions, however any attempt to use the radio chipset would inevitably fail. Another pitfall is that varying supply voltage complexifies the task of estimating the energy consumption of a system, should it be software or hardware.

In order to tackle the two downsides of directly wiring the power source onto the platform to supply, some works propose to add a voltage regulating stage between the energy storage and the platform in a harvest-store-use scenario [24, 25, 26]. This approach is also adopted by industrials [27], even for very constrained energy sources such as ambient radio waves. <sup>1</sup> Using a voltage regulator adds little complexity to the circuit, but introduces an additional component which efficiency is, in practice, not ideal. Some energy is wasted due to the fact that voltage regulator are not ideal, yet it is viable to design harvesting systems with a voltage regulator. A Game Boy that harvests solar energy and button press energy was designed thus [28].

#### Improving Harvesting Efficiency

Regardless of the kind of energy source, power managers also work close to the transducer in order to find an optimal configuration that would maximize the harvested energy. They often embed a Maximum Power Point Tracking (MPPT) circuit that is designed for that purpose. Harvesters are studied against I-V curves, *i.e.*, the relationship between voltage and the current that can be drawn from the transducer. These curves have peaks and MPPT circuits work towards the objective of getting closer to the peaks. MPPT consists in dynamically adapting the impedance seen by the transducer [29, 30]. To do so,

$<sup>^{1} \</sup>verb|https://e-peas.com/types/energy-harvesting/rf/|$

DC-DC converters can be used for their duty-cycle is controllable and directly affect the impedance. In order to compute the optimal impedance and duty-cycle, the MPPT circuit must first locate the instantaneous performance of the circuit on the I-V curve of the transducer. Traditional techniques of MPPT involve periodically disconnecting the transducer to automatically measure its open-circuit voltage. The fractional open-circuit voltage technique simply models the optimal voltage to be linear with the open-circuit voltage. The coefficient of that linear relationship is dependent on the transducer. For instance, a photovoltaic cell may optimally work at 75 % of its open-circuit voltage. Finally, measuring the open-circuit voltage must not be performed very often nor for very long, since the transducer is disconnected from the rest of the circuit and thus cannot deliver its energy to the platform or to the energy storage, if any.

#### 2.2 Traditional Platforms with Intermittent Power

Today's most widespread devices that harvest energy are devices such as Radio-Frequency IDentification (RFID) and Near-Field Communication (NFC) tags [31]. Throughout this chapter, such tags are informally referred to as credit cards. Credit cards embed a micro-controller programmed with an application. The application has to run to completion without power outage. Upon reboot, the application restarts from the beginning to initiate a new transaction. In order for that model to be viable, a card reader steadily provides a sufficient amount of energy to perform the transactions, without interruption during the entire process. Hence, the credit card model is a two-fold approach that requires (i) the credit card itself to communicate information and perform some operations and (ii) an external device that beams energy onto the credit card. The presence of the external device, here the card reader, is a very strong assumption for the credit card does not harvest energy from a natural environment, but rather from an environment made on purpose for the credit card. This is called Wireless Power Transfer. Credit cards may thus be energy neutral as defined in Section 2.3.2, however the card reader is not.

Harvesting radio energy often generates small power for the device may be far away form the source or health norms would not enable higher transmission power. PoWiFi [32] observes that Wi-Fi router have irregular traffic over time and repurposes Wi-Fi networks for power delivery. Wi-Fi routers are modified to inject superfluous broadcast traffic, called power packets, on available and non-overlapping Wi-Fi channels. An advantage of using Wi-Fi as the energy source is that the antenna may be used for both communication and energy harvesting. PoWiFi requires a modification of Wi-Fi traffic and thus is not entirely natural.

Ambient backscatter enables an efficient energy harvesting of radio power that does not require the injection of any additional energy source [33]. It comes from the observation that radio waves, especially television (TV) broadcast waves, are present in most locations. TV waves, in particular, have a large coverage since TV towers are designed for that purpose. The devices may thus harvest TV energy, without backup battery, and the communication between devices may be achieved by backscattering the TV signal. Changing the impedance of the antenna between two impedance values defines an encoding of zeros and ones, for a matching impedance would absorb the signal while a mismatching impedance would reflect it, hence backscatter it. Given that TV energy is always present and not initially designed for harvesting devices, it may be considered almost natural, albeit not being a natural phenomenon unlike sunlight.

#### 2.3 Embedded Programming

The software is often co-designed alongside the hardware. Programming on embedded targets differs from programming on desktop targets. Apart from the computing capabilities being different, the experience of developing is not the same, notably if the software is meant to be executed in a bare-metal manner, *i.e.*, there is no operating system to rely on.

#### 2.3.1 Programming Basics

Throughout this work, a certain amount of programming notions are referred to, notably CPU registers, peripheral control registers and stack; heap to a lesser extent.

The micro-controller contains, among others, a Central Processing Unit (CPU). The CPU itself contains registers which are fast memory units not mapped in memory. Most of the CPU registers are for general purpose; e.g., arithmetical operations. A few of them are rightfully called special registers. The program counter contains the address of the current instruction. The status register contains information about run-time execution, such as the interrupt status (i.e., enabled or disabled) and the condition flags used for branching. The stack pointer contains the address of the topmost part of the stack.

Stack is a portion of main memory dedicated to storing some of the local variables and information of functions and interrupt handlers. Stack may be ascending or descending, respectively grows towards higher or lower addresses. Orthogonally, stack may be full or empty, the stack pointer respectively points to the actual topmost item or points to the next location after the topmost item. Any combination of these two axes may exist and it is more a matter of implementation details, since the push and pop instructions, that respectively put an item on top of the stack and retrieve the topmost item, manage the stack pointer accordingly to the stack model of the CPU. At the end of the day, the only concerns about stack management, that truly depend on the stack nature, are its initial value and specific management operations (e.g., stack lookups without popping any value). These are concerns for a bare-metal bootloader or for an operating system, even the most basic ones, but not for the application itself, whose stack is usually managed by a compiler.

A program binary is usually split into several sections. The .text section contains the program instructions. Most of the time read-only, it may though be modified if the application needs that feature. Global variables are spread onto two sections: the .bss sections for global variables which initial value is zero and the .data section for the other global variables. Since the variables of the .data section have a non-zero but pre-defined initial value, these variables are relocated. The relocation section contains the initial values of all the variables from the .data section, in the same order and respecting variables sizes and alignment. The relocation section is allocated apart from the .data section, so that the application only works on the .data section and the relocation section is read-only. The implicit contract of run-times is that an external entity is responsible for zeroing the .bss section and copying the relocation section into the .data section, at run-time and before the application actually starts. This is one of the roles of bootloaders and operating systems. The stack is also a section on its own, since it must be reserved for stack purposes. As mentioned, the initial value of the stack pointer must be set before the application starts.

In bare-metal programming as well as in operating system programming, section locations and sizes must be carefully studied. Relying on the compiler, section mapping is usually achieved by handcrafted linker scripts that contain memory placement indications for the linker stage of the binary production. Specifically, the linker script must at least place the bootloader code at the address corresponding to the reset value of the program counter, defined by the micro-controller manufacturer.

Heap is a portion of memory dedicated to dynamically-allocated memory, whereas .bss and .data sections are statically-allocated, *i.e.*, allocated by the compiler. Heap comes with a heap manager, that proposes a certain amount of services. Amongst the most essential services are the memory allocation request, *e.g.*, malloc, and the memory liberation request, *e.g.*, free. The main concerns with heap is that heap memory becomes segmented over time. Memory segmentation may prevent the system from providing a memory block of the requested size at some point, resulting in a failure. It also makes the memory allocation and liberation slower. Hence, heap memory is often frowned upon by embedded developers albeit highly used in non-embedded programming. Static allocation is more predictable and faster, thus admittedly a good choice for embedded systems.

#### 2.3.2 Intermittent Programming Paradigms

Due to the scarce nature of the harvested energy, using low-power hardware is not sufficient in essence and the software must be energy-efficient by managing the different power-consuming components in a clever way.

Energy neutral systems only use the energy harvested from the environment and do not use any other energy source. Energy neutrality is a property that can be achieved in sundry ways. It depicts a large spectrum including tiny harvest-use systems on one hand, and larger systems equipped with batteries and larger harvesters on the other hand [34, 35]. Only smaller platforms are studied in this thesis, for they have to cope with harsher run-time conditions. The harvest-store-use and harvest-use(store) policies are

closer to the battery-powered systems, however the energy storage can be as small as a simple capacitor of a few dozens microfarads, which is orders of magnitude smaller than complex batteries of several ampere-hours. Existing battery-less systems usually bet on power outage scarcity, due to an efficient energy management and an energy harvesting source capable of delivering enough power to allow an almost infinite execution of the application. A cell-phone [36], eye-tracking goggles [37] and a video streamer [38] are examples of such battery-less systems. In order to reduce energy, these solutions directly wire the raw output of the sensor to a backscatter emitter. Encoding is simple and filtering is performed by the reader platform, which itself is not energy-constrained. Hence, these applications remain rather simple. Power outages occasionally occur, however these applications allow to be restarted from the beginning every time, as long as the power outages are not too frequent regarding the application performance expectations. More complex applications cannot be satisfied by these power-related conditions for they would require some mechanisms to spread across power outages.

Normally-off computing is a paradigm designed to power off components as soon as they are no longer needed [39]. Any component is concerned, should it be the micro-controller or any peripheral. Special attention must be drawn to the power-on times of each component though, for some hardware concerns such as clock stabilization may require dozens or hundreds milliseconds. Ultimately, the whole system can be turned off while waiting for an external event to occur for instance. Power outages are thus inherently part of the design. The usage of non-volatile RAM makes normally-off systems feasible as the memory now needs to be powered on only when reading or writing to it, and keeps its data despite power outages, while the fully volatile counterparts would need to be kept powered on even when no operation is performed on it. Considering the unfortunately still standing performance gap between volatile and non-volatile RAMs discussed in Section 2.5.2, normally-off systems may also embed volatile memory in addition to a volatile micro-controller and a memory hierarchy must be defined. To that extent, normally-off systems need a memory policy and need to guarantee consistency within heterogeneous memories.

#### 2.4 Embedded Operating Systems

After being introduced to embedded programming in general and in a bare-metal manner, one must consider that operating systems for embedded and constrained platforms do exist. Operating Systems provide a set of services to the applications they host. Amongst the most basic services are peripheral handling. The applications access the peripherals of the platform using the operating system's services, through a so-called Application Programming Interface (API). Operating Systems are also responsible for the boot sequence of the hardware platform as well as the software environment in which are executed the applications.

Operating systems generally support several applications, or *processes*, to execute in parallel, even if the micro-controller is not multi-threaded. This is called *scheduling*. The operating system keeps track of the currently running processes and constantly has to choose, at run-time, how much time or energy should be given to each process. Processes may be prioritized or, on the contrary, given the same proportion of execution time.

More sophisticated operating systems isolate processes so that each process cannot access the memory of other processes. More security-related services might be offered by the operating system, depending on its complexity and on whether it is relevant for the application that should run on the platform.

#### 2.4.1 Common Operating Systems

The most widespread operating system for embedded platform is likely any distribution of Linux that can execute on the considered platforms. For instance, Linux is commonly used in single-board computers. Single-board computers are complete systems, including micro-processors, memory and peripherals, that are embedded into a single board, as opposed to traditional computers that have a mother board and many daughter boards for modularity purposes. They are often about as small as credit cards, albeit not as flat. Popular single-boards include, and are not limited to, the Raspberry Pi, Orange Pi, Banana Pi, BeagleBoard and Odroid platforms. Single-board platforms tend to increase their computation capabilities with multi-core micro-processors, higher bus speeds, more RAM, etc. Today, the average single-board platform has a quad-core micro-processor and several gigabytes of volatile RAM, enabling

the execution of Linux-based systems. The kernel is often stored in a removable SD card. Some of them even embed Graphics Processing Units. The recent Nvidia Jetson Nano platforms embed 128 Maxwell graphical cores and consumes up to 5 W. Single-board platforms are widely used for teaching purposes and in robotics. They need a power supply capable of delivering several amperes. The energy demands of such platforms are a few orders of magnitude superior to those of the transiently-powered systems considered in this thesis.

A Linux-based operating system requires hundreds of megabytes of RAM, as well as hundreds of megabytes of storage. Of course, the actual requirements of Linux heavily depend on the considered distribution. However, even the most lightweight distributions need a fair amount of memory and this is to take into account when designing embedded platforms. Within the context of transiently-powered systems, today's non-volatile RAM technologies do not allow that much memory within small form factors.

Other operating systems target smaller devices. RIOT [40] fits in a few kilobytes, for both instruction code and RAM usage. RIOT supports multi-threaded applications. Its priority-based scheduler and its low interrupt latency also widen the applications of RIOT to real-time applications. Some operating systems incorporate real-time requirements as an inherent part of their design. A key challenge for real-time embedded systems is to provide deterministic services that execute for a known amount of time, regardless of the state of the platform. FreeRTOS provides a threading library that aims at ensuring a correct execution of a well-specified application.  $\mu$ C/OS-II [41] and  $\mu$ C/OS-III [42] are popular real-time preemptive operating systems. Zephyr is part of the Linux Foundation and inherits some concepts from Linux, including device trees. Unlike traditional Linux distributions, Zephyr provides a real-time environment. Finally, VxWorks is also very popular in the world of real-time systems. However, VxWorks is designed for embedded systems with higher capabilities, such as automotive and robotics.

Although these smaller operating systems consider hardware constraints that arise with the nature of embedded systems, they are still complex for smaller energy-harvesting devices. Furthermore, although real-time properties are useful for many applications, the very definition of time, and more specifically of real-time constraints, is substantially altered and does not have the same semantics when off-times become part of the application.

#### 2.4.2 Legacy Operating Systems for Constrained Platforms

TinyOS [43] targets sensor networks of constrained nodes that must be reactive to events. It proposes an event-driven system as an alternative to multi-threaded systems. The application is designed as separate tasks that are run to completion, *i.e.*, tasks do not hang indefinitely and or not preemptable. Tasks can be spawned upon event occurrence, either external or initiated by other tasks.

Contiki [44] primarily focuses on the ability to deploy applications and updates onto an entire network. Contiki aims at being used in constrained platforms. It thus proposes a library of protothreads [45] to simulate a multi-threaded environment on a single stack. When a protothread blocks, the stack is rewound to enable another protothread to execute. Contiki's model differs from that of TinyOS, mainly due to the protothreads being preemptable. In TinyOS, on the contrary, each task must execute to completion before another is scheduled and thus, lengthy computations may impede the overall performance of the task set and the reactivity of the system to external events.

Dewdrop [46] is a task scheduler, designed for computational RFID systems, that leverages energy-related data to make decisions. The platform is kept in deep sleep when either no action is required or no activity can be scheduled due to the instantaneous energy level. Taking energy concerns into account improves the efficiency of the computational RFID platforms, that can operate at longer ranges. Similarly to TinyOS, Dewdrop asks the application developer to decompose the different activities of the application into separate tasks, each task being designed to run to completion without interruption. However, Dewdrop's task model is more restrictive and more suited to RFID applications: the same task is repetitively executed. Dewdrop aims at starting the execution of the task at the optimal energy level, given the challenge that the radio energy source is unpredictable. QuarkOS [47], built on top of Dewdrop, attempts to address the issue of the long tasks by proposing a decomposition of the tasks into sub-tasks, yet still designed to run to completion without interruption. The platform may enter deep sleep between consecutive sub-tasks, in order to recharge the energy storage in the meantime. The granularity of a sub-task can be as fine as transmitting a single pulse belonging to a bit within an OOK-modulated packet.

At coarser granularity, a sub-task could, for instance, compute a single pixel from a camera sensor being read. This, of course, assumes that the activities are divisible, which constrains the network protocols and the sensing operations. However, an application may run on QuarkOS with a capacitor as small as  $0.1~\mu F$ .

TinyOS and Dewdrop assume that every task executes to completion before another can execute. Contiki slightly relaxes that assumption by allowing protothreads to be preempted only when explicitly requested by the application code or upon completion. These assumptions are broken when troublesome imminent power outages, that come along with intermittent supply, disturb the run-time conditions. Instead of trying to support intermittent power as a software wart inside existing operating systems that are not designed for such energy constraints, it thus becomes imperative to design operating systems, or at least helpers, for applications for transiently-powered systems. Chapter 3 and Chapter 4 comprehensively study such operating systems designed for transiently-powered systems, against the problematics identified in Section 2.6.

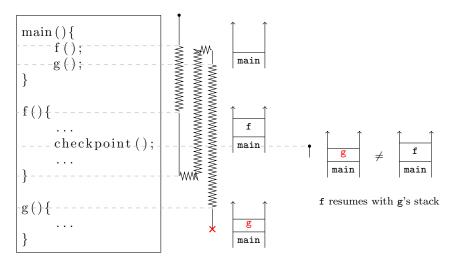

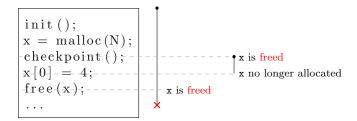

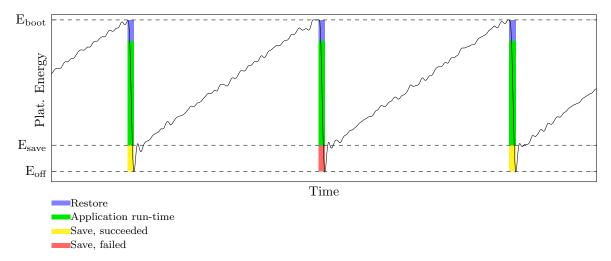

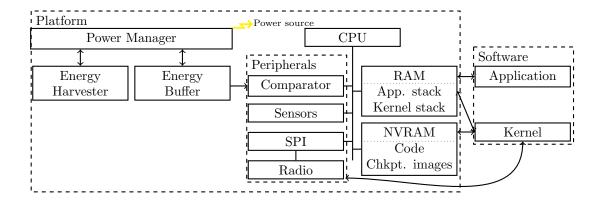

#### 2.4.3 Operating Systems for Energy-Harvesting Systems