# Moisture-related ageing mechanisms of interconnects $low-\kappa$ dielectrics

Matthias Vidal-Dho

### ▶ To cite this version:

Matthias Vidal-Dho. Moisture-related ageing mechanisms of interconnects low- $\kappa$  dielectrics. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2020. English. NNT: 2020GRALT066 . tel-03205937

### HAL Id: tel-03205937 https://theses.hal.science/tel-03205937v1

Submitted on 22 Apr 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES

Arrêté ministériel : 25 mai 2016

Présentée par

### **Matthias VIDAL-DHO**

Thèse dirigée par **Patrice GONON**, Maitre de Conférences, Université Grenoble Alpes et codirigée par **Bernard PELISSIER**, Ingénieur de Recherche Hors Classe (IRHC), Université Grenoble Alpes

préparée au sein du Laboratoire Laboratoire des Technologies de la Microélectronique dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Mécanismes de vieillissement liés à la pénétration d'humidité dans les matériaux diélectriques à faible permittivité des interconnexions.

# Moisture-related ageing mechanisms of interconnects low-K dielectrics.

Thèse soutenue publiquement le **3 décembre 2020**, devant le jury composé de :

### **Monsieur PATRICE GONON**

MAITRE DE CONFERENCES HDR, UNIVERSITE GRENOBLE ALPES, Directeur de thèse

#### Madame CHRISTINE ROBERT-GOUMET

MAITRE DE CONFERENCE, UNIVERSITE CLERMONT AUVERGNE, Examinatrice

#### **Monsieur ALAIN BRAVAIX**

PROFESSEUR DES UNIVERSITES, UNIVERSITE DE TOULON, Rapporteur

### **Monsieur QUENTIN HUBERT**

DOCTEUR-INGENIEUR, ST MICROELECTRONICS DE ROUSSET, Examinateur

#### **Monsieur ANTOINE GOULLET**

PROFESSEUR DES UNIVERSITES, UNIVERSITE DE NANTES, Rapporteur

#### Monsieur ALAIN SYLVESTRE

PROFESSEUR DES UNIVERSITES, UNIVERSITE GRENOBLE ALPES, Président

### Thèse de doctorat

### Matthias Vidal-Dhô

Mécanismes de vieillissement liés à la pénétration d'humidité dans les matériaux diélectriques à faible permittivité des interconnexions.

Dirigée par Patrice Gonon et co-encadrée par Quentin Hubert et Bernard Pelissier

Présentée en vue de l'obtention du grade de :

### Docteur en Nano-Électronique et Nano-Technologies de l'Université Grenoble Alpes

Préparée au sein du Laboratoire des Technologies de la Microélectronique (LTM) de l'Ecole Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Thèse soutenue le 3 décembre 2020 devant le jury présidé par Alain Sylvestre

Thèse soutenue le 3 décembre 2020 en visioconférence devant le jury composé de :

Alain Sylvestre, Maître de Conférence, Université Grenoble Alpes, *Président*. Alain Bravaix, Professeur, Aix-Marseille Université et Université de Toulon, ISEN *Rapporteur*.

Antoine Goullet, Professeur, Université de Nantes, Polytech Nantes, Rapporteur. Christine Robert-Goumet, Maître de Conférences, Université Clermont-Auvergne, Examinatrice.

Patrice Gonon, Maître de conférence, Université Grenoble Alpes, *Directeur de thèse*. Quentin Hubert, Docteur-Ingénieur, NAWA Technologies, *Invité*. Bernard Pelissier, Ingénieur de recherche, LTM, CNRS, *Invité*.

# Mécanismes de vieillissement liés à la pénétration d'humidité dans les matériaux diélectriques à faible permittivité des interconnexions.

### Résumé

La réduction des dimensions des dispositifs micro-électroniques élémentaires, notamment des transistors et des cellules mémoires, a permis au cours des dernières décennies d'augmenter la densité d'éléments intégrés et donc d'obtenir plus de fonctions au sein d'une même puce. Cette réduction des dimensions a notamment nécessité l'introduction de matériaux diélectriques à faible permittivité, particulièrement sensibles à l'humidité. Cette thèse détaille les propriétés électriques de tels matériaux ainsi que les conséquences de leur contamination par l'humidité sur leurs caractéristiques. Le procédé de fabrication des interconnexions à base de cuivre et de matériau à faible permittivité est détaillé puis, le matériau à faible permittivité utilisé dans les interconnexions avancées, appelé SiOC: H, est caractérisé afin d'en déterminer les principales propriétés chimiques et structurelles, nécessaires à la compréhension des phénomènes physiques menant à la dégradation des performances électriques de ces matériaux. Ensuite, une importante étape de conception et de fabrication de structures de caractérisation permettant l'étude de l'impact de la pénétration d'humidité sur les performances électriques du matériau SiOC :H est détaillée. Enfin, les résultats de caractérisations électriques effectuées sur ces structures sont présentés, permettant une compréhension des processus physiques menant à la dégradation des performances du matériau SIOC: H utilisé dans l'industrie microélectronique.

### Mots-clés

Matériaux diéléctriques à faible permittivité, SiOC :H, fiabilité des matériaux diélectriques, pénétration d'humidité, courant de fuite, dégradation.

# Moisture-related ageing mechanisms of interconnects low- $\kappa$ dielectrics.

### Abstract

Over the past decades, scaling of microelectronic chips, in particular transistors and memory cells, has allowed to increase substantially both the density of integrated circuit and integrate the number of functions offered. Such scaling required the introduction of low permittivity dielectrics, which are particularly sensitive to moisture pollution. This thesis details the dielectrics main properties and the consequences of moisture ingress in such low-permittivity dielectrics, also referred as SiOC :H dielectrics. The fabrication of low- $\kappa$ /copper-based interconnects is detailed. Then, the SiOC :H dielectric material is characterised to determine its chemical and molecular structure in order to understand underlying physical phenomenon leading to the material electrical performances degradation. Then, the conception and fabrication of electrical test structures required to evaluate the impact of moisture on the electrical properties and performances of integrated SiOC :H dielectric material is presented. Finally, the results of electrical characterisations carried out on these structures provide a better understanding of physical phenomenon leading to electrical performance degradation of SiOC :H dielectric material used in the semiconductor industry.

### Key words

Low permittivity dielectrics, SiOC:H, dielectric reliability, moisture ingress, leakage current, degradation.

### Acknowledgements

This thesis has undoubtedly been the occasion to develop my technical competences and my critical mind but it has also allowed me to meet valuable persons. I would like firstly to express my gratefulness to everyone that had sponsored my requests, I truly hope this manuscript will convince them that they were right to do so. For a thesis, it is clear that having an interesting topic matters a lot but what is even more important is the people around you. Patrice and Bernard have always been available to have fruitful chats and give me constructive advice and feedback at every of my solicitation. I would like obviously to thank Quentin for the extensive help, discussions and advice he provided. He is probably the most accountable for turning me from a student into a PhD graduate. Throughout all my curriculum, I cannot recall having such an invested tutor. I had also the chance to be part of probably the best team possible: the ECR team, such friendly atmosphere makes everything easier. I hope you will take care of TBE04 for me.

I also thank all the members of the PI, especially Bernadette who helped me a lot with WS and routes handling. I want now to thank all of you who endured my questions, requests, and helped me a lot with my experiments over the past three years: Névine R. for (very) repetitive FTIR and MIR measurements and advice, Ludo B., Philippe L., Philippe D., Patrice R. and Maxime M. for being very comprehensive and patient with this thésard who wanted some weird experiments and a lot of TEMs, obviously Pascal F. for the extensive help for the route setup and debug and feedback all along those three years, J-P E. for answering my numerous dumb questions about the process. To stay on this topic, I also thank Alex V., Guillaume P., Olivier F. and Wilfrid M. for their help for process experiments and material samples and Matthieu L. for the TOTEM PT, I also want to thank Eric C., Raphael M., Frédéric B. and Thierry C. from the MDG lab for their support and flexibility.

Despite the fact that a PhD is often presented as a period of suffering, mine did not thanks to all the persons I have met during these three years. STay young people: BAPs, Risks, ski, lunches, nights out, climb'up and surf sessions and so on will remain in my best memories, and I cannot wait for the next ones.

Last but not least, I have had the chance to be supported by my family, in particular my parents. I will never forget that, over the years, they made lots of sacrifices to let me pursue my hopes and supported me in periods of doubt. The Mimi's have also had a very special role since my youth, they continuously gave me invaluable knowledge, kindness and self-confidence. I hope this manuscript will make them proud too.

To all of them, Thank you!

## Contents

| G            | lossa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ury                                                                        | ix |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----|

| $\mathbf{G}$ | General introduction         1           Interconnects and dielectrics         3           1.1 Introduction         3           1.2 Modern microelectronics and Moore's law         3           1.2.1 From kettles to pacemakers: chips surround us         4           1.2.2 Moore's Law and interconnects         4           1.3 Dielectrics         5           1.3.1 Role of dielectrics in chips interconnects         5           1.3.2 Low permittivity dielectrics: macroscopic and microscopic principles         6           1.3.3 Strategies to reduce the permittivity         13           1.4 Interconnect reliability         13           1.4.1 Interconnect failure modes         14           1.4.2 Usual electrical characterisation techniques         17           1.4.3 Lifetime estimation: extrapolation models         22           1.5 Moisture and interconnects performances         24           1.5.1 Moisture ingress modalities         25           1.5.2 Moisture ingress countermeasures         26           1.5.3 Interconnect performance degradation indicators         26           1.6 Conclusion         30 |                                                                            |    |

| 1            | Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | erconnects and dielectrics                                                 | 3  |

|              | 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Introduction                                                               | 3  |

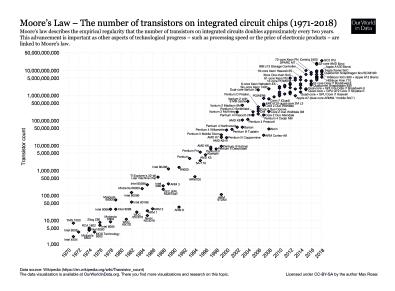

|              | 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Modern microelectronics and Moore's law                                    | 3  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.2.1 From kettles to pacemakers: chips surround us                        | 4  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.2.2 Moore's Law and interconnects                                        | 4  |

|              | 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Dielectrics                                                                | 5  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.3.1 Role of dielectrics in chips interconnects                           | 5  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.3.2 Low permittivity dielectrics: macroscopic and microscopic principles | 6  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.3.3 Strategies to reduce the permittivity                                | 13 |

|              | 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Interconnect reliability                                                   | 13 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.4.1 Interconnect failure modes                                           | 14 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.4.2 Usual electrical characterisation techniques                         | 17 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.4.3 Lifetime estimation: extrapolation models                            | 22 |

|              | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Moisture and interconnects performances                                    | 24 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.5.1 Moisture ingress modalities                                          | 25 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.5.2 Moisture ingress countermeasures                                     | 26 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.5.3 Interconnect performance degradation indicators                      | 26 |

|              | 1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Conclusion                                                                 | 30 |

| 2            | Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | egration process constraints and SiOC:H chemical structure                 | 31 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |    |

|              | 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                          |    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.2.2 SiOC:H deposition                                                    | 32 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            | 34 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.2.7 Wet and dry cleans                                                   | 35 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            | 36 |

|              | 2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | , 1                                                                        | 36 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.3.1 Required properties of materials used in the far BEOL                | 36 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.3.2 Encapsulation                                                        | 36 |

|   |      | 2.3.3 External moisture tightness                                    | 37 |

|---|------|----------------------------------------------------------------------|----|

|   | 2.4  | Process variability and SiOC:H specificity                           | 38 |

|   |      | 2.4.1 Generalities                                                   | 38 |

|   |      | 2.4.2 Process steps generating SiOC:H variability                    | 39 |

|   | 2.5  |                                                                      | 41 |

|   |      | 2.5.1 Surface Photovoltage measurements                              | 41 |

|   |      |                                                                      | 42 |

|   |      |                                                                      | 45 |

|   |      |                                                                      | 49 |

|   |      | 2.5.5 Conclusion                                                     | 53 |

| 3 | Elec | ctrical test structures conception, process control and optimisation | 55 |

|   | 3.1  | 1 / 1                                                                | 55 |

|   | 3.2  |                                                                      | 55 |

|   |      |                                                                      | 55 |

|   |      |                                                                      | 56 |

|   | 3.3  | 1 1                                                                  | 57 |

|   |      |                                                                      | 57 |

|   |      | •                                                                    | 58 |

|   |      |                                                                      | 58 |

|   |      |                                                                      | 59 |

|   |      | 1                                                                    | 59 |

|   | 3.4  |                                                                      | 61 |

|   |      | <del>-</del>                                                         | 61 |

|   |      |                                                                      | 62 |

|   | 3.5  |                                                                      | 64 |

|   |      |                                                                      | 65 |

|   |      | 3.5.2 Pad tightness                                                  | 66 |

|   | 3.6  | Conclusion                                                           | 69 |

| 4 | Mo   | isture and electrical characteristics of SiOC:H dielectric           | 71 |

|   |      |                                                                      | 71 |

|   | 4.2  |                                                                      | 71 |

|   |      | 9                                                                    | 72 |

|   |      |                                                                      | 73 |

|   |      | 4.2.3 Material considerations                                        | 75 |

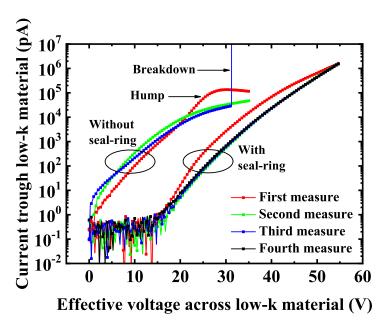

|   | 4.3  |                                                                      | 76 |

|   |      | 4.3.1 Intrinsic SiOC:H                                               | 77 |

|   |      | 4.3.2 Moisture ingress effect                                        | 80 |

|   |      | 4.3.3 Breakdown point localisation                                   | 81 |

|   | 4.4  | Breakdown mechanisms study                                           | 84 |

|   |      | · · · · · · · · · · · · · · · · · · ·                                | 84 |

|   |      |                                                                      | 86 |

|   |      |                                                                      | 89 |

|   | 4.5  | Conduction mechanism(s)                                              | 89 |

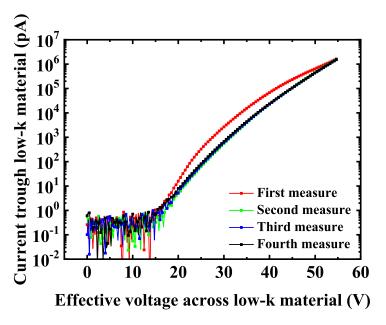

|   |      | 4.5.1 Static leakage current analysis                                | 89 |

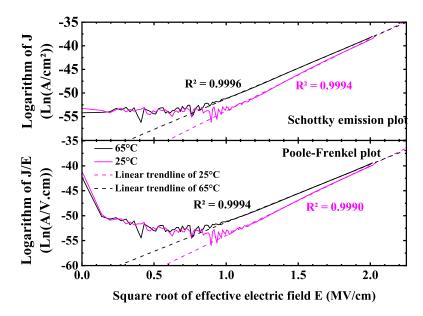

|   |      | 4.5.2 Schottky Emission and Poole-Frenkel tunnelling                 | 90 |

|        | 4.5.3   | Moisture influence on conduction mechanisms |

|--------|---------|---------------------------------------------|

|        | 4.5.4   | Triangular Voltage Sweep (TVS)              |

|        | 4.5.5   | Traps in SiOC :H dielectric                 |

| 4.6    | Concl   | 1sion                                       |

| Genera | al conc | lusion and perspectives 103                 |

### Glossary

```

.gds file .gds extension file format. 1, 55, 56

ABS Anti-lock Braking System. 1, 4

AFM Atomic Force Microscopy. 1, xiv, 44, 103

ATE Automatic Test Equipment. 1, 18

BEOL Back-End-Of-Line. 1, xiii, xvii, 3, 5, 6, 7, 13, 14, 15, 16, 18, 19, 20, 22, 23,

25, 26, 29, 32, 35, 38, 41, 55, 56, 57, 58, 61, 68, 69, 75, 81, 92, 103, 104

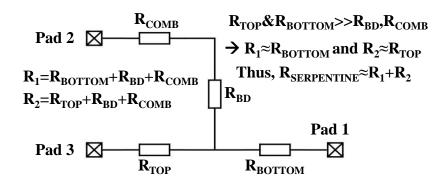

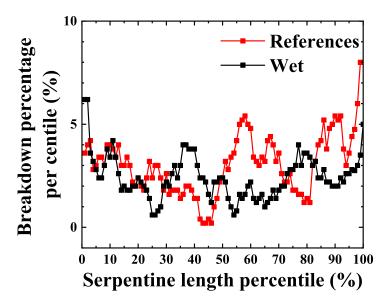

C/S/C interwoven Comb-Serpentine-Comb. 1, xvii, xix, 58, 59, 62, 78, 79, 80, 81,

82, 85, 86, 87, 104

C2M CAD-to-Mask. 1, 56, 57, 61, 69, 104

CAD Computer-Aided Design. 1, xiv, 40, 55, 56, 57, 61, 84, 104

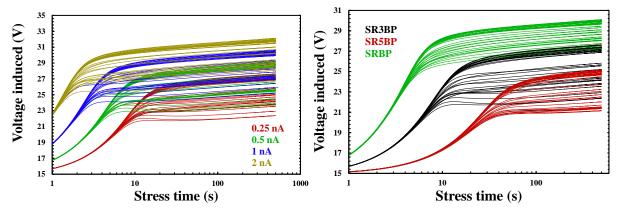

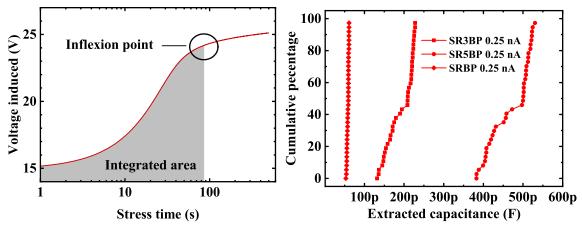

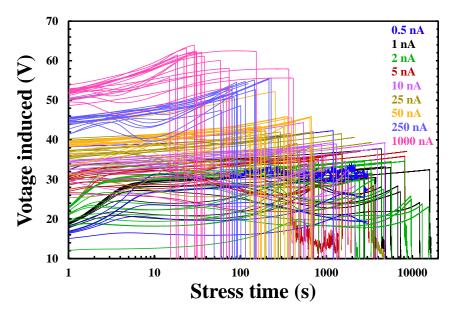

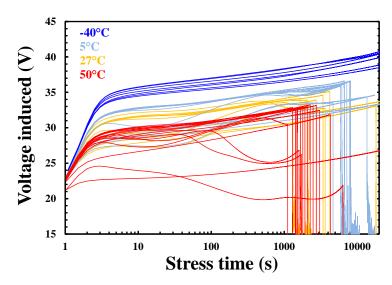

CCS Constant Current Stress. 1, xvii, 21, 22, 29, 86, 87, 88, 89, 97, 102, 105

CD Critical Dimension. 1, 39, 61, 63

CMOS Complementary Metal-Oxide Semiconductor. 1, 3

CMP Chemical-Mechanical Planarisation. 1, 14, 25, 34, 35, 38, 40, 83, 104

CVD Chemical Vapour Deposition. 1, 61

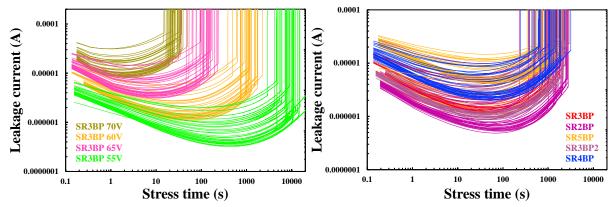

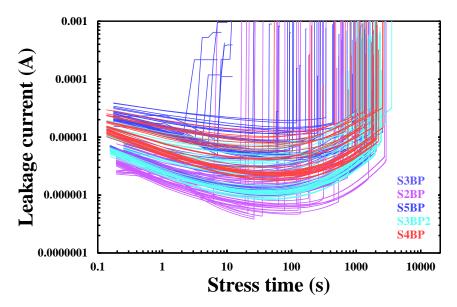

CVS Constant Voltage Stress. 1, xvii, xviii, 21, 22, 29, 77, 78, 80, 82, 84, 85, 86, 90,

99, 105

Design Rules Manual It refers to the document containing the ensemble of rules

which constrain the drawing of structures/chips, in order to guaranty electrical

functionality. These rules are established with the help of several parameters such

as process variability, processing tools capability and reliability assessments.. 1

DRM Design Rule Manual. 1, 56, 60

EDMR Electrically Detected Magnetic Resonance. 1, 100, 106

EDX Transmission Electron Microscopy (TEM) Energy Dispersive X-ray. 1, xv, 45,

47, 48, 103

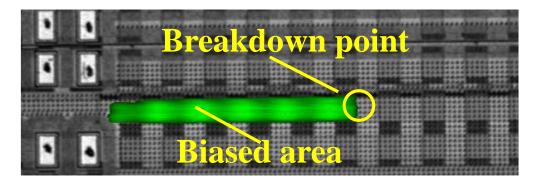

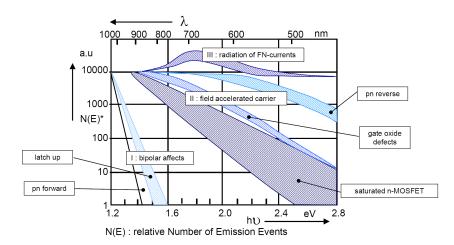

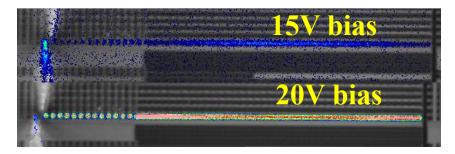

EMMI EMission Microscopy. 1, xviii, 93, 94, 102, 105

ERCS Exponential Ramp Current Stress. 1, 29

eV electron-Volts. 1, 92, 100

EWS Electrical Wafer Sort. 1, 2

Far BEOL Far Back-End-Of-Line. 1, 36, 37, 57, 71, 104

FEOL Front-End-Of-Line. 1, 3, 18, 26, 32, 63

```

```

FTIR Fourier Transform InfaRed. 1, xv, 9, 49, 50, 51, 52, 53, 101, 103

GISAXS Grazing-Incidence Small Angle X-ray Scattering. 1, xiv, xv, 42, 43, 44, 45,

Graphic Data System Misleadingly used to refer to files containing the physical

description of a structure layout. It is a quasi industrial standard in the semi-

conductor industry. OASIS for Open Artwork System Interchange Standard is a

similar format type and may replace GDS at some point. 1

HM Hard Mask. 1, xiv, 33, 35, 40

ID Impact Damage. 1, xvii, 23, 24, 77, 78, 100, 102, 103

IMD Inter-Metallic Dielectric. 1, 5, 6, 11, 17, 19

IoT Internet of Things. 1, 4, 106

ITRS International Technology Roadmap for Semiconductors. 1, 5, 7

low-\kappa low permittivity. 1, 2, 5, 6, 7, 13, 15, 21, 23, 24, 25, 26, 27, 30, 31, 32, 33, 34,

36, 37, 41, 45, 47, 49, 53, 55, 57, 61, 70, 71, 75, 81, 84, 89, 92, 98, 103, 104, 105,

106

LRVS Linear Ramp Voltage Stress. 1, 29

MIM Metal-Insulator-Metal. 1, 100

MIR Multiple Internal Reflections. 1, xv, xvii, 49, 50, 51, 52, 53, 75, 76, 101, 102,

103, 104, 105

MOL Middle-Of-Line. 1

MV Mega-Volts. 1, 92

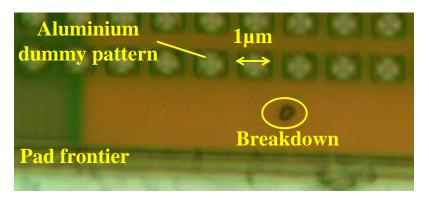

OBIRCH Optical Beam-Induced Resistance CHange. 1, xvii, 82, 83

OEM Original Equipment Manufacturers. 1

OPC Optical Proximity Correction. 1, 40, 56, 57, 61, 69, 104

PARXPS Parallel Angle Resolved X-ray Photoelectron Spectroscopy. 1, xv, 46, 47,

103

PECVD Plasma-Enhanced Chemical Vapour Deposition. 1, 32, 40, 61

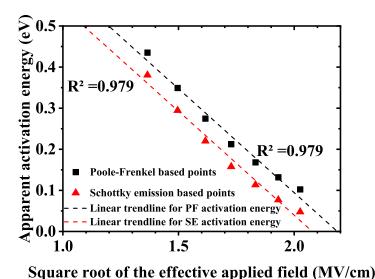

PF Poole-Frenkel trap-assisted tunnelling. 1, xvii, xviii, 23, 90, 91, 92, 97, 105

PL Power Law. 1, xvii, 23, 24, 77, 78, 103

PMD Pre-Metal Dielectric. 1, 32, 57

POR Process Of Reference. 1, xiv, xv, 41, 42, 43, 44, 45, 46, 47, 50, 51, 52, 75, 100

PT Parametric Test. 1, 2, 18, 26

PVD Plasma Vapour Deposition. 1, 37

R&D Research & Development. 1, 5, 7, 22

R-E Root-E. 1, xvii, 23, 24, 77, 78, 103

RH Relative Humidity. 1, xvi, 73, 74, 102

SE Schottky thermionic Emission. 1, xvii, xviii, 23, 90, 91, 92, 97, 105

SEM Scanning Electron Microscopy. 1, xiv, xvi, 39, 40, 44, 61, 67, 68, 69

```

```

SILC Stress-Induced Leakage Current. 1, 95

SPV Surface PhotoVoltage. 1, xiv, 41, 42

SSCM Standard Cubic Centimetres per Minute. 1, 32, 41

T<sub>BD</sub> Time-to-Breakdown. 1, 62

TDDB Time-Dependent Dielectric Breakdown. 1, xiv, 28, 29, 34, 36

TEM Transmission Electron Microscopy. 1, xv, 48, 62, 69

TEOS TetraEthyle OrthoSilicate. 1, 32, 34, 35, 36, 48

THB Temperature Humidity Bias. 1, 73, 76

TMS TetraMethylSilane. 1, 32, 41, 46, 47, 51, 52, 104

TVS Triangular Voltage Sweep. 1, xviii, 94, 95, 96, 97, 98, 105, 106

XPS X-ray Photoelectron Spectroscopy. 1, 45, 46, 47, 100, 103

```

# List of Figures

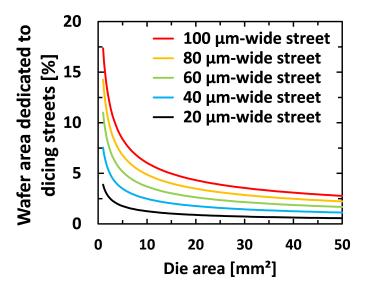

| 1.1  | Moore's law, with major commercial processors names                                            | 4  |

|------|------------------------------------------------------------------------------------------------|----|

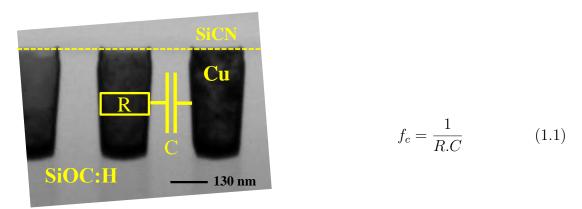

| 1.2  | Resistance-Capacitance equivalent circuit in the BEOL                                          | 6  |

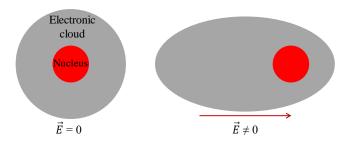

| 1.3  | Schematic principle of electronic cloud polarisation event around an atom                      |    |

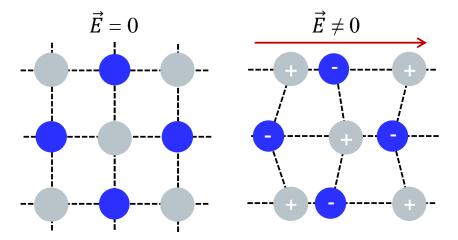

|      | under an electrical field $E$                                                                  | 8  |

| 1.4  | Schematic principle of ionic polarisation event in an ionic crystal under an                   |    |

|      | electrical field $E$                                                                           | 9  |

| 1.5  | Schematic principle of dipolar polarisation event in a dielectric under an                     |    |

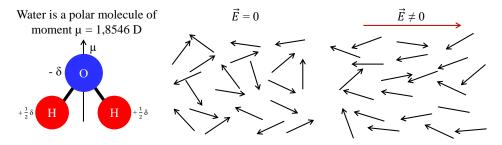

|      | electrical field $E$                                                                           | 10 |

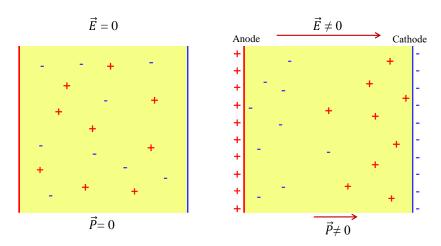

| 1.6  | Schematic principle of free space charges polarisation event in a dielectric                   |    |

|      | under an electrical field $E$                                                                  | 10 |

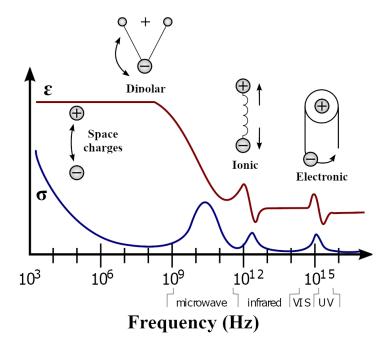

| 1.7  | Different polarizabilities mechanisms implies different frequency responses.                   |    |

|      | Here schematically, $\epsilon$ refers to the material dielectric constant, and $\sigma$ to its |    |

|      | conductivity (including dielectric loss)                                                       | 11 |

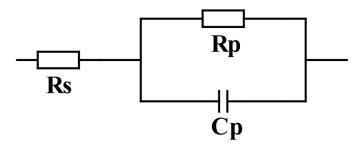

| 1.8  | Parallel capacitance measurement model with the addition of a series re-                       |    |

|      | sistance $R_s$ accounting for the access resistance of the structure                           | 12 |

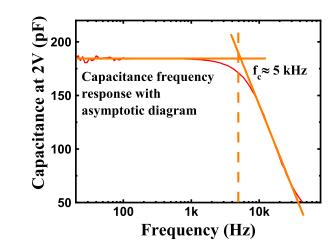

| 1.9  | Frequency response of standard BEOL structure (see section 3.3 for more                        |    |

|      | details) showing frequency limitation from access resistance                                   | 13 |

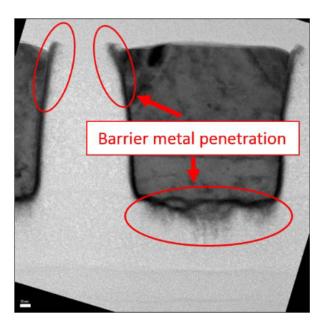

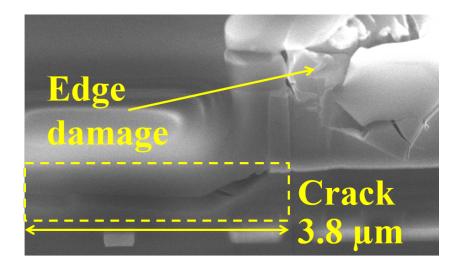

| 1.10 | Example of delamination and crack diffusion in a chip BEOL                                     | 14 |

| 1.11 | Example of tantalum diffusion barrier diffusion                                                | 15 |

| 1.12 | Electromigration structure and failure principle                                               | 16 |

|      | 1.12.a Electromigration structure                                                              | 16 |

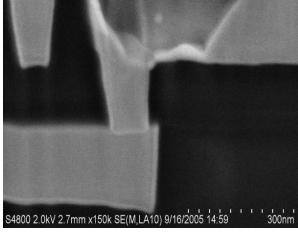

|      | 1.12.b SEM cross-section of a line after an electromigration test from                         |    |

|      | Cheng et al A void without copper is seen on top of the via                                    | 16 |

| 1.13 | Cross-section view of a catastrophic breakdown between metallic lines                          | 17 |

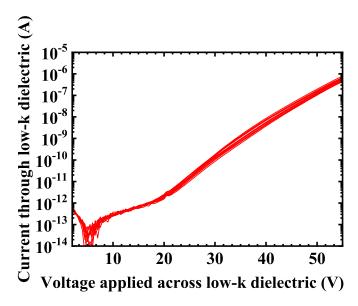

| 1.14 | Stacked leakage current-voltage characteristics of standard interconnect                       |    |

|      | structures                                                                                     | 18 |

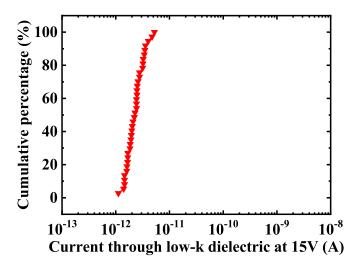

|      | Semi-log cumulative distribution of leakage currents measured at 15V bias.                     | 19 |

| 1.16 | Cumulative distribution of capacitances values measured at 1kHz, 200mV                         |    |

|      | amplitude AC signal under 0V DC bias                                                           | 20 |

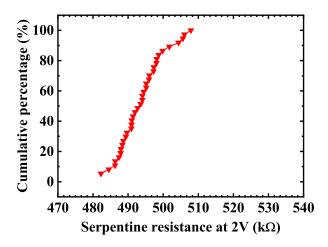

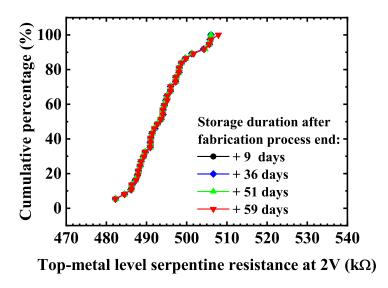

| 1.17 | Cumulative distribution of serpentine resistance values measured at 2V                         | 20 |

| 1.18 | CVS test and Weibull representation                                                            | 21 |

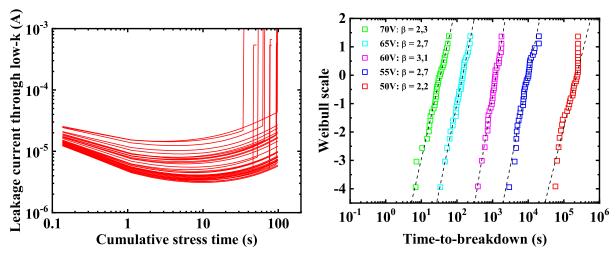

|      | 1.18.a Example of a leakage current measurement during CVS test at 65V.                        | 21 |

|      | 1.18.b Weibull distribution of time-to-breakdowns extracted from CVS                           |    |

|      | tests at different voltages                                                                    | 21 |

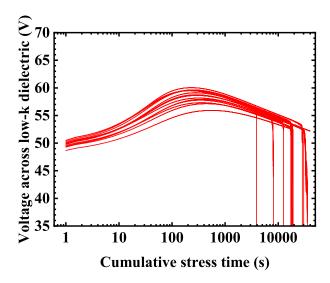

| 1.19 | Voltage measurement during CCS tests at $1\mu A$ on reference structures                       | 22 |

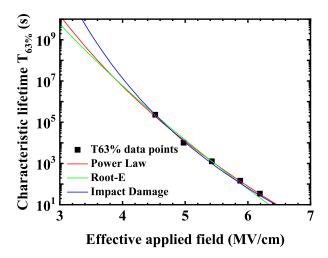

| 1.20 | Different lifetime extrapolation models fitted to experimental data points                     |    |

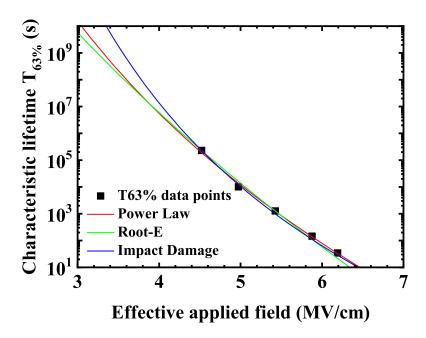

|      | from figure 1.18.b                                                                             | 24 |

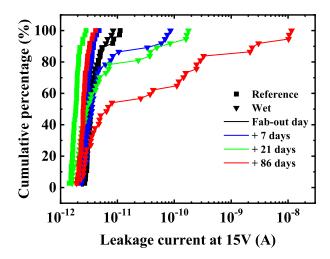

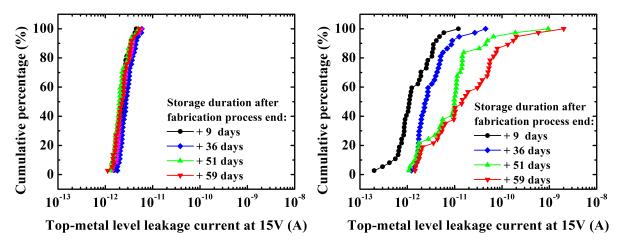

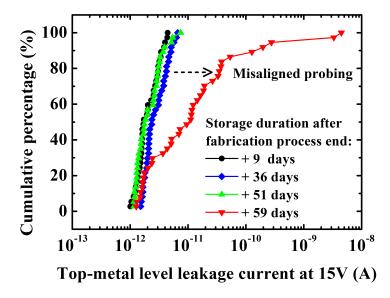

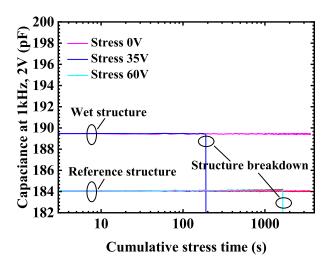

| 1.21 | Evolution of leakage current at 15V                                            | 27  |

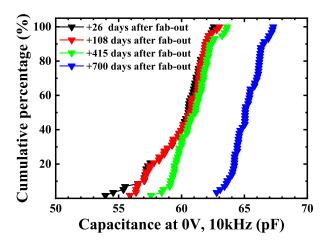

|------|--------------------------------------------------------------------------------|-----|

| 1.22 | Capacitance evolution over time of wet structures                              | 27  |

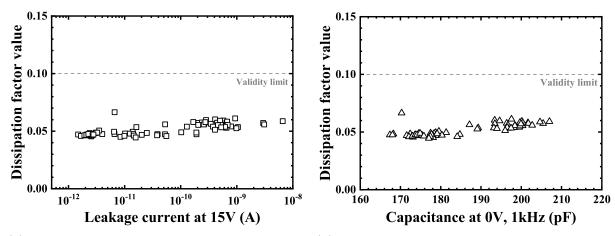

| 1.23 | Dissipation factor correlations with capacitance and leakage current           | 28  |

|      | 1.23.a Dissipation factor as a function of leakage current at 15V              | 28  |

|      | 1.23.b Dissipation factor as a function of capacitance value measured at       |     |

|      | 0v, 1kHz                                                                       | 28  |

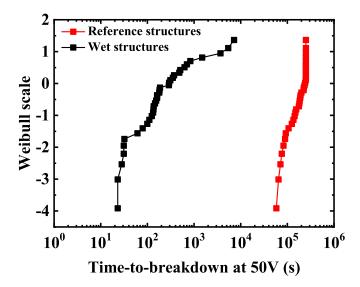

| 1.24 | Moisture impact on test structure TDDB performance                             | 29  |

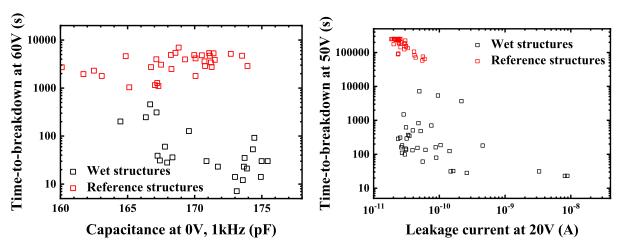

|      | PT parameters and time-to-breakdown correlation plots                          | 30  |

|      | 1.25.a Time-to-breakdown as a function of capacitance value measured           |     |

|      | just before stress                                                             | 30  |

|      | 1.25.b Time-to-breakdown as a function of leakage current measured at          |     |

|      | 20V just before stress                                                         | 30  |

| 0.1  |                                                                                | 26  |

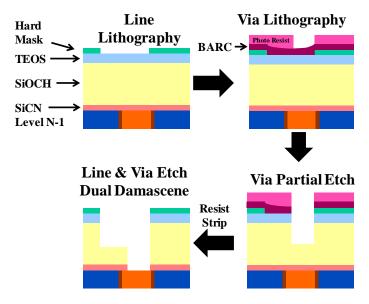

| 2.1  | Etching process steps in the dual-damascene process flow                       | 33  |

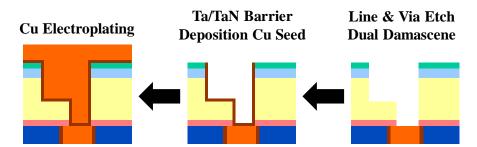

| 2.2  | Ta/TaN copper diffusion barrier deposition, copper seed, and copper elec-      | 2 / |

| 0.0  | troplating in the dual-damascene process flow                                  | 34  |

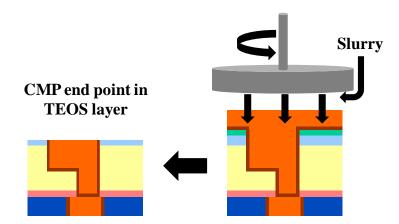

| 2.3  | Chemical Mechanical Polishing process step in the dual-damascene process flow. | 35  |

| 2.4  | Potential consequence of poorly controlled CMP followed by high-pressure       | Je  |

| 2.4  | water jet during wet cleaning                                                  | 35  |

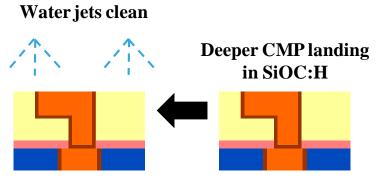

| 2.5  | Schematic representation of the pad fabrication after the encapsulation step.  |     |

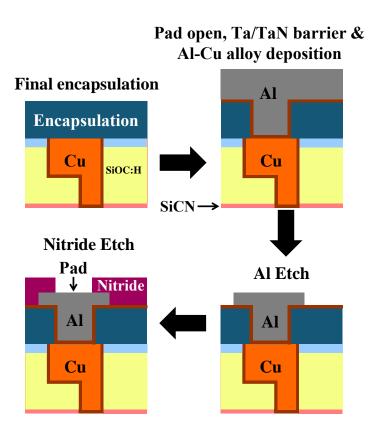

| 2.6  | Schematic representation of the different types of variability in the semi-    | 01  |

| 2.0  | conductor industry [104]                                                       | 38  |

| 2.7  | Example of a multiple chambers tool                                            | 39  |

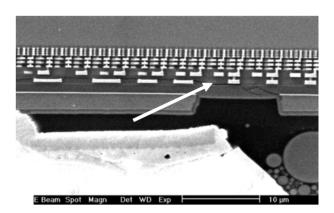

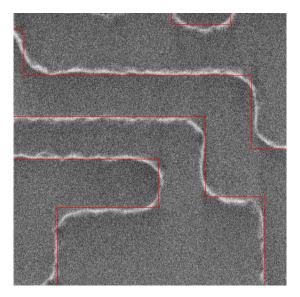

| 2.8  | SEM view of a first layer of interconnect after HM lithography and super-      | 00  |

| 2.0  | posed drawn metal 1 CAD layer boundaries (red). The area or the future         |     |

|      | copper lines are freed from HM                                                 | 40  |

| 2.9  | SPV measurement and effect of anneal on the relative dielectric constant of    |     |

|      | as-deposited POR SiOC:H (2.9.a), and POR SiOC:H treated with a 1-hour          |     |

|      | anneal at 400°C under nitrogen(2.9.b)                                          | 42  |

|      | 2.9.a                                                                          | 42  |

|      | 2.9.b                                                                          | 42  |

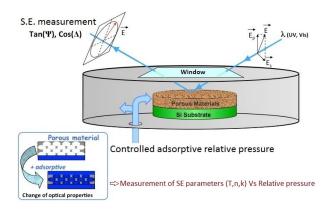

| 2.10 | Ellipsometric porosimetry working principle [118]. S.E. stands for Standard    |     |

|      | Ellipsometry.                                                                  | 42  |

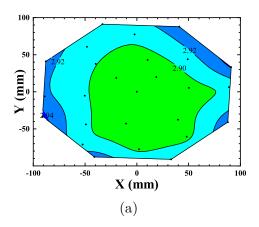

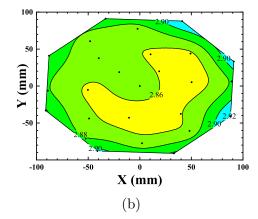

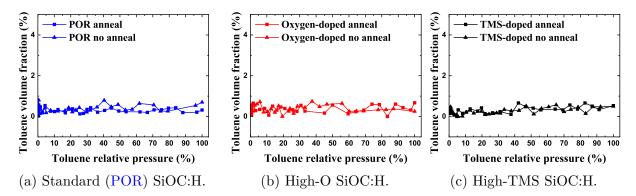

| 2.11 | Ellipsometric porosimetry measurements on different uncapped SiOC:H            |     |

|      | materials                                                                      | 43  |

|      | 2.11.a Standard (POR) SiOC:H                                                   | 43  |

|      | 2.11.b High-O SiOC:H                                                           | 43  |

|      | 2.11.c High-TMS SiOC:H                                                         | 43  |

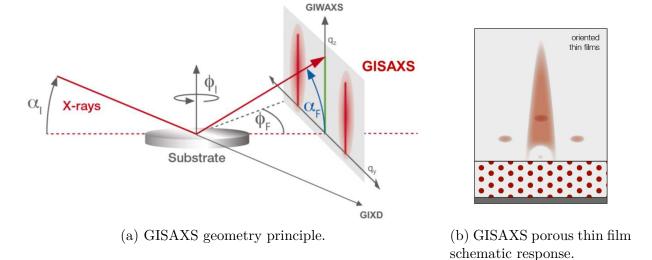

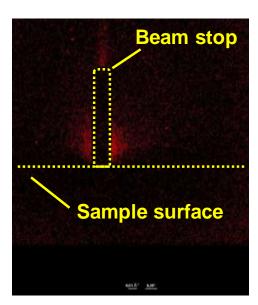

| 2.12 | GISAXS working principle and porous thin film schematic response $[121]$ .     | 44  |

|      | 2.12.a GISAXS geometry principle                                               | 44  |

|      | 2.12.b GISAXS porous thin film schematic response                              | 44  |

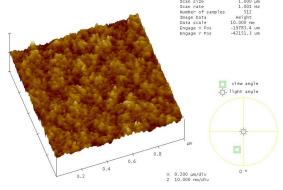

| 2.13 | Topological images of uncapped POR SiOC:H materials                            | 44  |

|      | 2.13.a SEM view of the as-deposited POR SiOC:H material surface                | 44  |

|      | 2.13.b AFM view of the as-deposited POR SiOC:H material surface                | 44  |

| 9 14 | 10h GISAXS measurements on uncapped POR SiOC:H materials                       | 45  |

|         | 2.14.a GISAXS raw signal of the as-deposited POR SiOC:H material                                                                      | 45         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------|------------|

|         | 2.14.b GISAXS raw signal of the annealed POR SiOC:H material                                                                          | 45         |

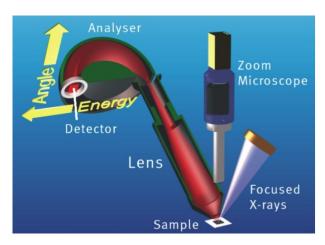

| 2.15    | Parallel Angle Resolved XPS working principle (without any sample tilt) [127]                                                         | 46         |

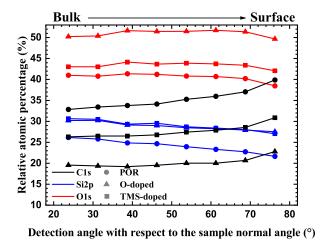

| 2.16    | As deposited SiOC:H materials chemical composition depth profiles mea-                                                                |            |

|         | sured by PARXPS. Higher angles correspond to photelectrons emitted by                                                                 |            |

|         | the sample surface                                                                                                                    | 47         |

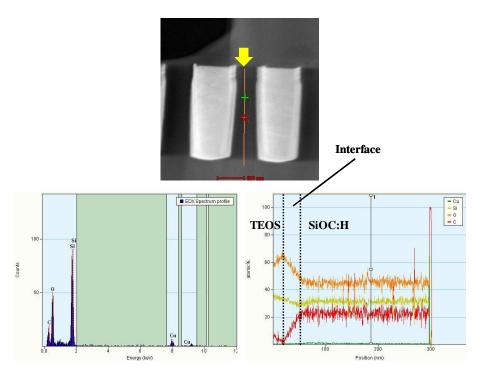

| 2.17    | TEM view of a cross-section perpendicular to the integrated copper line                                                               |            |

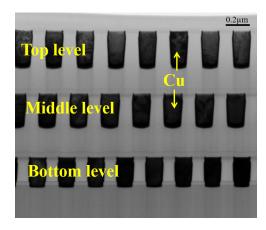

|         | (top). Left: spectrum recorded at the green cross. Right: EDX profile                                                                 |            |

|         | along the orange line on the TEM view (top)                                                                                           | 48         |

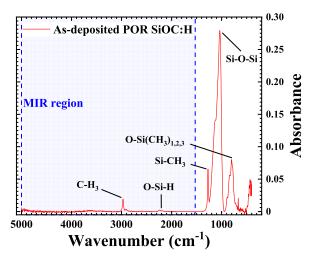

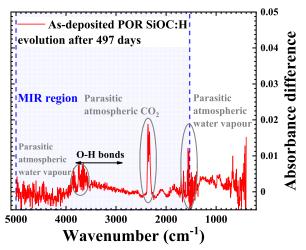

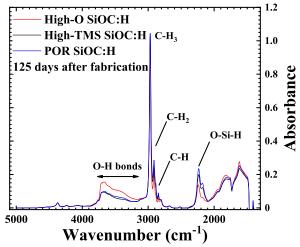

| 2.18    | FTIR spectrum and evolution of as-deposited SiOC:H blanket material                                                                   | 50         |

|         | 2.18.a FTIR spectrum of as deposited SiOC:H blanket material                                                                          | 50         |

|         | 2.18.b Evolution of as-deposited SiOC:H blanket material absorbance after                                                             |            |

|         | 497 days at room relative humidity and temperature measured with                                                                      | <b>E</b> 0 |

| 2.10    | FTIR                                                                                                                                  | 50         |

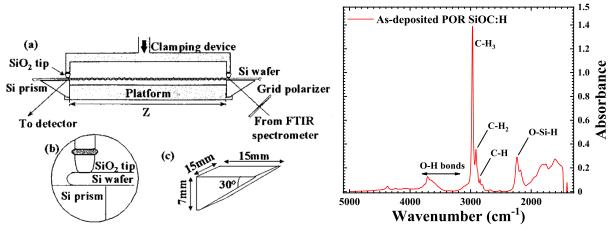

| 2.19    | FTIR and MIR spectra of as-deposited SiOC:H blanket material 2.19.a Working principle of Multiple Internal Reflections (MIR) measure- | 51         |

|         | ment setup [135]                                                                                                                      | 51         |

|         | 2.19.b MIR spectrum of as deposited SiOC:H blanket material                                                                           | 51         |

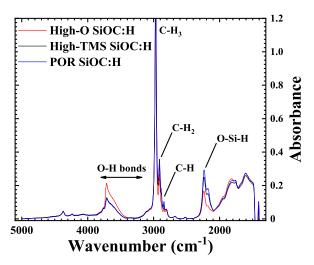

| 2.20    |                                                                                                                                       | 52         |

|         | 2.20.a Stacked MIR spectra of three variants of the SiOC:H dielectric ma-                                                             | Ŭ <b>-</b> |

|         | terial deposited on silicon and capped by silicon nitride (not visible                                                                |            |

|         | in spectrum).                                                                                                                         | 52         |

|         | 2.20.b Stacked MIR spectra of three variants of the SiOC:H dielectric ma-                                                             |            |

|         | terial deposited on silicon after 125 days of storage in ambient at-                                                                  |            |

|         | mosphere                                                                                                                              | 52         |

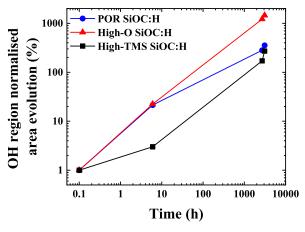

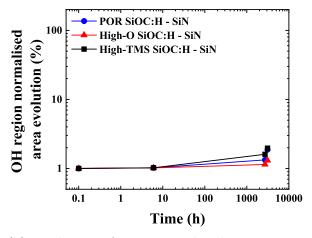

| 2.21    | Evolution of moisture-related peak area of three variant SiOC:H blanket                                                               |            |

|         | materials.                                                                                                                            | 53         |

|         | 2.21.a Evolution of moisture-related region normalised area of three un-                                                              | ۲۹         |

|         | capped SiOC:H blanket materials, stored in ambient atmosphere.                                                                        | 53         |

|         | 2.21.b Evolution of moisture-related region normalised area of three capped SiOC:H blanket materials, stored in ambient atmosphere    | 53         |

|         | 5100.11 blanket materials, stored in ambient atmosphere                                                                               | 00         |

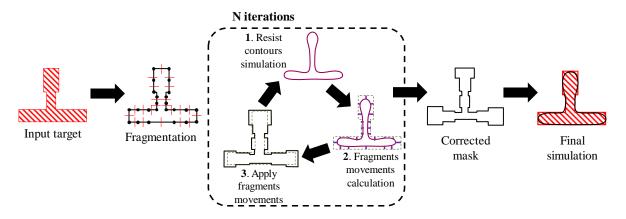

| 3.1     | Main C2M boolean operations performed on CAD layout                                                                                   | 56         |

| 3.2     | Example of OPC relevance on simple structures                                                                                         | 57         |

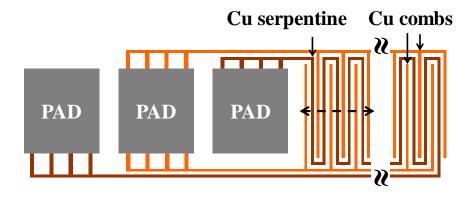

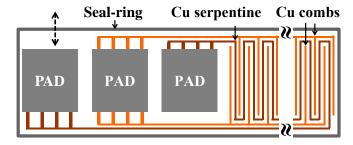

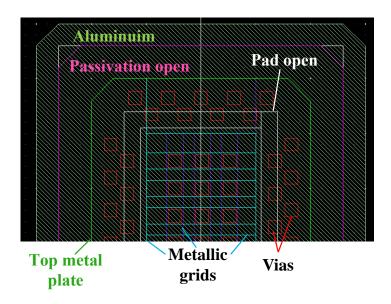

| 3.3     | Schematic top view of the elementary structures                                                                                       | 58         |

|         | 3.3.a Illustration of the elementary electrical test structure                                                                        | 58         |

|         | 3.3.b Illustration of alternated horizontal and vertical blocs                                                                        | 58         |

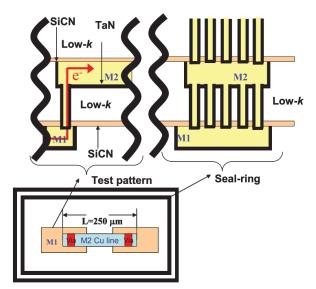

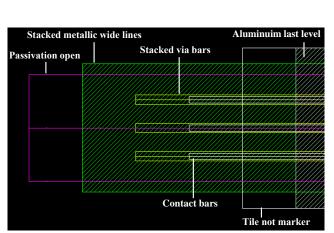

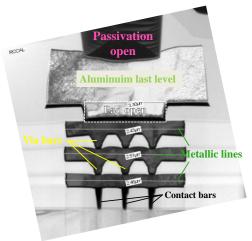

| 3.4     | Electrical test structure compatible seal-ring                                                                                        | 60         |

|         | 3.4.a Description of the seal-ring CAD layout                                                                                         | 60         |

|         | 3.4.b Perpendicular cross-section of a test structure seal-ring                                                                       | 60         |

|         | 3.4.c Example of use of seal-ring in test structures. The dashed arrow                                                                | 0.0        |

| 0.5     | corresponds to the cross-section in figure (b)                                                                                        | 60         |

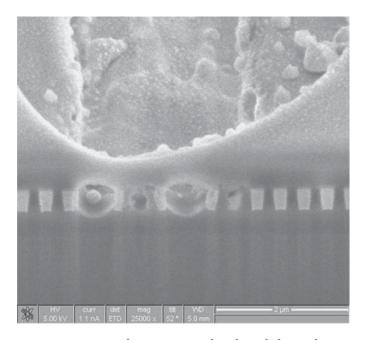

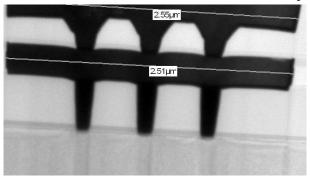

| 3.5     | Cross-sections before (3.6 a) and after (3.6 b) aluminium etching correction                                                          | 62<br>63   |

| . 1 1 1 | A TOSS-SECTIONS DEFORE LA ORICIANO RILECTA DELL'ADENTAMINAMINA DECENIO COTTOCTION                                                     | 11.5       |

|      | 5.0.a               | etch                                                                                          | 63  |

|------|---------------------|-----------------------------------------------------------------------------------------------|-----|

|      | 3.6.b               | Perpendicular cross-section of a test structure seal-ring after aluminium etching correction. | 63  |

| 3.7  | Contac              | ct level cross-section in the same direction than the seal-ring before                        |     |

| J.,  |                     | 3.7.b and after 3.7.c the contact etch recipe shape regularity improve-                       |     |

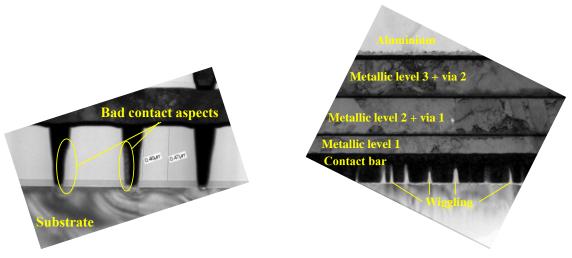

|      |                     |                                                                                               | 64  |

|      | 3.7.a               | Bad contact aspect before recipe modification                                                 | 64  |

|      | 3.7.b               | Contact bar wiggling in seal-ring longitudinal section before recipe modification.            | 64  |

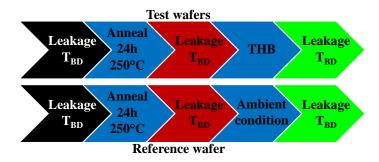

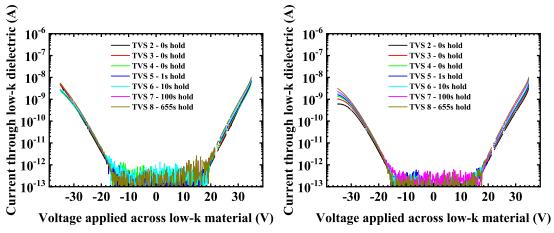

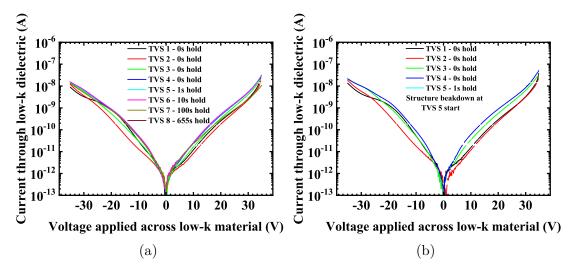

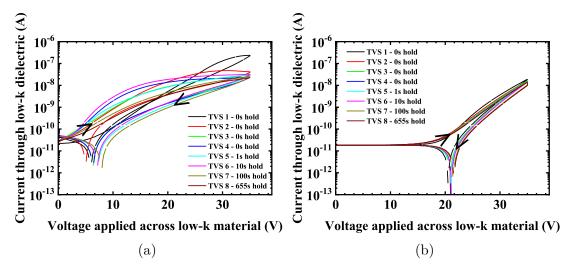

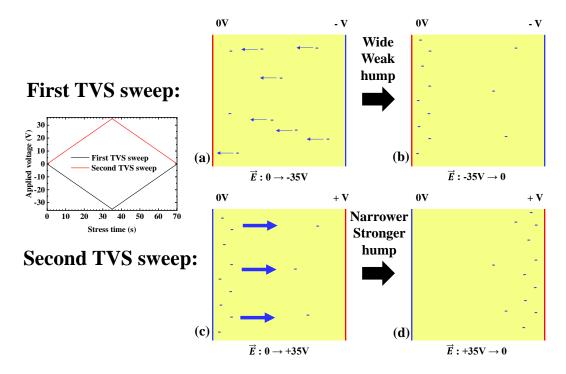

|      | 3.7.c               | Good contact aspect after recipe optimisation                                                 | 64  |