# Exploration, conception et mise en œuvre de circuit de pilotage pour micro-écrans à LED GaN

Yoann Seauve

#### ▶ To cite this version:

Yoann Seauve. Exploration, conception et mise en œuvre de circuit de pilotage pour micro-écrans à LED GaN. Micro et nanotechnologies/Microélectronique. Université Grenoble Alpes [2020-..], 2020. Français. NNT: 2020GRALT069. tel-03206480

### HAL Id: tel-03206480 https://theses.hal.science/tel-03206480

Submitted on 23 Apr 2021

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité: NANO ELECTRONIQUE ET NANO TECHNOLOGIES

Arrêté ministériel : 25 mai 2016

Présentée par

#### Yoann SEAUVE

Thèse dirigée par **Gilles Sicard**, Ingénieur de recherche, HDR, CEA-LETI, encadrée par **Margaux Vigier**, Ingénieure de recherche, CEA-LETI, et **Thomas Pilloix**, Ingénieur de recherche, CEA-LETI.

préparée au sein du Laboratoire d'Electronique et des Technologies de l'Information, CEA-LETI dans l'école doctorale EEATS

# Exploration, conception et mise en œuvre de nouveaux circuits de pilotage pour micro-écrans à LED GaN.

Thèse soutenue publiquement le **8 décembre 2020**, devant le jury composé de :

#### Pr. Raphaël CLERC

Laboratoire Hubert Curien – Université Jean Monnet de Saint-Etienne, Président du jury

#### Pr. Dominique GINHAC

Laboratoire ImViA - Université de Bourgogne, Rapporteur

#### Pr Wilfried UHRING

Laboratoire ICube - UMR 7357 - Université de Strasbourg, Rapporteur

#### Dr. François Templier

Ingénieur de recherche HDR, CEA-LETI, Grenoble, France, Examinateur

#### Dr. Gilles Sicard

Ingénieur de recherche HDR, CEA-LETI, Grenoble, France, Directeur de thèse

#### Mme. Margaux Vigier

Ingénieure de recherche, CEA-LETI, Grenoble, France, Invitée encadrante

#### M. Thomas Pilloix

Ingénieur de recherche, CEA-LETI, Grenoble, France, Invité encadrant

#### Dr. Rose-marie SAUVAGE

Responsable Innovation, Agence de l'Innovation de Défense, Invitée

### Remerciements

Je remercie sincèrement Gilles Sicard, Margaux Vigier, et Thomas Pilloix pour l'encadrement de ces travaux de thèse. Leurs conseils éclairés et remarques toujours constructives m'ont été précieux pour mener à bien cette thèse.

Merci à Raphael Clerc, Dominique Ginhac, et Wilfried Uhring de m'avoir fait l'honneur de constituer mon jury de thèse, respectivement en tant que président de jury et rapporteurs. Merci également à François Templier d'avoir pris part à ce jury en tant qu'examinateur.

Je remercie Fabrice Guellec de m'avoir accueilli au sein du laboratoire L3I durant ces trois années. Merci également à tous les membres du laboratoire permanents et non permanents, pour leur accueil chaleureux, leur bonne humeur, et l'aide qu'ils ont pu m'apporter à tous niveaux.

Enfin merci à tous les autres qu'il me serait difficile de nommer sans oublis, mais qui ont participé de près ou de loin, et qui m'ont permis d'arriver à ce résultat.

# Table des matières

| Ta | ıble d | es figures                                     | vii |

|----|--------|------------------------------------------------|-----|

| In | itrod  | uction générale                                | ix  |

| I  | Int    | roduction                                      | 1   |

| 1  | Fon    | ctionnement d'un micro-écran                   | 2   |

|    | 1.1    | Structure générale                             | 2   |

|    | 1.2    | Différentes technologies de micro-écrans       | 3   |

|    |        | 1.2.1 LCD                                      | 4   |

|    |        | 1.2.2 DMD                                      | 5   |

|    |        | 1.2.3 LBS                                      | 6   |

|    |        | 1.2.4 LED                                      | 7   |

|    | 1.3    | Mécanisme de contrôle d'un micro-écran à LEDs  | 7   |

|    |        | 1.3.1 Matrices passives                        | 7   |

|    |        | 1.3.2 Matrices actives                         | ç   |

| 2  | Cas    | d'emplois typiques des différents micro-écrans | 11  |

|    | 2.1    | Projection                                     | 11  |

|    | 2.2    | Réalité virtuelle                              | 12  |

|    | 2.3    | Réalité augmentée                              | 14  |

| 3  | Dio    | des électro luminescentes (LEDs)               | 16  |

|    | 3.1    | Physique de la LED                             | 16  |

|    |        | 3.1.1 Phénomène d'électroluminescence          | 16  |

|    |        | 3.1.2 Jonctions                                | 17  |

|    |        | 3.1.3 Puits quantiques                         | 18  |

|    | 3.2    | Fabrication des LEDs GaN                       | 19  |

|    |        | 3.2.1 Structure de la LED GaN                  | 19  |

|    |        | 3.2.2 Méthode de production                    | 19  |

|    | 3.3    | Comparaison des technologies LED               | 21  |

|    |        | 3.3.1 LEDs organiques                          | 21  |

i Table des matières

|    |      |         | LEDs GaN                                                               | 22<br>24 |

|----|------|---------|------------------------------------------------------------------------|----------|

| II | Mi   | cro-éc  | crans à LEDs GaN pour réalité augmentée                                | 26       |

| 4  | Ach  | emine   | ment des données                                                       | 28       |

|    | 4.1  | Débit   | de données nécessaire                                                  | 28       |

|    | 4.2  | Défin   | ition de régions d'intérêt                                             | 29       |

|    | 4.3  | Métho   | ode de sous résolution                                                 | 31       |

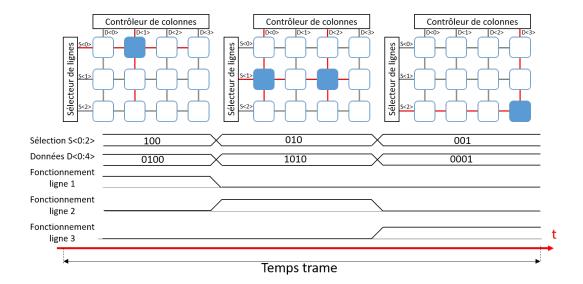

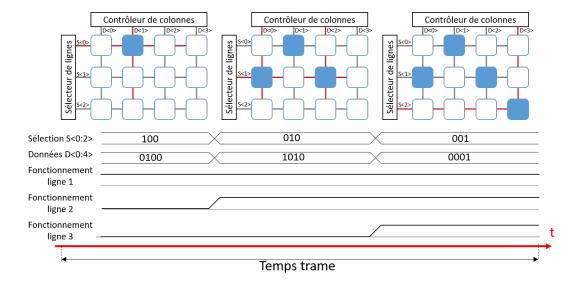

|    |      | 4.3.1   | Fonctionnement proposé pour les contrôleurs de lignes et de colonnes . | 31       |

|    |      | 4.3.2   | Sélecteur simple                                                       | 33       |

|    |      | 4.3.3   | Sélecteur de colonnes avec mémorisation                                | 35       |

|    |      | 4.3.4   | Conclusion                                                             | 37       |

| 5  | Arcl | hitectu | res de circuits pixels                                                 | 39       |

|    | 5.1  | Pilota  | ge en tension                                                          | 39       |

|    | 5.2  | Pilota  | ge courant                                                             | 42       |

|    |      | 5.2.1   | Programmation en tension                                               | 43       |

|    |      | 5.2.2   | Programmation en courant                                               | 44       |

|    | 5.3  | Pilota  | ge PWM                                                                 | 47       |

| 6  | Dév  | eloppe  | ement d'un circuit pixel faible pas                                    | 49       |

|    | 6.1  | Objec   | tif et ressources technologiques                                       | 49       |

|    |      | 6.1.1   | Circuit de pilotage compact                                            | 49       |

|    |      | 6.1.2   | Technologie CoolLed                                                    | 50       |

|    |      | 6.1.3   | Modèles de composants utilisés                                         | 53       |

|    | 6.2  |         | ecture du circuit pixel                                                | 53       |

|    |      | 6.2.1   | Pilotage PWM avec source de courant                                    | 53       |

|    |      | 6.2.2   | Interrupteur 5V                                                        | 55       |

|    |      | 6.2.3   | Source de courant                                                      | 57       |

|    | 6.3  | Signal  | PWM                                                                    | 62       |

|    |      | 6.3.1   | Signal analogique                                                      | 63       |

|    |      | 6.3.2   | Signal numérique                                                       | 66       |

|    |      | 6.3.3   | Mémoire dans le pixel                                                  | 69       |

|    |      | 6.3.4   | Solution retenue                                                       | 73       |

|    | 6.4  | Implé   | mentation                                                              | 75       |

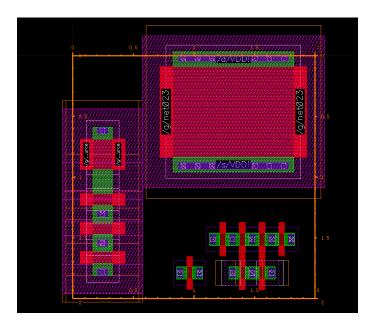

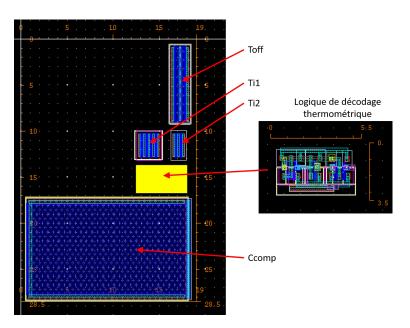

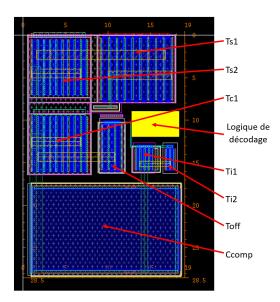

|    |      | 6.4.1   | Pixel 3D                                                               | 76       |

|    |      | 6.4.2   | Implémentation en matrice                                              | 83       |

| 7  | Con  | clusio  | n                                                                      | 91       |

Table des matières ii

| II | A <sub>I</sub> | oplication de transmission de données                         | 93  |

|----|----------------|---------------------------------------------------------------|-----|

| 8  | Intr           | oduction                                                      | 94  |

| 9  | Con            | nmunication en lumière visible (VLC)                          | 96  |

|    | 9.1            | Principe de fonctionnement                                    | 96  |

|    | 9.2            | Modulation OFDM                                               | 97  |

|    | 9.3            | Émetteurs mono LED                                            | 102 |

|    | 9.4            | Émetteur matricé                                              | 103 |

| 10 | Con            | ception d'un circuit pixel binaire                            | 105 |

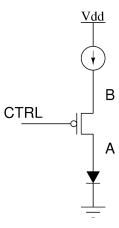

|    | 10.1           | LEDs utilisées                                                | 106 |

|    | 10.2           | Dynamique de tension LED                                      | 110 |

|    |                | 10.2.1 Extinction totale                                      | 110 |

|    |                | 10.2.2 Extinction partielle                                   | 112 |

|    | 10.3           | Constitution du circuit pixel                                 | 114 |

|    |                | 10.3.1 Source de courant                                      | 114 |

|    |                | 10.3.2 Mécanisme d'extinction                                 | 117 |

|    | 10.4           | Accélération de l'allumage                                    | 119 |

|    |                | 10.4.1 Principe de fonctionnement                             | 119 |

|    |                | 10.4.2 Dimensionnement                                        | 123 |

|    |                | 10.4.3 Limitations                                            | 125 |

|    |                | 10.4.4 Gestion du temps de rechargement                       | 126 |

| 11 | Fon            | ctionnement matriciel                                         | 129 |

|    | 11.1           | Sélection des pixels à allumer                                | 130 |

|    |                | 11.1.1 Groupes de puissance de 2                              | 130 |

|    |                | 11.1.2 Pixels indépendants                                    | 132 |

| 12 | Dim            | ensionnement du circuit pixel                                 | 134 |

|    | 12.1           | Méthode de dimensionnement                                    | 136 |

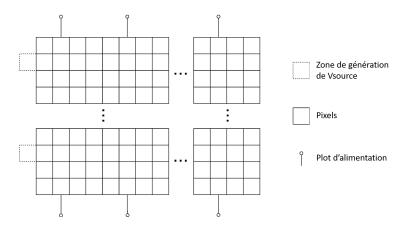

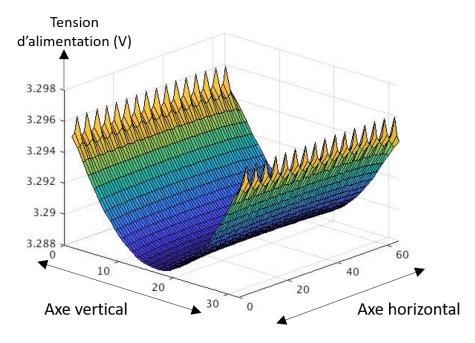

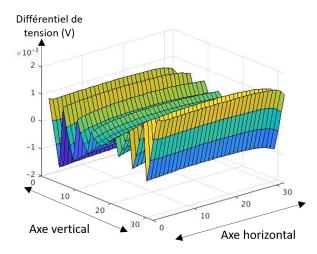

|    | 12.2           | Alimentation                                                  | 137 |

|    | 12.3           | Estimation de la linéarité                                    | 139 |

|    |                | 12.3.1 Méthode employée                                       | 139 |

|    |                | 12.3.2 Résultats                                              | 140 |

|    | 12.4           | Pixel retenu                                                  | 145 |

| 13 | Inte           | rférences entre pixels                                        | 147 |

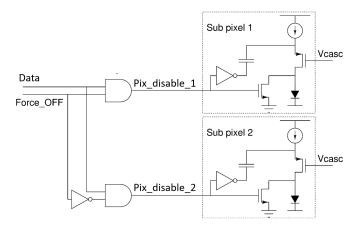

|    | 13.1           | Utilisation de sous-pixels – principe du control en ping-pong | 149 |

| 14 | Con            | clusion                                                       | 151 |

| iii                        | Table des matières |

|----------------------------|--------------------|

| Conclusion et perspectives | 153                |

| Publications               | 157                |

| Bibliographie              | 167                |

# **Table des figures**

| 1.1  | Décomposition d'une image en pixels                                               | 2  |

|------|-----------------------------------------------------------------------------------|----|

| 1.2  | Micro-écran comparé à une pièce de monnaie                                        | 3  |

| 1.3  | Constitution générale d'un micro-écran LCD de type transmissif                    | 4  |

| 1.4  | Schéma de principe d'une cellule à cristaux liquides                              | 5  |

| 1.5  | Structure d'un micro-écran DMD                                                    | 6  |

| 1.6  | Structure d'un micro-écran LBS                                                    | 6  |

| 1.7  | Structure d'un micro-écran à LEDs                                                 | 7  |

| 1.8  | Structure d'un écran LED à matrice passive                                        | 8  |

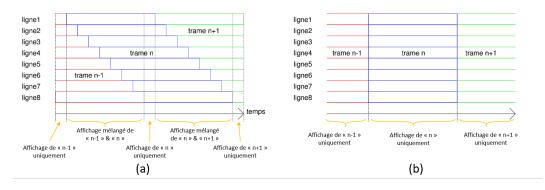

| 1.9  | Balayage de type "rolling shutter" d'un écran passif                              | 9  |

| 1.10 | Structure d'un écran LED à matrice active                                         | 9  |

| 1.11 | Balayage de type "rolling shutter" d'un écran actif                               | 10 |

| 2.1  | Exemple de projecteur en fonctionnement (a), et structure du système (b)          | 11 |

| 2.2  | Exemple de casques de réalité virtuelle (a), et structure d'un tel système (b)    | 12 |

| 2.3  | Exemple de lunettes de réalité augmentée                                          | 14 |

| 2.4  | Structure d'un système de réalité augmentée utilisant une lame semi réfléchis-    |    |

|      | sante (a), ou un guide d'onde (b)                                                 | 15 |

| 3.1  | Description d'une homo jonction                                                   | 18 |

| 3.2  | Diagramme de bande simplifié d'une double hétérojonction, avec formation          |    |

|      | d'un puit quantique                                                               | 19 |

| 3.3  | Illustration simplifiée du procédé de production des LEDs GaN en technologie      |    |

|      | planaire                                                                          | 20 |

| 3.4  | Exemple de micro-écrans OLED présentés par [37] et [11]                           | 22 |

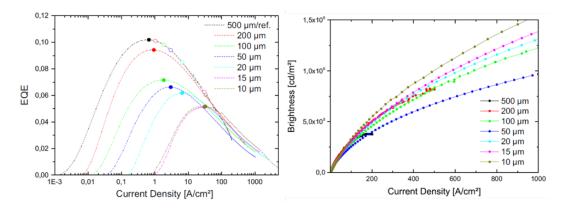

| 3.5  | Efficacité quantique extérieure et luminance pour des LEDs de différents di-      |    |

|      | mensions [42]                                                                     | 23 |

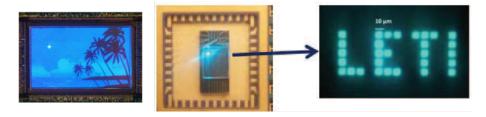

| 3.6  | Exemple de micro-écrans à LEDs GaN présentés par [4] et [45]                      | 24 |

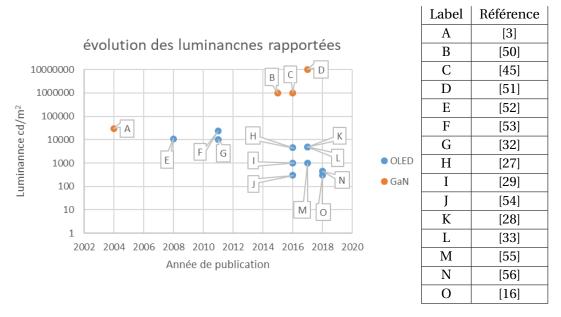

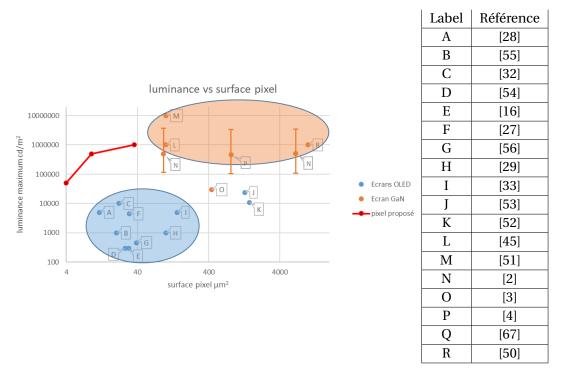

| 3.7  | Evolution des luminances rapportées dans la littérature                           | 27 |

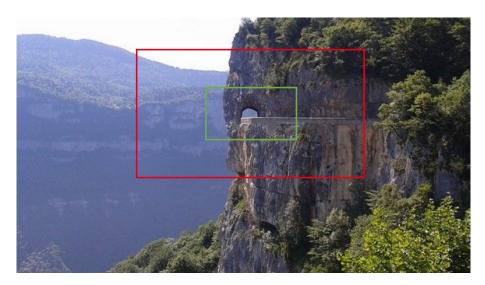

| 4.1  | Affichages classique (a), et avec une définition réduite (b) pour la vision péri- |    |

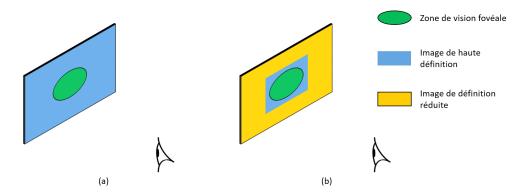

|      | phérique, par rapport au positionnement de la zone de vision fovéale              | 30 |

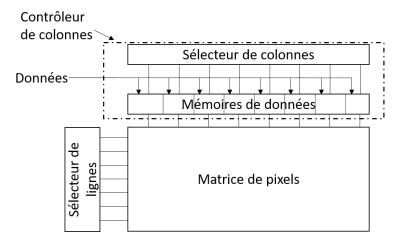

| 4.2  | Schéma de principe du mécanisme de distribution des données                       | 31 |

Table des figures

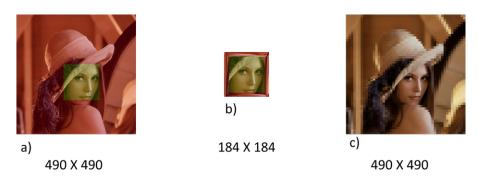

| 4.3  | Compression et décompression d'une image par sous résolution des régions             |    |

|------|--------------------------------------------------------------------------------------|----|

|      | d'intérêt moindre                                                                    | 32 |

| 4.4  | Répartition de 4 données sous résolues sur 7 pixels                                  | 32 |

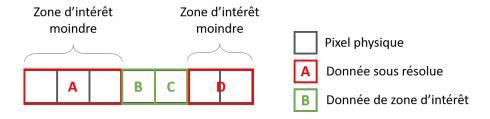

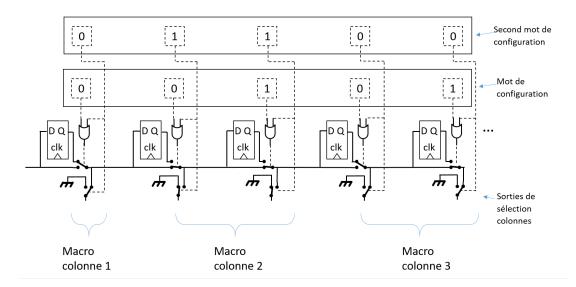

| 4.5  | Sélecteur de colonnes permettant la définition de macro colonnes                     | 33 |

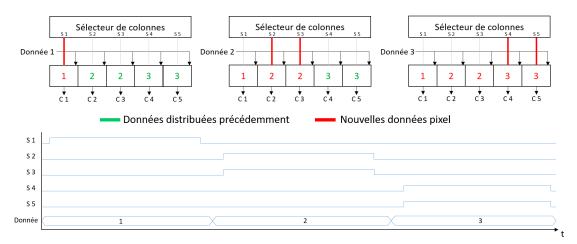

| 4.6  | Fonctionnement d'un contrôleur de colonnes permettant la définition de ma-           |    |

|      | cro colonnes                                                                         | 34 |

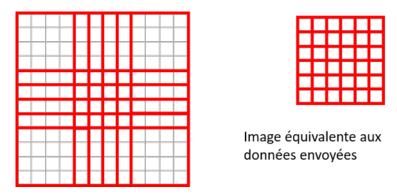

| 4.7  | Affichage d'une image multi résolution avec une configuration par image              | 34 |

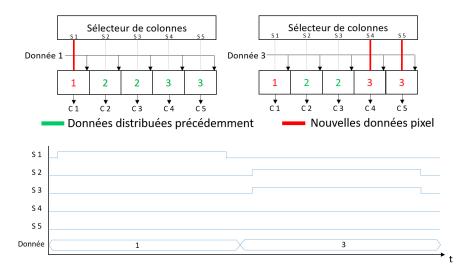

| 4.8  | Affichage d'une image multi résolution avec une nouvelle configuration par ligne     | 35 |

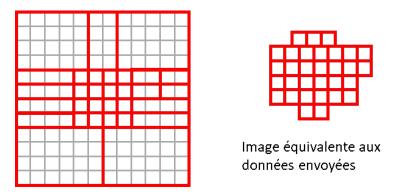

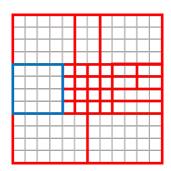

| 4.9  | Découpage en macro pixels impossible avec des copies de lignes entières              | 35 |

| 4.10 | Affichage d'une image compressée avec mémorisation inter lignes                      | 36 |

| 4.11 | Sélecteur de colonnes avec fonction de mémorisation                                  | 36 |

| 4.12 | Image sous résolue nécessitant un sélecteur avec mémorisation pour l'affichage       |    |

|      | de la seconde ligne                                                                  | 37 |

| 4.13 | Fonctionnement d'un contrôleur de colonnes avec fonction de mémorisation             |    |

|      | de données                                                                           | 37 |

| 4.14 | Exemple de définition de sous résolution                                             | 38 |

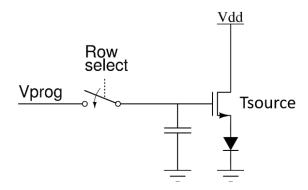

| 5.1  | Structure d'un circuit pixel avec pilotage en tension                                | 40 |

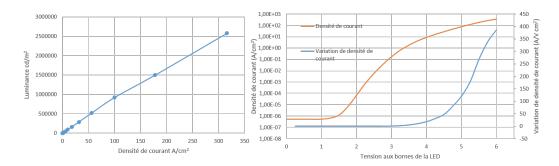

| 5.2  | Caractéristiques électro-optiques d'une LED GaN                                      | 41 |

| 5.3  | Contrôle en tension avec alimentations résistives                                    | 41 |

| 5.4  | Structure d'un circuit pixel avec pilotage en courant et programmation en tension    | 43 |

| 5.5  | Structure d'un circuit pixel avec pilotage en courant et programmation en courant    | 45 |

| 5.6  | Pixel à programmation en courant durant les phases de programmation (a), et          |    |

|      | fonctionnement (b)                                                                   | 45 |

| 5.7  | Séquence d'affichage PWM d'une trame                                                 | 47 |

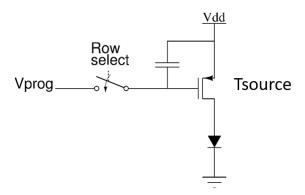

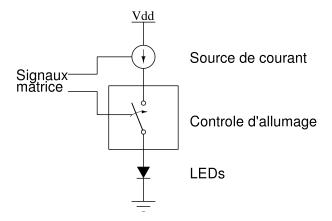

| 5.8  | Exemple de structure d'un circuit de pilotage PWM avec source de courant             | 48 |

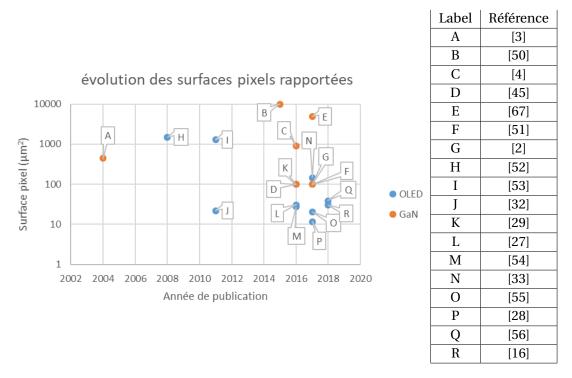

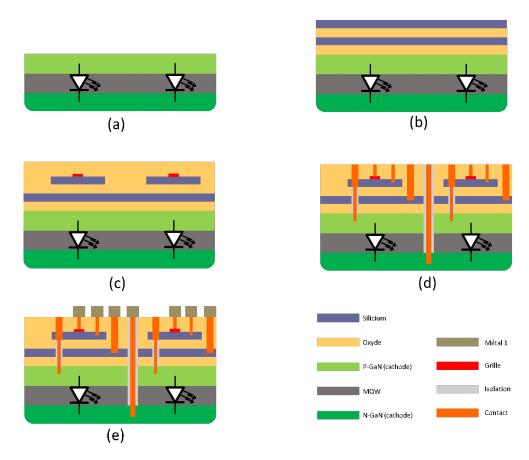

| 6.1  | Evolution de l'encombrement des pixels rapportés dans la littérature                 | 50 |

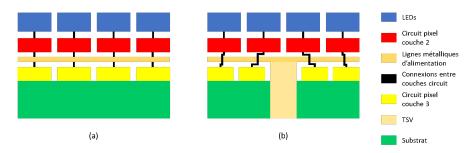

| 6.2  | Vue en coupe simplifiée des principales étapes d'association LED/circuit dans        |    |

|      | un procédé CoolLed                                                                   | 51 |

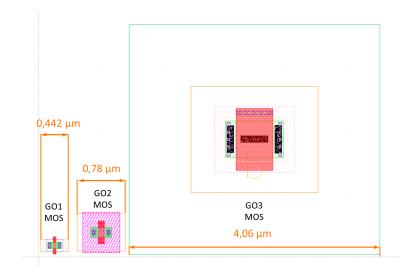

| 6.3  | Transistors GO1, GO2, et GO2 en dimensions minimum                                   | 53 |

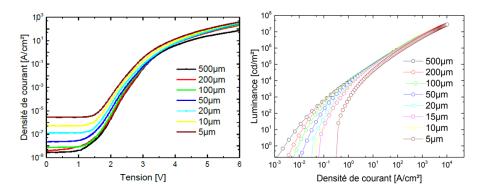

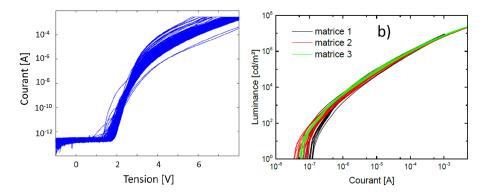

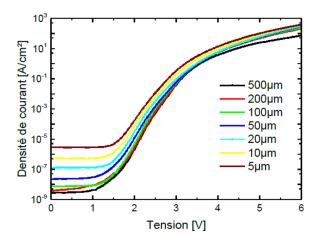

| 6.4  | Caractéristiques de LEDs GaN planaires [17]                                          | 54 |

| 6.5  | Dispersion des caractéristiques électro-optiques pour un ensemble de LEDs            |    |

|      | GaN [17]                                                                             | 54 |

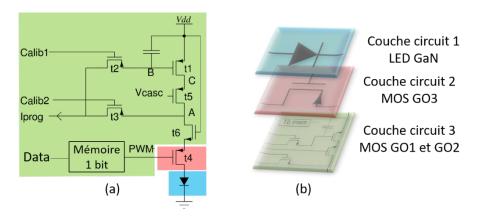

| 6.6  | Structure de circuit de pilotage pwm utilisée pour le circuit pixel 3D               | 55 |

| 6.7  | Domaines d'alimentations raccordés par la masse                                      | 56 |

| 6.8  | Domaines d'alimentations raccordés par $V_{DD}$                                      | 56 |

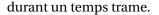

| 6.9  | Evolution du courant généré par t1 en fonction de sa tension grille source           | 59 |

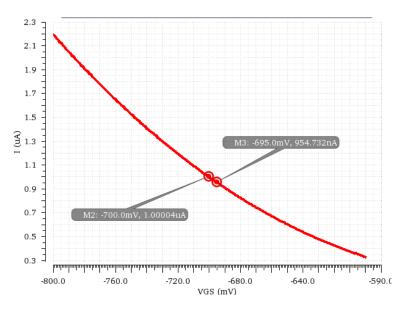

| 6.10 | Fuites de grilles en fonction de la tension $V_{gs}$ pour des transistors GO1 et GO2 | 60 |

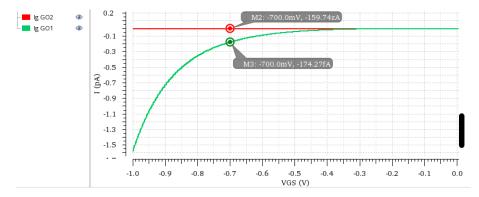

| 6.11 | Fuites d'interrupteurs fermés en fonction de la tension Vds pour des transistors     |    |

|      | GO1 et GO2                                                                           | 60 |

| 6.12 | Programmation en courant avec différentes valeurs de capacité de stockage .          | 62 |

| 6.13 | Représentation schématique de la séquence de control des pixels d'une matrice        | 63 |

**Table des figures** vi

| 6.14 | Pixel à PWM analogique, architecture générale (a),chronogramme de génération PWM (b) | 64  |

|------|--------------------------------------------------------------------------------------|-----|

| 6.15 | Implémentation d'un générateur PWM sans amplificateur différentiel                   | 64  |

| 6.16 | Courant de fuite pour un transistor GO2 échantillonnant un signal avec une           | 0 1 |

| 0.10 | dynamique de 1 V                                                                     | 66  |

| 6.17 | Pixel PWM avec mémorisation sur 1 bit                                                | 67  |

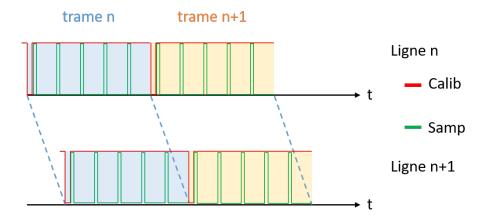

| 6.18 | Séquence de contrôle pixel PWM avec un rafraichissement par LSB                      | 67  |

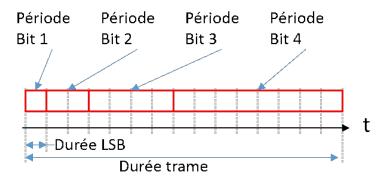

| 6.19 | Exemple de découpage en période de types BCM pour un signal codé sur 4 bits          | 68  |

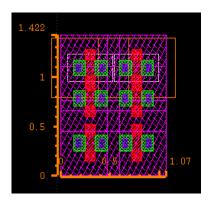

| 6.20 | Estimation d'encombrement d'un point mémoire 6t en GO2                               | 69  |

| 6.21 | Estimation d'encombrement d'un point mémoire 6t en GO1                               | 70  |

| 6.22 | Courant pixel en fonction du potentiel du signal PWM                                 | 71  |

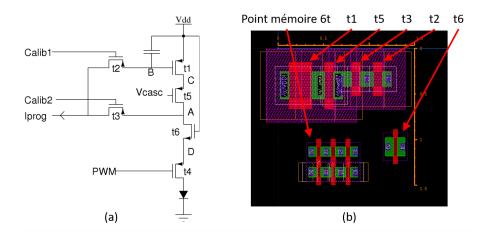

| 6.23 | Circuit pixel acceptant le signal d'un point mémoire GO1 (a), estimation d'en-       |     |

|      | combrement (b)                                                                       | 71  |

| 6.24 | Fonctionnement du pixel avec point mémoire GO1 lors d'une extinction                 | 72  |

| 6.25 | Principe de répartition des données dans une mémoire partagée par deux pixels        | 73  |

| 6.26 | Séquence d'écritures pour affichage BCM à flux constant                              | 74  |

| 6.27 | Chronogramme des signaux de contrôle durant un temps LSB, pour un signal             |     |

|      | BCM à flux constant                                                                  | 75  |

| 6.28 | Circuit pixel retenu et points de fonctionnement retenus pour l'implémentation       | 76  |

| 6.29 | Répartition du pixel sur 3 niveaux, découpage du circuit (a), constitution du        |     |

|      | circuit 3D (b)                                                                       | 77  |

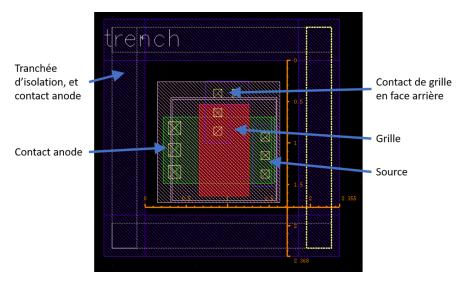

| 6.30 | Couche circuit 2 avec un transistor G03 en dimensions minimales                      | 77  |

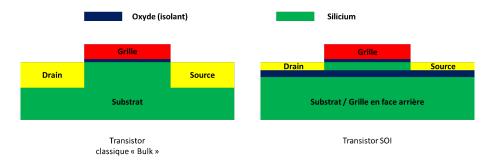

| 6.31 | Comparaison de la structure des transistors Bulk et SOI                              | 78  |

| 6.32 | Comparaison des courants de drain d'un transistor GO2 avec une back-gate             |     |

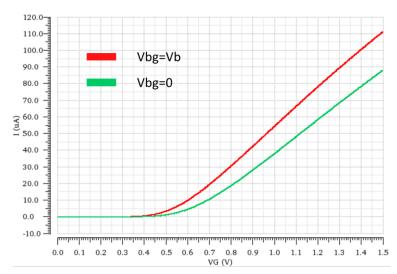

|      | connectée à la grille ou à la masse                                                  | 78  |

| 6.33 | Seconde couche circuit avec différentes dimensions du transistor G03                 | 79  |

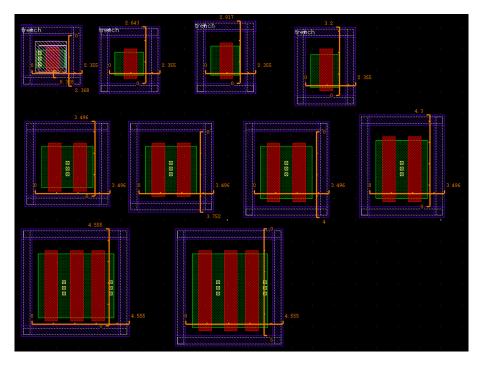

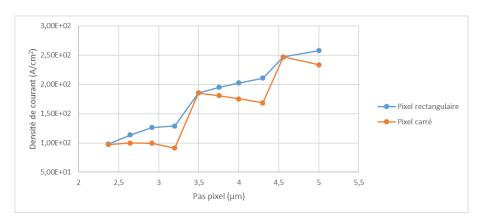

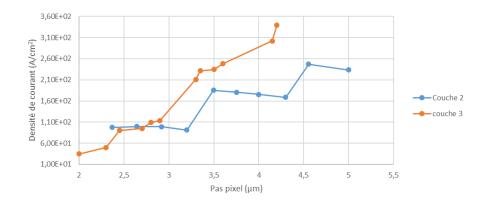

| 6.34 | Densité de courant permise par la couche 2 pour différents pas pixel                 | 80  |

| 6.35 | Encombrement couche 3 avec une capacité de stockage mixte MOS / MOM,                 |     |

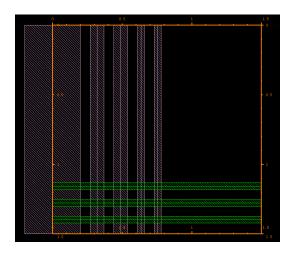

|      | pour un circuit en dimensions minimum                                                | 81  |

| 6.36 | Troisième couche circuit dimensionnée pour différents courants                       | 82  |

| 6.37 | Densité de courant permise par chaque couche circuit en fonction du pas pixel        | 82  |

| 6.38 | Estimation d'encombrement de routage des signaux au travers de la matrice .          | 83  |

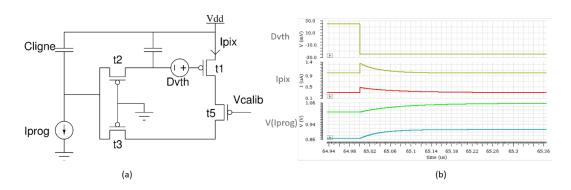

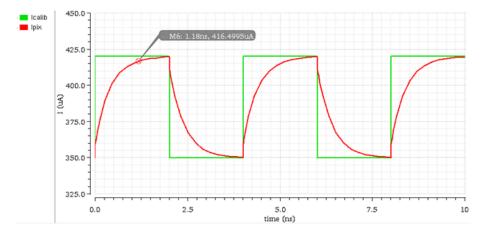

| 6.39 | Etude d'établissement de $I_{pix}$ durant la calibration d'un pixel : circuit simulé |     |

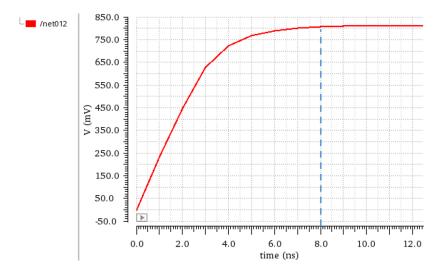

|      | (a), résultats de simulation (b)                                                     | 85  |

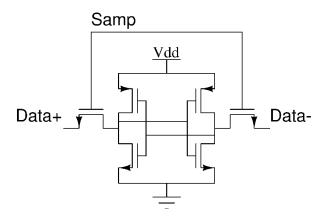

| 6.40 | Structure classique d'une cellule mémoire 6t                                         | 85  |

| 6.41 | Etablissement du signal "Data" distribué sur une colonne de 1080 pixels, avec        |     |

|      | une source de tension idéale                                                         | 86  |

| 6.42 | Représentation d'un barreau métallique                                               | 87  |

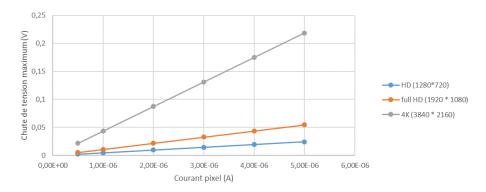

| 6.43 | Chute de tension maximum sur $V_{cathode}$ pour un pas pixel de 2 $\mu$ m            | 88  |

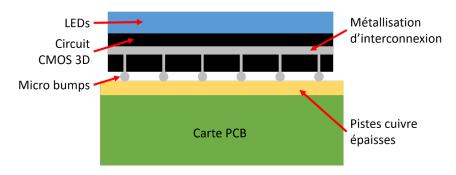

| 6.44 | Association du micro-écran à une carte PCB                                           | 89  |

| 6.45 | Construction schématique du circuit en trois couches sans TSV (a), et avec (b)       | 89  |

vii Table des figures

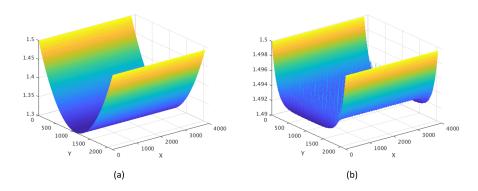

| 6.46  | Evolution de la tension d'alimentation au travers de la matrice sans reprise d'alimentation (a), et avec (b)                       | 90  |

|-------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.1   | Performances classiquement rapportées pour des micro-écrans GaN et OLED, comparées aux performances simulées pour le pixel proposé | 92  |

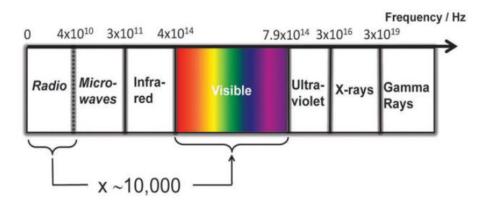

| 8.1   | Composition du spectre électro-magnétique [82]                                                                                     | 95  |

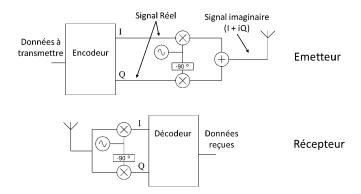

| 9.1   | Schéma de principe d'un émetteur/récepteur utilisant une modulation IQ                                                             | 97  |

| 9.2   | Schéma de principe d'un ensemble émetteur/récepteur de type VLC                                                                    | 97  |

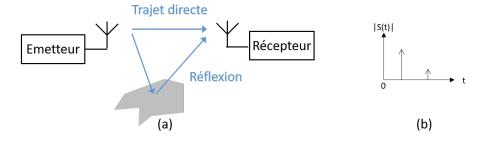

| 9.3   | Illustration d'une transmission au travers d'un canal présentant une réflexion                                                     |     |

|       | (a), réponse impulsionnelle du canal (b)                                                                                           | 98  |

| 9.4   | Sommation du signal transmis et d'un écho                                                                                          | 98  |

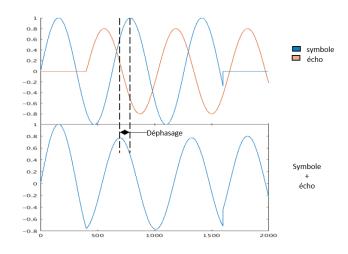

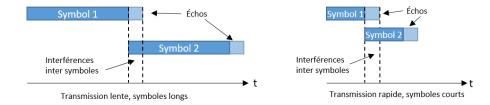

| 9.5   | Influence de la durée des symboles sur l'imprtance des interférences                                                               | 99  |

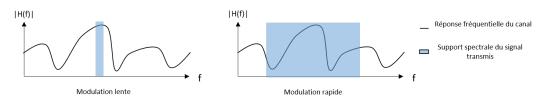

| 9.6   | Influence de la réponse du canal de transmission en fonction de la vitesse de                                                      |     |

|       | cette dernière                                                                                                                     | 99  |

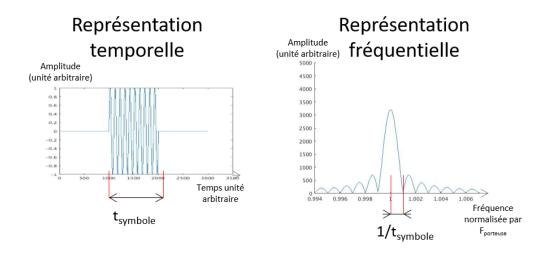

| 9.7   | Formes temporelle et spectrale d'un symbole sinusoidat de durée $T_{symbole}$                                                      | 100 |

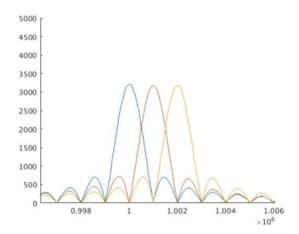

| 9.8   | Superposition des spectres de différents sous-canaux d'une transmission OFDM                                                       |     |

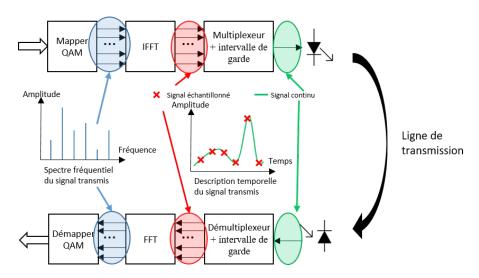

| 9.9   | Structure d'un ensemble émetteur et récepteur utilisant l'OFDM                                                                     | 101 |

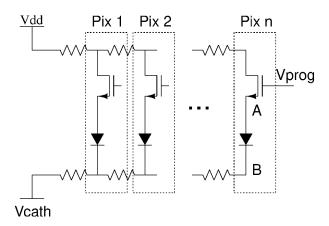

| 10.1  | Structure générale du pixel VLC                                                                                                    | 106 |

| 10.2  | Caractéristique électrique des LEDs de différentes dimensions [17]                                                                 | 107 |

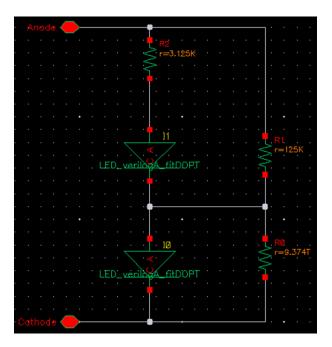

| 10.3  | Modèle électrique de jonction d'une LED GaN de 8 $\mu$ m                                                                           | 108 |

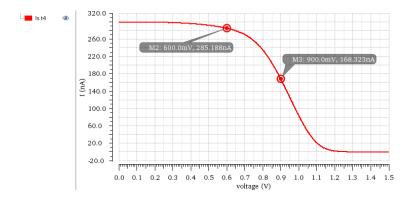

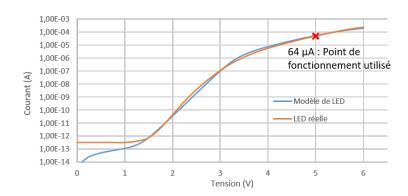

| 10.4  | Comparaison du courant prédit par le model de LED de 8 $\mu$ m avec celui mesuré                                                   | 108 |

| 10.5  | Deux cas extrêmes pour lesquels le courant de la capacité parasite ne traverse                                                     |     |

|       | pas la résistance série (A), ou la traverse dans son intégralité (B)                                                               | 109 |

| 10.6  |                                                                                                                                    | 109 |

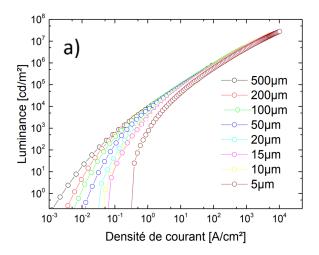

| 10.7  | Caractéristiques d'émission des LEDs de différentes dimensions [17]                                                                | 110 |

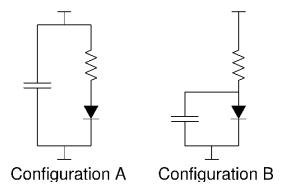

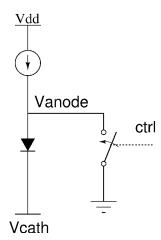

| 10.8  | Pixel à extinction totale                                                                                                          | 111 |

| 10.9  | •                                                                                                                                  | 111 |

| 10.10 | Tensions appliquées aux bornes de la LED pour une extinction complète (a), et                                                      |     |

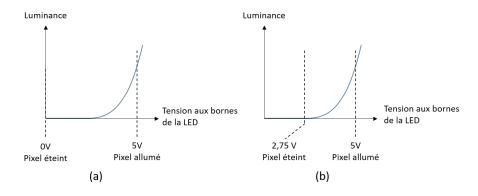

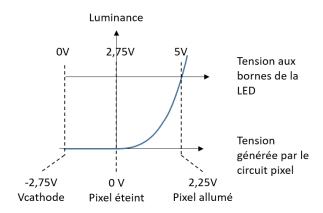

|       | un extinction partielle (b)                                                                                                        | 112 |

| 10.11 | Pilotage des LEDs en extinction partielle avec une tension de cathode distincte                                                    |     |

| 10.10 | de la masse du circuit                                                                                                             | 113 |

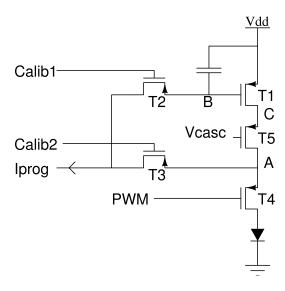

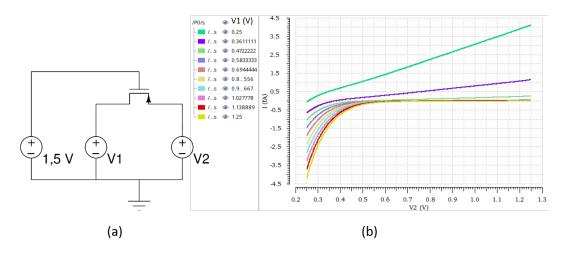

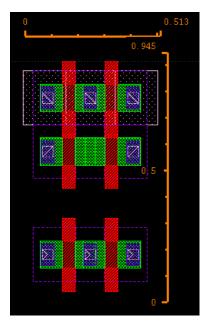

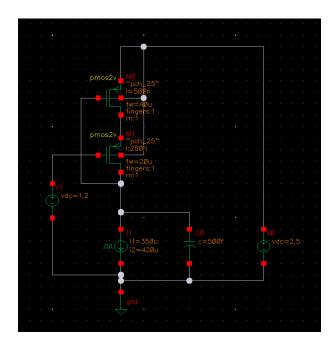

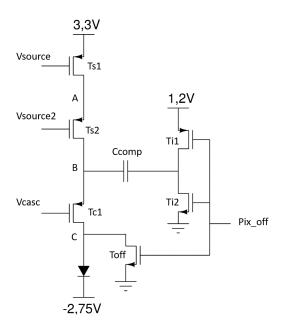

|       | Circuit d'évaluation de programmation d'une source de courant                                                                      | 115 |

|       |                                                                                                                                    | 115 |

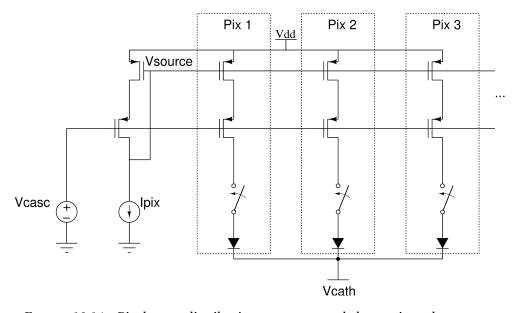

|       | Pixels avec distribution permanente de la consigne de courant                                                                      | 116 |

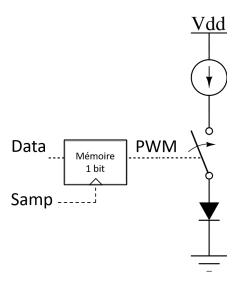

|       |                                                                                                                                    | 118 |

|       | Mécanisme d'extinction partielle du pixel                                                                                          |     |

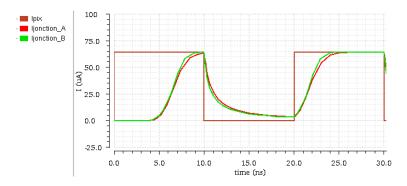

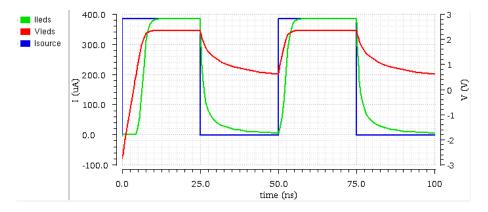

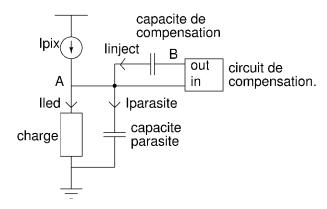

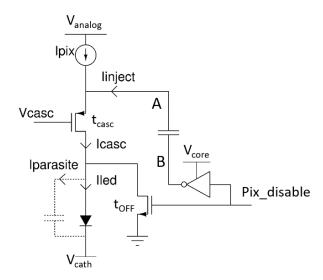

|       |                                                                                                                                    | 120 |

|       | Schéma de principe du pixel avec le mécanisme de compensation proposé                                                              |     |

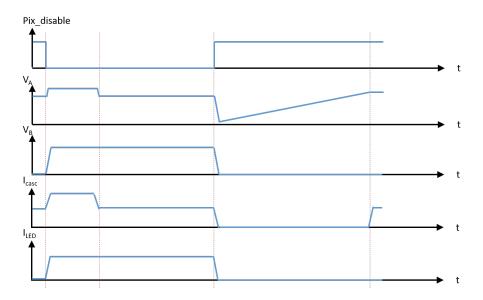

| 10.19 | Fonctionnement du pixel proposé sur un cycle allumage extinction                                                                   | 123 |

Table des figures viii

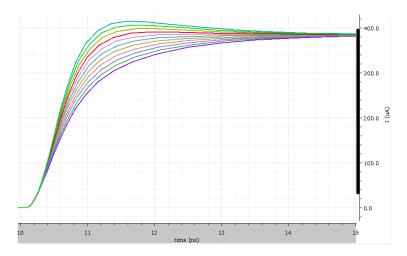

| 10.20 | Courant $I_{LED}$ lors d'une phase d'allumage pour des valeurs $C_{comp}$ allant de 800 |      |

|-------|-----------------------------------------------------------------------------------------|------|

|       | fF à 1pf                                                                                | 125  |

| 10.21 | Extinction du pixel, et rechargement du condensateur de compensation $\ \ \ldots$       | 126  |

| 10.22 | Circuit de rechargement                                                                 | 126  |

| 10.23 | Evolution du potentiel du nœud A durant le rechargement du condensateur de              |      |

|       | compensation, avec un circuit idéal                                                     | 127  |

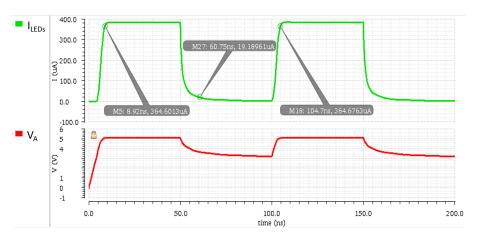

| 10.24 | Impact de la transconductance du circuit de rechargement sur l'évolution du             |      |

|       | potentiel $V_A$                                                                         | 128  |

| 11.1  | Fonctionnements schématiques des rafraichissements "rolling shutter" (a) et             |      |

|       | "global shutter" (b)                                                                    | 129  |

| 11.2  | Exemple de répartition des pixels par groupes en puissance de 2, pour une               |      |

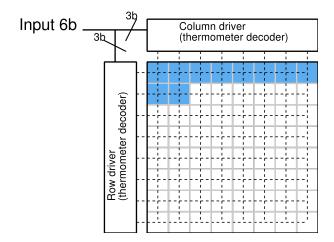

|       | entrée sur 6 bits                                                                       | 131  |

| 11.3  | Exemple de répartition thermométrique des pixels allumés pour une entrée                |      |

|       | sur 6 bits                                                                              | 132  |

| 12.1  | Schéma électrique du circuit pixel                                                      | 135  |

| 12.2  | Estimation d'encombrement des éléments de taille fixe du pixel                          | 135  |

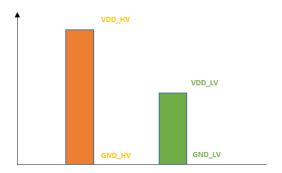

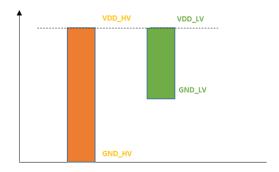

| 12.3  | Positionnement des plots d'alimentation par rapport à la matrice de LEDs                | 137  |

| 12.4  | Évolution de la tension d'alimentation au travers de la matrice de pixels               | 138  |

| 12.5  | Différence de tension d'alimentation entre les pixels et leur référence de couran       | t139 |

| 12.6  | Circuit d'évaluation de $gm_{Ts1}$ et $\sigma$ I                                        | 140  |

| 12.7  | Tensions appliquées aux différents transistors dimensionnés                             | 141  |

| 12.8  | Encombrement du circuit pixel avec $V_A = 2.7 \text{ V} \dots \dots \dots \dots \dots$  | 141  |

| 12.9  | Évaluation de la linéarité de conversion avec $V_A$ = 2,8 V                             | 142  |

| 12.10 | Évaluation de la linéarité de conversion avec $V_A$ = 2,9 V                             | 143  |

| 12.11 | Évaluation de la linéarité de conversion avec $V_A = 3 \text{ V} \dots \dots \dots$     | 144  |

| 12.12 | Évaluation de la linéarité de conversion avec $V_A$ = 3.1 V                             | 145  |

| 12.13 | Fonctionnement du circuit pixel avec le dimensionnement retenu                          | 145  |

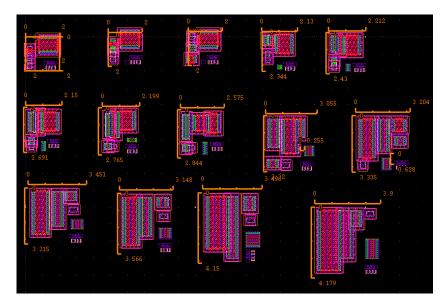

| 12.14 | Layout préliminaire du circuit pixel VLC retenu                                         | 146  |

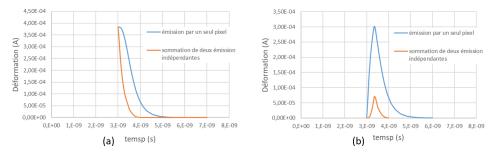

| 13.1  | Sommation de deux symboles "1" indépendants                                             | 147  |

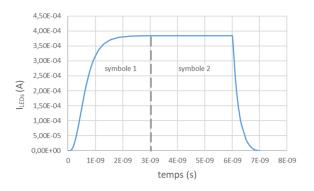

| 13.2  | Émission de deux symboles "1" successifs par un même pixel                              | 148  |

| 13.3  | Différentes fenêtres d'analyse associées à un symbole par le récepteur                  | 148  |

| 13.4  | Déformation du signal émis par rapport à un symbole isolé, avec un début de             |      |

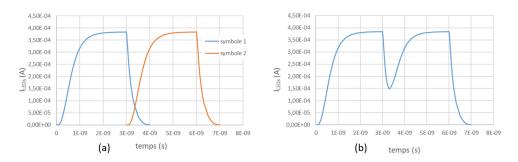

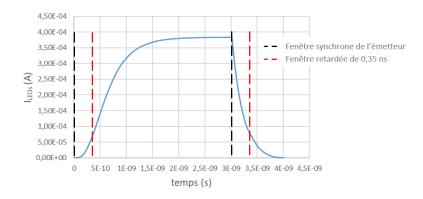

|       | fenêtre d'analyse à 3 ns (a) et 3,35 ns (b)                                             | 149  |

| 13.5  | Structure et contrôle d'un pixel comprenant deux sous-pixels                            | 149  |

# Introduction générale

Les diodes électroluminescentes (LEDs) sont utilisées dans divers domaines d'applications depuis déjà plusieurs décennies. Tout d'abord essentiellement cantonnées à la constitution de témoins lumineux, ces diodes sont aujourd'hui utilisées dans des domaines variés, tels que l'éclairage, les télécommunications, ou encore l'affichage. Les avancées récentes dans le domaine de la fabrication de LEDs Inorganiques permettent la production de LEDs GaN à l'échelle micrométrique. Ces composants optiques, jusqu'ici produits uniquement dans des dimensions importantes, peuvent être associés à un circuit de pilotage CMOS afin de produire des micro-écrans. Les micro-LEDs produites à partir de GaN atteignent de très hautes luminances, avec un meilleur rendement que leurs équivalents organiques, et une vitesse de commutation bien supérieure aux autres technologies LEDs généralement utilisées à l'échelle micrométrique. De tels dispositifs constituent un élément essentiel pour la production d'équipements de réalité augmentée par exemple, qui nécessitent des solutions d'affichages à la fois compactes et de forte luminance.

Cependant, les LEDs GaN présentent des caractéristiques électriques spécifiques différentes de celles des autres technologies LED, et doivent être placées dans des régimes de fonctionnement particuliers pour atteindre leurs performances maximales. Ainsi, les méthodes de pilotage couramment utilisées avec d'autres technologies LED telles que OLED s'avèrent peu adaptées pour exploiter le potentiel de ces nouveaux composants optiques. Ce travail a pour objectif le développement de circuits de pilotage pixel adaptés aux micro-LEDs GaN, autant par le type de pilotage mis en place que par un encombrement compatible avec la surface des LEDs employées.

Cette thèse se découpe en trois volets distincts. Une première partie est dédiée à la présentation des LEDs et au fonctionnement général des différentes familles de micro-écrans. Une seconde partie porte sur l'étude d'une solution permettant la production de micro-écrans à base de LEDs GaN avec un pas pixel réduit. Enfin une troisième partie est dédiée à l'utilisation du micro-écran comme émetteur pour de la communication en lumière visible, et à l'étude d'un micro-écran dédié à ce type d'usage.

# **Introduction Partie I**

# Chapitre 1

### Fonctionnement d'un micro-écran

#### 1.1 Structure générale

Un micro-écran constitue un dispositif d'affichage. Son rôle est de reproduire de la manière la plus fidèle possible, une image ou succession d'images qui lui est fournie. Afin de décrire le fonctionnement d'un micro-écran, il est nécessaire de s'intéresser dans un premier temps à l'image que ce dernier doit afficher.

Afin de décrire une image et pouvoir la transmettre à un écran, on considère cette dernière comme étant constituée d'un ensemble fini de points. Comme illustré en Figure 1.1, à chacun de ces points, aussi nommés pixels, correspond une valeur de luminance. Une valeur chrominance (définition de la couleur) leur est aussi associée dans le cas d'une image couleur. On parle alors de la "définition" de l'image comme le nombre de pixels utilisés pour la décrire dans les axes vertical et horizontal, et de la "résolution" pour définir le nombre de pixels par unité de longueur. Cependant, on constate une confusion entre ces deux paramètres dans le langage courant, le terme résolution étant régulièrement employé pour désigner la définition.

FIGURE 1.1 - Décomposition d'une image en pixels

D'une manière analogue à l'échantillonnage spatial permettant d'obtenir un ensemble de

pixels à partir d'une image continue, une scène mouvante est décrite par une succession d'images fixes appelées "trames". Le taux de rafraichissement désigne alors le nombre d'images utilisées par unité de temps, pour constituer un signal vidéo. Une résolution et un taux de rafraichissement suffisants pour dépasser les limites de distinction de la vision humaine, permettent de donner à l'observateur une illusion de continuité de l'image aussi bien dans l'espace que dans le temps.

Afin de générer une image ainsi décrite, un écran présente une surface émettant de la lumière, elle-même décomposée en une multitude de pixels. Ces pixels constituent un ensemble de sources lumineuses dont l'émission est contrôlée pour correspondre aux points de l'image qui leurs sont associés. L'état des pixels est mis à jour de manière régulière afin de permettre l'affichage de vidéos. Cette construction générale est commune aux écrans et micro-écrans. Ces derniers, tels qu'illustré en Figure 1.2, présentent des dimensions très réduites. Le micro-écran se distingue de l'écran classique par son faible encombrement, mais surtout par le fait qu'il est associé à un système optique plutôt qu'observé directement par l'utilisateur. Bien qu'un micro-écran comporte une surface capable d'afficher une image, son association à un système optique permet à l'image telle qu'observée par l'utilisateur de se former à un endroit de l'espace distinct de la surface de l'écran. En raison du grossissement dû à ce mode d'affichage, les micro-écrans présentent généralement une résolution beaucoup plus importante que les écrans classiques.

FIGURE 1.2 – Micro-écran comparé à une pièce de monnaie

#### 1.2 Différentes technologies de micro-écrans

Il existe une multitude de technologies différentes permettant l'obtention d'une matrice de sources lumineuses indépendantes, chacune mettant en œuvre des mécanismes qui lui sont propres. Nous allons ici nous intéresser aux principales technologies utilisées dans le cas des micro-écrans.

#### 1.2.1 LCD

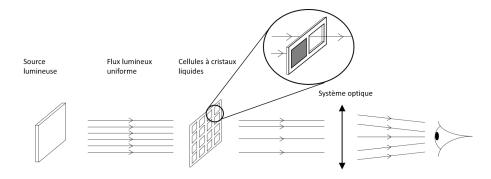

Un écran à cristaux liquides, plus connu sous le nom LCD (Liquid Crystal Display), fait partie des technologies d'écrans dits "à modulation de lumière". Dans ce type d'écran, la source de lumière et le moyen de moduler la luminance des différents pixels constituent deux éléments séparés. La Figure 1.3 illustre de manière schématique le fonctionnement d'un écran LCD transmissif. Une source lumineuse diffuse est partagée par tous les pixels de l'écran, et est associée à une matrice de cellules permettant pour chaque pixel de bloquer une part contrôlable de la lumière émise.

FIGURE 1.3 - Constitution générale d'un micro-écran LCD de type transmissif

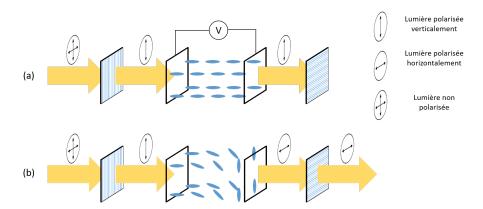

Les cellules à cristaux liquides, utilisées pour absorber une part contrôlable de la lumière les atteignant, exploitent la propriété de biréfringence du matériau utilisé. De tels cristaux peuvent modifier l'orientation de polarisation rectiligne d'un rayon lumineux les traversant, et l'importance de la déviation peut être modifiée en appliquant un champ électrique aux cristaux.

La Figure 1.4 illustre le mécanisme permettant le contrôle de l'opacité d'une cellule à cristaux liquides. L'élément modulant est constitué de deux filtres polarisants entre lesquels est inséré un cristal liquide entouré de deux électrodes transparentes. Une polarisation rectiligne de direction connue est imposée à la lumière par le premier filtre polarisant qu'elle traverse. Lorsque les rayons lumineux traversent le cristal, la direction de cette polarisation est modifiée dans des proportions dépendant de la tension appliquée entre les électrodes. Enfin, le second filtre polarisant absorbe une part de la lumière dépendant de l'orientation de la polarisation de cette dernière. Dans le cas présenté en Figure 1.4 (a), la lumière est polarisée verticalement après avoir traversé le premier filtre polarisant. En raison de l'état du cristal liquide, induit par la tension aplliquée à ses bornes, le rayon lumineux le traverssant ne subit aucune modification de sa polarisation. Lorsqu'elle rencontre le second filtre polarisateur, la lumière toujours polarisée verticalement est absorbée. Le pixel est donc éteint. La Figure 1.4 (b) présente une situation pour laquelle l'absence de tension appliquée au cristal liquide place ce dernier dans une position différente. La lumière le traversant voit sa polarisation varier de 90°. Le rayon lumineux rencontre alors le second filtre avec une polarisation horizontale et n'est pas absorbé. Le pixel est ici allumé.

FIGURE 1.4 – Schéma de principe d'une cellule à cristaux liquides

Les écrans LCD sont répartis entre deux familles principales, les écrans "transmissifs" traversés par la lumière telle qu'illustré en Figure 1.4, et les écrans "réflectifs" réfléchissant la lumière lorsqu'elle n'est pas absorbée. La structure du micro-écran de type "transmissif" découle directement de la miniaturisation des écrans LCD de grandes dimensions, et impose la construction de la matrice de cellules à cristaux liquides sur un support transparent. Dans le cas des micro-écrans "réflectifs", la source lumineuse et le système optique sont placés du même côté de la matrice d'éléments modulants. L'emploi d'une surface réfléchissante à la place d'un des filtres polarisants permet à la lumière qui n'est pas arrêtée par la cellule d'être réfléchie en direction du système optique. Cette seconde structure impose l'emploi d'un système optique plus complexe, mais permet la construction des cellules à cristaux liquides sur un substrat opaque.

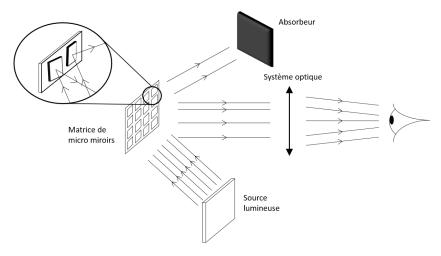

#### 1.2.2 DMD

Un micro-écran DMD (Digital Micromirror Device), comme son nom l'indique, fait usage de micro miroirs pour réaliser un affichage. Il s'agit d'un type de micro-écrans qui fait lui aussi partie des écrans à modulation de lumière, et dont le principe de fonctionnement s'avère proche de celui d'un écran LCD réflectif. Comme l'illustre la Figure 1.5, une source lumineuse éclaire une matrice d'éléments modulants constitués de micro miroirs dont l'inclinaison est contrôlable. La modulation du niveau de luminance de chaque pixel est obtenue grâce à l'orientation des micro miroirs correspondants, de manière à réfléchir la lumière vers le système optique pour un pixel allumé, ou bien vers une surface absorbante pour un pixel éteint. Afin d'obtenir un niveau de luminance intermédiaire, le miroir oscille entre les deux positions.

FIGURE 1.5 – Structure d'un micro-écran DMD

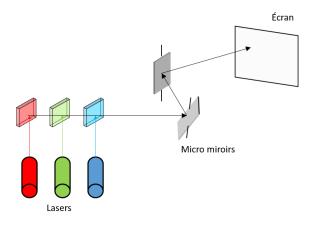

#### 1.2.3 LBS

Un système d'affichage LBS (Laser Beam Scanner) emploi aussi des micro miroirs afin de former une image. Il ne présente cependant pas une structure matricée, et un même ensemble de micro miroirs est utilisé pour afficher successivement les différents pixels d'une image. Comme l'illustre la Figure 1.6 La source lumineuse est formée d'émetteurs LASER dont la puissance est modulable. Le rayon lumineux issu de cette source est dirigé vers un ensemble de micro miroirs orientables. Les deux micro miroirs représentés dans l'exemple permettent de scanner l'écran selon les axes vertical et horizontal afin d'adresser successivement les différents pixels de l'image. La puissance des sources laser est continuellement adaptée en fonction des luminance et couleur souhaitées au point de l'image adressé par les micro miroirs.

FIGURE 1.6 – Structure d'un micro-écran LBS

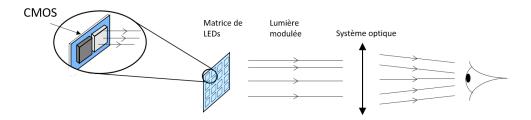

#### 1.2.4 LED

Les écrans à LEDs fonctionnent sur un principe différent, il s'agit d'écrans dits auto émissifs. La lumière est émise directement au niveau de chaque pixel, et non par une source extérieure. Comme l'illustre la Figure 1.7, le micro-écran à LEDs est composé d'une matrice de LEDs, correspondant chacune à un pixel de l'image à afficher. A chaque trame, l'alimentation fournie aux différentes LEDs est adaptée, pour que la lumière émise corresponde à l'image à afficher.

FIGURE 1.7 – Structure d'un micro-écran à LEDs

Il existe plusieurs technologies de LEDs utilisées pour réaliser des micro-écrans. Les principales sont les LEDs organiques (OLED) et les LEDs à base de nitrure de galium (GaN). Ces technologies LED seront présentées plus en détails et comparées par la suite, dans le chapitre 3.3.

#### 1.3 Mécanisme de contrôle d'un micro-écran à LEDs

Afin d'assurer la fonction d'affichage d'images d'un micro-écran, il est nécessaire de contrôler indépendamment la luminance de chacun de ses pixels. Selon la technologie utilisée, un circuit permettant de contrôler le comportement d'un pixel peut être placé sous chacun d'entre eux. Cependant il reste nécessaire de distribuer les données à afficher depuis le point d'entrée du signal vidéo vers chacun des pixels. Des mécanismes de distribution similaires peuvent être employés pour les différents types d'écrans, cependant nous nous intéressons ici en particulier aux mécanismes mis en œuvre dans des micro-écrans à LEDs.

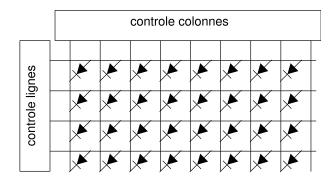

Un micro-écran, selon sa définition, peut contenir plusieurs millions de pixels. Controller le micro-écran depuis sa périphérie grâce à un signal dédié à chaque pixel est alors impossible, et la mise en place d'une forme de multiplexage des signaux de commande est indispensable. Dans une large majorité des cas, les données à afficher sont distribuées dans la matrice une ligne après l'autre, il s'agit d'un pilotage dit "rolling shutter".

#### 1.3.1 Matrices passives

Dans un écran à matrice passive, la zone d'émission est constituée uniquement des LEDs, aucun circuit de pilotage individuel ne leur est associé. Des lignes métalliques sont utilisées pour relier les anodes et cathodes par lignes et par colonnes, comme illustré en Figure 1.8. Ces

FIGURE 1.8 – Structure d'un écran LED à matrice passive

lignes métalliques constituent à la fois le moyen de contrôler et d'alimenter les LEDs. L'allumage d'une LED est en effet déclenché en alimentant simultanément la ligne et la colonne lui correspondant [1]. Sur ce type d'écran, comme l'illustre la Figure 1.9, seule une ligne de l'image est affichée à chaque instant. Les lignes de la matrice sont alimentées successivement, tandis que l'alimentation des différentes colonnes dépend du contenu à afficher sur la ligne sélectionnée. Ce mode de fonctionnement permet un contrôle relativement simple des pixels depuis le bord de la matrice. Cependant, plusieurs lignes de pixels ne peuvent pas fonctionner simultanément, et le temps maximum d'allumage d'un pixel durant une trame correspond à  $T_{ligne}$ , défini par l'équation 1.1. L'utilisation d'une matrice passive limite donc grandement

$$T_{ligne} = \frac{T_{trame}}{Nb_{lignes}} \tag{1.1}$$

$T_{ligne}$  : Durée de sélection d'une ligne de pixels

$T_{trame}$  : Durée de la trame

$Nb_{lignes}$  : Nombre de lignes de pixels que comporte l'écran

le temps d'allumage des pixels, or la luminance moyenne d'un pixel, définie par l'équation 1.2, dépend directement de cette durée. Une matrice passive présente donc une luminance

$$L_{moy} = L_{inst} \frac{T_{ligne}}{T_{trame}} \tag{1.2}$$

$L_{mov}$ : Luminance moyenne

$\mathcal{L}_{inst}$  : Luminance instantannée lorsque le pixel est allumé

$T_{ligne}$  : Durée de sélection d'une ligne de pixels

Ttrame: Durée de la trame

moyenne nettement inférieure à la luminance maximum des LEDs la composant. Ainsi les matrices passives sont généralement réservées aux écrans présentant une faible définition [1], telles que les micro-écrans de définition  $16 \times 16$  présenté par [2], ou de définition  $128 \times 96$  présenté par [3].

FIGURE 1.9 – Balayage de type "rolling shutter" d'un écran passif

#### 1.3.2 Matrices actives

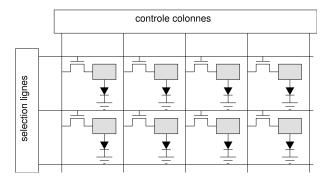

Dans le cas d'une matrice active telle que représentée en Figure 1.10, chaque LED est associée à un circuit de pilotage local. Des lignes métalliques reliant les pixels par lignes et colonnes sont utilisées pour contrôler le comportement des pixels depuis le bord de la matrice. Cependant ces lignes ne sont pas directement connectées aux LEDs. Les signaux véhiculés par les lignes et colonnes permettent en effet de configurer le circuit de pilotage présent dans chaque pixel [4]. La distribution des données s'effectue ligne par ligne. A chaque instant, une seule ligne de la matrice est sélectionnée et reçoit les données transmises sur les bus colonnes.

FIGURE 1.10 – Structure d'un écran LED à matrice active

La Figure 1.11 illustre le mécanisme de distribution des données pour une matrice active, ce dernier est très proche de celui d'une matrice passive. La différence réside dans l'existence d'un circuit de pilotage associé à chaque pixel. Ce dernier réalise une fonction de mémorisation et il maintient le fonctionnement de la LED lorsque la ligne correspondante est désélectionnée.

Ce type de matrice, bien que plus complexe qu'une matrice passive, ne souffre pas des mêmes

FIGURE 1.11 – Balayage de type "rolling shutter" d'un écran actif

limitations en ce qui concerne le temps d'illumination des pixels. Ce système permet donc de produire des matrices avec une grande résolution, puisque tous les pixels de l'écran peuvent être illuminés simultanément. Cela permet aussi d'atteindre une même luminance de l'écran avec des courants instantanés au travers des LEDs beaucoup plus faibles. Compte tenu des avantages qu'elles offrent, les matrices actives sont actuellement employées dans une large majorité des écrans et micro-écrans à LEDs.

# Chapitre 2

# Cas d'emplois typiques des différents micro-écrans

Des micro-écrans sont employés dans diverses applications nécessitant la production d'une image. Chaque type d'application présente des besoins d'affichage et des contraintes qui lui sont spécifiques. Ainsi, les caractéristiques permettant de juger de la qualité d'un micro-écran dépendent de l'application à laquelle il est destiné.

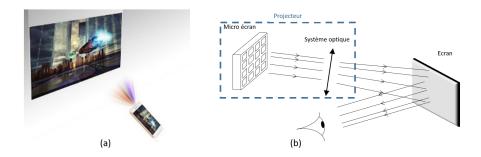

#### 2.1 Projection

Comme illustré en Figure 2.1 (a), les systèmes de projection vidéo visent à générer une image sur une surface distincte du projecteur lui-même, appartenant à l'environnement de l'utilisateur.

FIGURE 2.1 – Exemple de projecteur en fonctionnement (a), et structure du système (b)

La Figure 2.1 (b) présente les éléments essentiels d'un système de projection. Un microécran génère une image, qui est projetée à l'extérieur en direction de l'écran observé par l'utilisateur. Ce type de système est classiquement employé pour réaliser un affichage sur une surface largement supérieure à celle du micro-écran. De plus l'affichage est classiquement réalisé sur un objet non prévu à cet effet, qui ne présente donc pas des propriétés optiques optimales pour cet usage. Enfin l'affichage peut s'effectuer en présence d'une forte luminosité ambiante. Pour obtenir un affichage efficace dans de tels conditions, le micro-écran employé doit présenter une luminance très importante. Actuellement, dans le cas où le système emploie un micro-écran, ce dernier est généralement de type modulation de lumière, LCD ou DMD. Ces solutions permettent l'emploi d'une source lumineuse de forte puissance. En raison de la forte luminance nécessaire, et des problématiques de focalisation de l'image sur une surface dont la distance à l'émetteur n'est pas maitrisée, certains systèmes emploient un balayage de la surface de projection par une source laser plutôt qu'un micro-écran.

#### 2.2 Réalité virtuelle

Le principe général de réalité virtuelle consiste à plonger l'utilisateur dans un environnement fictif, et lui apporter une perception plausible de ce dernier. Les équipements offrant ce type d'expériences sont généralement construits autour d'un système d'affichage d'une image 3D, et couvrent une majorité sinon la totalité du champ de vision de l'utilisateur. Un capteur de positionnement est classiquement inclus afin de permettre une prise en compte des mouvements de l'utilisateur dans la génération des images. Cela permet à l'utilisateur de se déplacer de manière intuitive dans l'environnement virtuel.

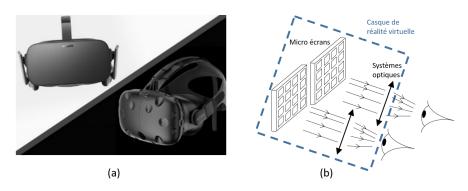

FIGURE 2.2 – Exemple de casques de réalité virtuelle (a), et structure d'un tel système (b)

Comme illustré par la Figure 2.2, les systèmes de réalité virtuelle prennent classiquement la forme de casques portés par l'utilisateur. Ces casques comportent pour chaque œil un écran associé à son optique, permettant une visualisation confortable malgré la proximité avec le visage de l'utilisateur. Afin de créer un rendu de profondeur sur l'image générée, les casques actuels utilisent la parallaxe, en générant deux image différentes, rendant compte de la différence de perspectives due à l'écart entre les deux yeux. Cette méthode de rendu de la profondeur, bien que fonctionnelle, n'est pas exempte de défaut et génère notamment une discordance entre vergence et accommodation. Fatigue visuelle et inconfort peuvent en effet découler de la différence entre la distance à laquelle l'image 3D est formée, et la distance d'accommodation de l'œil nécessaire pour obtenir une image nette [5]. Des solutions proposées dans la littérature pour remédier à cette limitation [6], s'appuient sur des modifications du

13 **2.2. Réalité virtuelle**

système optique et du signal vidéo utilisé, mais conservent l'emploi de micro-écrans dans une structure similaire à celle présentée par la Figure 2.2 (b).

Le casque de réalité virtuelle couvrant la totalité du champ de vision entraine une isolation de l'utilisateur par rapport à son environnement réel, en particulier de la luminosité ambiante de ce dernier. Dans le cas général d'utilisation d'un écran, l'existence d'une certaine luminosité ambiante rend acceptable l'émission d'une faible quantité de lumière par un pixel supposé noir. Cependant, en l'absence d'une telle luminosité l'œil humain est sensible à toute source de lumière, même de faible intensité. Un pixel présentant une luminance même réduite apparaitra alors gris plutôt que noir à l'utilisateur. Afin d'éviter ce problème, un casque de réalité virtuelle a besoin d'écrans offrant une grande qualité de noir, avec une émission de lumière extrêmement faible de la part des pixels affichant du noir [7].

Afin de rendre l'environnement virtuel cohérent, les mouvements de l'utilisateur sont compensés au niveau de l'image pour pouvoir présenter une scène en apparence immobile. Cette compensation des mouvements de l'utilisateur peut entrainer un flou gênant, en particulier pour des mouvements rapides tels que ceux de la tête. Un taux de rafraichissement très important du flux vidéo permet l'insertion de noirs entre les images afin de diminuer l'importance de ce phénomène [7]. Avec une conception adaptée, l'insertion de noir peut être réalisée directement au niveau de l'écran, augmentant alors virtuellement le taux de rafraichissement, sans que le débit de données à fournir au système n'augmente. La compensation des déplacements, si réalisée avec un délai trop important, peut entrainer l'apparition d'un inconfort de l'utilisateur [8] [9] [10] semblable au mal des transports. La réalisation de cette compensation avec un délai suffisamment faible implique nécessairement un intervalle réduit entre les images fournies à l'utilisateur. Afin de fournir un service de réalité virtuelle efficace et agréable, il est nécessaire d'employer des micro-écrans capables de fonctionner à une vitesse supérieure aux 30 Hz – 60 Hz typiquement rencontrés dans l'affichage de données vidéo.

Pour rendre l'affichage d'une scène convainquant, l'emploi d'images avec une définition importante apparait essentiel. Une résolution approchant les 100 pixels/degré, considérée comme la limite de l'œil humain, est couramment rencontrée avec d'autres types d'affichage, et est considérée comme l'objectif à atteindre [11]. Il est difficile de déterminer la résolution linéaire nécessaire au niveau du micro-écran pour atteindre une telle résolution angulaire, car le système optique utilisé dans le casque influence le lien entre ces deux grandeurs. Il est cependant admis que pour répondre à ce besoin de résolution, des micro-écrans présentant des pas pixels de  $5\mu$  m et moins sont nécessaires [12]. Les systèmes actuellement disponibles englobent une grande partie du champ de vision de l'utilisateur, un affichage sur un angle de  $100^{\circ}$  à  $110^{\circ}$  s'avèrant en effet nécessaire [11]. Cependant la combinaison d'une résolution importante et d'un large champ de vision implique l'emploi d'écrans présentant une très grande définition. L'emploi d'écrans 8k, comportant environ 8 000 pixels par ligne, est en effet présenté dans la littérature comme l'objectif à atteindre à terme pour satisfaire aux besoins des systèmes de réalité virtuelle [11].

Les casques actuellement disponibles utilisent des écrans construits en technologie LED ou LCD. L'adéquation entre la technologie LCD et les besoins de la réalité virtuelle est cependant remise en cause dans la littérature [7], en raison d'une trop grande latence et d'un trop faible contraste. Avec une contrainte d'encombrement relâchée comparativement à des applications de réalité augmentée, la majorité des systèmes de réalité virtuelle conçus à ce jour répondent au besoin de forte définition et large champ de vision par l'emploi d'écrans de dimensions importantes dont l'appartenance à la famille des micro écrans est contestable. Bien que des systèmes de réalité virtuelle puissent être construits à partir de micro-écrans, ce choix de conception ne concerne actuellement pas la majorité des cas.

#### 2.3 Réalité augmentée

Un système de réalité augmentée a lui aussi pour objectif de fournir à l'utilisateur l'expérience d'éléments virtuels. Cependant, contrairement à la réalité virtuelle, la réalité augmentée vise à maintenir la perception du réel tout en y intégrant des éléments virtuels. Comme illustré en Figure 2.3, ces systèmes se présentent généralement sous forme de lunettes au travers desquelles l'utilisateur peut voir son environnement.

FIGURE 2.3 - Exemple de lunettes de réalité augmentée

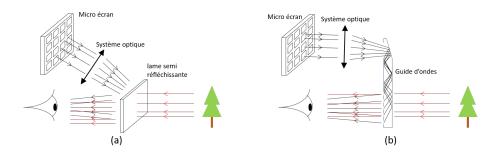

Afin de superposer une image virtuelle à la vision de l'environnement réel, un combineur est placé dans le champ de vision de l'utilisateur. Ce combineur permet à l'utilisateur qui regarde au travers de visualiser, à la fois son environnement réel, et l'image virtuelle générée par les lunettes. Deux structures sont alors couramment envisagées. Une première solution, illustrée en Figure 2.4 (a), utilise une lame semi réfléchissante comme combineur. L'image virtuelle est projetée sur cette lame, et réfléchie vers l'utilisateur. Cette solution est déjà employée dans des domaines tels que l'aviation [13] ou l'automobile [14] par exemple.

Une seconde option, illustrée en Figure 2.4 (b), consiste en l'emploi d'un guide d'onde comme combineur. Le guide d'onde est un objet optique beaucoup plus complexe, qui permet aux rayons lumineux d'entrer sur le bord du guide, et d'en ressortir dans l'axe de vision de l'utilisateur grâce à une série de réflexions internes [15]. Ce type de système, bien que plus complexe permet d'envisager l'implémentation de casques de réalité augmentée plus compacts [13].

Pour permettre une intégration satisfaisante de l'image virtuelle dans le milieu réel, il apparait

FIGURE 2.4 – Structure d'un système de réalité augmentée utilisant une lame semi réfléchissante (a), ou un guide d'onde (b)

nécessaire que les deux images présentent des luminances cohérentes entre elles. Lors d'une utilisation dans un environnement peu lumineux, l'émission de lumière parasite, même de faible intensité, n'est pas négligeable devant la luminosité de la scène réelle. On observe alors l'apparition d'un halo dans la zone d'affichage. Ce phénomène est observable dès lors que le micro-écran utilisé pour générer l'image virtuelle présente une qualité de noirs insuffisante [14] [11]. Pour cette raison, l'emploi de micro-écrans présentant un très faible niveau de fuites de lumière au niveau des pixels éteints est important dans les applications de réalité augmentée.

En cas d'utilisation dans un environnement très lumineux, la problématique inverse se pose. Afin que l'image projetée soit visible malgré sa superposition avec une scène très lumineuse, cette image doit elle aussi présenter une luminance importante. Pour permettre un affichage dans un environnement ensoleillé par exemple, une luminance de plusieurs milliers de cd/m2 est nécessaire [16]. De plus, selon le type de combineur utilisé, une perte importante peut être constatée dans le système optique, résultant en l'affichage d'une image 10 à 20 fois moins lumineuse que le micro-écran la produisant [11]. On peut alors distinguer les solutions destinées exclusivement à un usage en intérieur (ou milieu peu lumineux), et celles susceptibles d'être utilisées en extérieur (ou milieu très lumineuse). Tandis que les premiers peuvent être construits avec un micro-écran relativement peu lumineux, le second nécessite l'emploi d'un micro-écran très lumineux.

L'affichage d'éléments totalement intégrés à l'environnement, dans un but de divertissement par exemple, peut imposer des contraintes fortes quant à la définition d'affichage et à son taux de rafraichissement. L'affichage d'informations contextuelles essentiellement composées de texte fixe, tel qu'envisagé pour des applications professionnelles par exemple, s'avère beaucoup moins contraignant sur ces aspects [13]. Il est alors difficile de définir clairement la gamme de définition et de taux de rafraichissement nécessaires pour un micro-écran destiné à un système de réalité augmentée. Ces deux paramètres sont en effet très dépendants de l'application visée. Les systèmes de réalité augmentée actuellement disponibles utilisent principalement des micro-écrans de type LED, ou LCD, bien que les limitations de ces derniers en terme de luminance et qualité de noir soient mises en avant dans la littérature [14] [11].

# **Chapitre 3**

# Diodes électro luminescentes (LEDs)

#### 3.1 Physique de la LED

Afin de décrire le fonctionnement des diodes électroluminescentes, il est nécessaire de revenir sur certains éléments de la physique du semi-conducteur. Cependant cette thèse portant sur le pilotage des LEDs, et non sur leur développement, nous nous contenterons ici d'explications qualitatives ne rendant pas compte de toute la complexité de certains phénomènes physiques mis en jeux.

#### 3.1.1 Phénomène d'électroluminescence

Dans un cristal de semi-conducteur, une partie des électrons périphériques des atomes peuvent être excités par l'absorption d'énergie. Ces électrons quittent alors l'état de repos dans lequel ils participent à la cohésion du cristal, pour se déplacer plus librement.

Dans le diagramme d'énergie du matériau, qui permet de représenter les différents états des électrons dans le cristal, l'excitation des électrons correspond à leur passage de la bande de valence à la bande de conduction. L'absorption d'énergie par le matériau se traduit dans ce diagramme par l'apparition d'électrons libres dans la bande de conduction, ainsi que de trous dans la bande de valence. Ces derniers correspondent aux espaces libres laissés par les électrons lors de leur départ de cette bande. Ces trous et électrons libres sont responsables de la conduction électrique du matériau, et d'une manière plus générale, expliquent par leur comportement tous les phénomènes électriques observables dans un matériau semiconducteur.

Les transferts d'énergie entre le milieu extérieur et les électrons du matériau se font par absorption ou libération de particules, notamment des phonons ou photons. Ces échanges énergétiques étant réversibles, il est possible pour un électron excité et un trou de se recombiner en émettant, sous forme d'une particule, l'énergie perdue par l'électron qui quitte son état

excité. Sous certaines conditions sur la structure du matériau dans lequel cette désexcitation a lieu, l'énergie émise peut être transmise au milieu extérieur sous forme d'un photon dont la longueur d'onde dépend directement du gap du matériau. Cette émission de photons lors de la recombinaison de trous et électrons libres constitue le phénomène d'électroluminescence sur lequel repose le fonctionnement des LEDs.

#### 3.1.2 Jonctions

Une jonction est obtenue dès lors que deux matériaux semi-conducteurs différents sont mis en contact. Un cas classique consiste en la mise en contact de deux zones d'un même matériau dopées différemment, la jonction est alors appelée homo jonction.

La mise en contact d'un semi-conducteur de type P avec un semi-conducteur de type N entraine, au voisinage de la jonction, l'apparition d'une ZCE (zone de charge d'espace). Dans cette zone, les porteurs majoritaires (électrons ou trous) de chaque matériau, migrent vers la zone de type opposé pour s'y recombiner. Les électrons quittant le matériau N laissent dans ce dernier les ions positifs formés par les atomes dopants privés d'un électron, le cristal jusqu'ici électriquement neutre est alors chargé positivement. Le même phénomène au niveau du matériau P, entraine l'apparition d'une charge électrique négative, associée à une migration des trous vers la zone N. Le champ électrique induit par l'apparition de charges électriques empêche alors la migration de nouveaux électrons libres de la zone N vers la zone P, ainsi que celle des trous dans le sens opposé. La ZCE est alors dépourvue de porteurs libres. la Figure 3.1 illustre la structure de bande d'une telle jonction.

Une homo jonction constitue une diode, la déformation du diagramme de bande empêche la circulation des porteurs au niveau de la jonction. Cette circulation ne redevient possible que lorsqu'une tension suffisante est appliquée à l'ensemble pour annuler la barrière de potentiel créée par le champ électrique naturellement présent dans la ZCE.

FIGURE 3.1 – Description d'une homo jonction

#### 3.1.3 Puits quantiques

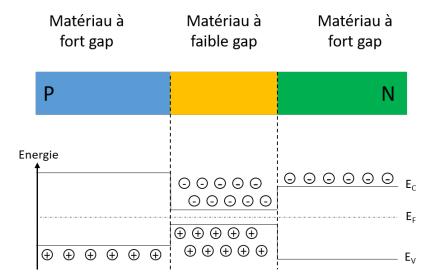

Les homo jonctions sont largement employées dans l'industrie du semi-conducteur, cependant ces dernières ne sont pas nécessairement les plus appropriées pour la production de composants optiques. La mise en contact de deux matériaux semi-conducteurs de natures différentes permet d'obtenir une structure appelée hétéro jonction. Les matériaux employés à cet effet présentent généralement des gaps assez différents. La mise en contact de ces matériaux entraine alors des déformations différentes dans les bandes de valence et de conduction, ce qui permet d'obtenir des structures de bande plus complexes. Parmi les structures possibles, on remarquera notamment la possibilité d'obtenir un puit quantique. Une telle jonction est présentée en Figure 3.2. Un matériau à faible gap est inséré à la jonction entre deux matériaux de gap plus important. Il apparait alors deux hétérojonctions. En raison du faible gap du matériau intermédiaire, le diagramme de bande de l'ensemble présente un point bas dans la bande de conduction et un point haut dans la bande de valence. Cette zone constitue alors un puit quantique qui a tendance à piéger à la fois trous et électrons libres [17]. Comme nous le verrons par la suite, le puit quantique est utilisé pour former des LEDs.

FIGURE 3.2 – Diagramme de bande simplifié d'une double hétérojonction, avec formation d'un puit quantique

#### 3.2 Fabrication des LEDs GaN

#### 3.2.1 Structure de la LED GaN

Les LEDs GaN émettent de la lumière grâce à l'accumulation de charges dans une hétérojonction. Tandis qu'une diode à homo jonction s'avère peu adaptée à l'émission de lumière car aucune zone du dispositif ne réunit trous et électrons libres en grandes quantités, les LEDs GaN sont constituées de couches d'alliage InGaN intercalées dans un matériau GaN. Le gap réduit de l'alliage InGaN entraine l'apparition d'une succession de puits quantiques. Ces puits, en concentrant trous et électrons libre dans une même zone augmente la probabilité de recombinaisons radiatives [17].

La proportion d'indium dans l'alliage InGaN influence le gap du matériau, et détermine la couleur de la lumière émise. Une modification de la teneur en indium permet en effet, avec la modification de la profondeur des puits quantiques, d'ajuster l'énergie et donc la longueur d'onde des photons émis par la LED [18]. Une concentration très importante en indium, telle que celle requise pour l'émission de lumière rouge entraine cependant des complications technologiques. Les LEDs rouges fonctionnent selon le même principe, il est cependant courant que ces dernières soient obtenues en utilisant des alliages à base de galium différents [19].

#### 3.2.2 Méthode de production

En raison de la structure des LEDs GaN, qui impose l'emploi de matériaux semi-conducteur de natures différentes, ces composants ne peuvent être produits sur une filière CMOS silicium

classique et nécessite l'emploi d'un procédé particulier. Les LEDs considérées dans ce document sont produites en technologie planaire, permettant la réalisation d'une unique LED couvrant la totalité du wafer. Ce mode de réalisation couvrant la totalité du wafer sera nommé "pleine plaque" par la suite.

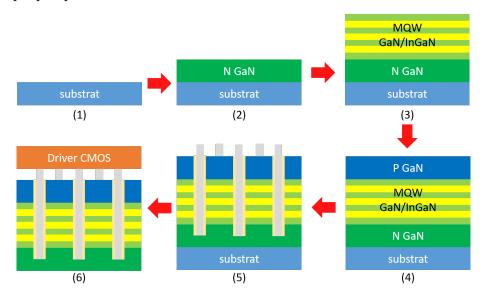

FIGURE 3.3 – Illustration simplifiée du procédé de production des LEDs GaN en technologie planaire

La Figure 3.3 illustre les principales étapes de fabrication des LEDS, il s'agit d'une vue simplifiée omettant certaines étapes, notamment le dépôt de couches tampons permettant d'associer des matériaux dont les paramètres de maille ne sont pas directement compatibles.

- 1. Un substrat classiquement en saphir est employé comme support pour la croissance du matériau GaN [20] [21]. Plus récemment, le procédé a été adapté pour l'utilisation d'un substrat silicium [22], permettant l'emploi de wafers de dimensions supérieures correspondant aux dimensions de ceux employés pour la production du circuit de contrôle associé.

- 2. Une étape de croissance de GaN dopé N est réalisée, cette couche constituera la cathode des LEDs.

- 3. Une succession de plusieurs couches de GaN et InGaN sont déposées pour constituer les MQWs (Multi Quantum Well). Cet ensemble comporte une succession de puits quantiques, lieux privilégiés d'émission de lumière par les LEDs.

- 4. Une couche de GaN dopé P est ensuite déposée pour former l'anode des LEDs.

- 5. Une étape de gravure permet, à partir des dépôts tous effectués en pleine plaque, de produire des LEDs unitaires. Dans le cas de la production d'une matrice de LEDs devant être reportées sur un circuit, ces gravures s'arrêtent dans la cathode qui reste commune à toutes les LEDs. Les tranchées ainsi effectuées sont ensuite isolées et remplies de métal permettant la connexion de la cathode au circuit. Un contact au niveau des anodes singularisées est aussi aménagé.

6. L'ensemble est reporté sur le circuit de pilotage. Enfin, le substrat utilisé pour faire croitre les différentes couches composant les LEDs peut être retiré [22].

La technologie planaire n'est pas la seule solution envisageable pour la production de LEDs GaN, il existe notamment la possibilité de construire les LEDs sous forme d'un ensemble de nano fils [23] [24]. Chacun de ces fils conserve la structure d'une LED, la succession des couches employées est identique à celle des LEDs planaires, mais est organisée depuis le centre des fils jusqu'à leur périphérie plutôt que depuis le substrat vers le haut. Chaque composant LEDs est alors généralement constitué d'une multitude de nano fils regroupés sur une même surface.

#### 3.3 Comparaison des technologies LED

La LED GaN constitue une part majeure des LEDs produites dans des matériaux non organiques. Il existe également des LEDs produites à l'aide de composés organiques : les OLED (Organic LED). Les deux types de LEDs, GaN et OLED, sont utilisées pour la production de micro-écrans. Ces deux technologies LED présentant des caractéristiques différentes, le choix de la technologie employée dépend des performances recherchées pour le micro-écran.

#### 3.3.1 LEDs organiques

La technologie OLED est employée depuis plusieurs années à l'échelle industrielle dans des solutions d'affichage, telles que celles présentées en Figure 3.4. Il s'agit d'une technologie relativement mature dont les procédés de fabrication sont maitrisés. Différents procédés de fabrication mis en œuvre ne comportent pas d'étapes particulièrement agressives pour les matériaux composant la LED, tel que des gravures comme c'est le cas pour les LEDs inorganiques [25] [26]. Les méthodes de déposition sélective utilisées permettent d'obtenir des ensembles de LEDs présentant une grande uniformité. Ces différentes méthodes de production permettent par ailleurs la cointégration de LEDs organiques de plusieurs couleurs sur une même matrice, comme en atteste la grande variété de micro-écrans OLED couleur rapportés dans la littérature [27] [28] [29] [30].

La technologie OLED est par ailleurs connue pour permettre la production de LEDs dont la couleur d'émission se situe en périphérie de l'espace de chrominance (u', v') [31], espace permettant de représenter le spectre de couleurs reproductibles avec un ensemble de LEDs donné. La position périphérique des LEDs dans cet espace, associé à la facilité de cointégration de LEDs de différentes couleurs, confère aux écrans OLED une grande qualité de rendu des couleurs.

Cette technologie est capable d'offrir une luminance importante, tout en présentant une efficacité électrique appréciable. Plusieurs publications rapportent en effet une efficacité de l'ordre de grandeur de 25 cd/A pour des points de fonctionnements offrant quelques milliers de cd/m2 [32] [27] [33]. Les technologies organiques, malgré leurs avantages, souffrent de

la faible stabilité des matériaux qu'elles emploient. La grande efficacité électrique des LEDs obtenue sur des dispositifs neufs, se dégrade durant leur utilisation [34]. La capacité des OLED à atteindre une luminance importante est par ailleurs difficilement exploitable, car la dégradation des dispositifs est d'autant plus grande qu'ils sont utilisés sous un fort courant [33]. En parallèle des travaux portants sur l'amélioration de la robustesse des OLEDs, des méthodes de pilotages limitant la dégradation ont été proposées [35], mais imposent l'emploi de circuits de pilotage complexes. D'autres méthodes visant à compenser la dégradation plutôt qu'à l'empêcher ont été proposées [36] mais présentent, elles aussi, des inconvénients tels qu'une compensation d'efficacité réduite en cas de vieillissement inhomogène des pixels. Ce type de compensation entraine par ailleurs l'utilisation de courants plus importants pour le pilotage de LEDs vieillies, ce qui accentue la vitesse de dégradation de ces dernières.

FIGURE 3.4 – Exemple de micro-écrans OLED présentés par [37] et [11]

#### 3.3.2 LEDs GaN

La technologie GaN est utilisée à l'échelle industrielle pour la production de LEDs de 0,1 mm à 1 mm destinées à des applications d'éclairage [38] [39]. Elle présente cependant une faible maturité technologique dans le cas de la production de micro-LEDs destinées à la production de micro-écrans.

Les Caractéristiques I(V) de pixels présentées dans [40] illustrent l'importance de ce phénomène. Sur une même matrice, le courant varie presque du simple au double selon les LEDs, pour une tension directe donnée. La dispersion de caractéristiques est particulièrement marquée pour les LEDs de faibles dimensions. Une telle dépendance de la dispersion vis-à-vis de la dimension des composants est classique en électronique, et généralement expliquée par un effet d'observation de performances moyennée sur la surface des composants [41]. Cependant, comme expliqué dans le chapitre 3.2.2 , la production des LEDs GaN en technologie planaire implique une étape de singularisation des composants par gravure. Cette gravure est soupçonnée d'être responsable d'une part importante de la dispersion à cause d'une dégradation du cristal GaN sur la périphérie des LEDs.

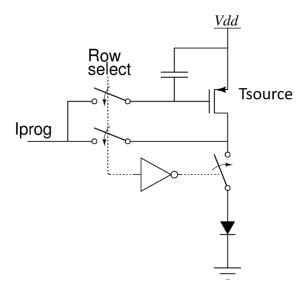

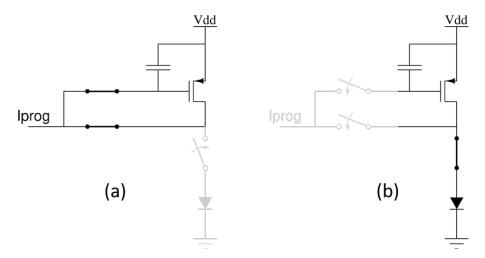

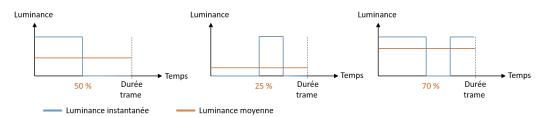

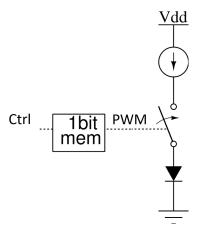

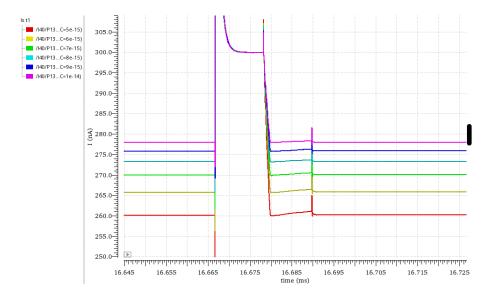

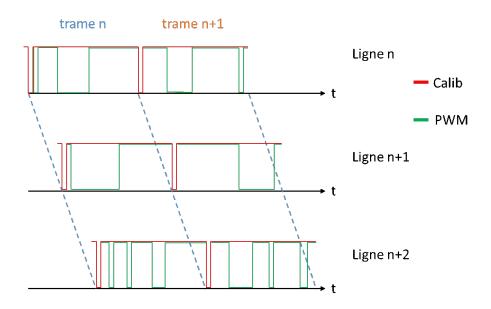

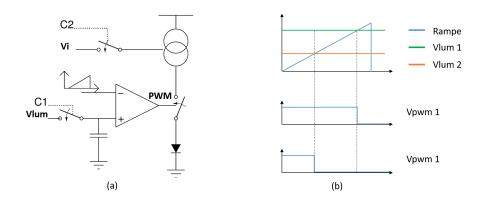

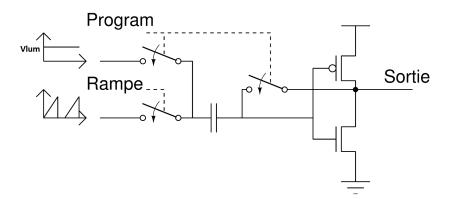

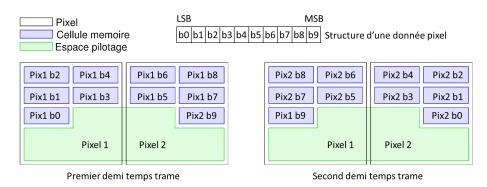

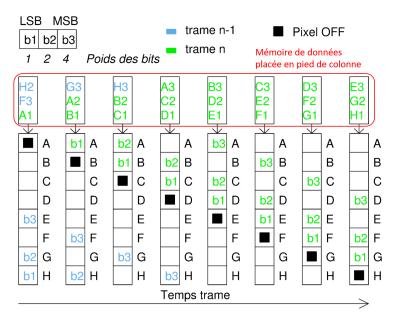

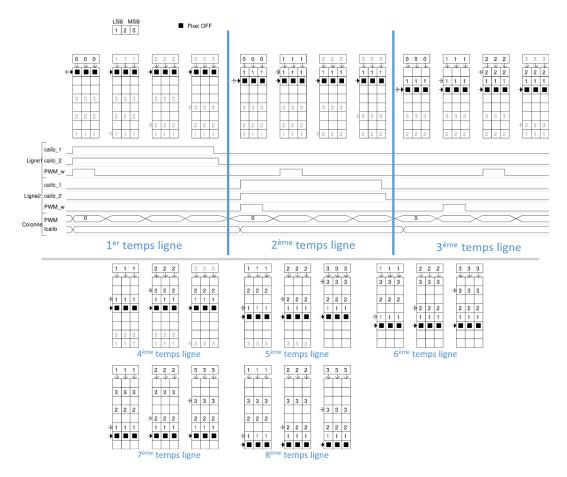

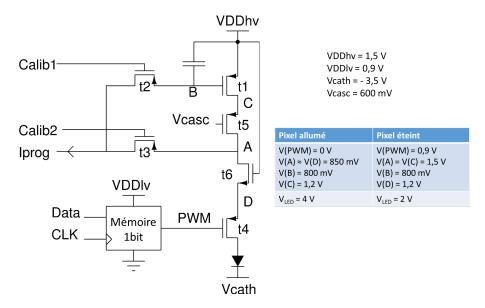

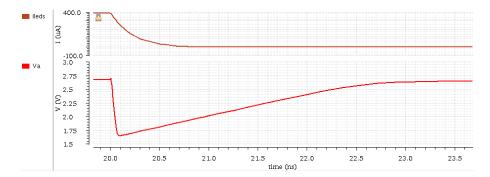

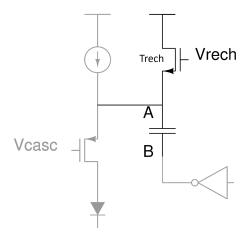

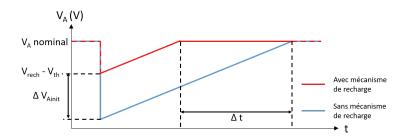

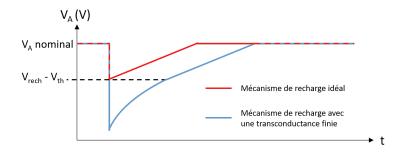

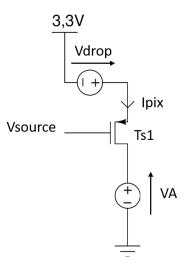

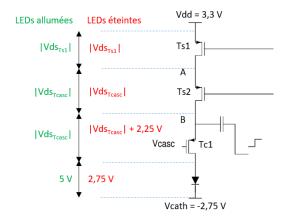

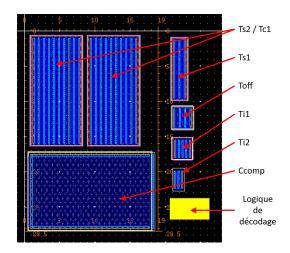

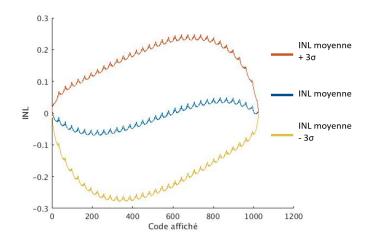

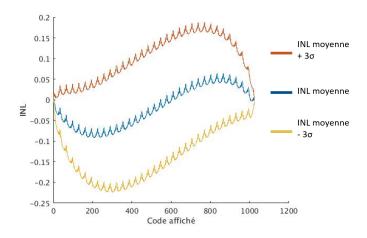

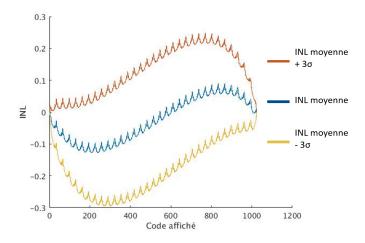

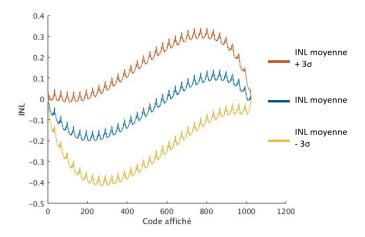

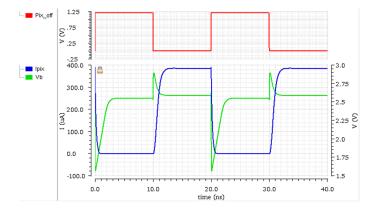

La méthode actuelle de fabrication des LEDs grâce au découpage d'une structure réalisée en pleine couche, associée aux difficultés d'obtention de LEDs rouges, rendent particulièrement difficile la production d'écrans GaN couleur.