## High Throughput Low Latency Online Image Processing by GPU/FPGA Data Coprocessors using RDMA Techniques

Raphael Ponsard

### ▶ To cite this version:

Raphael Ponsard. High Throughput Low Latency Online Image Processing by GPU/FPGA Data Coprocessors using RDMA Techniques. Signal and Image processing. Université Grenoble Alpes [2020-..], 2020. English. NNT: 2020GRALT071. tel-03211910

## HAL Id: tel-03211910 https://theses.hal.science/tel-03211910

Submitted on 29 Apr 2021

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité: SIGNAL IMAGE PAROLE TELECOMS

Arrêté ministériel : 25 mai 2016

Présentée par

#### RAPHAEL PONSARD

Thèse dirigée par **DOMINIQUE HOUZET**, Université Grenoble Alpes et codirigée par **Vincent FRISTOT**, Université Grenoble Alpes, et **Nicolas JANVIER**, ESRF, Grenoble

préparée au sein du Laboratoire Grenoble Images Parole Signal Automatiques

dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Traitement en temps réel, haut débit et faible latence d'images par coprocesseurs GPU & FPGA utilisant les techniques d'accès direct à la mémoire distante

# High Throughput, Low Latency Online Image Processing by GPU/FPGA Coprocessors using RDMA Techniques

Thèse soutenue publiquement le **10/12/2020**, devant le jury composé de :

#### Madame LAURENCE PIERRE

PROFESSEUR DES UNIVERSITÉS, UNIVERSITÉ GRENOBLE ALPES, Présidente du jury

#### **Monsieur DOMINIQUE HOUZET**

PROFESSEUR DES UNIVERSITÉS, GRENOBLE INP, Directeur de thèse

#### **Monsieur BRICE GOGLIN**

DIRECTEUR DE RECHERCHE, INRIA BORDEAUX – SUD - OUEST, Rapporteur

#### Monsieur EMMANUEL FARHI

INGENIEUR HDR, SYNCHROTRON SOLEIL- GIF-SUR-YVETTE, Rapporteur

#### Monsieur NICOLAS JANVIER

Ingénieur, ESRF GRENOBLE,

Invité

#### Monsieur VINCENT FRISTOT

MAITRE DE CONFÉRENCE, UNIVERSITÉ GRENOBLE ALPES, Invité

High Throughput Low Latency Online Image Processing by GPU / FPGA Data Coprocessors using RDMA Techniques

**Abstract**— The constant evolution of X-ray photon sources associated to the increasing performance of high-end X-ray detectors allows cutting-edge experiments that can produce very high throughput data streams and generate large volumes of data that are challenging to manage and store.

In this context, it becomes fundamental to optimize processing architectures that allow real-time image processing such as raw data pre-treatment, data reduction, data compression, fast-feedback. These data management challenges have still yet not been addressed in a fully satisfactory way as of today, and in any case, not in a generic manner.

This thesis is part of the ESRF RASHPA project that aims at developing a RDMA-based Acquisition System for High Performance Applications. One of the main characteristics of this framework is the direct data placement, straight from the detector head (data producer) to the processing computing infrastructure (data receiver), at the highest acceptable throughput, using Remote Direct Memory Access (RDMA) and zero-copy techniques with minimal Central Processing Unit (CPU) interventions.

The work carried out in this thesis is a contribution to the RASHPA framework, enabling data transfer directly to the internal memory of accelerator boards. A low-latency synchronisation mechanism between the RDMA network interface cards (RNIC) and the processing unit is proposed to trigger data processing while keeping pace with detector. Thus, a comprehensive solution fulfilling the online data analysis challenges is proposed on standard computer and massively parallel coprocessors as well.

Scalability and versatility of the proposed approach is exemplified by detector emulators, leveraging RoCEv2 (RDMA over Converged Ethernet) or PCI-Express links and RASHPA Processing Units (RPUs) such as Graphic Processor Units (GPUs) and Field Gate Programmable Arrays (FPGAs).

Real-time data processing on FPGA, seldom adopted in X ray science, is evaluated and the benefits of high level synthesis are exhibited.

The framework is supplemented with an allocator of large contiguous memory chunk in main memory and an address translation system for accelerators, both geared towards DMA transfer.

The assessment of the proposed pipeline was performed with online data analysis as found in serial diffraction experiments. This includes raw data pre-treatment as foreseen with adaptive gain detectors, image rejection using Bragg's peaks counting and data compression to sparse matrix format.

Traitement en temps réel, haut débit et faible latence, d'images par coprocesseurs GPU & FPGA utilisant une technique d'accès direct à la mémoire distante

**Résumé**— L'amélioration permanente des sources de rayonnement X, ainsi que les gains en performances des détecteurs de dernière génération rendent possibles des expériences qui peuvent produire des quantités énormes de données à haut débit, aussi difficiles à gérer qu'à stocker.

Dans ce contexte, il devient indispensable d'améliorer les systèmes de calculs et de permettre le pré-traitement en temps réel des données brutes, la réjection de celles qui sont inutiles, la compression voire la supervision en temps réel de l'expérience. Ces problématiques de gestion des flux de données n'ont pas encore reçu de réponse générique pleinement satisfaisante.

Cette thèse fait partie d'un projet plus vaste, le projet RASHPA de l'ESRF, visant à développer un système d'acquisition haute performance basé sur le RDMA (Remote Direct Memory Access). Une des caractéristiques essentielles de ce projet est la capacité à transférer directement des données de la tête du détecteur vers la mémoire de l'unité de calcul, au plus haut débit possible, en utilisant les techniques d'accès direct à la mémoire, sans copies inutiles, et minimisant le recours à un processeur.

Le travail réalisé pendant cette thèse est une contribution au système RASHPA, qui rend possible, non seulement le transfert de données dans la mémoire du système de calcul, mais aussi directement dans la mémoire interne de cartes accélératrices dans le cas de système à l'architecture hétérogène.

Un mécanisme de synchronisation à faible latence entre carte réseau et unité de calcul est proposé, déclenchant le traitement des données au rythme du détecteur.

Cela permet de fournir une solution globale au traitement de données en temps réel, tant sur ordinateurs classiques que sur accélérateurs massivement parallèles.

Pour illustrer la versatilité de l'approche proposée, plusieurs simulateurs de détecteurs ont été réalisés, s'appuyant sur les protocoles RoCEv2 ou PCI Express pour la partie transport, ainsi que diverses unités de calcul compatibles RASHPA à base de cartes graphiques (GPU) ou de circuits reconfigurables (FPGA).

Le traitement de données en temps réel sur FPGA, encore peu pratiqué dans les sciences du rayon X, est évalué en s'appuyant sur les récentes avancées de la synthèse de haut niveau (HLS).

La qualification du pipeline de calcul proposé a été faite en s'inspirant d'expériences de cristallographie en série (SSX). Il comprend un pré-traitement des données brutes comme prévu pour un détecteur à gain adaptatif, la réjection d'images en fonction du nombre de pics de Bragg, et la compression des données au format matrice creuse.

#### To Arlette and Nathalie,

Cette thèse n'aurait pas été possible sans l'esprit d'initiative de Pablo et Nicolas à la tête de ISDD et de EU. Ils m'ont fait confiance et ont bien voulu me confier un projet aussi important pour le rayonnement scientifique de l'ESRF. Je leur en suis profondément reconnaissant. Merci aussi à Marie qui gère le DDP avec brio pour son support constant.

Dominique et Vincent ont assuré l'encadrement universitaire, tâche peu commode à distance et leurs conseils et pressions m'ont permis d'aboutir dans les temps.

Je veux aussi saluer ici Andy et Petri grâce à qui j'ai pu faire mes premiers pas à l'ESRF dès 1999 et bien sûr l'équipe TANGO avec qui j'ai tout découvert à l'époque du fonctionnement de cette grandiose machine.

Pendant ces trois années de thèse passées si vite, Jérôme n'a pas compté son temps pour m'introduire aux subtilités de la programmation des GPUs, domaine dans lequel il excelle, mais aussi pour me faire découvrir la cristallographie ou les arcanes du calcul scientifique. Merci aussi à tous les collègues du DAU.

Pendant mon séjour, l'équipe RASHPA s'est progressivement étoffée et j'ai beaucoup appris avec Wassim, grand maître du FPGA et Aurélien qui m'a beaucoup impressionné avec son esprit de méthode. Je salue toute l'équipe EU pour son accueil sympathique.

Alejandro et Samuel m'ont aussi énormément apporté.

Laura a été très courageuse quand elle a accepté de relire et de corriger le manuscrit en anglais.

Je profite aussi de cette occasion pour saluer aussi tous mes anciens collègues de l'E.N. et bien sûr tous mes camarades que j'ai un peu laissé tomber pendant cette période un peu frénétique.

Pardon à tous ceux que je ne cite pas nommément, vous êtes bien trop nombreux ! Cela a été un grand bonheur.

## Contents

| C  | onter            | $\mathbf{nts}$ |                                                              | ii           |

|----|------------------|----------------|--------------------------------------------------------------|--------------|

| Li | $\mathbf{st}$ of | Figure         | es                                                           | $\mathbf{v}$ |

| Li | ${f st}$ of      | Tables         | S                                                            | vii          |

| Li | $\mathbf{sting}$ | $\mathbf{s}$   |                                                              | viii         |

| 1  | Intr             | oducti         | ion                                                          | 1            |

|    | 1.1              | Makin          | g Science using X-ray Radiation                              | 2            |

|    |                  | 1.1.1          | ESRF-EBS Grenoble, The European Synchrotron                  | 4            |

|    |                  | 1.1.2          | X-ray Detectors and Experimental Setup Overview              | 9            |

|    | 1.2              | Full T         | Throughput X-ray 2D Imaging Experiments                      | 11           |

|    | 1.3              | Resear         | rch Questions                                                | 12           |

|    |                  | 1.3.1          | Data Transfer Issues and RDMA Mitigation Techniques          | 12           |

|    |                  | 1.3.2          | Real-time Data Analysis with GPU/FPGA Accelerators           | 14           |

|    |                  | 1.3.3          | Contributions to RASHPA Data Acquisition Framework           | 15           |

|    | 1.4              | Organ          | ization of the Thesis                                        | 16           |

| 2  | Stat             | te of tl       | he Art: Data Transfer & RASHPA                               | 18           |

|    | 2.1              | High-t         | throughput Networking                                        | 19           |

|    |                  | 2.1.1          | Bottlenecks Related to Memory Management                     | 21           |

|    |                  | 2.1.2          | PCI-e Interconnect                                           | 23           |

|    |                  | 2.1.3          | Direct Memory Access Overview                                | 24           |

|    |                  | 2.1.4          | Memory Allocation Challenges                                 | 26           |

|    |                  | 2.1.5          | Limitations of Conventional Networking Techniques            | 27           |

|    |                  | 2.1.6          | Overview of RDMA Techniques                                  | 29           |

|    |                  |                | 2.1.6.1 RoCEv2 Assessment in the Frame of the RASHPA project |              |

|    |                  |                | 2.1.6.2 Messaging Accelerator Library                        | 33           |

|    |                  | 2.1.7          | Prospects beyond DMA Techniques                              | 33           |

|    | 2.2              |                | vare Accelerators Overview                                   | 34           |

|    |                  | 2.2.1          | GPU accelerators                                             | 35           |

|    |                  | 2.2.2          | PCI-e P2P Transfer into GPU/FPGA Device Memory               | 37           |

|    |                  | 2.2.3          | Parallel Algorithms                                          | 39           |

|    |                  | 224            | FPCA Accolorators                                            | 40           |

|   | 2.3            | The R          | ASHPA Framework                                         |

|---|----------------|----------------|---------------------------------------------------------|

|   |                | 2.3.1          | Paradigms                                               |

|   |                | 2.3.2          | Overview of the Frameworks in HEP or Astronomy          |

|   |                | 2.3.3          | Contribution to RASHPA Processing Unit Specifications   |

| 3 | ВΔ             | SHPA           | Data Source Simulators 4                                |

| J | ил             | 3.0.1          | Methods                                                 |

|   | 3.1            |                | J Detector Emulator                                     |

|   | 0.1            | 3.1.1          | Micro-benchmark of Network Protocols                    |

|   |                | 3.1.2          | Programming with Verbs                                  |

|   |                | 3.1.3          | Event Implementation                                    |

|   |                | 3.1.4          | Proof of Concept                                        |

|   | 3.2            |                | PA PCI-e Implementation                                 |

|   | J. <u>-</u>    | 3.2.1          | Reduced RASHPA                                          |

|   |                | 3.2.2          | FPGA Design                                             |

|   |                | 3.2.3          | Firmware                                                |

|   |                | 3.2.4          | Events                                                  |

|   |                | 3.2.5          | Allocation of Large Memory Buffers                      |

|   | 3.3            |                | PA RoCE using Xilinx IP                                 |

|   | 3.4            |                | me                                                      |

|   |                | 3.4.1          | Results of the RoCEv2 version                           |

|   |                | 3.4.2          | Results of the PCIe version                             |

| 4 | <b>Onl</b> 4.1 |                | celerated Data Processing using RASHPA Processing Units |

|   |                | 4.1.1          | General Working                                         |

|   |                | 4.1.2          | Address Translation System                              |

|   |                | 4.1.3          | CPU Accelerated RPU                                     |

|   |                | 4.1.4          | GPU Accelerated RPU                                     |

|   |                | 4.1.5          | FPGA Accelerated RPU                                    |

|   |                |                | 4.1.5.1 Proposed FPGA design                            |

|   |                |                | 4.1.5.2 HLS Kernel and Host Application                 |

|   | 4.2            | Image          | Processing for SSX Experiments                          |

|   |                | 4.2.1          | Raw-data Pre-treatment                                  |

|   |                | 4.2.2          | Data Rejection                                          |

|   |                | 4.2.3          | Compression to Sparse Matrix                            |

|   |                | 4.2.4          | Azimuthal Integration                                   |

|   |                | 4.2.5          | Ultra Low Latency Control                               |

|   | 4.3            |                | me                                                      |

|   |                | 4.3.1          |                                                         |

|   |                |                | Methods                                                 |

|   |                | 4.3.2          | Results with CPU / OpenMP                               |

|   |                | 4.3.2<br>4.3.3 | Results with CPU / OpenMP                               |

|   |                |                | Results with CPU / OpenMP                               |

|   |                |                | Results with CPU / OpenMP                               |

|         |                                      | iv  |

|---------|--------------------------------------|-----|

|         | 4.3.4 Results on FPGA                | 86  |

|         | 4.3.5 Results on POWER9 Computer     | 87  |

| 5 Cor   | nclusion                             | 92  |

| 5.1     | Outcome                              | 93  |

| 5.2     | Outlook                              | 94  |

|         | 5.2.1 Disaggregated Storage          | 94  |

|         | 5.2.2 Integration Challenges         | 96  |

| Bibliog | graphy                               | 97  |

| A Art   | cicles in Journals and Conferences   | 104 |

| В Наг   | rdware and Software Contributions    | 106 |

| C Rés   | sumé de la thèse en langue française | 108 |

|         |                                      |     |

## List of Figures

| 1.1  | The first Radiography                 | 3 |

|------|---------------------------------------|---|

| 1.2  | Just the good wavelength              | 1 |

| 1.3  | X ray source brilliance               | 5 |

| 1.4  | GE synchrotron                        | 3 |

| 1.5  | SR in the World                       | 7 |

| 1.6  | ESRF Construction work                | 3 |

| 1.7  | ESRF and Beamlines                    | 3 |

| 1.8  | Jungfrau 16M detector image           | 3 |

| 1.9  | Moore's Law in X sciences             | 1 |

| 2.1  | Multiple fields related to the work   | ) |

| 2.2  | RASHPA system overview                | L |

| 2.3  | Computer Memory Hierarchy             | 3 |

| 2.4  | Computer Memory Bandwidth             |   |

| 2.5  | PCI-Express topology                  | 5 |

| 2.6  | CPU affinity                          |   |

| 2.7  | TCP State Machine                     |   |

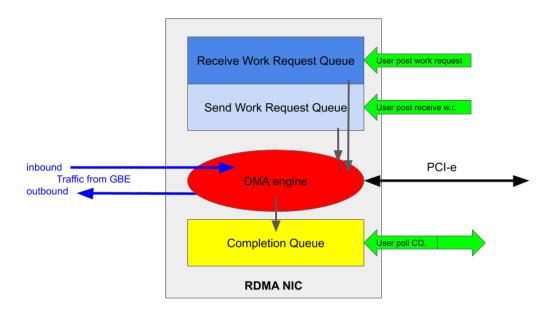

| 2.8  | RNIC programming internals            |   |

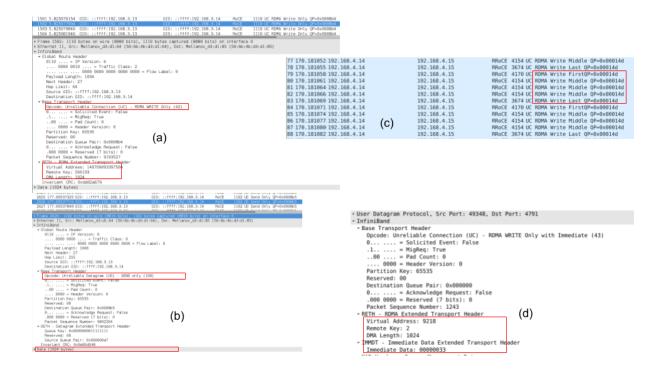

| 2.9  | RoCE Datagram                         |   |

|      | LibVMA Mellanox Messaging Accelerator |   |

|      | Gen-Z                                 |   |

|      | Hardware accelerators                 |   |

|      | Connectx-5 RNIC                       |   |

|      | View of a RASHPA system               | - |

|      | View of Region of Interests           |   |

| 2.16 | RASHPA GPU Overview                   | 5 |

| 3.1  | REMU Sequence diagram                 | 1 |

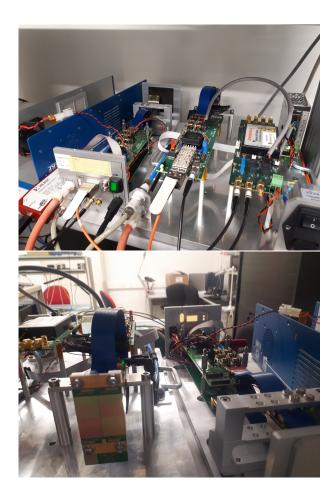

| 3.2  | Smartpix Detector                     |   |

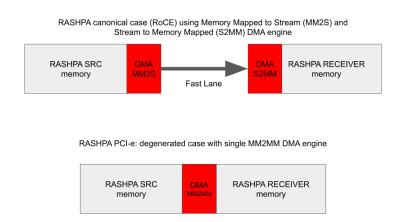

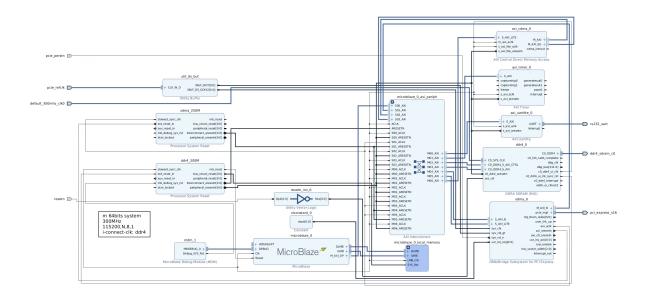

| 3.3  | RASHPA DMA Overview                   | 3 |

| 3.4  | Multiple data transfer using RASHPA   | 3 |

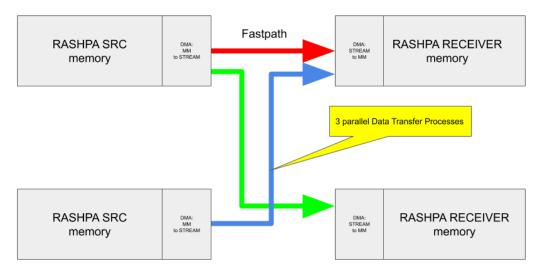

| 3.5  | REMU PCI-e block design               | ) |

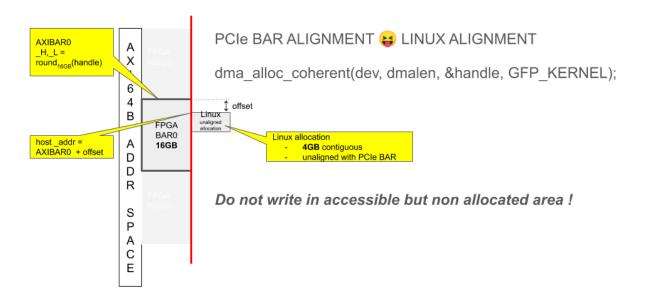

| 3.6  | PCIe BAR Alignment                    |   |

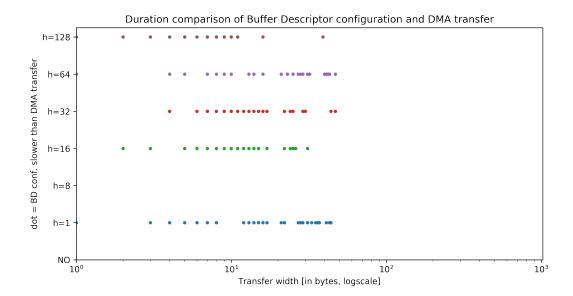

| 3.7  | Efficiency of BDs soft-processing     | 3 |

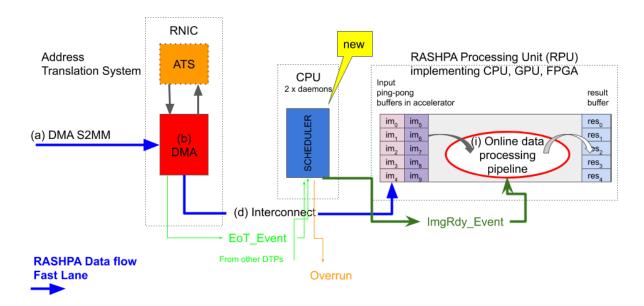

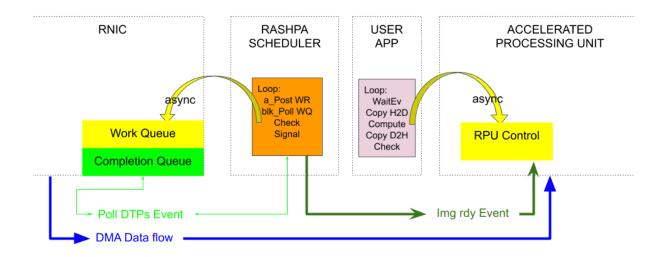

| 4 1  | Overview of a RASHPA-RPU 67           | 7 |

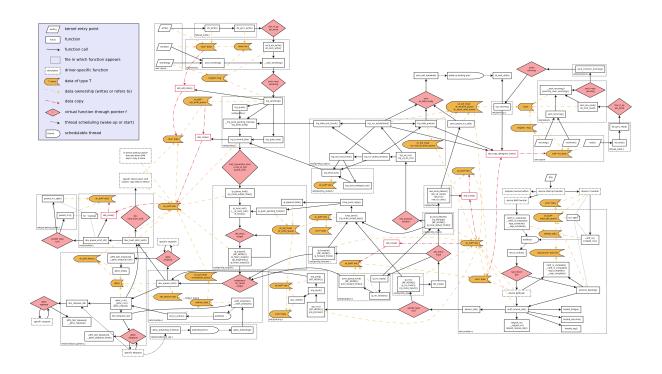

| 4.2  | The RASHPA-Scheduler                                |

|------|-----------------------------------------------------|

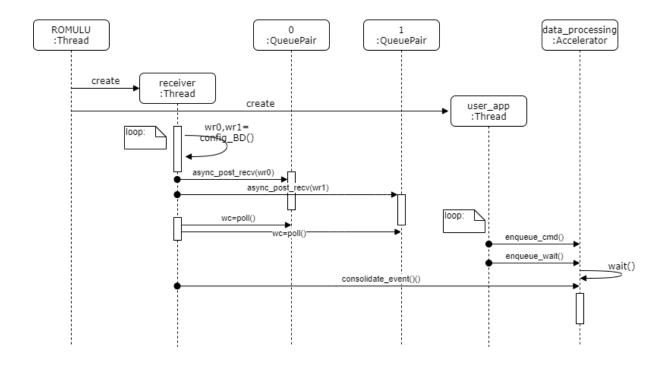

| 4.3  | ROMU sequence diagram                               |

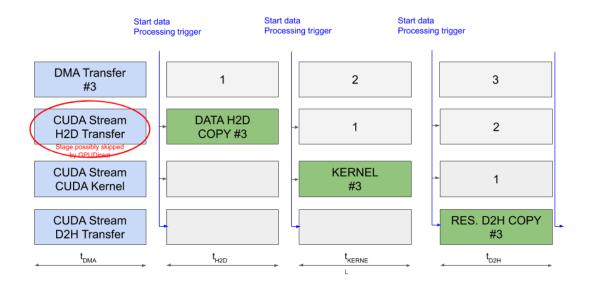

| 4.4  | GPU processing pipeline                             |

| 4.5  | Low latency synchronization mechanism               |

| 4.6  | RPU FPGA design                                     |

| 4.7  | Overview of an SSX Experiment                       |

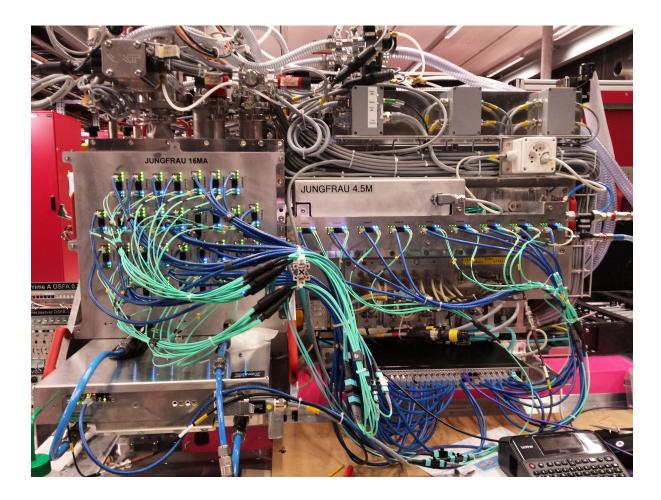

| 4.8  | Rear view of the Jungfrau 16M detector              |

|      | Maximum throughput along a GPU system               |

| 4.10 | CUDA Stream execution                               |

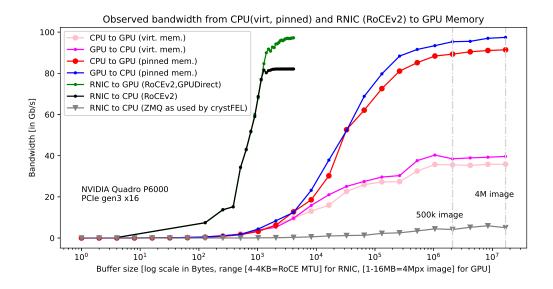

| 4.11 | Transfer throughput from CPU and RNIC to GPU memory |

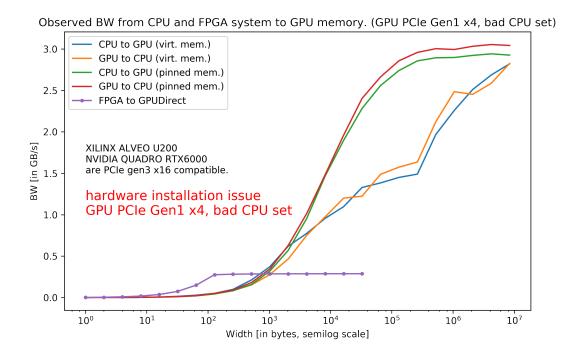

| 4.12 | Transfer throughput from FPGA board                 |

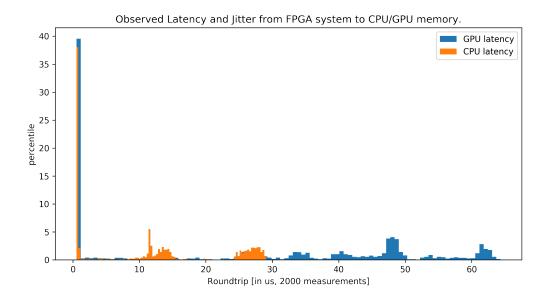

| 4.13 | PCI-e latency measurement                           |

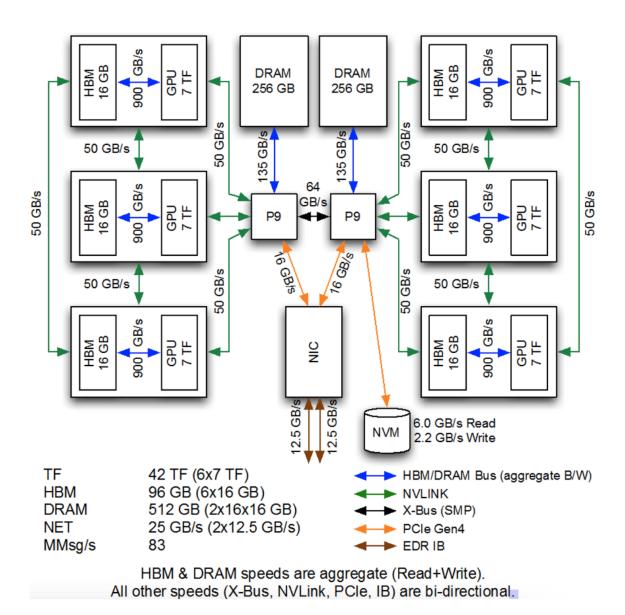

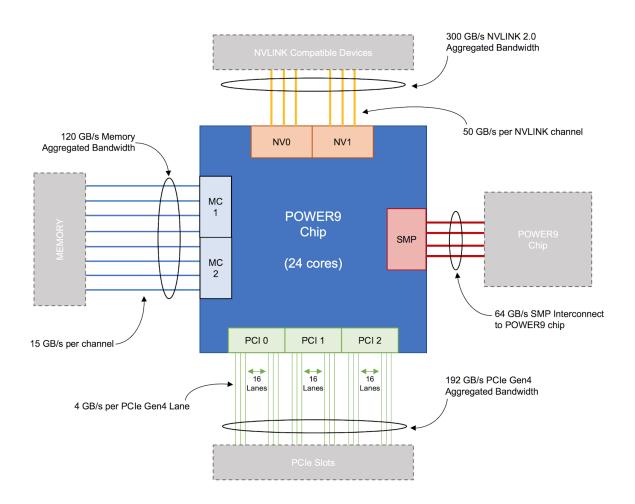

| 4.14 | IBM AC922 POWER9 Architecture                       |

| 4.15 | Overview of interconnect on the POWER9              |

| 5.1  | Overview of NVMEoF                                  |

## List of Tables

| 2.1 | RDMA variants                             | 31 |

|-----|-------------------------------------------|----|

| 3.2 | Available bandwidth without packet losses | 51 |

| 4.1 | GPU Results                               | 84 |

## Listings

| 3.1 | Buffer descriptors calculations            |

|-----|--------------------------------------------|

| 4.1 | Low latency task launch                    |

| 4.2 | AXI-Master interface                       |

| 4.3 | Host Application triggering FPGA computing |

| 4.4 | Raw data pre-processing using OpenMP 85    |

| 4.5 | OpenCL kernel                              |

| 4.6 | HLS Pipeline                               |

## Acronyms

**AXI** Advanced eXtensible Interface. 74

CPU Central Processor Unit. 12

CUDA Compute Unified Device Architecture. 17, 65

**DAQ** Data Acquisition System. 11

ESRF European Synchrotron Radiation Facility. 15, 19, 51

FPGA Field Programmable Gate Array. 12, 14, 27, 40, 72

GPU Graphics Processor Unit. 12, 14

**HLS** High Level Synthesis. 41

**HPC** High Performance Computing. 15, 31

I/O Input and Output. 22

MMU Memory Management Unit. 22

PCI-e Peripheral Component Interconnect Express. 17, 23, 49, 66

RASHPA RDMA-based Acquisition System for High Performance Applications. 15

RDMA Remote Direct Memory Access. 12

**REMU** RASHPA detector EMulator. 53

RNIC RDMA Network Interface Card. 12, 48

RoCEv2 RDMA Over Converged Ethernet. 17, 19, 93

ROMULU RASHPA back end receiver. 68

## Glossary

- **Data Transfer Process** is an ongoing data transfer Process between two RASHPA nodes. A RASHPA module can produce multiple concurrent DTPs from different data slices (temporal sampling) or from different Region of Interest (spatial sampling). 42

- **DMA** stands for Direct Memory Access and describes an inner computer component in charge of data transfer from one memory region to another. DMA can be of two forms: Memory Mapped or Streamed. 24

- **High Level Synthesis** is a development flow aiming at FPGA design using High Level language and concepts instead of convoluted low level, error prone, highly specialized techniques.. 74

- **RASHPA Buffer** is the memory region allocated in the destination computer for the data transfers. It must be compatible with DMA operations. 42

- **RASHPA Manager** is a software application in charge of configuring and monitoring a RASHPA system. It can perform capabilities retrieval of RASHPA nodes prior configuration, start/stop the acquisition and manage the errors. It uses XML telegram for communication on a dedicated control link. 42

- **RASHPA Processing Unit** is an hardware entity that can ingest incoming data flow from an RNIC in its internal memory and that can process those data when triggered properly.. 66

- **RDMA** Remote DMA is the generalization of the DMA concept to remotely connected computers. In this memoir, we focused on gigabit Ethernet links and RoCE protocol. 29

## ${\bf Acknowledgments}$

This work is part of the T2.a technology program proposed in the frame of ESRF-EBS Detector Development Plan (DDP).

## Chapter 1

## Introduction

|    | _  | 1      |     | 1 - |

|----|----|--------|-----|-----|

| ι, | on | 1 T. E | ınج | T.S |

| Controlled |                                                                                                                                                |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.1        | Making Science using X-ray Radiation                                                                                                           |  |  |

|            | 1.1.1 ESRF-EBS Grenoble, The European Synchrotron 4                                                                                            |  |  |

|            | 1.1.2 X-ray Detectors and Experimental Setup Overview 9                                                                                        |  |  |

| 1.2        | Full Throughput X-ray 2D Imaging Experiments                                                                                                   |  |  |

| 1.3        | Research Questions                                                                                                                             |  |  |

|            | $1.3.1  {\rm Data\ Transfer\ Issues\ and\ RDMA\ Mitigation\ Techniques}  .  .  12$                                                             |  |  |

|            | 1.3.2  Real-time Data Analysis with GPU/FPGA Accelerators  .  .  14                                                                            |  |  |

|            | $1.3.3  \hbox{Contributions to RASHPA Data Acquisition Framework}  .  .  15$                                                                   |  |  |

| 1.4        | Organization of the Thesis $\dots \dots \dots$ |  |  |

|            |                                                                                                                                                |  |  |

Exploiting the full performance of the new generation X-ray 2D image detectors in terms of throughput, is challenging when using existing hardware and software solutions. This thesis aims at proposing contributive techniques to mitigate these difficulties.

This first chapter will give a broad overview of photon science and the minimal prerequisites on detector hardware. Some X-ray imaging techniques demanding in processing power are presented as well. Then we will describe the problem in detail and present the original intentions for this project. The significance of the thesis and our contributions are then stated before finally specifying the outcome of our work.

## 1.1 Making Science using X-ray Radiation

Please note that this section provides merely a brief introduction to the long and rich history of X-rays.

X-rays have a history parallel to that of Modern Physics and to the general understanding of fundamental laws of electromagnetism in the late 19<sup>th</sup> century. This leads to the unification of formerly unrelated topics, such as light or electricity and mysterious artefacts in electrostatic or magnetic phenomenons.

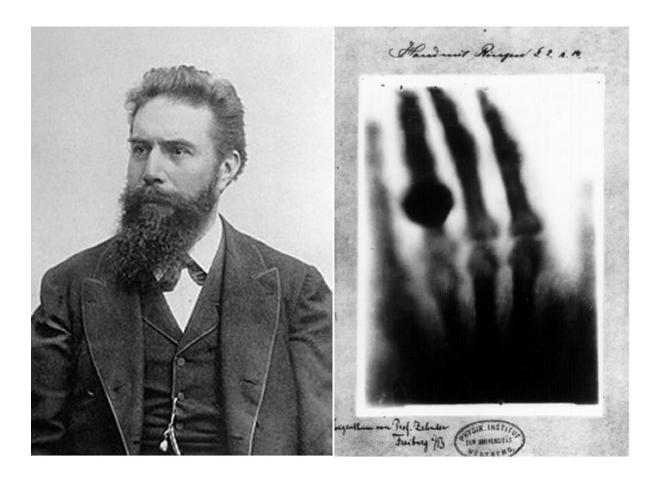

X-rays were discovered by chance in 1895 by W. Roengten, who noticed a faint shimmering from a fluorescent screen at a remote location while he was studying the effect of high voltage in vacuum tubes.

Shortly, he discovered some of the interesting properties of the invisible and yet unknown radiation and took the first radiography in history presented in Figure 1.1. Because he did not know their origin he named them X-rays after the x in mathematics, the symbol of an unknown value.

The first X-ray sources in the late  $19^{th}$  were evacuated sealed tubes. Last ones are the kilometer long linear accelerators called XFELs (XFree Electron Laser), built since late  $20^{th}$  century, and producing extremely short (femtosecond range) and intense X-ray flashes with the properties of laser light. X-rays produced in a sealed tube, XFELs or at a synchrotron facility are fundamentally the same form of electromagnetic radiations and differ only by their respective energy and by the process of how they are produced.

Charged particles (e.g., electrons and ions) moving at high speeds lose some energy when their acceleration is changed. This is the case when they hit the cathode in Crook's tube or when their trajectory is curved by a bending magnet. This lost energy is the source of the X-rays. Relativistic particles at high speed (close to the speed of light) are extremely energetic and produce intense X-ray beam.

There are no natural source of synchrotron radiation on Earth. But there are such natural sources in the Universe, e.g. in some rotating stars. Synchrotron Radiation (SR) is one of the most important emission processes in astrophysics.

Synchrotron radiation was first observed in year 1947 as a byproduct during the first high-energy-physics (HEP) experiments conducted in circular accelerators where particles get accelerated periodically when they go through an RF cavity. Thus, they acquire during each revolution, synchronously, more and more energy. This is the origin for the name. The first synchrotron accelerator, that could stand on a table, is shown in

Figure 1.1: Left: picture of W. Röngten. Right: The first medical radiography taken in history by W. Röngten, the hand of his wife Anna Bertha Ludwig and her ring. (Source: Wikipedia)

Figure 1.4. During these early discoveries, SR was mainly a kind of a nuisance for the experimentalists.

As the particle energy is higher, the produced X-rays are much more intense than those produced by Crooks-like tubes. A SR beam is also pulsed, highly collimated and has a narrow spectral range [44]. Indeed they have many interesting properties, that shortly attracted the attention of many researchers looking for powerful light sources.

Synchrotron radiation scientists became kind of parasites on nuclear physics experiments, during the so-called  $1^{st}$  generation synchrotron era, before they built their own facilities, those being the  $2^{nd}$  generation synchrotron facilities.

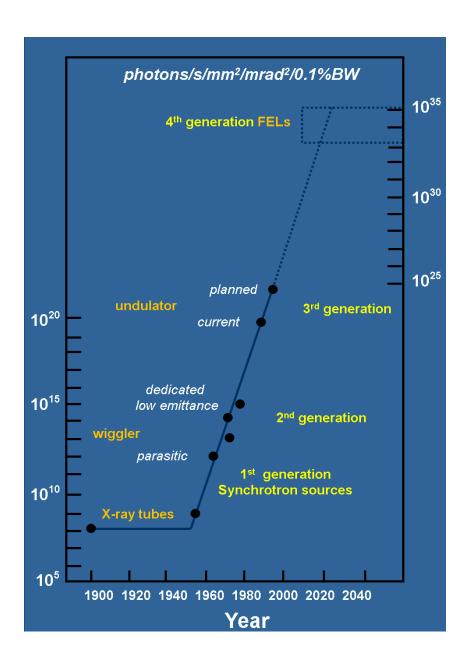

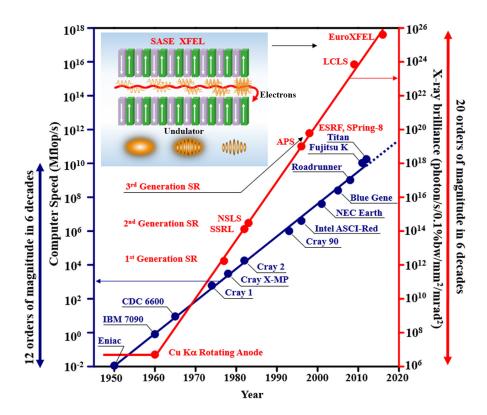

There has been an amazing increase in brilliance of X-ray sources, see Figure 1.3, and a successful new science and technology has emerged to fruitfully employ SR in multiple research fields. This has boosted new usages and applications in industry, structural biology, condensed materials investigation, anthropology or cultural heritage studies, etc. X rays are mainly used for observation purpose and may be used in combination with heated or cooling enclosure, high pressure diamond anvil, laser beam, etc.

SR facilities are essential to science today and are in use all around the world. The

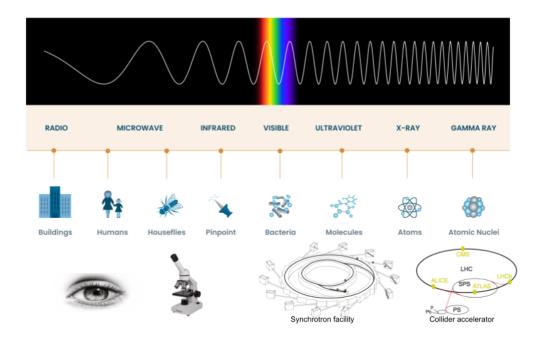

Figure 1.2: The electromagnetic spectrum comparing the size of objects that can be studied with various techniques. X-rays have the perfect wavelength necessary to perform investigations in material sciences.

fact is that X-rays have the right characteristics in terms of wavelength for many research fields as shown in Figure 1.2.

X-rays are not limited to 2D imaging based experiments. Many other techniques, fluorescence, spectroscopy, scalpel in brain surgery and uncountable other techniques are foreseen. However, in the context of this thesis, the focus will only be on the 2D image topic.

2D imaging techniques are not limited to collect digitized density variations of a sample, as done in the first X-ray image or modern scanners. It can also record scattering images containing information on the 3D atomic arrangement in a crystal. A high flux beam is likely to burn fragile samples during the data collection. Many techniques are under scrutiny in order to decrease the amount of radiation dose needed. This enables an increased acquisition rate in order to observe the kinetics of chemical reactions.

All this contribute to the success of X-ray science and explains why there are numerous SR sources operating all around the world, see Figure 1.5 and why so many scientists are competing for beam time.

### 1.1.1 ESRF-EBS Grenoble, The European Synchrotron

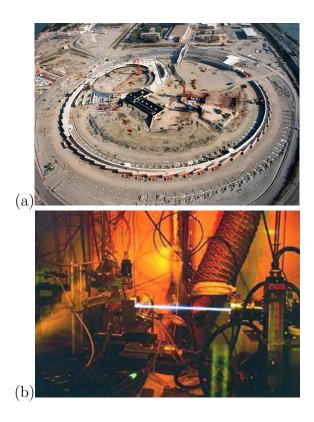

The european synchrotron project started in the 1980s, and construction work was completed 10 years later in 1995 see Figure 1.6. The ESRF accelerator ring was the first to implement Insertion Devices that boost brilliance by the mean of additive interference in

Figure 1.3: The brilliance measures the number of photons by unit of time, solid angle, square section. As no optical technique can improve it, it is considered as the best measure of X-ray flux. (Sources: J. Susini, ESRF)

Figure 1.4: From left to right: Langmuir, Elder, Gurewitsch, Charlton and Pollock made the first observation of the SR light around the vacuum chamber of a 1947 general electric synchrotron. (Source: NSLS, Brookhaven)

produced X-rays. Thanks to continuous innovations, the ESRF has since its early days been continuously in the top rank of the third generation synchrotrons.

A synchrotron radiation facility is a complex piece of engineering sections, including the core components shortly described below:

- a *linear accelerator* (linac), to produce the electrons at a given rate and give them a first acceleration, using a series of oscillating electric potentials.

- a booster synchrotron, to give them the equivalent of 6 GeV energy, in a fraction of a second, a level at which they behave as relativistic particles.

- a *storage ring*, a 850 m polygon, were electrons move straight in a high vacuum tube, focused by multi-pole magnets and bent by bending magnets at 32 edges.

- and multiple beamlines, tangent to the bending magnets, collecting the X-ray flux, that will be applied in the experimental hutches. Each beam line is 3 folded: optic hutch, experimental hutch, and control room.

- and there are also radiofrequency cavities (RF), vacuum pumps, beam alignment devices, timing system, computing and networking infrastructure, etc that we will not describe here.

Figure 1.5: World map of Synchrotron Radiation sources in operation or under construction. Proof of their invaluable service to science community, many SR facilities are in operation all around and counting. (Source: ESRF)

The ESRF is a world-class research center, with 700 staff members and a vast community of users. To keep its place in the world leading group of synchrotron, continuous upgrades and improvements are ongoing in all domains.

The ESRF resumed just recently to user-mode after one year and a half of shutdown. During this time the Extremely Brilliant Source (ESRF-EBS) upgrade program took place, which were mainly replacement of the storage ring. The ESRF is as of August 2020, the most brilliant fourth generation source!

Using recently invented HMBA (Hybrid Multi Bend Achromat) lattice by [51] in place of the standard bending magnets in the storage ring, a physicists dream enabling new science became a reality. Brilliance (x100) and focus (/30) have been considerably improved opening up new fields of investigation for fundamental research. It will also permit improved understanding of materials with the possibility to reach spatial resolution at the nanometer level, enabling unprecedented characterisation and understanding of materials and living matter.

Most of the 43 beamlines were kept as is with minor upgrades but eight are completely being redesigned.

Throughout this thesis, the ID29-EBSL8 beamline devoted to serial x-ray diffraction experiments, one of the most demanding in photon science, will serve us to exemplify the

Figure 1.6: The European Synchrotron, Grenoble, France. From construction work (a) in 1986 to the first light (b) in 1995: 10 years of hard work (Source: ESRF)

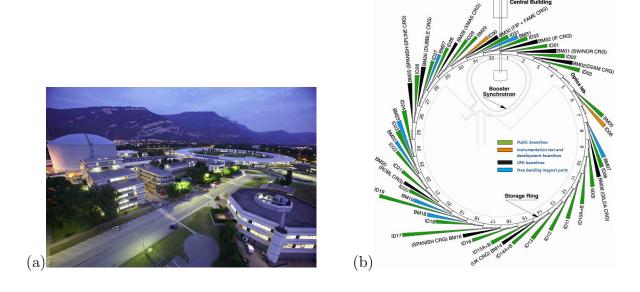

Figure 1.7: (a) The European Synchrotron Radiation Facility (ESRF) today in the European Photon and Neutron science campus (EPN) and (b) a map of the ESRF beamlines. (Source: ESRF).

data processing challenges.

### 1.1.2 X-ray Detectors and Experimental Setup Overview

X-ray science and SR are a vast research field and it is quite impossible to give a comprehensive overview of the topic. The size of the accelerator community to which SR contributes as a large part, the growing and counting number of facilities of any size all around the world, is a vivid proof that these light sources provide invaluable services in a broad spectrum of research topics. The work of [66] provides meaningful general insights on this topic.

For sure, not all X-ray experiments are producing large amounts of data and do not rely on online data processing. However a growing number does.

A selection of innovative demanding X-ray experimental setups is given below:

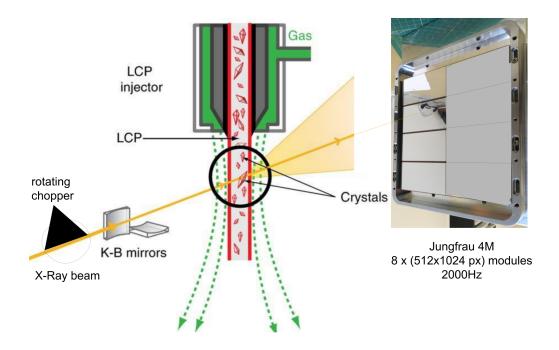

- In Serial Synchrotron X ray crystallography (SSX), i.e. diffraction experiments on proteins, a flow of a liquid containing small crystals is sent through a pulsed beam. The idea is to collect the signal of one unique crystal at a time. One of the major characteristics of serial diffraction is the amount of raw data produced. Most of the captured frames do not contain information, hence are useless. Up to 90% of all the collected signal is empty because no crystal is hit by the beam. The main data treatment is then to sort out frames to be saved and those which can be discarded. This selection is called the veto algorithm.

- X-ray Computed Tomography (XRCT) i.e. a scanner infers the density of the matter by measuring the image contrast. The first application of GPU computing for synchrotrons exploited the abilities of GPU to perform Fast Fourier Transform efficiently and ported the filtered backprojection algorithm for tomographic reconstruction [8]. This kind of processing is performed offline by PyHST2 software because the data collection needed to be completed before initiating the processing<sup>1</sup>.

- Coherent Imaging have appeared in the last decade at X Free Electron Lasers (XFELs) that were much brighter than SR and have a much more coherent X-ray beam. These sources are so bright that they blast the sample in femto-seconds but the electron cloud of the sample diffracts before the sample is destroyed. Collecting interference patterns from samples has paved the way to powerful microscopy techniques: Coherent Diffraction Imaging (CDI) and Ptychography<sup>2</sup> nowadays. They have become available on the most brilliant synchrotron sources.

Ptychography and other coherent imaging techniques rely on Fourier transform. Those analysis match perfectly with GPU computing as stated by [11] and is illustrated by the success of the PvNX suite<sup>3</sup>.

<sup>&</sup>lt;sup>1</sup>https://gitlab.esrf.fr/mirone/pyhst2

<sup>&</sup>lt;sup>2</sup>image reconstruction technique using many interference patterns obtained as the sample is displaced to various positions

<sup>&</sup>lt;sup>3</sup>https://github.com/nx-python/PyNX

Not all computations are possible online but a lot of low-level image pretreatment are: Bragg's peak detection, background normalization, mean and standard deviation calculation, thresholding, outliers removal, masking, rejection, ...

The new generation of X-ray detectors features cutting edge capabilities and benefits from the improvement in different fields of technology. Some of the most promising improvements are listed below:

- Larger sensor area and modular design for a wider acquisition area. From photons to digital value, there is a complex process, starting with photon to electron transformation by various means. Large sensors are difficult to manufacture. Therefore large detectors are comprised of assembly of multiple modules side by side.

- Higher pixel number by surface unit, higher acquisition rate and lower relaxation time. Last decades has seen the emergence of pixel detectors where every pixel embeds enough electronics to count each photons individually, benefiting from the better integration of ASIC chips. Therefore, a larger set of counting capabilities is possible, such as adaptive gain, pixel binning (merging in a single point the energy collected from neighboring pixels), etc. They are now collecting images routinely at hundreds of Hz and even a kHz. This produces a larger amount of raw data, in more complex formats and creates compelling needs for online data processing.

The SR community has identified some key topics to drive productivity and user experience in X-ray science [62]. Beside resolving high-throughput data transfer challenges, three different classes of crucially urgent problems are emerging. They could be worked out by online data processing. These challenges are sorted by related latency and are listed below:

- At human rate (fps < 1), it would be desirable to provide a minimum feed-back to the user, in order to monitor the proper functioning of the current experiment

- At control system rate (fps < 100), it would be interesting to enable remote control of experiments, automatically survey of sample alignment and similar control loop.

- At full acquisition rate (fps > 1000), performing low level data processing prior data rejection or compression. This includes raw data pretreatment needed prior any other processing, geometry reconstruction (offset, rotation), outliers removal (bad pixel) or masking (beam stop), binning...

In this context, the support of new computing hardware such as GPU and FPGA boards is clearly a way to explore. But this is not yet the end of standard CPU computing that are also evolving. By example, an attempt to tackle the challenges of sieving out in real time the data produced by one of the most challenging detector available as of today (Jungfrau 32M) is presented in [29] and this work evaluates the vectorized instruction set of a standard CPU.

All these problems are mostly addressed by RASHPA framework, demonstrating the strengths of the concepts of the work carried out.

## 1.2 Full Throughput X-ray 2D Imaging Experiments

Today the throughput of advanced detectors and the needs in associated online data processing are evolving faster than the capabilities of standard computers. Some of the encountered issues are related to the data throughput and the afferent bottlenecks along the data path. The others are related to the processing power required for the data processing itself and will be discussed later. Of course, these problems of transfer and processing of data are not specific to X-ray detectors. The following dissertation and proposal might apply to many other Data Acquisition System (DAQ) systems.

High throughput data transfer itself is a creative research topic and, in this field, innovative technologies emerge every day. However, there is yet no *one-size-fits-all* solution and probably never will be.

Targeting specifically 2D image detectors, we are somewhat narrowing the problem and are more prone to propose specific solutions, taking into account their peculiarities. Some of these particularities might be considered as extraneous constraints to the problem, e.g. the limited processing power of the detector-embedded readout-electronics. We could instead take benefit of other particularities, e.g. assuming that data transfer will be lossless in a lab environment. Thus, with properly configured and correctly sized networking devices, no packet losses should happen. That let us choose a lightweight transfer protocol.

Since detector developments are long processes that commonly take 5 to 10 years and detectors usually stay in operation around 10-20 additional years, the generality of the proposed system should be strongly considered. Most components of the framework should ideally be hardware agnostic and able to cope with the most disruptive future innovations. Of course, hardware implementations demonstrates the advantages the solution can offer to the user and are essential to verify that the targeted specifications are realistic. Due to the lack of available real detectors featuring all the advanced functionalities, we have developed simulators in order to benchmark the various alternatives of communication protocols.

The developed framework is intended to be scalable, i.e. possibly address the most demanding DAQ systems, but also more cost effective solution deprived of the latest innovative and expensive hardware. It is designed with X-ray detectors in mind, producing high throughput data streams, but the framework should also match the low-latency requirements of fast-feedback and control system.

The other significant characteristics of 2D imaging is the huge amount of data which is generated.

New generation pixel detector, as the PSI Jungfrau shown Figure 1.8, embed more and more processing power at the pixel level. Consequently the detector readout electronics that is collecting the data can generate huge throughput.

In many serial experiments, the setup comprises an automatic sample changing system, such as robotic arm, rotating disc or liquid jet carrying samples into the X-ray beam. Experiments like these producing large images (sizes in the MB range), acquired at high repetition rates (frames per second in the kHz range), are summing up in Tera Bytes of

data per minute. Obviously, merely storing the raw data would put a considerable strain on the storage file system.

As a consequence, end user will have to be ready to provide an online rejection algorithm at the time of the acquisition.

Nevertheless, the ubiquitous workflow: acquisition, transfer, storage and eventually batch processing, is no more the most effective. It now seems mandatory to perform online processing and proceed to some form of data compression or even rejection. These tasks require a considerable computing power and a high throughput that overwhelm traditional hardware architectures.

This challenge is not specific to photon science but it is tightly coupled to the previously mentioned data transfer bottlenecks. Many research fields focus on this topic and the impending end of Moore's Law has started a rethinking of the way to solve Big data analysis (see Figure 1.9). Certainly, the peak processing power of a single processor core does not increase the way it did, but hopefully new paradigms are emerging such as parallel processing and specialized hardware. The advent of high performance computing accelerators during the last decade, mainly based on Graphics Processor Unit (GPU) and Field Programmable Gate Array (FPGA), offer new opportunities to solve the computationally intensive tasks. One outcome of this work is the assessment of data transfer directly into the accelerator's memory, without neither Central Processor Unit (CPU) intervention or staged memory.

## 1.3 Research Questions

As the prerequisite for the work, we have identified the main causes of data transfer bottlenecks from detector to the standard computing unit. They are of multiple and mixed origins, rooted in both hardware and software.

## 1.3.1 Data Transfer Issues and RDMA Mitigation Techniques

In the early times of computing hardware the Central Processing Units (CPUs) where operating much faster than Input/Output (IO) devices. Real-time data processing was possible but this has not been true for a long time. The most annoying issues are linked to the complexity of the software stack used in modern architecture. Multiple data copies are also occurring between supervisor code executing in kernel memory space and user application in user space. In addition, the trivial task of using a CPU only for data transfer purposes, from input device to destination memory, wastes CPU cycles that should be more beneficial to user applications. The CPU must also acknowledge and handle interruptions issued by the communication device, using kernel context switches that are highly inefficient when using high-throughput links.

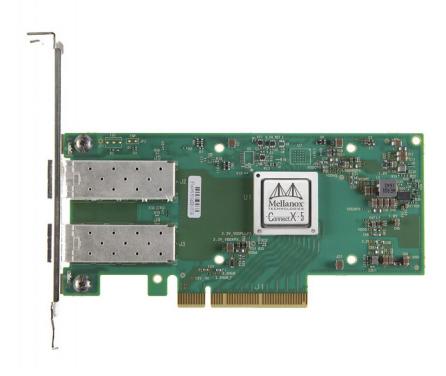

All these issues might be mitigated using Remote Direct Memory Access (RDMA) techniques and specialized hardware such as RDMA Network Interface Card (RNIC). DMA engines are specialized components embedded in computer devices such as RNICs and GPUs that can autonomously handle data transfer from PCI-e devices to the main memory or the reverse. CPU is thereby kept available for other tasks after having per-

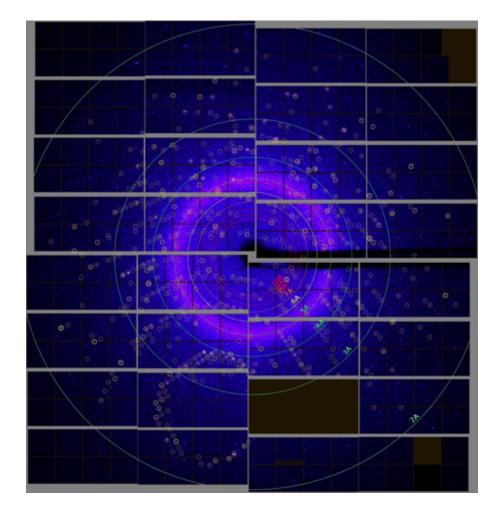

Figure 1.8: A scattering image produced by a PSI Jungfrau 16M detector featuring 32 modules, each of  $1024 \times 512$  pixels, 16 bit raw data, operating up to 2.2 kHz. Final image reconstruction from independent modules requires geometric transformations. (Sources: Shibom Basu, EMBL)

formed the data transfer configuration. It is even possible to transfer data from one PCI-e device to another one, using peer to peer (P2P) PCI-e DMA, completely bypassing intermediary staged CPU memory. To operate properly, all that machinery is using a dedicated programming model that is slightly different from the conventional one. The abstraction layer fulfilled by this project will perform the tricky details of the low-level implementation without the end user even noticing.

RDMA is the generalization of this mechanism to the remote computer. Instead of a single DMA engine, there are two in consideration: one at the source and a second at the destination. They are inter-connected by network links and the data are streamed between both ends. We have performed an evaluation benchmark of the alternative solutions available and selected those compatible with the requirements of the detector electronics.

Figure 1.9: (a) Moore's Law represented for the computer speed of CPU chips compared to the X-ray brilliance of coherent light sources. While the computer speed has increased 12 orders of magnitude in 6 decades, the X-ray brilliance has improved by 20 orders of magnitude in 6 decades. The inset shows the extremely intense XFEL pulses. (Sources: UCLA Coherent Imaging Group)

## 1.3.2 Real-time Data Analysis with GPU/FPGA Accelerators

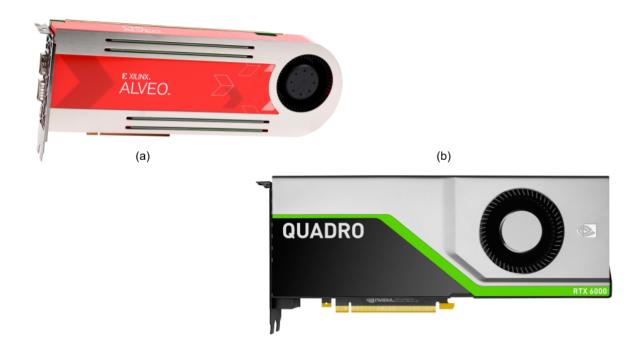

With the advent of the end of Moore's law, the peak processing power of a single CPU appears to be bounded. This enforces the use of heterogeneous computing systems, featuring new highly parallel hardware accelerators that have become more easily available the past 10 years. Among these are the well known Graphics Processor Unit (GPU), which is already successfully implemented in many demanding fields. But also Field Programmable Gate Array (FPGA), which has a still more limited adoption, but is geared towards critically low-latency scenario.

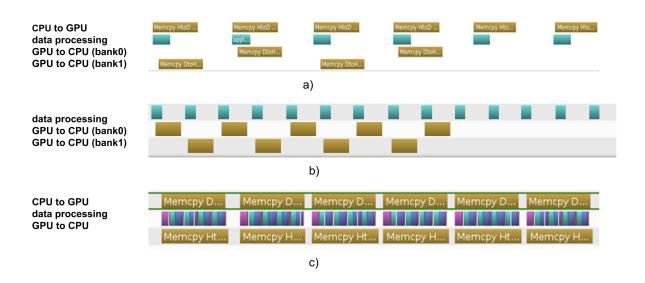

However, if those devices are efficient number crunchers, they are not fully autonomous black boxes, and thereby remain tightly coupled to the host computer. The main CPU must issue sequences of commands on a regular basis and must monitor the accelerator status as well. These commands include: i) explicit data movement from main CPU to accelerator memory, in both directions: Host to Device (H2D) and Device to Host (D2H), ii) launching the code processing on the accelerator synchronously with the DMA engine at data transfer completion.

This whole work of configuration cannot be done once, at the initial startup of FP-GA/GPU data processing. It definitely must be performed on the fly during the whole process, at least for GPUs.

### 1.3.3 Contributions to RASHPA Data Acquisition Framework

This work is part of a larger project, namely the RDMA-based Acquisition System for High Performance Applications (RASHPA) framework initiated by the Instrumentation Service and Development Division (ISDD) at the European Synchrotron Radiation Facility (ESRF) (ESRF). The initial ideas of the RASHPA framework date from year 2013 [37], but remained for a long time at the stage of draft specifications. In the frame of the ESRF Detector Development Plan (2017 DDP), it was decided to restart the project and to continue until the achievements of the work would be satisfying.

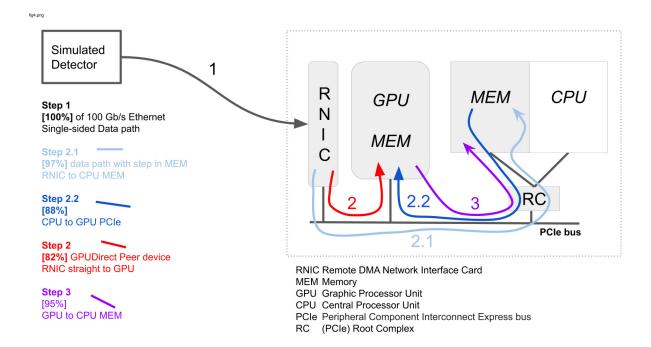

In addition to the assessment of the RDMA over Converged Ethernet (RoCE) as a sustainable and robust transfer solution in the frame of RASHPA, our contribution is an extension to this framework called RASHPA Processing Units (RPUs). We have added support for data processing by GPU & FPGA accelerated code, thereafter called *kernels*, thus offering a comprehensive solution to the online data processing challenges in the context of X-ray techniques.

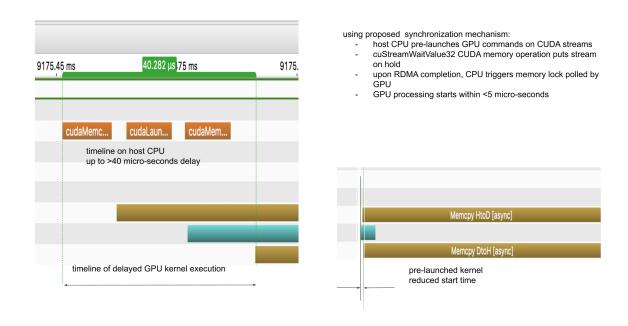

This extension includes a low-latency synchronization mechanism between RDMA network interface cards (RNIC) and the processing hardware, either CPUs, GPUs or FPGAs accelerator in charge of the online data processing. The transfer of the detector images onto the accelerator is made to overlap with the computation carried out, potentially hiding the transfer latency.

By applying a solution which is rarely reported in the literature, we managed to get the GPU kernels pre-launched and put them on hold in advance, in order to start them as soon as possible after being triggered by the RDMA engine at the end of the data transfer. The persistent kernel in the GPU, a continuously spinning kernel, despite being somewhat orthogonal to the underlying GPU's hardware, is investigated to limit the overhead due to kernel launch time. In addition we attempted to provide a programming methodology.

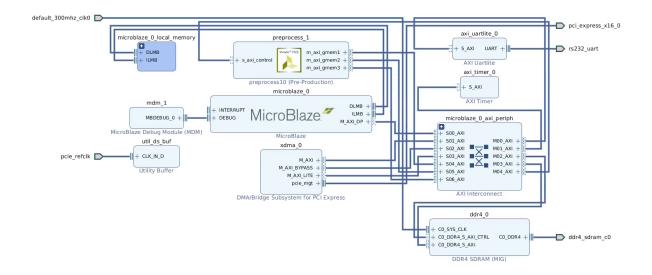

Another key contribution aiming at low-latency use, such as seen in alignment or control systems, is the successful deployment of the RASHPA paradigms with FPGA based accelerators. FPGAs have formerly been confined to very low level I/O. However, design of customized systems with demanding timing requirements are getting attention in High Performance Computing (HPC) fields for their highly configurable model and latency performances. In the same way as for other RPU instances, data are moved directly from the RNIC to the FPGA board internal memory, bypassing CPU and main memory, to be processed by user-defined IP blocks. These IP blocks usually designed using convoluted low level HDL, are evaluated in this work using high level synthesis language applying standard math expressions.

We supplemented the RASHPA framework with a collection of kernel modules, addressing the challenge of memory allocation suitable for DMA. This includes large (multi GB) contiguous memory allocation in Linux host. We also address memory allocation on

internal memory of GPU and FPGA devices. This is pertaining to PCI-e peer to peer compliant devices which memory can be accessed directly from network card.

Scalability and versatility of the proposed system is exemplified with several implementations of detector simulators. These are either full fledged software or FPGA-based implementations and hardware accelerated RPUs. They feature rejection and compression pipelines which are suitable for serial diffraction experiments conducted on synchrotrons on different hardware platforms and links.

The significance of this thesis it that the actual situation hampers the use at full capacity of existing new generation X-ray detectors and is detrimental to foreseen experimental setups. The data transfer architectures used today for data copying and dispatching are very CPU intensive. They implicitly attain performance limitations that impose the reduction of the maximum achievable frame rate or duty cycle of the detectors, consequently never exploiting their full capability. As a detrimental result, online data processing at their maximum throughput is simply not achievable.

Thanks to the approach proposed in this thesis, the RASHPA framework will hopefully help the scientists to get their result, or at least a preliminary feedback on them, in real time. This was a compelling need long hoped for, but only achievable by building the missing bridge between data flow and processing system. This is now becoming reality thanks to recent breakthrough in RDMA techniques and the tremendous processing power, low-latency of GPUs or other massively parallel architectures, like FPGA accelerators.

## 1.4 Organization of the Thesis

This thesis work emphasises the detailed specifications of efficient data transfer and processing framework for X-ray detectors, leveraging zerocopy / RDMA techniques.

The initial RASHPA draft, limited to transfer and storage into CPU memory problematic has been extended to data processing itself and generalized to support hardware accelerators. It takes benefit from GPUs and FPGAs, fully bypassing main memory and the CPU bottlenecks encountered in traditional processing flow.

The main contributions of this work can be outlined according to the chapters. After this introduction, the remainder of the memoir is structured as follows:

• The chapter 2 State of the Art: Data Transfer & RASHPA, gives a general overview of the key technologies involved in high throughput data transfers. We present the flaws of standard hardware and software and expose RDMA alternative capable to perform direct data movement from detector head to computing unit.

Then we present today available massively parallel processing hardware such as GPUs that are ubiquitous in High performance Computing (HPC) and FPGAs as well. These are emerging as a new competitive technology in the field of ultra low latency data processing.

The key concepts and philosophy behind RASHPA in its primitive stage are presented. Then we introduce our main contribution, the concept of RASHPA Pro-

cessing Unit (RPU), that supplements the already existing RASHPA Receiver (RR) with data processing capabilities.

• It is followed by chapter 3 RASHPA Data Source Simulators, where we perform the assessment of RDMA Over Converged Ethernet (RoCEv2) as a RASHPA-compliant protocol and describe the chosen approach to integrate a processing unit into a RASHPA system. We propose to add two new core components to the existing framework: i) a scheduler application in charge of event handling and recurring configuration, ii) an address translation system geared towards DMA engine of the data transfer in the RNIC of the receiver.

Adequacy study and performance measurements lead us to the development of detector simulators as proof of concept. First version is a full fledged RASHPA compliant mockup. It is targeting mainly the development of a code base hiding as much as possible the programming details related to RDMA transfer.

In addition, two FPGA-based RASHPA simulators are also presented as a feasibility study: i) a REMU-PCIE version, leveraging data transfer over Peripheral Component Interconnect Express (PCI-e) long distance links and performing its assessment, i) a REMU-ERNIC version, evaluating a recently available Xilinx IP (ERNIC) featuring RoCE protocol, and comparing its performance with an ESRF custom IP.

• Then chapter 4 Online Accelerated Data Processing using RASHPA, presents several versions of RASHPA data processing units: i) multi-threaded/vectorized application running on standard CPU that serves as a reference platform, ii) GPU accelerator, using Compute Unified Device Architecture (CUDA) on NVIDIA board or OpenCL kernel on AMD board, iii) configurable FPGA device, featuring ultra low latency data processing by programmable IP block developed by applying High Level Synthesis approach.

The synchronization of data processing at the end of RDMA transfer is discussed and implemented accordingly.

The assessment of a comprehensive acquisition chain is exemplified by online data analysis such as found in serial crystallography setup, featuring raw data pretreatment, rejection and compression algorithms.

- Finally chapter 4 concludes our work, summarizes our contributions and provides an outlook:

- i) Acceptance by the end-user of a new and complex framework might be improved with a better integration to more widely recognized parallel computing framework such as ESRF internally developed Lima [47], or Python Numpy scripting language which is very popular in the scientific community.

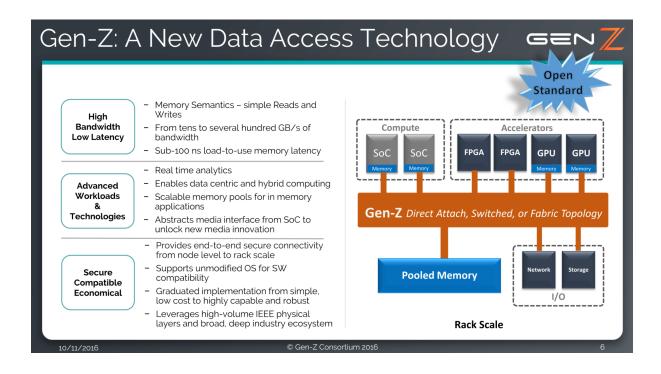

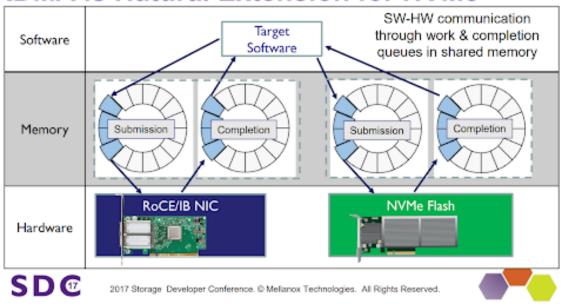

- ii) The direct data transfer to remote SSD, so called disaggregated storage, has gained momentum recently, as NVMEoF and RDMA technologies are well fitting together. The RASHPA philosophy being sufficiently generic, it will apply naturally to the crucial challenges of data persistence.

## Chapter 2

# State of the Art: Data Transfer & RASHPA

| Contents |        |                                                              |    |  |  |  |

|----------|--------|--------------------------------------------------------------|----|--|--|--|

| 2.1      | High-t | hroughput Networking                                         | 19 |  |  |  |

|          | 2.1.1  | Bottlenecks Related to Memory Management                     | 21 |  |  |  |

|          | 2.1.2  | PCI-e Interconnect                                           | 23 |  |  |  |

|          | 2.1.3  | Direct Memory Access Overview                                | 24 |  |  |  |

|          | 2.1.4  | Memory Allocation Challenges                                 | 26 |  |  |  |

|          | 2.1.5  | Limitations of Conventional Networking Techniques            | 27 |  |  |  |

|          | 2.1.6  | Overview of RDMA Techniques                                  | 29 |  |  |  |

|          | 2.1.7  | Prospects beyond DMA Techniques                              | 33 |  |  |  |

| 2.2      | Hardw  | are Accelerators Overview                                    | 34 |  |  |  |

|          | 2.2.1  | GPU accelerators                                             | 35 |  |  |  |

|          | 2.2.2  | PCI-e P2P Transfer into GPU/FPGA Device Memory $\ .\ .\ .$ . | 37 |  |  |  |

|          | 2.2.3  | Parallel Algorithms                                          | 39 |  |  |  |

|          | 2.2.4  | FPGA Accelerators                                            | 40 |  |  |  |

| 2.3      | The R  | ASHPA Framework                                              | 41 |  |  |  |

|          | 2.3.1  | Paradigms                                                    | 41 |  |  |  |

|          | 2.3.2  | Overview of the Frameworks in HEP or Astronomy               | 43 |  |  |  |

|          | 2.3.3  | Contribution to RASHPA Processing Unit Specifications        | 44 |  |  |  |

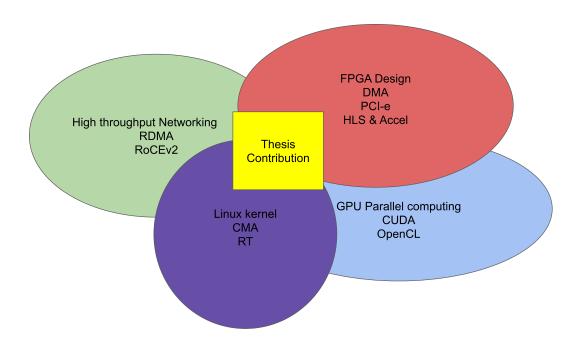

This chapter outlines what we learned from previous contributors to the field. As illustrated in Figure 2.1, this work is related to multiple and rather independent topics. In each domain, it is often dealing with unusual or corner case developments. We had to dig into cumbersome or not well documented features of API, encountered numerous issues caused by utilization of not yet mature technologies and have been struggling to get the advertised features working. Our main challenge has been devising generic components without relying on specific features of proprietary technologies.

These topics are mainly related to computer sciences, high performance networking and parallel processing, especially leveraging GPU coprocessors.

At first, an overview is given of the RASHPA Framework in its initial state at the beginning of this work. Then we present the methodology applied to perform the assessment of RDMA Over Converged Ethernet (RoCEv2) as a satisfactory RASHPA protocol and subsequently how has been implemented data processing support into the framework.

We then present some considerations on Linux operating system internals related to memory allocation, real time scheduling and high performance computing relevant with this work.

In this dissertation, the review of parallel algorithms is kept to the minimum. The algorithms are related to X-ray crystallography but the proposed implementations are simplistic as we are focusing on data transfer and synchronization mechanisms, rather than on data analysis itself. At this stage of the project, the only thing that matters, is the timing requirements which must remain compatible with the acquisition frame rate.

The rest of this chapter provides a presentation of the general concepts & philosophy behind the RASHPA framework that is the foundation of this thesis. Here is defined the working principle of a RASHPA Processing Unit.

## 2.1 High-throughput Networking

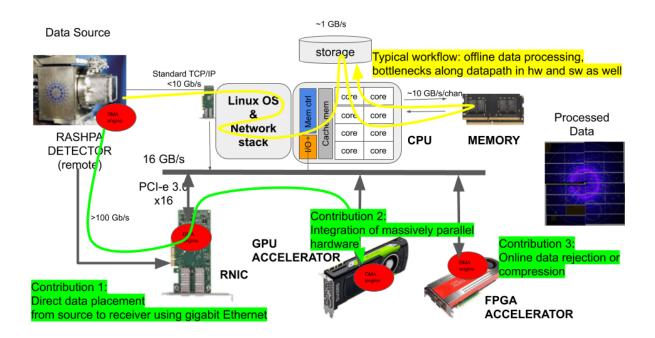

This section comprises discussions on the origin of the multiple bottlenecks encountered during data transfer. Figure 2.2 give an overview of the different devices and relative throughputs of the interconnects implemented in a typical acquisition system.

Data transfer bottlenecks may appear in multiple locations along the data path. They might be related to capacity of the links, to the hardware device in charge of the data transfer itself or to the software in use to perform the data movement. The affected data transfer throughput will obviously be capped by the slowest one.

The potential issues in the list presented below will be described and it will be specified which one are addressed by our contributions:

• The bottlenecks inside the detector electronics are not discussed in this work. This is the purpose of the readout electronics embedded in the detector side to solve these issues and for the rest of this project, we assume that the detector is able to push data on the network links at its full capacity. The actual work performed to design suitable RASHPA compliant detector electronics, performed by other contributors of the European Synchrotron Radiation Facility (ESRF), will not be described in this thesis [32].

Figure 2.1: This thesis embraces multiple research fields and topics of diverse technologies.

- Contention in network links from detector to the remote computing unit is also out of scope for this work. A RASHPA system is intended to have its own network infrastructure. If network infrastructure is shared with different applications and computers, it is possible to tune the network devices (switches) and reserve the required bandwidth for the data acquisition system. Using modern switches, Quality of Service (QoS) is configurable and neither packet loss nor contention will occur in a lab environment. However a lossless network is mandatory for proper RDMA transfer<sup>1</sup>.

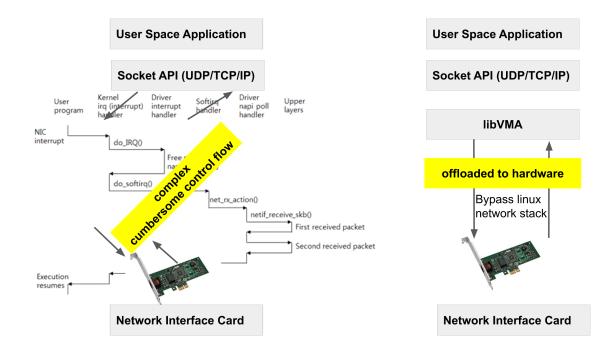

- The transfer from a Network card to the CPU memory by user application is the main bottleneck. Historically, due to the complexity of operating systems (OS), multiple data copies were required between driver running in kernel space and application in user space [33]. Handling the interrupts coming from the NIC board by the CPU was inefficient as well. These issues are addressed by RDMA techniques that are used extensively in this work. The highest bandwidth network cards commercially available are using this techniques. However, it is worth to note that many progress have been done in the Linux kernel design and networking driver as well.

- A CPU application fetches data and code from main memory. This uses the memory channels of the processor, which have various performances depending on the access pattern. Accesses to subsequent and properly aligned data (called coalescent) are

<sup>&</sup>lt;sup>1</sup>https://community.mellanox.com/s/article/understanding-qos-configuration-for-roce

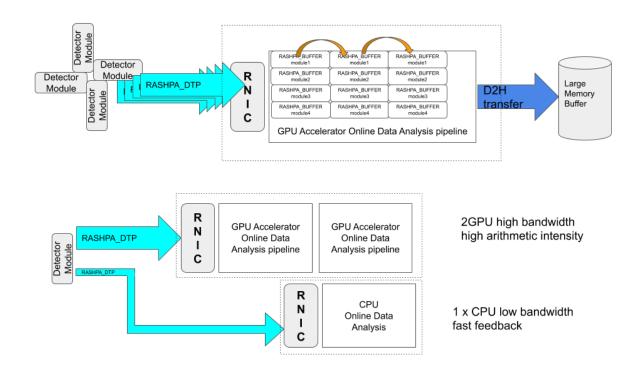

Figure 2.2: An overview of hardware in use and the general working of the investigated use case. A remotely connected X-ray detector by Gigabit Ethernet links produce data to a computing unit. On top is presented the standard solution: offline data processing by CPU. The proposed solution, below, features RDMA network card that offload CPU from data transfer and bypass software bottlenecks. Massively parallel hardware accelerators perform the online data analysis.

most efficient than random accesses to scattered data. It also greatly depends on the hardware topology in Non Uniform Memory Access (NUMA) systems as presented in [43]. Good CPU affinity and coalescent accesses are the key points of an efficient data processing.

## 2.1.1 Bottlenecks Related to Memory Management

We will at first consider the bottleneck issues inside the computer. Subsequently, we will deal with the network connected devices.

There is many different memory hardware in modern CPU design. The Dynamic Random Access Memory (DRAM) is used as main storage for data and instructions. It features high density storage but requires periodic refresh that limits its performances. Static Random Access Memory (SRAM) are found in Level 1 or 2 CPU caches. They are much more efficient in term of speed than DDR but more costly in term of power consumption and they require more transistors in the silicon chip. They are therefore available in more limited quantity<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup>one DDR cell: one transistor by bit, one SRAM cell: 6 transistors or 4 + 2 resistors

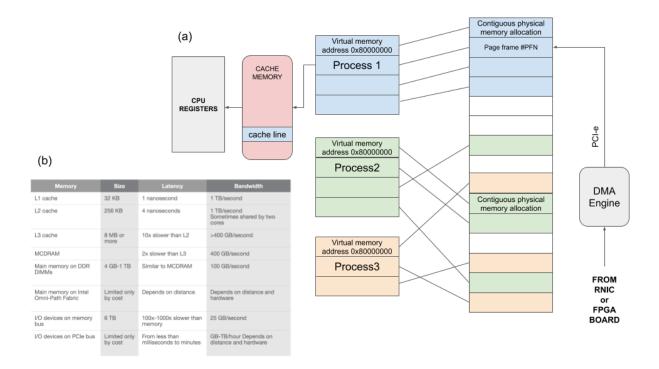

All these kinds of memory are used in the computer architecture. There is an access hierarchy, based on their relative speed and capacity as shown in Figure 2.3. Most frequently accessed data are stored in *cache line* of 64 bytes in high speed *memory cache*. These caches are embedded in each processor core (Level 1) or shared by multiple cores (Level 2). Caches are automatically flushed/invalidated when they are full or when the associated physical memory changes as in case of DMA transfer. Maintaining cache coherency takes time.

In addition, for robustness and security reasons, Linux operating system implements a sophisticated virtualization machinery to perform memory addressing. Data and instructions are referenced by virtual addresses that are translated to physical addresses by a Memory Management Unit (MMU) on the basis of four look-up tables, and cached in a Translation Lookaside Buffer (TLB). All processes are virtually executing at the same address, i.e. 0x80000000 in Linux system, but obviously, code and data are actually stored at different physical memory locations. A process has only access to its code and data segment, but not directly to other processes nor to kernel memory space. The mapping between virtual address and physical memory is made on the basis of pages. These pages are usually 4 KB long. The page location might be transparently changed by the Memory Management Unit. Memory pages are reputed movable when they are not explicitly pinned. Thus the memory management system can mitigate memory fragmentation by the aggregation of large chunks of contiguous free space.

Processors have at least two modes of operation referred to as rings, user and supervisor, which change the available instruction set in a given mode. It is allowed only in supervisor mode to perform Input and Output (I/O) operations or MMU configuration. One can go from user to supervisor mode only in a controlled way using interrupts or system-call. To ensure robustness of the system, user applications are denied direct access to supervisor space. Data buffers must be copied by kernel code to and from memory in application user space to and from kernel module or driver code memory space. Going from one run level to the other, called context switching, has a cost in time as it is storing register contents in the stack, and is restoring them later.

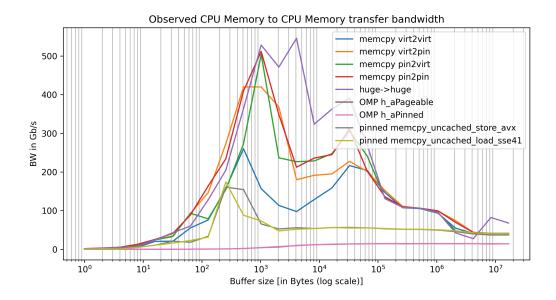

All this clever machinery, added to multiple translations involved in virtualization to translate from virtual to physical address, has a time budget that may not be negligible at high throughput. Figure 2.4 shows the different bandwidth measured during data transfer in memory.

Modern processors also feature rich sets of *vectored instruction* or Single Instruction Multiple Data (SIMD) applying once the same operation on multiple data such as Intel Intrinsics<sup>3</sup>. Application performances benefit automatically from these instructions generated by a properly configured compiler. Effective Vectorization with OpenMP SIMD is presented in [20].

The proposed system has to perform both smoothly and efficiently the foreseen data transfer while preserving virtualization, cache coherency and user / kernel space isolation. Bypassing the bottlenecks will require new approaches presented throughout this memoir.

$<sup>^3</sup> https://software.intel.com/sites/landingpage/IntrinsicsGuide/\\$

Figure 2.3: (a) Memory Hierarchy in modern computers includes several levels of caches. Data migration and coherency is performed by specialized hardware. Memory Management Unit performed the address translation related to virtualization. Table (b) shows some numbers on bandwidth and latency.

#### 2.1.2 PCI-e Interconnect

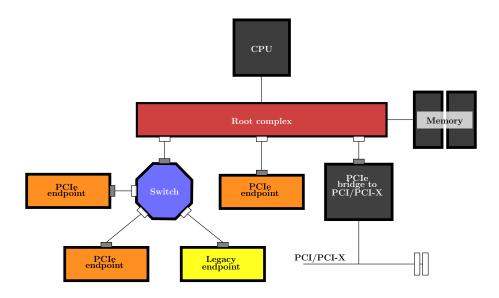

Peripheral boards and devices are connected to CPU and main memory by Peripheral Component Interconnect Express (PCI-e) which has its own specific data transfer limits.

The today standard, PCI-e gen 3.0, can carry up to 8 Gb/s per *lanes*. 1, 4, 8 or 16 lanes are generally available on a given device, depending on the processor capabilities. Hence a throughput of 128 GT/s could be expected for a PCIe gen. 3 device with a x16 width. A host processor (server versions) has generally 48 (Intel) or 128 (Amd) lanes.

Thus, PCIe gen3 x16 maximum bandwidth is approximately 126 Gb/s taking into account diverse overhead and data encoding. However, the observed throughput on commercially available hardware such as GPUs or FPGAs is capped around 12GB/s when using standard driver<sup>4</sup>.

*PCIe Root Complex* ensures transfer from/to device to/from main memory or from device to another device (peer to peer PCI-e (P2P) transfer). PCI-e switches can route data transfer from one PCI-e device to another on the same switch, completely bypassing the CPU.

The inter-node transfer performance vary mostly according to CPU affinity as shown Figure 2.6 and this is especially important for RNIC as explained in [36]. In servers

<sup>&</sup>lt;sup>4</sup>https://www.xilinx.com/support/answers/68049.html

Figure 2.4: Observed CPU to CPU bandwidth by several techniques and memory type. Due to cache size effect, small size transfer from pinned memory are the fastest. The numbers greatly depend on the chosen hardware, the cache hit ratio, etc and are given only for comparison purpose on the same server.

with multiple processor sets (or even on some high end CPU), there are multiple PCIe interconnects, at least one for each CPU. As the inter-CPU set interconnect<sup>5</sup> is a severe bottleneck, it is wise to allocate memory on the same interconnect as the CPU core in use and the PCI-e device.

## 2.1.3 Direct Memory Access Overview

Direct Memory Access (DMA) is a key feature to perform high bandwidth transfer for PCIe based applications. DMA frees up CPU resources from being wasted for data movement and helps improving the overall system performances. A CPU performs data transfer staged in its internal registers, requiring two operations: loading from memory to register, then storing. It can generally perform 8, 16, 32 or 64 bit wide (aligned) memory access. However, using instructions from the vectorized instruction sets when available, the CPU could transfer packed data, up to 512 bits (Intel SSE, AVX512) and saturate the available bandwidth of PCIe interconnect.

But in modern computers, data transfer are mainly the task of DMA controllers (also called DMA engines). Those controllers are located in peripheral devices (PCI-e end point) and handle data transfer to and from the main memory without CPU intervention. The DMA engine might also be synthesized in custom FPGA design using standard IP

<sup>&</sup>lt;sup>5</sup>Intel QuickPath Interconnect (QPI) or Amd Infinity Fabric

Figure 2.5: An overview of Peripheral Component Interconnect Express (PCI-e) topology showing PCI-e Root Complex and bridges (Source: Wikipedia).

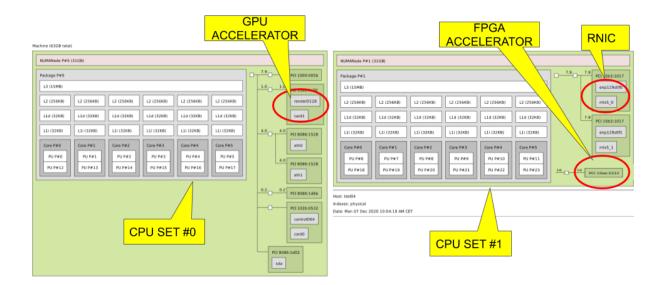

Figure 2.6: A snapshot from Istopo graphic user interface, showing a two CPU set computer and both PCIe-interconnects. Best throughput are achieved for data transfer from device to memory in the same interconnect and from PCI-e card to card with good affinity.

such as the Xilinx IPs CDMA<sup>6</sup> or the XDMA<sup>7</sup>.

The software application must configure the DMA controller with a list of data transfer commands, mainly Buffer Descriptors (BDs), i.e. addresses and length of the memory regions, both at source and destination. BD processing proceeds in three successive steps:

i) The memory buffer must be pinned to prevent the memory management unit from moving it during a DMA transfer. This can take some time. ii) Then the virtual addresses of BDs given by the main application must be translated into their respective physical addresses used by the DMA engine. iii) And then, the data movement operations are performed autonomously through the PCI-e interconnect.

Physical addresses of recently used BDs might be cached internally for later reuse and performance reasons, .

Taking all this in consideration, it is important to optimize the duration of the data transfer. An efficient online data analysis essentially depends on a judicious memory allocation strategy. How to do this depends on the size of the data, their actual location, the targeted destination, the cache states, the capabilities of the DMA engine involved.

#### 2.1.4 Memory Allocation Challenges

In the process of this work, we had to solve the problem of large memory buffer allocation suitable with RASHPA concepts and compatible with the Linux underlying operating system. Large memory allocation has always been a challenge for operating system designers and developers as explained in [42].

Here are some existing techniques on Linux based systems which include: