#### Simulation, fabrication and electrical characterization of advanced silicon MOS transistors for 3D-monolithic integration

Daphnée Bosch

#### ▶ To cite this version:

Daphnée Bosch. Simulation, fabrication and electrical characterization of advanced silicon MOS transistors for 3D-monolithic integration. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2020. English. NNT: 2020GRALT077. tel-03219902

#### HAL Id: tel-03219902 https://theses.hal.science/tel-03219902v1

Submitted on 6 May 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITE GRENOBLE ALPES

Spécialité : Nano Electronique et Nano Technologies

Arrêté ministériel : 25 mai 2016

Présentée par

#### Daphnée BOSCH

Thèse dirigée par Francis BALESTRA, IMEP-LAHC et codirigée par Claire FENOUILLET-BERANGER, CEA-LETI et co-encadrée par Francois ANDRIEU, CEA-LETI

préparée au sein du Laboratoire d'électronique et des technologies de l'information (CEA-LETI) dans l'École Doctorale électronique, électrotechnique, automatique et traitement du signal (EEATS)

# Simulation, fabrication et caractérisation de transistors MOS avancés pour une intégration 3D monolithique

Thèse soutenue publiquement le **17/12/2020**, devant le jury composé de :

#### Mr Guilhem LARRIEU

Directeur de recherche CNRS-LAAS, (Rapporteur)

#### **Mme Cristell MANEUX**

Professeur université de Bordeaux-IMS, (Rapporteur)

#### Mr Pierre Emmanuel GAILLARDON

Professeur associé université UTAH, (Examinateur)

#### Mme Anne KAMINSKI

Professeur Grenoble INP, (Examinateur, présidente du jury)

#### Mr Francis BALESTRA

Directeur de recherche CNRS-IMEP-LAHC, (Directeur de thèse)

#### **Mr Francois ANDRIEU**

Ingénieur de recherche au CEA-Leti, (Invité)

#### Mr Franck ARNAUD

Ingénieur STMicroelectronics, (Invité)

#### Acknowledgements

To whom it may concern,

Whoever is reading theses lines, I would like to thank you. Not just because you are a great person (I have no doubts in that), but because if you are here, you had an intent to read this manuscript, or at least the acknowledgements part. I wish you all the best for this colossal task, whatever the option you choose.

I spend most of my time during the third last year between CEA-LETI site, my home and to be honest, mountains. The climbing gym counts into the mountain category. I propose you the evident section subdivision: professional greetings, personal one and mountains. I'm not entirely certain of the content of the last section but no worries: rocks can be fascinating.

Before going further, I would like to thank the members of my jury, for reading my manuscript, attending the defense and for all the feedbacks that improved the quality of the manuscript. The final results is in your hands. It was an honor in having you in my jury.

From the workplace part, my warmest gratitude to the driving force of my PhD (apart myself) my supervisor Francois Andrieu. You succeed in canalizing my energy and my attention towards productivity. I am glad that you pushed me to write for conferences and challenged me several time to instill me a veritable researcher engineer spirit. Thanks again for your guidance, your enthusiasm, your reactivity and the different opportunities you offered me. I would like to thanks my thesis director Francis Balestra, for microelectronics questions related, administrative paperwork, but most important to grab a coffee and discuss about the world. I learned a lot with you about sugar industry, nutrition but also theater. I also had the opportunity to work with Jean-Pierre Colinge. Thanks for the junctionless transistor and to be available when I came to ask the very same question several times in a row. By the way, can you explain me again screening effect? Sorry dat ik ben sneller dan mijn e-mails, maar nogmaals bedankt. Speaking of the people that I could bothered with existential questions about transistors, Gerard Ghibaudo was always available (and willing) to derive equations about mismatch.

Still in the workplace area, the members of the Coolcube meeting helped me a lot when I started to take my marks into this new environment. Among them (I conserve the PhD students for later), Perrine, Didier, Laurent B. and Laurent B. (merci Laurent de m'avoir enseigné la rigueur indispensable pour une utilisation correcte d'EYELIT), Mickael, Hervé and Claire. At the same time, I learned a lot about design/PDK with the members of 3DMUSE: Sébastien, Olivier, Mehdi... And after, the IMC group: Sylvain, Joris (thanks for your support concerning TCAD ©), Sébastien, Mona, Bastien, Jean-Philippe, Jean-Michel: thanks for all the discussion, merging design and technology for the best brainstorm. Speaking of design, my warmest thanks to Lorenzo and Adam who supervised me and gave me all their knowledge about SRAM. Speaking of SRAM, a special thanks to Louis, with who we constructed, deconstructed and constructed again the same story about SRAM security. Between the member of this thematic (I may add Valérie and Heimanu), "la confiance règne". And last, but not the least, thanks to all the person who helped me, either in the characterisation laboratory, in the cleanroom, at the office, at the tea corner... Here, a non-exhaustive list: Bernard, Jean-Michel, Yves, Christophe, Alexandre, Zdeneck, Olivier, Benoit, Yves, Cyrille, Claude, Cyril, Thomas, Nils, Maud, Xavier, Denis, Jacques, Jean, Giovanni, Rabah, Arnaud, Christoforos, Jose, Angeliki, Jean-Luc, Artemisia, Alain, Fabienne, Gabriel, Laurent, Mickael, Fred, Jean-Michel, Pablo, Cédric, Ludivine, Christian, Pascal, Virginie, Aurélien, David, Aurélien, Ronald, François...

Special dedicace to people who shared my office (and had to manage me all day long): Sotiris, Romane, Simon, Giulia, Rony, Théophile and Thibaud. I wish to the last three names many debates about all kind of topics (I know, it already started). Concerning the PhD student, the "old" generation is composed of

the wise Remy (I'm still using part of your code), the social Jessy (our "spiritual guide", claimed only by itself) and the brave Lina (I always admire you, you are so strong!). For the "current" generation, Giulia and Camila have been the perfect speaker to chit-chat, complain but also low down the stress. Thanks Sylvan for the beautiful drawings in the office! For the "future" generation, good luck Théophile, you will need it.

Passons maintenant à la deuxième partie -qui pour l'occasion est devenue francophone-, un peu plus personnelle. De manière générale, merci pour le soutien de ma petite famille, de ma grande famille et de ma très grande famille qui englobe toutes les rencontres et contacts que j'ai pu nouer au cours de mes 26 ans d'existence. Merci à mes parents ainsi que ma petite sœur et mon petit frère pour mon éducation, votre soutien et votre confiance en moi sans failles. Je ne pourrais jamais vous remercier suffisamment ! Merci à toute ma grande famille, ma grand-mère et grande tante, mes oncles et tantes, neveux et nièces, cousins et cousines, la famille de Catalogne et je manque de vocabulaire pour qualifier le reste... Merci à mes amis d'enfance, Claire, Margot et Alexandra, votre amitié (depuis une vingtaine d'années pour certaines) m'est précieuse. A tous ceux de mes études avec qui j'ai gardé contact et que je revois régulièrement : Lucie, Arnaud, Sylvain, Mickael, Florian, Thomas, Maxime, Pierre, Quentin, Piel, Hélène, Gaëlle, Julie et tous les autres. Merci Julie pour les weekends en Suisses, chacun sont inoubliables à leur manière. Et le plus important à mes yeux, merci à mon partenaire Guillaume d'avoir vécu avec moi cette thèse au jour le jour, d'avoir su être content pour mes succès tout en sachant me soutenir dans les périodes difficiles.

Pour la dernière catégorie, j'aimerais remercier les parcs et massifs suivants pour m'avoir donné une bouffée d'oxygène et des souvenirs inoubliables : la Vanoise, les Dolomites, le Yosemite, le grand canyon, Taroko national park, le Vercors, la Chartreuse (boisson ou massif, à vous de choisir), Belledonne, les Ecrins...

Merci encore, Sincèrement, Daphnée Bosch

#### **Contents**

Chapter I: Introduction b. FDSOI architecture. Semi-conductor industry: current challenges, roadmaps and propositions to keep the race to i. ii. iii. Introduction to In-Memory Computing: 24 Thesis objectives: 26 Chapter II: Design Technology Co-Optimization: functionalities provided by 3D monolithic integration b. c. i. State of the art of 3D design performance assessment: Motivation for 3D monolithic integration for a. b. Performances 37 a. SPICE model 40 b.

| (  | 1.       | Methodolog       | y summary                                                                    | . 41 |

|----|----------|------------------|------------------------------------------------------------------------------|------|

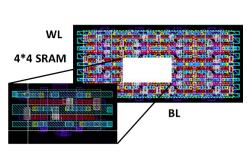

| (  | €.       | RO, SRAM         | benchmark: typical figure of merits                                          | . 42 |

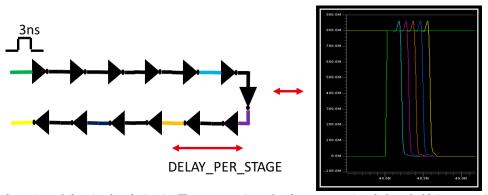

|    |          | i. Ring Osci     | llator                                                                       | . 42 |

|    |          | ii. SRAM         |                                                                              | . 42 |

| 4- |          | Routing in 3D    | designs                                                                      | . 45 |

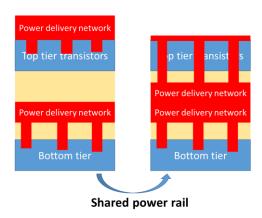

| ä  | ì.       | Buried powe      | er rail                                                                      | . 45 |

| 1  | э.       | Congestion 1     | mitigation and resources sharing between tiers                               | . 45 |

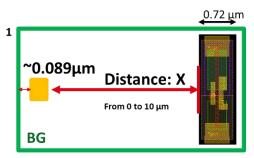

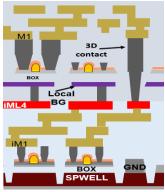

| (  | Э.       | Design guide     | elines for top-tier Back-plane contact                                       | . 48 |

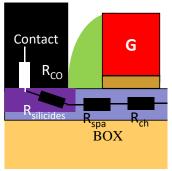

|    |          | i. Simulated     | structure                                                                    | . 48 |

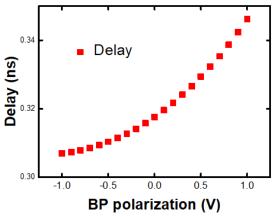

|    |          | ii. Static con   | sideration                                                                   | . 49 |

|    |          | iii. Dynami      | ic consideration                                                             | . 50 |

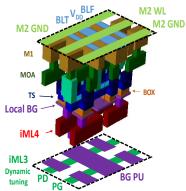

| 5- |          | Design-technol   | logy co-optimization: top-tier SRAM                                          | . 51 |

| á  | ı.       | 14nm techno      | ology performance                                                            | . 51 |

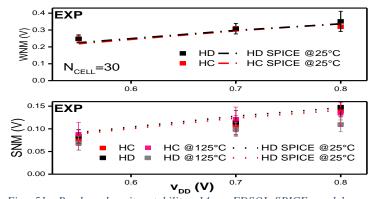

|    |          | i. Electrical    | characterization of typical FOM                                              | . 51 |

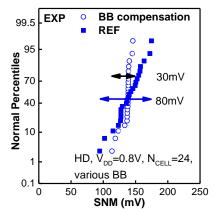

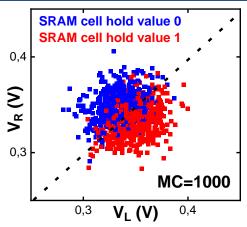

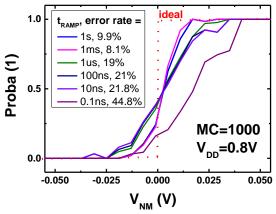

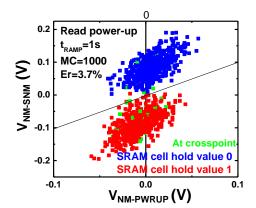

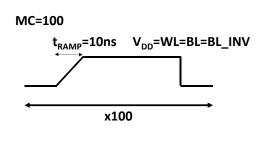

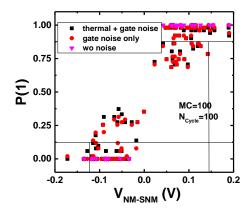

|    |          | ii. SRAM: va     | ariability issue and impact on FOM                                           | . 53 |

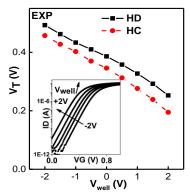

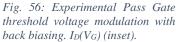

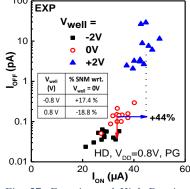

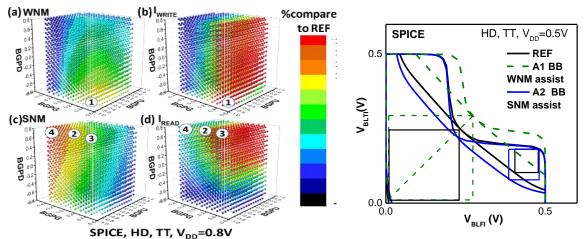

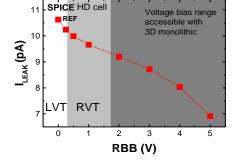

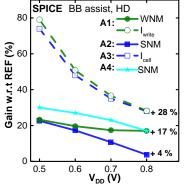

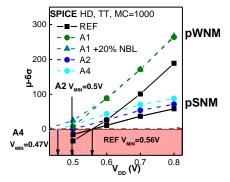

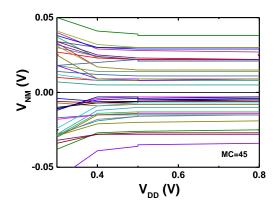

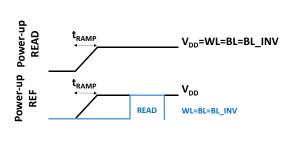

|    |          | iii. Back-bi     | ias assist                                                                   | . 54 |

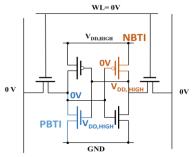

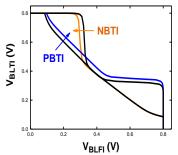

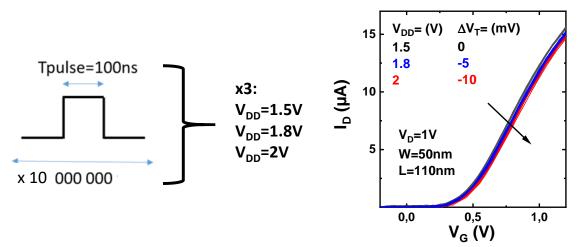

|    |          | iv. BTI-ind      | luced dynamic variability at the bitcell level                               | . 55 |

|    |          | a- BTI mech      | anism                                                                        | . 55 |

| 1  | э.       | BTI at the bi    | itcell level: experimental results                                           | . 56 |

|    | e.<br>Op | _                | of a novel fine-grain back-bias assist techniques for 3D-monolithic 14nm FDS |      |

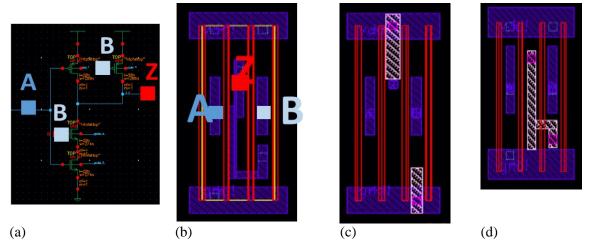

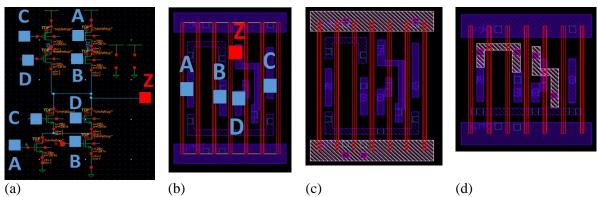

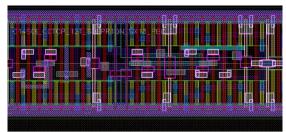

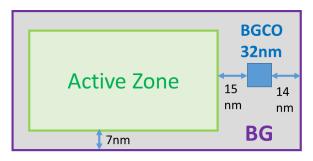

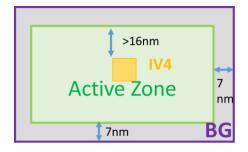

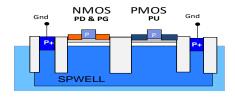

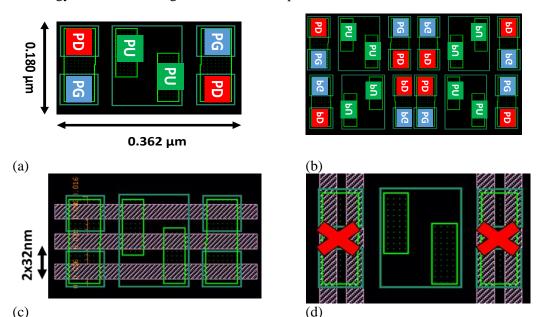

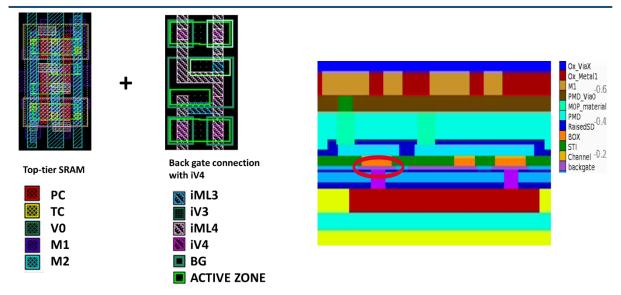

|    |          | i. 3D monol      | ithic design kit: layout considerations                                      | . 59 |

|    |          | ii. Fine grain   | and versatile back-bias assist                                               | . 60 |

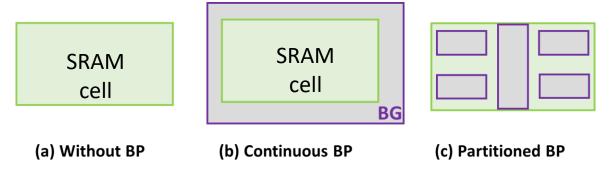

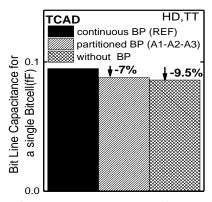

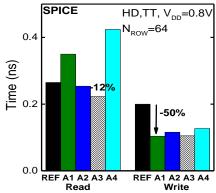

|    |          | iii. Parasiti    | c capacitances reduction                                                     | . 63 |

| 6- |          | Variability as a | nn asset: FDSOI SRAM PUF                                                     | . 65 |

| ä  | ì.       | PUF: SRAM        | I based fingerprint                                                          | . 65 |

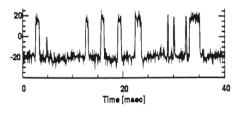

| 1  | ٥.       | Single dopar     | nt transport                                                                 | . 66 |

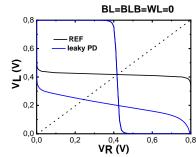

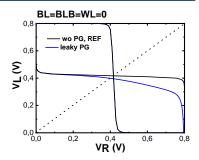

| (  | Э.       | Emulation of     | f leaky devices to assist technological choices                              | . 66 |

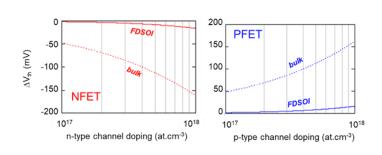

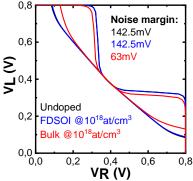

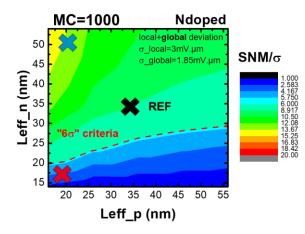

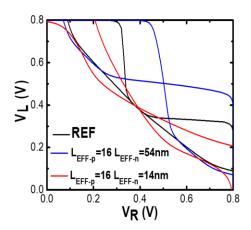

|    |          | i. Impact of     | channel doping on SRAM devices                                               | . 67 |

|    |          | ii. Simulatio    | n environment                                                                | . 67 |

|    |          | iii. Emulati     | ion of resonant transport                                                    | . 71 |

|    |          | iv. Conclus      | sion:                                                                        | . 73 |

| 7- |          | Conclusion of    | chapter II                                                                   | . 74 |

## Chapter III: Fabrication of junctionless transistor in the scope of 3D monolithic integration

| 1- | S   | State of-the art                                                        | 77  |

|----|-----|-------------------------------------------------------------------------|-----|

| a  |     | 3D sequential integration demonstration: review of literature           | 77  |

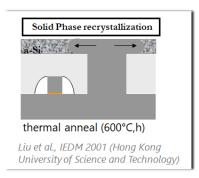

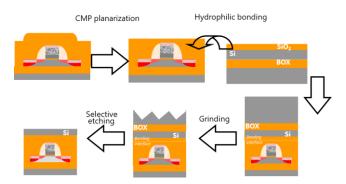

|    | i-  | i- Deposited top-tier channel material                                  | 78  |

|    | ii  | ii- Reported top-tier channel material                                  | 78  |

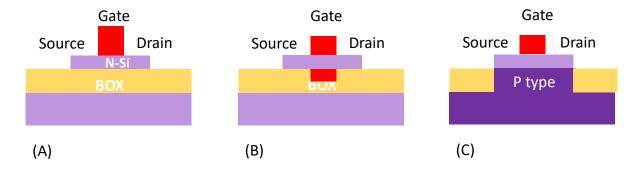

| b  | ).  | Junctionless transistors                                                | 80  |

|    | i-  | i- Short presentation of the JL transistor (JLT) architectures          | 80  |

|    | ii  | ii- Polycrystalline materials                                           | 81  |

|    | ii  | iii- Other materials                                                    | 82  |

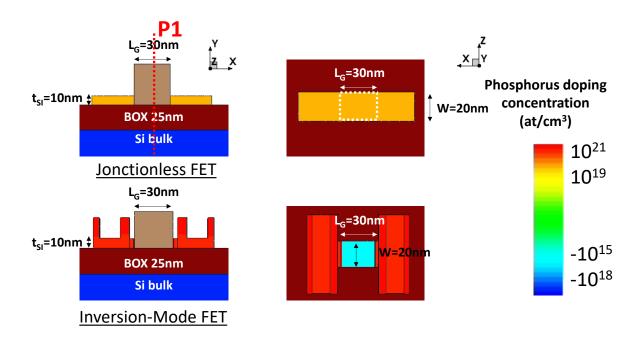

| 2- | 7   | TCAD simulations                                                        | 83  |

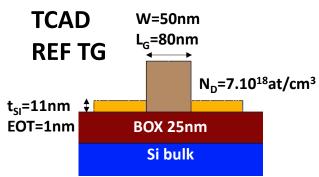

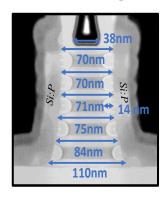

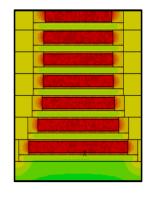

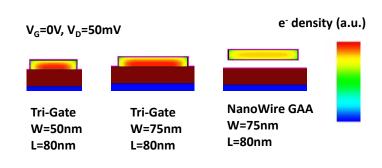

| a  |     | Chosen device architectures                                             | 83  |

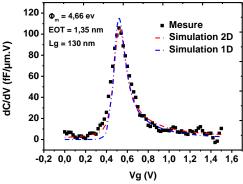

| t  | ).  | Physical Model used and justification                                   | 85  |

| 3- | J   | Junctionless MOSFET operation                                           | 86  |

| a  |     | Sub-threshold region: depletion                                         | 86  |

| t  | ).  | From threshold voltage to flatband voltage: volume conduction           | 87  |

| C  |     | Above flatband voltage: accumulation region                             | 88  |

| Ċ  | l.  | Analytical models                                                       | 88  |

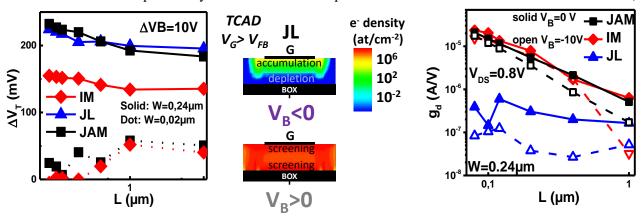

| 4- | C   | Characteristics of Junctionless devices                                 | 89  |

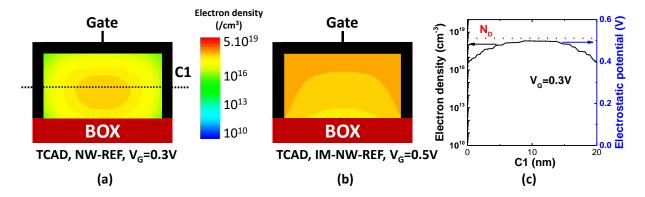

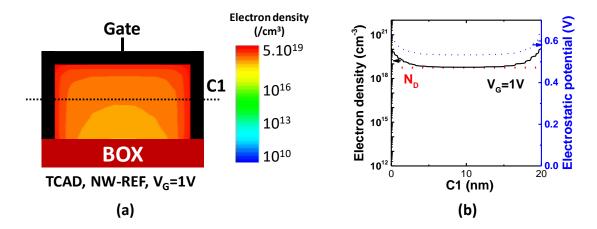

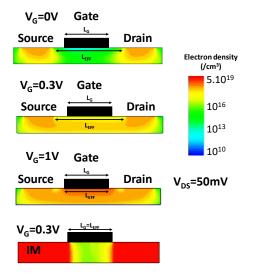

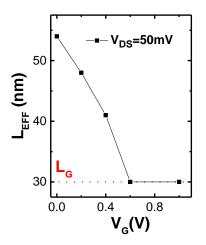

| a  |     | Effective channel length modulation                                     | 89  |

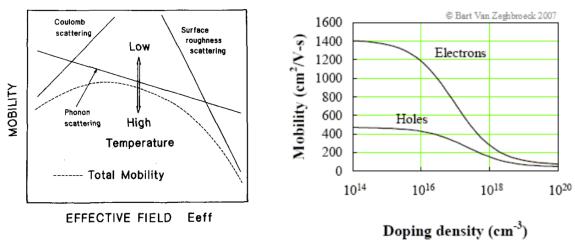

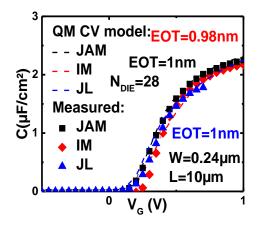

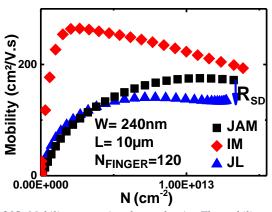

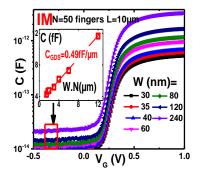

| t  | ).  | Mobility                                                                | 89  |

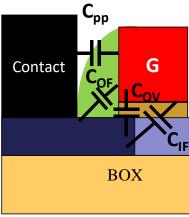

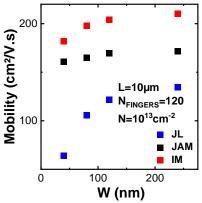

| C  | ٠.  | Capacitances                                                            | 91  |

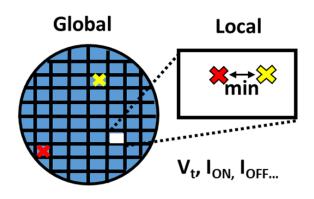

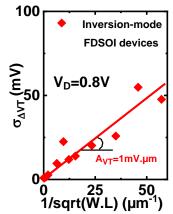

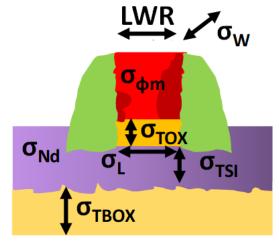

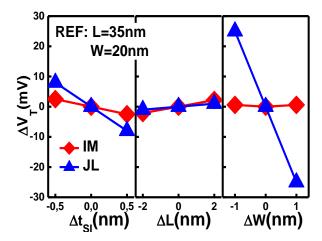

| Ċ  | l-V | Variability                                                             | 92  |

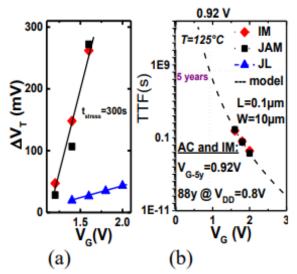

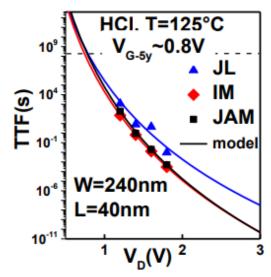

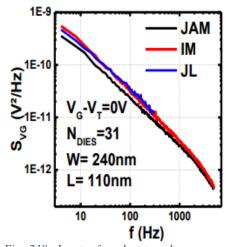

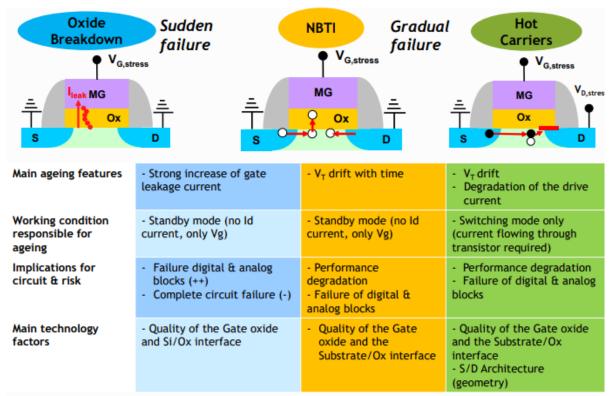

| Ċ  | l.  | Reliability                                                             | 94  |

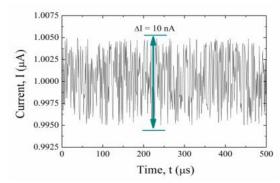

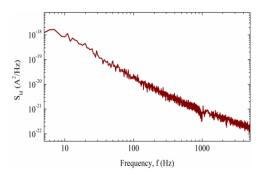

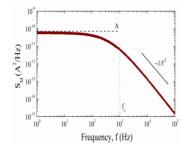

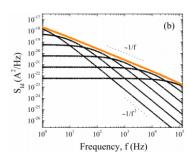

| e  | ·.  | Noise                                                                   | 95  |

| f  |     | Junctionless transistor applications                                    | 96  |

| 5- | Γ   | Device sizing                                                           | 98  |

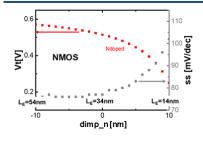

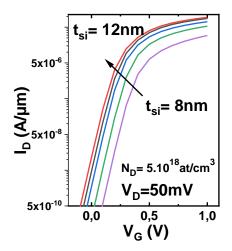

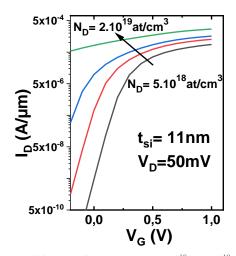

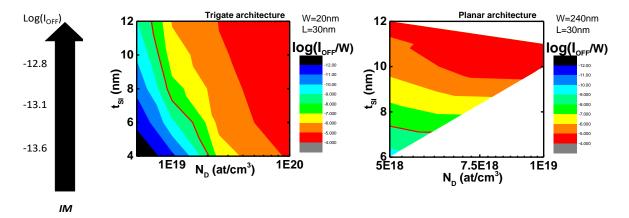

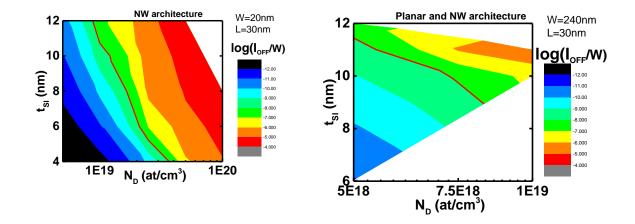

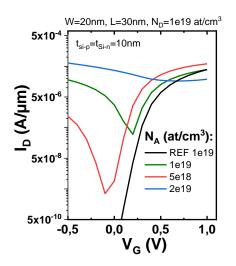

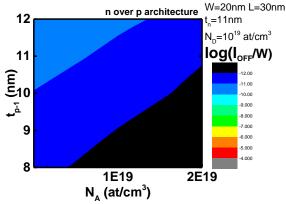

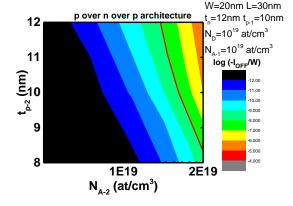

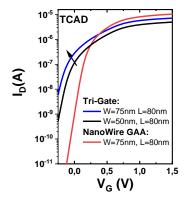

| a  |     | Tri-gate junctionless sensitivity to silicon thickness and doping level | 98  |

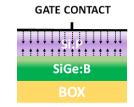

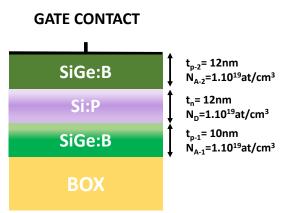

| b  | ).  | n over p channel                                                        | 100 |

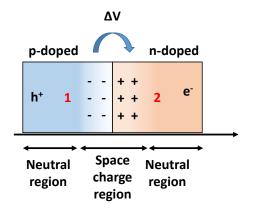

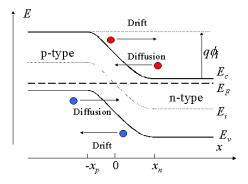

|    | i-  | i- PN junction physics                                                  | 100 |

|    | ii  | ii- CMOS Integration                                                    | 102 |

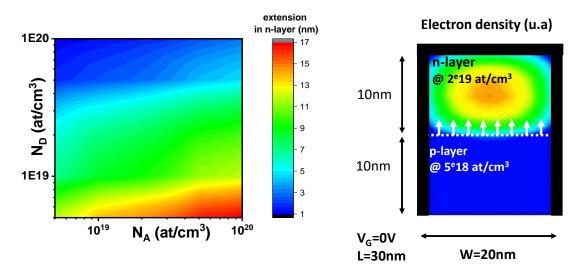

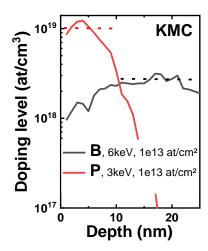

|    | ii  | iii- Sizing of the different layers: TCAD simulations                   | 104 |

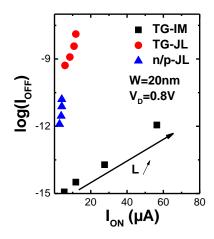

| C  | ٠.  | Performances of the different structures compared to IM devices         | 105 |

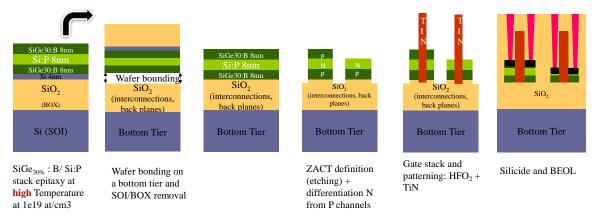

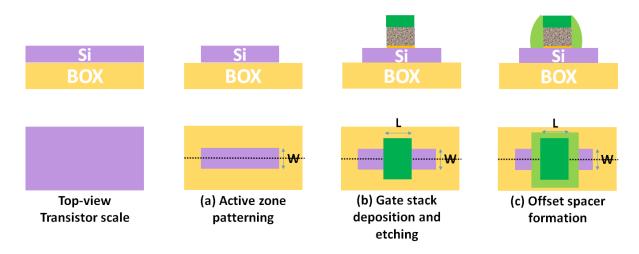

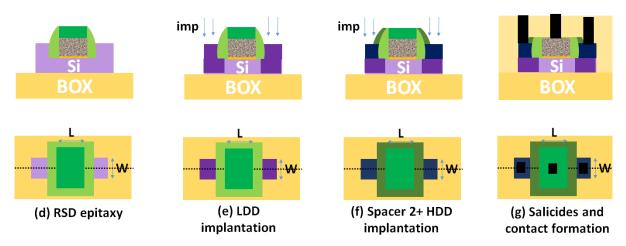

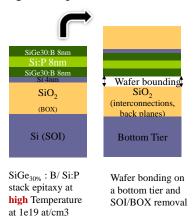

| 6- | F   | Fabrication process flow                                                | 108 |

| a  |     | Gate first integration at high temperature                              | 108 |

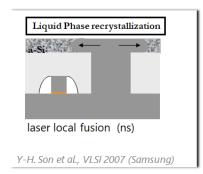

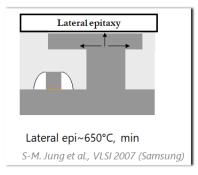

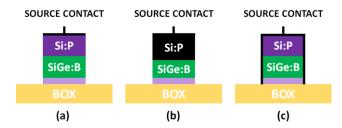

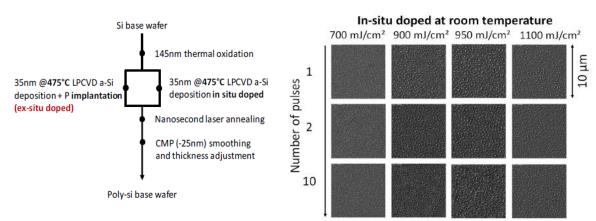

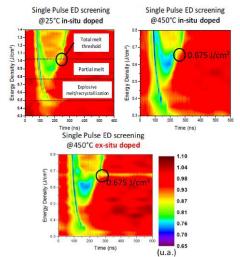

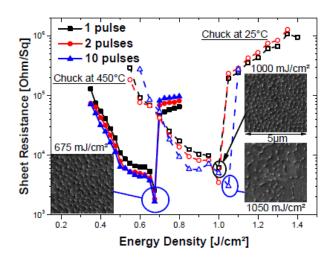

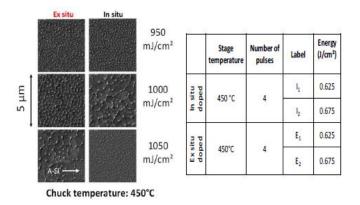

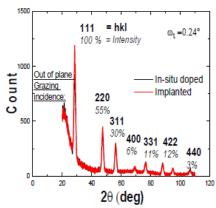

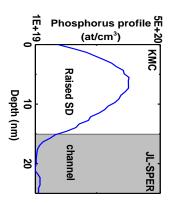

| t  | ).  | Channel material                                                        | 109 |

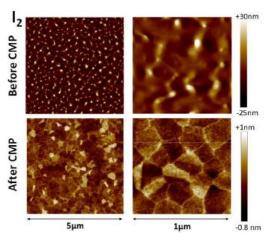

| c  |     | Active zone patterning                                                  | 113 |

|    |     |                                                                         |     |

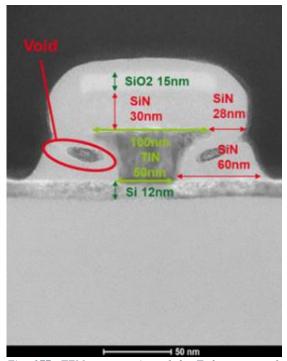

| d. Gate stack                                                                                                                                                                                               | 114              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| i- Gate stack materials                                                                                                                                                                                     | 114              |

| ii- Gate stack etching                                                                                                                                                                                      | 116              |

| e. Spacer                                                                                                                                                                                                   | 117              |

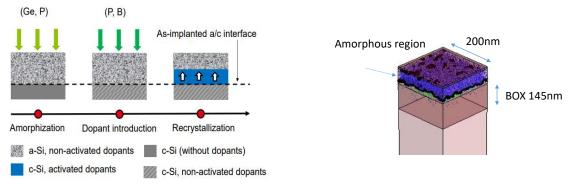

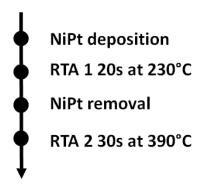

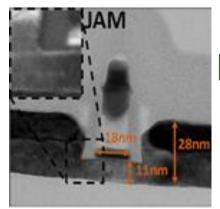

| f. Junction engineering SPER                                                                                                                                                                                | 118              |

| g. Thin silicides                                                                                                                                                                                           | 122              |

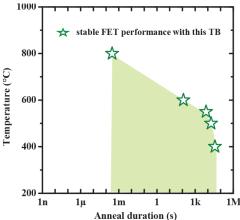

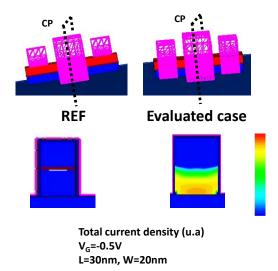

| 7- Overview of studies related to 3D monolithic integration                                                                                                                                                 | 123              |

| 8- Electrical results                                                                                                                                                                                       | 125              |

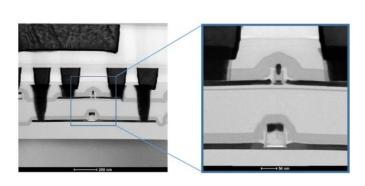

| a. Device fabrication                                                                                                                                                                                       | 125              |

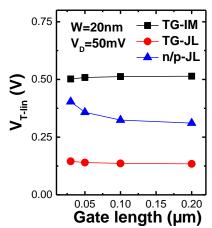

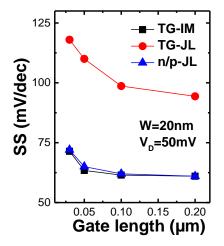

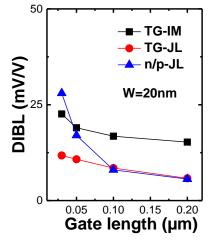

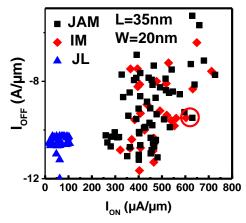

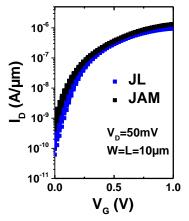

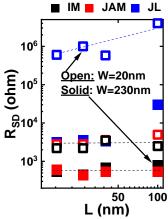

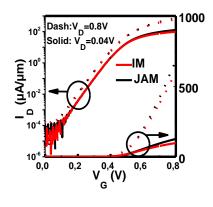

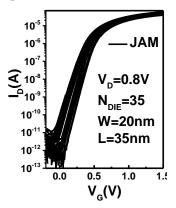

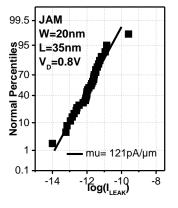

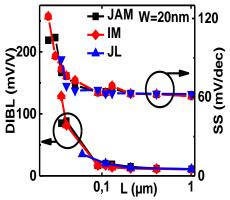

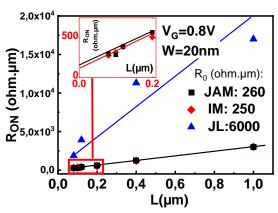

| b. Digital Figure-Of-Merit of Junctionless nMOS                                                                                                                                                             | 126              |

| i- Electrical performances                                                                                                                                                                                  | 126              |

| ii- Mobility                                                                                                                                                                                                | 128              |

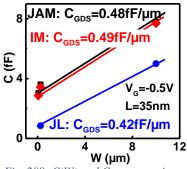

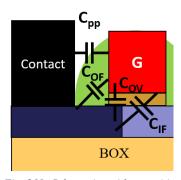

| iii- Overlap capacitance                                                                                                                                                                                    | 129              |

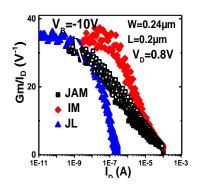

| c. Analog Figure-Of-Merit of junctionless nMOS                                                                                                                                                              | 130              |

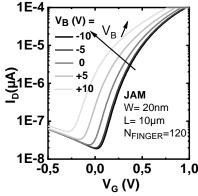

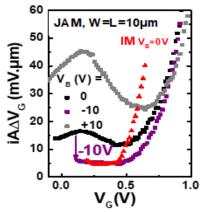

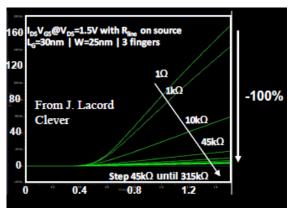

| i- Analog gain leveraged by back-bias                                                                                                                                                                       | 130              |

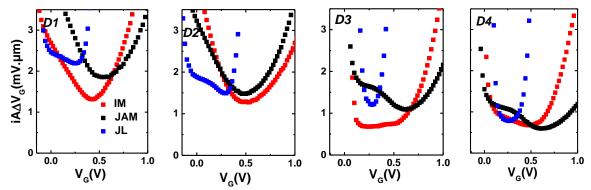

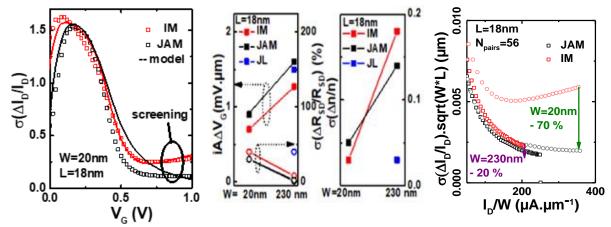

| ii- Reliability and noise                                                                                                                                                                                   | 131              |

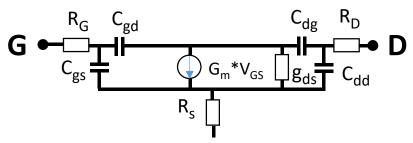

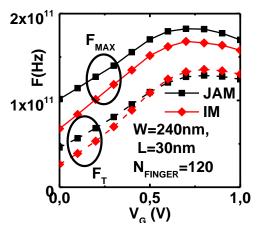

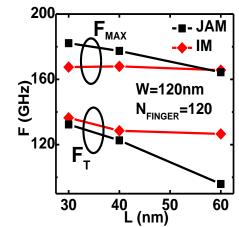

| iii- RF Figure-Of-Merit of junctionless nMOS                                                                                                                                                                | 133              |

| 9- Conclusion of Chapter 3                                                                                                                                                                                  | 135              |

|                                                                                                                                                                                                             |                  |

| Chapter IV: Assessment of an ultra-dense Non-Volade                                                                                                                                                         |                  |

| Memory cube for In-Memory Computing application                                                                                                                                                             | ns               |

| Memory cube for In-Memory Computing application  1- State of the art of In-Memory-Computing existing solutions                                                                                              | ns<br>138        |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns<br>138<br>138 |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns<br>138<br>138 |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns               |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns               |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns               |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns               |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns               |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns               |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns               |

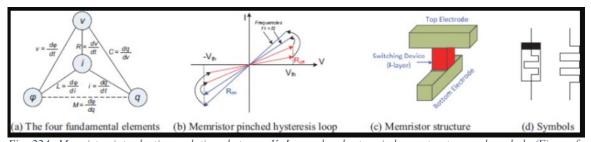

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions.  a. Existing In-Memory Computing implementations.  i. Memristors for IMC.  ii. Boolean logic | ns               |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns               |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns               |

| Memory cube for In-Memory Computing applicatio  1- State of the art of In-Memory-Computing existing solutions                                                                                               | ns               |

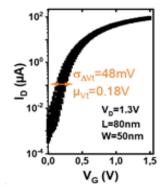

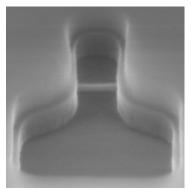

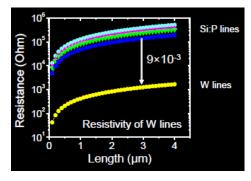

|    | i. | JL performances at W=50nm                                          | 150 |

|----|----|--------------------------------------------------------------------|-----|

|    | ii | . Drive current for stacked nanowires at W=75nm                    | 151 |

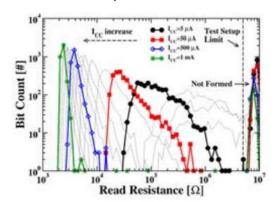

|    | ii | i. OxRAM distribution extraction                                   | 153 |

|    | c. | Scouting logic in the pillar                                       | 154 |

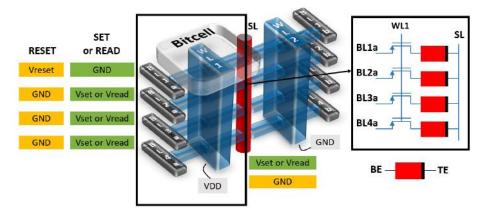

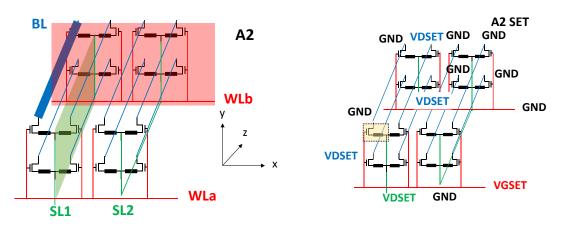

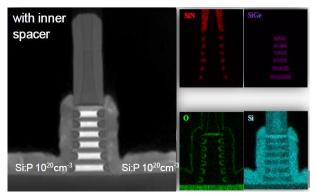

|    | d. | MY-CUBE: read and write schemes.                                   | 154 |

| 3- |    | Processing of stacked structures                                   | 156 |

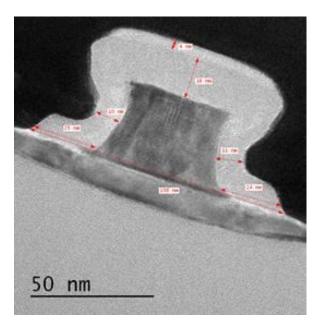

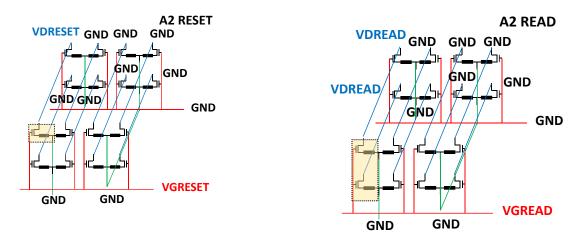

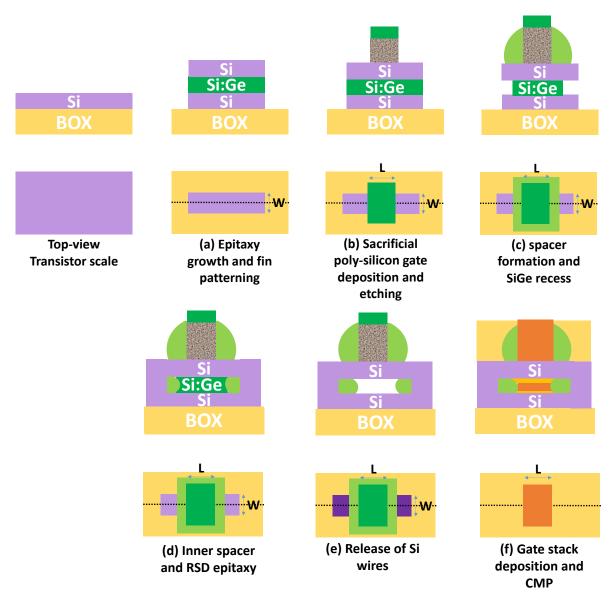

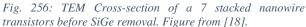

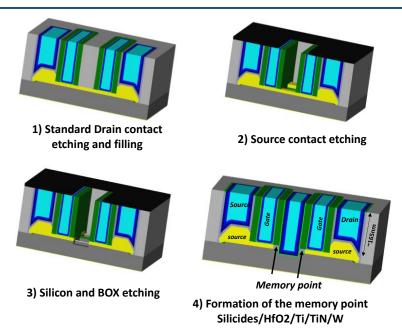

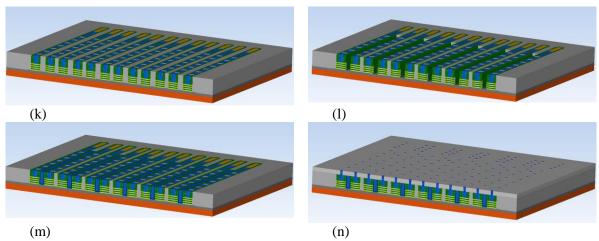

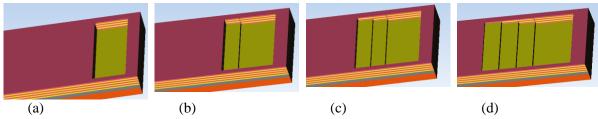

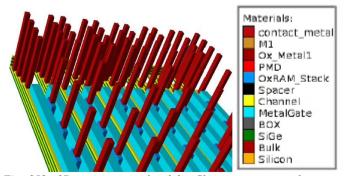

|    | a. | Gate-All-Around stacked nanowires detailed process flow            | 156 |

|    | b. | Modification to standard process flow to integrate memory elements | 157 |

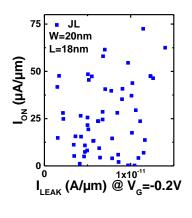

| 4- |    | Variability                                                        | 159 |

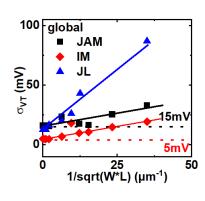

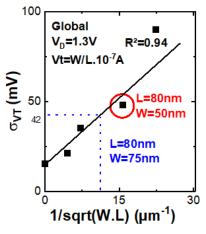

|    | a. | Standard evaluation of the mismatch: Pelgrom plots.                | 159 |

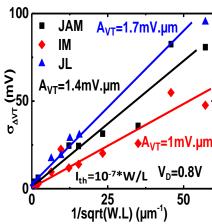

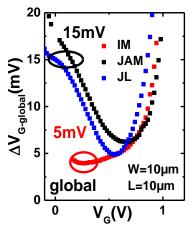

|    | b. | Gate input referred normalized matching parameter                  | 161 |

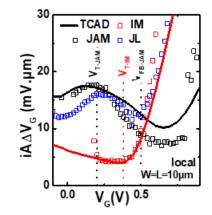

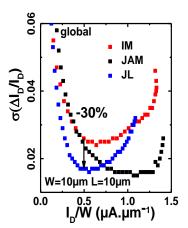

|    | c. | Drain current local and global variability in all-regimes          | 163 |

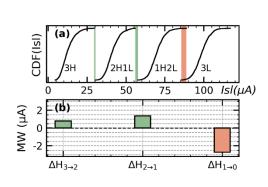

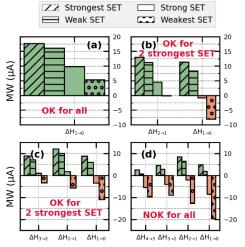

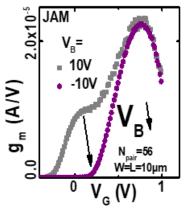

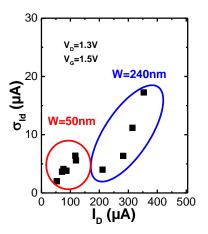

|    | d. | Variability of JAM devices for IMC                                 | 165 |

| 5- |    | Conclusion of chapter IV                                           | 166 |

| G  | en | eral conclusion                                                    |     |

| 1- | C  | onclusion                                                          | 187 |

| 2- | F  | uture Work: short term perspectives                                | 188 |

| 3- | Р  | erspectives                                                        | 189 |

#### Glossary

#### **Symbols:**

| $C_d$ Drain capacitance         F $C_g$ Gate capacitance         F $C_{gc}$ Gate-to-channel capacitance         F $E//$ Longitudinal field         V/m $E//$ Longitudinal field         V/m $E_C$ Conduction band energy         eV $E_G$ Band gap energy         eV $E_G$ Band gap energy         eV $E_{eff}$ Transverse effective field         V/m $f_{max}$ Maximum operating frequency         Hz $g_m$ Transconductance         A/V $I_{opt}$ OFF-state current or leakage current of a MOSFET         A (or A/μm) $I_{opt}$ OFF-state current or saturation current         A (or $I_{opt}$ $I_{opt}$ ON-current or saturation current         A (or $I_{opt}$ $I_{opt}$ Drain current criterion for threshold voltage extraction         A $I_{opt}$ Drain current criterion for threshold voltage extraction         A $I_{opt}$ A (opt $I_{opt}$ A (opt $I_{opt}$ $I_{opt}$ Drain current criterion for threshold voltage extraction         A (opt $I_{op$                                                                                                                      | Symbols                     | Definition                                               | Unit                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------|----------------------------------|

| $C_{gc}$ Gate-to-channel capacitance         F $C_{ox}$ Oxide capacitance         F $E//$ Longitudinal field         V/m $E_C$ Conduction band energy         eV $E_C$ Band gap energy         eV $EV$ Valence band energy         eV $E_{eff}$ Transverse effective field         V/m $f_{max}$ Maximum operating frequency         Hz $g_m$ Transconductance         A/V $I_{OFF}$ OFF-state current or leakage current of a MOSFET         A (or A/μm) $I_{ON}$ ON-current or saturation current         A (or $A/\mu m$ ) $I_{ON}$ ON-current or saturation current         A (or $\mu A/\mu m$ ) $I_{ON}$ Drain current criterion for threshold voltage extraction         A $k, k_B$ Boltzman constant         J/K $L_G$ Transistor gate length         m $N_A$ Acceptor impurities concentration         Atomes/cm³ $n_i$ Intrinsic carriers concentration         cm³³ $q$ Elementary charge         C $R_{ACC}$ Access                                                                                                                                                             | $C_d$                       | Drain capacitance                                        | F                                |

| $C_{ox}$ Oxide capacitance         F $E//$ Longitudinal field         V/m $E_{C}$ Conduction band energy         eV $E_{G}$ Band gap energy         eV $EV$ Valence band energy         eV $E_{eff}$ Transverse effective field         V/m $f_{max}$ Maximum operating frequency         Hz $g_m$ Transconductance         A/V $I_{OFF}$ OFF-state current or leakage current of a MOSFET         A (or $A/\mu m$ ) $I_{ON}$ ON-current or saturation current         A (or $A/\mu m$ ) $I_{ON}$ ON-current or saturation current         A (or $\mu A/\mu m$ ) $I_{th}$ Drain current criterion for threshold voltage extraction         A $k, k_B$ Boltzman constant         J/K $I_{th}$ Drain current criterion for threshold voltage extraction         A tomes/cm³ $n_t$ Intrinsic gate length         m $N_A$ Acceptor impurities concentration         cm⁻³ $n_t$ Intrinsic carriers concentration         cm⁻³ $q$ Elementary charge         C                                                                                                                                    | $C_g$                       | Gate capacitance                                         | F                                |

| E//         Longitudinal field         V/m $E_{\rm C}$ Conduction band energy         eV $E_{\rm G}$ Band gap energy         eV           EV         Valence band energy         eV $E_{\rm eff}$ Transverse effective field         V/m $f_{\rm max}$ Maximum operating frequency         Hz $g_m$ Transconductance         A/V $I_{OFF}$ OFF-state current or leakage current of a MOSFET         A (or $A/\mu m$ ) $I_{ON}$ ON-current or saturation current         A (or $A/\mu m$ ) $I_{ON}$ ON-current or saturation current         A (or $\mu A/\mu m$ ) $I_{th}$ Drain current criterion for threshold voltage extraction         A $k, k_B$ Boltzman constant         J/K $L_G$ Transistor gate length         m $N_A$ Acceptor impurities concentration         cm <sup>-3</sup> $q$ Elementary charge         C $R_{ACC}$ Access resistance $\Omega$ (or $\Omega/\mu m$ ) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdive $\Omega$ or $\Omega/\mu m$ SS         Substhreshold Slope         mV/dec                                            | $C_{gc}$                    | Gate-to-channel capacitance                              | F                                |

| $E_C$ Conduction band energy       eV $E_G$ Band gap energy       eV $EV$ Valence band energy       eV $E_{eff}$ Transverse effective field       V/m $f_{max}$ Maximum operating frequency       Hz $g_m$ Transconductance       A/V $I_{OFF}$ OFF-state current or leakage current of a MOSFET       A (or $A/\mu m$ ) $I_{ON}$ ON-current or saturation current       A (or $\mu A/\mu m$ ) $I_{IN}$ Drain current criterion for threshold voltage extraction       A $k$ , $k_B$ Boltzman constant       J/K $L_G$ Transistor gate length       m $N_A$ Acceptor impurities concentration       Atomes/cm³ $n_i$ Intrinsic carriers concentration       cm³³ $q$ Elementary charge       C $R_{ACC}$ Access resistance $\Omega$ (or $\Omega.\mu m$ ) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega/\mu m$ SS       Substhreshold Slope       mV/dec $t_{ox}$ Gate oxide thickness       m $V_B$ Back-bias voltage (Body voltage)       V                                                                                        | $C_{ox}$                    | Oxide capacitance                                        | F                                |

| $E_G$ Band gap energy       eV         EV       Valence band energy       eV $E_{eff}$ Transverse effective field       V/m $f_{max}$ Maximum operating frequency       Hz $g_m$ Transconductance       A/V $I_{OFF}$ OFF-state current or leakage current of a MOSFET       A (or $A/\mu m$ ) $I_{ON}$ ON-current or saturation current       A (or $\mu A/\mu m$ ) $I_{th}$ Drain current criterion for threshold voltage extraction       A $k$ , $k_B$ Boltzman constant       J/K $L_G$ Transistor gate length       m $N_A$ Acceptor impurities concentration       Atomes/cm³ $n_t$ Intrinsic carriers concentration       cm³³ $q$ Elementary charge       C $R_{ACC}$ Access resistance $\Omega$ (or $\Omega$ . $\mu$ m) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega/\mu$ m         SS       Substhreshold Slope       mV/dec $L_{ox}$ Gate oxide thickness       m $V_B$ Back-bias voltage (Body voltage)       V $V_D$ Drain voltage       V <t< td=""><td><i>E</i>//</td><td>Longitudinal field</td><td>V/m</td></t<> | <i>E</i> //                 | Longitudinal field                                       | V/m                              |

| EV       Valence band energy       eV $E_{eff}$ Transverse effective field       V/m $f_{max}$ Maximum operating frequency       Hz $g_m$ Transconductance       A/V $I_{OFF}$ OFF-state current or leakage current of a MOSFET       A (or $A/\mu m$ ) $I_{ON}$ ON-current or saturation current       A (or $\mu A/\mu m$ ) $I_{th}$ Drain current criterion for threshold voltage extraction       A $k, k_B$ Boltzman constant       J/K $L_G$ Transistor gate length       m $N_A$ Acceptor impurities concentration       Atomes/cm³ $n_l$ Intrinsic carriers concentration       cm³ $q$ Elementary charge       C $R_{ACC}$ Access resistance $\Omega$ (or $\Omega.\mu m$ ) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega/\mu m$ SS       Substhreshold Slope       mV/dec $t_{ox}$ Gate oxide thickness       m $V_B$ Back-bias voltage (Body voltage)       V $V_D$ Drain voltage       V $V_D$ Drain voltage       V                                                                                                     | $E_{\mathrm{C}}$            | Conduction band energy                                   | eV                               |

| $E_{eff}$ Transverse effective field         V/m $f_{max}$ Maximum operating frequency         Hz $g_m$ Transconductance         A/V $I_{OFF}$ OFF-state current or leakage current of a MOSFET         A (or A/μm) $I_{ON}$ ON-current or saturation current         A (or $\mu$ A/μm) $I_{th}$ Drain current criterion for threshold voltage extraction         A $k, k_B$ Boltzman constant         J/K $L_G$ Transistor gate length         m $N_A$ Acceptor impurities concentration         Atomes/cm³ $n_i$ Intrinsic carriers concentration         cm³³ $q$ Elementary charge         C $R_{ACC}$ Access resistance $\Omega$ (or $\Omega$ .μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega$ /μm           SS         Substhreshold Slope         mV/dec $t_{ox}$ Gate oxide thickness         m $V_B$ Back-bias voltage (Body voltage)         V $V_D$ Drain voltage         V $V_D$ Supply voltage         V                                                                                                            | $E_G$                       | Band gap energy                                          | eV                               |

| $f_{max}$ Maximum operating frequency         Hz $g_m$ Transconductance         A/V $I_{OFF}$ OFF-state current or leakage current of a MOSFET         A (or A/μm) $I_{ON}$ ON-current or saturation current         A (or $\mu$ A/μm) $I_{th}$ Drain current criterion for threshold voltage extraction         A $k, k_B$ Boltzman constant         J/K $L_G$ Transistor gate length         m $N_A$ Acceptor impurities concentration         Atomes/cm³ $n_i$ Intrinsic carriers concentration         cm³³ $q$ Elementary charge         C $R_{ACC}$ Access resistance $\Omega$ (or $\Omega$ .μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega$ /μm           SS         Substhreshold Slope         mV/dec $t_{ox}$ Gate oxide thickness         m $V_B$ Back-bias voltage (Body voltage)         V $V_D$ Drain voltage         V $V_D$ Supply voltage         V $V_B$ Flat-band voltage         V $V_$                                                                                                                      | EV                          | Valence band energy                                      | eV                               |

| $f_{\text{max}}$ Maximum operating frequency         Hz $g_m$ Transconductance         A/V $I_{OFF}$ OFF-state current or leakage current of a MOSFET         A (or A/μm) $I_{ON}$ ON-current or saturation current         A (or $\mu$ A/μm) $I_{th}$ Drain current criterion for threshold voltage extraction         A $k, k_B$ Boltzman constant         J/K $L_G$ Transistor gate length         m $N_A$ Acceptor impurities concentration         Atomes/cm³ $n_i$ Intrinsic carriers concentration         cm⁻³ $q$ Elementary charge         C $R_{ACC}$ Access resistance         Ω (or $\Omega$ .μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega$ /μm           SS         Substhreshold Slope         mV/dec $t_{ox}$ Gate oxide thickness         m $V_B$ Back-bias voltage (Body voltage)         V $V_D$ Drain voltage         V $V_D$ Supply voltage         V $V_B$ Flat-band voltage         V $V$                                                                                                               | $E_{eff}$                   | Transverse effective field                               | V/m                              |

| $I_{OFF}$ OFF-state current or leakage current of a MOSFET         A (or A/μm) $I_{ON}$ ON-current or saturation current         A (or μA/μm) $I_{th}$ Drain current criterion for threshold voltage extraction         A $k, k_B$ Boltzman constant         J/K $L_G$ Transistor gate length         m $N_A$ Acceptor impurities concentration         Atomes/cm³ $n_i$ Intrinsic carriers concentration         cm⁻³ $q$ Elementary charge         C $R_{ACC}$ Access resistance         Ω (or Ω-μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive         Ω or Ω/μm           SS         Substhreshold Slope         mV/dec $t_{OX}$ Gate oxide thickness         m           V <sub>B</sub> Back-bias voltage (Body voltage)         V           V <sub>D</sub> Drain voltage         V           V <sub>D</sub> Drain voltage         V           V <sub>D</sub> Supply voltage         V           V <sub>FB</sub> Flat-band voltage         V           V <sub>S</sub> Source voltage         V                                                  |                             | Maximum operating frequency                              | Hz                               |

| $I_{OFF}$ OFF-state current or leakage current of a MOSFET         A (or A/μm) $I_{ON}$ ON-current or saturation current         A (or μA/μm) $I_{th}$ Drain current criterion for threshold voltage extraction         A $k, k_B$ Boltzman constant         J/K $L_G$ Transistor gate length         m $N_A$ Acceptor impurities concentration         Atomes/cm³ $n_i$ Intrinsic carriers concentration         cm⁻³ $q$ Elementary charge         C $R_{ACC}$ Access resistance         Ω (or Ω.μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega/\mu m$ SS         Substhreshold Slope         mV/dec $t_{ox}$ Gate oxide thickness         m $V_B$ Back-bias voltage (Body voltage)         V $V_D$ Drain voltage         V $V_D$ Supply voltage         V $V_{FB}$ Flat-band voltage         V $V_S$ Source voltage         V                                                                                                                                                                                                 | $g_m$                       | Transconductance                                         | A/V                              |

| $I_{ON}$ ON-current or saturation current         A (or μA/μm) $I_{th}$ Drain current criterion for threshold voltage extraction         A $k, k_B$ Boltzman constant         J/K $L_G$ Transistor gate length         m $N_A$ Acceptor impurities concentration         Atomes/cm³ $n_i$ Intrinsic carriers concentration         cm³³ $q$ Elementary charge         C $R_{ACC}$ Access resistance $\Omega$ (or $\Omega$ .μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega$ /μm           SS         Substhreshold Slope         mV/dec $t_{ox}$ Gate oxide thickness         m $V_B$ Back-bias voltage (Body voltage)         V $V_D$ Drain voltage         V $v_d$ Drift velocity         m/s $V_{DD}$ Supply voltage         V $V_{FB}$ Flat-band voltage         V $V_S$ Source voltage         V                                                                                                                                                                                                                             |                             | OFF-state current or leakage current of a MOSFET         | A (or A/μm)                      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             | ON-current or saturation current                         | A (or μA/μm)                     |

| $L_G$ Transistor gate lengthm $N_A$ Acceptor impurities concentrationAtomes/cm³ $n_i$ Intrinsic carriers concentrationcm⁻³ $q$ Elementary chargeC $R_{ACC}$ Access resistance $\Omega$ (or $\Omega$ .µm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega$ /µmSSSubsthreshold SlopemV/dec $t_{ox}$ Gate oxide thicknessmVBBack-bias voltage (Body voltage)VVDDrain voltageV $v_d$ Drift velocitym/sVDDSupply voltageVVFBFlat-band voltageVVGGate voltageVVGGate voltageVVSSource voltageV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $I_{th}$                    | Drain current criterion for threshold voltage extraction | A                                |

| $N_A$ Acceptor impurities concentrationAtomes/cm³ $n_i$ Intrinsic carriers concentrationcm⁻³ $q$ Elementary chargeC $R_{ACC}$ Access resistance $\Omega$ (or $\Omega$ .μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega$ /μmSSSubsthreshold SlopemV/dec $t_{ox}$ Gate oxide thicknessm $V_B$ Back-bias voltage (Body voltage)V $V_D$ Drain voltageV $V_d$ Drift velocitym/s $V_{DD}$ Supply voltageV $V_{FB}$ Flat-band voltageV $V_G$ Gate voltageV $V_S$ Source voltageV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $k, k_B$                    | Boltzman constant                                        | J/K                              |

| $N_A$ Acceptor impurities concentrationAtomes/cm³ $n_i$ Intrinsic carriers concentrationcm⁻³ $q$ Elementary chargeC $R_{ACC}$ Access resistance $\Omega$ (or $\Omega$ .μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega$ /μmSSSubsthreshold SlopemV/dec $t_{ox}$ Gate oxide thicknessm $V_B$ Back-bias voltage (Body voltage)V $V_D$ Drain voltageV $V_d$ Drift velocitym/s $V_{DD}$ Supply voltageV $V_{FB}$ Flat-band voltageV $V_G$ Gate voltageV $V_S$ Source voltageV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $L_{G}$                     | Transistor gate length                                   | m                                |

| $q$ Elementary chargeC $R_{ACC}$ Access resistance $\Omega$ (or $\Omega$ .μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega$ /μmSSSubsthreshold SlopemV/dec $t_{ox}$ Gate oxide thicknessm $V_B$ Back-bias voltage (Body voltage)V $V_D$ Drain voltageV $v_d$ Drift velocitym/s $V_{DD}$ Supply voltageV $V_{FB}$ Flat-band voltageV $V_G$ Gate voltageV $V_S$ Source voltageV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $N_A$                       |                                                          |                                  |

| $q$ Elementary chargeC $R_{ACC}$ Access resistance $\Omega$ (or $\Omega$ .μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $\Omega$ or $\Omega$ /μmSSSubsthreshold SlopemV/dec $t_{ox}$ Gate oxide thicknessm $V_B$ Back-bias voltage (Body voltage)V $V_D$ Drain voltageV $v_d$ Drift velocitym/s $V_{DD}$ Supply voltageV $V_{FB}$ Flat-band voltageV $V_G$ Gate voltageV $V_S$ Source voltageV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $n_i$                       | Intrinsic carriers concentration                         | cm <sup>-3</sup>                 |

| $R_{ACC}$ Access resistance       Ω (or Ω.μm) $R_{ON}$ , $R_{TOT}$ ON-resistance in linear regime and at a given gate overdrive $Ω$ or $Ω/μm$ SS       Substhreshold Slope       mV/dec $t_{ox}$ Gate oxide thickness       m $V_B$ Back-bias voltage (Body voltage)       V $V_D$ Drain voltage       V $v_d$ Drift velocity       m/s $V_{DD}$ Supply voltage       V $V_{FB}$ Flat-band voltage       V $V_G$ Gate voltage       V $V_S$ Source voltage       V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | q                           | Elementary charge                                        |                                  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             | Access resistance                                        | $\Omega$ (or $\Omega$ . $\mu$ m) |

| $\begin{array}{c cccc} t_{ox} & \text{Gate oxide thickness} & \text{m} \\ \hline V_B & \text{Back-bias voltage (Body voltage)} & V \\ \hline V_D & \text{Drain voltage} & V \\ \hline v_d & \text{Drift velocity} & \text{m/s} \\ \hline V_{DD} & \text{Supply voltage} & V \\ \hline V_FB & \text{Flat-band voltage} & V \\ \hline V_G & \text{Gate voltage} & V \\ \hline V_S & \text{Source voltage} & V \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |                                                          | $\Omega$ or $\Omega/\mu m$       |

| $\begin{array}{c cccc} t_{ox} & \text{Gate oxide thickness} & \text{m} \\ \hline V_{\text{B}} & \text{Back-bias voltage (Body voltage)} & V \\ \hline V_{\text{D}} & \text{Drain voltage} & V \\ \hline v_{d} & \text{Drift velocity} & \text{m/s} \\ \hline V_{\text{DD}} & \text{Supply voltage} & V \\ \hline V_{\text{FB}} & \text{Flat-band voltage} & V \\ \hline V_{\text{G}} & \text{Gate voltage} & V \\ \hline V_{\text{S}} & \text{Source voltage} & V \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SS                          | Substhreshold Slope                                      | mV/dec                           |

| $\begin{array}{c cccc} V_B & Back-bias \ voltage \ (Body \ voltage) & V \\ V_D & Drain \ voltage & V \\ \hline v_d & Drift \ velocity & m/s \\ \hline V_{DD} & Supply \ voltage & V \\ \hline V_{FB} & Flat-band \ voltage & V \\ \hline V_G & Gate \ voltage & V \\ \hline V_S & Source \ voltage & V \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             | •                                                        | m                                |

| $\begin{array}{c cccc} V_D & Drain  voltage & V \\ \hline v_d & Drift  velocity & m/s \\ \hline V_{DD} & Supply  voltage & V \\ \hline V_{FB} & Flat-band  voltage & V \\ \hline V_G & Gate  voltage & V \\ \hline V_S & Source  voltage & V \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             | Back-bias voltage (Body voltage)                         | V                                |

| $ \begin{array}{c cccc} v_d & & Drift \ velocity & & m/s \\ \hline V_{DD} & & Supply \ voltage & V \\ \hline V_{FB} & & Flat-band \ voltage & V \\ \hline V_G & & Gate \ voltage & V \\ \hline V_S & & Source \ voltage & V \\ \hline \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |                                                          | V                                |

| $\begin{array}{c ccc} V_{DD} & Supply \ voltage & V \\ V_{FB} & Flat-band \ voltage & V \\ V_{G} & Gate \ voltage & V \\ V_{S} & Source \ voltage & V \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\overline{v_d}$            | •                                                        | m/s                              |

| $ \begin{array}{c cccc} V_{FB} & Flat-band\ voltage & V \\ V_G & Gate\ voltage & V \\ V_S & Source\ voltage & V \\ \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             | Supply voltage                                           | V                                |

| $egin{array}{cccc} V_G & Gate\ voltage & V \ V_S & Source\ voltage & V \ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $V_{\mathrm{FB}}$           | Flat-band voltage                                        | V                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             | Gate voltage                                             | V                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>S</sub>              | Source voltage                                           | V                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $V_{\mathrm{T}}$            | Threshold voltage                                        | V                                |

| V <sub>TLIN</sub> Threshold voltage in linear regime V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{TLIN}$                  | Threshold voltage in linear regime                       | V                                |

| V <sub>TSAT</sub> Threshold voltage in saturation regime V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $V_{TSAT}$                  |                                                          | V                                |

| W Transistor width m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             | Transistor width                                         | m                                |

| $\varepsilon_0$ Permittivity of vacuum F/m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\mathcal{E}_0$             | Permittivity of vacuum                                   | F/m                              |

| $\varepsilon_{\rm Si}$ Permittivity of silicon F/m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $\mathcal{E}_{\mathrm{Si}}$ | Permittivity of silicon                                  | F/m                              |

| γ Body Factor mV/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | γ                           | Body Factor                                              | mV/V                             |

| $\theta i$ Mobility attenuation parameters $V^{-i}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             | Mobility attenuation parameters                          | $V^{-i}$                         |

| λ0 Mean free path m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\lambda 0$                 | Mean free path                                           | m                                |

| μ0 Low-field mobility m²/Vs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\mu 0$                     | Low-field mobility                                       | m <sup>2</sup> /Vs               |

| μeff Effective mobility m²/Vs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | μeff                        | Effective mobility                                       | m <sup>2</sup> /Vs               |

| τ Relaxation time s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             | Relaxation time                                          | S                                |