### Linearity and Efficiency of Load Modulated Power Amplifiers

Kimon Vivien

#### ▶ To cite this version:

Kimon Vivien. Linearity and Efficiency of Load Modulated Power Amplifiers. Electronics. Université Paris-Est, 2020. English. NNT: 2020PESC2026. tel-03227382

### HAL Id: tel-03227382 https://theses.hal.science/tel-03227382v1

Submitted on 17 May 2021

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Université Paris-Est

Doctoral School of Mathematics, Science and Technologies of Information and Communication

### **Doctoral Thesis**

Specialty: Electronics, Optronics and Systems

by

Kimon VIVIEN

# Linearity and Efficiency of Load Modulated Power Amplifiers

Linéarité et Rendement des Amplificateurs de Puissance à Modulation d'Impédance

Directed by Pr. Genevieve Baudoin Co-directors Olivier Venard and Pascal Pierre-Charles-Felix

#### Jury:

Dr Didier Belot Reviewer Dr Nathalie Deltimple Reviewer Dr Dominique Morche Jury member Dr Edouard Ngoya Jury member Pr Jean-Marc Laheurte Jury member Pr Genevieve Baudoin Supervisor Pr Olivier Venard Co-supervisor Pascal Pierre-Charles-Felix Co-supervisor Dr Paolo De Falco Invited member Pr Taylor W. Barton Invited member

## **Acknowledgments**

I would like to express my gratitude to all the people that made this work possible.

First, I would like to thank my academic advisors Pr. Genevieve Baudoin and Associate Professor Olivier Venard for their guidance, encouragement and support throughout these years. You gave me the opportunity to follow this path and took me with you all around the globe. I look forward to seeing you again in some other conference in an other exotic place!

I would also like to thank Pascal Pierre-Charles-Félix, for taking me in SOMOS Semi, looking after me and encouraging me for the last four years.

Of course I will never forget all my colleagues from SOMOS Semi, for all the gossips, the afterworks, the trail running sessions, and everything I learned by your side. Thank you Guillaume, Arnaud, Manu, Hervé, Pascal, and everybody else. And special thanks to Stephanie for having yet another child to take care of!

My exchange in Colorado was one of the most interesting, exciting and prolific years so far. This would not have been possible without Pr. Taylor Barton. I cannot thank you enough for all the trust and support you showed me. Working in your team was an invaluable experience. A special mention goes to Dr Paolo De Falco, whose unconventional ideas, council and friendship followed me during my stay. I wish the best of luck to all the staff and students of the RF/MW group of Colorado University. I won't forget our adventures, trips and coffee breaks! Next time you will be visiting me for a small tour in the French Alps and Fontainebleau.

Thanks to all my friends, in Paris, Athens, and now the US. Without your distractions these four years would have felt much longer! And last but not least, I would like to thank my parents, my sister and my partner, whose support and patience has been total for these four years.

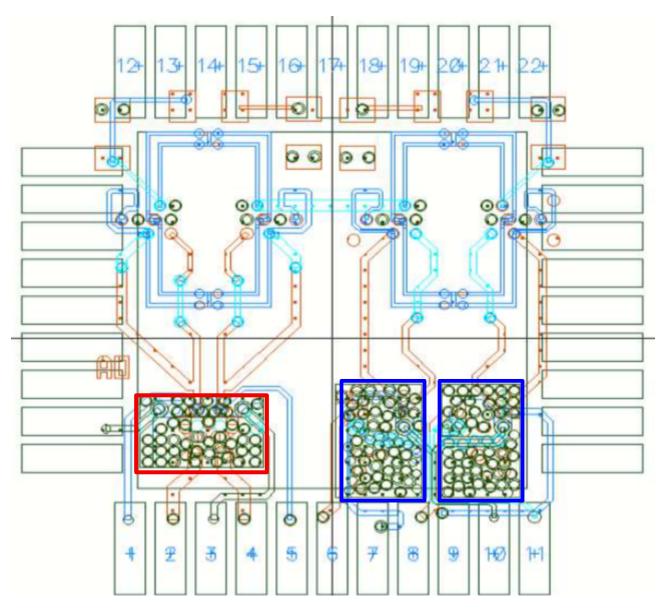

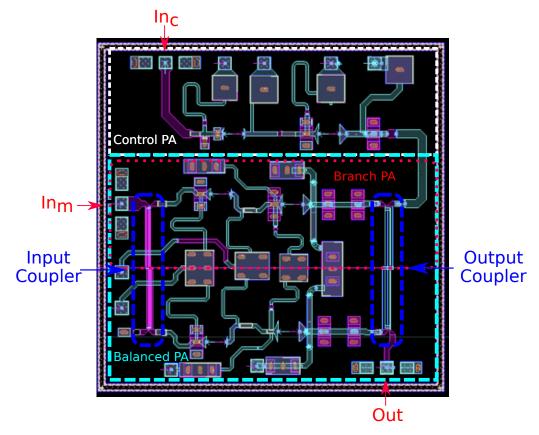

Allez, CIAO!

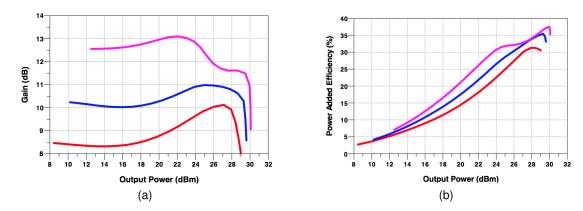

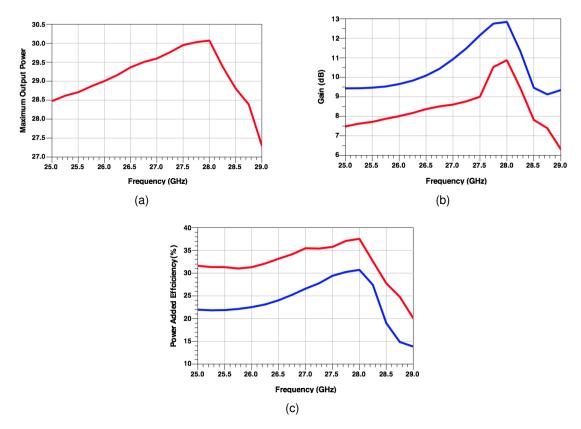

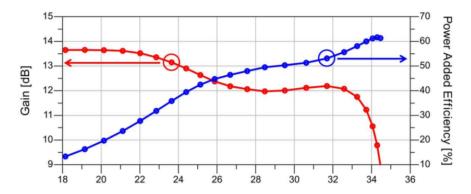

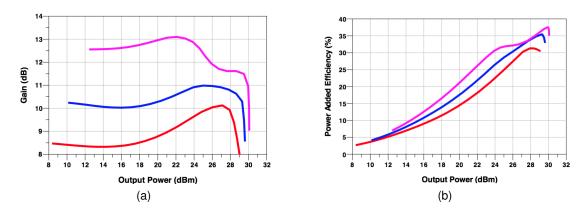

### **Abstract**

In modern communication standards, Power Amplifiers (PA) have to achieve high efficiencies over increasingly larger dynamic ranges and bandwidths, while maintaining stringent linearity requirements. Efficiency enhancement can be achieved by load modulated architectures such as the Doherty Power Amplifier. However, amplifiers based on this concept are typically associated with degradation in linearity. In 4G networks, digital predistortion was used to mitigate the non-linearities of load-modulated amplifiers. However, the greater bandwidths and complexity of 5G NR systems limit the applicability of DPD.

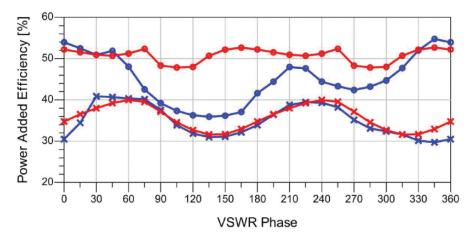

This thesis aims at addressing the inherent linearity of high efficiency power amplifiers, so that they can be operated efficiently without or with limited predistortion. It is focused on the Load Modulated Balanced Amplifier (LMBA).

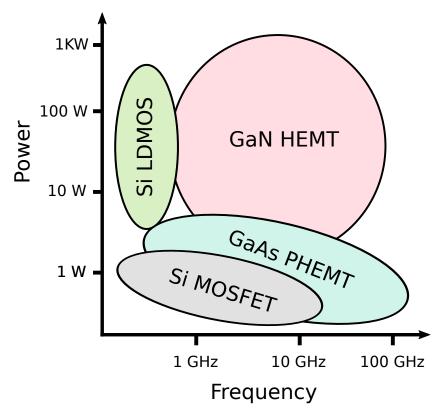

The LMBA is a recent architecture, presented as an alternative to the classic Doherty PA. A new mathematical analysis of the LMBA is proposed here, focused on the load modulation trajectory. This impedance-based analysis leads to the development of a new methodology for the design of linear/efficient power amplifiers from load-pull measurements of the main transistor. Applying this methodology to a 10W GaN HEMT, we show that three different amplifiers with similar performance in single-ended configuration result in very different performance when used inside an LMBA architecture. As predicted from our theory, the amplitude (AM-AM) and phase (AM-PM) distortions of the LMBA depend on the load trajectory. Choosing it so as to minimize the phase distortion, the second harmonic termination can then be selected to maximize the efficiency. The Class J second harmonic termination is identified as the best case, resulting in -40.5dBc ACLR (Adjacent Channel Leakage Ratio) with 40.5% drain efficiency at 2.4GHz when stimulated with a 10 MHz, 8.6dB PAPR (Peak to Average Power Ratio) LTE signal.

This same methodology is then applied at a K band 1W MMIC amplifier in GaAs technology. However, at these frequencies the second harmonic termination has a very small effect on the efficiency of the power amplifier. Lacking this extra degree of freedom, the load trajectory cannot be chosen for AM-PM mitigation, and the efficiency/linearity trade-off is degraded.

Finally, the origins and effects of impedance mismatch in power amplifiers is presented. The performance of the load modulated balanced amplifier under output impedance mismatch is studied. We observed that the efficiency enhancement of the LMBA is canceled if the optimal impedance is not presented at the output. A novel double balanced LMBA is then proposed to achieve mismatch resilience in high efficiency power amplifiers.

### Résumé

Les nouveaux standards de télécommunication, en particulier la cinquième génération, imposent aux amplificateurs de puissance de très hauts rendements énergétiques tout en respectant des limites très strictes en termes de linéarité. Ces hauts rendements pour des gammes de puissance étendues peuvent être atteint par des architectures d'amplificatuers à modulation de charge active, comme l'amplificateur Doherty ou Chireix. Cependant, ces derniers ont tendance à produire une grande degradation de linéarité. Dans le cadre de la 4G, la prédistorsion numérique était utilisée pour corriger ces non-linéarités. Les largeurs de bande étendues de la 5G et la complexité de certaines architectures de front-end limitent le champ d'action de ces techniques numériques.

Cette thèse vise à répondre aux problématiques liées à la linéarité des amplificateurs à modulation de charge active afin de permettre leur utilisation avec peu ou sans prédistorstion numérique. Elle se base sur une architecture récente, le Load Modulated Balanced Amplifier (LMBA). Un deuxième projet s'articule autour des performances du LMBA lorsque l'impédance présentée à la sortie de l'amplificateur est désadaptée.

Après une présentation des concepts de base des amplificateurs de puissance, l'architecture LMBA est présentée. Une nouvelle formulation mathématique en est dérivée, basée sur la trajectoire de la modulation d'impédance. Cette analyse conduit au développement d'une nouvelle méthodologie pour la conception de LMBA linéaires basée sur des mesures load-pull du transistor principal. En identifiant au préalable la trajectoire de charge qui minimise la distorsion de phase, l'impédance présentée à l'harmonique 2 peut être choisie afin de maximiser le rendement sur toute la gamme de puissance, tout en garantissant la linéarité.

En appliquant cette méthodologie à un transistor GaN de 10 W de Cree (CGH410F), on montre que trois amplificateurs avec des terminaisons harmoniques différentes conduisent à des grandes différences de performance quand utilisés dans un LMBA Une terminaison harmonique capacitive apporte le meilleur compromis rendement / linéarité. Le système final a présenté -40.5 dBc ACLR et 40.5% de rendement à 2.4 GHz stimulé avec un signal LTE de 10 MHz et 8.6 dB de PAPR.

Cette même méthodologie a été appliquée à un transistor GaAs en bande K. Cependant, à cette fréquence avec cette technologie nous avons constaté que l'harmonique 2 n'impactait que très peu les performances du transistor. Sans ce degré de liberté supplémentaire le compromis rendement/linéarité se trouve donc très limité.

Le deuxième objectif était concentré sur les origines et conséquences de la désadaptation d'impédance à des amplificateurs à modulation de charge active. Nous avons vu par simulation que l'amélioration du rendement du LMBA se trouvait très fortement dégradée lorsque l'impédaence de sortie n'était pas idéale. Une nouvelle architecture a donc été proposée, appelée le Double Balanced LMBA, qui présente une grande résilience à la désadaptation d'impédance.

# **Contents**

| Co  | ntents                                                                                                       | 1               |

|-----|--------------------------------------------------------------------------------------------------------------|-----------------|

| Lis | of Figures                                                                                                   | 2               |

| Lis | of Tables                                                                                                    | 9               |

| Int | Cellular Communication Standards                                                                             |                 |

| 1   | 1.4 Transistor Modelling                                                                                     | 28<br>33<br>35  |

| 2   | Conventional Load Modulation Architectures                                                                   | 49<br>63<br>66  |

| 3   | The Load Modulated Balanced Amplifier  3.1 Load Modulated Balanced Amplifier                                 | 83<br>89<br>92  |

| 4   | Practical Design of a linear and efficient LMBA  4.1 Design of three power amplifiers in classes J, B and J* | <b>95</b><br>95 |

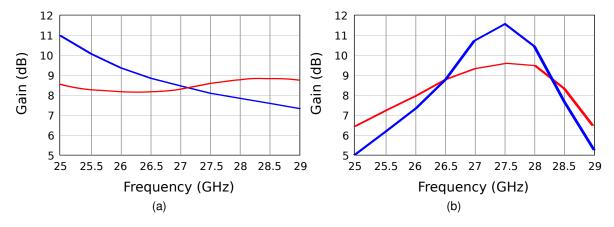

| 4                                             | Load Modulated Balanced Amplifier based on Harmonically Tuned Power Amplifiers .  4.4 Design of a 28 GHz LMBA in GaAs 0.10um technology                                                                                                                                                                                                                                                                                                                     | 118                              |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| !<br>!                                        | Mismatch Resilient Power Amplifier  5.1 Origins and effects of impedance mismatch on power amplifiers                                                                                                                                                                                                                                                                                                                                                       | 134<br>139                       |

| Cor                                           | nclusion and future work                                                                                                                                                                                                                                                                                                                                                                                                                                    | 147                              |

| Fre                                           | nch abstract – Résumé de la Thèse                                                                                                                                                                                                                                                                                                                                                                                                                           | 151                              |

| A I                                           | K Band MMIC Amplifiers in Win 0.10 $\mu\mathrm{m}$ pHEMT technology                                                                                                                                                                                                                                                                                                                                                                                         | 169                              |

| Bib                                           | liography                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 173                              |

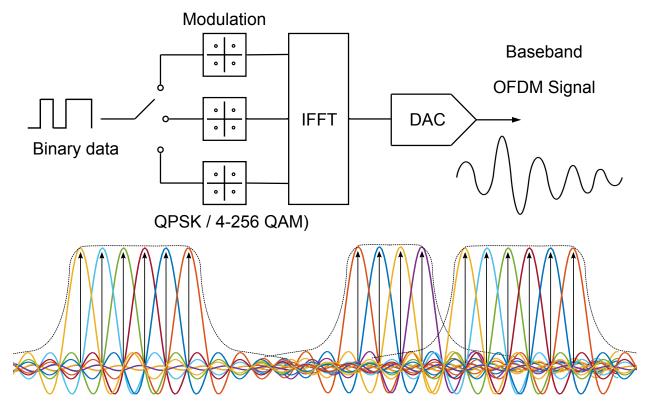

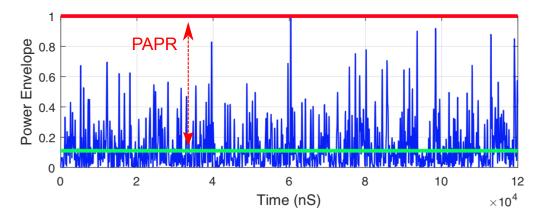

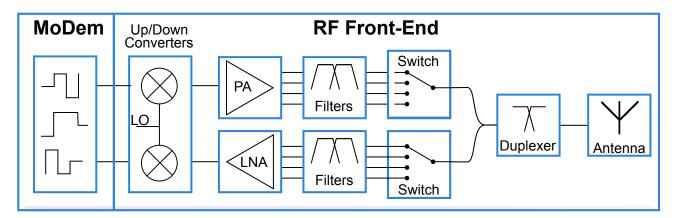

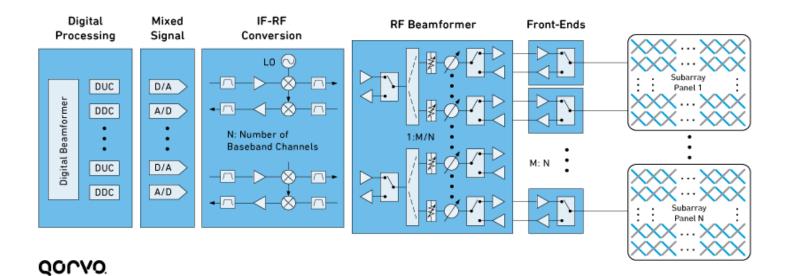

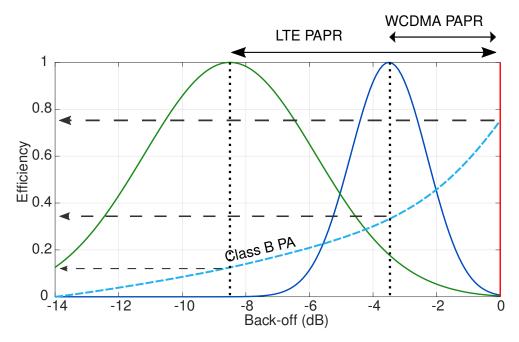

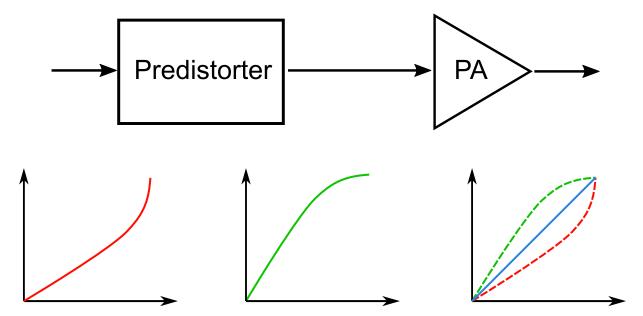

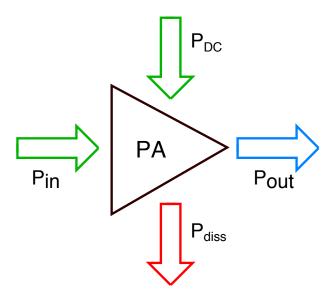

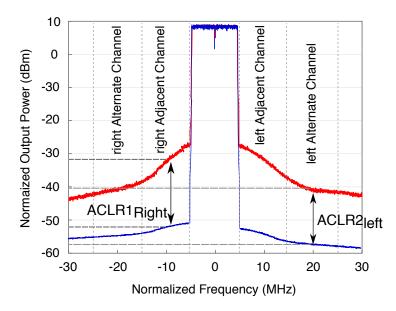

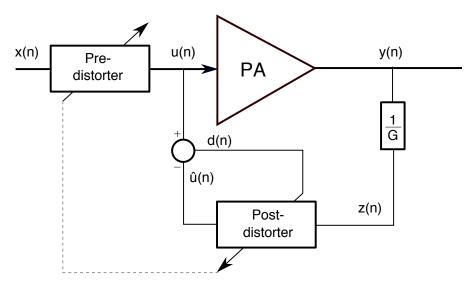

| I.1<br>I.2<br>I.3<br>I.4<br>I.5               | OFDMA Modulator and resulting spectrum 8.5dB PAPR OFDM waveform. In green the average power, in red the maximum power. Direct Conversion 5G RF transceiver Massive MIMO Transceiver Power Density Function of an LTE (green), WCDMA (dark blue) and GSM (red) signals versus OBO. In dashed blue line Class B PA efficiency versus OBO. Digital Predistortion: In red the predistorted signal, in green the PA characteristics, in blue the emitted signal. | 19<br>20<br>21<br>22             |

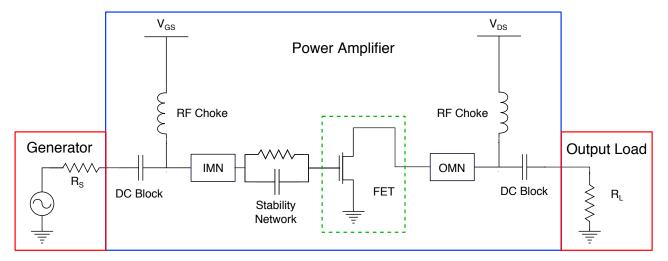

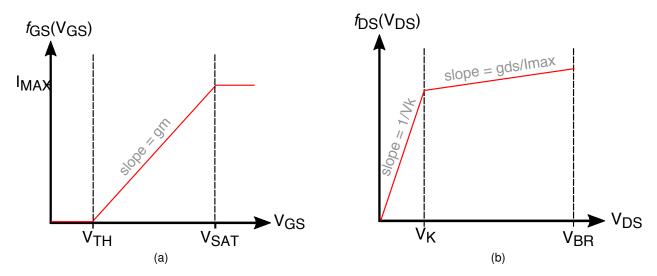

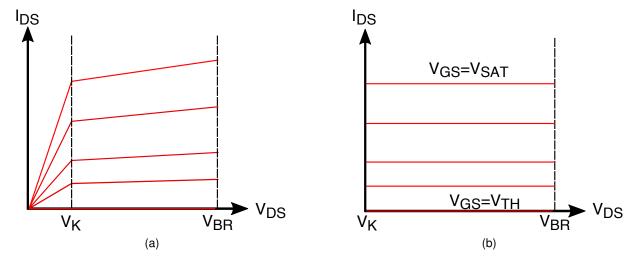

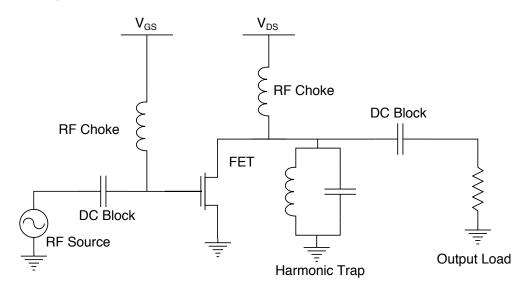

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7 | Power budget of a Power Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                           | 29<br>29<br>30<br>31<br>32<br>33 |

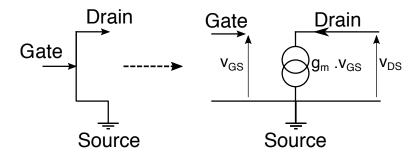

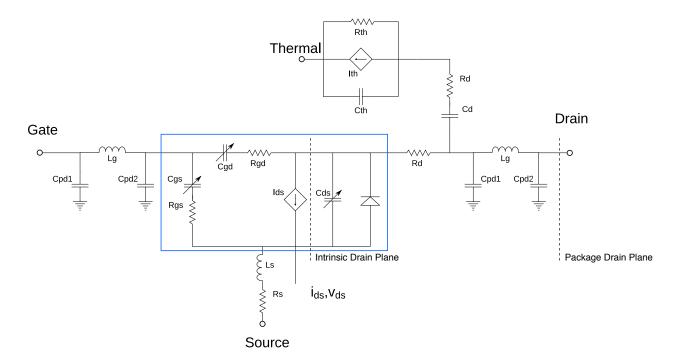

| 1.9<br>1.10<br>1.11                           | Symbol and simplified schematic of a Field Effect Transistor                                                                                                                                                                                                                                                                                                                                                                                                | 36<br>37<br>37                   |

|                                               | 2 Non-Linear model of the CGH Transistors from CREE                                                                                                                                                                                                                                                                                                                                                                                                         | 38<br>38                         |

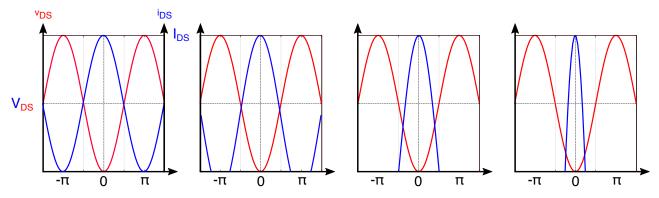

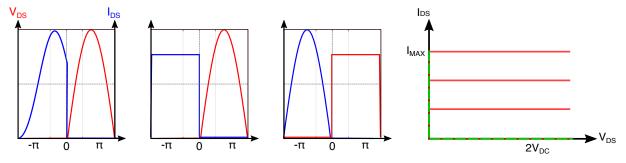

| 1.14 | The voltage (in red) and current (in blue) waveforms at maximum drive for the different amplifier classes A-AB-B-C, from left to right.                                                                                                                                                                                                                                                                                                            | 39 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

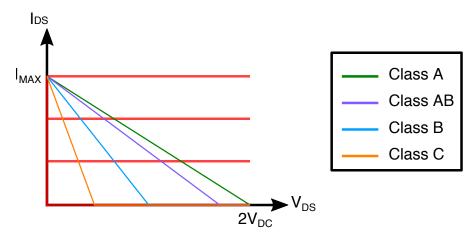

| 1.15 | Loadline for the different classes of operation                                                                                                                                                                                                                                                                                                                                                                                                    | 40 |

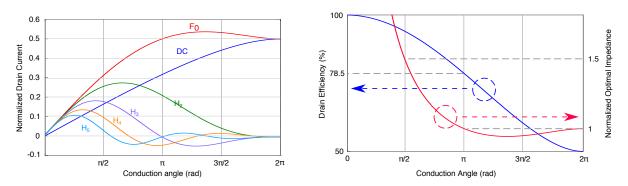

|      | On the left the different harmonic components of lds, on the right in red the drain efficiency and in blue the optimal impedance normalized to the class A impedance                                                                                                                                                                                                                                                                               | 42 |

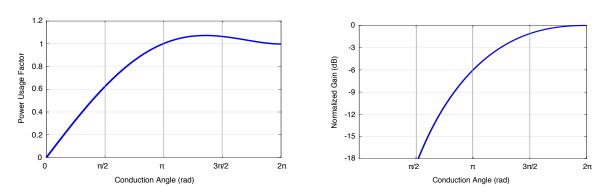

| 1.17 | On the left the Power Usage Factor, on the right the relative gain                                                                                                                                                                                                                                                                                                                                                                                 | 42 |

|      | Switched Mode Power Amplifier waveforms, from left to right class E, F, $F^{-1}$ . On the right the load line associated with SMPAs                                                                                                                                                                                                                                                                                                                | 43 |

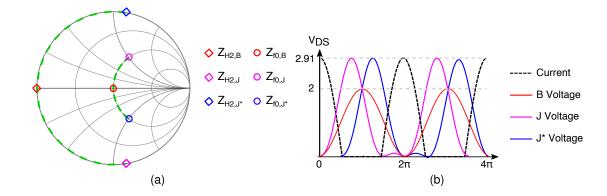

| 1.19 | (a) Continuous Modes impedance design space. In circles and squares the fundamental and second harmonic impedances for the $J/B/J^*$ cases. (b) Voltage and current waveforms for the $J/B/J^*$ cases                                                                                                                                                                                                                                              | 44 |

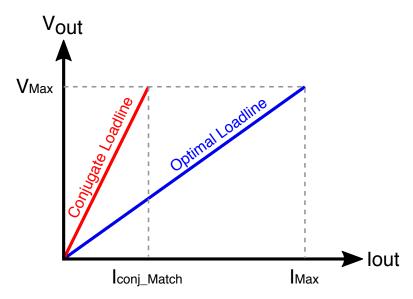

| 2.1  | Loadline associated with High Efficiency Architectures : on the left Load Modulation, on the right Supply Modulation                                                                                                                                                                                                                                                                                                                               | 47 |

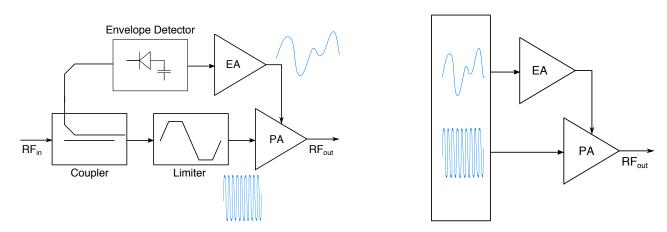

| 2.2  | (a) Envelope Elimination and Restoration (b) Polar Transmitter                                                                                                                                                                                                                                                                                                                                                                                     | 48 |

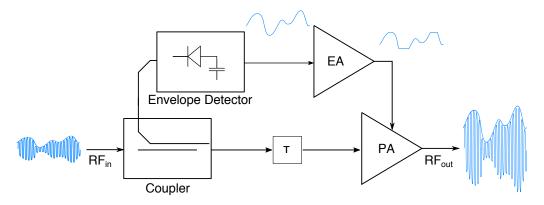

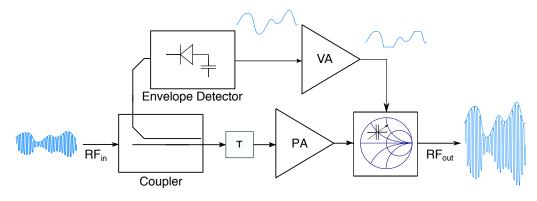

| 2.3  | Power Amplifier with Envelope Tracking                                                                                                                                                                                                                                                                                                                                                                                                             | 49 |

| 2.4  | Dynamic Load Modulation                                                                                                                                                                                                                                                                                                                                                                                                                            | 50 |

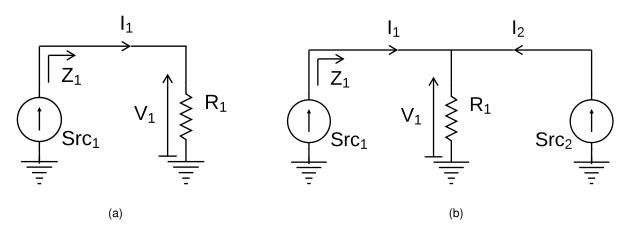

| 2.5  | Active Load Modulation mechanism                                                                                                                                                                                                                                                                                                                                                                                                                   | 51 |

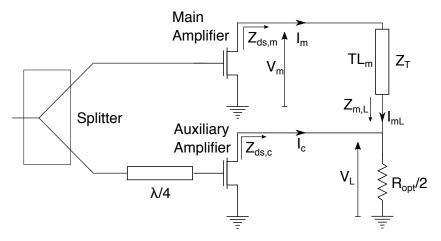

| 2.6  | Conventional Doherty Power Amplifier                                                                                                                                                                                                                                                                                                                                                                                                               | 52 |

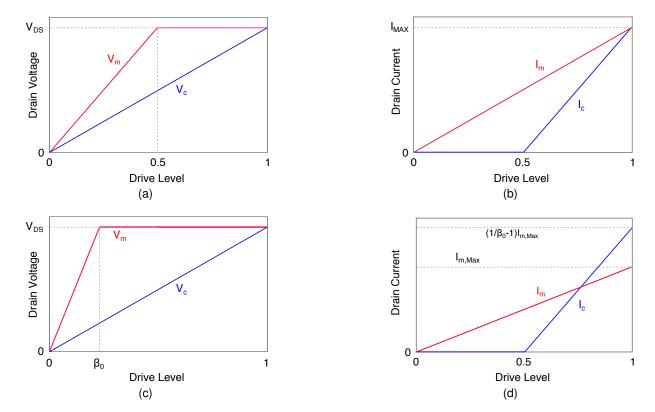

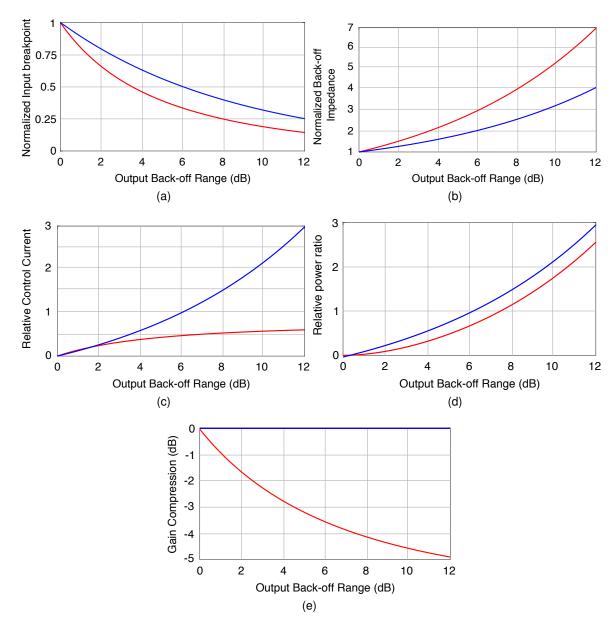

| 2.7  | (a) Voltage and (b) current profiles for the main (red) and auxiliary (blue) transistors of a 6 dB Doherty Power Amplifier. In (c) and (d) for an arbitrary output back-off                                                                                                                                                                                                                                                                        | 53 |

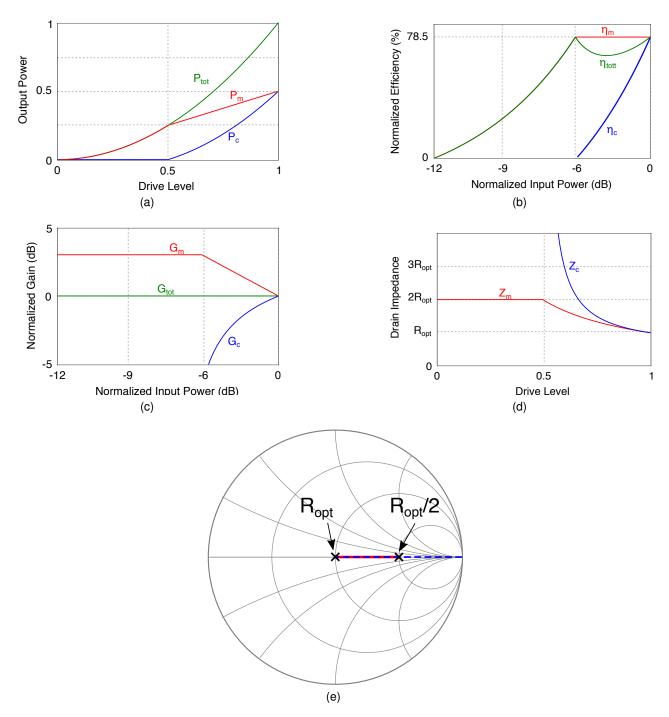

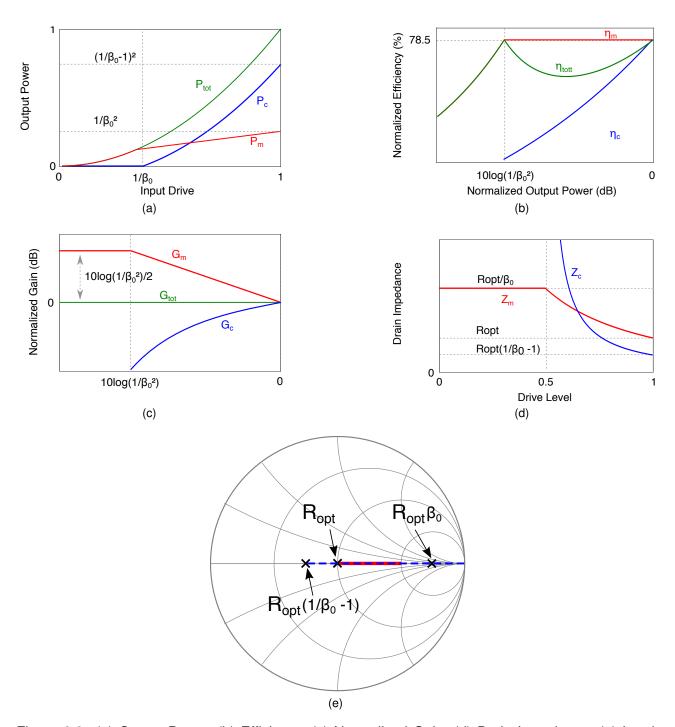

| 2.8  | (a) Output Power, (b) Efficiency, (c) Normalized Gain, (d) Drain Impedance, (e) Load Trajectory of main (in red) and auxiliary (in blue) transistors and at the output (in green) of a 6 dB back-off Doherty Power Amplifier                                                                                                                                                                                                                       | 56 |

| 2.9  | (a) Output Power, (b) Efficiency, (c) Normalized Gain, (d) Drain Impedance, (e) Load Trajectory of main (in red) and auxiliary (in blue) transistors and at the output (in green) of an X dB back-off Doherty Power Amplifier                                                                                                                                                                                                                      | 57 |

| 2.10 | Different outphasing combining: (a) Differential combining and (b) Series combining                                                                                                                                                                                                                                                                                                                                                                | 59 |

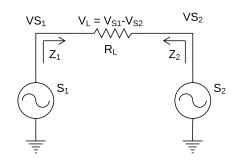

|      | Load Trajectory of the simple Outphasing combiner. (a) The equivalent parallel resistance $R_p$ , (b) the parallel susceptance $X_p$ and (c) the load trajectory on the Smith chart                                                                                                                                                                                                                                                                | 61 |

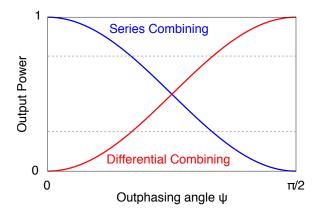

| 2.12 | Output power versus outphasing angle                                                                                                                                                                                                                                                                                                                                                                                                               | 61 |

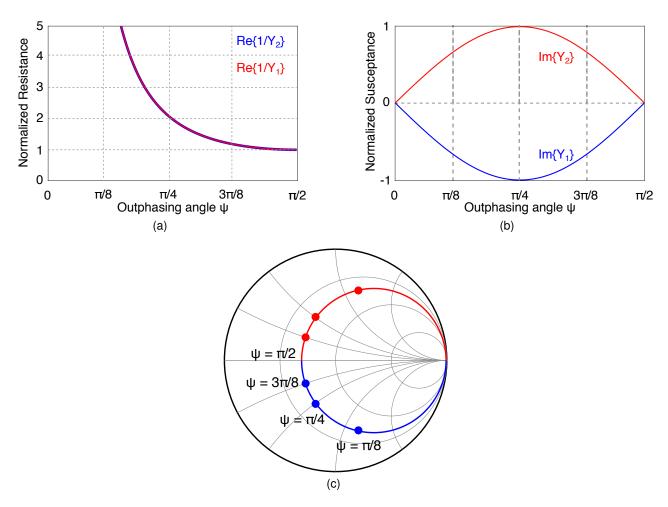

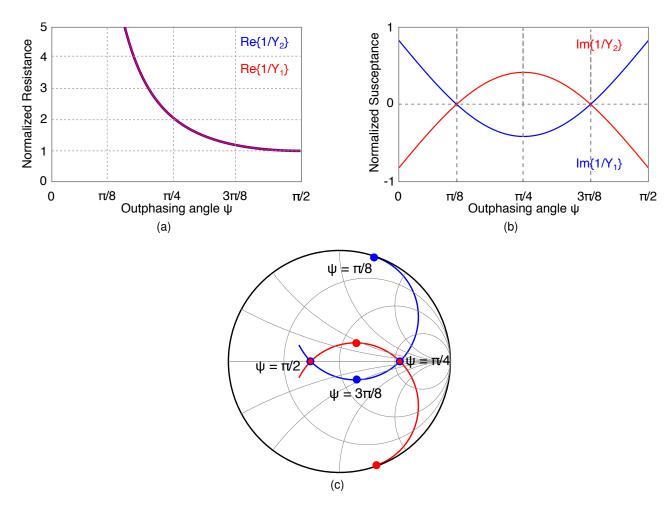

| 2.13 | Load Trajectory of the Chireix Outphasing combiner. (a) The equivalent parallel resistance $R_p$ , (b) the parallel susceptance $X_p$ and (c) the load trajectory on the Smith chart                                                                                                                                                                                                                                                               | 62 |

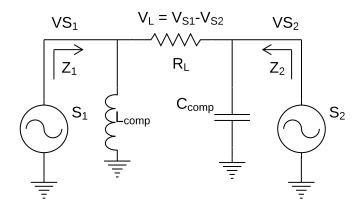

| 2.14 | Chireix Combiner                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62 |

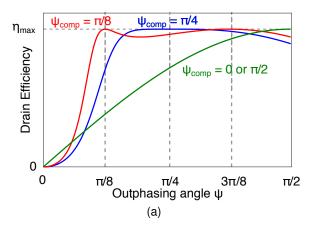

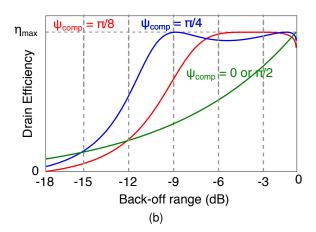

| 2.15 | OPA theoretical drain efficiency for different compensating reactances, in (a) versus the outphasing angle and in (b) versus the resulting output power                                                                                                                                                                                                                                                                                            | 63 |

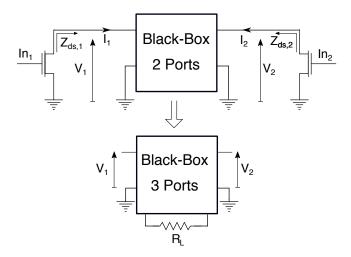

| 2.16 | Generalized Active Load Modulation Power Amplifier                                                                                                                                                                                                                                                                                                                                                                                                 | 65 |

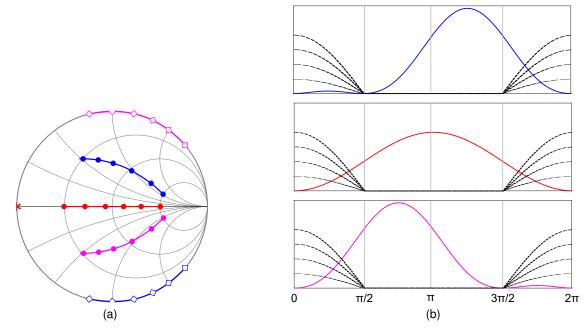

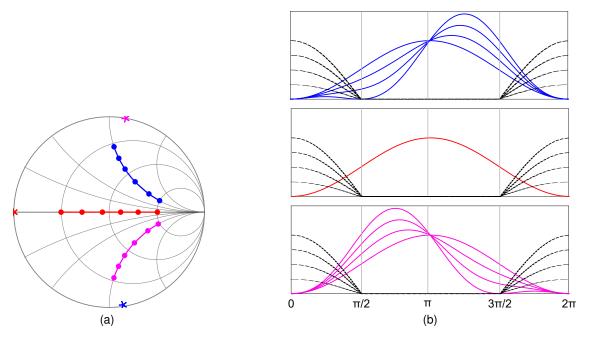

| 2.17 | Continuous Modes theory applied to load modulation. On the right, in dotted black lines the current waveform for different drive levels. In blue, red and magenta the voltage waveform for the classes J, B and $J^*$ second harmonic terminations, for different drive levels. On the Smith chart on the right we can see the corresponding fundamental (in dots) and second harmonic (in diamonds) terminations throughout the load modulation.  | 67 |

| 2.18 | Fixed Second harmonic continuous modes load modulation. On the right, in dotted black lines the current waveform for different drive levels. In blue, red and magenta the voltage waveform for the classes J, B and J* second harmonic terminations, for different drive levels. On the Smith chart on the right we can see the corresponding fundamental (in dots) and second harmonic (in diamonds) terminations throughout the load modulation. | 67 |

|      | acto, and cocond narmonic (in diamonic) terminations throughout the load modulation.                                                                                                                                                                                                                                                                                                                                                               | 51 |

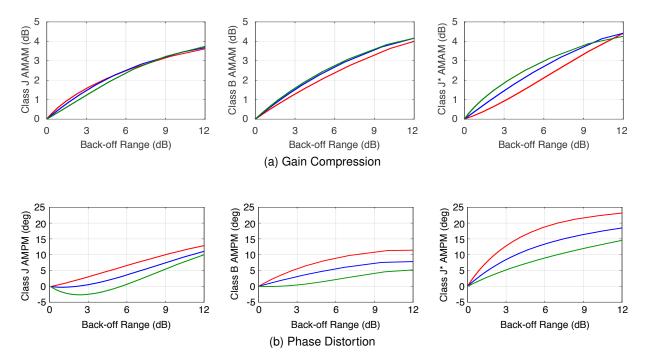

| 2.19 | on the right. From top to bottom, Class J, B and J* harmonic terminations. For the J and J* case, the back-off and peak power termination simulations are grouped. The dotted line show the performance of a load modulated amplifier with the corresponding second harmonic. The color code is identical as on the plotted trajectories on the Smith chart of figure 2.20                                                                                | 69 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.20 | In solid line with dot markers, load trajectories providing maximum drain efficiency for five different harmonic terminations, (a) at the transistor's package plane and (b) at the de-embeded intrinsic drain plane. The corresponding second harmonic terminations are marked with a cross, using the same color code.                                                                                                                                  | 70 |

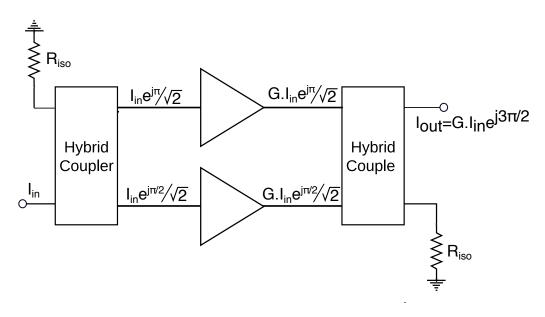

| 3.1  | Balanced Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73 |

| 3.2  | Load Modulatd Balanced Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                          | 74 |

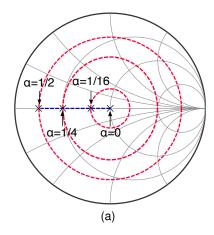

| 3.3  | LMBA's load modulation mechanism. In (a) the relative magnitude of the control current is varied while the relative phase is held constant. In (b) the relative phase is varied while the relative magnitude is held constant.                                                                                                                                                                                                                            | 75 |

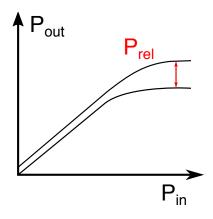

| 3.4  | Output power of the main and the control amplifiers in the proposed High Efficiency LMBA. $P_{rel}$ , the ratio of powers of the control amplifier to the balanced amplifier, increases in the high power region, resulting in load modulation.                                                                                                                                                                                                           | 76 |

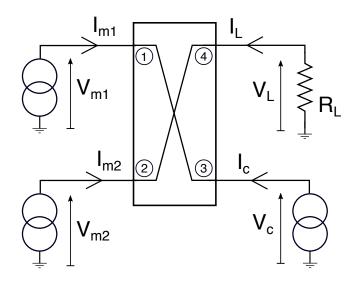

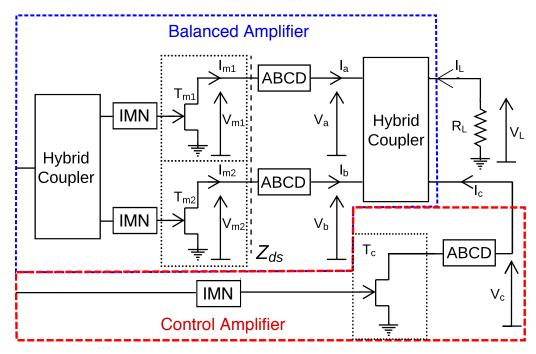

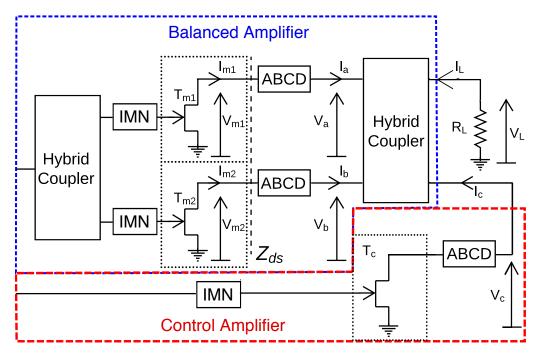

| 3.5  | Schematic diagram of a Load Modulated Balanced Amplifier                                                                                                                                                                                                                                                                                                                                                                                                  | 78 |

| 3.6  | Comparison of a Doherty PA (in blue) and a Doherty-like LMBA (in red)                                                                                                                                                                                                                                                                                                                                                                                     | 82 |

| 3.7  | Schematic of the Generalized LMBA                                                                                                                                                                                                                                                                                                                                                                                                                         | 83 |

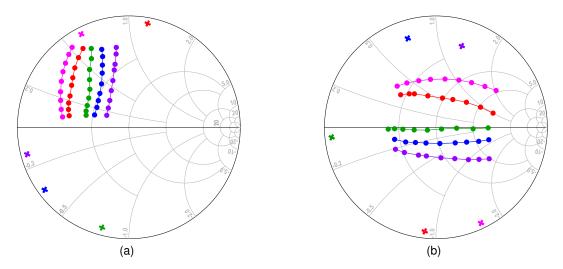

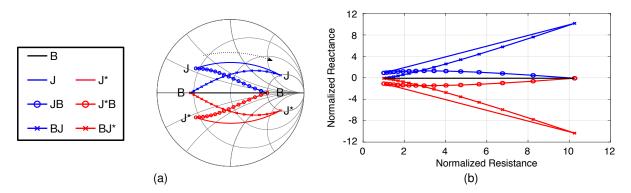

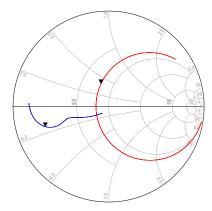

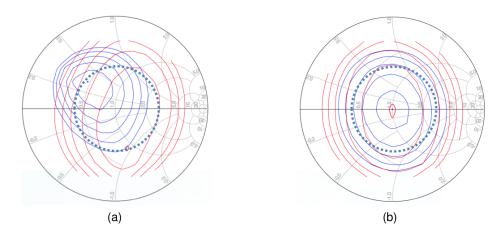

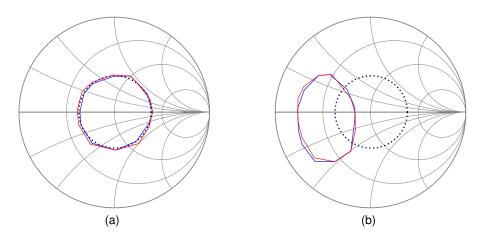

| 3.8  | The seven load trajectories compared in this section: B (black), J and J* (solid blue and red), BJ and BJ* (blue and red, cross markers), and JB and J*B (blue and red, circle markers), presented in the (a) Smith chart, and (b) impedance plane.                                                                                                                                                                                                       | 88 |

| 3.9  | (a) Phase distortion and (b) gain compression versus $\gamma$ for the different load trajectories presented in Fig. 3.8, calculated from (5.20)–(3.42)                                                                                                                                                                                                                                                                                                    | 88 |

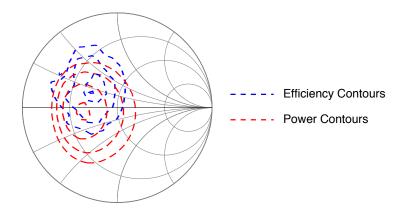

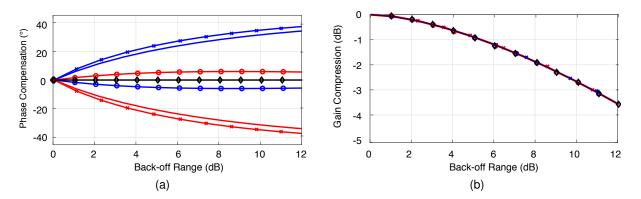

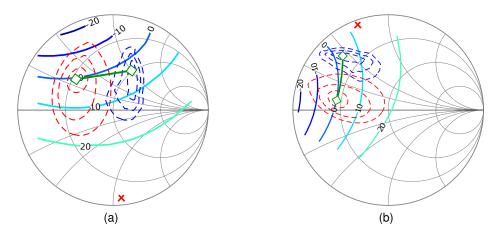

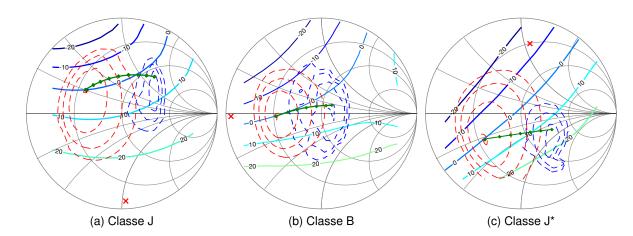

| 3.10 | Results of the load-pull measurements for the classes J/B/J*. The solid lines represent the intrinsic phase distortion contours. The dotted red and blue contours show respectively the maximum power and maximum efficiency at back-off. The red cross marks the second harmonic termination. The diamond markers represent the selected load trajection.                                                                                                |    |

|      | tories.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 90 |

| 3.11 | Estimated overall phase and amplitude distortion of an LMBA based on (3.42) and the load-pull data. In order to catch the distortion due to the load modulation only, the transistor is in a very linear zone, with input power of 15 dBm and 0 dB of compression.                                                                                                                                                                                        |    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 90 |

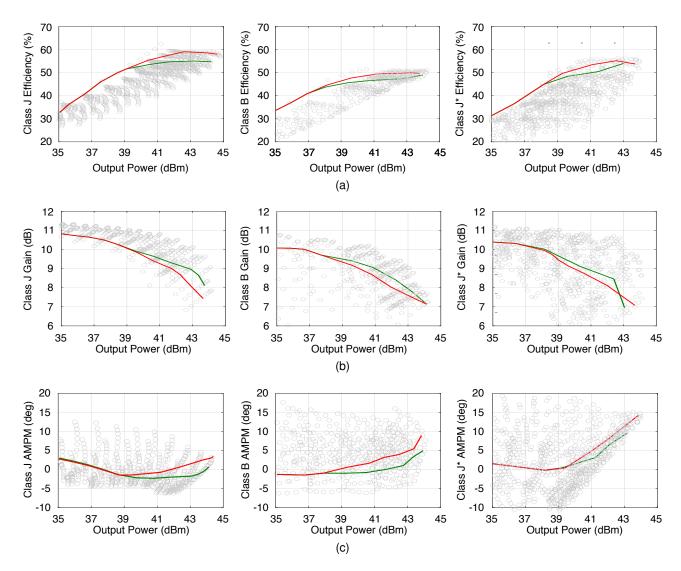

| 3.12 | From top to bottom, simulated drain efficiency, gain compression and phase distortion for the class $J/B/J^*$ , from left to right. The gain compression and phase distortion take into account both the load-pull data and the load trajectory, according to (3.42)                                                                                                                                                                                      | 91 |

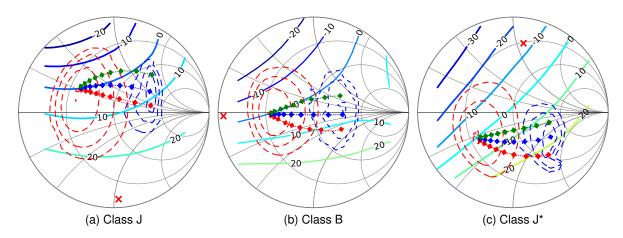

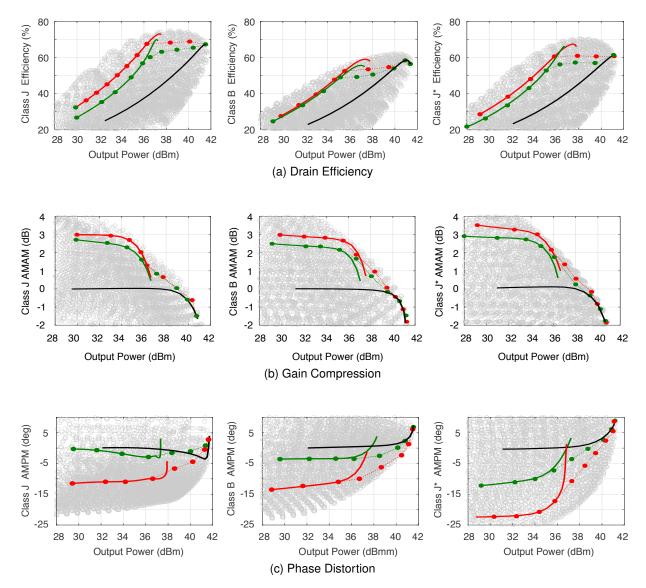

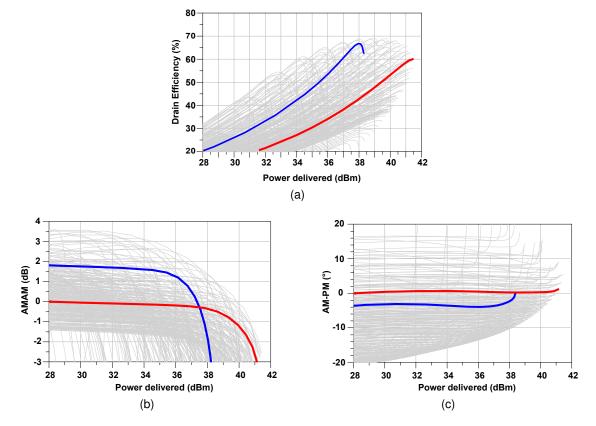

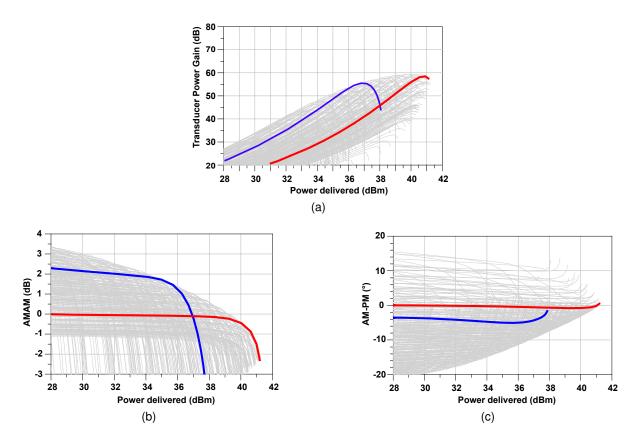

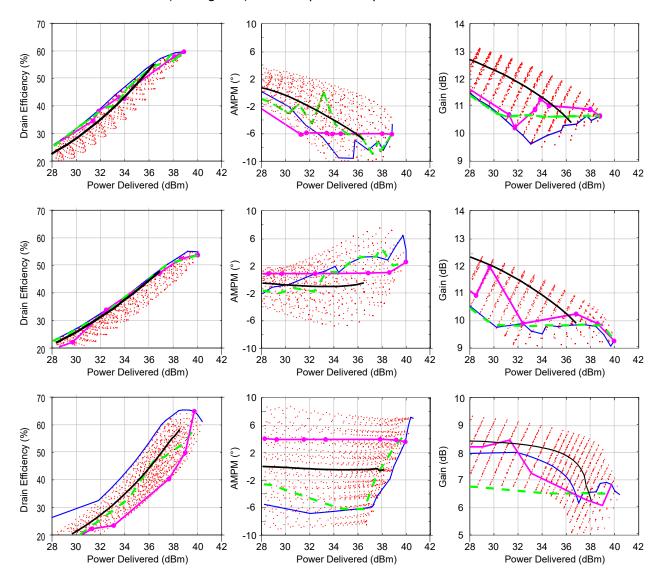

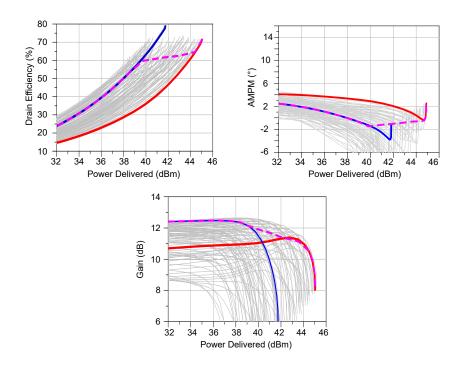

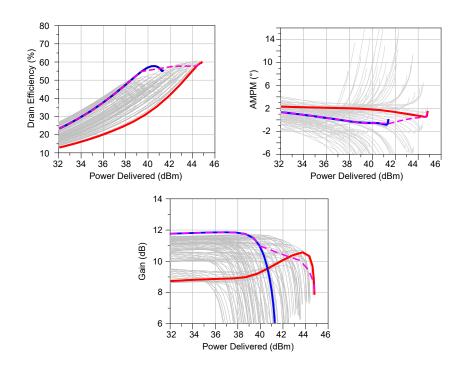

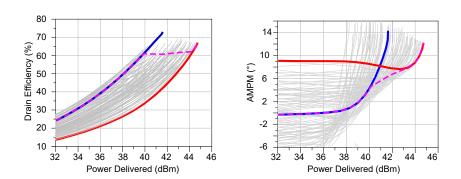

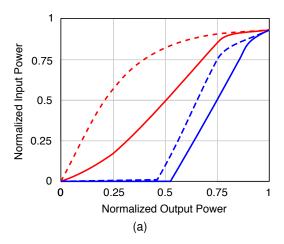

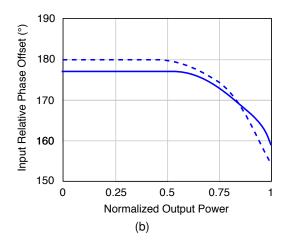

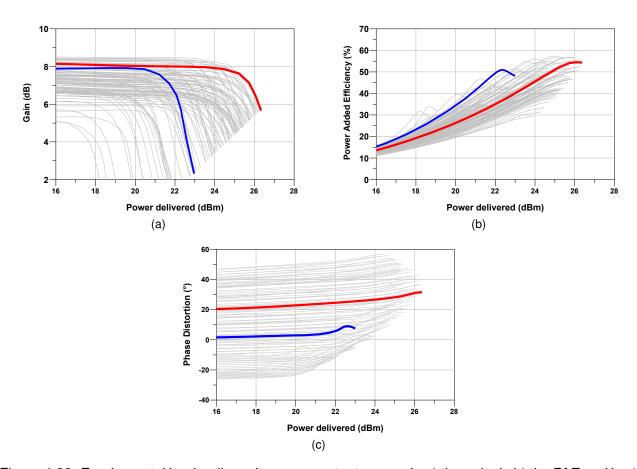

| 4.1  | (a) Drain Efficiency, (b) AM-AM and (c) AM-PM versus output power for the class J second harmonic termination. Each grey curve corresponds to a different output impedance. The red curves correspond to the impedance resulting in maximum output power. The blue curves correspond the selected back-off impedance. AM-AM and AM-PM curves are normalized to the value at low power (28 dBm) of the red curve, corresponding to a peak-power impedance. | 97 |

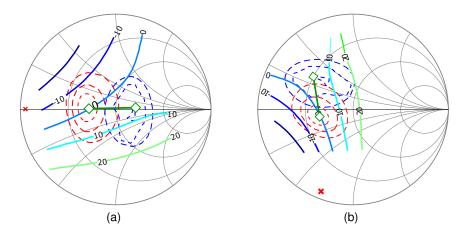

| 4.2  | Load pull contours at the intrinsic plane (a) and package plane (b) for the class J second harmonic termination. Maximum power contours are in red, maximum efficiency contours at an output power of 37 dBm are in blue. The two diamond markers represent the impedances chosen for maximum and back-off power. The red cross represents the second harmonic impedance                                                                                   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.3  | (a) Drain Efficiency, (b) AM-AM and (c) AM-PM versus output power for the class B second harmonic termination. Each grey curve corresponds to a different output impedance. The red curves correspond to the impedance resulting in maximum output power. The blue curves correspond the selected back-off impedance. AM-AM and AM-PM curves are normalized to the value at low power (28 dBm) of the red curve, corresponding to a peak-power impedance   |

| 4.4  | Load pull contours at the intrinsic plane (a) and package plane (b) for the class B second harmonic termination. Maximum power contours are in red, maximum efficiency contours at an output power of 37 dBm are in blue. The two diamond markers represent the impedances chosen for maximum and back-off power. The red cross represents the second harmonic impedance                                                                                   |

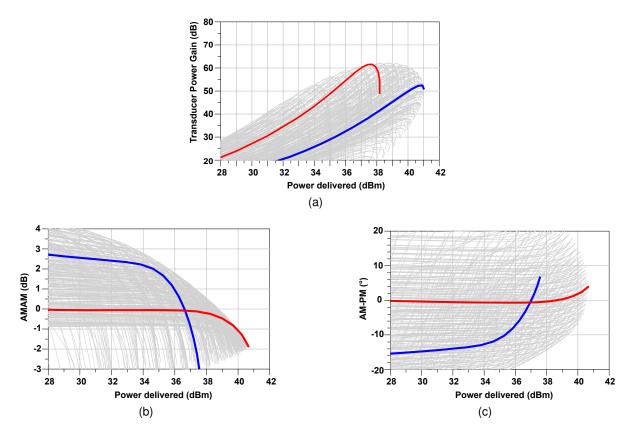

| 4.5  | (a) Drain Efficiency, (b) AM-AM and (c) AM-PM versus output power for the class J* second harmonic termination. Each grey curve corresponds to ba different output impedance. The red curves correspond to the impedance resulting in maximum output power. The blue curves correspond the selected back-off impedance. AM-AM and AM-PM curves are normalized to the value at low power (28 dBm) of the red curve, corresponding to a peak-power impedance |

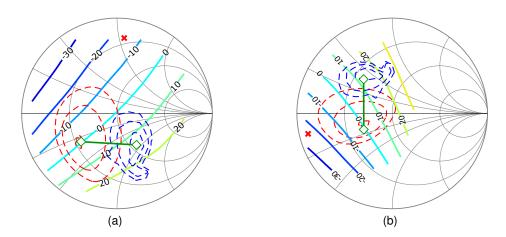

| 4.6  | Load pull contours at the intrinsic plane (a) and package plane (b) for the class J* second harmonic termination. Maximum power contours are in red, maximum efficiency contours at an output power of 37 dBm are in blue. The two diamond markers represent the impedances chosen for maximum and back-off power. The red cross represents the second harmonic impedance                                                                                  |

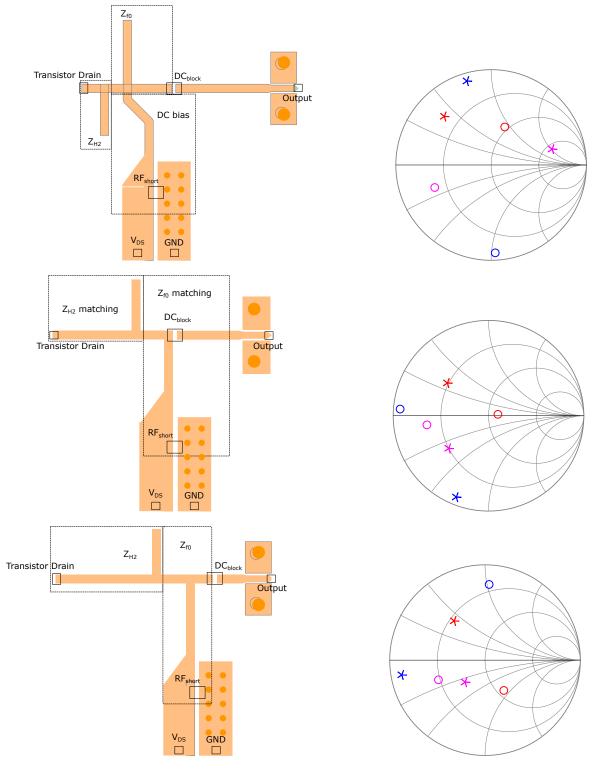

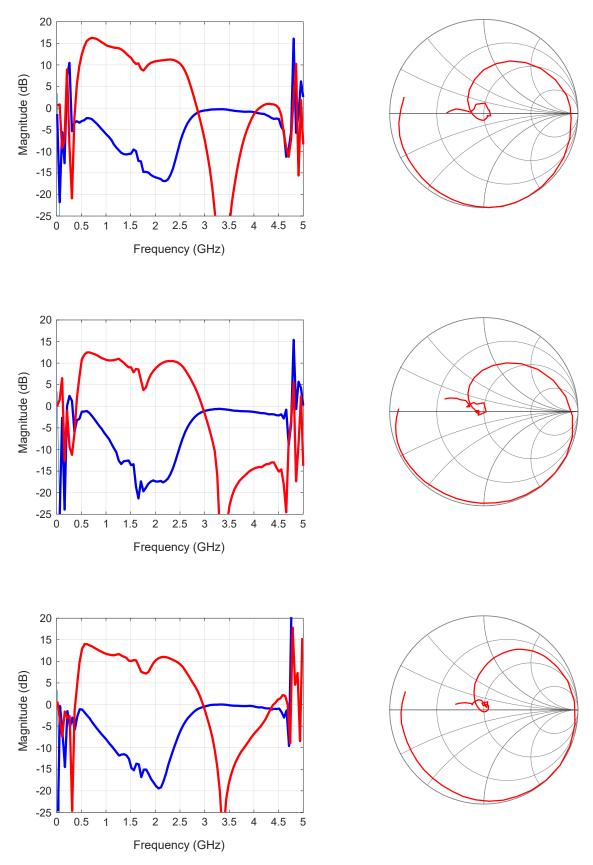

| 4.7  | On the left, from top to bottom Output Matching Networks of the class J, B and J* PAs. On the right the resulting fundamental (in red), second harmonic (in blue) and third harmonic (in magenta) terminations at the intrinsic drain plane (with circles) and at the package plane (with stars)                                                                                                                                                           |

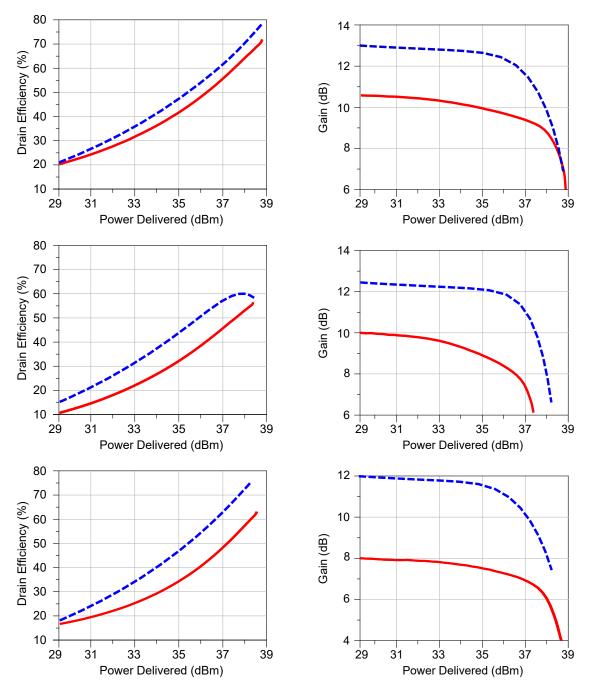

| 4.8  | Simulated performance for the class J, B and J* amplifiers, from top to bottom. The left charts present the drain efficiency (in blue) and gain (in red) versus output power. The charts in the midle show the voltage (in blue) and current (in red) waveforms at 1dB compression. The charts on the right show the resulting load-line in red and in grey the DC drain current versus drain voltage for different gate voltages                          |

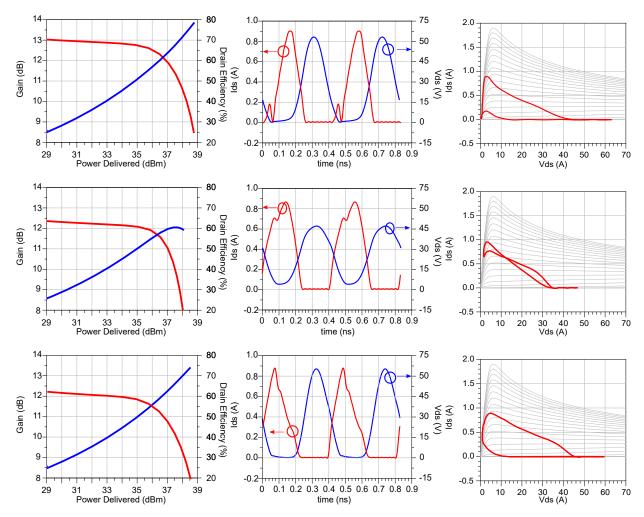

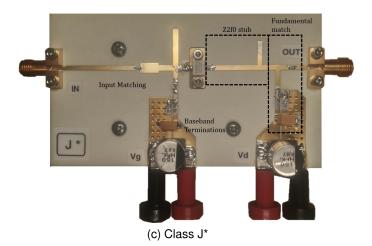

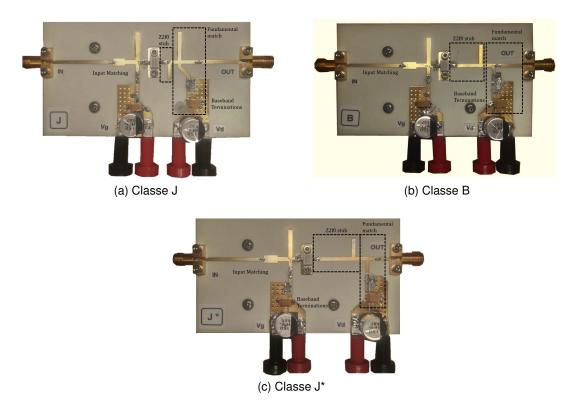

| 4.9  | Power Amplifier boards                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.10 | S parameters measuremets of the class J, B and J* boards, from top to bottom. On the left plots the S21 parameter is in red and the S11 in blue, and the Smith charts on the right present the S11                                                                                                                                                                                                                                                         |

| 4.11 | Measured and simulated results for the Class J, B and $J^*$ , from top to bottom. On the left the drain efficiency, on the right the gain. In red the measured performance, in dotted blue the simulated                                                                                                                                                                                                                                                   |

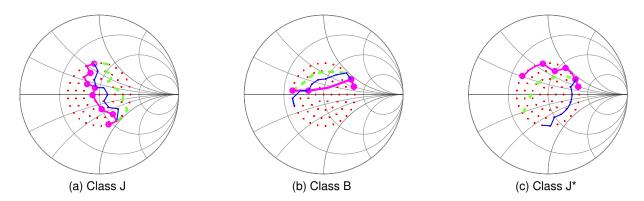

| 4.12 | Optimal Load trajectories for maximum efficiency (in blue), constant AM-AM (in green) and constant AM-PM (in magenta) for each power amplifier                                                                                                                                                                                                                                                                                                             |

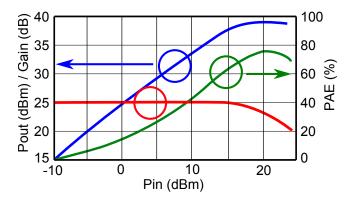

| 4.13 | Load-pull measurements of the class J,B and J* amplifiers, from top to bottom. From left to right drain efficiency, AM-PM and gain versus output power. The black curve shows the results under $50\Omega$ . The blue, green and magenta curves show the extrapolated results in a load modulation scenario, tracking the optimal trajectory for maximum efficiency, flat  |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | AM-AM or flat AM-PM respectively                                                                                                                                                                                                                                                                                                                                           | 107 |

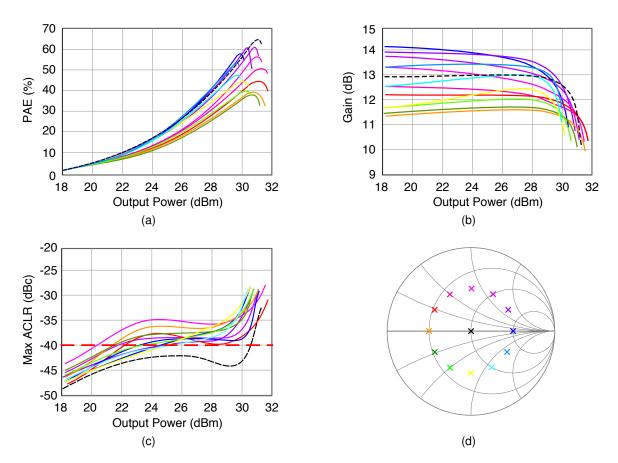

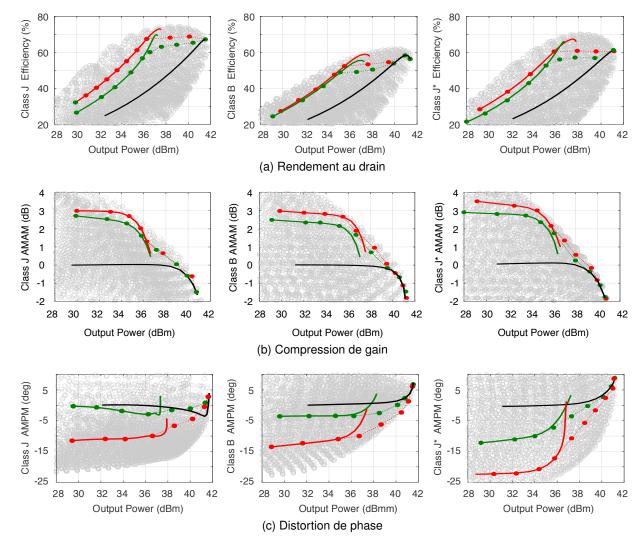

|      | Simulation test bench of the LMBA                                                                                                                                                                                                                                                                                                                                          | 109 |

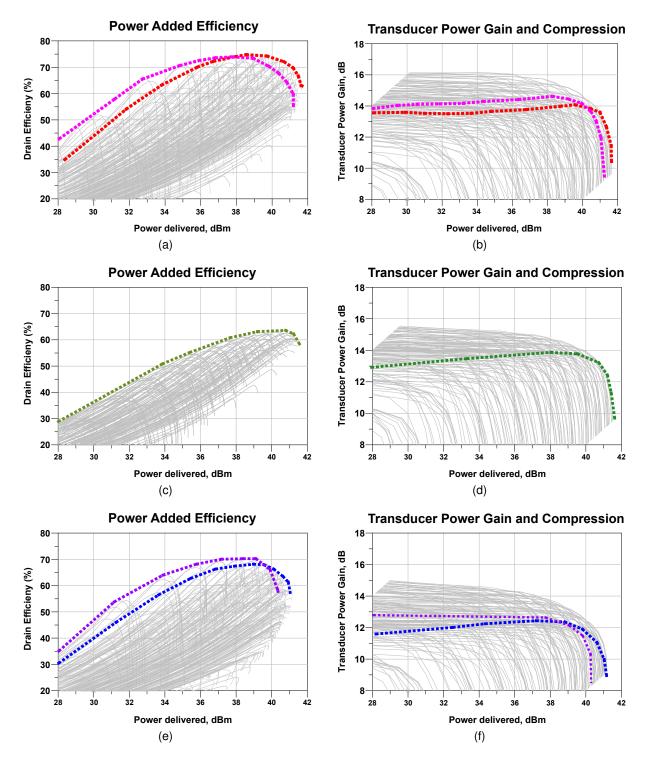

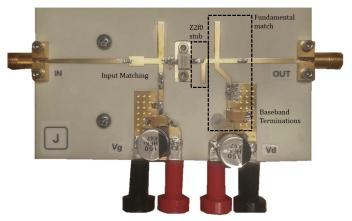

| 4.15 | Simulated Load Modulated Balanced amplifier. The constituent amplifiers are from top to bottom in classes J, B and J*. The input of the control amplifier is attenuated in order to obtain a control to branch amplifier signal ratio that is at first -30 dB, and then -9 up to +3                                                                                        |     |

|      | dB, in steps of 3 dB. In blue the attenuator is set at -30 dB, i.e. there is no control signal.                                                                                                                                                                                                                                                                            |     |

|      | In red the curve reaching maximum efficiency is highlighted                                                                                                                                                                                                                                                                                                                | 110 |

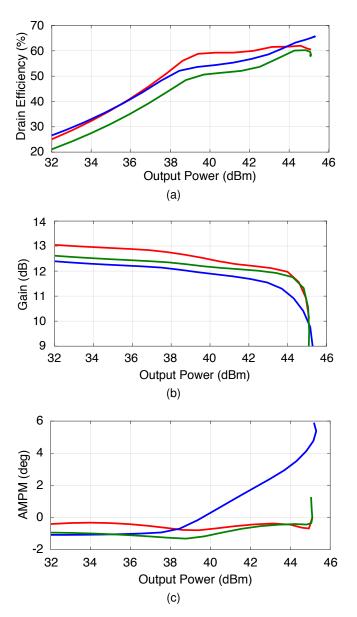

| 4.16 | Simulated performance for the class J (in red), B (in green) and J* (in blue) LMBA. (a) –                                                                                                                                                                                                                                                                                  |     |

|      | Drain Efficiency, (b) – gain and (c) – Phase distortion versus output power                                                                                                                                                                                                                                                                                                | 111 |

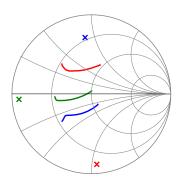

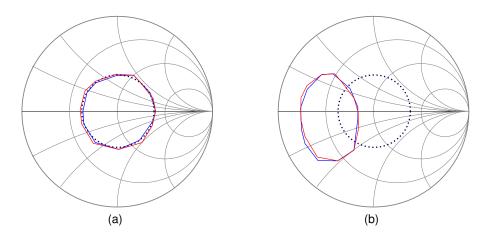

| 4.1/ | Simulated load trajectories for the class J (in red), B (in green) and J* (in blue) LMBA.                                                                                                                                                                                                                                                                                  | 440 |

| 4 40 | Crosses represent the corresponding second harmonic termination                                                                                                                                                                                                                                                                                                            |     |

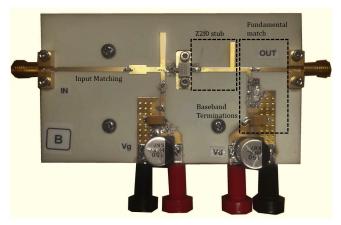

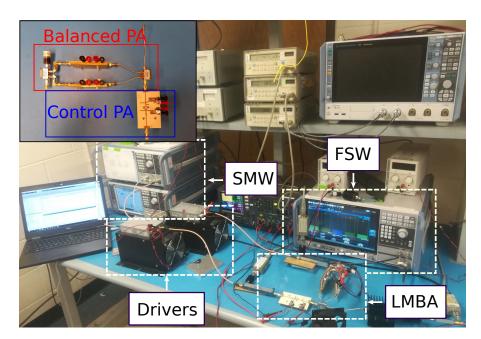

|      | Photograph of the experimental test setup, with inset showing detail of LMBA under test.                                                                                                                                                                                                                                                                                   | 112 |

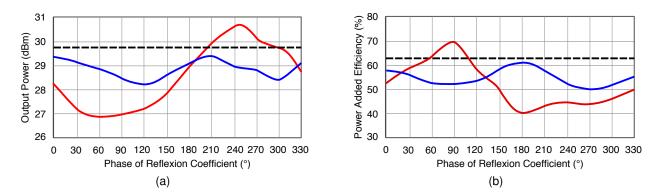

| 4.19 | Measured performance under CW stimulus of the class J, B and J* LMBA, from left to right. (a) – drain efficiency, (b) – gain and (c) – phase distortion versus output power.                                                                                                                                                                                               |     |

|      | The highlighted red curves present a high efficiency trajectory, the green curves present                                                                                                                                                                                                                                                                                  |     |

|      | a linear-efficient trajectory.                                                                                                                                                                                                                                                                                                                                             | 113 |

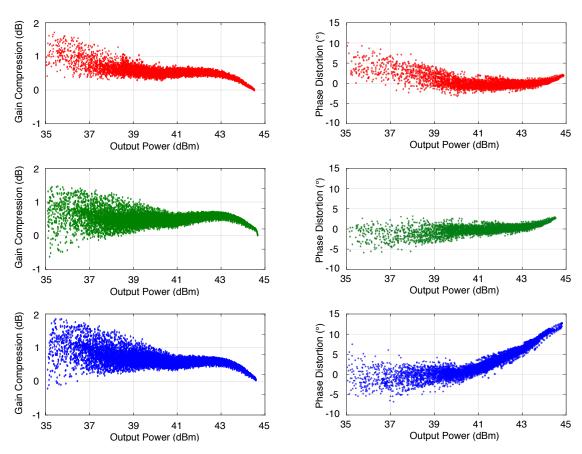

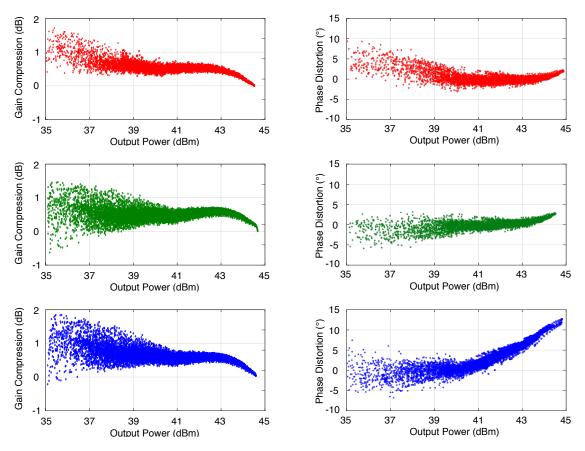

| 4.20 | Dynamic measurements of gain compression (on the left) and Phase distortion (on the                                                                                                                                                                                                                                                                                        |     |

|      | right) with a 10 MHz, 8.7 dB PAPR LTE signal for the classes J, B and J* Doherty-like                                                                                                                                                                                                                                                                                      |     |

|      | LMBA, from top to bottom                                                                                                                                                                                                                                                                                                                                                   | 115 |

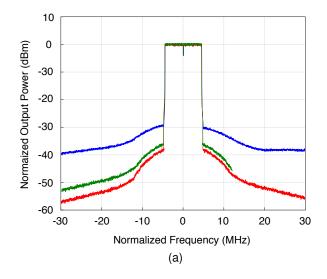

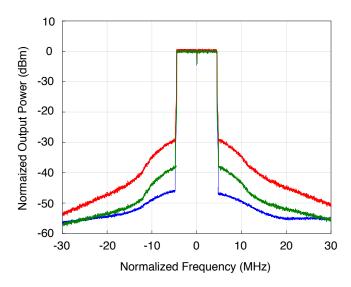

| 4.21 | Spectrum of the class J, B and J* Doherty-like LMBA in red, green and blue respectively,                                                                                                                                                                                                                                                                                   |     |

|      | with a 10 MHz, 8.7 dB PAPR LTE signal                                                                                                                                                                                                                                                                                                                                      | 115 |

| 4.22 | In red and blue, spectrum of the unlinearized Class J LMBA with a fixed phase offset of 190° (in red) and 170° (in green). In blue the spectrum with a 170° phase offset after                                                                                                                                                                                             |     |

| 4.00 | applying DPD                                                                                                                                                                                                                                                                                                                                                               | 116 |

| 4.23 | Shaping functions for the Dual-Input Class J Doherty-like LMBA. On the left the amplitude of the normalized input versus the normalized output for the balanced (in red) and control (in blue) amplifiers for a higher linearity (solid line) and higher efficiency (dotted line) shaping. On the right the input relative phase offset versus the normalized output power |     |

|      | for a higher linearity (solid line) and higher efficiency (dotted line) shaping                                                                                                                                                                                                                                                                                            | 117 |

| 4.24 | S11 (in blue) and S22 (in red) simulations of the transistor.                                                                                                                                                                                                                                                                                                              |     |

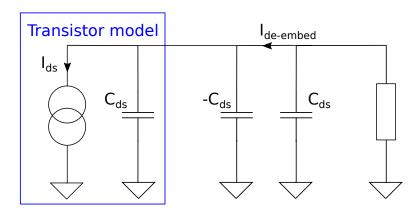

|      | De-embeding of the transistor's $C_{ds}$ parasitic capacitance                                                                                                                                                                                                                                                                                                             |     |

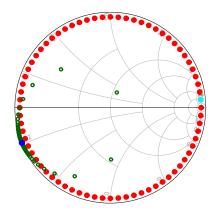

|      | Harmonic load-pull simulation results. In red the second harmonic impedances presented                                                                                                                                                                                                                                                                                     |     |

|      | at the transistor's physical drain access. In green the corresponding impedance seen at                                                                                                                                                                                                                                                                                    |     |

|      | the de-embeded intrinsic drain plane. The impedance highlighted by the cyan dot at the                                                                                                                                                                                                                                                                                     |     |

|      | physical drain access is transformed into the impedance highlighted by the blue dot at the                                                                                                                                                                                                                                                                                 |     |

|      | de-embeded intrinsic drain plane                                                                                                                                                                                                                                                                                                                                           | 120 |

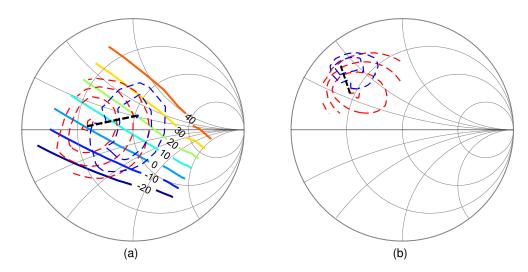

| 4.27 | Fundamental load pull results, on the left at the de-embeded intrinsic drain plane and on                                                                                                                                                                                                                                                                                  |     |

|      | the right at the physical drain access. In red maximum power contours, in blue maximum                                                                                                                                                                                                                                                                                     |     |

|      | PAE at a fixed output power of 22 dBm and in coloured lines the estimated overall AM-PM                                                                                                                                                                                                                                                                                    |     |

|      | of the corresponding LMBA at a fixed output power of 22 dBm. The black dotted line is the load trajectory that maximizes PAE                                                                                                                                                                                                                                               | 101 |

| 4 28 | Fundamental load-pull results versus output power. In a) the gain, in b) the PAE and in                                                                                                                                                                                                                                                                                    | 141 |

| 1.20 | c) the estimated overall AM-PM of the corresponding LMBA. In red and blue the curves                                                                                                                                                                                                                                                                                       |     |

|      | corresponding to the peak output power and maximum back-off efficiency respectivelly.                                                                                                                                                                                                                                                                                      | 121 |

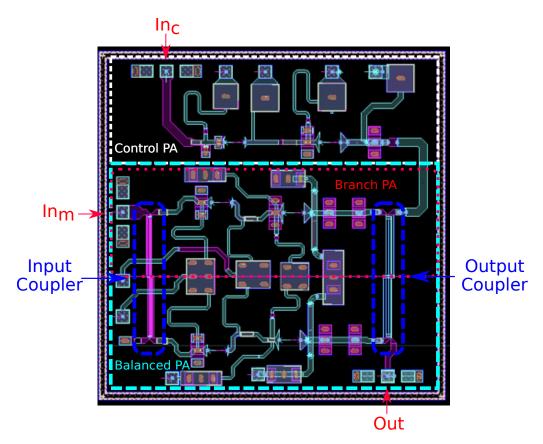

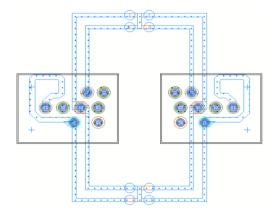

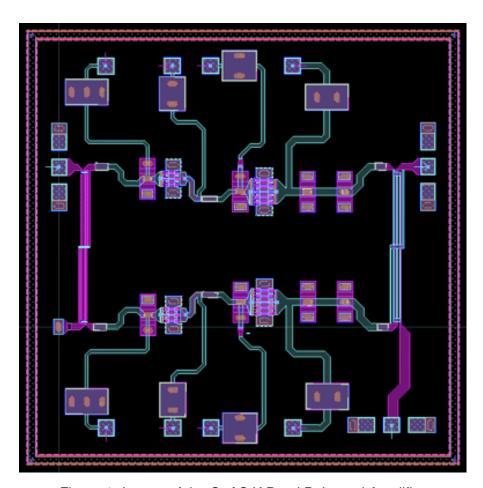

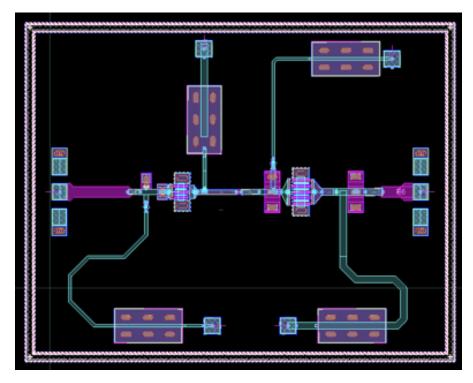

| 4.29 | Layout of the GaAs Load Modulated Balanced Amplifier                                                                                                                                                                                                                                                                                                                       |     |

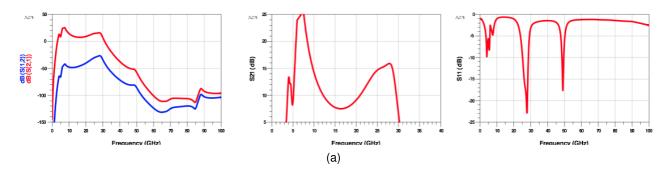

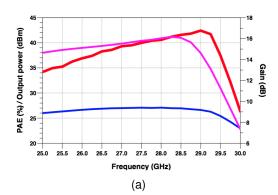

| 4.31<br>4.32<br>4.33 | at 27 GHz (in blue) 28 GHz (in pink) and 29 GHz (in red)                                                                                                                                                                                                                                                                    |     |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| E 1                  | ·                                                                                                                                                                                                                                                                                                                           |     |

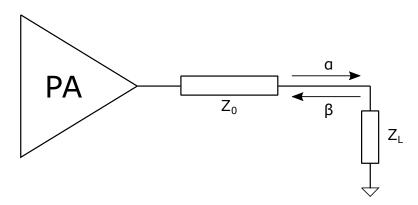

| 5.1                  | Impedance mismatch: When the output impedance $Z_L$ is different from the predifined characteristic impedance $Z_0$ , part of the forward wave $\alpha$ generated by the power amplifier will be reflected back. This reflected wave $\beta$ will perturb the operation of the power amplifier and decrease its performance | 129 |

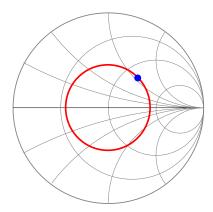

| 5.2                  | Graphic representation of impedance mismatch. The red circle represent a VSWR 2:1, equivalent to a $\Gamma=0.33$ . The blue dot corresponds to a $\Gamma=0.33e^{j\pi/4}$ , or, considering $Z_0=50\Omega$ , an impedance $Z_L=69.5+j36.8\Omega$                                                                             |     |

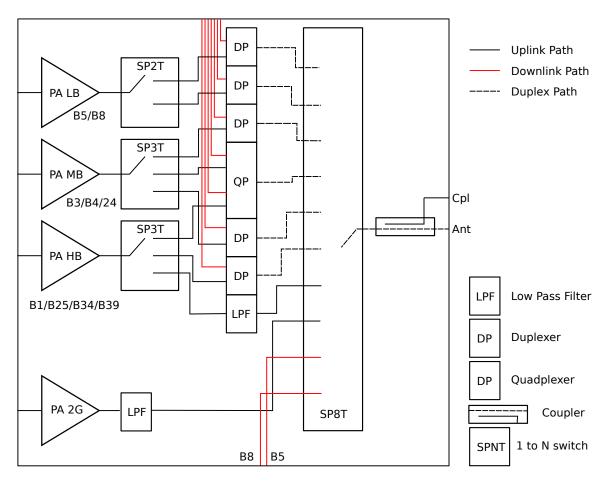

| 5.3                  | User Equipment RF Front End example. Here an LTE Cat 12 triple band 2G/3G/4G RFFE                                                                                                                                                                                                                                           | 130 |

| 0.0                  | from Mediatek Phase 5 platform. Source : SOMOS Semiconductor                                                                                                                                                                                                                                                                | 132 |

| 5.4                  | Load-pull measurements at 0.9 GHz of a 1W CMOS Power Amplifier from SOMOS Semi. In a), b) and c) PAE, Gain and maximum ACLR versus output power respectively, in d)                                                                                                                                                         | 400 |

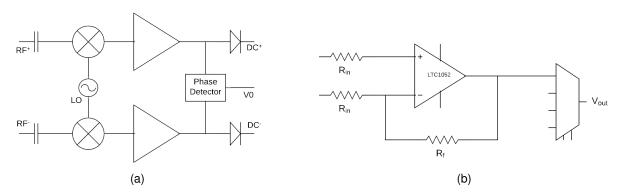

| 5.5                  | the presented impedances                                                                                                                                                                                                                                                                                                    | 133 |

| 5.5                  | VSWR=1:3. Dotted lines represent the values with $50\Omega$                                                                                                                                                                                                                                                                 | 133 |

| 5.6                  | In a) a complex impedance detector, measuring the amplitude and phase difference of two different voltages ( $RF_+$ and $RF$ . In b) the –simpler– voltage rms detector used in                                                                                                                                             |     |

|                      | the 6-ports reflectometry approach.                                                                                                                                                                                                                                                                                         | 135 |

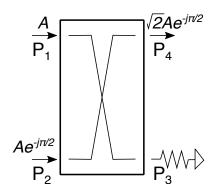

| 5.7                  | Schematic of a hybrid coupler. Ports 1 and 2 represent the in-phase and quadrature ports, and ports 3 and 4 the isolated and output ports                                                                                                                                                                                   | 137 |

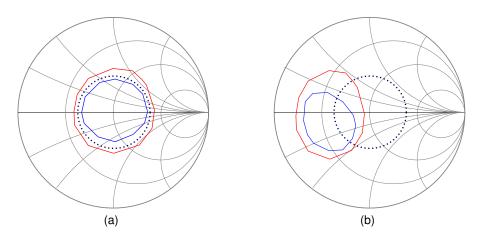

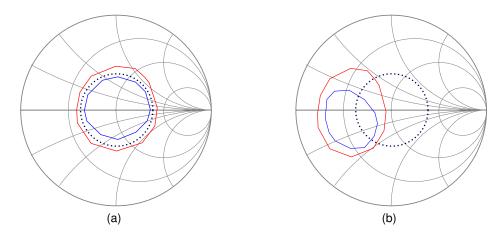

| 5.8                  | Comparison of load-pull measurements of –a a parallel combined amplifier (with a Wilkin-                                                                                                                                                                                                                                    | 137 |

|                      | son combiner) and -b a balanced amplifier (with hybrid couplers). In red we have peak                                                                                                                                                                                                                                       |     |

|                      | power contours and in blue peak PAE contours                                                                                                                                                                                                                                                                                | 138 |

| 5.9                  | Comparison of load-pull measurements of the parallel combined amplifier (in red) and balanced amplifier (in blue). Figure a) presents the peak output power and figure b) the                                                                                                                                               | 400 |

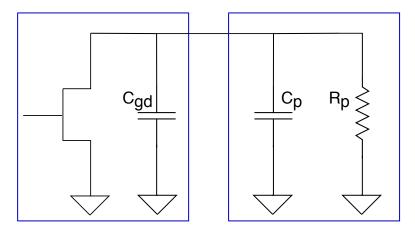

| 5 10                 | peak PAE versus the phase of the reflection coefficient for a $ \Gamma  = 0.33$ Model of transistor and output matching network in RFIC design. The $C_p$ capacitance is                                                                                                                                                    | 138 |

| 5.10                 | the exact opposite of the $C_{ds}$ capacitance, in order to cancel it out. The $R_p$ resistance is                                                                                                                                                                                                                          |     |

|                      | therefore the load presented at the intrinsic drain plane                                                                                                                                                                                                                                                                   | 139 |

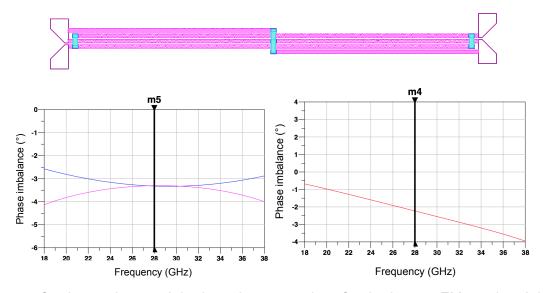

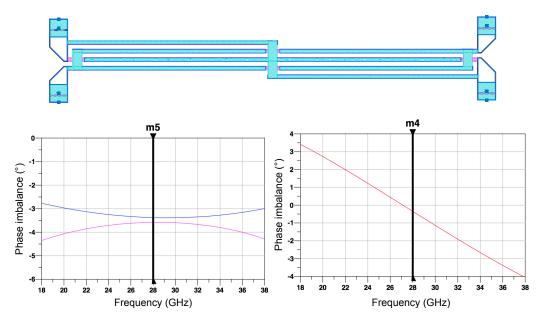

| 5.11                 | Layout of the hybrid coupler in BT technology. The square boxes represent the IPD                                                                                                                                                                                                                                           |     |

| <b>5</b> 40          | capacitors that have to be connected with copper pillars on the substrate                                                                                                                                                                                                                                                   | 140 |

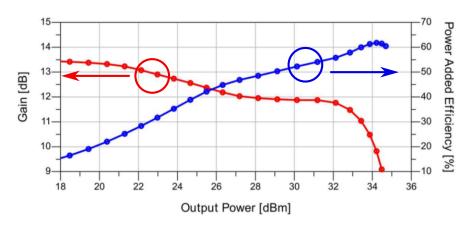

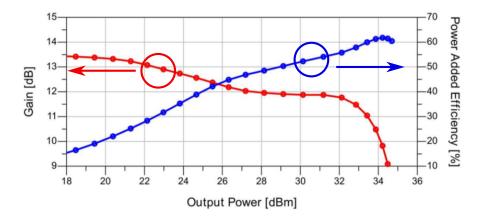

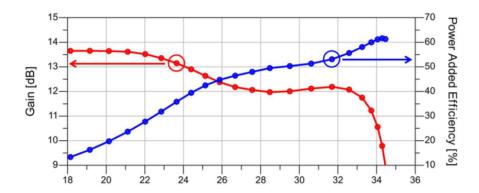

| 5.12                 | Performance of the CMOS Load Modulated Balanced Amplifier. In red the Gain versus the output power, in blue the Power Added Efficiency versus the output power                                                                                                                                                              | 140 |

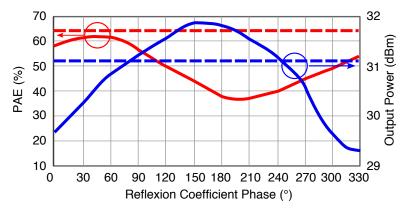

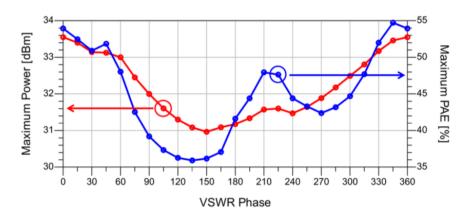

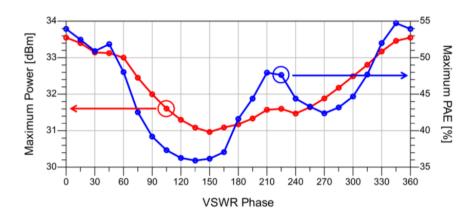

| 5.13                 | Maximum power (in red) and Power Added Efficiency (in blue) versus the phase of the                                                                                                                                                                                                                                         | 140 |

|                      | reflexion coefficient $\Gamma$ , for a VSWR of 3:1                                                                                                                                                                                                                                                                          | 142 |

| 5.14                 | In red and blue simulated drain impedance seen by each branch PA of the balanced                                                                                                                                                                                                                                            |     |

|                      | amplifier, in black the presented load impedance. On the left when at back-off, when the                                                                                                                                                                                                                                    |     |

| E 4 F                | control amplifier is turned-off. On the right at peak power, under load modulation                                                                                                                                                                                                                                          |     |

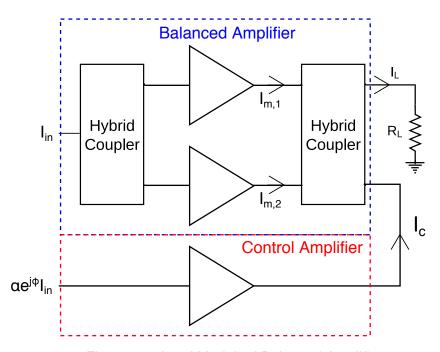

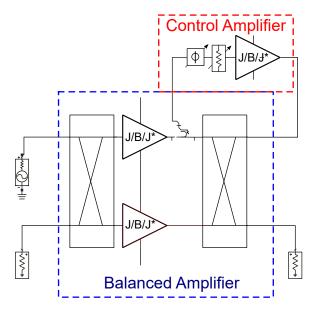

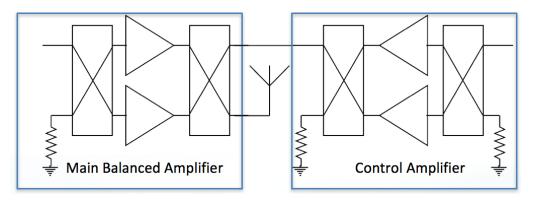

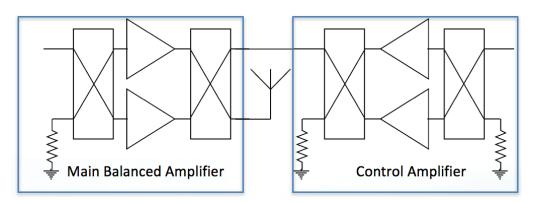

|                      | Schematic diagram of the Double Balanced Load Modulated Balanced Amplifier Performance of the Double Balanced Load Modulated Balanced Amplifier. In red the gain                                                                                                                                                            | 142 |

| 5.10                 | and in blue the Power Added Efficiency versus the output power                                                                                                                                                                                                                                                              | 143 |

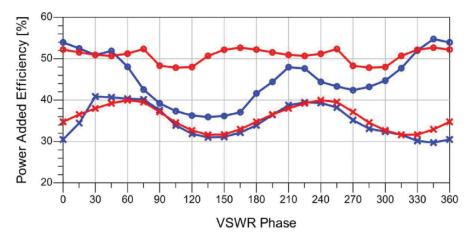

| 5.17 | reflexion coefficient $\Gamma$ , for a VSWR of 3:1. With dot markers at peak power, with x markers                                                                                                                                                                                |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.18 | at back-off power                                                                                                                                                                                                                                                                 |

|      | amplifier, in black the presented load impedance. On the left when at back-off, when the control amplifier is turned-off. On the right at peak power, under load modulation 144                                                                                                   |

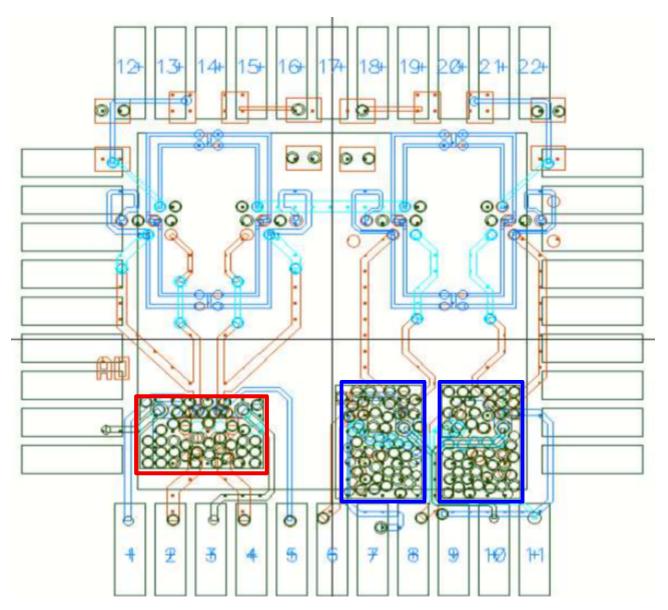

| 5.19 | Layout of the Double Balanced Load Modulated Balanced Amplifier. We see here the                                                                                                                                                                                                  |

|      | layout of the substrate (in BT technology) which incorporates the OMN and the output combiners                                                                                                                                                                                    |

| 20   | Schéma d'un amplificateur LMBA avec des blocks ABCD représentant les circuits d'adaptation                                                                                                                                                                                        |

|      | d'impédance de sortie                                                                                                                                                                                                                                                             |

| 21   | Simulation load-pull pour les trois terminaisons harmoniques J/B/J*. Les cercles de puis-<br>sance sont en pointillés rouges, les cercles de rendement à puissance de back-off en<br>pointillés bleus et la distorsion AM-PM en traits colorés. Les croix montrent la terminaison |

|      | harmonique 2. Les diamants rouges et verts présentent les deux trajectoires d'impédance.158                                                                                                                                                                                       |

| 22   | En (a) le rendement, en (b) et (c) les compressions AMAM et AMPM en fonction de                                                                                                                                                                                                   |

|      | la puissance de sortie, pour chaque impédance et chaque puissance de sortie. En                                                                                                                                                                                                   |

|      | rouge les courbes maximisant le rendement en back-off, en vert celles du compromis linéarité/rendement et en noir à l'impédance maximale. Les courbes pointillées montrent                                                                                                        |

|      | les performances extrapolées d'une modulation d'impédance                                                                                                                                                                                                                         |

| 23   | Les trois amplificateurs en classes J, B et J*                                                                                                                                                                                                                                    |

| 24   | Measures AM-AM (à gauche) et AM-PM (à droite) pour les LMBA J, B et J* de haut en                                                                                                                                                                                                 |

|      | bas, avec un signal modulé de 10MHz, 8.7 dB de PAPR                                                                                                                                                                                                                               |

| 25   | Layout du LMBA en technologie GaAs                                                                                                                                                                                                                                                |

| 26   | Gain (à gauche) et PAE (à droite) par rapport à la puissance de sortie du LMBA à 27 GHz (en bleu), 28 GHz (en rose) et 29 GHz (en rouge)                                                                                                                                          |

| 27   | En rouge le gain et en bleu la PAE du LMBA CMOS                                                                                                                                                                                                                                   |

| 28   | En rouge la puissance maximale et en bleu la PAE en fonction de la phase du coefficient de réflexion pour VSWR de 3:1                                                                                                                                                             |

| 29   | En rouge et bleu les impédances vue par chaque ampli-ficateur de branche et en pointillés                                                                                                                                                                                         |

|      | noirs l'impédance présentée à la sortie. A gauche à la puissance back-off, quand l'amplificateur de contrôle est éteint, et à droite à puissance maximale                                                                                                                         |

| 30   | Schéma de principe du Double Balanced LMBA                                                                                                                                                                                                                                        |

| 31   | Performances du Double Balanced LMBA. En rouge le gain et en bleu la PAE 166                                                                                                                                                                                                      |

| 32   | Le rendement du LMBA classique (en bleu) et du Double Balanced LMBA en rouge, à puissance back-off avec les marqueurs X et à puissance maximale avec les marqueurs                                                                                                                |

|      | ronds                                                                                                                                                                                                                                                                             |

| 33   | En rouge et bleu les impédances vue par chaque amplificateur de branche et en pointillés noirs l'impédance présentée à la sortie. A gauche à la puissance back-off, quand l'amplificateur                                                                                         |

|      | de contrôle est éteint, et à droite à puissance maximale                                                                                                                                                                                                                          |

| 34   | Layout du Double Balanced LMBA. On voit sur cette figure le substrat en technologie BT, qui contient les réseaux d'adaptation au drain des transistors et le coupleur de sortie 167                                                                                               |

| 1    | Layout of the GaAS K Band Balanced Amplifier                                                                                                                                                                                                                                      |

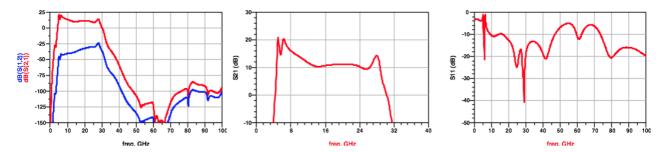

| 2    | S Parameters extraced from the electromagnetic simulation of the K band 30 dBm Bal-                                                                                                                                                                                               |

| •    | anced Amplifier MMIC                                                                                                                                                                                                                                                              |

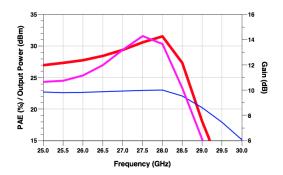

| 3    | Electromagnetic simulation results of the K band 30 dBm Balanced Amplifier MMIC. The blue, red and pink curves correspond to the peak output power, PAE and Gain respectively.170                                                                                                 |

| 4    | Layout of the GaAS K Band Single-ended Amplifier                                                                                                                                                                                                                                  |

| 5 | S Parameters extracted from the electromagnetic simulation of the K band 30 dBm single- |     |

|---|-----------------------------------------------------------------------------------------|-----|

|   | ended amplifier MMIC                                                                    | 171 |

| 6 | Electromagnetic simulation results of the K band 30 dBm single-ended amplifier MMIC.    |     |

|   | The blue, red and pink curves correspond to the peak output power, PAE and Gain re-     |     |

|   | spectively                                                                              | 171 |

|   |                                                                                         |     |

# **List of Tables**

| 1.1      | Comparison of the different generations of wireless cellular communication standards                                                                                                                                                                                       | 18  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|