# Coupling and dynamics of quantum dots in silicon MOS nanowires studied with gate-coupled radio frequency reflectometry

Anthony Amisse

### ▶ To cite this version:

Anthony Amisse. Coupling and dynamics of quantum dots in silicon MOS nanowires studied with gate-coupled radio frequency reflectometry. Quantum Physics [quant-ph]. Université Grenoble Alpes [2020-..], 2020. English. NNT: 2020GRALY057. tel-03241250

# HAL Id: tel-03241250 https://theses.hal.science/tel-03241250v1

Submitted on 28 May 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Physique de la Matière Condensée et du Rayonnement

Arrêté ministériel : 25 mai 2016

Présentée par

## **Anthony AMISSE**

Thèse dirigée par **Xavier JEHL**, Université Grenoble Alpes et codirigée par **Louis HUTIN**, CEA Leti

préparée au sein du Laboratoire PHotonique, ELectronique et Ingéniérie QuantiqueS dans l'École Doctorale Physique

Couplage et dynamique de boîtes quantiques en technologie MOS silicium étudiés par réflectométrie radio-fréquence sur grille

Coupling and dynamics of quantum dots in silicon MOS nanowires studied with gate-coupled radio frequency reflectometry

Thèse soutenue publiquement le **10 décembre 2020**, devant le jury composé de :

#### **Monsieur GEORGIOS KATSAROS**

PROFESSEUR ASSISTANT, INSTITUT SCIENCE TECHNOLOGIE - AUTRICHE, Rapporteur

#### Monsieur FRANCIS CALMON

PROFESSEUR, INSA LYON, Rapporteur

### **Monsieur LAURENT SAMINADAYAR**

PROFESSEUR DES UNIVERSITES, UNIVERSITE GRENOBLE ALPES, Président

#### **Madame MARYLINE BAWEDIN**

MAITRE DE CONFERENCES HDR, GRENOBLE INP, Examinatrice

## Acknowledgements

Finalement, les remerciements ! Bon, ce n'était pas une partie de plaisir comme disait le philosophe. 4 ans et demi après avoir commencé cette thèse, il est temps de rendre à César ce qui est à César, de remercier chaleureusement toutes les personnes qui ont cru en moi et qui ont tout fait pour assurer la réussite de cette aventure.

First and foremost, I would like to warmly thank Georgios Katsaros, Francis Calmon, Maryline Bawedin and Laurent Saminadayar for accepting to be part of the jury, despite the sanitary conditions. Special thanks to my two reviewiers, Georgios Katsaros and Francis Calmon, for their commentaries about the manuscript. I want to tell that it was a real pleasure to present some of my work to the four of you. The asked questions led to interesting discussions.

Il est temps de remercier les deux personnes les plus importantes de ce projet, mes deux directeurs de thèse, Xavier et Louis.

Xavier, quoi dire à part que je n'aurais pas pu espérer meilleur encadrant au quotidien. Ce n'était pas facile tous les jours, loin s'en faut, mais tu as su garder patience, continuer à me motiver. Ton expertise en cryogénie et en électronique, entre autres, fut une aide précieuse pour mener à bien ce projet. Même après trois ans de travail avec toi, je reste impressionné du niveau de connaissances que tu as dans ces domaines en particulier. Merci encore pour tout ce que tu as fait.

Louis, le parfait co-encadrant. On ne se voyait pas aussi souvent qu'avec Xavier mais à chaque fois que l'on se voyait, c'était rafraichissant. Parler dispos, process, composés chimiques, stratégie d'amélioration des dispos, tout en faisant des jeux de mots un peu partout, un peu tout le temps, c'était super agréable. Et quelle expertise également! J'avais l'impression que les MOSFET n'avaient pas de secrets pour toi. Quand on n'est pas de la microélectronique, ce domaine est assez déroutant. Tu incarnais à la perfection le pont entre la recherche fondamentale et l'industrie de la microélectronique. Merci à toi pour ta pédagogie, ta patience, ton humour.

A vous deux, je vous souhaite le meilleur pour la suite.

J'aimerais à présent rendre un hommage. Marc Sanquer, spécialiste de la physique mésoscopique, pilier de l'INAC et de la recherche sur les MOSFET à très basse température, s'en est allé le 15 février 2021. La soutenance de cette thèse est la dernière à laquelle il a assisté.

Lors de ma première année, Marc a été mon encadrant principal effectif, mon collègue de manip, un réel mentor. Les résultats présentés dans le chapitre 4 sont issus des dernières manip de Marc, ou presque. Il avait cette faculté à s'émerveiller de tout, y compris des choses semblant les plus simples. Je me suis fait la main sur *Diluette*, son cryostat wet. Il m'a initié à la physique des quantum dots comme personne n'aurait pu le faire.

Au delà de ses qualités de physicien, Marc était quelqu'un de très sympathique, aimé de ses collègues et de la communauté. Il méritait amplement la tranquillité attendue de la retraite. Puisse-t-il à présent reposer en paix. Merci pour ta contribution à la Science, merci pour ta contribution humaine au labo. J'ai une pensée pour tes proches. On ne t'oubliera jamais.

Place maintenant aux permanents du labo. Malgré l'état des locaux, il faisait bon vivre au C1, entre les équipes LaTEQS et IMAPEC. C'est en majeure partie dû à la bonne ambiance au sein des groupes. J'aimerais donc remercier François L., Vincent R., Claude C., Max H., Silvano D.F., Louis H., Christophe M., Etienne D. En particulier, je garde d'excellents souvenirs de ces GdRs à Aussois, des sorties skis, et d'un peu moins bons concernant les raclettes du labo. Mais bon, quelle idée aussi de ne pas aimer le fromage! De plus, je tiens à vivement remercier François pour les discussions importantes lors de la fin doctorat. Merci enfin Etienne pour le template de ma présentation! Je voudrais également remercier les membres de mon comité de suivi de thèse, Manuel H., Hermann S. et Jérôme P. Une pensée toute émue pour Jérôme qui nous a également quitté lors de ma thèse.

Je ne veux surtout pas oublier les techniciens permanents. Je tiens à remercier Fredéric G. & Fredéric P., Pierre P.B., Jean-Luc T. et Iulian M. En particulier j'adresse un grand merci à Iulian pour son aide ainsi que sa pédagogie concernant les cryostats. J'espère que tu es satisfait de ton protégé, que *Tritonito* tournes comme une horloge!

Entre les permanents (les trois-quarts) et les doctorants (les avants) il y a les post-docs (la charnière)<sup>1</sup>. Au début de ma thèse, ils étaient deux : Alessandro C. et Romain M. Depuis, Alessandro et parti et Romain est devenu permanent. Je veux vous adresser de sincères remerciements. Vous m'avez permis de m'initier à la physique des quantum dots, des MOSFET à basse température et, plus important encore, à la réflectométrie. Au delà des considérations de physique, merci Romain pour ton optimisme, ta bonne humeur et ton

<sup>&</sup>lt;sup>1</sup>J'ai pas pu m'en empêcher, c'est le 6 nations

soutien du début de cette thèse à la fin.

Deux autres post-docs ont fait leur apparition dans le labo au cours de ma thèse. Florian V. et Simon Z. Je remercie le premier pour sa bonne humeur infaillible et le second pour son efficacité redoutable !

Venons-en maintenant aux thésards, aux collègues, aux amis. J'ai commencé ma thèse par m'installer dans le bureau de Salha et Anaïs. C'était le bon vieux temps de l'innocence de la première année. Merci à vous deux pour l'accueil que vous m'avez réservé. Je repense encore aux nombreuses façons d'offusquer sans méchanceté Salha, sans faire exprès des fois ! Comme je repense à nos débats pré-présidentiels de 2017 avec toi Anaïs (*rend l'argent !!*) ! Je vous souhaite le meilleur pour vous deux. A l'époque, Loic H. était encore présent. C'était très chouette de te rencontrer, de m'avoir initié à Dominion, entre autres ! J'ai repensé il y a pas longtemps à la mission de monter le canapé par le balcon chez vous, quelle histoire ! Je vous souhaite également le meilleur pour toi et Caroline.

En 2016, nous étions trois nouveaux thésards au sein du groupe. Estelle M. *Mozarella* et Romain A. *Râle-bert* complétait notre trio. Cela faisait quelques mois que Florian B. *the python master*, avait également commencé sa thèse. Nous avons été rejoint par Thomas J. *un dénommé José*, au cours de l'année 2017. Je pense ne pas me tromper si je vous dis que vous avez été sûrement les personnes les plus importantes au sein du labo. Je n'aurais jamais été au bout sans vous. Pour tout ce que nous avons partagé ensemble, de l'escalade à la bière, des jeux à la musique, des nuits en altitude aux journées ski, des GdRs aux K'Fée des jeux, de la virée en Angleterre à celle d'Helsinki, merci, merci pour tout. J'espère vous revoir un de ces quatre! Et d'ici là, soyez heureux et portez-vous bien!

Je veux aussi remercier et encourager les derniers arrivants du groupe : Tom V., Rami E., Loïc L.G., Cécile Y., Agostino A., Florie M., Nicolas P., Estelle V., Gonzalo T., Chotivut T. En particulier, je veux remercier Tom qui me fait (entre autres choses) mourir de rire et Rami sans qui j'aurais mis beaucoup BEAUCOUP plus de temps à coder pour ma manip. Je vous souhaite à tous, y compris les nouveaux , de tenir le rythme et de prendre plaisir à ce que vous faîtes. Puisse le futur vous être favorable.

J'ai également une pensée chaleureuse pour les membres du groupe théorie et tous les thésards que j'ai rencontré lors des GdRs, ils se reconnaîtront (nom de code TipTop).

Comment parler de ces années Grenobloises sans parler des personnes que je voyais à côté du travail ? Je vous l'demande !

Je veux commencer par remercier Hugo D. et Jeannette R., Florian C., Jessy P. et Kilian M.

On se sera bien marré pendant ces années et sans vous tout aurait été plus compliqué depuis le début. Vous allez me manquer les gars, j'espère qu'on se reverra bientôt! Bonne chance pour ta nouvelle petite famille le Hug, et profite de tout ce bonheur! Je vous souhaite à tous les 5 de la réussite, que ce soit perso ou pro!

Je veux ensuite remercier Quentin F. et Palmerina G., Victor D., Alexis W. et Sophie C., le grand Nils, Paul et Marc M. Par où on commence ? Les blind tests au Metro ? Les tournois de coinche au Sub ? Les soirées billards au D'Enfer ? Les nuits drak' (ça manque tellement) ? Les soirées flims et séries ? Les fondues camembert ? C'était dingue, heureusement que vous étiez là au quotidien.

Je pense également à des amis de longues dates : Anthony L., tiens le coup mon pote la soutenance est en vue, Alexis T., Adrien G., Tobye X., Irina. On se reverra bien quelque part dans l'hexagone un de ces quatre !

Cette rédaction de thèse s'achève en plein contexte de pandémie du SARS-CoV 2. Drôle de façon de terminer son manuscrit que de vivre confiné du côté de sa ville natale. Mais indispensable. Je remercie donc infiniment tous mes potes de Brière (c'est mort je vous cite pas tous, c'est déjà bien assez long!) d'avoir été là dans la dernière ligne droite, en particulier Bastien G. (bon, 1 quand même), cette petite coloc de deux mois lors du premier confinement était idéale!

Je veux enfin remercier mes parents, mon frère et mon oncle d'avoir été un soutien sans faille durant ces longues années d'études. Merci de m'avoir laissé le choix. Merci d'avoir cru en moi.

Pour complètement terminer, je trouve que l'on ne remercie pas assez les professeurs, sûrement influents dans la vie d'un étudiant en doctorat, dans cette section. Alors j'ai une pensée sincère pour Mme Petit, Mme Villant, Mr Loncke, Mme Lefebvre, Mr Fournaise, Mr De Préville ainsi que la quasi-totalité de mes professeurs d'université et mes maîtres de stage. Je suis très fier d'avoir été l'un de vos élèves ou étudiants. Vous m'avez inspiré. Et vous continuerez.

## **Abstract**

### **Abstract**

We are measuring at low temperature silicon MOS nanowires transistors where quantum dots are created. We also built a radio frequency reflectometry setup allowing one to probe the charge and the spin states of a charge carrier trapped inside a quantum dot. One such apparatus could be used mainly for two things: electron pumps for the quantum metrology, the definition of the ampere and for spin quantum bits, called qubits.

In this PhD we focused on two important problematics of the qubits: the control of the coupling between quantum dots and state readout. More precisely we showed that i) the coupling between two quantum dots can be strongly influenced by the state of a third quantum dot placed in between and ii) the setup required for the energy selective spin readout, a new spin-to-charge conversion mechanism in our specific MOSFET based qubits community, works perfectly without magnetic field.

This work has been done in close collaboration with CEA-LETI for the design and the fabrication of the devices with their 300 mm CMOS SOI facilities.

## Résumé

Nous mesurons à très basse température des transistors nanofils silicium en technologie MOS dans lesquels des boîtes quantiques se forment. Nous avons aussi construit un dispositif de réfléctométrie radio-fréquence qui permet de sonder l'état de charge et de spin d'un porteur de charge piégé dans une de ces boîtes. Une telle expérience peut servir principalement pour deux choses : les pompes à électrons pour la métrologie quantique de l'ampère et les bits quantiques, ou qubits, de spin.

Dans le cadre de cette thèse, nous nous sommes concentrés sur les problématiques liées aux qubits de spin. Plus précisément, nous nous sommes penchés sur deux points essentiels du fonctionnement d'un tel qubit : le contrôle du couplage entre les boîtes quantiques, principalement via une troisième boîte et la lecture du spin par sélectivité en énergie, un mécanisme de conversion spin-charge relativement nouveau dans notre communauté de qubits à base de MOSFET.

Ce travail a été mené en étroite collaboration avec le CEA-LETI, pour le design et la fabrication des échantillons sur leur plate-forme SOI (Silicon-On-Insulator) CMOS 300mm.

# **Contents**

| 1 | Intr                                      | oductio                         | on                                                                   | 1  |  |

|---|-------------------------------------------|---------------------------------|----------------------------------------------------------------------|----|--|

|   | 1.1                                       | The pr                          | rospect of a quantum computer                                        | 1  |  |

|   | 1.2                                       | What                            | is a good qubit ?                                                    | 3  |  |

|   | 1.3                                       | Outlin                          | e of this thesis: scalability as a common thread                     | 5  |  |

| 2 | Basi                                      | ics of qu                       | uantum transport through quantum dots                                | 13 |  |

|   | 2.1                                       | 1 The single quantum dot system |                                                                      |    |  |

|   |                                           | 2.1.1                           | The many carriers regime                                             | 15 |  |

|   |                                           | 2.1.2                           | The few carriers regime: access to quantum states                    | 21 |  |

|   | 2.2                                       | The do                          | ouble quantum dot system                                             | 25 |  |

|   |                                           | 2.2.1                           | The many carriers regime and the stability diagram                   | 25 |  |

|   |                                           | 2.2.2                           | The few carriers regime and energy selective spin readout            | 36 |  |

|   |                                           | 2.2.3                           | Coupled quantum dots via a quantum mediator                          | 42 |  |

|   | 2.3                                       | The measurements techniques     |                                                                      |    |  |

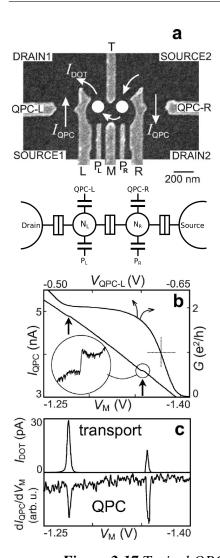

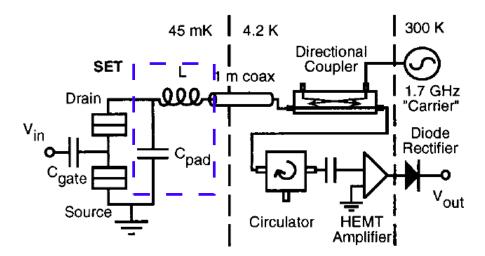

|   |                                           | 2.3.1                           | From charge detectors to radiofrequency (RF) reflectometry           | 46 |  |

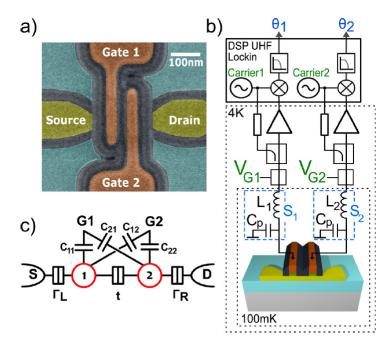

|   |                                           | 2.3.2                           | The gate-coupled RF reflectometry                                    | 49 |  |

| 3 | Device fabrication and electronic setup 5 |                                 |                                                                      |    |  |

|   | 3.1                                       | A brie                          | f history of the transistor                                          | 56 |  |

|   | 3.2                                       | From                            | transistors to qubits                                                | 57 |  |

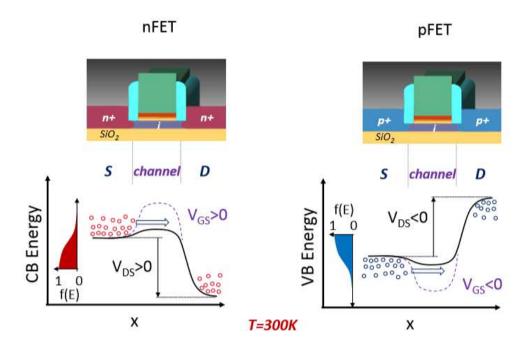

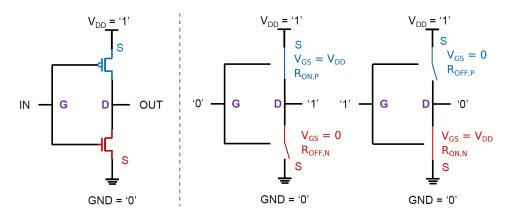

|   |                                           | 3.2.1                           | The transistor: a crucial tool for digital logic                     | 58 |  |

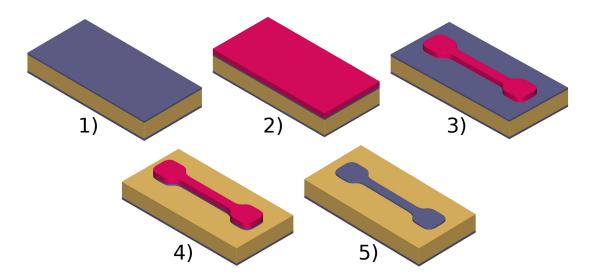

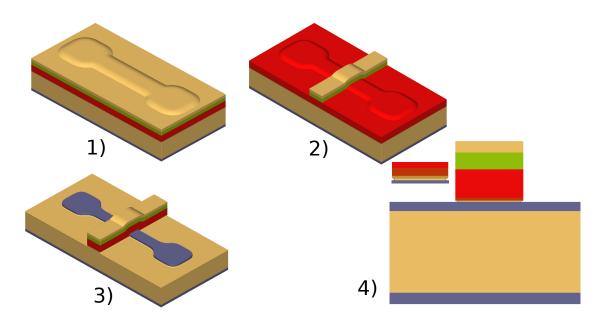

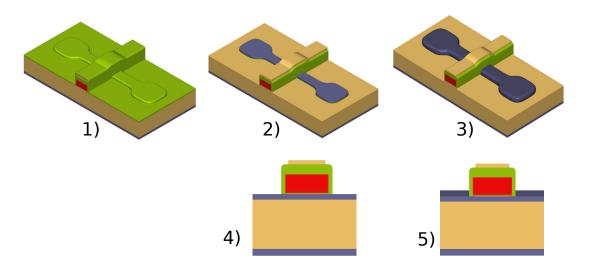

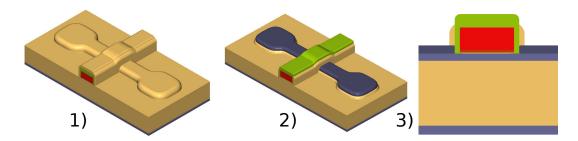

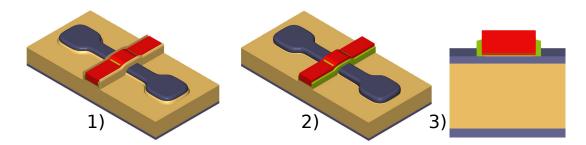

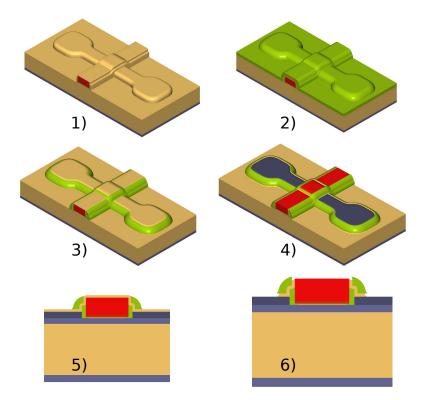

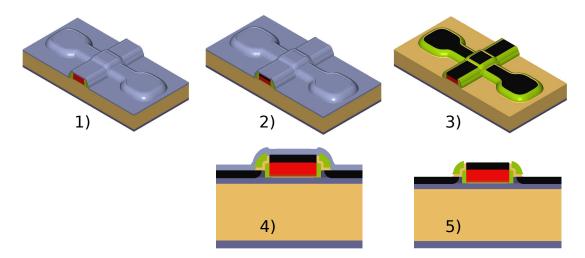

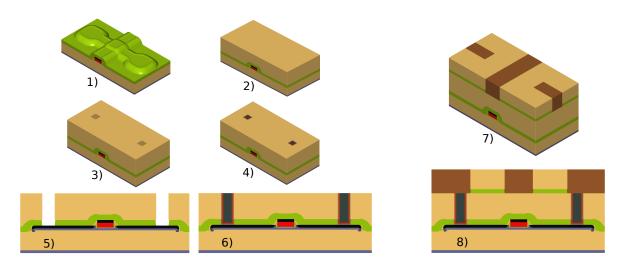

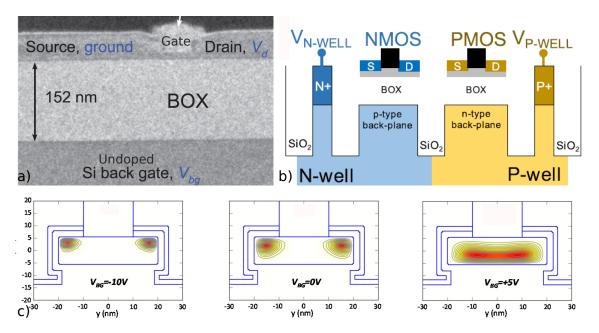

|   |                                           | 3.2.2                           | LETI's standard process flows and custom steps                       | 61 |  |

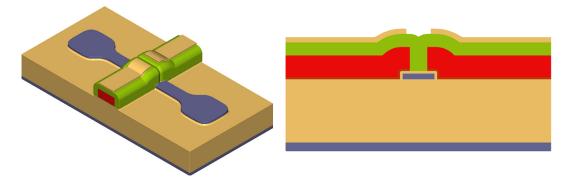

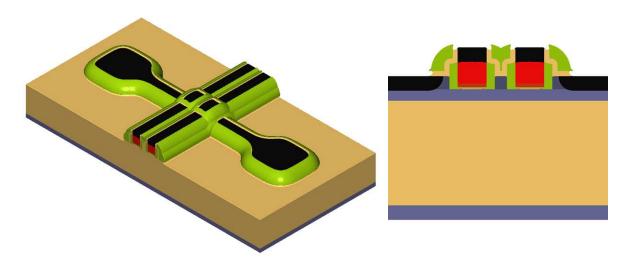

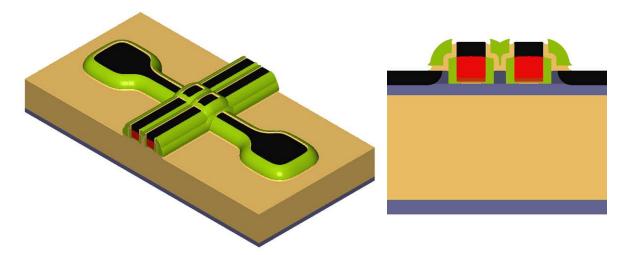

|   |                                           | 3.2.3                           | Presentation of the studied devices                                  | 71 |  |

|   | 3.3                                       | Electro                         | onic Setup                                                           | 75 |  |

|   |                                           | 3.3.1                           | Electronics for the radiofrequency reflectometry and the pulse lines | 75 |  |

| 4 | Tun                                       | ability (                       | of the couplings                                                     | 85 |  |

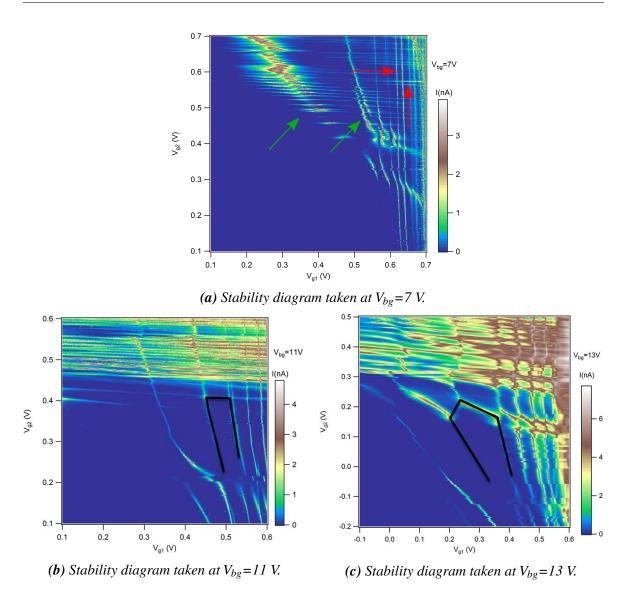

|   | 4.1                                       | The ba                          | ackgate approach                                                     | 86 |  |

**xii** Contents

|    |              | 4.1.1                                      | A natural degree of freedom in SOI devices                    | 86  |  |  |

|----|--------------|--------------------------------------------|---------------------------------------------------------------|-----|--|--|

|    |              | 4.1.2                                      | Some examples of backgate polarization                        | 88  |  |  |

|    |              | 4.1.3                                      | Advantages and disadvantages                                  | 90  |  |  |

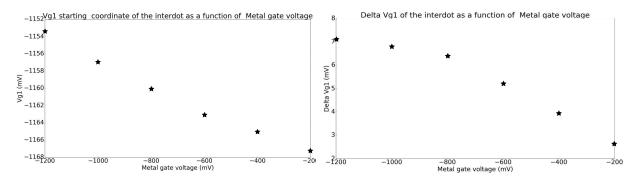

|    | 4.2          | The m                                      | etal line approach                                            | 90  |  |  |

|    |              | 4.2.1                                      | A new tool from the recent batches                            | 90  |  |  |

|    |              | 4.2.2                                      | Comparison with the backgate                                  | 91  |  |  |

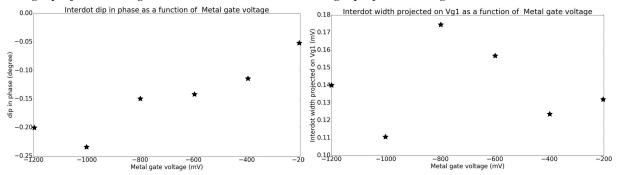

|    |              | 4.2.3                                      | Results                                                       | 91  |  |  |

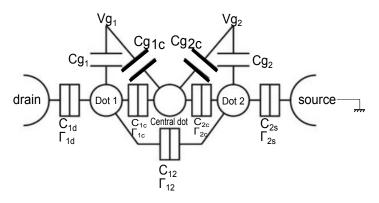

|    | 4.3          | The us                                     | se of a quantum mediator                                      |     |  |  |

|    |              | 4.3.1                                      | Interest in such systems                                      | 95  |  |  |

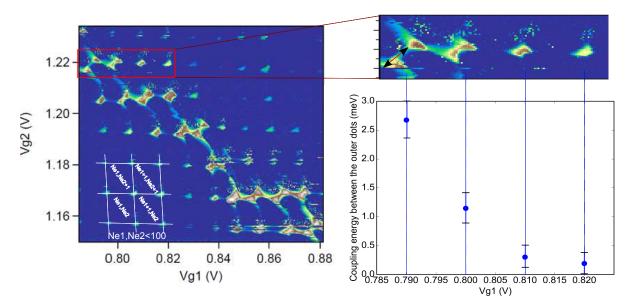

|    |              | 4.3.2                                      | Experimental realization and results                          | 95  |  |  |

|    | 4.4          | Conclu                                     | asion and outlook                                             | 103 |  |  |

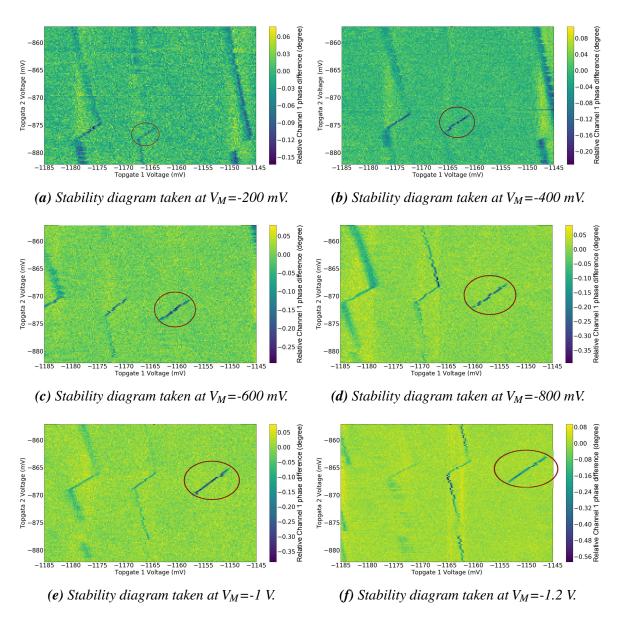

| 5  | Dyn          | amical                                     | experiments towards energy selective spin readout             | 107 |  |  |

|    | 5.1          | Motiva                                     | ntion                                                         | 108 |  |  |

|    | 5.2          | Practical requirements for such experiment |                                                               |     |  |  |

|    | 5.3          | Prelim                                     | inary results                                                 | 111 |  |  |

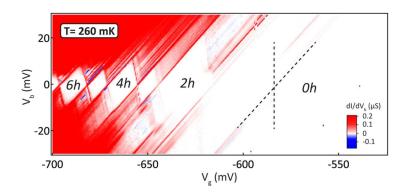

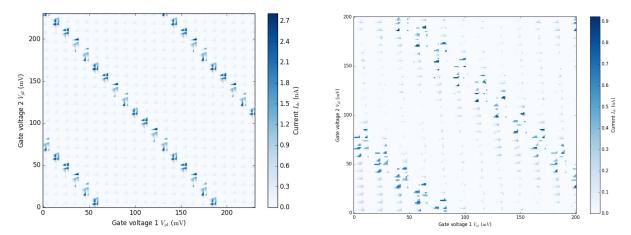

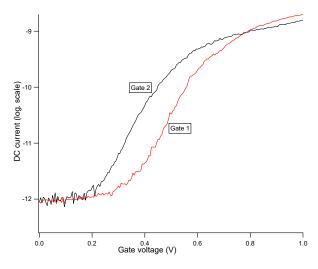

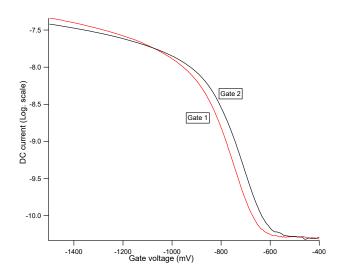

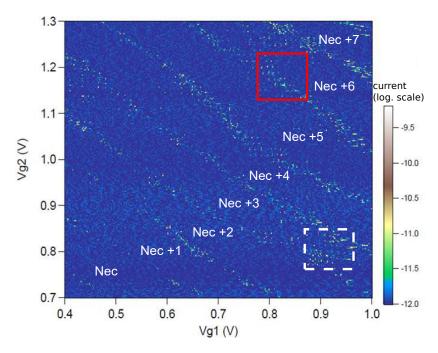

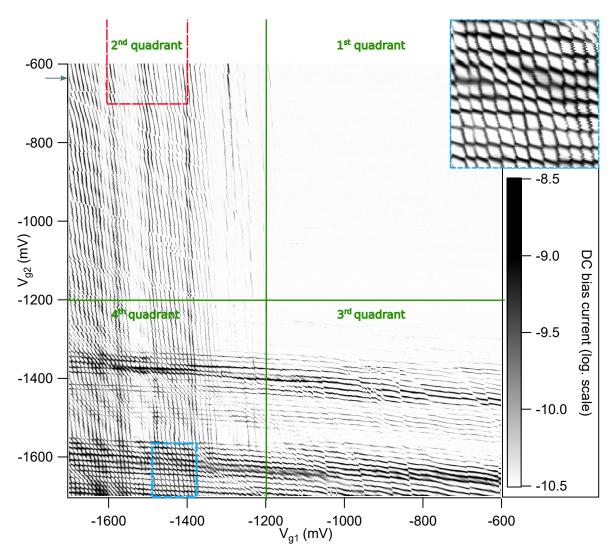

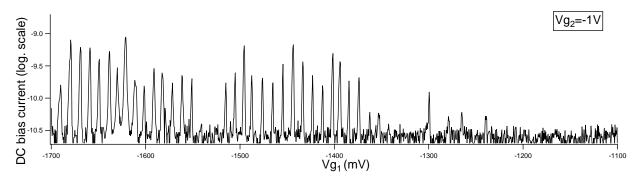

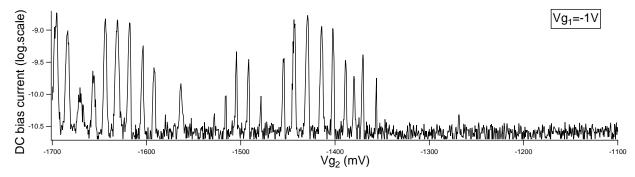

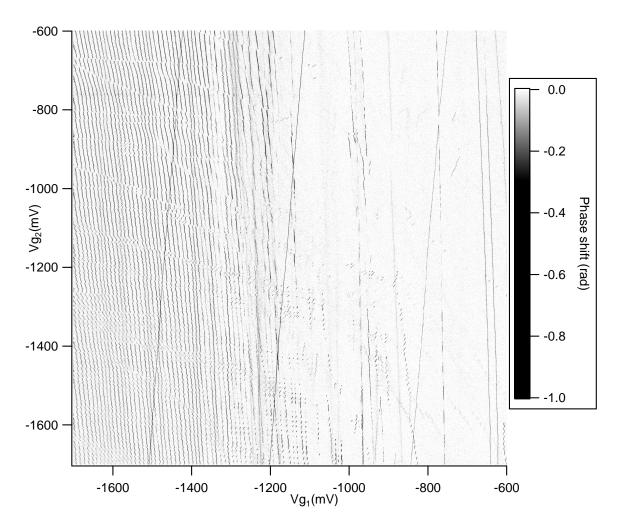

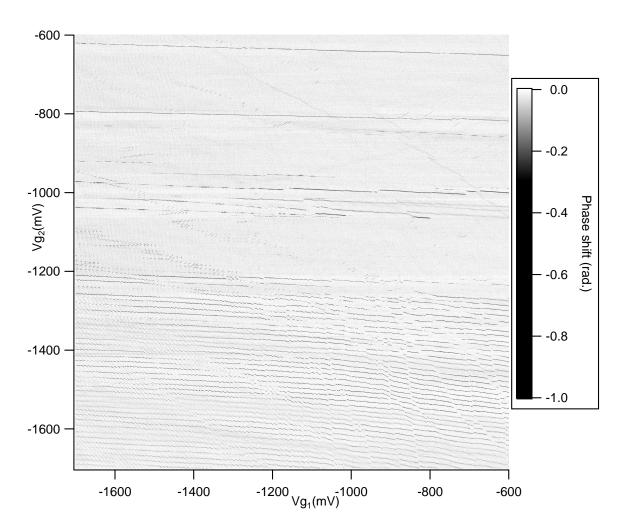

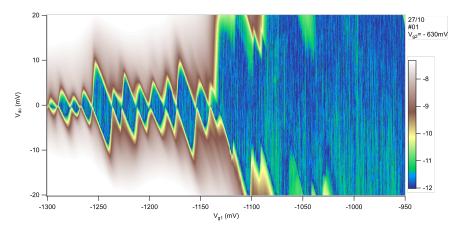

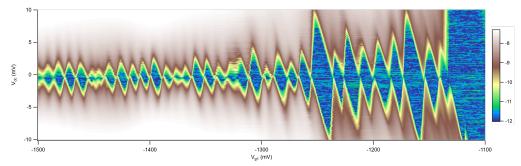

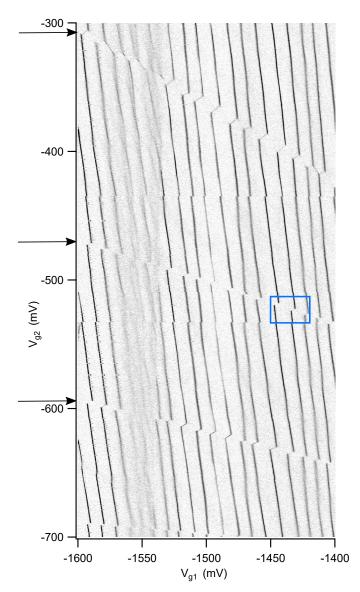

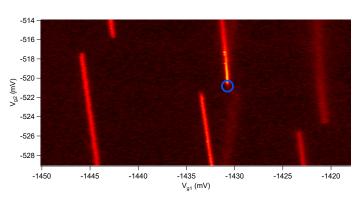

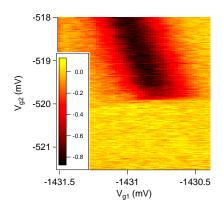

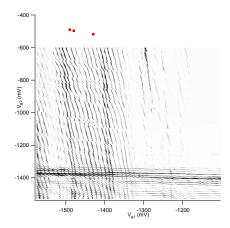

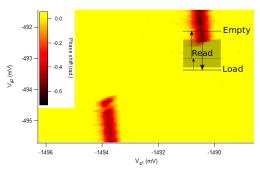

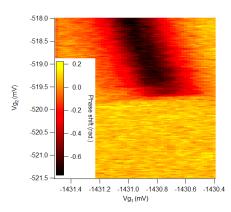

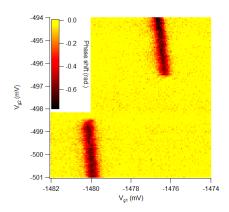

|    |              | 5.3.1                                      | Stability diagrams                                            | 112 |  |  |

|    |              | 5.3.2                                      | Coulomb diamonds                                              | 118 |  |  |

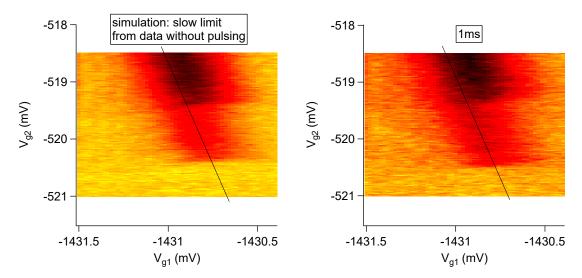

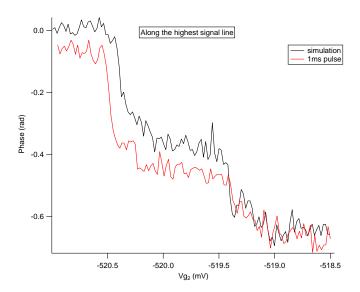

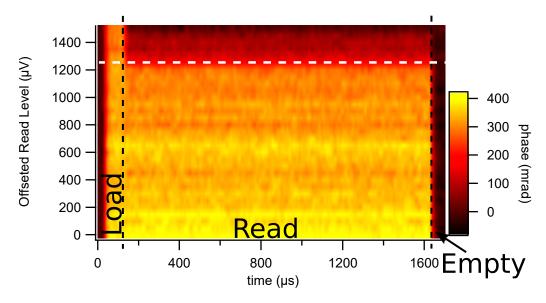

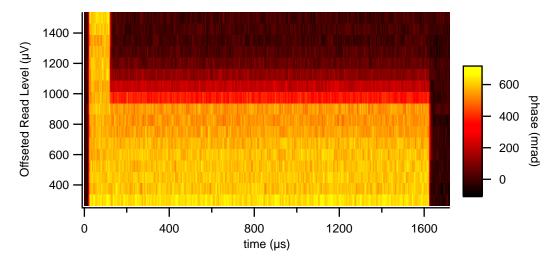

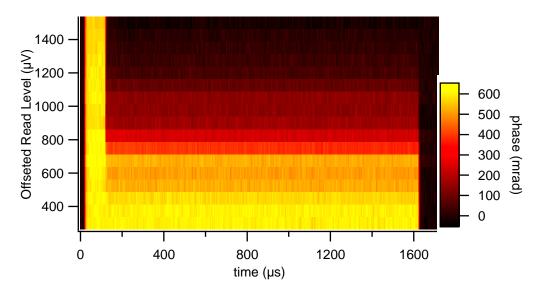

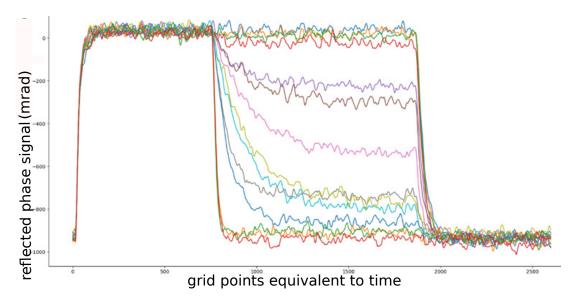

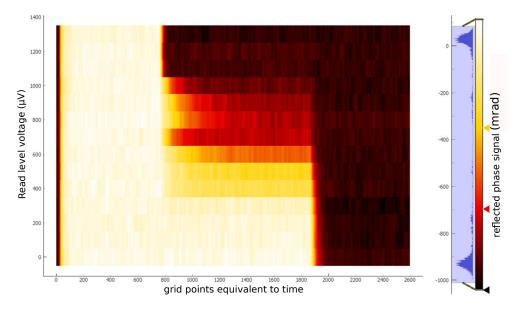

|    |              | 5.3.3                                      | Continuous pulsing                                            | 120 |  |  |

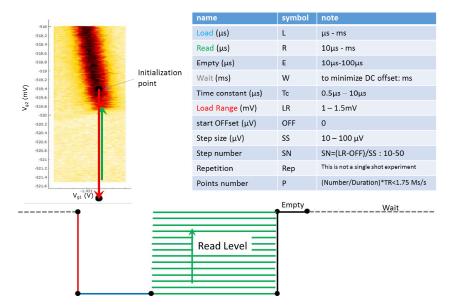

|    | 5.4          | The Load-Read-Empty-Wait (LREW) sequence   |                                                               |     |  |  |

|    |              | 5.4.1                                      | Principle                                                     | 130 |  |  |

|    |              | 5.4.2                                      | Preliminary calibrations of the pulses                        | 131 |  |  |

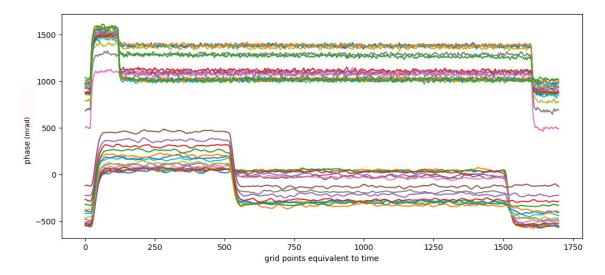

|    |              | 5.4.3                                      | Results                                                       | 133 |  |  |

| 6  | 6 Conclusion |                                            |                                                               |     |  |  |

| Bi | bliogi       | raphy                                      |                                                               | 153 |  |  |

| Ar | pend         | ix A P                                     | resentation of the Arbitrary Waveform Generator (AWG) and the | 2   |  |  |

| 1  | _            | isition                                    | •                                                             | 161 |  |  |

|    |              | A.0.1                                      | The Data Acquisition module of the UHF                        | 161 |  |  |

|    |              | A.0.2                                      | Setup the AWG module                                          | 164 |  |  |

|    |              | A.0.3                                      | AWG code for the Load-Read-Empty-Wait (LREW) sequence         | 168 |  |  |

# Chapter 1

# Introduction

"Back in the 1940s, researchers were just discovering how to use vacuum tubes as simple switches. These switches could then form logic gates, which could be linked together to form the first logic circuits. That's where we're at now with quantum processors. We have verified that all the components work. The next step is to engineer the smallest, yet most interesting circuit possible"

-Jungsang Kim, 2016

## 1.1 The prospect of a quantum computer

For 60 years and following the so-called Moore's law [1] about the evolution of the number of transistors per chip, electrical engineering has evolved exponentially both on the theoretical and on the technical aspects . The first Metal-Oxide-Semiconductor-Field-Effect-Transistor, called MOSFET was developed in the early 1960s within Bell labs by Kahng and Atalla [2]. Today, a processor can unbelievably host almost 20 Billions of MOSFET transistors<sup>1</sup>. Still, even with the biggest processors and supercalculators, some problems cannot be simulated by a classical computer.

Back in 1982 already, the famous R. Feynman wondered about this specific question: is it possible to exactly simulate quantum systems, like chemical bounds and chemical reactions, with a standard, classical computer? In this paper [3], collection of notes taken from a keynote speech, he is one of the first<sup>2</sup> to tell about a *universal quantum simulator*, the quantum computer. Altough the physical idea of a quantum computer was not clear yet, some

<sup>&</sup>lt;sup>1</sup>The introduction of chapter 3 gives a more detailed story of the transistor.

<sup>&</sup>lt;sup>2</sup>In 1980, the russian mathematician Yuri Manin also proposed the idea of a quantum computer in his book *Computable and Uncomputable*. In the early 1980s, the american Paul Benioff was one of the first to theoretically describe the quantum mechanical model of a computer.

2 Introduction

(mostly theoretical) researchers started creating new algorithms and protocols based on laws of quantum mechanics in different specific fields (for instance a new protocol, called BB84, in quantum cryptography [4] already in 1984 or the Shor's algorithm [5] built for solving the prime number factorization problem in a polynomial time, 1997). The idea of considering hardware devices designed to process quantum mechanically has become serious in the late 1990s.

The analog of the classical digital bits are the quantum bits, called qubits. While the digital bit has only two available states, 0 or 1, the qubit is a quantum mechanical system characterized by its wavefunction  $|\psi\rangle=c_0|0\rangle+c_1|1\rangle$ , a superpostion of the two eigenstates  $|0\rangle$  and  $|1\rangle$ . If one entangles N of such qubits, it represents  $2^N$  values simultaneously. By processing each of these values at the same time, a quantum computer operates exponentially faster than its classical counterpart.

In early 1998, D. Loss & D.P. DiVincenzo published a well-known proposal for a scalable semiconductor-based quantum computer made of quantum dots [6]. In this case, the qubit states are the two spin states of coupled single-electron quantum dots hosted in semiconductor materials. The computation is achieved by varying the coupling between the dots, acting as logical gates.

Later in the year, B. Kane published another proposal for a scalabe quantum computer made of donors in a silicon matrix [7]. In that case, the nuclear spin states of the donor are the qubits. Again, the computation is done by acting on conducting gates, varying the coupling between the donors.

Finally in 1998 J. Preskill published a theoretical paper [8] about fault tolerant quantum computation, the ability to overcome the leak of quantum information due to uncontrolled interactions of the qubits with the environment. This 1998 year could be considered as the beginning of the race towards scalable quantum computers.

Following these pionnering works, D.P. DiVincenzo published another paper in 2000 [9] about the physical implementation of quantum computation. From that paper have emerged the *DiVincenzo Criteria*, a list of five technical requirements in order for a quantum computer to be reliable, which are discussed in the next section.

As a consequence, researchers have looked into many different kinds of hosting materials for the qubits. The two aforementionned proposals involved semiconducting materials. For the last 20 years, GaAs heterostructures, silicon and silicon-germanium quantum dots have

been deeply studied. As an exemple, in 2016 R. Maurand et al from our group achieved the first qubit in a PMOS silicon device [10]. For more details about silicon and silicon germanium baseds qubits, see [11]. In 2020, only a few coupled qubits have been achieved in semiconducting materials. Very recently, a four qubit device has been demonstrated [12].

Semiconducting materials are only one possibility. In fact, a lot of different systems have been invented and designed such that trapped ions [13], superconducting qubit and photonic systems [14]. The three of them have been deeply investigated and many qubits arrays have been experimentally realized. I can also tell a word about neutral atoms [15], carbon nanotubes [16], NV center in diamonds [17] which have only achieved a single or a coupled of connected qubits and, lastly, topological systems [18], being only developed at the theoretical level. As of now, the most advanced candidates for quantum computation are the superconducting qubits and the phtonic qubit. In 2019, 53 working connected superconducting qubits on a chip have been achieved mainly from Google AI Quantum lab [19]. In near future, they plan to work with a 72-qubits chip<sup>3</sup>. A recent review covering the state of the art of superconducting qubits from a quantum engineer perspective is presented in [20]. In 2020, 50 connected photonic qubits have been realized by a chinese group [21]. Being able to work with such a number of connected qubits paves the way for pionner experimentations involving the quantum algorithms.

It is clear that, for the moment, superconducting qubits are ahead in the race towards a solid-state quantum computer. However it is still hard to imagine a superconducting chip hosting thousands of functional qubits. The surface of the chip and the scalability of individual qubit control are strong experimental challenges<sup>4</sup>. In the next section I will briefly present what should be a good qubit and how MOSFET-based qubits are still viable candidates for large scale quantum computation.

# 1.2 What is a good qubit?

As presented in the last section, the 1998-to-2000 era established the main technical necessities in order for a quantum computer to be reliable in the synthetic form of the five *DiVincenzo Criteria*:

<sup>&</sup>lt;sup>3</sup>https://ai.googleblog.com/2018/03/a-preview-of-bristlecone-googles-new.html

<sup>&</sup>lt;sup>4</sup>However, physicists are exploring a wide range of possible feasibility, for instance: https://singularityhub.com/2020/06/22/a-new-startup-intends-to-build-the-worlds-first-large-scale-quantum-computer/.

4 Introduction

• Scalability with well-characterized qubits. Practically, it is possible to build a system with one well characterized qubit. However it is very challenging to build a system with an arbitrary number of qubits. Currently, one of the biggest issue being faced is that one requires exponentially larger experimental setups to accommodate a greater number of qubits.

- Initialising qubits to a simple, standard state. Quantum computation is based on performing operations on states maintained by qubits and reporting the result. This procedure is strongly dependent on the initial state. In many cases, initialisation is accomplished by letting the system relaxing to the ground state. Alternate approaches, like optical pumping [22] also exist.

- Long relevant coherence times. Coherence characterizes (superposed) quantum states which carry a well defined phase. Loosing coherence is called decoherence. Decoherence is an intrisic issue experienced in large, macroscopic, quantum systems. Moreover, the more the quantum system is coupled to its environment, the more it experiences decoherence.

- A "universal" set of quantum gates. In computer science, the algorithms that we can compute are restricted by the number of gates we can implement. It has been shown that a universal quantum computer can be constructed using a very small set of 1-and 2-qubit gates. Any experimental setup that manages to have well-characterised qubits, quick, faithful initialisation, and long decoherence times must also be capable of influencing the Hamiltonian (total energy) of the system, in order to bring coherent changes capable of implementing a universal set of gates.

- In practice, the most important figure of merit is the ratio between the coherence time (previous item) and the average gate time, giving the numbers of gate operations one can perform before loosing coherence, and, thus, quantum information. In the mean time, it is desired to have a system that can be manipulated quickly so that one can interact with it as quick as possible. All together, one needs to find a trade-off between ability to implement control and decoherence.

- A qubit specific measurement capability. For any process modifying the quantum states of qubits, the final measurement of those states is of fundamental importance when performing computations. The measurement capabilities are heavily studied in the community (for instance, radiofrequency refletometry in our group).

In the framework of this thesis, the first criterion concerning scalability is of prime interest. As opposed to single-fabricated device, with a low throughput, still studied in the superconducting and semiconducting community, our group focuses on quantum dots in MOSFET silicon nanowires produced at industrial scale on 300 mm silicon wafers. Thus, all the devices studied in this manuscript come from the LETI institute, located in CEA Grenoble. The motivation has always been to study quantum effects such that charge quantization, coherence, state manipulation, readout and so on in MOSFET-derived test devices. The long term prospect is to derive and design arrays of quantum dots based on what we are learning on MOSFET-based quantum dots. This point is one main goal of the 20 years of collaboration between our laboratory and LETI.

## 1.3 Outline of this thesis: scalability as a common thread

Chapter 2 gives a theoretical basis on quantum transport through quantum dots. I will present the constant interaction model for the single and double quantum dots system, insisting on the double dot stability diagram, a crucial experimental tool. I will also discuss about the measurement techniques which have evolved throughout the story of quantum dots studies and, in particular, the gate radiofrequency reflectometry. This rather new and promising probing technique could be one of the answers to the first DiVincenzo criterion thanks to its sensitivity and potential scalability.

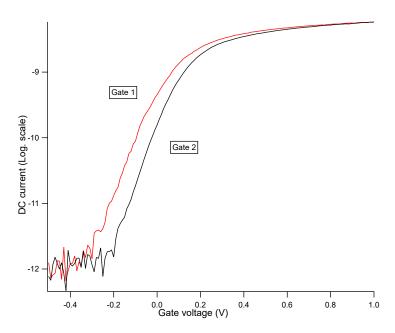

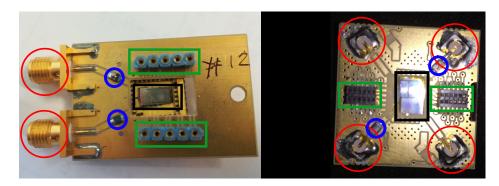

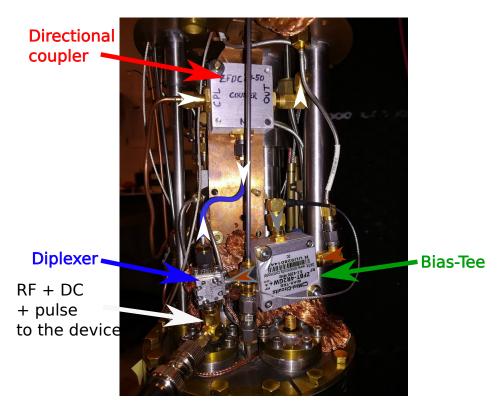

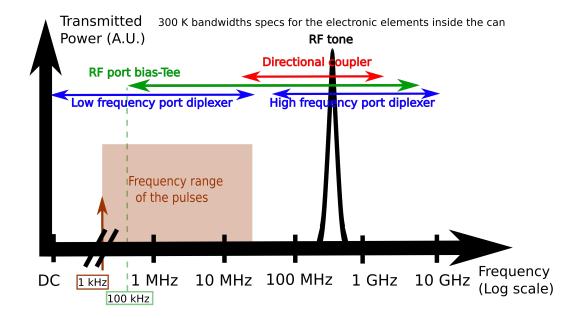

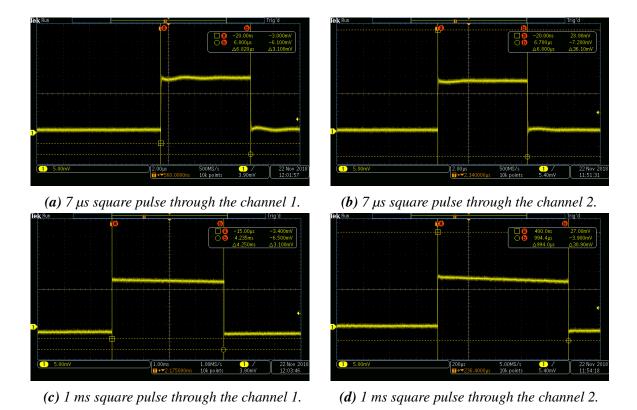

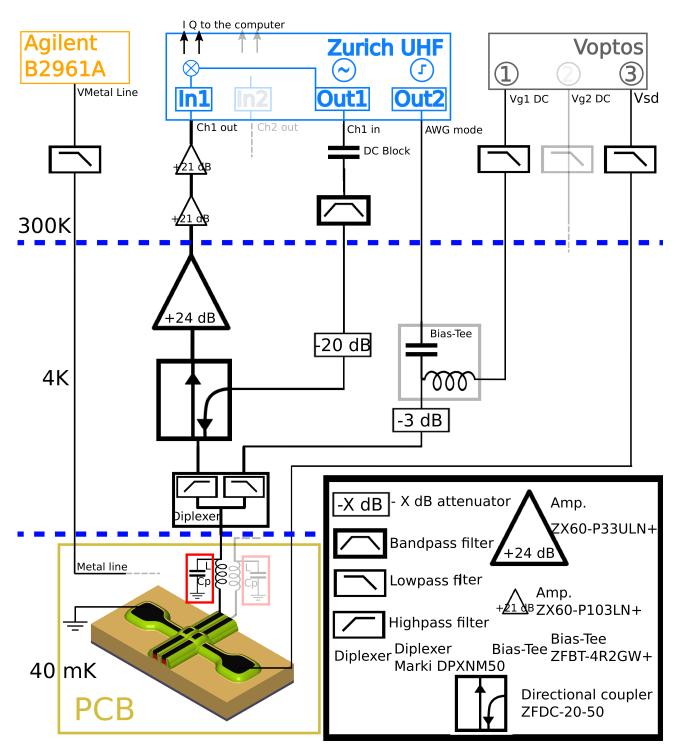

Chapter 3 deals moslty with device fabrication. After a brief story of the MOSFET and why it has great advantages as building blocks of classical computer science, I present the guideline of the industrial process developed at CEA LETI to create the MOSFET silicon nanowires. I also point out the specific needed variations from the routine process to our custom process in order for the devices to be as optimal as it is allowed by our knowledge. A presentation of each studied device is given. The reader shall be informed that i) I worked on two different double quantum dots geometries, namely the serial and parallel configurations and ii) I worked on the two possible dopings of the nanowires, namely N-doped devices with electrons as charge carriers and P-doped devices with holes as charge carriers. I complete the chapter with the presentation of the homemade cryogenic, dual channel reflectometry setup to study quantum transport in quantum dot systems. The particularity of the setup is that it also allows one to send pulses<sup>5</sup> through two channels onto the device, a feature which is necessary for the experiments that I will present in Chapter 5.

<sup>&</sup>lt;sup>5</sup>between hundreds of nanoseconds to a few millisecond.

6 Introduction

Chapter 4 is dedicated to the coupling between two quantum dots. As it is presentd in the Kane and DiVincenzo's proposals, one needs to carefully control the coupling between two quantum dots. Three different degrees of freedom are compared: the backgate approach being the historical approach; the metal line approach which is a new degree of freedom and the quantum mediator approach where a quantum object is placed in between two dots. The state of the inner dot will strongly influence the coupling between the two outer dots.

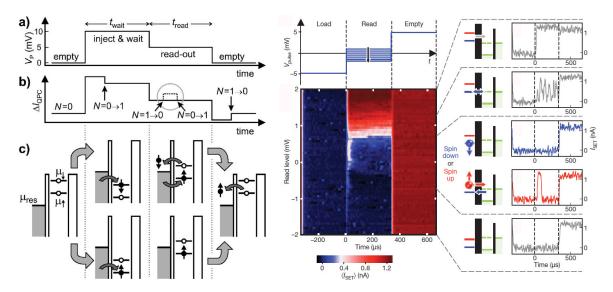

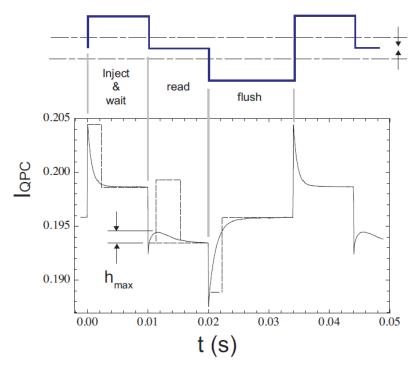

Finally, Chapter 5 presents the most ambitious experiment of the manuscript related to the fifth DiVincenzo criterion, the outcome measurement of the qubit. We decided to transpose the efficient energy selective spin readout, a pulse-required probing technique, from single-fabricated semiconducting devices to our industrial MOSFET silicon nanowire devices. I will first present the principle of the experiment and the practical needs for such experiment. Then I will show preliminary stationnary results, the stability diagrams and the Coulomb diamonds of the system. Going further, we decided to measure the stability diagrams while continuously pulsing on the device, hoping to gain information about the dynamics of the system. Finally, the energy-selective spin readout is attempted. I will present the main results both at zero magnetic field and finite magnetic field. The different codes used for that experiment are presented in the appendix.

At the very end, I will give my conclusion about these three years working on quantum dots in MOSFET silicon nanowires.

## La perspective d'un ordinateur quantique

Depuis 60 ans et suivant la loi dite de Moore [1] sur l'évolution du nombre de transistors par puce, le génie électrique a évolué de manière exponentielle, tant sur le plan théorique que sur les aspects techniques. Le premier transistor à effet de champ métal-oxyde-semiconducteur, appelé MOSFET a été développé au début des années 1960 dans les laboratoires Bell par Kahng et Atalla [2]. Aujourd'hui, un processeur peut accueillir près de 20 milliards de transistors MOSFET<sup>6</sup>. Pourtant, même avec les plus gros processeurs et supercalculateurs, certains problèmes ne peuvent être simulés par un ordinateur classique.

En 1982 déjà, le célèbre R. Feynman s'interrogeait : est-il possible de simuler exactement les systèmes quantiques, comme les liaisons chimiques ou les réactions chimiques, avec un ordinateur standard, classique ? Dans ce document [3], un recueil de notes prises lors d'un séminaire, il est l'un des premiers à parler d'un simulateur quantique universel, l'ordinateur quantique. Bien que l'idée concrète d'un ordinateur quantique ne soit pas encore claire, certains chercheurs (surtout théoriques) ont commencé à créer de nouveaux algorithmes et protocoles basés sur les lois de la mécanique quantique dans différents domaines spécifiques (par exemple un nouveau protocole, appelé BB84, en cryptographie quantique [4] déjà en 1984 ou l'algorithme de Shor [5] élaboré pour résoudre les problèmes de factorisation en nombres premiers avec un temps de calcul polynomial, 1997). L'idée de considérer des dispositifs matériels conçus pour traiter l'information de manière quantique est devenue sérieuse à la fin des années 1990.

L'analogie des bits numériques classiques sont les bits quantiques, appelés qubits. Alors qu'un bit numérique n'a que deux états disponibles, 0 ou 1, le qubit est un système quantique à deux niveaux caractérisé par sa fonction d'onde  $|\psi\rangle=c_0|0\rangle+c_1|1\rangle$ , une superposition des deux états propres  $0\rangle$  et  $|1\rangle$ . Si l'on intrique N de ces qubits, cela représente  $2^N$  états propres et donc autant de coefficients. En traitant chacun de ces coefficients en même temps, un ordinateur quantique fonctionne de manière exponentiellement plus rapide que son homologue classique.

Au début de 1998, D. Loss & D.P. DiVincenzo ont publié une proposition bien connue d'un ordinateur quantique à base de semi-conducteurs, constitué de boîtes quantiques [6].

<sup>&</sup>lt;sup>6</sup>L'introduction du chapitre 3 présente une histoire plus détaillée du transistor.

<sup>&</sup>lt;sup>7</sup>En 1980, le mathématicien russe Yuri Manin proposait également l'idée d'un ordinateur quantique dans son livre *Computable and Uncomputable*. Au début des années 1980, l'américain Paul Benioff fut l'un des premiers à décrire théoriquement un ordinateur fonctionnant avec les principes de la mécanique quantique.

8 Introduction

Dans ce cas, les deux états propres des qubits sont les deux états de spin d'électrons solitaires piégés dans des boîtes quantiques couplées, hébergées dans un matériau semi-conducteur. Le calcul est réalisé en faisant varier le couplage entre les boîtes, agissant comme des portes logiques.

Plus tard dans l'année, B. Kane a publié une autre proposition pour un ordinateur quantique intégrable à grande échelle, faite de donneurs dans une matrice de silicium [7]. Dans ce cas, les 2 états de spin nucléaire des donneurs sont les états propres des qubits. Là encore, le calcul est effectué en agissant sur des grilles conductrices, en faisant varier le couplage entre les donneurs.

Enfin, toujours en 1998, J. Preskill a publié un article théorique [8] sur la possibilité d'implémenter des codes de correction d'erreurs, la capacité de surmonter la fuite d'informations quantiques due aux interactions des qubits avec leur environnement. Cette année 1998 pourrait être considérée comme l'année de naissance de la course aux ordinateurs quantiques intégrables à grande échelle.

À la suite de ces travaux pionniers, D.P. DiVincenzo a publié un autre article en 2000 [9] sur la mise en œuvre pratique de l'informatique quantique. De ce papier sont nés les *critères de DiVincenzo*, une liste de cinq exigences techniques requises pour qu'un ordinateur quantique puisse être viable. Ces points sont abordés dans la section suivante.

En conséquence, les chercheurs ont examiné de nombreux types de matériel pouvant accueillir des qubits. Les deux propositions susmentionnées concernent les matériaux semi-conducteurs. Lors de ces 20 dernières années, les hétérostructures à base d'arsénure de gallium, les boîtes quantiques dans du silicium et du silicium-germanium ont été profondément étudiées. Par exemple, en 2016 dans notre groupe, R. Maurand et al ont réalisé le premier qubit dans un dispositif PMOS en silicium [10]. Pour plus de détails sur les qubits réalisés dans du silicium et du silinium-germanium, voir [11]. En 2020, seuls quelques qubits couplés ont été réalisé dans les matériaux semi-conducteurs. Très récemment, un dispositif de quatre qubits a été démontré [12].

Les matériaux semi-conducteurs ne sont qu'une possibilité. En fait, beaucoup de systèmes différents ont été inventés et conçus tels que les ions piégés [13], les qubits supraconducteurs et les systèmes photoniques [14]. Ces trois systèmes ont fait l'objet de recherches approfondies et de nombreux réseaux de qubits ont été réalisé de manière expérimentale. Je peux aussi dire un mot sur les atomes neutres [15], les nanotubes de carbone [16], les centres NV dans le diamant [17] qui n'ont atteint qu'un seul ou peu de qubits connectés et,

enfin, les systèmes topologiques [18], qui ont été développés au niveau théorique seulement. Aujourd'hui, les candidats les plus prometteurs pour réaliser un ordinateur quantique sont les qubits supraconducteurs et les qubits photoniques. En 2019, un puce de 53 qubits supraconducteurs connectés a été réalisé par Google AI Quantum labo [19]. Dans un avenir proche, ils prévoient de travailler avec une puce de 72 bits<sup>8</sup>. Une revue récente sur l'état de l'art des qubits supraconducteurs d'un point de vue d'ingénieur quantique est présenté dans [20]. En 2020, 50 qubits photoniques connectés ont été réalisé par un groupe chinois [21]. Pouvoir travailler avec un nombre élevé de qubits connectés entre eux ouvre la voie à des possibles expérimentations impliquant des algorithmes quantiques.

Il est clair que pour l'instant, les qubits supraconducteurs sont en avance dans la course à l'ordinateur quantique réalisé dans un solide. Cependant, il est encore difficile d'imaginer une puce supraconductrice pouvant accueillir des milliers de qubits fonctionnels. La surface de la puce et l'intégrabilité à grande échelle du contrôle individuel des qubits sont des défis expérimentaux importants<sup>9</sup>. Dans la prochaine section, je présenterai brièvement ce que devrait être un *bon qubit* et comment les qubits basés sur des MOSFET sont des candidats viables pour le calcul quantique à grande échelle.

# Quelles différences entre le bon et le mauvais qubit ?

Comme présenté dans la dernière section, l'ère 1998-2000 a établi les principales nécessités techniques pour qu'un ordinateur quantique soit réalisable. Elles peuvent être écrites sous la forme synthétique des cinq *critères de DiVincenzo* :

- Intégrabilité à grande échelle avec des qubits bien définis. En pratique, il est possible de construire un système avec un seul qubit bien caractérisé. Cependant, il est très difficile de construire un système avec un nombre arbitrairement grand de qubits. Actuellement, l'un des plus grands problèmes rencontrés est qu'il est nécessaire de construire des installations expérimentales exponentiellement plus grandes et complexes pour accueillir un plus grand nombre de qubits.

- Initialisation des qubits à un état simple et standard. Le calcul quantique est basé sur l'exécution d'opérations sur des états de qubits et la communication du résultat. Cette procédure est fortement dépendante de l'état initial. Dans de nombreux cas,

<sup>&</sup>lt;sup>8</sup>https://ai.googleblog.com/2018/03/a-preview-of-bristlecone-googles-new.html

<sup>&</sup>lt;sup>9</sup>Cependant, les physiciens explorent un large éventail de réalisations possibles, par exemple : https://singularityhub.com/2020/06/22/a-new-startup-intends-to-build-the-worlds-first-large-scale-quantum-computer/.

10 Introduction

l'initialisation est réalisée en laissant le système relaxer vers l'état fondamental. Il existe également d'autres approches, comme le pompage optique [22].

- Long temps de cohérence. La cohérence caractérise les états quantiques (superposés) qui portent une phase bien définie. La perte de la cohérence est appelée décohérence. La décohérence est un problème intrinsèque rencontré dans les grands systèmes quantiques macroscopiques. En outre, plus le système quantique est couplé à son environnement, plus il subit la décohérence.

- Un ensemble "universel" de portes logiques quantiques. En informatique, les algorithmes que nous pouvons coder sont limités par le nombre de portes logiques que nous pouvons mettre en œuvre. Il a été démontré qu'un ordinateur quantique universel peut être construit en utilisant un très petit ensemble de portes logiques à 1 et 2 qubits. Tout dispositif expérimental qui parvient à avoir des qubits bien caractérisés, une initialisation rapide et fidèle et de longs temps de cohérence doit également permettre d'influencer l'Hamiltonien (énergie totale) du système, afin d'apporter des changements cohérents capables de mettre en œuvre cet ensemble universel de portes logiques.

En pratique, le chiffre le plus important est le rapport entre le temps de cohérence (point précédent) et le temps moyen des portes logiques, ce qui donne le nombre d'opérations que l'on peut effectuer sur les états du qubits avant de perdre la cohérence, et donc l'information. D'un autre côté, il est souhaitable de disposer d'un système qui puisse être manipulé rapidement afin que l'on puisse interagir avec lui le plus vite possible. Dans l'ensemble, il faut trouver un compromis entre la capacité à mettre en œuvre le contrôle pour les portes logiques et la décohérence.

Une mesure spécifique au qubit. Pour tout processus modifiant les états quantiques des qubits, la mesure finale de ces états est d'une importance cruciale lors de l'exécution des calculs. Les diférentes possibilités de mesure des états quantiques sont énormément étudiées dans la communauté (par exemple, la réflectométrie radio-fréquence dans notre groupe).

Dans le cadre de cette thèse, le premier critère concernant l'intégrabilité à grande échelle est d'un intérêt primordial. Par opposition aux dispositifs fabriqués à l'unité, à faible débit, encore étudiés dans la communauté des supraconducteurs et des semi-conducteurs, notre groupe se concentre sur les boîtes quantiques dans des nanofils de silicium MOSFET produits à l'échelle industrielle sur des plaques de silicium de 300 mm de diamètre. Ainsi, tous les dispositifs étudiés dans ce manuscrit proviennent de l'institut LETI, situé au CEA Grenoble.

La motivation a toujours été d'étudier les effets quantiques tels que la quantification de la charge, la cohérence, la manipulation des états, la lecture des états, etc. dans les dispositifs de test dérivés des MOSFET. La perspective à long terme est de concevoir des réseaux de boîtes quantiques en se basant sur ce que nous apprenons sur les boîtes quantiques créés dans les MOSFET. Ce point est l'un des principaux objectifs des 20 années de collaboration entre notre laboratoire et le LETI.

# Plan du manuscrit : l'intégrabilité comme préoccupation majeure

Le chapitre 2 donne une base théorique sur le transport quantique à travers les boîtes quantiques. Je présenterai le modèle d'interaction constante pour les systèmes de boîtes quantiques simple et double, en insistant sur le diagramme de stabilité de la double boîte, un outil expérimental crucial. Je parlerai également des techniques de mesure qui ont évolué tout au long de l'histoire des études sur les boîtes quantiques et, en particulier, de la réflectométrie radio-fréquence sur grille. Cette technique de mesure plutôt nouvelle et prometteuse pourrait être l'une des réponses au premier critère de DiVincenzo grâce à sa sensibilité et à son potentiel d'intégrabilité.

Le chapitre 3 traite principalement de la fabrication des dispositifs. Après une brève histoire du transistor MOSFET et des raisons pour lesquelles il présente de grands avantages en tant qu'élément central de l'informatique classique moderne, je présente la ligne directrice du processus industriel développé au CEA LETI pour créer les nanofils de silicium MOSFET. Je souligne également les variations spécifiques nécessaires entre le procédé standard et notre procédé personnalisé afin que les dispositifs soient aussi optimaux que le permettent nos connaissances. Une présentation de chaque dispositif étudié dans ce manuscrit est donnée. Le lecteur est informé que i) j'ai travaillé sur deux géométries différentes de boîtes quantiques doubles, à savoir les configurations en série et en parallèle et ii) j'ai travaillé sur les deux dopages possibles des nanofils, à savoir les dispositifs dopés N avec des électrons comme porteurs de charge et les dispositifs dopés P avec des trous comme porteurs de charge. Je complète le chapitre par la présentation d'une expérience cryogénique autorisant deux canaux pour la réflectométrie radio-fréquence dans le but d'étudier le transport quantique dans les systèmes de boîtes quantiques. La particularité de ce dispositif est qu'il permet également d'envoyer des impulsions (entre des centaines de nanosecondes et quelques millisecondes) électriques sur deux canaux, une caractéristique nécessaire aux expériences que je présenterai au chapitre 5.

12 Introduction

Le chapitre 4 est consacré au couplage entre deux boîtes quantiques. Comme il a été présenté dans les propositions de Kane et DiVincenzo, il faut contrôler soigneusement le couplage entre deux boîtes quantiques. Trois différents degrés de liberté sont comparés : l'approche par la grille arrière, qui est l'approche historique ; l'approche par ligne métallique, qui est un nouveau degré de liberté ; l'approche par un médiateur quantique, qui consiste à placer un objet quantique entre deux boîtes. L'état de la boîte centrale influencera fortement le couplage entre les deux boîtes extérieures.

Enfin, le chapitre 5 présente l'expérience la plus ambitieuse du manuscrit, relative au cinquième critère de DiVincenzo, la mesure de l'état du qubit. Nous avons décidé de transposer la lecture sélective en énergie du spin, une technique de sondage par impulsions des dispositifs semi-conducteurs fabriqués en laboratoire, à nos dispositifs industriels en nanofils de silicium MOSFET. Je vais d'abord présenter le principe de l'expérience et les besoins pratiques de cette expérience. Ensuite, je montrerai les résultats statiques préliminaires : les diagrammes de stabilité et les diamants de Coulomb du système. Pour aller plus loin, nous avons décidé de mesurer les diagrammes de stabilité tout en pulsant continuellement sur le dispositif, dans l'espoir d'obtenir des informations sur la dynamique du système. Enfin, je tenterai de lire le spin par sélectivité en énergie. Je présenterai les principaux résultats à la fois à champ magnétique nul et à champ magnétique non nul. Les différentes codes informatiques nécessaires à la réalisation de l'expérience seront présentés en annexe

À la toute fin, je donnerai ma conclusion sur ces trois années de travail sur les boîtes quantiques dans les nanofils de silicium MOSFET.

# Chapter 2

# Basics of quantum transport through quantum dots

"We must be clear that when it comes to atoms, language can be used only as in poetry."

-Niels Bohr, 1920

## Résumé

Ce premier chapitre consiste en une introduction à la théorie du transport quantique à travers des boîtes quantiques ainsi qu'aux techniques de mesure pour sonder de tels systèmes.

Dans une première section, je commencerai par définir ce qu'est une boîte quantique. Je me concentrerai ensuite sur le cas d'une seule boîte quantique piégeant un grand nombre de porteurs de charge, électrons ou trous. Grâce au modèle de l'interaction constante entre les porteurs de charge piégés dans la boîte, je définirai l'énergie d'addition, énergie nécessaire pour ajouter un porteur dans la boîte. Dans ce cadre, l'énergie d'addition est constante. Suite à ce résultat, je donnerai une représentation en potentiels chimiques séparés par l'énergie d'addition, une représentation qui sera très utile pour tous les cas abordés dans ce manuscrit. Les phénomènes de pics de Coulomb et diamants de Coulomb sont présentés.

Le cas d'une seule boîte quantique contenant un faible nombre de porteurs est ensuite introduit. Je montrerai que, dans cette situation et contrairement au cas précédent, l'énergie d'addition n'est plus constante et nous sommes sensibles aux états quantiques excités.

La deuxième section est dédiée au système contenant deux boîtes quantiques. Dans ce manuscrit, ce type de système sera majoritairement étudié. Je commencerai cette section en présentant les deux géométries possibles, les deux boîtes en série ou en parallèle. La représentation en potentiels chimiques permettra de construire l'un des outils expérimentaux les plus importants de cette thèse, le diagramme de stabilité.

La suite de cette section concerne les systèmes de deux boîtes quantiques contenant un faible nombre de porteurs. Le diagramme de stabilité est présenté dans ce cas. En outre, un mécanisme de conversion spin-charge, la lecture de spin par sélectivité en énergie, est discuté. Le dernier chapitre de ce manuscrit tentera de mettre en oeuvre un tel mécanisme de conversion spin-charge en adaptant un cryostat du laboratoire.

Enfin, cette section présentera le cas où deux boîtes quantiques sont couplées *via* une autre boîte quantique. C'est le cas du médiateur quantique. Un modèle théorique sera présenté. Cette partie servira de support pour les expériences présentées dans le chapitre 4.

La dernière section traitera des techniques de mesures. Je discuterai surtout des détecteurs de charges locaux et de la réflectométrie radio-fréquence. En particulier, cette partie expliquera pourquoi, dans notre cas, nous avons préféré la réflectométrie aux détecteurs de charges.

As discussed in the introduction, the most important system we will work with in this thesis is the quantum dot or an ensemble of coupled quantum dots. In this chapter I am going to introduce a part of the theoretical background needed to properly understand the physics related to these systems. First, I will describe the single quantum dot system both in the many carriers and in the few carriers regime. Then I will present the double quantum dot system and the so-called stability diagram. Finally, I will say a few words about the measurement technics of such systems and in particular the introduction to the gate-coupled radiofrequency reflectometry.

## 2.1 The single quantum dot system

The single quantum dot is a canonical system and refers to a physical entity exhibiting charge quantization due to a three dimensional confinement potential. This entity might be a dopant, a region of the space where charge carriers are accumulated or a charge trap in the material. One must understand the physics behind it before going onto more complex systems. The simplest case is the many carriers regime that I will present first. Then I will move onto the few carriers regime.

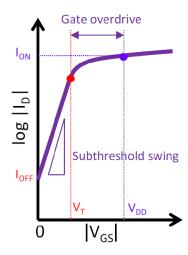

## 2.1.1 The many carriers regime

The single quantum dot in the many carriers regime, often called the single electron transistor, has been widely studied in many different systems: metallic nanostructures [23], GaAs heterostructures [24], silicon nanowires [25], carbon nanotubes [26], superconducting materials [27]. While the host material is very different, the model can be the same because it is essentially an electrostatic effect. Most of this part is inspired by Mathieu Pierre [28] and Max Hofheinz's [29] thesises, former students of the group who studied the single quantum dot system in the many carriers regime as well as single dopants and charge traps.

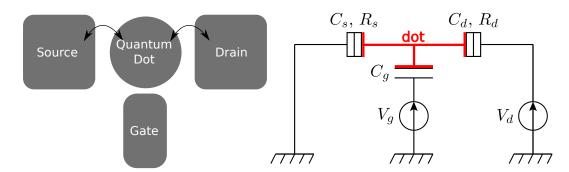

A single quantum dot can be represented by the schematic system shown in the left panel of the next figure 2.1. It consists of a small-size conducting island<sup>1</sup> capacitively coupled to a source, a drain and a gate. The source (drain) is supposed to be metallic and is described by a Fermi-Dirac distribution with its inflexion point at  $\mu_{s(d)}$ . They are the carrier reservoirs. The charge carriers are able to flow between the source and the drain through the dot. The transport is allowed because of the presence of tunnel barriers between both leads and the dot. To sum up, the gate is only capacitively coupled to the dot and the tunnel barriers between the

<sup>&</sup>lt;sup>1</sup>It should be clear hereafter why the island should be small.

leads and the dot can be modeled as a capacitance and a resistor in a *parallel configuration* and is schematized by the two rectangles in the electrical schematic shown in the right panel.

**Figure 2.1** Left panel: simple sketch of a single quantum dot tunnel coupled to the source and the drain and only capacitively coupled to the gate. Right panel: equivalent electronic schematic of that system. By applying a voltage between the source and the drain, charge carriers flow through the dot and the tunnel barriers, represented by the rectangle and characterized by a capacitance  $C_{s(d)}$  and resistor  $R_{s(d)}$  in parallel. By applying a voltage onto the gate, we will act on the dot only capacitively, characterized by the capacitance  $C_g$ . Eventually, we are going to modify the energy of the quantum dot. Adapted from [28].

The simplest way to model the electrostatic of such many carriers system is the constant interaction model. It is based on the assumption that the Coulomb interactions among electrons in the dot, and between electrons in the dot and those in the environment, are parametrized by a single, constant capacitance C which is the sum of the three capacitances introduced in the right panel of the figure 2.1:  $C = C_s + C_d + C_g$ . Thus, the total energy U(N) of a dot containing N carriers of charge q, with voltages  $V_s$ ,  $V_d$  and  $V_g$  applied to the source, the drain and the gate, respectively, is given by:

$$U(N) = \frac{[qN + C_s.V_s + C_d.V_d + C_g.V_g]^2}{2C} = E_{elec}(N)$$

(2.1)

where q is either -lel for electrons or lel for holes with e the elementary charge<sup>2</sup>. This energy of the dot has only an electrostatic contribution. Playing with the different voltages will change the electrostatic potential of the dot.

<sup>&</sup>lt;sup>2</sup>Since may 2019, the elementary charge e has been fixed in the SI and e=1.602176634 $e^{-19}A.s$ , exactly.

We define the electrochemical potential of the dot  $\mu(N)$  as the difference in electrostatic energies of two consecutive carriers numbers, hence:

$$\mu(N) \equiv U(N) - U(N-1)$$

$$= (N - \frac{1}{2})E_{C}$$

$$+ \frac{E_{C}}{q}(C_{s}.V_{s} + C_{d}.V_{d} + C_{g}.V_{g})$$

$$= \mu_{elec}(N)$$

(2.2)

where  $E_C = \frac{e^2}{C}$  is the so-called charging energy. This charging energy is inversely proportionnal to the dot size: the smaller the dot, the smaller the capacitance carried by the dot, the higher the electrostatic energy. In that many carriers regime, the contributions to the electrochemical potential is purely electrostatic. We go further and define the addition energy, the difference between two electrochemical potentials of successive occupation numbers N+1 and N or, equivalently, the energy needed to add 1 carrier when the dot is already occupied by N carriers:

$$E_{add}(N) = \mu(N+1) - \mu(N) = E_C$$

(2.3)

In the many carriers regimes, the addition energy is equal to the charging energy and does not depend on the occupation number  $N^3$ . This energy corresponds to the energy one has to pay to put one more carrier in the dot. This characteristic energy  $E_C$  has to be compared with the temperature: if  $k_BT >> E_C$ , no electrostatic effect will occur since the temperature alone is able to overcome the tunnel barriers and charge the dot whereas in the opposite case  $k_BT << E_C$ , the energy has to be provided by the gate. This is the reason why we are working at very low temperature with small-size island, we want to be sensitive to Coulomb interactions between the carriers within the dot. In practice, a good condition is  $E_C > 10k_BT$ .  $E_C$  does depend on the dot capacitance. So one can associate a capacitance to a temperature: for instance, using the practical condition given earlier, a 1 fF capacitance corresponds to a temperature of T=0.185 K and a 50 aF capacitance corresponds to a temperature of T=3.7 K. The smaller the dot and the lower the temperature, the stronger the electrostatic effects will be on electrical transport.

Equation 2.3 gives a useful representation of a many carriers quantum dot and is presented in the following figure 2.2 where we consider 0K-Fermi-Dirac distributions for the source

<sup>&</sup>lt;sup>3</sup>This is the reason why this model is called the constant interaction model.

and the drain. Carriers are allowed to flow through the quantum dot only when a dot chemical potential is aligned with  $\mu_s$  and  $\mu_d$ .

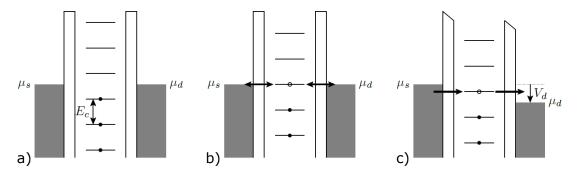

Figure 2.2 Schematic model of the electrostatic behind the many carriers quantum dot. Three different regimes are presented. The two grey rectangles in each regime represent the 0K-Fermi-Dirac distribution of the carrier reservoirs characterized by their potential  $\mu_{s(d)}$ . In between is the quantum dot, represented by a regular ladder characterized by the charging energy  $E_c$ . It is connected to the leads thanks to two tunnel barriers. We basically act vertically on the ladder with the gate. In the case a, no chemical potential is aligned with the chemical potentials of the leads, no carriers flow, there is no current. In the case b, One chemical potential is aligned with the source and the gate potentials. Charges are able to flow through the dot, hence current is allowed. In the case c, we apply a voltage between the leads, opening a energetic window proportionnal to the bias voltage. Any levels, here only one, which lie in that window will contribute to the current. Taken from [28]

This ladder of electrochemical potential can be moved up and down thanks to the gate voltage. In the case a) of figure 2.2 no electrochemical potentials of the dot is aligned with the source and drain chemical potentials, no carriers flow whereas in the case b), one chemical potential of the dot is aligned with the source-drain chemical potentials and hence, carriers flow. It is equivalent to say that the two energy levels E(N) and E(N+1) are degenerate. This is the reason why these kind of devices exhibits the so-called Coulomb Blockade regime. In the case a), the current is blocked until a potential of the dot is aligned with the source and drain thanks to the gate voltage or, equivalently, until the gate brings enough energy to counteract the Coulomb repulsion between carriers in the quantum dot. This Coulomb blockade regime can be easily revealed by the source-drain current versus gate voltage measurements and such a characteristics is presented in the following figure 2.3.

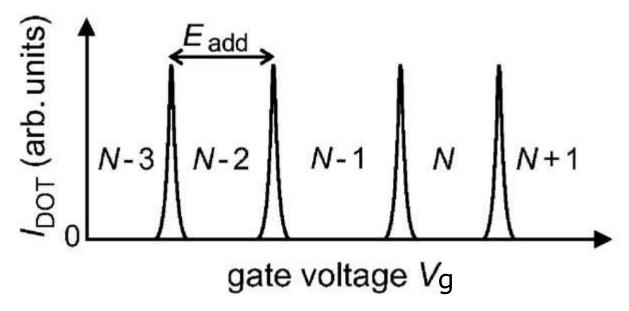

Each peak corresponds to one chemical potential aligned with the source and drain. Equivalently, the two energies corresponding to two consecutive Coulomb blockade areas are degenerate at the Coulomb peak. Between the peaks the occupation number is constant and

Figure 2.3 Current between the source and the drain through the dot as a function of the gate voltage. Globally, there is no current flowing through the dot except for specific values of the gate voltage where current peaks appear, called the Coulomb peaks. Between these peaks, the current is blocked. This is called the Coulomb blockade phenomenom. In these regions, the number of carriers is constant. Practically, we can count the carriers inside the dot. Taken from [30]

the peaks are intrisically separated by the addition energy  $E_{add}$ . However, on that graph, we do not directly extract the addition energy but rather the "addition gate voltage",  $\Delta V_g$ , which is directly linked to the gate capacitance:  $\Delta V_g = \frac{e}{C_g}$ . In fact, in the limit scenario where the electrostatic control of the chemical potentials of the dot by the gate is maximum, 1 mV of addition gate voltage leads to 1 meV of addition energy. This is not true in realistic devices, the electrostatic control of the dot is partially done by the gate, by the source and by the drain and, thus, we define the lever-arm parameter  $\alpha$ :

$$\alpha = \frac{C_g}{C} = \frac{C_g}{C_g + C_s + C_d} \tag{2.4}$$

This parameter gives the efficiency of the control of the dot potential by the gate.

The panels a) and b) of the figure 2.2 are representations of the system in the so-called linear regime where no (or very small) source-drain bias is applied. In the panel c), a source-drain bias  $V_d = \mu_d - \mu_s$  is applied, opening what is called a bias window. This is the non-linear regime and we can now plot the source-drain current (or equivalently, the

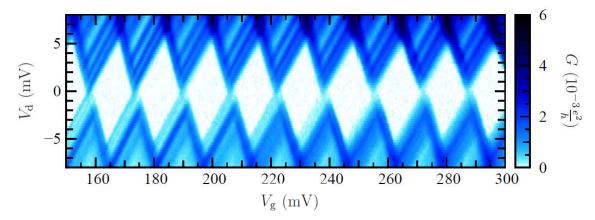

transconductance) as a function of the gate voltage and the source-drain bias in a colormap. Such a characteristic 2D colormap is presented in the figure 2.4.

Figure 2.4 2D-plot of the measured drain-source transconductance (equivalent to a current measurement) versus gate and drain voltages, presented in [29] showing regular so-called Coulomb diamonds. The carrier number is constant in the white region where no current flows. The half height of the diamond gives the addition energy in eV while the width between two consecutive diamond edges gives the equivalent of the addition energy but converted into gate voltage with the lever-arm parameter. In this presented case, the diamonds are pretty regular, showing a nice metallic dot in a clean region of the gate voltage paramater space.

This 2D-plot is referred to as Coulomb Diamonds. White color indicates 0 conductance so no current flows. The darker is the blue, the higher is the conductance and the higher is the current value. The figure 2.3 can be seen as a cut along the  $V_d=0$  mV horizontal line of the figure 2.4. The reader shall wonder why we see lines out of the diamonds. This is due to the fact that in this experiment, the quantum dot is not alone but in fact, it is coupled to one or more fluctuating charges. This observation shows that a quantum dot in the metallic regime, a single electron transistor, is a very good charge sensor and, thus, it can be used as a charge detector. I will come back to this point at the end of this chapter and use this specific charge detector effect in the last chapter of the manuscript. These Coulomb diamonds are a very powerful tool for the experimentalist as it gives several informations about the system: the 2 slopes are related to the three capacitances of the systems while the half height of the diamonds gives the charging energy of the dot.

This introduction to many carriers regime/metallic quantum dots gave only the essential informations and parameters. However I coud have told much more about the theory. For instance one can calculate the current between two metallic leads through the quantum dots in different regimes. ([28], part 1.1.3-1.2, [29], chap. 2).

So far, I have considered charge states only. However, one can ask about the more interesting spin states. Theoretically, with the presence of a magnetic field, we should be able to see the spin states in the addition energy spectrum of the quantum dot because of Pauli exclusion principle. Once we pay the charging energy  $E_C$ , the next time we should pay  $E_C + \Delta_{g \to e}$  with the second term being the energy splitting between two successive spin states.

This prediction of probing spin states in the many carriers regime has been seeked for a while with mitigate results. For instance the following paper [31] realized by our group measures the distribution of energy spacing in the addition energy spectrum. Although this many carriers regime has been extensively studied for the past decades, we have to go down to the few carriers regime if we really want to probe and effectively make use of spins states in such systems.

## 2.1.2 The few carriers regime: access to quantum states

A major advance for our group in the field of low carriers quantum dots has been done by B. Voisin and R. Maurand during their PhD and postdoc, respectively. I will present their main results inspired from Voisin's PhD manuscript and one of his papers [32].

We start from the same system presented in the figure 2.1. While in the many carriers regime the carriers lie in a continuum of orbital states within a single charge state (occupation number state), the few carriers regime offers the opportunity to populate orbital excited states. We then need to add the contribution of these excited states in the energy of the dot, equation 2.1:

$$U(N) = U_{elec}(N) + \sum_{n=1}^{N} E_n(B)$$

(2.5)

with the first term being the electrostatic term defined earlier and the second term taking into account the single-particle energy levels. This energy does depend on the magnetic field. The electrochemical potential of the dot will also have a contribution of this last term:

$$\mu(N) \equiv U(N) - U(N-1) \tag{2.6}$$

$$= \mu_{elec}(N) + E_N \tag{2.7}$$

with  $\mu_{elec}(N)$  being the electrostatic contributions defined in equation 2.2. While we were only dealing with ground states in the many carriers regime, we now have access to single-particle excited states. To avoid confusion, we will adapt the notation of the electrochemical

potential: the electrochemical potential for a transition between the (N-1)-carrier state  $|a\rangle$  and the N-carrier state  $|b\rangle$  is then denoted  $\mu_{a\to b} = U_b(N) - U_a(N-1)$ . We can also define an addition energy:

$$E_{add}(N) = \mu(N+1) - \mu(N) = E_C + \Delta E$$

(2.8)

with  $E_c$  the purely electrostatic charging energy defined earlier and  $\Delta E$  the energy spacing between two discrete quantum levels.  $\Delta E$  can be zero when two consecutive carriers are added to the same degenerated level.

The first big difference between the many and the few carriers regimes is the value of that addition energy which is not a constant anymore and does depend on the single-particle excited states. When one introduces the first carriers into the dot, the space between the different Coulomb peaks is not constant anymore (it was the case in figure 2.3). This also means (and it is equivalent to) that the height of the Coulomb Diamond is not constant anymore too (different from 2.4). The following figure 2.5 shows experimental Coulomb diamonds in a P-type single dot realized by B. Voisin and presented in the paper [32]. The carriers are holes.

Figure 2.5 Coulomb diamonds in the few carriers regime. Conductance as a function of gate and source-drain voltages. In that specific case, the carriers are holes. This is the reason why we increase the number of carriers carried by the dot by decreasing the gate voltage. Compare to the many carriers regime Coulomb diamonds of figure 2.4 which were regular and similar, we see that in the few carriers regime, the height of the diamonds as well as the width between two consecutive diamonds are not constant anymore. This is a strong experimental evidence that we are indeed dealing with a few carriers quantum dot. Taken from [32]

A strong, if not a sufficient observation that we are dealing with a few carriers regime quantum dot system is the fact that for a large source-drain bias, here defined as  $V_b$ , the height

of the first diamond tend to infinity. There is no energy levels playing a role in the transport below. This is pretty clear in the figure 2.5: in the left part of the 2D plot, beyond  $V_g = 600$  mV, we enter a region where the height of the Coulomb diamonds seems to be large. In fact, we could crank up the absolute value of the source-drain bias voltage and we would not see any current at all (this is also visible in [33] in a case of a double quantum dot system).

The following figure 2.6 shows on the left panel the device used during this study and the important results on the right panel. The device is a single quantum dot defined in a P-doped MOSFET device.

Figure 2.6 Main results of [32]lead by B. Voisin. The paper is focused on the few holes regime. The device is shown in the left panel. It consists of a P-type MOSFET (Metal Oxide Semiconductor Field Effet Transistor) commonly used in electronic devices. The leads are in green, the gate in grey and the channel hosting the electrostatically defined quantum dot in red. The blue spacers ensure appropriate tunnel barriers between the leads and the dot. The whole paper discusses the asymetry of the first holes transitions g-factor involved in the Zeeman energy relation:  $\Delta E_Z = g.\mu_B.||\vec{B}||$  with  $\mu_B$  being the Bohr magneton.

The main result of that paper is the measurement of the anisotropy of the g-factor g appearing in the Zeeman formula giving the splitting of spin states as a function of the magnetic field orientation  $\Delta E = g.\mu_B.||\vec{B}||$ . I am going to briefly present the result. They started looking at the evolution of the first Coulomb peaks, or equivalently the spacing between two transitions in the Coulomb diamonds 2D-plot, as a function of the magnitude of a magnetic field for a given direction of that field. This is presented in the figures a) and b) of the right panel of the figure 2.6. They also recorded that spacing for different orientations of

the magnetic field for a given amplitude. Thanks to the Zeeman formula, it is possible to plot the Zeeman g-factor as a function of the orientation of the magnetic field and they show that this g-factor is asymetric, figures c) and d) of the right panel of the figure 2.6. It does depend on the orientation of the magnetic field and on the occupation number of the dot, hence on  $V_g$ . For electrons, the g-factor is always close to 2. Here we see that, for different magnetic field orientations and occupation numbers, the g-factor spans between 1.5 and 2.5. For a 1T magnetic field and an electron g-factor equals to 2, the Zeeman energy spacing is roughly equal to  $\Delta E \approx 110~\mu eV$ .

This work on a P-type single quantum dot in the few carriers regime has lead to the realization of the first silicon CMOS hole spin qubit presented in 2016 in R. Maurand's paper [34].

The single quantum dot device is the canonical system. I have presented what I consider to be the most important concepts for this system both in the many carriers and the few carriers regime, namely the charging energy, the addition energy, the Coulomb diamonds. In quantum transport through quantum dots, the next natural step is the study of the double quantum dot system, where two dots are involved in the charge transport. The next part is dedicated to the double quantum dot system.

# 2.2 The double quantum dot system

The double dot system offers a richer physics than the simple quantum dot. Lots of practical realizations are available. Beyond the materials involved, the elementary configurations are the serial or parallel ones. The theoretical description is basically the same. First, I will present the double quantum dot for spinless particles then I will introduce the spin in the system.

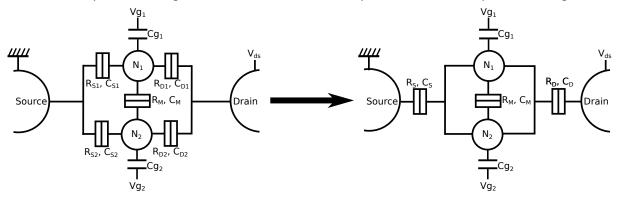

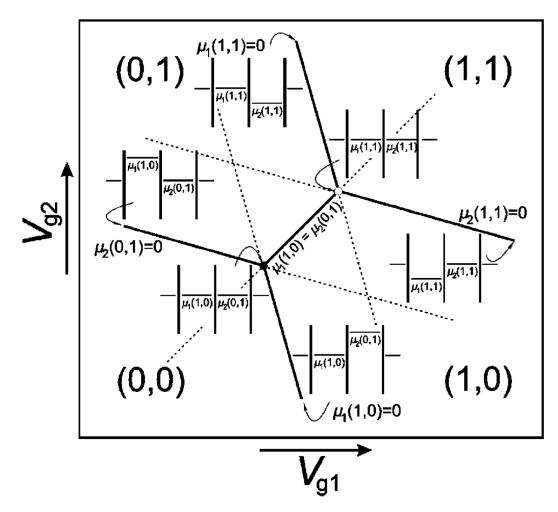

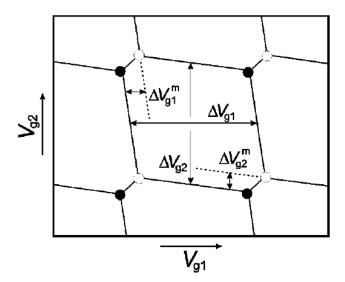

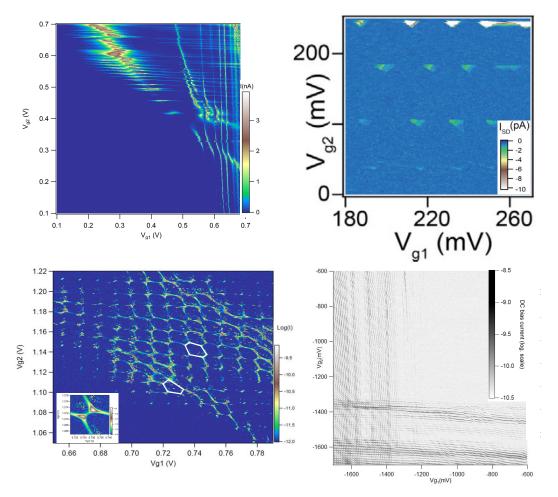

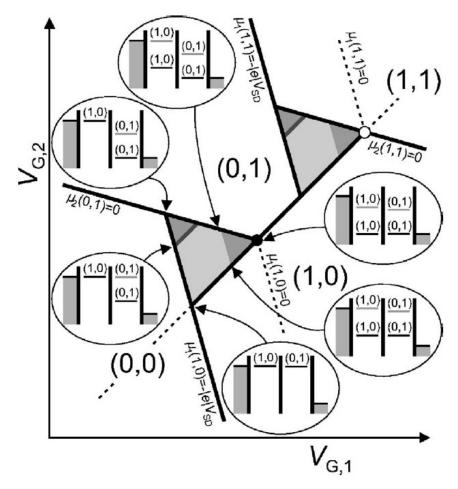

### 2.2.1 The many carriers regime and the stability diagram

As I said just before, the double quantum dot system gives rise to much more interesting physics. Most of this part is inspired by the Review of Van Der Wiel et al. [35] which gives the main ideas behind the many carriers double quantum dot system. I shall say that I will not talk about current modeling in quantum dots, the interesting reader can find a detailed study in [36].

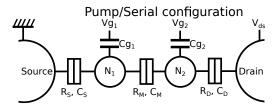

I shall start first with the configurations. The following figure 2.7 presents the two main electronic networks studied in the double quantum dot system. The top panel represents the serial, also called the pump configuration, and the bottom panel represents the parallel, often called face-to-face in this manuscript, configuration. The two configurations will be discussed in this manuscript.

The two dots 1 and 2 are represented by the circles and denoted with their occupation number  $N_1$  and  $N_2$ . Both are capacitively coupled to their own gate  $G_1$  and  $G_2$ , respectively, characterized by the capacitances  $Cg_1$  and  $Cg_2$ . I shall remark that for the sake of simplicity, I do not take into account the cross-capacitances between the gate 1 and the dot 2 and the opposite. As previously defined, the rectangles represent the tunnel barriers of the system modeled by a capacitance and a resistor in parallel, allowing carriers to flow. The source is grounded and the drain can be biased with the voltage  $V_{ds}$ . There are two kinds of tunnel barriers: the ones connecting the leads and the dots, responsible for dot-lead charge transitions and the one between the dots, responsible for interdot charge transitions.

Face-to-face/parallel configuration

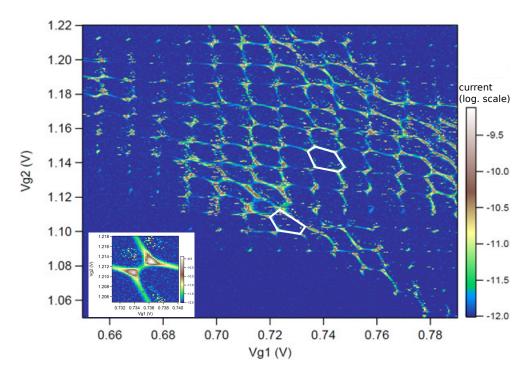

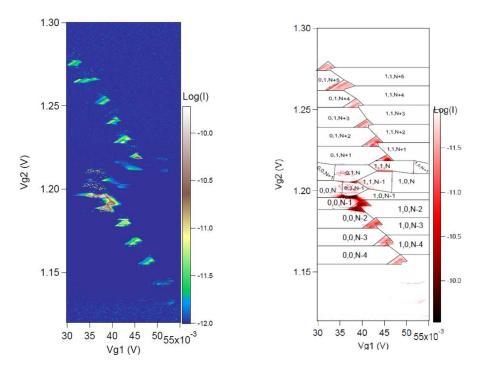

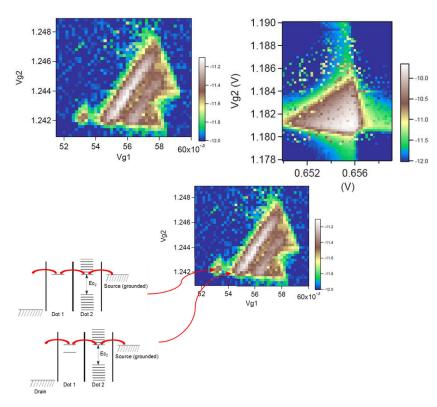

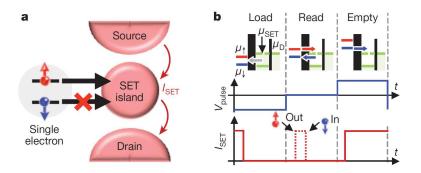

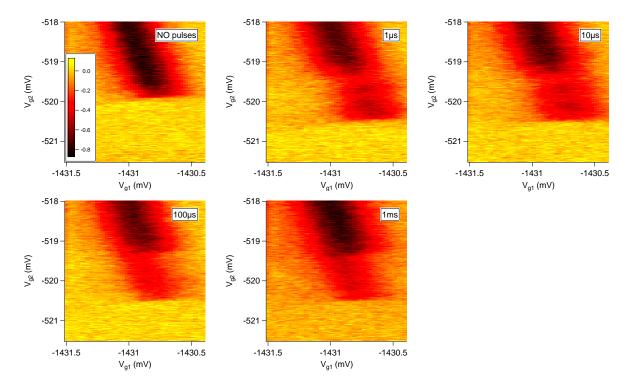

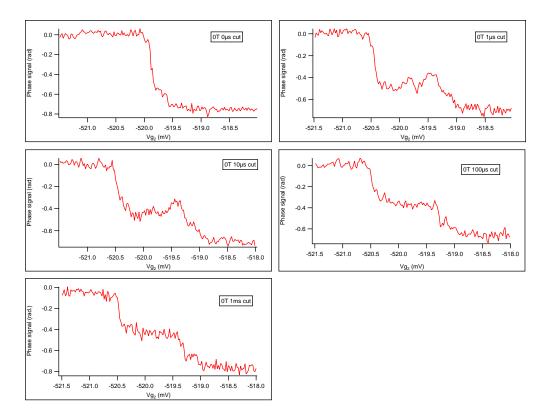

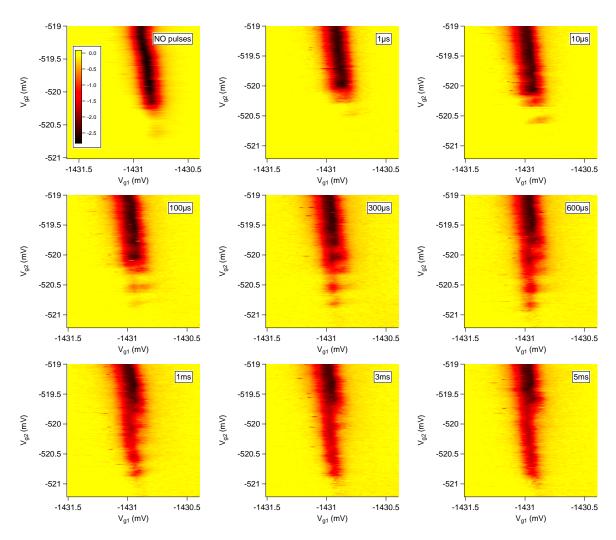

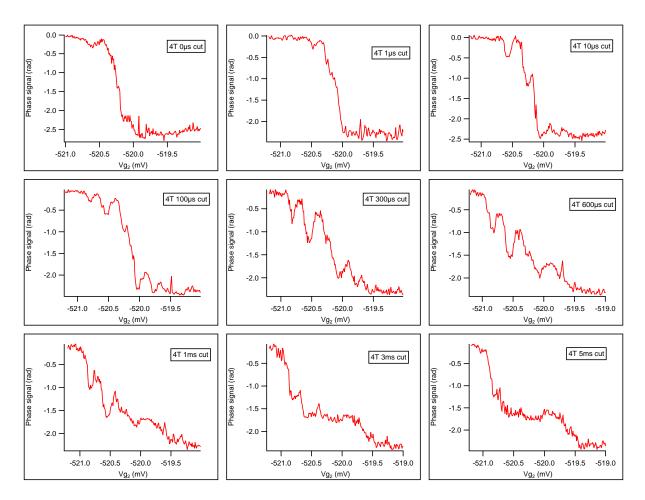

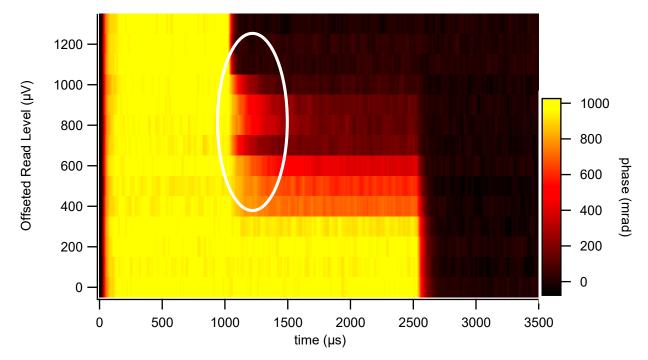

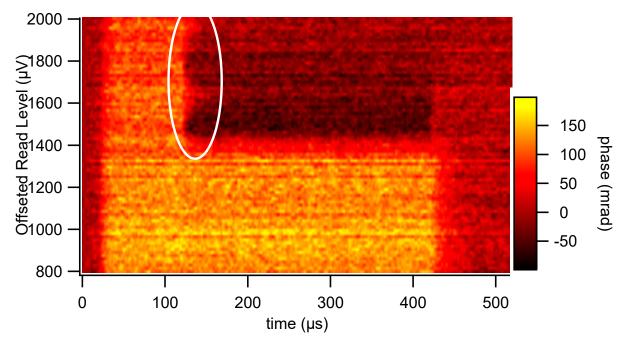

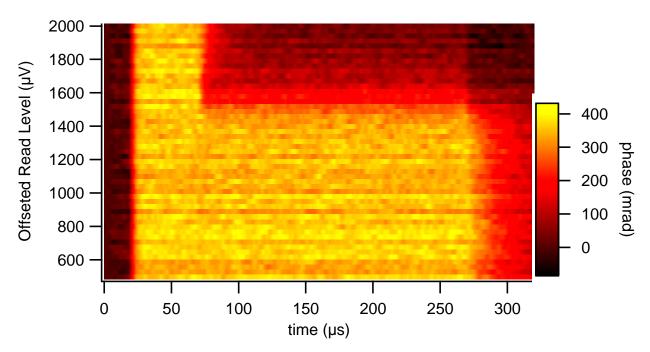

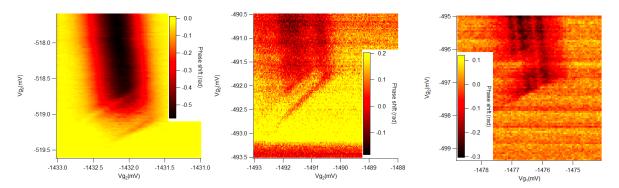

Simplified Face-to-face/parallel configuration