## Digital Implementation of Neuromorphic systems using Emerging Memory devices

Tifenn Hirtzlin

#### ▶ To cite this version:

Tifenn Hirtzlin. Digital Implementation of Neuromorphic systems using Emerging Memory devices. Micro and nanotechnologies/Microelectronics. Université Paris-Saclay, 2020. English. NNT: 2020UPAST071. tel-03245706

### HAL Id: tel-03245706 https://theses.hal.science/tel-03245706

Submitted on 2 Jun 2021

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Digital Implementation of Neuromorphic systems using Emerging Memory devices

#### Thèse de doctorat de l'université Paris-Saclay

École doctorale n°575: Electrical, Optical, Bio-Physics and Engineering Spécialité de doctorat:

> Electronique et Optoélectronique, Nano-et Microtechnologies Unité de recherche : Université Paris-Saclay, CNRS,

Centre de Nanosciences et de Nanotechnologies, 91120, Palaiseau, France.

Référent : Faculté des sciences d'Orsay

Thèse présentée et soutenue à Palaiseau, le 18/11/2020, par

## Tifenn HIRTZLIN

#### **Composition du Jury**

#### **Delphine MARRIS-MORINI**

Professeure, C2N, CNRS, Université Paris-Saclay

#### Ian O'CONNOR

Professeur, École Centrale de Lyon, Université de Lyon

#### **Benoît MIRAMOND**

Professeur, LEAT, Université Côte d'Azur

#### **Olivier SENTIEY**

Professeur, ENSSAT, Université de Rennes 1

#### François ANDRIEU

CEA-Leti, Université Grenoble-Alpes

#### Jean-Michel PORTAL

Professeur, IM2NP, CNRS, Aix-Marseille Université

#### Rapporteur & Examinateur

Présidente

Rapporteur & Examinateur

#### Examinateur

Examinateur

Examinateur

#### **Damien QUERLIOZ**

C2N, CNRS, Université Paris-Saclay

#### Marc BOCQUET

Professeur, IM2NP, CNRS, Aix-Marseille Université

#### Directeur de thèse

Invité

## Acknowledgements

The research results being presented here would not be what they are without the help of a large number of people whom I would like to thank for their involvement, enthusiasm, help, and advice.

First and foremost, I would like to sincerely thank Prof. O'CONNOR and Prof. MIRAMOND for their careful study of the manuscript and the time spent in writing their pre-submission report. I am also grateful to the examiners of the jury who devoted time to read this document for the defense. I have a special thought for Delphine, who advised me in my choice of orientation in the Master Nanosciences program at the University of Paris-Saclay she coordinates with Arnaud, as well as in my first research internship where I was able to approach the world of research for the first time.

I would also like to thank very warmly Jean-Michel and Marc who were almost my thesis co-supervisors. I was able to exchange new ideas, discuss, and of course, work hand in hand to both design this magnificent Bayesian circuit and to have been able to test it in Marseille despite a very unfavorable context. I have always truly enjoyed working with you and I hope to continue in the future with exciting joint projects.

Of course, I am extremely grateful to Damien for all the time devoted to my thesis, the resources given to bring all these projects to their fruition, and the advice and exchanges that were numerous during these three years. I can say that I couldn't have dreamed of a better thesis supervisor, he was always there, was able to push for the completion of the projects. Damien is not only a brilliant scientist with incredible knowledge, but he is also able to tackle new research topics very quickly to advise his students. The research group, as well as the different collaborations you have been able to set up, is extraordinary. As soon as I arrived in the group for my internship I felt in your team like in a family! For that, I thank Adrien, Damir, Alice, Chris, and Nicolas who welcomed me, made me feel at home, and also gave me the first advice for the research. Adrien taught me electronics from the bachelor's degree and he is one of the people who contributed to the special affection I have for the field. The brainstorming with Damir on the board in our office in building 220 will remain etched in my memory. Alice, whom I was able to work with to bring to fruition this magnificent project of population coding of super-paramagnetic junctions, as well as your involvement in the organization of collaborative meetings between the C2N and the CNRS-Thales. And Chris and Nicolas with whom I was also able to exchange. I hope to meet you again soon, Chris in Albuquerque if I ever pass by and Nicolas in Palaiseau and for sure I will pass by there often.

Then I would like to thank all the members of the IntegNano team, first of all, Maxence with whom I started my thesis and who is someone I care about, both for the scientific exchanges (sometimes a bit rough because we don't always agree), and from a friendly point of view, we could share very nice moments (I will always remember the missed boat in Roscoff after a jog around the island of Batz because you wanted to drink a coke!).

Next, I would like to thank Axel for his enthusiasm and his ability to tackle a variety of subjects. In the beginning, you were doing micro-magnetic simulations, then you had to do clean room and manufacturing, but in the end, given all the problems in the lab, you were able to tackle different subjects. I almost feel like you were there at the beginning of my thesis, your presence is so calming.

Thanks also to Bogdan, who was able to get the group to adopt the Deep Learning tools to the whole team, your arrival in the group did a lot of good to modernize the tools. But also for your friendliness, your fruitful exchanges, your critical and constructive remarks as well as the sharing of your innovative ideas. I enjoyed working with you.

I would also like to thank the new generation of doctoral students on the team. Kamel is an extremely calm and nice person, able to take the deadlines without too much stress while the whole team seems to be in a panic. I thank you very much for the work you have done for the design of the Bayesian chip, it is largely thanks to you that this chip could be designed. I also thank you for the soccer games that we've been able to play recently, it was a great time for me and it allows us to create moments with the members of the group. Atreya, I also thank you for the exchanges we had, the very interesting discussions, and I trust that you will take over the learning of binarized neural networks, it is a project I deeply believe in and I am sure that you will be able to carry it through to the end. Xing, you are brilliant, I wanted to thank you, I believe very much in the project you are doing, I think you don't realize the impact of your work but these are extremely important results that will have a huge impact in the field of numerical simulations in the whole field of physics! I also hope we will have the opportunity to share a moment to play table tennis or badminton soon! Clément, you are starting your thesis with a great team and I hope that you will take care to maintain this family atmosphere. With Kamel, you're taking over the chip design, and I think you make a great team for the next tap outs. I'm looking forward to seeing your next projects, which I'm sure will be very interesting.

More generally, I would like to thank all the other people on the team with whom I was able to interact. Mamour, we will surely have the opportunity to meet again since we will both work in the same institution. At both ends of France but I'm sure we will meet again! Thanks also to Liza, I am happy to have been able to discuss with you, and congratulations for all that you do both in the laboratory but also for your beautiful paintings which I am a big fan of.

Many thanks also to Julie and her entire team. Students, doctoral and post-doctoral students should be happy to have her as a supervisor. I have enjoyed interacting on the many occasions that have been joint meetings, conferences, and events such as BioComp. This stay

in Roscoff was for me the best opportunity to get to know the field of Neuromorphic, with an unequaled quality of speakers, a perfect organization which will remain a reference for me. I am also impressed by Julie for her vision of the field, her knowledge, her talents in writing papers, and above all her ability to identify an extremely innovative research topic and bring it to fruition. The collaboration of your CNRS-Thalès team with Damien's group is truly exceptional and very unique with a very high international reputation. I hope to have other opportunities to collaborate in the future.

I would also like to thank Dafiné Ravelosona, Jacques-Olivier Klein, Laurie Calvet, Nicolas Vernier, Rohit Pachat, Subhajit Roy, Guanda Wang, Guillaume Hocquet, Gyan van der Jagt, Marie Drouhin for the different discussions we had.

I would also like to thank Elisa Vianello for her help in getting the MAD 200 technology and for taking me on a postdoc in Grenoble, I'm sure we'll do great projects together.

A big thank you also to the entire Hawai.tech team for their discussions about the BM1: Pierre Bessière, Emmanuel Mazer, Jacques Drouez, Raphael Laurent, Raphael Frish, Marvin Faix, Karim Cherkaoui and Jean Simatic.

I would also like to thank all my friends who made me think of something else during my thesis, but especially the Triad: with Anthony and Amaury that support me for many years now, as well as the members of my athletic club that I leave with felt of pinching with the heart but for new adventures in Grenoble.

I would also like to thank my friends from the Master Nanosciences, Pierre, Léa, Raquel for the all-you-can-eat sushi dinners.

Finally, I would like to thank my family and especially my mother who has always been there to guide me in my orientation for my studies and who has always pushed me and my brothers to work. Also, my father who gave me a computer with internet, relatively young, in a naive way maybe but in the end, it didn't have so many drawbacks. Also for giving me the taste of the sport.

My two little brothers as well, Killian who has changed a lot and is now extremely accomplished and still has the smile and the word for laughs. My little Quentin with your big heart and a lot of sensitivity has also changed now that you have big biceps. I am really lucky to have you.

Finally, I would like to thank from the bottom of my heart my little Laura who supported me throughout my thesis and even before, and to all your family that I love, especially your father Laurent for the trail jog. Laura, you have changed me, I am happy to live with you and to start a new life in Grenoble made of nature and sport!

## **Contents**

| In | trod | uction                                                                 | 1  |

|----|------|------------------------------------------------------------------------|----|

| 1  | The  | brain as an inspiration                                                | 5  |

|    | 1.1  | The fundamental limitations of Electronic hardware                     | 6  |

|    | 1.2  | Advancing electronics another way: enhance communication               | 10 |

|    | 1.3  | The special case of memory                                             | 14 |

|    | 1.4  | Integration of Non-Volatile-Memory (NVM) for In-Memory Computing (IMC) | 20 |

|    | 1.5  | Bridging the gap between memory and computing                          | 24 |

|    | 1.6  | Existing implementation of neuromorphic hardware                       | 29 |

| 2  | Low  | Energy Inference Neuromorphic System                                   | 37 |

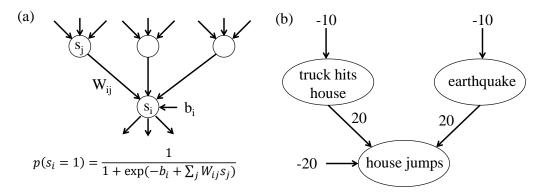

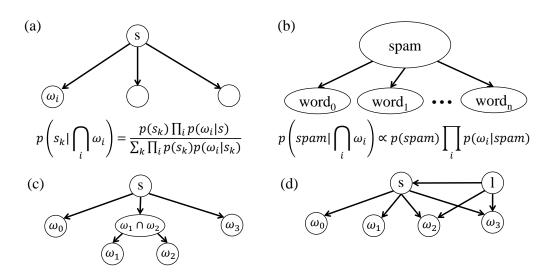

|    | 2.1  | Bayesian principle                                                     | 39 |

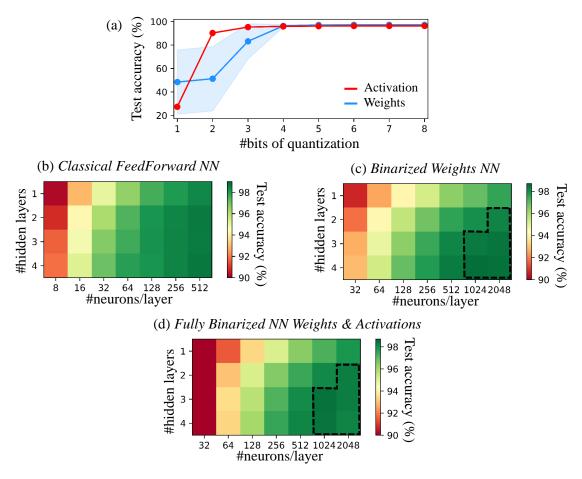

|    | 2.2  | Quantization of Neural Networks                                        | 43 |

|    |      | 2.2.1 Neural Networks : background                                     | 43 |

|    |      | 2.2.2 Reducing the resolution of neural network                        | 46 |

|    |      | 2.2.3 Binarized Neural Network                                         | 48 |

|    |      | 2.2.4 Quantized and Binarized Neural Network: a comparison             | 50 |

|    |      | 2.2.5 Specificities of Binarized Neural Network                        | 51 |

|    | 2.3  | Connection between Bayesian Reasoning and Neural Network               | 52 |

|    | 2.4  | Emerging memory devices for NN and Bayesian models                     | 54 |

| 3  | Har  | dware implementation of Bayesian Machine                               | 57 |

|    | 3.1  | Theoretical Bayes Inference                                            | 58 |

|    | 3.2  | Naive Bayes Assumption                                                 | 62 |

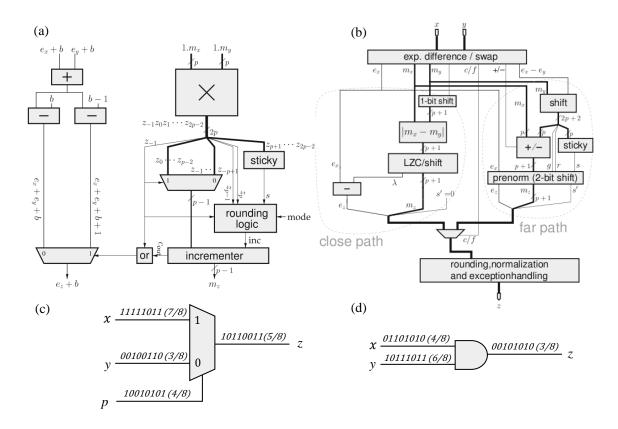

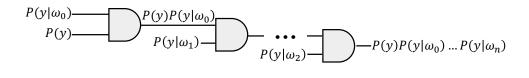

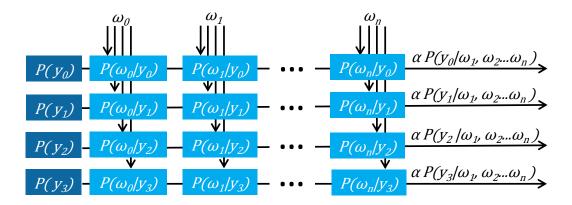

|    | 3.3  | Computing Bayesian Inference with Stochastic Computing                 | 64 |

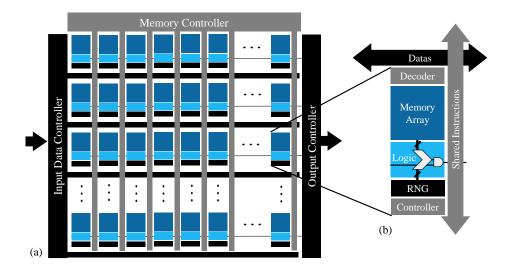

|    | 3.4  | The Bayesian Machine: hardware description                             | 68 |

|    |      | 3.4.1 General overview of the Architecture                             | 68 |

|    |      | 3.4.2 Global Architecture                                              | 71 |

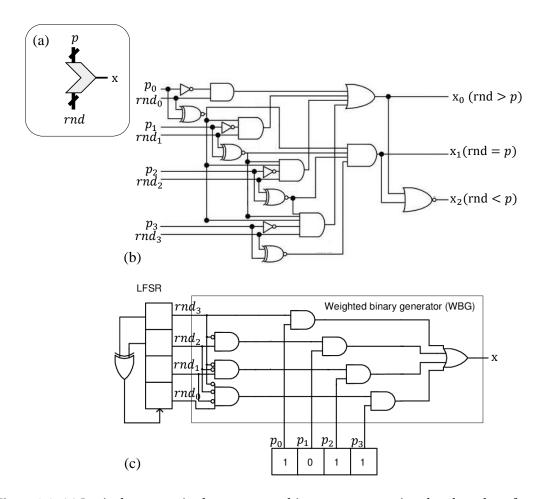

|    |      | 3.4.3 Random Number Generator                                          | 72 |

|    |      | 3.4.4 Weighted Binary Generator                                        | 73 |

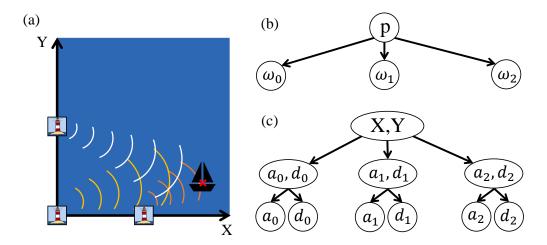

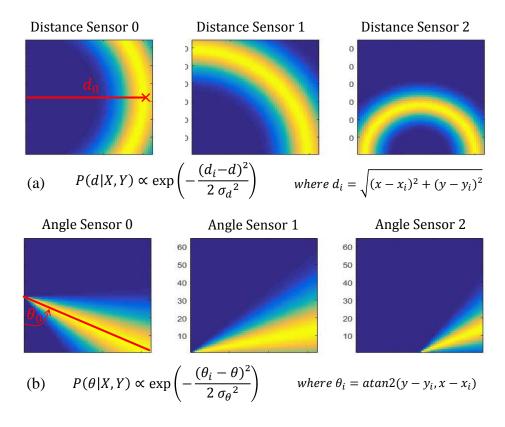

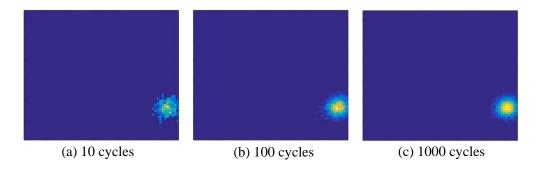

|    | 3.5  | The boat localization example                                          | 74 |

VIII CONTENTS

|   | 3.6 | The final Chip Design with RRAM                                                  | 77  |

|---|-----|----------------------------------------------------------------------------------|-----|

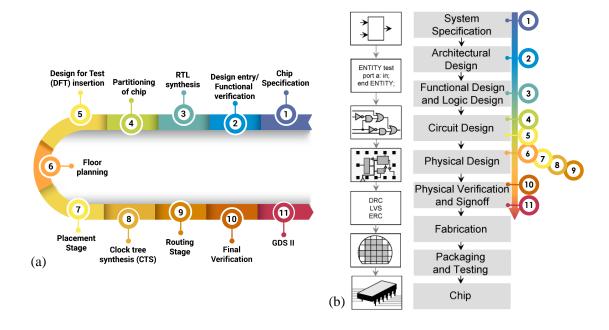

|   |     | 3.6.1 The Design Flow                                                            | 78  |

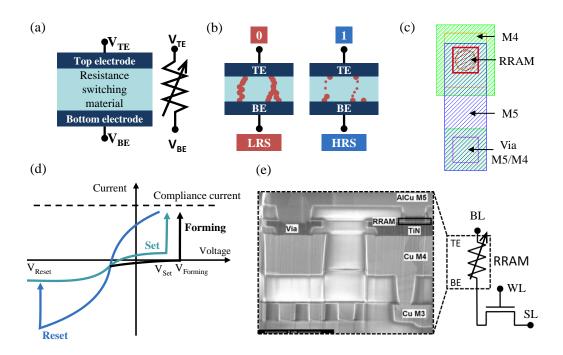

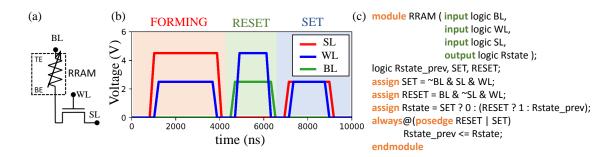

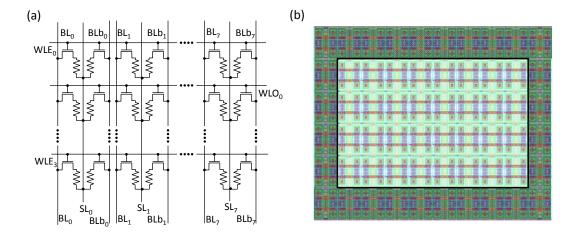

|   |     | 3.6.2 The RRAM memory array                                                      | 79  |

|   |     | 3.6.3 Digital Logic Blocks                                                       | 86  |

|   |     | 3.6.4 The Bayesian Machine full architecture                                     | 87  |

|   |     | 3.6.5 Final Design and small array test structures                               | 89  |

|   | 3.7 | Conclusion                                                                       | 90  |

| 4 | Har | rdware implementation of Binarized Neural Networks                               | 93  |

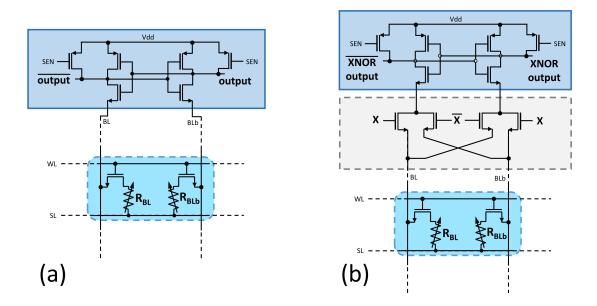

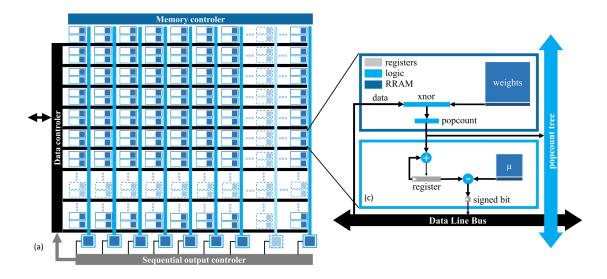

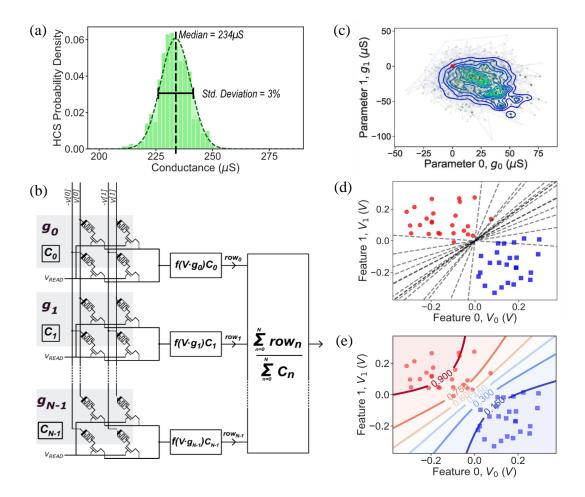

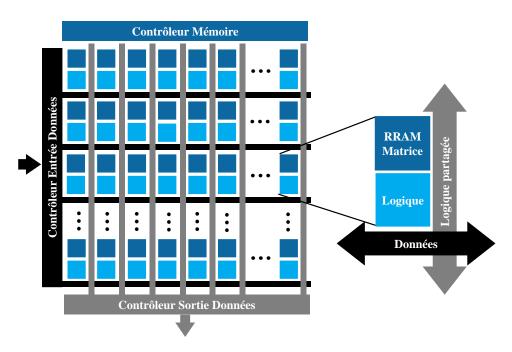

|   | 4.1 | Differential Memory Array for In-Memory Computing                                | 97  |

|   | 4.2 | Design of In-Memory Binarized Neural Network Based on the Differential Mem-      |     |

|   |     | ory Building Block                                                               | 100 |

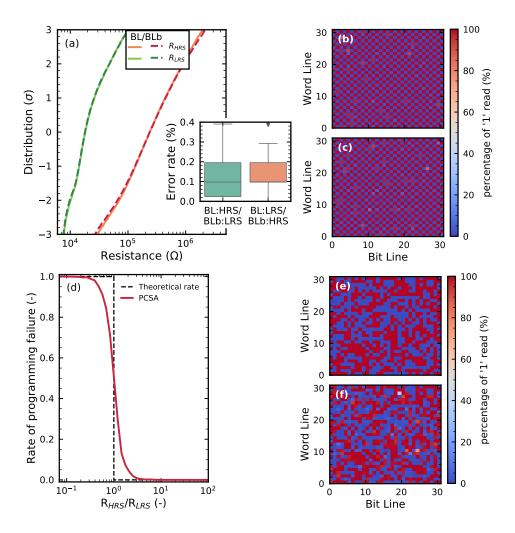

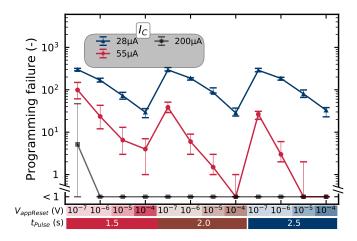

|   | 4.3 | Memory Operation at Reduced BER                                                  | 104 |

|   | 4.4 | Do All Errors Need to Be Corrected?                                              | 109 |

|   |     | 4.4.1 Impact of Errors on Binarized neural Network performances                  | 109 |

|   |     | 4.4.2 Reducing Error Impact using adapted learning                               | 111 |

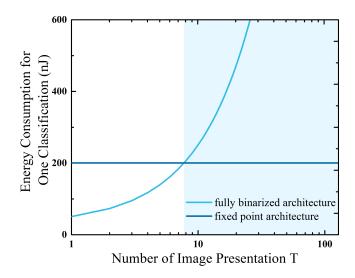

|   | 4.5 | Projection at the System Level                                                   | 112 |

|   |     | 4.5.1 Impact of In-Memory Computation                                            | 112 |

|   |     | 4.5.2 Impact of Binarization                                                     | 112 |

|   |     | 4.5.3 Comparison with Analog Approaches                                          | 113 |

|   |     | 4.5.4 Impact in Terms of Programming Energy and Device Aging                     | 114 |

|   | 4.6 | Stochastic Computing for Binarized Neural Networks                               | 115 |

|   |     | 4.6.1 Background                                                                 | 115 |

|   |     | 4.6.2 Stochastic Computing with Regular Training Procedure                       | 116 |

|   |     | 4.6.3 Adapted Training Procedure                                                 | 117 |

|   |     | 4.6.4 Energy and Area, comparison using stochastic computing                     | 117 |

|   |     | 4.6.5 Partially Binarized Convolutional Neural Network                           | 119 |

|   | 4.7 | Conclusion                                                                       | 120 |

| 5 | Sto | chastic components                                                               | 123 |

|   | 5.1 | Stochastic device behaviours for MCMC Sampling                                   | 124 |

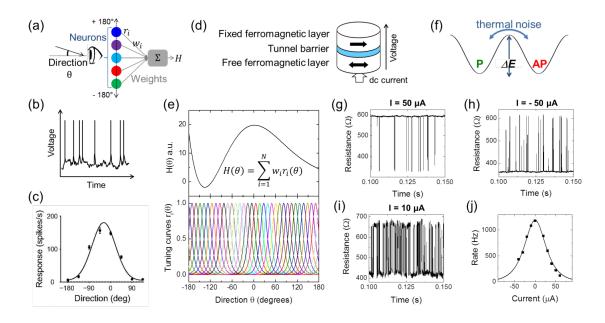

|   | 5.2 | Neural-like computing with populations of superparamagnetic basis functions $$ . | 127 |

|   | 5.3 | Tuning curve of a superparamagnetic tunnel junction                              | 129 |

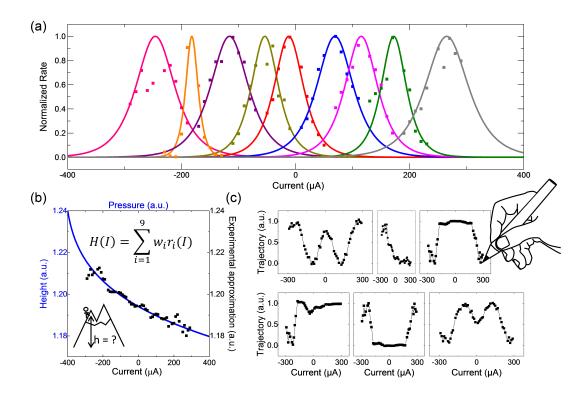

|   | 5.4 | Population coding with superparamagnetic tunnel junctions                        | 130 |

|   | 5.5 | A computing unit that can learn                                                  | 133 |

|   | 5.6 | Design of the full system                                                        | 137 |

|   |     | 5.6.1 Methods                                                                    | 138 |

|   |     | 5.6.2 Results                                                                    | 139 |

|   | 5.7 | Discussion                                                                       | 140 |

CONTENTS ix

| 6  | Ana   | log RI | RAMs                                                                  | 143 |

|----|-------|--------|-----------------------------------------------------------------------|-----|

|    | 6.1   | Terna  | arized Neural Network                                                 | 144 |

|    |       | 6.1.1  | Using the same amount of device to implement ternary synapse without  |     |

|    |       |        | memory overhead                                                       | 145 |

|    |       | 6.1.2  | Binarized Neural Network vs Ternarized Neural Network                 | 147 |

|    | 6.2   | Syna   | ptic Metaplasticity in Binarized Neural Networks                      | 148 |

|    |       | 6.2.1  | Catastrophic forgetting                                               | 148 |

|    |       | 6.2.2  | Interpreting the Hidden Weights of Binarized Neural Networks as Meta- |     |

|    |       |        | plasticity States                                                     | 149 |

|    |       | 6.2.3  | Learning two tasks with Metaplastic Binarized Neural Networks         | 150 |

|    |       | 6.2.4  | Metaplasticity using emerging nanodevices                             | 151 |

|    | 6.3   | Hybr   | id Analog-Digital Learning with Differential RRAM Synapses            | 152 |

|    |       | 6.3.1  | Principle of learning                                                 | 152 |

|    |       | 6.3.2  | A 2T2R complementary programming strategy                             | 154 |

|    |       | 6.3.3  | Reprogramming check strategy to avoid saturation                      | 156 |

|    |       | 6.3.4  | Device simulation                                                     | 157 |

|    |       | 6.3.5  | Device imperfection, impact on accuracy                               | 159 |

|    |       | 6.3.6  | Benefits of Operating in a Weak RESET Regime                          | 160 |

|    |       | 6.3.7  | Comparison with other approaches for RRAM-Based Learning              | 161 |

|    |       | 6.3.8  | Next requirement for a final on-chip learning implementation          | 162 |

| Co | onclu | sions  | and future work                                                       | 167 |

| Li | st of | public | eations                                                               | 173 |

| Aį | pen   | dix A  | Link between neural network and Bayesian models                       | 177 |

| Aį | pen   | dix B  | Practical example                                                     | 181 |

| Aį | ppen  | dix C  | Synthèse en Français                                                  | 187 |

| Bi | bliog | graphy |                                                                       | 226 |

## Introduction

"Listen to the technology; find out what it's telling you."

$Carver\ M \ EAD\ "Steve\ Jobs \ and\ the\ Economics\ of\ Elitism"\ by$   $Steve\ Lohr,\ in\ NY times,\ January\ 30,\ 2010.$

"The digital revolution of the 21st century has profoundly changed society. Access to information is now extremely easy, telecommunications are extremely efficient, and today's computing capacities are such that they are an indispensable tool for almost everything, including scientific research."

2 INTRODUCTION

HILE electronics has prospered inexorably for several decades, its leading source of progress will stop in the next coming years, due to the fundamental technological limits of transistors. However, the current state of microelectronics is not entirely satisfactory. Today, we can build extremely powerful computers, very flexible in the tasks that they can solve, but they are far from optimal in terms of energy. Smartphones are more powerful than the computers of the 90s, but their energy autonomy is relatively limited: one to two days of battery life without intense use. To add new interesting features to today's electronic circuits, it is necessary to increase their computing efficiency.

In particular, performing tasks for the Internet of Things (IoT) using extremely low energy is an exciting challenge. The number of potential applications is considerable: all the wearables and connected objects in the IoT are concerned. One of the most exciting applications concerns brain-computer interface and implants. Such types of equipment have some practical and useful applications in medicine for rehabilitation with intelligent prostheses, post-hospital monitoring at home, prevention for aged people, detection, and care for epileptic seizures, strokes, heart attacks, etc.

Currently, to have such services, data transfer through the Internet network is required, but it raises many issues:

- The energy consumption is very high.

- The reduced mobility when there is no signal.

- Privacy issues (Data on users may be collected).

- Security concerns (data manipulation, denial of service attack...).

To overcome all these challenges, a solution is to work at the edge, i.e. with autonomous and intelligent equipment. Therefore, electronics has to be able to meet all the constraints of embedded systems in terms of weight, size, integration of sensors, on-chip memory, and being able to process on-chip data with very low energy. Unfortunately, so far, running artificial intelligence algorithms required a high computing power which resulted in large energy consumption. A very important part of this energy consumption using classical computer architecture is due to the data exchange between the memory and the computation, conceptually, and physically separated. We might believe that continuous progress in microelectronics will enable the design of low energy circuits able to run such algorithms, however, we are coming to the end of Moore's law, which has governed the scheme of scaling Complementary Metal-Oxide-Semiconductor (CMOS) transistor size year after year.

Nevertheless, microelectronics is currently offering a major breakthrough: in recent years, memory technologies have undergone incredible progress, opening the way for multiple research venues in embedded systems. Additionally, a major feature for future years will be the ability to integrate different technologies on the same chip. For this reason, in this thesis, we explore the use of new emerging memory devices that can be embedded in the core of the CMOS, such as Resistive Random Access Memory (RRAM), Spin Torque Magnetic Tunnel Junction (ST-

INTRODUCTION 3

MTJ) memory, based on naturally intelligent in-memory-computing architecture.

In this thesis, inspired by neuroscience research and taking into account the latest advances in artificial intelligence, we have designed a hybrid RRAM/CMOS circuit implementing algorithms for In-Memory-Computing. Three brain-inspired algorithms are carefully examined: Bayesian reasoning, binarized neural networks, and an approach that further exploits the intrinsic behavior of components, population coding of neurons.

The first chapter of the thesis is introductory. We discuss the many opportunities available from a technological perspective for embedded system: first, we present the main limitations of today's electronics and then we investigate what are the new emerging memory technologies and what they enable. We also explore potential next developments of In-Memory-Computing using these memory devices, including those of bio-inspired algorithms and the recent literature on neuromorphic electronics.

The second chapter defines the differences and links between Bayesian models and neural networks, as well as some ideas about the importance of a hardware implementation of these models using innovative memory components.

The third chapter presents both a detailed presentation of a Bayesian inference algorithm, and more importantly, a complete description of the implementation of an In-Memory-Computing hybrid CMOS/RRAM chip (from the algorithm to the tape out) designed during this thesis.

Similarly, Chapter 4 focuses on the hardware implementation of an inference algorithm, this time based on neural networks. An in-depth study of the impact of the properties of memory devices is presented, in particular, the effect of errors on system performance.

To go even further in the use of memory devices, Chapter 5 presents how the stochastic character of magnetic tunneling junctions can be used to reproduce the population coding of neurons in the brain.

Finally, the chapter 6 shows how to go further in the use of the complex behaviour of memory devices. We mention our latest advances in the use of these memory devices, where we aim at developing new algorithms related to devices behaviour and/or adapt classical machine learning algorithm existing in the literature to hardware constraints.

## Chapter 1

# The brain as an inspiration for the future of electronics.

It would appear that we have reached the limits of what it is possible to achieve with computer technology, although one should be careful with such statements, as they tend to sound pretty silly in 5 years.

John Von Neumann in 1949

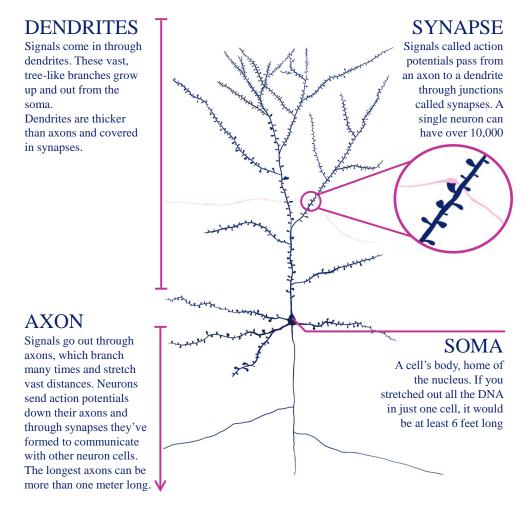

FROM the first computer to the present day, the evolution of the performance of electronic circuits has followed a major rule: improving the performance of transistors. Even if this component is extraordinary, because when its dimensions are reduced all its characteristics are improved, this rule is at its limits. Today, many nanotechnologies with exciting characteristics are emerging and their use can solve some of the limitations of transistors. One route of research to use them efficiently is the inspiration of the biological brain, which is composed of a very large number of complex features and which allows accomplishing complex and varied tasks."

ELECTRONIC chips are no longer extraordinary products as in our daily lives, electronic is present everywhere, in our cars, our coffee machines, our fridges, not to mention our telephones, which are almost a physical extension of ourselves. The large amount of data they provide requires processing, analysis, and decision-making. Advances in telecommunications have enabled massive data transmission over the cloud involving data centers where the data is processed. Even if new telecommunications technologies try to provide technical answers to the energy consumption of networks and the Internet of Things (IoT), energy consumption due to data sent by IoT will remain a major issue. Without a very large battery capacity, it is not certain that they will have a long autonomy.

Another approach would be to limit the data transmitted, so that only those data that are truly necessary would be transferred. Such an approach consists of integrating native intelligence into systems in order to select important information. But this data analysis is challenging; indeed, to be truly interesting, the associated energy consumption has to be lower than the energy consumption related to communication.

For now, electronic circuits have not been designed for this purpose. From the most complex computer to the smallest microcontroller in a watch, the operating principle remains the same. Rethinking the computer architecture paradigm is an opportunity to answer to some issues of modern electronics.

In this chapter, we will begin by detailing how the operating principles of today's electronics are coming to the end, detailing its limits, and how to reduce energy consumption by working on both technology and architectural level. We will highlight the important role of memory for the future of electronics by presenting bio-inspired architecture where memory plays a crucial role, in the brain.

#### 1.1 The fundamental limitations of Electronic hardware

In 1960, at the Bell Lab, the first MOSFETs (Metal-Oxide-Semiconductor-Field-Effect-Transistors) were invented [1]. This invention paved the way for a great adventure with the beginning of modern electronics. Between the first microprocessors composed of a few thousand transistors and today's multi-billion transistors [2], the implementation procedures are quite different. Today, highly complex tools are employed to be able to integrate all these transistors [3], but also because the constraints of today's technologies are much more demanding than in the past [4], when a design could be done by hand. At the same time, system architectures have become more and more complex, and most of them are owned by large companies that have been working on successful system architectures for decades with thousands of engineers.

Currently, from server and personal computer, to mobile processors, electronic circuits have reached incredible performance. It is possible to perform simulations extremely quickly and at low cost, to play video games with exceptional graphic quality even on mobile phones, to do augmented/virtual reality with VR headsets only limited by movement in a confined space.

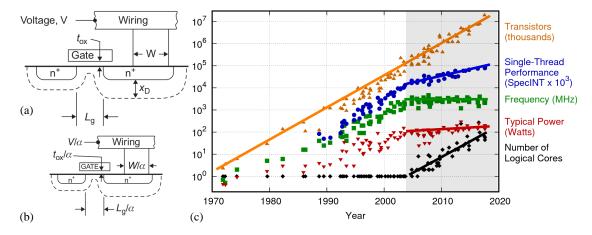

What is quite interesting is that all these advances in the field of electronics are linked to a single principle: the scaling of transistors, with the reduction of the dimension of a single transistor. The transistor scaling was theorized by Robert Dennard in the early 1970s (Figure 1.1 (a) & (b)).

Figure 1.1: Dennard scaling & Moore's law [5] adapted from [6], [7] & [8]: (a) Schematic illustration of a classic CMOS (Complementary Metal Oxide Semiconductor) Bulk transistor technology, (b) transistor following Dennard scaling –dimension reduced by factor alpha– and (c) Moore's law trend, around 2005, the Dennard scaling stops.

The operation principle of a transistor is very simple. It consists of controlling the current flowing under the gate of the transistor between the drain and the source by applying a voltage at the gate. By decreasing all its dimensions -including the thickness of the gate oxide - by a factor  $\alpha$ , and decreasing the voltage applied at the gate by the same factor, it is possible to maintain the same electric field value under the gate oxide. Since the main source of power consumption of the leak-free CMOS (Complementary Metal Oxide Semiconductor) transistors is the charging and discharging of the gate, the resulting energy consumption is  $E = CV^2$ . Likewise, with the scaling of transistors, the maximal operating frequency defined by the gate delay  $\tau = CV/I$ , with I proportional to  $(1/tox)(W/L)V^2$  is increased by a factor  $\alpha$ . Traditional scaling rules (but no longer valid), imply that the energy consumption of a single transistor can be decreased by a factor  $\alpha^3$ , the frequency increased by a factor of  $\alpha$ , the transistor density increased by a factor of  $\alpha^2$ , while keeping the power density constant. Thereby, to perform the same calculation, between 1971 and 2012, the number of transistors has not only exponentially increased, but also the individual performance of each transistor has been significantly improved. To perform the same logical operation, between 1971 and today, energy consumption is more than 400,000 times lower.

What about the coming decades? As can be seen in Fig. 1.1, a change in the scaling trends occurred in the mid-2000s as Dennard's scaling met some difficulties. The number of transistors still increased exponentially, but the operating frequency has been stuck around a few GHz. The reason for this stop in progress is the significant increase in variability, noise, and leakage of nanometer-scaled transistors. To rectify it, a simple solution has been used: reduc-

ing the supply voltage much slower than suggested by Dennard scaling. However, this trend has the consequences of increasing the temperature and, to the point that heat dissipation may no longer be possible with conventional techniques. Water cooling techniques exist but are very expensive [9]. As the size of the transistors continues to decrease, the energy density rises inexorably, until we are not able to power them anymore. However, the systems architectures are now composed of heterogeneous cores, with GPU (Graphical Processing Unit), CPU (Central Processing Unit), or more complex systems where the full architecture is not used 100% at the same time. Thus, the number of cores has been increased but most of them are used at half of their maximum performance. Remained cores will be "dark" or dimmed, this phenomenon is called Dark Silicon [10].

Despite these limitations, the electronics industry is making more and more efforts to continue to follow Moore's law with incredible sophistication of transistors [11]. The two main technologies used today to reduce transistor dimensions below 28nm are FDSOI [12] (Fully-Depleted Silicon-On-Insulator) and FinFET (Fin field-effect transistor) [13]. These two-transistor structures are very different from the classical structure of the Bulk CMOS transistor. The manufacturing techniques of these transistors is very complex, and the cost of production machinery has become extremely high [14]. Ultimately, the true limit of transistor scaling will be a physical limit. If we imagine the ultimate electronic device, it would work with a single electron. So, to make a binary switch, the state of the electron would have to be stable enough to not be activated by thermal energy. According to basic physics, a fundamental limit for this energy barrier is  $E_b = log(2)k_bT$  and is 0.003aJ at room temperature. However, following basic physical derivations, if we have 1010 devices in our microchip and we do not want errors for ten years then the energy barrier required is 0.24aJ [15]. Today, we have technologies that use around 20aJ per basic switch. Physics, therefore, allows possible improvements by a factor 100, which is not negligible, but this margin compared to the 400,000 factor that was obtained over the past 50 years.

What can we do next? The constraints that have just been set: one error every ten years among 10<sup>10</sup> devices is a minimum standard in the electronics industry, but in reality, it is extremely challenging to achieve this type of reliability, especially when it comes to memory. Already today, for many memory technologies, formal error correction algorithms are used [16]. By relaxing this constraint, performance could be much better, but system architectures were never designed to work in regimes where devices have errors. Innovative algorithms for electronics is therefore highly relevant today, with new nanodevices that promise fantastic opportunities.

Given the many limitations of competing devices, CMOS has so many advantages that finding a successor to it has never been successful. Traditionally these devices proposed as alternatives to CMOS are very complicated to use, they have a high variability, a low reliability, and are not scalable as easily as CMOS. To be useful in modern electronics, new devices must have strong qualities. They have to be competitive in terms of energy consumption or speed, but

also in slightly more diverse areas such as: a very high compactness (e.g.: nanotubes...), a complex behaviour (e.g., molecular electronics) or novel features (e.g., sensing, negative differential resistance, non volatility...). In most cases, CMOS is and will remain extremely competitive, so it is very critical before embarking on the use of new nanodevices, to understand its qualities. It is often difficult to develop devices with sufficient reliability for large-scale use. If the number of devices is very large, and a single device is defective, and this causes the entire chip to be discarded, it is certain that it will be impossible to market such a product in view of the costs involved. Adapting circuit design to system and device reliability is now essential. An example of a case study, is the retention time of memories, for 10 years retention an energy barrier 8000 times greater than a system of one hour retention is required. Working with low retention memory device would result in a much lower energy consumption. At the system level, we should consider new computational paradigms, such as approximate computing [17].

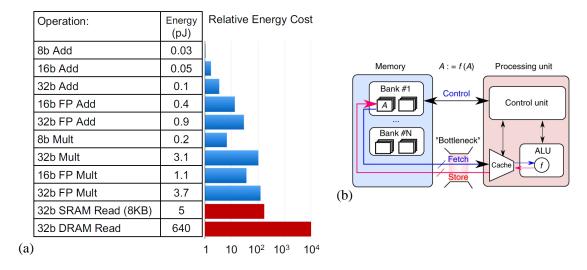

Figure 1.2: (a) Energy consumption for various operations in 45nm 0.9V CMOS technology, taken from [18], originally adapted from [19] & [20] and (b) Conventional operating principle of a processor based on the von Neumann architecture. In this type of architecture, the memory and the calculation are physically separated. A calculation operation frequires data A which is in memory, and at the end of the calculation the result f(A) will go to the same memory unit. The data therefore needs to be continuously moved back and forth between the computing unit and the memory unit, which leads to a communication bottleneck called von Neumann bottleneck. Taken from [21]

Until now, we have been talking about the power consumption of individual electrical devices, but what about the energy consumption of a whole system, for real applications? In Figure 1.2 (a), we can see the relative energy cost of various operations. An obvious observation is that the energy consumption related to the data movement is very high compared to the operations performed by transistors. When we look more closely, we can see that the dominant energy is the access to read DRAM (Dynamic Random Access Memory) data with 640pJ

for 32bit, which corresponds to the data in the central memory of a computer. This high energy consumption is related to the physical distance that separates the calculation from the memory which is considerable in comparison to the transistor level. In principle, energy consumption related to memory access would not be a concern if it did not happen very often. However, this data access is inherent to today's computer architecture, which is based on von Neumann's architecture as shown in Figure 1.2. To perform a calculation a computer needs data, e.g., if it wants to add x with y it will need to fetch the values x and y from the RAM of the computer. Then, the processing unit needs to store these data in the temporary memory called "cache memory", composed of SRAM (Static Random Access Memory) cells, in order to perform the calculation. Once the calculation has been performed, the result is returned to RAM. It is this continuous coming and going of data between different parts of the computer that is actually the dominant source of power consumption in today's computers.

## 1.2 Advancing electronics another way: enhance communication

The understanding of the high power consumption due to the physical distance between the memory and the computing cores explained in the previous section is not recent. It was already remarked in 1977 by John Backus [22]. Now, this information is therefore well known to integrated circuit designers. Despite considerable progress in reducing these data exchanges with architectures that reduce data flow by integrating more and more levels of memory cache, the energy consumption for cache access and power dissipation in electrical interconnect is still a big concern. Connections are indeed a main source of heat dissipation in electronic chips, and their scaling does not come without certain difficulties especially concerning the electric interconnects. The propagation time of a specific signal is limited by a time constant defined by the resistance and the capacity of the interconnection. When we reduce the size of a wire, the resistance increases. It means that for a wire going through the whole chip, the capacitance does not change a lot when the dimensions of the wires are reduced but the resistance is increased as well as the propagation time constant. In order to reduce the energy consumption of the connecting wires within a chip, there is a whole hierarchy of techniques from system level to circuit level [23]. Due to the use of all these techniques, the bandwidth between computation and memory is limited, which implies the use in modern computers of branch prediction [24] to speed up the execution speed of computations. This implies an important energy overhead at the computing core level since part of the performed computations is useless.

To measure the progress of future technologies, and highlight the increase importance of interconnections Wong et al. [25] propose a density metric to evaluate the performance of future developments. They propose to use a density metric that is decomposed into three parts, a transistor density DL for Logic transistor Density, DM for main Memory bit Density and DC

for main memory/logic Connection Density. In today's computers, the main memory is the DRAM, which is mainly composed of very finely integrated capacitors, but which cannot be integrated with the same manufacturing process as the computing core. So, even though both the transistor technology and the DRAM technology are very advanced the connection between the two is limited, so the margin for progress is quite large. This Logic Memory Connectivity (LMC) is very important to define the performance of a circuit. This idea is a guiding line in all our research work on neuromorphic electronics, and therefore, of this thesis.

Today, memory and computing densities are already very high, so an interesting question to ask is therefore how to improve the communication metric. In a conventional computer, a data bus allows the communication between the processor and the memory (cf. Figure 1.2 (b)). For this, the pipeline principle [26] is used, i.e., the data are not sent all at once but sequentially, which allows the calculation to be carried out even though not all the data have been received. The main reason for this sequential approach is that it allows large data processing even though the data bus is limited in size.

Moreover, in a conventional synchronous design of electronic circuit, one of the input signals is the clock that manages the other signals and their timing. The goal of this clock is to share within the circuit the same notion of time: two independent operations can be done at the same time, and then their result can be used at the next clock cycle, which allows a very good efficiency of calculation. Unfortunately, this clock, which by its nature switches continuously, is a very important source of energy consumption. The first reason is that it is always active, even when there is little or no demand on the circuit. Therefore, one of the tricks to reduce this source of unnecessary energy consumption is the use of clock gating [27]. It consists of turning off this clock signal on a part of the electronic circuit when it does not need it. The other reason for the high power consumption of the clock signal is that it has to be shared across the chip, and managing synchronization is very complex on large circuits. Indeed, two registers located at two opposite places in the chip must receive the same signal at the same time, which implies complex circuitry.

An interesting approach without clocks are asynchronous circuits [28] [29]. Asynchronous circuits do not have shared clocks. To perform calculations and communication of data, these circuits use the principle of handshaking. This communication protocol consists of communicating information between two entities by a process of waiting for a response, i.e., one entity performs an operation and transmits a control signal that tells that the calculation is accomplished. Thus, the performance of these circuits can be much higher than synchronous circuits because they are not limited to the longest critical path of the circuit. If a calculation is quick to perform, the result is quickly transmitted. Unfortunately, asynchronous circuits are difficult to design, and most of the time implies an overhead in terms of silicon area due to the handshaking implementation. Despite the growing interest in asynchronous circuits, their popularity is still limited today [30].

To improve the communication between the computing unit and the memory, it is also pos-

sible to avoid conventional communication by electronic wire. The use of light communication instead of electrical communication has been explored a lot in recent years. The growing interest in optical communications is certainly driven by the speed offered by optical fibers. Optical fibers allowed the broadband internet revolution of the 2010s. But when it comes to reducing the energy cost of long-distance communication, we are in a completely different field from the approach of reducing the energy related to communication between memory and computing. In order to replace short-range electrical communication with optics, it is not only important to have a low loss in optical communications but also to have all its devices with low power consumption such as photon generators (i.e., lasers), modulators (which convert information electrical signal into optical signal), and photodetectors [31]. Great progress has been made in this field and is starting to be commercialized but the communications that are replaced are not the ones that concern us in this thesis, in general, these optical circuits are used for communication in Datacenters [32] between the different motherboards of the different servers which are a significant source of the global energy consumption.

Optical circuits are objectively not easy substitutes for conventional electronic circuits at the transistor level. The first reason is that optical communications use waveguides that have relatively large dimensions (micrometers) compared to the dimensions of electrical communications. Nevertheless, the idea of working with silicon photonic optical circuits [33] would be very promising in the future if it becomes possible to integrate optical communications circuits closely to conventional electronic circuits. The exceptional bandwidth, multiplexing [34], and the fact that waveguides can cross each other without interfering are three properties that are largely underestimated for the future of electronics. To overcome the issue related to the size of optical waveguide, plasmonics [35] combines the qualities of both electronics and optics. The transmission losses and the difficulties to co-integrate this technology with conventional electronic are the two main issues that limit their use for the next generation of circuits.

Enhancing communications between processor and memory can be performed by reinventing communication techniques and technology. In my opinion, the idea of adding additional technology to the current CMOS technology seems very promising for future embedded systems. By pursuing this idea, we can then go further than Moore's Law.

The idea would be to reduce the energy consumption related to communication by increasing integration like Moore's law but using new technologies. This approach is therefore often called More than Moore [36]. The first benefit of using new technologies is that it adds new and complementary features to CMOS. CMOS is mostly powerful to perform simple binary operations. Even though it is possible to work with transistors in an analog regime their precision is very limited to perform real analog calculations, especially since scaling is not as easy in the analog regime. On the other hand, for features that cannot be present within a CMOS core, hybrid circuits that include several technologies with new features are a great opportunity for the future low-energy electronic circuits.

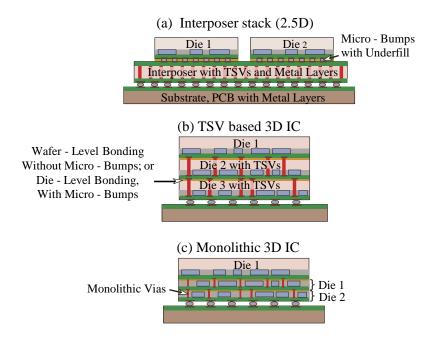

Figure 1.3: Overview of 3 different solutions to integrate different technologies on the same chip from [37] (a) Integration using an interposer, two different technologies placed side by side that communicate with each other through the interposer. Also called 2.5D. (b) 3D integration based on TSVs, the different technologies are superimposed on each other but during the manufacturing process the technologies were initially separated on different wafers, during the final assembling the TSVs pass through the whole chip to connect the different chips together. (c) Monolithic 3D integration approach, the different technologies are manufactured one after the other, there is no final assembly and the technologies are connected to each other through conventional metal connections.

In order to achieve the integration of different technologies within the same chip, different methods summarized in Figure 1.3, exist. With the advent of Through-Silicon Vias (TSVs) [38], even when manufacturing techniques are not compatible between the different technologies, 3D integration has become widely possible and is even being developed industrially. There is 3 types of 3D integration structures. The first one, often called 2.5D [39], is presented in Figure 1.3 (a) it use an interposer (i.e. an electrical connection interface) using TSVs to connect two dies together. The second one (Figure 1.3 (b)), called TSV based 3D-IC consists of directly connecting the different technologies manufactured on different dies by superimposing and connecting them using TSVs. This technique is very promising but the number of stacks is limited. First, because of the alignment problems and secondly because of the thermal heating involved by the technologies integration. The last approach, called monolithic 3D-IC or pure 3D (Figure 1.3 (c)), involves directly integrating different technologies on the same die using manufacturing processes that are compatible with each other. This technique seems to be the most appropriate, but it is the most difficult to implement, since it implies the compatibility of the different manufacturing processes. The more advanced the technologies are, the more it

becomes an issue.

While historically, memory and computing were physically very far from each other, using 3D and 2.5D integration technology has led to the emergence of High Bandwidth Memory (HBM) [40] (widely used in modern graphics cards (GPUs) [41]) where memory and computing core are very close physically. Despite recent advances in this type of integration, there remains a considerable challenge for this type of integration process, which concerns the thermal implications of such structures. In addition to the influence of temperature on its own structure, a stack of one technology can influence another stack. Despite the growing interest in 3D integration, it remains very difficult to implement. When designs are made with redundant patterns, such as memory arrays, it remains relatively simple to make designs. But when it comes to integrating different technologies with different features to perform different operations as one would do with a conventional CMOS circuit, it becomes much more complicated since there is no fully automatic placement routing flows, or they are very complex to set up. There is considerable industrial interest in 3D technologies and a lot of research is being done in this direction, but there are very important limitations for mass production. Reliability, testing possibilities, and high cost are difficulties that are rarely presented in pure academic research but are very important for industry.

To sum up, to limit the energy on communication, either we work on pure communication between the computing units, the memory, the inputs/outputs, the sensors, or we make it disappear by integrating the different technologies together as much as possible [42–44]. Especially, that it is now possible to integrate the different technologies with each other.

### 1.3 The special case of memory

Until very recently, the industry has focused on optimizing either memory technologies or high performance logic technologies independently. As these technologies have progressed, the manufacturing processes have become more complex. The monolithic 3D integration of memory with compatible high performance logic manufacturing processes is therefore very difficult. By being a little less demanding on the performance of the devices, but being able to integrate them with other devices that do not have the same function, it is possible to make very innovative chips. Some very impressive achievements have been made by research teams recently [44], and the industry seems to have embraced the importance of integration in the future chips [45, 46].

We have seen in Figure 1.2 that the communication between the CMOS computing core and the DRAM represents a large part of the power consumption in a full system. But the energy consumption of the memory in the CMOS core, i.e., for registers as well as SRAM, is also large, especially since it is used for the cache memory and is therefore very intensively used.

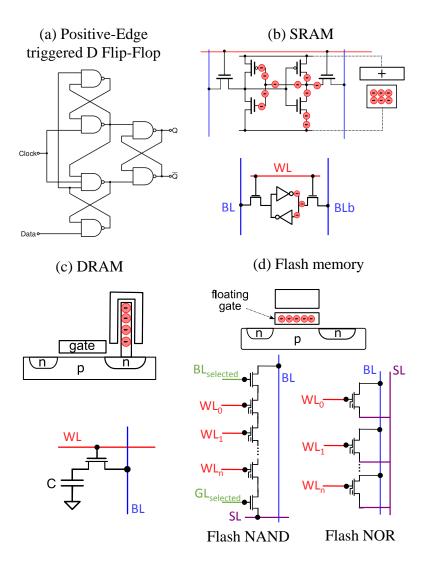

Figure 1.4: (a) Schematic of a Positive-Edge triggered D Flip-Flop acting as the classical register in CPUs, (b) Static Random Access Memory (SRAM): Two CMOS inverters connected back to back. The charge is confined within the barriers formed by FET channels and gate insulators. (c) DRAM, Capacitor connected in series to a transistor (d) Flash memory, charged are trapped in a floating gate influencing the current that flows in the transistor channel & the two configurations NAND and NOR that setup many devices.

An SRAM single array element is composed of 6 transistors (Figure 1.4 (b)): one flip-flop cell and two selecting transistors. The charge is confined in a feedback wire loop between the two barriers formed by the FET channels and the gate insulator. By contrast to a memory register, which by construction does not need a read circuit, an SRAM needs a slightly complex periphery to be read and programmed. To read an SRAM cell, the Bit Line (BL) & the complementary Bit Line Bar (BLb) are initially floating high, when the Word Line (WL) is raised. In the configuration of the Figure 1.4 (b), BLb is pulled down, and BL is pulled up, or the opposite to have the other binary value. In reality in large memory arrays, the load of the electrical wires

being relatively important, a more complex reading is implemented. It consists of charging BL & BLb to Vdd and when WL is active a slight voltage difference between BL & BLb appears and is detected by a sense amplifier. To write an SRAM as for a latch, BL is loaded to Vdd and BL to the ground or vice versa, and then WL is activated.

As shown in Figure 1.4 (c), the DRAM memory itself consists of a capacitor that stores the electrical charge rather than a feedback wire-loop connected to the drain of a transistor. It is more compact than SRAM, but slower, and needs to be refreshed regularly since reading destroys the content of the capacitance, and it is subject to capacitor leakage losses. The reading is achieved by first charging BL and then activating WL. According to the charge contained in the capacitor, a voltage change appears on BL and is compared with a voltage threshold by a sense amplifier. The SRAM manufacturing processes are compatible with high-performance CMOS, but DRAM does not have this compatibility, so DRAM is typically implemented in a dedicated chip. However, some foundries provide some embedded memory e-DRAM that can be implemented within high-performance CMOS [47, 48].

Flash memory, (Figure 1.4 (d)) relies on a special transistor, which contains an extra gate suspended in an oxide that can contain trapped charges. The reading is made by detecting the current flowing under the floating gate. When applying a voltage to the grid, if the floating gate is discharged, electrons can flow in the channel, but when the floating gate is charged, the electric field is not sufficient to let the electrons flow. Flash memories can be multilevelcell, depending on the possible level of charge in the floating gate. In this case, several gate voltages are required to sense the current. To write data, an electric current must flow between the source and the drain and a higher voltage must be applied to the control gate. Some of the electrons pass between the electrodes and will tunnel towards the floating gate, through the oxide. Erasing a cell is done in the same way, but by passing a negative voltage across the control grid. The electrons then tunnel from the floating gate to the substrate. The writing process tends to damage flash memories, resulting in a relatively low endurance. Reading is faster than writing or erasing, because the floating gate does not have to be filled or emptied with electrons.

There are two main categories of Flash memory: NAND Flash memory and NOR Flash memory, shown in Figure 1.4 (d). NOR memory is the conventional Flash memory where each device can be addressed separately; one end is connected to the source line and the other end is connected to the bit line. Flash memory is called NAND when several memory devices are connected in series. In NAND memory the access is sequential while in NOR Flash the access can be random. In modern process, the great advantage of NAND memory is that it can be stacked in 3D [49], and therefore its memory capacity is much larger than NOR Flash. In addition to being non-volatile memory, i.e., it is not erased when the power is turned off. Flash memory is an inexpensive and high-density memory. However, it has some drawbacks: an asymmetrical read/write speed performance, memory retention is poorer when its dimensions are reduced, the endurance is low, and decreases sharply when we increase the number of levels per cell.

Flash memory, therefore, requires the use of complex error-correcting codes, capable of correcting multiple errors. Finally, it is not Back-End-Of-Line compatible with high-performance CMOS core.

To work correctly a computer must continuously fetch data from memory, but this data is often very large and therefore needs to be stored in a memory space outside the computing chip, otherwise, it would saturate all the registers and the SRAM that the chip contains. Even when using the best caching strategies, a classical processor will sometimes fetch some data from the DRAM, even though it could store this data within the computing core to reuse it the next fraction of a second. The memory access speed, memory capacity, and compatibility of the technology with a CMOS core are interrelated and interdependent. The current solution is to make distinctions between each of the categories.

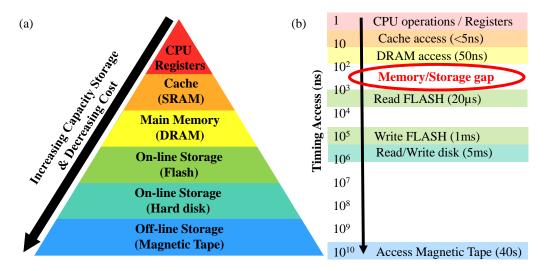

Figure 1.5: (a) Hierarchy of the different memory technologies in use today, there are two categories of memory, working memory, which is composed of registers, SRAM and DRAM, and storage memory, which is composed of flash memory, hard disks or magnetic tapes. The larger the storage capacity the lower the cost. (b) Corresponding the different memory technologies with their access and write times, it can be seen that there is a technology gap between DRAM and flash memory, and even more so if we consider writing time.

Each of these memories has different characteristics and performance, so they are not used for the same functions. The registers are very fast memories and are part of the computing core, they are used to synchronize data as well as to briefly store data between two clock cycles. The SRAM is also very fast, it is organized as a memory array, and data access is done by addressing. It is on the same chip as the computing core and is often used as cache memory to speed up data transfer between computing and DRAM. DRAM, on the other hand, is the computer's main memory, which is relatively compact and has a relatively short access time. Figure 1.5 (a) shows the memory hierarchy present in electronic computing systems and Figure 1.5 (b) highlights the access times required for different technologies. It can be seen that there is a clear

separation between two types of memory capacities, working memory and data storage, which do not have the same access times. The gap is quite clear, especially if we look at the write time of Flash memory compared to DRAM. NAND Flash can offer high-density storage, increasing as devices scale down to smaller dimensions; but while prices are dropping, the speed gap between memory and storage remains significant. Additionally, the device endurance of Flash is low and is not likely to improve.

Modern computers have long been designed to limit this constraint and hide this gap in memory access time. In data centers, the speed of DRAM and its high power consumption are a big concern, but the non-volatility of Flash memory, and its relatively long access time does not seem to be the ideal technology either. So very recently, to fill this gap in memory access time, new technologies have been explored and are now being commercialized [50]. This range of memories is called Storage-Class Memory [51]. There are a multitude of candidate technologies to fill this empty space in the memory hierarchy. The main ones are shown in Figure 1.6. These technologies come with two new features compared to DRAM: the non-volatility of the stored information and the Back-End-Of-Line compatibility. Therefore, open the way to new possibilities of circuit architecture.

The origin of these memories can be tied to the works of Leon Chia[52], who theorized a fourth elementary passive device, called the memristor M, in addition to the resistor R, the inductor L, and the capacitor C. A paper entitled "The missing memristor found" [53] published in 2008 claimed to have found this theoretical device. Many controversies appeared since theoretical guarantees were not provided [54]. There are serious doubts about the existence in the real world of the memristor as initially proposed. For this reason, we will not use this word in this thesis and prefer the more generic term resistive memory. But this is not because non-volatile memories do not correspond to the precise characteristics of an ideal "memristor" that they are not fascinating. As mentioned earlier, these memory devices are outstanding candidates to fill the gap between DRAM and storage memory. Each resistive memory technology has pros and cons and the main ones are listed in Figure 1.6.

The first memory device shown in Figure 1.6 (a) is the Spin Transfer Torque Magnetic RAM (STT-MRAM). This device consists of a free magnetic layer whose direction of the magnetization can be changed and a pinned magnetic layer which is fixed. By current injection, it is possible to detect the state of the free magnetic layer, the current being greater when both magnetic layers have their magnetization in the same direction. A spin transfer of the electrons passing through the junctions can reverse the direction of magnetization of the free layer. Before the end of the 2000's, magnetic junctions did not use spin transfer, and the direction of magnetization of the free layer had to be changed by a magnetic field, which made it poorly scalable. Today, this technology has made huge progress and manufacturing companies have their technologies ready to use [45] [46] [55].

|                       | (a) STT-MRAM                                                                                                                     | (b) RRAM<br>Filamentary / Interfacial                                                                                                                                                                  | (c) PCM                                                                                                                      | (d) FeRAM + FeFET                                                                                                                                                                        |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LRS<br>«1»            |                                                                                                                                  |                                                                                                                                                                                                        |                                                                                                                              |                                                                                                                                                                                          |

| HRS<br>«0»            |                                                                                                                                  |                                                                                                                                                                                                        |                                                                                                                              |                                                                                                                                                                                          |

| Physical<br>Principle | I polarized electrons that flow I oxygen-vacan                                                                                   |                                                                                                                                                                                                        | Phase transition between a<br>crystalline phase (low<br>resistivity) and an amorphous<br>phase (high resistivity)            | Ferroelectricity material have<br>electrical polarization in the<br>spontaneous state,<br>polarization can be reversed<br>with external electric field                                   |

| Strengths             | - Mature Technology<br>- Very fast<br>- Very good endurance<br>- Radiation-tolerant<br>- Back-End-Of-Line<br>compatible          | - Good retention at high temperature - Simple structure (low cost) - Fast & low current switching - Back-End-Of-Line compatible - Possible Co-Integration with Access Device - Possible 3D integration | - Mature Technology - Large (HRS-LRS)/LRS ratio - Good Endurance - Highly scalable - Back-End-Of-Line compatible - Very fast | - Fast - High density - High Endurance - Use of Ferroelectric for FeFET as embedded DRAM: compatible with high performance transistor - Opportunities with Ferroelectric Tunnel Junction |

| Weakness              | - High current switching - Small (HRS-LRS)/LRS ratio - Scaling strongly affect retention - Fast switching & reliability tradeoff | - Highly Immature technology - Low Endurance - Switching Reliability - Initial "forming" step - High Intra device variability                                                                          | - Power-Hungry RESET - Lower retention at high temperature - Device failure over time - Resistance Drift                     | - Destructive read<br>- Poor density<br>- FeFET low endurance like<br>flash                                                                                                              |

Figure 1.6: (a) Energy consumption for various operations in 45nm 0.9V CMOS technology, taken from [18], originally adapted from [19] & [20] and (b) Classic operating principle of a processor based on the von Neumann architecture. In this type of architecture the memory

The second category of memory shown in Figure 1.6 (b) is a oxide based resistive memory (RRAM). The basic idea is that a dielectric material, which is normally insulating, can be forced to conduct through a filament or conduction path after a sufficiently high voltage is applied. The formation of the conduction path can result from a variety of mechanisms, including defects, and metal migration. The switching process can be filamentary as well as over the entire contact surface with the electrode (interfacial). Once the device has been programmed to a low resistance, it may be reset (broken, resulting in high resistance) or set (re-formed, resulting in lower resistance) by an appropriately applied voltage. In this thesis, we will present a chip design that uses this technology using hafnium oxide (HfO2) [56].

The third technology shown in Figure 1.6 (c) is Phase Change Memory (PCM). This device is made of a nanometer volume of phase change material (that can switch between amorphous and crystalline phase) between two electrodes. The amorphous phase features a high electric resistance, while the crystalline phase is conductive. By applying a voltage to the electrodes, the increase in temperature at the material can induce a phase change, which then changes the resistance of the device.

The last memory device shown in Figure 1.6 (d) is the ferroelectric memories. Ferroelectric

memories are different from the three devices presented earlier, since to read their state, they rely on the electric charges located at the electrodes and not on the state of resistance. The circuits used for reading therefore look more like the circuits used for DRAM. The principle of FeRAM is similar to that of DRAM except that the capacitance of the device can be modulated according to the ferroelectric material state between the two electrodes of the capacitor. Due to the effect on the electric field of ferroelectric materials, it is possible to use it similarly to the flash memory at the gate of a transistor to affect on the electrons flowing under the gate: this memory device is called FeFET. There are also the Ferroelectric Tunnel Junction memories, which combine the tunnel effect with ferroelectric materials but which are still in very preliminary stages [57]. Moreover, these devices are very promising because their strong non-linearity allows matrix products to be produced without selectors [58].

## 1.4 Integration of Non-Volatile-Memory (NVM) for In-Memory Computing (IMC)

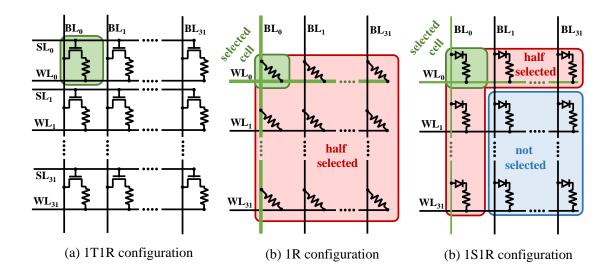

In order to integrate the different memory technologies mentioned in section 1.3, it is important to consider the method of integration, i.e., how to assemble them with each other. Since these are memory devices, it seems quite obvious at first glance to integrate them similarly to SRAM cells. In SRAM, two access transistors per bit are needed because the change of state can only be done by forcing the state of the SRAM cell from one side or the other. This constraint is specific to SRAMs and does not apply to memory devices based on their resistance state. That means that each device, needs to be only associated with one access transistor to be addressed sequentially (1T1R see Figure 1.7 (a)) to be programmed and read. It is this method that is classically used to use these devices digitally. The problem with this method is that it uses a transistor that is below the first metal level 1 to address devices that may be as high as metal level 4-5. Firstly, it means that all metal levels and transistors under the memory array are dedicated to it and therefore cannot be used for anything else and secondly, due to the dimensions of metals that increase at each level, the device itself can be smaller than the device access metal.

To increase the memory density per unit area, it is possible to do without access transistors, i.e., to design a memory array only consisting of memory devices (1R configuration 1.7 (b)). Only two levels of metals are therefore required to access the devices. To program a device, or to read it, it is enough to apply a voltage difference between the word line (WL) and the bit line (BL). Unfortunately, in this configuration, all devices will receive half of this voltage difference, which will induce leakage currents that will flow through all half-selected devices. The last configuration presented in Figure 1.7 (c) has associated a bipolar diode-type device that stops low positive and negative current, which eliminates the effects of sneak paths in a large part of the memory array. This method transfers the constraints on the manufacturing of

a selecting device other than CMOS. Many technologies are candidates and can be combined with the memory device technology [59]. Some are even already marketed by manufacturers. The technology is not public, but according to multiple news reports, it seems to be Ovonic

Threshold Switch (OTS) [60] [61].

Figure 1.7: (a) Memory cell array using 1T1R configuration, one cell gather one Transistor and one Resistor (1T1R). (b) Memory cell array without access transistor, when a voltage difference between  $BL_0 \& WL_0$  is applied, the device in green is programmed put all the other also receive a voltage difference (c) Configuration which associates a resistor with a selector, avoiding sneak paths (1S1R).

Given the advance of memory technologies, which now seems inevitable, it is fascinating to wonder what they can allow us to achieve from a system point of view. First, as we have seen, these memories can be very densely integrated within a CMOS core. It is therefore possible to envision systems that rely much more on memory.

First, an advantage of the new memory devices that are shown in Figure 1.6, is that they are non-volatile, whereas all memories that are usually used in processors are volatile. This feature offers possibilities to replace some memory registers with non-volatile ones [62] [63]. The possibility of using this non-volatility to replace registers may seem a little curious for today's architectures as these registers are continuously loaded. In reality, for many applications, –e.g. low utilization processors in satellites– these registers are not so much used, and finally maintaining the data in the register that needs to be continuously supplied with power can be an issue. A trade-off between the on-time and off-time of a register may therefore require the use of non-volatile memory within the CMOS itself for applications using a classical von Neumann architecture [64].

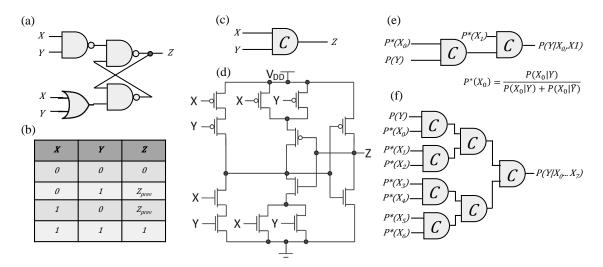

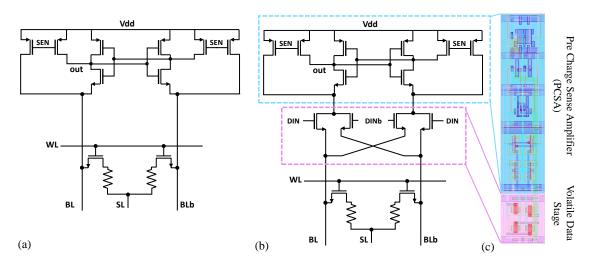

The possibilities offered by such memory devices are not only related to the registers or memories classically found in a processor. It is also possible to perform operations directly with these memory devices. The first method for performing calculations with memory devices is to use the read circuit of the binary value of the memory device and to augment it with logic functions. A circuit classically used to know the binary value of a memory device is a PCSA (Pre-Charge Sense Amplifier) [65]. The difference in resistance between two memory devices is detected using this PCSA circuit. In fact, it resembles to a pre-charged SRAM cell, which is configured in such a way that, depending on whether the current is higher in one branch or another, the SRAM cell ends up in one state or another. By adding transistors in the different branches where the memory devices are located, it is possible to perform resembles between the binary value stored in the memory and an input logic value [66]. The detailed operating principle and the circuits will be presented in detail in the chapter 4 of the thesis, since they are basic elements of our research.

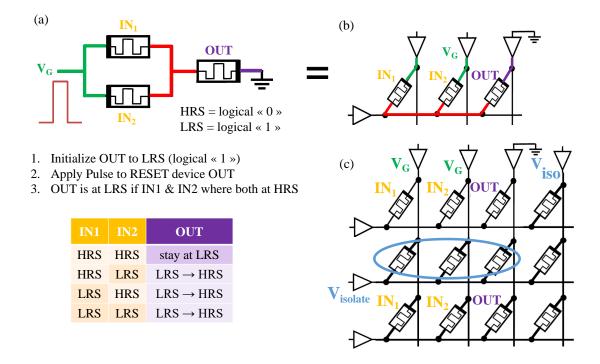

Figure 1.8: (a) Basic element of Memristor-Aided Logic, first the output memory device is initialized to low resistance state coding for a logical "1" then a pulse  $V_G$  is applied at the input of the gate which is such as it is able to RESET to high resistance state. If the two devices IN1 & IN2 are at high resistance state the main voltage difference is seen by the device two input devices and then the device is kept at LRS, otherwise if IN1 or IN2 is at low resistance state, the current mainly flow throw LRS devices and then the device OUT see the voltage difference and is RESET to HRS. (b) Same basic element but arranged in such a way that it match a memory array. (c) Full Memory Array with Magic basic element, to perform the NOR operation an isolation voltage is applied. The devices circled in blue do not see any voltage difference. Adapted from: [67]

The second method using memory devices for the calculation aims at relying only on mem-

ory devices without any CMOS overhead. The inventor S. Kvatinsky of this principle describes it as true In-Memory-Computing, in the sense that all operations are done only with memory devices. The operating principle is based on the memory arrays previously shown in Figure 1.7, but the logical inputs and outputs of the system are directly the resistance values stored in the memory devices. This method is called Memristor Aided LoGIC (MAGIC) [67]. The logical inputs and outputs of the system are directly the resistance values stored in the memory devices.

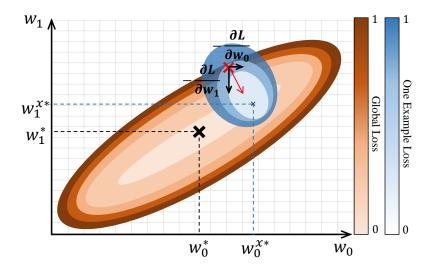

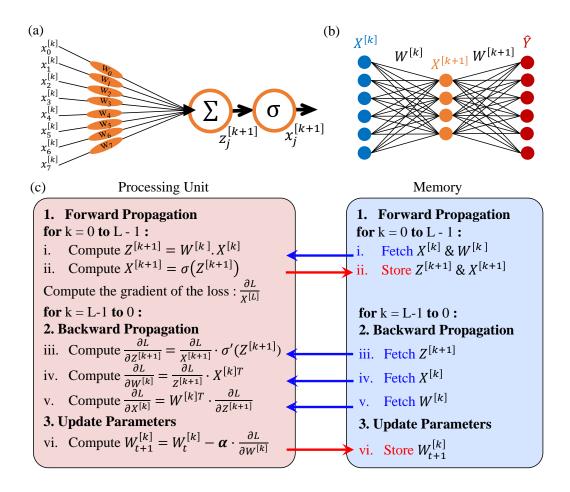

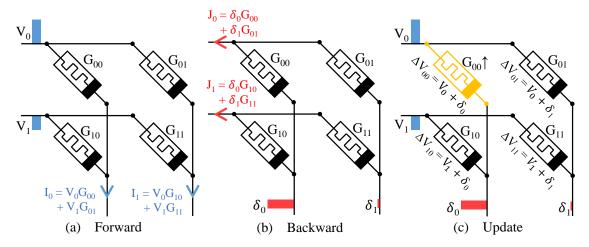

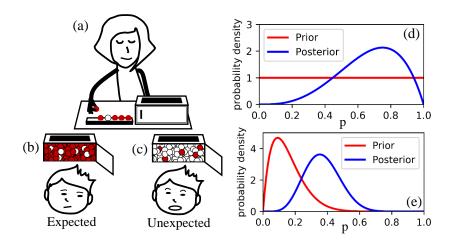

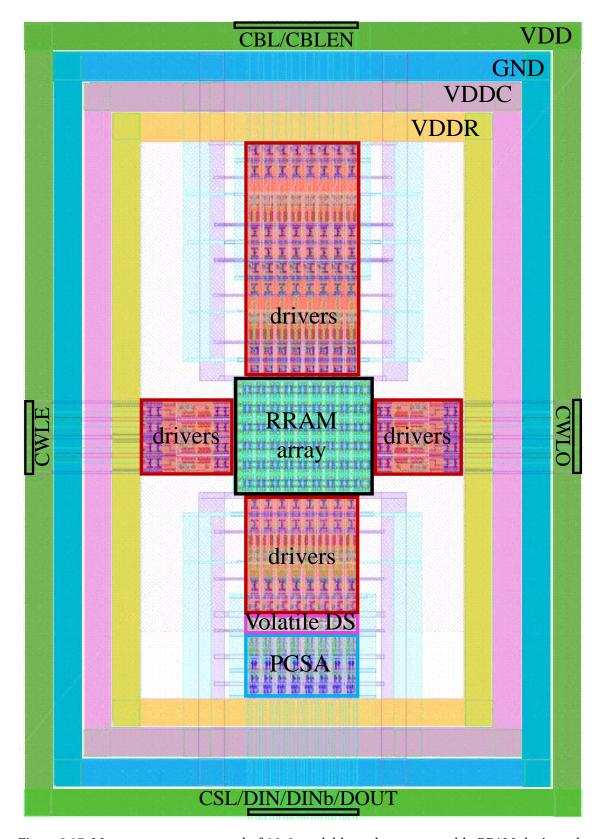

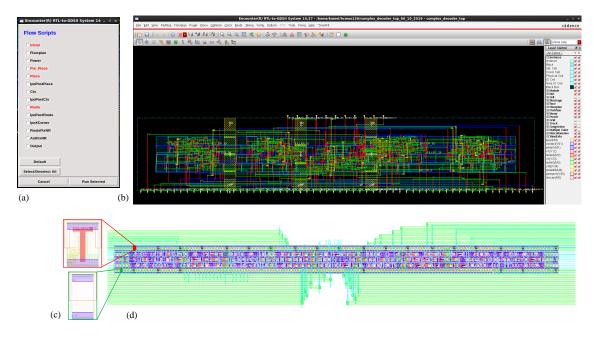

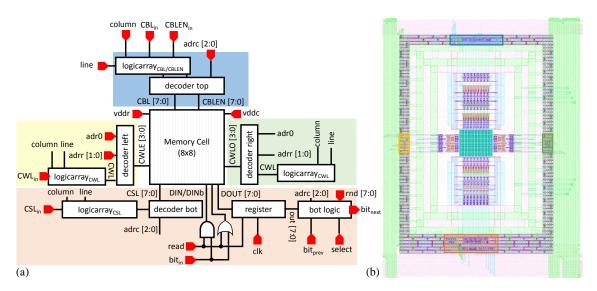

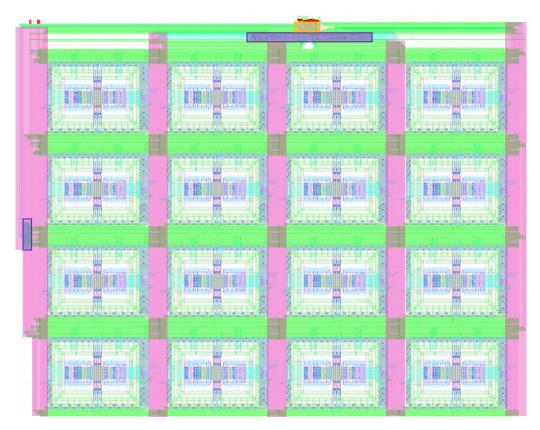

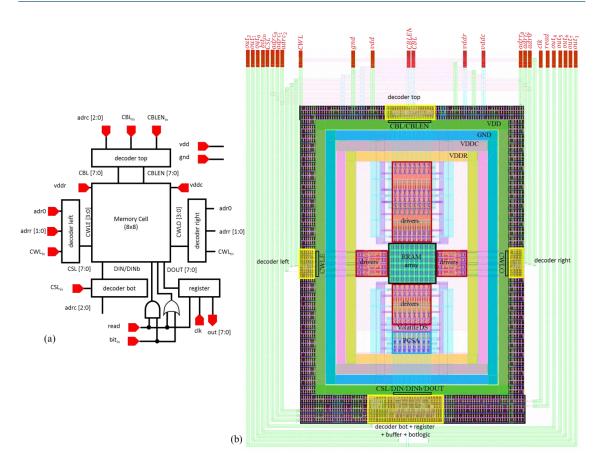

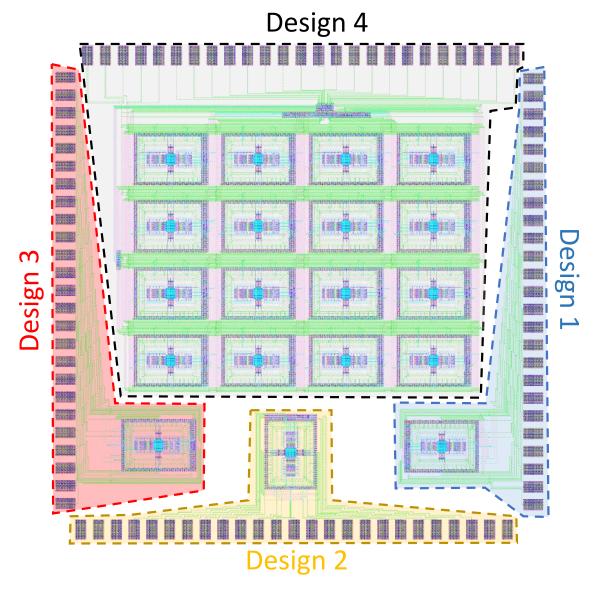

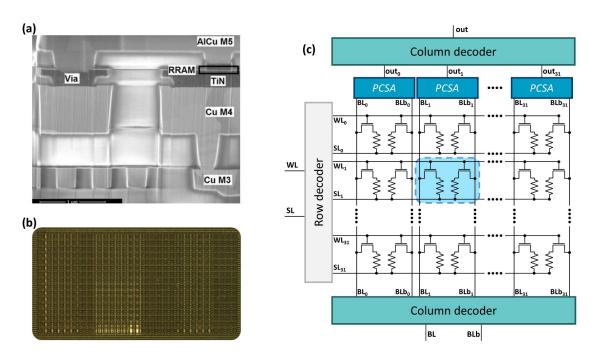

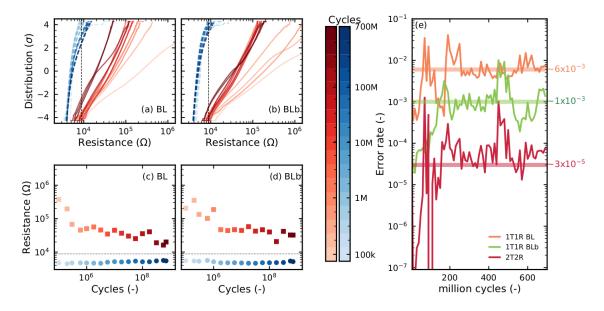

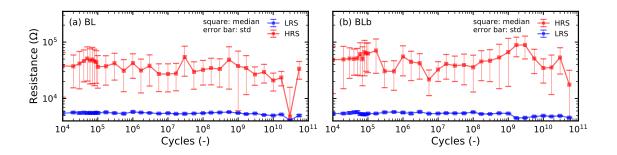

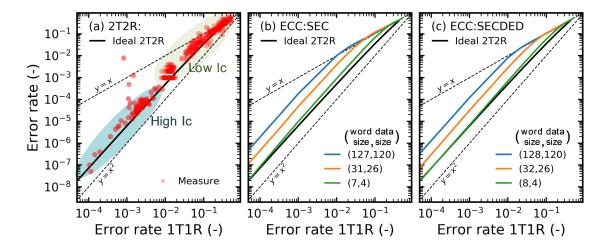

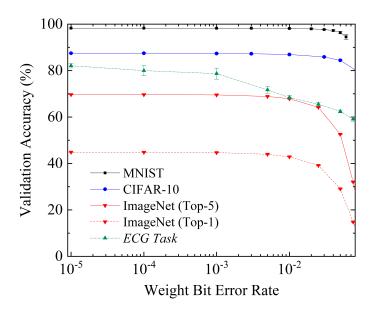

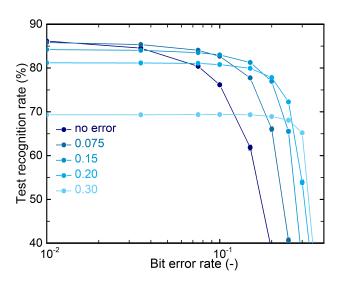

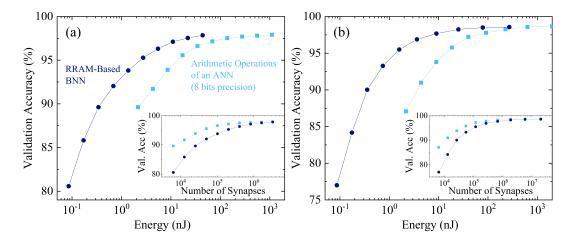

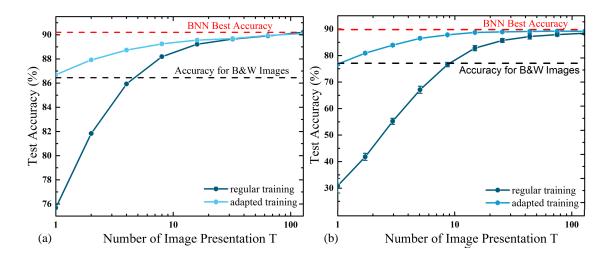

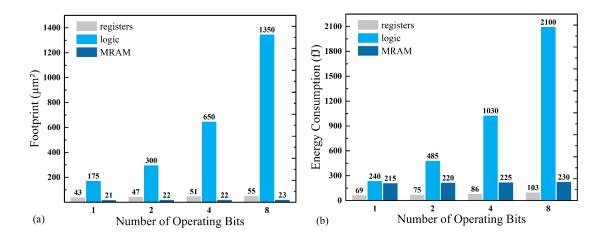

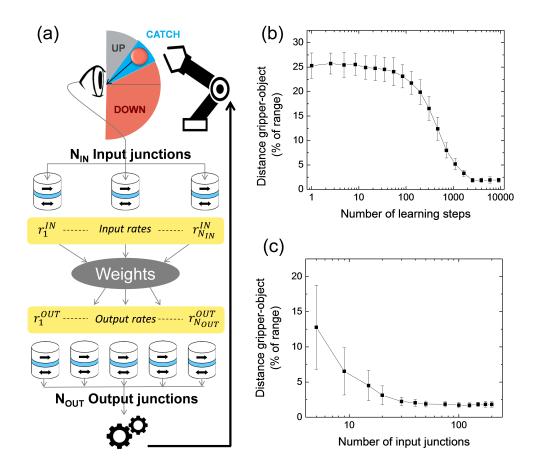

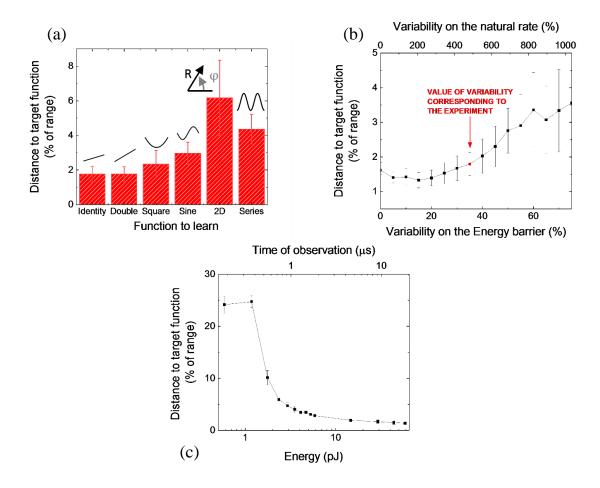

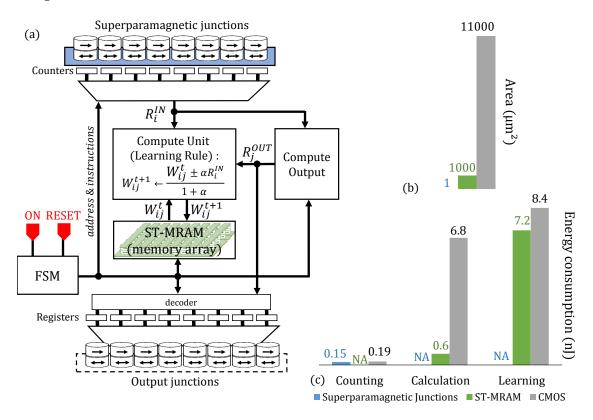

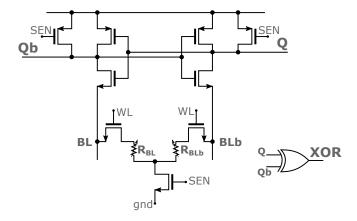

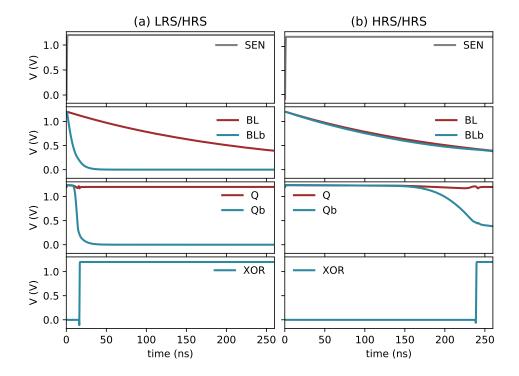

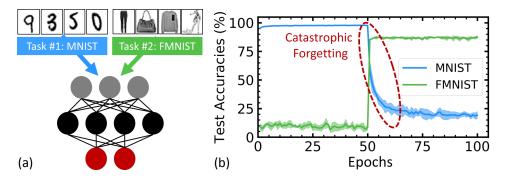

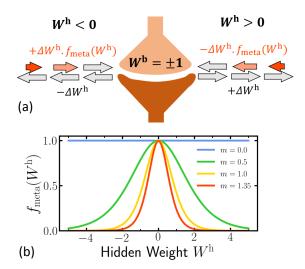

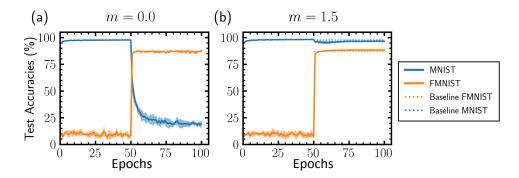

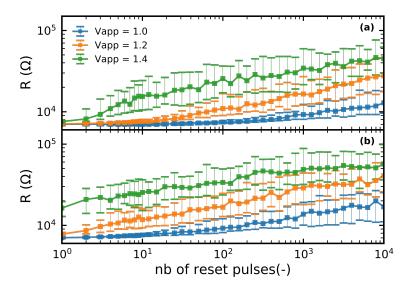

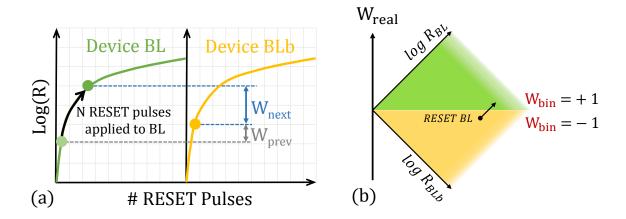

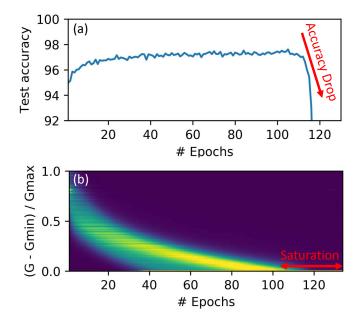

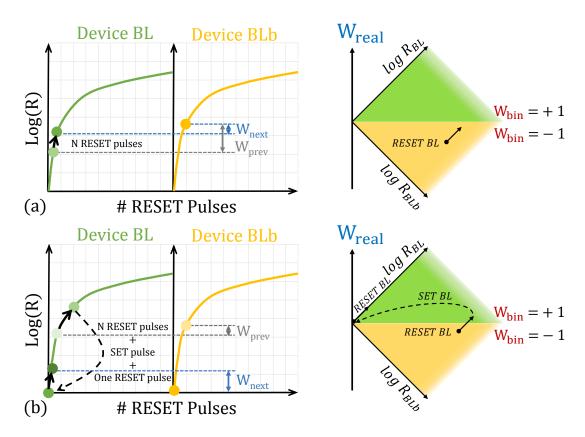

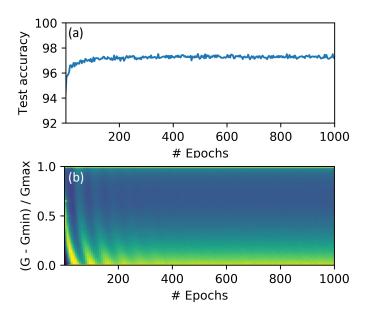

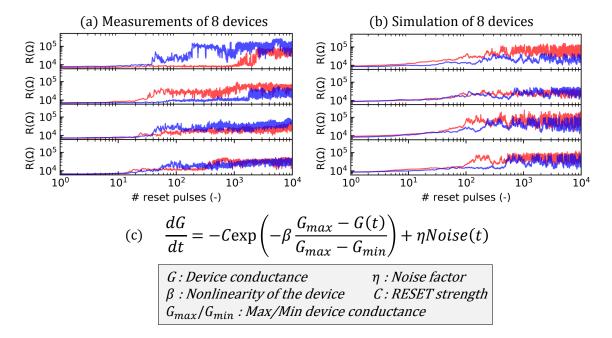

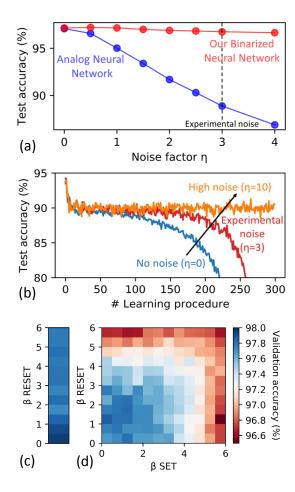

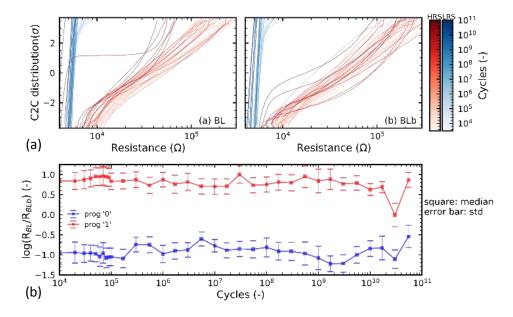

The operating principle is shown in Figure 1.8.