# Calcul Haute Performance: Caractérisation d'architectures et optimisation d'applications pour les futures générations de supercalculateurs

Jean Pourroy

#### ▶ To cite this version:

Jean Pourroy. Calcul Haute Performance: Caractérisation d'architectures et optimisation d'applications pour les futures générations de supercalculateurs. Théorie de l'information et codage [math.IT]. Université Paris-Saclay, 2021. Français. NNT: 2021UPASM020. tel-03249275

# HAL Id: tel-03249275 https://theses.hal.science/tel-03249275v1

Submitted on 21 Jun 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Calcul Haute Performance : caractérisation d'architectures et optimisation d'applications pour les futures générations de supercalculateurs

Thèse de doctorat de l'Université Paris-Saclay

Ecole Doctorale de Mathématique Hadamard (EDMH) n° 574 Spécialité de doctorat : Mathématiques appliquées Unité de recherche : Université Paris-Saclay, CNRS, ENS Paris-Saclay, Centre Borelli, 91190, Gif-sur-Yvette, France. Référent : Université Paris-Saclay

Thèse présentée et soutenue à Paris-Saclay, le 26 mars 2021, par

# Jean POURROY

# **Composition du jury**

Jean-Michel Ghidaglia

Professeur des universités, ENS Paris-Saclay

Jean-François Méhaut

Professeur (Université Grenoble Alpes), CNRS (LIG)

**Patrick Amestoy**

Professeur (ENSEEIHT), INP Toulouse (INPT-IRIT)

Jean-Yves Blanc

Architecte informatique en chef, CGG

Président

Rapporteur

Rapporteur

Examinateur

# Direction de la thèse

**Christophe Denis**

Maitre de Conférences, Sorbonne Université (LIP6)

**Patrick Demichel**

Technologue Distingué (DT), HPE

Directeur de thèse

Co-directeur de thèse

| école———       |

|----------------|

| normale ———    |

| supérieure———  |

| paris-saclay—— |

# **Hewlett Packard**Enterprise

# Résumé

**Titre :** Calcul Haute Performance : Caractérisation d'architectures et optimisation d'applications pour les futures générations de supercalculateurs

Mots clés: HPC; Exascale; Supercalculateur; Performance; Optimisation; Benchmark

Les systèmes d'information et les infrastructures de Calcul Haute Performance (HPC) participent activement à l'amélioration des connaissances scientifiques et à l'évolution de nos sociétés. Le domaine du HPC est en pleine expansion et les utilisateurs ont besoin d'architectures de plus en plus puissantes pour analyser le tsunami de données (simulations numériques, objets connectés), prendre des décisions plus complexes (intelligence artificielle), et plus rapides (voitures connectées, météo).

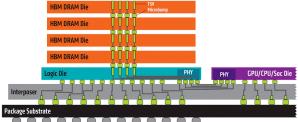

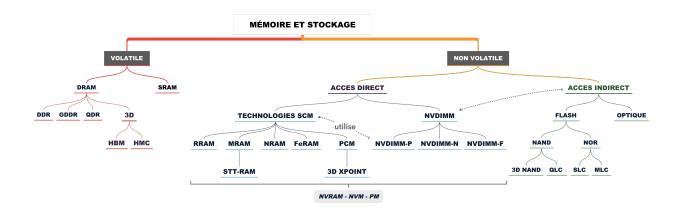

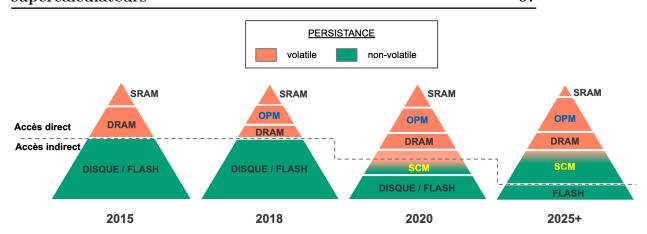

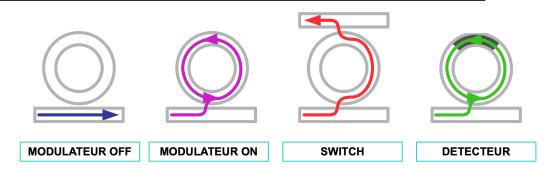

Dans ce travail de thèse, nous discutons des différents challenges à relever (consommation électrique, coût, complexité) pour l'élaboration des nouvelles générations de supercalculateurs Exascale. Alors que les applications industrielles ne parviennent pas à utiliser plus de 10% des performances théoriques, nous montrons la nécessité de repenser l'architecture des plateformes, en utilisant notamment des architectures énergétiquement optimisées. Nous présentons alors certaines technologies émergentes permettant leur développement : les mémoires 3D (HBM), la Storage Class Memory (SCM) ou les technologies d'interconnexions photoniques. Ces nouvelles technologies associées à un nouveau protocole de communication (Gen-Z) vont permettre d'exécuter de façon optimale les différentes parties d'une application. Cependant, en l'absence de méthode de caractérisation fine de la performance des codes,

ces architectures innovantes sont potentiellement condamnées puisque peu d'experts savent les valoriser.

Notre contribution consiste au développement d'une suite de codes (microbenchmarks) et d'outils d'analyse de performance. Les premiers ont pour objectifs de caractériser finement certaines parties de la microarchitecture. Deux microbenchmarks ont ainsi été développés pour caractériser le système mémoire et les unités de calculs. La deuxième famille d'outils permet d'étudier la performance des applications. Un premier outil permet de suivre l'évolution du trafic du bus mémoire, ressource critique des architectures. Un second outil permet d'obtenir le profil des applications en extrayant et caractérisant les boucles critiques (hot spots).

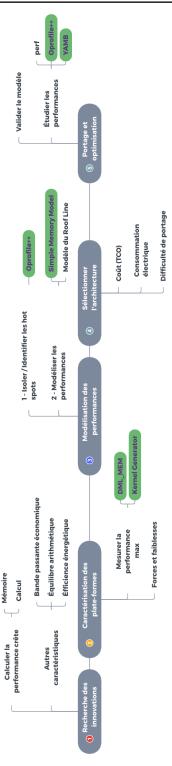

Pour profiter de l'hétérogénéité des plateformes, nous proposons une méthodologie en 5 étapes permettant d'identifier et de caractériser ces nouvelles plateformes, de modéliser les performances d'une application, et enfin de porter son code sur l'architecture choisie. Enfin, nous montrons comment les outils permettent d'accompagner les développeurs pour extraire le maximum des performances d'une architecture. En proposant nos outils en « sources ouvertes », nous souhaitons sensibiliser les utilisateurs à cette démarche et développer une communauté autour du travail de caractérisation et d'analyse de performance.

# Abstract

**Title:** High-Performance Computing: Architecture characterization and application optimization for future generations of supercomputers

**Keywords:** HPC; Exascale; Supercomputer; Performance; Optimization; Benchmark

Information systems and High-Performance Computing (HPC) infrastructures play an active role in the improvement of scientific knowledge and the evolution of our societies. The field of HPC is expanding rapidly and users need increasingly powerful architectures to analyze the tsunami of data (numerical simulations, IOT), to make more complex decisions (artificial intelligence), and to make them faster (connected cars, weather). In this thesis work, we discuss several challenges (power consumption, cost, complexity) for the development of new generations of Exascale supercomputers. While industrial applications do not manage to achieve more than 10% of the theoretical performance, we show the need to rethink the architecture of platforms, in particular by using energy-optimized architectures. We then present some of the emerging technologies that will allow their development: 3D memories (HBM), Storage Class Memory (SCM) or photonic interconnection technologies. These new technologies associated with a new communication protocol (Gen-Z) will help to optimally execute the different parts of an application. However, in the absence of a method for fine characterization of code performance, these emerging archi-

tectures are potentially condemned since few experts know how to exploit them.

Our contribution consists in the development of benchmarks and performance analysis tools. The first aim is to finely characterize specific parts of the microarchitecture. Two microbenchmarks have thus been developed to characterize the memory system and the floating point unit (FPU). The second family of tools is used to study the performance of applications. A first tool makes it possible to monitor the memory bus traffic, a critical resource of modern architectures. A second tool can be used to profile applications by extracting and characterizing critical loops (hot spots).

To take advantage of the heterogeneity of platforms, we propose a 5-step methodology to identify and characterize these new platforms, to model the performance of an application, and finally to port its code to the selected architecture. Finally, we show how the tools can help developers to extract the maximum performance from an architecture. By providing our tools in open source, we want to sensitize users to this approach and develop a community around the work of performance characterization and analysis.

# Remerciements

Ces premiers mots de ce manuscrit sont aussi les derniers que j'écris de ce (long?) manuscrit. Ce sont sûrement les plus importants et me permettent de remercier toutes les personnes qui ont rendu cette aventure possible.

Mes premiers remerciements vont à mon jury qui a accepté d'évaluer mon travail. Je remercie mes deux rapporteurs, **Patrick Amestoy** (INP Toulouse, INPT-IRIT) et **Jean-François Méhaut** (UGA, CNRS), pour avoir pris le temps de lire avec attention mes travaux et pour leurs retours très constructifs. Je remercie aussi **Jean-Michel Ghidaglia** (Professeur des Universités, ENS Paris-Saclay) et **Jean-Yves Blanc** (CGG) d'avoir accepté de faire partie de mon jury.

Je souhaite aussi remercier mes deux directeurs de thèse, **Patrick Demichel** (HPE) et **Christophe Denis** (Sorbonne Université, LIP6) pour leur soutien durant ces quatre années. Merci à **Jean-Jacques Braun** (HPE), **Jean-Luc Assor** (HPE), et **Jean-Michel Ghidaglia** de m'avoir fait confiance depuis le premier jour. Sans votre investissement, les nombreuses difficultés auraient eu raison de cette collaboration entre HPE et l'ENS Paris-Saclay et je souhaite vous remercier sincèrement d'avoir rendu cette thèse possible.

Je remercie aussi les deux administratrices du Centre Borelli (CMLA), **Véronique Almadovar** et **Alina Müller**, ainsi qu'**Agnès Desolneux** (Directrice de recherche CNRS, ENS Paris-Saclay) pour m'avoir épaulé à distance et aidé à relever les nombreuses difficultés administratives pouvant être rencontrées durant un doctorat.

Ce manuscrit aurait été très différent sans l'aide de quatre personnes en particulier que je souhaite remercier. Patrick Demichel, merci de m'avoir suivi durant ces quatre années et fait profiter de ton expérience du domaine du HPC, de l'analyse et de l'optimisation de code. J'ai essayé de retranscrire au mieux ce que tu m'as appris dans ces 320 pages, même s'il en avait fallu le double pour décrire seulement l'état de l'art. Tes nombreux conseils, toujours constructifs, m'ont permis d'avancer et m'ont aidé à retrouver la confiance en moi dont j'ai pu manquer à certains moments. J'espère que tu trouveras dans ce manuscrit une part de cette vision de l'Exascale que tu construis depuis toutes ces années. Je suis très fier d'avoir été ton premier thésard, et souhaite toute la réussite possible à ta prochaine étudiante qui semble avoir déjà bien commencé.

Je remercie **Thomas Guntz**, mon copilote, mon partenaire de B.U. et mon duo queue de la rédaction [Gun20]. Le destin voulait que nous traversions cette épreuve ensemble, après l'IUT d'Aix-en-Provence, nous nous sommes retrouvés à l'ENSIMAG pour finalement passer des centaines d'heures ensemble à la **Bibliothèque Universitaire Joseph-Fourrier** pour écrire nos manuscrits. Sans ton soutient et celui de la Brasserie du **Martin's Café** (Leboucher x2), je ne pourrais pas dire si j'y serai arrivé, mais on l'a fait (poke Nashor).

Je remercie aussi ma tante, **Geneviève Pourroy** (Directrice de recherche, CNRS) pour

ses nombreuses relectures du manuscrit, et son aide importante (même si tu en doutes) pour l'organisation de ses nombreuses sections, sous-sections, paragraphes...

Aussi, je remercie **Thibault Lambert** pour ses nombreuses corrections orthographiques et grammaticales.

Ces 4 années de thèse chez HPE, et les 3 années d'école d'ingénieur la précédente m'ont fait rencontrer de nombreuses personnes que je souhaite aussi remercier. Je souhaite tout d'abord remercier mes collègues de l'équipe HPC de Grenoble, merci pour votre accueil et ces nombreux évènements que nous avons partagés. Ce fut un plaisir de partager ces années avec vous.

Je remercie Jean-Jacques Braun, Pierre Hoffer, Nathalie Viollet et Philippe Vettori pour leur encadrement durant ces premières étapes de ma carrière. Merci à Fred et Sébastien, ce fut un réel plaisir de travailler avec des personnes aussi expérimentées que vous. J'ai beaucoup appris à votre contact et vous remercie pour le temps que vous m'avez consacré et les nombreuses discussions que nous avons partagées. Je remercie Sorin pour ton aide et tes conseils tout au long de mon parcours. Merci à Flo pour tous ces cafés (mais pas que) partagés au patio. Merci à mon meilleur voisin de bureau, Xavier, pour ta bonne humeur et ta joie de vivre. J'espère qu'on aura l'occasion de se croiser sur la route, à vélo. Je souhaite aussi remercier chaleureusement Hana pour ces 7 années que nous avons partagés. Tes conseils et ton aide quand j'en avais besoin m'ont été des plus précieux. Je te souhaite toute la réussite que tu mérites dans la suite de ta longue carrière et espère que nos chemins se recroiseront.

Avoir pu travailler dans une entreprise comme HPE a été une première expérience incroyable. L'avantage principal d'une telle entreprise est bien de pouvoir se retrouver le midi au Foot Loisirs. Je remercie donc mes partenaires Max, Titi et Ben pour leurs passes (toujours décisives). J'espère qu'on aura l'occasion de rechausser les crampons ensemble ou de partager une bière devant un match de Paris. Je pense aussi à Paul, Pierre-Antoine et Max, qui ont fait de ces années chez HPE un véritable plaisir et sans qui les matchs n'ont plus la même saveur.

Je souhaite aussi remercier de sincères remerciements à tous les enseignants que j'ai pu croiser durant mes études. Je pense notamment à Andreea Dragut, Patricia Gaëtan, Marc Laporte, Wojciech Bienia, Joëlle Thollot qui m'ont apporté leur soutien à chaque étape de mes études et qui m'ont transmis leur volonté d'enseigner et de partager le plus largement possible la connaissance. Ces expériences m'ont motivé pour enseigner durant trois ans à l'IUT de Grenoble auquel j'adresse mes remerciements et notamment à Jérôme Goulain et Philippe Martin.

La longue aventure que représente la thèse ne serait pas soutenable sans le soutien de ses amis. Merci à mes amis **Flo**, **Manu**, **Tom** et **Yanni** pour tous ces moments qui m'ont permis de m'évader de la thèse durant ces week-ends à lancer quatre boules ou à taper du pied sur des musiques électroniques à rythmes répétitifs. Les soirées, c'est encore mieux quand c'est nous qui

les organisons. Pour ça, je remercie **Shiki**, **Tom**, **Uppah**, **Hugo** et tous autres les bénévoles de **Carton-Pâte Records** pour toutes ces soirées organisées et ces bons moments partagés.

Merci à **Elora**, **Zoé**, **Pierre** et **Cathy** pour votre gentillesse et ces super moments passés à vélo à travers les Alpes ou en ski en Norvège.

Au temps du numérique et des confinements, les amis en ligne sont aussi importants pour s'échapper quelques heures après une longue journée de travail. Je remercie donc toute la **Team RTC** : **Gushu**, **D1aucy**, **Nilure**.

Merci à ma famille. Merci à mes **parents** pour l'éducation qu'ils m'ont donnée et leur soutien tout au long de mes 8 années d'étude. Merci à mon frère **Vincent** et à ma soeur **Clara** de toujours avoir été là pour moi. Je vous aime.

Pour finir, je remercie **Anna** qui m'a soutenu durant ce long parcours. On ne se rend pas compte de la place que peut prendre la thèse dans une vie de couple, mais tu as toujours été là pour m'aider et me changer les idées. Sans toi et ton soutien, je ne pense pas que j'aurai tenu, je te remercie sincèrement pour tout ce que tu m'as apporté.

# Table des matières

| $\mathbf{G}$ | lossa | ire                                                              | xi   |

|--------------|-------|------------------------------------------------------------------|------|

| A            | crony | ymes                                                             | xv   |

| N            | otati | ions                                                             | cvii |

| 1            | Inti  | roduction générale                                               | 1    |

|              | 1.1   | Supercalculateur exascale                                        | 2    |

|              | 1.2   | Travail de thèse                                                 | 6    |

|              | 1.3   | Contributions et plan du manuscrit                               | 9    |

| 2            | Cal   | cul Haute Performance                                            | 15   |

|              | 2.1   | Introduction au Calcul Haute Performance (HPC)                   | 16   |

|              | 2.2   | Évolution de la performance des supercalculateurs                |      |

|              | 2.3   | Opportunités pour le développement de nouveaux supercalculateurs |      |

|              | 2.4   | Caractérisation et analyse de performance des architectures      |      |

|              | 2.5   | Conclusion                                                       | 110  |

| 3            | Dév   | veloppements logiciels                                           | 113  |

|              | 3.1   | Introduction                                                     | 114  |

|              | 3.2   | Benchmark mémoire                                                | 118  |

|              | 3.3   | Benchmark d'unité arithmétique                                   | 143  |

|              | 3.4   | Monitoring du bus mémoire                                        | 166  |

|              | 3.5   | Profil de l'exécution d'instructions                             | 172  |

|              | 3.6   | Conclusion                                                       | 182  |

| 4            | Mé    | thodologie pour l'analyse de performance et le portage de code   | 185  |

|              | 4.1   | Introduction                                                     | 186  |

|              | 4.2   | Étape 1 : Rechercher les dernières innovations technologiques    |      |

|              | 4.3   | Étape 2 : Caractériser les architectures                         | 195  |

|              | 4.4   | Étape 3 : Extraire les noyaux et modéliser leur performance      | 199  |

|              | 4.5   | Étape 4 : Sélectionner la plateforme adaptée                     | 203  |

|              | 4.6   | Étape 5 : Porter et optimiser le code                            | 205  |

|              | 4.7   | Conclusion et perspectives                                       | 212  |

| 5            | Cor   | nclusion générale                                                | 215  |

|              | 5.1   |                                                                  | 216  |

|              | 5.2   | Contributions principales de la thèse                            | 217  |

|              | 5.3   | Conclusion                                                       | 220  |

| Anne  | xes                                                               | 225 |

|-------|-------------------------------------------------------------------|-----|

| Annex | e A Architecture des processeurs                                  | 225 |

| A.1   | Le circuit logique                                                | 226 |

|       | A.1.1 Les transistors                                             | 226 |

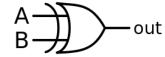

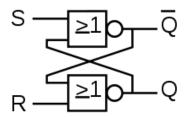

|       | A.1.2 Les portes logiques                                         | 226 |

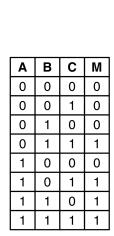

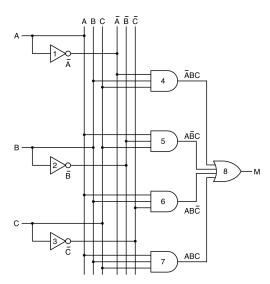

|       | A.1.3 Algèbre de Boole                                            | 227 |

|       | A.1.4 Circuits logiques                                           | 227 |

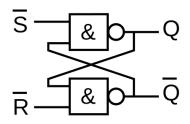

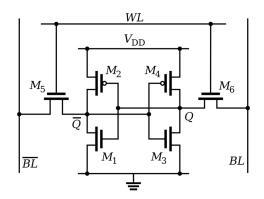

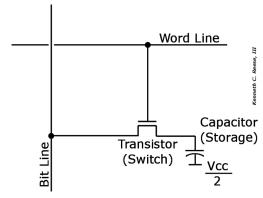

|       | A.1.5 Les mémoires RAM                                            | 229 |

|       | A.1.6 Évolutions des transistors                                  | 230 |

| A.2   | L'architecture                                                    | 232 |

|       | A.2.1 Architecture de processeur : origine et évolutions majeures | 233 |

|       | A.2.2 Améliorer l'efficacité de l'exécution                       | 237 |

|       | A.2.3 Accélérer l'exécution des instructions                      | 239 |

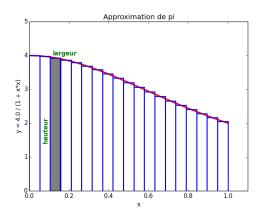

|       | A.2.4 Exécuter les instructions en parallèles                     | 246 |

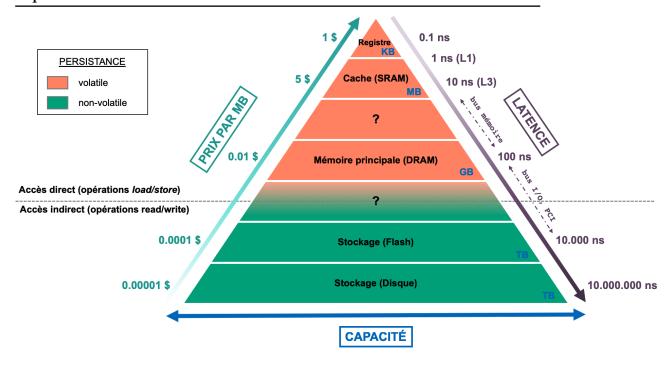

| A.3   | Hiérarchie mémoire                                                | 254 |

|       | A.3.1 Mémoire principale                                          | 255 |

|       | A.3.2 La hiérarchie mémoire                                       | 258 |

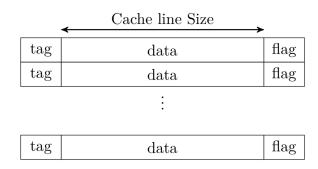

|       | A.3.3 Caches                                                      | 264 |

| A.4   | Mémoire virtuelle                                                 | 272 |

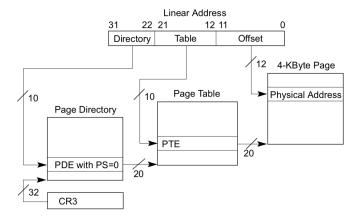

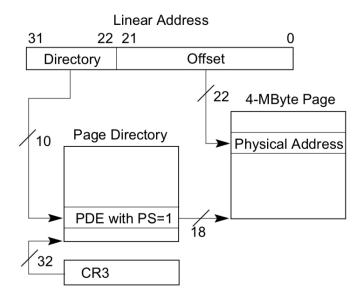

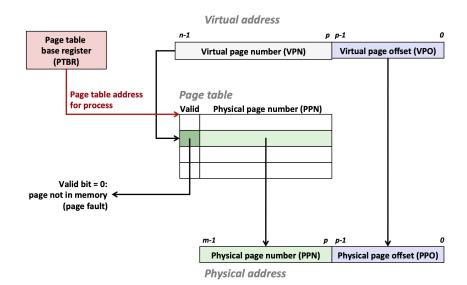

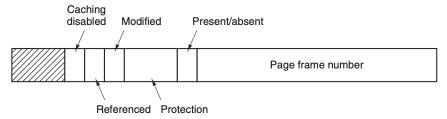

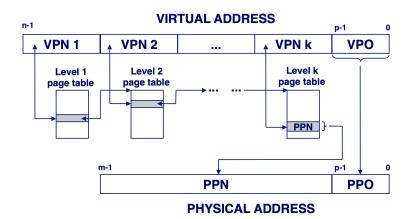

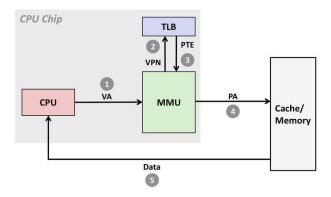

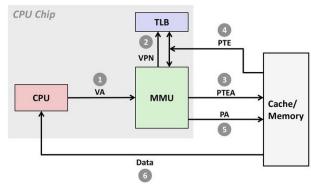

|       | A.4.1 La pagination                                               | 274 |

|       | A.4.2 Memory Management Unit (MMU)                                | 277 |

| Annex | e B Les compteurs matériels                                       | 283 |

| B.1   | Les compteurs                                                     | 283 |

|       | B.1.1 Les compteurs matériels                                     | 283 |

|       | B.1.2 Mode de mesure : comptage et échantillonnage                | 285 |

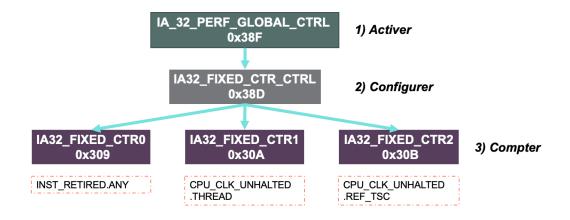

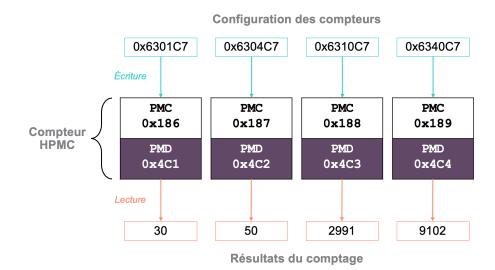

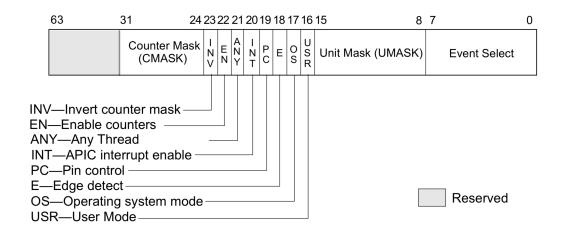

|       | B.1.3 Compteurs matériels des architectures Intel                 | 286 |

| B.2   | Unité de suivi de performance Intel : les PMU                     | 289 |

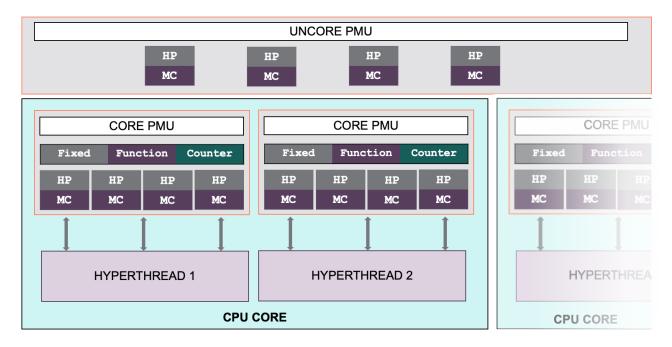

|       | B.2.1 PMU core                                                    | 290 |

|       | B.2.2 PMU uncore                                                  | 292 |

| B.3   | Discussion                                                        | 297 |

| B.4   | Conclusion                                                        | 299 |

# Glossaire

Benchmark

Code, ou un ensemble de codes, permettant de mesurer la performance d'une solution et d'en vérifier ses fonctionnalités. 7, 87, 88, 111, 114, 117, 143, 187, 196, 218, 219, 222

Compteur Matériel

Les compteurs matériels de performance (ou hardware counters) désignent les registres matériels du processeur utilisé pour enregistrés et compter les évènements matériels et logiciels arrivant sur la microarchitecture (voir PMU). 283, 296

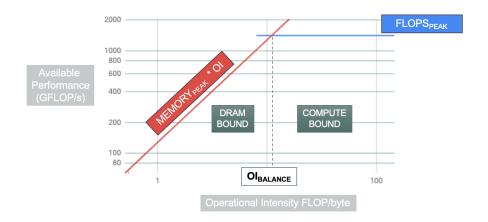

Compute Bound

Le terme "limité par le calcul" (compute bound) fait référence à une application (ou fonction) dont le temps d'exécution est principalement déterminé par la performance de calcul du processeur. Lorsqu'un code n'est pas compute bound il est généralement memory bound. xii, 107, 124, 125, 145, 189, 199, 200

Exascale

désigne la nouvelle génération de plateforme capable d'exécuter un  $10^{18}$  FLOPS (un exaFLOPS) ( $10^{18}$  opérations à virgule flottante par seconde) 2, 3, 45, 58, 60, 73, 77, 78, 86, 94, 186, 220

FMA

instruction processeur réalisant une addition et une multiplication entre trois valeurs a, b et c tel que a=a+b\*c. L'unité matérielle responsable de l'exécution d'une telle instruction s'appelle un multiplicateur-accumulateur (MAC) xv

**FPU**

Une unité de calcul à virgule flottante Floating Point Unit) est une partie d'un processeur, spécialement conçue pour effectuer des opérations sur des nombres à virgule flottante. xv

Framework

infrastructure logicielle désignant un ensemble de composants logiciels établissant les fondations d'un logiciel. 92

Goulot D'étranglement

105, 200, 257

Hot Spot

Désigne une région d'un programme où une grande proportion d'instructions sont exécutées pendant l'exécution d'une application. 11, 87, 95, 107, 117, 172, 173, 176, 189, 190, 199, 203, 219

**HPC**

Le but du HPC est de paralléliser des applications scientifiques à destination de ressources informatiques telles que les supercalculateurs xv

xii Glossaire

Kernel

Un noyau de calcul (kernel) est une partie de code restreinte d'une application, qui remplit une fonction clairement définie. En Calcul Haute Performance (HPC), les kernels sont des zones de codes de calculs intensifs responsables de la majorité du temps d'exécution d'une application. 8, 110, 115, 145, 147, 156, 164, 167, 186, 189, 191, 199–202, 205, 207

Memory Bound

Le terme "limité par la mémoire" (memory bound) fait référence à une application (ou fonction) dont le temps d'exécution est principalement déterminé par la performance du système mémoire. Lorsqu'un code n'est pas memory bound il est généralement compute bound. xi, 107, 124, 128, 189, 199, 200

Memory Gap

Traduit l'écart de performance entre la performance des processeurs et celle du système mémoire. 60

Miss

Un défaut de cache (ou *miss*) est un événement se produisant lorsqu'une donnée à accéder n'est pas présente dans la mémoire cache du processeur. Celle-ci doit alors être chargée depuis la mémoire principale. 8, 11, 116, 128, 139, 166, 168, 169, 218, 292

MPI

Standard de communication pour des programmes parallèles sur des systèmes à mémoire distribuée xv

PMU

La PMU est un matériel du processeur responsable de mesurer la performance de celui-ci à l'aide de compteurs matériels spécialisés (hardware counters). xv

Prélecteur Mémoire

Dispositif matériel du processeur permettant d'anticiper les accès mémoire en chargeant les données (ou les instructions) depuis la mémoire vers le processeur (en mémoire cache) avec qu'elles ne soient réellement utilisées. Ce mécanisme, aussi appelé memory prefetcher, permet de réduire la latence d'accès. 11, 118, 119, 122, 123, 125, 128, 131–134, 218

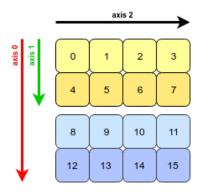

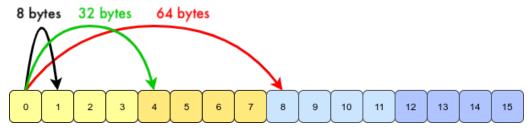

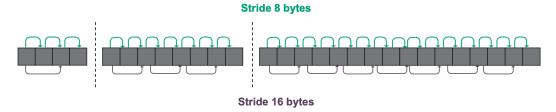

Stride

Certains algorithmes réalisent des accès mémoires en accédant aux données par des sauts, de taille régulière, en entre deux adresses mémoire. Ces sauts sont appelés des strides. 8, 93, 118–120, 125, 126, 132, 141, 187, 217, 218

**Thread**

ou processus léger ou tâche est similaire à un processus. Les threads d'un même processus se partagent le même espace mémoire. 31, 99 Glossaire xiii

**Translation Lookaside Buffer** ou répertoire de pages actives (TLB) permet d'accélerer la traduction des adresses virtuelles. 7, 120, 126, 139

# Acronymes

| $\mathbf{ALU}$ | Arithmetic Logic Unit ou unité arithmétique et logique 144                                                                                                                    |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASIC           | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                          |

| DSP            | $Digital\ Signal\ Processor$ ou processeur de signal numérique 24                                                                                                             |

| ExaFLOPS       | $10^{18} \text{ FLOPS xi, } 3, 45$                                                                                                                                            |

| FLOP           | Floating Point Operation ou opération à virgule flottante 8, 20, 42, 43, 86, 143, 176, 192, 195, 204, 217, 239, 255, 284, 288, 289                                            |

| FLOPS          | Floating Point Operation per Second ou nombre d'opérations à virgule flottante par seconde (FLOP/s) $2, 4, 34, 35, 40, 42, 46, 50, 75, 89, 145, 156, 157, 174, 192, 193, 199$ |

| FMA            | Fused Multiply-Add ou multiplication-addition fusionnées (voir glossaire:FMA) 27, 109, 147, 157, 162, 192, 194, 195, 197, 206                                                 |

| FPGA           | $\begin{tabular}{lll} Field & Programmable & Gate & Arrays & ou & r\'eseaux & logiques & programmables & 23, & 56 \end{tabular}$                                              |

| FPU            | Floating Point Unit ou unité de calcul à virgule flottante (voir glossaire:FPU) 8, 41, 143–145, 162, 163, 165, 192, 210, 218, 219, 228, 244                                   |

| GPU            | Graphics Processing Unit ou processeur graphique 22, 23, 186, 190                                                                                                             |

| HPC            | High Performance Computing ou Calcul Haute Performance (voir glossaire: HPC) xii, 1, 2, 7, 8, 13, 15, 18, 21, 86, 96, 111, 191, 215, 236                                      |

| IPC            | Instructions Par Cycle 11, 128, 136, 137, 151, 154–157, 160, 179, 208, 210, 287                                                                                               |

| MPI            | Message Passing Interface ou interface de passage de message (voir glossaire:MPI) 30, 210                                                                                     |

| PMU            | Performance Monitoring Unit ou unité de suivi de perfor-                                                                                                                      |

mance (voir glossaire:PMU) 167, 169, 286

# **Notations**

EQUILIBRE<sub>architecture</sub> L'équilibre arithmétique d'une architecture 204

FLOP<sub>cycle</sub> nombre d'opérations à virgule flottante (FLOP) exécuté par

cycle 192, 193

FLOPS<sub>max</sub> performance de calcul maximale mesurée d'une unité de calcul,

mesurée en FLOPS 145, 157, 162, 163, 165, 195–198, 202

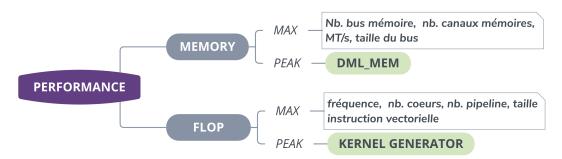

${\tt FLOPS_{\tt peak}} \qquad \qquad {\tt performance} \ de \ calcul \ th\'{e}orique \ d'une \ unit\'e \ de \ calcul, \ mesur\'ee$

en FLOPS 107, 108, 156, 157, 165, 192, 193, 195, 196, 200

$\mathtt{MEMORY}_{\mathtt{max}}$  débit mémoire maximale mesuré du bus mémoire, mesuré en

GB/s 196, 197, 201, 202, 211

MEMORY<sub>peak</sub> débit mémoire théorique du bus mémoire, mesuré en GB/s

107, 108, 192, 196, 200, 201

OI<sub>kernel</sub> l'intensité opérationnelle d'un kernel correspond au ratio entre

le nombre d'opérations exécutées et la quantité de données

transférées nécessaire. 199, 200, 202, 204

TEMPS<sub>optimal</sub> Temps optimal calculé pour exécuter un kernel 201, 203, 205–

207, 211, 213

# Introduction générale

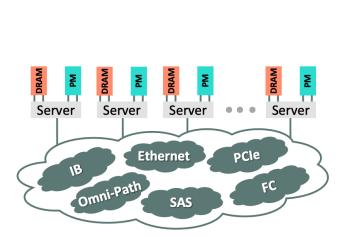

Le Calcul Haute Performance (HPC) est le domaine consistant à regrouper des milliers de ressources informatiques (processeurs, mémoire, stockage, réseau) pour exécuter des applications de simulations numériques complexes ou permettre le traitement massif de données. Ces simulations contribuent au développement de nouveaux produits (voitures, avions), à l'extraction d'énergies (recherche pétrolière, conception d'éolienne). Le HPC est un outil inhabituel, car il ne se limite pas à un domaine particulier et possède des applications dans de nombreux domaines :

- En physique théorique, les expérimentations réalisées au Grand Collisionneur de Hadrons (LHC) demandent de grandes puissances de calcul pour analyser les données générées chaque seconde par 600 millions de collisions. L'analyse de ces données en un temps raisonnable est rendue possible grâce à une plateforme distribuée entre plusieurs pays formés d'un million de coeurs et d'un exabyte de stockage (10<sup>18</sup> octets). Cette plateforme de calculs a permis d'importantes découvertes comme celle du boson de Higgs [Bel+17].

- Dans le domaine de la santé, le Living Heart Project [Bai+14] a pour objectif de modéliser un coeur pour aider à comprendre son fonctionnement. Depuis 2017, les fabricants peuvent utiliser cette modélisation pour tester un nouveau traitement avant de l'utiliser sur un patient. Un second projet nommé *Human Brain Project* [Mar12] a pour objectif de simuler d'ici 2024 le fonctionnement d'un cerveau humain permettant de développer des traitements pour les maladies neurologiques.

- En mécanique des fluides, les simulations numériques sont utilisées dans l'aéronautique (maximiser le portage des ailes), la recherche d'hydrocarbures (modélisation 3D des fonds marins), la météorologie...

Ainsi, le HPC participe activement à l'amélioration des connaissances scientifiques, mais aussi à l'évolution de nos sociétés, par exemple, en rendant nos vies plus sécurisées en anticipant certaines catastrophes naturelles (météorologie, épidémiologie, développement de médicaments <sup>1</sup>, etc.). Ces simulations nécessitent d'énormes quantités de calculs pour être exécutées et utilisent des plateformes informatiques constituées de milliers de ressources de calculs appelées supercalculateurs. L'amélioration de la performance de ces plateformes année après année a permis de réaliser de nombreuses avancés dans les domaines cités ci-dessus. En effet, leur performance a évolué exponentiellement ces 30 dernières années. Une montre connectée récente possède une puissance de calcul supérieure à la plateforme la plus puissante développée en 1985 (Cray-2),

<sup>1.</sup> En mars 2020, l'Institut Pasteur et les équipes de recherche de Sorbonne Université ont utilisé le supercalculateur Jean Zay, conçu par HPE, pour étudier la structure moléculaire du SARS-CoV-2 afin d'aider au développement de médicaments pour soigner le coronavirus - http://www.genci.fr/fr/node/1043.

alors utilisée dans le domaine nucléaire.

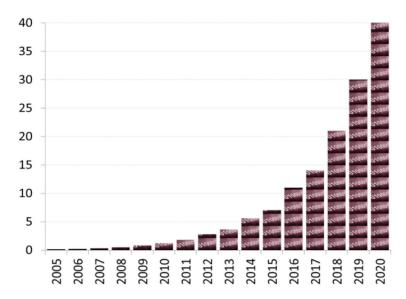

Le développement de plateformes de calculs plus puissantes va aider notre société à relever les nombreux défis qui lui font face : changement climatique (anticiper les catastrophes naturelles, étude du réchauffement des océans), recherche médicale (médecine personnalisée, recherche biomoléculaire), villes intelligentes, etc. Cette nouvelle génération de supercalculateurs permettra d'obtenir des réponses plus fiables et plus rapidement et permettra notamment d'analyser les grands volumes de données générées par les objets connectés. Ces analyses peuvent utiliser des algorithmes d'apprentissage automatique qui ne deviennent efficaces qu'après avoir suivi de nombreux entraînements, ces derniers nécessitant de grandes puissances de calcul. Ainsi, si la société veut continuer à profiter de nouvelles améliorations, la performance des supercalculateurs doit continuer à évoluer.

# 1.1 Supercalculateur exascale

Actuellement, le défi de l'industrie des semi-conducteurs est la construction d'une plateforme capable d'exécuter  $10^{18}$  opérations par seconde nommée supercalculateur exascale. L'accès à une telle plateforme permettra alors d'exécuter les applications actuelles sept fois plus rapidement  $^2$  (ou nécessitant sept fois plus d'opérations) que les systèmes petascale les plus puissants d'aujourd'hui. L'obtention du premier supercalculateur exascale est très convoitée et représente un symbole de réussite pour son acquéreur (pays, université, industrie), ainsi que pour l'entreprise qui aura réalisé sa construction. L'industrie du HPC, mais aussi les nations, se sont donc lancées dans cette course effrénée en y allouant des moyens considérables. Nous pouvons notamment citer les investissements réalisés par les États-Unis (PathForward, 400 millions d'euros) ou l'Union européenne (EuroHPC, 486 millions d'euros). Ces projets sont réalisés en partenariat avec des entreprises privées du domaine HPC (dont HPE) qui financent d'un même montant chaque projet.

#### 1.1.1 Les défis d'Exascale

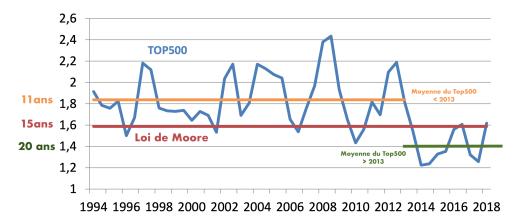

Pour comprendre la complexité des défis à relever pour construire une plateforme exascale, le classement du Top500 ³ peut être consulté. Le Top500 classe deux fois par an les 500 supercalculateurs les plus puissants de la planète à l'aide d'une application de calcul intensif High-Performance Linpack (HPL [DLP03]). Cette application permet d'évaluer la puissance de calcul d'une plateforme, mesurée en nombre d'opérations à virgule flottante par seconde (FLOPS). Ce classement existe depuis 1993 et permet de mesurer et d'apprécier l'évolution de la performance des supercalculateurs les plus puissants tous les 6 mois.

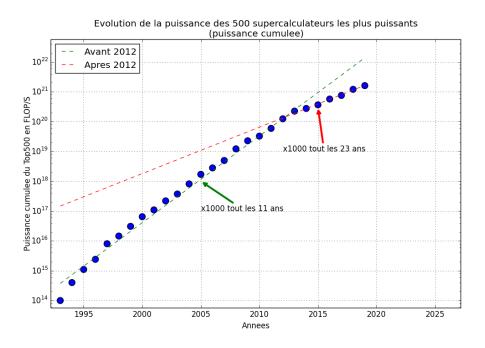

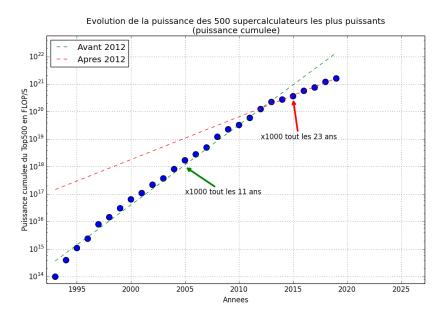

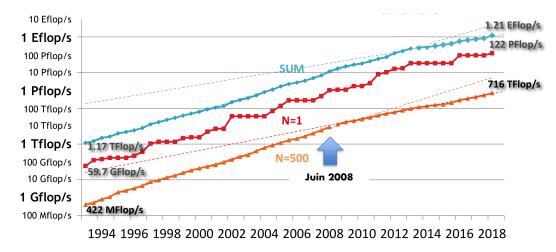

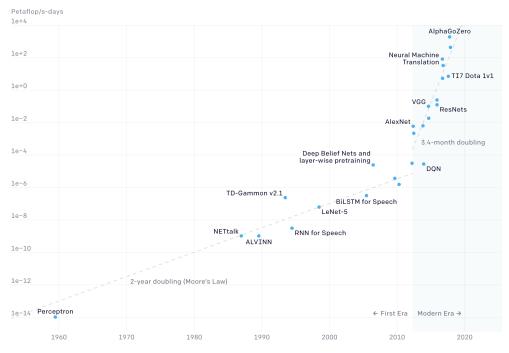

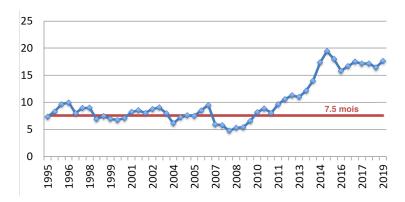

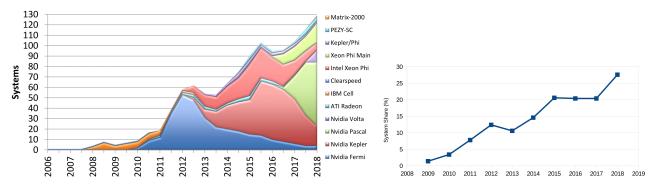

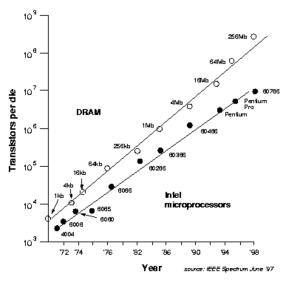

La figure 1.1 présente l'évolution de la performance cumulée des 500 supercalculateurs apparaissant dans chaque classement du Top500. De 1993 à 2012, cette performance cumulée a

<sup>2.</sup> En novembre 2019, le supercalculateur le plus puis sant de la planète est capable d'exécuter  $148 \times 10^{15}$  opérations par seconde.

<sup>3.</sup> Classement du Top500 - https://www.top500.org/

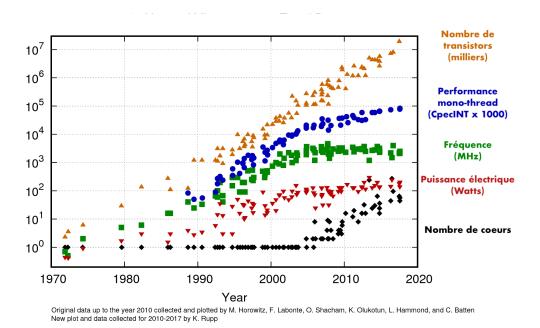

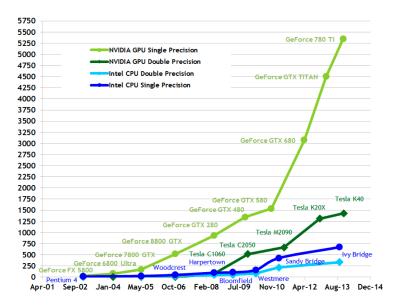

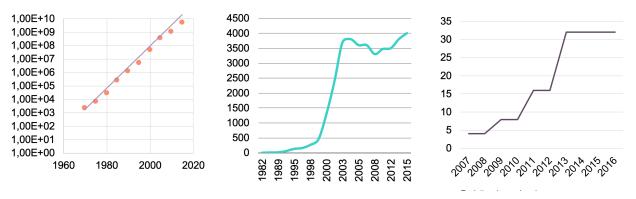

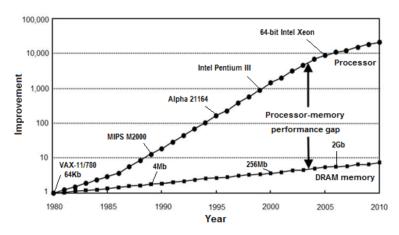

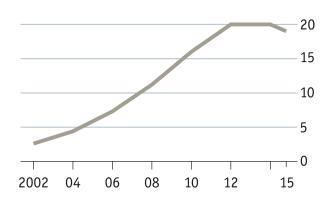

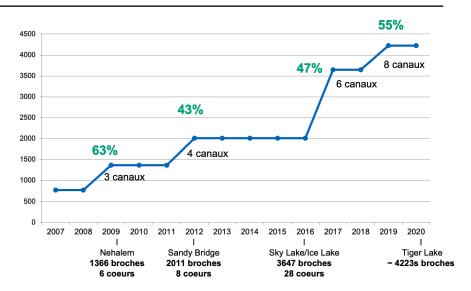

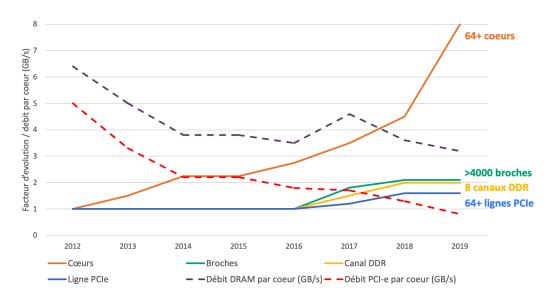

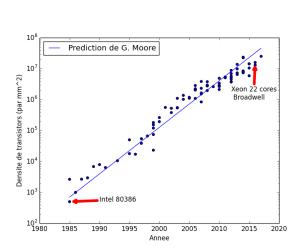

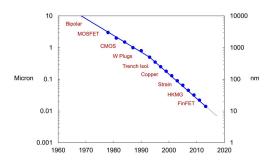

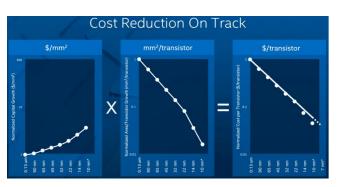

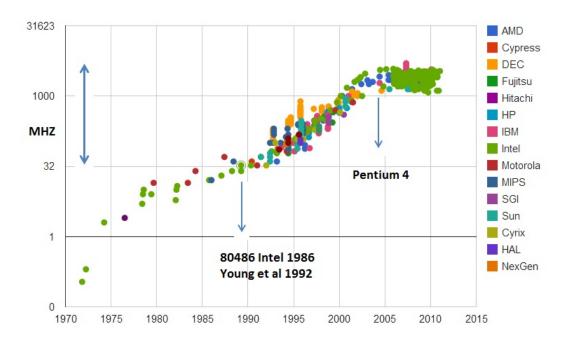

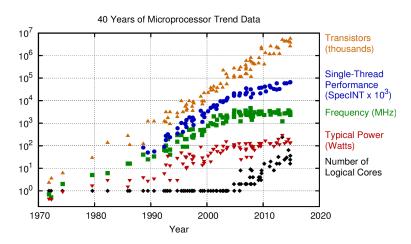

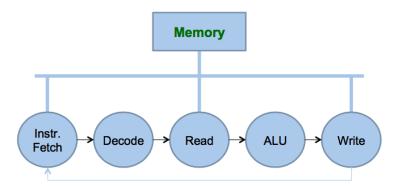

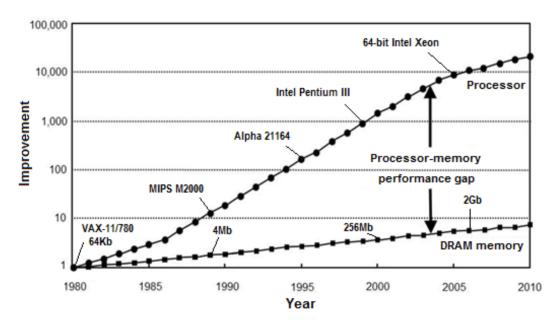

évolué d'un facteur 1000 tous les 11 ans pendant près de 20 ans. Durant cette période, les processeurs ont pu profiter de nombreuses évolutions technologiques (voir figure 1.2) : augmentation du nombre de transistors et de la fréquence des processeurs, augmentation du nombre de coeurs ou encore l'implémentation d'une hiérarchie mémoire accélérant les accès aux données.

Pour atteindre une puissance de 10<sup>18</sup> FLOPS (un exaFLOPS), nous pouvons ainsi nous demander s'il ne suffirait pas d'attendre les prochaines générations de processeurs et d'augmenter le nombre de serveurs formant un supercalculateur. Malheureusement, nous constatons, depuis 2012, un ralentissement de l'évolution des performances des supercalculateurs. Il faut depuis cette date attendre 23 ans, contre 11 jusqu'en 2012, pour voir la performance des supercalculateurs évoluer du même facteur 1000. Ce ralentissement est dû à un ensemble de contraintes qu'il n'est plus possible d'éviter, dont les deux principales sont :

- la fin de la validité de loi de Moore [Moo75], qui prévoyait l'augmentation du nombre de transistors chaque année;

- la fin de la loi de Dennard [Den+74], qui assurait l'augmentation de la fréquence de chaque nouvelle génération de processeur.

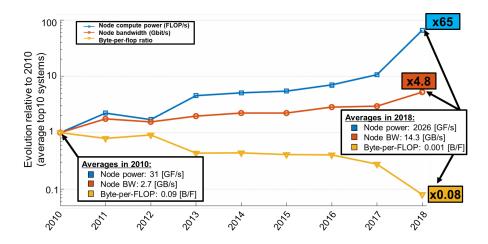

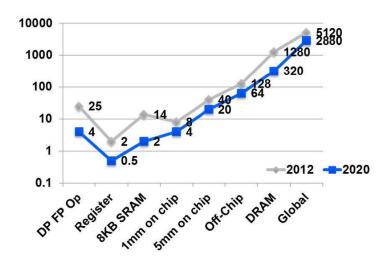

De plus, les systèmes mémoires et les capacités de traitement des processeurs ont évolué inégalement. Lorsque la performance calculatoire augmentait de 50% chaque année, le débit mémoire n'augmentait que de 23%. Ce déséquilibre entre ces deux parties fondamentales de l'architecture Von Neumann a donné naissance au "mur de la mémoire" [Wil01]. À cause de cette inégalité d'évolution, les supercalculateurs modernes ne parviennent à extraire qu'une fraction des performances théoriques des architectures. Celle-ci est même couramment inférieure à 10% [Oli+05] lors de l'exécution d'applications HPC utilisées dans le domaine du calcul scientifique.

En plus des freins présentés ci-dessus, de nombreux défis supplémentaires doivent être relevés afin de poursuivre le rythme d'évolution des performances des supercalculateurs. Plusieurs études [Sut05; Kog+08; Luc+14; HPE16] prédisent depuis plusieurs années les principales difficultés rencontrées pour développer une plateforme exascale :

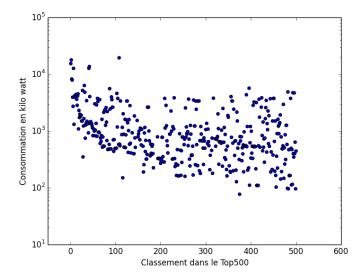

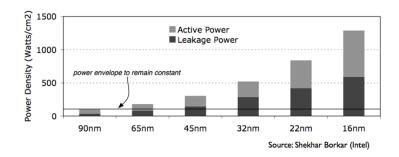

- amélioration de l'efficacité énergétique : la consommation électrique des plateformes doit être réduite de plusieurs facteurs pour permettre l'exécution de 10<sup>18</sup> opérations par secondes. Le défi énergétique s'applique à l'ensemble de la plateforme (processeur, mémoire, systèmes d'interconnexion et de refroidissement);

- développement de nouvelles technologies mémoire : de nouvelles mémoires doivent être développées permettant de fournir un débit suffisamment élevé et des capacités adaptés à l'exécution d'applications exascale;

- amélioration de la performance (débit, latence) des technologies d'interconnexion;

- résistance aux erreurs, sécurité des données sensibles, productivité des utilisateurs, etc.

Le principal défi est celui de l'énergie. Avec les technologies actuelles, un supercalculateur exascale consommerait plusieurs centaines de mégawatts, équivalent à la consommation électrique de deux villes comme Gap (19 000 foyers). Pour des raisons de coût et de faisabilité, l'objectif de l'industrie HPC est de construire une plateforme exascale consommant entre 20 et 30 MW.

FIGURE 1.1 – Évolution de la performance cumulée des 500 supercalculateurs les plus puissants au monde, mesurée en FLOPS à l'aide de l'application HPL [DLP03].

FIGURE 1.2 – Évolution des principales caractéristiques des processeurs (données originales tirées de [Rup15]  $^4$ ).

<sup>4.</sup> Les données sont accessibles sur le dépôt GitHub de l'auteur : https://github.com/karlrupp/microprocessor-trend-data

Le challenge est donc de construire une plateforme sept fois plus puissante que le supercalculateur le plus puissant actuel, tout en étant trois fois plus efficace énergétiquement. Les déplacements de données à l'intérieur (entre la mémoire et le processeur) et à l'extérieur (entre deux serveurs) des serveurs sont les principales opérations consommatrices d'énergie. Cette consommation peut être en partie expliquée par la complexité des microarchitectures, mais aussi par les technologies d'interconnexion utilisées. La complexité des processeurs récents, due aux nombreuses améliorations qu'ils ont connues ces dernières années (hiérarchies mémoire, pipeline, unité de préchargement mémoire), est à l'origine de la difficulté des applications à extraire plus d'une fraction des performances théoriques disponibles.

## 1.1.2 Les opportunités

L'incapacité des technologies actuelles à réaliser efficacement des calculs et l'explosion du nombre de données à traiter nécessite de repenser les matériels utilisés et l'architecture des systèmes informatiques. Heureusement de nouvelles technologies sont développées et représentent de réelles opportunités pour le développement des prochaines générations de plateformes de calculs.

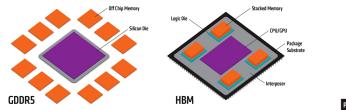

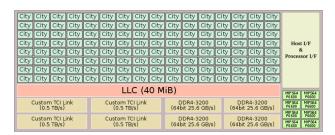

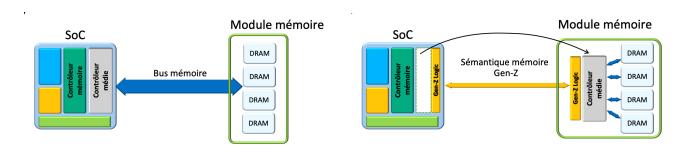

La première opportunité vient du développement de nouvelles technologies mémoire permettant de combler la différence d'évolution de performance constatée entre les processeurs et les mémoires. La faiblesse des débits mémoires et la consommation électrique du système mémoire obligent les architectures à évoluer drastiquement :

- la première solution est de rapprocher ces espaces mémoire des zones de calculs en plaçant la mémoire sur les puces de calculs (On Package Memory) ou en réalisant les calculs directement en mémoire (In Memory Computing);

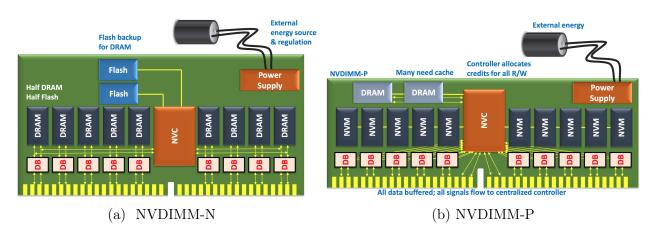

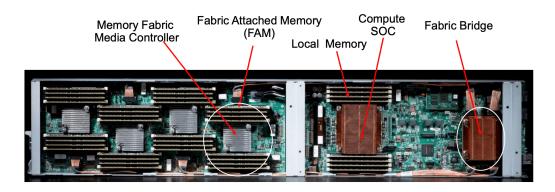

- la seconde solution est de développer de nouvelles technologies mémoire afin de combler le trou séparant les caractéristiques des mémoires DRAM et des disques de stockage flash. Pour cela des technologies NVRAM (non-volatile RAM) sont développées en s'appuyant notamment sur de nouvelles technologies mémoire SCM (Storage Class Memory).

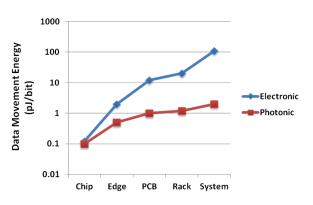

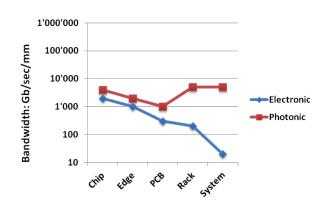

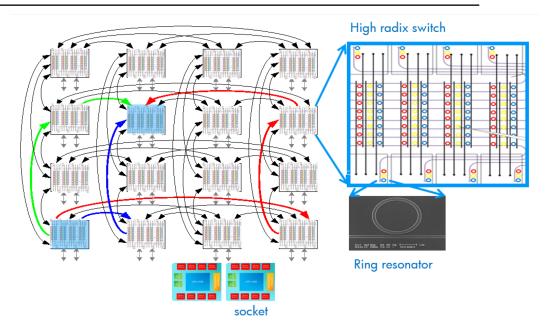

Une deuxième opportunité technologique pouvant aider à l'élaboration d'une plateforme exascale est le développement de technologies photoniques. Ces technologies utilisent la lumière pour transférer des informations et permettre d'atteindre des débits élevés avec des latences faibles. Une autre qualité de ces technologies est d'être indépendantes de la distance. Bien que la génération d'un signal optique ou électronique nécessite la même énergie, celle-ci n'évolue que faiblement avec la distance de communication. Le coût énergétique d'un accès mémoire local est alors proche de celui d'un accès distant.

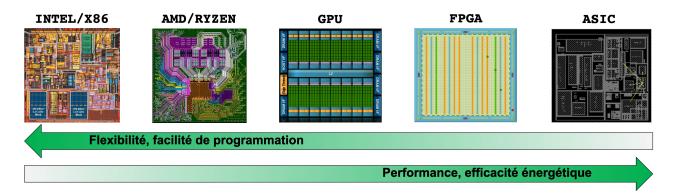

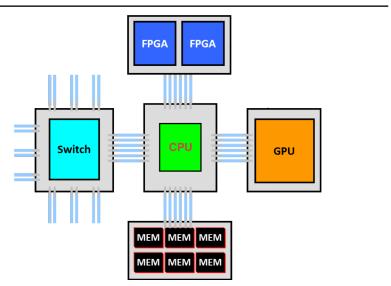

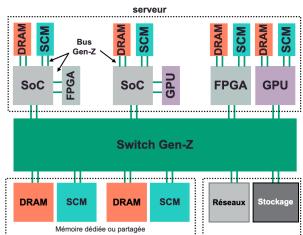

Ces nouvelles technologies, associées aux méthodes de co-design qui associent les utilisateurs et les fabricants, vont permettre de développer de nouvelles architectures optimisées pour certains algorithmes. L'utilisation d'architectures spécialisées pour l'exécution de certains codes dans une même plateforme a été démocratisée par l'utilisation massive des GPU. Cette approche de plateformes hétérogènes doit être poursuivie avec de nouvelles architectures très différentes de celles actuellement utilisées : les accélérateurs produits par Google (TPU), NEC

(SX-Aurora), ou encore Pezy (PEZY-SC2).

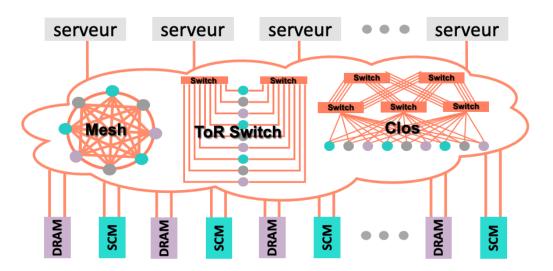

Afin de faciliter l'intégration de ces nouvelles technologies (mémoires, processeurs) provenant de différents constructeurs, un nouveau protocole est en cours de développement. Nommé Gen-Z, ce projet est développé par 70 des plus grandes sociétés des technologies de l'information (IT). Il repose sur l'utilisation d'un protocole de communication à sémantique mémoire load/store. Gen-Z permettra d'adresser un espace mémoire mille fois plus grand que notre espace numérique actuel et interconnecter 16 millions d'objets sur une même matrice de commutation (fabric). Les premières versions d'architecture Gen-Z permettront d'atteindre des débits mémoires de plusieurs téraoctets par seconde contre quelques centaines de gigaoctets actuellement.

## 1.2 Travail de thèse

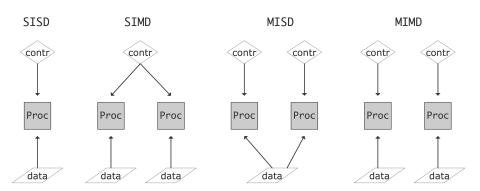

De nouvelles technologies vont permettre à l'industrie d'implémenter cette vision du calcul extrême qui consiste à l'exécution d'applications demandant des ressources dépassant de très loin les moyens disponibles actuels (villes intelligentes, analyse de données, etc.). Afin que l'exécution de ces applications puisse être réalisée dans des contraintes raisonnables (temps, budget, complexité), le calcul extrême nécessite de revoir l'architecture des plateformes de calculs de manière holistique. Face à l'explosion de la quantité de données générées, il est indispensable de repenser l'architecture des centres de données, mais aussi de la plateforme permettant leur collection, leur transfert et leur analyse.

# 1.2.1 Problématique

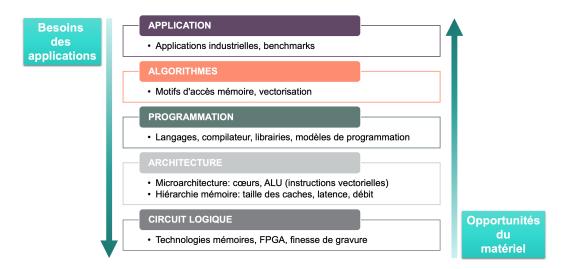

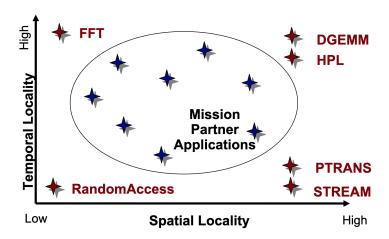

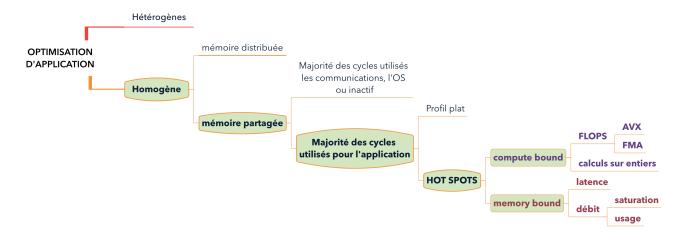

Pour subvenir au besoin de puissance grandissant et ne pouvant compter sur les anciens leviers à sa disposition, l'industrie doit s'appuyer sur l'utilisation de nouvelles technologies émergentes qui permettront de faire des sauts de performance de plusieurs facteurs (10, 100 voir 1000). Grâce au protocole universel Gen-Z et aux nouvelles technologies présentées précédemment, de nombreuses architectures vont être développées et seront très différentes de celles que nous utilisons actuellement (processeurs x86, GPU). Ces processeurs seront alors très efficaces pour l'exécution de certains types d'opérations et d'algorithmes. Afin de répondre aux besoins de performances supplémentaires et relever le défi de l'efficacité énergétique, il est nécessaire d'utiliser les architectures les plus adaptées pour l'exécution d'une application. Pour ce faire, trois tâches principales doivent être réalisées :

- 1. La première tâche est de caractériser l'ensemble de ces architectures pour trouver leurs forces et leurs faiblesses : débit et latence mémoire, capacité calculatoire, performance du système mémoire pour certains motifs d'accès, etc. Ces nouvelles architectures pouvant être très différentes de celles que nous utilisons actuellement, il est indispensable de disposer d'un ensemble d'outils permettant de les caractériser pour différents types d'algorithmes.

- 2. La deuxième tâche consiste à modéliser les performances d'une application pour en connaître ses besoins (débit et/ou latence mémoire, calcul vectoriel, système d'intercon-

nexion, stockage, etc.). Les gains de performance ne viendront pas seulement de l'utilisation d'accélérateurs puissants, mais de leur diversité et de la capacité des programmeurs à bien les utiliser. Pour une même application, plusieurs zones de code prenant une part importante dans son exécution peuvent avoir des besoins différents. Il est ainsi nécessaire de pouvoir identifier ces zones et de les modéliser indépendamment.

3. La troisième tâche est de sélectionner les architectures adéquates pour une application et adapter le code pour permettre son exécution. Il est ensuite nécessaire de pouvoir mesurer les performances de l'application et d'appliquer les optimisations adaptées pour obtenir une part significative de la performance théorique.

#### 1.2.2 Travaux existants

Afin de répondre aux tâches présentées ci-dessus, les programmeurs doivent alors avoir à leur disposition un ensemble d'outils permettant de caractériser le comportement des architectures et d'étudier la performance de leurs applications lors de l'exécution.

#### 1.2.2.1 Caractérisation des architectures

Afin de caractériser les architectures et d'en mesurer les performances atteignables, il est courant d'utiliser des benchmarks. En informatique, un benchmark est un code, ou un ensemble de codes, permettant de mesurer la performance d'une solution et d'en vérifier ses fonctionnalités. Dans ce travail de thèse, nous nous intéressons à la caractérisation de deux composants fondamentaux des processeurs utilisés pour l'exécution d'applications HPC : la hiérarchie mémoire et les unités de calcul vectorielles.

Caractérisation du système mémoire : le système mémoire étant la principale ressource limitant la performance des applications HPC, de nombreux travaux ont été menés pour aider à sa caractérisation. Le plus utilisé d'entre eux est le benchmark STREAM [McC95]. Ce code utilise 4 noyaux de calculs différents pour mesurer le débit mémoire atteignable par une architecture. Pour cela, un tableau de nombres aléatoires stocké en mémoire est accédé par des instructions de lecture/écriture pour réaliser quatre opérations différentes (copy, scale, add, triad). La simplicité de ces codes permet souvent d'atteindre les débits maximaux du bus mémoire et fait de STREAM un benchmark de référence. Un autre benchmark largement utilisé dans l'industrie est celui de Lmbench [Sta05]. Lmbench est une suite de microbenchmarks utilisée pour mesurer la latence et le débit atteignable par un coeur pour différentes opérations : accès mémoire, ouverture de fichier, création de pipes, etc. Il permet aussi de trouver certaines caractéristiques de la microarchitecture comme la taille d'une ligne de cache, la fréquence du processeur ou encore la taille et la latence du répertoire de pages actives (TLB).

Que ce soient STREAM, 1mbench ou d'autres benchmarks mémoires [YPS05; Lus+06; Gon+10; DH13; BLK18], aucun code disponible ne permet de caractériser la hiérarchie mémoire lors d'accès mémoire par sauts d'adresses. De nombreuses applications utilisent des accès mémoires

réalisant des sauts d'adresses (stride) de taille constante. Par exemple, le parcours d'un tableau d'objet pour accéder à un certain champ ou le parcours d'une matrice (en ligne ou en colonne). Pour accélérer ces accès, l'unité de préchargement mémoire peut anticiper les prochaines adresses accédées en comprenant le motif d'accès utilisé et commencer leur chargement avant qu'elles ne soient accédées. Pour des applications utilisant ce type d'accès par saut, il est primordial que ce composant fonctionne correctement pour réduire au maximum le défaut de cache (miss) d'une donnée dans le cache lors de son accès. Le benchmark s'approchant le plus de cet objectif est celui de Saavedra [SS95]. Il utilise une taille de saut fixée au début de l'exécution pour accéder à un jeu de données. La taille de ce dernier doit être un multiple d'une puissance de 2 et ne permet pas de dépasser la taille du dernier niveau de cache. Le problème d'une telle approche est de vouloir mesurer tous les niveaux de la hiérarchie simultanément. Les mesures peuvent alors être influencées par différents paramètres de différents niveaux de caches.

Caractérisation des unités de calculs vectorielles : la majorité des applications utilisées en HPC exécutent des opérations à virgule flottante (FLOP). Ces instructions sont exécutées par un matériel spécialisé nommé unité de calcul à virgule flottante (FPU). La capacité des FPU à exécuter plusieurs instructions vectorielles par cycle est alors primordiale pour la bonne performance des applications. La littérature dénombre plusieurs benchmarks couramment utilisés pour mesurer la performance de calcul des processeurs. Le benchmark HPL [DLP03] a été développé pour caractériser la microarchitecture d'un processeur lors de la résolution de problèmes algébriques. Ce code permet aujourd'hui de mesurer et classer les supercalculateurs dans le classement du Top500. Cependant, la simplicité du benchmark HPL n'est pas représentative d'applications réelles. Ainsi, un ensemble de codes a été rassemblé pour améliorer la caractérisation des supercalculateurs. Nommée HPCG [DH13], cette suite de codes permet de couvrir plusieurs motifs de communication et de calculs. Les versions récentes du Top500 publient pour certains supercalculateurs la performance obtenue sur le benchmark HPCG. Nous pouvons aussi citer le benchmark HPCC [Lus+06] qui est une suite de 6 benchmarks contenant notamment HPL et STREAM. Un seul exécutable est généré pour l'ensemble de la suite permettant d'éviter l'utilisation de certaines optimisations pour un code particulier (pages larges, réglage BIOS, utilisation d'une fréquence définie, etc.).

Les benchmarks existants se basent sur des noyaux de calcul (kernels) qui permettent de mesurer la performance que d'un ensemble d'opérations restreint. Une grande majorité des benchmarks n'utilisent pas de code assembleur. La performance mesurée peut alors fortement varier avec la qualité du compilateur utilisé. Ainsi, nous constatons le manque d'un outil permettant de valider précisément les performances des FPU. Un tel outil permettrait de mesurer le nombre d'instructions par cycle que le processeur est capable d'exécuter en faisant varier différents paramètres : type d'opérations, taille des instructions vectorielles, mélange d'instructions différentes, ajout de chaînes de dépendances, etc.

#### 1.2.2.2 Suivi de performance des applications

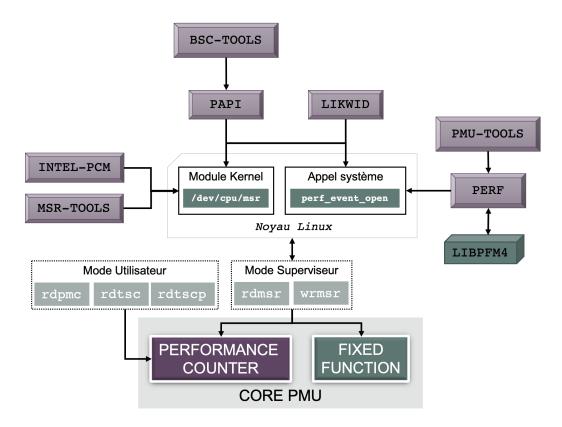

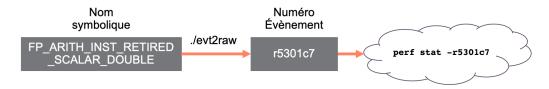

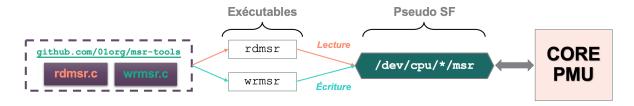

Le deuxième aspect de nos recherches concerne le suivi de performances des applications. L'objectif de celui-ci est de récolter des informations concernant l'exécution de l'application. Ces informations peuvent être obtenues en instrumentant le code (manuellement ou grâce au compilateur) ou en récupérant certaines informations de l'architecture. Pour cela, les processeurs possèdent des registres (compteurs) qui permettent de compter des événements (matériels ou logiciels) avec un faible impact sur l'application exécutée. Chaque famille de processeurs possède un jeu différent de compteurs matériels pouvant avoir des noms différents, rendant leur programmation difficile. Afin de faciliter leur programmation, des interfaces comme PAPI [Bro+00] et Perf Events [Wea13] ont été développées. Celles-ci permettent de développer des outils sans se préoccuper de l'implémentation matérielle des compteurs facilitant ainsi la portabilité des outils. Nous pouvons notamment citer les outils d'Intel (VTune), de Linux (perf) ou encore ceux développés au Barcelona Supercomputing Center (Extrae [Rod], Paraver [Pil+95] et Dymemas [LGC97]).

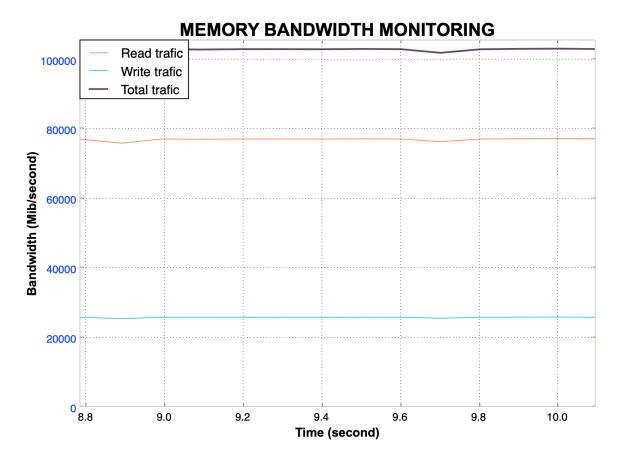

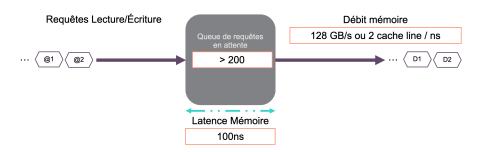

Afin de répondre aux différentes tâches de la problématique traitée dans ce travail de thèse, deux outils principaux sont nécessaires. Le premier doit permettre de suivre l'activité du bus mémoire. Ce bus est une ressource critique des architectures modernes, rendant sa bonne utilisation indispensable. Il est donc nécessaire de posséder un outil permettant de suivre l'état du trafic sur ce bus. Pour cela, des outils existent, mais sont soit propriétaires, soit trop complexes pour être facilement installés sur des architectures novatrices. Un second outil doit être capable d'extraire les zones de codes les plus intéressantes à porter sur ces nouvelles architectures. Les supercalculateurs seront hétérogènes et utiliseront plusieurs types d'accélérateurs adaptés à certaines fonctions. Une même application pourra alors faire appel à plusieurs d'entre eux. Il est donc nécessaire de posséder un outil permettant de caractériser les différentes fonctions d'une même application en extrayant ces zones de codes et en les caractérisant. Ce même outil pourrait alors aussi être utilisé pour comprendre les performances de l'application et appliquer les optimisations adéquates.

# 1.3 Contributions et plan du manuscrit

L'industrie va faire face à une multitude de révolutions technologiques (nouvelles mémoires, interconnexion photonique, protocole Gen-Z) et les utilisateurs de supercalculateur doivent se préparer à ces changements profonds pour pouvoir les exploiter au maximum. Contrairement aux évolutions précédentes où il suffisait d'installer un nouveau processeur ou d'ajouter des barrettes mémoires, il faut repenser entièrement notre façon d'appréhender les architectures des supercalculateurs et adapter les algorithmes qui y seront exécutés. Cependant, en l'absence de méthode de caractérisation fine de la performance des codes, ces architectures innovantes sont potentiellement condamnées puisque peu d'experts savent les valoriser. En effet, la loi de Moore [Moo75] a permis d'assurer une évolution constante de la performance des processeurs, laissant les domaines de l'analyse et de l'optimisation des codes, alors économiquement non rentables, en

second plan. Ainsi, nous avons constaté à travers de nombreuses rencontres avec les utilisateurs, mais aussi par les expériences internes à HPE, le manque d'outils et de connaissances nécessaires à la réalisation de ce travail.

#### 1.3.1 Contributions

Ce travail de thèse contribue à l'étude du domaine du calcul haute performance. Le déroulement de cette thèse dans un cadre industriel a permis de réaliser un large état de l'art de ce domaine complexe. Nous regroupons et expliquons les principaux défis auxquels les constructeurs font face dans le développement des prochaines générations de supercalculateurs. Afin d'y répondre, nous présentons les principales opportunités technologiques qui vont permettre de relever les défis présentés et notamment de la nécessité d'utiliser des architectures novatrices pour soutenir la contrainte énergétique.

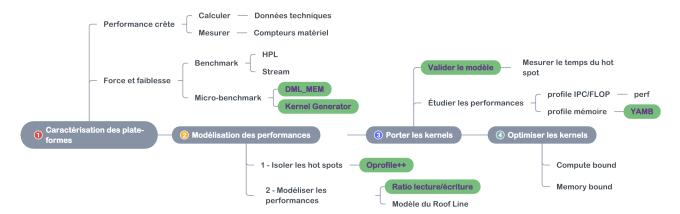

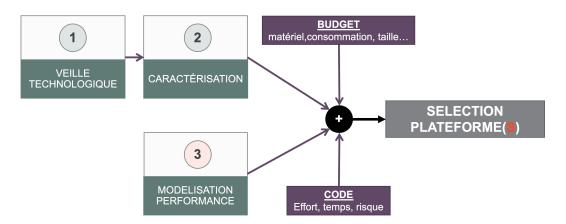

Afin de pouvoir profiter de ces nouvelles technologies, nous proposons dans ce travail une méthodologie en 5 étapes permettant de modéliser les performances d'une application, de les projeter sur de nouvelles architectures et d'en extraire la performance maximale. Pour chaque étape, nous avons développé et sélectionné des outils permettant de répondre aux challenges présentés et qui respectent les critères suivants :

- Les sources de l'outil doivent être disponibles pour permettre de les adapter à des architectures différentes et pour développer une communauté d'utilisateurs autour de ces sujets.

- Les outils doivent être simples, ne cherchant pas à répondre à une multitude de questions, ce qui rend généralement difficile leur portabilité, mais aussi les conclusions pouvant être tirées des résultats obtenus. La simplicité des outils permet aussi de réduire leur dépendance à des bibliothèques externes, souvent difficiles à installer dans les environnements HPC.

- Les outils doivent permettre d'analyser des applications HPC dont l'exécution peut durer plusieurs heures. Il faut aussi réduire au maximum la nécessité de posséder des droits spéciaux (root) pour les utiliser, ce dernier étant rarement disponible pour les utilisateurs de supercalculateurs.

Contrairement à une majorité d'outils existants, ceux développés durant ce travail de thèse n'ont pas vocation d'automatiser entièrement le travail d'analyse. La puissance de ces outils vient de leur utilisation complémentaire. Leur utilisation assume que l'utilisateur possède de solides connaissances. En fournissant une méthodologie permettant de bien les utiliser et en réduisant la complexité de l'outillage, nous espérons que leur adoption auprès des programmeurs sera plus grande. Un outil a été développé pour chaque étape de la méthodologie lorsqu'aucun programme existant ne répondait aux besoins, ou qu'il ne respectait pas les critères énoncés ci-dessus. La principale difficulté concernant l'utilisation ou le développement d'outils concerne leur compatibilité avec différentes architectures. Celles-ci pourront être produites par différents constructeurs (Intel, ARM, IBM, Nvidia, etc.), il était donc primordial d'utiliser ou de développer des outils ayant le plus de chances d'être compatibles avec ces nouvelles architectures.

Ce besoin de compatibilité nous a obligés à restreindre la dépendance des outils à certaines fonctionnalités des processeurs, notamment l'utilisation des compteurs matériels complexes.

**Développements :** les principales contributions de cette thèse sont le développement de quatre outils accessibles en libre accès <sup>5</sup> [Pou20] :

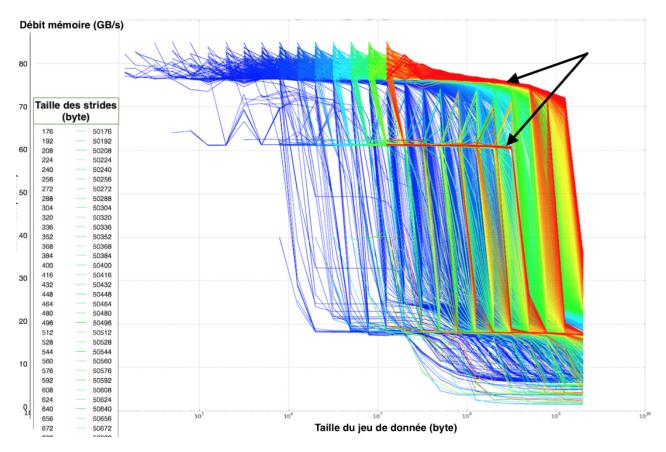

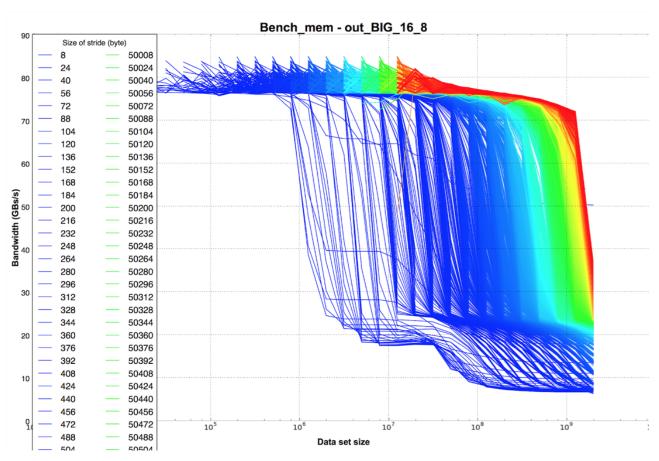

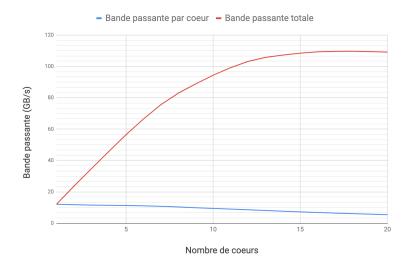

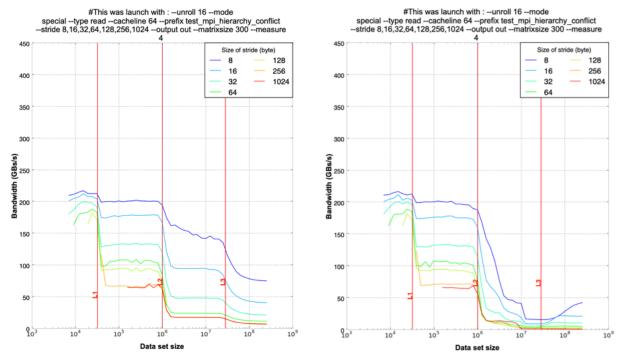

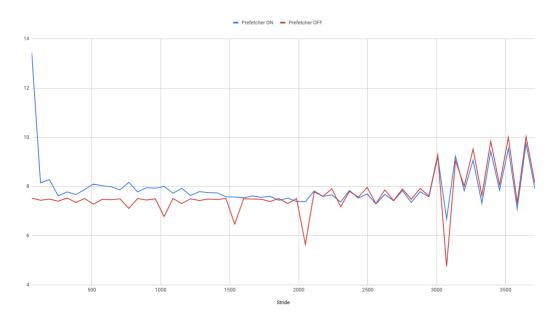

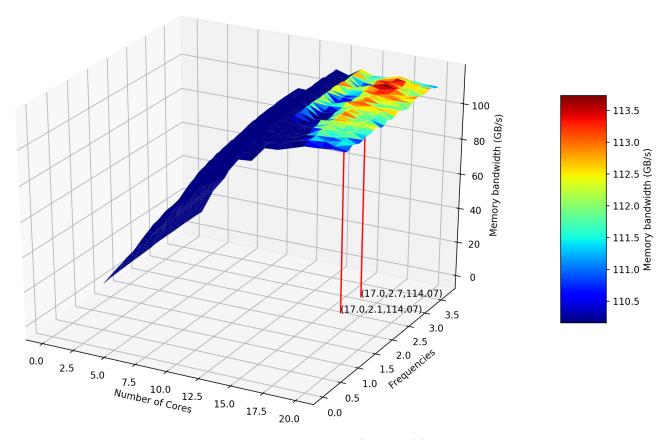

- 1. Un benchmark mémoire DML\_MEM: ce benchmark permet de mesurer le débit mémoire en réalisant des accès dans un tableau avec des motifs de sauts (strides). La taille du tableau et des sauts peut varier et permet de caractériser les différents niveaux de la hiérarchie mémoire. Cet outil est utile pour caractériser une nouvelle architecture, mais peut aussi être utilisé lors du design d'un nouveau processeur pour vérifier le bon fonctionnement du prélecteur mémoire.

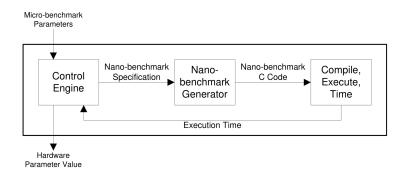

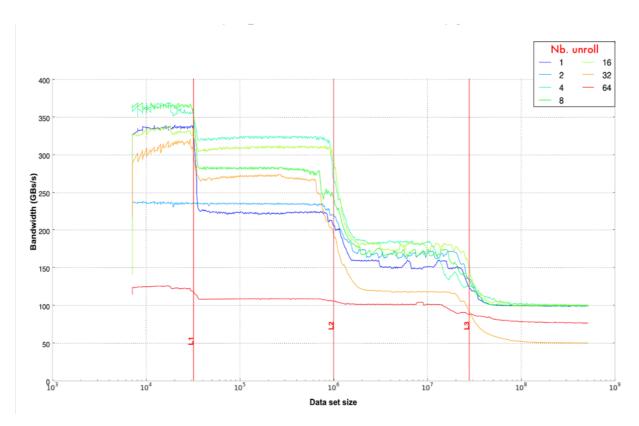

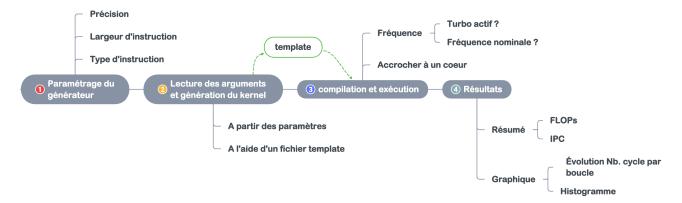

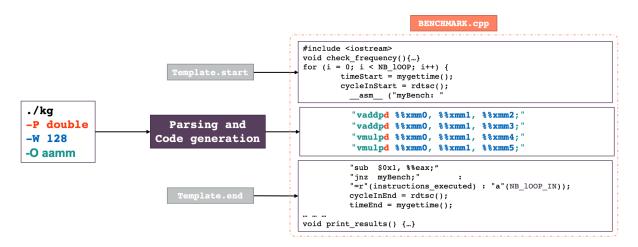

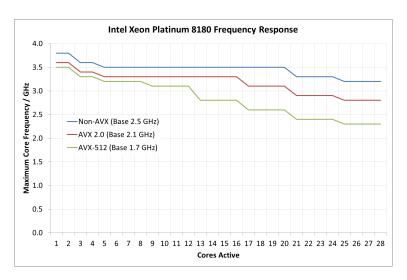

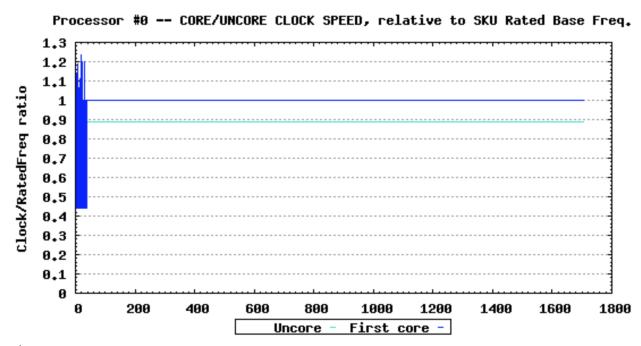

- 2. Un benchmark de FPU Kernel Generator : ce générateur permet de caractériser finement la performance des unités de calcul en virgule flottante (FPU). Pour cela, il génère un benchmark assembleur en utilisant des instructions vectorielles de taille différentes (SSE, AVX2, AVX-512). L'utilisateur peut alors choisir le type d'opération à exécuter (addition, multiplication, FMA) et la précision (simple, double). La partie du benchmark mesurée ne contient que des instructions de calculs et permet de mesurer très précisément la performance atteignable par le processeur (souvent proche ou égale à la performance théorique).

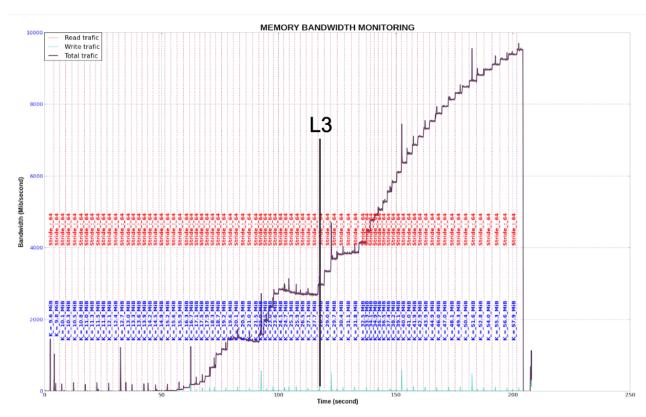

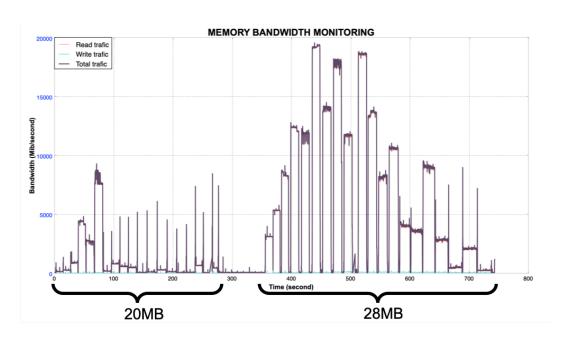

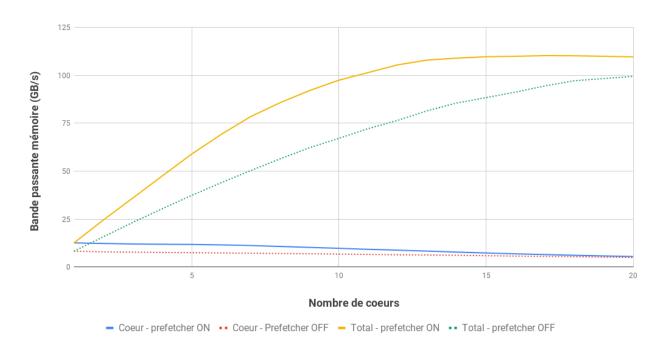

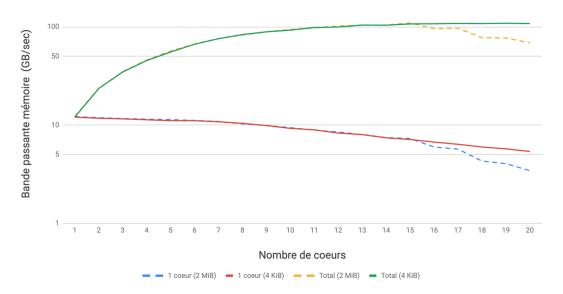

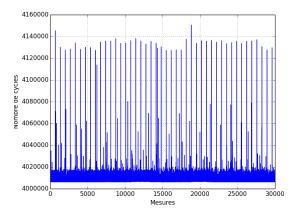

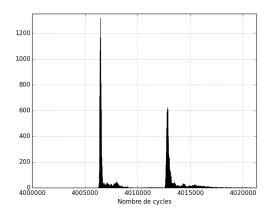

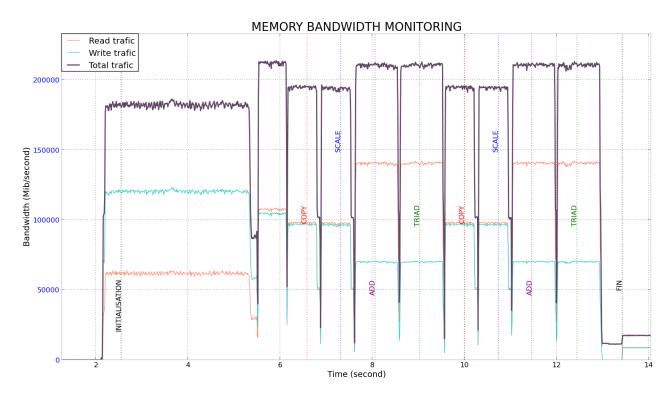

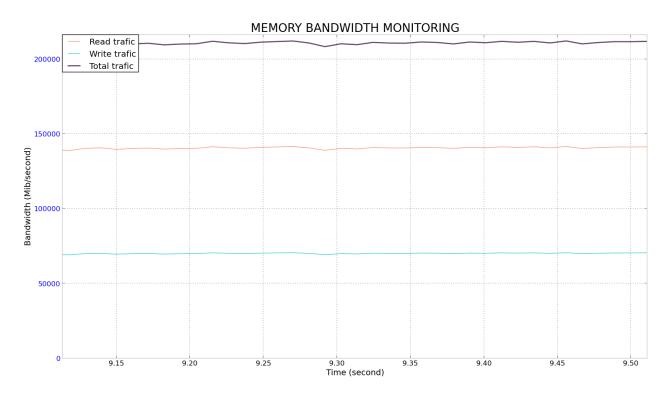

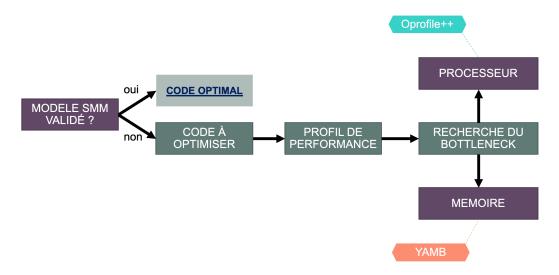

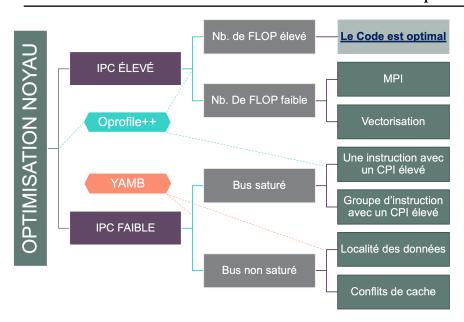

- 3. Un outil de suivi d'activité du bus mémoire YAMB : cet outil permet de suivre le trafic du bus mémoire. Pour cela, l'outil mesure l'activité de chaque contrôleur mémoire à l'aide de l'interface Perf Events en comptant le nombre de transactions (lecture et écriture) ainsi que le nombre d'accès manqués (miss) dans le dernier niveau de cache (LLC). Pour corréler l'activité du bus avec les parties du code qui en sont responsables, le graphique peut facilement être annoté en utilisant une bibliothèque C/C++/Fortran, appelée directement depuis le code source.

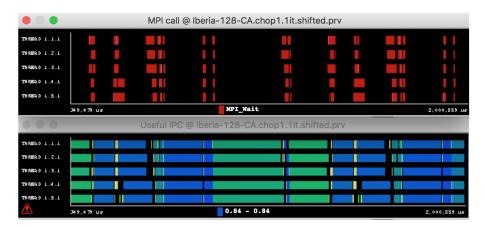

- 4. Un outil d'analyse de performance Oprofile++ : cet outil permet de désassembler le code d'une application, d'extraire les points chauds (hot spots) et d'en mesurer leur performance. Dans un premier temps, l'outil relie le profil de performance obtenu lors de l'exécution aux instructions assembleurs exécutées. Ensuite, il s'occupe d'extraire les boucles critiques et de mesurer le nombre d'instructions réalisées par cycle d'horloge (IPC). Il est ensuite possible de quantifier des opportunités d'amélioration, mais aussi de prédire la performance en fonction d'une amélioration du matériel ou du logiciel.

<sup>5.</sup> Répertoire Github regroupant les différents outils développés durant la thèse - https://github.com/PourroyJean/performance\_modelisation

Publications et communications : durant cette thèse, plusieurs occasions nous ont permis de communiquer et de partager nos résultats :

- L'outil Kernel Generator a fait l'objet d'une publication [PDC19] et d'une présentation dans une conférence internationale :

Jean Pourroy, Patrick Demichel et Denis Christophel. « Assembly micro-benchmark generator for characterizing Floating Point Units ». In: HPCS 2019 17th International Conference on High Performance Computing & Simulation. Dublin, Ireland: IEEE, juil. 2019

- 2. Un large état de l'art des compteurs matériels et des outils de suivi de performance à été présenté à l'occasion de la conférence HPE TSS 2018 <sup>6</sup> à La Haye (Pays-Bas). Cette présentation a permis de présenter les différentes façons d'interagir avec les compteurs matériels présents sur les processeurs et de présenter un état de l'art des outils utiles pour la compréhension et l'optimisation d'une application.

- 3. La méthodologie et les différents outils développés durant ces travaux de thèse ont été présentés lors de la conférence HPE TSS 2019<sup>6</sup> à Paris. Cet exposé nous a permis de présenter la méthodologie mise en place permettant d'utiliser les outils développés pour faciliter la recherche de nouvelles architectures.

- 4. Les travaux de thèse ont fait l'objet d'une présentation lors de la conférence interne HPE Tech Con 2020. Sur 548 papiers seul 16 d'entre eux ont été retenus par un comité d'experts reconnu dans ce domaine. La sélection d'un papier lors de cette conférence montre l'importance des travaux présentés aux yeux de l'entreprise.

**Autres évènements :** lors de ces quatre années de thèse, différents évènements ont permis de partager et d'appliquer les différents outils développés :

- 1. Nous avons délivré une formation de deux jours à l'ENS Cachan pour une vingtaine de participants venant du monde académique, comme du monde industriel. Cet évènement fut l'occasion de présenter les premiers développements, mais aussi de partager notre méthode de travail avec des développeurs spécialisés du domaine.

- 2. Les outils d'analyse de performance ont été utilisés pour remporter le Hackaton du HPC 2018. Ce concours, organisé par GENCI (Grand Équipement National de Calcul Intensif), et sponsorise par Intel, avait pour objectif d'optimiser une application de calcul distribué MPI pour la dynamique de systèmes particulaires. En utilisant les outils d'analyse de performance et en appliquant les optimisations adaptées, une accélération d'un facteur 10 a pu être réalisée permettant d'obtenir le prix de la meilleure optimisation [Pou+18].

<sup>6.</sup> Hewlett Packard Enterprise Technology & Solutions Summit (HPE TSS) est l'événement annuel de Hewlett Packard Enterprise le plus important et le plus complet en matière de transfert de connaissances techniques et de solutions pour les communautés techniques HPE et partenaires d'Europe, du Moyen-Orient et d'Afrique - https://h41382.www4.hpe.com/tss/application/assets/pdf/TSS.WhyAttendPartner.pdf

#### 1.3.2 Plan du manuscrit

Cette thèse propose une analyse étendue du domaine du HPC pour comprendre et contribuer à l'élaboration des prochaines générations de plateformes de calculs. Pour cela, le manuscrit suit la structure suivante :

- Le chapitre 2 introduit le domaine du calcul haute performance en étudiant ses origines et en présentant leur architecture actuelle et les moyens employés pour les programmer. Nous discutons ensuite de leur performance en étudiant l'évolution du classement du Top500 et nous expliquons les principaux freins qui empêchent de construire des plateformes toujours plus puissantes avec les méthodes actuelles consistant à ajouter indéfiniment des serveurs. Afin d'y parvenir, nous présentons les principales opportunités technologiques actuellement développées qui vont nous permettre de repenser l'architecture des plateformes. La fin de ce chapitre s'intéresse plus précisément à la caractérisation des microarchitectures et à l'analyse de performance d'applications.

- Le chapitre 3 présente les principaux outils développés durant ces travaux de thèse. Nous discutons des motivations et des critères de développement qui nous ont conduits à développer deux benchmarks et deux outils d'analyse de performance.

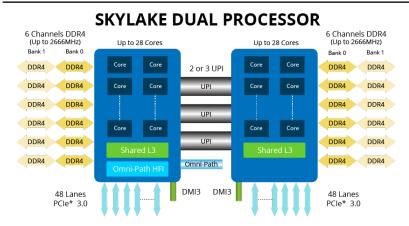

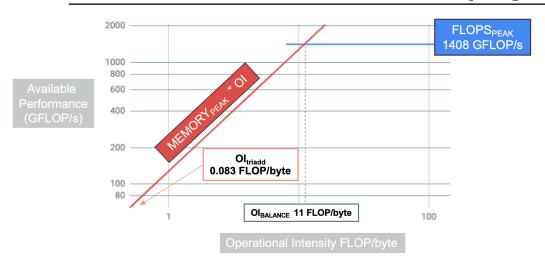

- Le chapitre 4 présente la méthodologie élaborée et utilisée pour caractériser et choisir une architecture pour une application donnée. Nous utilisons l'analyse du benchmark STREAM et d'un processeur Intel Skylake pour illustrer chacune des 5 étapes.

Afin de permettre la réalisation des différents codes développés, l'étude approfondie des différentes évolutions technologiques des processeurs et des techniques de suivi de performances sont présentées dans deux annexes :

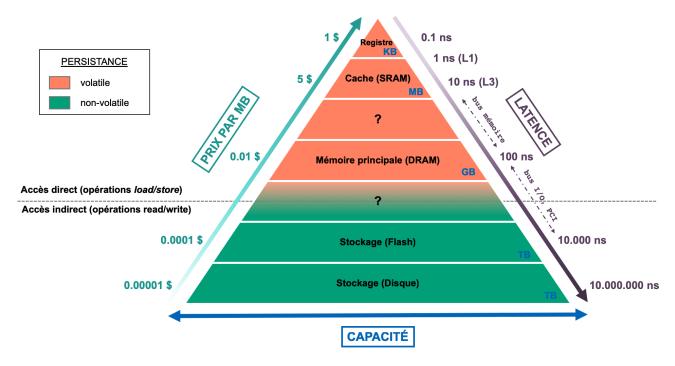

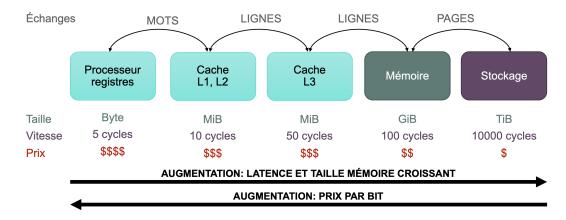

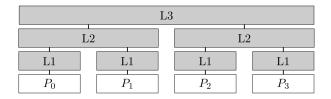

- L'Annexe A couvre l'origine et l'évolution de la microarchitecture des processeurs. Nous présentons les fonctionnalités clés des processeurs modernes qu'il est nécessaire de connaître pour comprendre la performance des applications : pipeline, instructions vectorielles, etc. Nous étudions plus précisément la hiérarchie mémoire qui est la ressource critique de nombreuses applications.

- L'Annexe B présente les compteurs matériels. Ces registres spéciaux du processeur permettent de suivre l'exécution d'une application en mesurant le nombre d'évènements logiciels et matériels. La programmation des compteurs est très difficile et nécessite le recours à des codes bas niveaux. Plusieurs méthodes peuvent alors être employées et demandent une bonne expérience pour être mises en oeuvre.

Nous faisons référence à ces deux annexes lorsque les concepts qui y sont étudiés sont utilisés dans le manuscrit.

# Calcul Haute Performance

Ce chapitre présente un état de l'art du domaine du HPC afin de motiver la nécessité de repenser l'architecture des supercalculateurs, mais aussi d'utiliser de nouvelles technologies. Pour comprendre quels challenges doivent être relevés, nous étudions le classement du Top500 et synthétisons les principaux freins au développement des performances des plateformes de calculs. Nous présentons ensuite les principales technologies qui devront être utilisées pour parvenir à développer les prochaines générations de supercalculateurs. Le chapitre se termine par l'étude des outils permettant la caractérisation et le suivi de performance des applications.

#### Sommaire

| 2.1 | Intro | oduction au Calcul Haute Performance (HPC)                    | 16        |

|-----|-------|---------------------------------------------------------------|-----------|

|     | 2.1.1 | Le calcul scientifique et la simulation numérique             | 16        |

|     | 2.1.2 | Le calcul haute performance                                   | 18        |

|     | 2.1.3 | Programmation parallèle et performance des supercalculateurs  | 25        |

|     | 2.1.4 | Performance de la parallélisation                             | 32        |

| 2.2 | Évol  | lution de la performance des supercalculateurs                | 34        |

|     | 2.2.1 | Comparer la performance des supercalculateurs                 | 34        |

|     | 2.2.2 | Évolution des performances des supercalculateurs              | 37        |

|     | 2.2.3 | Le futur du HPC                                               | 42        |

|     | 2.2.4 | Défis à relever pour l'élaboration d'une plateforme exascale  | 47        |

| 2.3 | Opp   | ortunités pour le développement de nouveaux supercalculateurs | <b>58</b> |

|     | 2.3.1 | Investissements financiers                                    | 58        |

|     | 2.3.2 | Nouvelles technologies mémoire                                | 60        |

|     | 2.3.3 | Nouvelles technologies d'interconnexion                       | 69        |

|     | 2.3.4 | Nouvelles architectures                                       | 72        |

|     | 2.3.5 | Gen-Z                                                         | 78        |

| 2.4 | Cara  | actérisation et analyse de performance des architectures      | 86        |

|     | 2.4.1 | Caractérisation des architectures                             | 87        |

|     | 2.4.2 | Analyse de performance d'une application                      | 94        |

| 2.5 | Con   | clusion                                                       | 110       |

# 2.1 Introduction au Calcul Haute Performance (HPC)

# 2.1.1 Le calcul scientifique et la simulation numérique

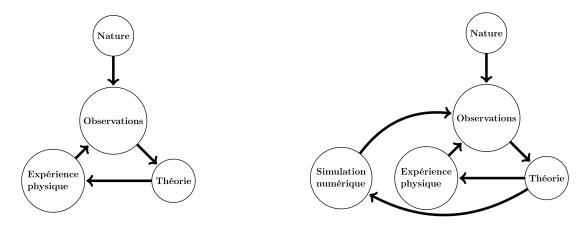

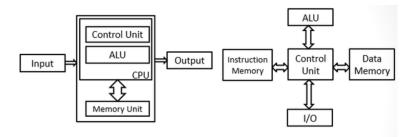

À l'origine, les scientifiques observaient la nature et émettaient des théories pour expliquer leurs observations (voir figure 2.1a). En se basant sur ces théories, ils réalisaient des expériences physiques pour les valider ou non. Ils faisaient alors de nouvelles expériences pour affiner leur théorie. Les simulations numériques sont alors apparues comme des alternatives aux expériences physiques qui étaient souvent longues et onéreuses (voir figure 2.1b). Des scientifiques comme Pythagore réalisaient ces simulations en faisant des calculs manuels ou en s'aidant de tables précalculées. Du fait de la limitation de leur capacité de calcul et du temps disponible, c'est avec l'apparition de l'informatique que les simulations numériques ont connu leur véritable essor.

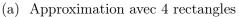

### 2.1.1.1 Principes de la simulation numérique

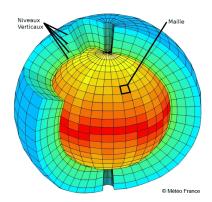

La majorité des simulations numériques sont basées sur des équations dites gouvernantes qui sont des approximations des phénomènes étudiés. Ces équations ont besoin d'être discrétisées pour pouvoir être exécutées par un ordinateur. En mathématiques, la discrétisation est un procédé qui permet de passer d'un modèle à son équivalent discret. Ce procédé ne permet pas de décrire le phénomène réel, mais de l'approcher avec plus ou moins d'erreurs. Pour améliorer ces simulations, ces représentations doivent utiliser des maillages les plus fins possible. La figure 2.2 montre comment Météo-France découpe une région à l'aide de mailles mesurant 2,5 km de côté. Une autre approche utilise des modèles probabilistes pour représenter un comportement. Cette approche est adaptée pour des phénomènes où chaque élément peut subir différents événements. Pour chaque étape du calcul, le résultat évolue grâce à des tirages aléatoires (méthode de Monte-Carlo [Kro+14]). Pour améliorer la précision des simulations, il est donc nécessaire d'augmenter

(a) Les expériences physiques permettent de valider les théories.

(b) La simulation numérique peut être une alternative aux expériences physiques.

FIGURE 2.1 – La simulation numérique a apporté une nouvelle façon d'expérimenter les théories.

FIGURE 2.2 – Le maillage le plus fin exploité par Météo-France <sup>1</sup>pour ses prévisions régionales restitue des mailles de 2,5 km de côté.

le nombre de tirages et donc le nombre de calculs à réaliser. Ainsi, que ce soit pour affiner la taille des maillages ou augmenter le nombre de tirages, les simulations numériques nécessitent de grandes puissances de calcul.

#### 2.1.1.2 Quelques applications de la simulation numérique

Lorsque nous évoquons la simulation numérique, nous pensons souvent aux domaines physiques (météorologie, mécanique, biologie). Cependant, elle est aussi largement utilisée dans d'autres domaines comme en sciences humaines (sociologie, analyse démographique) ou dans le domaine de la sécurité nationale. En effet, Alan Turing a développé les premiers ordinateurs lors de la fin de la Deuxième Guerre mondiale pour aider au décryptage des messages allemands. En 1936, il avait présenté les premiers concepts de programmes et donné naissance à l'aide d'une expérience de pensée à l'ancêtre des ordinateurs nommé machine de Turing. L'utilisation de simulations numériques a de nombreux avantages. En plus de profiter de la puissance de calcul des ordinateurs, elle permet de simuler des phénomènes dont les conditions ne sont pas reproductibles sur terre (physique théorique). Un autre avantage est de réduire drastiquement les coûts d'une expérience, par exemple pour la réalisation de crash automobile, où ce ne sont plus de réels modèles de voiture, mais bien des voitures virtuelles qui sont *crashées* sur des murs.

Dans le domaine de la santé, l'étude de la structure des protéines est primordiale. Ces molécules qui assurent les fonctions élémentaires d'une cellule interviennent dans la majorité des processus biologiques (régulation du métabolisme, défense immunitaire). Dans ce genre de simulation, le pas de temps est de l'ordre de la nanoseconde. Grâce à la simulation numérique, une meilleure compréhension de ces molécules permet la découverte de nouveaux médicaments ou antibiotiques. Aussi, des modélisations peuvent être utilisées pour analyser la propagation d'un virus comme la grippe aviaire à l'échelle mondiale pour mieux protéger les populations [CEA07]. En février 2020, le gouvernement français indiquait travailler sur la modélisation de la propa-

<sup>1.</sup> Source du graphique : http://www.irma-grenoble.com/

gation du COVID-19<sup>2</sup> (coronavirus). Cette modélisation fait intervenir plusieurs paramètres comme le lieu et la période d'incubation du virus ou encore la fréquentation et les destinations des passagers des 4000 principaux aéroports mondiaux. En mars 2020, le supercalculateur le plus puissant au monde (Summit) était utilisé pour identifier 77 molécules potentiellement efficaces contre la <sup>3</sup> COVID-19 [SS20].

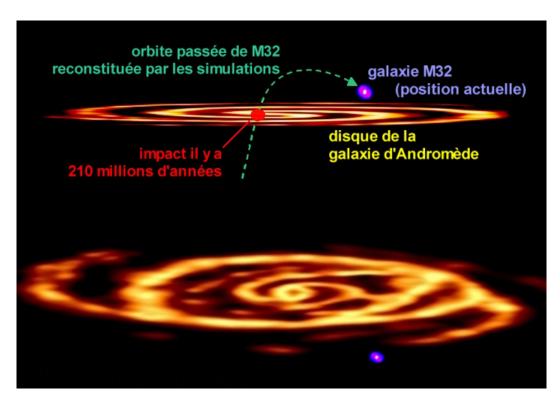

En astrophysique, la simulation numérique est aussi capitale du fait de la non-reproductibilité des expériences en laboratoire. À l'opposé de l'exemple précédent sur les protéines, elle permet d'étudier des objets aussi grands que complexes comme le système solaire, les galaxies ou bien l'univers. La simulation permet alors de faire évoluer le système avec un pas de temps allant jusqu'au million d'années. Une équipe du CEA a pu reconstituer le passé de la galaxie Andromède en analysant les observations réalisées grâce au satellite infrarouge Spitzer [Blo+06]. Après avoir mis au point le modèle adéquat et après plusieurs heures de simulation, ils ont pu déterminer qu'elle avait été percutée par une galaxie voisine il y a plus de 210 millions d'années et que sa forme actuelle résultait de cet impact (voir figure 2.3).

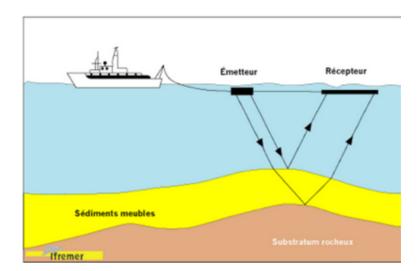

Pour la compétitivité et l'innovation des entreprises, les simulations numériques sont désormais un outil indispensable. Cet outil les aide à la conception, à la décision et au contrôle de leurs activités. Dans l'industrie des hydrocarbures, la recherche pétrolière est très coûteuse : le coût d'un forage d'exploration maritime peut atteindre 100 millions d'euros <sup>5</sup>. Les pétroliers utilisent la simulation numérique pour analyser les fonds marins, modéliser les réservoirs de pétrole et, in fine, optimiser l'extraction du pétrole. Pour cela, ils utilisent des bateaux tractant d'immenses lignes flottantes pourvues de capteurs. La figure 2.4 illustre comment de tels bateaux sont utilisés pour émettre des explosions, et analyser le réfléchissement des signaux sur le fond marin. Grâce à l'analyse de ces données, il est alors possible de construire une cartographie du fond marin et ainsi déceler la présence ou non de réservoirs d'hydrocarbures. En perçant le puits de façon optimale, il sera d'autant mieux exploité. De plus, le risque de forer au mauvais endroit est lui aussi diminué. Actuellement, le taux de succès est de deux forages sur trois.

# 2.1.2 Le calcul haute performance

Aujourd'hui, presque que tout ce que nous utilisons a été simulé, à un tel point que l'avancée de nos sociétés dépend de la puissance de calcul disponible pour réaliser ces simulations. La rapidité de l'exécution des simulations numériques dépend alors de la puissance de calcul disponible pour exécuter l'application. Le domaine du Calcul Haute Performance (HPC) est le domaine informatique qui consiste à exécuter ces applications le plus efficacement possible sur une plateforme. Celle-ci peut être un simple ordinateur personnel ou un centre de calculs dédié. De telles infrastructures sont utilisées dans de nombreux domaines dont les principaux sont la simulation numérique, la cryptographie, l'analyse de données (biq data), l'intelligence artificielle

<sup>2.</sup> https://www.gouvernement.fr/info-coronavirus

<sup>3.</sup> http://www.academie-francaise.fr/le-covid-19-ou-la-covid-19

<sup>4.</sup> Image et légende extraites de http://irfu.cea.fr/Phocea/Vie\_des\_labos/Ast/ast.php?id\_ast=958&t=actu

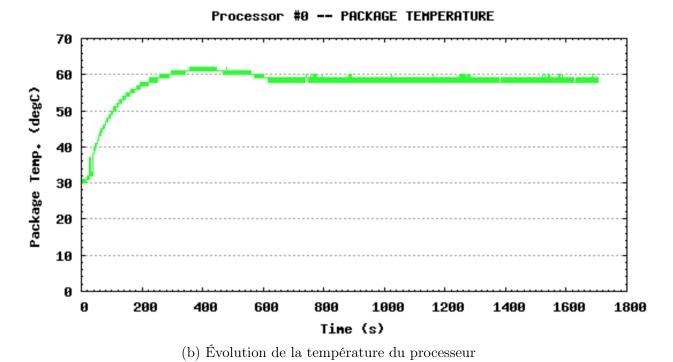

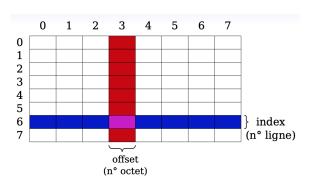

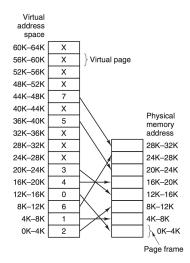

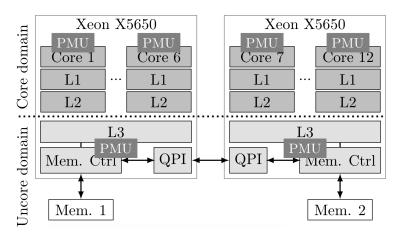

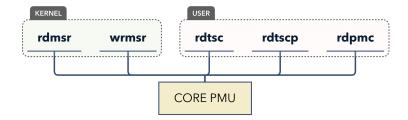

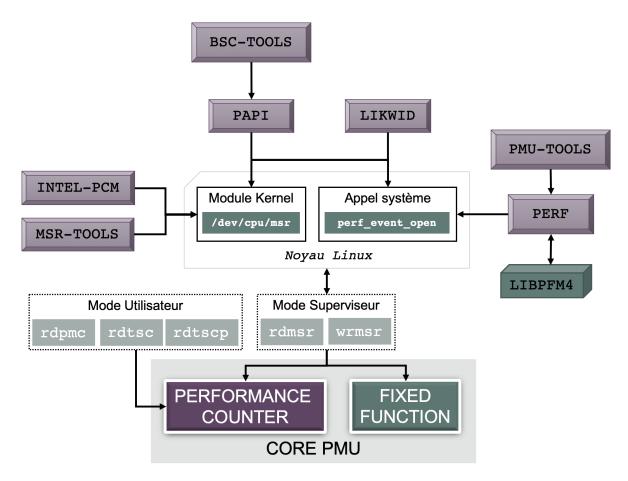

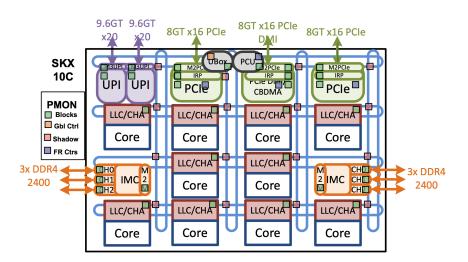

<sup>5.</sup> https://www.planete-energies.com/fr/medias/decryptages/la-difficile-decision-de-lancer-un-forage