# Integrating devices in FPGA using an end-to-end hardware/software co-designedmessage-based approach

Thomas Baumela

#### ▶ To cite this version:

Thomas Baumela. Integrating devices in FPGA using an end-to-end hardware/software codesignedmessage-based approach. Embedded Systems. Université Grenoble Alpes [2020-..], 2021. English. NNT: 2021GRALM004. tel-03259401

### HAL Id: tel-03259401 https://theses.hal.science/tel-03259401

Submitted on 14 Jun2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE

Pour obtenir le grade de

DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE ALPES Spécialité : Informatique

Arrêté ministériel : 25 mai 2016

Présentée par

### Thomas Baumela

Thèse dirigée par **Frédéric Pétrot** et codirigée par **Olivier Gruber**

préparée au sein des laboratoires **TIMA** (UMR5159) et **LIG** (UMR5217) et de l'École Doctorale **Mathématiques, Sciences et Technologies de l'Information, Informatique**

# Integrating devices in FPGA using an end-to-end hardware/software co-designed message-based approach

Thèse soutenue publiquement le 24 février 2021, devant le jury composé de :

**M. Tanguy Risset** Professeur, Laboratoire CITI, INSA-Lyon, Rapporteur

M. Gaël Thomas

Professeur, Laboratoire SAMOVAR, Telecom SudParis, Rapporteur

M. Noël de Palma

Professeur, Laboratoire LIG, Univ. Grenoble Alpes, Président

**M. Kevin Martin** Maître de conférences, Laboratoire Lab-STICC, Université de Bretagne Sud, Examinateur

**M. Frédéric Pétrot** Professeur, Laboratoire TIMA, Grenoble INP, Directeur de thèse

# Contents

| 1 | Introduction                                   |         |                                                |    |  |  |

|---|------------------------------------------------|---------|------------------------------------------------|----|--|--|

| 2 | Context and Problem overview                   |         |                                                |    |  |  |

|   | 2.1                                            | Proble  | em illustration                                | 9  |  |  |

|   | 2.2                                            | SoC a   | pproaches for HW/SW integration                | 11 |  |  |

|   | 2.3                                            |         | proaches to simplify device driver development | 12 |  |  |

|   | 2.4                                            | -       | hary                                           | 16 |  |  |

| 3 | Message-Based Integration for Embedded Systems |         |                                                |    |  |  |

|   | 3.1                                            |         | urrent Integration Challenge                   | 18 |  |  |

|   | 3.2                                            |         | round                                          |    |  |  |

|   | 3.3                                            | U       | ge-Based Integration Solution                  |    |  |  |

|   |                                                | 3.3.1   | The Software Perspective                       |    |  |  |

|   |                                                | 3.3.2   | The Hardware Perspective                       |    |  |  |

|   |                                                | 3.3.3   | The Overall Lifecycle                          |    |  |  |

|   | 3.4                                            | Messa   | ges and Class-Genericity                       | 30 |  |  |

|   |                                                | 3.4.1   | Using Messages                                 | 31 |  |  |

|   |                                                | 3.4.2   | Class-Generic Protocols                        |    |  |  |

|   |                                                | 3.4.3   | Heterogeneity                                  | 35 |  |  |

|   | 3.5                                            | Evalua  | ation                                          | 39 |  |  |

|   |                                                | 3.5.1   | Overhead Evaluation                            | 40 |  |  |

|   |                                                | 3.5.2   | Small Embedded Systems                         |    |  |  |

|   | 3.6                                            | Summ    | nary                                           |    |  |  |

| 4 | Lin                                            | ıx Inte | gration                                        | 51 |  |  |

|   | 4.1                                            |         | round                                          | 52 |  |  |

|   |                                                | 4.1.1   | Linux kernel modules                           |    |  |  |

|   |                                                | 4.1.2   | User-space interfaces                          |    |  |  |

|   |                                                | 4.1.3   | Linux Device Driver Model                      |    |  |  |

|   |                                                |         | 4.1.3.1 Devices, Drivers, Buses                |    |  |  |

|   |                                                | 4.1.4   | Software-Hardware communication in Linux       |    |  |  |

|   |                                                | 4.1.5   | Some bus implementation examples in Linux      |    |  |  |

|   |                                                |         | 4.1.5.1 PCI drivers                            | 62 |  |  |

|   |                                                |         | 4.1.5.2 USB drivers                            | 64 |  |  |

|   | 4.2                                            | The E   | xtension Proposal                              |    |  |  |

|   |                | 4.2.1  | A new message bus for Linux                    |  |  |  |  |  |

|---|----------------|--------|------------------------------------------------|--|--|--|--|--|

|   |                | 4.2.2  | Driver API                                     |  |  |  |  |  |

|   |                | 4.2.3  | Low Level Driver API                           |  |  |  |  |  |

|   | 4.3            | Experi | ments                                          |  |  |  |  |  |

| 5 | Xen            | Integr | ation 79                                       |  |  |  |  |  |

|   | 5.1            | The FP | GA Adoption in the cloud                       |  |  |  |  |  |

|   |                | 5.1.1  | The architecture of the cloud                  |  |  |  |  |  |

|   |                | 5.1.2  | The state of FPGA adoption in the cloud        |  |  |  |  |  |

|   | 5.2            | The im | pact of our proposal for the cloud             |  |  |  |  |  |

|   |                | 5.2.1  | Message-based communication                    |  |  |  |  |  |

|   |                | 5.2.2  | Class genericity                               |  |  |  |  |  |

|   | 5.3            | Feasib | ility                                          |  |  |  |  |  |

|   |                | 5.3.1  | Concepts offered by hypervisors                |  |  |  |  |  |

|   |                | 5.3.2  | Description of our solution                    |  |  |  |  |  |

|   | 5.4            | Deepe  | r Analysis                                     |  |  |  |  |  |

|   |                | 5.4.1  | Integration in Xen                             |  |  |  |  |  |

|   |                | 5.4.2  | Consequences of our solution for cloud systems |  |  |  |  |  |

| 6 | Conclusion 105 |        |                                                |  |  |  |  |  |

|   | 6.1            | Summ   | ary                                            |  |  |  |  |  |

|   | 6.2            | Perspe | ctives                                         |  |  |  |  |  |

|   |                |        |                                                |  |  |  |  |  |

\_\_\_\_\_

### Bibliography

111

# Chapter 1

# Introduction

The pace of hardware development tends to be continuously increasing. This is the case for instance with MultiProcessor System-On-a-Chip (MPSoC), embedding a lot of specific Intellectual Properties (IPs). Those systems evolve very quickly to match a specific consumer market. For instance, several versions of a Snapdragon platform can be released over a year<sup>1</sup>. Integrating hardware, meaning, making its features available to a high-level software application, is thus a very important issue. Indeed, as hardware is evolving, having new and changing capabilities, and systems become more and more complex thanks to more efficient tools and higher developers expertise, integrating hardware has a growing cost. If this is true for MPSoCs, this is worse for Field Programmable Gate Arrays (FPGA) for which their high programmability makes hardware development even faster and thus the hardware integration an even more critical problem.

The work addressed by this thesis aims therefore at improving the hardware integration in the context of FPGAs. FPGA technology is incrementally used across a wide variety of domains, from small embedded systems to cloud computing. They are often used to associate programmable hardware logics with processing systems. In such systems, hardware components can be designed and integrated by programming a preexisting chip without having to change the actual hardware. This opens great possibilities regarding programmability, power efficiency and performances. Though, this comes with some drawbacks: Not only programming FPGAs can be complex but integrating the newly created hardware with the software is also a heavy task.

<sup>&</sup>lt;sup>1</sup>https://en.wikipedia.org/wiki/List\_of\_Qualcomm\_Snapdragon\_processors

The advantages of using FPGAs for tasks with fine-grain parallelism increased their adoption in a lot of domains. In particular, their reprogrammability offers great evolution possibilities. It makes system updates easier by simply reprogramming the FPGA without having to change the actual hardware. Reprogramming an FPGA can even be made remotely, making the maintenance of such system easier. Their power efficiency, even though still lower than pure Application Specific Integrated Circuits (ASICs), is far better than running software on a CPU. They also allow faster prototyping thanks to their ability to design and implement hardware without having to build an actual chip. Implementations on an FPGA are made at the transistor level, allowing much better parallelization for applications that need it. This offers overall great performances compared to software implementations, making FPGAs a great solution for embedded systems, medium size systems and cloud computing systems.

In embedded systems, programmable logic is used to deploy hardware logic as devices. These devices can be controllers of external devices such as human interface devices (controllers and displays), storage and network devices, or sensors and actuators. They can also be accelerators for encryption, video and audio processing, and nowadays artificial neural network inference. This reduces the power consumption while offering better performances compared to software implementation running on a CPU.

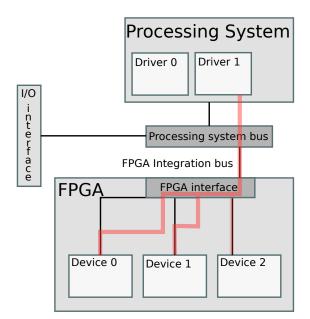

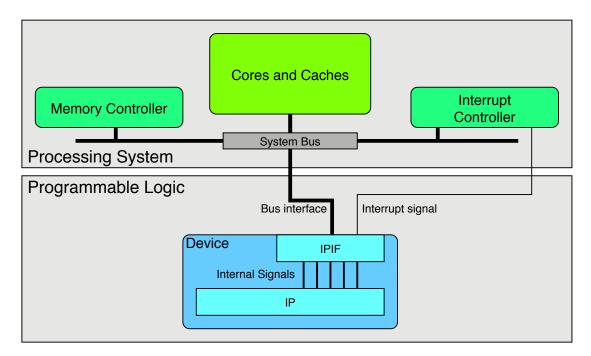

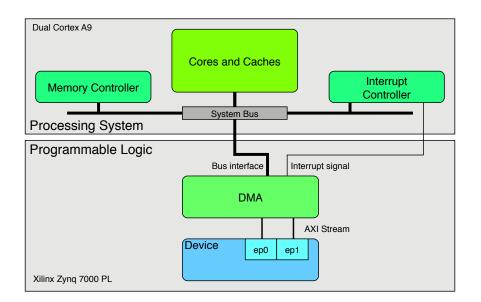

Figure 1.1 depicts the overall view of how FPGAs are integrated in embedded systems. This allows the FPGA to have access to an I/O interface allowing it to access external peripherals and buses such as USB, Ethernet or I2C. It also interfaces the FPGA with the system bus making possible for the software running on it to access devices on the FPGA. Devices deployed in such FPGAs are integrated through a software driver running on the processing system. Each device has an available driver that integrates the features it offers to upper layers of software.

FPGAs are also used this way for bigger systems, running full fledged operating systems. In those systems the FPGA either sits in the same SoC or board as the processing system or on a separate board usually connected through a PCI link. Even though those systems are bigger than embedded systems, FPGAs are integrated in similar ways. Hardware components are deployed in FPGAs and seen as devices from the software. Those devices must be integrated with their driver within the operating system. A task that can be very challenging regarding the fact that driver updates must follow the rules of each operating system update schedule.

FIGURE 1.1: FPGA Integration for Embedded Systems

FPGAs are also more and more used in cloud computing. Those systems are intrinsically made to share hardware resources to multiple clients. It means that no matter the level at which the client stands (virtual machine, operating system or application level), the FPGA resources must be shared among multiple clients. We decided to focus only on sharing devices implemented on FPGAs. Indeed, sharing the FPGA itself, meaning, allowing multiple clients to reprogram part or all the FPGA is a different topic and is currently addressed by several works. In our case, devices are deployed within FPGAs and shared with the clients that can come and go at any time. As these devices are on a FPGA, they may be updated, removed or new devices may come at any time. This means that integrating such devices requires more dynamicity in all layers.

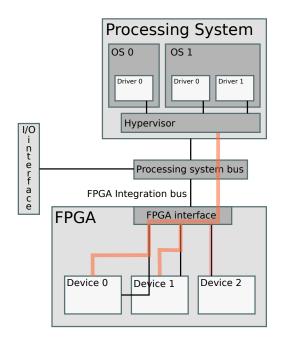

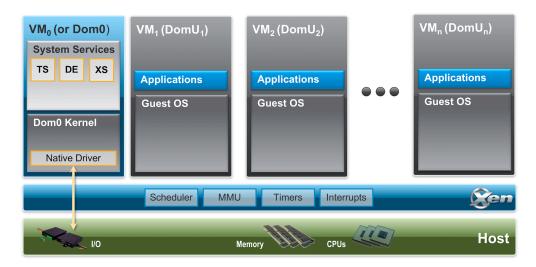

Figure 1.2 shows the overall picture of how FPGAs are integrated in cloud systems. Hardware side, the architecture is the same. Devices are deployed on the FPGA, integrated with the processing system bus to let the software access those devices. Software side the situation is different as multiple operating systems share the same hardware resources. A first layer of software called the hypervisor is in charge of sharing the hardware and thus the devices on the FPGA. There are multiple ways of sharing devices but the general idea is that each operating system has its own set of driver for the devices it wants to handle. Drivers communicate with the hypervisor to handle the device. The hypervisor is then in charge of sharing device operations coming from the drivers of all operating systems. Additionally, some devices may also be completely allocated to one specific guest, making the situation exactly the same as for previous systems.

FIGURE 1.2: FPGA Integration for Embedded Systems

As FPGAs come with many power and performance advantages for a lot of different applicative domains, one may ask why the adoption of such a great technology, even though it is moving forward, is so slow. The big part of the answer is that FPGAs come with a major drawback: Integrating devices deployed within FPGAs in an actual software intensive system is a real challenge. This challenge impacts both the hardware and the software sides, making it a co-design issue.

Device makers must adapt their device interfaces to the interrupts controller, Direct Memory Access (DMA) engine, and integration bus specifications of every system. Hardware interfaces are hard to standardize. Even though some efforts have been made no real standard has emerged. The two major actors of the industry recognized this challenge and started to address it, though only partially. They have drastically improved their tools over the years, offering great support for developing hardware with both Hardware Description Languages (HDLs) and High Level Synthesis (HLS). They have also grown their libraries of hardware components making it easier to reuse hardware commodities such as buffers, bus controllers or DMA engines. They also make a great effort into pushing the AXI standard offering great tools and components allowing to more easily interface with the standard. But those tools and resources are essentially focused on improving the design, integration and deployment of hardware on the programmable logic. Even though this is a major and necessary step to help integrate devices in FPGAs, it is only half of the challenge we address.

The integration challenge we face is across software and hardware. Of course, hardware features must be designed and deployed on the programmable logic, but software must be written and installed on the processing system to be able to exploit these hardware features. This means writing software drivers to drive hardware devices. Writing drivers requires both hardware and software skills that not everybody has, making their development time-consuming and costly. Developers must deal with the current hardware-software frontier based on registers and interrupts, exposing a lot of hardware implementation details. They have to work with ever growing documentations often being hundreds of pages long and describing every bit of every hardware register, as they must dive deeply into details to allow driver developers to understand how to drive the device. Those documentation are always evolving as devices are revised every few months, and are usually not free of ambiguity. Also, new devices are appearing all the time, making writing drivers a never-ending struggle. This leads to drivers being hard to maintain safe as they must be updated often, and as such are an important potential source of bug. Considering the diversity of software stacks for which drivers are needed, from bare-metal to various popular versions of the Linux kernel, the situation may become critical if not addressed.

In this thesis, we propose a new simple and effective approach to tackle this issue. Our approach does not require expensive or new technologies. It can be adopted incrementally without having to throw every existing solution out. It is compatible with existing FPGA and processing system technologies without having to change the existing tools. Our solution requires to follow an end-to-end design, taking into consideration a comprehensive view of the integration process across both the software and the hardware. This design can be followed using existing tools and technologies, meaning that a lot of existing improvements can be integrated in our design.

Our approach was inspired by the principles behind the Universal Serial Bus (USB) and adapted to devices deployed on FPGAs. The two core principles we retain from USB are: 1) provide a message conduit between devices and drivers, completely hiding the old frontier made of interrupts and registers, 2) define device classes allowing to have one driver able to drive multiple devices of the same class. Using a message conduit decouples the driver from its device, bringing a much needed separation of concerns. No more awkward documentations that are several hundreds of pages long, no more dozens of memory-mapped hardware registers and interrupt needed. The only requirement is a high-level message protocol. This will make driver smaller, easier to write and safer to operate. Additionally, it opens the possibility to standardize message

protocols for classes of devices rather than have one specific protocol for each specific device. With class-generic protocols, only one driver is necessary to drive an entire class of device.

The two principles, a message conduit and class-generic protocols, are the two key reasons why any USB key can be plugged into almost any host and work out of the box. It works first and foremost because the physical key itself can be plugged in, which requires standard plugs and cables. Then it works because the USB key is seen as a mass storage device, a class of device that support a standard mass storage protocol. Finally, it works because the processing system runs a generic driver for that specific class of device, integrating it with the rest of the software stack. The overall message-based approach provides the right separation of concerns between hardware design and software coding. Both sides only see the other side as a message sender and receiver ensuring a smooth and cost-effective integration. Unfortunately, the USB specification cannot be leveraged for this. USB is not open, not free and not abstract enough. Its specification is a closed world that locks adopters in and forces for certain cables and plugs, making it hard to customize for certain needs.

Our proposal is to define an open and abstract conduit for sending and receiving messages across the frontier between the programmable logic and the processing system. Fortunately, we do not need to build new cables and plugs. FPGAs already have integration solutions with processing systems that work well either being on the same SoC, board or through existing buses such as PCI. On the FPGA itself, the standardization efforts of the industry, in particular related to the AXI standard, are completely reusable in our solution. In particular, we built our solution using the AXI and AXIstream standards, using existing tools from FPGA vendors without feeling the need to change them or completely reinvent the wheel. Thus, the challenge is not here, all the building blocks we need exist and will be reused. The challenge is to design the message conduit in terms of its two interfaces:

- 1. The software interface that all drivers will be using to send and receive messages,

- 2. The hardware interface that all devices will be using to receive and send messages.

The first objective of this thesis is to define a fully abstracted interface that is simple and safe to use. Having an abstract interface is key because all the systems we will target are very heterogeneous. We thus cannot impose one specific existing standard as some users may need low-power low-performances interface while other may need high-performances. With an abstract interface, board providers will have the implementation freedom to adapt our proposal to the specifics of their boards, from small embedded systems to larger ones. Indeed, our proposal can accommodate with very different technologies in terms of processing systems, programmable logics and the interconnect buses between them. Adding a layer of abstraction means that we must be mindful of important requirements. Using messages must not introduce any undue overheads in terms of latency or throughput. We must also preserve the footprint and power consumption on the programmable logic side.

We designed our solution first for small embedded systems. This design addresses the integration challenge we described by defining both the software and the hardware interface of our new message conduit. Software side, we designed an asynchronous interface inspired from the Linux driver model, which is familiar to driver developers. Hardware side, we designed an abstract interface based on streaming interfaces used to send and receive messages with the software. The implementation of these streaming interfaces is not imposed by our solution, only the message protocol traveling in them is. This means that one may build our solution with a different implementation than ours and still benefits from its advantages. The prototype we built demonstrates that our solution fits for small systems with low latency and low throughput devices without growing much the size of the implementation.

We also integrated our solution within a Linux kernel, demonstrating its feasibility for bigger systems. We demonstrated that our solution can fit for high-performance devices with negligible performance overheads. We showed that our design integrates well within a Linux kernel without disturbing the existing solutions. It shows that our solution is flexible and can be incrementally adopted by having some devices integrated in our design and some other in existing solutions.

In the context of cloud computing, we analysed that our solution can offer great benefits to improve FPGA integration but also hardware support. Indeed, messages are good solution to share device among multiple guests. They also fit well in famous hypervisors, in particular Xen, which have all the features our solution requires without the need of modifying it. In addition, cloud computing benefits from class genericity enabled by our message-based solution. It allows guest operating systems to require less drivers to support hardware. Our solution also allows to reuse message-based drivers from a non-supervised operating system to a supervised one. The manuscript is organized as follows. Chapter 2 gives an overview of the context in which our work takes place, and discusses the related works that we believe are relevant to our proposal. Chapter 3 presents our first contribution, the design and implementation of a message-based approach that targets the context of embedded systems. Chapter 4 presents our second contribution, that details how our solution can be integrated in bigger systems, in particular those running the Linux kernel, and presents how it can be realized in Linux. Chapter 5 is a less mature contribution, more specifically the implementation is yet to be demoed, that shows how our solution can be useful for the cloud and how it can be integrated to a cloud system, through the Xen hypervisor. Finally, Chapter 6 summarizes the problem we addressed and the solutions we propose, and draws some perspectives.

### Chapter 2

## **Context and Problem overview**

#### **Chapter contents**

| 2.1 | Problem illustration                                | 9  |

|-----|-----------------------------------------------------|----|

| 2.2 | SoC approaches for HW/SW integration                | 11 |

| 2.3 | OS approaches to simplify device driver development | 12 |

| 2.4 | Summary                                             | 16 |

The work we address in this thesis is at the crossroad of several initiatives, some coming from System-on-a-Chip research, others from Operating System research. SOC and OS research have very different objectives, while at the end of the day the integration of both is mandatory to building a useful silicon-based system. We start this chapter by an illustration of the rapid pace of hardware development and the software difficulties it induces. Then, we analyse it by first focusing on the approaches that target integration of IPs into Systems-on-a-Chip from a bottom-up perspective. We then take the opposite standpoint in which Operating System is the core of the work and hardware is a necessary evil. Finally, we draw some conclusions about some missing pieces that would ease the integration of ad-hoc hardware in legacy OS software.

### 2.1 **Problem illustration**

Multiprocessor System-on-a-Chip are today what Application Specific Integrated Circuits were yesterday: pieces of silicon optimized towards an application or a class of applications. Even though they tend to be reusable and are able to handle more and more applications efficiently, the power and price budgets makes it necessary to embed specific hardware Intellectual Properties (IPs) depending on the target usage and market. Platform-based design [1] has been a keyword driving the industry, as it maximizes hardware reuse and thus shortens its development time.

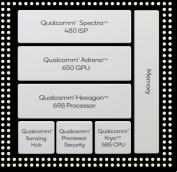

Looking at mobile platforms is quite instructive: Qualcomm has released more than 150 different Snapdragon platform instances to its customers between 2007 and 2020, Texas Instruments advertised 25 until it left this market and other players in the market have similar numbers. These platforms have become so complex overtime that the industry does not even try to give rough diagrams of what the SoC contains, as illustrated Figure 2.1.

(b) Snapdragon 865 block diagram

FIGURE 2.1: Typical marketing representation of a SoC in (a) 2010, (b) 2020

Even though fast and power efficient hardware design for SoC is still a real challenge, the huge number of platform versions only exacerbates the already difficult problem of hardware/software integration. Indeed, each platform contains a variable number of IPs and in most cases even the ones which provide the same features are slightly different. Thus, the hardware/software integration process has to deal with ten to a hundred IPs, each having themselves tens to hundreds registers. Morevover, each register has potentially a bit field with up to many functions. Even for the somewhat modest SoC in the Raspberry Pi 4 (Broadcom BCM2711), we counted already more than 2500 registers. Engineers at Texas-Instrument report that the sole bring-up of the clocks and power modes in modern SoCs involves reading and writing more than 1000 different registers [2]. In this context, using (and reusing) an IPs is a twofold problem. First, accessing, using loads and stores, the registers/bitfields at the correct addresses/offsets in the correct order at the right time, which can be seen as a "syntactic" problem. Second, setting the correct values in these resources so that the device does what it is expected to do, which is more of a "semantic" problem. Overall, having a working hardware/software system is a tremendous amount of work and debug. It

thus comes at no surprise that the vast majority of bugs in operating systems comes from the device drivers (about 70% of the bugs, with drivers being 70% of the source code in Linux kernel), among which a third is due to the interface between the OS and the device [3]. Provisioning for detecting part of these bugs at run-time is very costly and lead to overheads in the order of 100% [4].

The problem is even worse in the context of FPGAs. Their high programability makes the number of IP version growing even faster. Indeed, it is very easy to implement an IP using either an Harware Description Language (such as verilog or VHDL) or High Level Synthesis (which makes IP development even easier). For instance, only on the Xilinx IP public catalog more than 800 IPs can be found in their last version. Updating an FPGA-based platform is also very fast compared to ASICs or System-on-a-chip. In a couple of hours (sometime minutes), it is possible to update an IP, run a couple of tests, implement a platform embedding the new version and finally program the FPGA with the updated platform. After that, a software update is often required and a huge amount of work can be required to update and debug drivers, even for tiny updates.

### 2.2 SoC approaches for HW/SW integration

In the SoC domain, easy and early HW/SW integration has been of interest for long. This is due to the fact that because of high cost constraints, the easy exploration of the hardware/software design space is required to optimize the target system for a given application or a class of applications. Taking as an example SoCs that handle flows of data, which is typical for consumer applications, at some point the application ends up specified as a set of interconnected tasks. A first step is then to decide which tasks will be realized in hardware and which will be realized in software. How this partition is done depends on many factors, the least of which is the existence of an HW IP that would be suited for the tasks. Once this choice done, the tasks, independently of their hardware or software nature, have to communicate, taking into account latency and bandwidth constraints. Communication synthesis aims thus at automating the generation of hardware and software required for the communication [5]. Taking the example of streaming applications, [6] proposes a layered approach in which application level, system level, OS level and physical level interfaces are predefined using templates. Synthesizing the communications boils down to instantiating the

right hardware and software elements and setting the appropriate parameters. The approaches based on these principles are well suited for an *ad-hoc* usage, for applications that can be specified using a static task graph and data-flow like communications [7, 8].

More general approaches have been proposed which also target shared memory communication, as reviewed in [9]. They actually build finite state machines for the hardware and software parts from high level specifications. An orthogonal strategy based on the concept of remote procedure call is proposed in [10]. The principle here is to describe the communication in the application through what the authors call "shared objects", that are able to serialize requests and perform actions, either internally if they are hardware IPs, or forward them to a software task otherwise. Although interesting as a different abstraction, the management of the shared objects is a bit unusual, and describing applications with this semantic cumbersome, which make the proposal difficult to generalize.

Overall, the SoC centric approaches are not concerned with the notion of driver per se, and do not deal with kernel interfaces, device sharing, process isolation, etc. They focus on communication abstraction, which is nice, but set aside the OS legacy that simply cannot be ignored when targeting actual processor centric products.

### 2.3 OS approaches to simplify device driver development

As far as operating systems are concerned, the issue is known and recognized, and different solutions have been attempted, but all under the assumption that the hard-ware/software boundary remains unchanged. Hardware is seen as a (possibly huge) set of registers that has to be read and written following the constraints expressed in a datasheet.

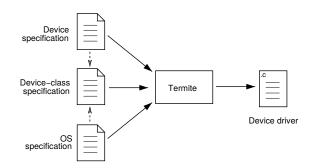

The first relevant work is automatic driver generation. Most approaches start by defining a domain specific language (DSL) in which the device specificities, described as a mix of hardware resources and behavior, are captured. Then, a tool, specific to an operating system (or even to a version of it to be fully accurate, for example Linux pre 2.6 had a big kernel lock, and now each device has its own set of locks), is used to generate the actual driver [11, 12]. The driver generation tool can be itself parameterized by a formal description of the OS interface [4, 13]. Figure 2.2 summarizes the idea.

FIGURE 2.2: Principle of driver generation from a DSL (taken from [4])

Another approach has been to push for writing device drivers using high-level programming languages, targetting software challenges such as memory management or synchronization. The work [14] proposes to write drivers in Java, running a Java Virtual Machine inside the kernel. The work [15] even argues to rewrite the kernel entirely in a high-level language, in this case the Go language.

Using DSLs is a direction, but not the only one. Tools and DSLs are expected to help with the syntactic issues, not really the semantic ones. Consequently, they do not help that much with robustness with respect of the complexities of using a particular device. They do help however regarding the driver integration with the operating system by abstracting its API. They ease the following the programming rules defined by the operating system, in particular the complex ones regarding dynamic driver loading and unloading.

Other efforts of the software community have been pushing tools rather than frameworks. Tools like Coccinelle [16] or Coverity [17] are efforts to help write safer kernel code and better support code evolutions. The tools help on the usual software challenges of writing kernel code, such as memory management or synchronization, but the challenges of actually driving hardware devices are not addressed. The work [18] discusses the integration flows based on IP-XACT, an XML format that describes hardware components in order to facilitate their integration.

We see a possible limitation to these approaches. Indeed, all cases have to be thought of when defining the high level languages, which is not easy. So either the language is very abstract and simple to use, but may be limited in scope, or the language allows to describe many details in which case it is hard to use in a generic manner, and a lot of work is required to model accurately the behavior. Therefore, each evolution of a given OS requires new developments, and so does the introduction of a new OS. The second work is focus at hiding hardware interfaces seen by the software. RIFFA [19], inspired by Microsoft Research's SIRC [20], proposes a reusable integration framework that targets the integration of accelerators deployed on programmable logic. RIFFA combines both software and hardware parts. Running on the processing system, RIFFA provides a C library and a Linux device driver. Deployed on the programmable logic, RIFFA provides a set of harware components. Both sides have been designed for a PCIe bus and a DMA engine used to pass data between the processing system and the accelerators on the programming logic. The RIFFA design is focused solely on accelerators with a design that is very DMA and PCIe specific, but the approach could certainly be extended to other bus technologies and other hardware devices.

It is interesting to note that the DMA transfers of the early RiFFA-1 [19] was later better abstracted by communication channels in RIFFA-2 [21], something very interesting that goes toward the idea of abstract conduits. But the RIFFA library is for applications, running in user mode. While this approach of dedicating accelerators on the programmable logic to a single application solves problematic issues, they do not integrate devices at the operating system level. Integrating it at the kernel level means that there would be a support for a device lifecycle since drivers may be loaded and unloaded and devices may fail. RIFFA does not include any lifecycle management which is something quite critical to address when integrating devices. Indeed, devices are sometimes more than just pieces of hardware booting at power-up and always running flawlessly. They can encounter issues, have some of their features unavailable for a certain period of time, or simply fail until they are reset.

Even though RIFFA has been of great help in its time, it is not maintained anymore. It has suffered a lot from Linux kernel updates making the amount of work to keep it up to date too much for the people still on the project. This shows that maintaining a software/hardware interface as they are today with all hardware and software updates they have to follow is a very hard task even for succesful projects such as RIFFA. It enlights once again that the complexity of this interface is a source of a lot of struggles, making us confident that reducing its complexity can help reducing the efforts required for driver maintenance and debugging.

The work MPRACE [22] follows a similar philosophy as RIFFA, very much centered on helping the development of PCIe devices that require very high bandwidth. The focus of the work is to help with being able to saturate a PCIe link, that is, being able to use all the throughput that a PCIe bus may provide. The C library aims at hidding the details of the DMA engine from the software developers. The DMA engine is hidden behind FIFO interfaces for the hardware designers. Those choices are in line with FPGA vendors pushing for a DMA engine fronting AXI streams. This represents a great inspiration to push the idea further more to a full message-based solution.

Finally, the third, quite different, domain of operating system research that we believe is inspiring for our own objective is virtualization. Looking at it from the hypervisor or microkernel point of view reaches the same conclusion [23]: accesses to devices by the guest OS are performed through an inter-process communication (IPC) mechanism. However, the intent of these approaches is not to change the hardware-software boundary, but to wrap interrupts as messages, leaving drivers still loading and storing values in and out of hardware registers.

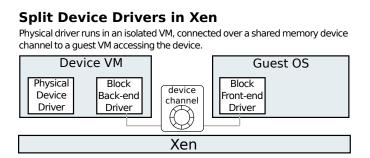

Figure 2.3 illustrates the *split driver* approach promoted by the Xen hypervisor to provide access to devices through an host OS (most commonly Linux). As explained in [24], the principle is to provide "a simple, narrow, and idealized view of hardware" to the guest OS, which has to be modified so that the drivers are substituted by a front-end relying on this hardware abstraction. The guest OS has a back-end which receives the requests of the front-end, and calls the native drivers to actually access the device. This strategy is simple and clean: the hardware abstraction provided to the front-end allows to access the legacy drivers unmodified on the host through the back-end. Fur-

FIGURE 2.3: Xen's split driver hypervisor architecture (borrowed from [24])

thermore, a single (front-end, back-end) couple is required for a given driver class, which minimizes the modifications to be done on the guest OS.

The work of [25] uses this concept to virtualize the devices on a SoC and provide access to them as OS services. The approach makes sense, but is very costly in terms of memory footprint and computing power, as it requires the use of the original Linux device drivers in the back-end of the split drivers.

#### 2.4 Summary

Whatever the perspective taken, the addition of a piece of hardware into a computing system requires the software to be aware of its existence and detailed expectations. This makes the integration of Systems-on-a-Chip, even when using legacy hardware, very complicated. We believe that raising the hardware-software interface abstraction above the register map is a way to ease this integration. It does have a hardware cost, as some wrapping will be necessary to expose an other interface, but the hope is that it will make system software simpler. We choosed to tackle this problem from the FPGA perspective, not only because they are a great candidate for fast prototyping but also because the integration problem we desribed are even worse in this case. Indeed, as hardware is much faster to implement on FPGAs, new updates come at an even higher pace requiring a very efficient integration process. Improving the integration problem for FPGAs thus improves it also for System-on-a-chip in general and makes the adoption of a solution easier.

# Chapter 3

# Message-Based Integration for Embedded Systems

#### **Chapter contents**

| 3.1 | The Current Integration Challenge  |                          |    |

|-----|------------------------------------|--------------------------|----|

| 3.2 | Background                         |                          |    |

| 3.3 | Message-Based Integration Solution |                          |    |

|     | 3.3.1                              | The Software Perspective | 23 |

|     | 3.3.2                              | The Hardware Perspective | 27 |

|     | 3.3.3                              | The Overall Lifecycle    | 29 |

| 3.4 | Messages and Class-Genericity      |                          | 30 |

|     | 3.4.1                              | Using Messages           | 31 |

|     | 3.4.2                              | Class-Generic Protocols  | 34 |

|     | 3.4.3                              | Heterogeneity            | 35 |

| 3.5 | Evaluation                         |                          | 39 |

|     | 3.5.1                              | Overhead Evaluation      | 40 |

|     | 3.5.2                              | Small Embedded Systems   | 45 |

| 3.6 | Sumn                               | 1ary                     | 49 |

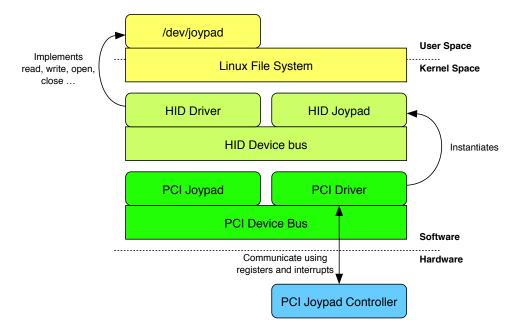

The "Soc on a Programmable Chip" trend in which reconfigurable fabrics are integrated into System-on-Chip (or the other way around) started in the early 2000's [26]. It is now legacy, and this technology is routinely used to associate software running on processing systems with hardware components in programmable logic. In the embedded system world, these components are often controllers of external physical devices such as human interface devices, mass storages, or sensors. They may also be accelerators such as encryption or audio and video processing components. Moving such functionalities from software implementations to hardware components is interesting when searching for better performance and lower power consumption, especially for small embedded systems. Moving more and more functionalities in hardware is thus the way to go to get the better out of a small system, but it comes with a huge trade-off: the integration challenge. Integrating hardware components is not only harder than implementing their software equivalent, but it spreads out the range of skills required by embedded system designers to make their system work. Indeed, the remaining software running on processor-centric systems have now to communicate with more hardware components than before, making the integration challenge a major concern for them.

The approach we propose to tackle the integration challenge is based on two principles: an abstract message conduit and class-generic protocols. Those concepts are the origin of the USB success story, showing how easy, low-cost and efficient it is to plug any device on any system. The philosophy of the approach is to provide to system designers a similar plug-and-play experience to integrate devices in their systems. It also provides device makers a consistent interface independent of the system in which their devices may be integrated. Finally it provides driver writers a generic interface simplifying the interface of devices by replacing hardware details with message protocols. This approach has been implemented and demonstrated for small embedded systems, including a bare metal software stack running on ARM based processing system and Xilinx programmable logic.

### 3.1 The Current Integration Challenge

The integration challenge consists of making hardware components functionalities exploitable by software. Those hardware components, also known as IPs (Intellectual Properties) are assembled and wrapped in devices waiting to be exploited by the software running in processing systems. The Figure 3.1 illustrates the integration process that embedded system designers are facing. The integration process requires both hardware and software skills.

Hardware skills are required to design a device and deploy it in the programmable logic. Designing and deploying a device consists of assembling one or more hardware components wired together and wrap them in an interface interconnected in turns to the processing system. To do that, the device must be implemented and integrated in

FIGURE 3.1: FPGA Device Integration

the system. The implementation phase consists of implementing and assembling all the components of the device using either Hardware Description Languages (HDL) or High Level Synthesis (HLS) tools [27–29]. The integration phase consists of putting the device in an hardware system typically consisting of a system bus and an interrupt controller. The system bus is used to send commands to the device, check its status or exchange data. The interrupt controller is used to notify processors of hardware events via single wires containing no other information than "something happened, check it out".

The software skills are necessary to allow the software stack running on the processing system to drive the deployed device. Each deployed device thus requires a device driver, a specific piece of software that knows how to exploit the specific features provided by the device. Device drivers are the vast majority of the time running in the bottom of the software stack, inside the operating system kernel. A typical example is a block device capable of storing blocks of data, exploited by its driver. The driver will perform read and write data block operations to its hardware device providing the foundation to a file system within an operating system.

A device driver drives its device through the system bus and the interrupt controller. This interfacing is done by a specific hardware component, often called an IP InterFace (IPIF), a hardware component acting as an interface bridge between the internal signals of the device and the system bus and interrupt controller. Some of these signals are combined to generate interrupt signals to the interrupt controller while others are grouped as bit fields of hardware registers.

Hardware registers are then memory-mapped within the address space of the processor by the system bus. That way, the device driver can read or write these hardware registers by issuing regular load and store operations to the system bus. Traditionally, the memory mapping of a device reserves a contiguous range of memory addresses in the processor address space. This means that each device is associated with a base address, the first address of the reserved range. Each hardware register is then mapped at a specific offset from that base address.

Hardware registers have two main purposes: control and data transfers. Some control registers are used to issue commands to the device while others are used to read the current status of the device. In contrast, data registers are used to send and receive data to and from a device. This means that data registers are usually implemented in hardware as FIFO queues. FIFO queues are simple to drive from software, through load and store operations, but they require the CPU to take charge of data transfers, something not always the best for performances. Therefore, most modern devices embed a Direct Memory Access (DMA) engine to optimize data transfers. With a DMA engine, data transfers to and from memory are under the responsibility of the device, writing and reading to and from memory buffers. These buffers are setup in memory by the device driver.

Overall, this integration process is complex, hard to debug, requiring both hardware and software skills and thus costly. From a hardware perspective, the main challenge comes from the interface heterogeneity, especially the diversity and number of interfaces for system buses and interrupt controllers. As a consequence, this diversity almost requires to design a different IPIF for each embedded system. For instance, each bus specification usually defines its own burst capabilities, cache coherency, or frequency limitations. There are also different interrupt controllers, each with different interrupt types, using different signals with different signal constraints.

From a software perspective, the situation is not any better. Writing a device driver is known to be a complex task even for kernel-space software engineers. The main reason is the complexity of the nature of the software-hardware interface. Each bit of each hardware register must be understood, along with timing constraints or ordering constraints across hardware registers. Too often, a deep understanding of some internal details of the device is necessary to correctly drive that device, which requires software developers to have hardware skills. Furthermore, error conditions are usually hard to understand and to handle properly from a software perspective. Finally, interrupts are completely asynchronous and requires an accurate handling of complex race conditions in software, especially when writing device drivers for high-performance devices.

All this is not good news knowing that device drivers account for 54% of the code base of the Linux kernel. It is no surprise then to see that 74% of bugs in operating system kernels are device driver bugs, most of them leading to a complete system crash [30, 31]. Worse, the integration process is a never ending struggle. New devices are constantly appearing requiring to repeat the whole process over and over. Indeed, new devices appear all the time and existing devices constantly evolve. Also, software stacks and kernel APIs are updated regularly requiring drivers to be updated to stay compatible. This requires writing new documentations or even worse, evolve existing documentations with many small edits scattered throughout pages.

This constant struggle makes it hard to have available drivers for the latest devices. Furthermore, it makes it hard to rely on safe drivers, unless a designer limits its design to integrate devices that are old enough to have well tested drivers. This leads to the unfortunate situation where a designer is trading innovation for safety.

### 3.2 Background

The integration challenge has been the subject of various related work, both on the hardware and software communities. Though, most of the efforts are rarely on both the software and the hardware side at the same time. Even more rarely has the message paradigm been advocated as an end-to-end game changer.

The Universal Serial Bus (USB) [32] standard is one exception. The work started on the hardware side, trying to solve the flood of plugs and cables in the 80's by adopting one unique physical standard to plug external devices to personal computers. In its hardware architecture, it is based on a master-slave serial bus, organized as a tree in which each node is a hub and each leaf a device. As a serial bus, the message paradigm seems logical and the USB standard built on that foundation to define device classes and promote class-generic drivers. We all know, including non expert people, how successful that approach has been. The success of the USB standard is explain by two key elements: A message-based interface and class-generic devices. They demonstrated that a message-based interface can be designed at a very low cost (the additional chip that must be put in front of a PS2 mouse to makes it a USB mouse cost only a few cents). A message-based interface is great for device drivers development. Drivers do not see hardware registers and interrupts, they only see a set of pipes connected to device endpoints. In those pipes, drivers can send and receive messages to drive their devices. For instance, a USB mouse driver will receive messages containing a set of bytes describing button states and movements deltas without having to read or write any registers or reacting to an interrupt. For software developers this is not only very easy to do but it also removes a lot of points where critical bugs can be introduced. For instance, not having to write interrupt handlers removes potential bugs that almost always lead to system failure [33].

Class-generic drivers are key to the success of USB because they tremendously reduce the number of drivers require to support hardware devices. A class of device is a set of message protocols that all devices belonging to this class understand. For instance all storage devices follow the same protocol allowing drivers to use the internal storage of such devices. This explains why all USB sticks works without ever installing additional drivers.

Internally, the USB standard is based on a host-device design. The host controller regroups all device connections in a star topology (that can be extended using hubs). A host controller driver handles all basic communications to probe existing devices, get their description. This driver also handles data transfers and provides to higher level device drivers the ability to open pipes and send and receive messages to their device.

Unfortunately, the USB standard is a closed world, still very focused on cables and plugs, and it has not been adopted to connect devices internally in SoC, let alone deployed in programmable logic. Even though the key concepts could apply to the challenge we are tackling, the USB standard cannot be adopted as is. The main reason is that the USB standard is not abstract enough, as it is too tied in many ways to its master-slave serial bus design. Though, the key concepts are inspiring to design a proposal whose foundation would be an abstract message conduit, insulating both the device and the driver from the implementation details of that conduit. This opens then the path to class message protocols that can be specified as completely abstract protocols, independent of any underlying conduit, even ours. This independence between the protocols and the conduit was inspired by the Small Computer System Interface (SCSI), an earlier attempt at physically connecting and transferring data between computers and peripheral devices [34]. SCSI has a much better separation between generic drivers, using abstract SCSI protocols, and underlying low-level drivers that are actually driving specific hardware devices. In fact, a SCSI device can be driven through any message conduit, even the Internet, with a mass storage located in a data center half way around the world. But unfortunately, the SCSI architecture does not address the challenges to write low-level drivers. Drivers are still written as they always have been, using registers and bitfields tied to hardware implementations. SPI and I2C are also examples of the SCSI story, even though they managed to offer abstract conduit, they are most of the time used the old way, using registers and bitfields [35].

In contrast, there has been quite a number of other efforts from the software community tackling the difficulty of writing device drivers. Most operating systems provide high-level frameworks for developing device drivers, helping with the integration within the surrounding operating system stack. Apple Corp. provides the *I/O Kit Fundamentals* [36]. Microsoft Corp. provides the *Windows Driver Framework* [37]. But again, none are improving the situation regarding the challenges of actually driving a hardware device. Nevertheless, these improvements would equally be applicable to ease the writing of message-based drivers.

### 3.3 Message-Based Integration Solution

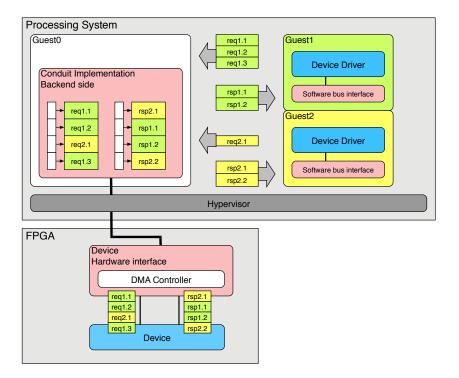

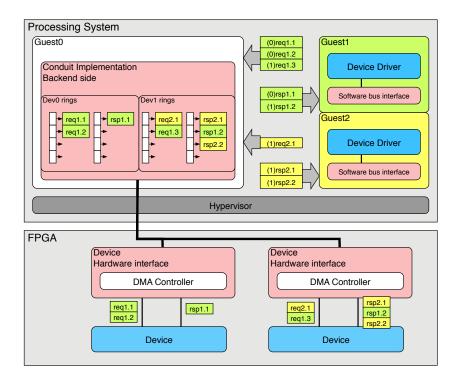

Our solution proposes to organize the interaction between a device and its driver via bidirectional channels that permit either side to send or receive messages, each message containing a variable-size payloads of uninterpreted bytes. Channels are therefore software-hardware constructs, acting as conduits for messages between the software stack running on a processing system and hardware devices deployed in programmable logic.

#### 3.3.1 The Software Perspective

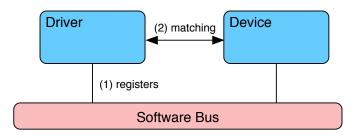

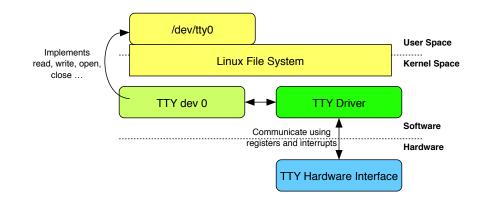

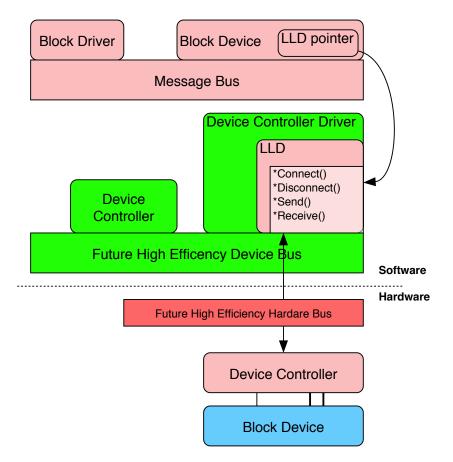

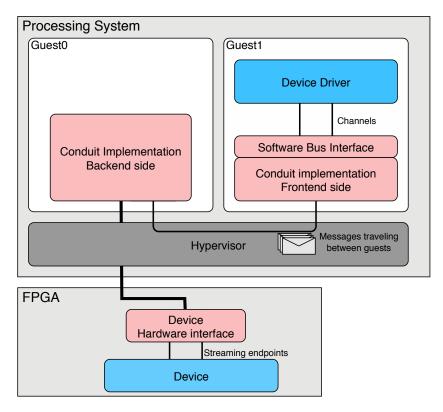

From a software perspective, the solution extends a fairly standard framework for matching devices with suitable drivers, illustrated in Figure 3.2. Inspired by Linux,

FIGURE 3.2: Focus on driver side

it is based on the same software constructs: a *bus*, *drivers*, and *devices*. Both devices and drivers are registered with the bus (1). For each available hardware device, the bus creates a corresponding *device*—a software construct that describes the hardware device. Once a device is created, the bus searches for a matching driver (2), picked amongst the drivers that are registered with the bus.

The bus is therefore fully dynamic with respect to available devices and registered drivers. Devices are created when they become available and removed when devices fail or become unavailable. Drivers may be registered and unregistered at any time, using the two functions listed below that are part of the software bus interface:

```

void register_driver(struct driver* driver);

void unregister_driver(struct driver* driver);

```

Notice that each driver is described by an in-memory data structure, see the Listing 3.1 below. In that structure, the field *devices* specifies a list of compatible devices as an array of device identities, an array that is used by the bus to filter devices that can be matched with this driver, simply comparing device identities. The identity of a device is composed of the usual numbers provided by all devices: vendor number, device number, and release number. Of course, this limited device identity is not enough for an accurate matching of devices and drivers, it is only a pre-filtering. Therefore, a driver needs to probe and tries to configure a device before a match can be considered as valid. This requires a specific matching protocol between the bus and a driver, using the following two function pointers: matched and unmatched.

```

struct driver {

const struct device_id* devices;

int (*matched)(struct device*);

void (*unmatched)(struct device*);

};

```

LISTING 3.1: "driver structure"

These two functions are defined by the driver and called by the bus. The bus calls the function matched to notify a driver that it has been matched with the given device, based on the simple device identity filtering. This is when the driver starts probing and configuring its device using messages. This is of course an asynchronous process that may require sending and receiving several messages. But as far as the bus is concerned, the driver and the device are matched. At any point in time, the driver may decide that the device is not a match after all and ask the bus to unmatch that device, calling the following function unmatch that is part of the bus interface:

```

void unmatch(struct driver* driver, struct device* device);

```

Of course, the bus may also decide unilaterally that a device and a driver must be unmatched. This may be needed for several reasons. A device may have failed. A device may be controlling an external device that has been unplugged. Or it is an administrative decision to either unload the driver or to disable the device. To achieve this unmatching, the bus calls the driver through the callback unmatched setup in the driver structure, seen earlier in Listing 3.1. Once a device have been umatched from a driver, that device is never rematched with that driver until the next reboot of the system or until the driver is unregistered and then registered from the bus.

While a driver and a device are matched, they solely communicate through sending and receiving messages through channels. The available channels are managed by the bus and described in the following device structure:

```

struct device {

struct device_id id;

unsigned int num_channels;

struct channels* channels;

};

```

Each channel provides the capability to both send and receive messages. The send function is setup by the bus and called by a driver to send a message through the channel. The received function is setup by the driver and called by the bus when a

message has been received from the device. Note that both sending and receiving messages are non-blocking asynchronous operations.

```

struct channel {

void (*send)(struct message msg);

void (*received)(struct message msg);

};

```

It is the responsibility of the driver to setup the received callback for all the channels defined by a device and this must happen when the driver is matched with that device. This means that a driver must, before returning from the matched call, setup the received callbacks in all the channels and then confirm this setup by asking the bus to connect the channels via the following bus function:

```

void connect_channels(struct device* device);

```

Once channels are connected, a driver can send and receive messages. As discussed earlier, this usually starts with probing and configuring the device, potentially negotiating which message protocol to use through which channel. Messages are variablesize payloads of uninterpreted bytes, described by the following structure:

```

struct buffer {

uint8_t* bytes;

size_t nbytes;

}

struct message {

struct msg_channel* channel;

struct buffer* payloads;

void (*released)(struct message msg);

};

```

A message refers to the channel it is travelling through and it refers to a payload. The payload may be only one buffer or a sequence of multiple buffers. This interface allows to exploit scatter-gather DMA engines and avoids unnecessary memory-to-memory copies. This is useful not only to add headers without inducing unnecessary copies but also in permitting application messages to be across multiple buffers. Received messages may also be scattered across multiple buffers, which is interesting to let device to send multi-part messages. This also leaves the bus designer the required implementation freedom when it comes to implementing channels and the corresponding exchange of messages between the processing system and the programmable logic.

Note the released callback that permits an efficient memory management protocol that is compatible with our asynchronous send and receive operations. The released

callback notifies the creator of a message that the message has been consumed: either it has been sent or it has been processed once received. When sending, the callback is set up by the driver and until it is called by the bus, the driver may not modify or free the message or the message payload. When receiving, the callback is set up by the bus and until it is called by the driver, the bus may not modify or free the message or the message payload.

Thanks to this protocol, we can avoid memory-to-memory copies entirely when sending or receiving messages. For received messages, the bus gives a direct pointer to its internal buffer where the message was received directly from the hardware device. If the driver is able to handle the message within the received callback, it can call the released callback before returning. This is the most efficient scenario. However, if the driver needs to make a copy, it can use a memory-to-memory DMA engine, in which case it will call the released callback upon the completion interrupt of the DMA request.

#### 3.3.2 The Hardware Perspective

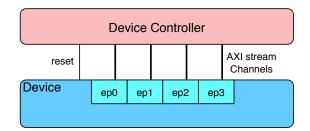

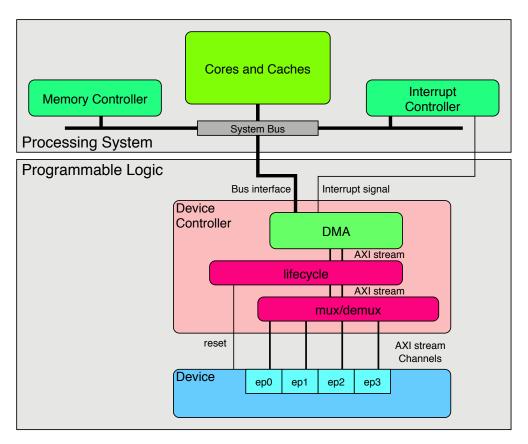

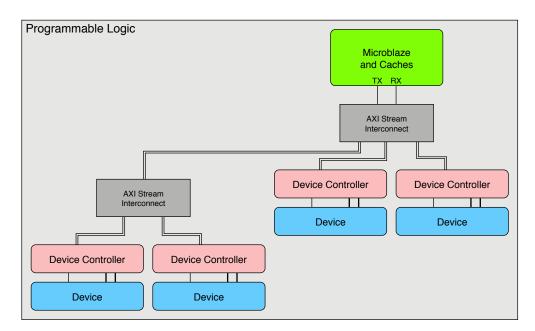

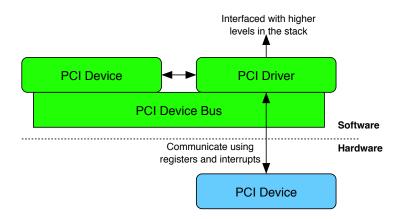

The Figure 3.3 illustrates the hardware perspective. The device, deployed on the programmable logic as a set of interconnected hardware components, is interfaced to a device controller. The device controller acts as a bridge to the software world. The device controller exposes a set of channels and a reset signal. The device controller comes as a generic hardware component that is configurable at design time. The designer can choose the number of channels, with the channel 0 being always present. The designer can also choose between high-performance or low-performance streams, depending on the expected bandwidth.

This suggests that device controllers will be ultimately designed and provided by the vendors of the programmable logic, such as Xilinx or Altera. Until then, device controllers can be designed as regular hardware components, using standard design tools and leveraging standard interfaces to system buses and interrupt controllers. For instance, we were able to design our device controllers using hardware components available in the Vivado tool from Xilinx. Although we used existing components, nothing precludes the complete design of specific device controllers that would exploit specific hardware features.

FIGURE 3.3: Hardware device perspective

From the device perspective, each channel is a pair of unidirectional data streams represented by endpoints, one endpoint being a stream slave to receive data and the other being a stream master to send data. These streams seem to require a full specification of the corresponding signals. While we suggest to use an existing standard, we do not impose any specific stream specification, leaving tools and boards designers with enough implementation freedom. For illustrative purposes, one could choose the AXI-stream standard that defines for each stream a set of data signals, a pair of control signals, and an end-of-packet signal that is useful to demarcate the last word of a message. We will discuss later the pros and cons of imposing a stream specification or letting each vendor choose their own.

Even though the details of the streams may be specialized, the concept of streams is not imposed. Furthermore, each stream is used to either send or receive messages, not both. This design is better than multiplexing channels onto a single pair of streams. Indeed, it simplifies the handling of messages for the device, with a simple automaton per endpoint. It also permits the hardware designer to tailor the buffering capabilities of each endpoints, better controlling resource consumption in the programmable logic. It also offers greater flexibility when it comes to bandwidth and latency. For instance, certain endpoints may be used to transfer large data messages while other endpoints are used for out-of-bound small messages. Finally, this allows to configure each endpoint as either high or low performance.

Messages have a very simple format. Each message includes a fixed-side header followed by a variable-size payload. The header contains two fields, one is the message type and the other is the length in bytes of the payload. The message type is used to differentiate control and data messages, a distinction that will become clear soon. Each message must be transmitted as a whole, therefore, each endpoint is a first-in-first-out lossless stream of messages. However, there is no timing constraints on the stream, a device may receive or send a message at its own pace.

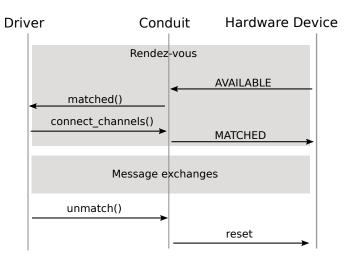

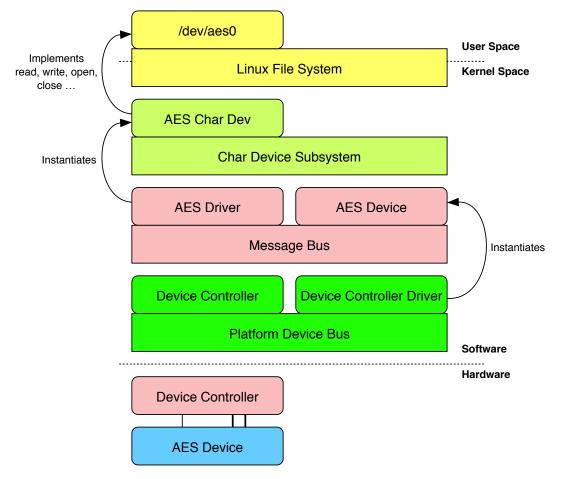

FIGURE 3.4: Device lifecycle

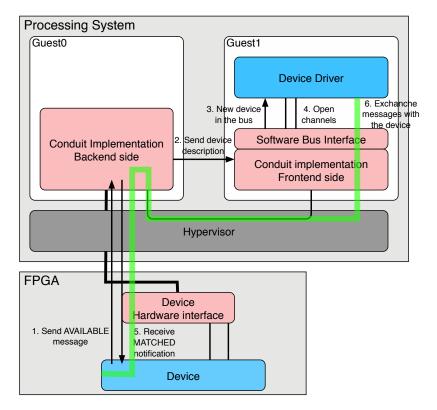

#### 3.3.3 The Overall Lifecycle

The Figure 3.4 illustrates the lifecycle of a hardware device. Notice that this lifecycle involves not only the hardware device and its controller controller on the programmable logic but also the software bus and the device driver on the processing system. Three actors are involved: (1) the device on the programmable logic, (2) the device driver on the processing system, and (3) the message conduit that sits in the middle, across the programming system and the programmable logic. This conduit is thus a mix of software and hardware, composed of the software bus on the processing system and the device controllers on the programmable logic. The conduit is responsible to route messages through channels but it is also responsible to coordinate the lifecycle of both devices and device drivers.

Upon a general reset, all device controllers are held in the reset state, in turn holding their devices in the reset state. When a device controller wakes up from the reset state, it wakes up its associated device, releasing the reset signal. When a device wakes up from the reset state, the device initializes internally and then sends a first message to its device controller, through the endpoint 0. This is entirely asynchronous and each device may take as long as necessary to send this first message. This means a device is allowed to never send that first message, which may happen because the device is currently disabled or because it cannot recover from a previous failure.

This first message, *AVAILABLE*, contains the identification of the device and indicates to the device controller that the device has initialized properly and is now available. Upon the reception of this message, the device controller informs the software bus running on the processing system that it should reify the available device and attempt

to match it with a driver. At this point, the device is waiting for a driver to be matched. This matching will happen on the processing system at some later time, if it happens at all. If it happens, the matched driver will call the function connect\_channels on the bus and the bus informs the device controller that in turn will send a message *MATCHED* to the device through the endpoint 1.

This message *MATCHED* finishes the rendez-vous between the hardware device and the software driver, both sides may now freely send or receive messages. Indeed, remember that channels are full-duplex and not master-slave, even though individual endpoints are master-slave streams. Note that sending messages advantageously replace the more traditional scheme of raising interrupts that was used to signal the processing system. The message can carry the right information describing the condition that requires the processing system attention rather than having the driver peek at the hardware register trying to discover what needs to be done.

This lifecycle is designed so that either party may break the rendez-vous. The most likely scenario is that a driver is unmatched from a device, either because the driver failed or because it is unregistered. In either case, the function unmatch is called on the software bus that will inform the corresponding device controller of the unmatch. The device controller will react by cutting all the data streams to and from all endpoints, preventing any further message transfers. Next, the device controller will reset the device, restarting a new lifecycle.

The driver may not be the source of the unpairing, it may be the device because of a failure. The failure may be a hardware failure or a failure resulting from requests from the driver. When a device detects a failure, it must send an *UNAVAILABLE* message to its device controller. Upon the reception of the *UNAVAILABLE* message, the device controller will cut all transfers through the streams to and from all endpoints, preventing any further message transfers. It will inform the software bus and then it will reset the device, restarting a new lifecycle. If the device cannot recover after being reset, it just does not send the *AVAILABLE* message.

### 3.4 Messages and Class-Genericity

The software-hardware interface proposed is based on messages. Even though this is not the only approach, it is superior to the traditional register/bitfield one when

dealing with more and more devices to integrate. The fact that USB is based on those concepts is a good hint but it is important to understand how important messages are.

#### 3.4.1 Using Messages

For software developers using messages is much simpler. With the traditional approach, developers have to have both software and hardware skills. Furthermore, they have to be capable of reading and understanding the complex documentations of both the operating system kernel in which the driver is to be integrated and the complex, dense, constantly evolving, documentation of the device. This type of knowledge is relatively rare and requires highly competent engineers hence making drivers not only hard but costly.

With the message approach, almost any kernel developer can write a device driver. There are no hardware documentations, just a message-based protocol to read and understand, something that any software developer knows how to do. All the hardware details are hidden, it is just about receiving and sending messages, just like it would be over regular POSIX sockets, over the Internet, to a standard web server. Of course, it is still about writing kernel code, which is harder than user-space code.

Channels and messages are kept as simple as possible. Full-duplex channels and variable-size payloads is quite standard and feels familiar to software developers. Note in particular that channels hide the complex setup of scatter-gather DMA engines. Of course, a DMA engine may be used for performance, but it is an internal implementation detail of the conduit that channels provide. If there is a DMA engine, it is part of the device controller, it is no longer part of the device itself. This contrasts with the traditional approach in which each driver would have to manage a DMA engine that would be specific to each device since it was part of the device design. The approach is also safer since devices are no longer provided a direct access to memory.

Failures are addressed by adopting a simple and well-known fail-stop model [38]. In the real life of a device driver, device failures are not handled very well [39]. In particular, most device drivers do ignore the overwhelming number of failure-related status flags that most modern devices exhibit. Worse, some of these flags may only hint at an error, with the documentation telling you that the device may properly work, or may not. It explains why most drivers just reset their device at the very first hint of something not working as it is supposed to. A fail-stop approach makes it clearer for software developers and hardware designers: a device or a driver either works correctly or it must stop without in-between status.

However, this simplicity does not prevent advanced error management, with complex error reporting. Indeed, there is a strong distinction between error reporting and lifecycle. From a lifecycle perspective, a device or a driver either runs correctly or stops. But regarding individual requests, the request may succeed or fail, without the device or the driver failing. For instance, a block device may report different error conditions when a write or read operation of a block fails, but this does not mean the block device has failed. The status report of a request is simply done by sending a response message once the request has been processed.

The use of messages provides a better separation of concerns, which impacts the size and complexity of the documentation. Today, the documentation of a device has two targeted audiences: the hardware community and the software community. This makes the writing of the documentation more complex than it ought to be. Also, it ties in one documentation the public interface of the device with the details of its implementation. With messages, the only public interface is the message-based protocol.

Additionally, this solution opens the way to have message-based protocols be specified independently from any given hardware implementations. As an example, open standard bodies such as the Linux Foundation<sup>1</sup> may become the reference to define such standards. Using message-based protocols also becomes really interesting when evolving existing devices with new functionalities. The new features will be designed as new messages, extending an already existing protocol. Therefore, it will be easy in most cases to preserve backward compatibility, it is just about supporting the nonextended protocol. This way, any previously existing driver would still be able to drive new releases of the device, just without the extended features. Furthermore, a messagebased protocol is easy to extend, just add new messages or extends existing messages, in a backward compatible way.

In the case of major revisions, it may not be possible to extend the protocol, a new protocol may be necessary. This does not mean losing backward compatibility. New devices may support both the old and the new protocols. It can be done using different channels for the two protocols. It can also be done through a single channel, with the negotiation of the appropriate protocol during the probe and configure phase between the driver and the device.

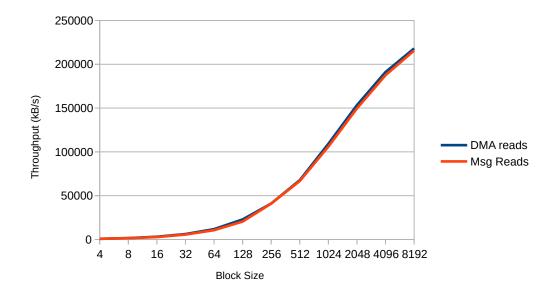

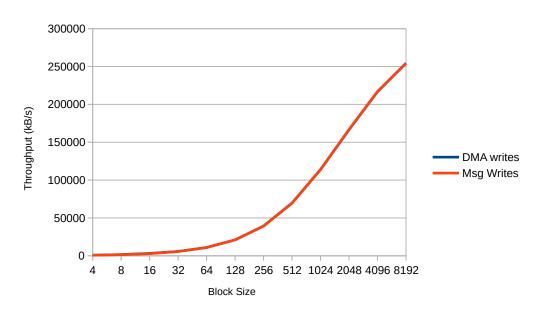

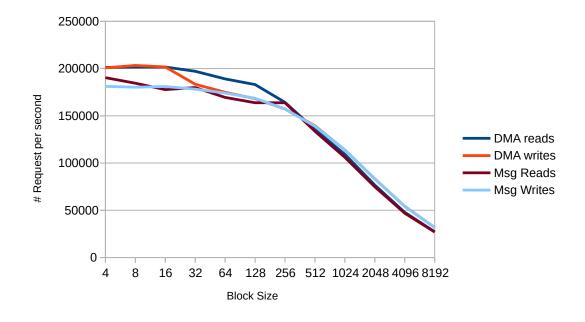

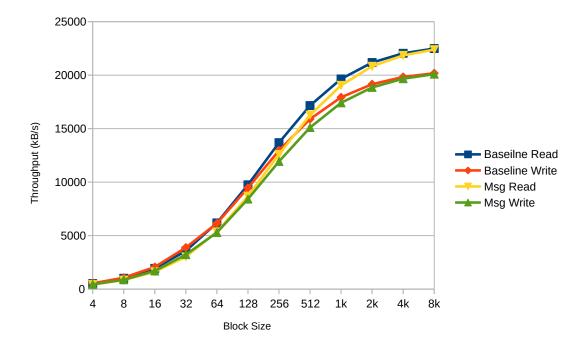

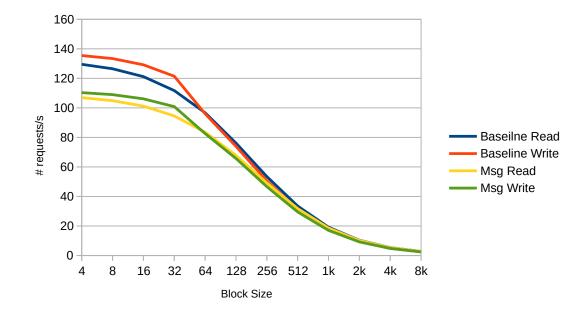

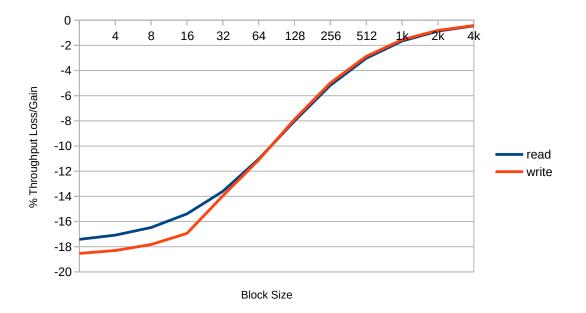

<sup>&</sup>lt;sup>1</sup>https://www.linuxfoundation.org