## Efficient scheduling of applications onto cloud FPGAs

Matteo Bertolino

#### ▶ To cite this version:

Matteo Bertolino. Efficient scheduling of applications onto cloud FPGAs. Modeling and Simulation. Institut Polytechnique de Paris, 2021. English. NNT: 2021IPPAT001. tel-03276708

#### HAL Id: tel-03276708 https://theses.hal.science/tel-03276708

Submitted on 2 Jul 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Efficient Scheduling of Applications onto Cloud FPGAs

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à Télécom Paris

École doctorale n°626 Institut Polytechnique de Paris (IPP) Spécialité de doctorat: Informatique

Thèse présentée et soutenue à Sophia Antipolis, le 22/01/2021, par

#### MATTEO BERTOLINO

#### Composition du Jury:

Robert De Simone

INRIA Sophia Antipolis Président

Liliana Cucu-Grosjean

INRIA de Paris Rapporteur

Frédéric Rousseau

Université Grenoble Alpes Rapporteur

Virginie Fresse

Université Saint Etienne Examinateur

Ludovic Apvrille

Télécom Paris Directeur de thèse

Renaud Pacalet

Télécom Paris Co-directeur de thèse

Andrea Enrici

Nokia Bell Labs France Co-encadrant de thèse

#### Résumé substantiel

Cette recherche doctorale a été réalisée en collaboration avec les laboratoires Nokia Bell Labs France et a été aussi financée par eux. Les Bell Labs sont connus par leur récente recherche dans le domaine de la télécommunication. Le domaine de recherche de cette thèse est une étude des algorithmes de programmation pour FPGAs. Cela est motivé par l'utilisation récente des accélérateurs comme FPGAs dans des infrastructures du centre de données dans le cloud pour mieux fournir les besoins de calcul du travail intensif. L'objectif de cette contribution est la minimisation du temps de latence des travaux pour les applications avec les dépendances de données internes lesquelles sont exécutées en cloud en louant l'utilisation de FPGAs car il peut être fait par d'autres ressources hardware (ex. : CPUs, stockage). Nous traitons les applications dont les tâches ne peuvent pas correspondre à la fois à la zone FPGA : ainsi, le FPGA peut être reconfiguré au moins une fois avant de compléter l'exécution de l'entière application. Le choix de quelles tâches nous devons attribuer à quel stage de reconfiguration, a un fort impact le temps de latence globale. Les algorithmes de planification efficaces, lesguels minimisent le temps de latence. sont intéressants tant pour les utilisateurs (le coût est lié au temps d'utilisation) que pour les fournisseurs (pour mieux utiliser le FPGA). Comme déjà vu dans le chapitre 3, la plupart des travaux existants sont basés sur des algorithmes lents et précis ou sur des heuristiques rapides dont la qualité n'est pas optimale. Dans ce manuscrit, on proposera une nouvelle solution de programmation dont la qualité est meilleure que les heuristiques courants tandis que le temps d'exécution est semblable à une de ces heuristiques (presque dizaine de millisecondes pour les applications communes). Il existe diffèrent ouvrages connexes qui capturent les applications et les architectures en utilisant des modèles trop abstraits pour trouver de bons (en termes de temps de latence) ou décisions valides de programmation. (ex : dans le Chapitre 3 nous verrons que le FPGA est souvent représenté avec un numéro unique qui indique la quantité de la logique reconfigurable). Pour cette raison, nous avons décidé de compter sur une ou plusieurs applications concrètes et modèles d'architectures dans notre contribution. En raison de la nécessité croissante pour exécuter des tâches de calcul intensif (ex. : apprentissage automatique, traitement de signal, cryptographie, etc.) pour lesquels l'exécution des software n'offre pas une performance suffisant, les architectures cloud équipées avec seulement le CPU ne sont pas plus suffisant. Une solution serait celle d'intégrer l'accélérateur de hardware, lequel inclut FPGAs et CPUs. En fait, il y a des différences entre eux et par conséquent ils ne sont pas complètement interchangeables. Ainsi, un FPGA peut être plus adapté à exécuter une application donnée, et réciproquement. Pour certains types de processus, FPGAs ont été démontré d'être capable d'assurer une meilleure efficacité énergétique que le GPUs. Dans ce document, les auteurs comparent l'exécution d'un Convolutional Neural Network (CNN) en un FPGA mais aussi

dans un GPU dans le système cloud de Microsoft Catapult. En effet, leur expérience ont démontré une efficacité énergétique d'un ordre de grandeur au bénéfice de l'exécution du FPGA.

Les applications pour lesquelles FPGAs sont le plus pratiques inclues les applications hautement parallèles et/ou avec des opérations élémentaires qui ne conviennent pas bien dans le modèles de programmation CPUs ou GPUS, par exemple, le changement de bit, les données personnalisés avec de largeurs de bits non standard, etc. Les canaux qui codent et décodent les algorithmes utilisés dans la télécommunication sont de bons exemples de ces applications. Dans quelques circonstances, l'apprentissage automatique et les algorithmes d'apprentissage profond peuvent être aussi de bons candidats, en particulier s'ils sont irréguliers et si les types de données utilisées sont optimisés aux représentations non standard. Un autre exemple est montré dans le chapitre 3, où le temps et l'efficacité énergétique meilleure de FPGAs sur le GPUs est démontrée par des applications de slindingwindows, appelées Sum of Absolute Differences, 2-D convolution et Correntropy. Les applications sliding-window sont une typologie spéciale de traitement de signaux numérique qui consiste à glisser un signal plus petit, appelée window (fenêtre). à travers différentes positions dans un signal plus grand. (ex, une image). À chaque position de la window (fenêtre), il y a souvent de nombreux calculs à exécuter. GPUs sont préférés pour les computations que peuvent exploiter leur parallélisme, quand les opérations concernent les opérations SIMD ou les opérations à virgule flottante, même certains FPGA récents intègrent aussi un grand nombre d'opérations à virgule flottante. Le rendu graphe est un exemple d'application dans laquelle le GPU est un ajustement naturel en raison du traitement à virgule flottante massivement parallèle. Les autres traitements de signal, l'apprentissage automatique ou les applications de l'apprentissage profond avec des caractéristiques très semblables sont fréquemment accélérés grâce à l'utilisation de GPUs. Les accélérateurs jouent un rôle fondamental dans le cloud computing. Dans cette thèse, nous nous concentrons sur les FPGAs. Comme nous verrons, FPGAs cloud sont gérés comme tout autre ressources informatique ou de stockage et loués aux utilisateurs finales par le fournisseur cloud, la plupart du temps à travers la virtualisation. Accordant avec le paradigme Software-as-a-Service (SaaS), les services fournis par un FPGA (ou par des FPGAs) sont accessibles par APIs. FPGAs peuvent être partagé et leurs usages est multiplexé entre les usagers de plusieurs manière: synchronisation, espacement etc. D'un point de vue de la synchronisation, les ressources de le hardware peuvent être efficacement utilisées par le fournisseur pour maximiser leur ROI (Return On Investment). La solution de programmation proposée dans ce manuscrit cible la minimisation du temps d'exécution d'une application (temps de latence), lequel est un avantage pour le prix payé par les utilisateurs. En effet, plus l'exécution du temps de latence est optimisée et moins de temps est loué à la ressource matériel (hardware). Dans le moderne data centers cloud les FPGAs sont architecturalement organisés en groupes]. Les applications qui sont l'objectif de cette thèse contiennent un grand nombre de tâches dépendantes et potentiellement parallèles. Un autre exemple est l'agrégation de différentes applications avec le but de minimiser le temps de latence de l'ensemble des applications résultantes. Par exemple, celui est le cas du Spark streaming où le temps de latence de ce batch est le temps de fin de la dernière tâche. Les solutions existantes pour la programmation des applications peuvent être divisées en macro-familles. Avant tout nous avons des solutions qui se basent sur des formulations mathématiques exactes (ex. : programmation MILP). Elles assurent des solutions exactes au prix d'un temps d'exécutions potentiellement haut (jusqu'à heures, jours où années en accord avec la grandeur du problème). Cela est dû au très grand espace de solution qui caractérise le problème de programmation auguel nous nous attaquons. Les paramètres qui contribuent à la grandeur du problème sont inclus, mais ne sont pas limités à : dépendances entre les tâches, temps d'exécution, numéro des ressources demandés, temps de reconfiguration, caractéristiques du FPGA. Une autre famille bien connue est représentée par les heuristiques. Parmi les heuristiques, nous nous intéressons surtout aux listbased heuristiques. Dans les list-based heuristiques, dont les tâches individuelles sont triées dans une liste de priorité et assignées, en séguence, à la première unité disponible que correspond à leur demande de ressources. Les priorités peuvent être assignées de façon statique ou dynamique selon le différents caractéristiques, ex. : le temps d'exécution où occupation des ressources. Les list-based heuristiques ont deux avantages sur la proposition de cette thèse, appelé ce (i) ils travaillent même dans le cas où travail arrivent séguentiellement à être exécutés avec aucune connaissance préalable des emplois ultérieurs et (ii) ils sont plus vite en termes de temps d'exécution. Malheureusement, comme montré dans le chapitre 3, ces heuristiques calculent une solution de programmation qui est, en moyenne, pire que le temps de latence calculé avec notre approche. Les travaux basés sur les Meta-Heuristiques (MHs) tels que les Genetic Algorithms (GAs), Simulated Annealing (SA), Tabu Search (TS) et ainsi de suite sont très communs. En général, MHs commencent d'une solution initiale et explorent de façon itérative un sous-ensemble de l'espace de solution. Leur usage a un sens spécialement quand l'espace de solution est très grand pour être exploré entièrement, comme le problème de la planification statique des tâches sur les FPGAs. Les MHs peuvent être appliquées à une grande variété de problèmes. Au contraire, notre solution, comme montré dans le chapitre 3 traite explicitement les FPGAs et les hypothèses relatives aux tâches. En outre, ils fournissent des solutions de bonne qualité mais le temps de calcul est plus élevé que celui de notre contribution. Pour résumer, les solutions MH offrent une bonne solution qui nécessite de beaucoup de temps pour les calculs et les list-based heuristiques n'offrent pas ces bonnes solutions de façon rapide. Comme le montre notre manuscrit, Slot effectué de manière rapide et trouve une solution meilleure que les list-based heuristiques. Dans cette thèse nous mettons l'accent sur le scheduling

d'application sur le FPGAs. Nous prenons comme hypothèse que les applications sont composées de tâche dépendant (exprimable comme DAGs). Ainsi nous supposons que la somme des ressources matérielles pour chaque tâche à exécuter dans le FPGA excède les ressources matérielles de le FPGA. Par conséquent, nous ciblons les applications qui nécessitent au moins deux stages de reconfigurations à exécuter. Chaque stage de reconfiguration est ainsi composé d'une reconfiguration totale du FPGA suivi par un sous-ensemble de tâches de l'application. Les stages de reconfiguration sont exécutés séquentiellement et la séquence des stages de reconfiguration doit respecter la dépendances de données de le DAG. En d'autres mots, si la tâche B dépend de la tâche A. la tâche A ne peut pas faire partie du stage de reconfiguration qui suit le stage de reconfiguration qui inclut la tâche B. Si la tâche A et la tâche B font partie du même stage de reconfiguration, alors A doit être totalement exécuté avant que B commence à être exécuté. Évidemment, la construction des stages de reconfiguration influence fortement l'application du temps de latence. Conséguemment, notre problème de programmation consiste dans l'identification rapide des stages de reconfiguration qui mènent à l'exécution d'une application avec un temps de latence lequel est proche ou égale au temps de latence optimale. La programmation sur FPGAs est diverse de la programmation sur les CPUs. En effet, l'implémentation hardware d'une tâche exige des ressources comme des éléments logiques reconfigurables, blocs de mémoire intégrés, etc. Ces ressources peuvent rassembler à des transformateurs, ex. : mémoires, registres, noyaux etc. En plus, les ressources hardware du CPUs et des FPGAs ne sont pas suffisantes pour exécuter toutes les tâches d'une application. Néanmoins, passer d'une tâche à une autre dans les CPUs est souvent plus rapide que reconfigurer un FPGA. Ainsi, reconfigurer un FPGA peut introduire à un chronométrage qui peut être comparé à le HET de la tâche. Par conséquent, le choix de quelles tâches il faut exécuter ensemble dans un stage de reconfiguration a un grand impact pour les FPGAs que des choix semblables pour le transformateur. En plus, à cause de cette surcharge, les reconfigurations sur le FPGAs devraient être moins fréquentes du changement de contexte sur le processeur. Le problème de programmation que nous ciblons dans cette thèse est semblable à la catégorie de Resource-Constrained Scheduling Problem (RCSP). Informellement un RCSP considère les ressources et les activités limitées à une durée connue. Un RCSP prévoit aussi que les demandes de ressources soient liées par des relations précédentes. Un RCSP consiste à finding a schedule of minimal duration en assignant un temps de départ à chaque activité ainsi les relations précédentes et les ressources disponibles sont respectées. Les travaux cités dans le chapitre 3 démontrent que le RCSP classique est un grand problème NPhard. Néanmoins, notre problème de recherche diffère du RCSP classique parce que la reconfiguration FPGA présente une nouvelle variable dans l'espace de solution dont le surcharge contribue considérablement au temps de latence totale. En considérant différents exemples, on peut remarquer les intuitions suivantes : (i) la

meilleure solution n'est toujours celle qui possède un plus petit nombre de reconfigurations et (ii) la mesure clé est la quantité de temps utilisé pour exécuter les tâches de façon parallèle et qui peuvent être aussi maximisés. Afin de le faire, les tâches qui consomment plus de temps doivent être probablement considérées comme les plus importantes parce que elles ont des avantages potentiellement plus grands.

Notre solution essaye de minimiser le temps de latence d'une application en regroupant les tâches en stages de reconfigurations. Comme montré dans les sections précédentes, le parallélisme entre tâches et tâche dominantes (ex. : tâches qui ont des HET plus élevés) sont les points clé des problèmes qui sont traités par nos solutions. En effet, notre solution est liée à la sélection des tâches dominantes et nous voulons aussi mettre ces tâches dominantes en parallèle avec un sous-ensemble de tâches qui peuvent être exécutés en parallèle. Afin de sélectionner quelles tâches mettre en parallèle à la tâche dominante, nous considérons tout le graphe, et pas seulement la qualité du parallélisme entre la tâche dominante et la tâche parallèle à elle. Ainsi, notre décision considère les ressources demandées et les HET des tâches, les dépendances des données entre eux, les caractéristiques du FPGA et le temps de reconfiguration. Parmi toutes les tâches possibles qui peuvent être mises en parallèle avec la tâche dominante, nous définissons, dans ce travail, un approche de base qu'aide à définir quelles sont les tâches à sélectionner.

Une fois que la tâche dominante et les tâches mises en parallèle ont été sélectionnées grâce au service de notation (ex. : la création d'un stage de reconfiguration), le graphe a été remanié pour fusionner toutes les tâches qui ont été sélectionnées dans cette itération dans un nœud unique. À chaque itération, il se crée un nouveau stage de reconfiguration et ses tâches se fussent ensemble dans un seul nœud du graphe. L'input du graphe devient une séquence de stages de reconfiguration. Cette séquence exprime la programmation sélectionnée. Pour rappel, un stage de reconfiguration contient la reconfiguration totale du FPGA suivi par l'exécution des tâches qui appartiennent aux stages de reconfiguration. Comme le montre le chapitre 4 un processus d'optimisation finale essaie de compacter davantage les stages de reconfiguration afin de continuer à réduire le temps de latence. Notre approche mire à identifier, très probablement, une bonne solution, que va minimiser le temps de latence, parce que au lieu de considérer seulement une partie donnée du graphe comme quand commence de la tâche initiale, nous préférons considérer la tâche dominante (quelle que soit son emplacement dans le graphe) et le parallélisme plus puissant du graphe pour mieux exploiter la capacité de parallélisme des FPGAs. Cet heuristique est présenté dans le Chapitre 4, tandis que l'efficience de cet heuristique est présenté dans le Chapitre 5. Les FPGAs modernes ne sont pas simplement un récipient de hardware reconfigurable mais ils peuvent aussi incorporer d'autres éléments comme les processeurs généraux, les DSPs et ainsi de suite. L'un des pionniers de ce type hétérogène de hardware reconfigurable par un software est le dispositif Xilinx Virtex II Pro, où le FPGA inclut un IBM PowerPC405. De ce moment. ont été apportées différentes améliorations. Par exemple, les produits Stellarton distribuent un processeur Intel Atom E6XX avec un FPGA Intel dans le même paquet. La dernière tendance pour le calcul d'haute performance est représentée par des projets comme Cygnus, un superordinateur qui a été développé près le Center for Computational Sciences (CCS), en Tsukuba, lequel intègre un mélange de CPUs, GPUs et FPGAs. Le calcul intensif n'est pas le seul domaine dans lequel les processeurs et les accélérateurs travaillent ensemble, parce qu'il est très commun dans les infrastructures cloud. Le problème de programmation que nous ciblons dans cette thèse est similaire à la catégorie de Resource-Constrained Scheduling Problem (RCSP). Les RCSP sont des problèmes programmés dont la programmation est influencée par la disponibilité ou le manque de ressources. Cela signifie, souvent, qu'en raison de la limitation des ressources, seulement une certaine application prendra plus de temps. Le chapitre 3 définit généralement le RCSP et présente la manière dont notre problème de programmation spécifique du FPGA s'adapte à cette classification. Le reste du travail est composé par deux aspects différents. On analyse comme chaque entité (ex. : application et architecture) est modelée avec la contribution du programme FPGA. En d'autres mots, on présente un aperçu concernant les inputs, les outputs, les hypothèses, les modèles et les paramètres nécessaires pour calculer le programme d'application dans les FPGAs. Les modèles sont utilisés pour décrire les applications et aussi l'architecture. En ce qui concerne les applications, nous mettons l'accent sur la présentation des assets de modélisation lesquels permettent de capturer les paramètres d'input pertinent pour résoudre le problème de programmation. Les modèles utilisés dans les problèmes de la programmation ont généralement beaucoup plus de paramètres grossières que les modèles utilisés par les travaux dont l'objectif est, par exemple, de générer une implémentation spécifique de hardware FPGA pour une application bien spécifique. Il est possible de conduire le même discours pour les architectures : comme nous verrons, les FPGAs sont caractérisés par une architecture complexe et les détails ne sont pas tous pertinents à la programmation. Les stratégies de programmation peuvent, en effet, faire une abstraction des paramètres avec un impact négligeable sur le temps d'exécution de l'algorithme de programmation. À cet égard, le chapitre 3 décrit comme les travaux connexes modèlent les architectures FPGA. Les modèles imprécis (ex. : les modèles qui ne considèrent pas les détails pertinents à la programmation) pourraient mener à des solutions de programmation sous-optimales ou erronées.

Modeler est important mais si nous faisons une comparaison avec la programmation, l'algorithme utilisé pour résoudre le problème de programmation est également important. Dans ce qui suit, nous allons désigner l'algorithme de résolution comme la « stratégie de programmation ». Ainsi, on va illustrerles œuvres principales de l'art qui traitent les stratégies de programmation et cela représente la partie la plus large de ce chapitre. Nous avons classifié les travaux principaux basés sur la stratégie

de programmation qui l'utilisent. En général, une stratégie de programmation peut être basée sur les meta-heuristique (MHs) ou sur les heuristiques. En outre, nous classons les derniers en list-based heuristiques et les packing-based heuristiques. Nous préférons nous concentrer seulement sur certaines de ces catégories pour les solutions d'haute qualité qu'elles fournissent (ex. : meta-heuristiques, formulations exactes) ou pour le temps d'exécution très rapide (ex. : list-based algorithmes de programmation). La contribution de cette thèse peut être placée dans la catégorie "packing-based" (ex. : les algorithmes qui prennent des décisions considérant les groupes des tâches. Cela permet d'atteindre des résultats qui peuvent se comparer avec les meta-heuristiques en termes de qualité tandis que maintenir le temps d'exécution peut être comparable aux list-based heuristiques. Pour ne pas être incomplète, les formulations mathématiques exactes peuvent être utilisées comme spécification du problème également par les heuristiques non exactes.

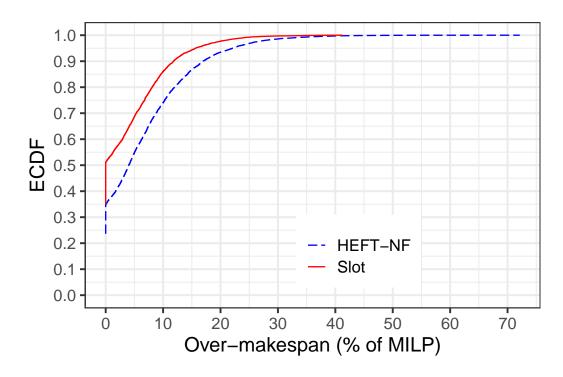

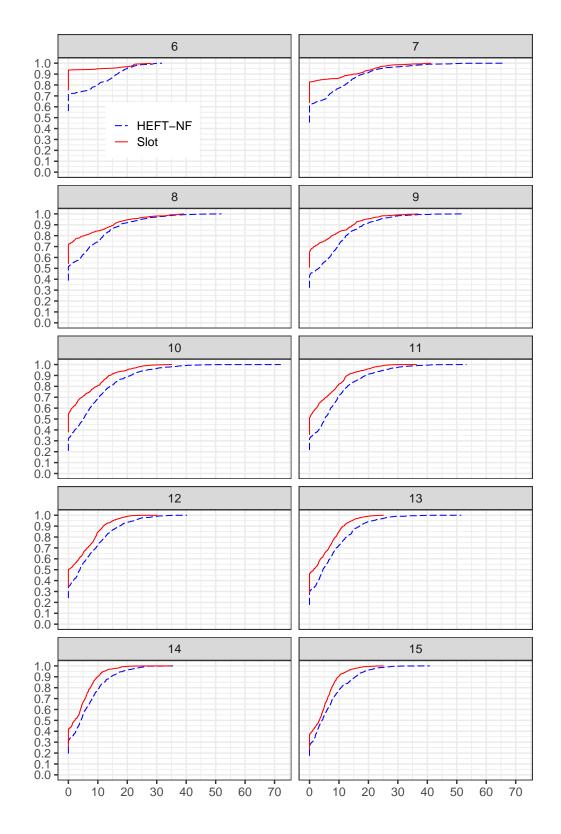

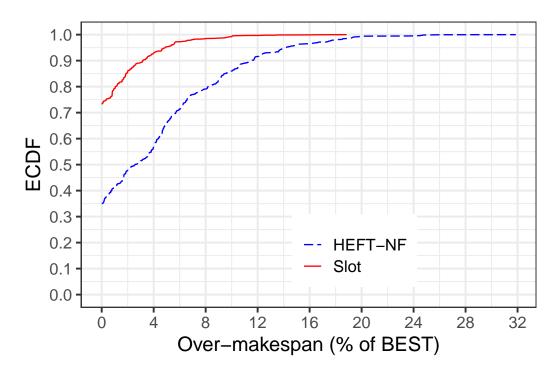

Afin d'évaluer la qualité du planning calculé par le Slot, nous devons comparer le temps de latence obtenu avec une référence optimale absolue. Donc, en premier lieu, nous avons formellement modelé le problème de programmation du FPGA et nous l'utilisons pour résoudre ces cas problématiques avec une approche exacte. Nous choisissons d'utiliser le Mixed Integer Linear Programming (MILP) parce qu'il semble vraiment adapté pour ces types de problèmes d'optimisation. Puis nous désignons un générateur d'instance aléatoire pour générer un grande nombre d'instances du problème de programmation du FPGA. Nous résoudrons ces instances avec un solveur MILP pour obtenir un temps de latence mineur et le comparer avec le temps de latence trouvé par le Slot dans les mêmes cas. Nous comparons aussi le temps d'exécution des deux approches. Enfin, nous comparons la qualité et les temps d'exécution du Slot avec le HEFT-NF heuristique dont nous avons déjà discuté. Au meilleur de notre connaissance HEFT-NF est la seule proposition comparable au Slot.

Dans le chapitre sur l'évaluation, nous avons montré parce qu'une analyse exhaustive est impossible du point de vue du temps de calcul. Puis, nous avons décrit comment nous capturons les ressources hardware et les applications. Enfin nous avons décrit les étapes principales du Slot et nous avons discuté sa complexité théorique. Nous pensons que le clé-force du Slot est son calcul intelligent des stages de reconfiguration lesquels exploitent efficacement le parallélisme d'un FPGA. Le chapitre suivant vous montrera l'évaluation d'un Slot sur un indice de référence synthétique composé par différentes instances générées de manière pseudo-aléatoire. En particulier, nous allons évaluer la qualité de la solution de programmation produite par le Slot et son temps d'exécution.

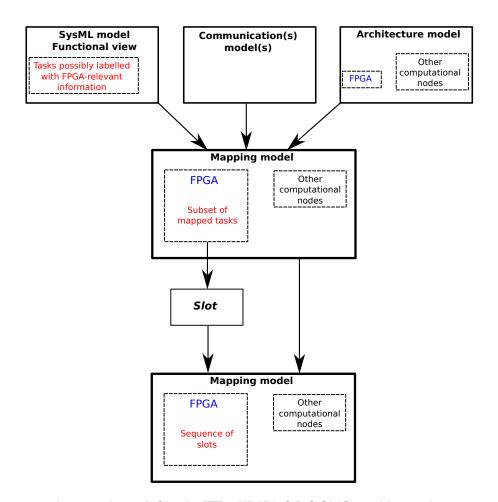

Nous comptons sur le fait que le Slot pourrait être également intéressant pour le design du système intégré complexe. Ainsi, dans ce chapitre, nous appliquons le Slot dans un contexte différent que les centres de données cloud, comme Model-Driven Engineering. Model-Driven Engineering (haut niveau) modèle le système

intégré en offrant des modèles dédiés pour capturer des composants hétérogènes de hardware/software. Les modèles peuvent représenter une application, une plate-forme et donc la manière dans laquelle une application peut être mappée sur une plateforme. En plus, les modèles peuvent être transformés afin de générer de modèles exécutables (pour des vérifications formelles ou pour des fins de simulation) et un code exécutable pour les modèles de haut niveau. Grâce à leurs abstractions internes, les modèles devraient aider à se concentrer sur les aspects les plus importants du système. À l'égard des FPGAs, nous pensons que ces deux caractéristiques importantes devraient être prises en considération : parallélisme de hardware et reconfiguration dynamique.

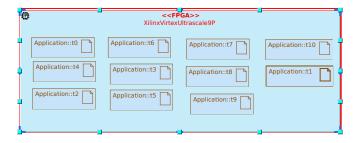

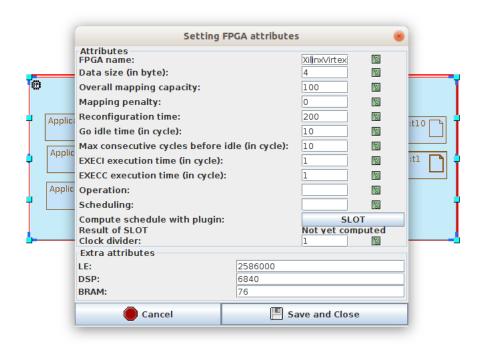

Pour mieux supporter le design des systèmes intégrés, nous avons intégré un Slot dans un cadre de Model-Driven Engineering (MDE) appelé TTool. TTool est un instrument gratuit et open-source qui supporte différents stages de développement avec UML/SysML (ex. : déterminations des besoins, analyses, partitioning hardware/software et design software (intégré). Parmi les différents instruments MDE, TTool a été sélectionné en raison de sa légèreté et de son extension facile, TTool, en effet, a déjà démontré de supporter les applications de traitement de signaux. Nous avons intégré le Slot aux TTool/DIPLODOCUS à travers un plugin. TTool/DIPLODOCUS étaient déjà capables de représenter les FPGAs et les reconfigurations dynamiques pour effectuer des simulations sur les tâches mappés sur le FPGA. Encore, la programmation des tâches pour les FPGAs devrait être faite à main. Étant donné une application mappée sur le FPGA, le Slot peut être appliqué pour déterminer les stages de reconfiguration de la programmation. Cet information de programmation peut être transmise au moteur de simulation – par exemple pour vérifier que cette programmation sélectionnée travaille bien avec les autres parties du système – où qu'elle peut être utilisée par le moteur Design Space Exploration qui peut utiliser l'information fournit par un stage de reconfiguration pour prendre des décisions davantage.

Le travail futur de cette thèse cible à des architectures différentes des celles présentées dans le Chapitre 7. En effet, nous voulons appliquer les principes du Slot aussi dans d'autres typologies de situation qui pourraient se vérifier dans les projets réels. Nous rappelons au lecteur que les stages principaux du Slot sont (i) privilégier les tâches dominantes, (ii) la génération d'un ensemble de stages de reconfiguration candidats commence par la tâche dominante, (iii) l'évaluation du stage de reconfiguration plus promettant à l'égard du temps de latence globale (pour cela nous utilisons un système de notation) et (iv) optimiser davantage la solution en compactant les stages de reconfiguration sélectionnés. Grâce à l'approche modulaire du Slot, nous comptons qu'avec une légère adaptation les différents stages peuvent utiliser le Slot pour d'autres problèmes de recherche.

Ainsi nous proposons les six directions suivantes:

Pour résoudre les problèmes d'évolutivité du Slot: de la complexité de la discus-

sion et l'évaluation, nous avons remarqué que le Slot ne s'adapte pas très bien avec le nombre des stages de reconfiguration candidats, même si les dépendances des données et les ressources disponibles limitent le nombre des stages de reconfiguration candidats. Cela peut affecter le temps d'exécution du heuristique dans le cas où il est appliqué aux graphes avec des centaines de tâches.

La programmation des tâches que peut requêter des ressources programmées dépendantes : nous avons classifié les ressources en deux typologies : appelé scheduling-independent et scheduling-dependent resources. Une scheduling-independent resource est une ressource qu'est assignée exclusivement à une tâche pour la durée totale du stage de reconfiguration et que contient la tâche. Ainsi, une requête pour une spécifique scheduling-independent resource (tels que LEs) sans un stage de reconfiguration peut être géré simplement en ajoutant les deux ensembles. Une scheduling-dependent resource est une ressource qui peut être assignée à une tâche pour la durée totale de la tâche. La dernière est toujours mineure ou égale à la vie totale du stage de reconfiguration qui contient la tâche. Les tâches qui enquêtent une scheduling-dependent resource excèdent la limite physique pour un FPGA spécifique qui peut faire partie du même stage de reconfiguration comme s'ils étaient scheduling-independent ainsi, probablement de façon pessimiste.

Une discussion intéressante est que le Slot travaille mieux quand toutes les tâches qui composent les graphes d'application diffèrent l'un de l'autre. En effet, dans le cas où le graphe d'application contient des multiples instances de la même tâche mais dans différent parties du graphe, nous pensons que la meilleure manière pour calculer les stages de reconfiguration devrait être bien définie. En plus, dans le Slot future il faut considérer des multiples implémentations pour la même tâche et décider quel peut apporter plus bénéfices à la réduction du temps de latence.

Le Slot courant est appliqué à une ou plusieurs applications qui sont exécutées sur un seul FPGA. En future, nous planifions de l'appliquer à des meilleures architectures ciblées lesquelles permettent d'exploiter les capacités des FPGAs à distance, comme dans Microsoft Catapult. Si nous supposons que cette latence est vraiment basse au regard du HET des tâches et au regard de la reconfiguration du FPGA, une solution pourrait simplement être celle d'adapter le Slot courant en résumant ensemble les ressources des FPGAs à distance.

Enfin, nous aimerions mieux adapter le Slot pour mieux aborder les changements dynamiques que le contexte des centres de données cloud peut nécessiter. En particulier, nous voulons relancer de façon dynamique le Slot chaque fois que la nouvelle application est assignée à un FPGA qui est déjà en train d'exécuter une application.

Ce manuscrit présente la programmation des applications sur les FPGAs. Nous avons supposé que les applications sont composées par des tâches dépendantes et les FPGAs soient totalement reconfigurés. Notre but est de minimiser le temps de latence de l'application. Nous avons placé notre contribution dans les centres de

données cloud. Nous montrons comment les architectures du centre de données cloud intègrent les accélérateurs de le hardware, comme les FPGAs, pour mieux supporter les besoins croissants des applications en termes de puissance de calcul. Le travail connexe montre que toutes ces approches existantes ne peuvent pas répondre de façon efficace à notre problématique. Nous présentons notre approche, Slot, laquelle offre un juste compromis entre la qualité de la solution (en termes de temps de latence) et le temps d'exécution qu'elle nécessite pour identifier cette solution. Le Slot est basé sur un processus itératif. Premièrement, cela considère tous les graphes et la tâche dominante de ce graphe. Dès les stages de reconfiguration qui peuvent être construits à partir de ce graphe, nous utilisons une méthode de notation qui permet de sélectionner le meilleur stage de reconfiguration. Quand un stage de reconfiguration a été sélectionné, nous fusionnons toutes les tâches de ce stage de reconfiguration ensemble dans le graphe. Enfin, cette itération extrants une séquence de stages de reconfiguration laquelle, après une optimisation finale, représentera la programmation proposée.

Nous avons montré que le Slot est efficace sur un benchmark de 37500 graphes générés de manière pseudo-aléatoire. Nous l'avons aussi comparé aux autres deux approches : Une formulation MILP, laquelle retourne souvent une solution optimale, et un heuristique existant lequel a été adapté pour mieux cibler le problème de la programmation du FPGA (appelé HEFT-NF). Dans la partie finale du manuscrit, nous montrons que le Slot peut être appliqué dans des contextes différents du centre de données cloud. Nous allons montrer comme nous l'avons intégré dans un outil d'ingénierie pilote, appelé TTool/DIPLODOCUS, lequel supporte la conception initiale des systèmes embarqués.

## **Contents**

| Contents                                              | 4  |

|-------------------------------------------------------|----|

| List of Figures                                       | 7  |

| List of Tables                                        | 10 |

| 1 Introduction                                        | 11 |

| 1.1 Introduction                                      | 11 |

| 1.2 Motivation                                        | 12 |

| 1.3 Glossary                                          | 14 |

| 1.4 Research Problem                                  | 16 |

| 1.5 Overview of the solution                          | 19 |

| 1.6 Outline of the thesis                             | 20 |

| 1.7 Conclusion                                        | 21 |

|                                                       |    |

| 2 Context                                             | 23 |

| 2.1 Main Context                                      | 23 |

| 2.2 A Short introduction to FPGAs                     | 25 |

| 2.3 FPGAs in the Cloud                                | 30 |

| 2.3.1 Microsoft Catapult                              | 32 |

| 2.3.2 Amazon Elastic Compute Cloud (F1 instances)     | 34 |

| 2.3.3 Future trend in distributed systems using FPGAs | 34 |

| 3 Related Work                                        | 27 |

|                                                       | 37 |

| 3.1 Introduction                                      | 37 |

| 3.1.1 Resource-Constrained Scheduling Problem         | 39 |

| 3.2 Modelling                                         | 40 |

| 3.3 Scheduling                                        | 43 |

| 3.3.1 Heuristics                                      | 43 |

| 3.3.1.1 List-based scheduling                         | 43 |

| 3.3.1.1.1 HEFT Next-Fit                               | 49 |

|   |      | 3.3.1.2 Packing-based scheduling                                    | 50        |

|---|------|---------------------------------------------------------------------|-----------|

|   |      | 3.3.2 Meta-heuristics                                               | 57        |

|   | 3.4  | Conclusion                                                          | 64        |

| A | Olat |                                                                     | <b>67</b> |

| 4 | Slot | <u>-                                      </u>                      | 67        |

|   | 4.1  |                                                                     | 67        |

|   | 4.2  | Assumptions                                                         | 67        |

|   | 4.3  | Unfeasibility of an exhaustive analysis                             | 69        |

|   | 4.4  | Abstracting hardware resources and applications                     | 72        |

|   | 4.5  | Sharing of applications over platforms                              | 75        |

|   | 4.6  | <u>Slot</u>                                                         | 77        |

|   |      | 4.6.1 Pseudocode                                                    | 79        |

|   |      | 4.6.2 Candidates Generation                                         | 84        |

|   |      | 4.6.3 Score                                                         | 86        |

|   |      | 4.6.4 Optimization Phase                                            | 89        |

|   |      | 4.6.5 Complexity discussion                                         | 90        |

|   | 4.7  | Conclusion                                                          | 92        |

| F | F.m. |                                                                     | 05        |

| 5 |      | erimental evaluation                                                | 95<br>05  |

|   | 5.1  |                                                                     | 95        |

|   |      | MILP Formulation                                                    | 95        |

|   | 5.3  |                                                                     | 100       |

|   | 5.4  | Evaluation results                                                  | 102       |

|   |      | 5.4.1 The practical complexity of the FPGA scheduling problem       | 104       |

|   |      | 5.4.2 Comparison of <i>Slot</i> and HEFT-NF quality                 | 106       |

|   |      | 5.4.3 Comparison of <i>Slot</i> and HEFT-NF CPU user times          | 109       |

|   |      | 5.4.4 Problem instances with completely random DAG                  | 112       |

|   | 5.5  | Conclusion                                                          | 112       |

| 6 | Inte | gration to Model-Driven Engineering                                 | 119       |

|   | 6.1  |                                                                     | 119       |

|   |      | <u> </u>                                                            | 121       |

|   | U.Z  | 6.2.1 TTool/Diplodocus overview                                     |           |

|   | 6.3  |                                                                     |           |

|   | 6.4  |                                                                     | 127       |

|   | 0.4  | Conclusion                                                          | 121       |

| 7 | Futu | re Work and Conclusion                                              | 129       |

|   | 7.1  | Resume of the contribution                                          | 129       |

|   | 7.2  | Future work                                                         | 130       |

|   |      | 7.2.1 Addressing scalability issues of <i>Slot</i>                  | 131       |

|   |      | 7.2.2 Scheduling of tasks that can request scheduling-dependent re- |           |

|   |      | sources                                                             | 132       |

| 7.2.2.1 Recall about scheduling-dependent resources  | 132 |

|------------------------------------------------------|-----|

| 7.2.2.2 Architectures                                | 133 |

| 7.2.2.3 Motivating example                           | 135 |

| 7.2.3 Scheduling of both hardware and software tasks | 137 |

| 7.2.3.1 Challenges                                   | 138 |

| 7.2.4 Particular features of tasks                   | 139 |

| 7.2.4.1 Addressing duplicated tasks                  | 139 |

| 7.2.4.2 Multiple implementations                     | 140 |

| 7.2.5 Exploiting the capabilities of remote FPGAs    | 140 |

| 7.2.6 Dynamic adaptation of scheduling in cloud      | 141 |

|                                                      |     |

| A Low-level details of the MILP formulation          | 143 |

| D. Lint of care name                                 | 140 |

| B List of acronyms                                   | 149 |

| Bibliography                                         | 153 |

## **List of Figures**

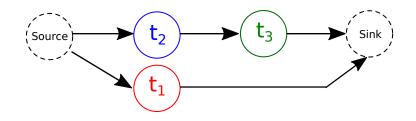

| 1.1  | 8-tasks DAG example                                                      | 17  |

|------|--------------------------------------------------------------------------|-----|

| 1.2  | 10-tasks DAG example                                                     | 18  |

| 1.3  | DAG of Figure 1.2 after merging task $D$ and task $E$ in slot $Slot$     | 18  |

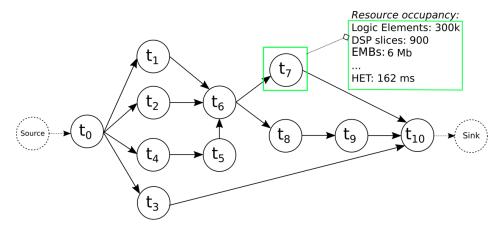

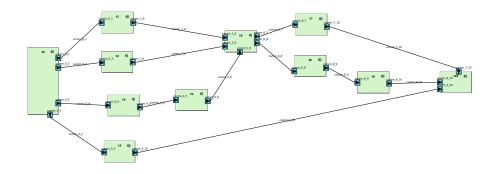

| 1.4  | A realistic application DAG                                              | 19  |

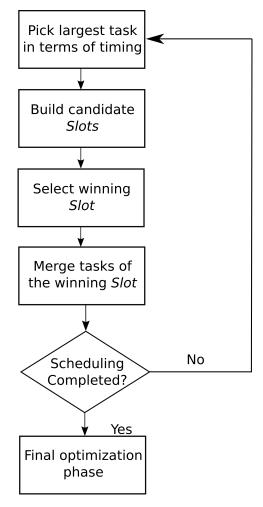

| 1.5  | The main steps of <i>Slot</i>                                            | 21  |

| 0 1  |                                                                          |     |

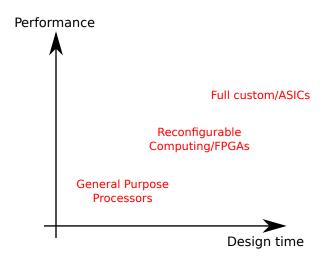

| 2.1  | Reconfigurable computing as a trade-off between GPPs and ASICs           | 25  |

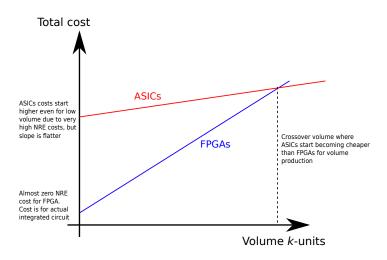

| 2.2  | ASICs vs FPGAs - production costs and NRE costs                          | 26  |

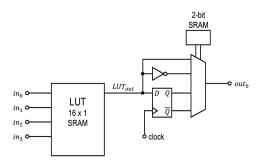

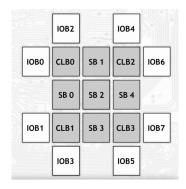

| 2.3  | Composition of a Logic Element                                           | 27  |

| 2.4  | LEs organization                                                         | 27  |

| 2.5  | FPGA interconnections - Switch boxes                                     | 28  |

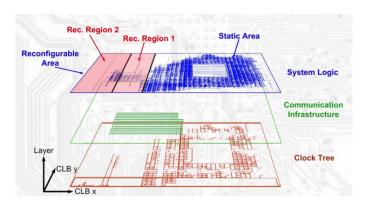

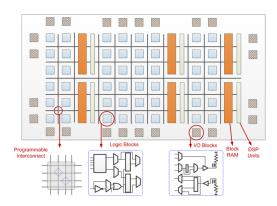

| 2.6  | FPGAs architecture - a global view                                       | 29  |

| 2.7  | Main components of FPGAs architecture                                    | 29  |

| 2.8  | Three possible connection scenarios between CPUs and FPGAs in cloud      |     |

|      | data centers                                                             | 31  |

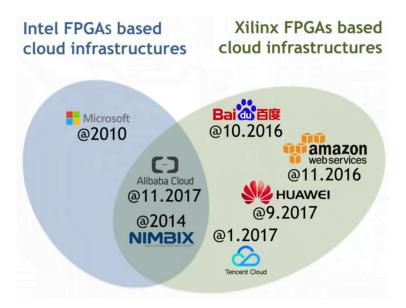

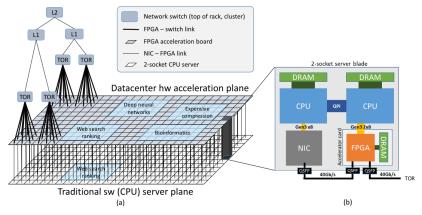

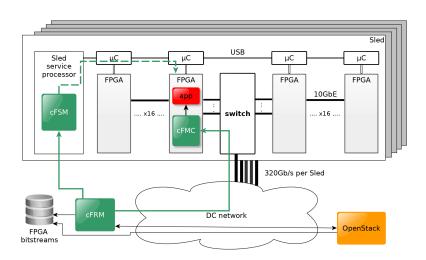

|      | The integration of FPGAs in some cloud data centers                      | 32  |

|      | Microsoft Catapul cloud data center architecture, from [33]              | 33  |

| 2.11 | Division Shell-Roles in Microsoft Catapul FPGAs, from [33]               | 33  |

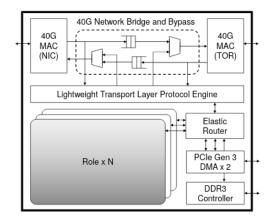

|      | Amazon Elastic Cloud 2 - F1 instance, from [4]                           | 35  |

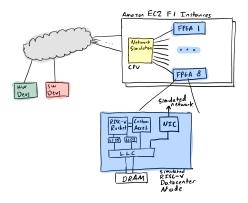

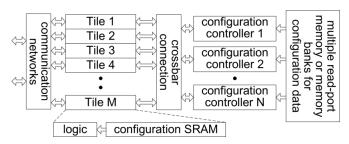

| 2.13 | System architecture of the IBM <i>cloudFPGA</i> platform, from [97]      | 36  |

| 0.4  | Aughitantura mandal of [00]                                              | 45  |

| 3.1  | Architecture model of 93                                                 | _   |

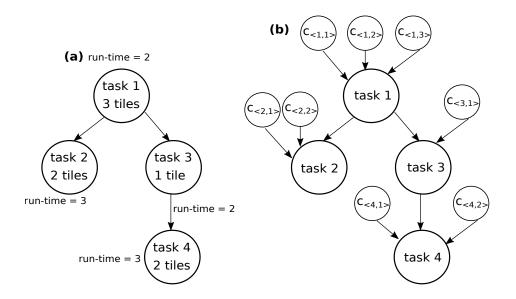

| 3.2  | Case study from [93]                                                     | 46  |

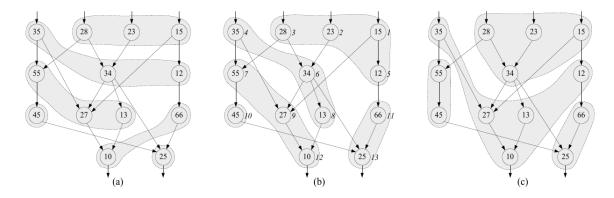

| 3.3  | Case studies from [64]. Figure (a) shows the application of WBS algo-    |     |

|      | rithm. Figure (b) shows the application of HPF-NF algorithm. Figure (c)  |     |

|      | shows the application of RDMS algorithm. The latter is explained in Sec- | 40  |

| 0.4  | tion [3.3.1.2]                                                           | 49  |

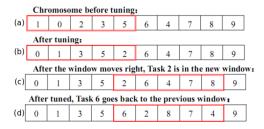

| 3.4  | GA-SW generation of the initial population of 39                         | 60  |

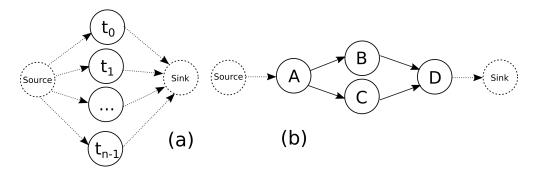

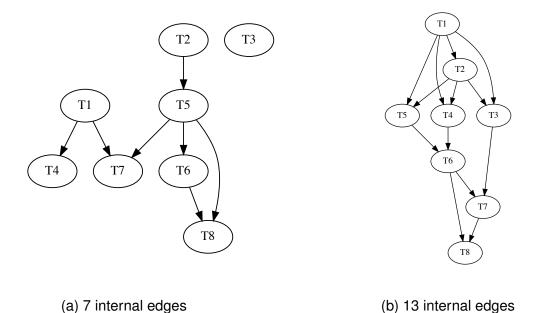

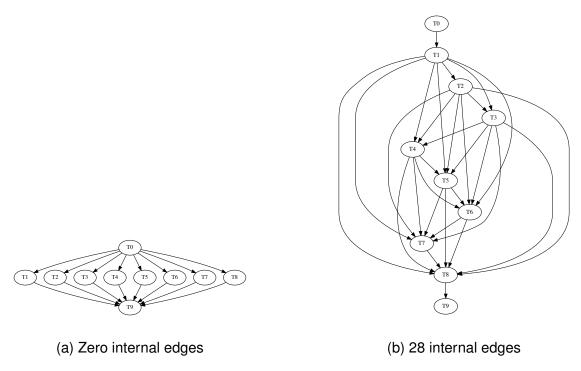

| 4.1  | Application DAGs - simple case studies                                   | 71  |

| 4.2  | 6-tasks application DAG                                                  | 72  |

|      | <u> </u>                                                                 | . – |

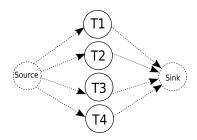

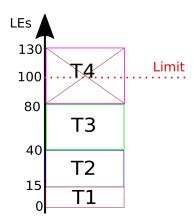

| 4.3  | Occupancy of the FPGA with regards to the number of used Logic Ele-               |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | ments (LEs). Tasks $T4$ cannot be part of the same slot of $T1$ , $T2$ and        |     |

|      | $\overline{T3}$                                                                   | 73  |

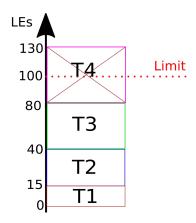

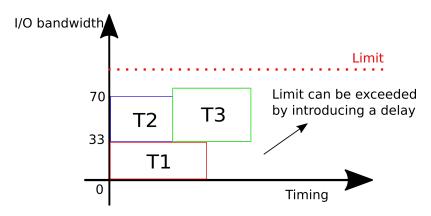

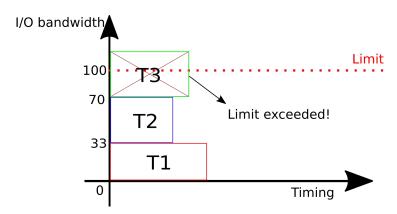

| 4.4  | Occupancy of the FPGA with regards to the required I/O bandwidth. Tasks           |     |

|      | T3 cannot run in parallel with tasks $T1$ and $T2$                                | 74  |

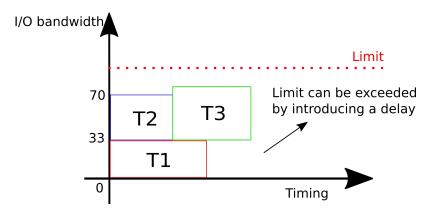

| 4.5  | Occupancy of the FPGA with regards to the required I/O bandwidth. Tasks           |     |

|      | T3 cannot run in parallel with tasks $T1$ and $T2$ , but they can be part of the  |     |

|      | same slot by introducing a delay                                                  | 74  |

| 4.6  | An example of application DAG which is the input of <i>Slot</i> : each node,      |     |

|      | representing a task, is labelled with resource requests information and           |     |

|      | <u>HET</u>                                                                        | 75  |

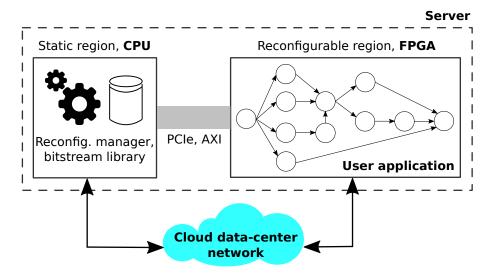

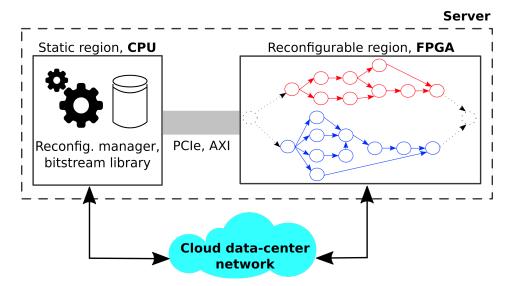

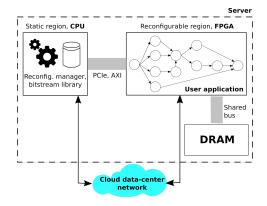

| 4.7  | The architecture of a modern FPGA-based server                                    | 76  |

| 4.8  | Sharing of applications on the same platform                                      | 77  |

| 4.9  | Sharing of the platform among different users through reconfigurable re-          |     |

|      | giorns                                                                            | 78  |

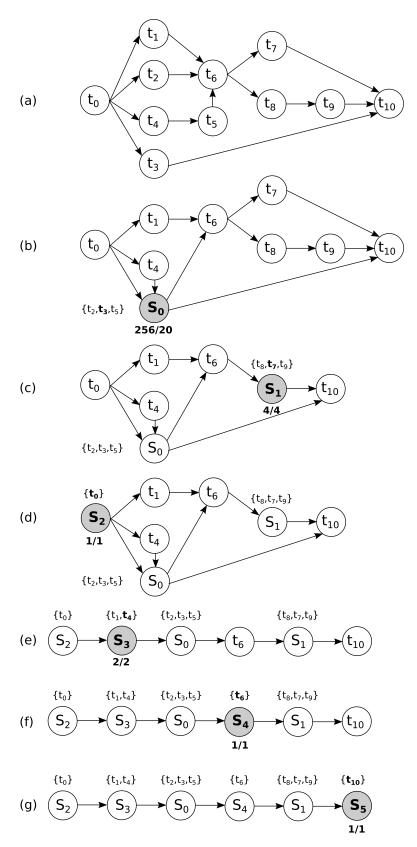

|      | 13-tasks application DAG, used as case study for this Chapter                     | 79  |

| 4.11 | First slot computed by <i>Slot</i> with respect to the case study of Figure 4.10. | 81  |

| 4.12 | Merging of the tasks which compose the slot identified in Figure 4.11             | 82  |

| 4.13 | All the steps of Slot applied to an example. To keep the figure ligher,           |     |

|      | artificial source and sink are not represented                                    | 83  |

| 4.14 | Removing tasks $t_0$ , $t_3$ and $t_{10}$ from case study of Figure 4.10          | 85  |

| 4.15 | DAG considered by the scoring-based system for the first iteration of Slot        | 88  |

| 4.16 | Reducing the makespan of Figure 4.13g as described in Algorithm 4                 | 90  |

| 5.1  | Randomly generated 10 tasks DAG                                                   | 103 |

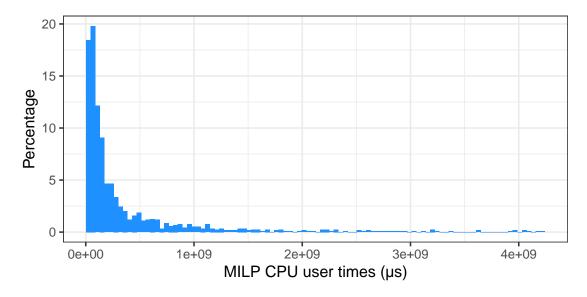

| 5.2  | Histogram of MILP CPU user times for $n_t = 15$ tasks                             | 105 |

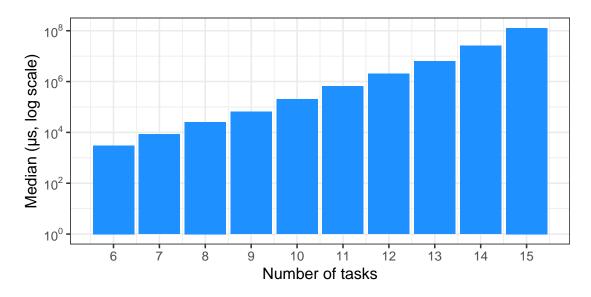

| 5.3  | Median of MILP CPU user times vs. the number of tasks                             | 106 |

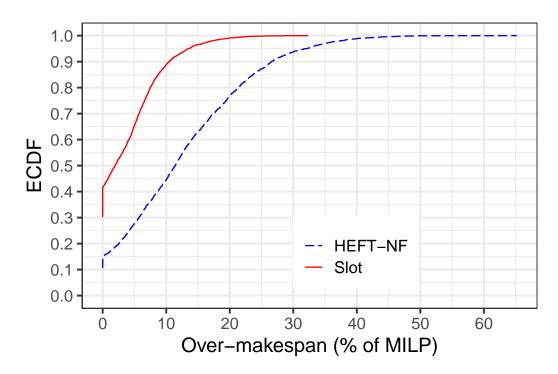

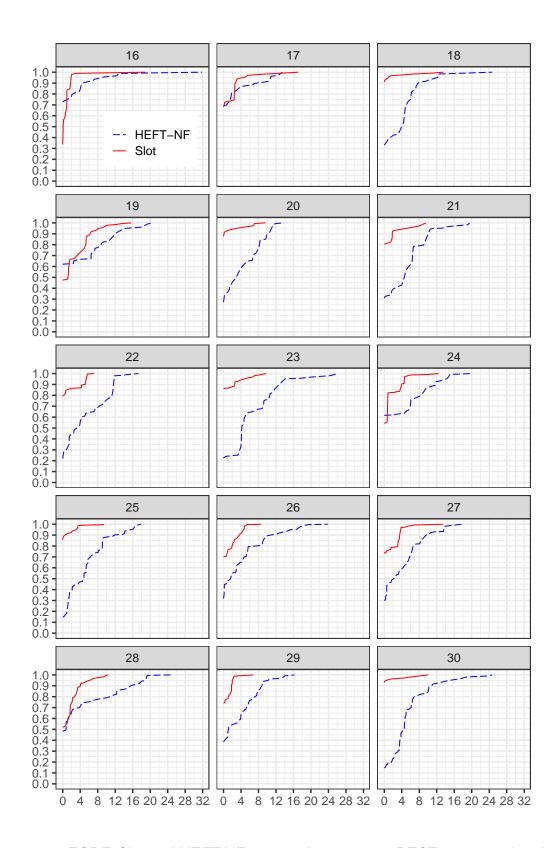

| 5.4  | ECDF of Slot and HEFT-NF over-makespans vs. MILP, all batches                     | 107 |

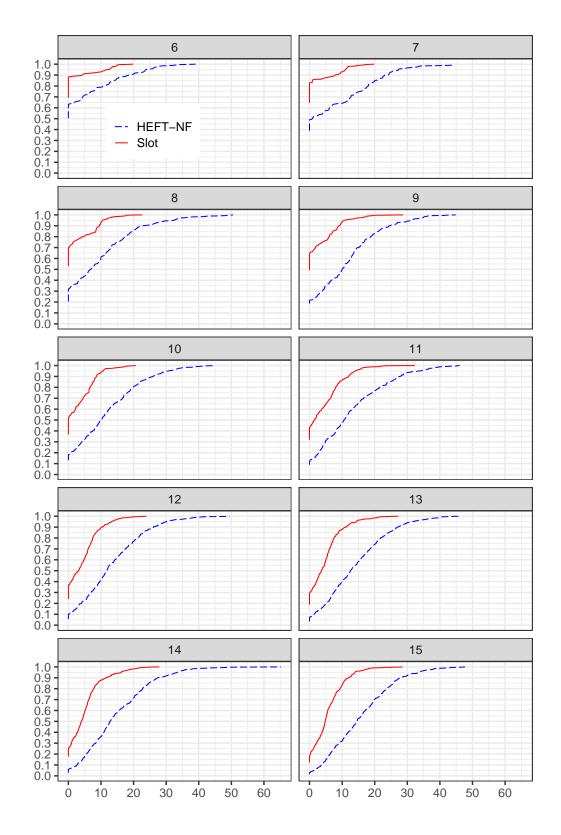

| 5.5  | ECDF Slot and HEFT-NF over-makespans vs. MILP, separate batches                   | 108 |

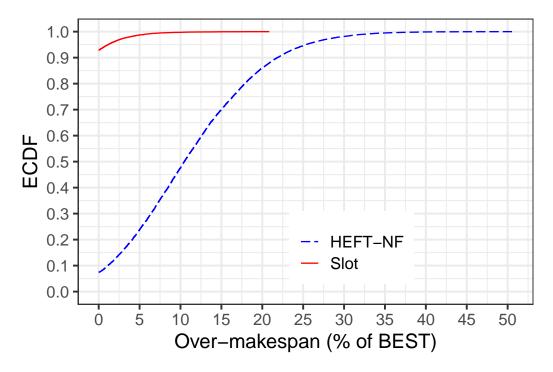

| 5.6  | ECDF of Slot and HEFT-NF over-makespans vs. BEST, all batches                     | 109 |

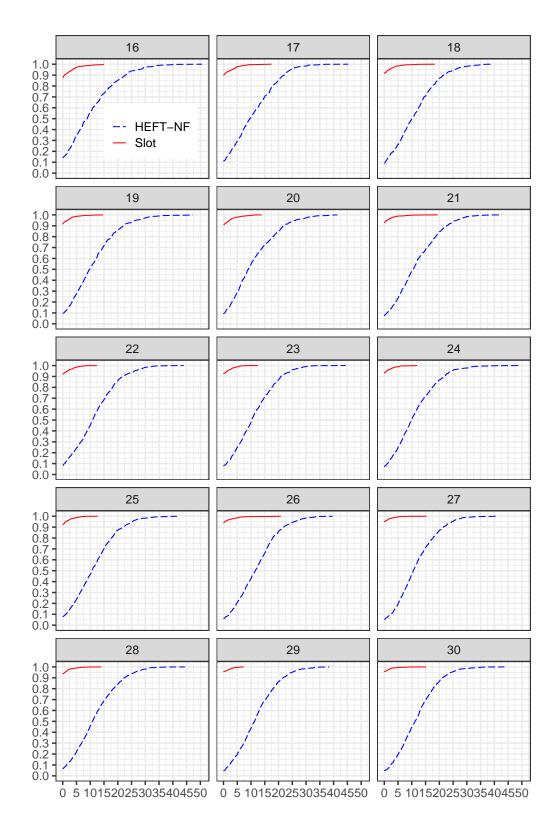

| 5.7  | ECDF Slot and HEFT-NF over-makespans vs. BEST, separate batches .                 | 110 |

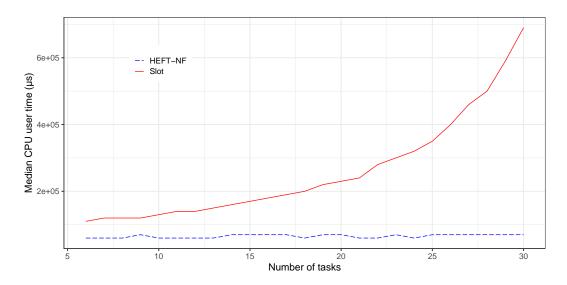

| 5.8  | Median CUT of Slot and HEFT-NF vs. number of tasks                                | 111 |

| 5.9  | Randomly generated 10 tasks DAG                                                   | 113 |

| 5.10 | ECDF of Slot and HEFT-NF over-makespans vs. MILP, all batches                     | 113 |

|      |                                                                                   | 114 |

|      | ECDF of Slot and HEFT-NF over-makespans vs. BEST, all batches                     | 115 |

|      | ECDF Slot and HEFT-NF over-makespans vs. BEST, separate batches .                 | 116 |

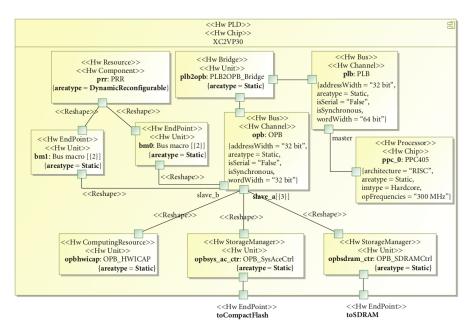

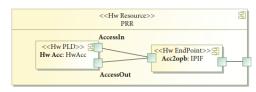

| 6.1  | FPGA modelling in Gaspard and MARTE, from [95]                                    | 120 |

| 6.2  | Internal composition of PRR block, from [95]                                      |     |

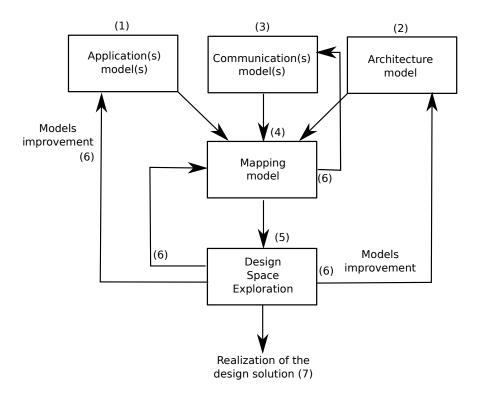

|      | Ψ-Chart approach from [48]                                                        | 122 |

| 6.4  | Integration of <i>Slot</i> in TTool/DIPLODOCUS and in $\Psi$ -chart approach                  | 124 |

|------|-----------------------------------------------------------------------------------------------|-----|

| 6.5  | TTool - Application view                                                                      | 125 |

| 6.6  | TTool - Mapping view                                                                          | 125 |

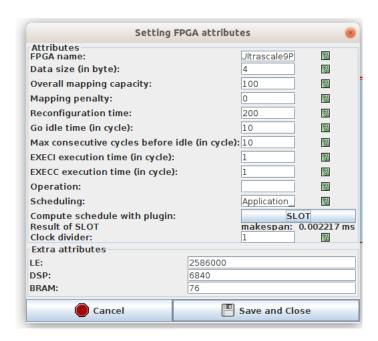

| 6.7  | TTool - Parameters for FPGA block                                                             | 126 |

| 6.8  | TTool - Activity Diagram for task $t_6$                                                       | 126 |

| 6.9  | TTool - Application of <i>Slot</i> to the mapping view                                        | 127 |

|      |                                                                                               |     |

| 7.1  | A schema which resumes the most important contents of this thesis                             | 131 |

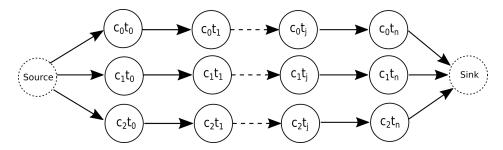

| 7.2  | DAG composed of three parallel <i>chains</i> (namely $c_0$ , $c_1$ and $c_2$ ) of $n$ tasks . | 132 |

| 7.3  | Occupancy of the FPGA with regards to the number of used Logic Ele-                           |     |

|      | ments (LEs). Tasks $T4$ cannot be part of the same slot of $T1$ , $T2$ and                    |     |

|      | <i>T</i> 3                                                                                    | 133 |

| 7.4  | Occupancy of the FPGA with regards to the required I/O bandwidth. Tasks                       |     |

|      | T3 cannot run in parallel with tasks $T1$ and $T2$ .                                          | 134 |

| 7.5  | Occupancy of the FPGA with regards to the required I/O bandwidth. Tasks                       |     |

|      | T3 cannot run in parallel with tasks $T1$ and $T2$ , but they can be part of the              |     |

|      | same slot by introducing a delay                                                              | 134 |

| 7.6  | A possible platform that includes scheduling-dependent resources. In this                     |     |

|      | respect, we can notice the presence of a DRAM, external to the reconfig-                      |     |

|      | urable chip, and a shared bus to this DRAM                                                    | 134 |

| 7.7  | 5-tasks DAG                                                                                   | 136 |

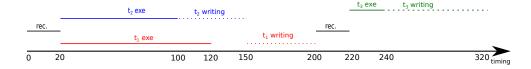

| 7.8  | Gantt diagram for <b>Scheduling 1</b>                                                         | 136 |

| 7.9  | Gantt diagram for <b>Scheduling 2</b>                                                         | 136 |

| 7.10 | The architecture of a modern FPGA-based server - scheduling of both                           |     |

|      | hardware and software tasks                                                                   | 137 |

| 7.11 | 13-tasks DAG. Each task has been labelled with the information about the                      |     |

|      | execution node that will execute it (either the CPU or the FPGA)                              | 139 |

| 7.12 | Microsoft Catapul cloud data center architecture, from [33]                                   | 140 |

## **List of Tables**

| 1.1         | Parameters of tasks for the example of Figure 1.1 - Occupacy represents     |     |

|-------------|-----------------------------------------------------------------------------|-----|

|             | the percentage of the hardware resources used by tasks in a given FPGA      |     |

|             | and the time represents the number of time units that the tasks take to     |     |

|             | execute in the given FPGA                                                   | 17  |

| 1.2         | Example of resources types and resources distribution in the realistic      |     |

|             | DAG of Figure 1.4                                                           | 19  |

| 3.1         |                                                                             | 64  |

| 4.1         | Parameters of tasks for the example of Figure 4.2 - Occupacy represents     |     |

|             | the percentage of the hardware resources used by tasks in a given FPGA      | 73  |

| 4.2         | The resource occupancy and $HET$ of the tasks in Figure 4.10                | 80  |

| 4.3         | Xilinx Virtex Ultrascale 9P FPGA - 3D Modelling                             | 80  |

| 4.4         | Computational complexity of the main steps of Slot. We remind the reader    |     |

|             | that $ N $ represents the number of nodes of the application DAG (i.e., the |     |

|             | number of tasks) and $ E $ represents the number of edges (i.e., the data-  |     |

|             | dependencies between tasks)                                                 | 91  |

| 5.1         | MILP CPU user times in micro-seconds                                        | 105 |

| 5.2         | Slot CPU user times in micro-seconds                                        | 109 |

| 5.3         | HEFT-NF CPU user times in micro-seconds                                     | 111 |

| 7.1         | Resources requests of tasks of Figure 7.7                                   | 135 |

| <b>A</b> .1 | Structural variables                                                        | 146 |

|             |                                                                             |     |

| A.2         | Auxiliary variables                                                         | 146 |

## Chapter 1

### Introduction

#### 1.1 Introduction

This doctoral research has been realized in collaboration with Nokia Bell Labs France laboratories and has been financed by it. Bell Labs are known for their recent research in the telecommunication domain. The research domain of this thesis is a study of scheduling algorithms for FPGAs. This is motivated by the recent use of accelerators such as FPGAs in cloud data center infrastructures to better supply the computation needs of intensive workloads. The target of this contribution is the makespan minimization for applications with internal data-dependencies, which are executed in cloud by renting the use of FPGAs as it can be done for other hardware resources (e.g., CPUs, storage). We address applications whose tasks cannot fit at once the FPGA area: thus, the FPGA must be reconfigured at least one time before completing the execution of the entire application. The choice of which tasks are assigned to which slot has a strong impact on the overall makespan. Efficient scheduling algorithms which minimize the makespan are interesting both for the users (cost is related to usage time) and for providers (to better utilize the FPGA pool).

As discussed in Chapter 3, the vast majority of existing works is either based on slow and precise algorithms or on fast heuristics whose quality is not close to the optimum. In this manuscript, we will propose a new scheduling solution whose quality is better than the current heuristics whila having run-time which is similar to the one of these heuristics (around tens of milliseconds for common applications). Several related works capture applications and architectures using models which in our opinion are too abstract to find good (in terms of makespan) or valid scheduling decisions. (e.g., we will see in Chapter 3 that the FPGA is often represented with a single number that indicates the amount of reconfigurable logic). For this reason, we have decided to rely on more concrete application and architecture models in our contribution.

#### 1.2 Motivation

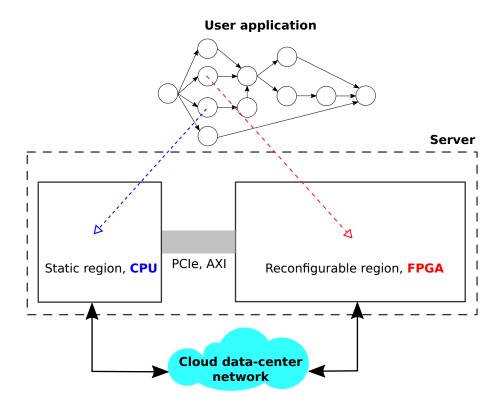

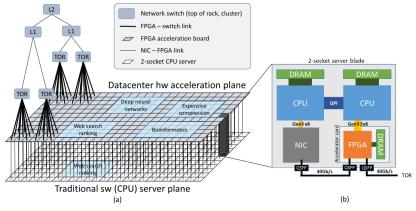

Because of the increasing necessity to execute computationally-intensive tasks (e.g., machine learning, signal processing, cryptography, etc.), for which software execution does not offer sufficient performance, cloud architectures equipped with only CPUs are not sufficient anymore. A solution is to integrate hardware accelerators, which include FPGAs and GPUs. Actually, there are important differences between them and thus they are not completely interchangeable. As a consequence, an FPGA can be most suitable to execute a given application, and reciprocally. For certain types of processing, FPGAs have been proved to be able to ensure a better energy efficiency than GPUs, as shown in [89]. In this paper, authors compare the execution of a Convolutional Neural Network (CNN) both in an FPGA and in a GPU in the Microsoft Catapult cloud system. Indeed, their experiments have shown an energy efficiency of one order of magnitude in favor of FPGA execution.

Applications for which FPGAs are the most convenient include highly parallel applications and/or with elementary operations that do not fit well in CPUs or GPUs programming models, for instance bit swapping, custom data types with non-standard bit widths, etc. Channel coding and decoding algorithms used in telecommunication are good examples of such applications [56] [99]. In certain circumstances machine learning and deep learning algorithms can also be good candidates, especially if they are irregular and if the used data types are optimized to non-standard representations.

Another example is shown in paper [50], where the better temporal and energy efficiency of FPGAs over GPUs is demonstrated for sliding-windows applications, namely Sum of Absolute Differences, 2-D convolution and Correntropy. Sliding-window applications are a special type of digital signal processing that consist in sliding a smaller signal, named window, across different positions in a larger signal (e.g., an image). At each window position, there is usually a computationally intensive function to execute.

GPUs are preferred for computations which can exploit their parallelism, when operations concern SIMD operations or floating point operations, even some recent FPGAs also embed large numbers of floating point units. Graphics rendering is a typical example of application where GPUs are a natural fit because of its massively parallel vector floating point processing. Other signal processing, machine learning or deep learning applications with similar characteristics are also frequently accelerated using GPUs.

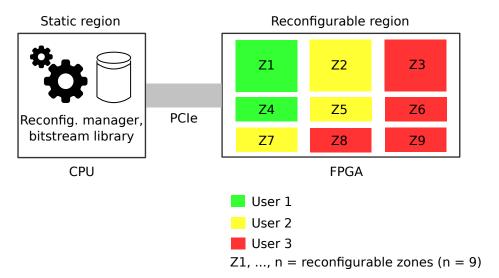

Accelerators play a crucial role in Cloud computing. In this thesis, we focus on FPGAs. As we will in Section 2.3, cloud FPGAs are managed like any other computing or storage resources and rented to final users by cloud providers, most of the time through virtualization. According with the paradigm Software-as-a-Service (SaaS), services provided by an FPGA (or by a pool of FPGAs) are accessed through APIs.

FPGAs can then be shared and their usage is multiplexed among users in various ways: timing, spacing, etc.

From a timing point of view, hardware resources must be efficiently utilized by the provider to maximize its ROI (Return On Investment). The scheduling solution proposed in this manuscript targets the minimization of the execution time of an application (makespan), which is an advantage for the price users pay. Indeed, the more the execution makespan is optimized, the less time is rented the hardware resource.

In modern cloud data centers FPGAs are architecturally organized in a pool [91]. Applications that are the target of this thesis contain a large number of dependent and potentially parallel tasks. Another example is the aggregation of different applications with the objective of minimizing the overall makespan of the whole resulting application. For instance, this is the case of Spark Streaming [111], where makespan of this batch is the termination time of the last task [112].

Existing solutions for the static scheduling of applications can be divided into macro-families. First, we have solutions based on exact mathematical formulations (e.g., MILP programming). These ensure exact solutions at the price of potentially high execution times (up to hours, days or years according to the size of the problem). This is due to the very large solution space which characterizes the scheduling problem we are addressing. Parameters that contribute to the size of the problem include, but are not limited to: dependencies among tasks, execution times, number of requested resources, nature of requested resources, reconfiguration time, FPGA features.

Another well-known family is represented by heuristics. Among heuristics, we will particularly deepen list-based heuristics. In list-based heuristics, which individual tasks are sorted in a priority list and assigned, in sequence, to the earliest available unit that fits their resource request. Priorities can be assigned statically or dynamically according to different characteristics, e.g., execution time or resource occupancy. List-based heuristics have two advantages over the proposal of this thesis, namely that (i) they work even in the case where jobs sequentially arrive to be executed with no prior knowledge of subsequent jobs and (ii) they are faster in terms of run-time. Unfortunately, as shown in Chapter 5, these heuristics compute a scheduling solution which is, in average, worse than the makespan computed by our approach.

Works based on Meta-Heuristics (MHs) such as Genetic Algorithms (GAs), Simulated Annealing (SA), Tabu Search (TS) and so on are also very common. In general, MHs start from an initial solution and iteratively explore a subset of the solution space. Their usage has a sense especially when the solution space is too large to be entirely explored, such as the problem of static scheduling of tasks onto FPGAs. MHs can be applied to a wide variety of problems. On the contrary, our solution as shown in Section 4.2, explicitly handle FPGAs and tasks related assumptions. More-

over, they provide good quality solutions but the computation time that is higher than the one of our contribution [93].

As a summary, exact and MH solutions offer a good solution but which take too much time to compute and list-based heuristics offer not that good solutions in a fast way. As shown in our manuscript, *Slot* performs in a fast way and find a solution which is better than list-based heuristics.

#### 1.3 Glossary

Following a list of most common concepts we use throughout the thesis. Some of these concepts may have more interpretations, so we state here which meaning they have within this manuscript.

- **Scheduling:** we define the scheduling of an application onto a reconfigurable device the process to select an execution order among dependent tasks.

- On-line/Off-line scheduling of applications: on-line scheduling consists in making scheduling decisions during the execution of the applications while off-line scheduling is precomputed before the applications executes. The choice between on-line and off-line scheduling is frequently guided by criteria like the frequency at which scheduling decisions must be made, the run-time of the tasks to schedule, the run-time of the scheduling algorithm itself, the determinism of the applications...

- **Makespan:** the total duration between the start and the end of execution of an application.

#### • Reconfiguration of an FPGA

- Full reconfiguration: it consists in saving the logical setting of an FPGA by using a bitstream.

- Partial reconfiguration: it allows a limited, predefined portion of an FPGA to be reconfigured while the configuration of the remainder of the device is unmodified

- FPGA scheduling problem: the problem of how to decide in which order the tasks of an application or of a set of applications shall be executed on an FPGA. These decisions must usually meet requirements (e.g. the inter-task dependencies or the instantaneous amount of available resources) and try to optimize one or more specific objectives (e.g. energy consumption or total makespan). The way scheduling decisions are taken also depends on the context (partial or total FPGA reconfiguration, on-line or off-line scheduling, etc.).

In this contribution we consider total FPGA reconfiguration and our objective is the minimization of the total makespan.

- Slot: it has a dual meaning

- If *Slot* is written in italic and with the uppercase S it refers to the name of the algorithm presented in this thesis.

- Else, if **slot** is written lowercase and not italicized it consists in a total reconfiguration of the FPGA, followed by the execution of the tasks in the configuration, and the release of the device. A slot usually includes one or more tasks whose (a part of) processing time (HET, explained later in this list) may overlap. In the rest of this thesis, we will use the following notation for a slot:  $[R, \{t_0 \ldots t_n\}]$ , where:

- \* "[" denotes the beginning of a slot;

- \* "R" represents a total FPGA reconfiguration;

- \* " $\{t_0 \ldots t_n\}$ " are the set of tasks which compose the slot. Tasks  $t_0 \ldots t_n$  are not executed sequentially, but they follow the dependencies of the application;

- \* "]" denotes the end of a slot.

#### Hardware Execution Time - HET:

- Task Hardware Execution Time task HET: the processing time of a task on the FPGA.

- Slot Hardware Execution Time slot HET: the total time taken by a slot.

- Valid solution: a scheduling solution is composed of a sequence of slots. In our FPGA scheduling problem, such solution is valid if it respects two conditions. First, tasks within a slot must not exceed the capabilities of the FPGA in terms of resources. Second, the sequence of slots must respect the data dependencies between tasks. This means that a task of slot N cannot be a successor of a task of slot N + k (k > 0).

- Scheduling-independent resource: a scheduling-independent resource is a resource which is exclusively assigned to a task for the entire lifetime of the slot that contains the task.

- Scheduling-dependent resources: a scheduling-dependent resource is a resource which is assigned to a task for the entire task's lifetime. The latter is always less or equal the entire lifetime of the slot that contains the task.

#### 1.4 Research Problem

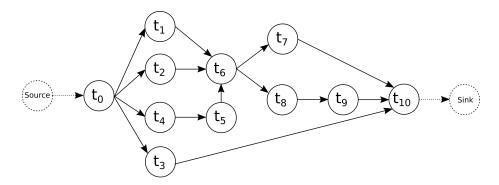

In this thesis we focus on the **scheduling of applications** onto FPGAs. We take the assumptions that applications are composed of **dependent tasks** (expressible as **DAGs**). We thus assume that the sum of the physical resources necessary for each task to execute in the FPGA exceeds the physical resources of the FPGA. As a consequence, we target applications which need at least two slots to execute. Each slot is thus composed of a total reconfiguration of the FPGA followed by a subset of tasks of the application. Slots are executed sequentially and the sequence of slots must respect data dependencies of the DAG. In other words, if a task B depends on a task A, task A cannot be part of a slot that follows a slot that includes task B. If tasks A and B are part of the same slot, then A must be totally executed before B can start being executed. Obviously, the construction of slots strongly influence the application makespan. Consequently, **our scheduling problem consists in identifying in an fast way slots that lead to execution an application with a makespan which is close or equal to the optimum makespan.**

Scheduling onto FPGAs is different than scheduling on CPUs. Indeed, a hardware implementation on FPGA of a task requires resources such as reconfigurable logic elements, embedded memory blocks, etc. These resources may look like the one of processors, e.g., memory, registers, cores, etc. Also, hardware resources of both CPUs and FPGAs may not be sufficient to execute all together all the tasks of an application. However, switching from one task to another in CPUs is usually much faster than reconfiguring an FPGA  $\boxed{107}$ . Thus, reconfiguring an FPGA may introduce a timing overhead comparable to the HET of a task. As a consequence, the choice of which tasks execute together in a slot has a larger impact for FPGAs than similar choices for processors. Additionally, because of this overhead, reconfigurations on FPGAs are expected to be less frequent than context-switching on processors.

The scheduling problem we target in this thesis is similar to Resource-Constrained Scheduling Problem (RCSP) category. Informally, a RCSP considers limited resources and activities of known durations. A RCSP also expects resource requests to be linked by precedence relations. A RCSP consists in **finding a schedule of minimal duration** by assigning a start time to each activity such that the precedence relations and the resource availabilities are respected [101]. For a taxonomy of RCSPs, we invite the reader to consult the work in [60]. The authors in [30] demonstrated that the classical RCSP is a strong NP-hard problem.

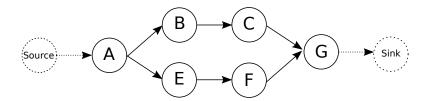

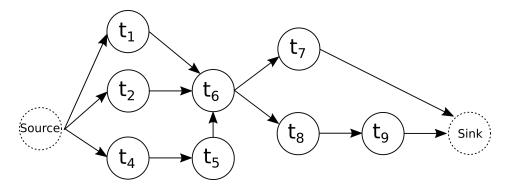

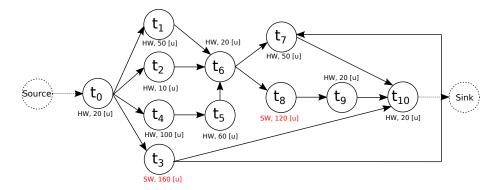

However, our research problem differs from the classical RCSP because FPGA reconfigurations introduce a new variable in the solution space whose overhead significantly contributes to the overall makespan. As said before, choices of tasks that compose a slot has a strong impact on the overall makespan. Let us for instance consider the example in Figure [1.1]. In this figure *Source* and *Sink* are artificial tasks,

Figure 1.1: 8-tasks DAG example

| Task | Occupancy | Time    |

|------|-----------|---------|

| Α    | 33%       | 10 [u]  |

| В    | 33%       | 300 [u] |

| С    | 33%       | 20 [u]  |

| Е    | 33%       | 150 [u] |

| F    | 33%       | 150 [u] |

| G    | 33%       | 10 [u]  |

Table 1.1: Parameters of tasks for the example of Figure 1.1 - Occupacy represents the percentage of the hardware resources used by tasks in a given FPGA and the time represents the number of time units that the tasks take to execute in the given FPGA

whereas other tasks are parametrised with hardware occupancy and HET; as listed in Table 1.1. For simplicity reasons, each task of this example occupies 33% of the FPGA. This means that up to three tasks can be put in the same slot.

We consider an FPGA whose reconfiguration R requires  $T_R=40$  units of time. We now compare two possible schedulings:

- Scheduling 1:  $[R, \{A \ B \ E\}], [R, \{C \ F \ G\}] \rightarrow 550 [u]$

- Scheduling 2:  $[R, \{A\}], [R, \{B E F\}], [R, \{C G\}] \rightarrow 460 [u]$

Scheduling 1 minimizes the number of reconfigurations. Since up to three tasks can share the FPGA area, A, B and E are put in the same slot. The next slot includes tasks C, F and G. The overall makespan is therefore 550 units of time, included 80 units spent in reconfigurations. Scheduling 2 is less intuitive. Indeed, the first slot contains only task A. The second slot includes task B in parallel with the sequence of tasks E and F. The last slot contains the sequence of C and C. The total makespan of Scheduling 2 is 460 units of time. Finally, Scheduling 2 has a shorter makespan than Scheduling 1. Considering this example and several others, we could notice the following intuitions:

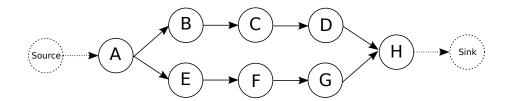

Figure 1.2: 10-tasks DAG example

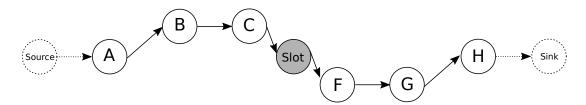

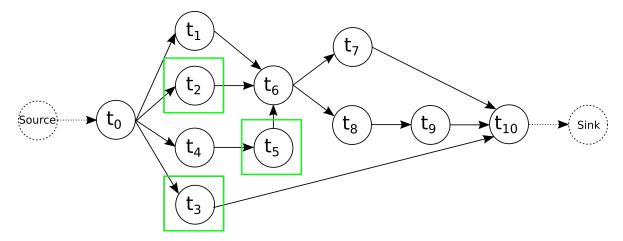

Figure 1.3: DAG of Figure 1.2 after merging task D and task E in slot Slot

- 1. The best solution is not always the one with the lowest number of reconfigurations. Indeed, Scheduling 1 reconfigures the FPGA twice, whereas in Scheduling 2 the FPGA is reconfigured three times.

- 2. The key metric is the amount of time spent executing tasks in parallel, which should be maximized. In order to do so, the most time-consuming tasks should probably be considered first because the potential gains are the largest. Indeed, in the second schedule the sequence of tasks E and F and the execution of task B (the three most time-consuming tasks) perfectly fit together.

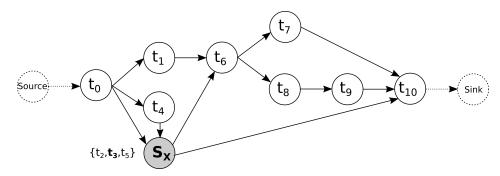

Another interesting example is given in Figure 1.2 For simplicity reasons, in this example each task is supposed to occupy exactly 50% of the FPGA. Let us imagine to schedule tasks D and E in the same slot. This choice totally remove the theoretical parallelisms between the two branches (except for tasks D and E). Indeed, following this choice any parallelism between B and C with F and G would become not valid because of the data dependencies, as shown in Figure 1.3.

It could be convenient though. The best choice depends on how much the gain derived from the scheduling of tasks D and E is with respect to the other tasks of the graph. For example, if the execution times of tasks D and E are similar and much higher than the other tasks, the minimum makespan is obtained by exploiting this parallelism, which implies forbidding any other parallelism. Thus, the choice of which tasks shall be put in parallel shall not consider only the tasks that could fill the slot, but it should also consider all the tasks of the whole graph.

Obviously, for larger examples, the exhaustive search may induce combinatory explosion. Indeed many parameters, which can be combined, have an impact on

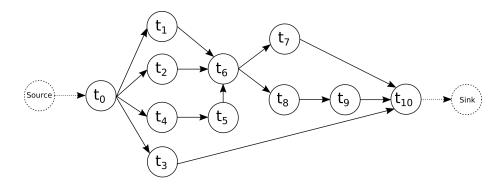

Figure 1.4: A realistic application DAG

| Task     | LEs | DSPs | <b>EMBs</b> | DRAM | Network bandwidth | Time[u] |

|----------|-----|------|-------------|------|-------------------|---------|

| $t_0$    | 33% | 11%  | 53%         | 65%  | 50%               | 187     |

| $t_1$    | 48% | 70%  | 3%          | 10%  | 91%               | 1662    |

| $t_i$    | 50% | 15%  | 90%         | 6%   | 17%               | 974     |

|          |     |      |             |      | •••               |         |

| $t_{10}$ | 22% | 78%  | 10%         | 49%  | 9%                | 563     |

Table 1.2: Example of resources types and resources distribution in the realistic DAG of Figure 1.4

the final solution. These include data dependencies, parallelism, HETs, requested resources and the availability of resources, reconfiguration overhead, number of reconfigurations and so on.

The objective of our thesis is to define a heuristic that targets specifically the static scheduling of tasks onto an FPGA. We expect our solution to provide a scheduling which is as good as the one that can be computed by meta-heuristics with a runtime which is much lower. Additionally, we also expect to handle situations where the standard deviation between the different parameters of tasks are much higher than the one presented in Figure 1.1 in which for instance all occupancies were similar. An example is illustrated in Figure 1.4 and Table 1.2. Finally, having generic models to represent resources and constraints make the approach more adaptable to various applications and FPGAs.

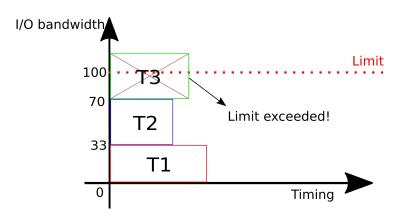

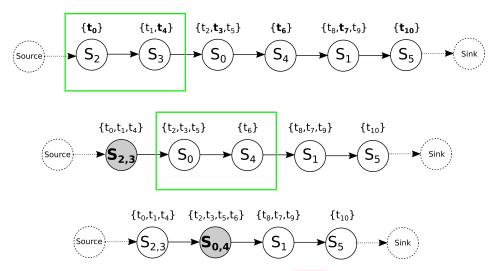

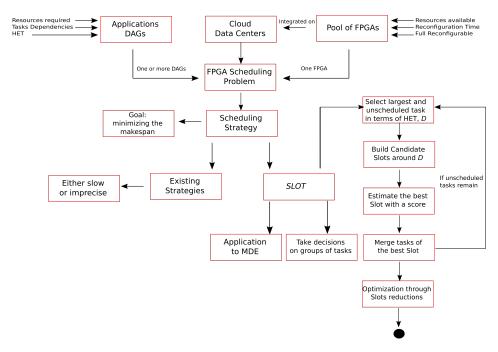

#### 1.5 Overview of the solution

Our solution is based on an iterative process summarised in the schema in Figure 1.5. Our solution tries to minimize the makespan of an application by grouping tasks in slots. As shown in previous sections, the parallelisms between tasks and dom-

inating tasks (i.e., tasks that have the higher HET) are key-points of the problems that are tackled by our solution. Indeed, our solution relies on the selection of the dominating tasks and it also relies on putting in parallel to these dominating tasks a subset of the tasks than can be executed in parallel.

In order to select which tasks to be put in parallel to the dominating task, we consider all the graph, and not only the quality of the parallelism between the dominating tasks and the tasks in parallel to it. For instance, our decision cosiders the requested resources and HET of tasks, data-dependencies among them, FPGA features and reconfiguration time.

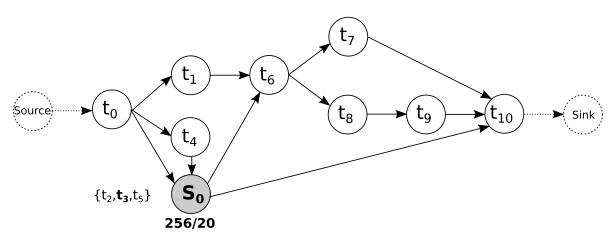

Among all the possible tasks that can be put in parallel with the dominating task, we define in this work a score-based approach that helps defining which tasks to select. Once the dominant task and the tasks to be put in parallel have been selected thanks to the scoring facility (i.e., a slot is created), the graph is reworked so as to merge in a single node all the tasks that have been selected in this iteration.

At each iteration a new slot is created and its tasks are merged together in one node of the graph. The input graph finally becomes a sequence of slots. Such sequence expresses the selected scheduling. As a reminder, a slot contain a total FPGA reconfiguration followed by the execution of tasks belonging to the slot. As shown in Section 4.6.4, a final optimization process tries to further compact the computed slots in order to further reduce the makespan.

Our approach is very likely to identify a good solution, which is the solution that minimizes the makespan, because instead of considering only a given sub-part of the graph, just like when starting from the source task, we rather favour the dominating task (regardless of its location in the graph) and the most powerful parallelism of the graph to better exploiting the parallelism capacity of FPGAs. This heuristic is presented in Chapter 4, while the efficiency of this heuristic is presented in Chapter 5.

#### 1.6 Outline of the thesis

The rest of this thesis is organized as follows. Chapter 2 illustrates the main context of this thesis by providing an overview of reconfigurable computing and how cloud data centers may integrate FPGAs. Chapter 3 discusses the related work in this domain. Chapter 4 describes the main steps of our approach, *Slot*. Chapter 5 experimentally evaluates *Slot* and compares it with other, exact or approximate, approaches. Chapter 6 shows how *Slot* might also be interesting for the design of complex embedded system. In this respect, we have integrated *Slot* in an open-source Model-Driven Engineering tool. Chapter 7 concludes the thesis and it illustrates the

Figure 1.5: The main steps of Slot

future work. Finally, Appendix A provides low level details of the MILP formulation that we used to calculate the optimal solution for each test-case of our benchmark and Appendix B contains a list of acronyms used in this thesis.

#### 1.7 Conclusion

As presented in this introduction, cloud data centers may now integrate hardware accelerators such as FPGAs. In ordert to efficiently use these FPGAs, we have also described the problem of scheduling dependent tasks onto these FPGAs. We have assumed that they are totally reconfigured. Unfortunately, as it will be more detailed in Chapter 3, there are not yet good solutions to tackle this problem. Solutions are either precise but far too long to be computed or they are very fast to compute but

they offer solutions in average too far from the optimum. We think that there is an intermediate approach that could compute solutions in a fast way while providing solutions much closer to the optimum.

Then, we have presented the main challenges that such scheduling problems introduce. For this, we have presented several examples. In particular, we have shown that only an algorithm which works on the global graph, that is by taking decision considering all the tasks of the graph together, their resources requirements, HETs, dependencies among them, the features of the targeted FPGA and the reconfiguration time, is more likely to compute a solution close to the optimum, because it can better exploit the parallelism of FPGAs.

We have also in this Chapter sketched our solution, named *Slot*, which is based on an iterative process that first considers all the graph and the dominating task of this graph. *Slot* also relies on a scoring approach to select the best slots among candidates. Also, our approach contains a final optimization stage.

The manuscript first elaborates on which elements of FPGAs must be taken into account for obtaining a good result. We then present in detail the heuristic and we compare it with other, exact or approximate, approaches.

## **Chapter 2**

### Context