# SoC physical security evaluation Thomas Trouchkine

## ▶ To cite this version:

Thomas Trouchkine. SoC physical security evaluation. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2021. English. NNT: 2021GRALT018 . tel-03282313

# HAL Id: tel-03282313 https://theses.hal.science/tel-03282313

Submitted on 9 Jul2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITE GRENOBLE ALPES

## Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES

Arrêté ministériel : 25 mai 2016

Présentée par

# Thomas TROUCHKINE

Thèse dirigée par **Jessy CLÉDIÈRE** Université Grenoble Alpes et codirigée par **Guillaume BOUFFARD**, Agence Nationale de la Sécurité des Systèmes d'Information

préparée au sein du **Laboratoire CEA/LETI** dans **l'École Doctorale Electronique, Electrotechnique, Automatique, Taitement du Signal (EEATS)**

# Évaluation de la sécurité physique des SoC

# SoC physical security evaluation

Thèse soutenue publiquement le **24 mars 2021**, devant le jury composé de :

Monsieur Jessy Clédière CEA-E5, Université Grenoble Alpes, Directeur de thèse Madame Karine Heydemann MAITRE DE CONFERENCE, Laboratoire d'Informatique de Paris 6, Rapportrice **Monsieur Philippe Maurine** MAITRE DE CONFERENCE, Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier (LIRMM), Rapporteur Madame Clémentine Maurice CHARGE DE RECHERCHE, CNRS, CRIStAL, Université de Lille, Examinatrice Madame Marie-Laure Potet PROFESSEUR, ENSIMAG, Examinatrice et Présidente du Jury Monsieur Jean-Max Dutertre PROFESSEUR, École des Mines de Saint Étienne, Examinateur **Monsieur Patrick Schaumont** PROFESSEUR, Worcester Polytechnic Institute, Examinateur Monsieur Lilian Bossuet

PROFESSEUR, Université Jean-Monnet, Examinateur Monsieur Patrick Haddad

DOCTEUR INGENIEUR, ST Microelectronics, Invité

Monsieur Guillaume Bouffard DOCTEUR, Agence Nationale de la Sécurité des Systèmes

d'Information/Ecole Normale Supérieure, Invité, co-encadrant

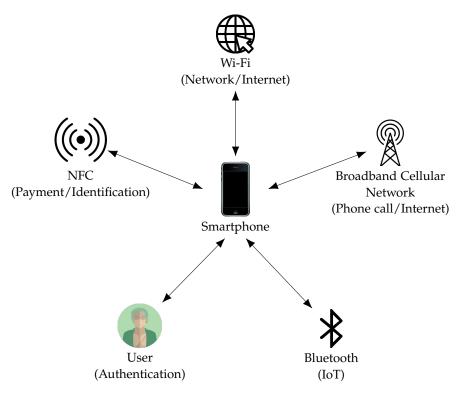

Since the democratization of mobile devices, sensitive operations like payment, identification or healthcare, usually done using security evaluated smartcards, are handled by these devices. However, mobile devices neither are designed for security nor security evaluated. Therefore, their resistance against powerful attacks, like physical attacks is questionable.

In this thesis, we aim at evaluating the security of mobile devices against physical attacks, in particular perturbation attacks. These attacks aims at modifying the execution environment of the device to induce bugs during its computation. These bugs are called faults. These faults can compromise the security of a device by allowing the cryptanalysis of its secret or forcing an unauthorized authentication for instance.

Mobile devices are powered by modern processors, which are the heart of this work, and are never evaluated against fault attacks. However, our knowledge about fault attacks on smartcards is not relevant as the processors powering smartcards are way less complex, in terms of number of modules, technology node and optimization mechanisms, than modern processors.

Regarding this situation, we aim at providing rationals on the security of modern processors against fault attacks by defining a fault characterization method, using it on representative modern processors and analyzing classical security mechanisms against the characterized faults.

We characterized three devices, namely the BCM2837, BCM2711bo and the Intel Core i3-6100T against fault attacks using two different injection mediums: electromagnetic perturbations and a laser. We determined that these devices, despite having different architecture and using different mediums are faulted in similar ways. Most of the time, a perturbation on these devices modify their executed instructions.

As this is a powerful fault, we also analyzed classical security mechanisms embedded in such devices. We successfully realized a differential fault analysis on the AES implementation of the OpenSSL library, which is used in every Linux based operating system. We also analyzed the Linux user authentication process involved in the sudo program. This work highlights the lack of tools to efficiently analyze Linux programs, which are rather complex with dynamic linking mechanisms, against fault attacks. De nos jours, nos appareils mobiles sont utilisés pour réaliser des opérations sensibles telles que du paiement, de l'identification ou la gestion de services santé. Historiquement, ces opérations sont réalisées par des appareils conçus et évalués pour résister à diverses attaques: les éléments sécurisés. En revanche, les appareils mobiles sont conçus pour fournir la meilleure performance possible et ne subissent aucune évaluation de sécurité. Cet état de fait interroge sur la résistance de ces appareils face aux attaques classiques contre lesquelles se protègent les éléments sécurisés.

Parmi ces attaques, nous nous proposons, dans cette thèse, d'étudier les attaques par perturbations. Ces attaques consistent à modifier les conditions d'exécution du circuit ciblé afin d'induire des erreurs dans son fonctionnement. Ces erreurs volontaires, communément appelées fautes, permettent de créer des failles dans la cible pouvant aller jusqu'à la cryptanalyse d'un algorithme de chiffrement ou l'authentification d'un utilisateur non autorisé.

Bien que ces méthodes d'attaques soient connues et étudiées sur les éléments sécurisés, les appareils modernes reposent sur des processeurs modernes présentant des différences par rapport aux processeur des éléments sécurisés. Cela peut être le nombre de module qu'ils embarquent, leur finesse de gravure ou des optimisations.

L'impact de ces différences sur la sécurité des processeur n'a pas été étudié en prenant en compte la possibilité d'induire des fautes. C'est ce que nous réalisons dans cette thèse. Nous définissons une méthode permettant de caractériser les effets de perturbations sur un processeur moderne que nous appliquons sur trois processeurs représentatifs des appareils existants: le BCM2837, le BCM2711bo et l'Intel Core i3-6100T. Nous avons également utilisés deux moyens de perturbation classiques: l'injection d'onde électromagnétique et l'utilisation d'un laser. L'étude de ces cibles, en variant les moyens d'injections de faute, nous a permis de déterminer qu'elles réagissent toutes de manière similaire aux différentes perturbations malgré leur différentes architectures. L'effet le plus marquant étant la modification des instructions exécutées.

Ce type de faute est très fort car il permet de modifier une partie du programme exécuté pendant son exécution. Vérifier le programme avant de l'exécuter ne protège en rien face à ce type de fautes, par exemple. C'est pourquoi nous avons également étudié la résistance des mécanismes de sécurité présents dans ces cibles face à ce type de faute. Nous avons notamment réussi à cryptanalyser l'implémentation de l'algorithme de chiffrement AES de la bibliothèque OpenSSL, très utilisé dans les systèmes utilisant Linux. Nous avons également étudié la résistance du mécanisme d'authentification des utilisateurs d'un système Linux en regardant le programme sudo. Cette étude nous a, en particulier, révélé que la communauté manque d'outils efficace pour analyser ce type de programmes face aux fautes. En effet, les programmes s'exécutent dans un environnement Linux bénéficient de nombreux mécanismes liés au noyau Linux qui rendent l'exécution d'un programme difficile à étudier.

*So what if you fail once or twice ? I don't even know how many thousand times I failed to control my rage.*

- Dragon Sin of Wrath, Meliodas (The Seven Deadly Sins)

#### REMERCIEMENTS

S'il est bien une chose que tous les efforts du monde ne peuvent égaler, c'est l'inspiration, l'aide et les conseils des personnes que nous croisons au cours de notre vie.

Et parce que cette thèse présente une partie des efforts que j'ai fourni durant ces trois dernières années, je tiens à dédier ce chapitre à ces personnes qui m'ont donné de quoi arriver jusqu'ici. Il est difficile de mettre un mot, ou une définition sur ce que j'ai reçu, mais je sais que cela m'a énormément aidé.

Avant toute chose, je tiens à remercier mon jury de thèse, Mme. Karine Heydemann, M. Philippe Maurine, Mme. Clémentine Maurice, Mme. Marie-Laure Potet, M. Jean-Max Dutertre, Mr. Patrick Schaumont, M. Lilian Bossuet et M. Patrick Haddad, qui, non seulement d'accepter de juger de mon travail, m'ont régulièrement aidé à travers des critiques et des échanges sur mes travaux qui ont souvent porté leurs fruits.

Je remercie également mon directeur de thèse, M. Jessy Clédière, pour son aide et ses conseils tout au long de la thèse malgré la distance qui nous sépare.

Et je remercie très chaleureusement mon encadrant, et collègue, et désormais ami, M. Guillaume Bouffard. Le remercier pour son encadrement ne lui rend pas justice tant son investissement dépasse celui d'un encadrant, nous avons pu échanger, partager et nous entraider tellement souvent que je ne peux tout énumérer ici. Il me tarde de pouvoir retourner partager des bières en terrasse avec toi !

D'autres remerciements, très forts, se doivent d'aller à mes parents Emmanuelle et François. Leur soutien ne se matérialise pas par des conseils sur la sécurité des processeurs ou sur une critique de la méthode de caractérisations des fautes mais par des choses bien plus indescriptibles pour moi. Ils ont été, sont et seront un soutien qui apporte bien plus que ce que je ne peux décrire. Que ce soit un foyer familial quand le moral est en baisse ou un stock de papier de toilette en pleine pandémie.

Une dédicace toute spéciale va à ma petite sœur, Julie. Encore une fois, décrire la nature exact de l'aide qu'elle m'apporte est très difficile, elle a ce magnifique défaut d'être incapable de voir mes défauts, mes erreurs et mes échecs et sera toujours une bonne raison de faire en sorte que je n'ai rien de tout ça.

Ma prochaine pensée va à l'ensemble des professeurs que j'ai eu durant ma scolarité. J'ai eu l'occasion de m'essayer à l'exercice de l'enseignement et j'ai bien compris que certains m'ont apporté plus que cela. Je pense en particulier à Livia, Khalid et Francesco, mes professeurs de collège lorsque j'étais en Roumanie, sans savoir pourquoi, c'est à partir de cette période que j'ai commencé à vraiment m'intéresser aux sciences. Je tiens également à remercier mes professeurs de lycée pour m'avoir poussé sur la voie vers les écoles d'ingénieurs. Je remercie également, justement, ces professeurs que j'ai rencontré, en école d'ingénieur, à Gardanne, et qui m'ont donné ou dévoilé cette fibre pour la micro-électronique et m'ont un peu poussé vers la thèse, je pense en particulier à M. Jean-Baptiste Rigaud.

J'en profite pour remercier mes camarades de promotion, avec qui j'ai passé des moments uniques que ce soit en cours, en soirée ou en association. Je remercie en passant l'équipe du mandat 9 de M-GaTE que j'ai eu la chance de présider pendant un an et avec lesquels j'ai beaucoup appris.

Naturellement, mes prochains remerciements vont envers mes amis, que je ne remercierai jamais assez et qui m'apportent énormément. Je pense aux Maissois, Benoît, Gaëlle et leur fille Maëlyne (aka. Choupette !) dont j'ai la chance d'être le parrain. Vous formez une famille exceptionnelle et je suis heureux d'en être un membre invité ! Je remercie également mes camarades judokas, Rodolphe et Sylvie, dont l'exigence et la douceur s'équilibrent parfaitement, Kathleen qui a hérité des deux, Yann et Sylvain, les frangins qui croquent la vie à pleine dent, Jérôme qui parcourt le monde, Rémi à la volonté infaillible avec qui j'ai eu la chance de passer les kata, André qui nous a formé pour ces kata, la famille Mota, l'équipe cadet: Killian, Sylvain, Morgan et Alexandre, la famille Reytier: Patrick et Brigitte, Fabien, Morgane (aka. Meuh) ainsi que Kévin, Kelly et Maiwen qui m'ont offert un vrai refuge avec des barbecues, des soirées et des séances de wakeboard ou de voile mémorables. Vous m'avez énormément appris, tant sur l'importance des amis et d'une équipe, que sur l'exigence personnelle ainsi que l'investissement physique et psychologique pour progresser, et évidemment la volonté de se battre malgré ce qui nous fait face. Tout ceci m'a servi, pour la réalisation des travaux présenté dans cette thèse, mais pas seulement. Parmi les Maissois qu'il reste, je tiens à remercier mes camarades de soirées, où nous avons tantôt montrer nos talents au Beer-Pong tantôt refait le monde, merci Florian, Jérémy B. et Juliette (le couple parfait !), Jérémy T., Adeline et Marjolaine, ma super voisine avec qui je courrais après le bus pour aller au lycée.

Une pensée particulière va envers Jean, qui m'a appris à jouer de la guitare mais qui au final m'a partagé bien plus que de la technicité sur un instrument. C'est une vrai philosophie de vie, mise à l'épreuve par la maladie, qui m'a été transmise et que je veux honorer.

Parmi les pensées particulières, il y en a pour ces amis de longue date, ces relations qui survivent à la distance et au temps, je pense en particulier à Thomas L., Antoine et Thibaut Tai. Savoir que vous êtes quelque part, plus ou moins dans le coin, et qu'on partagera de nouveaux de bons moments ensemble est toujours bon pour le moral. J'ai hâte d'entendre tout ce que vous avez à me raconter ! Et puisque que nous en sommes aux bons amis, je tiens à remercier des bandes particulières. Les Maissois et les judokas, que j'ai déjà eu l'occasion de remercier. Merci aux 6 doigts de la main (ordre de chevaliers encore meilleurs que les 7 pêchés capitaux), Arnaud le chanteur, Florian S. le sportif, Camille la motarde, Pierre (*aka*. Caillou) le futur astronaute breton ! et Paul (*aka*. Skøll) le viking, pour votre bonne humeur, votre soutien ainsi que les *Skypéro* ! Mention spéciale à Marie et Fanny, qui accompagnent deux d'entre eux dans la vie et qui me grillent (trop) facilement sur *Among Us*. Merci également à la *Dream Team*, David, le chevalier au cœur pur, Guillaume, que j'ai déjà eu l'occasion de mousser et Louiza, la plus grande adoratrice de plantes et de chats au monde, vous êtes des collègues exceptionnels.

Je tiens à remercier également les *Nakamas*, qui m'ont fait découvrir le *crossfit* et dont la bonne humeur n'égale que l'énergie, que ce soit pour enchaîner les *burpess*, à la *box* ou dans mon salon, ou pour dévorer des barbecues et des raclettes. Mention spéciale aux coachs: Jérémy, Mickael et Édouard qui sont des exemples à suivre dans bien des domaines.

Enfin merci à la Légion Jedi, une superbe guilde avec laquelle j'ai occupé de nombreuses heures de confinement et de couvre-feu à rigoler tout en sauvant la galaxie !

Et pour finir, je remercie également l'ensemble de mes collègues de l'ANSSI, et en particulier ceux du laboratoire de sécurité des composants, pour leur accueil, leur soutien, leur bonne humeur, les bières le soir et les discussions polémiques. Merci Eliane (*the boss*), Patrick, Guenaël, Emmanuel, Karim, Ryad, Adrian, Guillaume, Boris, David, Louiza, Julien et Yoan.

| i | INT         | RODUCTION 1                                           |  |  |  |  |

|---|-------------|-------------------------------------------------------|--|--|--|--|

| 1 | ABC         | OUT CYBERSECURITY 3                                   |  |  |  |  |

|   | 1.1         | Cybersecurity problematic 4                           |  |  |  |  |

|   | 1.2         | Secure Devices Evaluation 4                           |  |  |  |  |

|   | 1.3         | ANSSI's role in France 6                              |  |  |  |  |

|   | 1.4         | This thesis 6                                         |  |  |  |  |

| 2 | •           | DY CONTEXT 9                                          |  |  |  |  |

|   |             | Introduction 10                                       |  |  |  |  |

|   |             | Secure Elements 10                                    |  |  |  |  |

|   |             | 2.2.1 Architecture 11                                 |  |  |  |  |

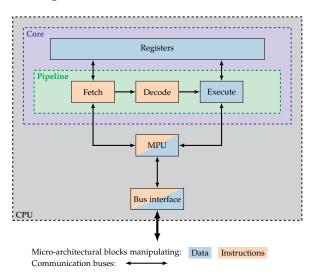

|   |             | 2.2.2 Central Processing Unit (CPU) 12                |  |  |  |  |

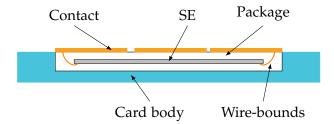

|   |             | 2.2.3 Packaging 13                                    |  |  |  |  |

|   | 2.3         | Systems On Chip 13                                    |  |  |  |  |

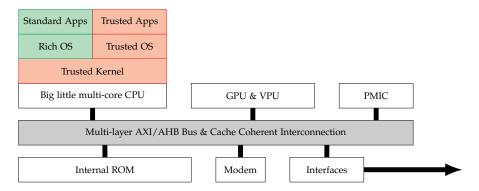

|   | <u> </u>    | 2.3.1 Architecture 15                                 |  |  |  |  |

|   |             | 2.3.2 CPU 17                                          |  |  |  |  |

|   |             | 2.3.3 Packaging 20                                    |  |  |  |  |

|   | 2.4         | Multi-application system security 21                  |  |  |  |  |

|   | -           | Conclusion 23                                         |  |  |  |  |

| 3 | -           | HYSICAL ATTACKS 25                                    |  |  |  |  |

| ) |             | Side-channel attacks 26                               |  |  |  |  |

|   | <i>J</i> .= | 3.1.1 Micro-Architectural Attacks 28                  |  |  |  |  |

|   |             | 3.1.2 Side-Channel countermeasures 28                 |  |  |  |  |

|   | 3.2         | Invasive attacks 28                                   |  |  |  |  |

|   | 5           | 3.2.1 Reverse engineering 29                          |  |  |  |  |

|   |             | 3.2.2 Focused Ion Beam 29                             |  |  |  |  |

| 4 | PER         | TURBATION ATTACKS 31                                  |  |  |  |  |

| ' |             | Genesis 33                                            |  |  |  |  |

|   | •           | Inducing a fault: injection mediums 34                |  |  |  |  |

|   | •           | 4.2.1 Design considerations 34                        |  |  |  |  |

|   |             | 4.2.2 Clock glitches 36                               |  |  |  |  |

|   |             | 4.2.3 Voltage glitches 36                             |  |  |  |  |

|   |             | 4.2.4 Temperature manipulation 37                     |  |  |  |  |

|   |             | 4.2.5 Electromagnetic perturbations 37                |  |  |  |  |

|   |             | 4.2.6 Optical perturbations 39                        |  |  |  |  |

|   |             | 4.2.7 Body biasing 41                                 |  |  |  |  |

|   |             | 4.2.8 X-Rays 41                                       |  |  |  |  |

|   |             | 4.2.9 Software induced perturbations 41               |  |  |  |  |

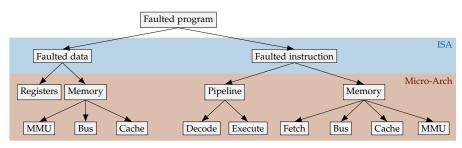

|   | 4.3         | Characterizing a fault 44                             |  |  |  |  |

|   |             | 4.3.1 Fault models 44                                 |  |  |  |  |

|   |             | 4.3.2 Fault analysis 46                               |  |  |  |  |

|   | 4.4         | Exploiting a fault 47                                 |  |  |  |  |

|   |             | 4.4.1 Fault attacks against multi-application systems |  |  |  |  |

|   | 4.5         | Countermeasures 56                                    |  |  |  |  |

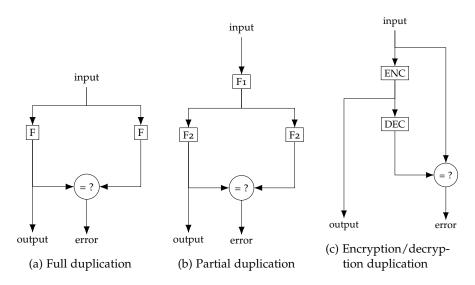

|   |             | 4.5.1 Space redundancy 57                             |  |  |  |  |

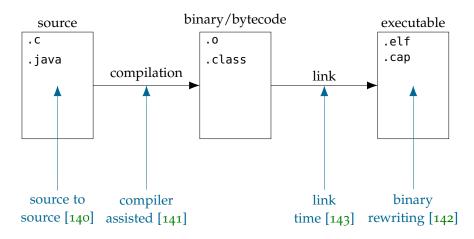

|   |             | 4.5.2 Operation duplication 57                        |  |  |  |  |

|   |             |                                                       |  |  |  |  |

47

- 4.5.3 Infection countermeasure 58

- 4.5.4 Code hardening 58

- 4.5.5 Sensors 60

- 4.6 Conclusion on perturbation attacks 60

- ii contribution 63

- 5 FAULT EFFECT CHARACTERIZATION ON SYSTEMS ON CHIP 65

- 5.1 SoC modeling 66

- 5.2 Attacker model 66

- 5.3 Experimental method 67

- 5.3.1 Top-down approach 67

- 5.3.2 Target setup 68

- 5.4 Determining the faulted element 73

- 5.5 Conclusion 75

- 6 EXPERIMENTAL WORK 77

- 6.1 Practical work setup 78

- 6.1.1 Attack benchs 78

- 6.1.2 Evaluated devices 81

- 6.1.3 Tools 85

- 6.2 BCM2837 characterization 91

- 6.2.1 Hot-spots maps 92

- 6.2.2 Analyzer results 94

- 6.2.3 Micro-architectural analysis using a test program 100

- 6.2.4 Micro-architectural analysis on a baremetal setup with JTAG 104

- 6.2.5 Conclusion on the BCM2837 characterization 107

- 6.3 BCM2711bo characterization 108

- 6.3.1 Hot-spots maps 108

- 6.3.2 Analyzer results 109

- 6.3.3 Conclusion on the BCM2711bo characterization 113

- 6.4 Intel Core i3 characterization 114

- 6.4.1 Hot-spots maps 114

- 6.4.2 Analyzer results 116

- 6.4.3 Conclusion on the Intel Core i3-6100T 119

- 6.5 Characterization conclusion 119

- 7 FAULT MODEL EXPLOITABILITY 121

- 7.1 DFA on the OpenSSL AES implementation 123

- 7.1.1 Source code location 123

- 7.1.2 Static analysis 124

- 7.1.3 Fault attack on the OpenSSL AES 126

- 7.1.4 DFA software 128

- 7.1.5 Conclusion on the OpenSSL AES DFA 132

- 7.2 Baremetal AES PFA [159] 132

- 7.2.1 PFA Result 132

- 7.2.2 Conclusion on the PFA on our baremetal AES 134

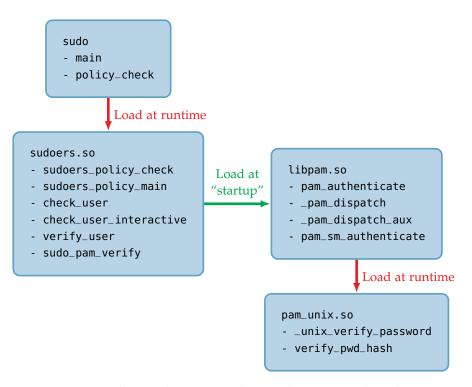

- 7.3 sudo authentication 134

- 7.3.1 Attack model 135

- 7.3.2 sudo analysis 135

- 7.3.3 Code analysis 141

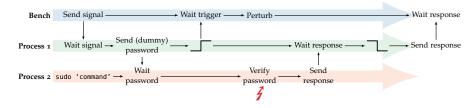

- 7.3.4 Program setup 142

- 7.3.5 Side channel analysis 144

- 7.3.6 Exploitation 145

- 7.3.7 Conclusion on the forced authentication 147

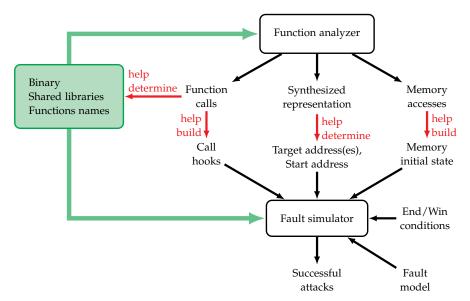

- 7.4 Analysis tools 147

- 7.4.1 The function analyzer 148

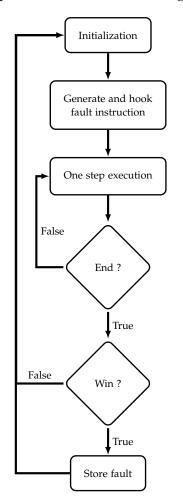

- 7.4.2 Fault simulator 149

- 7.5 Evaluation conclusion 151

- iii conclusion 153

- 8 CONCLUSION 155

- iv Appendix 159

- A BCM2837 MAPS PER FAULT MODEL 161

- B FAULT ANALYZER INTERFACE 163

- C GDB ANALYSIS OF SUDO WITH DEBUG SYMBOLS 167

- D sudoers\_policy\_check() DISASSEMBLY 169

- e OPENSSL AES aes\_encrypt() ROUND FUNCTION (DIS-SASSEMBLED) 171

- E.1 OpenSSL AES round computation (Disassembled) 171

BIBLIOGRAPHY 173

## LIST OF FIGURES

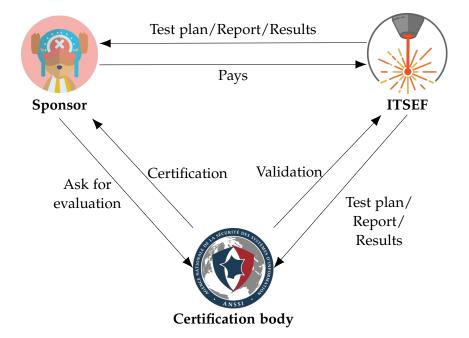

| Figure 1  | Evaluation process actors (example with Common Criteria (CC)) $5$ |  |  |  |  |

|-----------|-------------------------------------------------------------------|--|--|--|--|

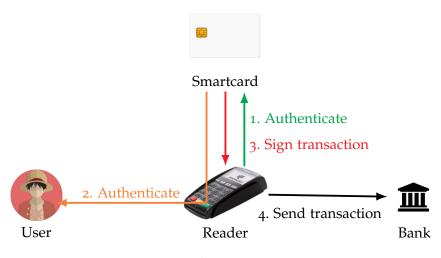

| Figure 2  | Smartcard in a payment environment 10                             |  |  |  |  |

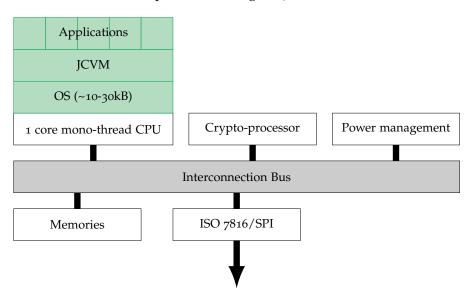

| Figure 3  | Secure element architecture 11                                    |  |  |  |  |

| Figure 4  | Secure element CPU architecture 12                                |  |  |  |  |

| Figure 5  | Secure element packaging 13                                       |  |  |  |  |

| Figure 6  | ISO7816 pins 13                                                   |  |  |  |  |

| Figure 7  | Smartphone environment 14                                         |  |  |  |  |

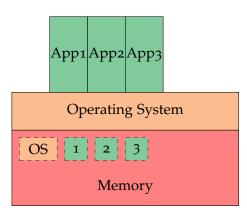

| Figure 8  | System on Chip architecture 15                                    |  |  |  |  |

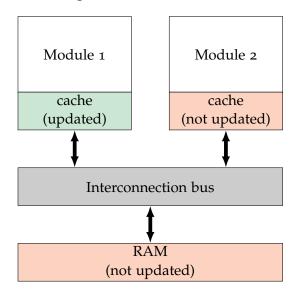

| Figure 9  | Cache incoherence after a module updated a                        |  |  |  |  |

| 0 ,       | data in its dedicated cache memory 16                             |  |  |  |  |

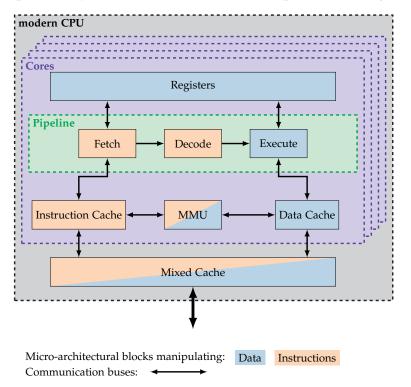

| Figure 10 | Modern CPU architecture 17                                        |  |  |  |  |

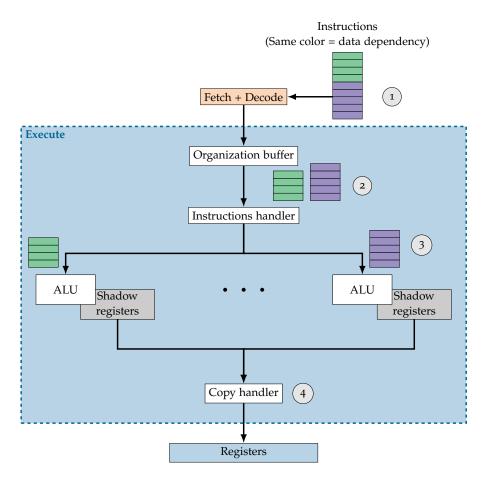

| Figure 11 | Out-of-order execution principle 19                               |  |  |  |  |

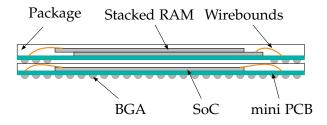

| Figure 12 | Package on package 20                                             |  |  |  |  |

| Figure 13 | BGA grid on a PCIe chip 21                                        |  |  |  |  |

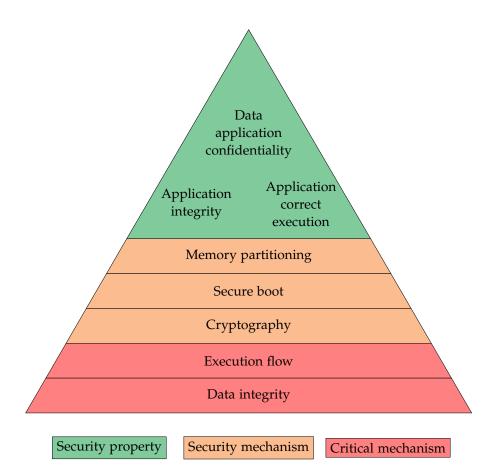

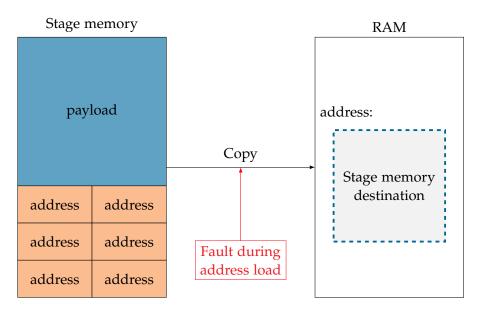

| Figure 14 | Multi-application system security dependencies 23                 |  |  |  |  |

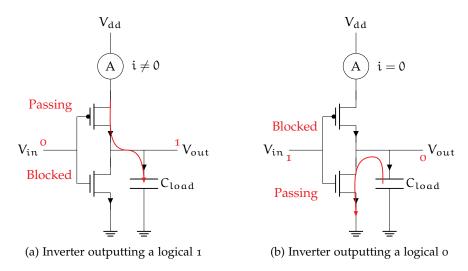

| Figure 15 | Current in a Complementary MOS (CMOS) log-                        |  |  |  |  |

|           | ical inverter gate for different inputs. 27                       |  |  |  |  |

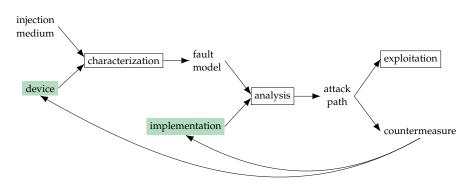

| Figure 16 | Perturbation attack analysis and evaluation pro-                  |  |  |  |  |

|           | cess 32                                                           |  |  |  |  |

| Figure 17 | <i>Stimuli</i> able to perturb a digital device 34                |  |  |  |  |

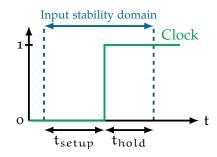

| Figure 18 | Timing constraints on the input for a DFF to                      |  |  |  |  |

|           | behave correctly 35                                               |  |  |  |  |

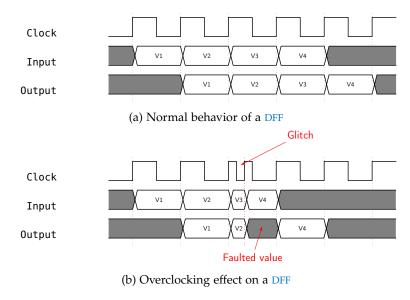

| Figure 19 | Timing constraint in digital devices 35                           |  |  |  |  |

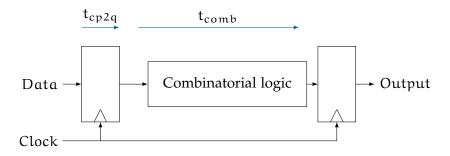

| Figure 20 | Clock glitch effect on a D Flip-Flop (DFF) 36                     |  |  |  |  |

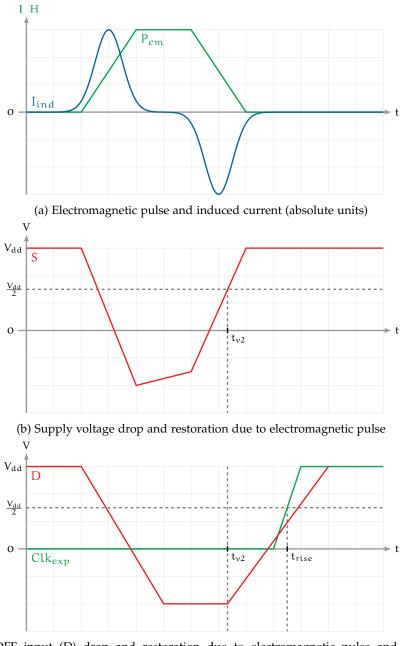

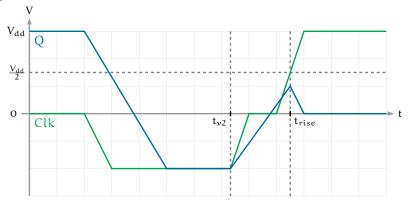

| Figure 21 | How ElectroMagnetic (EM) sampling faults oc-<br>cur [71] 38       |  |  |  |  |

| Figure 22 | ST Microelectronics M27C256B Erasable Pro-                        |  |  |  |  |

|           | grammable Read-Only Memory (EPROM) 39                             |  |  |  |  |

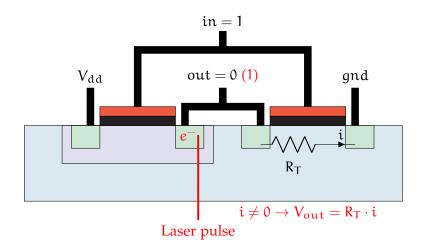

| Figure 23 | Laser effect on a CMOS logical inverter out-                      |  |  |  |  |

|           | putting a logical zero 40                                         |  |  |  |  |

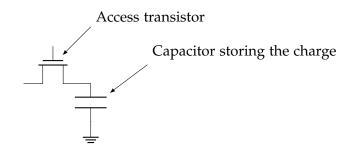

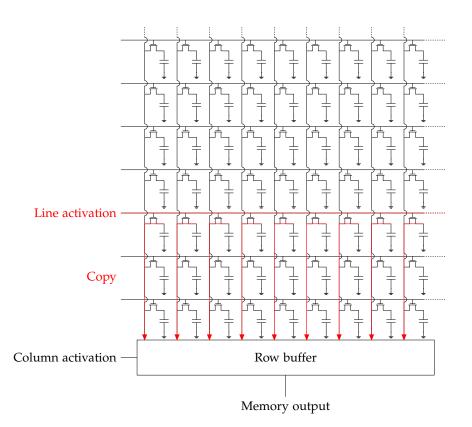

| Figure 24 | One-bit DRAM memory cell 42                                       |  |  |  |  |

| Figure 25 | DRAM line activation and copy in the row buffer 43                |  |  |  |  |

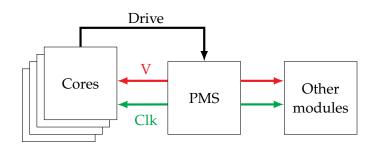

| Figure 26 | PMS supplying the power voltage and clock to                      |  |  |  |  |

| 0         | cores and module of a SoC 43                                      |  |  |  |  |

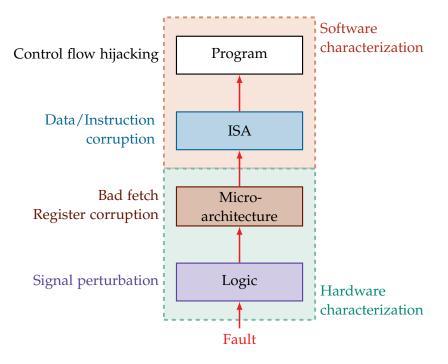

| Figure 27 | Fault propagation through digital devices ab-                     |  |  |  |  |

| 0         | straction layers with some fault effects as ex-                   |  |  |  |  |

|           | amples. Inspired from [94]. 45                                    |  |  |  |  |

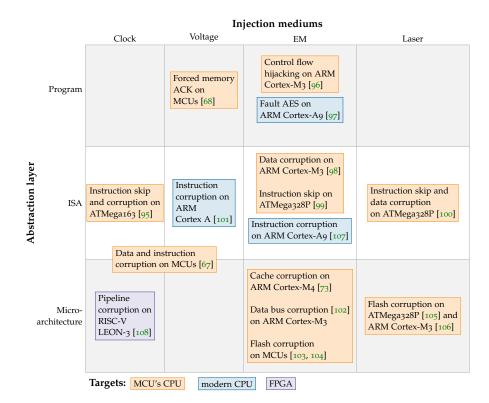

| Figure 28 | Fault injection characterization state of the art. 46             |  |  |  |  |

| Figure 29 | Differential Fault Analysis (DFA) Principle 52                    |  |  |  |  |

| Figure 30 | Propagation of a faulted byte before the last                     |  |  |  |  |

|           | MixColumns operation in the Advanced Encryp-                      |  |  |  |  |

|           | tion Standard (AES) 53                                            |  |  |  |  |

| Figure 31 | Memory partioning principle 54                                    |  |  |  |  |

|           |                                                                   |  |  |  |  |

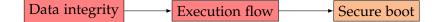

| Figure 32  | Boot loader stage for bypassing secure boot us-                                                       |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| rigure 32  | ing a fault attack [101] 55                                                                           |  |  |  |

| Figure 33  |                                                                                                       |  |  |  |

| Figure 34  | Operation duplication possible implementations 57<br>Software countermeasures integration in the com- |  |  |  |

|            |                                                                                                       |  |  |  |

| Eigenee -  |                                                                                                       |  |  |  |

| Figure 35  | Fault effect characterization overview 67                                                             |  |  |  |

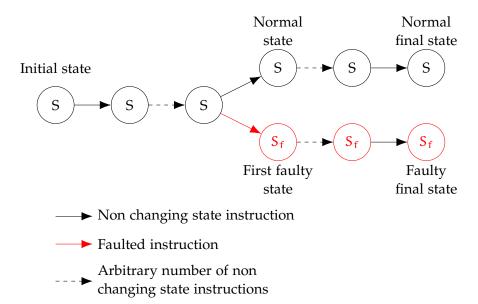

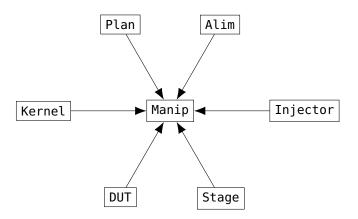

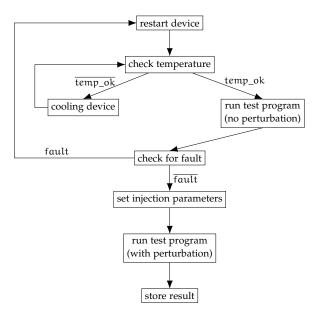

| Figure 36  | General program organization 68                                                                       |  |  |  |

| Figure 37  | Succession of states during the execution of a                                                        |  |  |  |

|            | program containing only non-changing state<br>instructions 69                                         |  |  |  |

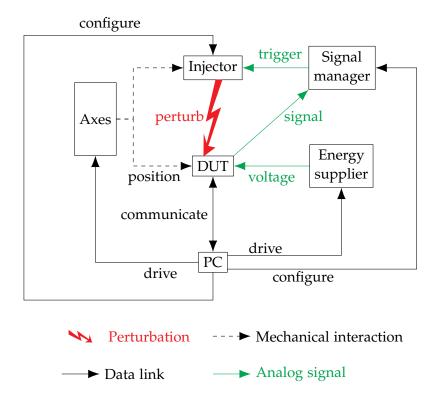

| Figure 28  | Generic attack bench organization and interac-                                                        |  |  |  |

| Figure 38  | tions 78                                                                                              |  |  |  |

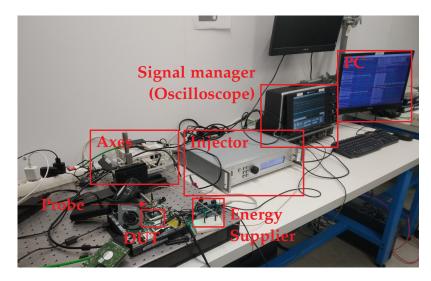

| Figure 39  | ANSSI's EM bench with Intel Core i3 DUT 80                                                            |  |  |  |

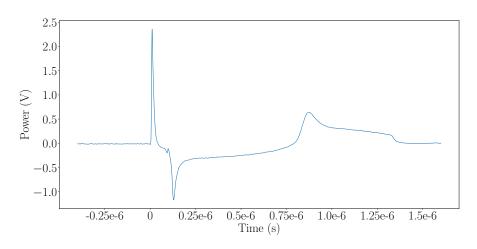

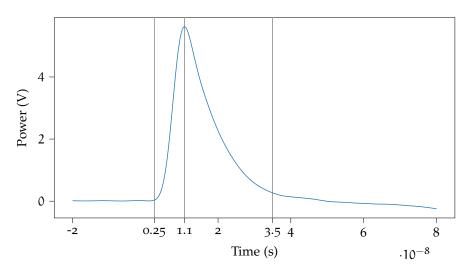

| Figure 40  | Pulse generated by the AvTech (100 V input) 80                                                        |  |  |  |

| Figure 41  | Pulse generated by the AvTech zoomed on the                                                           |  |  |  |

| 1.800.0 41 | first peak (200 V input) 81                                                                           |  |  |  |

| Figure 42  | Raspberry Pi 3 model B board 82                                                                       |  |  |  |

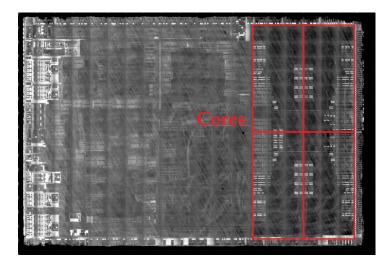

| Figure 43  | BCM2837 infrared backside layout image 83                                                             |  |  |  |

| Figure 44  | Open BCM2837 with the chip in its package 83                                                          |  |  |  |

| Figure 45  |                                                                                                       |  |  |  |

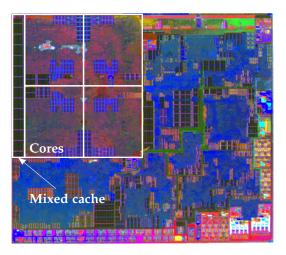

| Figure 46  | Raspberry Pi 4 board 84<br>BCM2711bo infrared backside layout image 84                                |  |  |  |

| Figure 47  | BCM2711bo infrared backside layout image 84<br>Intel Core i3 SoC 85                                   |  |  |  |

| Figure 48  |                                                                                                       |  |  |  |

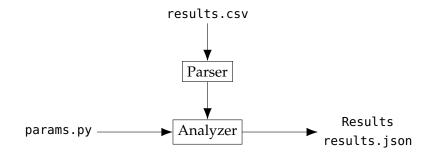

| Figure 49  | Bench manager software general organization85Example of an experiment process86                       |  |  |  |

| 0          |                                                                                                       |  |  |  |

| Figure 50  |                                                                                                       |  |  |  |

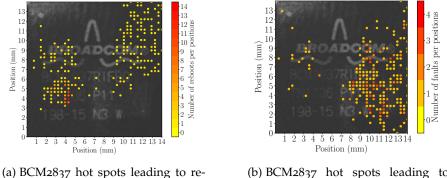

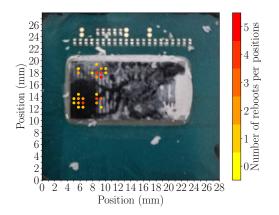

| Figure 51  | Hot spots of the BCM2837 regarding EM per-<br>turbation 93                                            |  |  |  |

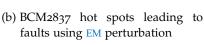

| Figure 52  | Input voltage amplitude effect on BCM2837 dur-                                                        |  |  |  |

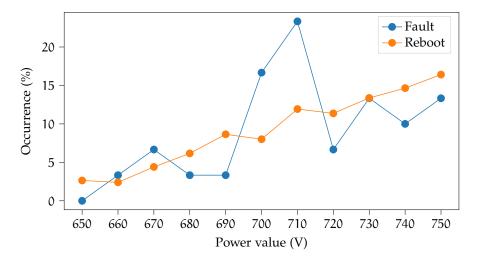

| 0 0        | ing EM perturbation 93                                                                                |  |  |  |

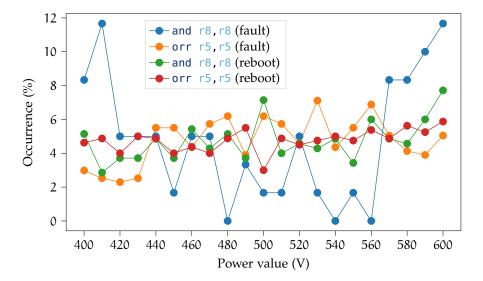

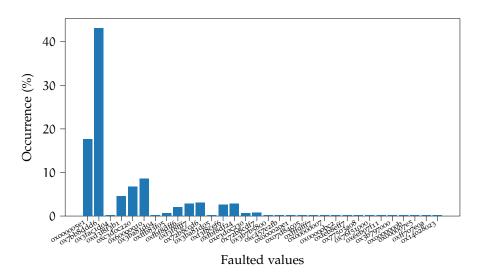

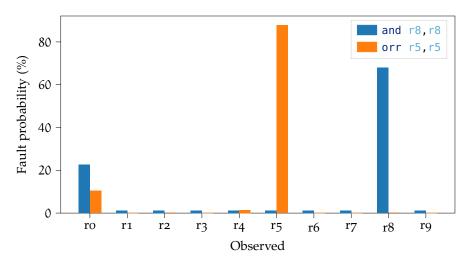

| Figure 53  | and r8, r8 faulted values distribution on BCM2837                                                     |  |  |  |

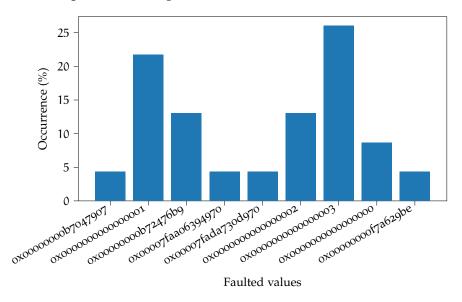

| 0 55       | using EM perturbation 94                                                                              |  |  |  |

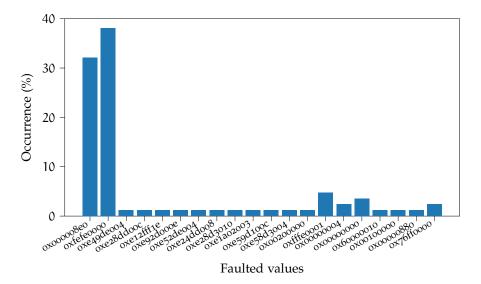

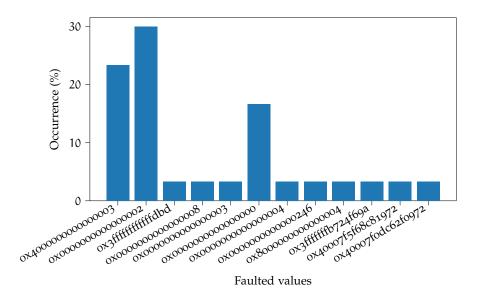

| Figure 54  | orr r5, r5 faulted values distribution on BCM2837                                                     |  |  |  |

| 0 51       | using EM perturbation 95                                                                              |  |  |  |

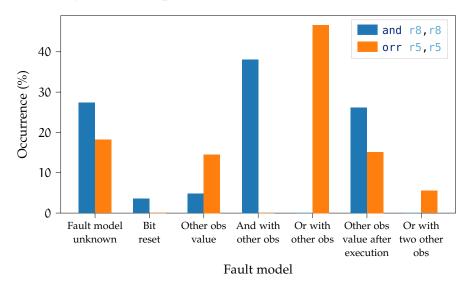

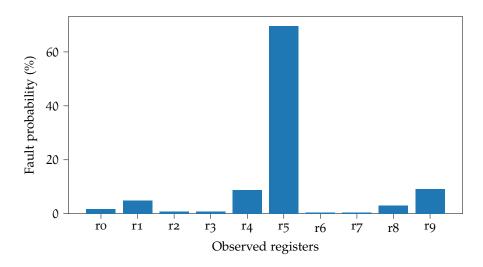

| Figure 55  | Probability of observed registers to be faulted                                                       |  |  |  |

| 0 00       | for both experiments on BCM2837 using EM                                                              |  |  |  |

|            | perturbation 95                                                                                       |  |  |  |

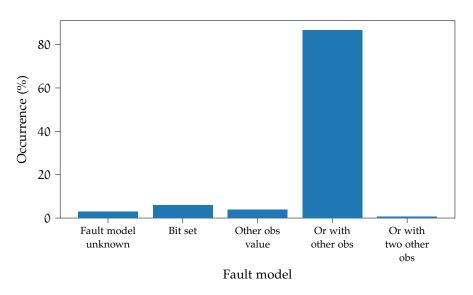

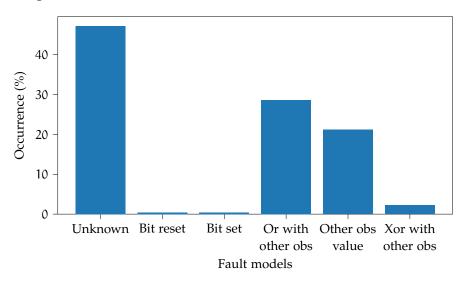

| Figure 56  | Probability of observing the different fault mod-                                                     |  |  |  |

| 0 5        | els for both experiments on BCM2837 using EM                                                          |  |  |  |

|            | perturbation 96                                                                                       |  |  |  |

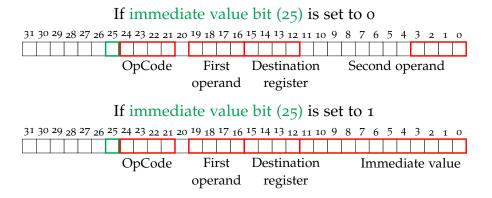

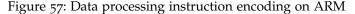

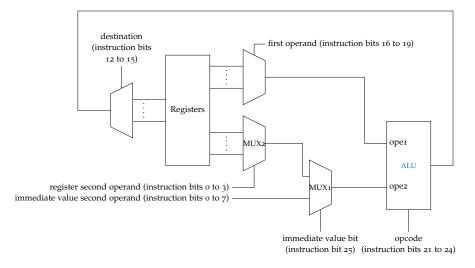

| Figure 57  | Data processing instruction encoding on ARM 99                                                        |  |  |  |

| Figure 58  | Pipeline execute stage architecture with ARM                                                          |  |  |  |

| 8 )*       | instruction (figure 57) corresponding bits 102                                                        |  |  |  |

| Figure 59  | Probability of observing the different fault mod-                                                     |  |  |  |

|            | els for orr r <sup>3</sup> , r <sup>3</sup> experiment on BCM2837 with                                |  |  |  |

|            | a baremetal setup using EM perturbation 105                                                           |  |  |  |

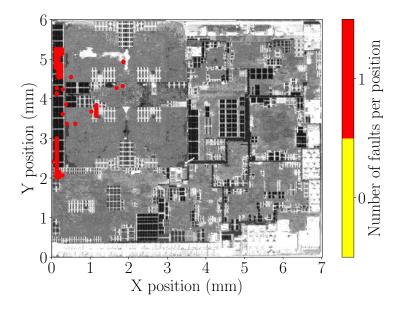

| Figure 60  | BCM2711bo hot spots leading to faults using                                                           |  |  |  |

| 1 1941C 00 | laser perturbation 108                                                                                |  |  |  |

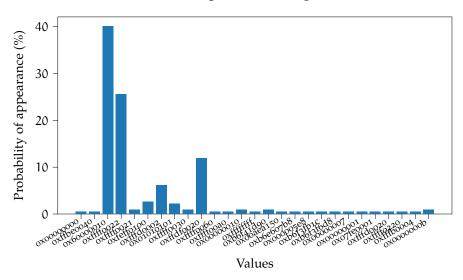

| Figure 61  | orr r5, r5 faulted values distribution on BCM2711bo                                                   |  |  |  |

| 116010 01  | using laser perturbation 109                                                                          |  |  |  |

|            | using inser perturbation 109                                                                          |  |  |  |

| Figure 62    | Probability of observed registers to be faulted                          |

|--------------|--------------------------------------------------------------------------|

|              | for orr r5, r5 experiment on BCM2711bo us-<br>ing laser perturbation 110 |

| Figure 63    | Probability of observing the different fault mod-                        |

| 118010 09    | els for orr r5, r5 experiment on BCM2711bo                               |

|              | using laser perturbation 110                                             |

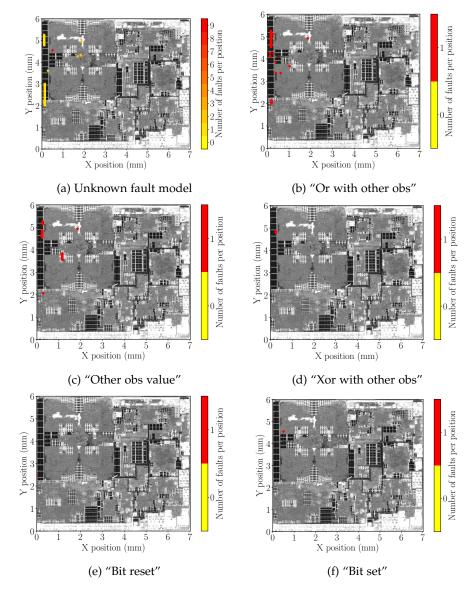

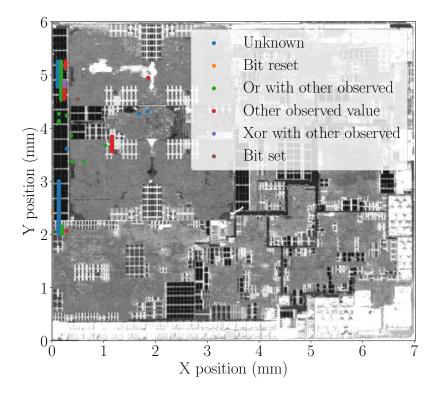

| Figure 64    | BCM2711bo hot spots leading to the different                             |

| 0            | observed fault models 112                                                |

| Figure 65    | BCM2711bo hot spots leading to the different                             |

| 0            | observed fault models (alternative version) 113                          |

| Figure 66    | Intel Core i3 hot spots leading to reboots using                         |

|              | EM perturbation 115                                                      |

| Figure 67    | Input voltage amplitude effect on Intel Core i3                          |

|              | during EM perturbation 115                                               |

| Figure 68    | mov rbx, rbx faulted value distribution on Intel                         |

|              | Core i3 using EM perturbation 116                                        |

| Figure 69    | orr rbx, rbx faulted value distribution on Intel                         |

|              | Core i3 using EM perturbation 117                                        |

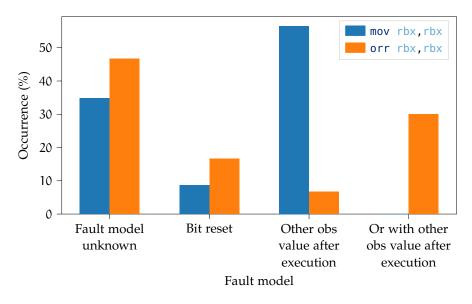

| Figure 70    | Probability of observing the different fault mod-                        |

|              | els for both experiments on Intel Core i3 using                          |

|              | EM perturbation 118                                                      |

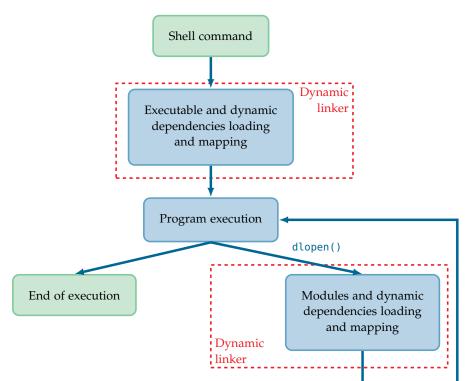

| Figure 71    | Linux dynamic linker interventions during pro-                           |

|              | gram execution 122                                                       |

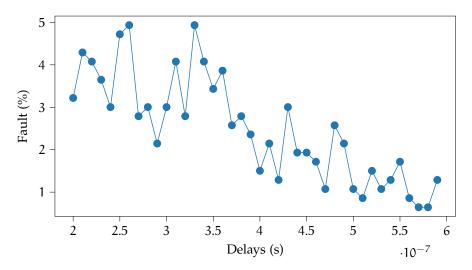

| Figure 72    | Impact of the delay on the probability while                             |

|              | faulting an OpenSSL AES encryption using EM                              |

|              | perturbation on BCM2837. 126                                             |

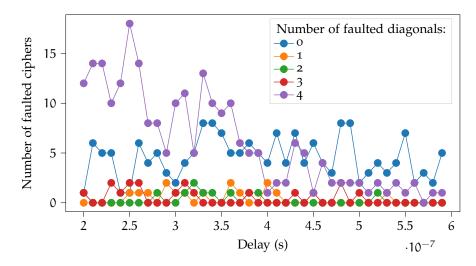

| Figure 73    | Impact of the delay on the number of faulted                             |

|              | diagonals while faulting an OpenSSL AES en-                              |

|              | cryption using EM perturbation on BCM2837. 127                           |

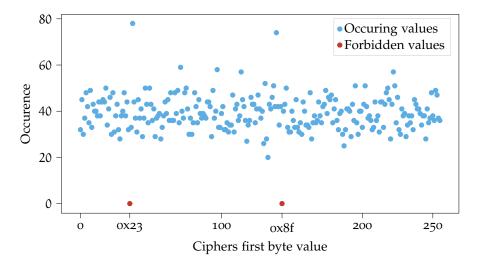

| Figure 74    | Distribution of the first byte for 10000 faulted                         |

|              | ciphers on our baremetal AES on the BCM2837. 133                         |

| Figure 75    | sudo calling architecture and dependencies re-                           |

|              | garding the user authentication process. 141                             |

| Figure 76    | Target program execution flow143                                         |

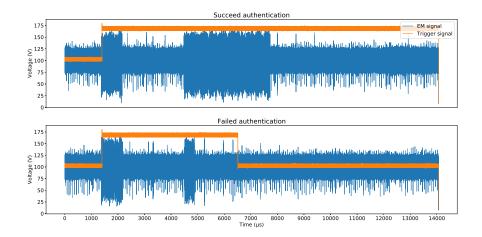

| Figure 77    | EM activity of the CPU during a user authenti-                           |

| <b>T</b> : 0 | cation on BCM2711bo 145                                                  |

| Figure 78    | Analyzer and simulator software architecture. 148                        |

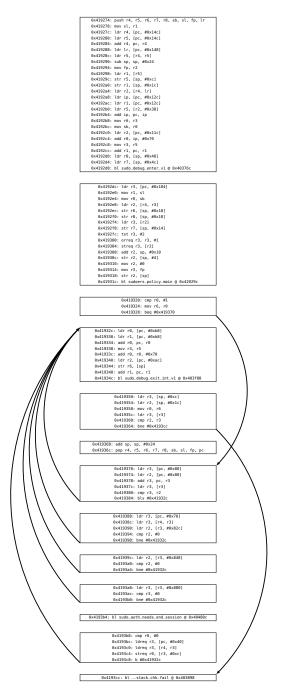

| Figure 79    | sudoers_policy_check function partial disas-                             |

| <b>F'</b> 0  | sembly printed in a shell. 150                                           |

| Figure 80    | Fault simulation process. 151                                            |

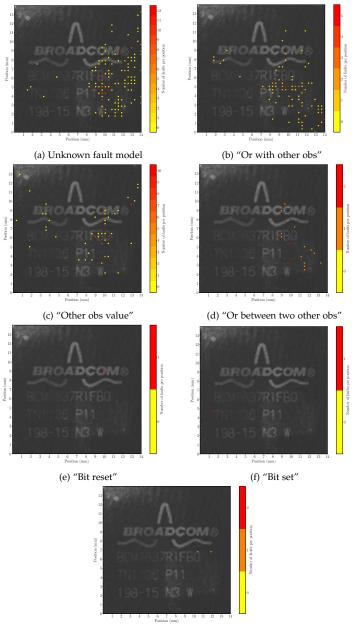

| Figure 81    | BCM2837 hot spots leading to the different ob-                           |

| Eigung 9-    | served fault models 161                                                  |

| Figure 82    | Fault analyzer graphical interface 164                                   |

## LIST OF TABLES

| Table 1  | Target initial values for fault characterization |  |  |

|----------|--------------------------------------------------|--|--|

|          | considering ten registers 73                     |  |  |

| Table 2  | Data fault models 74                             |  |  |

| Table 3  | Instruction fault models 75                      |  |  |

| Table 4  | orr r5, r5 corruptions regarding the "Or with    |  |  |

|          | other obs" fault model 97                        |  |  |

| Table 5  | orr r5, r5 corruptions regarding the "Or with    |  |  |

| <u> </u> | two other obs" fault model 98                    |  |  |

| Table 6  | orr r5, r5 corruptions regarding the "Other obs  |  |  |

|          | value" fault model 98                            |  |  |

| Table 7  | and r8, r8 corruptions regarding the "Other obs  |  |  |

|          | value" fault model 98                            |  |  |

| Table 8  | Binary values of the observed opcodes. 100       |  |  |

| Table 9  | Fault distribution on cmp test code 101          |  |  |

| Table 10 | orr r5, r5 corruptions regarding the "Other obs  |  |  |

|          | value" fault model on the BCM2711bo perturbed    |  |  |

|          | with a laser 113                                 |  |  |

| Table 11 | mov rbx, rbx corruptions regarding the "Other    |  |  |

|          | obs value" fault model 118                       |  |  |

| Table 12 | orr rbx, rbx corruptions regarding the "Other    |  |  |

|          | with other obs" fault model 119                  |  |  |

| Table 13 | Forbidden values for every byte of the observed  |  |  |

|          | ciphers. 133                                     |  |  |

| Table 14 | Possible key bytes for the correct guess $y_1 =$ |  |  |

|          | 0x30 with the correct key in red. 134            |  |  |

| Table 15 |                                                  |  |  |

## LISTINGS

| Figure 4.1 | Step counter countermeasure on a block of I instructions 60                        |

|------------|------------------------------------------------------------------------------------|

| Figure 5.1 | Example of a test program for fault characterization 70                            |

| Figure 5.2 | Example of a test program for fault characteri-<br>zation on memory accesses 70    |

| Figure 5.3 | Example of a test program for instruction skip/rep-<br>etition characterization 71 |

| Figure 5.4   | Example of a test program for instruction repe-                                             |

|--------------|---------------------------------------------------------------------------------------------|

| Figure 6.1   | tition with replacement characterization 71<br>Example of params.py file for the fault ana- |

| <b>-</b>     | lyzer 87                                                                                    |

| Figure 6.2   | Example of values for which the fault analyzer                                              |

| Figuro 6 a   | could not determine a fault model. 90                                                       |

| Figure 6.3   | Types of fault models as defined in fault<br>models.py 91                                   |

| Figure 6.4   | Or with other observed fault model test func-                                               |

|              | tion as implemented in fault_models.py 91                                                   |

| Figure 6.5   | Fault class as implemented in fault.py 92                                                   |

| Figure 6.6   | Two first instruction fault models as implemented                                           |

| -            | in fault_models.py 92                                                                       |

| Figure 6.7   | BCM2837 immediate value test program 101                                                    |

| Figure 6.8   | BCM2837 memory test code 103                                                                |

| Figure 6.9   | BCM2837 baremetal test program 105                                                          |

| Figure 6.10  | BCM2837 assembly code of the loop test pro-                                                 |

|              | gram 106                                                                                    |

| Figure 6.11  | BCM2837 with baremetal setup with correct                                                   |

|              | identity memory mapping 107                                                                 |

| Figure 6.12  | BCM2837 with baremetal setup with faulted                                                   |

|              | memory mapping 107                                                                          |

| Figure 7.1   | OpenSSL AES pre-computed tables (partial) 124                                               |

| Figure 7.2   | OpenSSL AES round computation (C) 125                                                       |

| Figure 7.3   | DFA program main loop 129                                                                   |

| Figure 7.4   | Example usage and result of the DFA program                                                 |

|              | on the first diagonal 130                                                                   |

| Figure 7.5   | AES correct key as implemented in the DFA                                                   |

|              | program 130                                                                                 |

| Figure 7.6   | Faulted ciphers used in our DFA (ciphers_diag0.txt) 130                                     |

| Figure 7.7   | Commands to identify the strcmp calls of the                                                |

| <b>T</b> : 0 | sudo program using gdb. 137                                                                 |

| Figure 7.8   | gdb output of a strcmp call comparing two hashes. 138                                       |

| Figure 7.9   | gdb output of a strcmp call comparing two hashes                                            |

|              | with libraries compiled with debug symbols. A                                               |

|              | bigger representation is available in appendix C. 139                                       |

| Figure 7.10  | sudo binary policy return value checking in                                                 |

|              | main function from sudo.c 141                                                               |

| Figure 7.11  | C code for the child process in the sudo evalu-                                             |

|              | ation setup. 143                                                                            |

| Figure 7.12  | Part of the C code for the parent process com-                                              |

|              | municating with the child process. 144                                                      |

| Figure B.1   | Fault analyzer command line interface (List of                                              |

|              | experiments). Experiments with a star (*) are                                               |

|              | already analyzed. 163                                                                       |

| Figure B.2   | Fault analyzer command line interface (List of                                              |

|              | results) 163                                                                                |

| Figure B.3   | Fault analyzer command line interface (Result) 164                                          |

| Figure B.4   | main of the fault analyzer 165                                                              |

|              |                                                                                             |

Figure C.1gdb output of a strcmp call comparing two hashes<br/>with libraries compiled with debug symbols.167

## LIST OF EQUATIONS

| Figure 4.1   | Setup timing constraint on clock cycle in a dig-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| rigure 4.1   | ital device. 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Figure 4.2   | Hold timing constraint on clock cycle in a dig-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 0 +          | ital device. 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Figure 4.3   | Fault masking attack model. 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Figure 4.4   | Computation of a cipher using RSA-CRT 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Figure 4.5   | Factorization of RSA modulus in a faulted CRT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 0 10         | implementation 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Figure 4.6   | Factorization of RSA modulus in a faulted CRT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|              | implementation (Lenstra's improvement) 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Figure 4.7   | Relation between the faulty signature obtained                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|              | by skipping the last squaring and the correct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|              | signature in the square and multiply algorithm. 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Figure 4.8   | Relation between the faulty signature obtained                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|              | by skipping the squaring in the $i^{th}$ and $(i - $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|              | 1) <sup>th</sup> iteration of the loop in the square and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|              | multiply algorithm. 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Figure 4.9   | Bézout's identity 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Figure 4.10  | AES last round <i>SubBytes</i> and <i>AddRoundKey</i> op-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| <b>T</b> .   | erations in the presence of a corrupted SBox 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Figure 4.11  | Relation between the forbidden value and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| <b>T</b> .   | secret key 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Figure 4.12  | Relation between the faulty ciphertext, the cor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|              | rect ciphertext and the possible faulty outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|              | of the <i>MixColumns</i> operation during a DFA on AES 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Figure 4.13  | AES 52<br>Relation between the faulty ciphertext and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 1 igure 4.15 | correct cipher text in the case of the skipping of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|              | the last <i>AddRoundKey</i> operation in AES 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Figure 4.14  | Relation between the virtual address and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 8            | physical address in Linux based OS 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Figure 4.15  | Infection countermeasure 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| -            | , and the second s |  |  |  |  |

| Figure 5.1   | Difference between all registers initial values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|              | property 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Figure 5.2   | No arithmetical links between registers initial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| <b>T</b> '   | values property 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Figure 5.3   | Registers initial values construction 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Figure 5.4   | State computation in a CPU 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Figure 5.5   | Faulted state computation in a CPU 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Figure 5.6   | Data fault model 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Figure 5.7 | Instru        | ction fault model | 74                    |

|------------|---------------|-------------------|-----------------------|

| Figure 7.1 | Pre-co<br>AES | 1                 | tables in the OpenSSL |

## ACRONYMS

\_\_\_\_

| se Secure Element                    |

|--------------------------------------|

| soc System on Chip                   |

| fi Fault Injection                   |

| emfi ElectroMagnetic Fault Injection |

| emp EM Pulse                         |

| tee Trusted Execution Environment    |

| iot Internet of Things               |

| pc Program Counter                   |

| dut Device Under Test                |

| iot Internet of Things               |

| cpu Central Processing Unit          |

| os Operating System                  |

| bga Ball Grid Array                  |

| dfa Differential Fault Analysis      |

pmic Power Management Integrated Circuit

mmu Memory Management Unit

io Input/Output

alu Arithmetical and Logical Unit

gpio General Purpose Input/Output

em ElectroMagnetic

**Ifi** Laser Fault Injection

dpa Differential Power Analysis

cpa Correlation Power Analysis

mos Metal Oxide Semiconductor

nmos N-doping MOS

pmos P-doping MOS

cmos Complementary MOS

aes Advance Encryption Standard

sca Side-Channel Analysis/Attack

mia Mutual Information Analysis

Ira Linear Regression Attack

tpm Trusted Platform Module

scp Secure Channel Protocol

iot Internet of Things

| rsa Rivest, Shamir, and Adelman                  |

|--------------------------------------------------|

| ecdsa Elliptic Curve Digital Signature Algorithm |

| aes Advanced Encryption Standard                 |

| fa Fault Attack                                  |

| vlsi Very Large Scale Integration                |

| ram Random Access Memory                         |

| dram Dynamic RAM                                 |

| des Data Encryption Standard                     |

| ecc Elliptic Curve Cryptography                  |

| mcu Micro-Controller Unit                        |

| fbbi Forward Body Biasing Injection              |

| dff D Flip-Flop                                  |

| rom Read-Only Memory                             |

eprom Erasable Programmable Read-Only Memory

eeprom Electrically EPROM

uv Ultra Violet

ir Infra Red

puf Physically Unclonable Function

gpu Graphics Processing Unit

rdma Remote DMA

- pms Power Management Subsystem

- pll Phase Locked Loop

- fpga Field Programmable Gate Array

- isa Instruction Set Architecture

- cfg Control Flow Graph

- crt Chinese Reminder Theorem

- pfa Persistent Fault Analysis

- sbox Substitution Box

- jcvm JavaCard Virtual Machine

- bcv ByteCode Verifier

- mpu Memory Protection Unit

- pte Page Table Entry

- ddr4 DDR version 4

- sram Synchronous Random Access Memory

- rop Return-Oriented Programming

- dos Deny Of Service

- ahb Advanced High-performance Bus

- axi Advanced eXtensible Interface

nfc Near Field Communication

jtag Join Test Action Group

mab Micro-Architectural Block

hdmi High-Definition Multimedia Interface

tlb Translation Lookaside Buffer

cc Common Criteria

cspn Certificat de Sécurité de Premier Niveau

anssi Agence Nationale de la Sécurité des Systèmes d'Information

eu European Union

gdpr General Data Protection Regulation

- rtl Register Transfert Level

- fib Focused Ion Beam

- bsz Beschleunigte Sicherheitszertifizierung

- bspa Baseline Security Product Assessment

- itsef Information Technology Security Evaluation Facility

- vna Vector Network Analyzer

## Part I

# INTRODUCTION

It's good to know where you come from...

*Even though we should learn from those who came before us, we must also forge our own path.*

— Avatar Korra (The Legend Of Korra)

ABSTRACT