# Radiation hardened design of CMOS pixel sensor for the micro-vertex detector of the CBM experiment

Yue Zhao

#### ▶ To cite this version:

Yue Zhao. Radiation hardened design of CMOS pixel sensor for the micro-vertex detector of the CBM experiment. Physics [physics]. Université de Strasbourg, 2021. English. NNT: 2021STRAE010 . tel-03284188

# HAL Id: tel-03284188 https://theses.hal.science/tel-03284188

Submitted on 24 Jan 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE STRASBOURG

# ÉCOLE DOCTORALE PHYSIQUE ET CHIMIE-PHYSIQUE Institut Pluridisciplinaire Hubert CURIEN (IPHC) - UMR7178

# THÈSE présentée par : Yue ZHAO

Soutenue le : Février 18 2021

pour obtenir le grade de : Docteur de l'université de Strasbourg

Discipline/ Spécialité : Physique

# Radiation Hardened Design of CMOS Pixel Sensor for the Micro-Vertex Detector of the CBM Experiment

THÈSE dirigée par :

M. HU YannM. BAUDOT JérômeProfesseur, Université de StrasbourgProfesseur, Université de Strasbourg

RAPPORTEURS:

M. BARBERO Marlon Professeur, Université d'Aix Marseille

M. GOIFFON Vincent Professeur, ISAE - SUPAERO

#### **AUTRES MEMBRES DU JURY:**

Mme. ORSINI FabienneM. UHRING WilfriedDirectrice de recherches, Synchrotron SOLEILProfesseur, Université de Strasbourg

| Contents   |                                            | I   |

|------------|--------------------------------------------|-----|

| Résumé     |                                            | VII |

| Chapter 1. | The MVD for the CBM experiment             | 1   |

| 1.1 Th     | e CBM experiment                           | 1   |

| 1.1.1      | The SIS Machine                            | 2   |

| 1.1.2      | The Physics Program                        | 3   |

| 1.1.3      | The subdetectors of CBM Experiment         | 5   |

| 1.2 Th     | e Micro Vertex Detector (MVD)              | 6   |

| 1.2.1      | Requirements                               | 6   |

| 1.2.2      | Geometries                                 | 8   |

| 1.2.3      | The predicted particle environment for MVD | 9   |

| 1.3 Th     | e introduction of Sensors for MVD          | 11  |

| 1.3.1      | Introduction into semiconductors           | 11  |

| 1.3.2      | Introduction to silicon sensors            | 13  |

| 1.3.3      | The Pixel Sensors for MVD                  | 14  |

| 1.4 Th     | e MIMOSIS for CBM MVD                      | 19  |

| 1.4.1      | Design of the Pixel                        | 20  |

| 1.4.2      | Buffer structure                           | 21  |

| 1.4.3      | The development schedules                  | 23  |

| 1.5 Th     | e strategy and focus of this work          | 23  |

| 1.6 Bi     | bliography                                 | 25  |

| C        | hapte | er 2. | The Radiation Effects on CMOS Sensors                   | .27 |

|----------|-------|-------|---------------------------------------------------------|-----|

|          | 2.1   | Ba    | sic Radiation Mechanism on Silicon Sensors and I.C      | .28 |

|          | 2.    | 1.1   | Electrons and positrons                                 | .28 |

|          | 2.    | 1.2   | Protons and ions                                        | .31 |

|          | 2.    | 1.3   | Energy loss, linear energy transfer and stopping power. | .32 |

|          | 2.2   | Sir   | ngle event effects                                      | .34 |

|          | 2.    | 2.1   | Mechanism                                               | .34 |

|          | 2.    | 2.2   | SEE terminology and classification                      | .37 |

|          | 2.    | 2.3   | SEE Response in Digital Circuits                        | .38 |

|          | 2.3   | To    | tal ionizing dose effects                               | .42 |

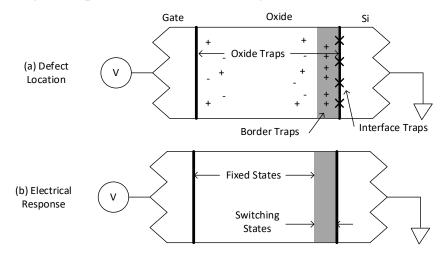

|          | 2.    | 3.1   | Mechanism                                               | .42 |

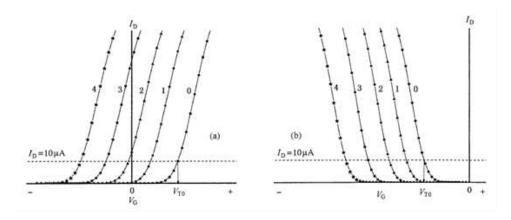

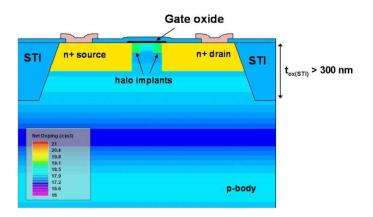

|          | 2.    | 3.2   | Impact of TID Deficiencies on Bulk MOS Structures       | .45 |

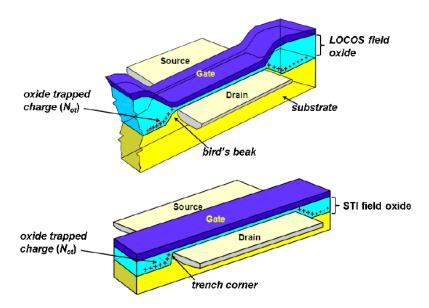

|          | 2.    | 3.3   | Impact of TID Deficiencies on STI MOS Structures        | .48 |

|          | 2.4   | Dis   | splacement damage                                       | .49 |

|          | 2.5   | Su    | mmary                                                   | .52 |

|          | 2.6   | Bil   | oliography                                              | .53 |

| С<br>ГID | hapte | er 3. | Radiation Harden Techniques for MVD against SEE a       | and |

|          | 3.1   | Int   | roduction to System Reliability                         | .59 |

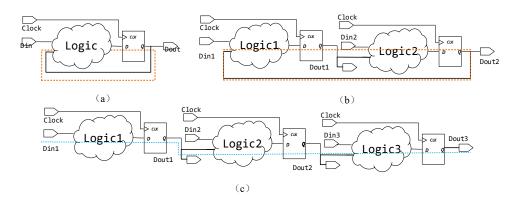

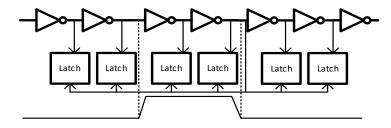

|          | 3.2   | Tri   | ple modular redundancy (TMR)                            | .61 |

|          | 3.    | 2.1   | Topologies of TMR in digital circuits                   | .61 |

|          | 3.    | 2.2   | The trade-off on reliability and cost                   | .63 |

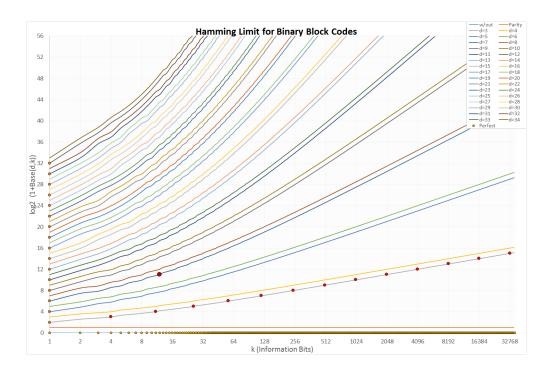

|          | 3.3   | Em    | or correction code (ECC)                                | .66 |

|          | 3.    | 3.1   | Mechanism and Codeword distance                         | .66 |

|          | 3.    | 3.2   | Hamming code                                            | .67 |

|          | 3.    | 3.3   | CRC                                                     | .68 |

|          | 3.    | 3.4   | Discussion                                              | .70 |

|            | 3.4   | Re   | freshing and reloading                            | 70       |

|------------|-------|------|---------------------------------------------------|----------|

|            | 3.5   | Re-  | -entrant gate layout and guard ring               | 72       |

|            | 3.6   | Re   | verse body biasing                                | 74       |

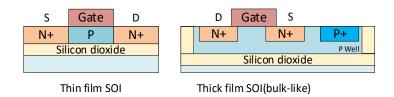

|            | 3.7   | Sil  | icon-on-insulator (SOI)                           | 75       |

|            | 3.8   | Su   | mmary                                             | 76       |

|            | 3.9   | Bił  | oliography                                        | 78       |

| C<br>Syste | -     | r 4. | The Radiation-Harden Design of The Frontend 80    | Readout  |

|            | 4.1   | De   | sign principle of the readout system              | 81       |

|            | 4.2   | Eva  | aluation                                          | 86       |

|            | 4.2   | 2.1  | The cross-section and hit density of MVD          | 86       |

|            | 4.2   | 2.2  | The error rate in control flows                   | 87       |

|            | 4.2   | 2.3  | The error rate in data flows                      | 88       |

|            | 4.2   | 2.4  | The error rate in global controller               | 88       |

|            | 4.3   | TM   | IR Deployment                                     | 89       |

|            | 4.3   | 3.1  | Design Flow with TMR                              | 89       |

|            | 4.3   | 3.2  | Detailed Deployment                               | 90       |

|            | 4.4   | EC   | C Deployment                                      | 95       |

|            | 4.5   | Ve   | rification                                        | 95       |

|            | 4.5   | 5.1  | Modelling SEE pulse                               | 96       |

|            | 4.5   | 5.2  | Simulation with SEE pulse injected                | 99       |

|            | 4.6   | TM   | IR Optimization                                   | 101      |

|            | 4.7   | Su   | mmary                                             | 103      |

|            | 4.8   | Bił  | oliography                                        | 104      |

| С          | hapte | r 5. | The Radiation Harden Design of the Phase-Lock 105 | ked Loop |

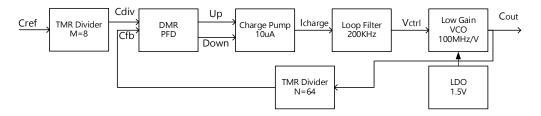

|            | 5.1   | Arc  | chitecture of PLL                                 | 105      |

| 5.1              | .1  | Topology                                               | 106   |

|------------------|-----|--------------------------------------------------------|-------|

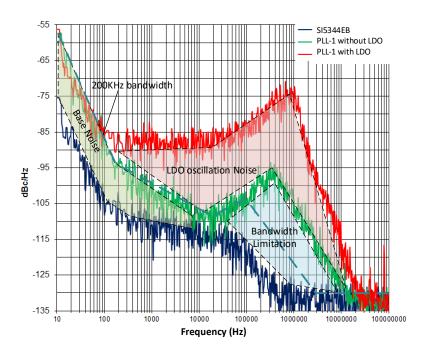

| 5.1              | .2  | Noise Model                                            | 107   |

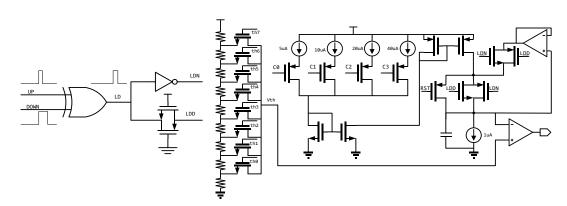

| 5.2              | Cir | cuit design                                            | 108   |

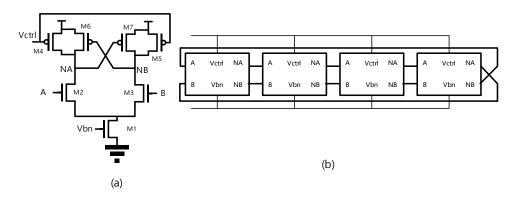

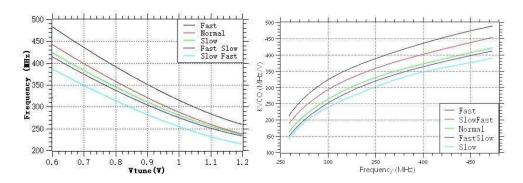

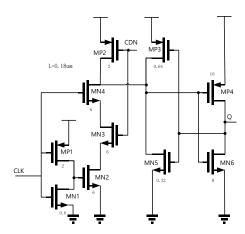

| 5.2              | 2.1 | VCO                                                    | 108   |

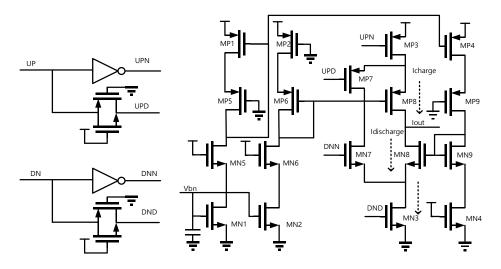

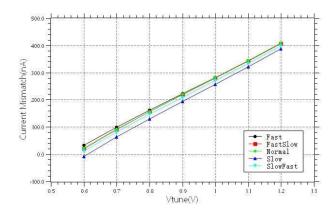

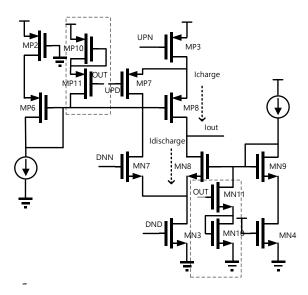

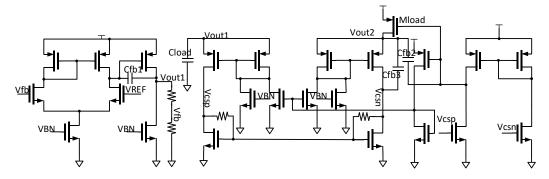

| 5.2              | 2.2 | Charge Pump                                            | 110   |

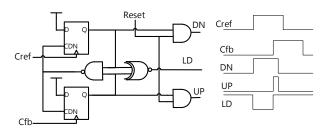

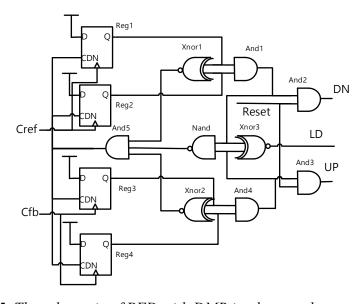

| 5.2              | 2.3 | Phase/Frequency Detector and Lock State Detector       | 111   |

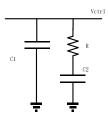

| 5.2              | 2.4 | Loop Parameter                                         | 113   |

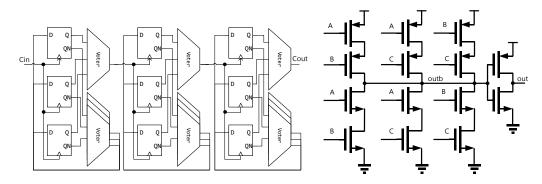

| 5.2              | 2.5 | Divider                                                | 114   |

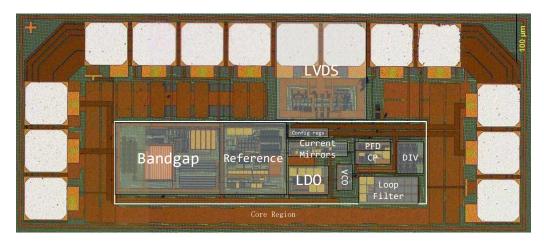

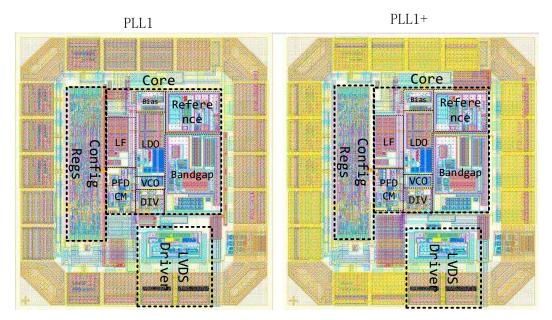

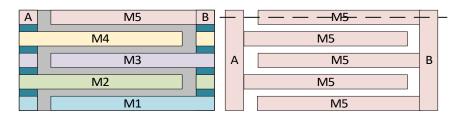

| 5.2              | 2.6 | Layout                                                 | 115   |

| 5.3              | Co  | rrections and Improvements                             | 115   |

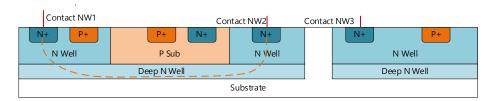

| 5.3              | 3.1 | The deep N-well connection                             | 115   |

| 5.3              | 3.2 | New lock detection structure                           | 116   |

| 5.3              | 3.3 | Dual Modular Redundancy on PFD                         | 117   |

| 5.3              | 3.4 | Charge Pump balance                                    | 118   |

| 5.3              | 3.5 | Re-entrant gate layout for bias                        | 119   |

| 5.3              | 3.6 | Compact layout                                         | 120   |

| 5.4              | Tes | st method and results                                  | 121   |

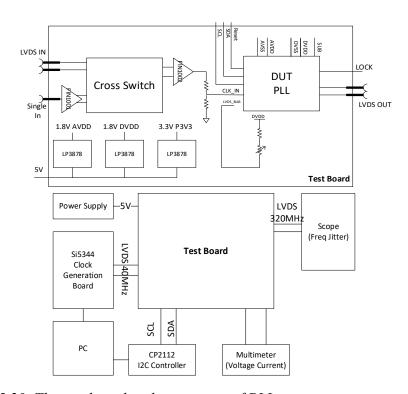

| 5.4              | 1.1 | Test board, system                                     | 122   |

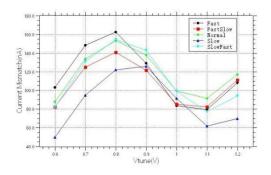

| 5.4              | 1.2 | Static test results                                    | 123   |

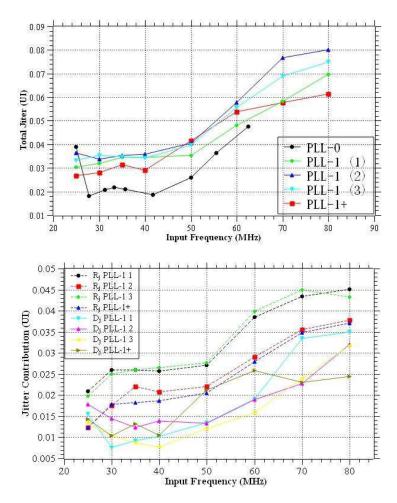

| 5.4              | 1.3 | Jitter performance                                     | 124   |

| 5.4              | 1.4 | Dynamic test results                                   | 126   |

| 5.5              | The | e improvements                                         | 128   |

| 5.6              | Sur | nmary                                                  | 131   |

| 5.7              | Bib | oliography                                             | 132   |

| Chapter MIMOSIS- |     | Preparation for the Radiation-Tolerance Evaluation 133 | on of |

| 6.1              | SE  | E Cross-section Calibration                            | 133   |

| 6.1     | .1  | Characterization Method                  | 134 |

|---------|-----|------------------------------------------|-----|

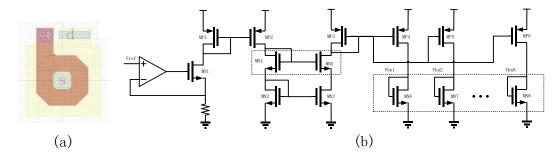

| 6.1     | .2  | Chip design                              | 135 |

| 6.1     | .3  | Test Design                              | 137 |

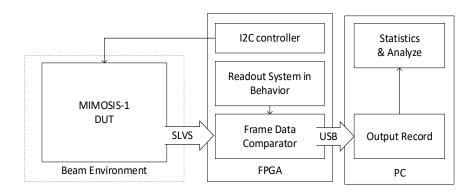

| 6.2     | SE  | E Beam Test Method of the Readout System | 140 |

| 6.2     | 2.1 | The testability design of MIMOSIS-1      | 140 |

| 6.2     | 2.2 | The in-Time Test Method of MIMOSIS-1     | 142 |

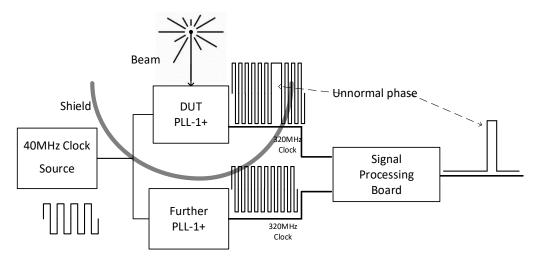

| 6.3     | TII | D and SEE Beam Test Method of the PLL    | 143 |

| 6.3     | 3.1 | TID Test Method                          | 143 |

| 6.3     | 3.2 | SEE Test Method                          | 144 |

| 6.4     | Su  | mmary                                    | 145 |

| 6.5     | Bił | bliography                               | 146 |

| Chapter | 7.  | Conclusions and Perspectives             | 147 |

| 7.1     | Co  | nclusions                                | 147 |

| 7.2     | Peı | rspectives                               | 151 |

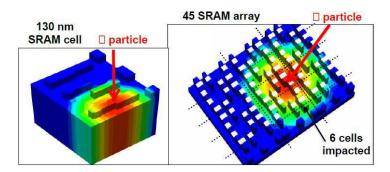

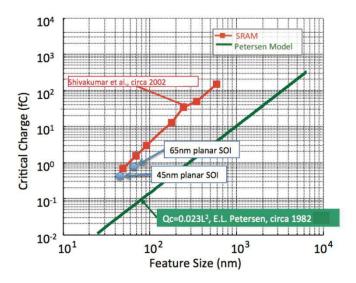

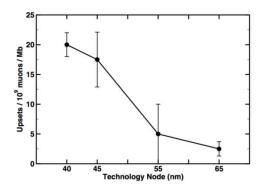

| 7.2     | 2.1 | SEE in smaller-scale process             | 151 |

| 7.2     | 2.2 | SEE evaluation by simulation             | 155 |

| 73      | Bił | bliography                               | 159 |

# Résumé

#### 1. Introduction

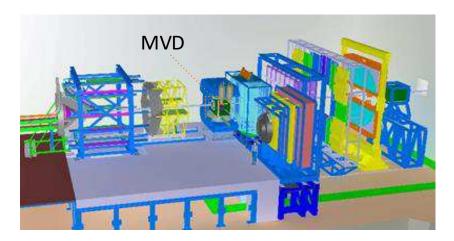

Il est prévu que l'expérience sur la matière baryonique comprimée (CBM) démarre vers 2024 auprès du complexe d'accélérateurs de particules FAIR (Facility for Antiproton and Ion Research in Europe) sur le site de GSI (Gesellschaft für Schwer Ionenforschung, Darmstadt). Son programme de recherche va consister à explorer le diagramme de phase de l'interaction nucléaire forte QCD (Quantum Chromo Dynamic) dans la région des densités baryoniques élevées en utilisant des collisions noyaunoyau à cible fixe de haute énergie ou proton-noyau. Il comprendra l'étude de l'équation d'état de la matière nucléaire à des densités élevées et la recherche du début du déconfinement et de la transition de phase chirale. Comme le montre la Figure 1, le détecteur de micro vertex (MVD) est le premier des instruments CBM, juste après la cible. Sa tâche sera de reconstruire avec une excellente résolution l'origine des différentes particules secondaires produites lors de la collision. L'instrument lui-même est composé de quatre plans de détection consécutifs, chacun équipés de capteurs mesurant la position grâce à une pixellisation d'environ 27×32  $\mu m^2$ . Pour répondre aux exigences de l'analyse physique, le MVD doit fonctionner dans le vide et présenter un très faible budget de matière d'environ 0,3% de longueur de radiation par plan.

Figure 1: Modèles 3D de l'expérience CBM, avec l'emplacement du MVD. Le faisceau arrive de la gauche.

Le capteur MIMOSIS-1 est un capteur à pixels actifs monolithique en technologie CMOS (MAPS) conçu par l'IPHC en tant que premier capteur prototype de taille réelle pour le MVD. Au-delà des fonctionnalités utiles à la physique, les conditions environnementales de fonctionnement du MVD ont dû être prises en compte dans la conception du circuit. Les particules hautement ionisantes générées par les collisions, telles que les ions or ou carbone et les protons, peuvent introduire différents effets de rayonnement dans les capteurs MVD : événements singuliers (SEE), effets de la dose ionisante totale (TID) et de la dose de dommages par déplacement. Mon objectif de thèse était de comprendre l'impact des effets SEE et TID sur les circuits de lecture du capteur, d'élaborer une stratégie de conception pour en atténuer l'impact et enfin de mettre en œuvre cette conception spécifique.

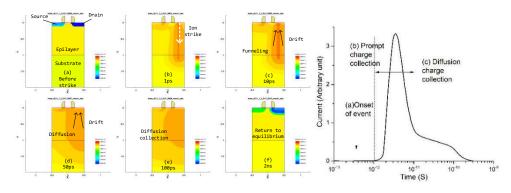

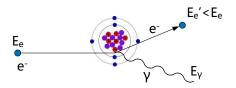

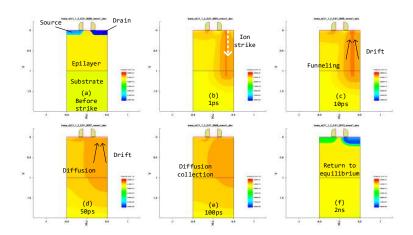

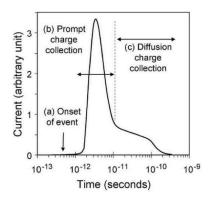

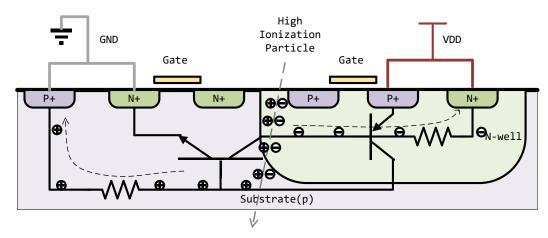

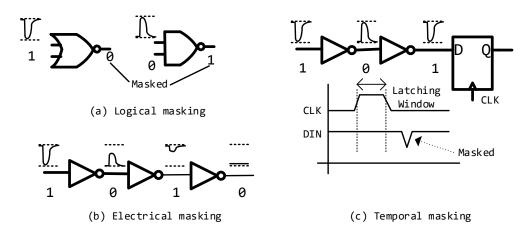

Un événement singulier est une perturbation électrique qui peut engendrer une modification du fonctionnement normal d'un circuit. La cause est liée au passage d'un seul ion à travers ou à proximité d'un nœud sensible dans un circuit. Les particules chargées perdent de l'énergie et génèrent une série de paires électrons-trous lorsqu'elles traversent le matériau semi-conducteur. Cet effet est utilisé pour détecter la particule initiale avec un nœud de collection spécifique (diode). Dans les autres micro-circuits nécessaires aux fonctionnalités du capteur, de telles paires électrons-trous déplacées par le champ électrique seront également collectées par les électrodes de circuit. Comme le montre la Figure 2, ces

charges collectées provoquent une courte impulsion de courant dans les micro-circuits qui peuvent provoquer une erreur (par exemple logique) dans leur fonctionnement. Les SEE tels que les événements provoquant un upset (SEU), l'apparition d'un courant transitoire (SET), un vérrouillage de courant ou latchup (SEL), une interruption fonctionnelle (SEFI)... peuvent entraîner des erreurs fonctionnelles temporaires ou permanentes du circuit.

Figure 2 La simulation TCAD de SEE

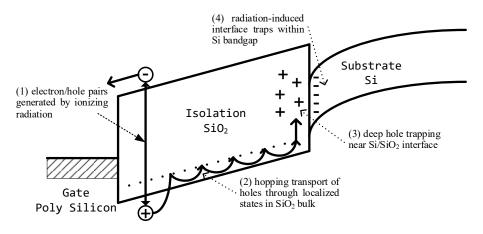

L'effet de dose ionisante totale est dû à la collecte de charges ionisées par le piégeage profond des trous près de la couche isolante et du substrat, c'est-à-dire proche des interfaces Si/SiO2 dans le MOSFET. L'effet TID peut entraîner un décalage de la tension de seuil et une augmentation du courant de fuite, ce qui peut provoquer un dysfonctionnement du circuit analogique et une augmentation de la consommation statique.

#### 2. Travail Doctoral

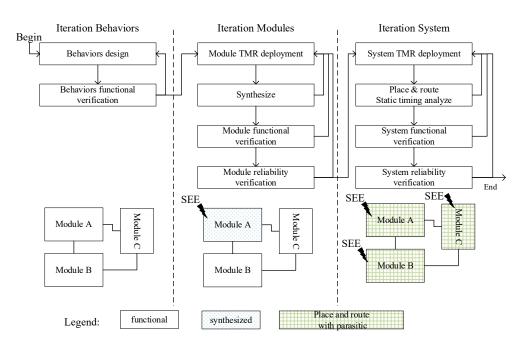

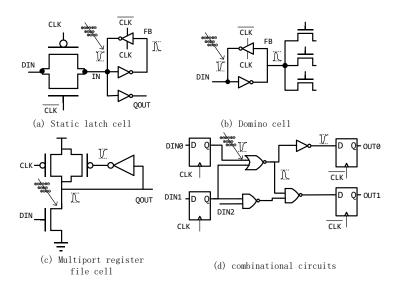

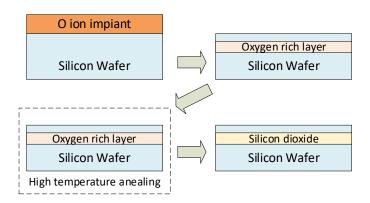

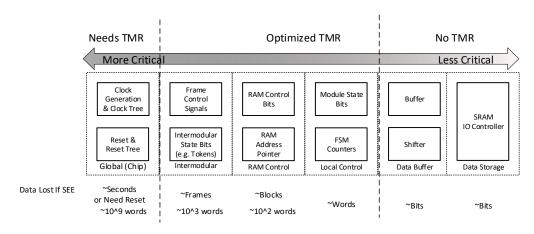

La première partie de mon travail a consisté à étudier les différentes techniques de durcissement des circuits intégrés contre les radiations. Trois méthodes peuvent être employées au niveau de la conception du système : Triple redondance modulaire (TMR), Code de correction d'erreur (ECC) et rafraîchissement et rechargement des registres. L'utilisation de transistors MOS fermés et la polarisation inverse du bulk sont des techniques de durcissement applicables au niveau de la conception de circuits. Enfin, la technologie SOI (Silicon-on-Insulator) est un procédé de fabrication qui présente une bonne tolérance aux effets d'événements singuliers. Les principes, les méthodes d'implémentations, les avantages et les inconvénients de ces différentes techniques seront discutés en détail durant

la thèse. Nous résumons ici les résultats. Le TMR est adapté aux blocs critiques et de petite taille. L'ECC est généralement utilisé pour le flux de données. Le rafraîchissement et le rechargement sont mieux adaptés aux registres de configuration et de monitoring pour protéger le flux opérationnel d'un système. Ces trois méthodes sont efficaces pour se protéger contre les SEE. L'utilisation de MOS fermés et la polarisation inverse du bulk conviennent davantage pour diminuer l'effet de dose TID. La technologie SOI peut éliminer les SEE en principe mais aurait nécessité de changer la technologie de détection déjà validée pour MIMOSIS-1 et pourrait présenté d'autres effets indésirables.

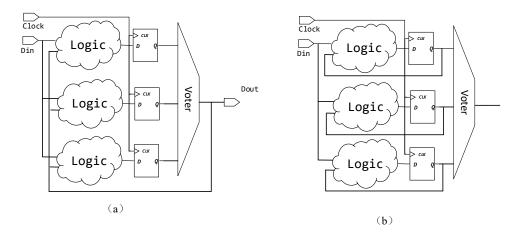

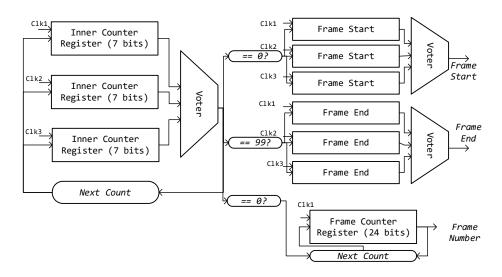

En se focalisant sur l'impact des SEE et l'effet de dose TID, deux modules de circuits critiques dans MIMOSIS-1 ont été identifiés. Le premier est le front-end gérant la lecture des données de mémoires tampons. Afin de répondre aux spécifications en termes de vitesse de lecture et de compression élevée des données, une structure à 3 couches de mémoires tampons a été proposée pour le système de lecture de MIMOSIS-1. Cette architecture permet de modifier le processus de lecture en passant d'un flux de données en rafale rapide en un flux de données séquentiel lent. Chaque couche de mémoire tampon a sa mémoire et sa logique de contrôle. L'utilisation de TMR et ECC est bien adapté pour le front-end de lecture et est décrit en détail dans la thèse. Il y a un compromis à trouver au niveau des paramètres de conception entre la fiabilité requise dans l'environnement radiatif, la surface occupée et les budgets de puissance dissipée du circuit.

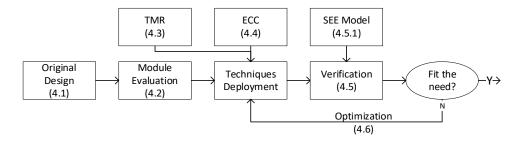

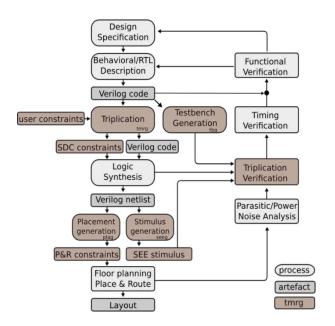

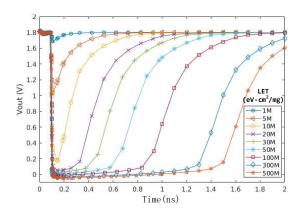

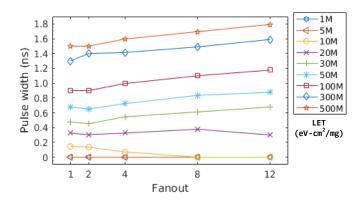

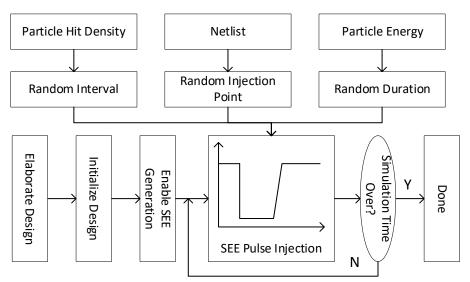

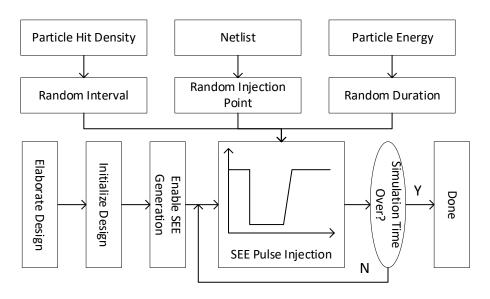

Afin de pallier maladroit de cette conception, nous proposons dans cette thèse une méthode d'optimisation de conception pour l'implémentation de TMR basée sur la simulation multi-niveaux. Pour estimer la fiabilité du circuit face aux SEE, deux grandeurs sont nécessaires : le taux de particules hautement ionisantes et la section efficace SEE du circuit. Les deux quantités consequence de grandes incertitudes puisque l'accélérateur et le capteur sont en développement. Par conséquent, l'évaluation est d'abord basée sur la section efficace connue d'un autre capteur à pixels CMOS similaire (ALPIDE) utilisé dans l'expérience ALICE, puis sur le modèle proposé dans la thèse. Les paramètres d'impulsion SEE correspondant à

différentes pertes d'énergie ionisante peuvent être obtenus grâce à une simulation TCAD basée sur les paramètres du processus de fabrication. L'outil de génération SEE peut ensuite injecter plusieurs impulsions SEE aléatoires basées sur le modèle SEE dans le circuit, alors que le système de lecture est en simulation. Grâce à l'étude statistique des résultats de la simulation, la stabilité du module subissant des SEE peut être évaluée. Avec une conception optimisée de la Figure 3, le système peut toujours fonctionner après 10<sup>7</sup> SEE, ce qui correspond à plus de cinq ans de fonctionnement du MVD. En même temps, le taux d'erreurs avec la conception durcie est réduit de 4 à 5 ordres de grandeur. De plus, le taux d'erreur de sortie de données équivalent dans l'environnement de travail est inférieur à 10<sup>-9</sup>.

Figure 3. Le processus de conception et de vérification avec le contrôle de fiabilité SEE.

Le second module critique est le circuit de génération de fréquence, principalement la boucle à verrouillage de phase (PLL). Le pilotage de MIMOSIS-1 est basé sur une logique numérique synchrone pour laquelle des horloges stables sont essentielles. Si la PLL reçoit une impulsion en sortie inattendue, cela peut amener à une période instable ou une perte de verrouillage et le circuit numérique qu'elle pilote aura de graves problèmes de fonctionnement. Dans le circuit réalisé dans ce travail, le TMR, les

transistors MOS fermés et la polarisation inverse du bulk sont implémentés. Là encore, la conception du circuit durci minimise la surface occupée et la dissipation de puissance.

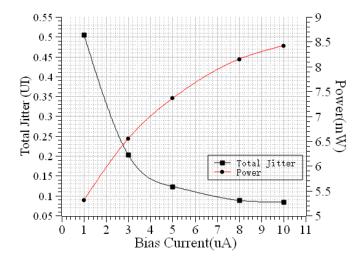

Avec une conception optimisée avec des techniques de durcissement aux radiations, le prototype PLL-1 + a une petite surface (0,115 mm²), une faible consommation de puissance (3,6 mW), un temps de verrouillage court (5us) et une fonction de détection de verrouillage. Il a un niveau de gigue total à 2% UI dans le test indépendant et 8% UI dans le test d'intégration à forte activité.

La dernière partie de cette thèse est consacrée aux méthodes de vérification du durcissement aux radiations. Afin de valider les résultats de la simulation, des tests en faisceaux sont prévus. Cependant, il est difficile de calculer directement la section efficace de la puce fonctionnelle de grande taille (MIMOSIS-1). Une autre puce d'évaluation a été conçue pour calibrer la section efficace du processus de fabrication. Les méthodes de test au SEE statique et dynamique pour la puce d'évaluation, MIMOSIS-1 et PLL-1+ ont toutes été conçues. Le test TID pour le circuit PLL-1+ est également abordé.

#### 3. Conclusion

En résumé, dans cette thèse, nous avons étudié les techniques de durcissement des circuits adaptées à l'environnement radiatif exigeant du MVD de l'expérience CBM et nous avons ensuite présenté une stratégie globale de durcissement au niveau de la conception où des contraintes supplémentaires (comme la taille des microcircuits et le budget de puissance) sont à satisfaire. La méthode est basée à la fois sur des simulations spécifiques et une évaluation du niveau critique de chaque fonctionnalité dans le circuit global.

La stratégie a été implémentée sur le premier prototype de capteur de taille finale pour le détecteur Micro Vertex de l'expérience CBM. La simulation et les résultats des tests montrent qu'il est possible de concevoir un détecteur avec des contraintes fortes pour répondre aux besoins de tolérance aux rayonnements. Les circuits numériques et analogiques fonctionnent correctement sous les effets SEE et TID grâce à la simulation.

Le procédé décrit dans cette thèse peut également être étendu à d'autres conceptions de circuits intégrés durcis aux radiations.

# Chapter 1. The MVD for the CBM experiment

This initial chapter introduces the background for the physics of the CBM experiment and the requirements on its detector, which is the source of this research work. Firstly, the physics motivation is summarized and emphasized by the exploration of the phase diagram of strongly interacting matter utilizing heavy-ion collisions at an energy scale below 5 GeV. Secondly, the chapter depicts the general concept of the CBM detector with a focus on the Micro Vertex Detector (MVD), which can achieve an excellent vertexing and tracking to reconstruct the secondary vertices and to measure precisely the momenta of tracks. With the physical requirements, high-precision vertex detector with outstanding performance in terms of flavor tagging and track reconstruction is presented. Finally, the chapter terminates with an introduction of the Monolithic Active Pixel Sensors (MAPS) that is proposed to equip the vertex detector, i.e., MIMOSIS. As the main theme of this thesis is the radiation hardness design of the MVD, the presentation will mainly focus on the context of the MVD and the necessity of radiation hardness.

# 1.1 The CBM experiment

Darmstadt's GSI Helmholtz Center will be adequately reinforced for many years to come. The new facility in construction, Future International Antiproton and Ion Research Facility (FAIR), will offer unparalleled research chances in nuclear, hadronic, atomic and plasma physics, which is a multipurpose accelerator facility, based on that will supply primary beams (protons up to 90 GeV, Uranium up to 35 AGeV, nuclei with Z/A from 0.5 up to 45 AGeV) and secondary beams (rare isotopes and

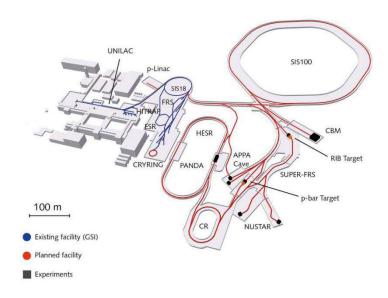

antiprotons) with high intensity and quality. The facility layout depicted in figure 1.1 consists of a double-ring synchrotron, rings for accumulation, cooling, and storage of primary and secondary beams, as well as dedicated detector arrangements. The research programs incorporate studies of nuclear matter at extreme densities, studies of nuclei far from stability, hadronic physics with antiproton beams, the investigation of plasmas induced by ion and laser beams, as well as atomic physics [1][2].

Figure 1.1 The planned FAIR facility.

#### 1.1.1 The SIS Machine

In this updated version, the SIS-18 synchrotron will be accompanied by the new SIS-100 and SIS-300 ring accelerators, both of which operate along in the same underground tunnel with a circumference of 1084 m and magnetic rigidities of 100 and 300 Tm, respectively. The floor tunnel is 17 m deep below the surface. The SIS-100 and SIS-300 accelerators can deliver beam energies of up to 11 AGeV and 35 AGeV for Au beams, respectively. Therefore, SIS-300 is anticipated to reach into the region of the highest baryonic densities. However, the great superiority of the new facility doesn't consist in the energy, but in the beam quality and intensity. Both accelerators are prospective to offer 10<sup>11</sup> ions per second and 10<sup>13</sup> protons per second [3].

The 300 Tm machine will operate at bending fields of 6 T at ramp rates of up to 1T/s. Through utilizing high charge states (e.g., U92+), heavy ion beams will be accelerated in SIS300 to energies of 35-45~GeV/u, with a maximum intensity of  $2\times10^{10}$  ions per cycle and allows to have long spills of up to 100~s while maintaining a sufficient average intensity. Moreover, SIS300 can be operated as a stretcher, and both primary and secondary (radioactive and antiproton) beams are then injected, cooled, and stored in a system of storage rings with internal targets and in-ring experiments. Based on the phase-space cooling techniques applied in the storage rings, the future program will broadly capitalize on the little emittance and low momentum spread of beams in high precision experiments.

The FAIR synchrotrons will compress heavy-ion and proton beams down to very short bunch lengths demanded for the production and subsequent storage, as well as efficient cooling of exotic nuclei (~60 ns) and antiprotons (~25 ns). With the double-synchrotron facility, continuous beams with high average intensities of up to  $3 \times 10^{11}$  ions per second are offered at energies of 1 GeV/u for heavy ions, either directly from the SIS100 or by transferring to the 300 Tm ring and slowly extracting from it. The SIS300 will supply ion beams of maximum energies around 45 GeV/u for Ne<sup>10+</sup> beams and close to 35 GeV/u for fully stripped U<sup>92+</sup> beams, respectively.

# 1.1.2 The Physics Program

Nowadays, the properties of the protons and neutrons are widely known, and the Standard Model theory and Quantum Chromo Dynamics (QCD) depict their fundamental interactions well. However, the current knowledge is still insufficient to forecast precisely the collective properties of multibody systems formed by these particles, especially in extreme conditions, for instance, in terms of temperature and pressure. The characteristics of this system currently require more in-depth theoretical and experimental research.

Of great concern is the existence of different stages of nuclear matter, among which the best known is the so-called liquid phase that is realized in the ground state of the nuclei. At a given temperature, the binding force between nucleons is not enough to maintain the stability of the nucleus, and protons and neutrons escape into a vacuum. Due to the comparability to the evaporation of a liquid, the process is explained as a phase change to a nuclear gas.

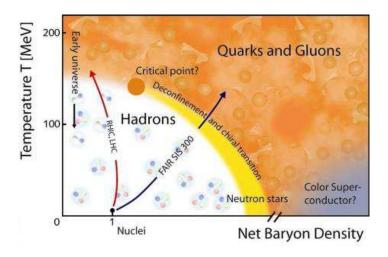

The CBM experiment parses the phase transition forecasted by QCD, which is much higher than the temperature demanded to evaporate the nucleus. This is a phase transition from a hadron matter to the so-called Quark-Gluon Plasma (QGP). If more and more energy is diverted into the hadron gas, its temperature will go up to the point where thermal excitation of nuclear resonance happens. Despite extreme conditions, the quarks of a single hadron are limited.

Figure 1.2 The phase diagram of hadronic matter as a function of the temperature (T) and the baryonic density  $(\mu_b)$  [4].

The discrepancy between the hadronic matter and QGP is defined by the emergence of a deconfinement of quarks. It is predicted that such deconfinement will result in dramatically high particle density, which will bridge the distance between the quarks of adjacent hadrons compared with the quarks that form the hadrons. In these circumstances, the "potentials" of hadrons merge, allowing the quarks to move freely among the conventional "potentials" [5].

In QGP, the distance between disparate hadrons becomes shorter due to high compression or strong particle generation towing to high temperature, which leads to the potential occurrence of single hadrons. In the potential of merging, the quarks of adjacent hadrons also attract quarks. In consequence, the barrier is weakened in the neighboring direction. At some point, the barrier between hadrons falls below the particle generation limit. As a result, a confined quark may now leave its partners and move towards the neighboring hadron. If the hadron density is high enough, the quark can be regarded as a quasi-plasmid-free equal to the conduction electrons in the metal. So far, this matter has reached the state of QGP.

# 1.1.3 The subdetectors of CBM Experiment

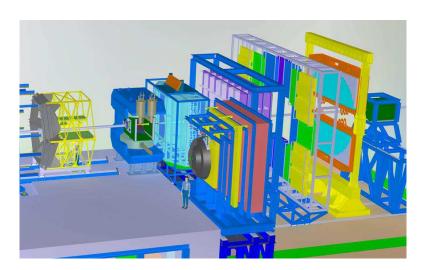

The CBM detector is devised with a fixed-target setup. A variety of subsystems is used to cover a wide range of possible heavy-ion studies at FAIR. The detector acceptance covers polar angles of 2.5°- 25° with full azimuthal coverage. It is necessary for the electronic components to be radiation hard to sustain the expected radiation dose. Besides, the sensors and support materials need to be constructed as thin as they can be to lessen multiple scattering. Moreover, fast operating sensors are required to support the highest beam intensities.

Figure 1.3 Structure of CBM detectors

The nucleus of the experiment will be a silicon tracking and vertex detection system installed in a large acceptance dipole magnet. The Micro-Vertex Detector (MVD) is required to determine high-precision secondary vertices for *D* meson recognition. The MVD consists of two layers of ultra-

thin and highly granular Monolithic Active Silicon Pixel Sensors (MAPS), located near the target.

The Silicon Tracking System (STS) is composed of a low material quality silicon microstrip detector and may be replenished by one or two layers of hybrid-pixel detectors to supply precise spatial point measurements. STS can execute track reconstruction over a wide range of momentum from about 100 MeV to over 10 GeV with a momentum resolution of about 1%.

The Ring Imaging Cherenkov (RICH) detector (for momenta < 8-10 GeV/c) together with Transition Radiation Detectors (TRD) (for momenta > 1.5 GeV/c) will be utilized for the survey of electrons. Muons will be measured by using an active hadron absorber system composed of an iron layer and a Muon Tracking Chamber (MuCh). For muon measurements, MuCh will take place in the RICH position. Charged hadron identification will be executed by a time-of-flight (TOF) detector. The Electromagnetic Calorimeter (ECAL) will offer information about photons and neutral particles. The Projectile Spectator Detector (PSD) is required for the measurement of the collision centrality and the orientation of the reaction plane.

# 1.2 The Micro Vertex Detector (MVD)

To illustrate the potential physics mechanisms of newly observed processes, the authentication of impact particles will play a crucial role. The Micro Vertex Detector (MVD) is the indispensable tool to achieve very high-performance particles tagging by reconstructing displaced vertices, and also plays a critical role in the track reconstruction, particularly for low momentum particles that do not reach the central tracker or barely penetrate its sensitive volume.

# 1.2.1 Requirements

The MVD requirements are mainly motivated by two competing sources of constraints: the physics goals and the running conditions.

The open charm physics program at CBM dominantly relies on D-mesons, which will be reconstructed by way of their hadronic decay

channels  $D^0 \to K^- + \pi^+$  and  $D^0 \to K^- + \pi^+ + \pi^+$ . Among the addressed D-mesons, D<sup>0</sup> is deemed to be the most difficult to reconstruct. The lifespan of the D-mesons is  $c\tau = 123.0 \ \mu m$  for  $D^0$  and  $c\tau = 311.8 \ \mu m$  for D<sup>±</sup>. Since the lifespan of charm mesons does not allow them to reach a detector, they must be reconstructed by detecting their daughter particles. Consequently, the design guidelines for the Mini Vertex Detector (MVD) and CBM's STS are based on the requirements determined by the observed object. The relatively low production multiplicity of open charm mesons raises additional requirements, that is an intense beam is required to produce a sufficient number of those particles in a reasonable amount of time. On the target, CBM's estimated collision speed is 10<sup>7</sup> collisions per second and approximately 10% of these hits can be regarded as central hits. The CBM physics goals dictate an unprecedented spatial three-dimensional point resolution and a very reduced material budget. At the same time, high granularity and fast readout compete and are inclined to increase the power dissipation, which will result in an augmented material budget in turn.

Table 1.1 The specifications of the MVD for CBM

| Requirement                 | Goal                        |

|-----------------------------|-----------------------------|

| Spatial resolution          | $5\mu m$                    |

| Material budget             | $0.3\% - 0.5\%X_0$          |

| Detection efficiency        | 99.5%                       |

| Hit rate (peak)             | $7.5 \times 10^7 hits/cm^2$ |

| Time resolution             | 50μs                        |

| Ionizing radiation hardness | 50 <i>KGy</i>               |

| (Without safety factor)     |                             |

| Non-ionizing radiation      | $10^{14}n_{eq}/cm^2$        |

| hardness                    |                             |

For purpose of detecting individual particles and their attenuation topologies, it is necessary to reconstruct the particle tracks passing through various sites of the silicon detector. Superconducting dipole magnets with a magnetic field of up to 1T will bend the tracks of the charged particles so that their momentum can also be reconstructed. An isolation envelope with

dimensions of  $1400 \times 2000 \times 1100 \, mm^3$  is needed to separate the tracking stations from the magnet, and the MVD will be placed in a vacuum vessel, but the vacuum environment is not conductive to the heat dissipation of electronic components. If it were not for the help of air convection, components would only dissipate heat through radiation and PCB conduction. Hence, designing additional heat dissipation structures is compulsory. However, this requirement goes against the low mass quality. A compromise solution is needed to balance these requirements.

#### 1.2.2 Geometries

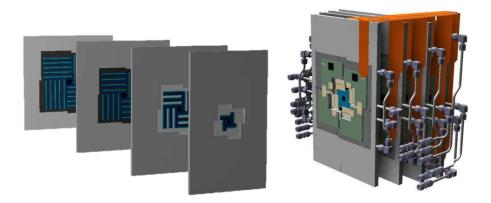

As shown in Figure 1.4, the MVD for CBM is composed of 4 stations of detectors and both sides of a station layer will attach detectors, distributed around the middle hole, where the beam will pass through. The front stations deploy fewer detectors than the rear stations, which means the front stations have a higher dose rate.

Figure 1.4 The geometry of MVD for CBM.

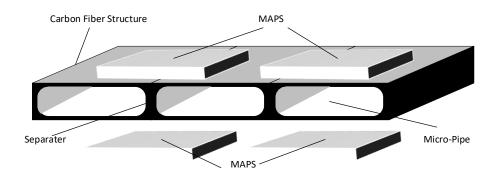

The design of station support is dictated by the cooling requirements and the material budget. As the equipment will be placed in a vacuum, it is necessary for the layer support to be designed as a part of the cooling system. As a result, in a vacuum, heat must be removed by heat conducting or liquid cooling. As shown in Figure 1.5, the support of the layer station is composed of carbon fiber material. Between two layers of carbon fiber material, there is a layer of "micro-pipes", which is mainly realized by

liquid cooling and some separator walls, and the latter is utilized to ensure mechanical stability. [6]

Figure 1.5 Cross-section of the proposed vertex detector station. Only some MAPS chips are shown for clarity. In reality, they are intended to match as close as possible.

# 1.2.3 The predicted particle environment for MVD

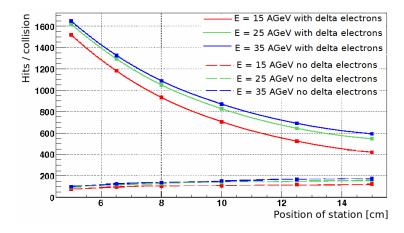

Figure 1.6 indicates the average number of hits in an MVD detector station as a function of its distance from the target, which comes from a detailed GEANT simulation study of Au + Au collisions at disparate incident energies. The dashed line illustrates the collision result of only the particles formed in the nuclear collision, and the solid line comprises delta electrons that shot down from the target by an electron beam [7].

Figure 1.6 The average number of hits on one MVD detector station per Au+Au collision as a function of the position of this station. Two cases are shown: with (full lines) and without (dashed lines) the inclusion of the contribution of delta electrons (see text). Three different incident energies were studied: 15, 25 and 35 AGeV [7]

From Figure 1.6, it can be known that if incremental electrons are deleted from the analysis, the average number of hits per collision will be less than 200 and will be completely independent of the station's position (dashed line). On the other hand, when delta electrons are not excluded, for a station located 5 cm (solid line), the average number of hits per collision prevails, reaching 1600 hits/collisions, which means that the number declines as the distance from the target increases. On account of these results, it can be summarized that at such a high hit density (up to 3.5 hits/mm²/collision), it is very fundamental to use a silicon pixel detector with high granularity.

The strong particle flux expected on the MVD will induce a considerable radiation dose, particularly for sites close to the target [6]. The expected ionizing and non-ionizing radiation doses in CBM experiments have been assessed through system simulation[6][8], which are normalized to a typical CBM operating year, assuming that the effective persistence of the operating year (i.e., the target beam) is about  $5 \times 10^6 s$  (about two months). Assuming a nominal beam intensity of  $10^9$  beams per second and an interaction possibility in the target of 1%, it can be anticipated that approximately  $5 \times 10^{13}$  collisions will happen during this period.

The non-ionizing doses provoked by different particles are calculated by means of the NIEL factor, which normalizes the radiation damage caused by 1 MeV neutrons [9]. For the ionizing dose, it is assumed that all charged particles are minimum ionizing particles. It has been found that at 25 AGeV, for each Au + Au collision, the ionizing and non-ionizing radiation doses hitting the MVD detector station can reach  $0.7 \,\mu Gay$  and  $30.2 \, n_{eq}/cm^2$ , respectively.

In order to meet the requirements for MVD radiation hardness, the numbers must be normalized according to the beam intensity. CBM will operate in two main phases: the first starts with the measurement of the SIS-100 synchrotron and the second begins with SIS-300, comprising the open charm measurement in the A+A collision. Currently, as for the second stage of SIS-300, it is anticipated that CBM-MVD will be used to conduct two stages of open charm measurement. The requirements for the detector

will be lower in the first phase and will be upgraded in the second. Due to diverse technical limitations, which will be discussed later in this thesis, it appears to be reasonable to operate the first generation MVD at a collision rate of about  $10^5$  collisions/sec. In the circumstances, the initial version of CBM-MVD on the SIS-300 should be able to withstand  $10^{13} n_{eq}/cm^2$ , and each CBM runs for approximately 30KGray [10].

## 1.3 The introduction of Sensors for MVD

With the continuing advance of semiconductor technology, silicon detector technology is persistently improved. In high-energy physics applications, silicon detectors show the advantages of high speed, small size, and high integration. Back in the early 1960s, silicon was used in radiation detection applications to replace gas detectors, which marked a revolution in particle physics experiments [11], because the moderate bandgap energy of silicon (~ 1.2 eV) is neither too high to generate a large number of charge carriers by ionized particles, nor too low to prevent large leakage currents from generating electron-hole pairs. Complementary Metal Oxide Semiconductor (CMOS) is a production process based on ideas emerging in the 1960s and prevailing in today's electronics market. The foundation is the Metal-Oxide Semiconductor Field Effect Transistor (MOSFET), which is a primary element in all modern electronic devices.

#### 1.3.1 Introduction into semiconductors

Pure silicon with negligible impurities, i.e., intrinsic silicon, has the same number of electrons and holes. The attributes of silicon can be adjusted by doping other additional elements in the intrinsic material. Donors (e.g., As, P, or Sb) are introduced into intrinsic silicon, resulting in electrons increasing to form n-type silicon. Likewise, acceptors (e.g., Al, Ga, or Sn) cause holes to form p-type silicon, and both n-type and p-type materials are called extrinsic semiconductors. External doping introduces additional energy levels into the material. In consequence, by adjusting the doping type and concentration, the electrical nature of silicon can be intentionally changed.

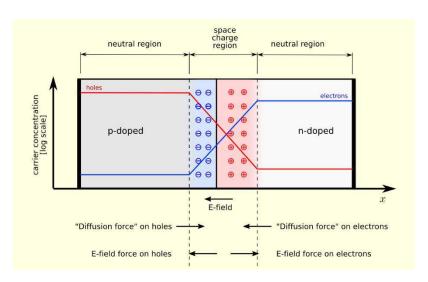

Figure 1.7. PN junction with zero bias thermal equilibrium. The electron and hole concentrations are indicated by blue and red lines, respectively. The gray area is electrically neutral. Bright red areas are positive, and bright blue areas are negative. The electric field is shown at the bottom. Electrostatic forces act on electrons and holes and their diffusion orientation [12].

As the most crucial structure in a semiconductor device, a p-n junction is constructed by joining two opposite doping types extrinsic semiconductors together. Diodes are easy to implement by using p-n junctions. As a two-terminal device, the feature of the diode is that in the case of an external voltage bias is applied, the current can only be conducted in one direction. For the sake of diode characterization, the analysis begins with the diode reaching thermal equilibrium. In the state of thermal equilibrium, the distribution of electrons and holes is consistent. Nevertheless, once the two semiconductors are connected, the discrepancy in concentration will bring electrons to diffuse from n-type silicon to ptype silicon, while holes will diffuse in opposite directions. The ionized donor retained in n-type silicon and the ionized acceptor in p-type silicon will have the consequence the building of an electric field, which will counteract the diffusion of electrons and holes. When the diffusion is compensated by the electric field, the diode is in dynamic thermal equilibrium and a neutral region without moving carriers is shaped as a depletion region. The depletion region of the diode can assemble the free charge generated very quickly. So, the reverse-biased diodes are implemented as charge collection nodes for silicon detectors.

#### 1.3.2 Introduction to silicon sensors

When passing through matter, charged particles lose energy by interacting with the electromagnetic fields inside the atoms and scattering with electrons and nuclei, which is described quantitatively in [13]. As the valence electrons are loosely combined with the silicon atom, the impacting particle generates an electron-hole pair cloud along its path. The charge carriers diffuse around until they lose the residual energy and recombine. If they were collected before the recombination, impacting particles could be detected. In a silicon detector, electron-hole pairs formed by incident charged particles are collected by an electrode. The travel of these charged carriers is controlled by the built-in electric field (drift) and the distribution (diffusion) of non-uniform charge carriers. Both mechanisms affect charge collection.

The principle of silicon detectors leans upon collecting the charges from incident particles, so fast signal response and high charge collection efficiency are fundamental. In the depletion region, drift is the elementary mechanism in the motion of charge carriers, which is more rapid and has less possibility of charge trapping compared with diffusion. Therefore, full depleted silicon detectors are favored for particle detection. Nevertheless, the use of fully depleted structures is commonly restricted by operational circumstances. The width W of the depletion region is estimated as

$$W = \sqrt{\frac{2\varepsilon_S}{q} \left(\frac{1}{N_A} + \frac{1}{N_D}\right) V_b} \tag{1.1}$$

In the equation,  $\varepsilon_s$  is the relative dielectric permittivity of the semiconductor,  $N_A$  and  $N_D$  is the doping spatial densities and q is the electron charge. As described in Eq. (1.1), the width W of the depletion region is proportional to the square root of the reverse-biased voltage  $V_b$ . For the sake of full depletion of the silicon, an external high voltage is required, but this high voltage is normally unavailable in the standard CMOS process owing to the limitation in breakdown voltage. Furthermore, the additional high voltage distributed to each sensor complicates the design of detectors. As a result, partial depletion is ordinary in silicon

detectors, such as in CMOS pixel sensors (CPS). In partially depleted silicon, drift is merely available in the vicinity of the anode of a diode. As the impurities present in the silicon bulk could trap charge carriers, the quantity of the collected charge depends on the carrier's lifespan. The longer charge collection time, the more loss of charge carriers. The different mechanisms in charge carrier's collection will affect charge collection time. In fully depleted detectors, charge collection time depends on the strength of the electric field, while in partially depleted ones, diffusion constant and doping concentration contribute mainly to charge collection time. Typically, a partially depleted n-type silicon with a thickness of 300  $\mu$ m and 10  $\mu$ m and 10  $\mu$ m resistance value has a typical charge collection time of approximately 30–90 ns, three times longer than that of the fully depleted structure.

#### 1.3.3 The Pixel Sensors for MVD

With the advance of physics and the progress of various High Energy Physics (HEP) experiments, various types of silicon detectors have been proposed and established, including strip detectors, hybrid pixel detectors, DEPleted Field Effect Transistor (DEPFET) detectors, and Monolithic Active Pixel.

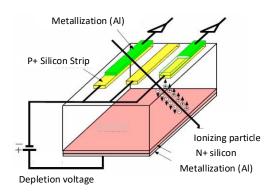

## • The strip detectors

The strip detectors are the first detector devices using the lithographic capabilities of microelectronics, which can be found in all high energy physics experiments of the last two decades. As shown in figure 1.8, the detector utilizes the arrangement of strip implants acting as charge collecting electrodes, placed on a low doped fully depleted silicon wafer; these implants create a one-dimensional array of diodes. A position-sensitive detector is built by connecting each of the metalized strips to a charge sensitive amplifier, and two-dimensional position measurements can be implemented by applying additional strip-like doping on the wafer backside (double-sided technology).

Figure 1.8 The principal of the silicon strip detector.

The structure of the silicon strip detector is simple and easy to implement, has also clear issues. Since the silicon strip detector can only tell one dimension of information at a time, the high particle fluences ambiguities create difficulties for the track reconstruction. In consequence, deriving the point resolution from just one coordinate is not enough information to reconstruct a secondary vertex.

## • Hybrid Pixel Sensor (HPS)

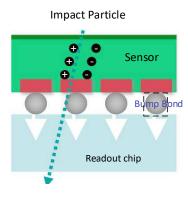

Meanwhile, pixel detectors allow track reconstruction at high particle rates without ambiguities. The Hybrid Pixel Sensor (HPS) is a classical idea for HEP as shown in figure 1.9, where the readout chip is mounted directly on top of the pixels by bump-bonding. Now that each pixel has its own readout amplifier, as there are two wafers, we can choose the appropriate process for sensor and readout chip separately. Due to the parallel working of the readout channels, the readout speed is very fast, and the separated wafers help to gain a high radiation tolerance performance.

Figure 1.9 The Principal of Hybrid Pixel Sensor

The defect of HPS is that the pixel area is defined by the size of the readout chip. Generally, the readout part is larger than the sensor part, which limits the improvement of spatial resolution. Another shortcoming is that because there are two chips, the material budget is high, and it is the same with the power consumption.

#### DEPFET Sensor

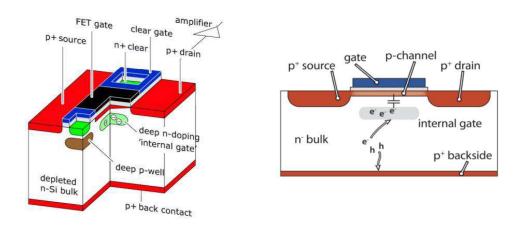

A DEPFET Sensor is composed of a field-effect transistor (FET) placed on the uppermost part of a high resistivity n-type completely depleted silicon bulk. As shown in figure 1.10, deep n-doping implantation, the "internal gate," situated under the transistor channel (around 1 μm below), generates a minimum of potential for the electrons. [14]

Figure 1.10 Sketch of a DEPFET pixel and the internal gate location.

The electrons generated by the incident particles are collected by the internal gate, and the transistor channel current is regulated by the internal gate potential changes. When the electrons on the internal gate need to be reset, a positive voltage pulse will be applied to the transparent gate.

The DEPFET has a higher amplification factor because of collecting the charges by its gate instead of the active part (source or drain). The internal gate also results in the disadvantage of weak radiation hardness, which is hard to manufacture in an industrial process. The reset of the internal gate requires a high power, which sets the limitation for high integration.

### Monolithic Active Pixel Sensor (MAPS)

With the continual advance of deep-well technology and double well technology, it is feasible to integrate signal sensing and readout electronics on a homogeneous substrate. In 2000, researchers of the LEPSI and IReS came up with a Monolithic Active Pixel Sensor (MAPS) for charged particle tracking and imaging, which have offered an attractive balance among granularity, material budget, radiation tolerance, and readout speed[15] [16].

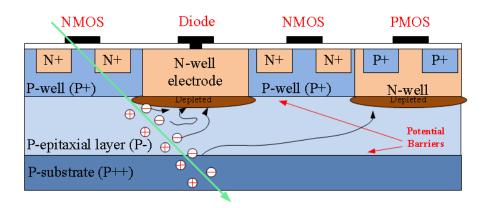

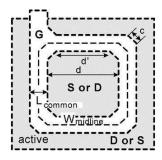

As shown in figure 1.11, the first generation of MAPS has been made of a photodiode by the P-N junction created between the N-well and the epitaxial layer (P-type). The doping level of the P well (P + type) and the P substrate (P ++ type) is higher than that of the epitaxial layer (P-type), bringing about two potential barriers. The first potential barrier is situated in the boundary region between the epitaxial layer and the P-well, and the second, in the boundary area between the epitaxial layer and the P substrate.

Figure 1.11: The principal of the first-generation MAPS structure.

When charged particles cross the MAPS detector, the energy emitted by the particles will be converted to e-/hole pairs, normally generating about 80 electron-hole pairs per micrometer. The electrons generated in the epitaxial layer thermally diffuse and converge at the N-well collector electrode. Owing to the high level of P-type doping, more electrons produced in the substrate will recombine, and only a few electrons will be transferred to the epitaxial layer and collected by the collection electrode.

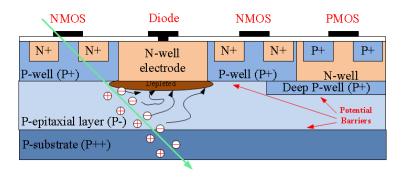

In the first-generation MAPS structure, only NMOS transistors could be used in pixels, because of N-wells that would host PMOS transistors would compete for charge collection with N-well / P-epi diodes. To avert this, the solution is to use a deep P-well in the P substrate to segregate the N-well from the epitaxial layer or substrate in the second-generation structure, as shown in Figure 1.12. The deeper P-well prohibits the N-well from collecting electrons, so a full CMOS process can be used in pixels [15][17][18].

Figure 1.12: The principal of the second-generation MAPS structure.

The MAPS structure was used for the first time in the vertex detector upgrade of the STAR (Solenoidal Tracker at RHIC) experiment at RHIC (Relativistic Heavy Ion Collider). The ALPIDE utilized in the ALICE experiment is a monolithic pixel sensor that is manufactured in the 180 nm CMOS imaging sensor process of TowerJazz, which achieves detection efficiency above 99%, a power consumption less than  $40 \, mW/cm^2$ , and a dimensional resolution of around 5 µm. These characteristics meet the excessive requirements of the ALICE experiment, even after neutron irradiation to  $1.7 \times 10^{13} \, n_{eq}/cm^2$  at 1 MeV [19].

Table 1.2: Advantages and disadvantages of various detector technologies

| Technology     | Advantages                  | Disadvantages          |  |

|----------------|-----------------------------|------------------------|--|

| Strip detector | Large area possible         | Expensive cost         |  |

|                | Fast speed                  |                        |  |

| Hybrid pixel   | Low detector capacitance    | Large power            |  |

|                | Low leakage current         | consumption            |  |

|                | large signal-to-noise ratio | Expensive cost         |  |

|                | High radiation-hard         |                        |  |

|                | High Readout Speed          |                        |  |

| DEPFET         | Integrated amplification    | Only small devices     |  |

|                | Low power consumption       | Not radiation-hard     |  |

|                | Low noise                   | High power at reset    |  |

|                | Fast readout speed          | No industry standard   |  |

| MAPS           | Standard IC process         | Moderate Readout Speed |  |

|                | Integrated amplification    | Moderate radiation     |  |

|                | Low noise                   | tolerance              |  |

|                | Low power consumption       |                        |  |

|                | High spatial resolution     |                        |  |

#### Conclusions

In consideration of the low material budget, low power consumption, and high spatial resolution requirements mentioned above, a MAPS-based detector is more appropriate for CBM-MVD application scenarios than other types of detectors. The MAPS process is based on the standard IC process with only one thin wafer used, which makes it easy to manufacture and has very low material quality. With the limitation of lower power consumption, it still has high spatial resolution and moderate readout speed, as well as certain radiation resistance under the current process, but it still needs to be optimized.

#### 1.4 The MIMOSIS in MVD for CBM

The MIMOSIS is now being devised as the CMOS pixel sensor in the MVD for the CBM experiment. The elementary design of the pixel's matrix is based on the ALPIDE sensor [14], which has been developed for the ALICE ITS upgrade. Nevertheless, the rate capability and the radiation

tolerance of MIMOSIS have to be drastically beyond the ones of ALPIDE, which have introduced the need for a dedicated CPS design [20].

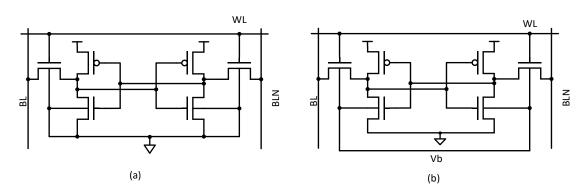

# 1.4.1 Design of the Pixel

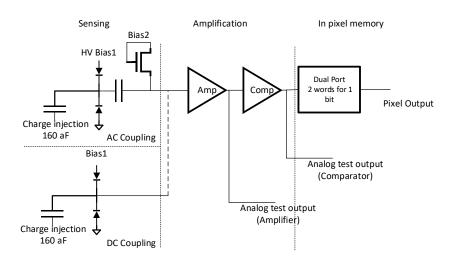

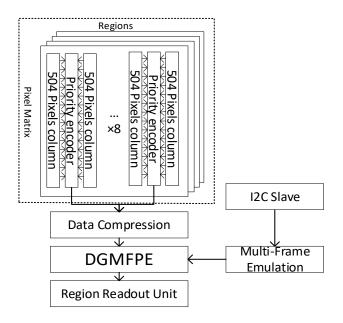

MIMOSIS leans upon the TOWER/JAZZ 180 nm quad-well technology, which allows to integrate a complete amplifier-shaper-discriminator chain into each pixel. The pixel matrix will comprise 1024 columns of 504 pixels with a size of  $26.88 \times 30.24 \, \mu m^2$ , and the block diagram of its layout is shown in Figure 1.13. The DC-coupled version of the pixels is inspired by ALPIDE's related pixels. Nevertheless, different from ALPIDE, which is optimized for triggering, MIMOSIS will run in a constant readout according to CBM requirements. Hence, the trigger logic is substituted by a different type of sample-and-hold logic, which will hold the potential signal for a frame time. This adjustable frame time is controlled by the global shutter signal, which is 5 µs by default. Once the global shutter reaches the pixel, the result of the sample-and-hold circuit will shift to the output buffer and clear the circuit. In the general case where the timeout threshold of a pixel goes beyond the frame time, digital edge detection will be used to avert double counting, which is necessary because, compared with earlier MIMOSA sensors, the readout rate of the MIMOSIS is extremely high. [21] This mechanism helps to minimize the data rate.

Figure 1.13 Block diagram of the pixel of MIMOSIS.

Besides the DC version, it is also considered to equip MIMOSIS with the AC-coupled pixel version, which is shown in Fig.1.13. Both pixels are analogical, but the transistor of the amplifier on the pixel of the AC pixel can be preserved from depletion voltage by a capacitor. As a result, the depletion voltage of the collection diode is not constrained by the voltage that can be accepted on the gate of the transistor and can be incremented up to +40V while keeping the active medium at the mass potential. AC pixels are compatible with the modified 180 nm TOWER/JAZZ process, which is optimized for enhanced depletion [22] and is anticipated to significantly fortify the sensor's radiation tolerance.

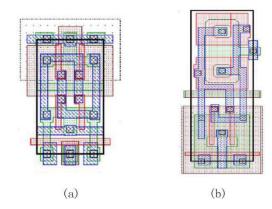

#### 1.4.2 Buffer structure

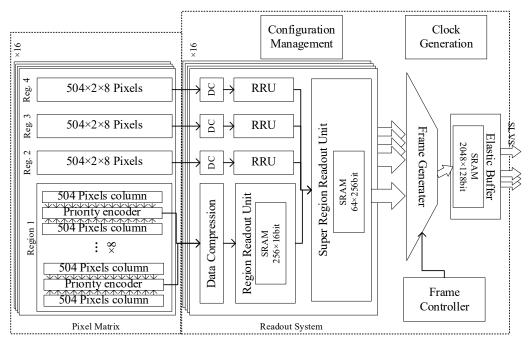

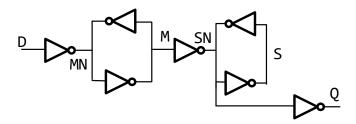

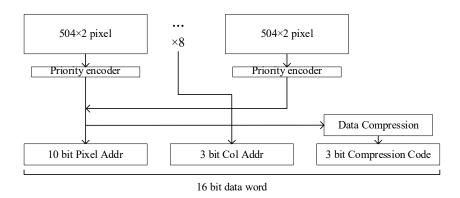

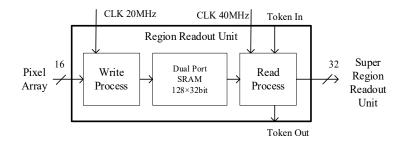

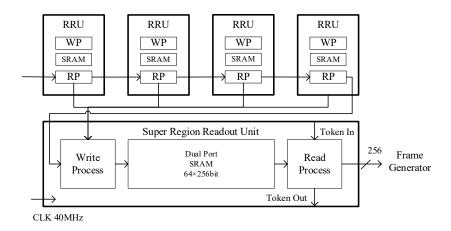

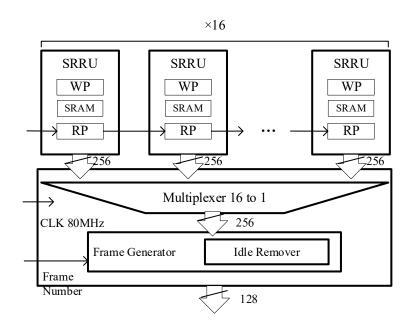

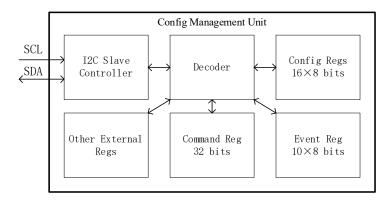

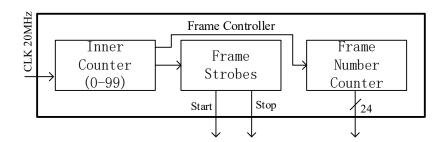

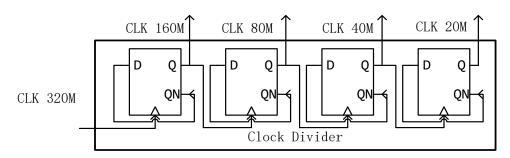

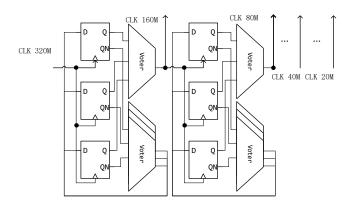

As shown in figure 1.14., the buffer structure of MIMOSIS must meet the requirement to read any record hits without reducing the data rate under the help of a trigger system. The reading of pixels is performed by a priority encoder, which works for two columns at a reading frequency of 20 *MHz*. The time resolution of the system is subject to the frame length, and the latter is expected to be 5 µs. Other values can be chosen within some restrictions at the cost of reducing the hit rate capability. The maximum number of hits recorded from the double column is consistent with the number of clock cycles within the frame time. If the number of hits surpasses this number, the unread hits will be abandoned.

The data of eight double columns will be supplied to a so-called region buffer by way of a data compression unit that identifies groups of up to four adjacent emission pixels in the reading order, which corresponds to a cluster found within the double-column, but it is not applicable to identify clusters spanning more than one double-column. The region buffer is devised as a double buffer, where one element applies a 16bit × 20 MHz bus to read the priority-encoded data from the double column, and the second buffer writes the data of the antecedent frame to the next level. The region buffer adds a dedicated "region" header, which decreases the number of bits required to encode the number of matching columns. The depth of the region buffer is 100 words, consistent with the theoretical maximum output of a single double-column, but it is usually shared among

these columns. This sharing symbolizes the first average of fluctuations in occupancy rates incurred by Poisson fluctuations.

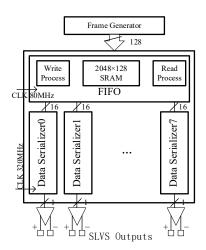

Fig. 1.14. MIMOSIS functional organization, with the three layers buffer (RRU, SRRU, and Elastic Buffer).

The 16 super regions converge data from the four regions through a 32-bit  $\times$  40 MHz bus with priority encoded with a depth of 256 words, whose purpose is to load balance and prepare data for transmission by way of the 256bit  $\times$  40 MHz main bus. The bus will transmit data to a central elastic buffer through the idle word removal. The intention of idle words removal is to eliminate possible idle words, which are created to fill messages with a width of more than 16 bits in the bus. Up to 3200 words can be processed every 5  $\mu$ s, and the data is thereby written to the elastic buffer with an input bandwidth of 3200 words per 5  $\mu$ s and depth of 16384 words, which is enough to store the peak data rate corresponding to 5 frames. The elastic buffer constitutes the key element of time and space load balance, which transmits data to up to 8 adjustable 320 Mbps output buffers. In the case of low data load, the number of output buffers can be decreased to save power and material budget for routing.

# 1.4.3 The development schedules

The final MIMOSIS sensor will be built through a dedicated R&D program, which is currently regarded to comprise three prototype submissions.

The first prototype, MIMOSIS-0, was presented in 2018, and both electrical function and radiation tolerance are tested. The sensor comprises 16 double columns, each with  $2\times504$  pixels, half of which are realized by AC and the other half by DC coupling. A priority encoder for pixel readout and a DAC needed for pixel control is carried out. A dedicated number of pixels can be read through an exclusive analog readout line, which allows direct observation of the analog signal in the extensive chain within the pixel. The test results indicate that both AC and DC coupling pixels sense with low noise, allowing the threshold to be set to <150 e, and the noise can be further decreased by applying a slight reverse bias of -1 V to the pwell structure. The pulse shape and length of the amplification chain within the pixel were studied, and it was summarized that it is conceptually adequate to achieve a time resolution of  $\sim$ 1  $\mu$ s combined with a lead time of  $\sim$ 10  $\mu$ s, which is quicker than the ideal frame time 5  $\mu$ s.

The second prototype, MIMOSIS-1, was submitted with in 2020 and is now under testing. MIMOSIS-1 is the first reticle size prototype with full  $1024 \times 504$  pixels. In this thesis, we will mainly discuss the design of radiation hard structures in these prototypes.

The final prototype is MIMOSIS-2, which will mainly correct the errors in MIMOSIS-1. Moreover, new modifications could be brought to this prototype if the radiation resistance does not meet the requirements of MVD.

# 1.5 The strategy and focus of this work

The main target of this thesis is to find an appropriate radiation harden design method for MVD. The backdrop and motive of the thesis have been shown in the first chapter, which explains the objective, requirements and detector composition of the CBM experiment, the principle, structure,

manufacture processing, working environment and the urgent radiation requirements of the MVD.

In the second chapter, the mechanism of radiation and its effect on CMOS detector (single event effects, total ionizing dose, and displacement damage) will be introduced in detail, and then the principles and trade-offs of the main methods of radiation harden design will be described in Chapter 3. Afterwards, there will be two part of the detailed design. The first part (chapter 4) is the data buffer in the readout circuit, which symbolized the design method of the digital circuit. The second part (chapter 5) is the phase-locked loop, which is used to generate the clock for the system and represents the analog part. The sixth chapter is the test design and results of the previous two parts, including electrical performance test and radiation tolerance test. Finally, there is the summary of this thesis and the prospect of the future work direction.

# 1.6 Bibliography

- [1] P. Senger, The CBM experiment at FAIR, J. Phys. Conf. Ser. 50, (2006) 357.

- [2] GSI "The Machine" https://www.gsi.de/en/researchaccelerators/fair/the\_machine.htm (26 February 2020).

- [3] P. Spiller, The Superconducting SIS100 Synchrotron for High Intensity Proton and Heavy ION Beams, in HB 2008 42nd ICFA Adv. Beam Dyn. Work. High-Intensity, High-Brightness Hadron Beams, (2008).

- [4] *Phasendiagram.jpg* (460×310)https://fias.uni-frankfurt.de/~hossi/Bilder/BR/Plotl/Phasendiagram.jpg (27 February 2020).

- [5] G. Rosner, Future Facility: FAIR at GSI, Nucl. Phys. B Proc. Suppl. 167, Elsevier, (2007) 77.

- [6] M. Deveaux, Development of fast and radiation hard Monolithic Active Pixel Sensors (MAPS) optimized for the D 0 detection with the CBM vertex detector, Building, (2007).

- [7] C. A. Dritsa, Design of the Micro Vertex Detector of the CBM experiment: Development of a detector response model and feasibility studies of open charm measurement, (2011) 207.

- [8] D. Bertini, Radiation dose simulations, CBM Collab. Meet., (2009).

- [9] A. Akkerman, J. Barak, M. B. Chadwick, J. Levinson, M. Murat and Y. Lifshitz, Updated NIEL calculations for estimating the damage induced by particles and γ-rays in Si and GaAs, Radiat. Phys. Chem. 62, Pergamon, (2001) 301.

- [10] M. Deveaux, S. Amar-Youcef, N. Bialas, D. Doering, M. Domachowski, H. Düring, I. Fröhlich, T. Galatyuk, J. Michael, et al., *Status of the Micro Vertex Detector of the Compressed Baryonic Matter Experiment*.

- [11] G. Lutz and G. Lutz, *Introduction*, in *Semicond. Radiat. Detect.*, Springer Berlin Heidelberg, (2007).

- [12] W. Shockley, The Theory of p-n Junctions in Semiconductors and p-n Junction Transistors, Bell Syst. Tech. J. 28, (1949) 435.

- [13] M. Tanabashi, K. Hagiwara, K. Hikasa, K. Nakamura, Y. Sumino, F. Takahashi, J. Tanaka, K. Agashe, G. Aielli, et al., *Review of Particle Physics*, in *Phys. Rev. D* **98**, American Physical Society, (2018).

- [14] M. Boronat, *DEPFET pixel detector for future e-e+ experiments*, *Nucl. Part. Phys. Proc.* **273–275**, Elsevier B.V., (2016) 982.

- [15] R. Turchetta, J. D. Berst, B. Casadei, G. Claus, C. Colledani, W. Dulinski, Y. Hu, D. Husson, J. P. Le Normand, et al., *Monolithic Active Pixel Sensor for charged particle tracking and imaging using standard VLSI CMOS technology, Nucl. Instruments Methods Phys. Res. Sect. A Accel. Spectrometers, Detect. Assoc. Equip.* 458, Elsevier Science B.V., (2001) 677.

- [16] C. Hu-Guo, J. Baudot, G. Bertolone, A. Besson, A. S. Brogna, C. Colledani, G. Claus, R. De Masi, Y. Degerli, et al., *CMOS pixel sensor development: a fast read-out architecture with integrated zero suppression*, *J. Instrum.* 4, (2009) P04012.

- [17] W. Snoeys, CMOS monolithic active pixel sensors for high energy physics, Nucl. Instruments Methods Phys. Res. Sect. A Accel. Spectrometers, Detect. Assoc. Equip. 765, Elsevier, (2014) 167.

- [18] C. Cavicchioli, P. L. Chalmet, P. Giubilato, H. Hillemanns, A. Junique, T. Kugathasan, M. Mager, C. A. Marin Tobon, P. Martinengo, et al., Design and characterization of novel monolithic pixel sensors for the ALICE ITS upgrade, Nucl. Instruments Methods Phys. Res. Sect. A Accel. Spectrometers, Detect. Assoc. Equip. 765, Elsevier, (2014) 177.

- [19] G. Aglieri Rinella, The ALPIDE pixel sensor chip for the upgrade of the ALICE Inner Tracking System, Nucl. Instruments Methods Phys. Res. Sect. A Accel. Spectrometers, Detect. Assoc. Equip. 845, Elsevier, (2017) 583.

- [20] M. Deveaux, B. Arnoldi-Meadows, G. Bertolone, G. Claus, A. Dorokhov, M. Goffe, A. Himmi, K. Jaaskelainen, P. Klaus, et al., *Observations on MIMOSIS-0, the first*

### Chapter 1. The MVD for the CBM experiment

- dedicated CPS prototype for the CBM MVD, Nucl. Instruments Methods Phys. Res. Sect. A Accel. Spectrometers, Detect. Assoc. Equip. 958, (2020).

- [21] M. Deveaux, B. Arnoldi-Meadows, G. Bertolone, G. Claus, A. Dorokhov, M. Goffe, A. Himmi, K. Jaaskelainen, P. Klaus, et al., *Observations on MIMOSIS-0, the first dedicated CPS prototype for the CBM MVD*, *Nucl. Instruments Methods Phys. Res. Sect. A Accel. Spectrometers*, *Detect. Assoc. Equip.* **958**, (2020) 1.

- [22] W. Snoeys, G. Aglieri Rinella, H. Hillemanns, T. Kugathasan, M. Mager, L. Musa, P. Riedler, F. Reidt, J. Van Hoorne, et al., A process modification for CMOS monolithic active pixel sensors for enhanced depletion, timing performance and radiation tolerance, Nucl. Instruments Methods Phys. Res. Sect. A Accel. Spectrometers, Detect. Assoc. Equip. 871, Elsevier B.V., (2017) 90.

# Chapter 2. The Radiation Effects on CMOS Sensors

In 1947, J. Bardeen, W. Brattain, and W. Shockley invented the semiconductor transistor, taking the lead in a new era in semiconductor microelectronics. In 1959, J.S. Kilby invented the first solid-state integrated circuit, which turned out to be a milestone in the history of microelectronics. From then on, the microelectronics industry has experienced tremendous progress over the past 40 years, particularly in the development of the performance of products (i.e., integrated circuits), while considerably reducing the manufacturing costs through fundamental integrated functions. The persistent decrease in the silicon surface occupied by these essential components retains the speed of integration at speed stipulated by the famous "Moore's Law," which states that the number of transistors per integrated circuit will duplicate every 18 to 24 months.

Dating back to the early 1960s, research done at the U.S. Naval Research Laboratory (NRL) has shown that MOS devices were sensitive to radiation. Prior to this, there were thoughts that MOS transistors (most-carrier devices) were not as sensitive to radiation as bipolar transistors. At that time, MOS devices were used in the first reconnaissance satellite around the world by NRL due to their high-impedance input and low current characteristics. By using  $\gamma$ -ray radiation from the Cobalt-60 source mainly for the passive oxide layer of the bipolar transistor, NRL began the study of the surface effect mechanism incurred by radiation.

As the dimension of the MOSFET decreases, it has been found that the sensitivity of integrated circuits to radiation from natural spaces or ground environments will be enhanced dramatically [1][2][3]. Nowadays, for processes that extremely scaled down, natural radiation is one of the reasons for the highest malfunction rate among all equipment and circuit reliability issues in the field of nanoelectronics [4][5].

# 2.1 Basic Radiation Mechanism on Silicon Sensors and Integrated Circuits (IC)

In order to understand the radiation effect caused by the collision of incident particles with the silicon semiconductor, we need first to grasp its physical process. The interaction between a particle and a substance is usually depicted by a single collision between the incident particle and one in the matter. The incident particles are mainly considered to be electronspositrons, protons, and ions, and the reference material can be an intrinsic semiconductor material, i.e., silicon.

# 2.1.1 Electrons and positrons

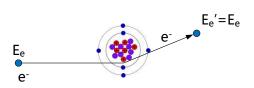

#### • Elastic collisions

Elastic collisions, caused by the Coulomb interaction of electrons with the nuclear field, have for consequence changes in the direction of electron and positron motion, but are not responsible for energy loss. Thus, this part will not cause ionization.

Figure 2.1 Diagram of electronic elastic collision. The electrons are scattered by the nucleus, leaving their energy almost unchanged.

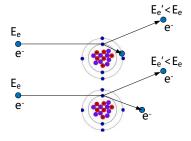

#### Inelastic collisions

Inelastic collisions and the emission of braking radiation will lead to the loss of energy from electrons (and positrons) in the matter, and this is the

primary energy loss mechanism for low to medium energy impact particles (up to 10 MeV). Inelastic scattering is the consequence of the Coulomb interaction between incident electrons and atomic electrons. Some of the energy and momentum of the incident electron is transferred into the target system, and the final state of the interaction can contain not only single-electron excitation or atomic ionization (accompanied by the generation of electron-hole pairs), but also many atoms in the solid [6].

Bethe [7] first obtained the quantum mechanical computation of inelastic collision based on the Born approximation. Special calculations for the particular cases of incident electrons and positrons will respectively bring about the theory of electron energy loss and the special formulas of Møller and Bhabha [8] for inelastic electron-positron scattering. The energy loss of the electron/positron can be expressed as

$$-\frac{dE}{dx} = K \frac{Z}{A} \frac{1}{\beta^2} \left[ \ln \left( \frac{\tau^2(\tau+2)}{2(I/m_e c^2)} \right) + F(\tau) - \delta - 2 \frac{C}{Z} \right]$$

(2.7)

In the formula,  $\tau$  is the kinetic energy of the particle in units of  $m_e c^2$ ,  $\delta$  is the density correction, C gives the shell correction, Z and A are the number of protons and nucleus,  $\beta$  is the speed in unit of c, and  $F(\tau)$  is different for electrons and positrons. For a detailed treatment of the energy loss of electrons and positrons, see also [9][10]. Section 2.1.3 incorporates energy loss formulae for protons and ions, besides the pertinent definitions of stopping power.

The energy loss caused by ionization can also be contrasted with the radiative component of electron energy loss so that the relative significance of the two energy loss mechanisms can be assessed based on the electron energy.

Figure 2.2 Diagram of inelastic electron collisions leading to atomic excitation or ionization.

#### • Braking radiation (Bremsstrahlung)

Electrons and positrons that pass-through substance undergoes deceleration and emit radiation when they interact with the electrostatic field of the atom. This effect is called bremsstrahlung or braking radiation, as shown in Figure 2.3.

At medium energies, without screening, the energy loss can be approximated as [10]

$$-\frac{dE}{dx_{Brem}} = 4Nr_e^2 \alpha Z^2 \left( \ln \frac{2E}{m_e c^2} - \frac{1}{3} - f(Z) \right)$$

(2.8)

and at high energies, for complete screening, as

$$-\frac{dE}{dx_{Brem}} = 4Nr_e^2 \alpha Z^2 \frac{E}{m} \left( \ln \frac{183}{Z^{1/3}} + \frac{1}{18} - f(Z) \right)$$

(2.9)

In the formula, If the logarithmic term is neglected, the energy loss rate can be approximately equivalent to the energy of the incident electron:

$$-\frac{dE}{dx_{Brem}} = \frac{E}{X_0} \tag{2.10}$$

In the formula,  $X_0$  is the radiation length and represents the distance over which radiative emission decreases the initial projectile energy by a factor 1/e. The dependence on 1/m makes braking radiation emission much more significant for electron than that for more massive particles such as muons, protons or ions, while the dependence on  $Z^2$  makes it extremely significant for high-Z materials, with important consequences for shielding strategies.

Figure 2.3 Diagram of the electron-induced radiation emission process. The electron emits a photon by the deceleration induced by the atomic electrostatic field.

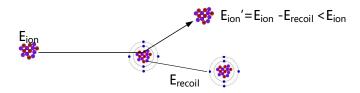

#### 2.1.2 Protons and ions

Finally, the effects for protons and ions passing through matter can be summarized as particle deceleration (energy loss) and deflection. The main interactions that lead to these effects are elastic collisions with atomic nuclei and inelastic collisions with atomic electrons in the matter.

#### • Elastic collisions

The elastic scattering of protons and ions in matter occurs because of the interaction with the nuclei of the matter shielded by the electron cloud. This process is the same as the elastic scattering of electrons mentioned above, and the main discrepancy is the non-negligibility of the mass of the projectile. Although the total kinetic energy is retained, the kinetic energy has been partially transferred from the projectile to the target core.

Figure 2.6 Diagram of the elastic electromagnetic interaction of an incident ion with a target atom, screened by the electron cloud, with the transfer of part of the energy to the target nucleus.

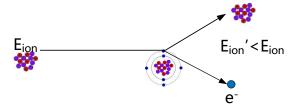

#### Inelastic collisions

Ion electromagnetic inelastic collisions are interactions of the incident ions with the field of the atomic electrons in the matter, the result of which is the excitation or the ionization of the target atom.

Figure 2.7 Diagram of inelastic electromagnetic interaction of incident ions with electrons of the target atoms, inducing atomic excitation or ionization.

# 2.1.3 Energy loss, linear energy transfer and stopping power

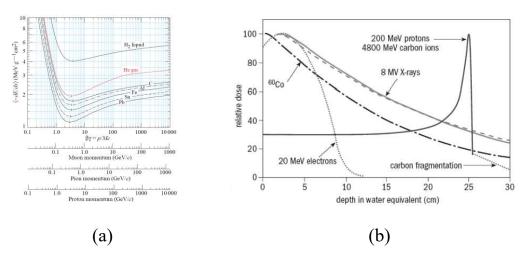

Stopping power is the average energy loss per unit path-length as a charged particle passes through a material, for which the typical units are MeV/cm or  $KeV/\mu m$ . What can also be ignored is the dependence of the stopping power on material density with reference to mass stopping power, providing the average energy loss per unit areal mass, for instance,  $MeV \ cm^2/mg$ .

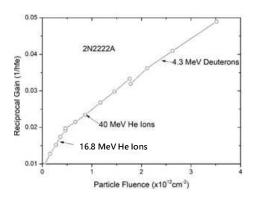

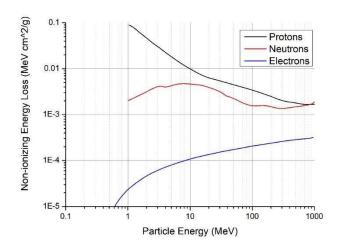

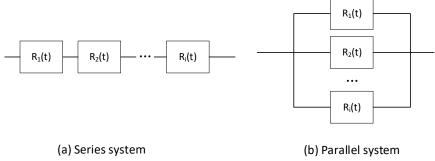

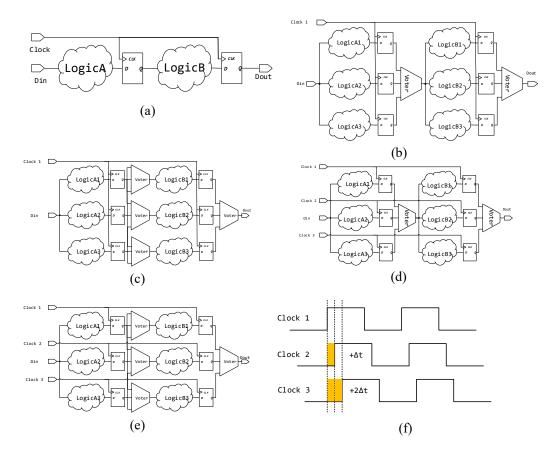

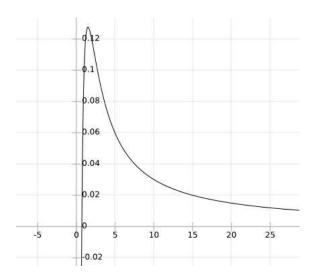

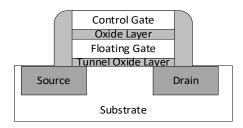

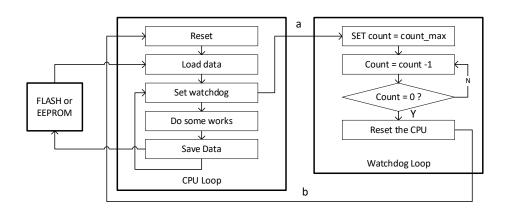

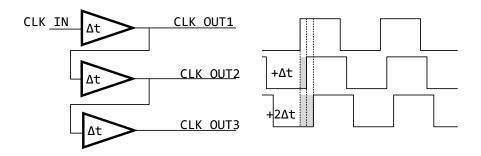

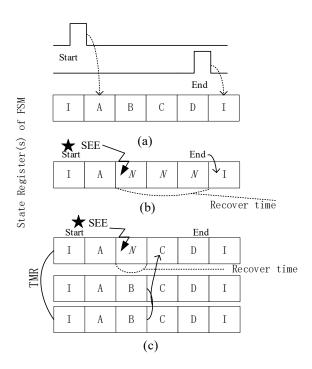

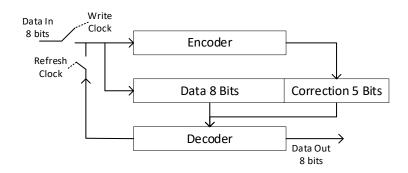

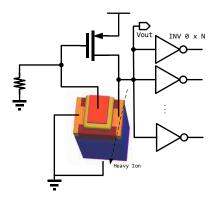

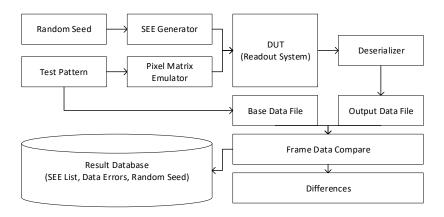

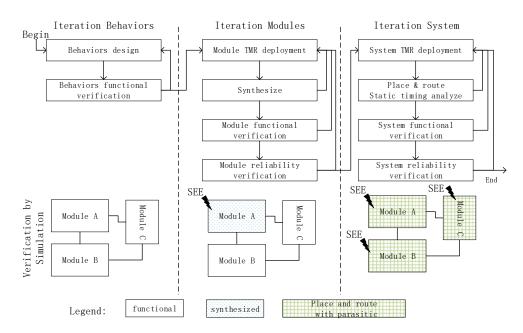

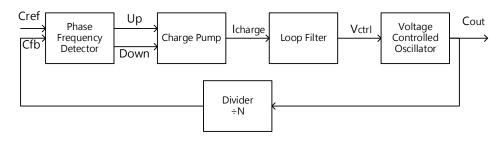

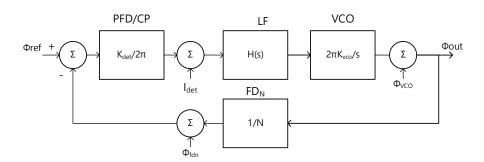

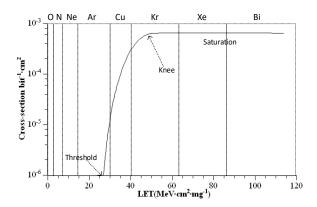

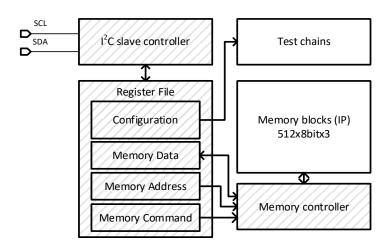

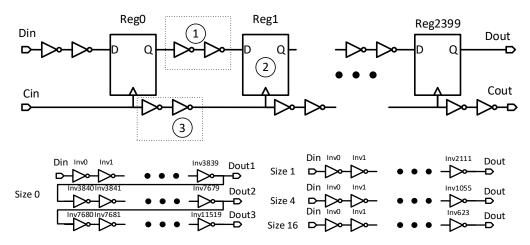

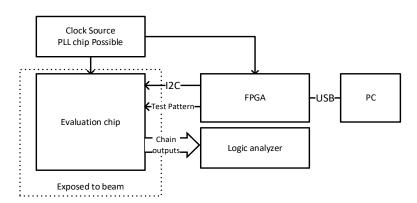

Generally due to the inelastic interaction of the projectiles with the field of the electrons in the target nucleus, a major part of the energy loss of electrons and ions in a material is widely known as electronic stopping power or linear energy transfer (LET). The quantity of energy transferred to the electrons in each collision for ions is a small fraction of the projectile energy, but the number of collisions in media of average density is high, giving rise to a significant loss of kinetic energy. Collisions with a finite transfer of energy are described as soft, while less frequently hard collisions occur, which cause atomic excitation with the ejection of energetic, fast electrons (often referred to as  $\delta$ -rays). The part of the electronic stopping power that does not contain the production of  $\delta$ -rays above a given threshold  $\Delta$  is denominated as restricted stopping power.