#### New hardware platform-based deep learning co-design methodology for CPS prototyping: Objects recognition in autonomous vehicle case-study

Quentin Cabanes

#### ▶ To cite this version:

Quentin Cabanes. New hardware platform-based deep learning co-design methodology for CPS prototyping: Objects recognition in autonomous vehicle case-study. Other [cs.OH]. Université Paris-Saclay, 2021. English. NNT: 2021UPASG042. tel-03287903

#### HAL Id: tel-03287903 https://theses.hal.science/tel-03287903

Submitted on 16 Jul 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# New hardware platform-based deep learning co-design methodology for CPS prototyping: Objects recognition in autonomous vehicle case-study

Nouvelle méthodologie de co-conception pour de l'apprentissage en profondeur basée sur une plate-forme matérielle pour le prototypage de SCP: reconnaissance d'objets dans une étude de cas de véhicule autonome

#### Thèse de doctorat de l'université Paris-Saclay

École doctorale n°580 : Sciences et Technologies de l'Information et de la Communication (STIC)

Spécialité de doctorat : Informatique

Unité de recherche : Université Paris-Saclay, UVSQ, LISV,

78124, Vélizy -Villacoublay, France.

Référent : Université de Versailles -Saint-Quentin-en-Yvelines

Thèse présentée et soutenue à Paris-Saclay, le 07/06/2021, par

#### **Quentin CABANES**

#### **Composition du Jury**

#### **EI-Bey BOURENNANE**

Professeur des Universités, Université de Bourgogne

#### **Dong Seog HAN**

Professeur, Kyungpook National University

#### **Nicole LEVY**

Professeure des Universités, Conservatoire National des Arts et Métiers (CEDRIC)

#### **Akash KUMAR**

Professeur, Technische Universität Dresden

#### Président

Rapporteur & Examinateur

Rapporteuse & Examinatrice

Examinateur

#### Direction de la thèse

**Amar RAMDANE-CHERIF**

Professeur, UVSQ (LISV) **Benaoumeur SENOUCI**

Maître de conférences, ECE Paris

Directeur de thèse

Co-Encadrant

NNT 2021UPASG042

### Acknowledgements

I would like to sincerely thank my supervisors, Dr Benaoumeur Senouci and Pr Amar Ramdane-Cherif, for their help and contribution during this work.

I would also like to thank the members of the jury, who accepted to evaluate my work.

A big thanks to all the ECE Paris lab team for their help and support during this thesis.

I would like to thank Alain Houelle for his review and advices.

A special thanks to my partner, Anaïs, who was by my side during that tumultuous time, and to Nikki, who proofread my thesis.

Finally, a big thanks to my family for believing in me all this time and helped me achieve all these projects.

## Contents

| 1        | Ger                    | neral Introduction 11                                                        |    |  |

|----------|------------------------|------------------------------------------------------------------------------|----|--|

|          | 1.1                    | Introduction                                                                 | 12 |  |

|          | 1.2                    | Context and Motivations                                                      | 12 |  |

|          | 1.3                    | Problematics                                                                 | 15 |  |

|          | 1.4                    | Thesis Contributions                                                         | 16 |  |

|          | 1.5                    | Thesis Outline                                                               | 18 |  |

| <b>2</b> | Cyl                    | er-physical systems and embedded artificial intelligence                     | 21 |  |

|          | 2.1                    | Introduction                                                                 | 22 |  |

|          | 2.2                    | Cyber-physical systems design                                                | 22 |  |

|          | 2.3                    | .3 Hardware accelerators for smart cyber-physical systems                    |    |  |

|          | 2.4                    | 4 Artificial intelligence in cyber-physical systems                          |    |  |

|          | 2.5                    | 3D object detection and recognition for CPS                                  | 27 |  |

|          |                        | 2.5.1 3D vision techniques using 2D/3D sensors                               | 27 |  |

|          |                        | 2.5.2 Software deep learning for 3D object detection and recognition $2.5.2$ | 28 |  |

|          |                        | 2.5.3 Hardware acceleration of 3D object detection and recognition ap-       |    |  |

|          |                        | plication                                                                    | 29 |  |

|          | 2.6                    | Design and prototyping time of a hardware accelerated object detection       |    |  |

|          |                        | and recognition application for CPS                                          | 30 |  |

|          | 2.7                    | Conclusion                                                                   | 31 |  |

| 3        | $\mathbf{A}\mathbf{n}$ | embedded Deep Learning methodology for hybrid CPU/FPGA-                      |    |  |

|   | base | ea Cyb          | er-Physical Systems platform design using a nardware Neural                  |    |  |

|---|------|-----------------|------------------------------------------------------------------------------|----|--|

|   | Net  | twork Processor |                                                                              |    |  |

|   | 3.1  | Introduction    |                                                                              |    |  |

|   | 3.2  | Hybrid          | d CPU/FPGA platform                                                          | 37 |  |

|   | 3.3  | A stan          | dard process for HW/SW co-design prototyping                                 | 38 |  |

|   | 3.4  | HW/S            | W co-design methodology in the deep learning AI era                          | 41 |  |

|   |      | 3.4.1           | Understanding the standard workflow for deep learning algorithms .           | 41 |  |

|   |      | 3.4.2           | Exploration of deep learning inside a $\mathrm{HW/SW}$ co-design application | 43 |  |

|   |      | 3.4.3           | Prototyping automation tools for hybrid CPU/FPGA platforms $$                | 46 |  |

|   | 3.5  | Propos          | sed embedded Deep Learning methodology around a FPGA-based                   |    |  |

|   |      | Neural          | Network Processor                                                            | 49 |  |

|   |      | 3.5.1           | The methodology design flow                                                  | 49 |  |

|   |      | 3.5.2           | Toward the automation of the design flow                                     | 53 |  |

|   | 3.6  | Challe          | nges of deep learning in hybrid CPU/FPGA-based CPS $\ \ldots \ \ldots$       | 54 |  |

|   | 3.7  | Conclu          | ısion                                                                        | 56 |  |

| 4 | Λh   | andrua          | re Neural Network Processor: core of the methodology                         | 57 |  |

| 4 |      |                 | <del></del>                                                                  |    |  |

|   | 4.1  |                 | uction                                                                       | 58 |  |

|   | 4.2  | Neural          | Network Processor                                                            |    |  |

|   |      | 4.2.1           | Definition                                                                   | 58 |  |

|   |      | 4.2.2           | Design and Architecture                                                      | 59 |  |

|   |      | 4.2.3           | Validation of the NNP                                                        | 67 |  |

|   | 4.3  | NNP i           | ntegration into the full prototype                                           | 69 |  |

|   |      | 4.3.1           | Embedded processing to improve performance                                   | 69 |  |

|   |      | 4.3.2           | Control software for reconfiguration purposes                                | 70 |  |

|   |      | 4.3.3           | Workflow of an application using the NNP                                     | 74 |  |

|   | 4.4  | Experi          | mentation and results                                                        | 75 |  |

|   | 4.5  | Concl           | ision                                                                        | 79 |  |

| 5            | Imp                                        | dementation and validation: a smart LIDAR for pedestrian detec- |     |  |

|--------------|--------------------------------------------|-----------------------------------------------------------------|-----|--|

|              | tion                                       |                                                                 | 81  |  |

|              | 5.1                                        | Introduction                                                    | 82  |  |

|              | 5.2                                        | Autonomous Vehicle Case Study: Description                      | 82  |  |

|              | 5.3                                        | Design of the application                                       | 83  |  |

|              | 5.4                                        | Experimentations                                                | 86  |  |

|              |                                            | 5.4.1 Embedded processing algorithms                            | 87  |  |

|              |                                            | 5.4.2 Deep learning algorithms                                  | 96  |  |

|              |                                            | 5.4.3 Implementation and results                                | 97  |  |

|              | 5.5                                        | Conclusion                                                      | 102 |  |

| 6            | Gen                                        | neral conclusion and future works                               | 105 |  |

|              | 6.1                                        | General conclusion                                              | 106 |  |

|              | 6.2                                        | Future works                                                    | 109 |  |

| A            | Syst                                       | temC source code of the Neural Network Processor                | 113 |  |

| В            | Ten                                        | sorflow source code for Dense Neural Network topologies         | 123 |  |

| $\mathbf{C}$ | Tensorflow source code for SUOD dataset 12 |                                                                 |     |  |

| D            | Rés                                        | umé de thèse                                                    | 133 |  |

## List of Figures

| 1.2 | Past and future evolution toward automated and cooperative driving                         | 14 |

|-----|--------------------------------------------------------------------------------------------|----|

| 1.3 | Thesis outline                                                                             | 17 |

| 2.1 | Cyber-physical systems architecture                                                        | 23 |

| 3.1 | Methodology global view around embedded DL                                                 | 36 |

| 3.2 | Hybrid CPU/FPGA platform with DRAM                                                         | 38 |

| 3.3 | $\rm HW/SW$ co-design prototyping for hybrid CPU/FPGA-based platform $$                    | 39 |

| 3.4 | V-model: $HW/SW$ co-design prototyping based on hybrid $CPU/FPGA$                          |    |

|     | platform                                                                                   | 40 |

| 3.5 | Deep learning classification standard steps                                                | 43 |

| 3.6 | $\rm HW/SW$ co-design prototyping for a hybrid CPU/FPGA-based Deep learn-                  |    |

|     | ing application. Compared to the previous methodology (Figure 3.3): the                    |    |

|     | deep learning requirements are added inside the software requirements,                     |    |

|     | the data processing and feature calculation are added inside the hardware                  |    |

|     | requirements, the model training and testing is added between the host                     |    |

|     | application and host code compiler, and the model parameters are added                     |    |

|     | before the host executable                                                                 | 44 |

| 3.7 | Design flow diagram for a hybrid $\mathrm{CPU}/\mathrm{FPGA}\text{-based HW/SW}$ co-design |    |

|     | deep learning software application                                                         | 45 |

| 3.8 | Application Tasks Graph                                                                    | 46 |

| 3.9 | Prototype automated deployment                                                             | 47 |

| 3.10 | Our methodology implementation. The differences with previous method-         |    |

|------|-------------------------------------------------------------------------------|----|

|      | ology (Figure 3.6) are: the addition of the NNP IP integration and the        |    |

|      | removal of a host software development and compilation                        | 50 |

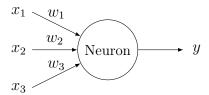

| 4.1  | Neuron in a neural network                                                    | 59 |

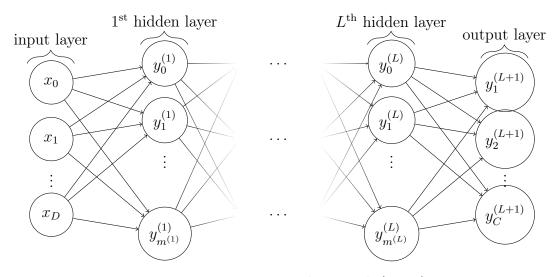

| 4.2  | Dense Neural Network (DNN)                                                    | 60 |

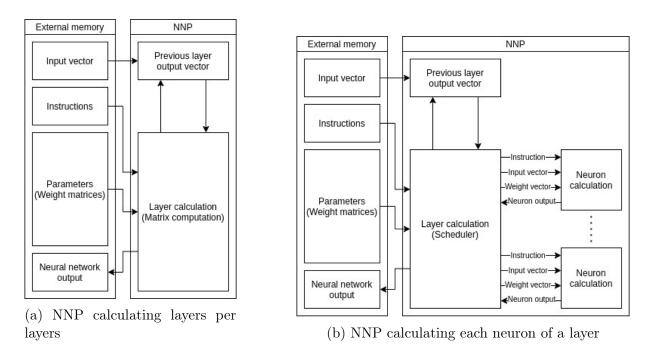

| 4.3  | Data and tasks representations of a NNP                                       | 61 |

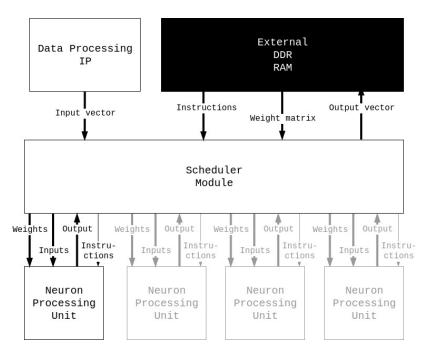

| 4.4  | NNP data flow with 4 cores                                                    | 64 |

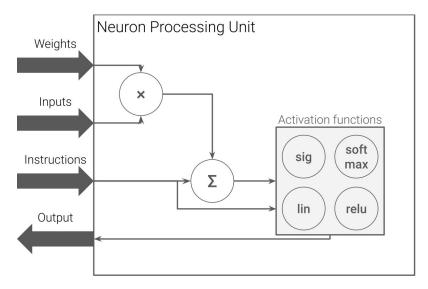

| 4.5  | Neuron processing unit architecture. The weights, inputs and output ar-       |    |

|      | rows represents 32-bit floating points                                        | 66 |

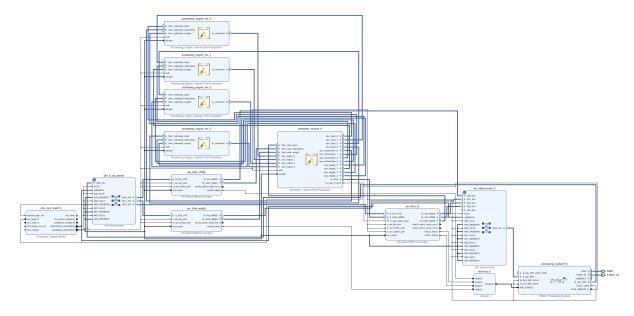

| 4.6  | Vivado diagram of our NNP using the PS/PL with three DMA and the              |    |

|      | scheduler connected to four neural processing unit                            | 69 |

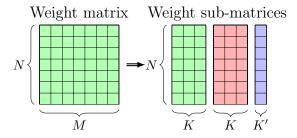

| 4.7  | Splitting the weight matrix into sub-matrices with their size depending on    |    |

|      | the number of cores. $N$ is the number of neurons in the current layer. $M$   |    |

|      | is the number of neurons in the next layer. $K$ is the number of neuron       |    |

|      | processing unit. $K'$ is the size of the last sub-matrix, with $K' \leq K$    | 71 |

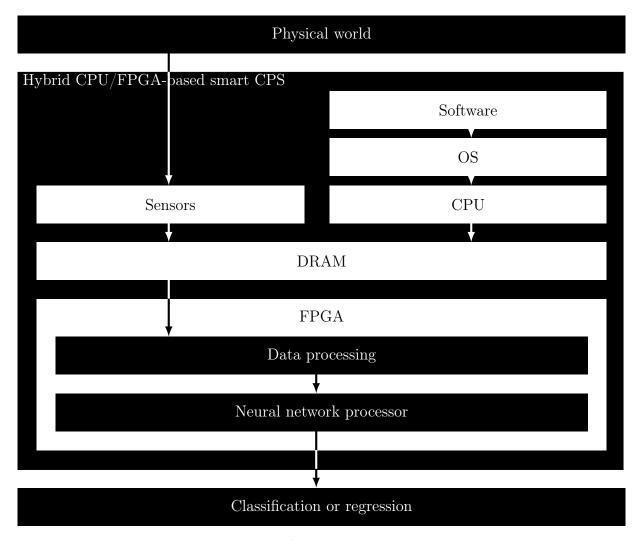

| 4.8  | Hybrid CPU/FPGA-based smart CPS workflow                                      | 74 |

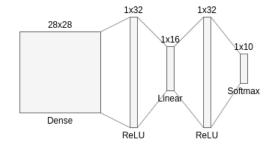

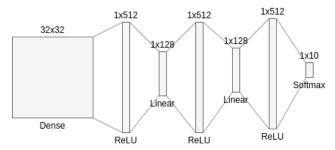

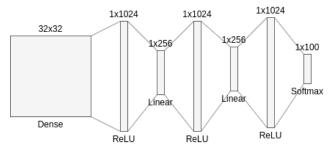

| 4.9  | DNN Topologies for each Dataset                                               | 76 |

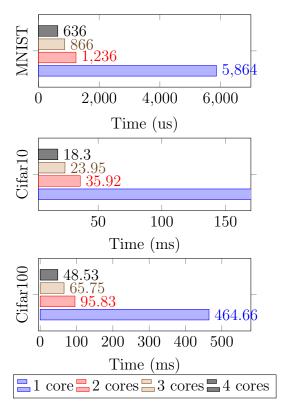

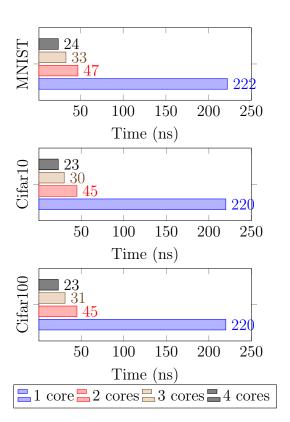

| 4.10 | Tests results of the NNP, the execution time is for one feed forward sequence | 78 |

| 4.11 | Execution time per parameter with different number of cores and topologies    | 78 |

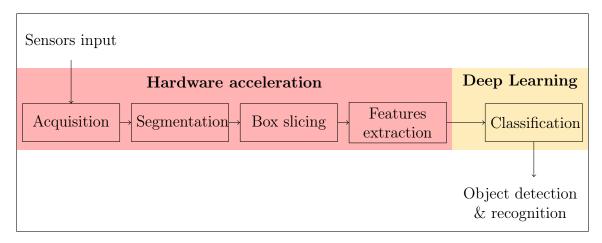

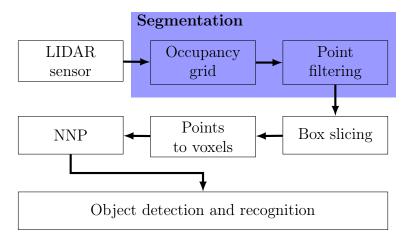

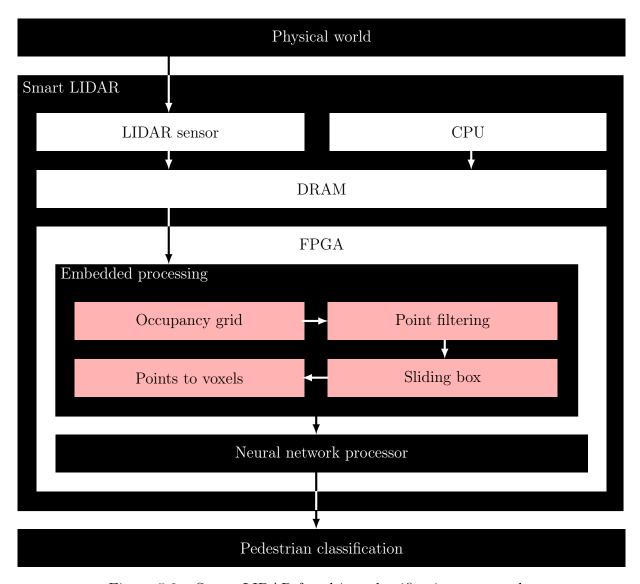

| 5.1  | Smart LIDAR use-case task flow                                                | 83 |

| 5.2  | Smart LIDAR for object classification case study                              | 85 |

| 5.3  | Design flow for the embedded DL methodology                                   | 86 |

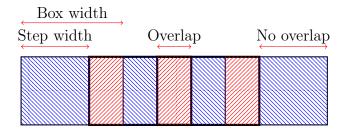

| 5.4  | Box simple overlapping hierarchical problem. The blue zone represents no      |    |

|      | box overlapping, the red zone represents two boxes overlapping                | 92 |

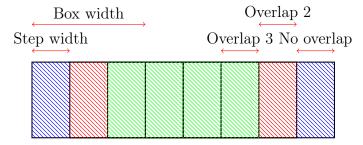

| 5.5  | Box multiple overlapping hierarchical problem. The blue zone represents       |    |

|      | no box overlapping, the red zone represents two boxes overlapping. The        |    |

|      | green zone represents three boxes overlapping                                 | 93 |

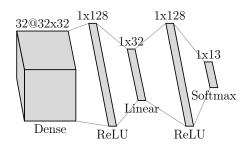

| 5.6  | DNN topology for SUOD dataset                                             |

|------|---------------------------------------------------------------------------|

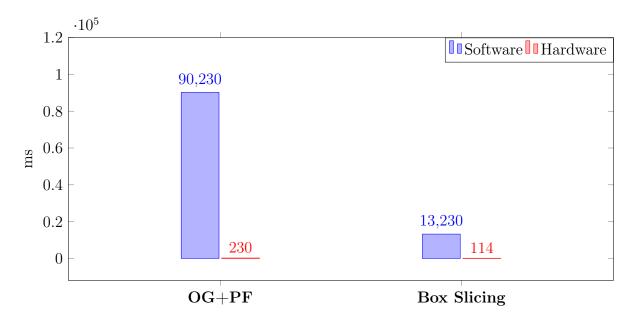

| 5.7  | Comparison between software and hardware application execution times $98$ |

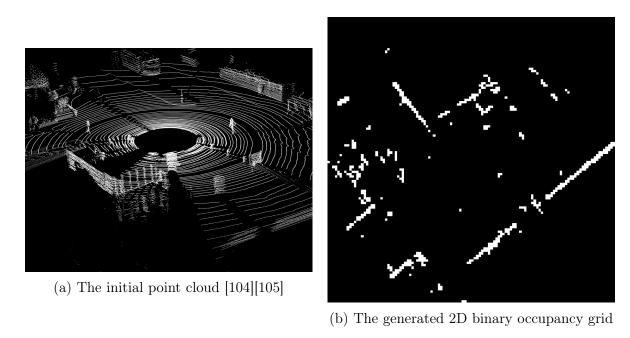

| 5.8  | Example of the occupancy grid task                                        |

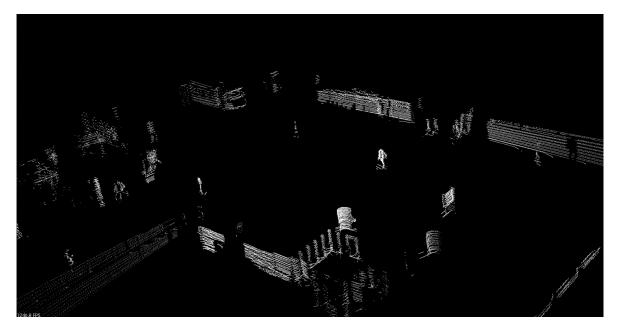

| 5.9  | Example of the point filtering task results                               |

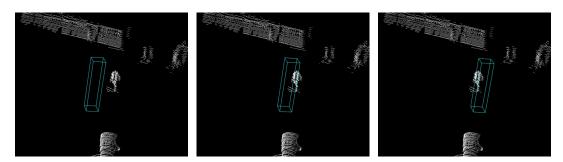

| 5.10 | Example of three sliding boxes on a pedestrian                            |

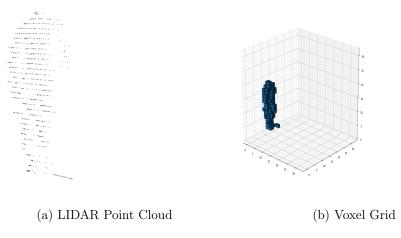

| 5.11 | Pedestrian extracted from a box                                           |

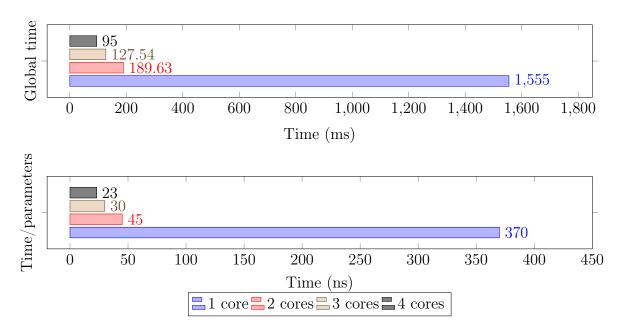

| 5.12 | Time performance and time per parameter for the SUOD neural network       |

|      | topology                                                                  |

## List of Tables

| 4.1 | Number of bits for each piece of data in instruction word 63              |

|-----|---------------------------------------------------------------------------|

| 4.2 | Hardware resource utilization of the scheduler module with a 10 ns clock  |

|     | target                                                                    |

| 4.3 | Hardware resource utilization of one neuron processing unit module with a |

|     | 10 ns clock target                                                        |

| 4.4 | Direct register mode DMA registers [95]                                   |

| 4.5 | Description of the different steps to configure a DMA                     |

| 4.6 | Accuracy for each dataset                                                 |

| ۳ 1 |                                                                           |

| 5.1 | Comparison of SW and HW Applications Execution Time 98                    |

| 5.2 | Hardware "points to voxels" resource utilization                          |

| 5.3 | Results from hardware "points to voxels" module                           |

| 5 4 | Accuracy results per dataset 102                                          |

### Acronyms

**ADAS** Advanced Driver-Assistance System.

AI Artificial Intelligence.

**AMBA** Advanced Microcontroller Bus Architecture.

**ANN** Artificial Neural Network.

**ASCII** American Standard Code for Information Interchange.

**ASIC** Application-Specific Integrated Circuit.

**AXI** Advanced eXtensible Interface.

CD Continuous Deployment.

CI Continuous Integration.

CNN Convolutional Neural Network.

**COTS** Commercial Off-The Shelf.

**CPS** Cyber-Physical System.

**CPU** Central Processing Unit.

**DL** Deep Learning.

**DMA** Direct Memory Access.

**DNN** Dense Neural Network.

**DRAM** Dynamic Random Access Memory.

**DSP** Digital Signal Processor.

**EEPROM** Electrically-Erasable Programmable Read-Only Memory.

**EXT4** 4th EXTended file system.

**FIFO** First In First Out.

**FPGA** Field-Programmable Gate Array.

FSBL First Stage Boot Loader.

**GPU** Graphics Processing Unit.

**HDL** Hardware Description Language.

**HLL** High Level Language.

**HLS** High Level Synthesis.

**HW** HardWare.

**IoT** Internet of Things.

**IP** Intellectual Property.

JTAG Joint Test Action Group.

**LIDAR** Light Detection And Ranging.

MM2S Memory-Mapped to Stream.

**NNP** Neural Network Processor.

**NoC** Network on Chip.

**NPU** Neural Processing Unit.

NTFS NT File System.

**OS** Operating System.

**PE** Processing Element.

PLD Programmable Logic Devices.

**RADAR** RAdio Detection And Ranging.

**RAM** Random Access Memory.

**RGB** Red Green Blue.

**RGBD** Red Green Blue Depth.

**RNN** Recurrent Neural Network.

RTL Register-Transfer Level.

**S2MM** Stream to Memory-Mapped.

**SPP** Single Purpose Processor.

**SW** SoftWare.

**U-Boot** Universal Boot Loader.

V2X Vehicle-to-Everything.

## Chapter 1

## General Introduction

| Contents |                         |

|----------|-------------------------|

| 1.1      | Introduction            |

| 1.2      | Context and Motivations |

| 1.3      | Problematics            |

| 1.4      | Thesis Contributions    |

| 1.5      | Thesis Outline          |

#### 1.1 Introduction

This chapter introduces the thesis context with four parts: context and motivations, problematics, thesis contributions, and finally, the thesis outline. The context and motivation explains the reason of this subject. The problematic is the expression of the problem isolated in the motivation. The contribution outlines how this work can be useful for the scientific community. Finally, the thesis outline details all chapters in the manuscript.

#### 1.2 Context and Motivations

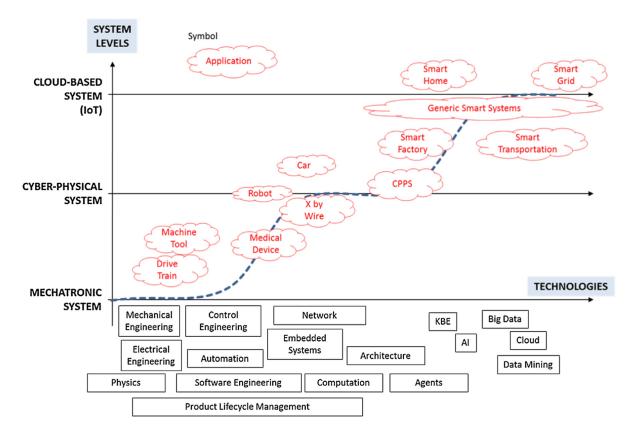

Embedded systems are a robust solution for many technological challenges in our society and are able to deliver precise, predictable and robust behavior. Their evolution gave birth to a new type of system called Cyber-Physical Systems (CPS) which combine computation and physical processes. A CPS can be defined as a networked embedded system that can analyze a physical environment and make decisions from its current state to affect it toward a desired outcome. Such systems possess a great potential, because the physical components of such systems introduce safety and reliability requirements, different from those in general-purpose computing [1]. A large spectrum of fields can benefit from the use of CPS, like smart city, smart mobility, smart health care, etc [2]. Fig 1.1 is an example of the evolution from early embedded systems adapted for the physical world (mechatronics) toward CPS and modern Internet of Things (IoT) systems [3]. Although CPS are a great solution for problems related to physical environment, they are constrained with processing resources, real-time, prototyping, etc. In this work, we are focusing on specific constraints: embedded AI implementation and prototyping time. Because of the limited calculation resources available on such systems, the integration of modern AI, particularly machine learning inference, is a tough problem. Mainly because those types of algorithms are computational heavy when analyzing data to extract the features related to the learnt pattern. For this purpose, lightweight and optimized algorithms made their appearance, but because of modern sensors and new techniques, such

Figure 1.1 – Transition process from early Embedded Systems (Mechatronics) to CPS to Internet of Things [3]

as data fusion, data size keeps increasing faster than the processing power of general purpose systems. This is where Single Purpose Processors (SPP) come in handy. Designing a digital circuit for one specific task has many advantages, such as faster computation, lower power, or smaller memory footprint. However, the prototyping time of specific hardware (also called hardware accelerators or hardware threads) to process AI algorithms is longer than software solutions. This is where the use of reconfigurable digital circuits is advantageous. Programmable Logic Devices (PLD), such as Field-Programmable Gate Array (FPGA), decrease prototyping time compared to Application-Specific Integrated Circuits (ASIC) because there is no need to produce a circuit board for each version of the project. Moreover, using High Level Synthesis (HLS) software, which can translate high level programming language to Hardware Description Language (HDL), further decreases the prototyping time [4]. For all these reasons, this thesis is focused on a methodology for AI applications in CPS based on hybrid CPU/FPGA platforms. In addition, a use case

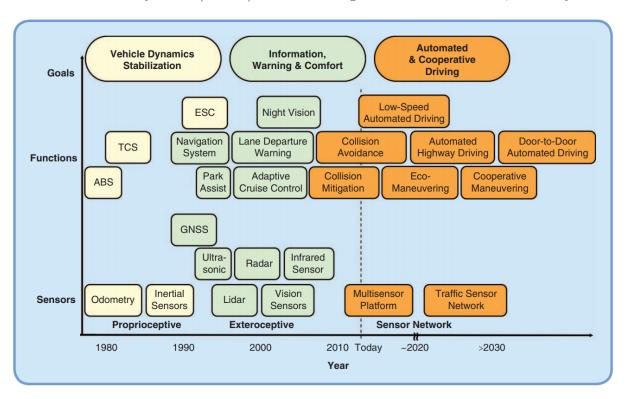

is chosen, according to the lab thematic: the autonomous vehicle. Since the apparition of vehicles as cheap transportation for individuals, a lot of progress has been made to improve the comfort of the driver and the safety of vehicles. But the interesting part of this evolution is the technologies used to implement such challenges. In most of today's approaches, the usage of AI in specific modules of the vehicle is one of the solutions to make it smart. Moreover, functionalities in cars are approached as independent parts that will analyze the environment and take decisions from the environmental state. In a way, an autonomous vehicle is a CPS. A key example of the evolution of those challenges is the development of vehicles and their evolution to smart vehicles thanks to Advanced Driver-Assistance Systems (ADAS) as seen in Figure 1.2. In this work, to analyze the

Figure 1.2 – Past and future evolution toward automated and cooperative driving [5].

environment, Artificial Intelligence (AI) technologies are used. More specifically, the use of Deep Learning (DL) with Neural Networks (NN). DL technologies became a hot topic in solving problems such as data analytics and object recognition [6]. Since the late 20th century, it has evolved in a substantial way and tends to be applied in many different fields and applications related to computer science and engineering, such as CPSs [7] [8].

For this purpose, we are using a specific field of the DL spectrum: object recognition. In the case of autonomous vehicles, object recognition is a way to make the vehicle recognize every object in its environment in order to smoothly pass across obstacles, obey traffic laws and predict the behavior of other agents (pedestrians, cars, bicycles, ...). However, with the increased accuracy requirements and complexity of NN architectures, DL technologies have been known to need a lot of computational power, mostly because of their huge number of parameters [9]. Unlike distributed cloud computing, where a lot of power processing is available, embedded systems impel some restrictions in the use of DL technologies. Even when optimizing/compressing NN or using Graphics Processing Units (GPU) for embedded systems, there is still some possible optimization through the usage of specialized processing systems [10] [11]. Also, if we want to build an application using specialized hardware processing for NN (ex: FPGA/ASIC based), we need a complete design methodology for embedded DL inference in order to decrease prototyping time.

#### 1.3 Problematics

Nowadays, CPS are a great solution to analyze a physical environment and interact with it. Moreover, the use of DL algorithms increased the accuracy of such analysis. But integrating DL applications in a CPS comes with many constraints that either conflict with the calculation performances because of the needed calculation resources, or with the prototyping time because of the use of a specific hardware. In the case of a specific hardware, such as deep learning accelerators, we observed a lack of a defined methodology in the context of hybrid CPU/FPGA-based CPS. NN accelerators have become a hot topic since 2014+ [12] and many papers are proposed about it, such as Neuflow, DianNao, etc. But methodologies are missing to integrate those NN accelerators in real-world case studies using hybrid CPU/FPGA-based CPS. We feel this is a bummer because combining NN accelerators with a suitable design methodology means a lot of possibilities and solutions in the context of modern problematics. This is why we are trying to explore

a consistent way of mixing NN accelerators and CPS with the use of hybrid CPU/FPGA platforms. This type of platform is able to bring an easy way to prototype hardware threads specialized in NN calculation with the flexibility of software automation. Our belief is that a methodology using hardware principles such as design re-use [13] and design automation might decrease the prototyping time of DL-based CPS, while still being able to optimize calculation time. In this thesis, we explore the problematic of prototyping time for hardware platform-based deep learning in the context of CPS using a co-design methodology. We also consider the use of software tools for automation in our methodology. Nevertheless, we keep in mind the usage of specific purpose hardware to speed up deep learning calculation, in order to decrease prototyping time and increase CPS analysis performances.

#### 1.4 Thesis Contributions

Our aim is to find a methodology to make CPS with DL algorithms hosted on hybrid CPU/FPGA platform while decreasing prototyping time of such systems. This issue is a real challenge, because of the constraints of CPS and the integration of AI in such systems. In this work, AI conception is mainly about DL architectures and inference. The contributions can be described as follows:

- 1. A methodology to develop DL applications for CPS using a hybrid CPU/FPGA platform

- 2. A hardware Neural Network Processor (NNP) architecture, design and prototype

- 3. A configuration and benchmarking software for the NNP

- 4. A validation of the NNP with different configurations and results

- 5. An automation tool to setup a hybrid CPU/FPGA prototype board for embedded DL applications

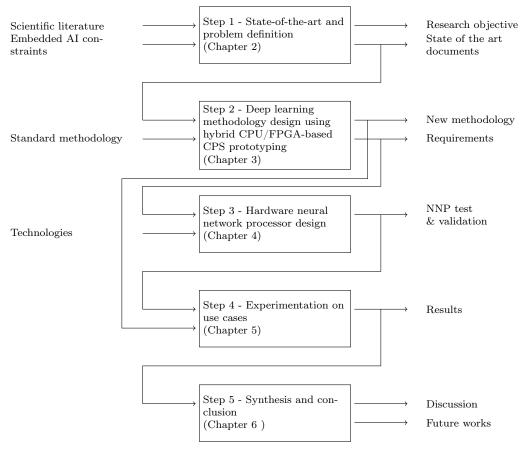

Figure 1.3 – Thesis outline

6. Case study validation: pedestrian detection for autonomous vehicles with several algorithms using a 3D PointCloud from a LIDAR

A thesis outline is described in Figure 1.3 and roughly describes the order of the chapters and the link between each chapter. The figure represents all chapters of this thesis except the context chapter (Chapter 1). This thesis outline presents a specific approach to explore a problem and find a logical pathway to a solution through components. The first step is the exploration of the scientific literature about embedded AI in order to delimit the research objectives and extract all documents necessary in order to study the problem. The second step will use the related works to extract from them the standard methodology for designing a hybrid CPU/FPGA-based prototype using DL. From this are inferred the requirements for a NNP and a new methodology is designed. The third step is about the design of this NNP, from the methodology requirements and the current

technologies, a hardware NNP is designed and validated. The fourth step will use the newly made NNP and the new methodology in order to experiment on a use case and get results. The fifth step is the synthesis of this work, which will highlight out discussions and future works. Embedded DL and hardware platform-based prototyping methodology are tackled, because they are great tools to improve prototyping time in CPS. Embedded DL is used as an analysis tool to infer an environmental state. The hardware platform-based prototyping methodology serves as a support for embedded DL application by easing the development and deployment. These domains are explored to find one solution among many that will fit the problematic and this exploration is described in the coming chapters.

#### 1.5 Thesis Outline

Chapter 2 presents a background exploration of the different domains tackled in this work: hybrid CPU/FPGA-based design for CPS and their related prototyping methodology, DL techniques for object recognition, neural networks design for FPGA hardware and a review of the existing architectures. Those four domains are mixed together from a methodology to the hardware and software development.

Chapter 3 describes an embedded DL methodology for hybrid CPU/FPGA-based CPS platform design using a hardware NNP. Starting from the standard methodology for CPU/FPGA platform-based design, this chapter explains the required modification of the methodology to include DL applications and ease the development for implementing such application. A dedicated hardware for DL computing is made as part of the methodology, in order to simplify some development steps.

Chapter 4 provides the architecture and design of a hardware NNP. Those choices are explained in detail in this chapter, in order to understand how it can be used. Then is presented the NNP IP (Intellectual Property) architecture as hardware accelerators. Finally, some experimentation and results on the NNP are presented in order to display some performances. Experimentations are done to validate the NNP in standalone mode

in order to determine its limitation.

Chapter 5 explains how to use the methodology with a specific use case: a smart LI-DAR for pedestrian detection. A first implementation of a hybrid CPU/FPGA-based DL application is presented using this work's methodology, and the already conceived NNP is validated in this real world case study. A design flow is presented, made from the methodology in chapter 3, in order to detail the different steps of prototyping.

Chapter 6 concludes this work with a synthesis of our contribution. The final solution is discussed and future works are highlighted.

## Chapter 2

# Cyber-physical systems and embedded artificial intelligence

"Prendre des p'tits bouts d'trucs et puis les assembler ensemble"

Stupeflip

| Contents |                      |                                                                |    |  |

|----------|----------------------|----------------------------------------------------------------|----|--|

| 2.1      | 2.1 Introduction     |                                                                |    |  |

| 2.2      | $\operatorname{Cyb}$ | er-physical systems design                                     | 22 |  |

| 2.3      | Har                  | dware accelerators for smart cyber-physical systems            | 24 |  |

| 2.4      | Arti                 | ficial intelligence in cyber-physical systems                  | 25 |  |

| 2.5      | 3D (                 | object detection and recognition for CPS                       | 27 |  |

|          | 2.5.1                | 3D vision techniques using 2D/3D sensors                       | 27 |  |

|          | 2.5.2                | Software deep learning for 3D object detection and recognition | 28 |  |

|          | 2.5.3                | Hardware acceleration of 3D object detection and recognition   |    |  |

|          |                      | application                                                    | 29 |  |

| 2.6      | Desi                 | gn and prototyping time of a hardware accelerated ob-          |    |  |

|          | ject                 | detection and recognition application for CPS                  | 30 |  |

| 2.7      | Con                  | elucion                                                        | 21 |  |

#### 2.1 Introduction

Nowadays, Cyber-Physical Systems (CPS) interact with the physical world by analyzing their environment using a variety of sensors. For this purpose, a powerful analysis tool is needed, such as Artificial Intelligence (AI), more precisely Deep Learning (DL) algorithms. Since the late 20th century, DL algorithms have evolved in a substantial way, and tend to be applied in many different fields and applications related to computer science and engineering, such as CPSs [7] [8]. However, with the increased accuracy requirements and complexity of Neural Networks (NN) architecture, DL technologies have been known to need a lot of computational power, mostly because of their huge number of parameters. Unlike distributed cloud computing where a lot of power processing is available, embedded systems impel some restrictions for the use of DL technologies. Optimizing/compressing NN or using Graphics Processing Units (GPU) for embedded systems is a great way to embed DL algorithms, nevertheless the usage of single-purpose processing systems boast great results [10] [11]. Moreover, if we want to build an application using single-purpose hardware processing for NN (eg. FPGA or ASIC-based), we need a complete design methodology for embedded DL in order to speed up the development. In this chapter, the state of the art is presented in five main points: 1) techniques for cyber-physical systems design in order to understand what a CPS is 2) the hardware used for CPSs and its constraints for smartness, 3) the integration of AI in CPSs from a hardware point of view, 4) the evolution of object recognition techniques in deep learning and the computation of such applications on specific hardware, 5) the prototyping time issues of a 3D object recognition application for CPS.

#### 2.2 Cyber-physical systems design

Cyber-physical systems (CPS) are mainly characterized as systems with a physical input and output. Their goal is to analyze a physical environments from sensor data and determine the correct action to perform to guide the environment into a desired state [1].

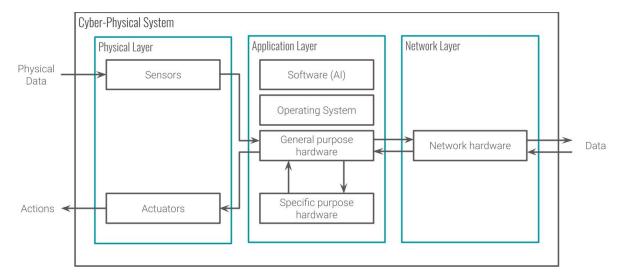

Figure 2.1 – Cyber-physical systems architecture

In this thesis, autonomous vehicles are represented as examples of networked CPS: the environment contains physical objects such as pedestrians, signs and other vehicles, with the sensors being cameras, RADARs, LIDARs, etc; and the actions to perform are about controlling the vehicle, with the final goal being reaching its intended destination. Figure 2.1 describes the architecture of a CPS as three layers communicating with each other. The physical layer is in charge of the interaction with the physical world: observing the surrounding environment to turn it into data for the system with sensors and influencing its environment to reach a desired state with actuators. The application layer is in charge of the analysis of the physical data and the communication with other CPSs on the network. This layer is composed of a general purpose hardware in charge of the software stack, which executes the main application of the CPS, and of an optional specific purpose hardware if some operations need to be accelerated (GPU, ASIC, FPGA, ...). The network layer is simply in charge of the communication between CPSs in the network to share data for a more resilient analysis of the physical world. In our context, the autonomous vehicle, the physical layer is composed of 3D sensors such as LIDARs, RADARs, and 2D sensors such as cameras. Actuators would be the vehicle movement such as braking, acceleration and controlling the wheel. The application layer would be composed of a software dedicated to decision-making running on a general purpose hardware, and a hardware

deep learning application represented by the specific purpose hardware. Meanwhile, the network layer would be represented as V2X (Vehicle-to-Everything) communications [14] [15] [16].

However the design of such systems is a real issue because of its multidisciplinary approach [17] [18]. The increasing complexity of such systems means the need for specific design methodology, such as contract-based or model-based, in order to decrease the prototyping time [19] [20] [3] [21]. In order to decrease the prototyping time in this thesis, we are oriented toward a platform-based design methodology for our CPS prototype. Because we are focusing the prototyping part of the design, full software solution would be the first approach; however to tackle performance issue we need the possibility of hardware accelerated solutions. What we have in mind in this work is to prototype on a hybrid CPU/FPGA platform to benefit the flexibility of the software and the performance of the hardware.

# 2.3 Hardware accelerators for smart cyber-physical systems

Hardware is an important constraint in CPS, because it will guide the development and deployment of the applications toward the prototype. Subsequently, the choice of hardware is an important decision to make. For all these reasons, FPGA-based chipsets are valuable, because they can emulate any type of hardware with performances near ASIC (Application Specific Integrated Circuit). Platform-based design and prototyping has seen an increase in its relevance, because of today's pressure on time-to-market and design costs. Techniques to design such systems have greatly progressed as explained by A. Sangiovanni-Vincentelli [13] and Pinto et al. [22]. The overall methodology also evolved, thanks to automation tools and design reuse. Platform-based design made evolve topics such as cyber-physical systems as shown by Nuzzo et al. [23]. But our interest is specifically focused on the integration of neural network in FPGA-based methodology. Guo et

al. [24] demonstrated the resource utilization of neural network calculation in terms of parameters and operations. Their survey shows that FPGA is a promising platform for neural network acceleration because of speed and energy efficiency. Li et al. [25] proposed a model-based design methodology involving deep neural network. They proposed an integrated set of tools and libraries alongside their methodology, in order to assist designers of signal processing systems. Shawahna et al. [26] made a survey about FPGA-based accelerators for deep learning networks, in particular convolutional neural network (CNN), and tried to isolate a methodology for their conception. Their survey revealed a specific pattern for FPGA-based accelerated neural network architecture, which is presented with techniques to optimize design and specific tools to automate the design process. Now we have a perspective for the design of a FPGA accelerator and specifically a NNP on FPGA platform. But there is a lack of prototyping methodology including a NNP as a tool in their design steps to prototype a fully functional embedded DL-based application.

#### 2.4 Artificial intelligence in cyber-physical systems

In this work, we tackle the principle of smartness in embedded systems, especially embedded CPSs. Our vision of smartness in this thesis is mainly based on the concept of learning systems, because of their versatility toward analysing environments. Furthermore, as we are mainly working on hybrid CPU/FPGA-based systems, we are trying to find a way to compute neural networks with specialized hardware. Hardware accelerated neural network is not a new topic, either as an analog chip with Säckinger et al. [27] [28] or in FPGA: Botros et al. [29] who made a hardware implementation of an artificial neural network (ANN) in 1994. With the rise of cyber-physical systems and the progress in performance of deep learning, this topic soon became a hot one. Several FPGA implementations were done like Ferrer et al. [30], Ormondi and Rajapakse [31] or Sahin et al. [32] even using floating points arithmetic. Farabet et al [33] [34] [35] [36] [37] proposed several architectures for the hardware implementation of convolutional neural networks (CNN) and even

a runtime reconfigurable architecture. Pham et al [38] designed an ASIC to accelerate neural network with a DMA for configuration purposes from Farabet et al. FPGA-based NeuFlow system. Esmaeilzadeh et al. [39] proposed a reconfigurable neural accelerators architecture. Lozito et al. [40] proposed an FPGA implementation of a feed forward neural network with floating point arithmetic and presented their speed performance. Chen et al. [41] proposed a high-throughput ASIC processor for CNN and DNN computation. Architecture models for neural network have emerged and their optimization was tackled: Zhang et al. [42] [43] [43] showed a way to optimize CNN accelerators as well as sparse NN accelerators. Venkatesh et al. [44] showed a way to optimize sparse and low-precision neural network. Wang et al. [10] proposed a scalable deep learning accelerator in order to optimize performance and maintain low power cost for large neural network. Gokhale et al. [45] proposed a CNN accelerator which is agnostic to CNN workload. Kreinar [46] presented a C++ library for the Vivado HLS [47] software to deploy trained neural network on FPGA. Zhou et al. [48] proposed a binary neural network on FPGA. Mittal [49] did a survey for FPGA-based accelerators for CNNs to highlight the key ideas of several dozens of works. Venieris et al. [50] proposed a survey of CNN-to-FPGA toolflows and compared their characteristics and features. Wang et al. [51] presented a survey about FPGA-based DL accelerators in order to demonstrate their advantages and disadvantage for research purpose. Shawahna et al. [26] presented a survey of FPGA-based deep learning accelerators and introduced a table that compared 30 papers using, among others, the precision, operations per second and power. FPGA-based accelerators for DL is a rising topic, especially for CNN accelerators considering their accuracy. All those works inspired us when conceiving our own NN accelerator but the main difference is that our accelerator is made to be integrated in our prototyping methodology and focused on the ease to prototype and use. Moreover, those work are mainly focused on CNN, while we are working on DNN. Now we need to understand what type of DL architecture needs to be studied in order to find the equilibrium between accuracy, power and computing time.

#### 2.5 3D object detection and recognition for CPS

Object detection and recognition applications are a crucial part of navigation inside a physical environment. The possibility to detect and understand a surrounding environment open doors to many opportunities in the scope of CPSs. In our case, 3D object detection and recognition for CPS is a way to give an autonomous vehicle an understanding of its surroundings to enforce traffic laws and reduce accidents. But in order to set up object detection and recognition, three parts are needed: sensors, object recognition algorithms and hardware capable of computing information in real time.

#### 2.5.1 3D vision techniques using 2D/3D sensors

Nowadays, sensors boast improved accuracy and heterogeneous type of information perceived. With the current state of technologies, autonomous vehicles are equipped with a large variety of heterogeneous sensors. As such, it is needed to understand how those sensors work, related to 3D vision techniques, to enhance 3D object detection and recognition algorithms. Thus, in order to correctly design a 3D object detection and recognition application for CPS, we need to choose the correct algorithm, as well as the correct sensors and hardware, considering the whole system's requirements.

#### 2.5.1.1 2D sensors

Most of the 2D sensors in autonomous vehicles are cameras. Their primary function is to convert light waves into a 2D images consisting of pixels (often a mix of the colors Red Green and Blue [RGB]). The resolution (number of pixels in an image) of modern cameras make it easier to detect and recognize objects in an image as well as increasing the detection distance. But the main problem about 2D sensors in autonomous vehicles is the lack of the depth dimension. This dimension is somewhat required for moving vehicles, even if it can be determined using specific algorithms [52] [53], but this means more calculations for the system. Hence, 2D sensors are often combined with 3D sensors

to improve the accuracy of the vehicle perception.

#### 2.5.1.2 3D sensors

Autonomous vehicles are equipped with a large variety of 3D sensors like RADARs, LI-DARs or 3D cameras. RADARs (RAdio Detection And Ranging) use radio waves in predetermined directions to find an object when the original signal is reflected or scattered back. LIDARs (LIght Detection And Ranging) use the same technique as a RADAR but with laser light. 3D cameras can either be RGBD (Red Green Blue Depth) cameras, a type of camera with a depth sensor embedded in it, or stereo camera, two or more lenses to simulate human binocular vision and thus able to capture 3D images. Moreover, it is possible to combine 2D and 3D sensor data (often called data fusion), to enhance the quality of the vehicle's vision [54]. Therefore, with such sensors, the capabilities of 3D object detection and recognition is improved, but the computation time of those algorithms is also increased because, with the addition of one more spacial dimension, data size increases exponentially.

## 2.5.2 Software deep learning for 3D object detection and recognition

3D object classification is a hot topic considering current sensors such as LIDAR or 3D camera. The usage of deep learning applications may help reach great accuracy in classification of 3D objects. Maturana and Scherer [55] proposed a 3D convolutional neural network (CNN) using voxels as input, and proposed a way to convert a point cloud to a voxel model. Brock et al. [56] proposed a voxel-based autoencoder and convolutional neural network to generate and classify 3D objects. Garcia-Garcia et al. [57], Hegde and Zadeh [58] and Jing Huang and Suya You [59] proposed different 3D convolutional neural networks (CNN) architectures using voxels as inputs to classify objects. Qi et al. [60] proposed a deep learning architecture to directly classify and segmentate point cloud instead of voxels. Zhi et al. [61] proposed a lightweight version of 3D convolutional network which

is interesting for embedded computation. Ioannidou et al. [62] proposed a residual neural network (ResNet) for 3D object classification using voxels. So 3D volumetric binary grid like voxels seems to be the way to process 3D data in order to make pattern prediction for object classification. 3D object classification using deep learning is a hot topic, because of today's 3D sensors and the accuracy they can yield. But software deep learning 3D object detection is heavy on computing power, especially for embedded systems.

## 2.5.3 Hardware acceleration of 3D object detection and recognition application

There are a lot of different hardware platforms available to accelerate 3D object detection and recognition applications. In this work, we will look into GPU, ASIC and FPGA hardware platforms and compare them. Birk et al [11] made a comparison between a GPU and a FPGA on a reflection image reconstruction application for 3D ultrasound computer tomography. Their results show that the GPU is 2.2 times faster, but with the estimated power consumption of the FPGA board (estimated to a maximum of 40W), the FPGAbased accelerator has a better performance per watts ratio (compared to the GPU using 250W). Nurvitadhi et al. [63] [64] [65] tried to answer the question about FPGAs beating GPUs in accelerating deep neural networks and showed that the current trend in deep learning algorithms may favor FPGAs, at least in term of performance/watts. FPGAbased hardware accelerated neural network seems to be a promising ways to compete with GPU in embedded approach such as CPS. The main conclusions about these comparisons is that ASIC-based platforms are the best choice for acceleration, but the prototyping time of such systems is the longest. GPU-based platforms are the easiest to prototype because it is fully reprogrammable, but they have the greatest power consumption, which means it is not always suitable in the context of CPS. FPGA-based platforms offer a middle ground between ASIC and GPU. Coupled with the current progress in FPGA design and the current hybrid CPU/FPGA platforms, it might become the best hardware platform choice when prototyping CPS-based applications.

### 2.6 Design and prototyping time of a hardware accelerated object detection and recognition application for CPS

Object detection and recognition applications are already difficult to develop and prototype because of the skill set needed, such as data processing and AI algorithms. If you add a layer with hardware acceleration, the complexity of such systems is increased exponentially because of the new heterogeneous skills needed and the cooperation between the software and hardware world. And if you add embedded system constraints such as the ones in CPS, it becomes a real challenge. That is why the prototyping time of those systems need to be tackled; in this thesis, we are specifically tackling the prototyping part and not the time to market. Andrews et al. [66] [67] is tackling the problem with Commercial Off-The Shelf (COTS) components in order to reduce design costs and time to market. Moreover, they are introducing hybrid CPU/FPGA chips with a threadoriented programming model for a faster development. One of the interesting parts is about programming languages for reconfigurable architectures and the usage of high-level languages for system-level design. From this, High Level Synthesis (HLS) software comes into view. Inggs et al. [4] investigated into the maturity of HLS software for business. They concluded that HLS tools can be reliable for industrial business but an expertise into embedded systems and particularly FPGA systems is still needed to yield more performance. Nane et al. [68] made a survey about the different HLS tools available, in order to compare academic and commercial tools. They concluded that academic and commercial HLS tools are not drastically far apart in terms of quality, but they may yield different optimization depending the target application. If we now return to the CPSs world, Hehenberger et al. [3] presented the importance of design, modelling, simulation and integration of CPS, and particularly showed that it is still a multidisciplinary world. So prototyping time of hardware accelerated object detection and recognition application for CPS still needs to be improved with solutions such as the usage of COTS, design

re-use and specific methodologies. An example of COTS product for DL-application in CPS would be industrial neural network accelerators such as the Google TPU [69], Apple A12 Bionic [70], Intel Nervana NNP [71] or Intel Movidius [72].

#### 2.7 Conclusion

In this chapter, we presented five main points: 1) techniques for CPSs design in order to understand what a CPS is 2) the hardware used for CPSs and its constraints for smartness, 3) the integration of AI in CPSs from a hardware point of view, 4) the evolution of object detection and recognition techniques in deep learning and the computation of such applications on specific hardware, 5) the prototyping time issues of an object recognition application on a hybrid CPU/FPGA hardware in the CPS context. The lack of methodologies for the integration of NN accelerators for hybrid CPU/FPGA-based CPS applications built up our interest into developing a methodology for DL-based 3D object detection and recognition applications accelerated on a hybrid CPU/FPGA hardware platform. The next chapter starts to introduce the standard methodology for HW/SW design and present how we achieved our methodology.

### Chapter 3

An embedded Deep Learning

methodology for hybrid

CPU/FPGA-based Cyber-Physical

Systems platform design using a

hardware Neural Network Processor

#### Contents

| 3.1 | Intro                      | oduction                                                         | 35 |

|-----|----------------------------|------------------------------------------------------------------|----|

| 3.2 | Hyb                        | rid CPU/FPGA platform                                            | 37 |

| 3.3 | A st                       | and ard process for $HW/SW$ co-design prototyping                | 38 |

| 3.4 | $\mathbf{H}\mathbf{W}_{i}$ | /SW co-design methodology in the deep learning AI era            | 41 |

|     | 3.4.1                      | Understanding the standard workflow for deep learning algorithms | 41 |

|     | 3.4.2                      | Exploration of deep learning inside a HW/SW co-design appli-     |    |

|     |                            | cation                                                           | 43 |

|     | 3.4.3                      | Prototyping automation tools for hybrid CPU/FPGA platforms       | 46 |

| 3.5 | Proposed embedded Deep Learning methodology around a |                                                                                       |    |  |

|-----|------------------------------------------------------|---------------------------------------------------------------------------------------|----|--|

|     | FPG                                                  | GA-based Neural Network Processor                                                     | 49 |  |

|     | 3.5.1                                                | The methodology design flow                                                           | 49 |  |

|     | 3.5.2                                                | Toward the automation of the design flow                                              | 53 |  |

| 3.6 | Cha                                                  | llenges of deep learning in hybrid $\mathrm{CPU}/\mathrm{FPGA}$ -based $\mathrm{CPS}$ | 54 |  |

| 3.7 | Con                                                  | $\operatorname{clusion} \ldots \ldots \ldots \ldots \ldots$                           | 56 |  |

#### 3.1 Introduction

In the previous chapter, we presented the state of the art and explained the need of a DL methodology for hybrid CPU/FPGA-based CPSs. In this chapter, we will present our work toward our embedded DL based methodology for CPU/FPGA-based CPS platform design using a hardware NNP (Neural Network Processor). We will introduce Hardware/-Software (HW/SW) co-design methods, their involvement in systems such as CPS and the usefulness of hybrid CPU/FPGA platforms. Because of modern algorithms, the hardware resources needed in order to reach a result are far more substantial than in the past. And because of the constraints of embedded systems, a full software calculation system may not have enough hardware resources to perform in a granted time. Using HW/SW codesign allows a system to expand software calculations to specific hardware accelerators in order to speed up computations. Because of this, HW/SW co-design methods have become more and more popular in recent years, when designing embedded systems, and thus CPS when designing modern systems. CPS comes from the evolution of embedded systems in the 20th century. Over recent years, significant effort has been put into understanding the relationship of the individual with the physical environment. CPS are a great base toward conceiving systems that interact with the physical environment but with an analysis of the environment. The better the analysis, the better the understanding of the environment, and thus, the better the interaction with the physical world. However, improving the analysis comes from two main factors: better sensors and better algorithms. One occurrence that greatly affected the CPS topic is the appearance of modern sensors that were much more accurate and could detect a large choice of physical information. In our case, we are mainly talking about 3D sensors such as RADAR, LIDAR and 3D cameras. Those sensors improved the quantity of data available and enhanced the performance of analysis algorithms. This is especially important when looking at modern methods using deep learning. The current understanding of deep learning shows that the more information available, the more accurate the result. Subsequently, the usage of deep learning algorithms in CPS can improve the analysis of the physical environment, but at

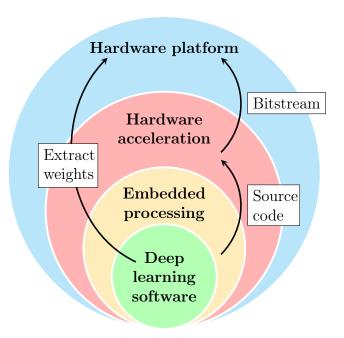

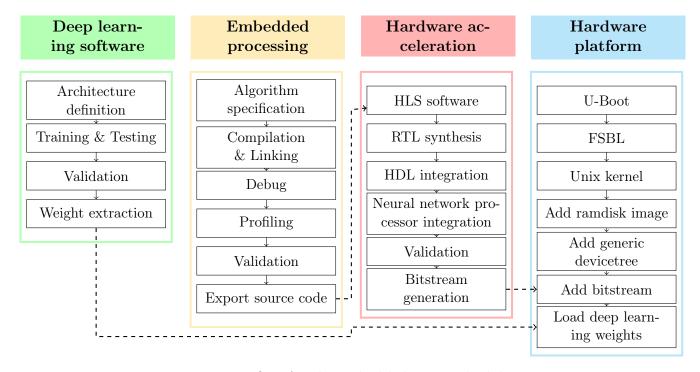

the cost of resource-heavy computation. This is where HW/SW co-design methods can be a great help toward the conception of smart CPS. That is why we are trying to embed DL algorithms inside the system using a hybrid CPU/FPGA platform. The use of software is an important part in CPS prototyping, and making a hardware deep neural network accelerator as part of this system is a way to reduce the toll of the computation. From this point, we want to describe our path toward a CPU/FPGA-based DL methodology using a NNP as its core. The exploration to propose a new methodology starts with the understanding of hybrid CPU/FPGA platform and the standard processes for HW/SW co-design prototyping. Then, we present a simple methodology to develop a HW/SW codesign application using deep learning software. Finally, we present a CPU/FPGA-based DL methodology using a hardware deep neural network accelerator as its core. Figure 3.1 is a global view of our final methodology. It consists of four parts: the deep learning software represents the deep learning architecture design, its training and testing to finally extract all trained weight matrices; the embedded processing is the design of the different data processing algorithms and describing them as embedded system code; the hardware acceleration transforms the embedded processing source code as HDL (Hard-

Figure 3.1 – Methodology global view around embedded DL

ware Description Language) either with HLS tools (High Level Synthesis) or manually; finally, the hardware platform can be prepared with the extracted weights loaded inside (using file systems, EEPROM, ...) and with the bitstream containing the FPGA architecture consisting of the hardware accelerated data processing and the NNP. In order to describe this methodology, we will explain from where we started and the different steps toward our goal.

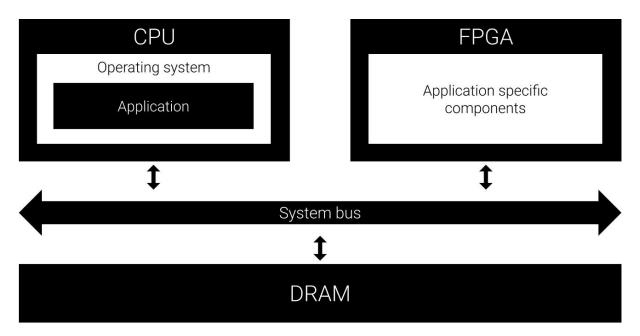

#### 3.2 Hybrid CPU/FPGA platform

Hybrid CPU/FPGA platforms are systems containing both CPU and FPGA components communicating between themselves. The CPU and FPGA are either two different chips or in the same chip such as the Xilinx Zynq, the Intel Altera Stratix and the MicroSemi SmartFusion. This union enables many types of design by combining the flexibility of software-driven development with the performance of a hardware-driven one. The main purpose of such platforms is to design a platform with hardware application-specific components to speed up performance-critical functions. Figure 3.2 presents a view of a simple hybrid CPU/FPGA plaform with a DRAM (Dynamic Random-Access Memory). An example of a simple application on this type of platform would be a software calling FPGA application specific components as hardware threads while computing something else. DRAM can be used here to exchange data between the software threads processed by the CPU and the hardware threads on the FPGA. Such structure is a great way to speed up performance-critical functions that require complex calculations. In this thesis, we consider performance-critical functions as data processing and deep neural network calculation. With application specific components computing inferences, the software threads can focus on other tasks such as network communication or UI display. We consider HW/SW co-design using hybrid CPU/FPGA platform a great way to speed up CPS prototyping, because it merges software development with hardware performances and enables prototype automation.

Figure 3.2 – Hybrid CPU/FPGA platform with DRAM

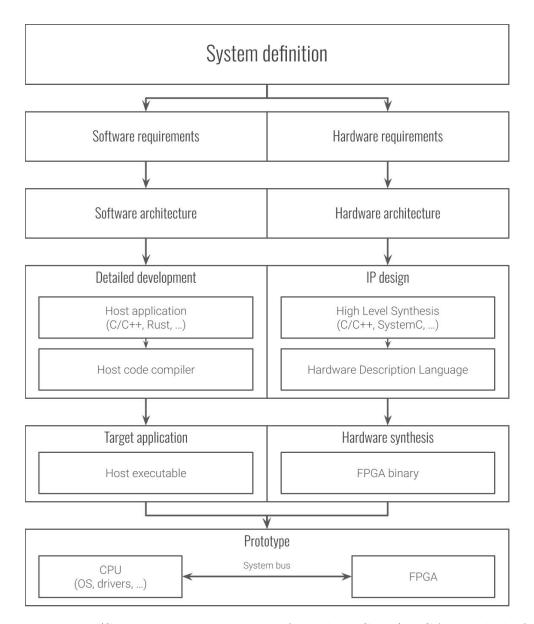

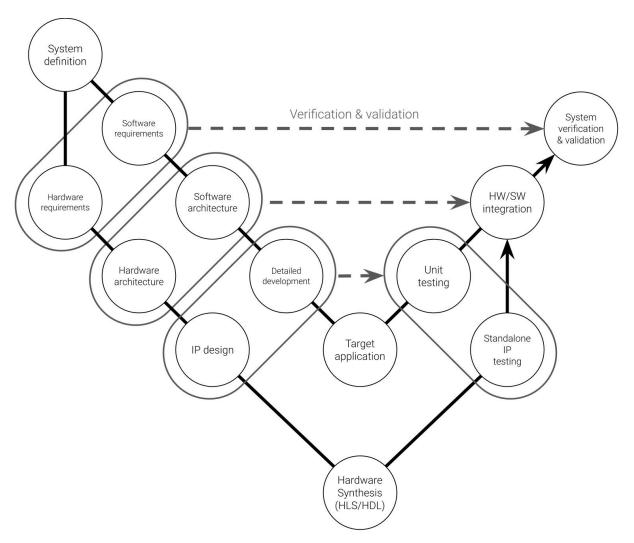

### 3.3 A standard process for HW/SW co-design prototyping

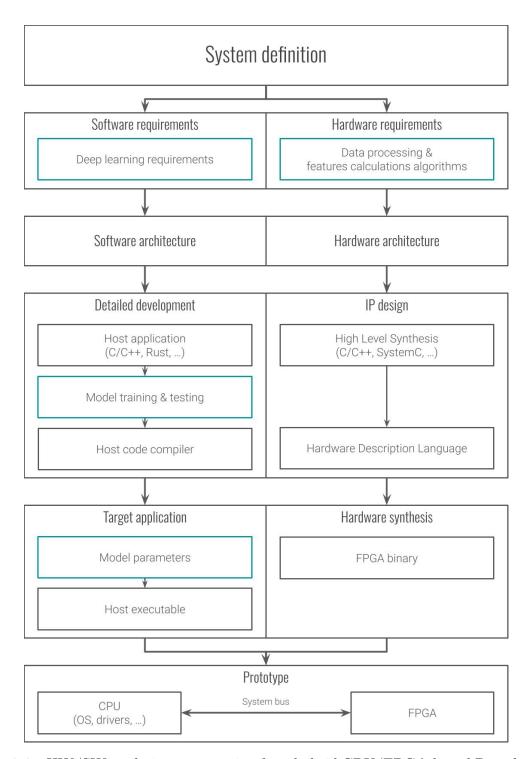

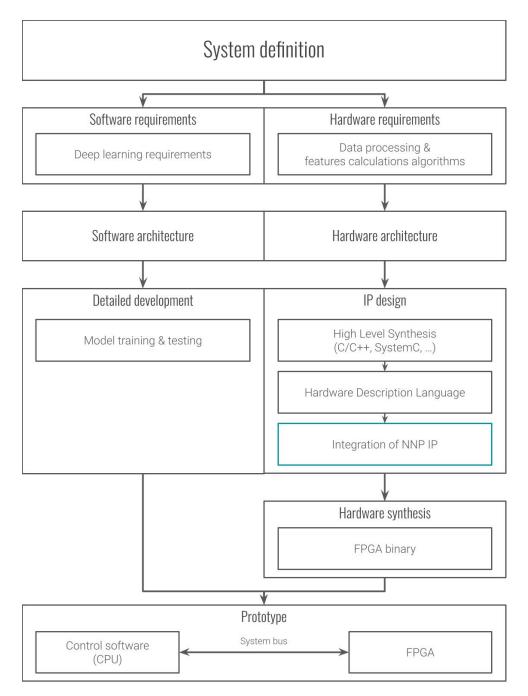

In order to make a new methodology using HW/SW co-design prototyping for hybrid CPU/FPGA-based platform, it is necessary to understand how it works. Figure 3.3 is a diagram representing a standard design flow for HW/SW co-design prototyping for CPU/FPGA-based platform. We can consider the standard design flow as a V-model [73] as seen in Figure 3.4. The system definition part is the first step to define and dissociate the software and the hardware processes. The goal is to isolate the different processes in the system in order to achieve the desired result. Once the processes defined, we need to determine if it should be executed as software or hardware threads. In the case of HW/SW co-design, hardware is mostly used for hardware acceleration, which means executing tasks the software will be slow at processing, whereas software processing is about controlling the hardware and manipulating data that hardware processing has trouble with. In this work, we have two ways of deciding: either the function is determined as performance-critical because we want it to be as fast as possible, thus a hardware thread is chosen, or we make the function as a software thread and measure its performance;

Figure 3.3 – HW/SW co-design prototyping for hybrid CPU/FPGA-based platform

depending on the results we choose between software and hardware threads. Once the requirements and architectures have been defined, the development part starts. This part is one of the most time-consuming tasks because of the iterations done to stick with the requirements set beforehand. Moreover, the need to separate software and hardware applications means that the skills required are heterogeneous, which mostly suggests two teams of individuals working on those tasks: one team for the software and the other for the hardware. Finally, the implementation and deployments are also key parts, and often subject to going back to the development stage when the integration between software

Figure 3.4 – V-model: HW/SW co-design prototyping based on hybrid CPU/FPGA platform

and hardware are not up to the system definition and requirements. Figure 3.4 represents the HW/SW co-design prototyping for hybrid CPU/FPGA-based platform but as a V-model. The system definition forks in two branches: one for software and the other for hardware. In the software branch, the software requirements refers to defining the behavior of the software and its constraints. The software architecture refers to designing the interactions between software threads. The detailed development refers to programming the functions. The target application is the compiled software adapted to the desired host. The unit testing refers to testing each software thread individually to verify and validate the detailed development. In the hardware branch, the hardware requirements refers to defining the behavior of the hardware and its constraints. The hardware architec-

ture refers to designing the interactions between hardware threads. The IP (Intellectual Property) design refers to describing the programmable logic of each hardware thread. The hardware synthesis is the use of HLS tools or/then HDL to describe the hardware architecture. The standalone IP testing is to verify the behavior of each IP individually. Finally, the HW/SW integration is the fusion of the hardware and software with their verification and validation toward the software and hardware architecture. The system verification and validation is the final test, checking that the current system is compliant with the requirements. Once this step has been cleared, the prototype can be started. The goal of this thesis is to simplify and optimize the standard design flow for embedded AI with the usage of specific constraints, dedicated hardware and automation tools.

# $3.4~~{ m HW/SW}$ co-design methodology in the deep learning AI era

This section is about the first step of this work toward the final methodology. We want to explore a simple methodology for HW/SW co-design using hybrid CPU/FPGA platform and include a deep learning application for classification as a software. It is divided in two parts: 1) the update of the standard methodologies to fit our goal, 2) a first methodology with software deep learning and hardware accelerated data processing.

### 3.4.1 Understanding the standard workflow for deep learning algorithms

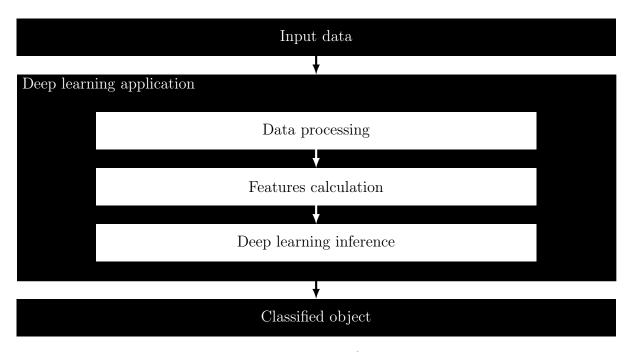

In order to take a first step toward the wanted methodology, we want to modify the standard methodology to our needs. But first, it is necessary to understand the standard workflow of a deep learning application for classification, so it can be fused with the methodology. Figure 3.5 presents a standard workflow for a pre-trained deep learning-based classifier application. There are three steps before the inference of an object cate-

gory:

- 1. Data processing is the action of filtering a signal (our input) in order to remove noise or irrelevant pieces of information. This step is important to reveal meaningful information used for pattern recognition. What is filtered out of the input will depend on the nature of the input data and the pieces of information required to determine a pattern.

- 2. Calculating the features for the deep learning inference. A feature can be defined as a measurable property of an observed phenomenon. Ideally, a feature should be unique to each category of object in order to easily determine a pattern. As it is seldom possible to determine the category of an object with only one feature, multiple features are used to find the pattern. Although those features should be independent from each other. In the case of deep learning, those features are often learnt inside the neural network. But in some cases, it is better to pre-process those features to reduce the size of the neural network architecture.

- 3. Inferring the object class with the learnt model. It implies that training and testing of the DL application is already done. The inference will use the value of each feature to determine the category of the input corresponding to the pattern learned.

Of those three steps, the heaviest computations are the data processing and the feature calculation. As the data processing task is making calculations from the raw input, it means this is the part with the greatest amount of information. Moreover, the performance greatly depends on how noisy the input is. The feature calculation is also resource intensive depending on the number of features and the complexity of said features. This means that those tasks are the ones we are most likely to hardware accelerate.

With the deep learning workflow in mind, Figure 3.6 presents an example of how to prototype a deep learning application on top of a HW/SW co-design platform. The main changes are: 1) the hardware architecture which is only about hardware accelerating data processing and feature calculation algorithms, 2) the DL requirements, which refers to

Figure 3.5 – Deep learning classification standard steps

determining the dataset to train and test the model, the algorithm to use for the learning, and the target accuracy and error, 3) the model parameters that need to be embedded either into the host executable or into the prototype hardware (File System, EPROM, DRAM, ...), so the host software can use it.

## 3.4.2 Exploration of deep learning inside a HW/SW co-design application

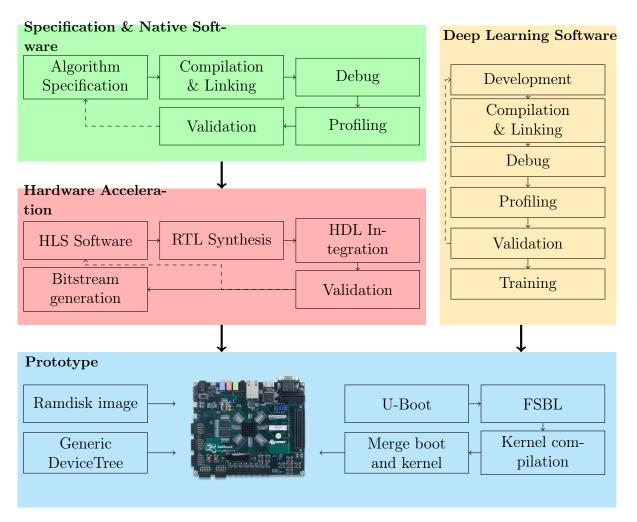

Now that we have a better understanding of the conception of a HW/SW co-design application using deep learning, lets first make a design flow in order to describe the steps before the final prototype. Our approach is oriented toward a platform-based design using a hybrid CPU/FPGA platform. Figure 3.7 shows the design flow of a co-design deep learning system where preliminary data processing tasks are hardware accelerated and the learning system is pure software. Some steps of this design flow have been automated to accelerate the development, prototyping and validation of the HW/SW co-design application, such as the configuration of the prototyped hardware co-design application [74]. There are four main steps toward the prototype phase: The **Specification & Native**

Figure 3.6 – HW/SW co-design prototyping for a hybrid CPU/FPGA-based Deep learning application. Compared to the previous methodology (Figure 3.3): the deep learning requirements are added inside the software requirements, the data processing and feature calculation are added inside the hardware requirements, the model training and testing is added between the host application and host code compiler, and the model parameters are added before the host executable.

Figure 3.7 – Design flow diagram for a hybrid CPU/FPGA-based HW/SW co-design deep learning software application

Software part refers to the development of the data processing software on a native platform in order to validate it. Once the software has been profiled and its results meet requirements, the application source code is considered the input of the next step, the Hardware Acceleration. The Hardware Acceleration part refers to transforming the data processing software threads to hardware threads. The native software source code is to be converted to Register-Transfer Level abstraction (RTL) with a High-Level Synthesis (HLS) software, then to be implemented in any Hardware Description Language (HDL) project. If simulation results meet the requirements, the final bitstream file that came from the HDL project is deployed on the prototype. The Deep Learning Software part refers to the development of the learning system which represents the smartness of the

Figure 3.8 – Application Tasks Graph

System. This part does not differ from traditional embedded deep learning development. Once finished and compiled, the software is deployed on the prototype. The **Prototype** part refers to the platform on which the hardware threads and the deep learning software are deployed and tested. The prototype configuration and deployment are fully automated in our work (see Section 3.4.3). As an example of this design flow, let's imagine a simple application of pedestrian recognition using a LIDAR point cloud [75]. Figure 3.8 presents the task graph of this application, in red are the hardware threads and in yellow is the software thread. If applying the design flow, in order to design this system, we first need to define an algorithm that is validated through native software development. Once this software has been defined, we can hardware accelerate it thanks to HLS tools. Meanwhile we also need to develop the software deep learning and validate it correctly. Once everything is done, we can deploy the hardware threads as well as the deep learning software executable to the prototype.

### 3.4.3 Prototyping automation tools for hybrid $\mathrm{CPU}/\mathrm{FPGA}$ platforms

As seen beforehand, we automated the deployment of our prototype platform in order to decrease prototyping time. We developed an automation software using *GNU make* [76] available in our git repository [74]. GNU make is an automation software using a

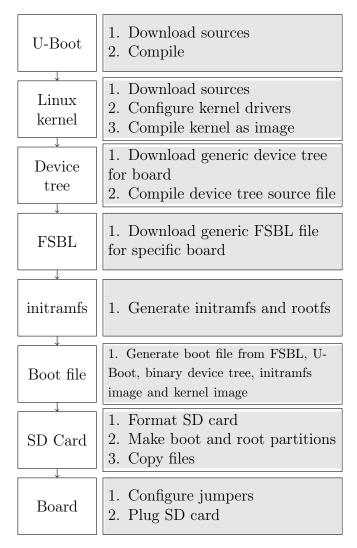

Figure 3.9 – Prototype automated deployment

Makefile to perform various actions. Figure 3.9 shows the different steps of our automation software to deploy the prototype. It automates the build of the U-Boot and Linux kernel by downloading the sources from their respective git repository and compiling them. U-boot (Universal Boot Loader) is an open-source boot loader for embedded device which contains instructions to boot the available operating system kernel. In our case, the kernel is a Linux one. The Linux kernel is a free and open-source operating system kernel. It is often deployed in embedded devices because of how light it is. The purpose of this kernel is to run an operating system which will execute our NNP control software. A generic device tree is available inside our repository in order to be compiled for the board beforehand. For now, only a device tree for a Zedboard [77] has been made, because

it was the development board used during this work. A device tree is a data structure describing the different hardware components available on our platform. Its purpose is to enable the operating system kernel to use and manage those components (e.g. FPGA and DRAM mostly in our case). A FSBL (First Stage Boot Loader) is also available, and already compiled, inside our repository, but only a ZedBoard one. A FSBL is a specific file responsible for loading the FPGA bitstream and configuring the Processing System (PS) at boot time. There also is an already made initramfs (initial RAM file system) image with necessary drivers and libraries for the OS and control software, in order to get access to a read-only file system inside the DRAM. The initramfs is an image of a temporary root file system loaded into memory (DRAM) that acts as a read-only file system for the operating system. Then a boot file is generated from the FSBL, U-Boot file, binary device tree, initramfs and kernel image. This boot file can be considered as a compressed and executable version of the necessary files needed for the booting of the kernel and the operating system. The FPGA bitstream can also be added to the boot file in order to be loaded at boot by the FSBL. Finally, all files are placed inside a folder to be copied into the SD card. The SD card needs to be correctly formated with a NTFS (NT File System) boot partition for files generated by our script, and an EXT4 (4th EXTended filesystem) partition for persistent storage. A script available inside the initramfs mounts the EXT4 partition to the /root folder at OS startup. This means the embedded deep learning software is copied inside the EXT4 partition to be executed. It also allows a better control of continuous integration/continuous deployment (CI/CD), because it allows us to deploy our updated software through the network on which the prototype was connected. Moreover, we also succeeded in deploying the FPGA bitstream over a network thanks to the  $\frac{dev}{xdev} cfg$  channel, which allowed us to reprogram the FPGA at runtime by sending the bitstream to this FPGA device file.

# 3.5 Proposed embedded Deep Learning methodology around a FPGA-based Neural Network Processor

In this section, we propose an embedded DL based methodology for FPGA-based CPSs platform design using a hardware NNP. Furthermore, the automation of the methodology is tackled to determine how to decrease prototyping time.