### Modeling, Scheduling, Pipelining and Configuration of Synchronous Dataflow Graphs with Throughput Constraints

Alexandre Honorat

#### ► To cite this version:

Alexandre Honorat. Modeling, Scheduling, Pipelining and Configuration of Synchronous Dataflow Graphs with Throughput Constraints. Signal and Image processing. INSA de Rennes, 2020. English. NNT: 2020ISAR0010. tel-03337988

### HAL Id: tel-03337988 https://theses.hal.science/tel-03337988v1

Submitted on 8 Sep 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE

### L'INSA RENNES

ÉCOLE DOCTORALE Nº 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Signal, Image, Vision

Par

### **Alexandre HONORAT**

### Modeling, Scheduling, Pipelining and Configuration of Synchronous Dataflow Graphs with Throughput Constraints

Thèse présentée et soutenue à Rennes (35 000), le 27 novembre 2020 Unité de recherche : IETR – UMR 6164 du CNRS Thèse Nº : 20ISAR 20 / D20 - 20

#### **Rapporteurs avant soutenance :**

| Claire PAGETTI | HDR, Ingénieur de Recherche à l'ONERA, Toulouse                |

|----------------|----------------------------------------------------------------|

| Frédéric SUTER | HDR, Directeur de Recherche au CNRS (USR 6402 - CCIN2P3), Lyon |

#### **Composition du Jury :**

| Président :<br>Examinateurs :         | Alain GIRAULT<br>Johan LILIUS<br>Claire PAGETTI<br>Frédéric SUTER | HDR, Directeur de Recherche à l'INRIA Grenoble<br>Professeur à l'Åbo Akademi, Turku (Finlande)<br>HDR, Ingénieur de Recherche à l'ONERA, Toulouse<br>HDR, Directeur de Recherche au CNRS (USR 6402 – |  |  |  |  |  |

|---------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Dir. de thèse :<br>Encadr. de thèse : | Jean-François NEZAN<br>Karol DESNOS                               | CCIN2P3), Lyon<br>HDR, Professeur à l'INSA Rennes<br>Maître de Conférences à l'INSA Rennes                                                                                                           |  |  |  |  |  |

## Contents

| C  | onter | ats                                                  |       |   | iii  |  |

|----|-------|------------------------------------------------------|-------|---|------|--|

| Li | st of | Figures                                              |       |   | v    |  |

| Li | st of | Tables                                               |       |   | vii  |  |

| Li | st of | Algorithms                                           |       |   | ix   |  |

| Li | st of | Listings                                             |       |   | xi   |  |

| A  | cknov | wledgements                                          |       |   | xiii |  |

| R  | ésum  | né en français                                       |       |   | xvii |  |

| In | trod  | uction                                               |       | x | xvii |  |

| 1  | Bac   | kground                                              |       |   | 1    |  |

|    | 1.1   | Introduction: hardware, software, and parallelism    | <br>• |   | 2    |  |

|    | 1.2   | The SDF dataflow model and its flavors               | <br>  |   | 13   |  |

|    | 1.3   | Scheduling of SDF graphs                             |       |   | 22   |  |

|    | 1.4   | The PREESM tool                                      | <br>  |   | 30   |  |

|    | 1.5   | Conclusion                                           | <br>• |   | 41   |  |

| 2  | Mo    | deling nested for loops, with SDF graphs             |       |   | 43   |  |

|    | 2.1   | SIFT keypoints detection application                 | <br>• |   | 45   |  |

|    | 2.2   | Modeling of single loops having explicit parallelism | <br>• |   | 47   |  |

|    | 2.3   | Modeling of nested loops having explicit parallelism | <br>• |   | 49   |  |

|    | 2.4   | When and how to use SDF iterators?                   | <br>• |   | 52   |  |

|    | 2.5   | Evaluation                                           | <br>• |   | 55   |  |

|    | 2.6   | Related work                                         | <br>• |   | 57   |  |

|    | 2.7   | Conclusion                                           | <br>  |   | 59   |  |

| •  | <b>G</b> 1 |                                                           | 01  |

|----|------------|-----------------------------------------------------------|-----|

| 3  |            | eduling partially periodic SDF graphs                     | 61  |

|    | 3.1        | Background                                                | 64  |

|    | 3.2        | Partially periodic constraints                            | 66  |

|    | 3.3        | Discussion on the schedulability conditions               | 75  |

|    | 3.4        | Scheduling SDF graphs with partially periodic constraints | 77  |

|    | 3.5        | Evaluation                                                | 84  |

|    | 3.6        | Related work                                              | 91  |

|    | 3.7        | Conclusion                                                | 93  |

| 4  | Pip        | elining SDF graphs automatically                          | 95  |

|    | 4.1        | Admissible graph cuts for pipelining                      | 97  |

|    | 4.2        | Automatic pipelining of SDF graphs                        | 103 |

|    | 4.3        | Automatic cycle breaking of SDF graphs                    | 108 |

|    | 4.4        | Evaluation                                                | 111 |

|    | 4.5        | Related work                                              | 117 |

|    | 4.6        | Conclusion                                                | 119 |

| 5  | Con        | figuration of parameterized SDF graphs                    | 121 |

|    | 5.1        | PREESM parameters                                         | 123 |

|    | 5.2        | DSE: entangled problems                                   | 128 |

|    | 5.3        | An exhaustive DSE method                                  | 132 |

|    | 5.4        | Improving DSE with automatic delay placement              | 134 |

|    | 5.5        | A naive heuristic for Integer malleable parameters        | 137 |

|    | 5.6        | Evaluation                                                | 139 |

|    | 5.7        | Related work                                              | 144 |

|    | 5.8        | Conclusion                                                | 147 |

| Co | onclu      | ision                                                     | 149 |

| Bi | bliog      | graphy                                                    | 155 |

|    | _          |                                                           | 100 |

| Lı | st of      | published contributions                                   | 183 |

| Ac | crony      | /ms                                                       | 185 |

| Ec | litior     | n notice                                                  | 189 |

|    | Auto       | prisation de Reproduction                                 | 190 |

|    | Atte       | station de Corrections                                    | 191 |

iv

# List of Figures

| 1   | Exemple de graphe SDF avec son équivalent SRSDF, et deux ordonnan-<br>cements possibles      |

|-----|----------------------------------------------------------------------------------------------|

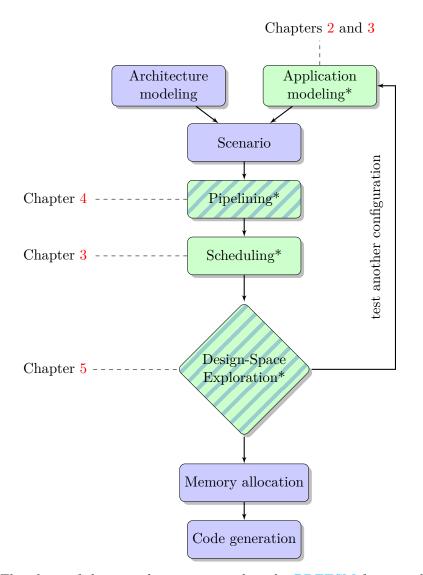

| 2   | Logigramme des contributions telles qu'utilisées dans l'outil PREESM xxir                    |

| 3   | Flowchart of the contributions as used in the PREESM framework xxx                           |

| 1.1 | Odroid XU3 heterogeneous multi-processor                                                     |

| 1.2 | SDF graph example with its equivalent $SRSDF$ graph and two possible                         |

|     | static schedules with the corresponding buffer usage                                         |

| 1.3 | SRSDF graph equivalent representations                                                       |

| 1.4 | ${ m SDF}$ graph example with its equivalent ${ m SRSDF}$ graph and a possible static        |

|     | schedule with the corresponding buffer usage                                                 |

| 1.5 | CSDF graph example with its equivalent SRSDF graph and a possible                            |

|     | schedule                                                                                     |

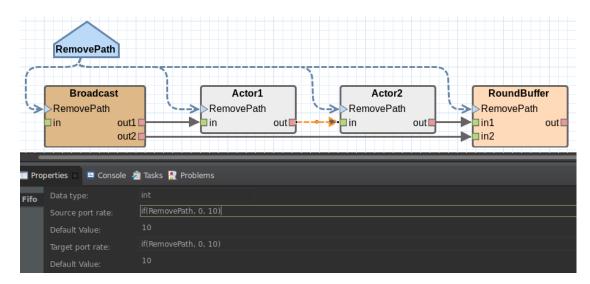

| 1.6 | Example of PISDF graph in PREESM                                                             |

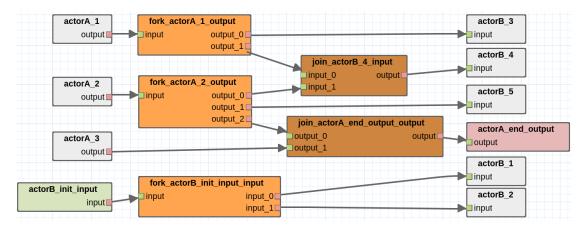

| 1.7 | Example of generated SRSDF graph in PREESM 40                                                |

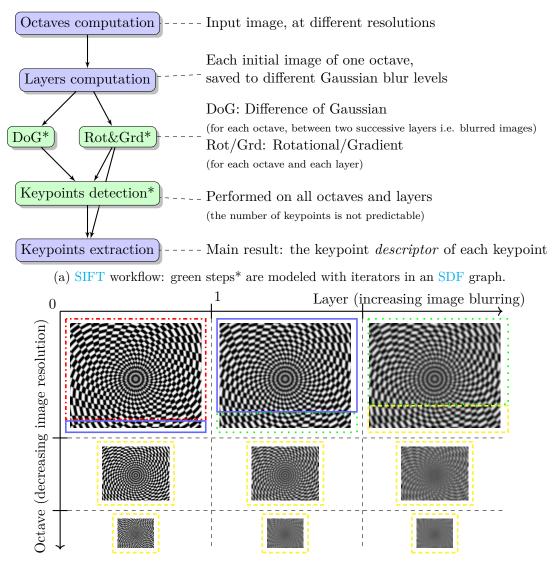

| 2.1 | SIFT image processing application                                                            |

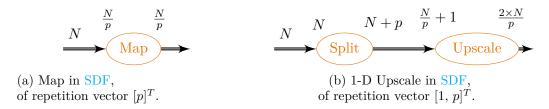

| 2.2 | Map and Upscale at a coarse-grain level                                                      |

| 2.3 | Modeling of iterators with SDF                                                               |

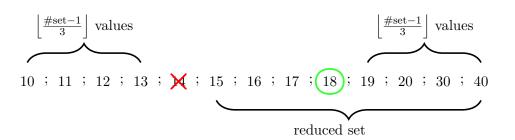

| 2.4 | Reduce of N elements in SDF, with chunk size $c > 153$                                       |

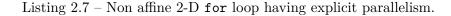

| 2.5 | Modeling of iterators with SDF, with broadcast actor                                         |

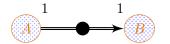

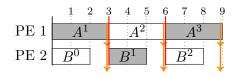

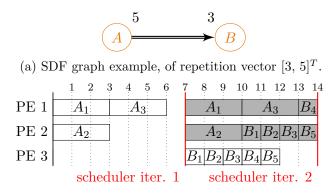

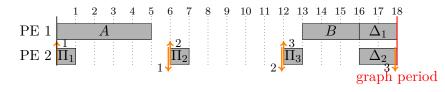

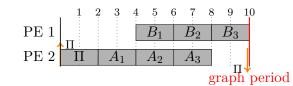

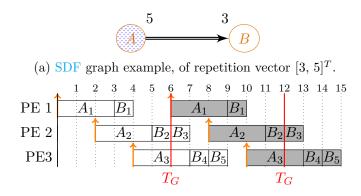

| 3.1 | SDF graph scheduling examples                                                                |

| 3.2 | Example of scheduler and graph iterations, with pipelining                                   |

| 3.3 | Example and counter-example of Assumption 1                                                  |

| 3.4 | Periodic actor $\Pi$ generating an underflow. $\ldots \ldots \ldots \ldots \ldots \ldots 70$ |

| 3.5 | Valid schedule example of graph 3.4a                                                         |

| 3.6 | Counter-example to generalization of Equation (3.6)                                          |

| 3.7 | Floor function underestimation example, as used in Equation (3.7) 73                         |

|     |                                                                                              |

|                                                                            | 70                                        |

|----------------------------------------------------------------------------|-------------------------------------------|

|                                                                            | 76                                        |

| · · · · · · · · · · · · · · · · · · ·                                      | 77                                        |

| SDF graph $G$ and its corresponding SRSDF version $G^*$                    | 78                                        |

| Schedule with an actor period smaller than its WCET.                       | 84                                        |

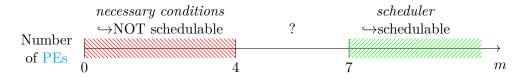

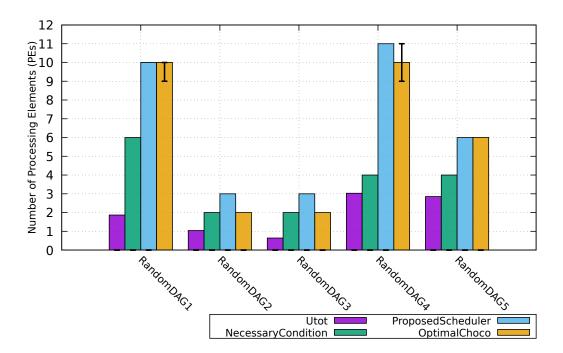

| Scheduling bounds on the number of PEs $m$                                 | 86                                        |

| Evaluation of the schedulability gap on small random graphs                | 89                                        |

| Evaluation of the schedulability gap on large random graphs.               | 90                                        |

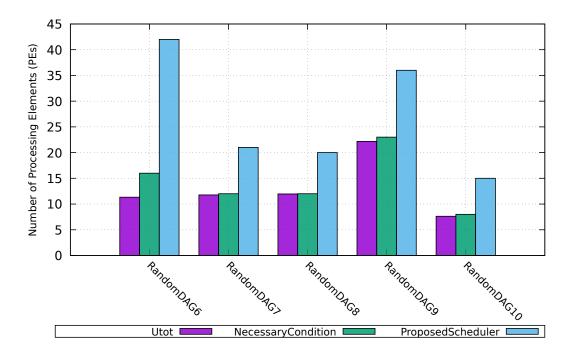

| Graph period refinement example.                                           | 91                                        |

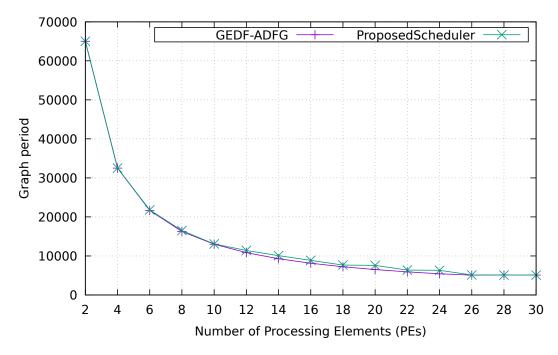

| Evaluation of the graph period computed by Algorithm 3.3 compared to       |                                           |

| ADFG with global EDF policy.                                               | 91                                        |

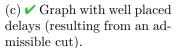

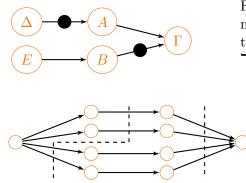

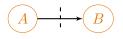

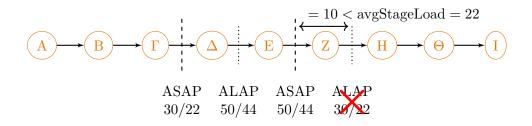

| Topological ordering and schedule example without and with pipeline.       | 99                                        |

| Delay placement examples, resulting from invalid and admissible graph      |                                           |

| cuts                                                                       | .00                                       |

| Graph with valid delay placement distributed on the paths                  | 01                                        |

| Split-join graph with four parallel branches                               | .01                                       |

| Schedule example where pipelining does not compensate for the presence     |                                           |

| of a global barrier                                                        | .03                                       |

| Graph cut example and related schedule for ALAP topological ordering. 1    | .05                                       |

| Graph cut example and related schedule for ASAP topological ordering. 1    | 05                                        |

| Graph cut examples for regular and modified ALAP topological ordering. 1   | .05                                       |

| Preselected and final cuts computed by the delay placement heuristic on    |                                           |

| a sample graph                                                             | 08                                        |

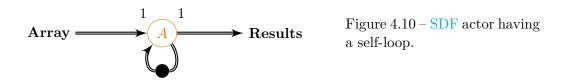

| SDF actor having a self-loop                                               | .09                                       |

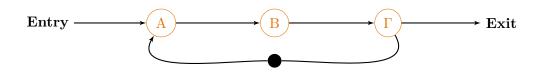

| Cycle example with an entry actor, an exit one and a normal one 1          | 10                                        |

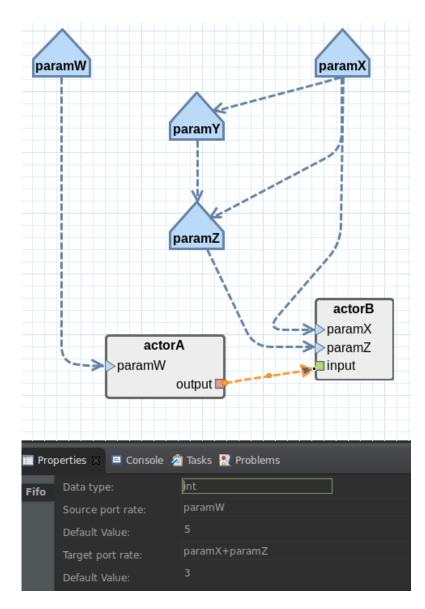

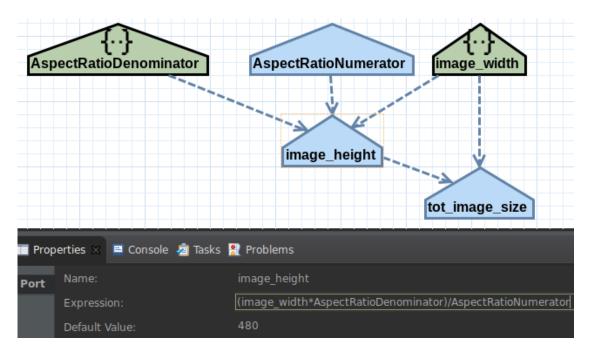

| Example of parameters and their dependencies, here to express image        |                                           |

| resolution choices                                                         | 24                                        |

| Example of a parameterized PISDF graph path                                | 27                                        |

| Example to estimate number of cuts in DSE                                  | 37                                        |

| Dichotomy bounds example of an Integer malleable parameter 1               | 39                                        |

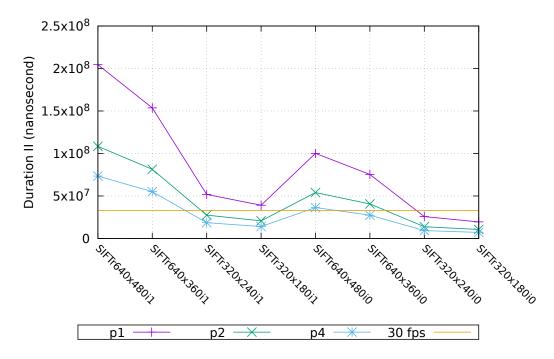

| Duration of II as function of the SIFT application configuration, for dif- |                                           |

| ferent degrees of parallelism $p$                                          | 42                                        |

|                                                                            | Scheduling bounds on the number of PEs m. |

## List of Tables

| 1.1 | Main notations used in this thesis.                                                                                  | 42  |

|-----|----------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Number of scheduled tasks, execution times in ms, and speedup for dif-<br>ferent number of cores                     | 57  |

| 3.1 | Details of the random directed acyclic <b>SDF</b> graphs generated by Turbine, and execution time of the algorithms. | 88  |

| 4.1 | Characteristics and throughput gain with delays (H) of SDF benchmark applications, on four PEs.                      | 114 |

| 4.2 | Throughput gain with delays (H) of SDF benchmark applications, on four PEs.                                          | 115 |

| 4.3 | Throughput gain with delays (H) of SDF benchmark applications, on sixty-four PEs.                                    | 115 |

| 4.4 | Throughput and memory increases with delays (H), on four PEs, for dif-<br>ferent parallelism parameters (p)          | 117 |

| 4.5 | Throughput increases with delays (H), on four PEs, for different paral-<br>lelism parameters (p).                    |     |

| 5.1 | Results of DSE on SIFT video.                                                                                        | 144 |

# List of Algorithms

| 1.1 | Modified DFS before computing the repetition vector $\vec{r}$                           | 37  |

|-----|-----------------------------------------------------------------------------------------|-----|

| 1.2 | Computation of the repetition vector $\vec{r}$ based on the result of Algorithm 1.1     | 38  |

| 3.1 | Modified <b>BFS</b> to compute $nblf_{\pi}^{\uparrow}$ and related necessary conditions | 74  |

| 3.2 | Subroutines for partially periodic scheduling of tasks                                  | 80  |

| 3.3 | Partially periodic scheduling of tasks                                                  | 81  |

| 4.1 | Selection of buffer breaking cycles                                                     | 111 |

# List of Listings

| 1.1 | <b>PISDF</b> parameter definitions and use in Figure 1.6                  |

|-----|---------------------------------------------------------------------------|

| 2.1 | Simple one dimensional (1-D) for loop having explicit parallelism 47      |

| 2.2 | Simple 1-D upscale, by interpolation on the element and its successor 48  |

| 2.3 | Spit SDF actor code                                                       |

| 2.4 | Upscale SDF actor code                                                    |

| 2.5 | Three perfectly nested for loops having explicit parallelism 50           |

| 2.6 | Iteration space simulator for three perfectly nested for loops having ex- |

|     | plicit parallelism                                                        |

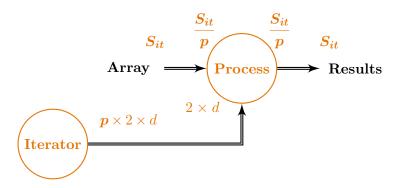

| 2.7 | Non affine 2-D for loop having explicit parallelism                       |

| 2.8 | Non affine 2-D for loop SDF actor code                                    |

| 2.9 | Original non affine 4-D for loop in SIFT                                  |

| 5.1 | Parameter expression implementing a dictionary                            |

| 5.2 | Parameter expression of nLocalKptmax in the SIFT application 126          |

| 5.3 | Sample objective input for the DSE algorithm                              |

| 5.4 | Code of the power threshold comparator of DSE points                      |

| 5.5 | Code of the global comparator of DSE points                               |

| 5.6 | Objective input for the DSE evaluation                                    |

### Acknowledgements

This thesis has received funding from the European Union's (EU) Horizon 2020 research and innovation programme under grant agreement  $N^{\circ}732105$  (project CERBERO) and from the Région Bretagne (France) under grant ARED 2017 ADAMS. First of all, I would like to thank all persons involved in this project. More information about this EU's research program can be found on their website: http://www.cerbero-h2020.eu/.

I would like to thank all the jury members to have reviewed and accepted my thesis: Alain Girault, Johan Lilius, Frédéric Suter and Claire Pagetti. I understood it was quite difficult to read, but thanks to your reviews, I hope that this final version is now readable by anyone interested in Synchronous DataFlow (SDF) graphs. However, I do not guarantee the usefulness of this thesis for the reader!

This thesis has been supervised by Karol Desnos and Jean-François Nezan, and I thank them for all their valuable advice and for their patience. I took a few detours, but finally, we have worked on malleable parameters! I have really liked to work on the topic of this thesis, and I am lucky that you hired me. Actually, I was not the only one that you hired to work on this, I also have to thank Florian Arrestier and Antoine Morvan; the majority of my work relies on their huge SDF and coding skills. Besides, after three years in the same office, Florian has almost convinced me that artificial intelligence and neural networks are useful; I acknowledge my own defeat on this point! During the thesis, I have also been pleased to work with Maxime Pelcat, Mickaël Dardaillon and Shuvra S. Bhattacharyya on different publications. In another collaboration, we have worked with Michael Masin and his team; I thank you and your family for your warm welcome in Haifa!

For sure, I also want to thank all my other colleagues of INSA Rennes and especially the VAADER team. Despite the fact that we are working in a creepy building above a stock of deadly toxic gaz, you manage to make this place enjoyable. And now I understand why everyone likes to work in such a big team, because it means that we have more conference trips, birthdays, and even newborns (!), to celebrate with pastries! I cannot mention all of you here (yes, it is a big team), so I will mention one person who incarnates the most the spirit of the VAADER team, the peaceful and funny guy who never misses a joke nor a crossword: Pierre-Loup Cabarat! And special thanks to Thomas Amestoy, the only person (except my supervisors) who physically attended my defense. Moreover I thank all the team visitors, especially Claudio Rubattu (the beaver pacifier) and Leonardo Suriano (the beaver imitator)!

Before working at INSA Rennes, I also worked during two years approximately 500 meters from there, at INRIA Rennes. When I arrived in Rennes, I did not know anyone so I am deeply grateful to the welcoming TEA, PANAMA and RAINBOW teams and their visitors. Thanks to you I discovered the spirit of life of Brittany, mainly consisting in salty butter, *galettes*, beers, music, and friends to share all of this with. I was thinking to stay only two years at the beginning ... you clearly changed my mind! In the end, I am not even able to leave Rennes a single week-end by fear of missing the amazing Lices' market (one of the biggest in France, even having one "more organic than organic") producer). Again, it is not possible to mention all of you here, but I will start with Simon Lunel, the most Breton of all persons I met in Brittany! Be careful Simon, as Hai-Nam Tran lives in Brest now, he might dethrones you one day... Moreover, I want to mention two friends of the PANAMA team who have defended their PhD one week before and one week after me, and who have supported, if not worsen, my weird taste in movies (Braguino!): Antoine Chatalic (master of *crêpes* baking) and Diego Di Carlo (master of tiramisu baking, or is Giorgia Cantisani the true master of this recipe??). Regarding my weird taste in music, it has been even more worsen by Corentin Louboutin and Valentin Gillot. However, not only food and music are important, so thank you Cássio Fraga Dantas and Jean-Joseph Marty for all the board games you made me discover! And of course, special thanks to my *belote* and billiards partners: Clément Gaultier, Nicolas Bellot and Lesley-Ann Duflot! During the thesis, I also "played" LATFX a lot, a very funny sort of escape game, where you have to find your way out of the numerous bugs that you face while solving some challenges; thank you Katharina Boudgoust for the ultimate LATEX challenge of putting the chapter title in the right margin of this thesis.

This thesis is actually the result of long studies, and by extension the result of all the teachers and supervisors I have had (at ENSEIRB-MATMECA, Pothier, Bertran de Born, ...). I would like to thank them all here, from music teachers (especially French horn and piano) to mathematics teachers. I will only mention Olivier Aumage, Denis Barthou and Jean Roman who have particularly motivated me to finish my engineering diploma, and to continue in the academic field. I do not regret it.

Before Rennes, I have studied in Bordeaux, Orléans and Périgueux. It turns out that almost one third of my friends from there did a PhD. Among them I am currently the last one to have started and defended a PhD, with two or three years of delay, and I have to say: well, you trapped me! But I have no regrets, the friends I have met during the PhD, and the food I have eaten during trips for the PhD (in Sardegna, Haifa and Samos!) clearly compensate for these three years of severe stress. Yes, food is almost as important as friends, especially because it is the first thing you want to share with them! For brevity, I will mention only four of these friends. First, I thank Nicolas Lafon, whose wedding date forced me to send my PhD manuscript on time! Then, I congratulate Thomas Quezel, who managed to avoid my (yet remote) PhD defense thanks to the birth of his first child on the same day! I also want to thank Anastasia Gkolfi, who has inspired me with her sheerest determination to start a PhD, whatever it takes, even to live in the Nordic cold (for her)! Last but not least, Raphaël Angel is certainly the friend who has unconsciously driven me to this PhD. I am deeply grateful to him, especially for having initiated me to my first programming language (Ruby).

Finally, I thank my family, especially my parents and my sister, who know better than anyone at what point this three years were stressful. Thank you for your support, during the thesis, and of course, during all my life. I remember that, as a child, you subscribed me to the *Research EU* magazine which describes the research projects funded by the EU; well, more than fifteen years later, I have been funded by the EU too, it might have had a greater influence than what you think.

To conclude these acknowledgements, I would like to thank XKCD to have perfectly described the entanglement problem of the configuration challenge studied in this PhD:

#### Credit Card Rewards / XKCD

To put you in a good mood before reading this thesis, I suggest you to listen to nice music first, as "La frite équatoriale" composed by François de Roubaix. Playing a good old "Carcassonne" board game might also help, but only if you win at the end!

À Georges, Brigitte et Élisabeth.

## Résumé en français

Au fur et à mesure que les processeurs sont devenus de plus en plus petits et de moins en moins coûteux, ils ont été utilisés dans de plus en plus d'appareils facilitant la vie de tous les jours. L'un des exemples majeurs est le *smartphone*, qui est presque aussi puissant qu'un ordinateur personnel. Les smartphones contiennent même plus de composants qu'un ordinateur : au moins une caméra et une antenne. En 2019, 77% des Français possédaient un smartphone, et 76% avaient accès à un ordinateur personnel<sup>1</sup>.

Chaque composant d'un smartphone peut en réalité contenir son propre processeur. Par exemple, la dernière *smartcamera* Sony MX 500  $\square$  intègre sur une même puce un processeur situé en dessous du capteur d'image, pour une largeur n'excédant pas 1,5 centimètre. Les Systèmes Multi-Processeurs Intégrés sur Puce (MPSoC)<sup>2</sup> sont l'un des principaux ingrédients de ce succès de miniaturisation. Comme les MPSoCs contiennent plusieurs processeurs sur une même puce, ils abritent efficacement une forte capacité de calcul. Cette capacité de calcul peut servir par exemple à stabiliser une vidéo en temps-réel, en utilisant uniquement des algorithmes plutôt que de lourds stabilisateurs mécaniques.

Un smartphone ne contient pas un, mais plusieurs processeurs hétérogènes : des processeurs génériques pour les applications standards, et des processeurs spécifiques à certains types de calcul, tels que pour le traitement du signal. Les calculs se composent généralement de plusieurs tâches à exécuter, formant un graphe. Pour accélérer les calculs, les tâches sont distribuées aux différents processeurs selon leur capacité à exécuter tel type de calcul. La sélection de l'emplacement et de l'ordre des tâches à exécuter sur les processeurs s'appelle l'*ordonnancement*. Le problème d'ordonnancement est complexe à résoudre, et est aussi lié aux moyens de communication reliant les composants.

La création de panorama à partir d'images prises depuis différents points de vue est un autre exemple d'application pour les smartphones et smartcameras. Plusieurs algorithmes peuvent être utilisés pour ces applications logicielles, chacun offrant un dif-

$<sup>^{-1}</sup>$ Ces statistiques sont extraites du rapport officiel Baromètre du numérique 2019  $\square$  .

$<sup>^{2}</sup>$ Les acronymes sont gardés en langue anglaise afin de pouvoir les repérer dans le reste du document, rédigé en anglais. Seules leurs formes étendues sont traduites.

férent niveau de qualité et de rapidité. En sus, l'utilisateur spécifie généralement une Qualité de Service (QoS) minimale définissant des exigences logicielles telle qu'une résolution d'image ou une cadence de prises de vue minimales. Cependant, les applications logicielles de stabilisation d'image ou de création de panorama doivent aussi respecter des contraintes matérielles : cadence et résolution maximales du capteur d'image, puissance maximale de la batterie, ou fréquence maximale du MPSoC. Satisfaire les exigences logicielles en même temps que respecter les contraintes matérielles est également un problème complexe. Ce problème de *configuration* est en général résolu en testant différentes configurations de l'application et du matériel jusqu'à ce que l'une des configurations satisfasse toutes les exigences et contraintes. Le test des configurations possibles correspond à l'Exploration de l'Espace des Designs (DSE). Les configurations diffèrent les unes des autres par la fréquence du MPSoC ou par la résolution d'image supportée par l'application. Si aucune configuration ne satisfait toutes les exigences et contraintes, un compromis est nécessaire et certaines d'entre elles doivent être assouplies.

Au bout du compte, l'adaptation d'une application logicielle à une architecture matérielle telle qu'un smartphone n'est pas triviale. Cette adaptation nécessite de résoudre plusieurs problèmes à la fois, au moins l'ordonnancement et la configuration. Pour ce faire, l'application ainsi que l'architecture sont toutes les deux *modélisées*. Le but du modèle est d'abstraire les propriétés essentielles qui participent aux problèmes d'ordonnancement et de configuration.

Ces problèmes de modélisation, d'ordonnancement et de configuration existent depuis quelques dizaines d'années et sont des sujets actuels de recherche. Par exemple, le Modèle de Calcul (MoC) Synchrone de Flux de Données (SDF) [LM87b] est dédié aux applications de traitement du signal, pour les images ou les antennes. Dans le modèle SDF, les tâches à exécuter et leurs données sont toutes deux représentées. Les tâches et les échanges de données sont prédéterminés par le concepteur, ce qui permet une exécution déterministe de l'application. Le modèle SDF peut être paramétré avec le Méta-Modèle Interfacé et Paramétré (PiMM) [Des+13] par exemple, qui introduit le choix entre plusieurs valeurs de paramètres et le rend donc éligible au problème de configuration. SDF appartient à la grande famille des MoCs orientés flux de données, qui se concentrent sur la représentation des échanges et des traitements de données.

De nombreux outils existent pour automatiquement générer et optimiser le code informatique d'une application logicielle sur une architecture matérielle donnée, tel que SynDEx [GLS99] qui repose sur la méthodologie *Adéquation Architecture Algorithme*. SynDEx optimise l'exécution d'une application de flux de données sur une architecture MPSoC ou autre, en déterminant l'ordonnancement offrant la meilleur cadence par exemple. Cependant, il ne *configure* pas lui-même l'application pour satisfaire des exigences et contraintes. Autrement dit, SynDEx ne va pas automatiquement sélectionner la meilleure résolution d'image pour des contraintes matérielles et des exigences logicielles données. D'autres modèles et outils, comme AADL<sup>3</sup> [Hug+08] et Ptolemy<sup>4</sup> [Guo+14], permettent au concepteur de représenter plus d'informations : l'application, l'architecture, et respectivement les exigences et les contraintes associées. Cette approche aide grandement la vérification de la satisfaction des exigences et contraintes ; mais de même qu'avec SynDEx, le concepteur a toujours besoin de tester lui-même plusieurs configurations avant de choisir la meilleure. L'utilisation d'algorithmes de DSE accélère ce processus, mais ne le résout pas complètement lorsqu'il faut configurer les exigences de QoS. En effet ces outils n'ont pas connaissance des compromis acceptables pour le concepteur.

Finalement, la sélection de la meilleure configuration satisfaisant contraintes matérielles et exigences logicielles sur une architecture matérielle hétérogène est toujours un défi à l'heure actuelle. Ce problème de configuration est composé de plusieurs autres problèmes, dont certains sont introduits dans la section suivante. Les contributions proposées dans cette thèse, concernent trois de ces problèmes en sus de la configuration elle-même. Les sections restantes présentent brièvement le modèle SDF, puis les contributions exposées dans cette thèse, et leurs possibles extensions.

#### Définition du problème

Cette thèse aborde le problème de configuration d'applications SDF paramétrées ayant des exigences logicielles et étant exécutées sur des architectures de multi-processeurs ayant des contraintes matérielles. Nos contributions ne concernent malheureusement que le cas des multi-processeurs homogènes. Le problème de configuration se pose également pour les architectures hétérogènes et est alors d'autant plus difficile à résoudre.

Exécuter un graphe SDF nécessite de résoudre plusieurs problèmes : l'ordonnancement de l'exécution des tâches et celui des échanges de données, l'allocation de la mémoire pour l'exécution des tâches et les échanges de données, tout en prenant en compte les contraintes telles que le nombre de processeurs dans l'architecture et la périodicité de certains tâches. Chacun de ces problèmes est complexe, NP-complet en général. Alors que de nombreux algorithmes existent déjà pour résoudre chacun de ces problèmes, nous nous concentrons sur ceux qui sont rapides et peuvent traiter de grands nombres de

<sup>&</sup>lt;sup>3</sup>C.f. AADL C et OpenAADL C websites.

$<sup>^{4}</sup>$ C.f. Ptolemy  $\square$  website.

tâches à la fois, de sorte que toutes les solutions possibles peuvent être testées dans un court laps de temps, par exemple moins d'une heure.

La rapidité est particulièrement importante pour les graphes SDF paramétrés. Les paramètres sont toujours fixés lors de l'exécution des tâches du graphe les utilisant, mais ils permettent d'explorer automatiquement toutes les configurations possibles, et de réagir dynamiquement à certaines données en entrée qui les modifieraient. En effet, pour l'exploration des configurations, le nombre de configurations peut exploser de manière exponentielle en fonction du nombre de paramètres. Pour l'exécution dynamique, la rapidité est aussi nécessaire pour limiter la surcharge de calculs créée par la résolution dynamique des problèmes d'ordonnancement et d'allocation. Dans cette thèse, nous utilisons le modèle PISDF, qui est l'extension du modèle SDF obtenue en y appliquant le méta-modèle PIMM. Les propriétés dynamiques de PISDF ne sont pas utilisées, et notre travail se restreint à sa sémantique statique afin de trouver à l'avance une bonne configuration de l'application satisfaisant au mieux l'ensemble des contraintes. Pour information, les paramètres matériels tels que la fréquence du processeur, peuvent aussi être représentés par des paramètres de graphes PISDF.

Dans cette thèse, le mot *contrainte* peut autant signifier contrainte matérielle qu'exigence logicielle. Bien que nous ayons distingué les deux notions jusqu'à présent, toutes deux peuvent être liées à la même métrique. Par exemple, la cadence d'images est contrainte par une valeur minimale du côté logiciel, et par une valeur maximale du côté matériel. Les contraintes que nous considérons peuvent être : la périodicité de certaines tâches, la minimisation de l'énergie ou de la puissance à chaque exécution du graphe, la minimisation de la latence ou la maximisation de la cadence des exécutions, la minimisation ou la maximisation de n'importe lequel des paramètres apparaissant dans le graphe PISDF. La sélection de la meilleure configuration s'appuie sur une DSE pour évaluer les plus intéressantes d'entre elles. Ce problème principal de configuration peut être divisé en plusieurs problèmes, dont :

- paramétrisation d'une application statique dans le modèle PISDF;

- modélisation de tâches périodiques dans le modèle PISDF ;

- ordonnancement rapide de graphes PISDF ayant des tâches périodiques ou non;

- modélisation des contraintes de cadence, latence, énergie, puissance ou QoS.

Cette liste est largement incomplète. Nous détaillons maintenant le modèle (PI)SDF, qui est utilisé par toutes les contributions.

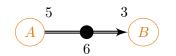

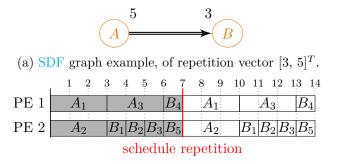

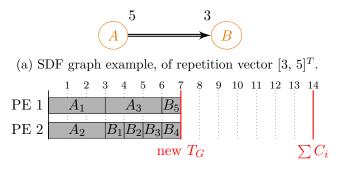

#### Modèle de calcul synchrone de flux de données SDF

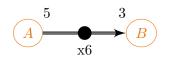

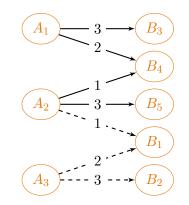

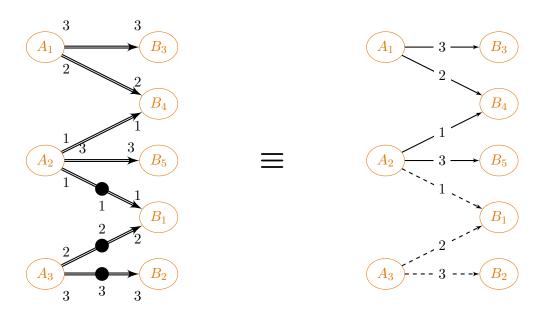

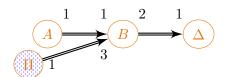

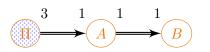

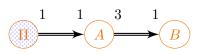

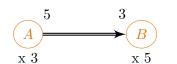

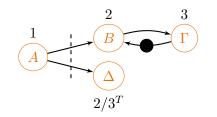

Cette thèse utilise le modèle de calcul PISDF, une extension paramétrée du modèle SDF [LM87b]. La Figure 1a présente un exemple de graphe SDF. Les tâches à exécuter, A et B dans la figure, y sont représentées par les nœuds du graphe. Les échanges de données, de A vers B dans la figure, y sont représentés par les arcs dirigés du graphe. Ces arcs possèdent deux propriétés : un nombre entier précisant la quantité de données produites lors de l'exécution de la tâche à l'extrémité de départ, et symétriquement un nombre entier précisant la quantité de données consommées à l'extrémité d'arrivée. Les arcs correspondent à des files d'attente stockant les données d'une tâche vers l'autre. Chaque tâche peut être le départ ou l'arrivée de plusieurs arcs à la fois. Les arcs peuvent aussi contenir des données présentes avant l'exécution de chacune des extrémités; ces données sont alors appelées délais.

Un des avantages du modèle SDF est son déterminisme. Un effet, grâce aux deux propriétés de consommation et de production de chaque arc, il est possible de déterminer le nombre d'exécution de chaque tâche de sorte que la taille des files d'attente reste bornée au cours du temps. Ce nombre d'exécutions de chaque tâche s'appelle le vecteur de répétition du graphe. Un tel vecteur n'existe pas toujours, et dans cette thèse nous nous intéressons uniquement au cas des graphes SDF cohérents, c'est-à-dire lorsque le vecteur de répétition existe. En somme le vecteur de répétition garantit qu'en exécutant autant de fois toutes les tâches, les files d'attente contiendront toutes autant de données qu'initialement. Dans la Figure 1a, la tâche A est ainsi exécutée trois fois et produit 15 données sur la file d'attente. À l'autre extrémité de l'arc, la tâche B est exécutée cinq fois et consomme donc en tout 15 données également.

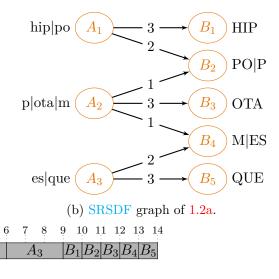

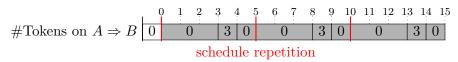

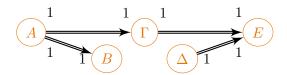

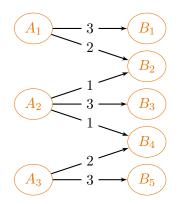

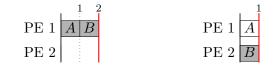

Le problème d'ordonnancement correspond au choix de l'ordre d'exécution des tâches. Cet ordre doit garantir que chaque tâche a suffisamment de données disponibles dans les files d'attente y arrivant, afin de pouvoir consommer autant de données que spécifié au début de son exécution. Quant à la production des données, elle n'est effective qu'à la fin de l'exécution. Pour garantir cet ordre, le graphe SDF est souvent déroulé en un graphe Single Rate SDF (SRSDF) afin d'expliciter les dépendances de données entre les tâches. Un exemple est donné dans la Figure 1b. Les arcs y sont représentés par de simples traits car la quantité de donnée envoyée et reçue sur ces arcs y est fixée et égale ; elle est spécifiée au milieu de chaque arc. Par ailleurs, le graphe SDF original contenait un délai de 6 données, qui supprime donc les premières dépendances de données représentées en pointillé. En effet, grâce au délai, les deux premières exécutions de la tâche B peuvent démarrer avant même que A n'ait commencé à être exécutée. Les 6 données du délai se

#### RÉSUMÉ EN FRANÇAIS

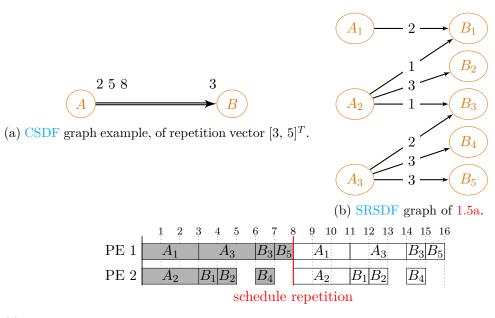

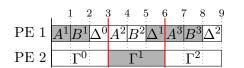

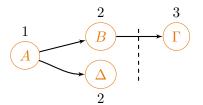

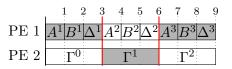

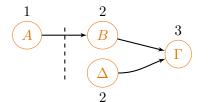

(a) Exemple de graphe SDF, ayant pour vecteur de répétition  $[3, 5]^T$ . Un délai est présent sur l'unique canal de transmission de données, ce qui supprime la dépendance de données depuis les tâches  $A_1$  et  $A_2$  vers  $B_1$  et  $B_2$ .

(b) Graphe SRSDF de **1a**. Les dépendances de données cassées par le délai sont représentées par une ligne en pointillé.

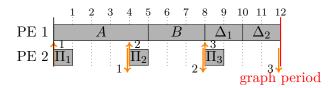

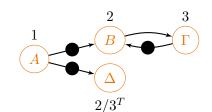

|         | 1 | $\frac{2}{2}$ | 3 | 4 | 5     | 6 | 7 | 8     | 9 | 10      | $1 \atop : 1$ | 12      | 13      | 14    |

|---------|---|---------------|---|---|-------|---|---|-------|---|---------|---------------|---------|---------|-------|

| Proc. 1 | A | $l_1$         |   | Ā | $l_2$ |   | Ā | $l_3$ | I | $B_1 E$ | $B_2 E$       | $B_3 E$ | $B_4 E$ | $B_5$ |

(c) Exemple d'ordonnancement du graphe 1a sur un processeur.

|                                |   | ) 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10  | 11 | 12 | 13 | 14 |

|--------------------------------|---|-----|---|---|---|---|---|---|---|---|-----|----|----|----|----|

| #Données sur $A \Rightarrow B$ | 6 |     | 6 |   | 1 | 1 |   | 1 | 6 | ] | .8] | 15 | 12 | 9  | 6  |

(d) Remplissage de la liste d'attente lors de l'ordonnancement sur 1c. Les nombres sont la quantité de données présente à chaque unité de temps sur la liste d'attente entre les acteurs A et B.

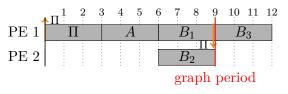

|                                | 1 2      | 3 4   | 5 - 6       | 7 8   | $9 \ 10$  | 11 12 |  |  |  |  |  |  |

|--------------------------------|----------|-------|-------------|-------|-----------|-------|--|--|--|--|--|--|

| Proc. 1                        | $A_1$    | $B_3$ | $A_1$       | $B_3$ | $A_1$     | $B_3$ |  |  |  |  |  |  |

| Proc. 2                        | $A_2$    | $B_4$ | $A_2$       | $B_4$ | $A_2$     | $B_4$ |  |  |  |  |  |  |

| Proc. 3                        | $A_3$    | $B_5$ | $A_3$       | $B_5$ | $A_3$     | $B_5$ |  |  |  |  |  |  |

| Proc. 4                        | $B_1B_2$ | I     | $B_1   B_2$ | 1     | $B_1 B_2$ |       |  |  |  |  |  |  |

| répétition itération du graphe |          |       |             |       |           |       |  |  |  |  |  |  |

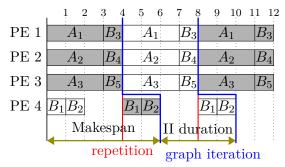

(e) Exemple d'ordonnancement du graphe 1a sur quatre processeurs. Trois répétitions de l'ordonnancement statique sont représentées, séparées par une ligne verticale rouge. Une exécution du graphe de bout en bout est délimitée par les lignes bleues.

(f) Remplissage de la liste d'attente lors de l'ordonnancement surle. Les nombres sont la quantité de données présente à chaque unité de temps sur la liste d'attente entre les acteurs A et B.

FIGURE 1 – Exemple de graphe SDF avec son équivalent SRSDF, et deux ordonnancements possibles avec le remplissage de liste d'attente correspondant. retrouvent initialement dans la file d'attente dont l'évolution est décrite en Figure 1d.

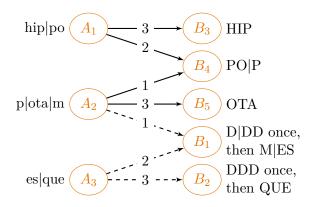

Grâce au graphe de dépendances de données il est possible de réaliser l'ordonnancement, dont un exemple est représenté sur la Figure 1c pour un processeur. L'ordonnancement correspond au placement et à l'ordre d'exécution d'autant de tâches que spécifiées dans le vecteur de répétition. Cet ordonnancement est ensuite répété indéfiniment (une fois dans la figure). L'écoulement du temps est représenté par l'indexation au-dessus de l'ordonnancement. La durée d'exécution de chaque tâche est fixée a priori et ne varie pas en fonction du temps. L'ordonnancement de la Figure 1c dure 14 unités de temps et la cadence du graphe est donc 1/14. L'ajout de délais permet parfois de réduire ce temps d'exécution lorsque plusieurs processeurs sont disponibles. L'ordonnancement représenté en Figure <u>le</u> pour quatre processeurs ne dure que 4 unités de temps. Dans ce cas, comme des dépendances de données sont supprimées grâce au délai du graphe initial, on parle de *pipelinage.* En effet, certaines exécutions de *B* chevauchent dans le temps les exécutions de A correspondant à une précédente exécution du graphe de bout en bout, ce qui ne serait pas possible sans délai. Une exécution du graphe de bout en bout, aussi appelée itération du graphe, est représentée en Figure 1e sans couleur de fond et délimitée par les lignes bleues.

Finalement, la paramétrisation des graphes SDF revient simplement à remplacer les nombres entiers utilisés pour les tailles de délais, les propriétés de consommation et de production, et pour les durées d'exécution des tâches, par des expressions arithmétiques utilisant des variables mathématiques. Ces expressions sont évaluées avant la transformation du graphe SDF vers le graphe de dépendance de données SRSDF correspondant.

#### Contributions

Dans cette thèse, nous présentons quatre contributions, dont la principale est la configuration automatique de graphes PISDF grâce à une DSE. Les trois autres contributions aident toutes à réaliser cette DSE, par le biais de la modélisation de contraintes ainsi que de l'ordonnancement respectant ces contraintes. Les contributions sont brièvement résumées dans les paragraphes suivants ; chaque contribution correspond à un chapitre de la présente thèse. L'application de traitement d'image SIFT [Low04] est notre principal cas d'utilisation et sert à réaliser les évaluations expérimentales des contributions présentées dans les chapitres 2, 4 et 5.

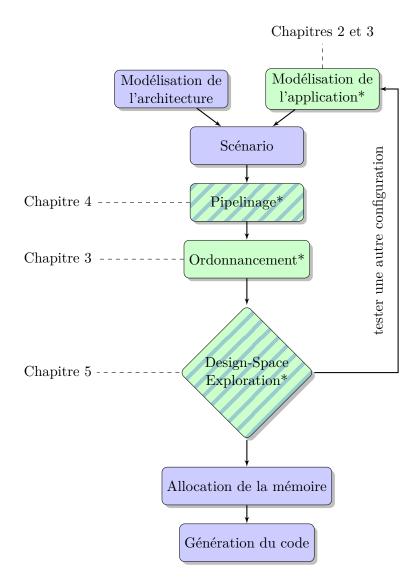

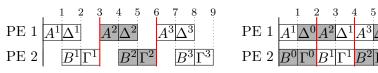

La Figure 2 représente schématiquement comment nos contributions sont intégrées au l'outil PREESM [Pel+14] qui permet de développer des applications dans le modèle PISDF. Comme SynDEx, PREESM sépare la modélisation de l'architecture de celle de l'application. La phase *Scénario* dans la Figure 2 permet de définir les informations spécifiques à la fois à une application et à la fois à une architecture, telles que les durées d'exécution de chaque tâche. Nos contributions correspondent aux phases vertes<sup>\*</sup> : modélisation de l'application, pipelinage, ordonnancement et DSE. La configuration est réalisée lors de la DSE.

FIGURE 2 – Logigramme des contributions telles qu'utilisées dans l'outil PREESM. Les boîtes vertes<sup>\*</sup> correspondent aux contributions. Le motif hachuré indique les contributions qui sont optionnelles lors de l'utilisation de PREESM.

Chapitre 2 : modélisation des boucles for imbriquées dans le modèle SDF. Le point de départ de la conception d'une application est sa modélisation. Cependant, il n'est pas commun de commencer directement par le modèle SDF, et beaucoup de concepteurs développent d'abord un prototype utilisant les langages de programmations impératifs les plus répandus comme C ou Java. Dans cette contribution, nous étudions la modélisation des boucles for, l'une des plus importantes structures de contrôle des langages impératifs. Plus spécifiquement nous introduisons les *itérateurs SDF*, qui permettent la modélisation des boucles for parfaitement imbriquées avec du parallélisme explicite. Les itérateurs SDF sont particulièrement utiles lorsqu'ils sont paramétrés. Dans ce cas, nous montrons comment adapter la parallélisation des boucles aux nombres de processeurs disponibles dans l'architecture. La parallélisation est le fait de répartir les calculs des tâches sur plusieurs processeurs de sorte que le temps d'exécution de l'ordonnancement est plus court.

Chapitre 3 : ordonnancement partiellement périodique des graphes SDF. Dans cette contribution, nous étudions la modélisation de contraintes de périodicité de certaines tâches, par exemple exécutées toutes les 10 unités de temps. Dans le contexte des graphes SDF, ces contraintes entraînent l'existence d'une période du graphe. Nous détaillons un algorithme permettant d'ordonnancer le graphe en respectant les contraintes de périodicité de ses tâches. Cet algorithme est rapide car il appartient à la famille des ordonnanceurs par liste de priorité, statiques et non préemptifs. Non préemptif signifie que lorsqu'une tâche commence son exécution, il n'est pas possible de l'arrêter avant sa complétion.

Chapitre 4 : pipelinage automatique de graphes SDF. Dans cette contribution, nous présentons un algorithme calculant automatiquement les tailles de délais nécessaires au pipelinage. Cette contribution n'est pas mentionnée dans le problème de départ mais elle aide à réduire le temps d'exécution d'un ordonnancement. De ce fait, cette contribution aide à réaliser la configuration sous contrainte de cadence.

Chapitre 5 : configuration de graphes SDF paramétrés. Cette dernière contribution aborde le problème principal de configuration automatique de graphes PISDF. Plusieurs algorithmes de DSE sont proposés, exhaustifs ou non, afin de sélectionner la meilleure configuration de graphes PISDF en fonction des contraintes spécifiées. Les contraintes peuvent concerner l'énergie, la puissance, la latence, la cadence ou la QoS par le biais de n'importe quel paramètre du graphe, tel que la résolution d'image. Cette contribution repose sur les trois précédentes : elle paramétrise les itérateurs SDF avec le niveau de parallélisme adéquat, elle évalue chaque configuration grâce à l'ordonnanceur de tâches avec périodicité, et finalement elle ajoute des délais pour améliorer la cadence lorsque cela est possible.

#### Conclusion et extensions

Dans cette thèse, nous avons étudié le problème de configuration des graphes SDF paramétrés ayant des contraintes de QoS et étant exécutés sur des architectures multiprocesseurs hétérogènes ayant des contraintes matérielles. Pour résoudre ce problème, nous avons proposé quatre contributions concernant la modélisation, l'ordonnancement, le pipelinage et la configuration elle-même. Malheureusement ces contributions sont limitées au cas des architectures multi-processeurs homogènes. Néanmoins, les évaluations expérimentales ont montré que le problème de configuration peut être résolu pour le cas homogène en un temps raisonnable de quelques minutes, avec des contraintes sur la résolution d'image ou la fréquence du MPSoC. Les contraintes d'énergie, de puissance, de latence et de cadence sont aussi considérées. En particulier nous avons pu configurer l'application de traitement d'image SIFT pour une utilisation en temps-réel, de sorte que la qualité d'image est maximisée tout en respectant une contrainte de cadence de 30 images par seconde. Toutes nos contributions sont implantées dans l'outil libre PREESM.

Parmi les extensions possibles, il est primordial de résoudre le problème de configuration pour les architectures hétérogènes, qui sont la norme des MPSoCs modernes. Par ailleurs, nos contributions ne prennent pas en compte les temps de communications ni les limites de la mémoire des systèmes intégrant ces MPSoCs. Pour attaquer ce cas plus général, nous pensons que deux domaines sont particulièrement importants : (1) l'analyse symbolique des paramètres et (2) le raffinement de solution par mesures réelles. Le domaine (1) permettrait de rapidement connaître l'évolution des objectifs en fonction des paramètres sans avoir à tester toutes les configurations. Le domaine (2) permettrait d'évaluer la configuration choisie dans son environnement réel, car un modèle ne modélise jamais tout. Enfin, l'extension de nos travaux par les domaines (1) et (2) rendrait possible d'effectuer les configurations de manière dynamique, par exemple pour pallier en temps-réel la panne d'un des processeurs.

### Introduction

As computer processors went smaller and cheaper, they have been used in more and more devices easing the human life. One of the most iconic example is the smartphone, which is now almost as powerful as a personal computer. Smartphones embed even more components than a computer: at least one camera and an antenna. In 2019, 77% of French people owned a smartphone, and 76% had a personal computer<sup>5</sup>.

Each component of a smartphone may actually contain its own processor. For example, the latest *smartcamera* Sony MX 500 C<sup>2</sup> integrates a processor directly on the chip embedding the image sensor, not larger than 1.5 centimeter. Multi-Processor Systemon-Chips (MPSoCs) are one of the main ingredients for this miniaturization success. Since MPSoCs contain multiple Processing Elements (PEs) on a single chip, they host on-site efficient computation capacities which for example, allow us to stabilize a video in real-time on our smartphone using algorithms instead of heavy mechanical stabilizers.

A smartphone contains not one, but multiple heterogeneous processors: multiple generic processors for regular applications, and specific processors dedicated to a kind of computations such as signal processing. Computations are generally composed of multiple tasks to execute, forming a graph. To accelerate the computations, their tasks are shared over the processors and the specific processors execute the tasks they are dedicated to. To select where and when to execute the tasks, that is *scheduling*, is a complex problem to solve, also related to means of communication between the components.

Another smartphone and smartcamera application example is the creation of panorama pictures thanks to regular pictures from different point of views. Multiple algorithms may be used in such software applications, each offering a different degree of quality and rapidity. Moreover, the user generally sets software requirements defining its minimal Quality of Service (QoS), such as the minimum image resolution or the minimum frame rate. Yet, stabilization or panorama software applications require to be adapted to the smartphone hardware constraints: maximum image resolution and frame rate of the camera, maximum available power of the battery, maximum frequency of the MPSoC. Meeting software requirements while respecting hardware constraints is also a

$<sup>^5</sup>$  Statistics extracted from the official French report Baromètre du numérique 2019  $\ensuremath{\ensuremath{\mathbb{C}}}$  .

#### xxviii

challenging problem. This *configuration* problem is generally solved by testing different configurations of the application and the hardware, that is Design Space Exploration (DSE), until one matches all constraints and requirements. For example, configurations may differ by the MPSoC frequency, or by the image resolution supported by the application. If no configuration matches all constraints and requirements, a trade-off is necessary. In such case, a few constraints or requirements have to be relaxed.

In the end, the adaptation of a software application to a target hardware architecture, such as a smartphone application, is not trivial. This adaptation requires to solve multiple problems at the same time, at least scheduling and configuration. To solve these two problems, both the application and the architecture are *modeled*. The goal of the model is to abstract the key properties which are involved in the scheduling and configuration problems.

These modeling, scheduling, and configuration problems are all active research fields existing for a few decades. For example, the Synchronous Data Flow (SDF) [LM87b] Model of Computation (MoC) is dedicated to signal processing applications, including processing tasks on image and antenna signals. In the SDF model, both processing tasks and their data are represented. Processing tasks and data exchanges are fixed by the designer and the SDF model allows for a deterministic execution of the application. SDF may be *parameterized* with Parameterized Interfaced Meta-Model (PIMM) [Des+13] for example, giving choice between multiple possible values and making it eligible for the configuration problem. SDF belongs to the wide family of *dataflow* MoCs, which focus on the representation of data exchanges and data processing.

Many tools exist to automatically generate and optimize the code of a software application on a specific hardware architecture, as SynDEx [GLS99] implementing the *Algorithm Architecture Adequation* methodology. SynDEx optimizes the execution of a dataflow application on an architecture as an MPSoC, by selecting the shortest possible schedule for example. However, it does not *configure* the application in order to meet both hardware constraints and software requirements. For instance, SynDEx will not select automatically the best parameter value of image resolution given hardware constraints and software requirements. Other models and related tools, such as Architecture Analysis and Design Language (AADL)<sup>6</sup> [Hug+08] and Ptolemy<sup>7</sup> [Guo+14], enable the designer to represent more information: the application, the architecture, and respectively some of their requirements are met, but as with SynDEx, designers still need to test

<sup>&</sup>lt;sup>6</sup>See AADL  $\square$  and OpenAADL  $\square$  websites.

<sup>&</sup>lt;sup>7</sup>See Ptolemy ♂ website.

different configurations before selecting the best one. Using DSE algorithms accelerates this selection process, but does not completely solve it yet, especially when configuring software requirements or software QoS.

Finally, selecting the best configuration to meet hardware constraints and software requirements on an heterogeneous hardware architecture is still a modern challenge. This configuration problem is composed of multiple other problems, some of which are introduced in the next section. The contributions proposed in this thesis concern three of theses problems plus the configuration itself. The configuration and related problems are introduced in the next section. Our contributions are listed in the second section of this introduction. Then, chapter 1 presents the background of this thesis. The contributions are detailed in Chapters 2 to 5 and each contribution has its own specific related work. As the last contribution uses the three previous ones, we advise the reader to read this thesis in order.

#### **Problem statement**

This thesis tackles the configuration problem of parameterized SDF applications having software requirements and running on multi-processor architectures having hardware constraints. The contributions proposed in this thesis consider only homogeneous multi-processor architectures containing multiple identical PEs. However, the same configuration problem applies for heterogeneous architectures, and is even more difficult to solve in such case.

Executing an SDF graph requires to solve multiple problems: the scheduling of the tasks and the one of data exchanges, the memory allocation for tasks execution and the one for data exchanges, while taking into account constraints such as the number of PEs in the architecture and the periodicity of some tasks. Each of this problem is complex, NP-complete in the general cases. While many algorithms already exist to solve each problem, we focus on the fast and scalable ones, so that all solutions can be tested in a short time, for example, in less than one hour.

Rapidity is especially needed when considering parameterized SDF graphs. The parameters have still to be fixed when executing the processing tasks of the SDF graph using them, but they allow algorithms to automatically explore different configurations, or to react dynamically to inputs. Indeed for configuration exploration, the number of configurations may explode exponentially in the number of parameters. And in the dynamic case, rapidity is needed to limit the overhead created by online solving of the scheduling and allocation problems. In this thesis, we use the Parameterized Interfaced Synchronous Data Flow (PISDF) MoC, an extension of SDF parameterized with PIMM. The dynamic properties of PISDF are not used, and instead we restrict our work to its static semantics to find offline a suitable configuration of the modeled application, fitting all its constraints when possible.

In this thesis, the word *constraint* may refer to both hardware constraint and software requirement. Although we have distinguished software requirement from hardware constraint in the previous paragraphs, both may be related to the same metric. For instance, the frame rate is constrained by a minimum value the software side and a maximum value on the hardware side. Constraints may be the real-time periodicity of some tasks, the minimization of energy or power consumption per execution, the minimization of latency and the maximization of throughput of the executions, the minimization or maximization of any graph parameter to ensure QoS. The choice among multiple configurations results from a DSE to evaluate the interesting ones. This main configuration problem may be split into multiple problems, a non-exhaustive list follows:

- parameterization of static applications in the PISDF MoC;

- modeling of periodic tasks with the PISDF MoC;

- rapid offline scheduling of **PISDF** graphs having periodic tasks;

- modeling of the throughput, latency, energy, power and QoS constraints.

We now detail our contributions with regard to the main problem and the list above.

#### Contributions

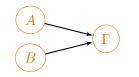

In this thesis we present four contributions, one of which is the configuration of PISDF graphs via automatic DSE. The three other contributions all help to perform this DSE, by the modeling of constraints and the scheduling of tasks respecting them. The contributions are briefly summarized in the next paragraphs; each contribution corresponds to a chapter of this thesis. The Scale Invariant Feature Transform (SIFT) [Low04] image processing application provides our main use-case; it is used in the experiments all along the thesis, in Chapters 2, 4 and 5.

Figure 3 illustrates how our contributions are related in the design process. All have been implemented in the Parallel and Real-time Embedded Executives Scheduling Method (PREESM) [Pel+14] tool supporting the PISDF model. Note that as SynDEx, PREESM separates architecture modeling from application modeling, and the *scenario*

Figure 3 – Flowchart of the contributions as used in the PREESM framework. Green<sup>\*</sup> boxes correspond to contributions. The hatch pattern indicates the contributions which are optional in the PREESM workflow.

node in Figure 3 stores information specific to one architecture and one application, as the Execution Times (ETs) of each task. Our contributions concern the green\* steps: application modeling, pipelining, scheduling and DSE, which performs configuration.

**Chapter 2: Modeling nested for loops, with SDF graphs.** The starting point of the design of an application is its modeling. However, it is not common to start with an SDF model, and many designers first develop a prototype using widespread imperative

programming languages as C or Java. In this contribution we study the modeling of **for** loops, one of the most important control structure in imperative languages. More specifically we introduce *SDF iterators*, which support the modeling of perfectly nested **for** loops having explicit parallelism. SDF iterators are especially useful if parameterized. In such case, we show how to adapt the parallelization of loops to the number of **PEs** in the target architecture. Parallelization is the process of splitting computations of a task on multiple **PEs**, so that its execution time is shorter.

**Chapter 3:** Scheduling partially periodic SDF graphs. In this contribution, we study the modeling of periodicity constraints, expressed on some tasks but not all. In the context of SDF graphs, we show that any task period enforces a common graph period. We develop an algorithm to schedule the graph while respecting the periodicity constraints. This algorithm belongs to the family of offline static non-preemptive *list schedulers* and thus is rapid and scalable. Non-preemptive means that when starting the execution of a task, it is not possible to stop it.

**Chapter 4:** Pipelining SDF graphs automatically. SDF graphs model the exchange of data between tasks, and it is possible to feed these exchanges with initial data, present before the execution. These initial data are called *delays*. They break the data dependencies and thus they may improve the scheduling result, giving a greater execution throughput. In this contribution, we present an algorithm to automatically add such delays on an SDF graph. This process is called *pipelining*. While this contribution is not mentioned in the problem statement, it helps to solve the main problem by providing more possible configurations.

**Chapter 5:** Configuration of parameterized SDF graphs. This contribution tackles the main problem, that is the automatic configuration of PISDF graphs. It provides multiple DSE algorithms, exhaustive or not, to select the best PISDF graph configuration with regard to multiple constraints. Constraints may be on energy, power, throughput, latency, or QoS via any parameter, as the image resolution. This contribution uses all the three others; it parameterizes the SDF iterators with the correct amount of parallelism, it evaluates each configuration thanks to our fast list scheduler and finally, it adds delays if the throughput can be improved.

## Chapter 1

# Background

#### Contents

| 1.1 I | troduction: hardware, software, and parallelism 2 |  |

|-------|---------------------------------------------------|--|

| 1.1   | 1 Common tools and hardware 3                     |  |

| 1.1   | 2 Software side                                   |  |

| 1.1   | 3 Hardware side                                   |  |

| 1.2 7 | ne SDF dataflow model and its flavors             |  |

| 1.2   | 1 Original SDF                                    |  |

| 1.2   | 2 Static SDF flavors                              |  |

| 1.2   | 3 Dynamic SDF flavors                             |  |

| 1.3 S | heduling of SDF graphs 22                         |  |

| 1.3   | 1 Scheduling techniques                           |  |

| 1.3   | 2 Tools and benchmarks                            |  |

| 1.3   | 3 Analysis for scheduling efficiency              |  |

| 1.4 7 | ne PREESM tool                                    |  |

| 1.4   | 1 Architecture of a PREESM project                |  |

| 1.4   | 2 Definition of PISDF graphs and parameters       |  |

| 1.4   | 3 Computation of the repetition vector            |  |

| 1.4   | 4 Single-Rate graph and special actors            |  |

| 1.5 C | onclusion                                         |  |

| 1.5   | 1 Model used in this thesis 41                    |  |

| 1.5   | 2 Main notations                                  |  |

In this thesis, we study the configuration of a software application with Quality of Service (QoS) constraints which has to be executed on a specific hardware architecture. In this chapter, we briefly introduce the main concepts related to this configuration problem, especially *parallelism*, on the hardware and software sides. In Section 1.2, we introduce the main model used in this thesis, the Synchronous Data Flow (SDF) Model of Computation (MoC). For each contribution, a specific related work is presented at the end of the corresponding chapter. Thus, the Section 1.3 presenting the scheduling and the analysis of Synchronous Data Flow (SDF) graphs only gives an overview of these concepts. The Parallel and Real-time Embedded Executives Scheduling Method (PREESM) tool used to implement the contributions of this thesis is described in Section 1.4. In Section 1.5, we briefly recall the characteristics of the model used in this thesis and give notations which are common to all chapters.

#### 1.1 Introduction: hardware, software, and parallelism

*Parallelism* is the simple fact to execute two tasks in parallel. In the everyday life, cooking is an example of activity where we often parallelize tasks. The parallelism is clearly written in good recipes, in general stating: "while this thing is cooking, do something else". In the french recipe of "la tourte aux blettes ✷ ", it is possible to cook the pears while preparing the grapes and pine nuts. This kind of parallelism is called *task parallelism*. To perform multiple different and independent tasks in parallel accelerates the cooking process. Another way to accelerate the process is to have multiple cookers performing the same task, for example each cooker peels one pear. This is data *parallelism*, where the same task is performed on multiple inputs. The metaphor between cooking and computer science can also be used for the software and hardware sides. The software side is the recipe itself, that is the list of tasks to execute and extra instructions on how to perform those tasks. The hardware side corresponds to the equipment and the cookers. Cookers are the Processing Elements (PEs) processing the food. When the food is not used, you place it in the fridge, that is the memory of a computer. Last but not least, cooking comes with QoS constraints: the food must be good and served before it becomes cold. In any restaurant, the main ingredient to respect the QoS actually is parallelism. The chef is not only here to create the recipes but also to schedule the tasks of the cookers.

In computer science, parallelism helps to accelerate the computations when multiple Processing Elements (PEs) are available. Then, heavy computations such as weather forecast, can be executed in a reasonable time. In the following subsections, we list

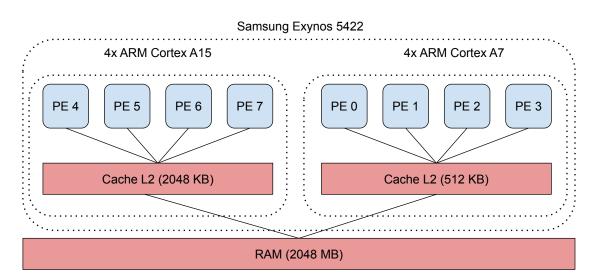

Figure 1.1 – Samsung Exynos 5422 MPSoC architecture: ARM big.LITTLE design with 4x Cortex A15 (@ 2.1 GHz) and 4x Cortex A7 (@ 1.5 GHz) CPUs. It also embeds a GPU, not depicted here. Odroid XU3 board contains one Samsung Exynos 5422 and 2 Gbytes of RAM. Only LLC size is specified.

some of the main tools to perform parallelism. In Section 1.1.1, we list programming languages and libraries dedicated to parallelism on regular Multi-Processor System-on-Chips (MPSoCs). Programming languages are a common way to represent the recipes in computer science, and we precise their main concepts in Section 1.1.2 dedicated to the software side. Multiple kinds of hardware are listed in the last Section 1.1.3.

#### 1.1.1 Common tools and hardware

Parallelism is made possible on the hardware side by the possibility to use multiple PEs of a multi-processor architecture. Figure 1.1 depicts a MPSoC architecture having 8 PEs of two different types. A main Random Access Memory (RAM) memory is accessible from all PEs. To continue the cooking metaphor, the architecture is the map and the elements of the kitchen, that is the position of the fridge compared to the gas stoves, and the number of gas stoves.

The most common way to use all PEs at the same time is to create *threads* defined by the Operating System (OS) running on the MPSoC. Threads are a Model of Computation (MoC). Each thread contains a list of tasks to execute successively. There might be more threads than PEs. In such case, extra threads are not executed until a currently executed one finishes or is suspended. The OS may suspend the execution of any thread to execute

3

another one; this is called *preemption*. Suspended threads can continue their execution later on any PE, not necessarily the same as previously. One role of the OS is to ensure that threads will be completed sooner or later.

Threads can express both data and task parallelism. When there is only one *shared* memory, threads can exchange data between them without specific communication *library*. A library is a set of predefined functions made available to the designer. However, if multiple threads have to work on the same data, a lock system may be needed to ensure that multiple data writes do not occur at the same time for example. Semaphores between threads are the main lock system to temporarily limit parallelism. Parallelism limitations are called *bottlenecks* and reduce the execution time of an application. The extreme case of parallelism limitation is *mutual exclusion*, which enforces that only one thread is executed at a time, even with multiple available PEs.

### Parallelism through programming languages

Programming languages help to express the computations of an application. The text files written in any programming language are called the *code* of the application. They correspond to the language in which the cooking recipe is written. Their main advantage is to be readable by human programmers, and by either *compilers* or *interpreters* which translate the code into binary instructions for the OS or directly for the PEs.

Most of the modern programming languages support the thread MoC through native libraries: C/C++, Python, Java, etc. Some languages can even represent parallel computation directly in the language without exposing a thread library: ADA, Cilk, Chapel, Erlang, LARA [Car+12], ABS [Joh+12], etc. Programming languages supporting threads generally offer at least two functions: one function to create and launch a thread, that is to make the thread executable by the OS, and one function to wait for the completion of a thread. This is the *fork-join* model. Waiting for the completion of multiple threads is called a *synchronisation*. It is also possible to synchronize threads before their completion, usually with semaphores.

### Parallelism through compiler

Mastering programming languages is difficult, especially when using threads. Human programmers have to find which tasks may be executed parallel, which data have to be protected for writing, which threads to wait and when, etc. The compiler does not only translate the code for the PEs, but it can also perform parallelism automatically in a few cases. For example, C/C++ compilers can control fine grain parallelism available

on vector PEs implementing the SSE/AVX binary instruction sets. Such instruction sets offer data parallelism at the instruction level: the same instruction is executed on multiple data at the same time by only one PE.

However, both fine grain parallelism controlled by the compiler and coarse grain parallelism controlled by the programmer are difficult to use properly. Thus, it is common to perform automatic code analysis and source-to-source transformations, such as in the PIPS [IJT91] tool, to discover and improve parallelism. An important class of static analysis is the polyhedral analysis [FL11], used in [Bon+08; NC12] for example. Another alternative is to use modulo scheduling [RST92]. In order to guide the transformation, it is also common to use annotations as in [KL12] or pragma as for the OpenMP or OpenACC libraries. Sometimes transformations are guided by interaction with the programmer as in Parascope [Bal+89] in the past and in a few modern tools [Lar+12].

The OpenMP library is a major library for data and task parallelism. It is especially useful to parallelize **for** loops, iterating over an array for example. If operations on the elements of the array can be performed in parallel, the programmer indicates to OpenMP and the compiler that the operations of the loops may be split over threads. OpenMP will automatically create the threads and wait for them.

### Parallelism through task and array manager

However OpenMP is not perfect for multiple reasons. The main reason is that OpenMP offers a small amount of scheduling policies managing the start time of the threads. Policies of OpenMP are efficient for homogeneous architectures having identical PEs, but not always for heterogeneous architectures. Many libraries are designed for this purpose, as StarPU [Aug+11], PaRSEC<sup>1</sup>, or XKaapi [Gau+13]. Such libraries can be interfaced with OpenMP so that the programmer does not change the pragma annotations in the code, but the scheduling policy of OpenMP is replaced by the one of the library. Such libraries are usually called *runtime managers*. Many other parallelism libraries exist, especially for arrays: DASK<sup>2</sup> and Kokkos [ETS14].

In any case, with such parallelism libraries, programmers need to indicate by themselves where parallelism is available in the code and when synchronizations are needed. Dedicated tools may help to locate where parallelism is possible and when it is not, for example, STABILIZER [CB13] and COZ [CB18]. To locate where parallelism is possible is a difficult task, depending on the model used to represent applications. In

<sup>&</sup>lt;sup>1</sup>http://icl.utk.edu/parsec/

<sup>&</sup>lt;sup>2</sup>https://dask.org/

this subsection, we have listed the main programming languages and libraries supporting the thread MoC. In the next subsection, we present concepts and MoCs related to parallelism, especially data flow programming which is used in this thesis.

#### 1.1.2 Software side

Modern programming languages such as Python or Java are widely used for regular applications. Threads or libraries upon threads are available in these languages and ease the expression of parallelism, but they require caution from the programmer and extensive analysis of the compilers or the libraries to be used efficiently. Indeed, managing data accesses between threads is error-prone, and introduce synchronizations to avoid concurrent data accesses, thus creating bottlenecks. A common source of errors with threads is the introduction of *deadlocks*, for example when two threads wait for the completion of the other one before continuing the execution of their own tasks. Another source of error is the memory management when exchanging or storing data. Some concepts and MoCs are dedicated to model specific behaviors of the applications, so that the design process is easier to use for programmers and easier to analysis for compilers. Such main concepts are: *control flow* and *data flow*.

#### Control flow and data flow

Control flow fixes the order of the computational tasks to execute. Especially, the **if/else** control flow conditional statements of *imperative* languages, such as Python or Java, enable the programmer to select a *branch* of instructions depending on the result of previous computations. In a way, it is the opposite of parallelism since only one branch is executed among all possible, the other branches of **if/else** statements will never be executed. Threads available in imperative languages are the only way to escape such exclusive choices and fixed orderings. Threads actually move part of the ordering of tasks from the programmer responsibility to the OS or runtime library responsibility. Imperative languages are control flow oriented.