## Etude de durcissement de la technologie 28 nm FDSOI aux très fortes doses de radiation ionisante

Alejandro Urena Acuna

## ► To cite this version:

Alejandro Urena Acuna. Etude de durcissement de la technologie 28 nm FDSOI aux très fortes doses de radiation ionisante. Other. Université Paris-Saclay, 2021. English. NNT : 2021UPAST082 . tel-03339535

## HAL Id: tel-03339535 https://theses.hal.science/tel-03339535

Submitted on 9 Sep 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Etude de durcissement de la technologie 28nm FDSOI aux très fortes doses de radiation ionisante

Thèse de doctorat de l'Université Paris-Saclay

École doctorale n° 575, EOBE: Physique et ingénierie: Electrons, Photons, Sciences du vivant Spécialité de doctorat: Electronique et optoélectronique, nano- et microtechnologies Unité de recherche: Université Paris-Saclay, CEA, Institut LIST, 91191, Gif-sur-Yvette, France Référent: ENS Paris-Saclay

> Thèse présentée et soutenue à Palaiseau, France, le 6 Juillet 2021, par

## **Alejandro URENA ACUNA**

## **Composition du jury:**

| Arnaud BOURNEL                                                                                           | Président    |

|----------------------------------------------------------------------------------------------------------|--------------|

| Professeur des universités, Université Paris-Saclay<br>Jean-Luc AUTRAN                                   | Rapporteur   |

| Professeur des universités, Aix-Marseille Université, Université de Toulon                               |              |

| Jerôme BOCH                                                                                              | Rapporteur   |

| Professeur des universités, Université de Montpellier<br>Lirida ALVES DE BARROS NAVINER                  | Examinatrice |

| Professeure, Telecom ParisTech<br><b>Luigi DILILLO</b><br>Chargé de recherche, Université de Montpellier | Examinateur  |

| Philippe DOLLFUS                                                                                         | Directeur    |

| Directeur de recherche CNRS, Université Paris-Saclay<br>Jean-Marc ARMANI                                 | Encadrant    |

| Ingenieur chercheur, CEA-LIST<br>Mariem SLIMANI<br>Ingenieur chercheur, CEA-LIST                         | Encadrante   |

| Ingenieur chercheur, CLA-LIST                                                                            |              |

'hèse de doctorat

NNT: 2021UPAST082

#### ÉCOLE DOCTORALE

Physique et ingénierie: Electrons, Photons, Sciences du vivant (EOBE)

**Titre:** Etude de durcissement de la technologie 28nm FDSOI aux très fortes doses de radiation ionisante

**Mots clés:** Dose Totale Ionisante (TID), Microélectronique, Fully-depleted Silicon-On-Insulator (FDSOI), Durcissement, Régénération, Température, Compensation, Tension de grille arrière.

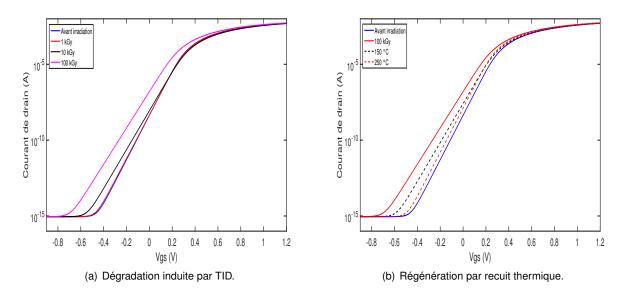

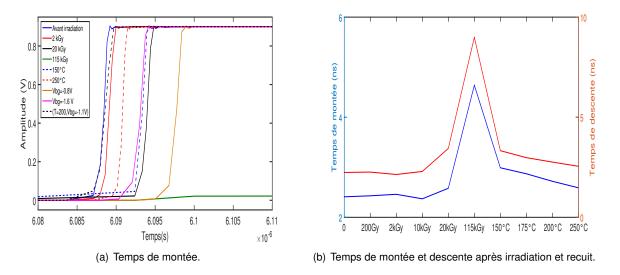

**Résumé:** Les rayonnements ionisants provoquent des dysfonctionnements dans les systèmes électroniques, de la simple erreur de calcul au dysfonctionnement total de l'appareil. Å l'échelle nanométrique, les rayonnements ionisants d'énergie élevée produisent des charges susceptibles d'être piégées dans les oxydes isolants du dispositif. Ces charges piégées produisent des dégradations électriques qui se manifestent dans les dispositifs MOSFET par un décalage négatif de la tension de seuil, un affaiblissement de la pente sous-seuil et une augmentation des courants de fuite. La résilience des systèmes électroniques à ces dégradations est essentielle dans les environnements radiatifs tels que l'espace, les centrales nucléaires ou dans le cas le moins souhaité des accidents nucléaires. Ce travail vise à explorer deux axes de recherche dans le but d'étudier leur impact sur la récupération des caractéristiques élec-

triques de dispositifs 28nm FDSOI ayant été exposés à des rayonnements ionisants. Cette thèse propose une nouvelle méthode de durcissement par régénération-compensation basée sur le dépiégeage des charges par application de cycles de recuit thermique d'une part et d'autre part sur la compensation électrique de la tension de seuil autorisée par la capacité inhérente à la technologie 28nm FDSOI d'appliquer une polarisation back-gate. Cette méthode a pu être validée par la modélisation physique des effets des rayonnements et des mécanismes de récupération, ainsi que par des expériences avec des dispositifs FDSOI. De plus, des simulations réalisées avec des cellules FDSOI basiques typiquement utilisées dans les circuits numériques ont permis de prédire leur dégradation et leur récupération, validant ainsi davantage la méthode de récupération proposée.

**Title:** Hardening study of 28nm FDSOI technology at very high doses of ionizing radiation

**Keywords:** Total Ionizing Dose (TID), Microelectronics, Fully-depleted Silicon-On-Insulator (FDSOI), Hardening, Regeneration, Compensation, Back-gate voltage.

**Abstract:** Ionizing radiation causes malfunction in electronic systems, from miscalculations to a total device failure. At nanometric scale, high-energy radiation produces charges liable to be trapped in the insulating oxides of the device. These trapped charges will produce electrical degradation that manifest in MOSFET devices as a negative threshold voltage shift, a subthreshold slope weakening, and an increase in leakage currents. The resilience of electronic systems to these degradation is essential in radioactive environments such as space, nuclear power plants or in the least desired case, nuclear accidents. This work seeks to explore two research approaches with the aim of studying their impact on the recovery of the electrical characteristics of 28 nm FDSOI devices after

their exposure to ionizing radiation. This thesis proposes a new regeneration-compensation hardening method based on the detrapping of charges by applying thermal annealing cycles on the one hand and on the other hand the electrical compensation of the threshold voltage allowed by the inherent possibility of the 28nm FDSOI technology to apply a back-gate bias. This method could be validated through physical modeling of radiation effects and recovery mechanisms, as well as experiments with FDSOI devices. Furthermore, simulations carried out with basic FDSOI cells typically used in digital circuits enabled the prediction of their degradation and recovery, thus further validating the proposed recovery method.

A mis padres, hermanos, y a la mas bella sorpresa de esta experiencia... mi Audrey.

## Acknowledgements

I would like to first thank my thesis supervisor Philippe Dollfus, for his great support, advice, help, patience and his incredible human quality, with whom it was a pleasure to work during these 3 years. Muchas gracias Philippe.

To my CEA tutors Jean-Marc Armani and Mariem Slimani for their incredible dedication, advice and effort during my PhD. For their professionalism in the follow-up of the thesis, but more for their friendship during these years of working together.

To all members of the LFIC laboratory with whom I had the opportunity to share experiences and joke around during these three years: Nour Taki, Dzila Adjamian, Emna Farjallah, Emmanuel Molina, Wafa Ben-Hassen, Jaume Benoit (JB), Esteban Cabanillas, Cyril Chastang, Mickael Cartron, Nicolas Ravot, Nicolas Gregis, Thierry Basseville, Jozy Cohen, Moussa Kafal, Marie Benedicte Jacques, Nicolas Dassibat, Louis Allart, Maxime Bonnaud, Geoffrey Beck, Antoine Dupret, Tanguy Sassolas, Valentin Gherman and a special thanks to the CEA coffee machine.

I would like to thank the CEA as well as the Paris-Saclay University for the financial and academic support to carry out this research work.

A thank to the CEA-LETI staff, Sébastien Martinie, Thierry Poiroux, Mickael Cassé, Fred Gaillard, Caroline Arnaud, Adrien Evans, Ivan Miro, Alexandre Valentian, Renaud Moureau, and Youcef Fellah for their very important contributions to these works and specially to my dear friend Pierre Vincent (Pedro Vicente).

To Hortènse (Hortensia) Desjonqueres, Stéphane (Esteban) Poirier and Laurent Cortella for their help during the irradiations and experiments carried out in this thesis.

A special thanks to the people who made coffee mornings enjoyable: Christian Gamrat, Mickael Guibert, Frederic Surleau, Marie Isabelle Giudici, Selma Asaiez, Fabrice Auzanneau, Olivier Heron and Ewa Pichon in addition to the Nanno-Innov staff, for those fun discussions, Gérald (GG), Delphine.

To my Family in France Cesar Zamilpa, Denisse, Axel, Baptiste y Lilinha.

To Laura Diaz, Kuba Janusz, Morgane Henocque, Olivier Ngan, Jordan Censic, Jennifer Badoin, Fiona Rose Murphy, Marie, Nathan and Eugenio for all those wonderful moments together.

A mis queridas amigas Judith (Madrina) Martin del Campo, Lauren Manzanero (AMH), Ana Gissel Fernandez (Marrokina), Alexa Salcedo, Linda Hernandez por su constante apoyo, y su maravillosa amistad.

A la familia de Aztecas París FC y la asociación Maguey: Adrian Varela, Alejandra Jarillo, Luis (Washicol) Rendon y Sonia Zurita, Daniel (Capi) Rivas y Margaux Becquart, Daniel Valenzuela y Julia, Daniel Orozco, Angel Ruiz y Mila, Gabriel (grandote de cerro azul, gigante de la noria) Martinez y Jeanne Claire, Erick Ibañez y Mayliss, Omar (Pomar) Guisa y Charlotte Lavennant, Jorge Garza, Elliot Peña y Vainille, Carlos Suarez y Camille, Carlos Vega, Rodrigo (Gallo negro de oro) Talavera, Damian Dania, Daniel Dania y Daniela, Diego Cueva, Jesus (Chuy es mi carnal) Lugo , Gonzalo Garcia, Manuel (la flecha) Varese, Fernando Garcia, Ricardo Cano, Alejandro Berlanga, Saul (cientifico del gol) Villafañe, Ricardo Maldonado, Eder Moyeda, Pepe Nieva e Isabel, Alan Mar, Benoît Gicquiaux, por todas esas tardes y noches de futbol, viajes y convivencia y especialmente a mi hermano Adan Ortiz y su familia por haberme integrado a este maravilloso grupo.

A todos y cada uno de ustedes gracias.

# Contents

| Introduction                                                                            | 1      |

|-----------------------------------------------------------------------------------------|--------|

| 1 Radiation and their effects on electronic components                                  | 5      |

| 1.1 Radiation environments                                                              | <br>5  |

| 1.2 Photon-matter interactions                                                          | <br>7  |

| 1.3 Total ionizing dose effects on MOS devices                                          | <br>7  |

| 1.3.1 MOSFET structure                                                                  | <br>8  |

| 1.3.2 I-V characteristics of conventional MOSFETs                                       | <br>9  |

| 1.3.3 Physical mechanisms of the TID in MOSFET devices                                  | <br>11 |

| 1.3.4 Impact on electrical characteristics                                              | <br>15 |

| 1.3.5 Dose-Rate effects                                                                 | <br>18 |

| 1.4 Radiation-induced effects on silicon on insulator technology                        | <br>19 |

| 1.4.1 The SOI technology                                                                | <br>19 |

| 1.4.2 Effects of radiation on SOI transistors                                           | <br>23 |

| 1.5 Radiation Hardening Techniques                                                      | <br>24 |

| 1.6 Conclusion of the chapter                                                           | <br>27 |

|                                                                                         |        |

| 2 Theoretical study of the TID degradation and recovery mechanisms of FDSOI transistors | 29     |

| 2.1 Physical analysis of radiation-induced effect on FDSOI transistor                   | <br>29 |

| 2.2 Effect of oxide and interface trapped charges                                       | <br>35 |

| 2.2.1 Oxide trapped charges $N_{ot}$                                                    | <br>35 |

| <b>2.2.2</b> Interface trapped charges $D_{it}$                                         | <br>35 |

| 2.3 Control of the threshold voltage with back-gate bias                                | <br>36 |

| 2.3.1 Threshold voltage with the back-gate in accumulation mode                         | <br>37 |

| 2.3.2 Threshold voltage with the back-gate in inversion mode                            | <br>37 |

|   |     | 2.3.3 Threshold voltage with the back-gate in depletion mode:                     | 37 |

|---|-----|-----------------------------------------------------------------------------------|----|

|   | 2.4 | Recovery mechanisms of irradiated FDSOI MOSFETs                                   | 38 |

|   |     | 2.4.1 Tunnel effect                                                               | 38 |

|   |     | 2.4.2 Thermal annealing                                                           | 39 |

|   |     | 2.4.3 Threshold voltage compensation                                              | 43 |

|   | 2.5 | Electrical characterization of FDSOI MOSFETs                                      | 44 |

|   |     | 2.5.1 Threshold voltage $V_{th}$                                                  | 45 |

|   |     | 2.5.2 Extraction of trapped charges                                               | 47 |

|   |     | 2.5.3 Split C-V method                                                            | 50 |

|   | 2.6 | Conclusion of the chapter                                                         | 52 |

| 3 | Мос | leling of radiation effects and regeneration on FDSOI MOSFET devices              | 53 |

| - | 3.1 |                                                                                   | 53 |

|   | 3.2 | TCAD Simulation of TID effects on FDSOI transistors                               |    |

|   |     | 3.2.1 Effect of Oxide trapped charges $N_{ot}$                                    |    |

|   |     | 3.2.2 Effect of interface trapped charges                                         |    |

|   |     | 3.2.3 Subthreshold slope comparative                                              | 63 |

|   | 3.3 | Physical Modeling of the radiation damage                                         | 64 |

|   |     | 3.3.1 General description of oxide trapped charges $N_{ot}$ model                 | 65 |

|   |     | 3.3.2 Parameters used for the $N_{ot}$ dynamics                                   | 68 |

|   |     | 3.3.3 General description of interface trapped charges $D_{it}$ dynamics          | 69 |

|   | 3.4 | Linear response of the $N_{ot}$ and $N_{it}$ models                               | 72 |

|   | 3.5 | Thermal regeneration modeling                                                     | 72 |

|   |     | 3.5.1 Dynamic of annealing                                                        | 74 |

|   | 3.6 | SPICE implementation of the physical models                                       | 75 |

|   | 3.7 | Conclusion of the chapter                                                         | 77 |

| 4 | Evn | erimental setup and analysis of radiation effects on irradiated FDSOI transistors | 78 |

| 4 | 4.1 |                                                                                   | 78 |

|   | 7.1 | 4.1.1 Devices                                                                     |    |

|   |     | 4.1.2 Irradiation                                                                 |    |

|   |     | 4.1.3 Electrical measurements                                                     |    |

|   |     | 4.1.4 Annealing cycles                                                            |    |

|   |     | 4.1.5 Experimental procedure                                                      |    |

|   | 4.2 | Results analysis                                                                  |    |

|   |     |                                                                                   |    |

|             | 4.2.1 Radiation effects on FDSOI transistors                                              | 82        |

|-------------|-------------------------------------------------------------------------------------------|-----------|

|             | 4.2.2 Annealing effect on irradiated transistors                                          | 86        |

|             | 4.2.3 Effect of Back-gate bias $V_{bg}$                                                   | 89        |

| 4.3         | Dose-rate effects                                                                         | 92        |

| 4.4         | Oxide and interface trapped charge dynamics                                               | 93        |

|             | 4.4.1 Activation energies                                                                 | 96        |

| 4.5         | TCAD validation of extracted parameters                                                   | 97        |

| 4.6         | C-V measurements                                                                          | 98        |

| 4.7         | Conclusion of this chapter                                                                | 98        |

| E Toi       | tal ionizing dose mitigation methodology for 28nm FDSOI devices and systems               | 00        |

|             |                                                                                           | <b>99</b> |

| 5.1         |                                                                                           |           |

| 5.2         |                                                                                           |           |

|             | 5.2.1 NMOS devices                                                                        |           |

|             | 5.2.2 PMOS devices                                                                        |           |

|             | 5.2.3 Optimal recovery parameters                                                         |           |

|             | 5.2.4 Potential reliability issues                                                        |           |

| 5.3         |                                                                                           |           |

|             | 5.3.1 SPICE simulation of the mixed hardening methodology on elementary FDSOI transistors |           |

|             | 5.3.2 Study of a MOSFET-FDSOI Inverter                                                    |           |

|             | 5.3.3 Study of a Ring oscillator                                                          |           |

| 5.4         |                                                                                           |           |

| 5.5         | Application example: 32 bit DSP 28nm FDSOI                                                |           |

|             | 5.5.1 Description of the devices                                                          | 115       |

|             | 5.5.2 Experimental details                                                                | 116       |

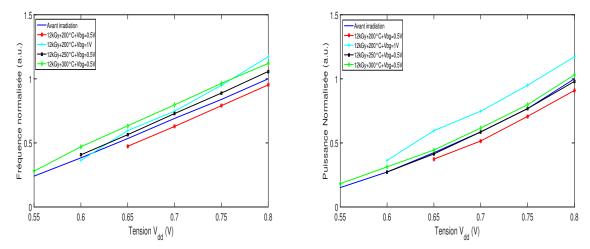

|             | 5.5.3 Performance degradation                                                             | 117       |

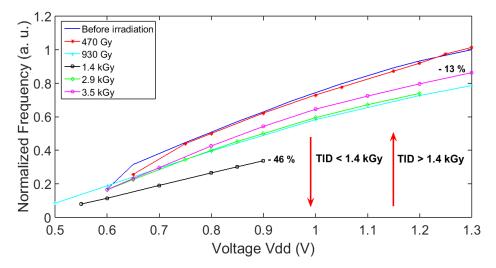

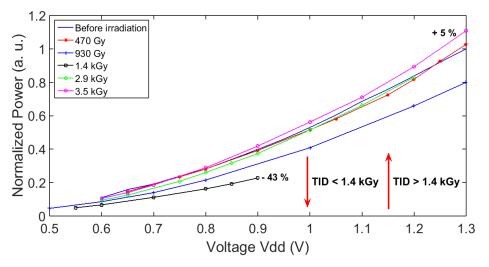

|             | 5.5.4 Frequency $(f_{max})$ and power consumption (P) degradation after irradiation       | 117       |

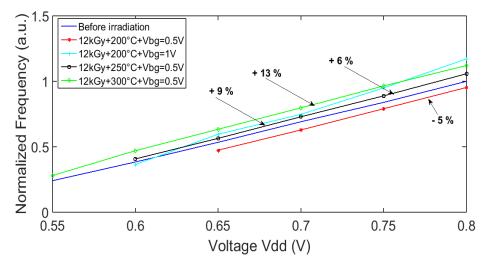

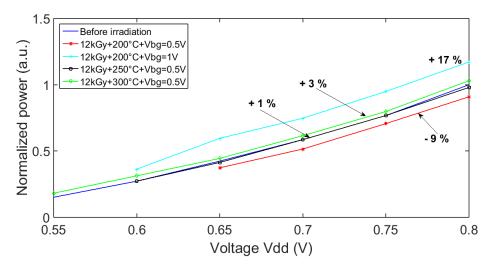

|             | 5.5.5 Performance recovery                                                                | 119       |

| 5.6         | Conclusion of the chapter                                                                 | 120       |

| Concl       | usions                                                                                    | 123       |

|             |                                                                                           |           |

| A Fir       | st Appendix                                                                               | 125       |

| <b>A</b> .1 | Front and back-gate equations of a SOI structure                                          | 125       |

| A.2         | 2 Subthreshold Swing analysis                                                             | 126       |

|    | A.3 Threshold voltage analysis                       | . 127 |

|----|------------------------------------------------------|-------|

| В  | Second Appendix                                      | 129   |

|    | B.1 Thermal annealing model                          | . 129 |

|    | B.2 Activation energy and characteristic temperature | 130   |

| Re | ésumé                                                | 135   |

# **List of Figures**

| 1.1      | Nuclear environment.                                                                                 | 6  |

|----------|------------------------------------------------------------------------------------------------------|----|

| 1.2      | Photon-matter interactions.                                                                          | 7  |

| 1.3 (    | Cross-section view of a Bulk-MOSFET.                                                                 | 8  |

| 1.4 (    | Operation modes of a MOS structure.                                                                  | 9  |

| 1.5 I    | I-V Operation modes of a conventional long-channel MOS transistor.                                   | 10 |

| 1.6 I    | Electrical response of a conventional MOSFET.                                                        | 11 |

| 1.7      | Model of radiation effects in oxides.                                                                | 12 |

| 1.8 \$   | Schematic view of E' centers 11.                                                                     | 12 |

| 1.9 I    | Representation of interface states.                                                                  | 15 |

| 1.10     | Effect of oxide and interface trapped charges on the threshold voltage of NMOS and PMOS transistors. | 17 |

| 1.11 l   | Leakage current in a NMOS transistor.                                                                | 17 |

| 1.12     | Effect of dose rate in oxides.                                                                       | 19 |

| 1.13 (   | Cross section view of a PDSOI transistor.                                                            | 20 |

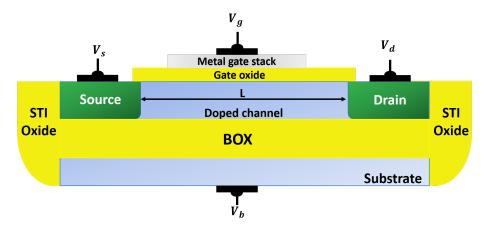

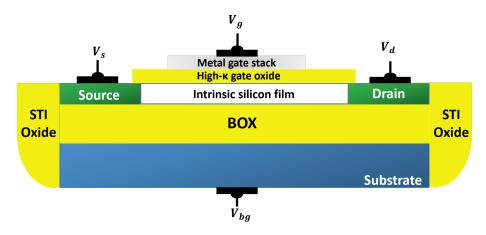

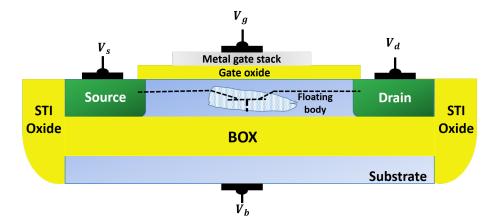

| 1.14 (   | cross section view of a FDSOI transistor.                                                            | 21 |

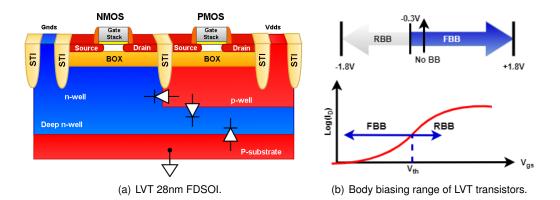

| 1.15 (   | Cross-sectional view of an FDSOI LVT device with the back-gate voltage range.                        | 22 |

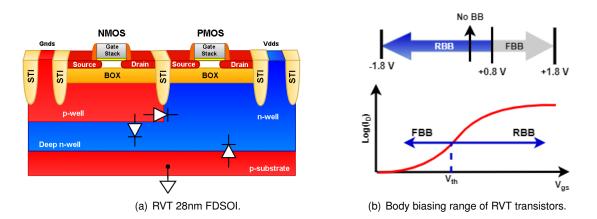

| 1.16 (   | Cross-sectional view of an FDSOI RVT device with the back-gate voltage range.                        | 23 |

| 1.17 I   | Parasitic bipolar structure in PDSOI devices.                                                        | 23 |

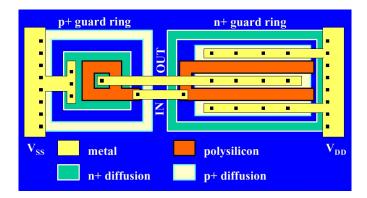

| 1.18 (   | CMOS inverter designed with RHBD techniques.                                                         | 25 |

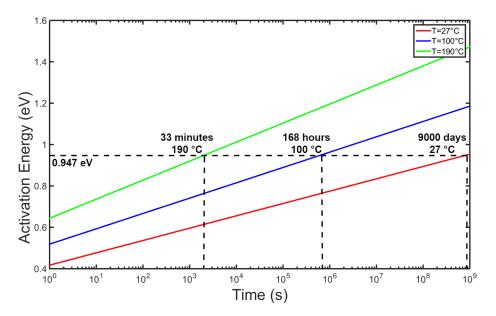

| 1.19     | Time-temperature equivalence of annealing model.                                                     | 26 |

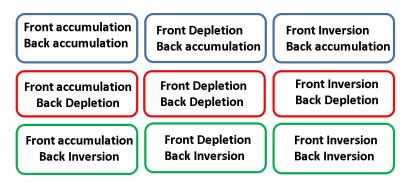

| 2.1 (    | Operation modes of a FDSOI transistor.                                                               | 30 |

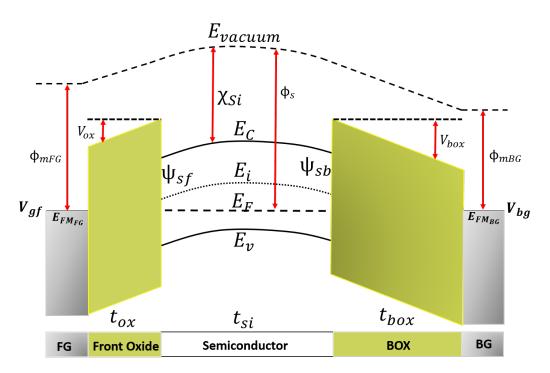

|          | Band Diagram of a SOI structure.                                                                     | 30 |

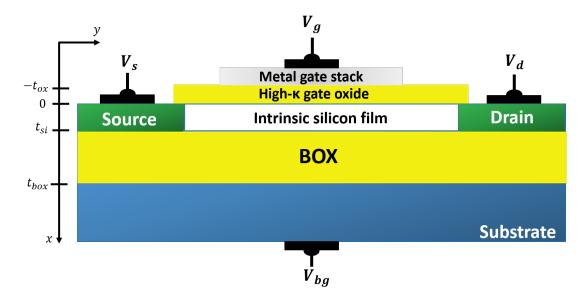

|          | Cross section view of different regions of a FDSOI transistor.                                       | 32 |

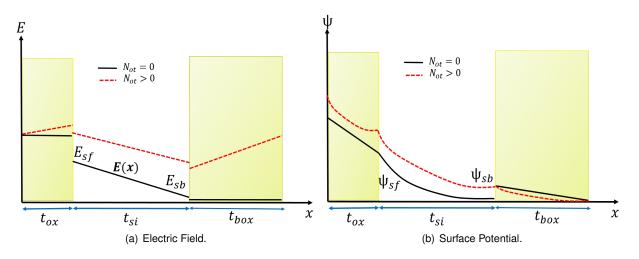

|          | Electric field and surface potential profile in the intrinsic channel.                               | 33 |

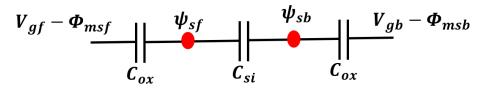

|          | Capacitive equivalent circuit of a SOI structure.                                                    | 33 |

| <u> </u> |                                                                                                      | 00 |

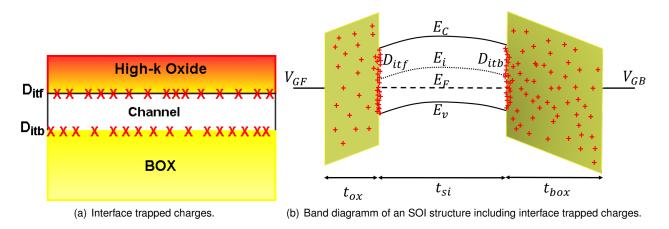

| 2.6 Interface trapped charges in a FDSOI device.                                                             | 35 |

|--------------------------------------------------------------------------------------------------------------|----|

| 2.7 Operating modes of a SOI transistor as a function of the back-gate bias.                                 | 38 |

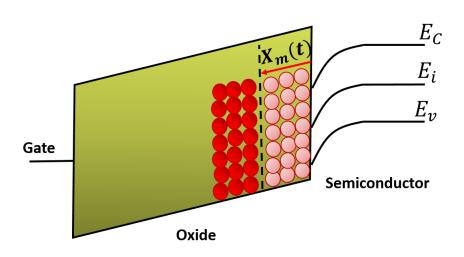

| 2.8 Tunnel effect model.                                                                                     | 39 |

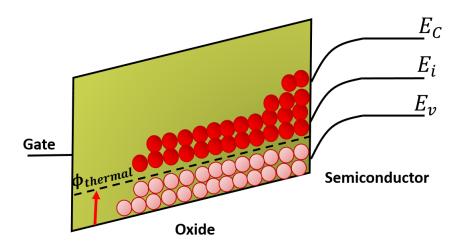

| 2.9 Thermal annealing model.                                                                                 | 40 |

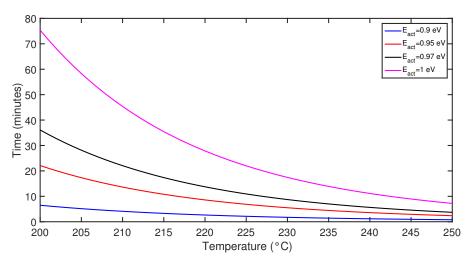

| 2.10 Time-Temperature equivalence for different activation energy levels                                     | 41 |

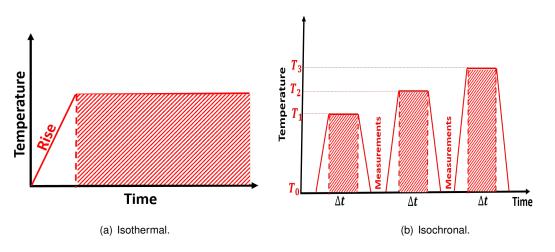

| 2.11 Methods for the thermal annealing.                                                                      | 41 |

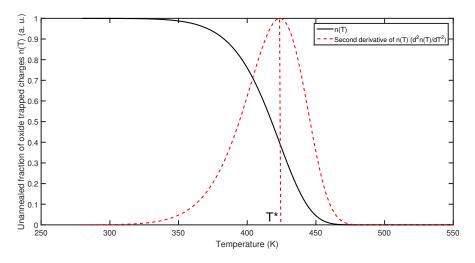

| 2.12 Relation between activation energy and characteristic temperature.                                      | 43 |

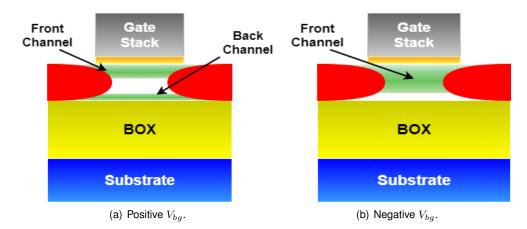

| 2.13 Body-biasing of a FDSOI device.                                                                         | 43 |

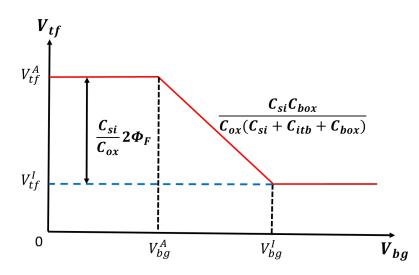

| 2.14 Threshold voltage modulation by apllying a $V_{bg}$                                                     | 44 |

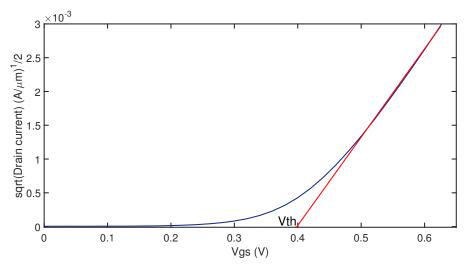

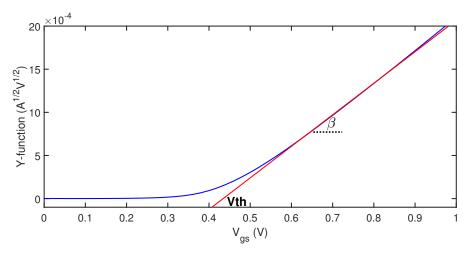

| 2.15 Extraction of threshold voltage by square-root of drain current method.                                 | 45 |

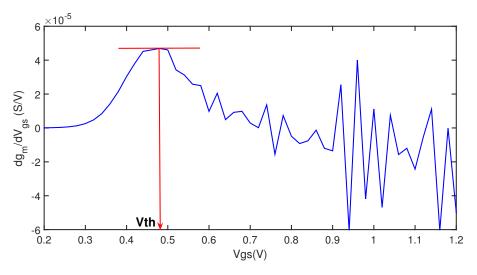

| 2.16 Extraction of threshold voltage by transconductance derivative method.                                  | 46 |

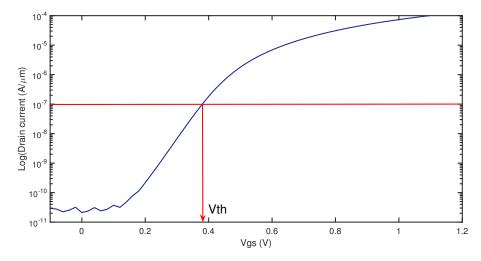

| 2.17 Extraction of threshold voltage by constant current method.                                             | 46 |

| 2.18 Extraction of threshold voltage by Y-function method.                                                   | 47 |

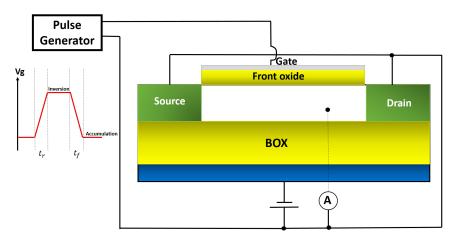

| 2.19 Charge pumping experimental setup for SOI devices.                                                      | 48 |

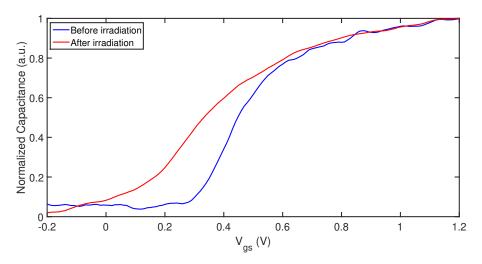

| 2.20 C-V measurement of a NMOS FDSOI transistor before and after irradiation.                                | 49 |

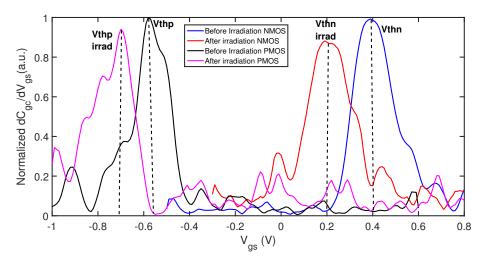

| 2.21 Threshold voltage extraction of NMOS and PMOS transistors.                                              | 49 |

| <b>2.22</b> $N_{ot}$ and $N_{it}$ separation method.                                                         | 50 |

| <b>2.23</b> $N_{ot}$ and $N_{it}$ t separation method.                                                       | 51 |

| D.1. Challenges of compositional line                                                                        |    |

| 3.1 Challenges of compact modeling.                                                                          |    |

| 3.2 Comparison between experimental measurements, a PDK SPICE simulation and TCAD simulation.                |    |

| 3.3 Cross-section view of a 28nm FDSOI model used in TCAD.                                                   |    |

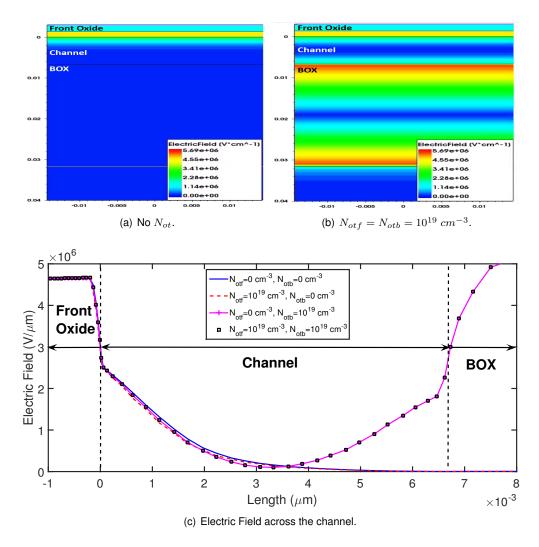

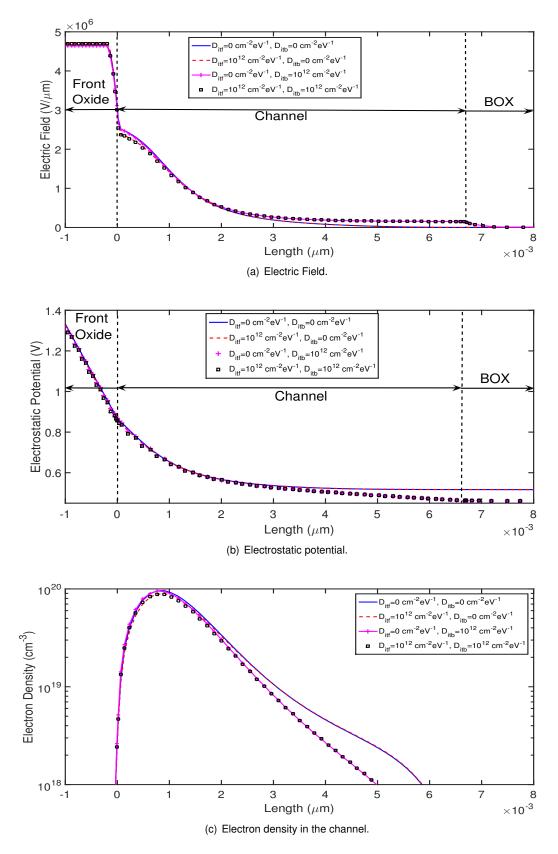

| 3.4 Effect of $N_{ot}$ on the absolute value of the electric field in a 28nm FDSOI transistor.               |    |

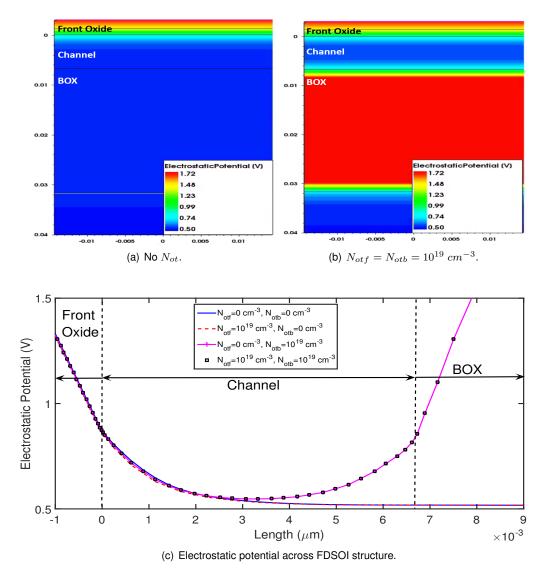

| 3.5 Effect of $N_{ot}$ on the electrostatic potential in a 28nm FDSOI transistor.                            |    |

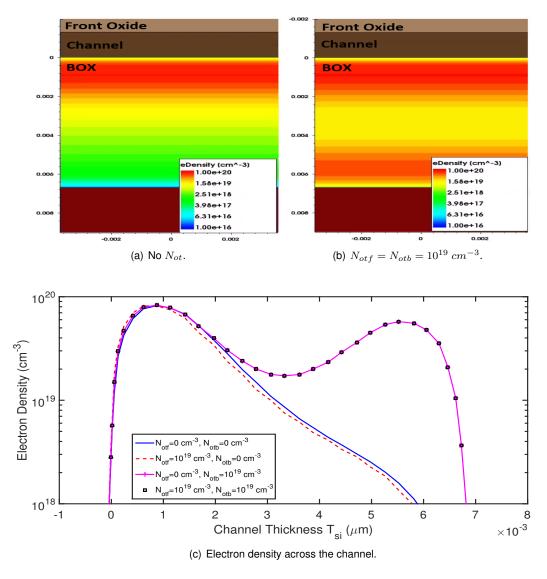

| 3.6 Effect of $N_{ot}$ on the electron density in a 28nm FDSOI transistor.                                   |    |

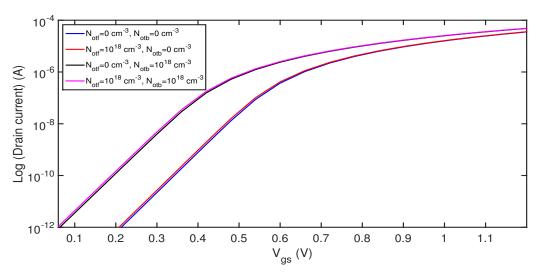

| <b>3.7</b> $I_d(V_{gs})$ curve of an NMOS transistor for different combinations of $N_{otf}$ and $N_{otb}$ . |    |

| 3.8 Effect of interface trapped charges on a FDSOI device.                                                   |    |

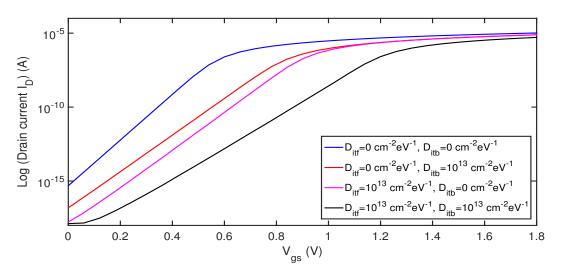

| <b>3.9</b> $I_d(V_{gs})$ with the only influence of $D_{it}$ .                                               |    |

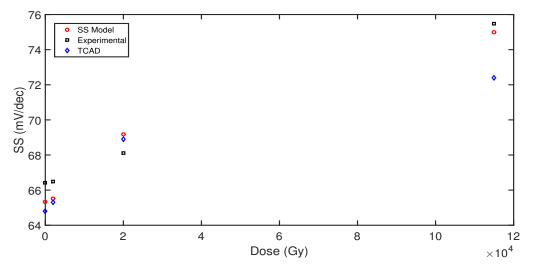

| 3.10 Comparison of experimental ans simulated subthreshold slope variation.                                  |    |

| 3.11 Expected response of trapped charges in MOSFET oxides during irradiation and annealing                  |    |

| 3.12 Various charge yield functions used for a $^{60}Co$ irradiation.                                        | 68 |

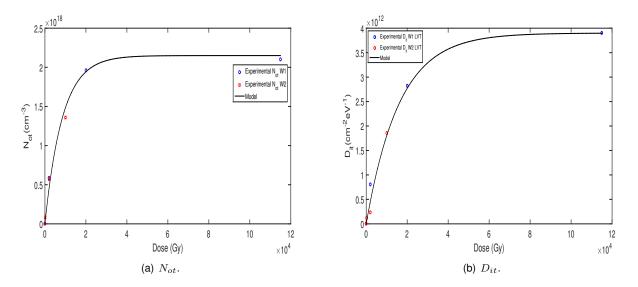

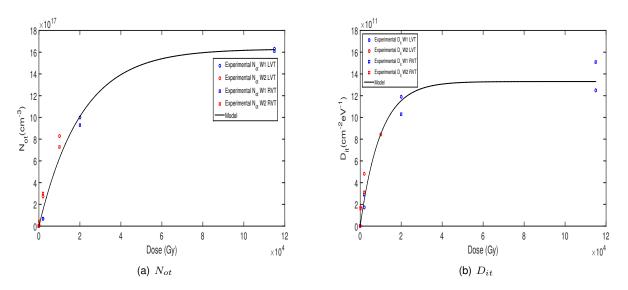

| 3.13 Dynamics of oxide trapped charges density Not at high levels of TID. Comparison between experi-         |    |

| mental data of a PMOS transistor $W = 0.3 \ \mu m, L = 0.03 \ \mu m$ [this work] and the model [Eq. 3.10].   | 69 |

| 2.14 Dunamica of interface transad charges. Comparison between superimental data of a DMOO trans                   |     |

|--------------------------------------------------------------------------------------------------------------------|-----|

| 3.14 Dynamics of interface trapped charges. Comparison between experimental data of a PMOS tran-                   |     |

| sistor $W = 0.3 \ \mu m$ , $L = 0.03 \ \mu m$ [this work] and the model [Eq. 3.14].                                | 71  |

| 3.15 Annealing model applied to an irradiated transistor.                                                          | 74  |

| 3.16 Evolution of the activation energy level with each thermal annealing cycle. Comparison between                |     |

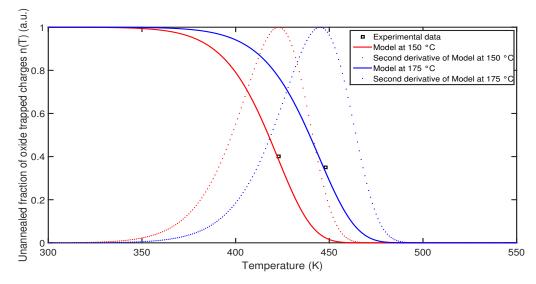

| experimental data of extracted from NMOS transistors [this work] and the model [Eq. 3.27].                         | 75  |

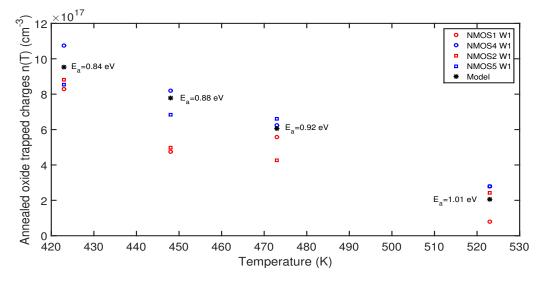

| 3.17 Block Diagram of UTSOI2 model including the TID effects and regeneration by annealing cycles                  | 76  |

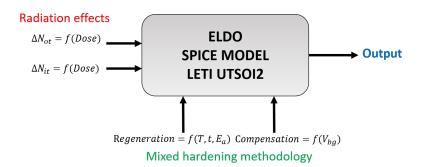

| 3.18 Simulation of TID-induced degradation and the recovery methods in a NMOS $W=L=2~\mu m$ SPICE                  |     |

| library.                                                                                                           | 77  |

| 4.1 Configuration used for the irradiation of elementary FDSOI transistors.                                        | 79  |

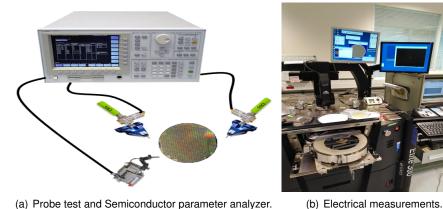

| 4.2 Set-up used for electrical measurements.                                                                       | 80  |

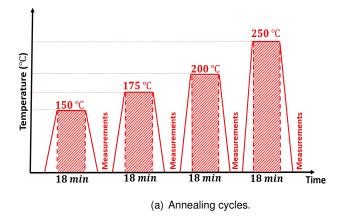

| 4.3 Annealing procedure.                                                                                           | 81  |

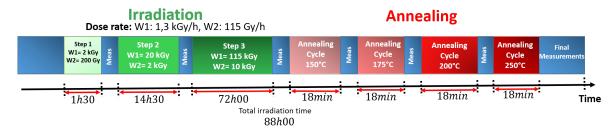

| 4.4 Experimental procedure timeline.                                                                               | 82  |

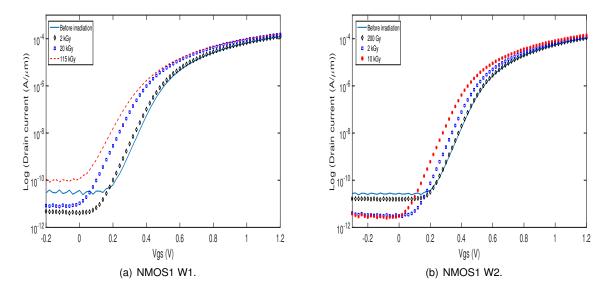

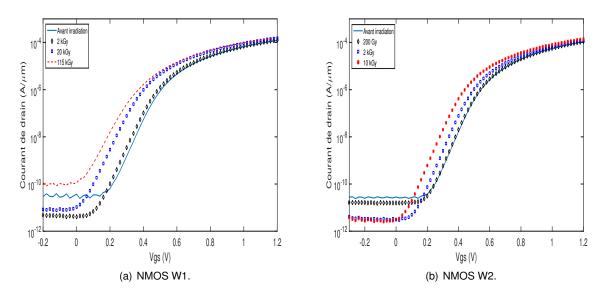

| 4.5 Radiation response of a NMOS LVT transistor $W = L = 1 \ \mu m$ .                                              | 83  |

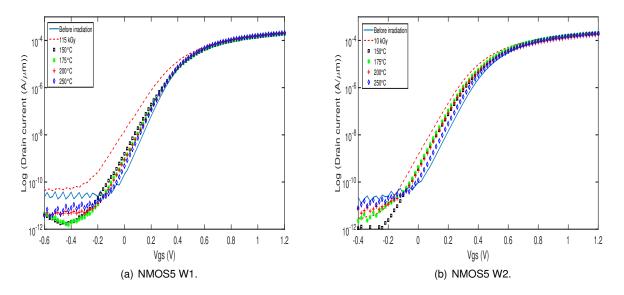

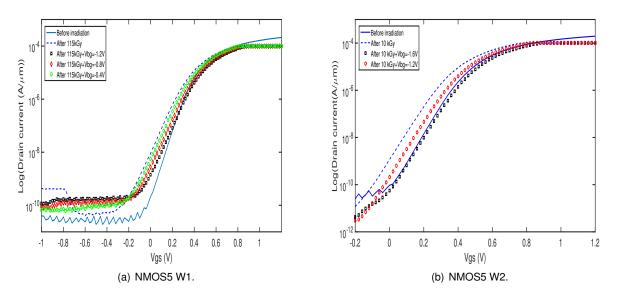

| 4.6 Radiation response of a NMOS LVT transistor W=0.21 $\mu m$ , L=0.03 $\mu m$ .                                  | 84  |

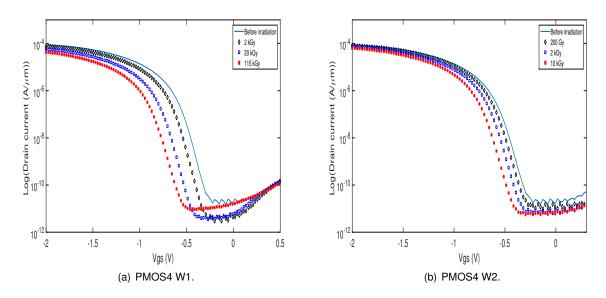

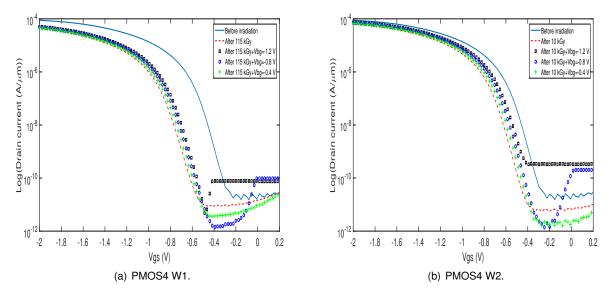

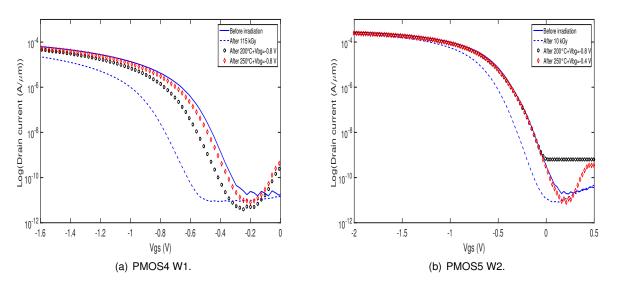

| 4.7 Radiation response of a PMOS-RVT transistor $W = L = 1 \ \mu m$ .                                              | 85  |

| 4.8 Radiation response of a PMOS-RVT transistor W=0.3 $\mu m$ , L=0.03 $\mu m$ .                                   | 85  |

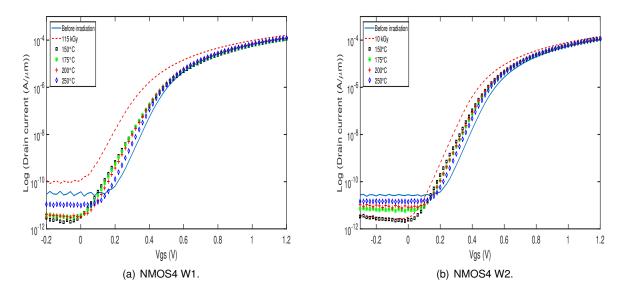

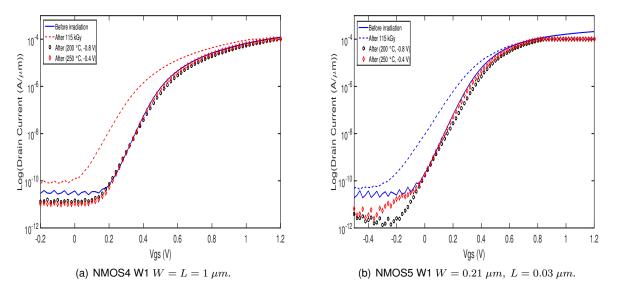

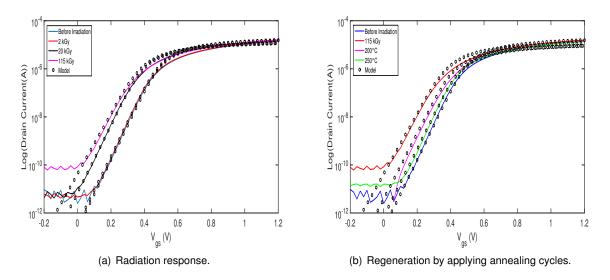

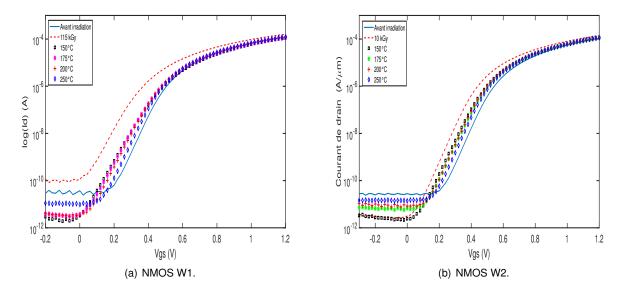

| 4.9 Regeneration of degraded electrical characteristics of a NMOS RVT transistor $W = L = 1 \ \mu m$ .             | 86  |

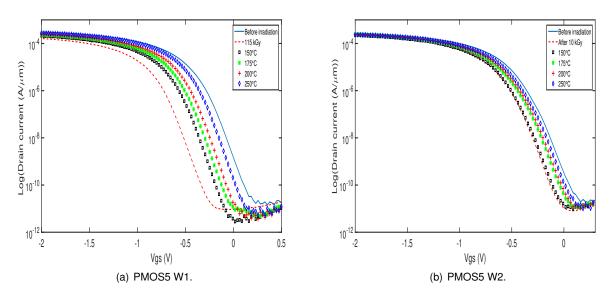

| 4.10 Regeneration of the electrical characteristics of a NMOS RVT transistor $W = 0.21 \ \mu m, L = 0.03 \ \mu m.$ | 87  |

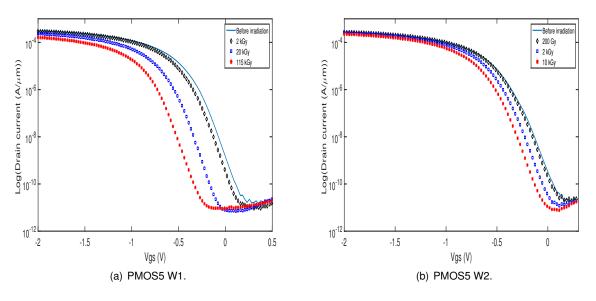

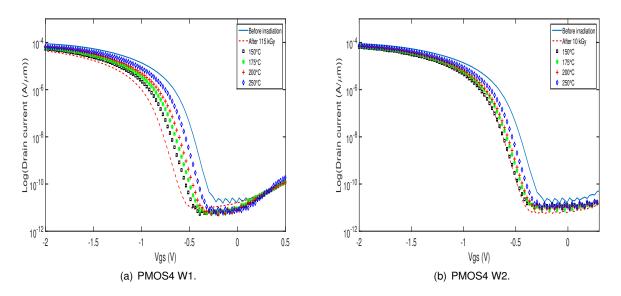

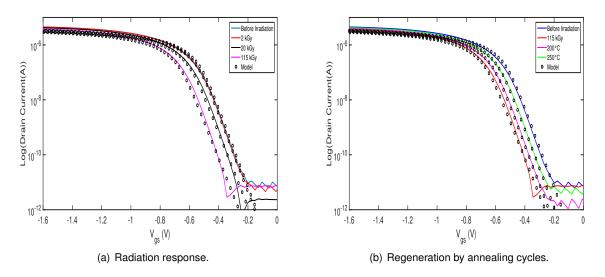

| 4.11 Response of irradiated PMOS transistors with $W = L = 1 \ \mu m$ to thermal regeneration.                     | 88  |

| 4.12 Response of irradiated PMOS transistors with $W=0.3~\mu m,L=0.03~\mu m$ to thermal regeneration.              | 88  |

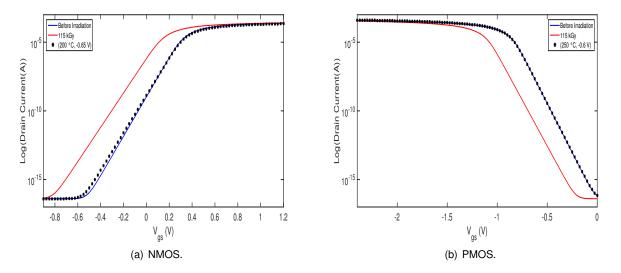

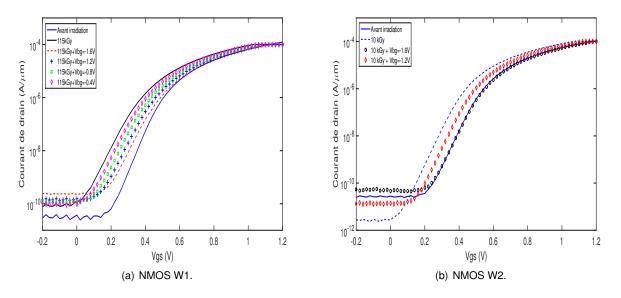

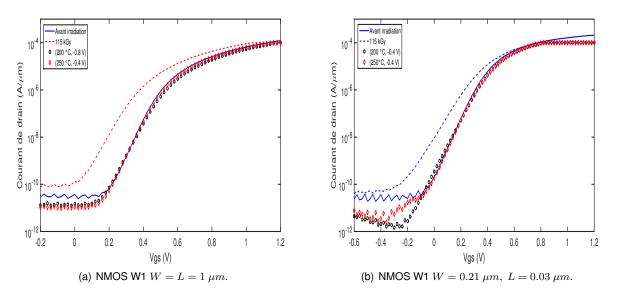

| 4.13 Back-bias response of irradiated NMOS RVT transistors with $W = L = 1 \mu m$ .                                | 90  |

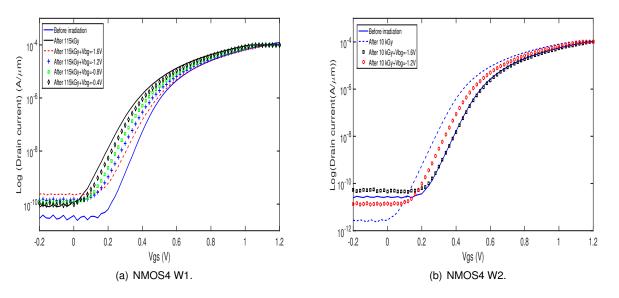

| 4.14 Back-bias response of irradiated short channel NMOS RVT transistors $W=0.21~\mu m, L=0.03~\mu m.$ .           | 91  |

| 4.15 Back-bias compensation of irradiated PMOS RVT transistors with $W = L = 1 \mu m$ .                            | 91  |

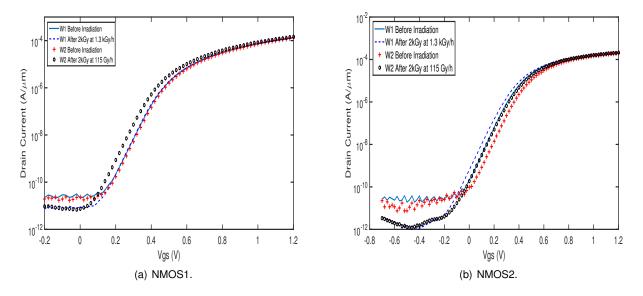

| 4.16 NMOS transistors irradiated up to a common point of 2 kGy at different dose rates.                            | 92  |

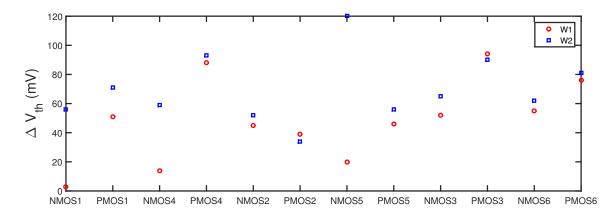

| 4.17 Threshold voltage shift at a common TID level of 2 kGy for all transistors.                                   | 93  |

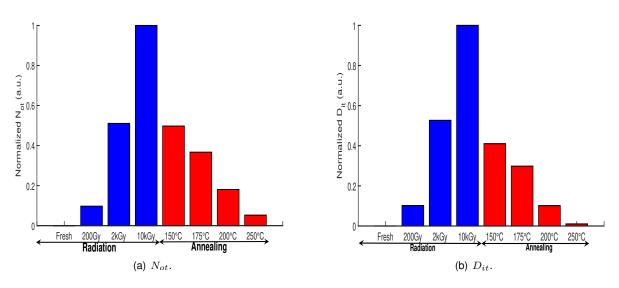

| 4.18 $N_{ot}$ and $D_{it}$ dynamics after the irradiation and annealing procedure.                                 | 94  |

| 4.19 Values of $N_{ot}$ and $D_{it}$ extracted for a PMOS $W = L = 2 \ \mu m$ irradiated at a high dose-rate (W1). | 94  |

| 4.20 Values of $N_{ot}$ and $D_{it}$ extracted for a PMOS $W = L = 1 \ \mu m$ irradiated at a high dose-rate (W1)  | 95  |

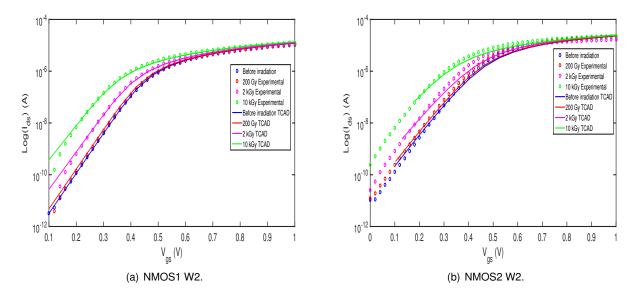

| 4.21 TCAD simulation and experimental measurements for different levels of TID.                                    | 97  |

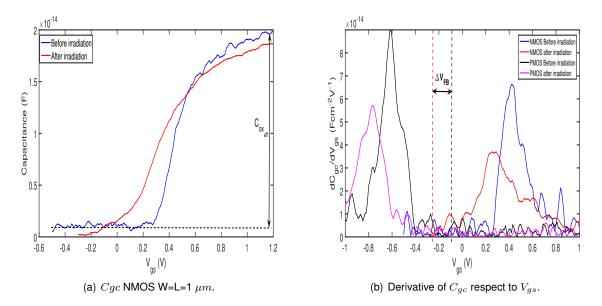

| 4.22 C-V measurements of a NMOS transistor before and after irradiation.                                           | 98  |

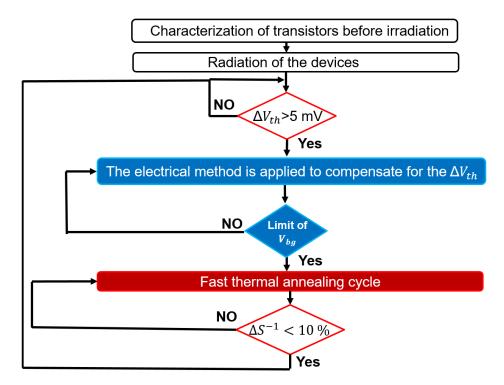

| 5.1 Mixed mitigation strategy flow diagram.                                                                        | 101 |

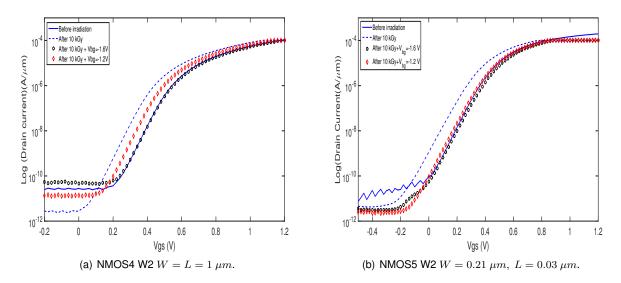

| 5.2 Mixed mitigation strategy of TID effects applied to NMOS RVT transistors.                                      | 102 |

| 5.3 Mixed mitigation strategy of TID effects applied to NMOS RVT transistors                                       | 103 |

|  | B.12 Récupération des performances du DSP FDSOI irradié |  |

|--|---------------------------------------------------------|--|

|--|---------------------------------------------------------|--|

# **List of Tables**

| 1.1 | Different bias configurations of FDSOI transistors.                            | 24  |

|-----|--------------------------------------------------------------------------------|-----|

| 3.1 | Different analyzed $D_{it}$ cases.                                             | 61  |

| 3.2 | Subthreshold slope for NMOS $W = L = 1 \ \mu m$ .                              | 64  |

| 3.3 | Parameters used for $N_{ot}$ model.                                            | 69  |

| 3.4 | Parameters used for $N_{it}$ model.                                            | 71  |

| 4.1 | Characteristics of tested MOSFETS of both wafers.                              | 79  |

| 4.2 | Electrical measurements of tested MOSFETs of both wafers.                      | 80  |

| 4.3 | Maximum degradation and recovery of all irradiated devices.                    | 89  |

| 4.4 | Values for $N_{ot}$ model extracted after fitting.                             | 95  |

| 4.5 | Extracted values for $D_{it}$ model after fitting.                             | 96  |

| 4.6 | Activation energies of NMOS transistors.                                       | 96  |

| 4.7 | Extracted activation energies of PMOS transistors.                             | 97  |

| 4.8 | Comparison of experimental measurements and TCAD simulation.                   | 98  |

| 5.1 | $(T-V_{bg})$ Optimum pair for mitigating TID effects on FDSOI-RVT transistors. | 104 |

| 5.2 | Oscillation frequency and power consumption of the five-stages RO.             | 111 |

| 5.3 | Irradiation characteristics.                                                   | 117 |

| 5.4 | Recovery parameters.                                                           | 120 |

# List of symbols and acronyms

| Symbol       | Name                                               | Unit         |

|--------------|----------------------------------------------------|--------------|

| $V_{gf}$     | Front gate Voltage                                 | V            |

| $V_{gb}$     | Back-gate Voltage                                  | V            |

| $t_{ox}$     | Gate oxide thickness                               | cm           |

| $t_{box}$    | BOX Thickness                                      | cm           |

| $t_{si}$     | Silicon thickness                                  | cm           |

| Ψ            | Surface potential                                  | V            |

| $\Psi_{sf}$  | Front surface potential                            | V            |

| $\Psi_{sb}$  | Back surface potential                             | V            |

| $e_0$        | Dielectric constant of Vacuum                      | $F/cm^2$     |

| $e_{si}$     | Dielectric constant of silicon                     | $F/cm^2$     |

| eox          | Dielectric constant of silicon-Oxide               | $F/cm^2$     |

| Cox          | Gate oxide capacitance                             | $F/cm^2$     |

| $C_{box}$    | BOX capacitance                                    | $F/cm^2$     |

| $C_{si}$     | Silicon capacitance                                | $F/cm^2$     |

| $C_{gc}$     | Gate to Channel capacitance                        | $F/cm^2$     |

| E            | Electric Field                                     | $MV.cm^{-1}$ |

| $E_{sf}$     | Front electric field                               | $MV.cm^{-1}$ |

| $E_{sb}$     | Back electric field                                | $MV.cm^{-1}$ |

| $\Phi_{msf}$ | Front metal-semiconductor Work-function difference | eV           |

| $\Phi_{msb}$ | Back metal-semiconductor Work-function difference  | eV           |

| $V_d$        | Drain voltage                                      | V            |

| $V_g$        | Gate voltage                                       | V            |

| $V_s$        | Source voltage                                     | V            |

| $V_{ds}$        | Drain-to source voltage                                  | V                                               |

|-----------------|----------------------------------------------------------|-------------------------------------------------|

| $V_{th}$        | Threshold Voltage                                        | V                                               |

| $V_{FB}$        | Flat-band Voltage                                        | v                                               |

| V <sub>bg</sub> | Back-gate Voltage                                        | v                                               |

| $V_{mg}$        | Mid-gap Voltage                                          | v                                               |

| $I_{mg}$        | Mid-gap Current                                          | A                                               |

| Ids             | Drain-to-source Current                                  | A                                               |

| Ion             | ON Current                                               | A                                               |

|                 | OFF Current                                              | A                                               |

| Ioff            | Body Factor                                              | mV/V                                            |

| <i>n</i>        |                                                          |                                                 |

| D<br>D'         | Dose                                                     | Gy or rad                                       |

|                 | Dose rate                                                | $Gy.h^{-1}$ or $rad.s^{-1}$<br>$cm^{-3}Gy^{-1}$ |

| $g_0$           | Electron-hole pairs generation                           |                                                 |

| $f_y(E)$        | Charge yield                                             | _ 3                                             |

| Not             | Oxide trapped charges density                            | cm <sup>-3</sup>                                |

| Notf            | Front oxide trapped charges density                      | cm <sup>-3</sup>                                |

| $N_{otb}$       | BOX oxide trapped charges density                        | cm <sup>-3</sup>                                |

| $D_{it}$        | Interface trapped charges density                        | $cm^{-2}eV^{-1}$                                |

| $D_{itf}$       | Font interface trapped charges density                   | $cm^{-2}eV^{-1}$                                |

| $D_{itb}$       | Back interface trapped charges density                   | $cm^{-2}eV^{-1}$                                |

| $C_{it}$        | Interface trapped charge capacitance                     | $Fcm^{-2}$                                      |

| $C_{itf}$       | Font interface trapped charges capacitance               | $Fcm^{-2}$                                      |

| $C_{itb}$       | Back interface trapped charges capacitance               | $Fcm^{-2}$                                      |

| $\Delta V_{ot}$ | Threshold voltage shift due to oxide trapped charges     | V                                               |

| $\Delta V_{it}$ | Threshold voltage shift due to interface trapped charges | V                                               |

| $E_{act}$       | Activation energy                                        | eV                                              |

| Т               | Temperature                                              | к                                               |

| q               | Electron charge                                          | С                                               |

| k               | Boltzmann constant                                       | eV/K                                            |

| t               | Time                                                     | s                                               |

| f               | Frequency                                                | s <sup>-1</sup>                                 |

| $f_{osc}$       | Oscillation Frequency                                    | $s^{-1}$                                        |

| •             | <b>–</b> ( )                                            | _1                    |

|---------------|---------------------------------------------------------|-----------------------|

| A             | Frequency factor                                        | s <sup>-1</sup>       |

| Ar            | channel area of the transistor                          | $cm^2$                |

| $\mu_n$       | Electron mobility                                       | $cm^{-2}V^{-1}s^{-1}$ |

| $\mu_p$       | Hole mobility                                           | $cm^{-2}V^{-1}s^{-1}$ |

| $m^*$         | Effective mass of carriers                              | kg                    |

| $\sigma_h$    | Holes capture cross-section                             | $cm^2$                |

| h             | Planck's constant                                       |                       |

| $\Phi_{mFG}$  | Front gate work-function                                | eV                    |

| $\Phi_{mBG}$  | Back gate work-function                                 | eV                    |

| $\chi_{si}$   | Electron affinity of silicon                            |                       |

| $E_c$         | Conduction band level                                   |                       |

| $E_v$         | Valence band level                                      |                       |

| $E_i$         | Intrinsic Fermi-level                                   | eV                    |

| $E_F$         | Fermi-level                                             | eV                    |

| $E_{Vacuum}$  | Energy level of vacuum                                  | eV                    |

| N             | Number of available defect in the oxide volume          | $cm^{-3}$             |

| n(D)          | number of trapped charges as function of total dose     | $cm^{-3}$             |

| n(T)          | number of trapped charges to be annealed                | $cm^{-3}$             |

| $N_{it}$      | Interface trapped charges density                       | $cm^{-2}$             |

| $N_{SiH}$     | Density of passivated bonds                             | $cm^{-2}$             |

| $N_{DH}$      | Density of hydrogen defects                             | $cm^{-2}$             |

| $\sigma_{DH}$ | Capture cross-section of holes reacting with DH centers | $cm^2$                |

| $\sigma_i$    | Capture cross-section for interface traps               | $cm^2$                |

| x             | Depth                                                   | cm                    |

| $P_{static}$  | Static Power                                            | W                     |

| $P_{dynamic}$ | Dynamic Power                                           | W                     |

| $P_{total}$   | Total Power                                             | W                     |

| MOSFET | Metal-Oxide-Semiconductor Field Effect Transistor |

|--------|---------------------------------------------------|

| TFET   | Tunneling Field Effect Transistor                 |

| CMOS   | Complementary Metal-Oxide-Semiconductor           |

| VLSI   | Very-Large-Scale-Integration                      |

| BJT   | Bipolar Junction Transistor                         |

|-------|-----------------------------------------------------|

| IC    | Integrated Circuit                                  |

| DSP   | Digital Signal Processor                            |

| UTBB  | Ultra Thin Body and Box                             |

| RVT   | Regular Threshold Voltage                           |

| LVT   | Low Threshold Voltage                               |

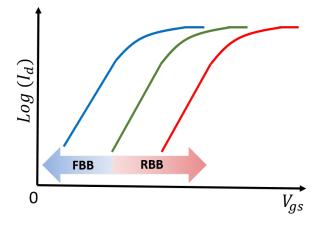

| RBB   | Reverse Body Bias                                   |

| FBB   | Forward Body Bias                                   |

|       |                                                     |

| GO1   | Gate Oxide 1                                        |

| GO2   | Gate Oxide 2                                        |

| TID   | Total Ionizing dose                                 |

| SEE   | Single Event Effects                                |

| SCE   | Short Channel Effects                               |

| SEL   | Single Event Latchup                                |

| SOS   | Silicon-On-Sapphire                                 |

| SOI   | Silicon-On-Insulator                                |

| PDSOI | Partially-Depleted Silicon-On-Insulator             |

| FDSOI | Fully-Depleted Silicon-On-Insulator                 |

| BOX   | Buried Oxide                                        |

| SS    | Subtreshold Slope                                   |

| ELT   | Enclosed Layout Transistor                          |

| CTRW  | Continuous Time Random Walk                         |

| STI   | Shallow Trench Isolation                            |

| RHBD  | Radiation Hardening by Design                       |

| RHBP  | Radiation Hardening by Process                      |

| PSP   | Surface Potential based models                      |

| PDK   | Process Design Kit                                  |

| EOT   | Equivalent Oxide Thickness                          |

| WF    | Work Function                                       |

| TCAD  | Technological Computer-Aided Design                 |

| SPICE | Simulation Program with Integrated Circuit Emphasis |

| TSC   | Thermo-Stimulated-Current                           |

| W1   | Wafer 1                               |  |

|------|---------------------------------------|--|

| W2   | Wafer 2                               |  |

| NBTI | Negative Bias Temperature Instability |  |

| RO   | Ring Oscillator                       |  |

| PLL  | Phase-Locked-Loop                     |  |

| VLIW | Very-Long Instruction Word            |  |

## Introduction

The nuclear accidents of Three Mile Island in 1979, Chernobyl in 1986 and Fukushima in 2011 have considerably boosted the market for hardened electronic devices during the past 30 years. The need to carry out interventions in harsh environments such as nuclear sites has promoted the research to develop electronic systems able to withstand high levels of ionizing radiation. Numerous studies have shown that *Total Ionizing Dose* (TID) electrically degrades semiconductor devices resulting in early aging up to a total failure of the device. Physically, a high-energy radiation, such as X- and  $\gamma$ -rays, creates charges liable to be trapped in the insulating oxides of a *Metal-Oxide-Semiconductor Field Effect Transistor* (MOSFET). These trapped charges alter the electrical characteristics of the transistor having as a first consequence a negative threshold voltage shift on both n- and p-type metal-oxide semiconductor (NMOS and PMOS) transistors and, an increase in the subthreshold slope producing a decrease in the operating frequency, as well as an increase in the leakage currents that impacts the consumption power of a Very-Large-Scale-Integration (VLSI) circuit.

Since the invention of the transistor in 1947, electronic devices have evolved in complex ways thanks to the advances in manufacturing processes. In 1965, Gordon E. Moore predicted with his postulate that the number of transistors in a microprocessor will double every 24 months. However, nowadays the scaling of devices is reaching its physical limits, therefore new solutions in terms of materials and structures have appeared in recent years, such as high- $\kappa$  materials used in gate oxides in addition to great advances in photolithography processes. One of these structures is the Silicon-On-Insulator (SOI) technology with its two variants, Partially Depleted-Silicon-On-Insulator (PDSOI) and Fully-Depleted-Silicon-On-Insulator (FDSOI). These variants have been extensively studied for decades, but in recent years, and due to great advances and precision in manufacturing processes, they have become popular thanks to their high performance compared to Bulk-type transistors. In particular, the FDSOI technology has been considered as an ideal candidate to replace conventional Bulk-MOSFETs and continue with the downscaling.

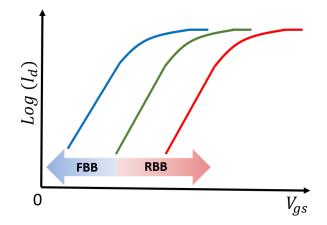

FDSOI technology has multiple advantages over other known technologies such as high frequency performance, low power consumption, no short channel effects (SCE), an intrinsic silicon channel that reduces variability between

devices due to the manufacturing process, and the possibility of modulating its threshold voltage  $V_{th}$  by applying a body bias voltage or also called back-gate voltage  $V_{bg}$ . In addition, FDSOI transistors have the advantage of being planar, so their manufacturing process is much simpler compared to other emerging technologies such as FinFETs or nanowires. Besides, FDSOI technologies are nowadays increasingly used in space applications thanks to their architecture proved to be intrinsically resistant to single event effects (SEE) and particularly to latchup effects. However, these technologies have shown a significant sensitivity to TID effects due to radiation-induced charge trapping in the buried oxide (BOX).

An electronic system must be hardened to prevent degradation or total failure due to radiation during its mission. Many techniques can be used for that purpose, each of them presenting advantages and disadvantages that have to be taken into account. Historically, shielding was the first hardening method used to make electronic devices resistant to radiation. However, this method can be impractical or inefficient for embedded systems for which weight can be crucial. In applications that include the design of a microcircuit, radiation hardening by design (RHBD) methods have taken a great importance due to their efficiency. Radiation hardening by process (RHBP) is often used for safety demanding applications due to the hardness guaranty it provides. Nevertheless, a significant cost increase due to the important modifications of the manufacturing process is the major drawback of this method.

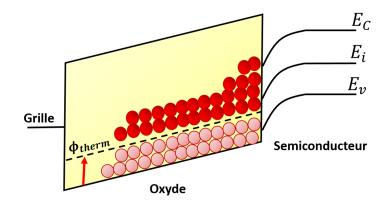

Hardening strategies to mitigate TID induced-effects in FDSOI devices have been explored in some recent works. They include hardening by design using 3D FDSOI transistor structure, layout techniques, and substrate biasing. This later consist to apply a body biasing that allow tuning the threshold voltage of FDSOI transistors. This technique has been widely used to increase the performance of ICs at the expense of power consumption. Recently, it has been exploited to compensate for the negative shift of threshold voltage produced by radiation effects. On the other hand, thermal annealing has demonstrated to be an effective method to improve the resistance of CMOS devices to TID. This technique consists of applying annealing cycles at high temperature in order to recover the degraded characteristics of electronic components. The higher the applied temperature, the higher the recovery. However, it is well known that high temperature cycles applied to semiconductor devices can accelerate aging and reduce their lifetime.

The technology chosen for this thesis is the 28nm FDSOI from STMicroelectronics, considering that it has shown to be promising for the design of high speed and low power integrated circuits. The goal of the thesis is to propose a new mitigation strategy based on the combined application of thermal annealing and body biasing techniques to guarantee that FDSOI devices can withstand high cumulated dose levels ( $\geq$  10 kGy) in civilian nuclear environments. We have started this work by carrying out a set of experiments on NMOS and PMOS FDSOI transistors of different sizes, including irradiation at different TID levels, annealing cycles and back gate electrostatic compensation. From the observed results, we have developed a hierarchical ensemble of modeling

2

approaches to describe all stages of the irradiation-regeneration process at the device level, with the goal to deduce predictable and reliable models, simple enough to extend their use at the circuit level.

This manuscript is organized as follows:

**Chapter 1** presents the state of the art: the concepts related to total ionizing dose and the effects on classic and advanced MOSFET transistors as well as the main hardening methods are explained. A comparative study between different technologies is shown in order to justify the use of FDSOI transistors in this work.

**Chapter 2** analyses the effect of TID on SOI structure and presents the recovery mechanisms applied sor far to this technology. A review of the principal methods, used throughout this thesis, to extract the electrical parameters of FDSOI transistors is also presented.

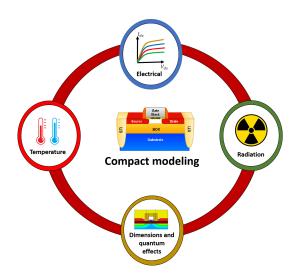

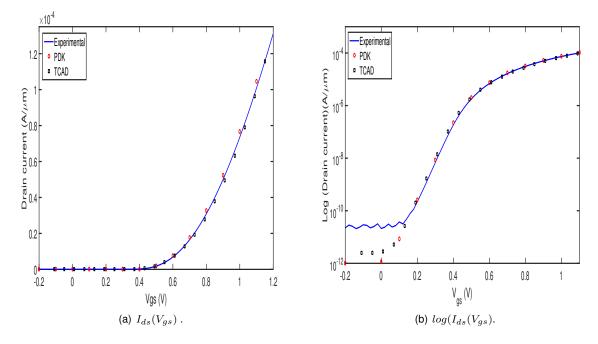

**Chapter 3** presents a SPICE model describing TID induced degradation and thermal regeneration effect on FDSOI transistors characteristics. Results of TCAD simulations, carried out to better understand the physical impact of charge oxide trapping and interface trapping, are analyzed.

**Chapter 4** explains the experimental process carried out on 28nm FDSOI transistors. The irradiation, annealing and electrical measurements are explained in detail. A complete analysis of radiation effects, back-gate voltage response and temperature effects is done to observe the influence of these phenomena separately. We extract the values of the electrical parameters affected by TID and those corresponding to annealing parameters in order to calibrate the proposed physical models.

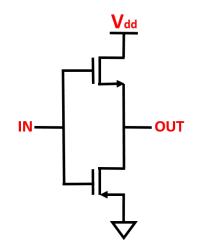

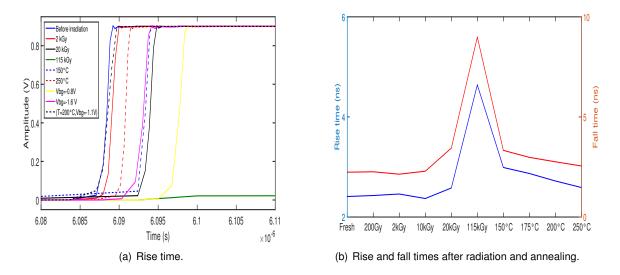

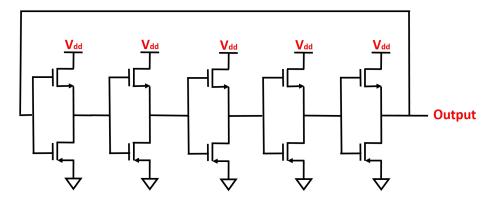

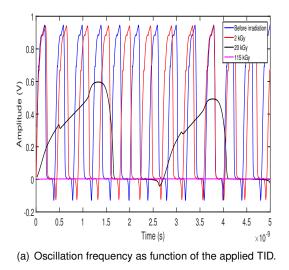

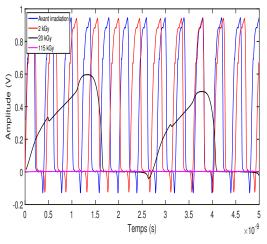

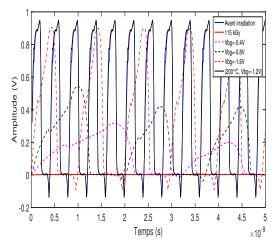

**Chapter 5** presents the new mixed strategy based on the regeneration-compensation of the TID effects in FDSOI transistors. This strategy has been applied to a 32-bit DSP designed with the studied 28nm FDSOI technology to show its efficiency. The physical models describing the effect of radiation and thermal annealing are applied to the basic cell of a digital circuit to confirm the effectiveness and predictability of the proposed models. For this purpose, the SPICE model of a CMOS inverter including all these add-ons is used to simulate with the tool ELDO the behavior of a ring oscillator built with 28nm FDSOI transistors.

## **Chapter 1**

# Radiation and their effects on electronic components

During the last decade, new materials and structures have emerged in the manufacturing of semiconductors in order to sustain the trend in scaling of transistors and improve integrated circuits (ICs) performance. Among these structures, some have proved to be resistant to harsh environments such as high temperature, space or nuclear plants. Nevertheless, the response of these structures under the most extreme conditions, such as radiation environments, should be known to guarantee their operation during the whole mission.

In this chapter, we first introduce the harmful radiation mostly present in space and nuclear environments. Then, we describe the impact of ionizing radiation on MOSFET characteristics. A focus on radiation-induced effects on silicon on insulator technology is carried out. Finally, different hardening techniques used so far to build hardened reliable circuits are presented.

## 1.1 Radiation environments

A radiation environment can be defined as a specific complex set of particles, having different energies, that may degrade electronic systems reliability. Radiation can be divided into two categories: ionizing radiation or non-ionizing radiation, depending on its interaction with matter. Unlike non-ionizing radiation, ionizing radiation have enough energy to break molecular bonds and remove electrons from atoms [2, 3, 4]. Ionizing radiation is characterized by their energy and their type of particle. These particles can be grouped in three categories: photons, charged particles and neutrons [5].

- Photons are zero charge and zero mass particles traveling at speed of light with an energy inversely proportional to its wavelength .

Highly energetic photons are quantum of electromagnetic radiations with short wavelength that are capable of significantly penetrating materials .

There are either X or γ-rays. Generally X-rays are less energetic than γ-rays but both of them have the same type of interaction with matter that we will explain later in this chapter .

- Charged particles have an electrical charge that determines their interaction with matter. They include electrons, positrons, that correspond to  $\beta$ -rays, protons or alpha particles, and heavy ions [9]. Charged particles are produced either by the radioactive decay of a nucleus or by using particle accelerators.

- Neutrons are particles with no charge and are part of the nucleus of an atom. Neutrons are produced with nuclear fission and fusion reactions. They are classified according to their energy: thermal neutrons  $(E \approx 25 \text{ meV})$ , intermediate neutrons (300 eV < E < 1 MeV) and fast neutrons (E > 1 MeV).

These kinds of radiation exist in different environments such as space or nuclear power plants.

In the space environment, electronic systems may be exposed to earth's radiation belts, galactic cosmic-rays or radiation produced by solar wind and flares. The main particles in this environment consist on protons, electrons and heavy ions having an energy range from few hundred keV to some GeV [10].

On other hand, in civil nuclear industry, the levels of radiation can reach the tens of kGy. And in the case of a nuclear accident, these levels can be even higher. In such environments, there are commonly  $\gamma$ -rays and neutrons which can be harmful for both humans and electronic systems.

(a) Nuclear plant in Tihange, Belgium.

(b) Nuclear accident in Chernobyl.

Figure 1.1: Nuclear environment.

This work investigates the response of new generation semiconductor devices to ionizing radiation, particularly in civil nuclear environment where electronics are mainly exposed to high-energy  $\gamma$ -rays [11].

## 1.2 Photon-matter interactions

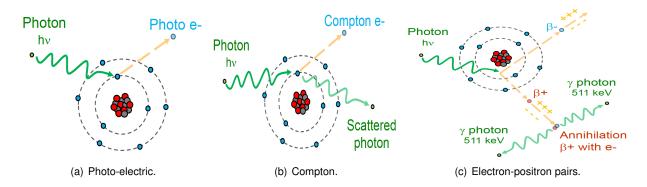

When photons interact with matter, different effects can occur depending on their energy. First, there is the photoelectric effect (Figure 1.2(a)) which occurs when a photon is absorbed by interacting with an electron bound to an atom. If the photon energy is greater than the binding energy of the electron, the later can be ejected from his shell and become free [12]. This effect is predominant for photons with energies between 1 and 100 keV [12].

The second effect is known as the Compton effect or the Compton scattering effect (Figure 1.2(b)). It occurs when a high-energy photon collides with a loosely-binded electron from the outer shell of an atom, giving a part of its kinetic energy to the electron which is released. However, unlike the photoelectric effect, the photon is not absorbed but proceeds on a deviated course with a lower energy [13].

Another effect of photon-matter interaction is the electron-positron pairs generation (Figure 1.2(c)). It occurs when an incident photon with energy greater than 1.022 MeV interacts in the vicinity of an atom nucleus. The energy of the photon is totally absorbed to create an electron-positron pair. The materialized positron annihilates eventually with an electron, generating a pair of 511 keV photons emitted at 180° from each other [12].

Figure 1.2: Photon-matter interactions.

The total amount of energy deposited by a particle that results in the production of electron-hole pairs in materials is called total ionizing dose (TID) [14]. The unit used to quantify the absorbed dose of radiation is the Gray (Gy), which is defined as the quantity of ionizing radiation necessary to transfer an energy of one Joule to one kg of the exposed material. The quantity of energy deposited in a material during a time interval is called dose rate.

## 1.3 Total ionizing dose effects on MOS devices

This section aims to explain radiation-induced effects on MOS devices. First, a brief overview of conventional MOS-FET stucture is presented. Then, the physical mechanisms impacting the most sensitve parts of this device during its exposure to ionizing radiation are decribed. The impact of these phenomena on the electrical characteristics of the transistors are shown at the end if this section.

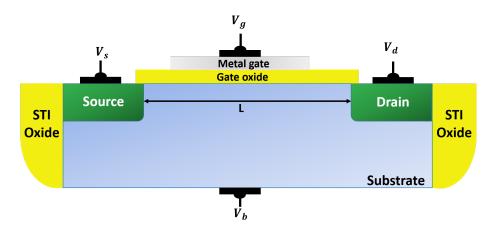

#### 1.3.1 MOSFET structure

Today, the Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) is the main element in the manufacture of integrated circuits due to its high density of integrability in an integrated circuit. Its structure, displayed in Figure 1.3 is composed of a doped substrate, p- or n-type. For NMOS transistors, the substrate is p-type doped while it is n-type doped for PMOS ones. A metal gate contact induces the inversion layer in the channel at the Oxide-Semiconductor interface. An oxide layer isolates the gate from the substrate and allows its capacitive coupling. Two heavily doped regions (n- or p-type) called drain and source serve as carrier reservoirs. In addition, Complementary-MOS (CMOS) transistors include a pair of shallow-trench Isolation oxides to isolate the NMOS and PMOS structures, facilitating their manufacturing process.

Figure 1.3: Cross-section view of a Bulk-MOSFET.

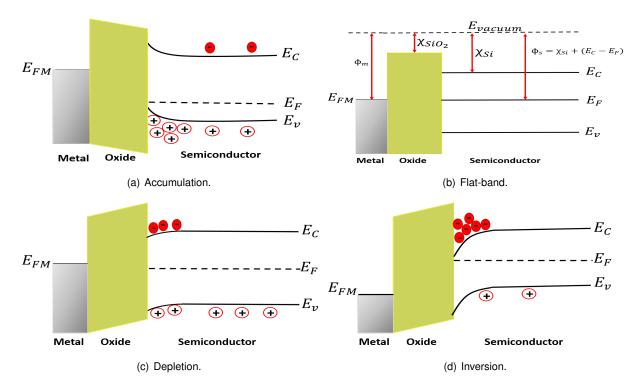

Depending on the voltage applied to the gate terminal, four operating regimes can be achieved as depicted in Figure 1.4.

- Accumulation: The majority carriers of the substrate are attracted to the Si Oxide interface, i. e. the channel area. In this case the transistor is blocked because the carrier concentration prevent the passage of electrons from source to drain [15].

- **Flat-band:** This regime occurs when the applied gate voltage  $V_{gs}$  cancels the bent of bands of the semiconductor. This voltage is called Flat-band voltage  $V_{FB}$ , thus,  $V_{gs} = V_{FB}$ . This allows a constant concentration of majority and minority carriers in the silicon substrate.

- **Depletion:** In this regime,  $V_{gs}$  is not sufficient to attract a large number of holes under the oxide and not positive enough to attract a large number of electrons [16], so, there is neither accumulation of holes in the

valence band nor electrons in the conduction band. The channel area is deserted, hence the term depletion or desertion zone. From this voltage, the inversion channel is considered created, since, due to the increase of  $V_{gs}$ , the electron density is greater than the number of holes in the bulk. The MOSFET operated in this region is said to be in weak inversion or the subthreshold regime [16].

• Inversion: also called strong inversion regime, the minority carriers are accumulated at the Si - Oxide interface, therefore a carrier path is created connecting the drain and source regions. The current flowing in the channel can be modulated by applying a voltage between the drain and the source.

Figure 1.4: Operation modes of a MOS structure.

## 1.3.2 I-V characteristics of conventional MOSFETs

The electrical operation of the MOSFET depends directly on the induction of a carrier inversion channel at the Oxide-Semiconductor interface. This inversion channel is controlled by the voltage applied to the gate, while the intensity of the current  $I_{ds}$  flowing across the channel, drain and source is controlled by the voltage applied to drain  $V_{ds}$ . Hence, when the voltage  $V_{ds}$  increases, the MOSFET transistor can have four operating modes displayed in Figure 1.5 and 1.6. We define the threshold voltage  $V_{th}$  as the minimum gate voltage value able to establish the conduction channel in a transistor [17]:

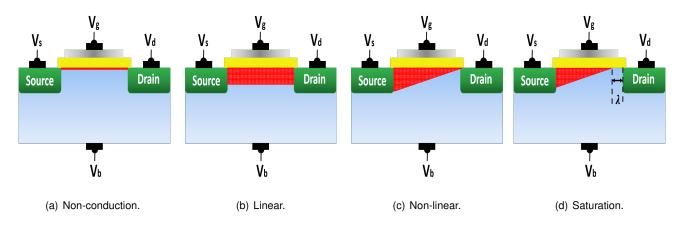

Figure 1.5: I-V Operation modes of a conventional long-channel MOS transistor.

• Non-conduction regime or blocked mode: The non-conduction regime implies a gate voltage  $V_{gs} < V_{th}$ . The applied gate voltage is not sufficient for the channel formation, as a result, the drain-source current is practically zero  $I_{ds} \approx 0$ . However, there is a small current that flows before reaching the threshold voltage called subthreshold current which is expressed as [18]:

$$I_{ds} \propto exp(\frac{qV_{gs}}{nKT}) \tag{1.1}$$

With n the idealty factor.

• Linear or ohmic regime: A gate voltage  $V_{gs}$  produces an electric field that can attract the minority carriers of the substrate to the  $Si - SiO_2$  interface. As a result, a small inversion layer near the insulating oxide becomes less p-type and, their conductivity is reduced [19]. As  $V_{gs}$  increases, the area near the oxide will attract more electrons than holes and will behave like an n-type channel. For values slightly superior to threshold  $V_{gs} > V_{th}$  and  $V_{ds} << V_{dsat}$  the channel region has the characteristics of a resistor, then the drain current increase linearly [16].

$$I_{ds} = \frac{W}{L} \mu_n C_{ox} (V_{gs} - V_{th}) V_{ds}$$

(1.2)

• Non-linear ohmic regime: This regime occurs when the potential induced by the voltage applied to  $V_{ds}$  is large enough to modify the vertical electric field, causing a loss of uniformity of the density of electrons in the channel [19]. A "pich-down" or pinch occurs at the end of the channel on the drain side, therefore, the characteristic  $I_d(V_{ds})$  will be non-linear as given in equation [1.3]:

$$I_{ds} = \frac{\mu_n C_{ox} W}{L} ((V_{gs} - V_{th}) V_{ds} - \frac{V_{ds}^2}{2})$$

(1.3)

Saturation regime: When V<sub>gs</sub> > V<sub>th</sub> and V<sub>ds</sub> ≥ V<sub>dsat</sub>, the channel ceases to exist near the drain, i.e. the channel is "pinched-off" [17], [20]. In this case, the drain current remains constant even if V<sub>ds</sub> continue to increase, the characteristic equation of this mode is given by:

$$I_{ds} = \frac{\mu_n C_{ox} W}{2L} (V_{gs} - V_{th})^2$$

(1.4)

Figure 1.6: Electrical response of a conventional MOSFET.

#### 1.3.3 Physical mechanisms of the TID in MOSFET devices

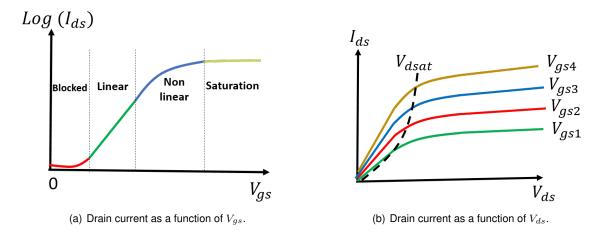

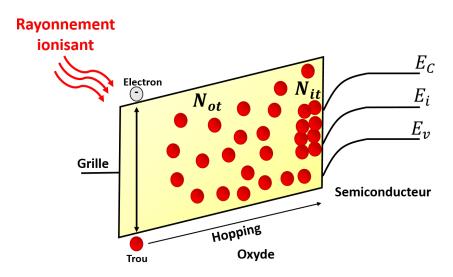

The physical mechanisms that take place in the creation of ionization defects in  $SiO_2$  are illustrated in Figure 1.7. First, radiation deposit energy through generation of electron-hole pairs. A fraction of these pairs recombine and the remaining free carriers are transported in the oxide. Then, near the interface, either holes trap in defect sites or interface traps are created via  $H^+$  reactions. These mechanisms will be described in details in the following sections.

#### Hole trapping

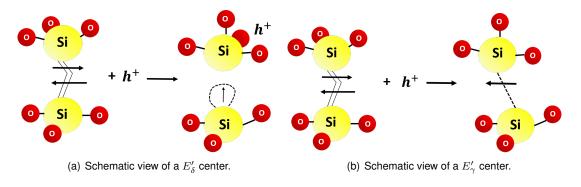

Oxide layers are the most sensitive parts of MOS devices affected by ionizing radiation. Actually, oxide traps are defects already existent in insulators that are related to oxygen vacancies in Si - O bonds [1, [21]]. The oxide trapped charge is typically net positive due to the capture of a hole in neutral oxygen vacancies and subsequent formation of E' centers. E' centers in amorphous  $SiO_2$  are defects due to Si dangling bonds that occur during removal of an oxygen atom. The principal types of E' centers are:  $E'_{\delta}$  and  $E'_{\gamma}$  (see Figure 1.8).

Figure 1.7: Model of radiation effects in oxides.

The  $E'_{\delta}$  centers have an energy level between 0.5 eV and 1.0 eV above the valence band, so they are involved in the transport of holes in the oxide volume. It is considered that the  $E'_{\delta}$  are shallow levels while the  $E'_{\gamma}$  are deeper levels 1.

Another characteristic of the  $E'_{\delta}$  centers is their ability to exchange charges with a near semiconductor region. Indeed, both the  $E'_{\delta}$  and the significantly deeper level hole trap center,  $E'_{\gamma}$ , can exchange charge with a semiconductor. When E' centers are located within 2.5 nm from the  $SiO_2 - Si$  interface, they are called border traps [22].

Figure 1.8: Schematic view of E' centers 1.

In silicon oxides, the density value of oxygen vacancies is  $10^{17} cm^{-3}$  and  $10^{20} cm^{-3}$ , for buried oxides and for conventional "silica glass" oxides, respectively [23].

For decades, silicon dioxide has been the insulating material used for MOSFET gate oxides, but with the continuous

scaling, its thickness has reached a physical limit. Indeed, a layer of  $SiO_2$  thinner than 1.2 nm can be permeable to gate-to-channel tunneling that can lead to a detrimental increase in leakage current. To solve this problem, high- $\kappa$  oxides have been implemented in new generations of transistors. Hafnium-based dielectrics, such as  $HfO_2$ , HfSiON or  $ZrO_2$ , have shown good compatibility with silicon technology as gate oxides [24, 25]. The concept of equivalent oxide thickness (EOT) has been introduced in order to describe the high- $\kappa$  dielectric with respect to  $SiO_2$ . EOT is the equivalent thickness of  $SiO_2$  oxide giving the same capacitance for any dielectric of physical thickness  $t_{ox}$  and dielectric constant  $\epsilon_{ox}$ . Then, the EOT is expressed as:

$$EOT = t_{ox} \frac{\epsilon_{SiO_2}}{\epsilon_{ox}}$$

(1.5)

The effects of radiation on  $SiO_2$  gate oxides have been studied extensively [26, 27] as opposed to  $High - \kappa$  dielectrics which are still a subject of study [25, 28, 29, 30].

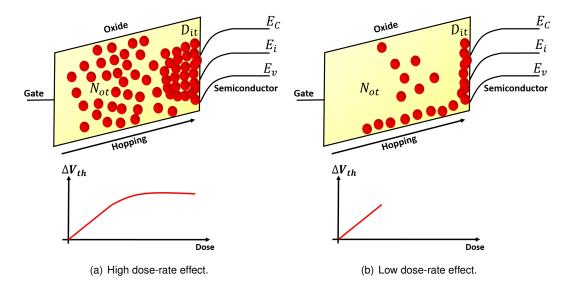

When the device is exposed to high energy ionizing radiation (X or  $\gamma$ ), electron-hole pairs are created. The released electrons remain in the oxide for a short period of time (few ps) due to their high mobility ( $20 \ cm^2 V^{-1} s^{-1}$ ) and move towards the gate. On the other hand, a fraction of the created holes recombine immediately (prompt recombination), and the remaining fraction move slowly, due to its very low mobility in oxides (in the range of  $10^{-4}$  to  $10^{-11} \ cm^2 V^{-1} s^{-1}$ ), by discrete stochastic jumps (hopping) towards the  $Si - SiO_2$  interface [31, 32]. In consequence, the net charge induced by the radiation in the oxide is positive.

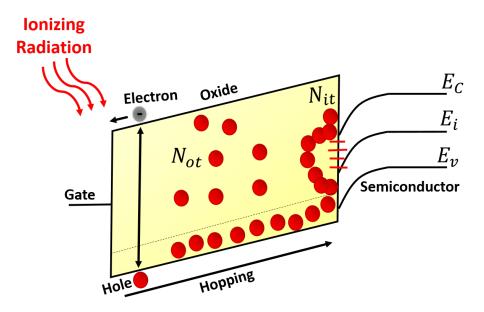

#### Interface traps creation

The build-up of interface traps is a more complex process than that of oxide charge trapping. The presence of interface traps is inherent in the manufacturing process of the device due to the incompatibility in lattice parameters between the insulating oxide ( $SiO_2$ ) and the semiconductor (Si) [33, [34].

The radiation-induced interface traps,  $N_{it}$  in  $cm^{-2}$  or  $D_{it}$  in  $cm^{-2}eV^{-1}$ , are dominated by a family of  $Si - SiO_2$  interface silicon dangling bond defects called  $P_b$  centers [33], [34]. The most important and abundant of these centers is called the  $Pb_0$  center. A secondary contribution is provided by a closely related defect called  $Pb_1$ . Both Pb centers are silicon dangling bond defects in which the central silicon is back bonded to three other silicon atoms [34, 35].

It is well known that the formation of interface traps initiates after irradiation, either immediately (prompt generation), or slowly (delayed generation) depending on the temperature and the applied electric field [36, 37]. Several hypotheses have been formulated to explain this phenomenon, all of which coincide on the fact that the main elements responsible for the formation of interface traps are hydrogen impurities. Lai [38, 39] has proposed a two-step model in which he describes that the holes generated in the oxide are capable of breaking the Si - O - Si bonds at the interface. The second step corresponds to the formation of interface traps due to the capture of electrons.

McLean [40] proposed in his work published in 1976 a two-step model to describe the origin of interface traps. The first step corresponds to the transport of holes through the oxide towards the  $Si - SiO_2$  interface. It is shown that the hole transport can be well described by a model of holes moving via polaron hopping between localized sites. The second step of the model corresponds to the radiation-induced buildup of interface traps.

This model helps to explain the difference between the rate of accumulation and creation of discrete levels at the interface. However, this model is not able to predict the quantity of interface traps generated according to the applied electric field.

The Hole-Trapping / Hydrogen-Transport  $(HT^2)$  [39, [41] model is a variation of the McLean model and explains that the discrete levels are generated by the interaction of hydrogen ions with the holes trapped at the interface. The interaction is proportional to the cross section of the trapped holes and proportional to  $E^{-1/2}$ . However, this model does not explain if the ions are generated throughout the oxide or only in the region close to the interface nor if there is a relationship with the manufacturing process.

The best experimental description is given by the *continuous time random walk* (CTRW) model [32, 40], in which the transport mechanism is based on discrete jumps of the holes with a random distribution of traps. The term "Polaron" refers to the situation where the carrier interacts with the medium and creates a lattice distortion in the neighborhood. It is important to note that all the assumptions have been made on the interaction of radiation with hydrogen. However, this model fails to correctly explain the phenomenon of trap formation at the interface.

The interface trap build up is a time-dependent phenomenon. When MOS devices are exposed to ionizing radiation, interface trapped charges multiply, which is an immediate effect of the interaction between the interface and ionizing radiation commonly called "early" component [42, 43]. The second component, called the "delayed component", occurs seconds to thousands of seconds after irradiation and consists of a severe increase in the number of charges trapped at the interface [44, 45]. It is presumed that this phenomenon is due to the slowness of transport of the charges trapped in the oxide towards the interface [4].

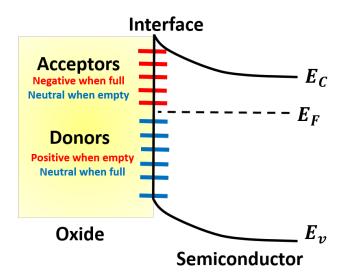

Interface traps can be classified into two categories, as shown in Figure 1.9:

- · Donor: exhibits neutral behavior when it is filled with an electron and positive when it is empty.

- · Acceptor: is negatively charged when filled with an electron and neutral when empty.

Figure 1.9: Representation of interface states.

Generally, the interface states  $(eV^{-1}cm^{-2})$  are mainly donor-like in the lower half, and acceptors-like in the upper half of the silicon bandgap [4] and their density  $D_{it}$  vary between  $10^9 \ eV^{-1}cm^{-2} \le Dit \le 10^{12} \ eV^{-1}cm^{-2}$ .

#### 1.3.4 Impact on electrical characteristics

#### Threshold voltage shift

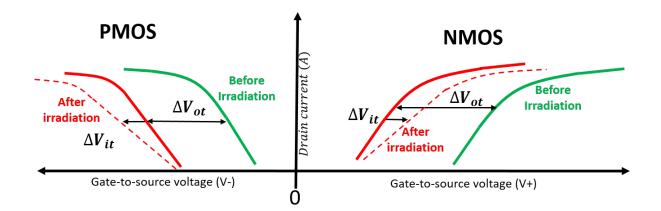

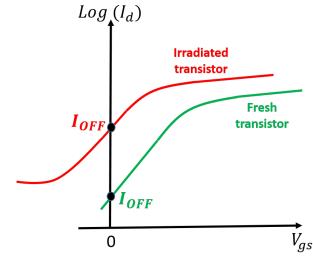

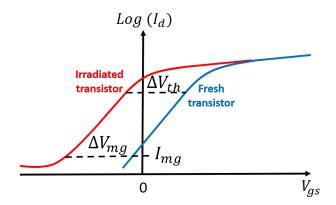

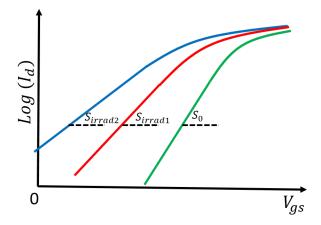

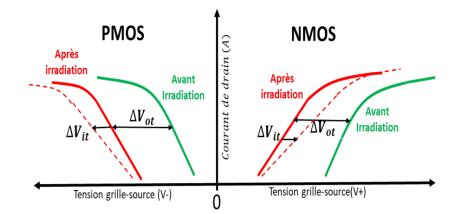

The main parameter affected by the radiation-induced trapped charges is the threshold voltage of the transistor. As a matter of fact, the oxide trapped charges increase the effective electric field and contribute to make easier or more difficult the inversion of the n-type or p-type channels, respectively, which consequently leads to a negative threshold voltage shift ( $\Delta V_{th}$ ). The interface trapped charges interact with the carriers of the channel close to the interface, which modifies the surface potential of the MOS structure according to the gate voltage, producing a variation in the subthreshold slope *SS* [27] [46]. These failure mechanisms are present in both NMOS and PMOS transistors. In NMOS devices, the negative  $\Delta V_{th}$  makes the transistor able to turn-on with a lower gate voltage until the loss of control of the channel, i.e. when the transistor becomes conductive though no gate voltage is applied. For a PMOS transistor, the excess of oxide trapped charges also leads to a negative  $\Delta V_{th}$ . In this case, it becomes more difficult to switch-on the transistor [2] [4].

The contribution to  $\Delta V_{th}$  due to the oxide trapped charges is [4]:

$$\Delta V_{ot} = -\frac{1}{C_{ox}} \int_0^{t_{ox}} \Delta \rho(x) \frac{x}{t_{ox}} dx = -\frac{\Delta Q_{ot}}{C_{ox}}$$

(1.6)

While the contribution of the interface trapped charges to  $\Delta V_{th}$  is:

$$\Delta V_{it} = -\frac{\Delta Q_{it}}{C_{ox}} \tag{1.7}$$

And then, the total  $\Delta V_{th}$  is expressed as the shift caused by the oxide trapped charges and the interface trapped charges.

$$\Delta V_{th} = \Delta V_{ot} + \Delta V_{it} = -\frac{1}{C_{ox}} (\Delta Q_{ot} + \Delta Q_{it})$$

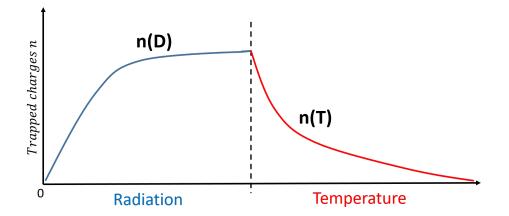

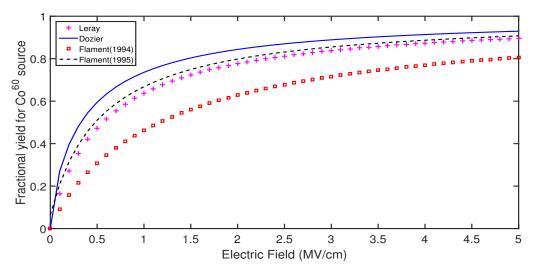

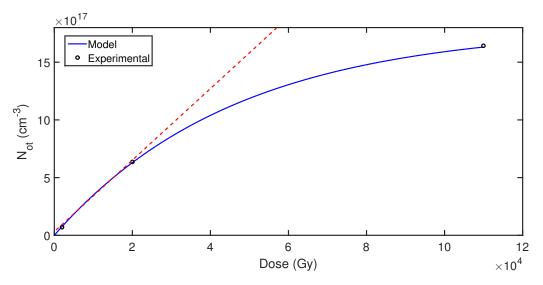

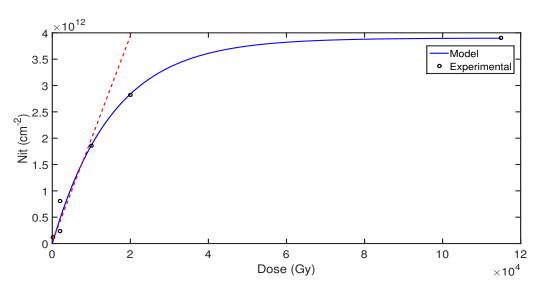

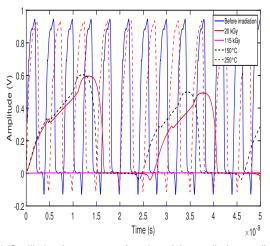

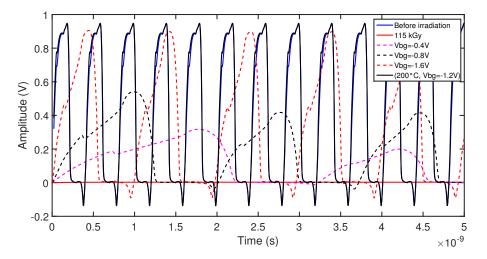

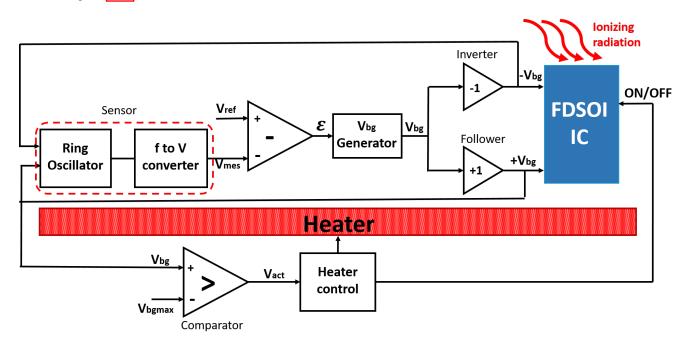

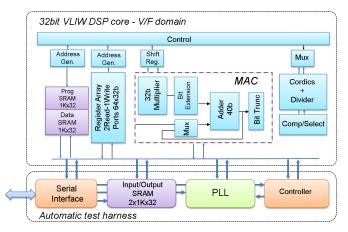

(1.8)