## Primitives de sécurité à base de mémoires magnétiques

Frédéric Martial Ouattara

#### ▶ To cite this version:

Frédéric Martial Ouattara. Primitives de sécurité à base de mémoires magnétiques. Micro et nanotechnologies/Microélectronique. Université Montpellier, 2020. Français. NNT: 2020MONTS072 . tel-03348805

### HAL Id: tel-03348805 https://theses.hal.science/tel-03348805v1

Submitted on 20 Sep 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITE DE MONTPELLIER

En SyAM - Systèmes Automatiques et Micro-électroniques

École doctorale I2S - Information, Structures et Systèmes

Unité de recherche LIRMM

## Primitives de sécurité à base de mémoires magnétiques

### Présentée par Frederic Ouattara Le 06/11/2020

Sous la direction de Lionel TORRES

#### Devant le jury composé de

Lilian BOSSUET

Jean-Michel PORTAL

lan O'CONNOR

Bertrand CAMBOU

Pascal NOUET

Ken MACKAY

Lionel TORRES

Professeur à l'Université Jean-Monnet Professeur à l'Université Aix-Marseille Professeur à l'Ecole Centrale de Lyon Professeur à Northern University of Arizona Professeur à l'Université de Montpellier Ingénieur à CROCUS Technology Professeur à l'Université de Montpellier Rapporteur

Rapporteur

Examinateur

Examinateur

Président

Invité

Directeur de thèse

#### REMERCIEMENTS

Ces travaux de thèse n'auraient pu être réalisés sans le soutien et l'aide de certaines personnes. Je tiens par la présente à remercier toutes les personnes qui ont participé, de façon plus ou moins directe, à cette étape si importante pour moi.

Tout d'abord, j'adresse un immense remerciement à mon directeur de thèse Lionel TORRES. Merci pour la confiance accordée, son dynamisme et sa bonne humeur. Je n'aurai jamais pu aller aussi loin dans ce travail sans sa disponibilité, sa patience, ses conseils et son savoir. Je le remercie encore pour la rigueur scientifique qu'il a su m'insuffler.

Je souhaite ensuite remercier Lilian BOSSUET et Jean-Michel PORTAL qui m'ont fait l'honneur de consacrer du temps pour relire cette thèse et en être les rapporteurs. Je tiens également à remercier lan O'CONNOR, Bertrand CAMBOU, Pascal NOUET et Ken MACKAY d'avoir accepté d'assister à la soutenance de cette thèse, je les remercie pour leurs commentaires constructifs et leur participation active et fondamentale lors de ma soutenance.

Mes années au LIRMM ont été une formidable expérience grâce à mes collègues et au personnel administratif que je tiens à remercier. Je remercie particulièrement Caroline Lebrun, secrétaire du département microélectronique pour sa disponibilité et son aide si précieuse. Merci également à mes collègues doctorant du LIRMM pour leur sympathie et leur accueil chaleureux. Ils ont participé à ce que l'ambiance de travail soit très agréable à travers nos pauses café et les différentes sorties organisées.

J'exprime ma gratitude à Arash, pour sa disponibilité, son implication dans mes travaux de thèse, à travers nos moments de collaboration.

Mes remerciements vont aussi à ma famille notamment mes parents, mes frères, mes cousins. Je les remercie pour leur soutien, leur encouragement qui ont été sans faille durant ces années de thèse.

Enfin je remercie ma tendre Sahadatou pour sa patience et son soutien inconditionnel. Elle est pour beaucoup dans l'achèvement de ce travail de thèse.

## Table des matières

| Table o | des m  | natières                                                                      | 5  |

|---------|--------|-------------------------------------------------------------------------------|----|

| Table o | des fi | gures                                                                         | 9  |

| Liste d | es ta  | bleaux                                                                        | 13 |

| Glossa  | ire    |                                                                               | 15 |

| Chapit  | re I   | Introduction Générale                                                         | 17 |

| 1. (    | Conte  | exte                                                                          | 17 |

| 2. (    | Objec  | tif de la thèse                                                               | 19 |

| Chapit  | re II  | Les Mémoires magnétiques à accès aléatoire (MRAM)                             | 21 |

| 1. I    | ntro   | duction                                                                       | 21 |

| 2. L    | La spi | ntronique                                                                     | 22 |

|         |        | La Magnétorésistance à effet tunnel (TMR)                                     |    |

| 2       |        | La Jonction tunnel magnétique (JTM)                                           |    |

| 3. L    | Les te | echnologies MRAM                                                              | 29 |

|         |        | Mécanisme d'écriture FIMS: Field Induced Magnetic Switching                   |    |

| 3       | 3.2.   | Mécanisme d'écriture Toggle                                                   | 30 |

| 3       | 3.3.   | Mécanisme d'écriture TAS: Thermally Assisted Switching                        | 32 |

| 3       | 3.4.   | Mécanisme d'écriture STT : Spin Transfert Torque                              | 38 |

| 3       | 3.5.   | Mécanisme d'écriture VCMA : Voltage-Controlled Magnetic Anisotropy            | 40 |

| 3       | 3.6.   | Mécanisme d'écriture SOT : Spin Orbit Torque                                  | 42 |

| 4. (    | Concl  | usion                                                                         | 43 |

| Chapit  | re III | Générateur de nombres véritablement aléatoires à base de STT-MRAM             | 45 |

| 1. I    | ntro   | duction                                                                       | 45 |

| 2. L    | Les ge | énérateurs de nombres pseudo aléatoires (PRNG)                                | 46 |

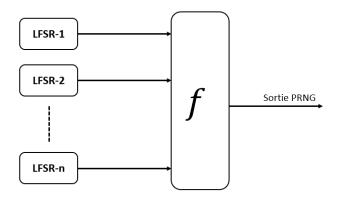

| 2       | 2.1.   | Principe et fonctionnement des PRNG                                           | 47 |

| 2       |        | Conception de PRNG                                                            |    |

| 3. L    | Les ge | énérateurs de nombres véritablement aléatoires (TRNG)                         | 51 |

| 3       | 3.1.   | Les sources d'aléa et les différentes techniques d'extraction d'aléa dans les |    |

|         |        | circuits électroniques                                                        | 52 |

| 3       | 3.2.   | Méthodes de post-traitement des TRNG                                          | 56 |

| 3       | 3.3.   | Evaluation des générateurs de nombre aléatoires                               | 58 |

| 4. 1    | TRNG   | à base de STT-MRAM                                                            | 61 |

| 2       | 4.1.   | La revue des travaux dans la littérature                                      | 62 |

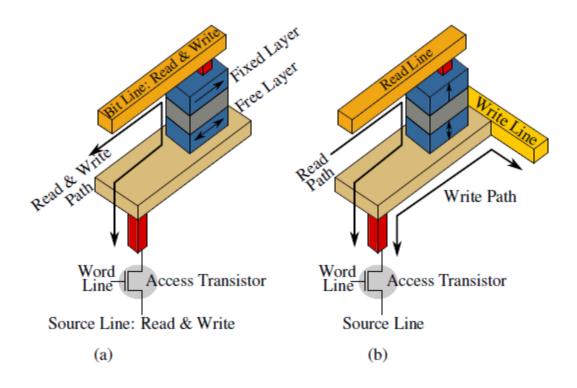

|     | 4.2.     | Environnement de conception hybride CMOS/STT-MRAM                           | 70   |

|-----|----------|-----------------------------------------------------------------------------|------|

|     | 4.3.     | Les amplificateurs de lecture                                               | 74   |

|     | 4.4.     | Comparaison des différentes cellules de lecture                             | 79   |

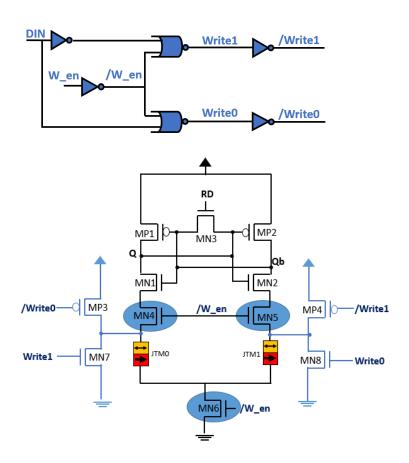

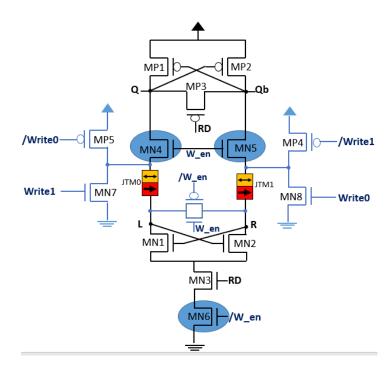

|     | 4.5.     | Le circuit d'écriture                                                       | 81   |

|     | 4.6.     | Système complet basé sur le spin dice                                       | 83   |

|     | 4.7.     | Flot de conception du TRNG                                                  | 85   |

|     | 4.8.     | Caractérisation et test du démonstrateur                                    | 86   |

| 5   | . Cond   | clusion                                                                     | 89   |

| Cha | oitre I\ | Générateur de nombre véritablement aléatoire à base de TAS-MRAM             | 91   |

| 1   | . Intro  | duction                                                                     | 91   |

| 2   | . Princ  | cipe de fonctionnement                                                      | 91   |

| 3   | . Outi   | ls et méthodes d'extraction d'aléa dans les TAS-MTJ                         | 92   |

| 4   | . Instr  | umentation et expérimentation                                               | 94   |

|     | 4.1.     |                                                                             |      |

|     | 4.2.     | Exploration de TRNG sur une jonction TAS                                    | 96   |

|     | 4.3.     | Utilisation des procédures de post-traitement pour améliorer la probabilité | de   |

|     |          | sortie                                                                      | 97   |

|     | 4.4.     | Amélioration du biais à travers une boucle de contre réaction               | 99   |

| 5   | . Evalı  | uation statistique des nombres aléatoires générées                          | 101  |

| 6   | . Cond   | clusion                                                                     | 102  |

| Cha | oitre V  | Fonctions Non Clonables Physiquement à base de MRAM                         | 105  |

| 1   | . Intro  | duction                                                                     | 105  |

| 2   | . Prop   | riétés et paramètres des PUF                                                | 106  |

|     | 2.1.     | Intra-distance ou la reproductibilité                                       | 107  |

|     | 2.2.     | Inter-distance ou l'unicité                                                 | 108  |

| 3   | . La Cl  | assification des PUF                                                        | 109  |

|     | 3.1.     | Les PUF à base de dispositif silicium et non-silicium                       | 109  |

|     | 3.2.     | PUF fort et PUF faible                                                      | 116  |

| 4   | . Les r  | néthodes d'évaluation des PUF                                               | 116  |

|     | 4.1.     | Méthode d'évaluation basé sur le calcul de la distance ou du poids de Hamr  | ning |

|     |          | 116                                                                         |      |

|     | 4.2.     | Méthode d'évaluation statistiques de la qualité des PUF                     | 118  |

| 5   | . Revu   | ies sur les PUF à base de MRAM                                              | 119  |

|     | 5.1.     | Extraction basée sur l'écriture des JTM                                     | 119  |

| 5.2         | . Extraction basée sur les variations aléatoires de la résistance des JTM | 121 |

|-------------|---------------------------------------------------------------------------|-----|

| 5.3         | . Synthèse                                                                | 121 |

| 6. For      | nction non clonable physiquement basée sur la TAS-MRAM                    | 122 |

| 6.1         | Principe d'extraction                                                     | 122 |

| 6.2         | . Instrumentation et Expérimentation                                      | 122 |

| 7. Cor      | nclusion                                                                  | 127 |

| Chapitre '  | VI Conclusion générale et perspectives                                    | 129 |

| 1. Cor      | nclusion générale                                                         | 129 |

| 2. Per      | spectives                                                                 | 130 |

| Publication | ons et communications                                                     | 132 |

| Public      | ations                                                                    | 132 |

| Poster      | S                                                                         | 132 |

| Référence   | es                                                                        | 133 |

## Table des figures

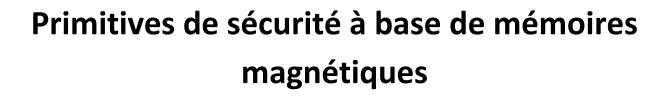

| Figure I-1 :  | Projection de l'évolution du marché des MRAM [1]                                                                                                                            | 17 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

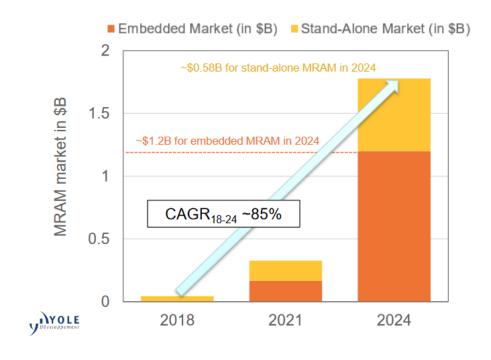

| Figure II-1 : | Orientation des moments magnétiques selon le type de matériau [6]                                                                                                           | 22 |

| Figure II-2 : | Effet de la magnétorésistance anisotrope (AMR) [7]                                                                                                                          | 23 |

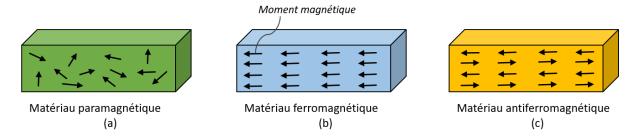

| Figure II-3 : | Première observation de la GMR sur des multicouches Fe/Cr à 4,2 K [11]                                                                                                      | 24 |

| Figure II-4 : | Effet de la magnétorésistance géante (GMR) [7]                                                                                                                              | 25 |

| Figure II-5 : | Jonction tunnel magnétique [6]                                                                                                                                              | 28 |

| _             | (a) Distribution des valeurs de résistances min et max d'une mémoire MRAM d<br>8Kbits (b) Dépendance de la TMR à la tension de lecture pour des JTM à base d<br>MgO et AlOx | e  |

| Figure II-7 : | (a) Structure d'une JTM en technologie FIMS (b) Principe d'écriture FIMS                                                                                                    | 30 |

| Figure II-8 : | (a) Structure d'un JTM en technologie Toggle (b) Principe de lecture/écriture Toggle                                                                                        | 31 |

| Figure II-9 : | Séquence d'écriture Toggle                                                                                                                                                  | 32 |

| Figure II-10  | : Structure d'une JTM en technologie TAS                                                                                                                                    | 33 |

| Figure II-11  | : Séquence d'écriture d'une JTM TAS : Passage d'un état parallèle à un état antiparallèle                                                                                   | 34 |

| Figure II-12  | : Structure d'une jonction SR ou MLU                                                                                                                                        | 35 |

| Figure II-13  | : Unité logique magnétique (a) cellule TAS-MTJ (b) cellule SR-MTJ (c) porte logique virtuel XOR                                                                             | 37 |

| Figure II-14  | : Principe du « Match in place » (a) code non valide, (b) code valide                                                                                                       | 37 |

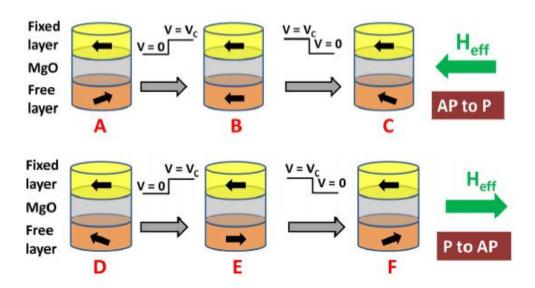

| Figure II-15  | : (a) structure de la STT-JTM (b) Passage d'un état AP => P (c) Passage d'un état<br>P=> AP                                                                                 |    |

| Figure II-16  | : Commutation induite par tension (MeRAM) [38]                                                                                                                              | 41 |

| Figure II-17  | : Spin Orbit Torque- MRAM (a) Jonction STT (b) Jonction SOT                                                                                                                 | 43 |

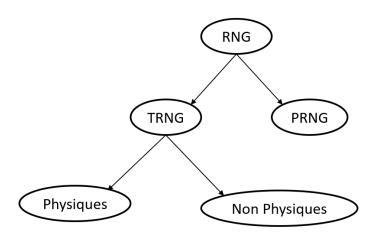

| Figure III-1  | : Classification des générateurs de nombres aléatoires                                                                                                                      | 46 |

| Figure III-2  | : Combinaison de LFSR par une fonction booléenne                                                                                                                            | 48 |

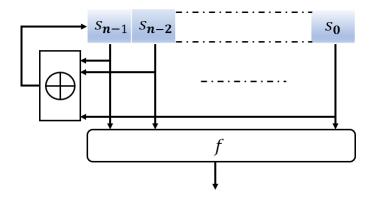

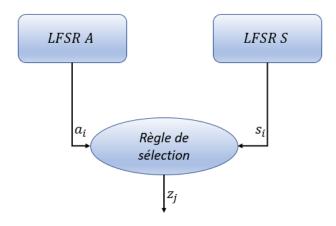

| Figure III-3  | : PRNG filtré à base de LFSR                                                                                                                                                | 49 |

| Figure III-4 | : Générateur par rétrécissement                                                                                                                                                                                                                  |

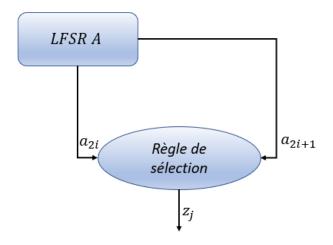

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure III-5 | : Générateur par auto-rétrécissement 5                                                                                                                                                                                                           |

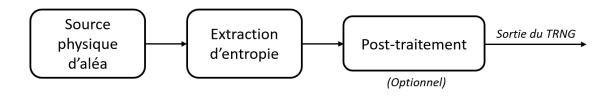

| Figure III-6 | : Structure générique d'un TRNG                                                                                                                                                                                                                  |

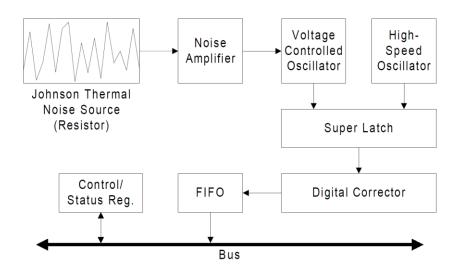

| Figure III-7 | : Schéma de principe du TRNG développé par Intel et discuté dans [68] 5                                                                                                                                                                          |

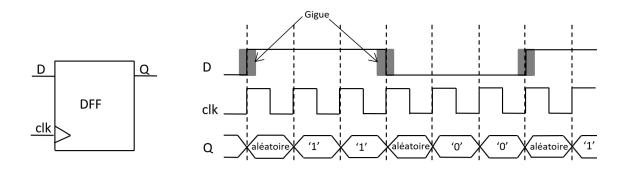

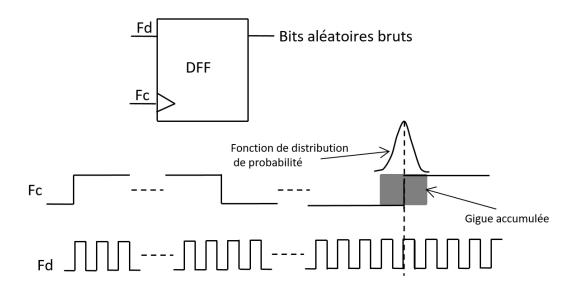

| Figure III-8 | : Echantillonnage de la gigue d'un signal périodique par un signal d'horloge 54                                                                                                                                                                  |

| Figure III-9 | : TRNG basé sur l'accumulation de la gigue proposée dans [72] 54                                                                                                                                                                                 |

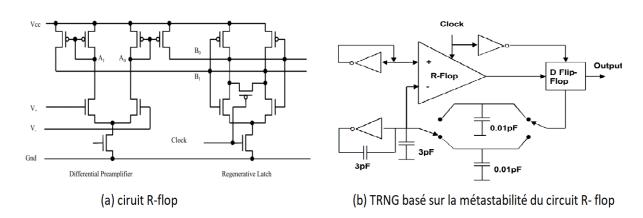

| Figure III-1 | 0 : TRNG basé sur la métastabilité présenté dans [77]5                                                                                                                                                                                           |

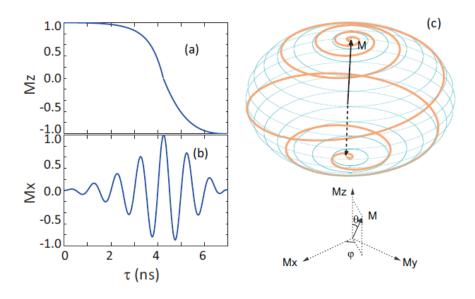

| Figure III-1 | 1 : Précession de l'aimantation sous l'influence d'un courant de spin : dépendance temporelle de (a) Mz et (b) Mx, (c) processus d'inversion du moment magnétique. θ et φ représente l'état initial du moment magnétique de la couche libre [91] |

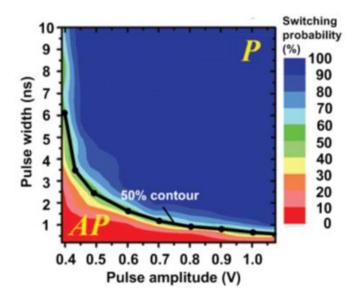

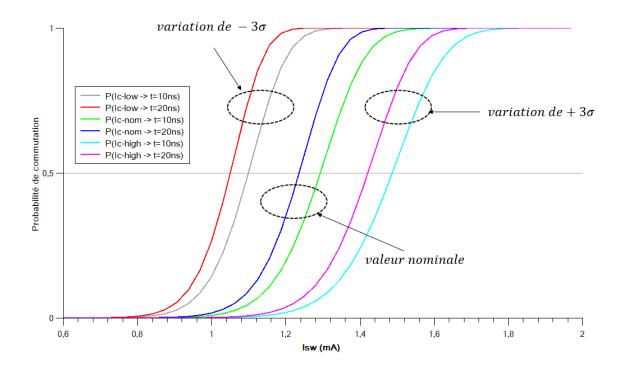

| Figure III-1 | 2 : Probabilité de commutation d'une JTM-STT en fonction de l'amplitude du courant d'écriture et de la durée de l'impulsion. (Commutation AP -> P) [95] 6                                                                                        |

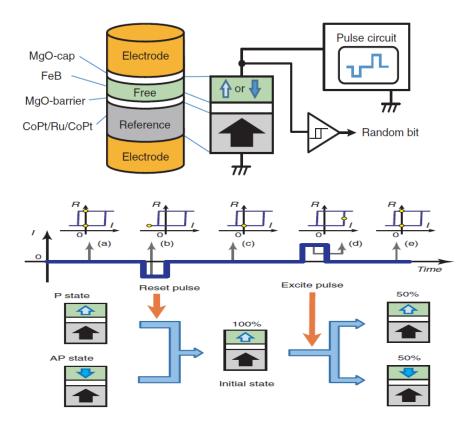

| Figure III-1 | 3 : La méthode « spin dice ». Les impulsions de réinitialisation et d'excitation sont appliquées de manière séquentielle [93]6                                                                                                                   |

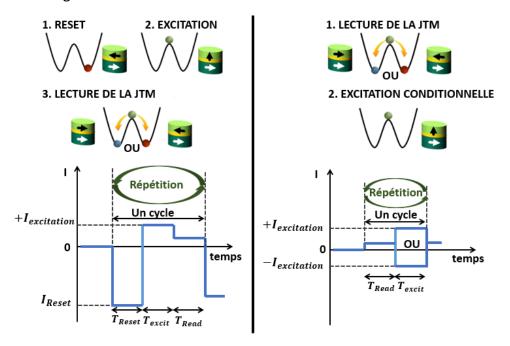

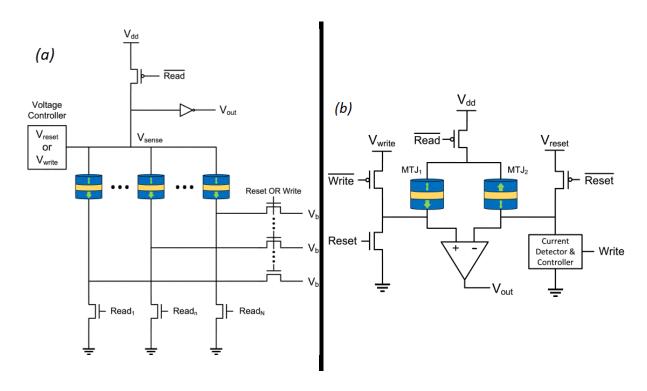

| Figure III-1 | 4 : Méthodes de génération des Rbs (à gauche) la méthode avec réinitialisation de la JTM proposé dans [97].                                                                                                                                      |

| Figure III-1 | 5 : TRNG basé sur une jonction STT avec écriture d'excitation conditionnelle, suivi<br>d'un contrôle de la probabilité de sortie en temps réel6                                                                                                  |

| Figure III-1 | 6 : TRNG basé sur (a) plusieurs JTM en parallèle et (b) sur une paire de JTM en<br>série[104]6                                                                                                                                                   |

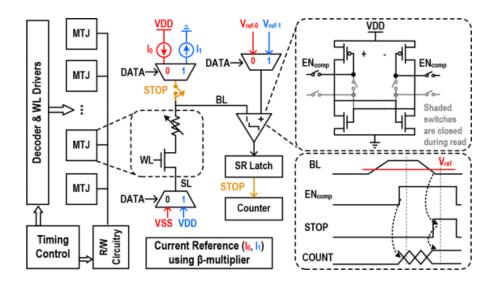

| Figure III-1 | 7 : Circuit mémoire STT-MRAM utilisé comme TRNG à travers un échantillonnage<br>du temps de commutation de la JTM lors de son écriture à courant faible [105].                                                                                   |

| Figure III-1 | 8 : Simulation d'une séquence d'écriture d'une jonction STT7                                                                                                                                                                                     |

| Figure III-1 | 9 : Probabilité de commutation de la JTM en fonction du courant d'écriture 7                                                                                                                                                                     |

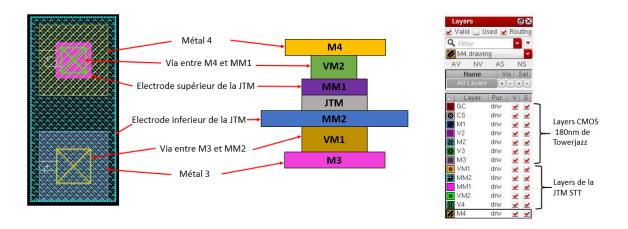

| Figure III-2 | 0 : Vue layout de la JTM ainsi que les layers magnétiques du DKIT7                                                                                                                                                                               |

| Figure III-2 | 1 : Structure de Black & Das avec deux JTM STT et le circuit d'écriture7                                                                                                                                                                         |

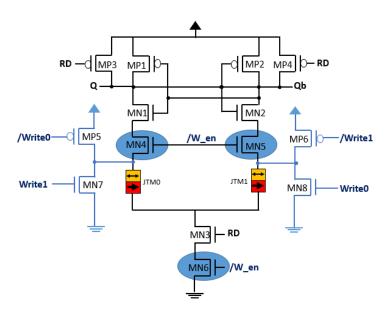

| Figure III-2 | 2 : Structure de lecture Hass adaptée au circuit d'écriture STT7                                                                                                                                                                                 |

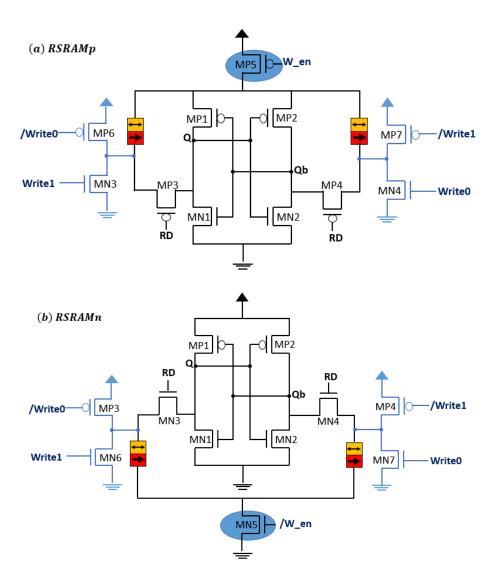

| Figure III-23 | 3 : Structure de lecture PCSA                                                                                                                                                                                                                                                                                                                                                                    | 78 |

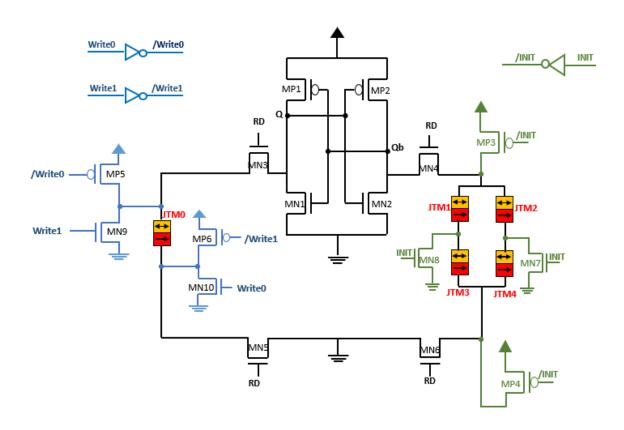

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure III-24 | 4 : Structure de lecture SRAM Rémanent (RSRAM) (a) avec transistor d'accès PMOS et (b) avec transistor d'accès NMOS                                                                                                                                                                                                                                                                              | 79 |

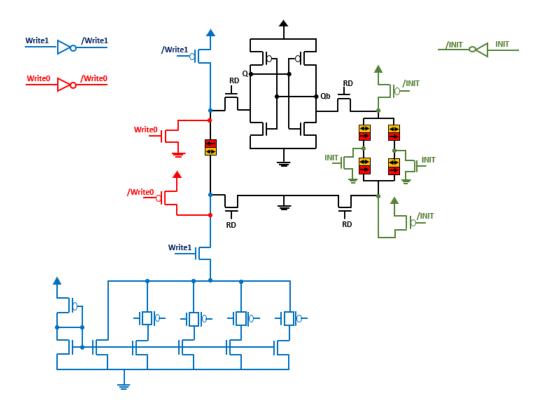

| Figure III-25 | 5 : Cellule RSRAMn adaptée à un système d'écriture non complémentaire<br>(référence composée de 4JTM avec le circuit d'initialisation)                                                                                                                                                                                                                                                           | 31 |

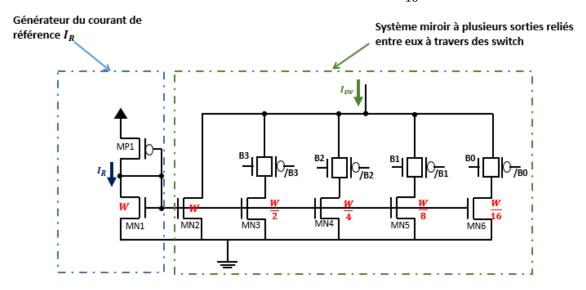

| Figure III-26 | 6 : Miroir de courant programmable comme source de courant pour l'écriture de la JTM                                                                                                                                                                                                                                                                                                             |    |

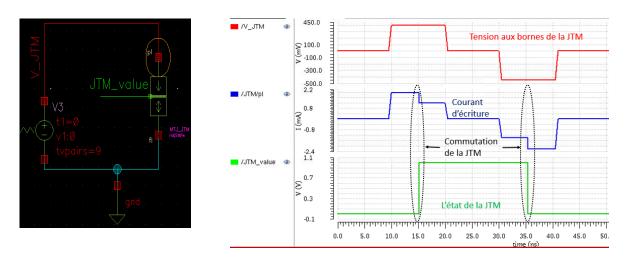

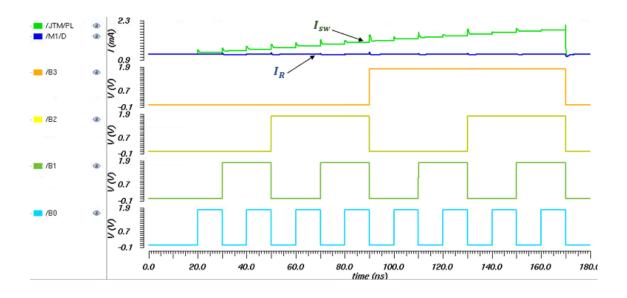

| Figure III-27 | 7 : Simulation comportementale de la source de courant programmable                                                                                                                                                                                                                                                                                                                              | 33 |

| Figure III-28 | 8 : Circuit d'écriture et de lecture d'une JTM avec la possibilité de faire varier le courant d'écriture a « 1 » de la JTM                                                                                                                                                                                                                                                                       | 34 |

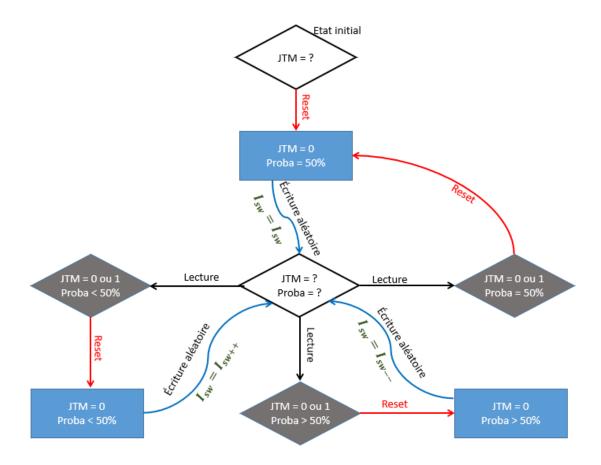

| Figure III-29 | 9 : Algorithme de contrôle et de gestion de la probabilité de sortie à « 1 » de la JTM. Les trois états en rectangle correspondent aux probabilités de sortie calculées après chaque reset. L'état au milieu indique l'état inconnu de la JTM après chaque écriture aléatoire et les 3 états en gris indiquent l'état de la JTM ainsi que la probabilité de sortie actuelle après chaque lecture | 35 |

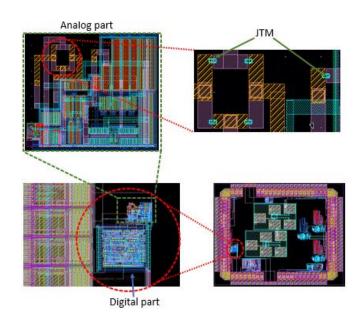

| Figure III-30 | 0 : Layout du circuit et son packaging dans un boitier de type DIL40                                                                                                                                                                                                                                                                                                                             | 36 |

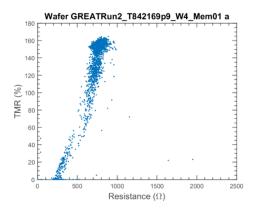

| Figure III-31 | 1 : Mesure de la résistance parallèle et de la TMR sur deux wafers contenant notre circuit (résultats de SPINTEC)                                                                                                                                                                                                                                                                                | 37 |

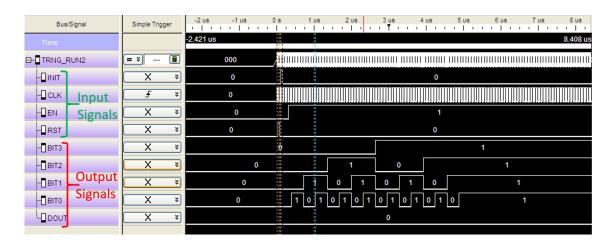

| Figure III-32 | 2 : Test d'un circuit validant le fonctionnement de la partie digital du TRNG                                                                                                                                                                                                                                                                                                                    | 38 |

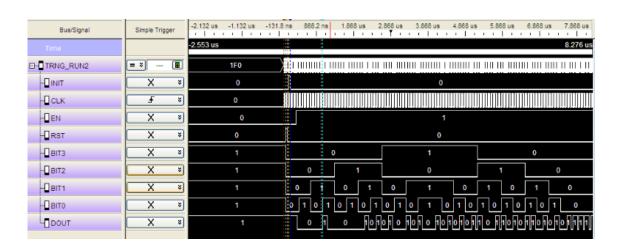

| Figure III-33 | 3 : Résultats de mesures d'un circuit présentant un phénomène qui semble aléatoire                                                                                                                                                                                                                                                                                                               | 38 |

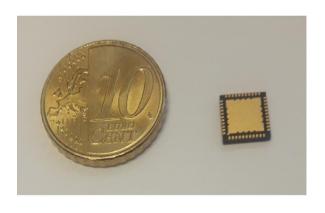

| Figure IV-1   | : (a) 1kbits TAS-MRAM dans un Package QFN44 (b) image microscopique de l'intérieur du QFN44                                                                                                                                                                                                                                                                                                      | 93 |

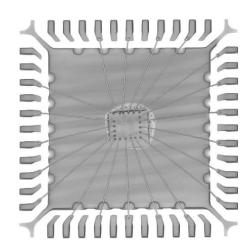

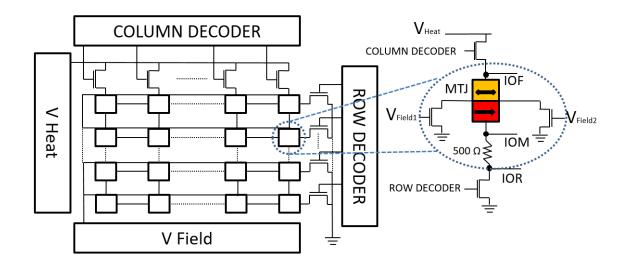

| Figure IV-2   | : Architecture de la puce composée de 1024 bits TAS-MRAM                                                                                                                                                                                                                                                                                                                                         | €  |

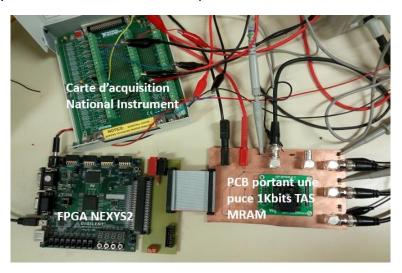

| Figure IV-3   | : Banc de test comportant une carte FPGA pour la programmation des composants utilisés pour l'écriture de la JTM TAS, une carte d'acquisition pour la lecture et le PCB contenant une puce 1kbit de TAS-MRAM                                                                                                                                                                                     |    |

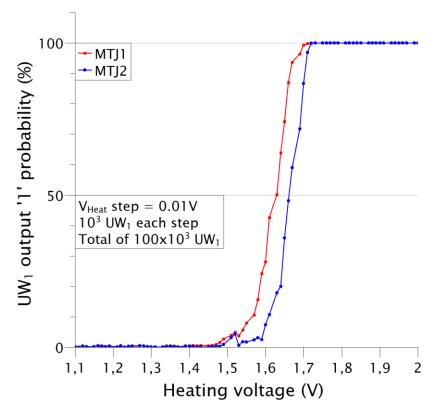

| •             | : Probabilité de commutation des JTM TAS en fonction de l'amplitude de la tension de chauffage                                                                                                                                                                                                                                                                                                   | 95 |

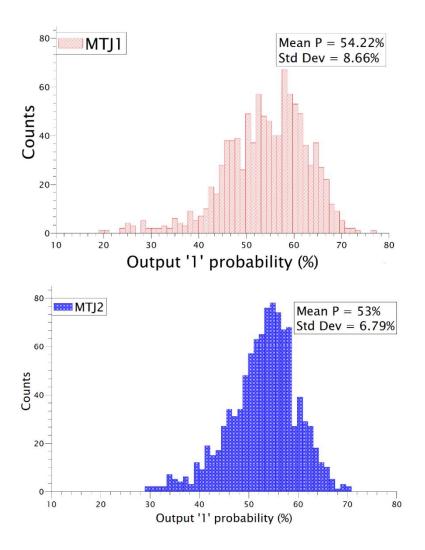

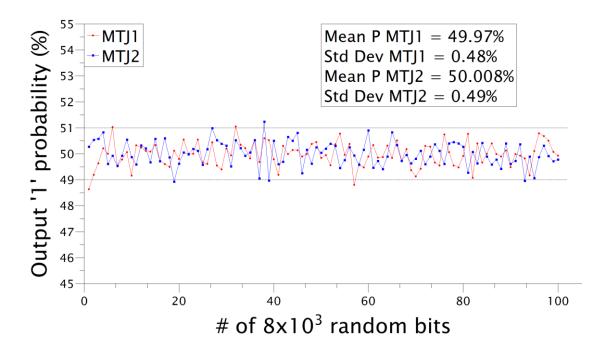

| Figure IV-5 | Rbs sur un total de 10 <sup>7</sup> Rbs générés par les jonctions MTJ 1 (rouge) et MTJ 2                                                                                         |      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|             | (bleu).                                                                                                                                                                          | . 97 |

| Figure IV-6 | : La probabilité de commutation après un post-traitement de Von Neumann                                                                                                          | . 98 |

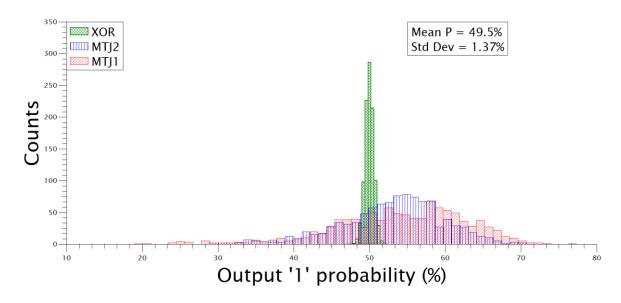

| Figure IV-7 | : Histogramme de la probabilité de commutation après un post-traitement XO sur deux JTMs (MTJ1 et MTJ2)                                                                          |      |

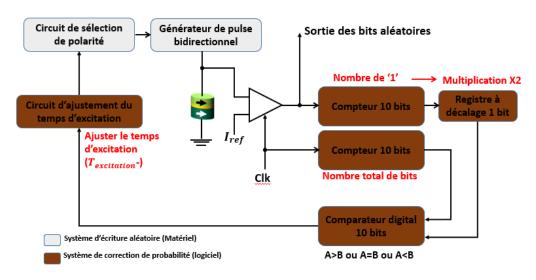

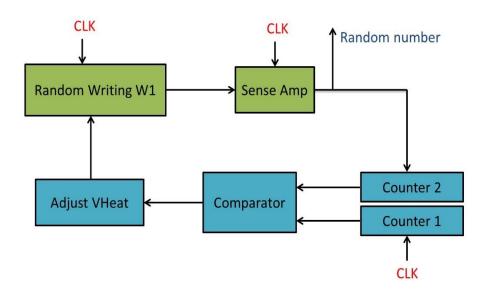

| Figure IV-8 | : Architecture de la boucle de contre réaction                                                                                                                                   | 100  |

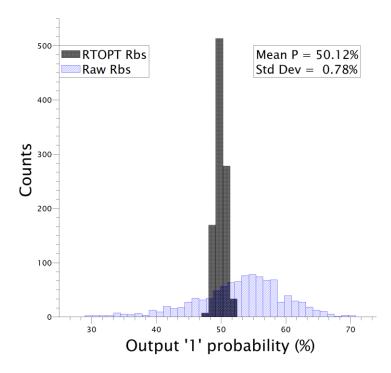

| Figure IV-9 | : Histogramme de la probabilité de commutation après un post-traitement bas<br>sur la RTOPT                                                                                      |      |

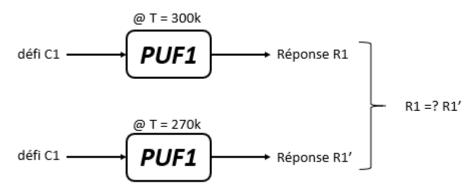

| Figure V-1  | : Evaluation de la reproductibilité de la réponse d'une PUF sous différentes températures de fonctionnement                                                                      | 107  |

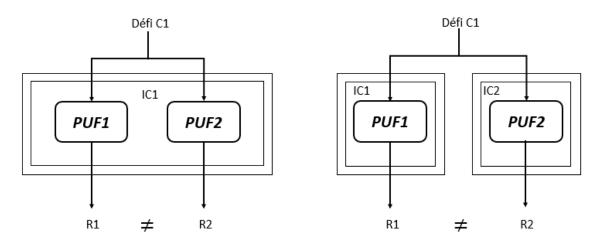

| Figure V-2  | : Evaluation de l'unicité de la réponse des PUF                                                                                                                                  | 108  |

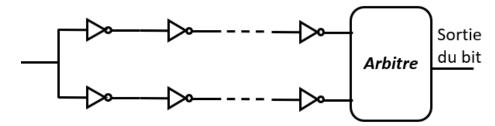

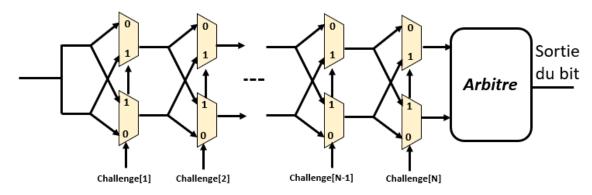

| Figure V-3  | : Principe de base des PUF à base de délai à travers la comparaison de deux ter de propagation de deux chemins identiques                                                        | •    |

| Figure V-4  | : Principe de base de la PUF d'arbitrage                                                                                                                                         | 111  |

| Figure V-5  | : Une PUF d'arbitrage typique avec deux chemins de propagation nominalement identiques suivis par un arbitre pour générer un bit de réponse en fonction du chemin le plus rapide | J    |

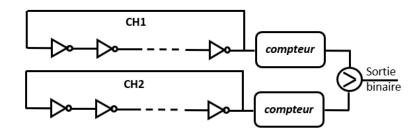

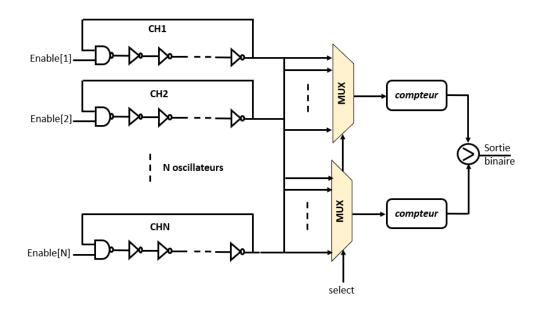

| Figure V-6  | : Principe de base d'une PUF à base d'oscillateur en anneau                                                                                                                      | 112  |

| Figure V-7  | : PUF à base d'oscillateur en anneau présenté dans [133]                                                                                                                         | 113  |

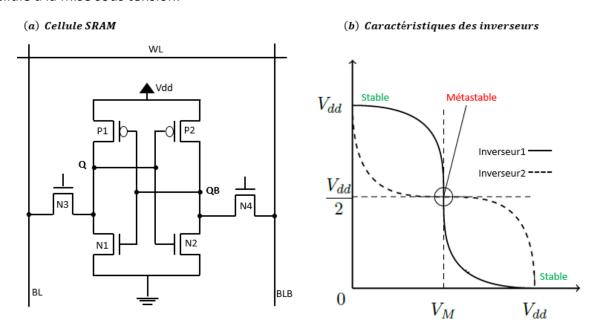

| Figure V-8  | : (a) Cellule SRAM typique à 6 transistors et ses caractéristiques en tension des inverseurs rebouclés                                                                           |      |

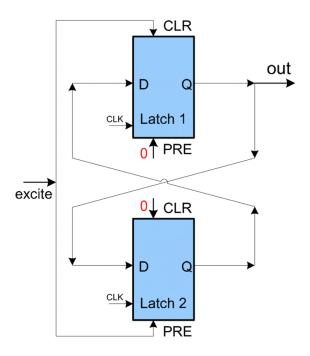

| Figure V-9  | : Butterfly-PUF basé sur le rebouclage de deux verrous [135]                                                                                                                     | 115  |

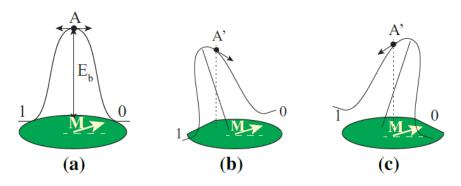

| Figure V-10 | D : Paysage énergétique dans (a) une JTM à géométrie parfaite, (b) et (c) une JT avec des variations dans la geometrie de la couche de stockage                                  |      |

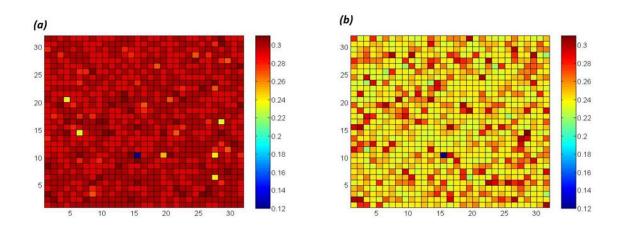

| Figure V-11 | 1 : Lecture d'une matrice 32X32 de JTM TAS (a) après écriture à "1" de toutes le<br>JTM et (b) après écriture de toutes les JTM à "0"                                            |      |

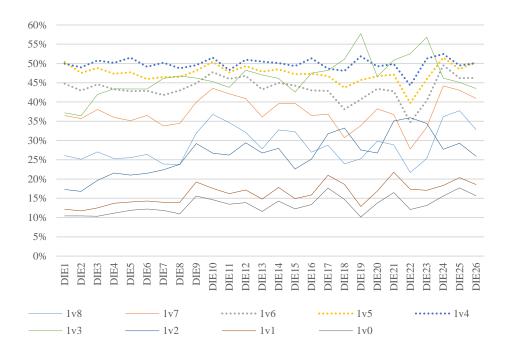

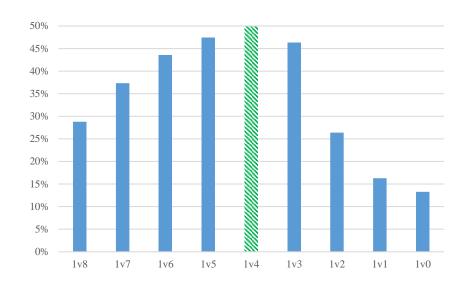

| Figure V-12 | 2 : Variations inter-PUF correspondant à chaque puce pour différentes tensions chauffage                                                                                         |      |

| Figure V-13 | 3 : Variation inter-PUF entre toutes les 26 puces pour différentes tensions de chauffage                                                                                         | 125  |

Liste des tableaux Frederic Ouattara

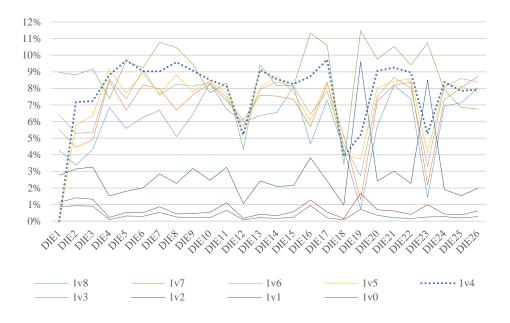

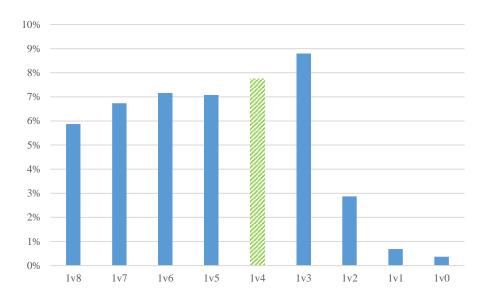

| Figure V-14 : Variation intra-PUF correspondant à chaque puce pour différentes tensions de chauffage                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure V-15 : Variations intra-PUF moyenne entre toutes les puces pour différentes tensions de chauffage                                                                                                                                                   |

| Figure V-16 : Uniformité moyenne entre toutes les matrices pour différentes valeurs de tensions de chauffage126                                                                                                                                            |

| Liste des tableaux                                                                                                                                                                                                                                         |

| Tableau II-1 : Les Technologies MRAM44                                                                                                                                                                                                                     |

| Tableau III-1 : Comparaison des TRNG à base de jonctions magnétiques dans la littérature .70                                                                                                                                                               |

| Tableau III-2 : Paramètres électriques de la jonction STT utilisé dans le projet GREAT72                                                                                                                                                                   |

| Tableau III-3 : Valeurs des paramètres électriques de la JTM sous les 3 principaux corners 72                                                                                                                                                              |

| Tableau III-4 : Caractéristiques des différentes cellules de lecture à base de SRAM dans [114]                                                                                                                                                             |

| Tableau IV-1: Résultat des tests de NIST sur les nombres aléatoires générés sans correction (Raw) ainsi qu'après les corrections XOR³, Von Neumann, RTOPT et une combinaison de RTOPT et XOR². Les tests sont validés si P-value ≥ 0,0001 et Prop ≥ 96/100 |

| Tableau V-1 : Comparaison des differents PUF à base de MRAM dans la littérature122                                                                                                                                                                         |

Glossaire Frederic Ouattara

#### Glossaire

AMR Anisotropic Magnetoresistance

**CMOS** Complementary Metal-Oxyde Semiconductor

**DKit** Design Kit

FIMS Field Induced Magnetic Switching

**FSR** Feedback Shift Register

**GMR** Giant Magnetoresistance

JTM Jonction Tunnel Magnétique

**LFSR** Linear Feedback Shift Register

MLU Magnetic Logic Unit

MRAM Magnetic Random Access Memory

MTJ Magnetic tunnel Junction

NIST National Institue of Standards and Technology

**PRNG** Pseudo Random Number Generator

**PUF** Physically Unclonable Function

**PVT** Process Voltage Temperature

**RA** Resistance Area products

**Rb** Random bit

**RTOPT** Real Time Output Probability Tracking

**SAF** Synthetic Antiferromagnet

**SoC** System on Chip

Frederic Ouattara Glossaire

**SOT** Spin Orbit Torque

**SRAM** Static Random Access Memory

**SR-MRAM** Self Referenced MRAM

**STT** Spin Transfert Torque

**TAS** Thermally Assisted Switching

**TMR** Tunneling Magnetoresistance

**TRNG** True Random Number Generator

Introduction Générale Frederic Ouattara

## Chapitre I Introduction Générale

#### 1. Contexte

Le développement rapide des systèmes sur puce (SoC, System on chip) à faible consommation d'énergie, haute densité et haute performance a poussé les mémoires embarquées à leurs limites et a ouvert le champ au développement des technologies de mémoires émergentes. La mémoire magnétique à accès aléatoire (MRAM, magnetic random access memory) est apparue comme un choix prometteur pour les mémoires intégrées en raison de sa latence de lecture/écriture réduite et de sa grande capacité d'intégration CMOS. En effet cette technologie émergente qui a été rapidement commercialisée, intègre plusieurs propriétés, notamment la non-volatilité, une haute densité, une endurance illimitée, une robustesse thermique et une immunité aux radiations, lui permettant de se développer sur diverses plateformes d'application.

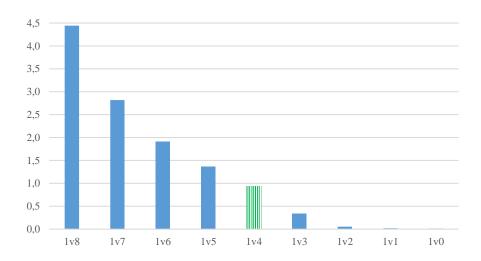

Une projection de l'évolution du marché des MRAM présentée sur la Figure I-1 montre l'intérêt suscité par cette mémoire émergente [1].

Figure I-1: Projection de l'évolution du marché des MRAM [1].

En outre, cette forte croissance du marché des MRAM peut être mise en relation avec l'utilisation croissante des appareils électroniques dans tous les aspects de la vie quotidienne et pour un large éventail d'application augmentant dans le même le temps le besoin de

sécurité de l'information circulant à travers ces appareils. En effet l'industrie électronique ayant toujours été confronté aux problèmes de sécurité, consacre un budget assez conséquent dans la sécurisation de ses produits.

La cryptographie est la technique traditionnelle utilisée pour remédier aux problèmes de sécurité. En fonction du système à sécuriser et de la nature des informations sécrètes, une ou toutes les mesures de sécurité suivantes peuvent être appliquées : l'authentification, l'intégrité, la confidentialité et la non-répudiation. Toutefois leur niveau de sécurité dépend fortement de la clé utilisée dans le cas du cryptage, et de l'identifiant dans le cas d'une authentification et donc de la qualité des primitives de cryptographie utilisées.

Les primitives de cryptographie classiques basées sur des algorithmes ou des fonctions mathématiques sont difficile d'implémentation et le plus souvent sont très onéreux. Comme alternative à ces primitives, de nouvelles primitives de sécurité matérielle sont utilisées aujourd'hui, telles que les générateurs de nombres véritablement aléatoires (*TRNG*, true random number generator) et les fonctions physiques non-clonable (*PUF*, physically unclonable function). Les TRNG et les PUF sont des primitives émergentes utilisées pour la génération des clés secrètes sécurisées et l'authentification ou l'identification des dispositifs à faibles coûts.

Les TRNG sont utilisés pour générer des nombres aléatoires à partir d'un processus physique, plutôt que d'un programme informatique. Ils sont généralement mis en œuvre en tirant parti du bruit thermique ou d'autres phénomènes physiques imprévisibles et sont censés générer des bits aléatoires avec une entropie très élevée et une corrélation nulle. Une conception de TRNG sur puce devrait occuper une petite surface, avoir un débit binaire élevé et avoir une faible consommation d'énergie, tout en assurant des flux binaires non biaisés avec une entropie élevée par bit et une faible, voire aucune, corrélation.

Les PUF exploitent la variabilité intrinsèque de fabrication introduite dans des dispositifs au cours de leur processus de fabrication pour générer une signature, unique à chaque dispositif. Afin de garantir sa sécurité, la signature générée doit être unique d'un dispositif à l'autre (non clonable), et, pour un même dispositif, elle doit être robuste par rapport au vieillissement et aux variations environnementales (reproductible).

En plus de leurs fonctionnalités traditionnelles de stockage d'information, les propriétés internes des MRAM les rendent adaptées pour la mise en œuvre de ces deux primitives de cryptographie. L'utilisation astucieuse de ces propriétés internes des MRAM pourrait contribuer à réduire le coût lié à la sécurisation des dispositifs électroniques.

#### 2. Objectif de la thèse

Les recherches intensives autour des MRAM ces dernières années ont placé cette technologie émergente comme un candidat prometteur des mémoires non volatiles embarquées. Parallèlement à leur fonction principale de stockage d'information, les MRAM sont des dispositifs offrant des possibilités dans plusieurs autres domaines d'applications telles que les capteurs, les récepteurs RF, la sécurité matérielle, etc.

Dans cette thèse, nous nous sommes intéressés principalement à l'utilisation des MRAM dans la conception des primitives de cryptographie de base. Plus concrètement une exploration au niveau de la conception de TRNG basée sur des jonctions de type STT-MRAM a été étudiée puis des expérimentations pratiques sur des MRAM de type TAS dans le but de générer des nombres aléatoires ainsi que des identifiants pour en faire des PUF ont été effectuées.

Ce document est organisé comme suit :

- Le Chapitre II présente un état de l'art sur les MRAM à travers une brève historique des principales découvertes ayant abouti à sa conception. Les différents types de MRAM y sont présentés ainsi que leurs méthodes d'écriture et de lecture.

- Dans le Chapitre III, nous abordons la conception de TRNG à base de STT-MRAM. Nous faisons d'abord un état de l'art des méthodes de génération de nombres aléatoires utilisées dans la littérature puis une proposition de conception est présentée. Elle est basée sur l'extraction d'aléa lors de l'écriture d'une jonction STT à travers un calibrage des impulsions d'écriture.

- Le Chapitre IV aborde également la génération de nombres aléatoires à travers cette fois ci des jonctions de type TAS. Des expérimentations pratiques sont menées dans ce sens sur des circuits de test fabriqués par la société CROCUS Technologie. Les résultats de ces expérimentations y sont présentés.

- Dans le Chapitre V, nous présentons une méthode pour l'extraction de signatures unique de ces circuits de test. Des expériences permettant d'analyser l'efficacité d'une PUF conçue avec ces circuits sont menées. Le comportement de commutation stochastique des jonctions TAS comme source d'aléa est mis en évidence.

- Enfin dans le Chapitre VI, une conclusion générale est donnée avec quelques perspectives.

# Chapitre II Les Mémoires magnétiques à accès aléatoire (MRAM)

Ce chapitre présente les bases de la spintronique en présentant les principales découvertes relatives aux interactions des spins des électrons avec les propriétés magnétiques des matériaux. De plus, un aperçu des applications de la spintronique est donné avec un accent particulier sur les dispositifs mémoires.

#### 1. Introduction

En électronique, la charge électrique de l'électron a longtemps été la seule propriété fondamentale utilisée dans le traitement de l'information. Dans les années 1980, des découvertes sur les phénomènes de transport d'électrons dépendant du spin ont donné naissance à ce qu'on appelle aujourd'hui la spintronique [2]. La spintronique est un nouveau paradigme pour le stockage d'informations et le traitement logique utilisant une autre propriété fondamentale de l'électron : le spin. L'information est portée à travers les spins de l'électron en lieu et place de sa charge électrique. L'information est contenue dans l'orientation magnétique relative des spins (« up » ou « down ») par rapport à une référence (par exemple l'orientation magnétique d'une couche ferromagnétique). La détection de l'orientation magnétique relative des spins se fait en utilisant les propriétés de transport d'électrons à travers ces matériaux semi-conducteurs ferromagnétiques. Comparés aux dispositifs à semi-conducteurs classiques, les dispositifs de la spintronique sont potentiellement plus rapides, plus économes en énergie et plus denses en plus de leur non volatilité [3].

La MRAM est le fruit de recherches menées dans le domaine de la spintronique qui ont déjà abouti à de grandes avancées dans le domaine du stockage d'information. Une des plus importantes avancées est l'invention de la vanne de spin [4] utilisée dans les disques durs et qui a permis d'augmenter la densité et d'accroître significativement la quantité d'information pouvant y être stockée.

La suite du chapitre est organisée comme suit : La section II2 présente les principaux phénomènes liés aux interactions de spin dans les dispositifs à semi-conducteurs. Ensuite, l'élément de base dans la conception des mémoires magnétiques est introduit. La section II.3 passes en revue les technologies MRAM existantes. La section II.4 conclut ce chapitre.

#### 2. La spintronique

Le terme « spintronique » résulte de la contraction de deux mots « spin » et « électronique » faisant référence à l'électronique de spin. Le spin est une propriété quantique intrinsèque associée à une particule, qui est caractéristique de la nature de la particule au même titre que sa masse et sa charge électrique. Par analogie le spin peut être vu comme étant l'équivalent quantique du moment angulaire intrinsèque d'une particule élémentaire en physique classique [5].

Les électrons ont une charge et un spin mais, pendant longtemps, charge et spin ont été utilisés séparément. L'électronique classique ignore le spin et déplace les électrons en agissant seulement sur leur charge tandis que la spintronique ou l'électronique de spin, est une technique qui associe contrôle de courants de spins et de charges dans des nouveaux dispositifs intégrables aux circuits de la microélectronique. Le spin d'un électron peut avoir deux états : spin « up » ou spin « down ». Il est communément décrit comme étant la « rotation » de l'électron sur lui-même : la rotation dans un sens correspond au spin up et dans l'autre sens au spin down.

Dans un matériau, c'est le spin des électrons qui est responsable de ses propriétés magnétiques. Ainsi, dans un matériau conducteur classique tel que le cuivre ou l'aluminium, les moments magnétiques sont désordonnés on dit que c'est un matériau paramagnétique (Figure II-1 a) [6]. Par contre dans un matériau comme le fer ou le nickel, les moments magnétiques sont tous alignés dans la même direction et orientés dans le même sens, ce qui se traduit par une aimantation non nulle à l'échelle macroscopique au sein du matériau. Ce type de matériau est dit ferromagnétique (Figure II-1 b). Enfin dans un matériau antiferromagnétique (Figure II-1 c) tel que le chrome, les moments magnétiques sont parallèles entre eux mais avec des orientations opposées au voisinage. Ce qui se traduit par une aimantation nulle à l'échelle macroscopique.

Figure II-1 : Orientation des moments magnétiques selon le type de matériau [6]

Lorsqu'un courant électrique traverse une couche ferromagnétique, les électrons à travers leurs spins sont filtrés en fonction du sens de l'aimantation du matériau. En effet, les

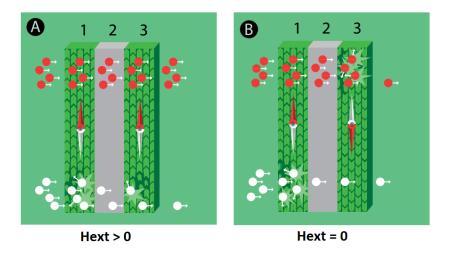

électrons qui ont leurs spins orientés dans la même direction que ceux du matériau, traversent plus facilement la couche ferromagnétique que ceux qui ont leurs spins orientés dans la direction opposée. Ce phénomène a été mis en évidence par William Thomson en 1856 à travers la magnétorésistance anisotrope (AMR, anisotropic magnetoresistance) grâce à des expériences sur le fer et le nickel. La Figure II-2 [7] présente l'effet AMR résultant de l'interaction entre l'aimantation du matériau (flèches vertes sur la figure) et le spin de l'électron. Les électrons dont le spin est dans le sens inverse de l'aimantation (sphères blanches sur la figure) sont plus dispersés que les électrons dont le spin est parallèle à l'aimantation (sphères rouges sur la figure). Dans les matériaux ferromagnétiques, l'AMR affecte la résistance de l'ordre de quelques pourcents. Cependant, à la fin des années 1970, cela suffisait à développer avec succès des capteurs AMR pour remplacer les capteurs inductifs comme tête de lecture dans les disques durs.

Figure II-2 : Effet de la magnétorésistance anisotrope (AMR) [7]

Le concept général de la spintronique est de placer des matériaux ferromagnétiques sur le trajet des électrons et d'utiliser l'influence du spin sur la mobilité des électrons dans ces matériaux. Cette influence, d'abord suggérée par Mott [8] en 1936, a été ensuite démontrée expérimentalement et décrite théoriquement à la fin des années 60 [9] [10].

Le développement de la spintronique a permis la découverte de la magnétorésistance géante (GMR, giant magnetoresistance) en 1988 par deux groupes de chercheurs dirigés respectivement par Albert Fert et Peter Grunberg, de façon indépendante, et qui leur a valu le prix Nobel de physique en 2007 [11] [12]. Le phénomène de la GMR intervient dans des structures qui alternent des couches ferromagnétiques (FM) et des couches non magnétiques (NM).

Le groupe de Albert Fert a étudié la magnétorésistance de trente à soixante structures composées de fer et de chrome (Fe / Cr) empilés et a observé un facteur de presque 2 entre

les résistivités des structures sous champ magnétique externe nul et les résistivités des structures sous champ magnétique externe saturé (Figure II-3).

Figure II-3: Première observation de la GMR sur des multicouches Fe/Cr à 4,2 K [11]

D'autre part, le groupe de P. Grünberg a étudié la magnétorésistance d'une structure composée de Fe / Cr / Fe et a constaté qu'un alignement antiparallèle de l'aimantation des deux couches Fe augmente la résistivité électrique, bien plus que l'effet AMR. La Figure II-4 présente bien ce phénomène. Lorsque le spin des électrons est parallèle à la direction d'aimantation de la couche FM (Fe), les électrons sont faiblement dispersés (traversent facilement les couches FM) et la couche FM présente une faible résistance. D'autre part, lorsque le spin des électrons est antiparallèle à la direction d'aimantation de la couche FM, les électrons ont une forte diffusion et la couche FM présente une grande résistance.

En absence de champ magnétique externe, la structure FM / NM / FM présente un comportement antiferromagnétique c'est-à-dire que les aimantations des deux couches FM s'opposent. Dans une telle structure, les électrons de spin up et les électrons de spin down auront une forte diffusion car ils devront nécessairement traverser une couche avec une aimantation antiparallèle au spin. Alors la résistivité électrique de la structure est grande. Par contre lorsqu'un champ magnétique externe est appliqué de sorte à ce que les deux couches FM soient alignées dans la même direction, les électrons dont le spin est parallèle à l'aimantation des couches FM seront faiblement dispersés. Dans ce cas, la résistivité électrique est faible par rapport à la configuration antiparallèle de la structure.

Figure II-4 : Effet de la magnétorésistance géante (GMR) [7]

Une conséquence de la découverte de la GMR a été l'invention de la vanne de spin. Dans ce cas, le dispositif est constitué de plusieurs couches minces. Le plus simple est 3 couches minces : deux couches ferromagnétiques séparées par une couche non ferromagnétique conductrice. Une des deux couches ferromagnétiques a une aimantation fixe. C'est la couche de référence. L'autre couche ferromagnétique a une aimantation libre, c'est la couche de stockage, on peut donc l'orienter dans les deux directions, parallèle ou antiparallèle à celle de la couche de référence, en appliquant un champ magnétique externe. On change donc l'orientation de la couche de stockage en fonction de la donnée à écrire. Pour lire l'information, il suffit de faire passer un courant à travers l'empilement et déterminer si l'on a une faible ou une forte résistance. Cette invention a permis d'accroître fortement la densité des disques durs actuels et est la principale application industrielle de la spintronique. Ce pendant la différence de résistance que l'on peut obtenir avec un tel dispositif ne dépasse pas 20%. L'augmentation de cette différence de résistance a été possible avec la découverte de la magnétorésistance à effet tunnel (TMR, tunneling magnetoresistance).

#### 2.1. La Magnétorésistance à effet tunnel (TMR)

En 1960, I. Giaever démontre pour la première fois que les électrons sont capables de traverser un isolant pour passer d'une couche conductrice à une autre couche conductrice par effet tunnel [13]. Il reçoit le prix Nobel de la Physique en 1973 pour ces travaux [13] [14] [15]. En 1971, P.M. Tedrow et R. Meservey observent l'effet de conservation de spin à travers un tel tunnel composée d'une couche supraconductrice d'aluminium et une couche ferromagnétique de nickel séparées par un isolant [16]. Et en 1975, l'effet tunnel magnétique (TMR) est démontré par M. Jullière qui étudie la conductance de deux couches

ferromagnétiques séparées par un mince isolant (Fe/Ge/Co) [17]. Il observe que la conductance d'une telle jonction est liée à l'orientation magnétique relative des 2 couches ferromagnétiques (Fe et Co). Cet empilement de couche (« ferromagnétique / isolant / ferromagnétique ») appelé jonction tunnel magnétique (JTM ou *MTJ pour Magnetic Tunnel Junction*) est le composant principale des MRAM.

Contrairement au GMR qui est lié à la diffusion d'électrons, la TMR repose sur la polarisation des spins des électrons. En effet, dans une configuration parallèle des orientations magnétiques des couches ferromagnétiques, les électrons dont les spins sont parallèles à la direction de l'aimantation des couches vont « creuser » facilement un tunnel à travers la barrière isolante, alors que les électrons dont les spins sont antiparallèles à la direction de l'aimantation des couches seront majoritairement filtrés ou réfléchis. Dans une configuration antiparallèle de la structure, les flux d'électrons à la fois de spin up et de spin down seront réduits, ce qui entraı̂ne une grande résistance. La variation de résistance dans les jonctions tunnel magnétiques est exprimée en pourcentage par la TMR selon l'équation (II-1), où Rp est la résistance de la jonction quand l'aimantation des couches ferromagnétiques est parallèle, Rap quand l'aimantation est antiparallèle, P1 et P2 sont les polarisations de spin des deux couches ferromagnétiques :

$$TMR = \frac{\triangle R}{Rp} = \frac{Rap - Rp}{Rp} = \frac{2.P1.P2}{1 - P1.P2}$$

(II – 1)

La valeur de la TMR est étroitement liée au type de matériau ferromagnétique et surtout de l'isolant utilisé. Les premières expériences, faites à température ambiante sur des jonctions à base d'alumine ( $Al_2O_3$ ), ont montré des TMR de l'ordre des dizaines de pourcent (de 11.8% obtenu par J. Moodera en 1995 [18] jusqu'à 70% obtenu en 2004 par D. Wang [19]).

Cependant, l'évolution concernant la TMR viendra avec des jonctions à base de l'oxyde de magnésium (MgO) comme isolant. En 2001, Butler et al. et Mathon et Umersk ont prédit théoriquement qu'une TMR supérieur à 1000% pourrait être obtenu dans des structures de type Fe (001) / MgO (001) / Fe (001). Ainsi, beaucoup de travaux ont été réalisés, notamment au niveau des procédés de fabrication des couches magnétiques et en 2004, des jonctions à base de MgO du type Fe/MgO/Fe, atteignant une TMR de 200% à température ambiante [20] ont été fabriqués. Puis en 2008, des TMR de 600% ont été observées, toujours à température ambiante sur des structures à base de MgO, mais avec des couches magnétiques à base de Fer, Colbalt et Bore (CoFeB/MgO/CoFeB) [21].

Grace aux différentes recherches et découvertes de ces dernières années, le niveau de la TMR n'a cessé d'augmenter, ce qui est une satisfaction du point de vue de la conception microélectronique. En effet, dans le but d'intégrer des composants magnétiques du type

jonctions tunnel magnétiques aux procédés CMOS, toujours de plus en plus à la pointe de la technologie, et toujours de plus en plus performants, il est important d'avoir une TMR la plus élevée possible. Cela permet de coder et décoder facilement et de façon stable un niveau logique « 0 » ou « 1 ».

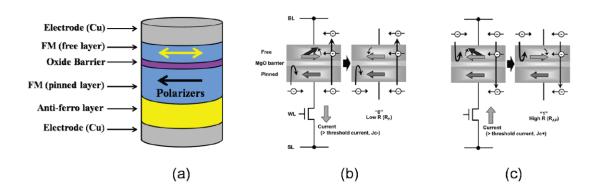

#### 2.2. La Jonction tunnel magnétique (JTM)

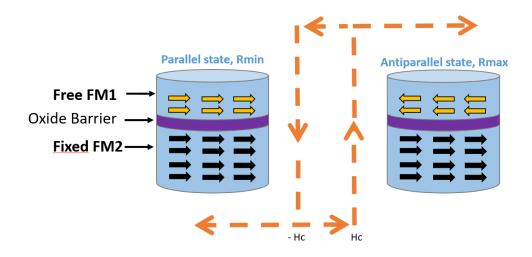

Une JTM est composée de trois couches, deux couches ferromagnétiques séparées par une mince barrière isolante appelée barrière tunnel. La Figure II-5 montre la structure de base d'une telle jonction, soit dans une configuration où les 2 aimantations sont dans le sens parallèle (a), soit dans le cas où les aimantations sont dans le sens antiparallèle (b). Le fonctionnement est similaire à celui de la vanne de spin. Une des couches ferromagnétiques, appelée couche de référence, a une aimantation fixe tandis que l'autre couche, la couche libre ou couche de stockage, peut voir son aimantation orientée dans les deux sens, parallèle ou antiparallèle à celle de la couche de référence, avec un comportement hystérétique. Ainsi, lorsque les aimantations des deux couches sont dans une configuration parallèle, la résistance de la JTM est faible tandis que dans une configuration antiparallèle, la résistance est grande. Le courant passe à travers la jonction par effet tunnel. L'effet physique qui intervient dans le cas de la JTM est la magnétorésistance à effet tunnel (TMR) comme décrit précédemment. Il est nécessaire d'appliquer un champ magnétique suffisamment important pour passer de l'état parallèle à l'état antiparallèle. Ce champ est appelé champ coercitif (Hc) et doit être orienté dans un sens ou dans l'autre en fonction de la donnée à écrire. Lorsque que le champ est en dessous de cette valeur (en valeur absolue), l'état de la jonction reste stable, la donnée est donc bien stockée de façon permanente. En effet, lorsque le champ magnétique extérieur est nul, l'aimantation d'un matériau ferromagnétique s'aligne spontanément parallèlement à une direction. Il existe deux types d'anisotropie : l'anisotropie magnéto-cristalline et l'anisotropie de forme. Dans le cas de l'anisotropie magnéto-cristalline, le moment magnétique a tendance à s'aligner sur un axe, l'axe dit facile, dont la direction dépend de la structure cristalline du matériau. L'anisotropie de forme est due à la forme de la jonction tunnel. A champ nul, l'aimantation du matériau est parallèle à l'axe facile qui est la position dans laquelle l'énergie d'anisotropie est minimale. C'est pourquoi, dans le cas d'une JTM en forme d'ellipse par exemple, le moment magnétique s'aligne dans la direction du plus grand axe et reste dans le plan des couches. Lorsqu'un champ magnétique extérieur est appliqué, l'anisotropie s'oppose au changement d'aimantation car elle tend à l'orienter dans la direction de l'axe facile. L'anisotropie permet donc une bonne stabilité de l'aimantation de la couche de stockage et permet en particulier d'éviter les changements spontanés d'aimantation dus aux fluctuations thermiques. Cependant, il est nécessaire d'appliquer un champ magnétique

extérieur suffisamment élevé pour contrer l'anisotropie, ce qui augmente l'énergie nécessaire pour l'écriture de la JTM. Il y a donc un compromis à trouver entre stabilité de la donnée et énergie d'écriture de la jonction. En pratique, les mémoires non-volatiles ont une stabilité ou une durée de rétention minimale de 10 ans [22].

Figure II-5: Jonction tunnel magnétique [6]

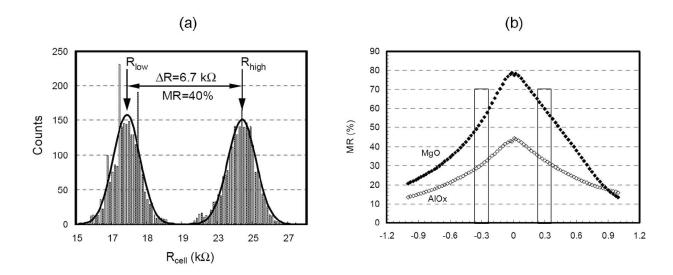

L'opération de lecture de la JTM s'effectue à travers la mesure de la résistance effective de la jonction, qui est fonction de l'état d'aimantation de la couche de stockage. Ceci peut être réalisé en appliquant une tension de polarisation à travers la jonction et en mesurant le courant résultant (approche de détection de courant), ou en envoyant un courant dans la jonction puis en mesurant la tension correspondante (approche de détection de tension). Dans les deux cas, le paramètre détecté est comparé à une valeur de référence pour déterminer l'état de la couche de stockage et ainsi connaître l'information binaire mémorisée dans la JTM (0 pour l'état parallèle et 1 pour l'état antiparallèle). Un amplificateur de détection à base de CMOS (Sense Amplifier) est généralement utilisé pour obtenir cette information. La lecture fiable de la donnée écrite nécessite que les niveaux de résistance parallèle et antiparallèle soient bien définis et surtout suffisamment éloignés. La Figure II-6 (a) montre les dispersions de résistance mesurées avec une tension de polarisation de 350mV sur une assemblé de 8 milles JTM à base de MgO obtenus sur un circuit mémoire présenté dans [23].

Néanmoins, la valeur de résistance de la jonction ne dépend pas uniquement de l'orientation relative des couches ferromagnétiques, mais aussi de la tension de polarisation appliquée aux bornes de la JTM pendant la lecture [23]. Comme le montre la Figure II-6 (b) pour des jonctions utilisant des barrières tunnel en AlOx et en MgO, la TMR est fortement affectée par la tension de lecture, par conséquent, la tension de lecture doit être aussi faible que possible.

Le mécanisme de lecture est suffisamment mature en comparaison au mécanisme d'écriture. Plusieurs générations différentes de JTM ont été élaborées. Toutes se distinguent par leur mécanisme d'écriture ainsi que par l'empilement des couches qui les composent. Ces différents mécanismes d'écriture seront présentés dans les sections suivantes.

Figure II-6 : (a) Distribution des valeurs de résistances min et max d'une mémoire MRAM de 8Kbits (b) Dépendance de la TMR à la tension de lecture pour des JTM à base de MgO et AlOx.

#### 3. Les technologies MRAM

Les MRAM font partie de la catégorie des mémoires ferromagnétiques. L'élément principal des MRAM est la jonction tunnel magnétique (JTM), dont les différentes variantes seront décrites ci-après dans ce manuscrit selon leur mode d'écriture. Les mémoires MRAM sont aujourd'hui considérées comme de très bonnes candidates parmi toutes les mémoires non volatiles émergentes, grâce à leurs caractéristiques et propriétés intéressantes pour une majeure partie des applications du monde actuel : consommation, vitesse, endurance quasi infinie, immunité aux radiations et miniaturisation.

#### 3.1. Mécanisme d'écriture FIMS: Field Induced Magnetic Switching

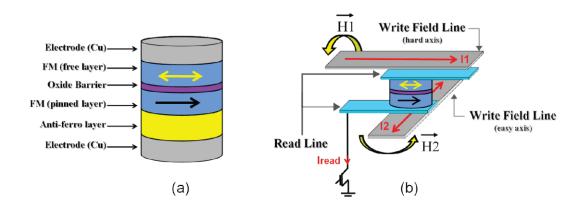

La technologie FIMS (*Field Induced Magnetic Switching*) est la première génération de JTM à être intégrée aux procédés de fabrication CMOS. Pour cette techno, le champ nécessaire au changement de l'aimantation de la couche de stockage est si élevé que le courant nécessaire pour générer ce champ est bien trop grand (plusieurs dizaines de mA). Alors deux lignes de champ magnétique (lignes d'écritures) perpendiculaires sont utilisées pour générer un champ magnétique suffisant au retournement de la couche de stockage. La JTM est située à

l'intersection de ces deux lignes de champ disposées en angle droit au-dessus et en dessous de la cellule comme présenté dans la Figure II-7 (b). Au cours de l'écriture, deux courants électriques sont envoyés dans les lignes de champ, générant un champ magnétique au point de croisement des lignes d'écriture, la composition des deux champs magnétiques génère un champ plus élevé que le champ coercitif de la couche de stockage impliquant le changement de son orientation magnétique.

Deux problèmes se sont posés avec cette méthode. Premièrement, un courant important est nécessaire pour générer un champ magnétique suffisant pour inverser la magnétisation de la couche de stockage. Deuxièmement, cette approche présente un problème de sélectivité dans des matrices de JTM dense. En effet, dans un réseau de mémoire, pour obtenir une densité convenable, la taille des JTM doit être réduite ainsi que les distances qui les séparent. Cependant, la réduction des JTM n'impacte pas son champ de seuil de commutation, par conséquent, la probabilité d'écrire une jonction à moitié sélectionnée augmente très fortement lorsque la densité mémoire augmente, rendant l'approche FIMS difficilement scalable.

Figure II-7: (a) Structure d'une JTM en technologie FIMS (b) Principe d'écriture FIMS

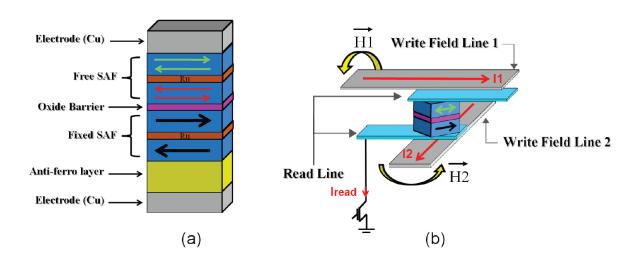

#### 3.2. Mécanisme d'écriture Toggle

La méthode d'écriture toggle a été proposée par Savtchenko [24] dans le but de résoudre le problème de sélectivité observé dans la technologie FIMS. La structure de la cellule mémoire toggle se diffère de celle de la mémoire FIMS par l'empilement plus complexe de couches constituant la JTM, la position de la jonction par rapport aux lignes de champ et la séquence d'écriture. La Figure II-8 (a) présente une cellule de type toggle qui est constituée d'un empilement d'une dizaine de couches ultra minces. En remplaçant la couche de référence et la couche de stockage par des systèmes antiferromagnétiques synthétiques (SAF, Synthetic antiferromagnet), on obtient un empilement dont l'aimantation totale est nulle, ce qui permet

d'augmenter la stabilité du système. L'écriture d'une telle jonction se fait en commutant l'orientation magnétique des deux couches ferromagnétiques constituant le « Free SAF » et la résistance totale de la jonction est déterminée en fonction de l'orientation magnétique de la couche de référence et celle de la couche de stockage au contact de la barrière tunnel (oxide barrier).

Figure II-8 : (a) Structure d'un JTM en technologie Toggle (b) Principe de lecture/écriture Toggle

Les jonctions sont aussi orientées à 45 degrés par rapport aux lignes de champ comme indiqué sur la Figure II-8 (b). La commutation du « Free SAF » constituant la couche de stockage se fait en appliquant une séquence spécifique de champs magnétiques permettant un retournement uniforme de la structure (Figure II-9). Cette technique permet de faire basculer l'orientation magnétique de la couche de stockage dans un sens comme dans l'autre. Avant d'écrire, il faut donc d'abord lire la donnée stockée pour ensuite la comparer à la donnée à écrire. Si les deux valeurs sont différentes, alors on applique la séquence de courant pour faire basculer l'orientation magnétique de la « Free SAF », sinon il n'est pas nécessaire d'appliquer la séquence d'écriture.

Le fait d'appliquer une séquence d'impulsions de courant pour générer un champ permet de s'affranchir des problèmes de sélectivité observés dans la techno FIMS. Cependant, le courant d'écriture reste encore très élevé ce qui rend la miniaturisation de cette technologie difficile en dessous du nœud technologique 90 nm.

Figure II-9 : Séquence d'écriture Toggle

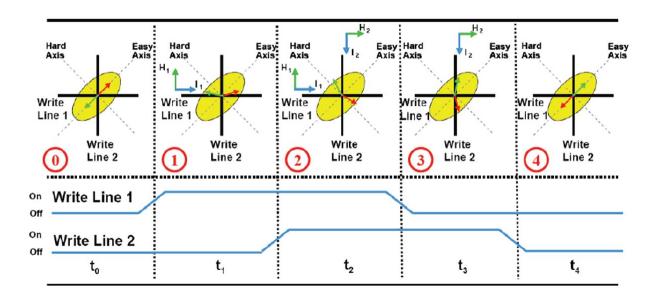

#### 3.3. Mécanisme d'écriture TAS: Thermally Assisted Switching

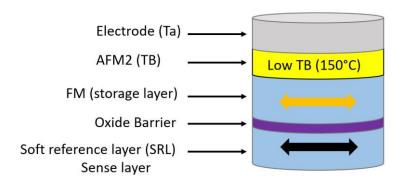

Pour résoudre à la fois le problème de sélectivité et de miniaturisation des JTM, une autre méthode d'écriture a été développée et brevetée par le laboratoire SPINTEC, CEA/CNRS en 2001 appelée TAS (Thermally Assisted Switching). La structure de la jonction est présentée sur la Figure II-10. Deux couches antiferromagnétiques (AFM1 et AFM2) avec des températures de blocage différentes sont ajoutées de part et d'autre de la jonction. Ces couches antiferromagnétiques permettent de maintenir l'aimantation des couches FM de stockage et de référence stable à température ambiante. La couche AFM2 placée au-dessus de la couche de stockage, a une température de blocage faible (environ 150°C). L'orientation magnétique de la couche de stockage peut donc être changée lors de l'écriture en chauffant la JTM à une température supérieure à celle de AF2 (T°>150°C). Afin d'éviter toute commutation de la couche de référence, la couche AFM1 placée en dessous de la couche de référence, a une température de blocage beaucoup plus élevée (autour de 300°C). La direction de l'orientation magnétique de la couche de référence est donc choisie et fixée lors de la fabrication.

La particularité de ce type d'empilement est qu'il est très stable du point de vue de l'aimantation à température ambiante. Afin de pouvoir changer l'aimantation de la couche de stockage il est nécessaire de chauffer la couche antiferromagnétique placée au-dessus de la couche de stockage, au-delà de sa température de blocage. Lorsque la jonction est suffisamment chauffée, les spins de la couche de AFM2 sont complètement désordonnés et un faible champ magnétique suffit pour imposer une aimantation à la couche de stockage, pour laquelle les spins vont être dans une direction dépendante du champ. La température ne

doit pas non plus être excessive pour ne pas risquer de dé-piéger l'aimantation de la couche de référence.

Figure II-10: Structure d'une JTM en technologie TAS

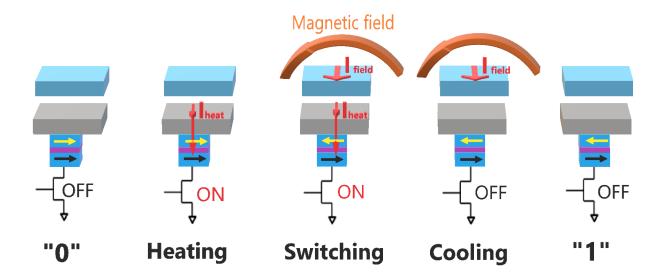

Le principe d'écriture TAS est décrit par la Figure II-11. Tout comme avec la méthode d'écriture toggle, la méthode TAS est séquentielle et se fait en 3 étapes. On part d'un état initial de la JTM en configuration parallèle. La première étape consiste à chauffer la jonction à l'aide d'un courant à travers le transistor en série, c'est la phase dite « Heating ». Lorsque la température de la JTM est supérieure à la température de la couche AFM2, on passe à l'étape 2 en faisant circuler un courant dans la ligne de champs induisant un champ magnétique tout en continuant à chauffer la jonction. La couche de stockage étant dé-piégée, un faible champ magnétique suffit à retourner son aimantation c'est la phase dite « Switching ». Enfin, pour piéger l'aimantation de la couche de stockage dans son nouvel état, on passe à la troisième étape en stoppant le courant de chauffage tout en maintenant le champ magnétique actif à travers le courant de ligne d'écriture. C'est la phase de refroidissement sous champ magnétique dite « Cooling ». Le refroidissement sous champ permet de stabiliser le couplage d'échange entre la couche AFM2 et la couche de stockage. La jonction est alors, à l'état final dans une configuration antiparallèle. Chaque étape a une durée d'une dizaine de nanosecondes pour une durée totale d'une trentaine de nanosecondes pour un cycle d'écriture.

Figure II-11 : Séquence d'écriture d'une JTM TAS : Passage d'un état parallèle à un état antiparallèle

Ce principe d'écriture permet d'économiser de l'énergie par rapport aux deux précédentes méthodes. En effet le courant pour chauffer la cellule dépend fortement de la résistance de la jonction définie par le paramètre RA (Resistance-Area products) et la surface de la JTM, comme le montre l'équation (II-2). Aussi, le paramètre PA ( $mW/um^2$ ) correspondant à la puissance nécessaire pour atteindre la température de blocage peut être réduit en intégrant des barrières thermiques afin de confiner la chaleur. De plus, les lignes de champ d'écriture ainsi que les générateurs de courant nécessaires à la génération de ce champ peuvent être mutualisés entre plusieurs jonctions permettant ainsi d'écrire plusieurs jonctions simultanément dans une configuration matricielle de mémoire TAS-MRAM. Ce qui réduit considérablement l'énergie globale d'écriture de la mémoire. Cette méthode TAS permet également de palier au problème de sélectivité, car en effet il est facile de maitriser les jonctions qui seront chauffées et celles qui ne le seront pas.

$$I_{heat}(mA) = \sqrt{\frac{Pheat}{Rp}} = \sqrt{\frac{PA * S}{\frac{RA}{S}}} = \sqrt{\frac{PA * S^2}{RA}}$$

(II – 2)

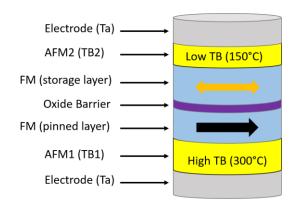

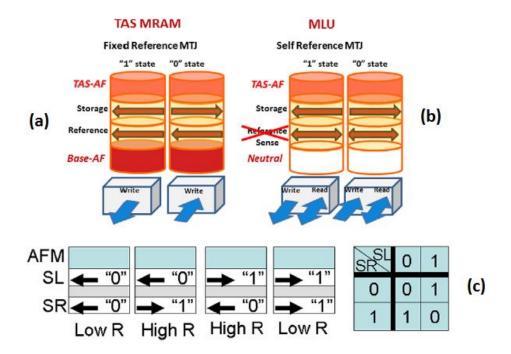

La Société Crocus Technology, issue du laboratoire Spintec en 2004, détient les brevets de la TAS-MRAM et exploite actuellement cette technologie. Son portefeuille de produits s'étend des puces de mémoire aux capteurs magnétiques ainsi qu'aux microcontrôleurs à sécurité renforcée. En 2010, la société crocus a breveté une autre implémentation de la TAS appelée « Self referenced » MRAM (SR-MRAM ) ou Magnetic logic unit (MLU) [25]. La MLU diffère des structures MRAM habituelles en ce qu'elle ne comporte aucune couche de référence dure dont la direction d'aimantation reste fixe pendant le processus de fabrication, mais plutôt une

couche de référence souple à aimantation commutable, appelée couche de détection (SRL). Dérivée de la TAS-MRAM, sa couche de stockage est toujours piégée à température ambiante par une couche antiferromagnétique pour assurer la conservation des données. La Figure II-12 présente la structure simplifiée de la MLU.

Figure II-12: Structure d'une jonction SR ou MLU

La couche de référence SRL n'étant pas soumis à l'effet d'une couche antiferromagnétique de blocage, un faible champ magnétique externe suffit à faire commuter son orientation magnétique. De plus, en absence d'un champ magnétique externe, les interactions magnétostatiques entre les deux couches ferromagnétiques feront que la couche SRL passera spontanément à une configuration antiparallèle par rapport à la couche de stockage. La seule valeur de résistance mesurable sera donc la valeur maximale (Rmax) en l'absence de champs. La MLU ne peut donc pas être lue avec un schéma de mesure de résistance directe comme dans les précédentes JTM.

Bien que le principe d'écriture reste le même pour la TAS que pour le MLU, l'opération de lecture est assez différente. Dans ce cas, la résistance de la jonction est mesurée deux fois pour une lecture. Une première fois avec la magnétisation de la couche SRL commutée dans un sens et une seconde fois avec la magnétisation de la SRL commutée dans le sens opposé. La variation de résistance entre les deux mesures fournit des informations sur la magnétisation de la couche de stockage. Cette nouvelle approche augmente le temps de lecture, mais la tolérance aux variations de procédés de fabrication est nettement améliorée puisque chaque cellule est auto-référencée. De plus, cette approche réduit considérablement les erreurs de lecture observées dans les autres technologies et qui sont principalement liées aux problèmes de chevauchement des résistances Rp et Rap des JTMs quand la densité de la mémoire augmente. Pour une cellule MLU, l'utilisation de la lecture différentielle de résistance n'est pas sensible à ce problème de fabrication. En outre, le matériau antiferromagnétique à haute température de blocage utilisé dans les couches de référence

des TAS-MRAM n'est plus nécessaire dans les cellules SR-MRAM, ce qui entraîne une augmentation importante de la plage de températures de fonctionnement. En effet, dans la TAS-MRAM l'utilisation de deux couches antiferromagnétiques avec des températures de blocage différentes limite la plage de température de programmation (par exemple une cellule avec 150 ° C pour la couche de stockage contre 300 ° C pour la couche de référence, permet des opérations dans une plage inférieure à 130 ° C). Grâce à l'utilisation d'une seule couche antiferromagnétique, l'une de ces limites est supprimée et la plage de programmation peut s'étendre à des températures beaucoup plus élevées car il n'y a plus de risque de dépiéger la couche de référence lors de l'écriture. Des couches antiferromagnétiques avec une température de blocage plus élevée peuvent également être utilisées pour piéger la magnétisation de la couche de stockage pour les applications à haute température.

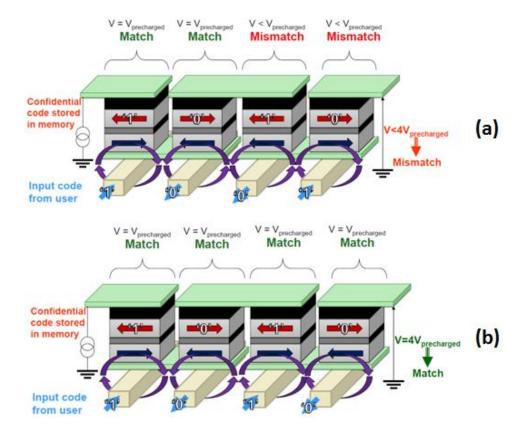

En outre, le fonctionnement de la SR-MRAM conduit également à une autre caractéristique intéressante : la cellule peut également servir de porte logique OU exclusif (XOR). En supposant que les deux couches magnétiques soient les entrées et que la résistance de la JTM soit la sortie, la table de vérité d'une porte logique XOR peut être construite (Figure II-13) [26]. Cela fait de la SR-MRAM un composant particulièrement utile dans des applications de sécurité. Un exemple d'application introduite par la technologie Crocus est le match in place [27], illustré à la Figure II-14. Si la direction actuelle appliquée sur la ligne de champ pendant une opération de lecture est considérée comme une entrée d'information, le dispositif peut utiliser sa capacité logique XOR pour comparer in situ les données stockées en mémoire avec l'entrée (et contrôler s'il existe une concordance ou non, en comparant la résistance de sortie avec une référence). D'autres applications possibles de SR-MRAM sont les suivantes: mémoire à contenu adressable, NOR-MRAM, NANDMRAM [26].

Bien que la structure de la TAS-MRAM lui confère une meilleure évolutivité que celle des technologies précédentes, elle a besoin d'un délai non négligeable pour terminer son opération d'écriture en raison des processus de chauffage / refroidissement. De plus, puisqu'un champ magnétique externe est utilisé pour commuter la JTM, le courant reste élevé, même s'il est inférieur à celui de la technologie Toggle. Un moyen possible de réduire l'énergie d'écriture consiste à combiner la méthode TAS avec l'effet STT (que nous verrons juste après). La TAS-MRAM pourrait être extensible jusqu'à 45 nm [26]. Cependant, l'association de la TAS et la STT a pour objectif d'améliorer encore la miniaturisation de la jonction. Le principal avantage de la TAS-MRAM est sa grande stabilité thermique grâce à sa structure. Cette dernière permet une très bonne conservation des données et une bonne fiabilité contre les perturbations de champ magnétique.

Figure II-13: Unité logique magnétique (a) cellule TAS-MTJ (b) cellule SR-MTJ (c) porte logique virtuel XOR

Figure II-14: Principe du « Match in place » (a) code non valide, (b) code valide

## 3.4. Mécanisme d'écriture STT : Spin Transfert Torque