#### A Time-Based Resource-Sharing Account of Switching Costs between: Processing and Storage in Working Memory

Miriam Debraise

#### ► To cite this version:

Miriam Debraise. A Time-Based Resource-Sharing Account of Switching Costs between: Processing and Storage in Working Memory. Psychology. Université Côte d'Azur, 2021. English. NNT: 2021COAZ2014. tel-03357655

#### HAL Id: tel-03357655 https://theses.hal.science/tel-03357655

Submitted on 28 Sep 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT

Coûts d'alternance entre traitement et maintien d'informations en mémoire de travail : Mise à l'épreuve du modèle de partage temporel des ressources

## **Miriam DEBRAISE**

Laboratoire BCL : Bases, Corpus, Langage - UMR 7320 CNRS

#### Présentée en vue de l'obtention

du grade de docteur en Psychologie Université Côte d'Azur Dirigée par : Fabien Mathy Co-encadrée par : Nicolas Gauvrit Soutenue le : 25 juin 2021

#### Devant le jury, composé de :

Valérie CAMOS, Professeure, Université de Fribourg Nicolas GAUVRIT, MCF-HDR, Université de Lille Fabien MATHY, Professeur, Université Côte d'Azur Sophie PORTRAT, MCF, Université Grenoble Alpes Arnaud SZMALEC, Professeur, Université catholique de Louvain

Evie VERGAUWE, Professeure associée, Université de Genève

## Coûts d'alternance entre traitement et maintien d'informations en mémoire de travail : Mise à l'épreuve du modèle de partage temporel des ressources

Directeurs de thèse: Nicolas Gauvrit, MCF-HDR, Université de Lille Fabien Mathy, Professeur, Université Côte d'Azur

Président du jury: Valérie Camos, Professeure, Université de Fribourg

Rapporteurs: **Sophie Portrat**, MCF, Université Grenoble Alpes **Arnaud Szmalec**, Professeur, Université catholique de Louvain

Examinateur: **Evie Vergauwe**, Professeure associée Université de Genève

## A Time-Based Resource-Sharing Account of Switching Costs between Processing and Storage in Working Memory

PhD Advisors: **Nicolas Gauvrit**, Associate Professor, Université de Lille **Fabien Mathy**, Full Professor, Université Côte d'Azur

President of the jury: Valérie Camos, Full Professor, Université de Fribourg

**Referees:**

**Sophie Portrat**, Associate Professor, Université Grenoble Alpes **Arnaud Szmalec**, Full Professor, Université catholique de Louvain

Examinator: Evie Vergauwe, Associate Professor, University of Geneva

#### Abstract

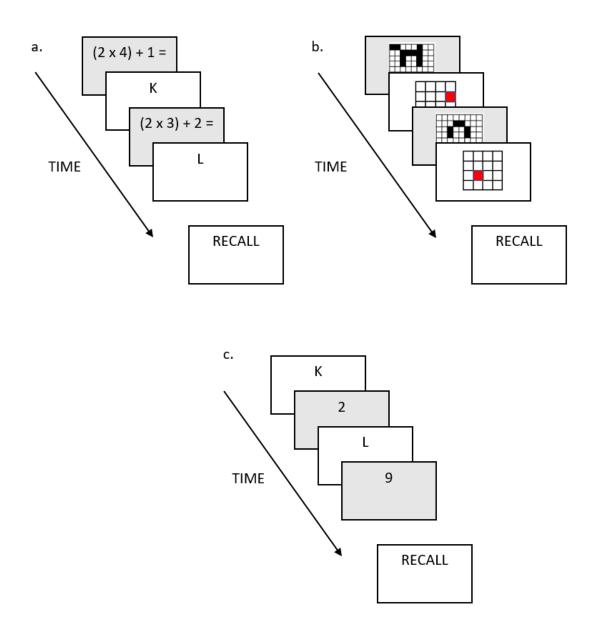

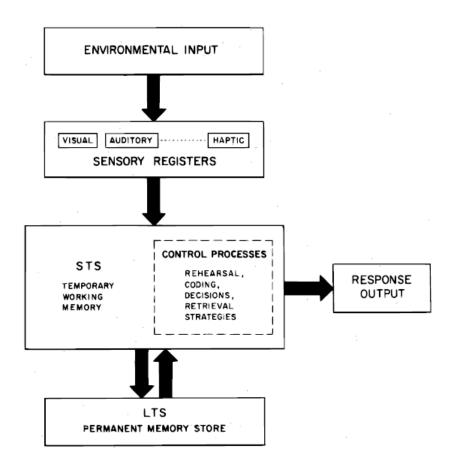

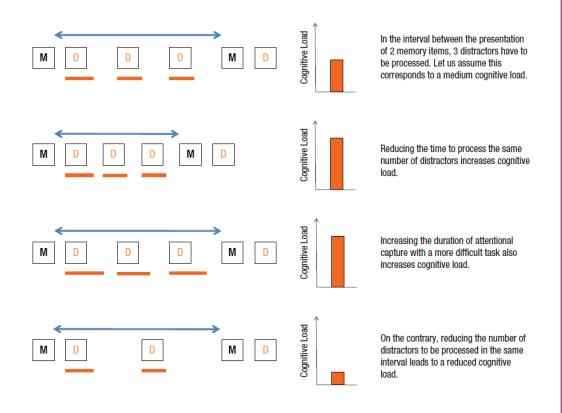

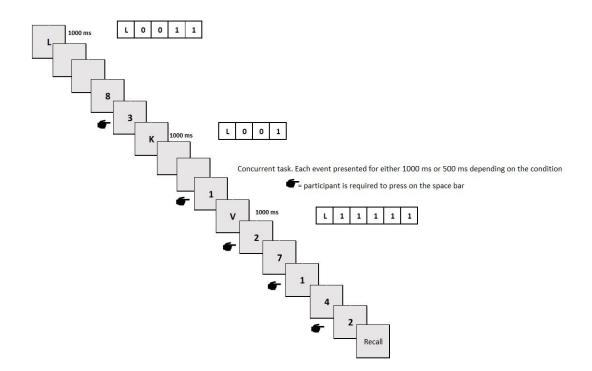

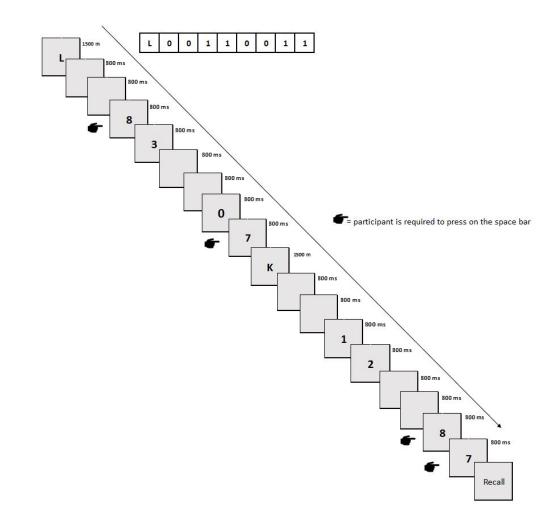

Working memory allows the temporary storage and processing of a limited amount of information. According to the Time-Based Resource-Sharing Model, working memory functions by rapidly switching between storage and processing activities. The complex span tasks generally used to evaluate this process require this rapid alternation. The task involves a primary memory task interspersed with a secondary processing task designed to direct attention away from the memory task.

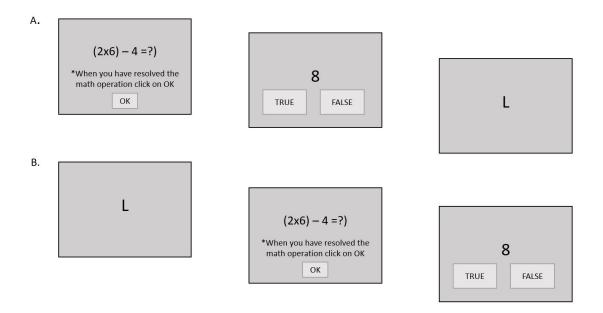

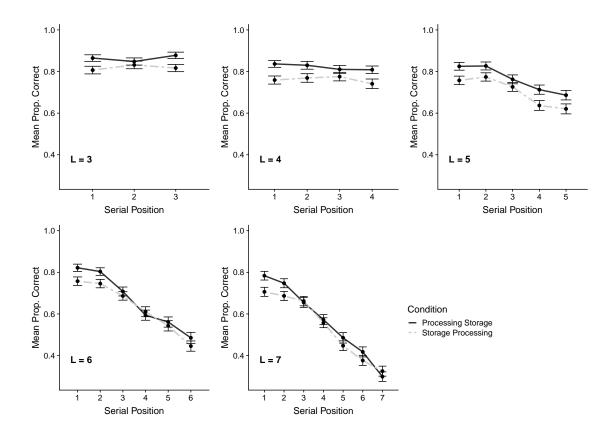

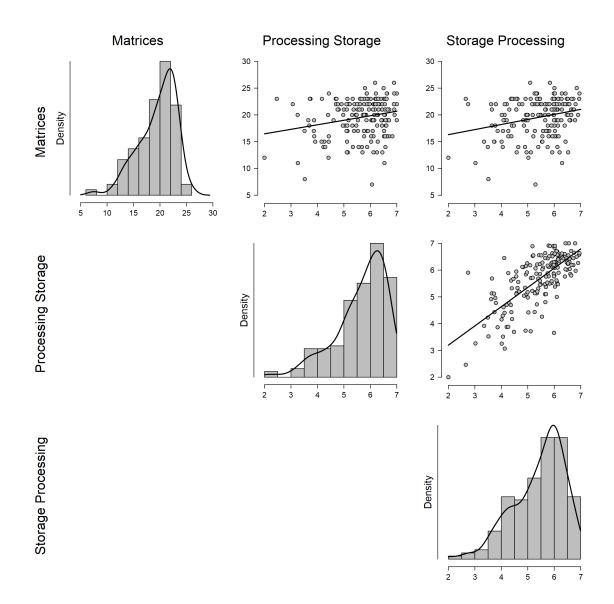

The present dissertation aimed at manipulating the structure of the complex span task to examine untested predictions from the TBRS. I first identified in the literature two types of structures across the available complex span tasks. The unnoticed difference (at least conceptually) between the two types of tasks relies on whether the task begins with a processing episode (that captures attention) or by a storage episode (that requires the encoding of a to-be-recalled item). After providing evidence that this discrepancy does have an influence on the estimate of working memory capacity, I pursue my exploration of more subtle induced variations of task structure on working memory performance.

I argue that how storage and processing activities are distributed within a concurrent task may induce switching costs in working memory performance that have gone unnoticed in past and current experimental studies.

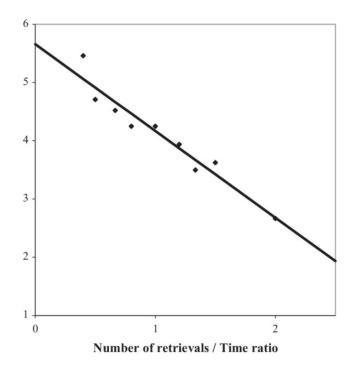

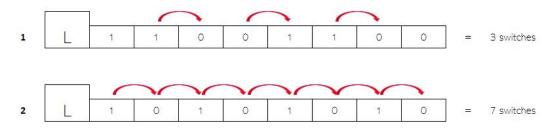

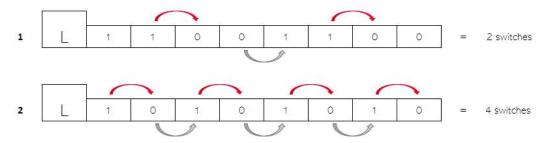

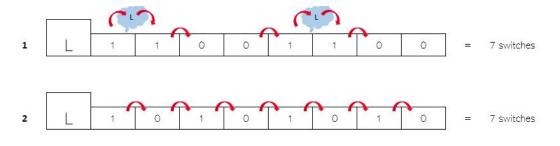

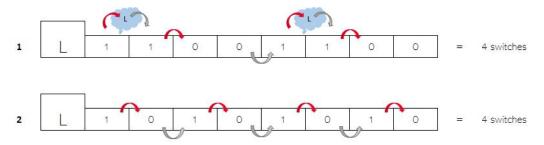

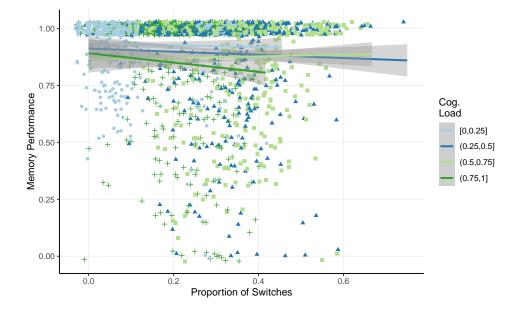

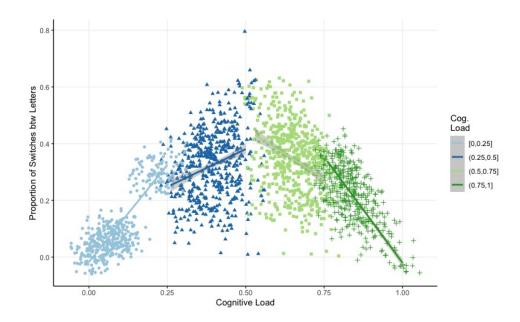

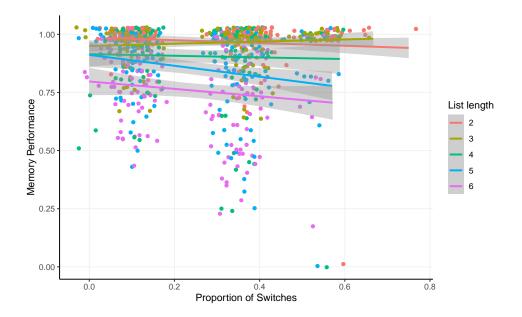

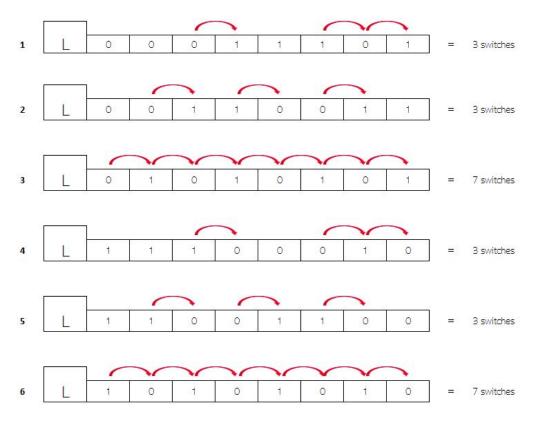

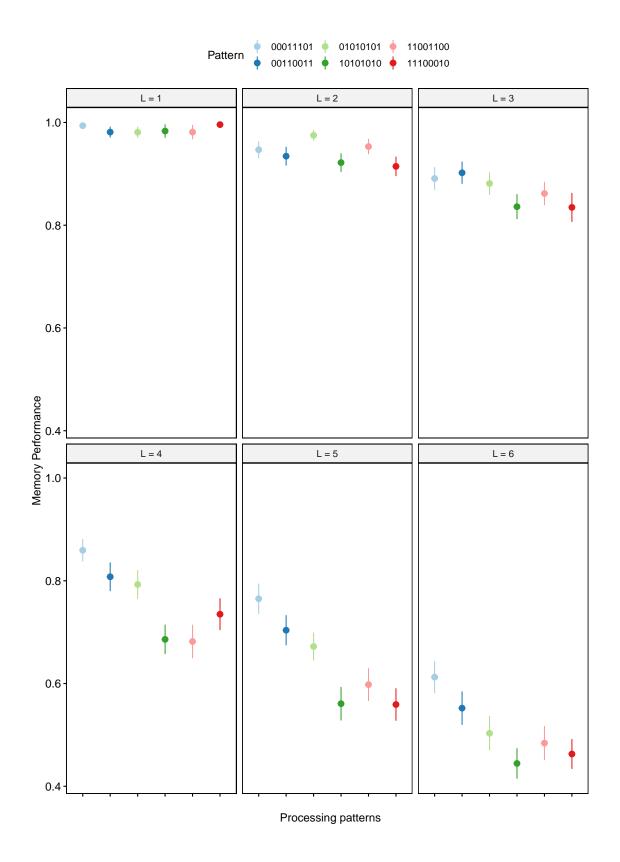

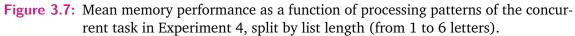

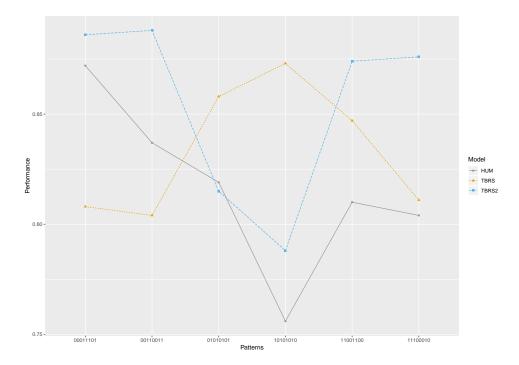

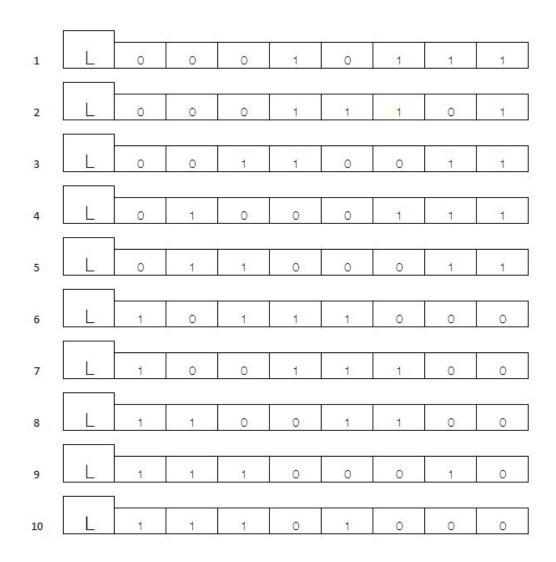

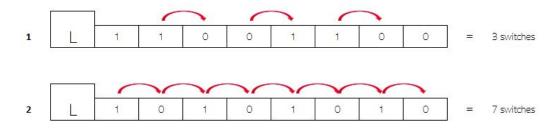

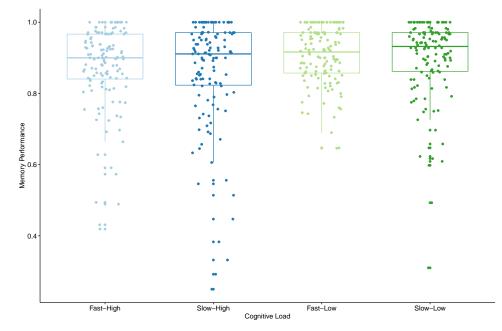

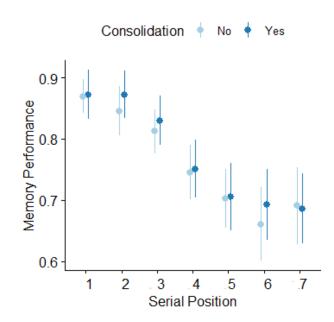

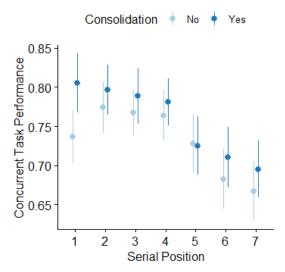

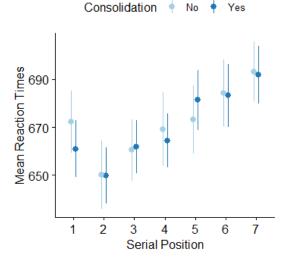

Switching costs are induced by any kind of multitasking situations that complex span tasks should not be exempt of. We tested whether switching costs could be implemented into the TBRS to improve fit to the data. For this purpose, we used complex span tasks that involved elementary processing steps presented at a predefined pace to manipulate switch costs. The number of switches was manipulated by the use of different rhythmic patterns within the concurrent task. The results showed that these patterns can slightly influence working memory performance in some cases but not in others. However, the rhythmic patterns used in our secondary tasks may have introduced a confound variable as some of the patterns containing fewer alternations between storage and processing also introduced longer delays of free time, hence possibly enhancing the consolidation of the memoranda. A last part of the thesis addresses this confound using rhythmic patterns designed to test specifically the switching cost and the consolidation accounts. We conclude that the TBRS in its original form offers a satisfying fit of the data.

Keywords: Working memory, complex span task, switching costs, TBRS model

#### Résumé

La mémoire de travail permet le stockage et le traitement temporaire d'une quantité limitée d'informations. Selon le modèle du partage temporel des ressources (Time-Based Resource-Sharing model - TBRS), la mémoire de travail fonctionne grâce à une alternance rapide entre le stockage et le traitement. Les tâches d'empan complexes généralement utilisées pour évaluer ce double processus utilisent une tâche de mémoire entrecoupée par une tâche secondaire. La tâche secondaire est conçue pour détourner l'attention. L'objectif principal du présent travail était de manipuler la structure de la tâche d'empan complexe afin d'éprouver le modèle TBRS.

Nous avons identifié en premier lieu dans la littérature deux types de structures de tâche d'empan complexe. Cette différence négligée jusqu'alors (du moins conceptuellement) entre ces deux types de tâches repose sur l'ordre des activités de stockage et de traitement. La tâche commence soit par un épisode de traitement (qui capture l'attention) soit par un épisode de stockage (qui nécessite l'encodage d'un élément à rappeler). Après avoir montré que cette divergence de procédure influence les mesures de capacité en mémoire de travail, nous poursuivons notre exploration en construisant des variations plus subtiles de la structure de la tâche concurrente. L'idée est que l'ordre des activités de traitement et de maintien au sein d'une tâche concurrente pourrait induire des coûts de switching en mémoire de travail. Nous faisons l'hypothèse que ces coûts de switching ne devraient pas faire exception dans les tâches d'empan complexe, puisqu'ils sont présents dans d'autres activités nécéssitant d'alterner entre plusieurs tâches. Nous avons donc proposé d'étudier si ces coûts d'alternance pouvaient être implémentés dans le TBRS afin d'améliorer ses prédictions. Dans cet objectif, nous avons utilisé des tâches d'empan complexes impliquant des épisodes de traitements élémentaires présentées à un rythme prédéfini. Le nombre de switching a été manipulé par l'utilisation de différents patrons rythmiques au sein de la tâche concurrente. Les résultats ont montré que ces coûts d'alternance peuvent légèrement influencer les performances en mémoire de travail, mais de façon ni franche ni systématique. Néanmoins, les patrons rythmiques utilisés dans nos tâches secondaires pourraient avoir introduit une variable confondue. En effet, certains patrons rythmiques ont introduit des délais plus longs de temps libres susceptibles d'améliorer la consolidation en mémoire. Une dernière partie de cette thèse aborde cette question afin de dissocier les potentiels effets de consolidation et de switching. Nous concluons que le modèle TBRS permet de rendre compte des données expérimentales de façon satisfaisante.

## Mots clés: Mémoire de travail, tâche d'empan complexe, coûts d'alternance, modèle TBRS

#### Acknowledgement

Avant tout, je tiens à remercier les membres du Jury, Valérie Camos, Sophie Portrat, Arnaud Szmalec et Evie Vergauwe de m'avoir fait l'honneur de participer à l'évaluation de ce travail.

Je remercie très chaleureusement mes directeurs de thèse pour leur soutien et leur confiance. Merci à Fabien Mathy pour ses conseils toujours excellents, sa disponibilité plus qu'impressionnante, son pragmatisme et pour m'avoir guidée de manière si constructive. Merci à Nicolas Gauvrit pour sa disponibilité malgré la distance géographique et les échanges instructifs sur le modèle TBRS2.

Merci à Sophie Portrat et à Benoit Lemaire pour les suggestions, les conseils, les corrections lors de mes premiers posters, ainsi que pour leur insight sur le modèle TBRS\*.

Merci à la direction et à l'ensemble des membres de BCL pour leur accueil chaleureux et la bonne ambiance, mais aussi pour les financements qui m'ont permis de participer aux conférences.

Merci Anja Dordevic, Mélanie Laine et Charlotte Lang qui ont contribué aux passations expérimentales. Merci à Christophe Cauchi pour avoir accepté de partager ses données. J'adresse aussi mes remerciements aux 740 étudiants ayant participé aux expériences.

Suuri kiitos perheelleni ja läheisilleni. Uskoitte että pystyn tähän, silloinkin, kun minä en siihen uskonut. Erityisesti kiitos Äiti et Papa ehtymättomästä tuesta ja rakkaudesta. Merci à ma sœur Nora de toujours tout comprendre ( $\heartsuit$ ).

Merci à mes amis pour leur précieux soutien...Merci aux doctorants et docteurs de la MSHS pour leur multiples conseils et tous les moments de joie partagés...Rakkaille ystävilleni kiitos, olette korvaamaton iso osa elämääni etäisyydestä huolimatta. Kiitos että tuotte pirskahtelevaa ja kuplivaa iloa harmaissakin hetkissä...

Enfin, pour terminer sur le meilleur, merci à Cyril pour son soutien sans faille, pour être tout simplement là et de toujours trouver les mots pour me rassurer dans les moments de doutes ou me faire rire dans les moments désespoirs. Merci aussi pour son aide et sa patience infinie pour les cours de programmation ou de math... ce fût beaucoup de travail (comme pour un album d'Astérix). Cette thèse c'est aussi la tienne.

## Contents

| 1 | Intr | Introduction |                                               |    |

|---|------|--------------|-----------------------------------------------|----|

|   | 1.1  | Measu        | ares of working memory                        | 8  |

|   |      | 1.1.1        | Working memory capacity limits                | 9  |

|   | 1.2  | Mode         | ls of working memory                          | 12 |

|   |      | 1.2.1        | Modal model                                   | 14 |

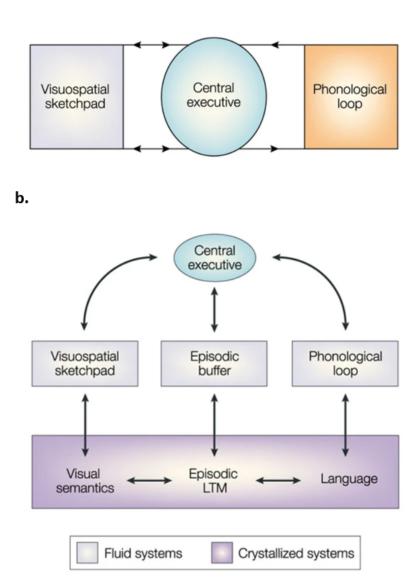

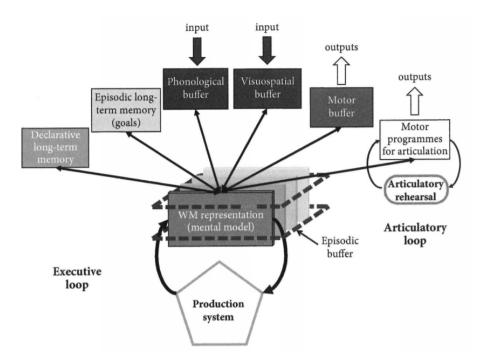

|   |      | 1.2.2        | Multicomponent Model                          | 19 |

|   |      | 1.2.3        | Theoretical context of the TBRS model         | 25 |

|   |      | 1.2.4        | Time-Based Resource-Sharing model             | 30 |

|   | 1.3  | Mode         | ling                                          | 41 |

|   |      | 1.3.1        | TBRS*                                         | 42 |

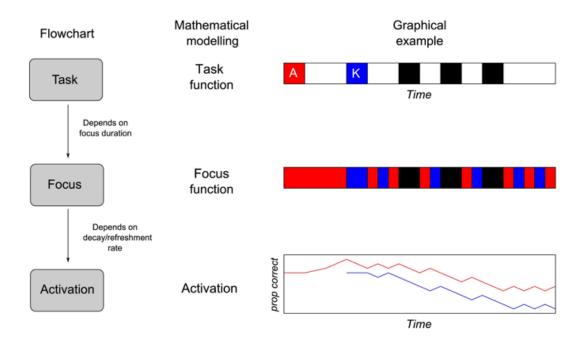

|   |      | 1.3.2        | A mathematical transcription of the TBRS      | 43 |

|   |      | 1.3.3        | Concept underlying the TBRS2                  | 44 |

|   |      | 1.3.4        | Overview of the TBRS2                         | 45 |

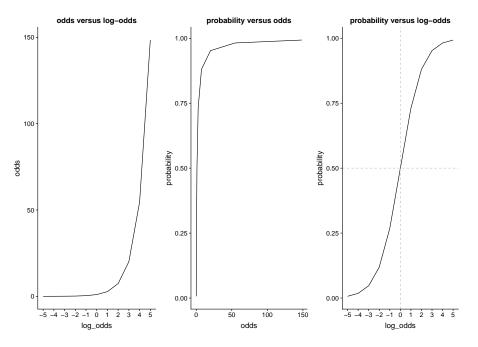

|   |      | 1.3.5        | Probabilities, odds & log-odds                | 47 |

|   |      | 1.3.6        | TBRS2 explained                               | 50 |

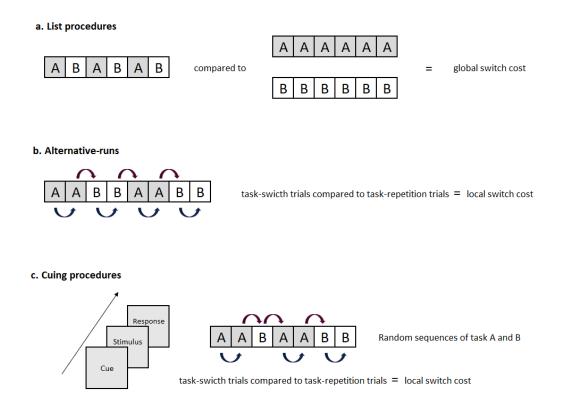

|   | 1.4  | Switch       | hing                                          | 55 |

|   |      | 1.4.1        | Switching paradigms                           | 56 |

|   |      | 1.4.2        | Explaining the switch cost                    | 61 |

|   |      | 1.4.3        | Working memory & switching                    | 64 |

|   | 1.5  | Chapt        | er description                                | 73 |

| 2 | Con  | plex s       | pan tasks & fluid intelligence                | 75 |

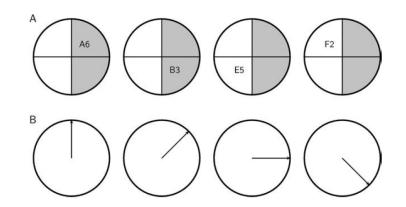

|   | 2.1  | Subtle       | e variations of complex span tasks            | 76 |

|   | 2.2  |              | iment 1                                       | 80 |

|   |      | 2.2.1        | Method                                        | 80 |

|   |      | 2.2.2        | Results                                       | 83 |

|   |      | 2.2.3        | Discussion                                    | 88 |

|   | 2.3  | Conclu       | usion                                         | 90 |

| 3 | Vari | ations       | of processing schedules in complex span tasks | 93 |

| - |      |              | iment 2                                       | 94 |

|   |      | T            |                                               |    |

|   |                                                                                          | 3.1.1                                                                                                                                       | Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|   |                                                                                          | 3.1.2                                                                                                                                       | Statistical analysis method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.1.3                                                                                                                                       | Estimates of statistical fit based on AIC values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.1.4                                                                                                                                       | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.1.5                                                                                                                                       | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | )4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   | 3.2                                                                                      | Experi                                                                                                                                      | ment 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | )5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.2.1                                                                                                                                       | Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | )7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.2.2                                                                                                                                       | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.2.3                                                                                                                                       | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   | 3.3                                                                                      | Experi                                                                                                                                      | ment 4 $\ldots$ $\ldots$ $\ldots$ $11$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.3.1                                                                                                                                       | Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.3.2                                                                                                                                       | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

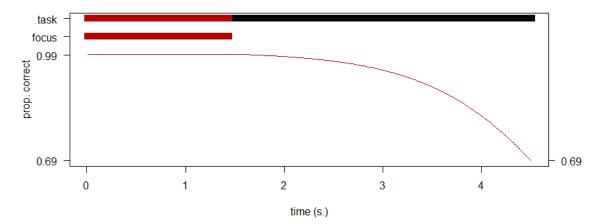

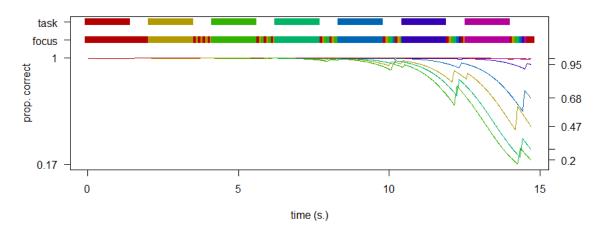

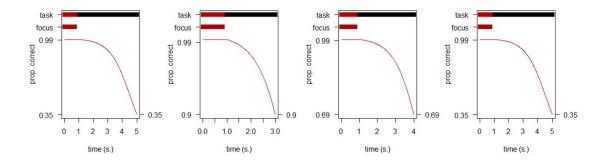

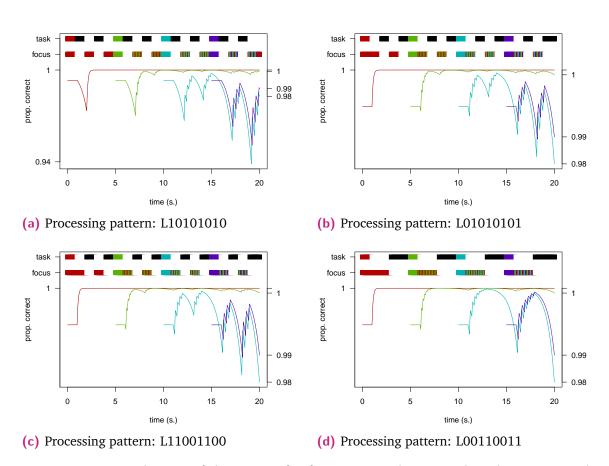

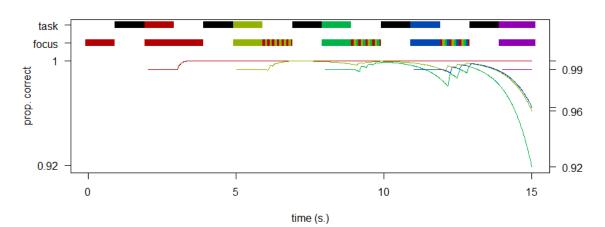

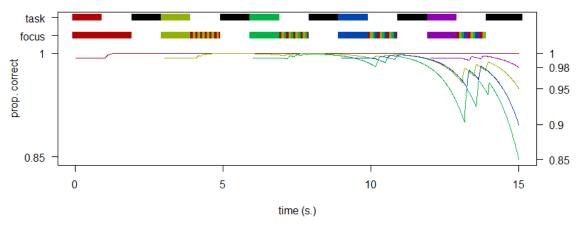

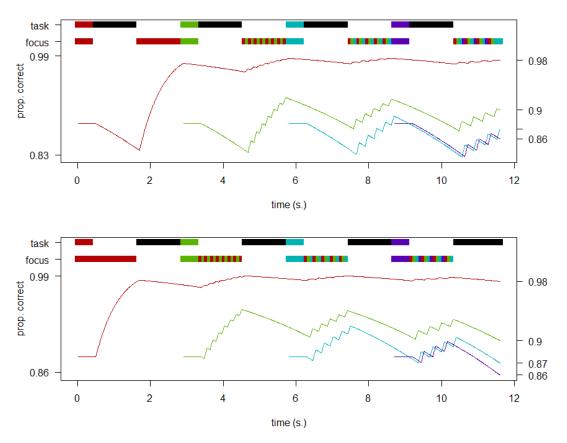

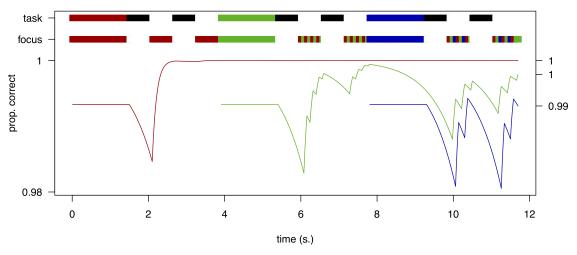

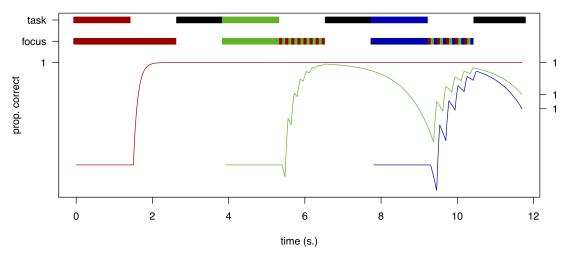

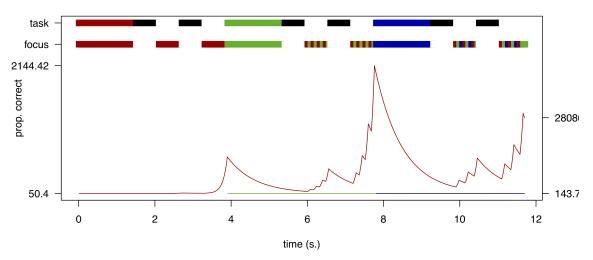

|   |                                                                                          | 3.3.3                                                                                                                                       | Computational simulations of processing patterns 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.3.4                                                                                                                                       | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   | 3.4                                                                                      | Experi                                                                                                                                      | iment 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.4.1                                                                                                                                       | Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   |                                                                                          | 3.4.2                                                                                                                                       | Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   | 3.5                                                                                      | Conclu                                                                                                                                      | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|   | Switching in complex span tasks 1                                                        |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 4 | Swit                                                                                     | t <b>ching</b> i                                                                                                                            | in complex span tasks 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 4 | Swit<br>4.1                                                                              | •                                                                                                                                           | in complex span tasks 14<br>iment 6a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 4 |                                                                                          | Experi                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 4 |                                                                                          | Experi<br>4.1.1                                                                                                                             | ment 6a $\ldots$ $\ldots$ $1^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12<br>12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 4 | 4.1                                                                                      | Experi<br>4.1.1<br>Experi                                                                                                                   | $1^{4}$ $1^{4}$ $1^{4}$ $1^{4}$ Method $1^{4}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12<br>12<br>13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 4 | 4.1                                                                                      | Experi<br>4.1.1<br>Experi<br>4.2.1                                                                                                          | iment 6a       14         Method       14         iment 6b       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12<br>12<br>13<br>13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 4 | 4.1                                                                                      | Experi<br>4.1.1<br>Experi<br>4.2.1<br>4.2.2                                                                                                 | iment 6a       14         Method       14         iment 6b       14         Method       14         Method       14         iment 6b       14         Method       14         Method       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12<br>12<br>13<br>13<br>13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

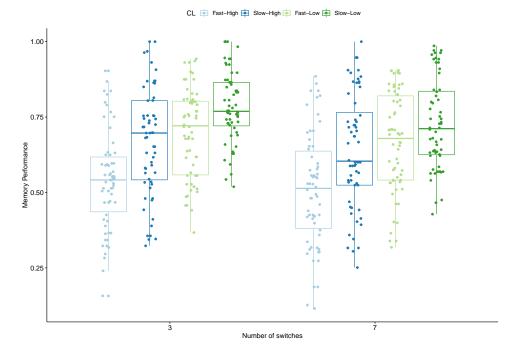

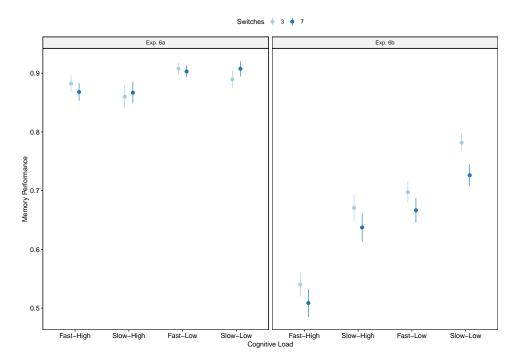

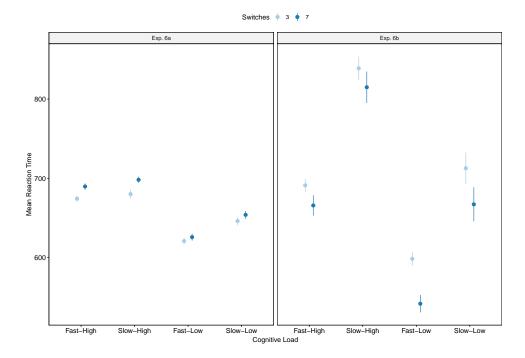

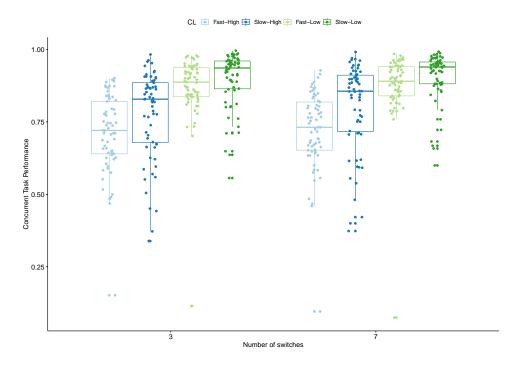

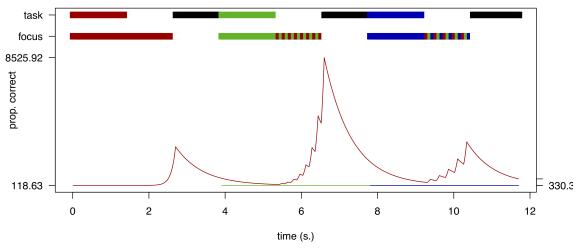

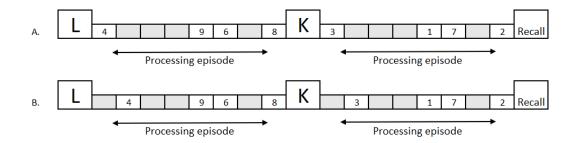

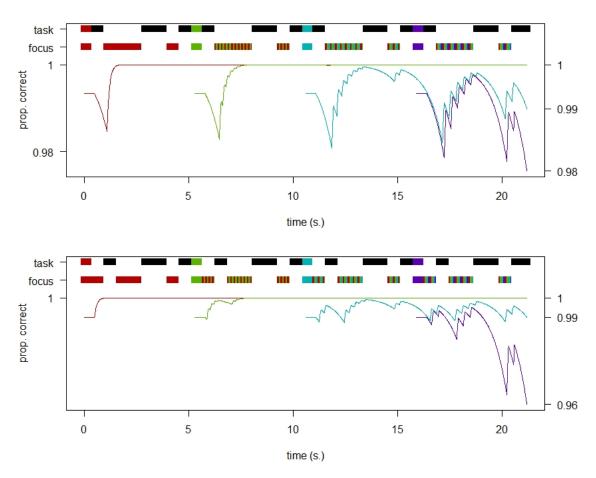

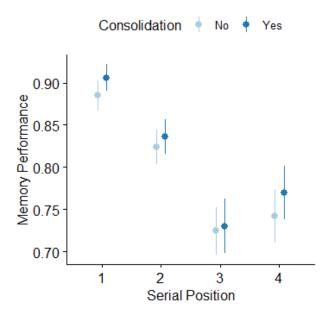

| 4 | 4.1                                                                                      | Experi<br>4.1.1<br>Experi<br>4.2.1<br>4.2.2<br>4.2.3                                                                                        | iment 6a       14         Method       14         iment 6b       14         iment 6b       14         Method       14         Results of Experiments 6a and 6b       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12<br>12<br>13<br>13<br>14<br>51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |