# Memory management for operating systems and runtimes

Alexis Lescouet

#### ▶ To cite this version:

Alexis Lescouet. Memory management for operating systems and runtimes. Distributed, Parallel, and Cluster Computing [cs.DC]. Institut Polytechnique de Paris, 2021. English. NNT: 2021IPPAS008. tel-03358288

### HAL Id: tel-03358288 https://theses.hal.science/tel-03358288

Submitted on 29 Sep 2021

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Memory management for operating systems and runtimes

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à Télécom SudParis

École doctorale n°626 École doctorale de l'Institut Polytechnique de Paris (EDIPP) Spécialité de doctorat : Informatique

Thèse présentée et soutenue à Palaiseau, le 12 Juillet 2021, par

#### **ALEXIS LESCOUET**

#### Composition du Jury :

Amel BOUZEGHOUB

Professeure, Télécom SudParis (SAMOVAR) Président

Laurent RÉVEILLÈRE

Professeur, Université de Bordeaux (Labri) Rapporteur

Michaël HAUSPIE

Maître de Conférence HDR, Université de Lille (CRIStAL)

Rapporteur

Samuel THIBAULT

Maître de Conférence HDR, Université de Bordeaux (Labri) Examinateur

Gaël THOMAS

Professeur, Télécom SudParis (SAMOVAR)

Directeur de thèse

Élisabeth BRUNET

Maître de Conférence, Télécom SudParis (SAMOVAR)

Co-directeur de thèse

### Abstract

During the last decade, the need for computational power has increased due to the emergence and fast evolution of fields such as data analysis or artificial intelligence. This tendency is also reinforced by the growing number of services and end-user devices. Due to physical constraints, the trend for new hardware has shifted from an increase in processor frequency to an increase in the number of cores per machine.

This new paradigm requires software to adapt, making the ability to manage such a parallelism the cornerstone of many parts of the software stack.

Directly concerned by this change, operating systems have evolved to include complex rules each pertaining to different hardware configurations. However, more often than not, resources management units are responsible for one specific resource and make a decision in isolation. Moreover, because of the complexity and fast evolution rate of hardware, operating systems, not designed to use a generic approach have trouble keeping up. Given the advance of virtualization technology, we propose a new approach to resource management in complex topologies using virtualization to add a small software layer dedicated to resources placement in between the hardware and a standard operating system.

Similarly, in user space applications, parallelism is an important lever to attain high performances, which is why high performance computing runtimes, such as MPI, are built to increase parallelism in applications. The recent changes in modern architectures combined with fast networks have made overlapping CPU-bound computation and network communication a key part of parallel applications. While some degree of overlap might be attained manually, this is often a complex and error prone procedure. Our proposal automatically transforms blocking communications into nonblocking ones to increase the overlapping potential. To this end, we use a separate communication thread responsible for handling communications and a memory protection mechanism to track memory accesses in communication buffers. This guarantees both progress for these communications and the largest window during which communication and computation can be processed in parallel.

## Acknowledgements

This document concludes four years of work that would not have been possible without the support of many people.

First and foremost, I would like to thank my advisors, Gaël Thomas and Élisabeth Brunet for their guidance during these years full of unforeseen developments and their unfaltering proofreading during the last months. I would like to extend special thanks to François Trahay, for being my unofficial advisor, and helping me decipher the MPI specification.

I would like to thank Laurent Réveillère and Michaël Hauspie for taking the time to read and evaluate this document as well as being part of my jury. I also thank Amel Bouzeghoub and Samuel Thibault for their participation in my jury.

These four years in the PDS Group, former HP2, would have been very different if not for the great atmosphere cultivated by all professors and students. Thanks to Denis Conan and Amina Guermouch for their counseling and the conversations we had over a cup of tea.

I am grateful to Gauthier Voron, for bearing with me while I discovered virtualization. I would also like to express my gratitude to the PhD students of room B312 and affiliated, which are always available for a coffee or two.

Alexis Colin, our C++ expert, for all the metaprogramming and template conversations. Tuanir Franca-Rezende for sharing with me the ups and downs of the daily PhD student life. Anatole Lefort for convincing me of the benefits of vertical screens. Damien Thenot for sharing Scalevisor with me.

Special thanks to Yohan Pipereau, my reference for kernel issues, and Subashiny Tanigas-salame, for their great musical tastes.

Finally, I would like to thank my friends and family for their unfailing support.

My grand-parents and my sister for always asking me about my work. Thanks to Vivien for its great proofreading. Thanks to Sylvie for finding the right words. Deep thanks to Laure for being there when it mattered the most. And to my mother, thank you for always believing in me.

# Contents

| A                | bstra | $\operatorname{\mathbf{ct}}$                                | iii  |

|------------------|-------|-------------------------------------------------------------|------|

| $\mathbf{A}$     | ckno  | vledgements                                                 | v    |

| $\mathbf{C}_{0}$ | onter | ${f ts}$                                                    | vi   |

| Li               | st of | Figures                                                     | viii |

| $\mathbf{Li}$    | st of | Tables                                                      | x    |

| 1                | Intr  | oduction                                                    | 1    |

| <b>2</b>         | Bac   | kground and motivation                                      | 5    |

|                  | 2.1   | An overview of multicore architectures                      | 6    |

|                  |       | 2.1.1 SMP architectures                                     | 6    |

|                  |       | 2.1.2 Non Uniform Memory Access architectures               | 10   |

|                  | 2.2   | Memory management in the operating system                   | 17   |

|                  |       | 2.2.1 Paging and the page table structure                   | 17   |

|                  |       | 2.2.2 Paging and memory management in user space            | 23   |

|                  | 2.3   | State of the art: resources management and NUMA             | 25   |

|                  |       | 2.3.1 User space solutions                                  | 25   |

|                  |       | 2.3.2 Runtimes and kernel policies                          | 29   |

|                  |       | 2.3.3 Operating system solutions                            | 32   |

|                  | 2.4   | Conclusion                                                  | 34   |

| 3                | Cor   | nmmama, motivation and design                               | 35   |

|                  | 3.1   | Background and motivation                                   | 36   |

|                  |       | 3.1.1 MPI primitives and semantics                          | 37   |

|                  |       | 3.1.2 Overlapping communication with computation            | 39   |

|                  |       | 3.1.3 Commmama: blocking simplicity, nonblocking efficiency | 44   |

| vi |

|----|

|    |

|                  | 0.0          |                                                  | 4.0 |  |  |  |  |  |  |  |

|------------------|--------------|--------------------------------------------------|-----|--|--|--|--|--|--|--|

|                  | 3.2          | Our overlapping infrastructure: Commmama         | 46  |  |  |  |  |  |  |  |

|                  |              | 3.2.1 The interception layer                     | 47  |  |  |  |  |  |  |  |

|                  |              | 3.2.2 The offloading system                      | 48  |  |  |  |  |  |  |  |

|                  |              | 3.2.3 The protection mechanism                   | 49  |  |  |  |  |  |  |  |

|                  | 3.3          | Evaluation of the overlapping potential          | 55  |  |  |  |  |  |  |  |

|                  |              | 3.3.1 Base overhead analysis                     | 55  |  |  |  |  |  |  |  |

|                  |              | 3.3.2 Overlap evaluation                         | 56  |  |  |  |  |  |  |  |

|                  | 3.4          | Conclusion                                       | 59  |  |  |  |  |  |  |  |

| 4                | A n          | nulticore resource management driver             | 61  |  |  |  |  |  |  |  |

|                  | 4.1          | Background and motivation                        | 63  |  |  |  |  |  |  |  |

|                  |              | 4.1.1 Software techniques                        | 63  |  |  |  |  |  |  |  |

|                  |              | 4.1.2 Hardware techniques                        | 65  |  |  |  |  |  |  |  |

|                  |              | 4.1.3 State of the art: Virtualization           | 71  |  |  |  |  |  |  |  |

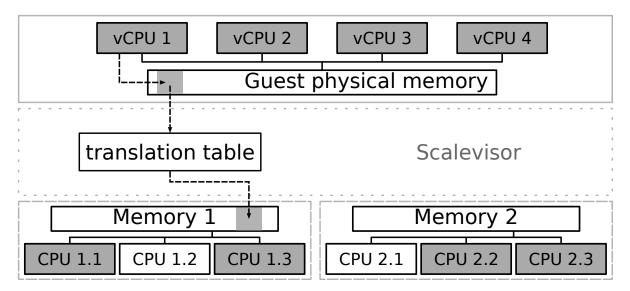

|                  | 4.2          | A driver for NUMA architectures: Scalevisor      | 81  |  |  |  |  |  |  |  |

|                  |              | 4.2.1 Presenting an abstract memory/CPU topology | 81  |  |  |  |  |  |  |  |

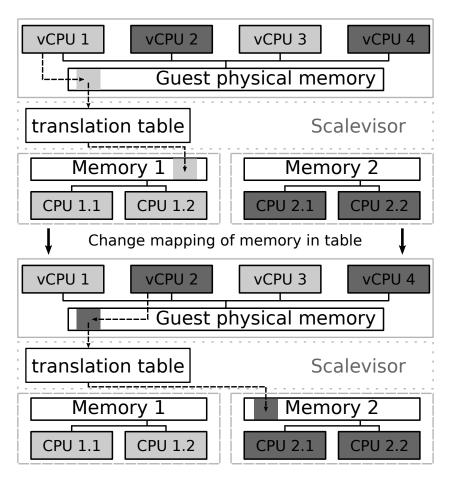

|                  |              | 4.2.2 Managing memory migration                  | 83  |  |  |  |  |  |  |  |

|                  |              | 4.2.3 Managing CPU migration                     | 83  |  |  |  |  |  |  |  |

|                  |              | 4.2.4 Scalevisor internals                       | 85  |  |  |  |  |  |  |  |

|                  |              | 4.2.5 Assessments                                | 90  |  |  |  |  |  |  |  |

| 5                | Con          | aclusion and future work                         | 91  |  |  |  |  |  |  |  |

| $\mathbf{B}^{i}$ | Bibliography |                                                  |     |  |  |  |  |  |  |  |

# List of Figures

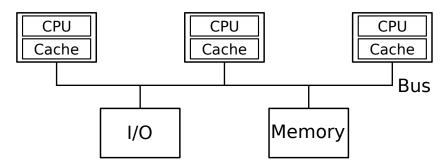

| 2.1  | SMP architecture                                                                    | 6  |

|------|-------------------------------------------------------------------------------------|----|

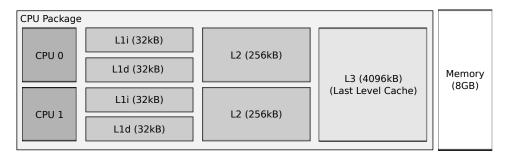

| 2.2  | Example cache hierarchy                                                             | 7  |

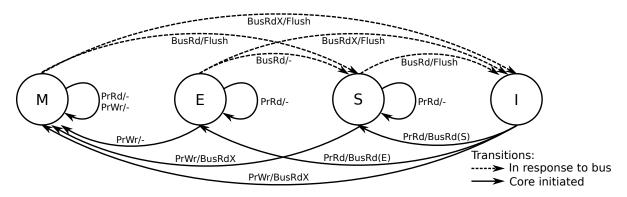

| 2.3  | MESI State diagram                                                                  | 9  |

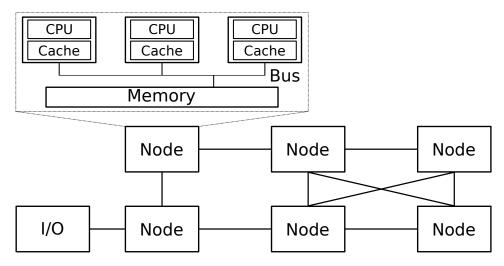

| 2.4  | NUMA architecture                                                                   | 1  |

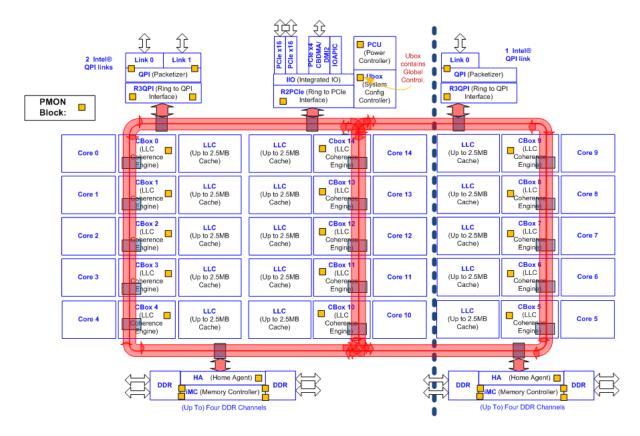

| 2.5  | Intel Xeon E5 ring architecture (Intel documentation [27, chap. 1.1])               | 3  |

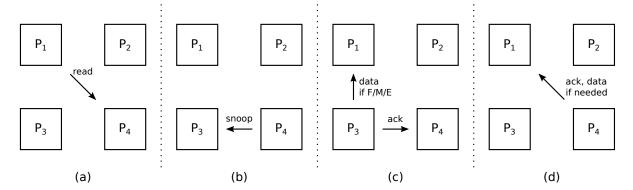

| 2.6  | Intel's directory-based coherency example                                           | 4  |

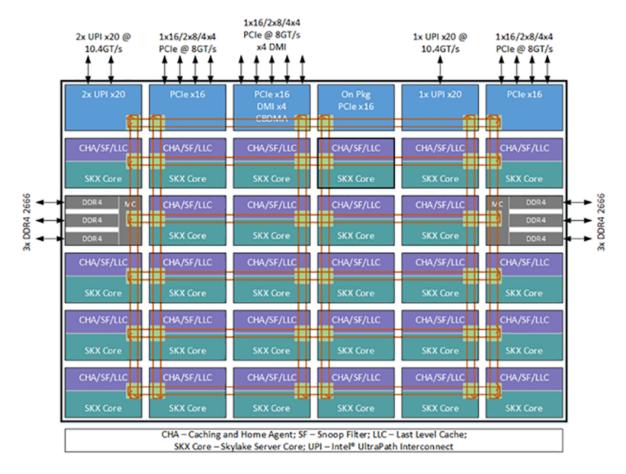

| 2.7  | Intel Xeon Scalable family mesh architecture (Intel documentation [26]) 1           | 5  |

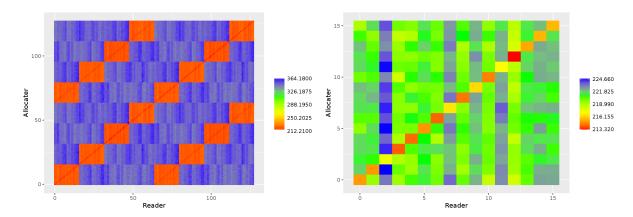

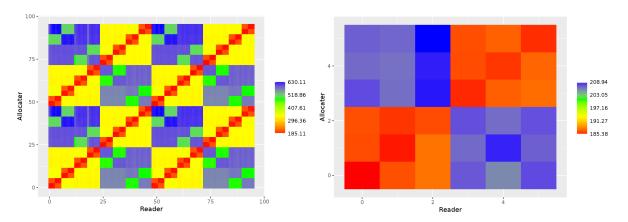

| 2.8  | Latency (CPU cycles), for the Skylake Scalable machine (left) and one die (right) . | 6  |

| 2.9  | Latency (CPU cycles), for the AMD EPYC machine (left) and one die (right) $1$       | 6  |

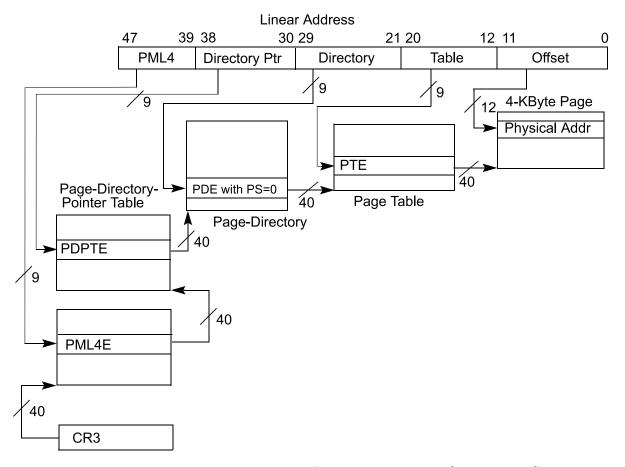

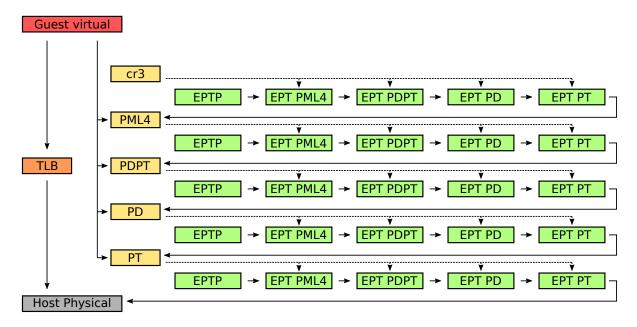

| 2.10 | Translation mechanism (Intel documentation [28, chap. 4.5])                         | 9  |

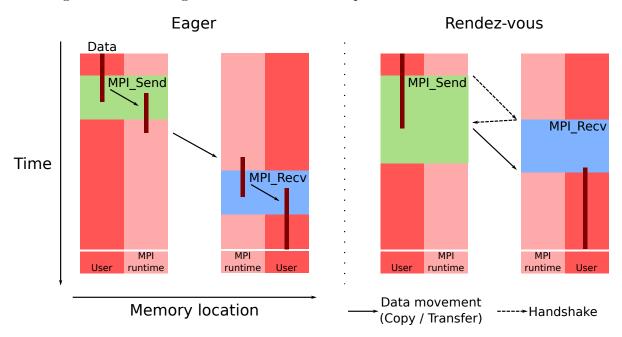

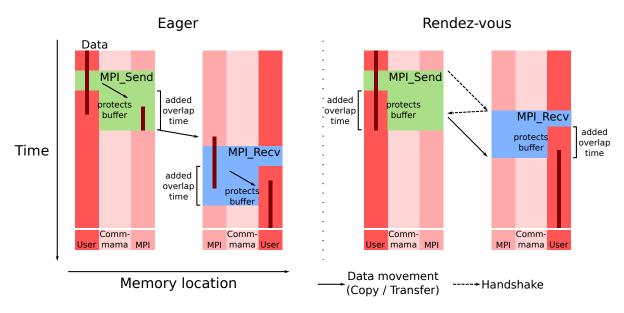

| 3.1  | Comparison of eager and rendez-vous for blocking communications                     | :0 |

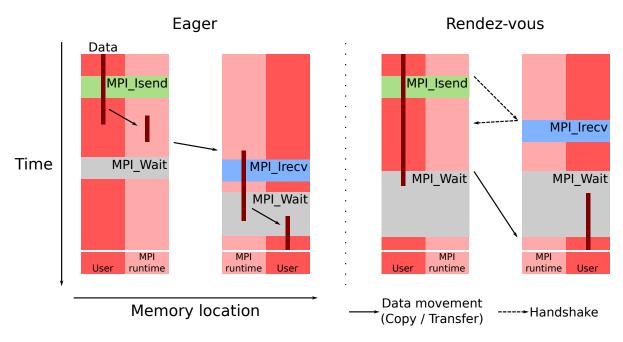

| 3.2  | Comparison of eager and rendez-vous for nonblocking communications 4                | 2  |

| 3.3  | Comparison of eager and rendez-vous with Commmana                                   |    |

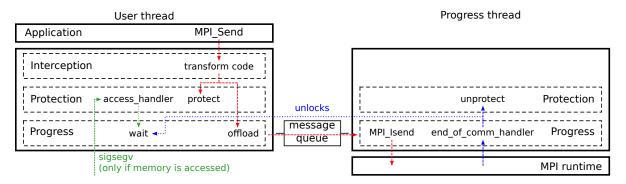

| 3.4  | Commmama's architecture                                                             | 7  |

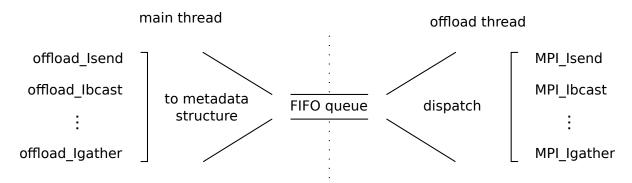

| 3.5  | Queuing procedure, from local thread to offload thread                              | 9  |

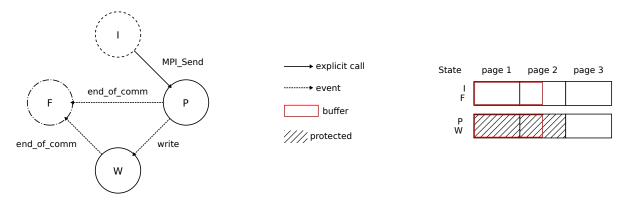

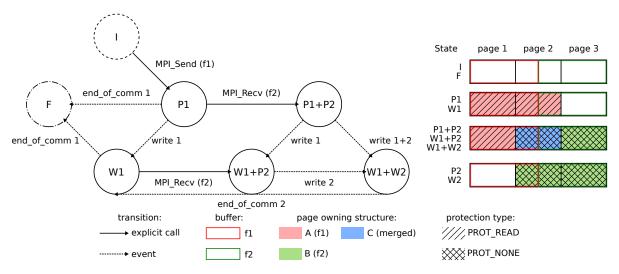

| 3.6  | Evolution of the memory state through a simple send operation                       |    |

| 3.7  | The two types of shared memory between buffers                                      |    |

| 3.8  | Evolution of the memory state during a merge procedure                              | 3  |

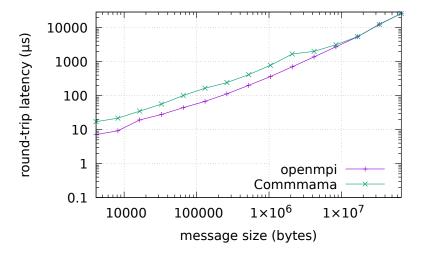

| 3.9  | Round-trip latency with no compute                                                  | 6  |

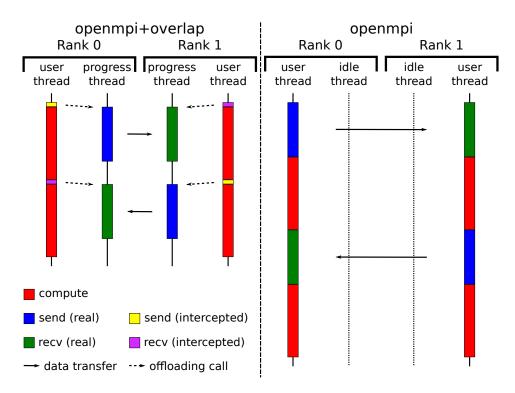

| 3.10 | Expected execution timeline for microbenchmark                                      | 7  |

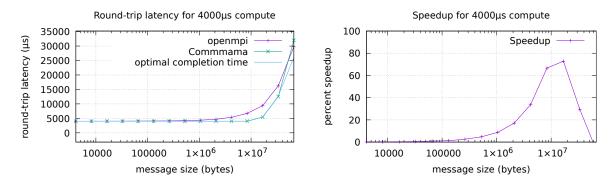

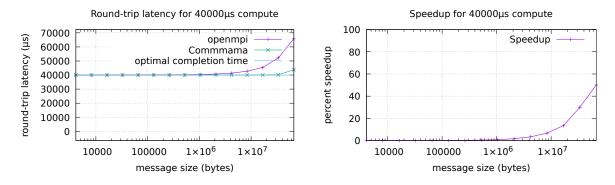

|      | Round-trip latency and speedup for $t_{compute} = 4000 \ \mu s \ \dots \ \dots \ 5$ | 8  |

|      |                                                                                     | 8  |

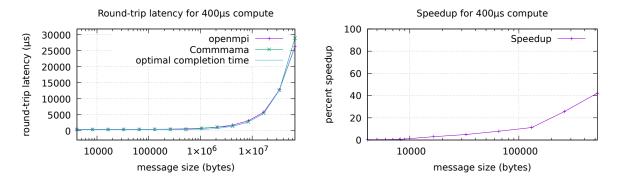

| 3.13 | Round-trip latency and speedup for $t_{compute} = 400 \ \mu s$                      | 9  |

| 4.1  | Software stack including Scalevisor                                                 | 2  |

| 4.2  | Shadow Page table                                                                   | 4  |

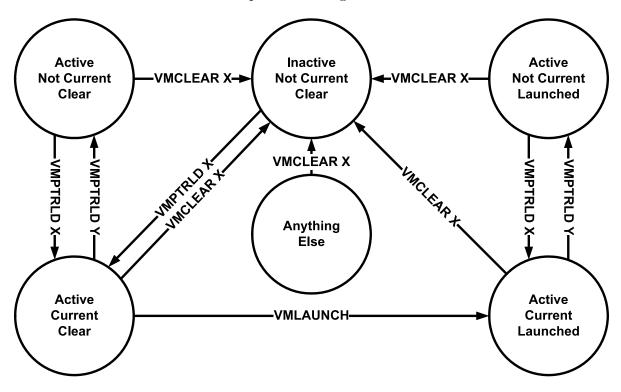

| 4.3  | VMCS state machine (Intel documentation [28, chap. 24.1]) 6                         | 6  |

| 4.4  | Second level translation overhead                                                   | 8  |

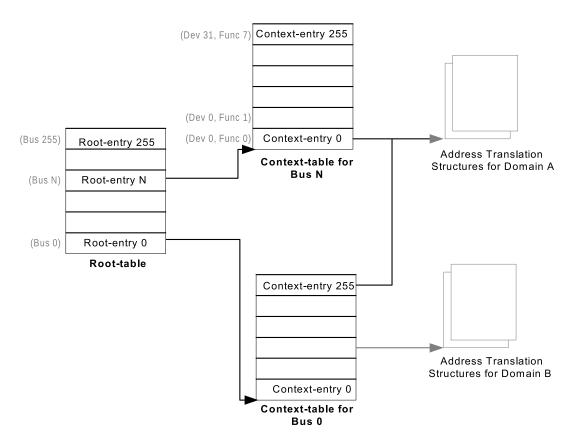

| 4.5  | Intel VT-d tree hierarchy (Intel documentation [29, chap. 3.4.3])                   | 1  |

| LIST | LIST OF FIGURES                                                           |    |  |  |  |  |  |  |  |

|------|---------------------------------------------------------------------------|----|--|--|--|--|--|--|--|

| 4.6  | Abstract topology                                                         | 82 |  |  |  |  |  |  |  |

| 4.7  | Migration using EPT mappings                                              | 84 |  |  |  |  |  |  |  |

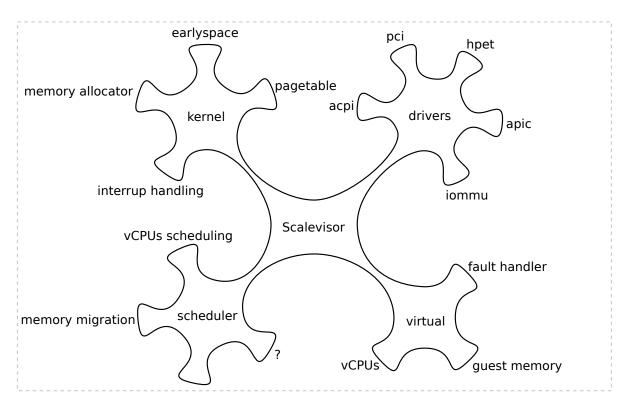

| 4.8  | Software architecture of Scalevisor                                       | 86 |  |  |  |  |  |  |  |

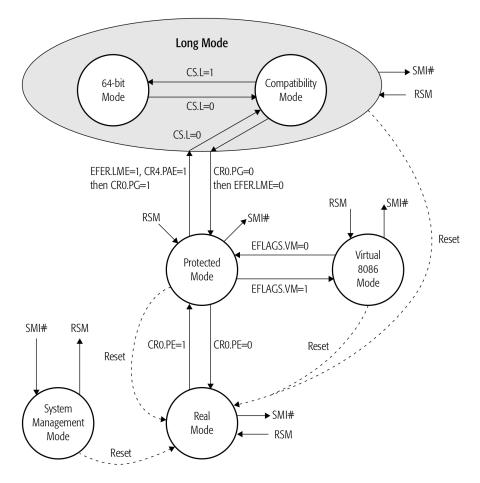

| 4.9  | Operating modes of x86_64 architecture (AMD documentation [1, chap. 1.3]) | 87 |  |  |  |  |  |  |  |

# List of Tables

| 2.1 | Format of a last level page table entry                       | 20 |

|-----|---------------------------------------------------------------|----|

| 2.2 | Correspondence between x86 page table bits and mprotect flags | 24 |

| 2.3 | Related work on NUMA: user space solutions                    | 25 |

| 2.4 | Related work on NUMA: runtime and kernel approaches           | 29 |

| 2.5 | Related work on NUMA: New operating system designs            | 32 |

| 3.1 | Blocking send modes                                           | 38 |

| 4.1 | Related work on virtualization                                | 72 |

| 4.2 | Related work on virtualization and NUMA                       | 76 |

### Chapter 1

### Introduction

Recently, the computation power and network throughput have reached unprecedented heights. While this much needed power helps to develop new fields of research such as data analysis or artificial intelligence, it also requires new techniques to fully exploit its potential.

This growth of computation power and network throughput has only been possible through the use of complex internal hardware structures for the new machines supporting them. First of all, with the increased frequency of the processor clocks, the rate at which instructions are executed has far exceeded the rate at which the memory controller can answer queries. This led to the introduction of smaller but faster memory banks, called caches, to decrease the visible latency of memory requests. Moreover, as all the cores of the machine shared the bandwidth of a unique memory controller, increasing the number of cores led to an overwhelming pressure on the memory controller. As it became impossible to further extend machines featuring a single memory controller, multiple memory controllers, distributed inside the machine, have been added. Because the access time of a given CPU to a given memory location depends on the proximity of the CPU and the memory controller owning this specific location, this architecture is named Non-Uniform Memory Access (NUMA).

This new topology, made of an important pool of processing, memory and network resources, requires to efficiently manage parallelism in order to leverage the full machine potential. In order to increase parallelism and simplify the use of NUMA architecture, this document proposes an approach in two parts.

Commmama The first obstacle to parallelism is to overlap network communication with computation. For this part, we focus on user space level with the MPI (Message Passing Interface) runtime. MPI provides two types of communication primitives, blocking ones, which are simple to use but cannot overlap communication with computation, and nonblocking ones which are more complex to use but have some overlapping capabilities. This forces developers to choose between the simplicity of blocking communications and the efficiency of nonblocking

communications.

In order to avoid trading simplicity for efficiency, we propose *Commmama*, which automatically transforms blocking MPI primitives into nonblocking ones at runtime. Moreover, we show that two main factors contribute to increasing the overlapping ratio. First, background progress which guarantees communications are processed while computation is running. Second, the size of the window during which both communication and computation can be run in parallel. Commmama addresses both these factors.

The second obstacle to parallelism is the contention on shared hardware resources. As explained above, the complexity of multicore machines has greatly increased to answer the need for computational power. As core frequencies rose, the performance gap with the memory controller has increased. This is commonly known as the memory wall. To avoid modern processors being blocked by the memory subsystem, small but fast memory caches have been added on the memory path to mask the latency of the slow main memory. Some of these caches are shared among cores, making them a contented resource. Moreover, as the number of cores per machine increases, so does the pressure on the memory subsystem. To overcome this issue, NUMA architectures feature multiple memory controllers, each managing a part of the machine's memory. While the multiplicity of memory controllers helps dealing with the contention on a given memory controller, it introduces another issue, the congestion on the network linking the different parts of the machine. This congestion is aggravated by the caches synchronization protocol which also uses this same internal network. Finally, each new addition to the already complex machine topology forces the overlying software to take into account the changes. Current operating systems already incorporate different resource management policies trying to deal with the different topologies, including NUMA architectures. However, modifying and maintaining efficient heuristics in code bases with millions of lines of code is a very difficult task.

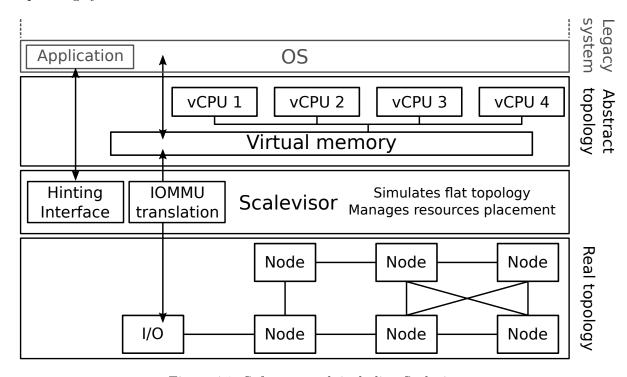

In order to mask the complexity of the hardware while managing memory efficiently, the second part of our approach is a multicore resource management driver that uses virtualization technology, *Scalevisor*. Scalevisor is a small layer placed between the hardware and the operating system, which masks the real topology of the machine and exposes a simpler abstract topology for the overlying operating system. Virtualization technology thus allows Scalevisor to manage resources below the operating system transparently. Moreover, as Scalevisor tends to remain simple, focusing only on resource management, implementing or extending policies should be easier than changing kernel code.

This document is divided in multiple chapters. Chapter 2 describes the challenges of multicore architectures and more specifically of NUMA architectures. Chapter 3 describes the design and implementation of Commmama. Chapter 4 presents the design and implementation of Scalevisor. Chapter 5 concludes this document and presents future work. These chapters are organized as follows.

#### Background and motivation

Chapter 2 addresses the challenges of resources management on multicore machines. First, this chapter describes the internals of multicore machines, and more specifically of NUMA machines, in detail. This entails explaining the hardware mechanisms responsible for the performance issues from which multicore architectures suffer. Because Scalevisor masks the hardware topology to the overlying operating system, these mechanisms need to be understood in order to be correctly dissimulated. Second, we present a commonly used technique to manage memory: paging. This technique is important for both Commmana and Scalevisor as it is used in both cases to manage resources, either with the user space interface in Commmana, or by directly programming the hardware in Scalevisor. We present specifics of the x86 hardware mechanism that impact implementation of both Commmana and Scalevisor. Finally, this chapter describes solutions proposed in related work to solve the challenges of multicore architectures. We show that the main factors leading to non optimal performances are hardware resource contention and the increased latency of memory accesses, due to wrong memory placement.

#### Commana, motivation and design

Chapter 3 presents a specific aspect of resource management: overlapping network communication with CPU-bound communication in the scope of the MPI user space runtime. First, this chapter describes the semantics of MPI communication primitives. The chapter then shows that two key factors influence how well primitives can overlap communication with computation, background progress and the duration during which the overlapping can occur. Studies targeted at improving either of these factors are presented. The chapter then introduces Commmama, which transforms blocking communications into nonblocking ones at runtime to improve the overlapping window while providing efficient background progress. Second, this chapter details the internal design of Commmama, composed of three different layers, the interception layer, offload layer, and protection layer. We present how each of these layers works. Finally, we present an evaluation of Commmama for communication with different message sizes and computation time. This final section shows that Commmama is able to overlap almost all the communication with computation when enough computation time is provided. This leads to a speedup of up to 73% for medium sized messages.

#### A multicore resource management driver

Chapter 4 presents Scalevisor, our approach to resource management using virtualization techniques. First, it presents virtualization techniques, both software and hardware assisted to emulate parts of the machine behavior. This section details the issues related to virtualization in general. It also presents studies related to the impact of virtualization on performances in general and on NUMA architectures in particular. Second, this chapter describes the design

of Scalevisor. The chapter shows how Scalevisor uses virtualization techniques to abstract the machine topology and to mask complex hardware resources, such as CPU caches, but also the distributed nature of NUMA architectures. The section then details the implementation of Scalevisor. The implementation of Scalevisor is incomplete. Scalevisor is able to boot a complete Linux operating system on an Intel machine, but, because of a lack of time, we have not implemented the interface to access hard drives. For this reason, we don't have evaluations that highlight the performance impact of Scalevisor. Instead, the chapter discusses our finding regarding the implementation of a new operating system, and especially reflects on the difficulty to create a new system given the complexity of current hardware without a full-time dedicated team.

#### Conclusion and future work

Chapter 5 concludes this thesis. It sums up the different contributions and teachings about managing resources to increase parallelism on complex topologies for both Commmana at the user space level and Scalevisor, at the hypervisor level. This chapter then discusses future work on both proposals. For Commmana, the main axis of evolution should be decreasing the overhead of the protection mechanism, with a secondary axis being the evaluation of MPI collective primitives and larger applications. For Scalevisor, the first task should be to finish the implementation of necessary parts of the system, and furthermore, developing and studying resource management heuristics.

### Chapter 2

## Background and motivation

As presented in chapter 1, both Commmama and Scalevisor aim to improve resource management. Commmama increases the parallelism of network communication and CPU computation using memory management techniques (paging and memory protection). Scalevisor uses virtualization techniques, among which virtualized paging to manage resources below the operating system, while exposing an abstract topology. In both cases, understanding how memory and paging work is important. In the case of Scalevisor, masking the topology requires an even better understanding of specifics of the hardware and the related issues.

This chapter thus addresses the challenge of managing resources in machines exhibiting complex topologies, known as NUMA architectures: as multicore architectures are composed of an important number of computation units, reaching good parallelism is important to fully exploit a machine potential. However, the distributed topology of NUMA machines induces new performance issues. We show that topology awareness is key in avoiding these issues and favoring scalability.

First, in order to better understand the aforementioned challenges, this chapter presents the architectural details of multicore machines in general and the specificities of NUMA machines in particular. We describe the hardware mechanism and protocols responsible for smooth operation of the architecture and the associated issues.

Then, we explain how operating systems and applications in the user space can leverage this hardware to manage memory through a commonly used data structure, the page table, and associated mechanisms.

Finally, we present solutions proposed in related work to increase efficiency of operating systems and applications on such architectures. We show that the main factors leading to non optimal performances are the contention of hardware resources or the increased latency of access, both due to wrong memory placement.

#### 2.1 An overview of multicore architectures

Previously, Moore's law, which implied a doubling of the number of transistors per processing unit every two years, had the direct consequence of raising the frequency of processors. As evidenced by the number of transistors in recent processors, Moore's law is still valid as of today, but due to physical constraints, such as thermal dissipation, these transistors cannot contribute to the frequency factor as much as they used to. Since the introduction of IBM's POWER4 processor in 2001, the increasing number of transistors serves the different purpose of adding more computing nodes in a single chip, marking the debut of a change in paradigm for computer software, from sequential to parallel programs.

At its core, a computer is composed of three different hardware units, a processing unit or CPU, some memory accessed using a memory controller and some I/O devices accessed through an I/O controller. These three components communicate with one another using the system bus.

This layout was later extended to use multiple CPUs on the system bus to increase the computational power in ways that were unattainable by simply increasing the core frequency. This architecture, composed of multiple CPUs, a memory controller and an I/O controller is commonly known as *Symmetric Multiprocessing* (SMP) and was already in service decades ago in mainframes.

Figure 2.1: SMP architecture

#### 2.1.1 SMP architectures

In SMP architectures, represented in Figure 2.1, the cost of accessing a memory location is the same for all processors as they are all connected through the single bus to the memory controller.

A standard multicore processor is composed of several computation units called *cores*, capable of executing multiple instructions at the same time. These cores are packed into a

single chip package, generally referred to as *CPU* or *processor*, which, when connected to a system bus featuring a memory controller and an I/O controller, acts as an SMP system.

To fully leverage the power of an SMP machine, the different processors must be used in parallel which in turn implies the need for the software run on such an architecture to leverage parallelism. As with many parallel systems, performance limitations lie in shared states and synchronization. For SMP machine, whether built from a multicore CPU or multiple processor, there are multiple hardware parts which are shared or need synchronization.

The first of these shared devices is the memory controller. In an SMP system, all the processing units are running in parallel and interact with the memory controller simultaneously. With the evolution of processor frequency, most modern multicores are now executing instruction at a very fast pace compared to the latency at which the memory controller can respond. This effect, commonly called *memory wall* pushes multicore CPUs to include fast memory, used as a cache, inside the CPU package to mask the latency of the main memory.

In modern CPUs, there are multiple such caches organized as a hierarchy with smaller and faster memory being used first, while bigger, slower caches are used when previous caches did not contain the wanted memory. Current hierarchies of caches generally contain three different levels of caches. The first one on the path to main memory called L1, is composed of two separate caches, one for data fetches called L1d and one for instruction fetches called L1i. These L1 caches are per core and thus replicated for each core of a CPU package. The next cache level, L2 is also private to each core, the Last Level Cache (LLC), L3 is the biggest cache and shared by all the cores of the CPU package. Common sizes for these caches are respectively 32 KB each for L1i and L1d, between 256 KB (laptop) and 1024 KB (high performance server) for the L2 cache. Because it is shared by all the cores, the size of the L3 cache varies more, with approximately 2 MB per core for modern CPUs, leading to 4 MB on a laptop computer and around 20 MB for server class CPUs. Figure 2.2 shows an example hierarchy of caches on a dual-core processor with three cache levels.

Figure 2.2: Example cache hierarchy

The first level of cache is separated into two distinct caches, L1i and L1d, for two reasons. First, separating caches multiplies the throughput allowing instruction fetches and data fetches

to be independent. Second, separating the caches allows to specialize their behaviors. In the case of the instruction cache, it allows to encode the cache content differently than random data.

While these caches may participate in increasing the overall performances by masking most of the latency of instruction and data fetches compared to the main memory, caches private to core must be synchronized in order to present a correct, uniform view of the sequence of load and stores on all cores. Different procedures have been developed to keep processor reads and writes consistent with the states of the different caches and main memory.

Cache coherency protocols for SMP architectures Caches are said to be coherent if all loads and stores of all cores to a given memory location appear to execute in a total order that respects the program order. In order to guarantee the sequential consistency of the memory, two properties must be satisfied.

First, write propagation, if a processor P1 reads from a shared memory location X after a write by another processor P2 to the same memory location X, P1 must read the value written by P2 and not the old value. Second, serialization, if two values A and B are written to location X in this order from two different processors, no processor may read B then A.

To ensure caches are coherent in an SMP system, multiple protocols have been designed, starting with the MSI protocol and its derivatives, such as the MESI and MOESI protocols. In these protocols, the blocks of data, called cache lines, which reside in a cache are tagged with a state. These states represent the state of the memory in regards to both the state of the memory (modified or not) and the state of the same location across the different caches (exclusive or shared). The protocol names are derived from the names of the different possible states of a memory location in the cache, M stands for *Modified*, S for *Shared*, I for *Invalid*, E for *Exclusive* and O for *Owned*.

The original MSI protocol operates as a reader-writer lock (single writer, multiple readers). The *Modified* state represents exclusive ownership as a writer, the *Shared* state represents shared ownership as a reader while *Invalid* means neither reader nor writer. Traditionally with reader-writer locks, acquiring the lock to write means no reader currently holds the lock. For cache coherency protocol, transitioning to the *Modified* state forces all other caches to forgo their *Shared* state and invalidate the location. Alternatively, when a cache requests to load a location, if another cache holds this location in the *Modified* state, meaning the value stored in memory is not up to date, the modified value is first committed to main memory transitioning both caches to the *Shared* state.

While this protocol is theoretically correct, it is not optimal in regard to the number of bus messages. When a cache is the only one to contain the value for a given location and writes to this location, it must broadcast a message on the bus to force other caches to invalidate their entries, which could be avoided in this case. To solve this issue and avoid unneeded messages on the bus, the MESI protocol was introduced by Papamarcos et al. [43]. According to Intel's

Software Developer Manual [28, chap. 11.4], the MESI protocol is still in use in current Intel processors.

The MESI protocol contains an additional state, *Exclusive* which means a value at a given location is valid but not present in any other caches. When a memory location is read by the core and tagged as *Invalid*, the core broadcasts a message on the bus to request the value, if at least one other cache contains the wanted value they both transition to the *Shared* state. This is true for both the MSI and MESI protocols, but in the MESI protocol, if all responses are negative, the requester cache loads the value from memory and transition to the *Exclusive* state. Once in this state, any write to the same location causes a transition to the *Modified* state without the need to issue a message on the bus invalidating this location for other caches.

When using the MESI protocol, in case of a load request directly followed by a write, if the requesting core is the only one using the data it saves one bus message. This is especially important on sequential parts of an application as only one core will access and modify a given location at a time, resulting in improved performances over the MSI protocol.

The MESI protocol can be implemented using two core-side requests and three bus-side requests. Core-side requests, for cache transactions initiated by the core are PrRd to get access to the value of a cache line and PrWr to write a value to a cache line. Bus-side requests are BusRd to get the value of a cache line (emitted after a read miss), BusRdX to get ownership of a cache line for writing or notify of a write (emitted after a write miss), Flush to commit a block to main memory, generally in response to a BusRd or BusRdX request. A complete state transition diagram presenting the interaction of these different messages and the evolution of a cache line state in response is presented in Figure 2.3.

Figure 2.3: MESI State diagram

The issue with MSI and less importantly in MESI is the repeated use of the system bus to convey different cache protocol messages and data.

A standard implementation of a cache coherency protocol such as MESI operates using two types of communications as mentioned previously, local to core (core to cache) and through the bus linking the different cores and the main memory. The two local operations are a request from the core either to read from the cache, or write to the cache. Depending on the state of the cache location targeted by these operation, the core may need to issue messages on the bus to either request the wanted value, or request the value and notify it intends to modify it, or inform other components of a modification of an already cached value. Because of the distributed nature of the caches and the wanted coherency property, all these messages are broadcast on the bus and decrease the available bandwidth for other operations.

Moreover, when a memory location is frequently used by multiple cores, it is still flushed to the main memory store<sup>1</sup> which is shared by all cores.

The SMP architecture, while providing more processing power with parallelism is limited by the strain it incurs on the shared components, the system bus, and both the memory and I/O controllers. This architecture is thus viable for a reasonable number of cores but cannot scale efficiently.

#### 2.1.2 Non Uniform Memory Access architectures

The cache hierarchy of SMP architectures does reduce the amount of requests reaching the memory controller. However, when there is an important number of cores and amount of shared data, the SMP model with its unique shared memory controller does not scale well. In order to reduce the load on the memory controller, a new layout featuring multiple memory controllers distributed in different nodes is used, *Non Uniform Memory Access* (NUMA) architectures. These architectures feature multiple memory controllers distributed among the cores, which alleviates the pressure on a given controller and allows for better memory performances.

As represented in Figure 2.4, this kind of machines is composed of different nodes, each with its own memory region and cores which are connected with an inter-socket network called an *interconnect*. The topology of the communication network varies from one machine to another. Common topologies for NUMA machines comprising four sockets are either ring (all sockets have two peers) or crossbar (complete graph). For machines comprised of eight sockets, there are more variations, commonly, no more than two hops from any given socket are necessary to reach any other socket.

While having completely separate memory controllers, NUMA machines still provide a global address space in which every memory zone in the system is accessible by other hardware with its unique physical address.

Given this new topology, NUMA machines have two different kinds of memory accesses, local ones, when the targeted memory is managed by the controller located on the same node as the CPU and remote ones, when a CPU is accessing another node's memory.

By adding more memory controllers, NUMA machines can make use of more cores without overloading the memory subsystem as SMP would. However, the distributed topology exhibits

<sup>&</sup>lt;sup>1</sup>This can be the LLC when it is inclusive, which is the case for most L3 caches in Intel processors.

Figure 2.4: NUMA architecture

different kinds of performance issues. On one hand, memory accesses through the interconnect are slower than local ones, making locality of memory accesses important, on the other hand, the interconnect has a limited bandwidth which can lead to congestion in the event too many distant accesses would occur.

Moreover, as explained in Section 2.1.1, for performance reasons, modern CPUs have a cache hierarchy used to reduce the number of memory accesses reaching the high latency main memory. This cache hierarchy is also present in NUMA architectures and creates two subtypes of NUMA machines, the ones in which the cache coherency is local to a given node and the ones for which cache coherency is ensured between nodes. The latter are called cache coherent NUMA or ccNUMA.

While non-cache-coherent NUMA machines have some use cases, the lack of a global cache coherence breaks the usual shared memory abstraction, making these suffer from a lack of programmability as described in Yunheung Paek et al. [42]. Thus, most currently used NUMA machines are cache coherent and according to Martin et al. [35] this is not going to change in the foreseeable future for mainstream machines. They argue there still is some design space to make cache coherent hardware scale, but more importantly, forcing software to explicitly manage coherence would simply shift the complexity of cache coherency protocols from hardware to software.

However, while cache-coherency is very important to ease programming of such machines, it comes with its drawbacks as well. Using the MESI cache protocol for NUMA machines would force communications between the cache controllers of different nodes, which was already an expensive solution for SMP machines with a far smaller number of cores. To avoid overloading the interconnect network with cache protocol messages, multiple modifications to the cache

coherency system are made.

Cache coherency for NUMA machines Independently of the protocol used, cache coherency implementations can be realized using messages directly broadcast on the bus as explained earlier but the resulting traffic on the interconnect network would scale proportionally with the number of cores in the system. This approach called bus snooping is thus inappropriate for large NUMA machines which can contain hundreds of cores.

In snoop-based implementations of the cache coherency protocol, the LLC is responsible for broadcasting the relevant messages on the system bus. In directory-based implementations, the so called *directory* maintains the information of the state of cache lines and which nodes, if any, are sharing that line. This system avoids the need to broadcast the coherency protocol messages on the bus, allowing a given requester cache to directly target the right cache through the use of the directory.

The directory system can be implemented using multiple possible methods, for example using a different component, acting as the bookkeeper or with each cache tracking the potential other copies of a given memory address using a range of bits co-located with the state tag in the cache line metadata.

Intel machines use their own form of directory-based protocol for their NUMA servers. Recent hardware from the manufacturer has been using a Network-on-Chip design, in which cores, caches and memory controller are linked via a specific on-chip network. The interconnect network then connects chips. Two iterations of this network have been in use in modern servers, QuickPath Interconnect (QPI) before 2017 and UltraPath Interconnect (UPI) with the introduction of the new Skylake Scalable (Skylake-SP) microarchitecture.

For Intel's platform, the part responsible for handling the interface between private caches (L1 and L2) and the LLC is called the *caching agent*. This caching agent is thus responsible for starting caches transactions, as well as sending and receiving the bus messages generated by these transactions. There is one caching agent per core.

The caching agent communicates with the private cache levels through a basic snoop-based cache coherency protocol which is local to the core. For outgoing communications, all caching agents are linked using a ring topology to the QuickPath Interconnect and communicate using a directory-based approach with a *home agent* as represented in Figure 2.5.

There is one home agent per memory controller, each responsible for its range of memory addresses. When a cache miss occurs in the caching agent of a given core, the caching agent sends a request to the home agent responsible for the wanted memory location. This home agent then uses the information of its directory to send a snoop request only to the caching agents of the cores which may have a cached copy of the wanted memory. One of the agents<sup>2</sup> with a copy of the data sends a copy to the requester caching agent and an acknowledgment to

<sup>&</sup>lt;sup>2</sup>The one with the F (Forward) state from the MESIF protocol explained below.

Figure 2.5: Intel Xeon E5 ring architecture (Intel documentation [27, chap. 1.1])

the home agent. The home agent concludes the transaction. These four steps are illustrated in Figure 2.6.

As the number of message increases with the number of caching agent involved, avoiding to broadcast these messages reduces the consumption of the already limited interconnect bandwidth. This methods thus reduces interconnect bandwidth consumption in exchange for an increased latency of cache coherency transactions.

In addition to the directory information used by the home agent which is an implementation of directory-based cache coherency, Intel's cache agents also use a modified version of the MESI protocol, called MESIF, initially proposed by Goodman et al. [22], [23]. The MESIF protocol introduces an additional specialized form of the *Shared* state, the *Forward* state which is a read-only (cache line has not been modified) state attributed to at most one cache agent for a given cache line. It designates the given cache agent as the primary responder for requests concerning the given cache line. This additional state allows direct cache-to-cache transfers,

Figure 2.6: Intel's directory-based coherency example

thus avoiding either the home agent having to fetch data from the slow main memory or all peers in the *Shared* state responding at the same time. The *Forward* state is given to a cache agent after a read miss, either by the previous *Forward* owner responding to the request or because no cache agent currently has the *Forward* state for given cache line.

However, even with the multiple enhancements brought by the QPI network and cache coherency system, the increase in the number of cores per CPU in the Skylake-SP microarchitecture forced a new on-chip network to be designed as well as a new interconnect network.

The new Skylake Scalable CPU aims to further increase the number of cores per CPU leading to NUMA machines with even higher number of cores. The new UltraPath Interconnect developed for Skylake-SP machines has several improvements over its QuickPath Interconnect predecessor, among these an updated cache coherency protocol, and is integrated more tightly in the new Skylake-SP chips due to different modifications of the socket internal topology.

First, the network topology has been changed from a ring in old Xeon processors to a mesh in new Skylake-SPs reducing the number of hops from a given caching agent to another. This aims to improve the performances by decreasing latency of the cache coherency system. Moreover, the home agent previously located between the on-chip network and the memory controller is now fused with the caching agent at a rate of one per core to further increase scalability. This new architecture is represented in Figure 2.7. Each home agent has a cache for directory lookup used when performing a cache coherence transaction.

The new mesh topology and the distributed Caching-Home Agent (CHA) greatly improve sockets performances for cache coherency transactions and memory loads. However, our experiments show that NUMA effects, while reduced are still present, thus increasing the latency of memory accesses over the interconnect network.

The still existing limitations of NUMA architectures Our experiments are run on a quad socket Skylake Scalable Platform machine with four Xeon Gold 6130 processors.

Figure 2.7: Intel Xeon Scalable family mesh architecture (Intel documentation [26])

These processors are organized as follows. The CPU package (the whole processor container) is composed of one die which is a single continuous piece of silicon. This die features a number of cores, in our case 16 cores in the only die, physical cores expose two logical cores due to Intel's Hyper-threading.

Our experiments consist in measuring the time of a read operation done by a reading core r of a memory location which is allocated by an allocator core a for different couples (r, a). Figure 2.8 shows the results as a heat map, for all core combinations on the left and only one die on the right.

On the left, featuring all the processors, the figure shows a latency around 220 cycles for node local reads and around 350 cycles for non-local reads. This still represents a 59% increase for distant loads.

Figure 2.8: Latency (CPU cycles), for the Skylake Scalable machine (left) and one die (right)

Moreover, while previous explanations about the cache coherency mechanism and architecture of modern Intel servers are not identical to the mechanism used in machines manufactured by AMD, the global theory can be transposed. The same experiments run on a dual socket AMD EPYC server shows similar results as shown on Figure 2.9.

Figure 2.9: Latency (CPU cycles), for the AMD EPYC machine (left) and one die (right)

AMD EPYC processors contain four distinct dies per physical package, each containing multiple cores grouped by *Compute clusters* (two by die). Each compute cluster contains 4 cores and a shared last level cache. Once again, memory accesses inside a die are between 180 and 200 cycles, but due to the hierarchical nature of the AMD machine, we observe NUMA

effects in two different types of accesses. The first NUMA effect is visible between a die local access, at around 200 cycles, and a socket-local access on another die, at around 300 cycles. The second NUMA effect can be seen when accessing memory of another socket, with up to 600 cycles.

These measurements show that the placement of memory even in modern NUMA architectures is very important to avoid degrading the performances of running software. As forcing the software to manage memory placement using only physical memory would be limiting, the hardware supplies a number of facilities to ease the task of memory management as well as different mechanisms to increase efficiency.

#### 2.2 Memory management in the operating system

There are multiple possible techniques that can be used in order to manage memory. Common techniques which are supported by hardware include memory segmentation and paging. Segmentation uses a segment base, and an offset to represent linear addresses, this technique was in use in early x86 processors and still exists in modern processors in compatibility modes such as real mode, protected mode in order to keep some backward compatibility with old software. While segmentation is not available anymore in 64-bit mode for modern x86\_64 processors, its simplicity and efficiency lead to its consideration as an alternative to paging by Taebe et al. [52].

Paging memory is the most common technique existing at the moment in modern computers and has many advantages. This mechanism and its implementation are developed in the next subsection.

#### 2.2.1 Paging and the page table structure

The paging mechanism allows the operating system to use an abstract view of the memory. This is done by using a translation mechanism to resolve memory addresses in executed code, called virtual addresses as physical addresses which are direct identifiers for real memory zones.

The paging mechanism is beneficial in a number of ways as it allows virtual memory addresses to exist independently of the resident storage on which are located the real data.

One of the most important feature of virtual memory is to isolate different memory spaces. This is used to isolate the memory of processes from one another, but also to isolate the memory from the processes and the kernel. The memory of processes is separated by only mapping physical memory of a process in the virtual space of its owner. The kernel memory is separated from the rest using a different mechanism provided by the hardware. Memory pages can be marked available for kernel only or for everyone. This distinction allows to isolate the memory of the kernel from the rest of the system. These two distinct memory spaces are commonly called kernel space and user space (or userland).

Virtual memory is also at the base of the swap system in which some data are offloaded to another storage type, mostly hard drive, to alleviate the strain on RAM. When some memory is accessed rarely, the content of the corresponding pages is written to disk and the physical memory used to store them is made available for other use. When the virtual addresses of such memory are accessed, the access is detected by the operating system which in turns loads the content back from disk transparently.

By the same token, virtual memory can be used to reserve memory without any resident storage, processes can thus allocate more virtual memory than physically available memory in a given machine. This mechanism, called memory overcommitment is commonly used by operating systems and virtualization systems when processes or virtual machine are requesting more memory than they need to maximize the number of such processes or virtual machines on a given hardware unit. In the case where the full amount of requested memory would be required by the processes, the system can use swap to fulfill requests albeit with worse performances.

Additionally to the above system mechanisms, paging is can also be used to share physical memory between processes (shared memory segments), to optimize process creation by duplicating the pages of a parent process on the first write, or to optimize file access with on-demand paging.

The page table structure In modern computers, the translation mechanism is done by specialized hardware, called the Memory Management Unit (MMU) which is now a part of the CPU. The MMU uses an in-memory structure to store the different mappings between physical and virtual address space. This structure is called a page table.

The format of a page table is hardware dependent as it is determined by the MMU which expects a specific layout. Modern x86 CPUs use a multi-level page table (four level in current hardware, five in upcoming Intel processors) which takes the form of an n-ary tree, more precisely a tree of arity 512 for x86 processors. The root of the tree, which is needed as the staring point for traversals, is available to the MMU through a CPU register called cr3 in which the system needs to write the physical address of the page table root.

As presented by Figure 2.10, this tree structure is traversed by splitting a requested virtual address in five part (for a four level paging structure). The first 12 bits represent the offset in the 4 KB page, the four next parts (9 bits each) represent an offset in the levels of the page table tree structure. The Page Map Level 4 (PML4) entry at the offset given by the bit 39-47 of the virtual address contains the address to a Page Directory Pointer Table (PDPT). The pointer at the offset given by bits 30-38 of the virtual address gives access to the Page Directory (PD) and the rest of the bits to the Page Table (PT) level and finally the index inside the PT level which contains the physical address of the four kilobyte page corresponding to the given virtual address. The offset in the page is obtained by adding the 12 least significant bits to this four kilobytes aligned physical page address (12 last bits are null).

Figure 2.10: Translation mechanism (Intel documentation [28, chap. 4.5])

As the entries of each level in the page table nodes are physical addresses of page frames in physical memory, these addresses are four kilobytes aligned, meaning the twelve least significant bits of such an address must be zero. The page table mechanism can thus use these bits to store some metadata about the pointed memory. The format of a last level page table entry is given in Table 2.1.

Access rights and page fault Some metadata stored in the least significant bits of the page table entries are related to access rights, these are the bits "Present (P)", "Read/write (R/W)", "User/Supervisor (U/S)". When an access occurs to a virtual address belonging to a given page frame, the page table entry describing this page frame is loaded by the MMU while traversing the page table. If the combination of bits P, R/W or U/S does not allow the access, the processor emits a "page fault" exception.

| 63     | 62 | 61 | 60 | 59 | 58 | 57 | 56 | 55 | 54  | 53   | 52  | 51 | M   | M-1 |    |    |    |   |     | • • •       |   |   |             |             |             |             | 32 |

|--------|----|----|----|----|----|----|----|----|-----|------|-----|----|-----|-----|----|----|----|---|-----|-------------|---|---|-------------|-------------|-------------|-------------|----|

| X<br>D |    | Ρŀ | ŒΥ |    |    |    |    |    |     |      |     |    | MBZ |     |    |    |    | A | ddr | ess .       |   |   |             |             |             |             |    |

| 31     |    |    |    |    |    |    |    |    |     |      |     |    |     |     | 12 | 11 | 10 | 9 | 8   | 7           | 6 | 5 | 4           | 3           | 2           | 1           | 0  |

|        |    |    |    |    |    |    |    |    | . A | ddre | ess |    |     |     |    |    |    |   | G   | P<br>A<br>T | D | A | P<br>C<br>D | P<br>W<br>T | U<br>/<br>S | R<br>/<br>W | Р  |

| Offset   | Name    | Description                                                                                                                                                       |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63       | XD      | If IA32_EFER.NXE = 1, execute-disable (if 1, instruction fetches are not allowed from the 4-KByte page controlled by this entry); otherwise, reserved (must be 0) |

| 62:59    | PKEY    | Protection key; if CR4.PKE = 1, determines the protection key of the page; ignored otherwise                                                                      |

| 58:52    |         | Ignored                                                                                                                                                           |

| 51:M     | MBZ     | Reserved (must be 0)                                                                                                                                              |

| (M-1):12 | Address | Physical address of the 4-KByte page referenced by this entry                                                                                                     |

| 11:9     |         | Ignored                                                                                                                                                           |

| 8        | G       | Global; if CR4.PGE = 1, determines whether the translation is global; ignored otherwise                                                                           |

| 7        | PAT     | Indirectly determines the memory type used to access the 4-KByte page referenced by this entry                                                                    |

| 6        | D       | Dirty; indicates whether software has written to the 4-KByte page referenced by this entry                                                                        |

| 5        | A       | Accessed; indicates whether software has accessed the 4-KByte page referenced by this entry                                                                       |

| 4        | PCD     | Page-level cache disable; indirectly determines the memory type used to access the 4-KByte page referenced by this entry                                          |

| 3        | PWT     | Page-level write-through; indirectly determines the memory type used to access the 4-KByte page referenced by this entry                                          |

| 2        | U/S     | User/supervisor; if 0, user-mode accesses are not allowed to the 4-KByte page referenced by this entry                                                            |

| 1        | R/W     | Read/write; if 0, writes may not be allowed to the 4-KByte page referenced by this entry                                                                          |

| 0        | P       | Present; must be 1 to map a 4-KByte page                                                                                                                          |

Table 2.1: Format of a last level page table entry

This exception can (and must) be intercepted by the operating system in order to correct the situation before continuing the execution of the faulting context. This mechanism is at the foundation of the multiple use cases of paging.

The operating system can give a process an address range with a bit P set to zero to load data only when an access to the given page frame would cause a page fault, this is called lazy mapping and is used by the swap and memory overcommitment mechanisms mentioned before, but also lazy file access for file with an arbitrary big size.

Similarly, copy-on-write (COW) semantics for memory are obtained by giving a range of addresses without write access. While accessible for read accesses, the memory will cause a page fault to be emitted when an attempted write operation occurs, thus giving the system the opportunity to copy the content of the faulting page frame to another location in physical memory, updating the page table mapping to point to this new location and continue the

execution. From there, the write operation will occur in the new location, effectively modifying a copy of the old read-only data. Copy-on-write is used in the fork system call to avoid copying all the parent process data to the offspring process while unneeded.

Finally, the U/S bit is used to differentiate between user-accessible pages and kernel-only pages when running a process in user mode and is the base of kernel and process memory isolation, and thus, of the userland concept mentioned earlier.

Extending access rights for user page: protection keys While the three bits described above are used to determine access rights for an access regarding a given page frame, changing the permissions for a large number of pages is costly as it forces to change the permission bits of each page. To avoid this overhead, another mechanism called *protection keys* has been introduced for processors Intel Skylake and newer.

This mechanism assigns a key to any number of pages, thus creating a group of pages all tagged with given key. The permissions of this group of pages are then determined by the permissions affected to the key. Therefore, when using this mechanism, there is no further need to modify the page table after setting the key for all the wanted pages.

Protection keys use the aforementioned PKEY zone in a page table entry to store a number between 0 and 15 as well as a new 32-bit CPU register called "Protection Key Right for User access (PKRU)".

When the protection key system is enabled, any access to a memory range causes the protection key system to be checked. The key stored in the page table entry PKEY slot is retrieved and used as an offset in the PKRU register. For  $0 \le key \le 15$ , the bit PKRU[ $2 \times key$ ] controls the access right and PKRU[ $2 \times key + 1$ ] controls the write right to the memory zone with PKEY set to key.

Modifying the PKRU register is done using the two RDPKRU and WRPKRU instructions to respectively read or write to the register. Setting the bit  $PKRU[2 \times key]$  disables all data accesses to the memory location, this does not include instruction fetches, setting bit  $PKRU[2 \times key + 1]$  disables write accesses to the memory location.

Such a system may seem redundant with the already existing permissions enforced by the P and R/W bits, but has multiple advantages. Firstly, as mentioned earlier, after setting the PKEY value of the page only the PKRU register needs to be modified. Secondly, while clearing bit P leads to a page being totally inaccessible even for instructions fetches, setting bit P and a PKEY with all accesses disabled results in an execute-only mapping, such permissions cannot be achieved with only the legacy permission bits.

The Translation Look-aside Buffer and paging structure caches As shown, the paging mechanism adds multiple convenient behaviors, allowing for techniques like swap or ondemand loading of frames to be used. At the same time it inevitably adds some overhead due

to the translation process. In order to reduce this overhead, modern MMUs possess caching capabilities through the use of the Translation Look-aside Buffer (TLB).

The TLB stores individual translation information by associating the page number to the physical address of the associated page in the page table. The page number is the part of the virtual address which is used in the page table to identify a given page frame and thus depends on the size of the page. It is composed respectively of bits 47:12, 47:21, or 47:30 for pages of respectively four kilobytes, two megabytes or one gigabyte. Other important information is cached with this page number to physical address mapping, such as the permission for the page represented by the logical-AND of the R/W flags of all the page table entries leading to the page frame, the logical-AND of the U/S flags of these same pages and the PKEY field if the protection key feature is enabled.

The CPU can also cache translation information about the top three levels of paging structure, PML4 entries, PDPT entries and PD entries. Such that in trying to translate an address, if the TLB does not contain a corresponding cached translation for the page number, the CPU will search for cached information in the PDE cache, if none is found, search in the PDPT cache, and finally in the PML4 cache. If the TLB contains the cached translation, the CPU uses it, else it finishes the translation using the page table in memory from the last level obtained from the paging structure cache.

Because the cached information may become false at some point when mappings are changed in the page table, cached information must be invalidated. Different actions naturally invalidate translation caches, this includes loading a new page table root in the cr3 register (MOV instruction with cr3 as a target), a context transition between guest and host when using virtualization extensions. The INVLPG instruction is used to manually invalidate translations with a finer grain.

However, invalidating the whole TLB at every context transition when scheduling another process is costly. To avoid this cost, especially when switching between the same processes multiple times, hardware manufacturers added a feature called Process-Context Identifiers (PCIDs) which are used to tag a given entry in the translation caches with the process identifier allowing invalidation to target a smaller portion of the TLB.

When PCIDs are enabled, switching page tables when scheduling another process does not force an invalidation of the whole TLB. An instruction, INVPCID was introduced to allow finer grained control over which entries of the TLB are invalidated, for example invalidating all the entries tagged with a given PCID.

The TLB and paging-structure caches are important additions to current MMUs as they speed up the translation process by avoiding a complete traversal of the page table tree for each virtual address translation and are used not only for data accesses but also for instruction fetches and prefetches in case of speculative execution.

The multiple benefits of paging, such as isolation or memory reservation, make the paging a preeminent part of current memory management systems. This is reinforced by the TLB cache which decreases the overhead of paging translation and thus of paging in general.

#### 2.2.2 Paging and memory management in user space

While the page table structure is maintained by the kernel, its benefits are also available in user space both indirectly: isolation of kernel and user space, isolation between processes; and directly, through the use of different system calls.

The paging mechanism is activated per CPU and so is activated for both the kernel and user space. Depending on the kernel model, the page table could be common for all execution contexts, but using a different page table enforces some isolation between processes being executed in user space.

The Linux kernel uses a different page table for each process in user space, with several consequences. On one hand, the memory spaces of processes are separated, forbidding access for a process to the memory of another. On another hand, Linux allows mappings to be reused across different processes in order to create shared memory segments.

This ability is important to avoid a change of page table when switching to kernel mode, as each process needs the kernel to be mapped in its address space for system calls. The kernel uses a clever trick to avoid having to change every process page table when modifying kernel mappings by reserving one top level entry in the PML4 for kernel usage when a process page table is instantiated. This top level entry is the same for every process allowing the kernel to change mappings in subsequent entries without having to modify the page table of each process.

Moreover, using copy-on-write semantics described previously, shared library containing mutable data can be shared without inducing a big memory footprint as the memory is shared until a mutable part is modified in which case copy-on-write is used to copy only the modified page frame.

Creating a mapping mmap is the most preeminent system call for user space memory low level management. It enables the programmer to create a new mapping between virtual and physical memory space. Depending on the parameters (MAP\_ANONYMOUS or not) the physical memory is either empty memory or file backed memory. In case the memory is file-backed, this system call exhibits the different advantages mentioned in Section 2.2.2. Using the MAP\_PRIVATE option creates a copy-on-write mapping. As mmap mappings are page table mappings, they only manipulate virtual memory, backing physical memory is only allocated when needed (first access).

Changing access rights mprotect is a primitive used to modify permissions on a given memory mapping previously obtained by using mmap. As explained in Section 2.2.1, the page table entries contain permission bits determining which types of access are allowed for a given zone of memory. The mprotect system call defines several boolean flags among which PROT\_NONE, PROT\_READ, PROT\_WRITE and PROT\_EXEC which can be combined to define if a page can be read, written or executed.

While these flags are defined by the POSIX standard and thus used in the Linux system call, their presence in the system call interface does not imply every combination is actually supported by the underlying hardware.

The bits from an x86 page table entry used to determine access rights are bit "Present (P)", "Read/write (R/W)", "User/Supervisor (U/S)", from Table 2.1. Because the bit U/S is always activated for page meant to be accessed in user space, bits P and R/W are the only ones used to determine permissions. However, as putting the present bit to 0 causes a page fault when trying to access the page either by reading or writing, this means no combination of bits can fulfill a PROT\_WRITE only permission set. This is summed up in Table 2.2. Moreover, x86 processors have a bit to disable execution on a given page but for the same reasons as above, the PROT\_EXEC flag is equivalent to the PROT\_READ flag in Linux.

| mprotect flags         | Page table bits   |

|------------------------|-------------------|

| PROT_NONE              | $\neg P$          |

| PROT_READ              | $P \mid \neg R/W$ |

| PROT_WRITE             | not possible      |

| PROT_READ   PROT_WRITE | $P \mid R/W$      |

Table 2.2: Correspondence between x86 page table bits and mprotect flags

Working with protection keys In kernel version starting from 4.9, the protection key feature introduced by Intel is also available in user space memory management through the pkey\_alloc, pkey\_free, and pkey\_mprotect system calls and the pkey\_set utility function. The protection key mechanism allows a developer to further restrict accesses to a memory zone by disabling write or all kinds of accesses (read and write) to the given zone.

This is done by first using pkey\_alloc to allocate a protection key with the right set of permissions, either PKEY\_DISABLE\_ACCESS or PKEY\_DISABLE\_WRITE, and then use pkey\_mprotect to atomically change both regular protection flags available to mprotect and set a protection key to the given memory range.

Thanks to this interface, the advantages of protection keys described previously are available in user space, it is thus possible to create an execute-only mapping by combining the PROT\_EXEC (equivalent to PROT\_READ) flag with a protection key allocated with PKEY\_DISABLE\_ACCESS. This method also reduces the cost of changing permissions on pages, as it requires neither changing all the permission bits as explained before nor switching to kernel space as the RDPKRU and WRPKRU instructions are available in user space and usable through the wrapper pkey\_set. Only the initial setup of the PKEY using pkey\_alloc and pkey\_mprotect is switching to kernel space.

To summarize, this section presents the hardware mechanisms and tools built on them which are commonly used to manage memory, either in kernel space or user space. As explained, changing mappings have a cost, both directly, and indirectly by forcing the TLB cache to be flushed. Therefore their efficiency relies on the ability of the system to properly use them.

#### 2.3 State of the art: resources management and NUMA

Resources management is a vast subject, which has been studied since the inception of computer science. With new topologies being born, new problems and new solutions are discussed. SMP architectures and even more so NUMA architectures both provide shared memory and use parallelism as a mean to increase performances. Thus, contention of shared resources, either hardware or software, is the main cause of performance degradation.

The effect of different resource management schemes on the performances of NUMA architectures, either in user space or inside the operating system has been extensively studied and is an ongoing work. Among the different solutions proposed to manage multicore architectures, some solutions try to enhance application performances by proposing better user space resource management, others consider a more global approach by modifying the operating system or even replacing it. This section is organized as follows. Section 2.3.1 presents user space related solutions, Section 2.3.2 introduces runtimes or kernel modifications, and Section 2.3.3 describes new operating system designs built to tackle multicore architectures.

#### 2.3.1 User space solutions

User space solutions include several techniques, from scalable memory allocation to specific profiler for NUMA architectures. All these solutions share the common characteristic of managing memory in multicore systems. They proceed using different methods, either aware of topology or not, to maximize performances by reducing contention on shared hardware resources or data structures. Works described below are summed up in Table 2.3.

| Proposal   | Issue(s)                                                | Approach(es)              |

|------------|---------------------------------------------------------|---------------------------|

| Hoard      | false sharing (cache contention)                        | load balancing            |

| Streamflow | lock contention + TLB contention                        | load balancing + lockless |

| MemProf    | locality + interconnect contention                      | monitoring                |

| NAPS       | locality + interconnect contention<br>+ lock contention | load balancing + lockless |

Table 2.3: Related work on NUMA: user space solutions

Hoard: A Scalable Memory Allocator for Multithreaded Applications As explained in Section 2.1.1 and 2.1.2, processor caches carry at the same time an important increase in terms of memory access latency but also introduce different issues related to the cache coherency mechanism. False sharing is the name given to one such issue that arises when different processors are accessing data from two different locations that are close and thus share a cache line. As cache controllers load and store data at the granularity of a cache line, when two different processors write to different data in the same cache line they force each other to invalidate the cache line even though there is no logical reason to do so, greatly degrading performances.

Berger et al. [4], propose Hoard, a memory allocator which avoids false sharing when possible.