## Parallel Standard-Compliant SystemC Simulation of Loosely-Timed Transaction Level Models

Gabriel Busnot

#### ▶ To cite this version:

Gabriel Busnot. Parallel Standard-Compliant System C Simulation of Loosely-Timed Transaction Level Models. Computation and Language [cs.CL]. Université de Lyon, 2020. English. NNT: 2020 LYSE 1315. tel-03364390

## HAL Id: tel-03364390 https://theses.hal.science/tel-03364390v1

Submitted on 4 Oct 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT: 2020LYSE1315

#### THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de

l'Université Claude Bernard Lyon 1

**Ecole Doctorale** N° 512 **InfoMaths**

Spécialité de doctorat : Informatique

Soutenue publiquement le 18/12/2020, par :

**Gabriel Busnot**

# Simulation parallèle et conforme au standard SystemC de modèles transactionnels à temps relâché

#### Devant le jury composé de :

| Guérin Lassous, Isabelle | Professeur des Universités | Université Claude Bernard Lyon 1 | . Présidente du jury |

|--------------------------|----------------------------|----------------------------------|----------------------|

| Maraninchi, Florence     | Professeur des Universités | Université Grenobles Alpes       | Rapporteure          |

| Pêcheux, François        | Professeur des Universités | Sorbonne Université              | Rapporteur           |

| Andrade, Liliana         | Maître de Conférences      | Université Grenobles Alpes       | Examinatrice         |

| Dömer, Rainer            | Professeur des Universités | Université de Californie         | Examinateur          |

| Maillet-Contoz. Laurent  | Responsable Industriel     | STMicroelectronics               | Examinateur          |

| Moy, Matthieu            | Maître de Conférences      | Université Claude Bernard Lyon 1 | Directeur de thèse   |

| Sassolas, Tanguy         | Ingénieur-chercheur        | CEA                              | Co-Encadrant         |

| Ventroux, Nicolas        | Responsable Industriel     | Thales                           | Co-Encadrant, invité |

## Remerciements

Il me sera difficile de nommer toutes celles et tous ceux qui m'ont soutenu au cours de cette thèse. J'espère néanmoins que chacun se reconnaitra dans l'une des quelques lignes qui suivent.

Je tiens tout d'abord à remercier Matthieu Moy, Maître de conférence à l'Université Claude Bernard Lyon 1, pour avoir dirigé ma thèse avec attention malgré la distance qui le séparait de la capitale. Je remercie également chaleureusement Tanguy Sassolas et Nicolas Ventroux du CEA, List, pour leur encadrement au quotidien et leur optimisme permanent sans lequel je n'aurais sans doute pas mené ces travaux à leur terme.

Un grand merci aussi à Florence Maraninchi de l'Université Grenobles Alpes et à François Pêcheux de Sorbonne Université pour avoir accepté d'être rapporteurs et de consacrer de nombreuses heures à une lecture critique de mon manuscrit. Je remercie par la même occasion le reste de mon jury de soutenance : Liliana Andrade, Rainer Dömer, Isabelle Guérin Lassous et Laurent Maillet-Contoz.

Mais cette section serait largement incomplète sans y remercier tout mon entourage : mes collègues de travail avec qui j'ai pu échanger sur toutes sortes de sujets, du plus technique au plus informel, et qui ont pu m'apporter leur aide à plusieurs reprises; mes amis, ceux du CEA et d'ailleurs, qui m'ont patiement écouté me plaindre avec plus ou moins de théâtralité trois années durant; Jason qui a bénévolement relu intégralement mon manuscrit à quelques jours du rendu final; et enfin ma famille et à ma compagne qui, bien que n'ayant pas la moindre idée de ce que je faisais chaque jour devant mon écran, ont toujours cru en moi et ont eu raison puisque j'écris ces lignes aujourd'hui!

Merci enfin au CEA pour avoir financé ces trois années de thèses de doctorat.

## Résumé détaillé

### Présentation générales

Cette thèse porte sur la simulation parallèle SystemC. Spécifiquement, elle vise une famille de modèles dit transactionnels à temps relâché. La contribution principale de cette thèse porte sur la conception et le développement d'un noyau de simulation SystemC parallel. Ce noyau permet l'exécution parallèle de modèles SystemC standard après ajout d'annotations spécifiques.

Le manuscrit se divise en 5 chapitres. Le premier chapitre présente des notions générales relatives à SystemC ainsi qu'au parallélisme et à la concurrence en informatique. Le second chapitre présente la problématique de la thèse ainsi qu'un état de l'art des techniques de simulation SystemC parallèle. Le troisième chapitre est le cœur du manuscrit. Il explique les procédés principaux mis en œuvre pour permettre la simulation SystemC parallèle de modèles transactionnels à temps relâché. Le quatrième présente les expérimentation du procédé expliqué chapitre 3. Ces expérimentations mettent en valeur des limitations dans le cas de simulation de logiciels exécutés sous un système d'exploitation tel que Linux. Le cinquième et dernier chapitre analyse les causes de ces observations et propose des solutions spécifiques ainsi que leur évaluation expérimentale.

## Chapitre 1

Dans ce premier chapitre, les notions générales de concurrence et de parallélisme qui cohabitent étroitement dans le contexte de la simulation SystemC parallèle sont introduites. Les similitudes et différences parfois subtiles entre ces deux notions y sont illustrées à l'aide d'exemples. Le langage de description matérielle SystemC est ensuite présenté. Le niveau de description RTL, cible initiale de SystemC, est utilisé pour illustrer les bases de SystemC que sont la simulaiton à événements discrets, les modules, les ports, les « channels » ainsi que les processus. Enfin le plus récent niveau de description transactionnel est introduit. Les deux niveaux de précision de gestion du temps « approximatif » et « relâché » sont décrits ainsi que des techniques de modélisation modernes standards telles que l'interface mémoire directe (DMI) et le découplage temporel. Les procédés développés dans ce manuscrit s'emploient à supporter l'ensemble des techniques de modélisation proposées.

### Chapitre 2

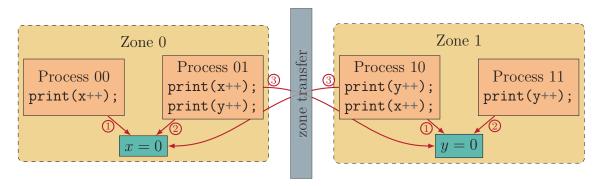

Le deuxième chapitre débute par un bref tour d'horizon des techniques d'accélération usuelles applicables à la simulation de modèles SystemC. Le choix de la parallélisation entre les processus SystemC au niveau du noyau de simulation est ainsi justifié. Les obstacles qui s'opposent spécifiquement à l'évaluation parallèle de processus SystemC sont alors exposés. En particulier, les problématiques de « thread-safety » 1 et d'atomicité des processus SystemC sont introduites au travers d'exemples. Une évaluation non atomique de processus est ici désignée sous le terme de *conflit*.

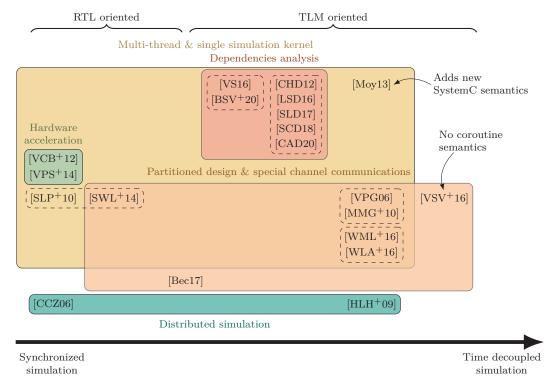

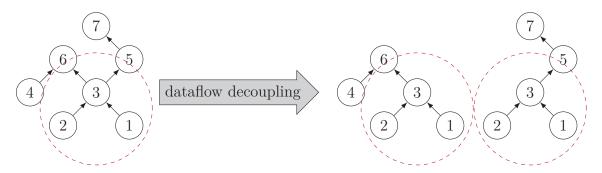

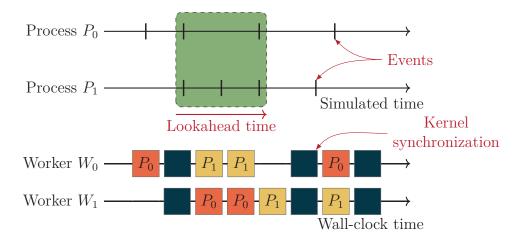

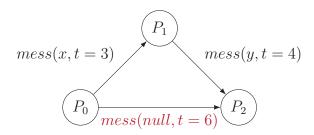

La seconde partie du deuxième chapitre est un état de l'art des techniques de simulation SystemC parallèle. De nombreuses approches y sont rapportées : simulation à temps synchronisé ou découplé, simulation accélérée sur GPU ou sur matériel dédié, simulation distribuée ou centralisée, exécution reproductible ou non ou encore simulation RTL ou TLM. Il ressort de cette étude qu'une unique approche supporte efficacement les modèles transactionnels à temps relâché, spécialement ceux faisant usage du découplage temporel et du protocole DMI.

Il s'agit de SCale 1.0, un noyau de simulation SystemC parallèle qui a servi de point de départ aux travaux présentés ici. SCale 1.0 est donc présenté de manière plus détaillée dans la fin du chapitre 2 et ses limitations font l'objet d'une analyse méticuleuse. Il en ressort que bien que présentant des mécanismes théoriquement efficaces, ces derniers inapplicables avec de nombreux logiciels simulés, en particulier ceux exécutés sous Linux. Des problèmes de performance importants se posent également.

## Chapitre 3

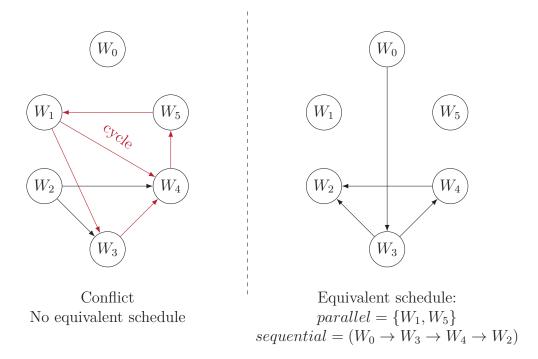

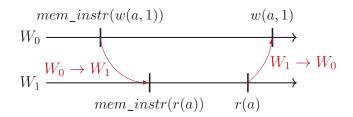

Ce chapitre présente SCale 2.0, une refonte majeure de SCale 1.0. La plupart des mécanismes de SCale 1.0 y sont remplacés et seule l'approche générale reste comparable : l'instrumentation des accès mémoire simulés dans le but de contrôler les interactions entre processus et de préserver leur atomicité. L'idée principale consiste en effet toujours à garantir que les interactions par accès mémoire entre les processus décrivent un ordre partiel entre ces derniers, c'est à dire qu'il existe un évaluation séquentielle produisant le même résultat que l'évaluation parallèle en cours.

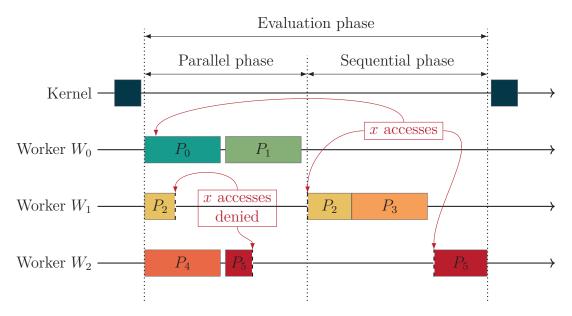

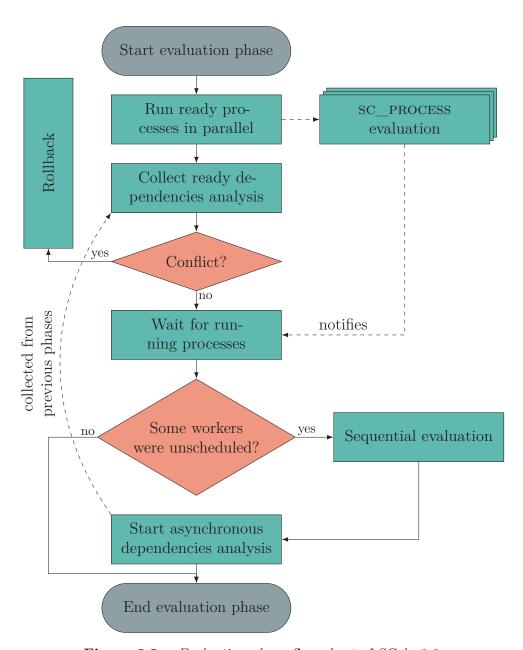

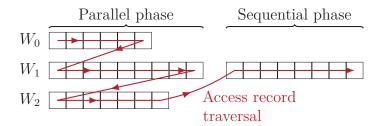

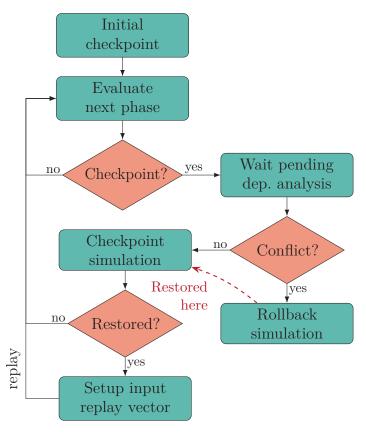

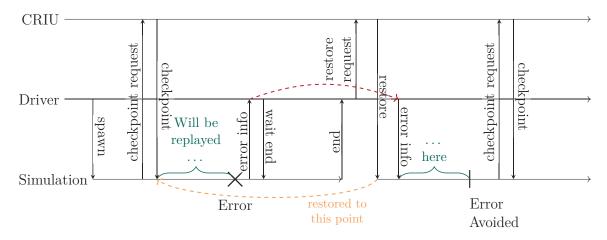

Le chapitre s'ouvre sur la description du flot d'exécution globale d'une phase d'évaluation sous SCale 2.0 : évaluation parallèle de processus suivie d'une évaluation séquentielle dans le cas où certains on été suspendus; analyse des dépendances entre processus en cas de phase séquentielle et récupération d'erreur par retour en arrière.

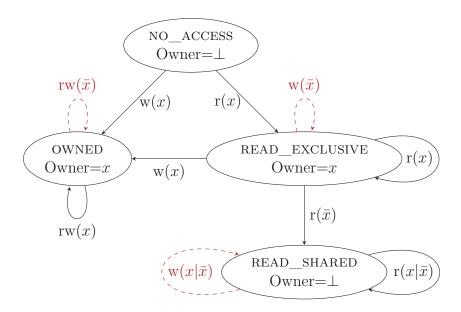

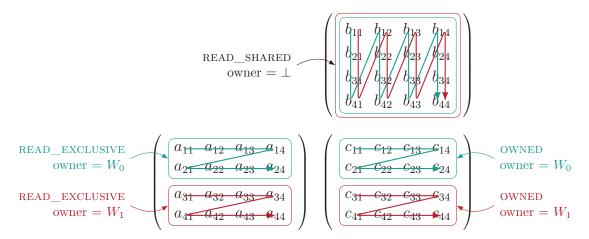

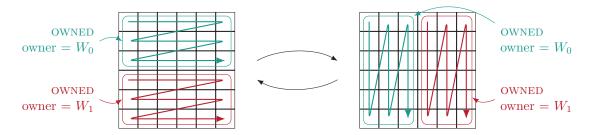

Les procédés appliqués lors de la phase parallèle spécifiquement sont ensuite détaillés en commençant par la garantie de non dépendance entre processus lors de la phase parallèle, une propriété fondamentale autorisant de nombreuses optimisations. Une

<sup>&</sup>lt;sup>1</sup>La thread-safety désigne le fait qu'une portion de code peut être exécutée simultanément par plusieurs fils d'exécution sans causer d'incohérence.

politique d'autorisation d'accès mémoire offrant la garantie en question ainsi qu'une implémentation efficace sont ensuite définies.

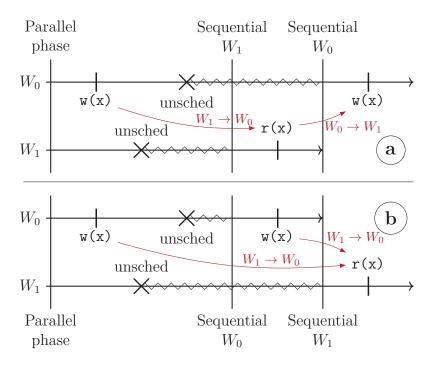

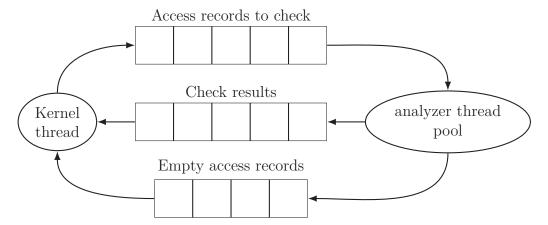

La phase parallèle peut être suivie d'une phase séquentielle qui est alors décrite : ordre d'évaluation des processus suspendus lors de la phase parallèle, vérification des dépendances entre processus à l'aide de l'enregistrement préalable des accès mémoire, génération de la trace permettant le reproduction de simulation et retour en arrière en cas de violation d'atomicité des processus.

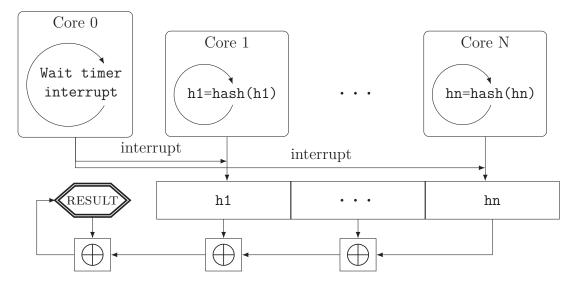

Enfin, le système de gestion des interactions via mémoire partagée est généralisé à tout type d'interaction en considérant chaque partie du modèle simulé comme une ressource pouvant être, au sens large, soit lue, soit écrite, à l'instar d'une adresse mémoire. Cela permet, par exemple, de supporter les interactions par interruptions (timer, inter-processeur, etc.).

## Chapitre 4

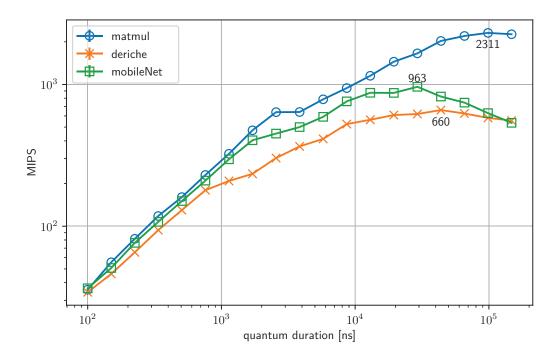

Le quatrième chapitre est une analyse expérimentale du procédé décrit chapitre 3. Le serveur pourvu de 36 cœurs hébergeant les expérimentations est décrit ainsi que le modèle simulé : une architecture symétrique à mémoire partagée pourvue de 1 à 32 cœurs RISC-V simulés par QEMU. Les benchmarks baremetal<sup>2</sup> de multiplication de matrice parallèle, de détection de contours par filtrage de Deriche et de réseau de neurones convolutif Mobilenet sont présentés, ainsi que leurs versions sous Linux additionnées des benchmarks Blackscholes et Swaptions issues de la suite Parsec.

Un protocole de validation fonctionnelle expérimentatale de SCale 2.0 basé sur un benchmark hautement aléatoire est également exposé. Il illustre la capacité de SCale 2.0 à produire toujours le même résultat lors de l'utilisation de la fonction de reproduction de simulation. Lorsque cette dernière n'est pas activée, le résultat du benchmark de test présente une forte variabilité.

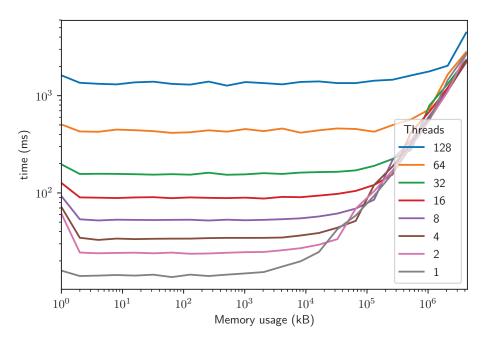

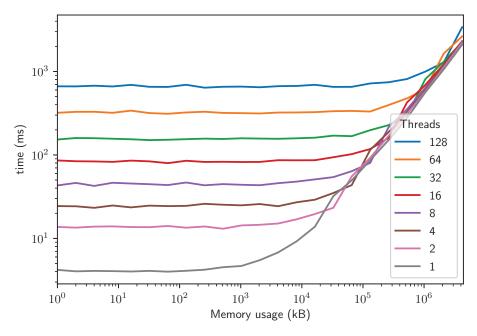

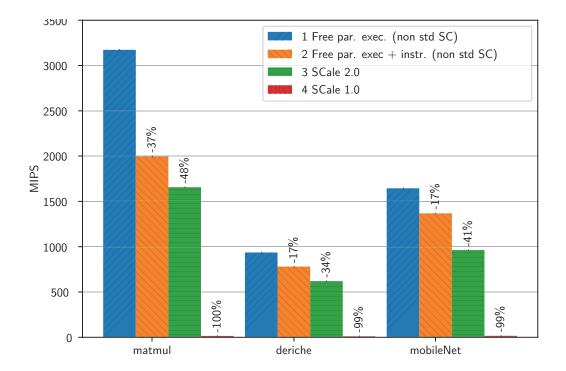

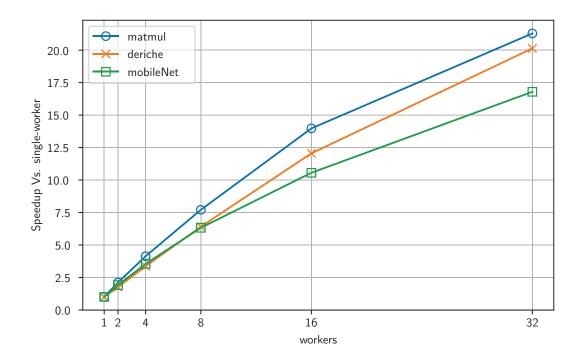

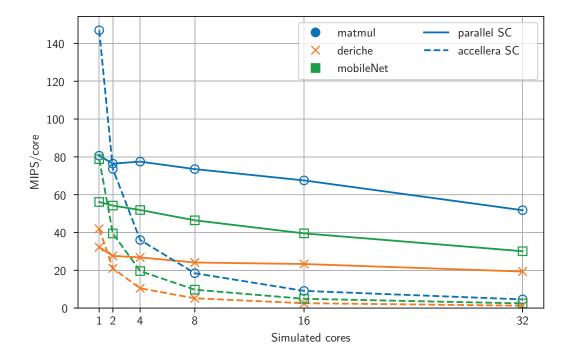

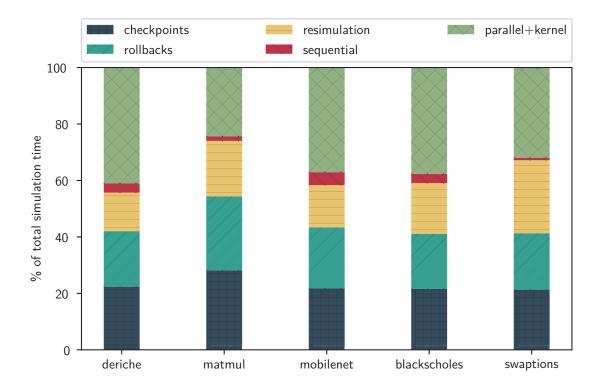

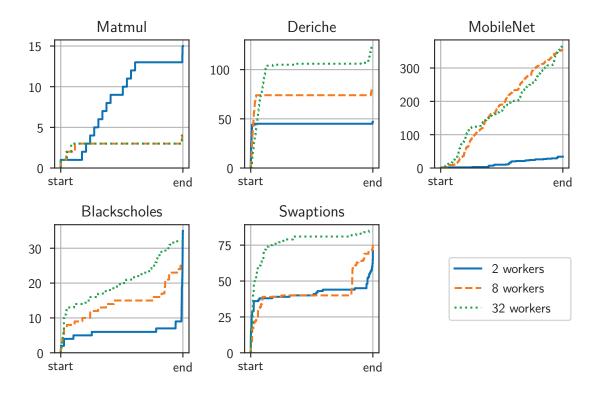

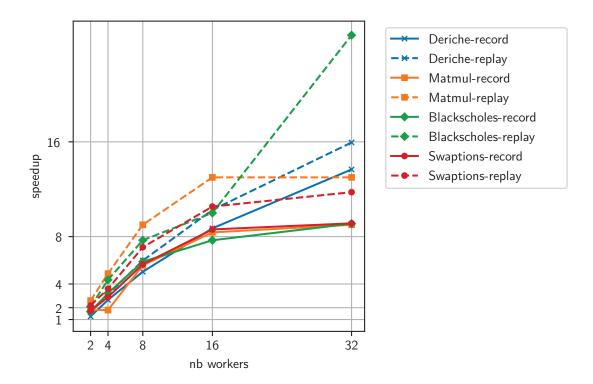

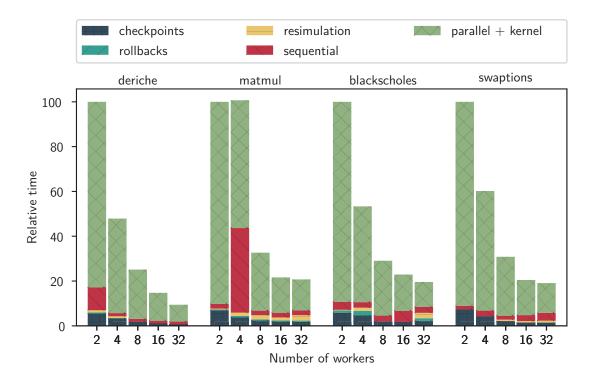

La suite du chapitre présente les performances de simulation offerte par SCale 2.0. Des accélérations atteignant  $\times 15$  face au noyau SystemC de référence et de  $\times 110$  face à SCale  $1.0^3$  sont observés.

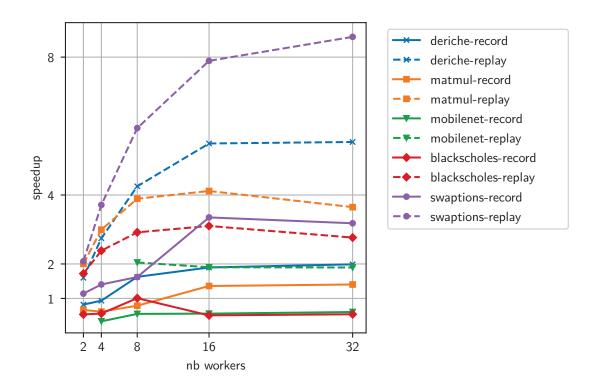

Les accélérations concernant les applications sous Linux sont en revanche nettement moins satisfaisants puisque toujours inférieurs à 4. Ces résultats sont analysés en détail dans la suite du chapitre. Cette analyse met en valeur divers facteurs tels que le mauvais potentiel de parallélisation lors de la simulation du boot et de l'extinction de Linux. La raison principale réside cependant surtout dans la présence d'un grand nombre de

<sup>&</sup>lt;sup>2</sup>Logiciel s'exécutant à même le matériel, sans le support d'un système d'exploitation.

<sup>&</sup>lt;sup>3</sup>Les performances très en retrait de SCale 1.0 sont expliquées par son utilisation dans un contexte très différent de celui dans lequel il a été développé. La fréquence des accès mémoire, notamment est plusieurs ordres de grandeur supérieur dans le cas présent, saturant totalement sont système d'instrumentation et causant cette régression.

conflits qui nécessitent autant de retours en arrière coûteux. Ce constat révèle que malgré la grande efficacité de SCale 2.0 dans la majorité des situations, il existe des schémas d'accès mémoire notamment qui causent de nombreux conflits.

## Chapitre 5

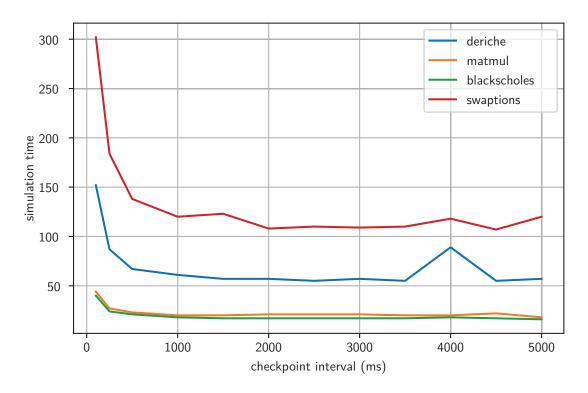

Le cinquième et dernier chapitre propose des solutions spécifiques aux problèmes identifiés dans la dernière partie du chapitre 4. La première concerne les partie de la simulation faiblement parallélisables telles que le boot de Linux. Ces parties sont aussi souvent peu intéressantes pour l'utilisateur de SCale 2.0 qui cherche surtout à tester le logiciel qu'il a développé et qui s'exécute sous Linux. Un système de variation de la précision de simulation est proposé. Il permet de choisir dynamiquement le mode de simulation des accès mémoire, permettant notamment de les effectuer directement dans QEMU sans recourir au modèle SystemC. En contrepartie, la simulation parallèle n'est plus possible mais les vitesses de simulations sont alors comparables. Ce mode de simulation séquentielle peu précise mais rapide et déterministe est particulièrement adapté à la simulation des parties du code sans intérêt directe pour l'utilisateur.

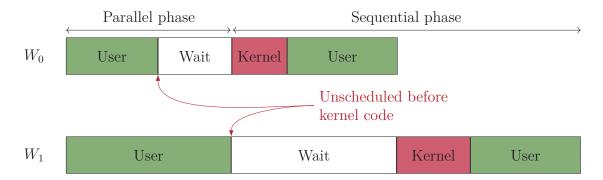

La seconde cause majeure de ralentissement est le grand nombre de conflits concentrés dans certaines parties de la simulation et responsables à eux seuls de la détérioration globale des performances. L'étude de l'origine de ces conflits montre que le code provenant du noyau Linux est responsable de la majeure partie des conflits (e.g., support des fautes mémoire et gestion du système de fichiers). Ces conflits sont par nature difficile à anticiper et donc à éviter avec fiabilité. La solution retenue consiste alors à ne pas paralléliser la simulation du code appartenant au noyau Linux. Le niveau de privilège des processeurs simulés est utilisé à cet effet : dès qu'un processeur qui le niveau de privilège minimal utilisateur, le processus simulant ce processeur est exécuté séquentiellement jusqu'à ce que son niveau de privilège retombe au niveau utilisateur. La quasi totalité des conflits est alors évitée au prix d'un ralentissement à peine mesurable, la majorité du code simulé étant exécuté en mode utilisateur.

Une nouvelle mesure des performances de SCale 2.0 est enfin réalisée avec ces dernières techniques. Des accélérations d'environ ×9 face au noyau séquentiel de référence ont obtenus pour l'intégralité des benchmarks. La comparaison avec SCale 1.0 n'est pas possible, ce dernier ne supportant pas la simulation de systèmes exécutant Linux.

## **Publications**

#### • Articles:

- Gabriel Busnot, Tanguy Sassolas, Nicolas Ventroux, Matthieu Moy. Standard-compliant Parallel SystemC simulation of Loosely-Timed Transaction Level Models. ASP-DAC 2020

25th Asia and South Pacific Design Automation Conference, Jan 2020, Beijing, China. pp.1-6. <hal-02416253>

- Gabriel Busnot, Tanguy Sassolas, Matthieu Moy, Nicolas Ventroux. Standard-compliant Parallel SystemC simulation of Loosely-Timed Transaction Level Models: from baremetal to Linux-based applications support. VLSI

- Amir Charif, Gabriel Busnot, Rania Mameesh, Tanguy Sassolas, Nicolas Ventroux. Fast Virtual Prototyping for Embedded Computing Systems Design and Exploration. 11th Workshop on Rapid Simulation and Performance Evaluation: Methods and Tools, Jan 2019, Valence, Spain. <10.1145/3300189.3300192>.<hal-02023805>

#### • Patents:

- Gabriel Busnot, Tanguy Sassolas, Nicolas Ventroux. Procédé de simulation parallèle reproductible de niveau système électronique mis en œuvre au moyen d'un système informatique multicœurs de simulation à événements discrets. FR1911332

- Gabriel Busnot, Tanguy Sassolas, Matthieu Moy. Procédé de simulation parallèle reproductible de niveau système électronique mis en œuvre au moyen d'un système informatique multicœurs de simulation à événements discrets. FR2012150

#### • Poster:

Gabriel Busnot, Tanguy Sassolas, Nicolas Ventroux, Matthieu Moy. Parallel SystemC Simulation Of Multicore Platforms Running Linux. ACACES Poster Session, Jul 2018, Fiuggi, Italy.

# Contents

| In | trod  | uction        |                                                       | 13 |

|----|-------|---------------|-------------------------------------------------------|----|

| 1  | Par   | allel C       | computing and SystemC Simulation Background           | 17 |

|    | 1.1   |               | luction                                               | 18 |

|    | 1.2   |               | urrency and Parallelism                               |    |

|    |       | 1.2.1         | Concurrency                                           |    |

|    |       | 1.2.2         | Fine-Grained Control Over Concurrency with Coroutines |    |

|    |       | 1.2.3         | Parallelism                                           |    |

|    |       | 1.2.4         | Enabling Parallel Computation with Threads            |    |

|    | 1.3   | Syster        | nC Modeling and Simulation Overview                   |    |

|    |       | 1.3.1         | Virtual Prototyping in the SoC Design Flow            |    |

|    |       | 1.3.2         | The SystemC Modeling Language                         |    |

|    |       | 1.3.3         | Discrete Event Simulation of SystemC Models           |    |

|    | 1.4   | TLM-          | 2.0                                                   |    |

|    |       | 1.4.1         | TLM: Abstraction of the Communication Layer           |    |

|    |       | 1.4.2         | Coding Styles in TLM                                  | 34 |

| 2  | Par   | allel S       | ystemC Simulation: Challenges and Existing Solutions  | 39 |

| _  | 2.1   |               | el SystemC-TLM Simulation: Problem Statement          |    |

|    |       | 2.1.1         | SystemC Acceleration Strategies                       |    |

|    |       | 2.1.2         | Parallelizing SystemC                                 |    |

|    | 2.2   |               | ng Approaches                                         |    |

|    |       | 2.2.1         | Synchronous SystemC Parallelization                   |    |

|    |       | 2.2.2         | Time Decoupling                                       |    |

|    |       | 2.2.3         | SCale 1.0: Runtime Processes Interactions Monitoring  |    |

| 3  | D., . |               | Calation for IT TIM Develled Circulation              | 63 |

| 9  | 3.1   | -             | Solution for LT-TLM Parallel Simulation iew           |    |

|    | 0.1   | 3.1.1         |                                                       |    |

|    |       | 3.1.1         | Simplified Model                                      |    |

|    |       | 3.1.2         |                                                       |    |

|    | 2.0   |               | mem_instr Outline                                     |    |

|    | 3.2   | 3.2.1         | arallel Evaluation Phase                              |    |

|    |       | 3.2.1 $3.2.2$ | Advantages of Zero Dependencies Parallel Phase        |    |

|    |       | 3.2.3         | Correct Memory Access Recording Order                 |    |

|    |       | 0.2.0         | COLLECT METHOLY ACCESS DECOLUTING OLDER               | 14 |

#### CONTENTS

|    |                 | 3.2.4   | Efficient FSMs Reset                                          | 75  |

|----|-----------------|---------|---------------------------------------------------------------|-----|

|    |                 | 3.2.5   | Fast Scalable FSM Storage                                     | 77  |

|    | 3.3             | The Se  | equential Evaluation Phase                                    | 79  |

|    |                 | 3.3.1   | Choosing the Sequential Evaluation Order                      | 80  |

|    |                 | 3.3.2   | Asynchronous Dependencies Analysis                            | 81  |

|    |                 | 3.3.3   | Simulation Replay                                             | 85  |

|    |                 | 3.3.4   | Rollback-Based Conflict Recovery                              | 87  |

|    | 3.4             | Genera  | alization to Any Shared Resources                             | 94  |

| 4  | Eval            | luation | n of the Proposed Simulation Technique                        | 97  |

|    | 4.1             | Experi  | imental Setup and Use Cases                                   | 98  |

|    |                 | 4.1.1   | The Host Computer                                             | 98  |

|    |                 | 4.1.2   | Simulated Architecture                                        | 99  |

|    |                 | 4.1.3   | Simulated Software                                            |     |

|    |                 | 4.1.4   | Metrics and Measurement Protocol                              | 102 |

|    | 4.2             | Functi  | onal Validation                                               | 104 |

|    |                 | 4.2.1   | Case Study: the Spinlock-Based Barrier                        | 104 |

|    |                 | 4.2.2   | Experimental Functional Validation                            |     |

|    | 4.3             |         | mance on Baremetal and Linux-Based Use Cases                  |     |

|    |                 | 4.3.1   | Baremetal Performance Evaluation                              |     |

|    |                 | 4.3.2   | Linux Performance Evaluation                                  | 113 |

| 5  | Full            | Softw   | are Stack Simulation Challenges and Solutions                 | 115 |

|    | 5.1             |         | uction                                                        |     |

|    | 5.2             |         | igating the Performance of Linux-Based Benchmark Simulation . |     |

|    | 5.3             |         | equential Mode                                                |     |

|    |                 | 5.3.1   | Region of Interest                                            |     |

|    |                 | 5.3.2   | Variable Accuracy                                             |     |

|    |                 | 5.3.3   | Dynamic Scheduling Policy                                     |     |

|    | 5.4             |         | Mode-Based Unscheduling                                       |     |

|    |                 | 5.4.1   | Conflicts Study                                               |     |

|    |                 | 5.4.2   | Executing OS Kernel Code Sequentially                         |     |

|    | 5.5             | Final S | SCale 2.0 Performance Evaluation                              | 130 |

| Co | onclu           | sion    |                                                               | 135 |

| Bi | ibliography 143 |         |                                                               |     |

## Introduction

This manuscript presents the work that I have conducted at the Commissariat à l'Énergie Atomique et aux Énergies Alternatives (CEA) in Saclay (France) during my Ph.D. thesis. I was a member of the Design Automation & Architecture Laboratory (LECA), a laboratory working in the virtual prototyping field, as well as a member of the Laboratoire de l'Informatique du Parallélisme (LIP) for the University Claude Bernard Lyon 1. My thesis is the sequel of my Projet de Fin d'Études (PFE) — a 6-month internship that concludes masters and engineering degrees — on variable accuracy SystemC simulation. I have carried on my work on this topic during the first months of my thesis and integrated the developed features in the final version of the presented work.

## System on a Chip

Electronic System Level (ESL) design and verification is increasingly challenging due to the soaring complexity of Systems on Chips (SoCs) and time-to-market constraints. An SoC is an advanced electronic component that gathers on a single chip a complete computing system. SoCs are to be found in all places where a conventional computer is not suited like, for instance, automotive, aeronautics & aerospace, smartphones, USB devices or Internet of Things (IoT) devices. All these applications present strong integration constraints with respect, for example, to power consumption, area, real-time features, efficiency, reliability, or even electro-magnetic compatibility.

While a regular computer Central Processing Unit (CPU) is composed of a set of identical processing cores connected to external main memory and peripherals, an SoC embeds on a single chip various regular processing cores (e.g., ARM cortex A7 and A15 in the big.LITTLE architecture), memory, communication modules (e.g., Bluetooth, Wi-Fi and cellular networking), accelerators (e.g., Graphical Processing Unit (GPU) and codecs) or security devices (e.g., secured biometric identification). The only limit to SoC architecture is the manufacturing process used to engrave these Intellectual Properties (IPs) and the complexity that the hardware designer can embrace.

Following the path set by Moore's law, SoCs complexity reaches unprecedented levels year after year. With multi-billion-transistor chips integrated even in entry-level devices, new design techniques must help architects grasp this level of intricacy. Thus,

Electronic Design Automation (EDA) tools strive to enable architects to fully exploit the new possibilities offered by each leap in manufacturing techniques. In that respect, abstraction is the sinews of war. SoCs are now provided with configurable IPs viewed as black boxes which can be dropped in larger designs with minimal effort. This helps significantly reducing hardware design cycles.

However, hardware is only one side of a coin that has the software on the other. Software complexity is growing even faster than hardware complexity with the democratization of multi-core architectures and hardware heterogeneity that brings new challenges to software developers. Also, when power and efficiency requirements get too high, complexity tends to shift to software with the use of simpler hardware like non-coherent cache architectures. As a result, EDA tools must also enable faster and easier software development tools.

## Simulation in The Design Flow

Developing complex software requires systematic testing which in turn necessitates to run this software on the SoC it targets. Waiting for validated hardware to be available before starting software development is not an option, especially considering that hardware development also takes advantage of feedbacks from software teams. As a result, both processes must take place concurrently through the adoption of the hardware and software co-design workflow.

The industry standard solution to that necessity is Virtual Prototyping (VP). It consists in assembling a software model of the SoC under design to build a simulator able to run the software targeting this SoC. For this technique to be viable, VP must fulfill the following requirements:

**Cost:** The Virtual Prototype (VP) must be cheap and fast to develop.

**Speed:** The VP must execute fast enough in order not to slow down the build-test-fix software development cycle.

**Accuracy:** The VP must provide accurate-enough information needed by the software developer in the early development phases.

**Debug:** The VP must provide useful information relative to errors caused by the software under development.

**Repeatability:** Bugs often need to be reproducible to be fixed efficiently.

The Transaction-Level Modeling (TLM) [Ayn09] standard has been developed to fulfill these requirements. It is part of the C++-based SystemC [IEE12] Hardware Description Language (HDL). TLM first enables interoperability, allowing independent actors to provide their IP in the form of a standard black-box model that can be easily

#### **CONTENTS**

integrated into a bigger VP. In a transaction-level model, only components behavior is modeled as opposed to a Register Transfer Level (RTL) model where components internals are also simulated. This difference gives a significant edge to TLM models when it comes to development cost and speed. It also drastically increases simulation speed at the cost of a moderate yet inevitable loss in accuracy (i.e., speed-accuracy trade-off). In addition to the possibility of hooking up a debugger to the simulated processors, all regular C++ debugging techniques can be applied to a TLM model simulation. Finally, a TLM simulation relies on the co-routine semantics enforced by the SystemC standard as for most HDL, thus providing repeatability.

Still, state-of-the-art simulation techniques are now struggling to keep up with modern hardware complexity and simulation speed tends to shrink inexorably. This is a direct consequence of the standard SystemC simulation kernel provided by Accellera [ScR] being single threaded as a direct implementation of co-routines, thus exploiting a single core of the host machine. At a time where computation power increase relies on more and more cores being fitted into a single chip, simulation techniques can no longer rely on single core performance improvement to keep up with the increasing SoC complexity.

### Contributions and Outline Of The Manuscript

This thesis tackles precisely parallel and standard-compliant simulation of TLM models. In particular, parallel simulation must not give up on the co-routine semantics as it would imply harder modeling and potentially non-reproducible bugs. This work especially focuses on a specific type of TLM models: Loosely-Timed models. These are the most abstract but also fastest models by up to two orders of magnitude when compared to the other types of SystemC models (RTL or even Approximately-Timed TLM models). LT-TLM models are particularly challenging to simulate in parallel, which this work strives to achieve.

We propose SCale 2.0, a standard-compliant parallel SystemC kernel that guarantees co-routine semantics preservation and simulation reproducibility as a direct consequence. This work was started after SCale 1.0 [VS16]. We support any TLM model including the Loosely-Timed coding style with the use of the Direct Memory Interface (DMI) protocol. Our technique based on lightweight shared-resources access monitoring has a limited overhead even when used with the fastest Instruction Set Simulators (ISS's) available.

This manuscript is organized as follows: Chapter 1 lays down the bases necessary to understanding the present work: concurrency and parallelism concepts, parallel programming challenges and SystemC simulation principles.

Chapter 2 exposes the challenges of parallel SystemC simulation and the existing solutions described in the literature. In particular, SCale 1.0, the starting point of the present work is introduced in detail in this chapter.

Chapter 3 exposes the core mechanisms implemented in SCale 2.0 that have been published at ASP-DAC 2020 conference in [BSV<sup>+</sup>20]. These mechanisms include: a lightweight FSM-based shared-resources access granting policy that prevents most process atomicity violations during parallel evaluation; a fast and highly scalable data-structure for FSM instances storage; a general process-level rollback system to recover from process atomicity violations; and a deterministic simulation replay mechanism for bug reproduction.

Chapter 4 describes the experimental setup including the host platform, the simulated platform, the functional validation benchmark, and the performance benchmarks. Experimental results are then analyzed: baremetal benchmarks show very good scaling on a 36-core host but Linux-based benchmark are not efficiently supported at that point.

Consequently, Chapter 5 further analysis the challenges brought by the simulation of complex guest OS simulation and introduces additional solutions including: a variable accuracy system coupled with adaptive parallel/sequential evaluation for simulation fast-forwarding; and a simulated-CPU-mode-based process scheduling algorithm for improved conflict avoidance before giving the final experimental results. The solutions and results presented in this chapter have been submitted to the ASP-DAC 2020 journal and are under second review.

# Chapter 1

# Parallel Computing and SystemC Simulation Background

| 1.1 | Introd                                   | luction                                               | 18 |

|-----|------------------------------------------|-------------------------------------------------------|----|

| 1.2 | Concu                                    | urrency and Parallelism                               | 18 |

|     | 1.2.1                                    | Concurrency                                           | 18 |

|     | 1.2.2                                    | Fine-Grained Control Over Concurrency with Coroutines | 19 |

|     | 1.2.3                                    | Parallelism                                           | 2  |

|     | 1.2.4                                    | Enabling Parallel Computation with Threads            | 23 |

| 1.3 | SystemC Modeling and Simulation Overview |                                                       |    |

|     | 1.3.1                                    | Virtual Prototyping in the SoC Design Flow            | 26 |

|     | 1.3.2                                    | The SystemC Modeling Language                         | 27 |

|     | 1.3.3                                    | Discrete Event Simulation of SystemC Models           | 29 |

| 1.4 | TLM-                                     | 2.0                                                   | 33 |

|     | 1.4.1                                    | TLM: Abstraction of the Communication Layer           | 33 |

|     | 1.4.2                                    | Coding Styles in TLM                                  | 34 |

#### 1.1 Introduction

In this chapter, concepts that are necessary to the understanding of the rest of the manuscript are exposed. The primary goal is to illustrate these concepts and to help build an intuition of them. This chapter does not aim at being an exhaustive lecture on these topic but instead attempts to hide the complexity of some aspects of these topics when possible.

First, the general concepts of concurrency and parallelism as used in this document are explained: what are they, what are their similarities but above all, what makes them different and often incompatible? An algorithmic approach is first used to introduce these concepts before presenting how they can be used when programming actual applications. Then the SystemC HDL is introduced through the industrial needs that motivate its use. Next, the fundamentals of SystemC are exposed through a simple RTL use case. Modules, ports, channels, processes, and simulation kernel are defined at that point. Finally, the TLM level of abstraction, the target of this work, is explained as well as DMI and the global quantum, two standard acceleration techniques that we strive to support with our parallel SystemC simulation kernel.

### 1.2 Concurrency and Parallelism

Concurrency and parallelism are two closely related concepts yet very different. This section aims at defining and differentiating them to better understand the standard SystemC mechanisms and the contribution of this thesis: SystemC parallelization. It should be noticed that SystemC-specific concepts are not used in this section.

### 1.2.1 Concurrency

In this section, we define a *process*<sup>1</sup> as a succession of related instructions being executed. In the context of computer science, a process consists in a processor fetching and executing coded instructions (e.g., x86 or ARMv8 [Int19; ARM20]) often located in memory to perform the corresponding register manipulations and memory accesses.

It is often assumed that a process is executed *in isolation*, that is without interacting with other processes. As a result, when a process reads several times a given memory location without writing to it in between, it can expect to read the same value again and again. On the opposite, if a process is not running in isolation, unexpected state mutations (e.g., register content modification) can compromise the process validity.

One such case where processes no longer are in isolation occurs when several processes run *concurrently*, that is if they are *in progress* simultaneously. Formally, with process A (respectively process B) executing during the time interval  $T_A$  (respectively  $T_B$ ), then A and B are concurrent if and only if  $T_A \cap T_B \neq \emptyset$ . In particular, if two

<sup>&</sup>lt;sup>1</sup>Process is not used in the sens of a SystemC process in this section.

processes A and B are running concurrently, it does not imply that A and B are doing progress simultaneously at any time. As a result, concurrency can be achieved on singlecore processors by doing process multiplexing, that is by executing several processes alternately, each for a small period of time.

In practice, concurrency can be observed at many places in a conventional computer system. At the Operating System (OS) level, thousands of processes can coexist simultaneously. One of the major OS roles is then to keep all of these processes isolated from each other while letting them share the available processing time as fairly as possible. At the program level, the developer can exploit the concurrency capabilities of its system and language to implement control flows that rely on multiple call stacks as detailed in Section 1.2.2. At the hardware level, multiple processing units can execute multiple processes concurrently and even simultaneously as developed in Section 1.2.3.

# 1.2.2 Fine-Grained Control Over Concurrency with Coroutines

Concurrency can be exploited and controlled at the program level using *coroutines* to implement *cooperative multi-tasking*. A coroutine is an independent control flow (i.e. an execution stack) that is resumed and suspended by the application programmer. In each thread, these control flows are active one at a time as they get suspended and resumed by the programmer. When a coroutine suspends itself, it is said that it *yields*.

Coroutines effectively allow a program to be composed of multiple tasks interacting with each-other in a cooperative manner, that is, all tasks are aware of what each other do and of when they do it. Because a coroutine has its own call stack, that is its own context of execution, the terms *context* and *coroutine* can often be substituted.

Coroutine usage is illustrated by Algorithms 1 and 2 describe two different implementations of the Fibonacci sequence generation. The goal is to generate the numbers of the Fibonacci sequence one at a time and to print each value before generating the next: the values cannot be stored in an array before being all printed at once, that is the values generation and printing must happen concurrently. We also assume that the Fibonacci sequence generator is provided by an external source, which means that the printing cannot be inserted in the middle of the Fibonacci generation function. Such apparently artificial constraints are representative of typical SystemC use cases: several complex IP models provided by various vendors as black boxes and assembled together by the end user.

In Algorithm 1, the generator is a classic function that returns a value and takes no argument. It implies that a specific mechanism is needed to memorize the last computed value in order not to return the same value over and over. Here, two values of the Fibonacci sequence are memorized instead of one to speedup the computation of the next value. The printing function is then responsible for printing the successive values returned by the generator.

On the opposite, in Algorithm 2, the generator function does not need to specify what data needs to be persistent as it never returns, and its stack frame is never cleared. Instead, it stores the successive computed values in a global buffer accessible to the printing coroutine. Once a new value is computed, the generator *self-suspends* to pass control to the printing loop which later also self-suspends to pass control back to the generator, and so on.

**Algorithm 1** Iterative computation of the n first values of the Fibonacci sequence

```

1: procedure PRINT(n)

for i in [0..n] do

print(FIBONACCIGENERATOR())

3:

4:

end for

5: end procedure

6: procedure fibonacciGenerator

static fib0 = 0

▶ Local persistent state

7:

static fib1 = 1

▶ Local persistent state

8:

ret = fib0

9:

next = fib0 + fib1

10:

11:

fib0 = fib1

fib1 = next

12:

return ret

13:

14: end procedure

```

# **Algorithm 2** Coroutine-based computation of the n first values of the Fibonacci sequence

```

1: fib = 0

▶ Global state shared by all coroutines

2: procedure PRINT(n)

for i in [0..n] do

3:

print(fib)

4:

resume fibonacciGenerator

5:

end for

6:

7: end procedure

procedure FIBONACCIGENERATOR

▶ Runs in a dedicated coroutine

8:

fib1 = 1

9:

while true do

10:

next = fib + fib1

11:

fib = fib1

▷ Set global variable to pass the new computed value

12:

fib1 = next

13:

resume PRINT

14:

15:

end while

16: end procedure

```

In that simple example, the coroutine based version seems needlessly complex but it quickly takes the advantage when the persistent state gets more complex, for instance,

in the presence of a lot of data or when the suspend and resume points can change. Without co-routines, the entire state of each task needs to be explicitly saved and restored each time the task suspends and resumes, which is cumbersome, error prone and less flexible. Therefore, coroutines are well suited to programs where several mostly unrelated complex tasks need to run concurrently. Coroutines are typically used in graphical user interface engines. Hardware modeling happens to fall right under this category and SystemC, as most hardware modeling languages, relies on coroutines to model hardware behavior as detailed in Section 1.3.

However, while coroutines are well suited to program concurrent tasks, they are often bad candidates for parallel execution as they specifically expect to run in alternance with one another but never in parallel. The next sections explain what parallelism is, how it is achieved on regular computers and why it does not combine well with coroutines.

#### 1.2.3 Parallelism

While concurrency describes several tasks *in progress* at the same time, parallelism describes several tasks *doing progress* at the same time.

Despite being semantically close, parallelization sets strong additional constraints on the tasks involved. Indeed, with cooperative multitasking, coroutines suspend and resume at deterministic points in the program, making all interactions happen in a well-defined and easily predictable order. When enabling parallelism between tasks, they will inevitably desynchronize without the programmer introducing extra synchronization. In other words, the tasks will progress at different speeds and interactions will happen in an undefined and unpredictable order. When the order of a sequence of interactions between several parallel tasks is not well defined and can cause variations in the program output, this is called a *race condition*.

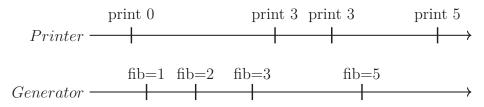

Race conditions sometimes have no impact on the validity of the program but can also compromise it, as in Algorithm 3. Here, the printing loop is running while the Fibonacci generator loop computes the successive values of the Fibonacci sequence. Unless the printing loop iterates at exactly the same speed as the generator loop, they will desynchronize, and the printed values will not be those of the Fibonacci sequence like on the example Figure 1.1.

**Figure 1.1** – Possible interleaving when executing the printing and the Fibonacci generator loops in parallel without synchronization like in Algorithm 3.

**Algorithm 3** Parallel computation and printing of the n first values of the Fibonacci sequence with race conditions

```

1: fib = 0

2: Start Print and fibonacciGenerator in parallel

3: procedure PRINT(n)

for i in [0..n] do

4:

print(fib)

5:

end for

6:

7: end procedure

8: procedure fibonacciGenerator

fib1 = 1

9:

while true do

10:

next = fib + fib1

11.

fib = fib1

12:

fib1 = next

13:

end while

14:

15: end procedure

```

In order for tasks to run in parallel and interact in a well-defined manner, synchronization must be added by the programmer. Synchronization can take several forms like:

- 1. waiting: A task waits for one or more tasks to complete some specific operations before continuing. Mutual exclusion, barriers or condition variables are common primitives used to wait for various types of events.

- 2. atomic operations: the state on which an atomic operation is performed can either be observed before the operation starts or after it finishes but never while it is happening. Atomic instructions like compare-and-swap or transactional memories [HLR10] enable atomic operations on memory.

In Algorithm 3, additional synchronization is required. A simple approach implemented in Listing 1 would be for example to add a flag specifying if the generator is allowed to write fib, the only shared variable: if the flag is true, the generator is allowed to write to fib but the printer cannot read it safely and vice versa if the flag is false. Both tasks then wait for the flag to have the appropriate value before doing an access to fib and flips it once done before continuing to release the other task. In that case, the generator can compute the next value while the printer prints the current one and only needs to wait before updating fib. The program is now not only concurrent but also parallel.

Parallelizing a program in practice however involves several technicalities at the software and hardware level that are introduced in the next section.

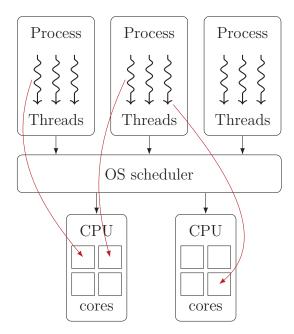

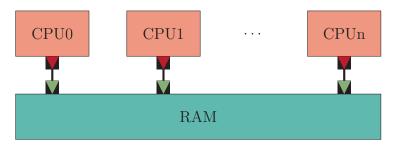

**Figure 1.2** – Organization of a multi-core dual-socket system executing multithreaded processes

#### 1.2.4 Enabling Parallel Computation with Threads

The notion of thread starts at the language level and percolates down to the hardware layer through the operating systems as illustrated in Figure 1.2. While the semantics of a thread is completely defined at the programming language level, the performance of a multi-threaded program is conditioned by the hardware behavior. This section describes the most important of these aspects regarding the developments of this work.

#### Threads at the Language Level

Threads of execution are the fundamental concept behind parallel programming. As a coroutine, a thread is an independent control flow in an application but as opposed to a coroutine, threads *can* execute simultaneously. A program that makes use of multiple threads is said to be multithreaded.

In order to program a multithreaded application, the language must first provide the thread construct either natively or via a library. For instance, in C++11 [C] or later, a thread can be spawned using the std::thread class. The Listing 1 is a parallel C++ implementation of Algorithm 3 with a flag used to order the accesses to fib done by each thread.

Functions fibonacciGenerator and print are both called in a dedicated thread at lines 28 and 30. The generator thread is then *detached*, that is it becomes independent from the main thread. It allows the program to exit normally without waiting for the generator thread to finish as it will never finish. The printer thread is *joined*, that is the main thread waits for it to finish (i.e., the print function returns) before proceeding

**Listing 1** C++ parallel implementation of the printing of the Fibonacci sequence.

```

#include <thread>

#include <atomic>

#include <iostream>

3

4

int fib = 0;

5

std::atomic_bool write_fib(false);

6

7

void print(int n){

8

for(int i = 0 ; i < n ; ++i){

9

while(write_fib){} // Wait

10

std::cout << fib << std::endl;</pre>

11

write fib = !write fib; // Let the generator resume

12

}

13

}

14

15

void fibonacciGenerator(){

int fib1 = 1;

16

while(true){

17

int next = fib + fib1;

18

int next1 = fib1;

19

fib1 = next;

20

while(!write fib){} // Wait

fib = next1;

22

write_fib = !write_fib; // Let the printer resume

23

}

24

}

25

int main(){

26

// Start the generator and let it run independently

27

std::thread(fibonacciGenerator).detach();

28

// Start the printer and wait for it to finish

29

std::thread(print, 8).join();

30

}

31

```

to the end of the program.

It can be noticed that the write\_fib flag is of type std::atomic\_bool instead of bool. This is mandatory to avoid data races, that is concurrent accesses to a same memory location with at least one write. A data race would here occur between lines 11 and 22: the printer reads fib and the generator writes to it. Another data race would also occur on the write\_fib flag itself. Defining the flag as an atomic boolean instead of a regular boolean solves the issue by constraining the order of execution of the program statements surrounding the atomic memory accesses. Incidentally, when defining write\_fib as a regular bool instead, depending on the optimization level and

on whether gcc or clang is used to compile the program, the printer thread will either print the Fibonacci sequence, print only zeros or fall into an infinite empty loop. This is the result of a data race making the program ill-formed, which basically lets the compiler produce whatever behavior it wants.

Atomic variables are the first step toward the complex and sometimes remarkably counter intuitive C++ memory model defined starting from version 11 upwards. Some brief incursions into the C++ memory model will be required to demonstrate some key aspects of the contributions of this thesis like in Section 3.2.2. Without getting into details, a memory model describes the semantics of memory accesses: it constrains how memory accesses can be reordered and in which order memory writes should appear to the other threads. Indeed, all CPU — or more accurately all Instruction Set Architectures (ISA's) — have their own memory model according to which instructions and specifically memory accesses can be reordered. Fortunately, as long as the program is well defined and the compiler is standard-compliant, the programmer does not need to think about the CPU memory model but only to the (usually simpler) language memory model.

#### Threads at the System Level

Threads at the program level are supported at the OS level using OS threads. OS threads are basically what the OS scheduler can manage. When a thread is spawned in a process, it leads to the creation of an OS thread that can be scheduled independently from other threads. As a result, all threads become independent tasks executed whenever the OS scheduler decides to. While the scheduler strives to be fair amongst all threads, significant execution time variations between threads can still be observed.

At the hardware level, OS threads are executed by the CPU, specifically, one CPU core can execute one thread at a time<sup>2</sup>. The OS scheduler then decides which thread is executed by which core at what time.

Now that everything is setup to program and run multithreaded parallel applications, one should wonder whether it will be faster than its equivalent sequential version. The answer is far from being always yes. Several algorithmic and hardware considerations can make a parallel program slower than its sequential counterpart, among them being:

- Overloading the CPU by spawning many more active threads than there are available cores will result in numerous context switches as a result of the OS scheduler attempting to be fair to all threads.

- Poorly decoupled threads, i.e., threads that constantly wait for each other.

- Frequent non-read-only data sharing causing systematic cache line invalidation on coherent architectures like all mainstream computers.

<sup>&</sup>lt;sup>2</sup>Simultaneous MultiThreading (SMT) can raise this limit to 2 or more

- False sharing, that is two or more pieces of data that are not shared between several threads but happen to live in the same cache line<sup>3</sup>, causing frequent cache line invalidation despite no data being shared in the program.

- Use of inappropriate synchronization primitives.

- Non-Uniform Memory Access (NUMA), which describes a configuration where some memory locations are slower to access than others depending on the core being considered.

- SMT where all logical cores mapped onto the same physical core must share most of its resources. Thus, scheduling two threads on the same core is often not advisable for best performance.

Luckily, the OS scheduler is usually decent enough at dealing with NUMA and SMT to dispense the programmer from thinking about it. The rest is left to the programmer and has been carefully refined in the present work in order for the proposed parallel SystemC kernel to be faster than the sequential reference version.

## 1.3 SystemC Modeling and Simulation Overview

Now that the general computer science notions useful to the understanding of SystemC and its parallelization are laid down, this section explains the fundamental concepts of SystemC and TLM-2.0 modeling and simulation, as well as their role in the SoC industry.

### 1.3.1 Virtual Prototyping in the SoC Design Flow

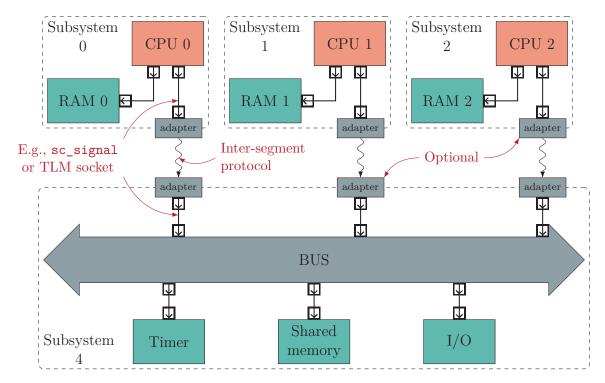

An SoC is an integrated circuit that gathers on a single chip one or more processing units, memory and optionally a GPU, external communication modules and various accelerators. The electronic design industry refers to these components as IPs that are interconnected with either a bus or more recently a Network on a Chip (NoC). SoCs are most often tailored to specific applications requiring various sets of features from computing power to wireless communication capabilities including security, efficient codec decoding or other specialized data processing. In addition, the SoC design industry is increasingly competitive with rapidly evolving technologies and needs. The ability to design an SoC in a reduced amount of time is key to fulfill the ever-tighter time-to-market constraints: typically, a new high-end smartphone chip is released every year with strong timing constraints involving huge market shares.

Designing a new SoC involves two major tasks: the hardware design and validation and the software development. These two tasks are strongly interdependent: the software needs the hardware to be developed and tested and the hardware can require an

$<sup>^3</sup>$ Even two adjacent cache lines can cause false sharing on Intel processors for instance.

upgrade if, for instance, the performance of the software cannot meet the requirements on a given hardware.

In order for software to be developed independently from hardware availability, the industry relies on VP. A VP is a software model of the hardware under development able to run the software targeting this hardware. Thanks to VP, the hardware design and software development are decoupled and can happen simultaneously in a process called hardware/software co-design, cutting down on the overall SoC design cycle duration.

However, for a VP to be profitable, it must be fast to develop. This is achieved mostly through IP model reuse. Most IP vendors license there products together with models that can be used to develop VPs. But for models to be compatible with each other out of the box, they must conform to a same standard. One of them is SystemC/TLM-2 [IEE12; Ayn09], a C++ based hardware modeling library and simulation engine. SystemC/TLM-2 offers a collection of constructs suitable for hardware modeling. But more importantly, it specifies the interfaces that IP models must expose so that they can integrate conveniently and reliably with other models inside full SoC models.

Also, VPs must run fast enough not to slow down the *build-test-fix* software development cycle. The main variable of adjustment is the speed-accuracy trade-off: the more details are simulated, the slower the simulation. This thesis aims at providing solutions to accelerate simulations without sacrificing accuracy.

#### 1.3.2 The SystemC Modeling Language

SystemC is a C++-based HDL standardized in 2005 as IEEE Std 1666<sup>TM</sup>-2005 and updated in 2011 as IEEE Std 1666<sup>TM</sup>-2011 [IEE12]. It initially aimed at competing with other HDL such as VHDL [VHD97] or Verilog [Ver91]. It quickly became a popular VP tool by enabling system-level modeling at various and possibly mixed levels of abstraction ranging from cycle-accurate-bit-accurate to loosely-timed TLM and including RTL. This thesis being focused on TLM model simulation, RTL models will only be used in this section to illustrate the general principles of SystemC modeling and simulation.

An SoC is composed of hierarchical hardware blocks that communicate together through various communication channels such a wires, buses or NoCs. SystemC being based on the object-oriented language C++, such modular hardware design naturally translates into class-based modeling. A collection of SystemC classes provide the basic interfaces and features to model each building block of an SoC:

- sc module is the base class for all hardware blocks.

- sc\_port and sc\_export are the base classes for block ports, that is interfaces for sc modules to connect to the outer world.

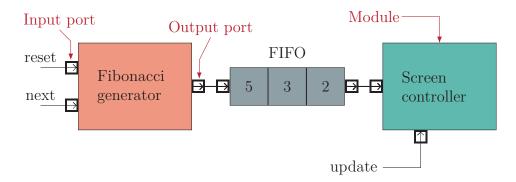

**Figure 1.3** – A simple SystemC model of a hardware implementation of Algorithm 2 with the addition of the control signals reset, next and update.

• sc\_prim\_channel and sc\_channel are the base classes for communication channels between blocks and are meant to connect instances of sc\_port and/or sc\_export together.

A variety of specializations of these classes are provided to model the most common type of components. For instance, sc\_in, sc\_out and sc\_inout are specialization of sc\_port that provide specialized interfaces used to read and/or write from/to a channel. Also, sc\_signal models a simple wire and sc\_fifo models a fixed capacity queue. Both are specializations of sc\_prim\_channel and can carry a wide variety of data types thanks to template parameterization<sup>4</sup>.

The aforementioned classes allow to describe the architecture of a design. The internal logic of the components can then be defined using SystemC processes. Processes are special methods in the sc\_module they belong to. A process can then access and modify all the data contained in its sc\_module just as a regular method can. SystemC processes can be of two kinds:

- SC\_METHOD: A process that always runs from start to end without persistent context from an execution to the next (i.e., a regular function).

- SC\_THREAD: A process with persistent context that can suspend and resume (i.e., a coroutine). SC\_THREAD processes present a slight memory and speed overhead over SC\_METHOD.

To illustrate these concepts, the Fibonacci sequence generator and printer example is modeled in Figure 1.3 using a seven-segment display controller as a printer. If there is some room left in the FIFO and the next signal rises, the generator computes a new value and stores it in the FIFO. The display controller fetches a new value from the FIFO whenever the update signal rises and the fifo is not empty. The Fibonacci

$<sup>^4</sup>$ Specific requirements can be imposed on the types used as template arguments like being trivially copiable.

generator module is connected to the reset and next signal using two input ports. Its output port is connected to the head of the FIFO channel whose tail is connected to an input port on the display controller. The display controller also has an input port used to trigger an update of the screen.

The generator behavior must be implemented as an SC\_THREAD to preserve the context from one iteration to the next, just as in the Algorithm 2. The display controller only requires an SC\_METHOD sensitive to the update signal as it only fetches data from the FIFO and computes the command of the display.

The next section will now describe when and how the processes in a SystemC simulation are executed to simulate the behavior of a real hardware system.

#### 1.3.3 Discrete Event Simulation of SystemC Models

Just as with most HDL, a SystemC model can be simulated using Discrete Event Simulation (DES) [Nan93]. DES models a system as a succession of events occurring at discrete successive time points. As a broad outline, the simulator advances time to the next closest scheduled event and runs the processes *sensitive* to this event in a sequential fashion. These processes may then schedule new events to occur in the future. This sequence repeats until the end time is reached or no more events are scheduled.

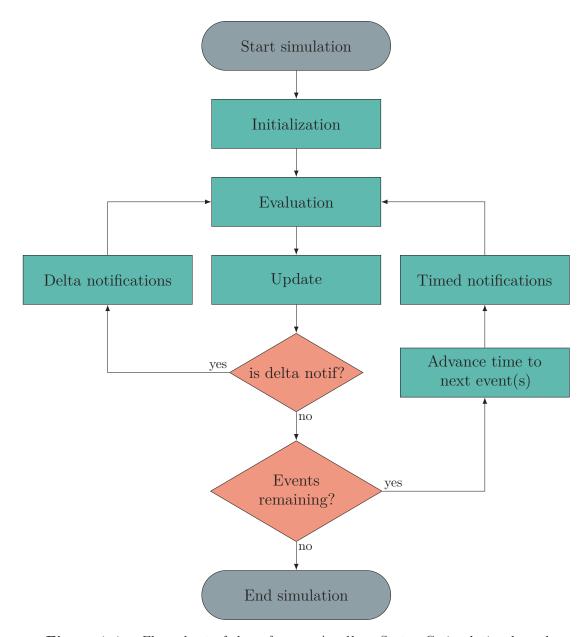

SystemC applies this scheme following the execution flow chart Figure 1.4. The platform is first initialized by running all processes once and then starts the main simulation loop. It is composed of these three steps:

- 1. The evaluation phase: all runnable processes are evaluated in a sequential unspecified order. Please note that though unspecified the order is deterministic for a given SystemC kernel with a given SystemC model to ensure reproducible simulation

- 2. The *update phase*: when accessing an sc\_prim\_channel like an sc\_signal during the evaluation phase, any modification of the state of the channel is postponed to the following update phase. That way, the visible state of all channels is immutable during each evaluation phase.

- 3. The delta or timed notification phase: the earliest notification time (which is the current time in case of a delta notification) is computed and the corresponding events are triggered, making the sensitive processes runnable during the next evaluation phase.

Processes can be made sensitive to an event either using *static sensitivity* or *dynamic sensitivity*. Static sensitivity is defined during the initialization of the platform using the sensitive SystemC command right after declaring a process. Also, an SC\_METHOD

Figure 1.4 – Flow chart of the reference Accellera SystemC simulation kernel.

(resp. an SC\_THREAD) can be made dynamically sensitive to an event by calling next\_trigger() (resp. wait()) with an event and/or a delay as parameters. For instance, in Figure 1.3, the generator SC\_THREAD is statically sensitive to a rising edge on the reset signal and on the next signal and the display controller SC\_METHOD is statically sensitive to a rising edge on the update signal.

Let us now assume that we want to simulate the time required for the generator to compute a new value and for the controller to convert an input into a command. In DES, processes evaluation always takes place in a null simulated time. Thus, the simulation accounts for the duration of the simulated tasks between processes evaluation, during the timed notification phase. This is achieved by adding timing information in the processes in the form of wait(time) or next\_trigger(time) statements. These statements will trigger the continuation of the process evaluation after the timing statement.

A complete SystemC model of the generator in the example Figure 1.3 could then be like on Listing 2. It can be noticed that genThread is registered as an SC\_THREAD and thus is executed as a coroutine with a persistent state (fib0 and fib1 in that case). The events triggered by a rising edge of reset or next are registered in the static sensitivity list of the genThread process in the constructor. The time taken by either the reset or the next value computation is accounted for by calling wait(sc\_time) with the desired amount of time before calling wait() without arguments to wait for an input signal rising edge.

Though, modeling at this level of abstraction (RTL) is time consuming and simulations are very slow at a few thousand simulated instructions per second for full system simulation. For fast virtual prototyping and (much) higher simulation speed, the TLM level of abstraction is a better choice.

#### Listing 2 SystemC model of the Fibonacci sequence generator.

```

#include <systemc>

using namespace sc_core;

// Macro for sc_module definition

SC_MODULE(fibo_gen){

sc_in<bool> reset, next;

6

7

sc_out<int> out;

8

void genThread(){

9

// Initialization

10

int fib0 = 0, fib1 = 1;

11

wait();

12

13

// Infinite loop

for(;;){

14

if(reset){

fib0 = 0;

16

fib1 = 1;

17

// Account for reset duration (2ns)

18

wait(sc_time(2, SC_NS));

19

} else if(next) {

20

out = fib0;

21

int fib2 = fib1 + fib0;

22

fib0 = fib1;

23

fib1 = fib2;

24

// Account for computation duration (10ns)

wait(sc_time(10, SC_NS));

26

}

27

wait(); // wait for reset or next signal

28

}

29

30

// Macro for sc_module constructor declaration

31

SC_CTOR(fibo_gen){

32

// Register genThread as an SC_THREAD

33

SC_THREAD(genThread);

34

// Register reset and next rising edges in

35

// the static sensitivity list of genThread

sensitive << reset.pos() << next.pos();</pre>

}

38

};

39

```

#### 1.4 TLM-2.0

TLM-2.0 [Ayn09] (which will now be referred to as TLM) is a standard built on top of SystemC and released in 2008. It provides an interoperability layer together with utility features to facilitate model development and improve cross compatibility for model reuse. The main goal of TLM is to speed up VP development and simulation speed of memory-mapped bus-based platforms. The present manuscript describes a new parallelization technique targeted at the loosely-timed TLM models.

#### 1.4.1 TLM: Abstraction of the Communication Layer

TLM introduces new constructs for communication modeling. While in classic SystemC, communication between models usually involves signals and protocol simulation, TLM communications rely on interface method calls. When in classic SystemC a module writes data on a channel in order for the module on the other end to receive this data, a TLM-enabled module sends data to another module calling an interface method directly exposed by the targeted module.

This form of memory access simulation is referred to as a *transaction*. It consists in the transmission of a data structure called the *payload* that packs together all the information needed to describe a memory access request. It includes (among other things) the type of memory access (read or write), the targeted address, the length of the access, the status of the transaction and the data being either read or written.

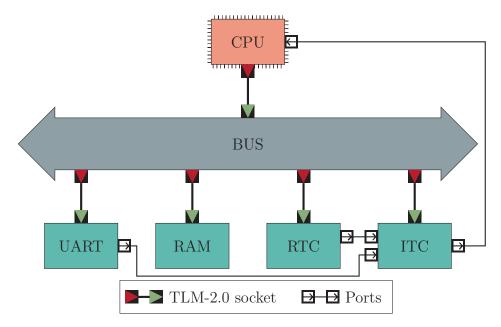

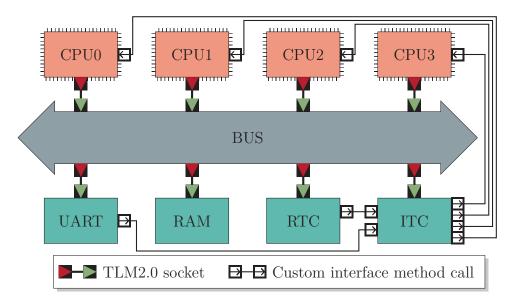

A simple TLM model is illustrated in Figure 1.5. Three types of modules can be

**Figure 1.5** – A basic platform modeled at the TLM abstraction level. A single CPU is connected to a RAM memory, a UART, a real time clock and an interrupt controller. Address based communications rely on TLM while interrupt signals use regular ports and channels.

distinguished on this example:

- Initiator: a module that actively initiates transactions targeted at other modules. A processor is a typical example of initiator.

- Target: a module that passively responds to transactions initiated by other modules. Memories, peripherals, and coprocessors are often target modules.

- Interconnect: a module that transmits transactions initiated and targeted by and to other modules. Buses and NoCs are classic interconnects.

In order for modules to be compatible with each other, the TLM standard defines a set of standard interfaces called *sockets*. An initiator module exposes *initiator sockets*, a target module exposes *target sockets*, and an interconnect exposes both target and initiator sockets.

As a result, a TLM transaction consists in a generic payload being passed from a module to the next through a succession of interface method calls. Each module on the path of a transaction can alter the payload according to its intended behavior. Once the payload has reached its target, it follows the backward path to the initiator and each module can check and update the transaction status.

#### 1.4.2 Coding Styles in TLM

TLM defines two coding styles: approximately timed (TLM-AT) and loosely timed (TLM-LT). The former provides greater timing accuracy at the cost of a slower simulation speed. On the opposite, the later gives access to several standard acceleration techniques like the global quantum and the DMI. Both techniques provide consequent speedup at the cost of a coarser grain timing. The coding styles defined in the TLM standard are only guidelines that the user is strongly encouraged to use. They enforce no specific modeling rules. It is however assumed that these guidelines are followed by the user in the rest of this manuscript.

This work focuses on TLM-LT as it provides the greatest base speed. However, TLM-AT will also be presented as many of the work introduced in Chapter 2 target the TLM-AT coding style.

#### TLM-AT

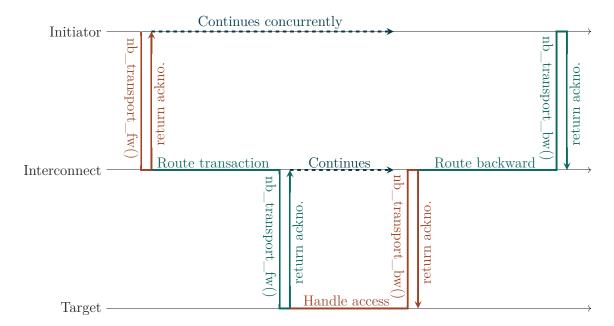

Let us begin with the most accurate but also most complex coding style: TLM-AT. Using the TLM-AT coding style, transactions can be split into several phases to better represent the real communication protocol and timing of the simulated system. In particular, the query and answer phases of a transaction, called *forward* and *backward* paths, are modeled in two distinct steps. Two different socket interfaces are used for the two phases of a transaction: nb\_transport\_fw (for non-blocking transport forward) of

**Figure 1.6** – Chronogram of a non-blocking transaction from initiator to target routed through interconnect.

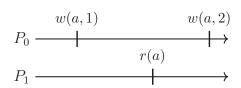

target sockets and nb\_transport\_bw (for non-blocking transport backward) of initiator sockets. Such transactions are said to be *non-blocking* as an initiator does not have to wait for a transaction to complete to continue.

A TLM-AT transaction would then follow the lines in Figure 1.6: The initiator starts the transaction using the nb\_transport\_fw interface of the interconnect target socket. The interconnect acknowledges the transaction to the initiator which can then continue to run concurrently. In the meantime, the interconnect routes the payload to the target following the same protocol. Once the target has processed the request, it calls the nb\_transport\_bw of the interconnect and the transaction is routed back to the initiator similarly to the way it got to the target in the first place. After every step of the transaction, i.e., roughly after every acknowledgment, the corresponding simulation time required can be consumed by calling wait(). It is important to note that the transaction is handed over from a process to the next by transferring the payload. It allows each process to continue running concurrently to the transaction, thus better representing the real hardware concurrency.

This coding style allows for modeling complex phenomenons such as interconnect contention but limits the simulation speed to only a few Million Simulated Instructions Per Second (MIPS). Also, the complexity of TLM-AT models makes them a rather unusual choices for VP as ease of development is a key feature.

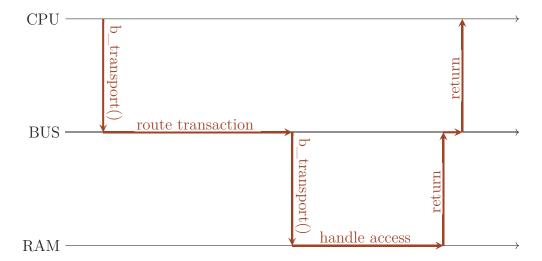

**Figure 1.7** – Chronogram of a blocking transaction from CPU to RAM routed through BUS in Figure 1.5.

#### TLM-LT

When using the TLM-LT coding style, a process is allowed to perform several operations and account for the total amount of time they took with a single call to wait(). For instance, a complete memory access can be simulated in a single evaluation phase. This helps reducing the number of context switches between processes to accelerate the simulation.

In TLM-LT, transactions are said to be *blocking* and thus use the b\_transport (for blocking transport) target socket interface. Blocking means that a transaction completes in a single function call and a single evaluation phase. As a result, interconnect and target modules are not allowed to call wait() and the entire transaction is executed in the context of the initiator process.

In order to account for the simulated processing time of the various modules on the path of a blocking transaction, a delay variable follows the payload and is updated at every step of the transaction. On the example Figure 1.5, if the CPU performs a blocking transaction toward the RAM, the access will be simulated according to the chronogram Figure 1.7.

#### **Direct Memory Interface**

TLM enables DMI accesses. It consists for an initiator to directly access the underlying memory buffer of a target. This protocol is exclusively used for memory components as their only function is to store data in a buffer. It is also much more common in combination with the TLM-LT coding style as it would seriously degrade TLM-AT timing accuracy.

In order for an initiator to access a target with DMI, the target must first provide

a pointer to its internal memory buffer. An initiator knows if a target supports DMI by looking at the *DMI hint* field in the payload after completing a transaction. If the target supports DMI, it should have set it to true. The initiator can then query the DMI pointer by sending a specific request to the target using the <code>get\_direct\_mem\_ptr</code> target socket interface. The initiator can finally access the memory of the target as a classic C-style array. A rough access time estimation also provided by the target can be used to preserve decent timing accuracy when using DMI.

A target module can revoke DMI permissions by calling the initiator socket interface called invalidate\_direct\_mem\_ptr. It can happen in case the target configuration has changed or if the target is an accelerator only providing DMI between computational phases for instance.

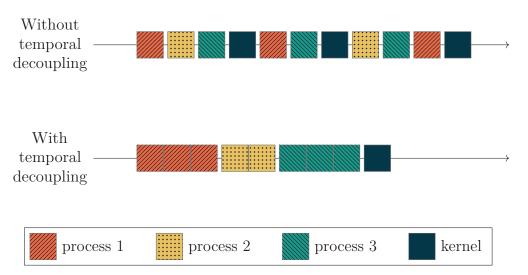

#### Temporal Decoupling

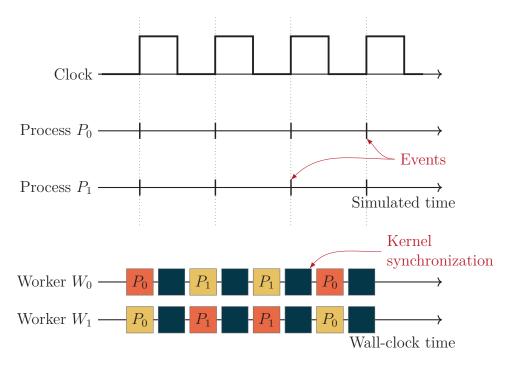

Temporal decoupling<sup>5</sup> is the last standard feature of TLM that aims at speeding up simulations. It is also reserved to the TLM-LT coding style as it favors speed against timing accuracy, too. It allows an initiator to run ahead of global simulation time by a certain amount of time called the *global quantum*.

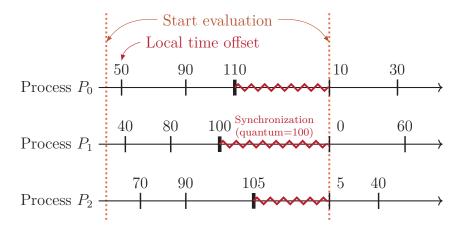

Temporal decoupling is illustrated Figure 1.8. Without temporal decoupling, all three initiator processes are evaluated alternately for short periods of time usually corresponding to a single transaction. It results in numerous context switches between processes but also with the SystemC simulation kernel. On the contrary, with temporal decoupling, each initiator process evaluates for much longer periods of time (typically 100 to 10.000 times longer depending on the quantum and average transaction durations) until their local time gets greater than the global quantum.

As a result, the number of context switches is reduced by several orders of magnitude which provides consequent speedups. Combined with DMI, simulation speed can reach hundreds of MIPS.

$<sup>^5</sup>$ Not to be confused with *time decoupling* which relates to Parallel Discrete Event Simulation (PDES) as explained in Chapter 2

**Figure 1.8** – Illustration of the effect of temporal decoupling on a three process simulation. Context switches happen at every color change and are symbolized by a small gap. Simulation time is only updated during kernel phases.

### Chapter 2

## Parallel SystemC Simulation: Challenges and Existing Solutions

| 2.1 | Parallel SystemC-TLM Simulation: Problem Statement |                                                         |  |  |  |

|-----|----------------------------------------------------|---------------------------------------------------------|--|--|--|

|     | 2.1.1                                              | SystemC Acceleration Strategies                         |  |  |  |

|     | 2.1.2                                              | Parallelizing SystemC                                   |  |  |  |

| 2.2 | Existing Approaches                                |                                                         |  |  |  |

|     | 2.2.1                                              | Synchronous SystemC Parallelization                     |  |  |  |

|     | 2.2.2                                              | Time Decoupling                                         |  |  |  |

|     |                                                    | SCale 1.0: Runtime Processes Interactions Monitoring 55 |  |  |  |

# 2.1 Parallel SystemC-TLM Simulation: Problem Statement

#### 2.1.1 SystemC Acceleration Strategies